(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5730332号

(P5730332)

(45) 発行日 平成27年6月10日(2015.6.10)

(24) 登録日 平成27年4月17日(2015.4.17)

(51) Int.Cl.

F 1

|             |           |      |       |      |

|-------------|-----------|------|-------|------|

| HO1L 21/338 | (2006.01) | HO1L | 29/80 | H    |

| HO1L 29/778 | (2006.01) | HO1L | 29/78 | 617V |

| HO1L 29/812 | (2006.01) | HO1L | 29/78 | 617U |

| HO1L 21/336 | (2006.01) | HO1L | 29/78 | 618B |

| HO1L 29/786 | (2006.01) | HO1L | 29/78 | 618F |

請求項の数 7 (全 11 頁) 最終頁に続く

(21) 出願番号 特願2012-551188 (P2012-551188)

(86) (22) 出願日 平成23年1月12日 (2011.1.12)

(65) 公表番号 特表2013-518436 (P2013-518436A)

(43) 公表日 平成25年5月20日 (2013.5.20)

(86) 國際出願番号 PCT/US2011/020916

(87) 國際公開番号 WO2011/094059

(87) 國際公開日 平成23年8月4日 (2011.8.4)

審査請求日 平成26年1月10日 (2014.1.10)

(31) 優先権主張番号 12/697,235

(32) 優先日 平成22年1月30日 (2010.1.30)

(33) 優先権主張国 米国(US)

(73) 特許権者 591150672

ナショナル セミコンダクター コーポレーション

NATIONAL SEMICONDUCTOR CORPORATION

アメリカ合衆国 カリフォルニア州 95051 サンタクララ エム/エス ディー3-579 セミコンダクター ドライブ 2900

(74) 代理人 100098497

弁理士 片寄 恒三

(72) 発明者 ジャマール ラムダニ

アメリカ合衆国 04074 メーン州

スカーバラ, パイン レッジ ドライブ

20

最終頁に続く

(54) 【発明の名称】低リードGaN MOSFET

## (57) 【特許請求の範囲】

## 【請求項 1】

エンハンスマント・モード・トランジスタであって、

GaNを含むチャネル層と、

InAlGaNを含む障壁層であって、開口を有する前記障壁層と、

前記障壁層に接する下位遷移層と、

前記障壁層に接する金属ソース領域と、

前記障壁層に接する金属ドレイン領域であって、前記金属ソース領域から間隔を空けて配置されている、前記金属ドレイン領域と、

前記開口内に配置され、その下位側で前記下位遷移層に接する第1の非導電性領域であって、前記下位遷移層を生成するために前記非導電性領域と前記障壁層とが陰イオンを共有し、前記金属ソース領域と前記金属ドレイン領域から間隔を空けて配置されている、前記第1の非導電性領域と、

前記第1の非導電性領域の上位側で前記第1の非導電性領域に接する上位遷移層であって、前記第1の非導電性領域の酸化により生成される、前記上位遷移層と、

前記上位遷移層と前記金属ソース領域と前記金属ドレイン領域とに接する第2の非導電性領域であって、前記第1の非導電性領域の上に位置し、上面を有する、前記第2の非導電性領域と、

前記第2の非導電性領域の前記上面に接する底面を有し、前記開口の上に垂直的に位置し、前記金属ソース領域と前記金属ドレイン領域と前記第1の非導電性領域とから間隔を

10

20

空けて配置されている、金属ゲート領域と、

前記障壁層に接する金属ソース領域であって、前記金属ゲート領域から空間を空けて配置されている、前記金属ソース領域と、

前記障壁層に接する金属ドレイン領域であって、前記金属ゲート領域と前記金属ソース領域とから空間を空けて配置されている、前記金属ドレイン領域と、

を含み、

前記金属ゲート領域に実質的に 0 V が印加され、前記金属ゲート領域と前記金属ドレイン領域とが異なってバイアスされるときに、実質的に電子が、InAlGaN を含む前記障壁層と GaN を含む前記チャネル層の間に 2 次元電子ガス領域を構成しないように、前記 InAlGaN を含む前記障壁層が厚さのしきい値より下であり、

10

前記エンハンスマント・モード・トランジスタのしきい値電圧を超える電圧が前記金属ゲート領域に印加され、前記金属ソース領域と前記金属ガス領域とが異なってバイアスされるときに、InAlGaN を含む前記障壁層と GaN を含む前記チャネル層との間の前記 2 次元電子ガス領域内に電子が蓄積され、前記電子が前記金属ソース領域から前記金属ドレイン領域に流れる、トランジスタ。

#### 【請求項 2】

請求項 1 に記載のエンハンスマント・モード・トランジスタであって、

前記障壁層に接して前記障壁層の下に位置するチャネル層を更に含み、

前記チャネル層と前記障壁層とが異なる材料を有し、前記開口が前記チャネル層を露出する、トランジスタ。

20

#### 【請求項 3】

請求項 2 に記載のエンハンスマント・モード・トランジスタであって、

前記第 1 の非導電性領域が窒化シリコンを含み、前記第 2 の非導電性領域が酸化シリコンを含む、トランジスタ。

#### 【請求項 4】

請求項 1 に記載のエンハンスマント・モード・トランジスタであって、

前記障壁層がアルミニウムを更に含む、トランジスタ。

#### 【請求項 5】

請求項 4 に記載のエンハンスマント・モード・トランジスタであって、

前記障壁層がインジウムを更に含む、トランジスタ。

30

#### 【請求項 6】

請求項 4 に記載のエンハンスマント・モード・トランジスタであって、

前記第 1 の非導電性領域が窒化シリコンを含み、前記第 2 の非導電性領域が酸化シリコンを含む、トランジスタ。

#### 【請求項 7】

請求項 1 に記載のエンハンスマント・モード・トランジスタであって、

前記 Si<sub>3</sub>N<sub>4</sub> の層と前記 InAlGaN 障壁層との間の前記下側遷移層が実質的に 1 × 10<sup>11</sup> / cm<sup>2</sup> より小さい界面状態の密度を有する、トランジスタ。

#### 【発明の詳細な説明】

##### 【技術分野】

40

##### 【0001】

本発明は、GaN MOSFET に関し、更に特定して言えば、低漏れ電流及び改善された信頼性を備えた、エンハンスマント・モード GaN MOSFET に関する。

##### 【背景技術】

##### 【0002】

GaN MOSFET は、当業界で周知であり、高電力、高周波数、及び高温の応用例において用いられている。GaN MOSFET は、典型的にチャネル層として知られる GaN 領域と典型的に障壁層として知られる上にある AlGaN 領域との間のヘテロ接合の形成に基づくのが典型的である。GaN チャネル層及び AlGaN 障壁層は異なるバンドギャップを有し、これらの異なるバンドギャップは、GaN チャネル層と AlGaN 障

50

壁層の間の接合に位置しGaNチャネル層へ延びる、二次元電子ガス（2DEG）の形成を引き起こす。

【0003】

トランジスタの「チャネル」として機能する2DEGは、高濃度の電子を生成し、これは、従来のように形成されるGaN MOSFETに空乏モードデバイス（ゼロボルトがデバイスのゲートに印加され、このデバイスのソース及びドレイン領域が異なってバイアスされるとき、ノミナリー・オン）として機能させる。

【0004】

空乏モードGaN MOSFETのための応用例はあるが、空乏モードトランジスタのノミナリー・オン状態は、スタートアップの間トランジスタ内のソース - ドレイン導通が早まって始まらないことを確実にするため、制御回路の利用を必要とする。これに対し、エンハンスメント・モードGaN MOSFET（ゼロボルトがデバイスのゲートに印加され、そのデバイスのソース及びドレイン領域が異なってバイアスされるとき、ノミナリー・オフ）は、制御回路を必要としない。というのも、このトランジスタは、ゼロボルトがゲートに印加されるときスタートアップ時にノミナリー・オフであるためである。

【0005】

しかし、エンハンスメント・モードGaN MOSFETを形成するため、ゼロボルトがデバイスのゲートに印加され（かつ、そのデバイスのソース及びドレイン領域が異なってバイアスされ）るとき、2DEG領域に実質的に電子が存在せず、また、閾値電圧を超える電圧がデバイスのゲートに印加され（かつ、そのデバイスのソース及びドレイン領域が異なってバイアスされ）るとき、2DEG領域に電子がたまり、ソース領域からドレイン領域へ流れるように、AlGaN障壁層は充分に薄く（例えば、数nm厚み）される必要がある。

【0006】

AlGaN障壁層の厚みを低減することに伴う問題の1つは、高レベルの漏れ電流がAlGaN障壁層を介してゲートへ通過し得ることであり、これは、従来は、ショットキーコンタクトとして実装される。この問題に対する1つの解決策は、AlGaN障壁層とゲートとの間に位置するゲート絶縁層を付加することである。

【0007】

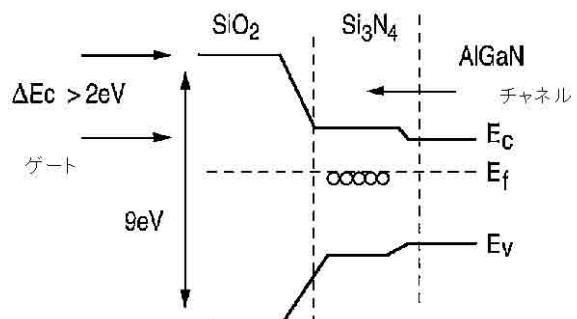

電流生成、エンハンスメント・モードGaN MOSFETは、ゲート絶縁層を形成するため種々の堆積される酸化物を用いる。これらの堆積される酸化物は、Al<sub>2</sub>O<sub>3</sub>、HfO<sub>2</sub>、MgO、Gd<sub>2</sub>O<sub>3</sub>、Ga<sub>2</sub>O<sub>3</sub>、ScO<sub>2</sub>、及びSiO<sub>2</sub>を含む。これらの酸化物の全ての中で、SiO<sub>2</sub>は9eVのバンドギャップEgと2.5eV程度まで高くなり得るAlGaNに対するEcを有し、これが、最低漏れ電流及び2.5ボルト程度に高い閾値電圧につながる。

【0008】

SiO<sub>2</sub>を含むこれらの堆積される酸化物のすべてに関する1つの問題は、これらの堆積される酸化物が高密度の界面準位（例えば、4×10<sup>11</sup>/cm<sup>2</sup>より大きい）を有し、その結果、ゲート絶縁層とAlGaN障壁層との間の接合のトラップサイトの数が多くなることがある。トラップサイトの数が多いことはゲート絶縁層のブレークダウンにつながり、これによりGaNデバイスの長期的信頼性が低下する。そのため、低い漏れ電流を有するエンハンスメント・モードGaN MOSFETが必要とされている。

【発明の概要】

【0009】

本発明のエンハンスメント・モードGaN MOSFETは、AlGaN（又はInAlGaN）障壁層上のSiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>ゲート絶縁層を用いる。SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>ゲート絶縁層のSi<sub>3</sub>N<sub>4</sub>部分は、ゲート絶縁層と障壁層との間の接合での界面準位の形成を著しく低減させ、SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>ゲート絶縁層のSiO<sub>2</sub>部分は、漏れ電流を著しく低減させる。

【0010】

10

20

30

40

50

本発明のGaN MOSFETは障壁層を含み、障壁層はAlGaNを含む。本発明のGaN MOSFETは、障壁層に接するSi<sub>3</sub>N<sub>4</sub>の層を更に含む。本発明のGaN MOSFETは更に、Si<sub>3</sub>N<sub>4</sub>の層に接しSi<sub>3</sub>N<sub>4</sub>の層上に位置するSiO<sub>2</sub>の層と、SiO<sub>2</sub>の層に接し、SiO<sub>2</sub>の層及びSi<sub>3</sub>N<sub>4</sub>の層の上に位置する金属ゲートとを含む。

【0011】

本発明のGaN MOSFETを形成する方法が、AlGaNを含む障壁層を形成することを含む。この方法は、障壁層に接するSi<sub>3</sub>N<sub>4</sub>の層を形成することを更に含む。この方法は、Si<sub>3</sub>N<sub>4</sub>の層に接するSiO<sub>2</sub>の層を形成すること、及びSiO<sub>2</sub>の層に接しSiO<sub>2</sub>の層の上に位置する金属ゲートを形成することを更に含む。 10

【図面の簡単な説明】

【0012】

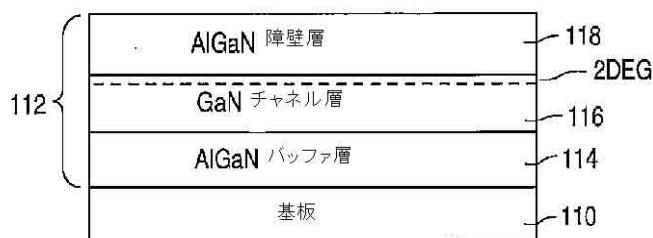

【図1】本発明に従って、エンハンスマント・モードGaN MOSFET100を形成する方法の一例を図示する一連の断面図である。

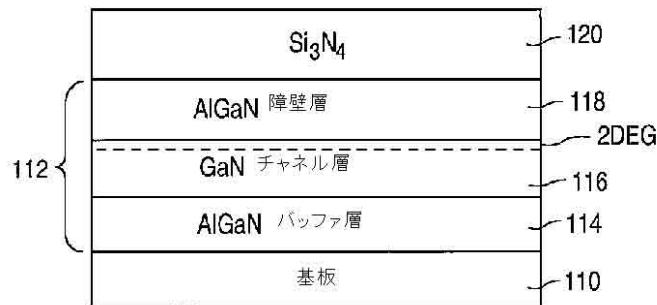

【図2】本発明に従って、エンハンスマント・モードGaN MOSFET100を形成する方法の一例を図示する一連の断面図である。

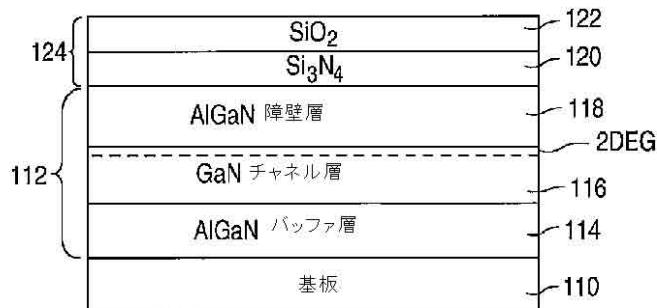

【図3】本発明に従って、エンハンスマント・モードGaN MOSFET100を形成する方法の一例を図示する一連の断面図である。

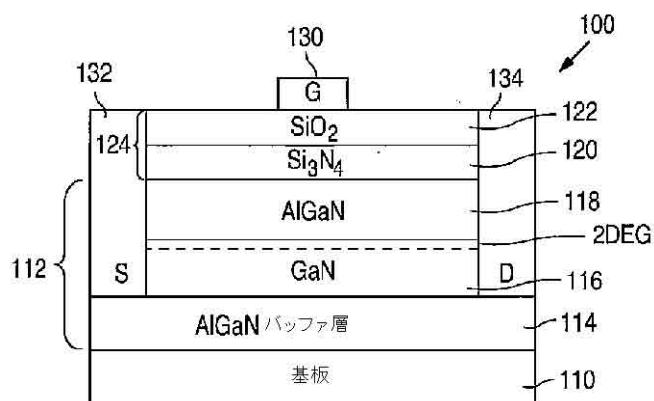

【図4】本発明に従って、エンハンスマント・モードGaN MOSFET100を形成する方法の一例を図示する一連の断面図である。 20

【図5】本発明の代替実施例に従って、エンハンスマント・モードGaN MOSFET500を形成する方法の一例を図示する一連の断面図である。

【図6】本発明の代替実施例に従って、エンハンスマント・モードGaN MOSFET500を形成する方法の一例を図示する一連の断面図である。

【図7】本発明の代替実施例に従って、エンハンスマント・モードGaN MOSFET500を形成する方法の一例を図示する一連の断面図である。

【図8】本発明の代替実施例に従って、エンハンスマント・モードGaN MOSFET500を形成する方法の一例を図示する一連の断面図である。

【図9】本発明の代替実施例に従って、エンハンスマント・モードGaN MOSFET500を形成する方法の一例を図示する一連の断面図である。 30

【図10】本発明に従った漏れ電流バンド図を示す。

【発明を実施するための形態】

【0013】

下記に更に詳細に説明するように、本発明は、AlGaN障壁層（又は任意のInAlGaN障壁層）上にSiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>ゲート絶縁層を形成して、ゲート絶縁層と障壁層との間の接合の界面準位の形成を著しく低減させる。界面準位の密度を低減することは、トラップサイトの数を著しく低減させ、これは、GaNデバイスの長期的信頼性を改善する。

【0014】

図1～4は、本発明に従って、エンハンスマント・モードGaN MOSFET100を形成する方法の一例を図示する一連の断面図を示す。図1に示すように、本発明の方法は、従来のように形成される半導体基板110を用いる。基板110は、絶縁基板として、又はシリコン（例えば、<111>）、サファイア、又はシリコンカーバイドなど、高度に抵抗性の材料を備えて、実装され得る。図1に更に示すように、本発明の方法は、基板110上にエピタキシャル層112を形成することにより始まる。エピタキシャル層112は、従来のプロセスを用いて有機金属化学気相成長（MOCVD）リアクターで形成され、ドーピングされていないAlGaNバッファ層114、ドーピングされていないGaNチャネル層116、及びドーピングされていない又はn型ドープされたAlGaN障壁層118（又は任意でドーピングされていない又はn型ドープされたInAlGaN障壁層118）を含む。AlGaNバッファ層114は、応力を緩和するために用いられる 40

、異なるアルミニウム組成を備えた多数のドーピングされていないAlGaN層を含む。

【0015】

図2に図示するように、本発明に従って、エピタキシャル層112が形成された後、Si<sub>3</sub>N<sub>4</sub>層120が、SiH<sub>4</sub>及びNH<sub>3</sub>を用いてAlGaN障壁層118と同じMOCVDリアクターで直接AlGaN障壁層118上にエピタキシャル成長される。言い換えると、Si<sub>3</sub>N<sub>4</sub>層120が、AlGaN層118を備えた構造をMOCVDリアクターから取り出すことなく、AlGaN層118が成長された後にエピタキシャル成長される。

【0016】

Si<sub>3</sub>N<sub>4</sub>層120は、約10～100nmの厚みを有するように成長されることが好ましく、その特定の厚みはアプリケーションに依存する。SiN及びAlGaNは同じ陰イオンを共有し、その結果、Si<sub>3</sub>N<sub>4</sub>層120とAlGaN障壁層118との間に、例えば $1 \times 10^{11} / \text{cm}^2$ 未満であることが予測される、非常に低い界面準位密度を有する遷移層が生成される。

【0017】

図3に図示するように、Si<sub>3</sub>N<sub>4</sub>層120が成長された後、Si<sub>3</sub>N<sub>4</sub>層120の一部がスチーム/ウェット高速熱酸化プロセスで酸化されて、残ったSi<sub>3</sub>N<sub>4</sub>層120上に位置するSiO<sub>2</sub>層122を形成する。本発明において、Si<sub>3</sub>N<sub>4</sub>とSiO<sub>2</sub>層との組み合わせが、例えば、64オングストリームの厚みのSi<sub>3</sub>N<sub>4</sub>層及び128オングストリームの厚みのSiO<sub>2</sub>層を有する、トランジスタのゲート絶縁層124を形成する。Si<sub>3</sub>N<sub>4</sub>層120の酸化が、Si<sub>3</sub>N<sub>4</sub>層120とSiO<sub>2</sub>層122との間の遷移層を生成し、これも非常に低い密度の界面準位を有する。

【0018】

図4に図示するように、SiO<sub>2</sub>層122の形成に続いて、この方法は、従来の方式で、例えばチタンアルミニウムコンタクトを用いて、金属ゲート領域130、金属ソース領域132、及び金属ドレイン領域134を形成することにより、GaN MOSFET100の形成を終了し、その後、上にあるパッシベーション層の従来の形成が続く。金属ゲート領域130は、ゲート絶縁層124のSiO<sub>2</sub>層122に接するように形成される。金属ソース132及び金属ドレイン領域134は、GaNチャネル層116及びAlGaN障壁層118とのオーミックコンタクトをつくるように形成される。

【0019】

上述のように、障壁層のAlGaNとチャネル層のGaNとが異なるバンドギャップを有し、従来、AlGaN障壁層とGaNチャネル層との間の接合に位置しGaNチャネル層へ延びる、二次元電子ガス(2DEG)を引き起こすように形成される。

【0020】

更に上述したように、トランジスタの「チャネル」として機能する2DEGは、高濃度電子を生成し、これは、従来のように形成されるGaN MOSFETを空乏モードデバイス(ゼロボルトがデバイスのゲートに印加され、ソース及びドレイン領域が異なってバイアスされるとき、ノミナリー・オン)であるようにさせる。

【0021】

そのため、図4に示すGaN MOSFET100をエンハンスマント・モードのデバイス(ゼロボルトが金属ゲート領域130に印加され、金属ソース領域132及び金属ドレイン領域134が異なってバイアスされるとき、ノミナリー・オフ)として形成するため、ゼロボルトが金属ゲート領域130に印加され(かつ金属ソース領域132及び金属ドレイン領域134異なってバイアスされ)るとき、2DEG領域に電子が実質的に存在せず、閾値電圧を超える電圧が金属ゲート領域130に印加され(かつ金属ソース領域132及び金属ドレイン領域134が異なってバイアスされ)るとき、2DEG領域に電子がたまり、金属ソース領域132から金属ドレイン領域134へ流れるように、AlGaN障壁層118は充分に薄く(例えば、数nm厚み)される必要がある。

【0022】

10

20

30

30

40

50

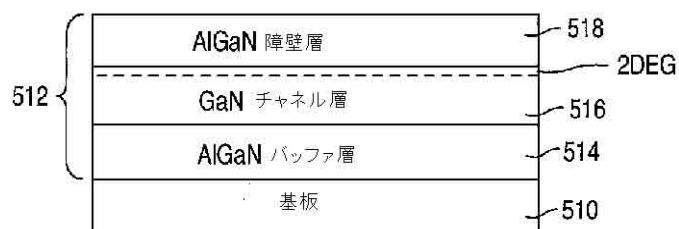

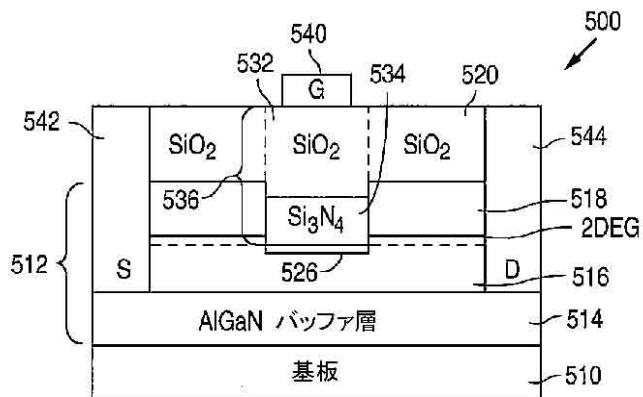

図5～9は、本発明の代替実施例に従って、エンハンスマント・モードGaN MOSFET500を形成する方法の一例を図示する一連の断面図を示す。図5に示すように、本発明の代替の方法も、従来のように形成される半導体基板510を用いる。基板110と同様、基板510も、絶縁基板として、又はシリコン（例えば、<111>）、サファイア、又はシリコンカーバイドなどの高度に抵抗性の材料を備えて、実装され得る。

【0023】

図5に更に示すように、本発明の代替の方法は、（従来のプロセスを用いてMOCVDリアクターで）エピタキシャル層112が形成されるのと同じ方式で、基板510上にエピタキシャル層512を形成することにより始まる。その結果、エピタキシャル層512は、ドーピングされていないAlGaNバッファ層514、ドーピングされていないGaNチャネル層516、及びドーピングされていない又はn型ドープされたAlGaN障壁層518（又は任意でドーピングされていない又はn型ドープされたInAlGaN障壁層518）を含む。このAlGaNバッファ層514は、応力を緩和するために用いられる異なるアルミニウム組成を備えた多数のドーピングされていないAlGaN層を含む。

【0024】

しかし、GaN MOSFET100とは異なり、AlGaN障壁層518は、従来の（空乏モード）厚みを有するように形成され、その結果、AlGaN障壁層518とGaNチャネル層516との間の接合に位置しGaNチャネル層516内に延びる、二次元電子ガス（2DEG）の形成を引き起こす。AlGaN障壁層518とGaNチャネル層516との間の接合に位置する2DEGは、高濃度電子を生成する。

【0025】

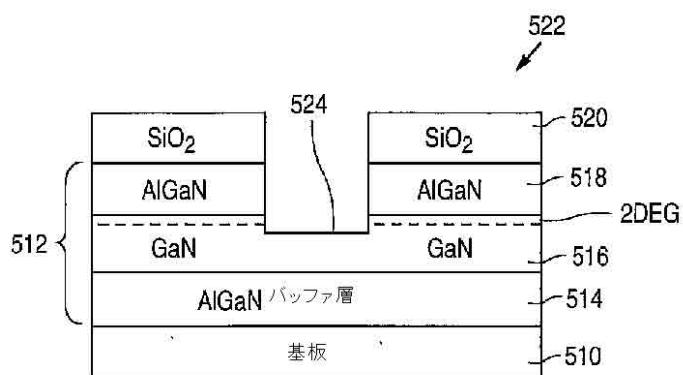

図6に図示するように、本発明に従って、エピタキシャル層512が形成された後、AlGaN障壁層518の上面に、SiO<sub>2</sub>の層などのマスク520が形成され、パターニングされる。マスク520が形成されると、マスク520により露出された領域がドライエッチングされる。このドライエッチングは、GaNチャネル層516の上面に位置する2DEGの最低レベルより上で、又は最低レベルで、或いは、最低レベルより下で、停止し得る。（図6は、2DEGの最低レベルのすぐ下で停止するドライエッチを図示する。）

【0026】

図6に更に示すように、ドライエッチングは、露出された領域524を有する中間MOSFET構造522を生成する。ドライエッチングに続いて、中間MOSFET構造522は次に、MOCVDリアクターでH<sub>2</sub>及びNH<sub>3</sub>でベークされて、ドライエッチングにより生じる格子への損傷を修復する。言い換えると、MOCVDリアクターから中間MOSFET構造522を取り出すことなく、ドライエッチング後に中間MOSFET構造522がベークされる。

【0027】

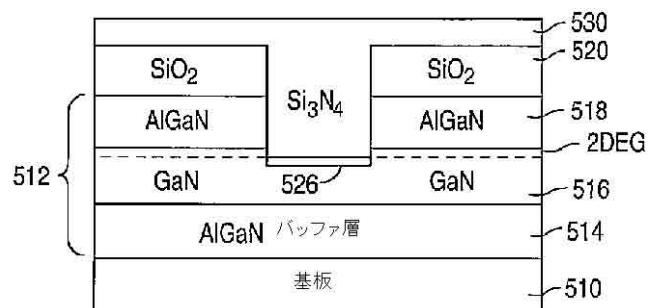

図7に図示するように、中間MOSFET構造522がベークされた後、薄いドーピングされていない又はn型ドープされたAlGaN障壁フィルム526（又は任意で薄いドーピングされていない又はn型ドープされたInAlGaN障壁フィルム526）が、露出された領域524上にエピタキシャル成長される。薄いAlGaN障壁フィルム526の上面は、2DEGの最低レベルより上、又は最低レベル、或いは、最低レベルより下に位置し得る。（図7は、AlGaN障壁フィルム526の上面が2DEGの最低レベルに位置することを図示する。）薄いAlGaN障壁フィルム526は、AlGaN障壁層518の最大厚みより薄い厚みを有する。

【0028】

薄いAlGaN障壁フィルム526が成長されると、Si<sub>3</sub>N<sub>4</sub>層530が、SiH<sub>4</sub>及びNH<sub>3</sub>を用いて薄いAlGaN障壁フィルム526と同じMOCVDリアクターで直接薄いAlGaN障壁フィルム526上にエピタキシャル成長される。言い換えると、Si<sub>3</sub>N<sub>4</sub>層530は、薄いAlGaN障壁フィルム526を備えた構造をMOCVDリアクターから取り出すことなく、薄いAlGaN障壁フィルム526が成長された後エピタ

10

20

20

30

40

50

キシャル成長される。(図7に図示するように、 $\text{Si}_3\text{N}_4$ 層530は、 $\text{AlGaN}$ 障壁層518の側壁上及び $\text{SiO}_2$ マスク520上にも成長する。)

【0029】

$\text{Si}_3\text{N}_4$ 層530は、薄い $\text{AlGaN}$ フィルム526の上に約10~100nmの厚みを有するように成長されることが好ましく、この特定の厚みはアプリケーションに依存する。前述したように、このプロセスは、 $\text{Si}_3\text{N}_4$ 層530と薄い $\text{AlGaN}$ 障壁フィルム526との間に、例えば、 $1 \times 10^{11} / \text{cm}^2$ 未満であることが予測される、非常に低い界面準位密度を有する遷移層を生成する。

【0030】

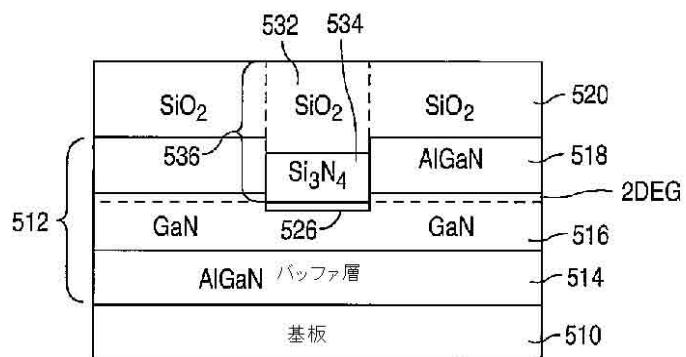

図8に図示するように、 $\text{Si}_3\text{N}_4$ 層530の成長に続いて、スチーム/ウェット高速熱酸化プロセスで $\text{Si}_3\text{N}_4$ 層530の一部が酸化されて、 $\text{Si}_3\text{N}_4$ 領域534の上に位置する $\text{SiO}_2$ 領域532を形成し、これは、薄い $\text{AlGaN}$ 障壁フィルム526の上に位置する。図8に更に示すように、 $\text{AlGaN}$ 障壁層518は、 $\text{Si}_3\text{N}_4$ 領域534の横方向に近接して位置する。(この酸化プロセスは、 $\text{SiO}_2$ マスク520の上に位置する $\text{Si}_3\text{N}_4$ 層530も酸化し、それにより、 $\text{SiO}_2$ マスク520の厚みを増加させる。)

【0031】

本発明において、 $\text{Si}_3\text{N}_4$ 領域534と $\text{SiO}_2$ 領域532との組み合わせは、例えば、64オングストリームの厚みの $\text{Si}_3\text{N}_4$ 領域及び128オングストリームの厚みの $\text{SiO}_2$ 領域を有する、薄い $\text{AlGaN}$ フィルム526の上に位置するゲート絶縁層536を形成する。前述したように、 $\text{Si}_3\text{N}_4$ 層530の酸化は、 $\text{Si}_3\text{N}_4$ 領域534と $\text{SiO}_2$ 領域532との間の遷移層を生成し、これも非常に低い密度の界面準位を有する。

【0032】

図9に図示するように、 $\text{SiO}_2$ 領域532の形成に続いて、この方法は、従来の方式で、例えば、チタンアルミニウムコンタクトを用いて、金属ゲート領域540、金属ソース領域542、及び金属ドレイン領域544を形成することにより、 $\text{GaN MOSFET}$ 500の形成を終了し、その後、上にあるパッシベーション層の従来の形成が続く。金属ゲート領域540は、ゲート絶縁層536の $\text{SiO}_2$ 領域532に接するように形成される。金属ソース542及び金属ドレイン領域544は、 $\text{GaN}$ チャネル層516及び $\text{AlGaN}$ 障壁層518とのオーミックコンタクトをつくるように形成される。

【0033】

そのため、図9に示す $\text{GaN MOSFET}$ 500は、ゼロボルトが金属ゲート領域540に印加され(かつ金属ソース領域542及び金属ドレイン領域544が異なってバイアスされる)るとき、ゲート絶縁層536及び金属ゲート領域540の直下に実質的に電子がまったくまらず、閾値電圧を超える電圧が金属ゲート領域540に印加され(かつ金属ソース領域542及び金属ドレイン領域544が異なってバイアスされる)るとき、ゲート絶縁層536及び金属ゲート領域540の直下に電子がたまり、金属ソース領域542から金属ドレイン領域544へ流れるように、 $\text{AlGaN}$ 障壁フィルム526を充分に薄く(例えば、数nm厚み)形成することにより、エンハンスマントモードデバイス(ゼロボルトが金属ゲート領域540に印加され、金属ソース領域542及び金属ドレイン領域544が異なってバイアスされるとき、ノミナリー・オフ)として形成される。

【0034】

本発明の利点の一つは、 $\text{SiO}_2 / \text{Si}_3\text{N}_4$ ゲート絶縁層の $\text{Si}_3\text{N}_4$ 部分が、ゲート絶縁層と $\text{AlGaN}$ 障壁層(又は任意の $\text{InAlGaN}$ 障壁層)との間の接合の界面準位の形成を著しく低減させることである。電子がトラップされ得るサイトの数を著しく低減することは、 $\text{GaN}$ デバイスの長期的信頼性を著しく改善する。

【0035】

本発明の更なる利点は、 $\text{SiO}_2 / \text{Si}_3\text{N}_4$ ゲート絶縁層のキャップ層として $\text{SiO}_2$ を利用することにより、本発明は、最低漏れ電流及び2.5ボルト程度に高い閾値電圧

10

20

30

40

50

を有する（即ち、 $\text{SiO}_2$  は 9 eV のバンドギャップ  $E_g$  と 2.5 eV 程度まで高くなり得る  $\text{AlGaN}$  に対する  $E_c$  を有する）ことである。

【0036】

図 10 は、本発明に従った漏れ電流を図示するバンド図を示す。図 10 に示すように、バンドラインナップは、界面準位の低密度及び  $\text{SiO}_2$  の広いバンドギャップに起因するゲート酸化物内に制限されたトンネリングが存在することを示す。また、2 V より大きい閾値電圧  $V_t$  で、 $\text{SiO}_2$  から  $\text{AlGaN}$  に対する有効  $E_c$  が 2 eV より大きい。

【0037】

上述の説明は本発明の例であり、本明細書に記載した本発明の種々の代替例を本発明を実施して用いられ得ることを理解されたい。従って、添付の特許請求の範囲が本発明の範囲を定めること、また、これらの特許請求の範囲内の構造及び方法及びそれらの同等物が本発明に包含されることが意図されている。

10

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

| (51)Int.Cl.             | F I           |   |

|-------------------------|---------------|---|

| H 01 L 21/318 (2006.01) | H 01 L 21/318 | B |

| H 01 L 21/316 (2006.01) | H 01 L 21/316 | S |

| H 01 L 21/205 (2006.01) | H 01 L 21/316 | M |

|                         | H 01 L 21/205 |   |

審査官 須原 宏光

(56)参考文献 特開2006-173294 (JP, A)

特開2008-305816 (JP, A)

特開昭64-000756 (JP, A)

特開2009-231396 (JP, A)

特開2009-076673 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 78

H 01 L 29 / 80