(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4662474号

(P4662474)

(45) 発行日 平成23年3月30日(2011.3.30)

(24) 登録日 平成23年1月14日(2011.1.14)

(51) Int.Cl.

F 1

|            |           |            |      |

|------------|-----------|------------|------|

| GO6F 1/18  | (2006.01) | GO6F 1/00  | 320F |

| GO6F 15/78 | (2006.01) | GO6F 15/78 | 510F |

| GO6F 13/16 | (2006.01) | GO6F 13/16 | 510A |

| GO6F 12/00 | (2006.01) | GO6F 12/00 | 550K |

| HO1L 27/04 | (2006.01) | HO1L 27/04 | A    |

請求項の数 5 (全 26 頁) 最終頁に続く

(21) 出願番号

特願2006-33513 (P2006-33513)

(22) 出願日

平成18年2月10日 (2006.2.10)

(65) 公開番号

特開2007-213375 (P2007-213375A)

(43) 公開日

平成19年8月23日 (2007.8.23)

審査請求日

平成21年2月2日 (2009.2.2)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100089071

弁理士 玉村 静世

(72) 発明者 別井 隆文

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

(72) 発明者 田岡 直人

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

(72) 発明者 諏訪 元大

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】データ処理デバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

第1反転データストローブ信号回路用端子および第1非反転データストローブ信号回路用端子を有する第1メモリデバイスが搭載されたプリント配線基板に搭載されるデータ処理デバイスであって、

前記データ処理デバイスは、上面および前記上面とは反対側の下面を有するパッケージと、第1反転データストローブ信号回路および第1非反転データストローブ信号回路を有し、かつ前記パッケージの前記上面に搭載されたマイクロコンピュータチップと、前記パッケージの前記下面に形成された複数のボール電極とを含み、

前記パッケージの平面形状は、第1辺を有する四角形からなり、

10

前記マイクロコンピュータチップの平面形状は、第2辺を有する四角形からなり、

前記マイクロコンピュータチップは、平面視において、前記マイクロコンピュータチップの前記第2辺が前記パッケージの前記第1辺と並ぶように、前記パッケージの前記上面に搭載され、

前記第1反転データストローブ信号回路および前記第1非反転データストローブ信号回路は、前記マイクロコンピュータチップの前記第2辺に沿って隣接配置されており、

前記複数のボール電極は、平面視において、前記第1辺に沿って、かつ、複数列に亘って配置されており、

前記複数のボール電極のうち、前記パッケージに形成された第1配線を介して前記マイクロコンピュータチップの前記第1非反転データストローブ信号回路と電気的に接続され

20

、かつ、前記第1メモリデバイスの前記第1非反転データストローブ信号回路用端子と電気的に接続される第1非反転データストローブ信号回路用ボール電極は、前記複数のボール電極のうち、前記パッケージに形成された第2配線を介して前記マイクロコンピュータチップの前記第1反転データストローブ信号回路と電気的に接続され、かつ、前記第1メモリデバイスの前記第1反転データストローブ信号回路用端子と電気的に接続される第1反転データストローブ信号回路用ボール電極と、前記下面における前記第1辺と交差する方向に沿って隣接配置されており、

前記第1反転データストローブ信号回路用ボール電極および前記第1非反転データストローブ信号回路用ボール電極は、前記複数のボール電極のうちの第1周目および第2周目、または第3周目および第4周目に、それぞれ割り当てられていることを特徴とするデータ処理デバイス。

【請求項2】

前記第1メモリデバイスは、上位バイト用の前記第1反転データストローブ信号回路用端子と、上位バイト用の前記第1非反転データストローブ信号回路用端子と、下位バイト用の第2反転データストローブ信号回路用端子と、下位バイト用の第2非反転データストローブ信号回路用端子とを有しており、

前記マイクロコンピュータチップは、上位バイト用の前記第1反転データストローブ信号回路と、上位バイト用の前記第1非反転データストローブ信号回路と、下位バイト用の第2反転データストローブ信号回路と、下位バイト用の第2非反転データストローブ信号回路とを有しており、

前記複数のボール電極のうち、前記パッケージに形成された第3配線を介して前記マイクロコンピュータチップの前記第2非反転データストローブ信号回路と電気的に接続され、かつ、前記第1メモリデバイスの前記第2非反転データストローブ信号回路用端子と電気的に接続される第2非反転データストローブ信号回路用ボール電極は、前記複数のボール電極のうち、前記パッケージに形成された第4配線を介して前記マイクロコンピュータチップの前記第2反転データストローブ信号回路と電気的に接続され、かつ、前記第1メモリデバイスの前記第2反転データストローブ信号回路用端子と電気的に接続される第2反転データストローブ信号回路用ボール電極と隣接配置されていることを特徴とする請求項1記載のデータ処理デバイス。

【請求項3】

前記第2反転データストローブ信号回路用ボール電極および前記第2非反転データストローブ信号回路用ボール電極は、前記複数のボール電極のうちの第1周目および第2周目、または第3周目および第4周目に、それぞれ割り当てられていることを特徴とする請求項2記載のデータ処理デバイス。

【請求項4】

第1反転データストローブ信号回路用ボール電極は、前記プリント配線基板の第1配線層に形成された第1差動信号配線を介して前記第1反転データストローブ信号回路用端子と電気的に接続され、

第1非反転データストローブ信号回路用ボール電極は、前記プリント配線基板の前記第1配線層に形成され、かつ前記第1差動信号配線の隣に形成された第2差動信号配線を介して前記第1非反転データストローブ信号回路用端子と電気的に接続され、

第2反転データストローブ信号回路用ボール電極は、前記プリント配線基板の前記第1配線層に形成された第3差動信号配線を介して前記第2反転データストローブ信号回路用端子と電気的に接続され、

第2非反転データストローブ信号回路用ボール電極は、前記プリント配線基板の前記第1配線層に形成され、かつ前記第3差動信号配線の隣に形成された第4差動信号配線を介して前記第2非反転データストローブ信号回路用端子と電気的に接続されることを特徴とする請求項3記載のデータ処理デバイス。

【請求項5】

前記プリント配線基板には、さらに、上位バイト用の第3反転データストローブ信号回

10

20

30

40

50

路用端子と、上位バイト用の第3非反転データストローブ信号回路用端子と、下位バイト用の第4反転データストローブ信号回路用端子と、下位バイト用の第4非反転データストローブ信号回路用端子とを有する第2メモリデバイスが搭載されており、

前記マイクロコンピュータチップは、さらに、上位バイト用の第3反転データストローブ信号回路と、上位バイト用の第3非反転データストローブ信号回路と、下位バイト用の第4反転データストローブ信号回路と、下位バイト用の第4非反転データストローブ信号回路とを有しており、

前記複数のボール電極のうち、前記パッケージに形成された第5配線を介して前記マイクロコンピュータチップの前記第3非反転データストローブ信号回路と電気的に接続され、かつ、前記第2メモリデバイスの前記第3非反転データストローブ信号回路用端子と電気的に接続される第3非反転データストローブ信号回路用ボール電極は、前記複数のボール電極のうち、前記パッケージに形成された第6配線を介して前記マイクロコンピュータチップの前記第3反転データストローブ信号回路と電気的に接続され、かつ、前記第2メモリデバイスの前記第3反転データストローブ信号回路用端子と電気的に接続される第3反転データストローブ信号回路用ボール電極と隣接配置されており、

前記複数のボール電極のうちの前記第4非反転データストローブ信号回路と電気的に接続され、かつ、前記第2メモリデバイスの前記第4非反転データストローブ信号回路用端子と電気的に接続される第4非反転データストローブ信号回路用ボール電極は、前記複数のボール電極のうちの前記第4反転データストローブ信号回路と電気的に接続され、かつ、前記第2メモリデバイスの前記第4反転データストローブ信号回路用端子と電気的に接続される第4反転データストローブ信号回路用ボール電極と隣接配置されていることを特徴とする請求項4記載のデータ処理デバイス。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、メモリインターフェース回路を備えたマイクロコンピュータ、更にはモジュール基板にマイクロコンピュータ及びメモリとを搭載したSIP (System In Package) のような半導体装置に関し、例えば、JEDEC STANDARD No.79-2Bに準拠したDDR (Double Data Rate) 2 - SDRAM (Synchronous Dynamic Random Access Memory) を接続可能とするメモリインターフェース回路を備えたマイクロコンピュータに適用して有効な技術に関する。

【背景技術】

【0002】

SDRAMに対する国際標準としてJEDEC標準(JEDEC STANDARD)があり、これは端子配列、端子機能、動作モードなどについての規格を標準化する。例えば非特許文献によるJEDEC STANDARD No.79-2Bが規定するDDR2 - SDRAMにおいて、データストローブ信号及びクロック信号は差動対とされ、また、データ及びデータストローブ信号系の端子群とコマンド及びアドレス系の端子群は分離配置され、特に、並列データ入出力ビット数を16ビット(×16ビット)とするインターフェース仕様に対しては上位バイトのデータ及びデータストローブ信号系の端子群と、下位バイトのデータ及びデータストローブ信号系の端子群との配置も分離される。

【0003】

【非特許文献1】JEDEC STANDARD, DDR2 SDRAM SPECIFICATION JESD79-2B(Revision of JESD79-2A), January 2005, JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

【発明の開示】

【発明が解決しようとする課題】

【0004】

本発明者は、メモリコントローラを備えたマイクロコンピュータにおけるDDR2 - SDRAMに対応するメモリインターフェース回路について検討した。即ち、動作電圧の低電圧化や回路素子の微細化等の流れの中で、マイクロコンピュータについても、チップ及び

10

20

30

40

50

パッケージの小型化が促進されている。チップが小型化されると、チップ周辺に配置可能な入出力回路セル（I/Oセル）の数が制限される。例えば、DDR2-SDRAMのデータ及びデータストローブ系インタフェースはデータ1バイトにつき更にこれに対応するデータストローブ信号の差動対とデータマスク信号の3ビットの合計11ビットのI/Oセルを必要とする。一つのI/Oセルのセル幅を約80μmとすると、1バイト分のインターフェース信号だけで少なくとも880μmの幅が必要になる。電源およびGNDセルが入ることを考慮して幅が約2倍になると想定すると1760μmを費やす。4バイト分でも7040μmとなり、データ及びデータストローブ系だけで7mm以上の幅が必要になり、これを1辺に配置しようとすれば、1辺が7mm以下の正方形チップは採用することができない。また、長辺が7mm以上の長方形チップを採用してもよいが、そうすると、チップ上における回路位置と回路特性との相関が大きくなり、信頼性低下の虞が増すことになる。本発明者はマイクロコンピュータチップやパッケージの小型化に資することができるメモリインタフェース端子群の配置について検討した。さらに、高密度のモジュール基板に複数のペアチップ等を搭載する場合はメモリインタフェース端子の配列だけでなく、小型化に伴う別の観点による対応の必要が明らかにされた。別の観点とは、高密度配線故の耐ノイズ性、電子部品の外付け位置、封止された複数チップに対するテスタビリティ一等である。

#### 【0005】

本発明の目的は、マザーボード上における配線設計容易性や、モジュール基板上における配線設計容易性を実現可能にするマイクロコンピュータを提供することにある。

#### 【0006】

本発明の別の目的は、8ビット又は16ビットのようにデータ入出力ビット数の仕様が異なる複数種類のメモリへの対応が容易なメモリインタフェース回路を備えたマイクロコンピュータを提供することにある。

#### 【0007】

本発明の更に別の目的は、モジュール基板に複数の半導体デバイスを搭載する半導体装置の小型化に伴う信頼性を向上させることにある。

#### 【0008】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

#### 【課題を解決するための手段】

#### 【0009】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

#### 【0010】

##### 〔1〕《データ系のメモリインタフェース配置》

本発明に係るマイクロコンピュータ（1）は、矩形の半導体基板に形成されメモリインタフェース回路（4，5）を有する。前記半導体基板の一つのコーナー部を基点とする両側の縁辺に沿って、前記メモリインタフェース回路が分割配置されている。半導体基板の一辺にメモリインタフェース回路を集中させる場合に比べて半導体基板はサイズ縮小の制約を受け難い。

#### 【0011】

前記分割配置された両側の各々の部分回路は、データ及びデータストローブ信号に関し相互に等しいデータ系ユニットを持つ。マザーボード上における配線設計容易性や、モジュール基板上における配線設計容易性の実現が可能になる。

#### 【0012】

前記データ系ユニットは単位ユニット（LBIFF，UBIFF）を有し、前記単位ユニットは前記データの単位をバイトとすればよい。メモリインタフェース回路が備えるべきインターフェース規模に応じて単位ユニットのレイアウト数を変えればよいから、メモリインタフェース回路に対する設計の容易化に資することができる。8ビット又は16ビットの

10

20

30

40

50

ようにデータ入出力ビット数の仕様が異なる複数種類のメモリへの対応が容易である。8ビットの整数倍のデータインターフェースに対応するとき、前記データ系ユニットは、直列的に配置された複数の前記単位ユニットを有することになる。

【0013】

本発明の更に具体的な形態として、前記単位ユニットは、前記コーナー部側から順に、7個のデータ入出力回路(10)、データマスク信号回路(11)、反転データストローブ信号回路(12)、非反転データストローブ信号回路(13)、及び1個のデータ入出力回路(14)を有する。これは、JEDEC標準のDDR2-SDRAMの端子配列を考慮したものである。即ち、DDR2-SDRAMは、その長辺に沿ってデータ及びデータストローブ信号系の端子群とコマンド及びアドレス系の端子群は分離配置され、特に、並列データ入出力ビット数を16ビット( $\times 16$ ビット)とするインターフェース仕様に対しては上位バイトのデータ及びデータストローブ信号系の端子群と、下位バイトのデータ及びデータストローブ信号系の端子群との配置も分離されている。この長辺をマイクロコンピュータのデータ系ユニットに対向させたとき、バイトのデータ及びデータストローブ信号系の端子群からデータ系ユニットに向く配線経路を単純化することが可能になる。このことが、マザーボード上における配線設計容易性や、モジュール基板上における配線設計容易性を実現可能にする。

【0014】

〔2〕《差動端子配置》

本発明の別の具体的な形態によれば、前記マイクロコンピュータは前記半導体基板が搭載されるパッケージを有し、前記パッケージは外部接続端子に関しボールグリッドアレイ形態を有する。前記反転データストローブ信号回路に接続する外部接続端子と前記非反転データストローブ信号回路に接続する外部接続端子とはボールグリッドアレイの最外周より第1周目と第2周目に隣接配置され、又は第3周目と第4周目に隣接配置されて、差動端子を構成する。ボールグリッドアレイ形態の外部接続端子に接続する実装基板上の配線において、ボールグリッドアレイの最外周より第1周目の外部接続端子に接続する配線はそのまま外側に引き出され、第2周目の外部接続端子に接続する配線は第1周目の外部接続端子に接続する2本の配線の間を通り外側に引き出される。第3周目と第4周目の外部接続端子に各々接続する配線は第1周目と第2周目の外部接続端子とは異なる配線層を通り同様に外側に引き出される。このような一般的な配線構造への対応を考慮すると、差動端子を第1周目と第2周目に隣接配置し、又は第3周目と第4周目に隣接配置することにより、差動端子に接続する配線は同一配線層上で隣接して相対するから、実装基板上においても同相ノイズ成分のキャンセル効果を維持することが容易になる。

【0015】

〔3〕《アドレス・コマンド系のメモリインターフェース配置》

本発明の更に別の具体的な形態によれば、前記マイクロコンピュータにおいて、分割配置された両側の各々の部分回路はアドレス信号及びコマンドに関するコマンド及びアドレス系ユニット(CAIF)を有し、前記コマンド及びアドレス系ユニットは前記データ系ユニットに直列的に配置され、前記コマンド及びアドレス系ユニットは前記データ系ユニットよりも前記半導体基板の一つのコーナー部寄りに配置される。これによれば、半導体基板の左右の縁辺部分に分割配置されたメモリインターフェース回路部分の夫々に対向してDDR2-SDRAMを実装基板上に配置するとき、マイクロコンピュータから夫々のDDR2-SDRAMにコマンド及びアドレスを供給する配線を、前記一つのコーナー部を基点に前記DDR2-SDRAMの間の領域を通し、途中で分岐して各々の前記DDR2-SDRAMの端子に至る経路を採用することが可能になる。実装基板上におけるコマンド及びアドレス系配線経路の等長化が容易になる。

【0016】

上記コマンド及びアドレス系を考慮した構成は、次の構成と等価である。即ち、前記メモリインターフェース回路は、JEDEC標準の端子配列を備えたDDR2-SDRAMが接続可能にされ、且つ、前記DDR2-SDRAMの長辺のデータ及びデータストローブ

10

20

30

40

50

信号に関するデータ系データ端子群とアドレス信号及びコマンドに関するコマンド及びアドレス系端子群との配置に則したインターフェース機能の配置を有すればよい。

【0017】

〔4〕《同期クロック用モジュール端子の配置》

本発明に係る半導体装置は、モジュール基板の一方の面に複数のメモリデバイスとデータ処理デバイスが搭載され、前記モジュール基板の他方の面に複数のモジュール端子が形成される。前記モジュール基板は、前記データ処理デバイスから出力される差動クロック信号を前記メモリデバイスに伝達するための差動クロック配線と、前記差動クロック配線に接続する差動終端抵抗接続用の一対のモジュール端子（BCKa, BCKb）とを有する。前記差動終端抵抗接続用の一対のモジュール端子は、相互に隣接され、且つ、他のモジュール端子が配置されていない領域に隣接し又はテスト専用モジュール端子に隣接して形成されている。

【0018】

上記によれば、前記半導体装置が実装される実装基板上にはテスト専用モジュール端子に接続されるべき配線は形成されていないから、差動終端抵抗接続端子を、他のモジュール端子が配置されていない領域に隣接し又はテスト専用モジュール端子に隣接して形成することにより、当該差動終端抵抗接続端子に直接終端抵抗を搭載することが容易になる。このことは分基点から差動終端抵抗までの配線経路を極めて短く且つ等長化するのに好適である。

【0019】

〔5〕《メモリコアへの給電ビア複数化》

本発明の半導体装置は、モジュール基板の一方の面にメモリデバイスとデータ処理デバイスが搭載され、前記モジュール基板の他方の面に複数のモジュール端子が形成される。前記モジュール基板はコア層とその表裏に形成されたビルドアップ層とを有する。前記モジュール端子として、前記データ処理デバイスにメモリインターフェース用電源を供給する第1モジュール電源端子（Vcc-DDR）と、前記メモリデバイスにコア回路用電源を供給する第2モジュール電源端子（Vdd-DRAM）と、前記メモリデバイスに外部出力及び外部入出力インターフェース用電源を供給する第3モジュール電源端子（Vddq-DRAM）と、前記データ処理デバイス及びメモリデバイスにグランド電圧を供給するモジュールグランド端子と、を各々電気的に分離して別々に備える。これは、メモリデバイスとデータ処理デバイスの電源を分離して個別テストをやり易くするための考慮である。外部出力及び外部入出力インターフェース用電源と、コア用電源を分離するのは、入出力動作に伴う電源ノイズによってコア回路が影響され難くするためである。このとき、前記第2モジュール電源端子をメモリデバイスに接続する給電経路において前記コア層の1個のビアに対してビルドアップ層に形成されるビアの数は、前記第3モジュール電源端子をメモリデバイスに接続する給電経路において前記コア層の1個のビアに対してビルドアップ層に形成されるビアの数よりも多くされる。メモリデバイスのコア回路による消費電力が外部出力及び外部入出力インターフェース回路部分よりも大きくなることを考慮したとき、コア層のビアに比べて導電面積の小さなビルドアップ層のビアによる電流供給能力不足を生じないようにすることができる。例えばメモリデバイスがDDR2-SDRAMのときは、ダイナミック型メモリセルのリフレッシュ動作で比較的大きな電力を消費する。

【0020】

上記したメモリコアへの給電ビアの複数化の手段に対する上位概念的発明について説明する。これによる半導体装置は、モジュール基板の一方の面にメモリデバイスとデータ処理デバイスが搭載され、前記モジュール基板の他方の面に複数のモジュール端子が形成される。前記モジュール基板はコア層とその表裏に形成されたビルドアップ層とを有する。前記モジュール端子として、前記データ処理デバイスに電源を供給するモジュール電源端子（Vcc-DDR）と、前記メモリデバイスに電源を供給するモジュール電源端子（Vdd-DRAM, Vddq-DRAM）とが分離される。前記メモリデバイスに電源を供給するモジュール電源端子はコア用電源と外部出力及び外部入出力インターフェース用電源

10

20

30

40

50

とで分離される。前記コア用電源をメモリデバイスに供給する給電経路において前記コア層の1個のビアに対してビルドアップ層に形成されるビアの数は、前記外部出力及び外部入出力インターフェース用電源をメモリデバイスに供給する給電経路において前記コア層の1個のビアに対してビルドアップ層に形成されるビアの数よりも多くされる。

【0021】

〔6〕《グランドスリットによるノイズ対策》

本発明に係る半導体装置は、モジュール基板の一方の面にメモリデバイスとデータ処理デバイスが搭載され、前記モジュール基板の他方の面に複数のモジュール端子が形成される。前記モジュール基板はコア層とその表裏に形成されたビルドアップ層とを有する。前記モジュール端子として、前記データ処理デバイスにメモリインターフェース用電源を供給する第1モジュール電源端子(Vcc-DDR)と、前記メモリデバイスにコア回路用電源を供給する第2モジュール電源端子(Vdd-DRAM)と、前記メモリデバイスに外部出力及び外部入出力インターフェース用電源を供給する第3モジュール電源端子(Vdq-DRAM)と、前記データ処理デバイス及びメモリデバイスにグランド電圧を供給するモジュールグランド端子と、を各々電気的に分離して別々に備える。前記メモリデバイスは、前記第2電源モジュール端子から供給される電源と共に利用されるコア回路用グランド電圧を入力する第1デバイスグランド端子(VSS)と、前記第3電源モジュール端子から供給される電源と共に利用される外部出力及び外部入出力インターフェース用グランド電圧を入力する第2デバイスグランド端子(VSSQ)とを有する。前記コア層とビルドアップ層は前記モジュールグランド端子と前記第1及び第2デバイスグランド端子に接続するグランドパターン(GPTN)を有し、前記グランドパターンは、前記第1デバイスグランド端子に接続するパッド又はビアと、前記第2デバイスグランド端子に接続するパッド又はビアとを結ぶ線分の間にスリット(SLT)を有する。

【0022】

上記手段において、モジュールグランド端子と、前記コア層及びビルドアップ層のグランドパターンとは電気的に一体化され、電源系のような分離は行なわれていないから、ESD(Electrostatic Discharge)耐性の低下、リターンパス経路の阻害に寄る電気的特性の劣化、グランドレベルのずれ等の問題は生じない。異種グランド間でのノイズ回り込みの虞に対しては、前記スリットがグランドパターン上で異種グランドのビアやパッド間の電気的導通経路を長くする。要するに、グランドパターンの平面上において異種グランド間の電気的導通経路が長くなる。これにより、実装基板に搭載されたバスコンへの縦方向の電気的導通経路にAC的なノイズが誘導され易くなるから、電流が相対的に流れ易くなるから、結果として、異種グランド間でのグランドノイズの回り込みを抑制若しくは緩和することができる。

【0023】

信号配線のガードに利用されるグランドプレーン(55)の縁辺部分に対してもスリット(SLT)を適用することができる。即ち、前記第1デバイスグランド端子に接続するパッド若しくはビア、又は、前記第2デバイスグランド端子に接続するパッド若しくはビアと、信号配線に対向する前記グランドプレーンの縁辺との間に、スリットを形成する。信号配線のガードに利用されるグランドプレーンの縁辺部分には信号配線に並行してリターン電流が流れるが、スリットは前記信号配線に隣接する縁辺部分に対してリターンパスを確保するように作用し、且つ、リターンパスを流れる電流がノイズとしてデバイスのグランド端子に回り込むのを抑制する。

【0024】

〔7〕《メモリデバイスとデータ処理デバイスの配置》

本発明に係る半導体装置は、モジュール基板の一方の面に複数のメモリデバイスとデータ処理デバイスが搭載され、前記モジュール基板の他方の面に複数のモジュール端子が形成され、前記データ処理デバイスは、一つのコーナー部を基点とする両側の縁辺に沿って分割配置されたメモリインターフェース回路を有し、前記メモリデバイスはJEDEC標準の端子配列を備えたDDR2-SDRAMである。前記DDR2-SDRAMの長辺は、

10

20

30

40

50

前記メモリインターフェース回路が配置された前記データ処理デバイスの前記縁辺に対向して配置される。前記DDR2-SDRAMは、前記一つのコーナー部寄りの一つの短辺を基点に長辺に沿って、順次アドレス信号及びコマンドに関するコマンド及びアドレス系端子群とデータ及びデータストローブ信号に関するデータ系データ端子群とに分けた端子配置を有する。コマンド及びアドレス系端子群を対応するDDR2-SDRAMの端子に接続するための主なコマンド及びアドレス配線は、前記一つのコーナー部を基点に前記DDR2-SDRAMの間の領域を通り、途中で分岐して各々の前記DDR2-SDRAMの端子に至る経路を有する。

【0025】

モジュール基板上におけるデータ及びデータストローブ信号系の配線設計容易性と、モジュール基板上におけるコマンド及びアドレス系配線経路の等長化が容易になる。 10

【0026】

本発明の具体的な形態では、前記モジュール基板は前記データ処理デバイスから出力される差動クロック信号を前記メモリデバイスに伝達するための差動クロック配線を有し、前記差動クロック配線は前記主なコマンド及びアドレス配線の経路に沿って配置される。クロック信号はコマンド及びアドレス信号の取り込みタイミングを規定するからタイミングの整合という点において両者を並走させること、即ち同じトポロジとするのが好都合である。

【0027】

本発明の別の具体的な形態では、前記DDR2-SDRAMのデータ系データ端子群の端子と前記データ処理デバイスの対応端子とを接続するデータ及びデータストローブ信号系配線は、相互に対応するデータストローブ信号配線とデータ配線とが相互に等長化配線とされ、等長化配線の一部は等長化のために同一配線上に折り返し経路を有する。折り返し経路によってデータ及びデータストローブ信号系配線の等長化が容易になる。 20

【0028】

本発明の更に別の具体的な形態では、前記DDR2-SDRAMのコマンド及びアドレス系端子群の端子と前記データ処理デバイスの対応端子とを接続するコマンド及びアドレス系配線は、相互に等長化配線とされ、等長化配線は等長化のために同じDDR2-SDRAMへの相互に異なる配線間で伝播方向が逆にされた逆方向経路を一部に有する。逆方向経路によってコマンド及びアドレス系配線の等長化が容易になる。 30

【発明の効果】

【0029】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記の通りである。

【0030】

すなわち、マザーボード上における配線設計容易性や、モジュール基板（半導体パッケージ基板）上における配線設計容易性を実現可能にするマイクロコンピュータを得ることができる。

【0031】

8ビット又は16ビットのようにデータ入出力ビット数の仕様が異なる複数種類のメモリへの対応が容易なメモリインターフェース回路を備えたマイクロコンピュータを得ることができる。 40

【0032】

モジュール基板に複数の半導体デバイスを搭載する半導体装置の小型化に伴って、給電能力、グランドノイズ低減、配線の等長化等の点で信頼性を向上させることができる。

【発明を実施するための最良の形態】

【0033】

《マイクロコンピュータのメモリインターフェース回路配置》

図1には本発明に係るマイクロコンピュータにおけるメモリインターフェース形態が例示される。1はマイクロコンピュータ(MCU)であり、2,3はDDR2-SDRAMで 50

ある。特に 1 A はマイクロコンピュータチップ ( M C U \_ C H P ) を意味する。ここではマイクロコンピュータ 1 及び DDR 2 - S D R A M ( 以下単に S D R A M とも記す ) 2 , 3 は各々パッケージされ、プリント配線基板 ( P C B ) に実装される場合を想定する。 S D R A M 2 , 3 は B G A ( Ball Grid Array ) パッケージを有し、その端子配列は前記非特許文献 1 にて規定される。例えば並列データ入出力ビット数が  $\times 16$  ビットの場合における端子配列は図 2 に示される。この端子配列に従えば、データ及びデータストローブ系信号端子群とコマンド及びアドレス系端子群 C A P A が分離され、データ及びデータストローブ系信号端子群も上位バイトユニット端子群 U B P A と下位バイトユニット端子群 L B P A に分離される。それら端子群は、前記規格における A 1 番端子側の短辺を基点に、長辺に沿って、上位バイトユニット端子群 U B P A 、下位バイトユニット端子群 L B P A 10 、コマンド及びアドレス系端子群 C A P A の順に配列される。図 2 において、 D Q 0 ~ D Q 15 がデータ入出力端子、 L D Q S , L D Q S B は D Q 0 ~ D Q 7 の下位バイトデータに対する差動のデータストローブ端子、 U D Q S 、 U D Q S B は D Q 8 ~ D Q 15 の上位バイトデータに対する差動のデータストローブ端子、 A 0 ~ A 15 がアドレス入力端子、 B A 0 ~ B A 2 がバンクアドレス入力端子である。 R A S B , C A S B , W E B はコマンド入力端子、 C S B はチップ選択端子、 C K , C K B は差動のクロック入力端子、 C K E はクロックイネーブル端子、 L D M は D Q 0 ~ D Q 7 の下位バイトデータに対するデータマスク端子、 U D M は D Q 8 ~ D Q 15 の上位バイトデータに対するデータマスク端子である。 V D D , V D D Q はメモリ電源端子、 V S S 、 V S S Q はグランド端子である。 V D D Q 、 V S S Q は DDR 2 - S D R A M のデータ入出力系及びデータストローブ信号の入出力系回路 ( 外部出力及び外部入出力回路 ) の電源とグランドに専用化される。 V D D 、 V S S は DDR 2 - S D R A M のその他の回路 ( コア回路 ) の電源とグランドの外部端子とされる。ここでは V D D Q と V D D の電圧レベルは例えば 1.8 V で等しく、 V S S Q と V S S の電圧レベルも 0 V で等しいものとする。 V D D L , V S S D L は内部タイミングの生成に利用する D L L ( Delay Locked Loop ) 回路に専用の電源及びグランド電圧とされる。 V R E F は参照電位の入力端子であり、 S S T L ( Stub Series Terminated Transceiver Logic ) における外部インタフェース用の判定レベルが与えられる。 N C は非接続端子である。 20

#### 【 0 0 3 4 】

図 1 における配列 A と配列 B の双方において、マイクロコンピュータチップ ( 半導体チップ ) 1 A は、その一つのコーナー部を基点とする両側の縁辺に沿って S D R A M 2 , 3 のためのメモリインタフェース回路 4 , 5 が分割配置されている。分割配置する理由は次の通りである。即ち、 S D R A M のデータ及びデータストローブ系インタフェースはデータ 1 バイトにつき更にこれに対応するデータストローブ信号の差動対とデータマスク信号の 3 ビットの合計 11 ビットの I / O セルを必要とする。一つの I / O セルのセル幅を約 80  $\mu$ m とすると、 1 バイト分のインタフェース信号だけで少なくとも 880  $\mu$ m の幅が必要になる。電源および G N D セルが入ることを考慮して幅が約 2 倍になるとすると 1760  $\mu$ m を費やす。 4 バイト分でも 7040  $\mu$ m となり、データ及びデータストローブ系だけで 7 mm 以上の幅が必要になり、これを 1 辺に配置しようとすれば、 1 辺が 7 mm 以下の正方形チップは採用することができない。また、長辺が 7 mm 以上の長方形チップを採用してもよいが、そうすると、チップ上における回路位置と回路特性との相関が大きくなり、信頼性低下の虞が増すことになる。そこで、マイクロコンピュータチップ 1 A やパッケージの小型化に資することができ、マイクロコンピュータチップの信頼性も損なわないようにするために、前述のメモリインタフェース回路 4 , 5 の分割配置を採用した。 40

#### 【 0 0 3 5 】

図 1 において、マイクロコンピュータチップ 1 A に対する S D R A M 2 , 3 の接続形態として、 S D R A M 2 , 3 の短辺をマイクロコンピュータに対向させる形態 ( 配置 A ) と、 S D R A M 2 , 3 の長辺をマイクロコンピュータに対向させる形態 ( 配置 B ) とが示される。 B G A パッケージの端子ピッチが縦横同じであることに鑑みれば、長辺を対向させた方がマイクロコンピュータ 1 と S D R A M 2 , 3 とを接続する配線 ( P C B 配線 ) の密 50

度を低くするのが容易であるから、この点で配置 B が優れる。更に、SDRAM 2, 3 の端子配列は、その長辺に沿って、上位バイトユニット端子群 U B P A と下位バイトユニット端子群 L B P A とが分離されていることを考慮すると、配置 B を採用する方が、バイトユニット単位毎に P C B 配線を規則化することが容易になる。また、配置 B を採用することになれば、マイクロコンピュータチップ 1 A におけるメモリインターフェース回路 4, 5 のデータ及びデータストローブ信号系回路についてもバイトユニット単位毎に規則化することができ回路設計の容易化にも資することができる。これらの点においても配置 B が優れる。更に、データ及びデータストローブ系信号端子群から分離されたコマンド及びアドレス系端子群 C A P A をマイクロコンピュータ 1 のコーナー部寄りとすることによりそれら端子とマイクロコンピュータ 1 を接続する。P C B 配線は、マイクロコンピュータ 1 から引出した信号配線が 2 つに分岐し、分岐後の 2 本の配線長が等しい配線トポロジとすることができる（以下本明細書では、信号配線が 2 つに分岐し、分岐後の左右の配線長が等しい配線トポロジを「T 字型トポロジ」と記す）。この場合も配置 B の方が P C B 配線長が短くなる。図 1において U B C L は上位バイトユニット系 P C B 配線、L B C L は下位バイトユニット系 P C B 配線、C A C L はコマンド及びアドレス系 P C B 配線を意味する。

。

### 【 0 0 3 6 】

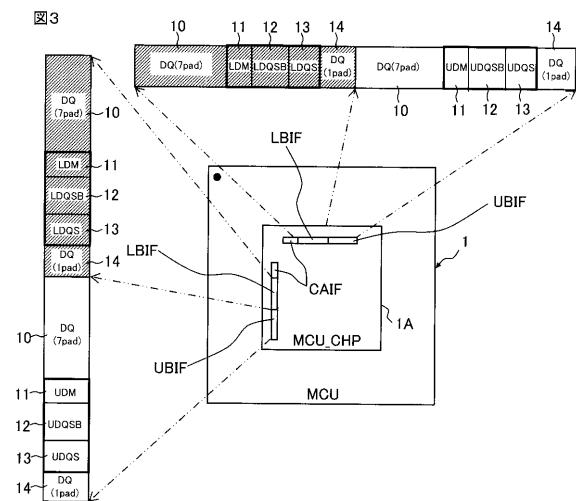

図 3 にはマイクロコンピュータ 1 のメモリインターフェース回路 4, 5 におけるデータ系ユニットのインターフェース機能が例示される。マイクロコンピュータ 1 において分割された各々のメモリインターフェース回路 4, 5 も、SDRAM 2, 3 の長辺に沿ったコマンド及びアドレス系端子群 C A P A 、下位バイトユニット端子群 L B P A 、上位バイトユニット端子群 U B P A の配置に対応して、コマンド及びアドレス系インターフェースユニット C A I F 及びデータ系ユニットとして 2 個のデータ系単位ユニットを持つ。一方のデータ系単位ユニットは上位データ系インターフェースユニット U B I F 、他方のデータ系単位ユニットは下位データ系インターフェースユニット L B I F である。コマンド及びアドレス系インターフェースユニット C A I F はコマンド及びアドレス系端子群 C A P A 等に接続されるアドレス出力及びコマンド入出力インターフェース回路を備える。各々のデータ系単位ユニット L B I F , U B I F はデータ入出力の単位をバイトとするものであり、回路構成それ自体は下位バイト対応であろうと上位バイト対応であろうと同じであり、データやストローブ信号の割り当てが相違されるだけである。J E D E C 標準の D D R 2 - S D R A M の端子配列によれば、D D R 2 - S D R A M は、その長辺に沿ってデータ及びデータストローブ信号系の端子群 U B P A , L B P A とコマンド及びアドレス系の端子群 C A P A は分離配置され、特に、並列データ入出力ビット数を 16 ビット ( × 16 ビット ) とするインターフェース仕様に対しては上位バイトのデータ及びデータストローブ信号系の上位バイトユニット端子群 U B P A と、下位バイトのデータ及びデータストローブ信号系の端子群 L B P A との配置も分離されている。この長辺をマイクロコンピュータ 1 のデータ系ユニット U B I F , L B I F に対向させたとき、バイトのデータ及びデータストローブ信号系の端子群 U B P A , L B P A からデータ系ユニット U B I F , L B I F に向く配線経路を単純化することができる。このことは、P C B における配線設計容易性や、モジュール基板（半導体パッケージ基板）上における配線設計容易性を保障することになる。

### 【 0 0 3 7 】

図 3 において各々のデータ系単位ユニット L B I F , U B I F は、マイクロコンピュータチップ 1 A の一つのコーナー部側から順に、7 個のデータ入出力回路 1 0 、データマスク信号回路 1 1 、反転データストローブ信号回路 1 2 、非反転データストローブ信号回路 1 3 、及び 1 個のデータ入出力回路 1 4 を有する。要するに、マイクロコンピュータチップにおけるパッド電極配置が上述の配置になると言ふことである。

### 【 0 0 3 8 】

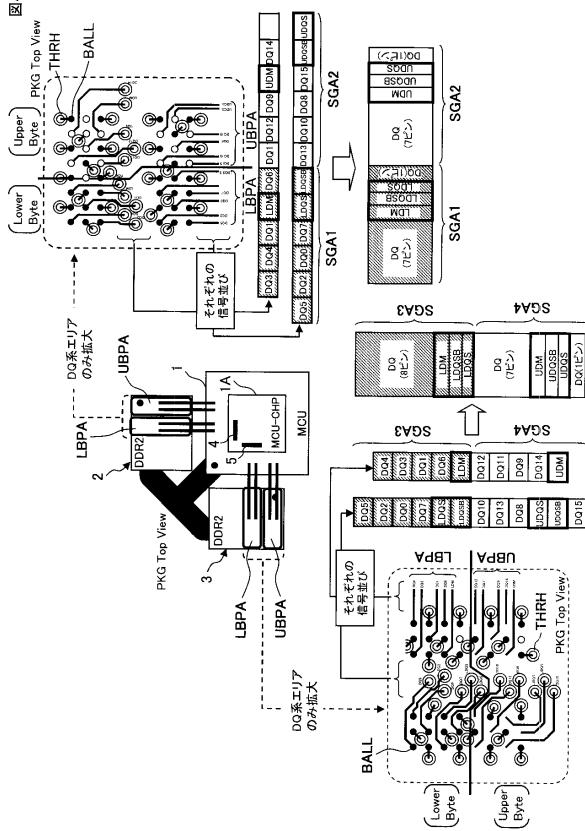

図 4 には図 3 のデータ系単位ユニット L B I F , U B I F におけるインターフェース機能の配置を採用する理由が示される。図 4 において S D R A M 2, 3 のボール電極 ( B A L L ) から P C B への配線引出し経路が例示されているが、ここではボール間を通る配線を

10

20

30

40

50

1本とし、P C B上では貫通スルーホール( T H R H )を用いて配線層間の接続を行なうものとする。要するに、低成本のP C Bを用いる場合を想定する。このときの引出し配線の信号配列は、S D R A M 2の下位バイトのデータ及びデータストローブ信号系の端子群L B P Aに対しては配列S G A 1となり、上位バイトのデータ及びデータストローブ信号系の端子群U B P Aに対しては配列S G A 2となる。S D R A M 3の下位バイトのデータ及びデータストローブ信号系の端子群L B P Aに対しては配列S G A 3となり、上位バイトのデータ及びデータストローブ信号系の端子群U B P Aに対しては配列S G A 4となる。前記信号配列S G A 1, S G A 2, S G A 4は等しく、それらに対して信号配列S G A 3はデータ1ビットの配列が相違されるだけである。そこで、図3で説明したデータ系単位ユニットL B I F, U B I Fにおけるインターフェース機能の配置を信号配列S G A 1, S G A 2, S G A 4と一致させる。要するに、マイクロコンピュータチップ1 Aにおけるメモリインターフェース回路4, 5のデータ及びデータストローブ信号系回路の構成をバイトユニット単位毎に同一として、その回路設計の容易化を優先させるようとする。高々1ビットのデータ端子配置をP C B配線に対して最適化するために一部の回路ユニットの構成を変更することを回避する。10

#### 【0039】

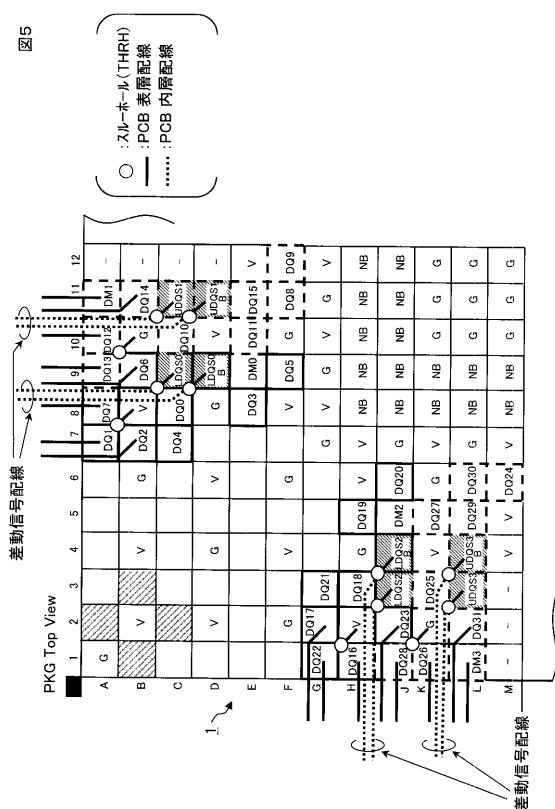

図5にはマイクロコンピュータ1のボール電極配置が例示される。実際にはボール電極は縦横方向に所定ピッチでマトリクス配置されているが、ここでは便宜上、個々のボール電極を正方形の枠として作図している。マイクロコンピュータのパッケージはB G A形態とされ、マイクロコンピュータチップのパッド電極はチップ表面のW P P配線(再配線層)を介して半田バンプ電極(図示せず)に接続され、半田バンプ電極はボール電極に接続される。ボール電極に対する端子機能の割り当てはD D R 2 - S D R A M 2, 3の端子及び引出し配線の配置(図4)とマイクロコンピュータチップにおけるパッド電極配置(図3、図4)との対応関係を極力維持できるようにすればよい。その一例が図5に例示される。20

#### 【0040】

ボール電極に対する端子機能の割り当てに関しては差動端子の配列を考慮している。即ち、L D Q SとL D Q S Bのペア、U D Q SとU D Q S Bのペア、C KとC K Bのペアは、ペア毎に、最外周より第1周目と第2周目の隣接するボール電極に割り当て、又は第3周目と第4周目の隣接するボール電極に割り当てて、差動端子を構成させる。ここではP C B上においてボール間を通る配線を1本とし、P C B上では貫通スルーホール( T H R H )を用いて配線層間の接続を行なうものとする。そうすると、ボールグリッドアレイの最外周より第1周目のボール電極に接続する配線はそのまま外側に引き出され、第2周目のボール電極に接続する配線は第1周目のボール電極に接続する2本の配線の間を通って外側に引き出される。第3周目と第4周目のボール電極に各々接続する配線は第1周目と第2周目のボール電極とは異なる配線層を通って同様に外側に引き出される。このような一般的な配線構造への対応を考慮すると、差動端子を第1周目と第2周目に隣接配置し、又は第3周目と第4周目に隣接配置することにより、差動端子に接続する配線は同一配線層上で隣接して相対することができるから、P C B上においても同相ノイズ成分のキャンセル効果を維持させることができ容易になる。なお、C KとC K Bのペアはコーナーに配置されることが多く、他エリアほど配線が密ではない。よって、C KとC K L Bのペアこの形態の限りではない。30

#### 【0041】

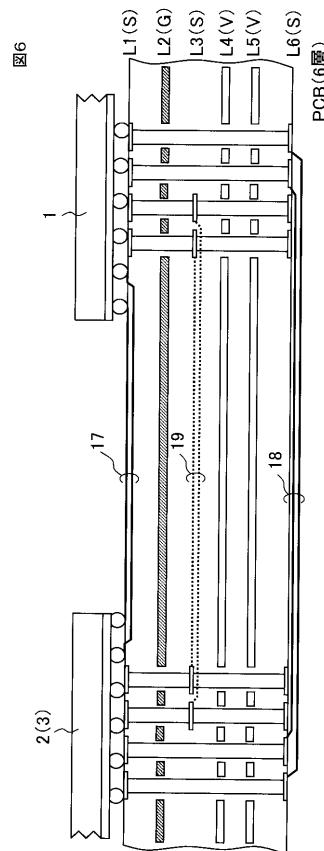

図6にはマイクロコンピュータとD D R 2 - S D R A MをP C Bに実装したときの縦断面図が例示される。ここでは6層のP C Bを示すが、配線層数はこれに限定されない。17、18はマイクロコンピュータ1とD D R 2 - S D R A Mを接続する表層配線を模式的に示す。19はマイクロコンピュータ1とD D R 2 - S D R A Mを接続する内層配線を模式的に示す。40

#### 【0042】

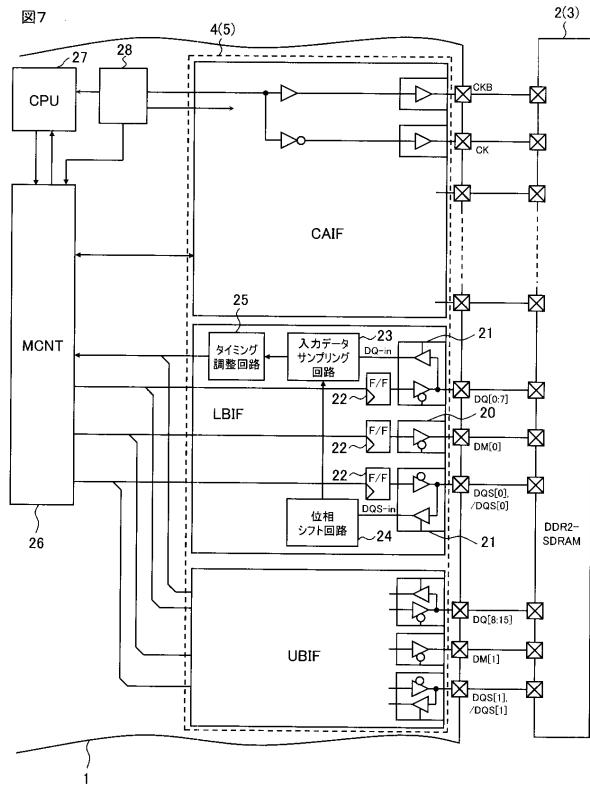

図7にはメモリインターフェース回路のデータ系単位ユニットL B I F, U B I Fの一例50

が示される。データ系単位ユニット L B I F , U B I F は、例えば出力バッファ 2 0 、出入力バッファ 2 1 、出力ラッチ 2 2 、入力データのサンプリング回路 2 3 、データストローブ信号に従って入力データのサンプリング信号を生成する位相シフト回路 2 4 、及びサンプリングデータの転送タイミングを調整するタイミング調整回路 2 5 を有する。データ系単位ユニット L B I F , U B I F はメモリコントローラ ( M C N T ) 2 6 に接続される。メモリコントローラ 2 6 は中央処理装置 ( C P U ) 2 7 からの D D R 2 - S D S R A M 2 , 3 に対するメモリアクセス要求に応答して、 D D R 2 - S D S R A M 2 , 3 のインターフェースプロトコルに従ったメモリアクセス制御を行う。このときデータ系単位ユニット L B I F , U B I F はメモリコントローラ 2 6 と D D R 2 - S D R A M 2 , 3 との間のインターフェースを行う。2 8 はクロック発生回路 ( C P G ) である。前記メモリコントローラの機能はバスステートコントローラで実現する場合もある。 10

#### 【 0 0 4 3 】

以上の説明では B G A 形態のパッケージに半導体チップを封止したマイクロコンピュータについて説明したが、チップの半田バンプ電極における端子機能の配列はパッケージのボール電極における端子機の配列と基本的に同じである。したがって、マイクロコンピュータチップ 1 A をそのままベアチップとして用いる用途においても、ボール電極の配置に関する技術的事項も含めて上記と同様の作用効果を得ることができる。

#### 【 0 0 4 4 】

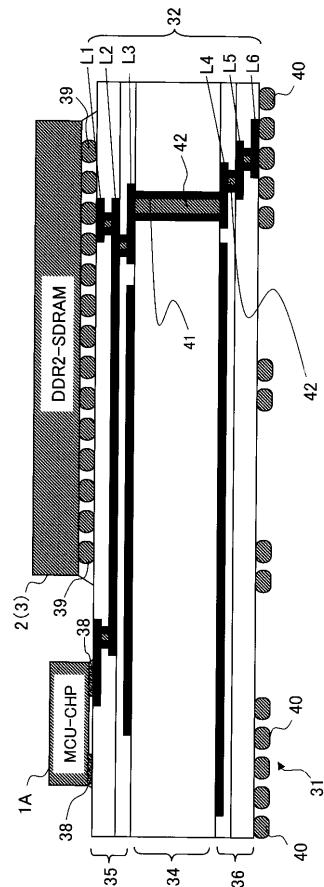

##### 《 マルチチップモジュール 》

図 8 には本発明に係る半導体装置の一例であるマルチチップモジュールの縦断面図が例示される。マルチチップモジュール 3 1 は、モジュール基板 3 2 の一面に、データ処理デバイスとして 1 個のマイクロコンピュータチップ ( M C U \_ C H P ) 1 A と、複数個のメモリデバイスとして 2 個の D D R 2 - S D R A M 2 ( 3 ) を有する。マイクロコンピュータチップ ( M C U \_ C H P ) 1 A と D D R 2 - S D R A M 2 ( 3 ) は、モジュール基板 3 2 との隙間がアンダーフィル樹脂 ( 図示せず ) で充填されている。このマルチチップモジュール 3 1 はシステム・イン・パッケージのマイコンモジュールとして位置付けられる。 20

#### 【 0 0 4 5 】

マイクロコンピュータチップ 1 A はベアチップであり、半田バンプ電極を下にして、モジュール基板 3 2 にフェースダウンで実装される。 D D R 2 - S D R A M 2 ( 3 ) は非特許文献 1 の J E D E C 標準を満足した図 2 の端子配置を備えたボールグリッドアレイのパッケージに封止されて構成される。 30

#### 【 0 0 4 6 】

モジュール基板 3 2 はコア層 3 4 とその表裏に形成されたビルドアップ層 3 5 、 3 6 とを有し、多層配線の樹脂基板として構成される。コア層 3 4 は例えば 0 . 8 m m 程度の厚みを有する。ビルドアップ層 3 5 は例えば 3 0 ~ 4 0  $\mu$  m 程度の厚みを有し、コア層 3 4 の側より配線層 L 3 、 L 2 、 L 1 が形成されている。ビルドアップ層 3 6 は例えば 3 0 ~ 4 0  $\mu$  m 程度の厚みを有し、コア層 3 4 の側より配線層 L 4 、 L 5 、 L 6 が形成されている。配線層 L 1 、 L 2 は、主にマイクロコンピュータチップ 1 A のバンプ電極 3 8 と、 D D R 2 - S D R A M 2 ( 3 ) のボール電極 3 9 とを接続するための配線の形成に利用される。配線層 L 3 は主にグランドプレーン ( グランドパターン ) の形成に利用される。配線層 L 4 は主に電源プレーンの形成に利用される。配線層 L 5 、 L 6 は、配線層 L 1 ~ L 4 に形成される信号配線、グランドプレーン及び電源プレーンをモジュール基板の外部接続端子であるモジュールボール電極 4 0 に接続するための配線の形成に利用される。図において 4 1 は代表的に示されたスルーホールでありコア層 3 4 を貫通する。 4 2 はビアであり、ビアホール若しくはスルーホールの内面に導電性メッキを施した導電部を総称し、その上下の配線層若しくは金属パターンを導通させる。 40

#### 【 0 0 4 7 】

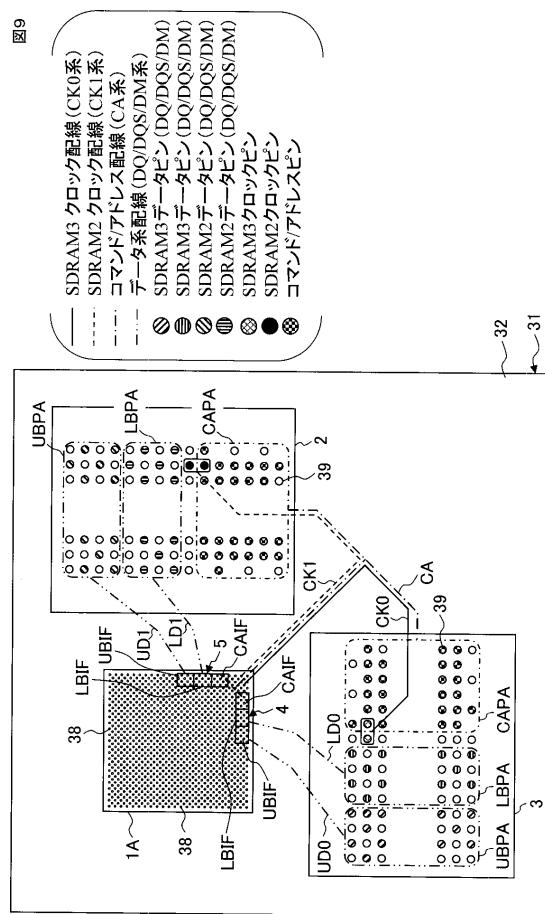

##### 《 アドレス・コマンド系のメモリインターフェース 》

図 9 にはマルチチップモジュール 3 1 の平面なレイアウト構成が例示される。モジュール基板 3 2 上におけるマイクロコンピュータチップ 1 A と D D R 2 - S D R A M 2 , 3 と 50

の相対位置関係は図1の配置Bと同じである。図1の配置Bにおいて、PCBをモジュール基板32に代え、マイクロコンピュータ1をマイクロコンピュータチップ1Aに代えて考えればよい。端子配列は図1の配置Bと等価である。

【0048】

マイクロコンピュータチップ1Aにおけるメモリインタフェース回路4,5の構成は図3等で説明したのと同じである。メモリインタフェース回路5の上位データ系インタフェースユニットUBIFとSDRAM2の上位バイトユニット端子群UBPAはモジュール基板32のデータ系配線UD1で接続される。メモリインタフェース回路5の下位データ系インタフェースユニットLBIIFとSDRAM2の下位バイトユニット端子群LBPAはモジュール基板32のデータ系配線LD1で接続される。メモリインタフェース回路4の上位データ系インタフェースユニットUBIFとSDRAM3の上位バイトユニット端子群UBPAはモジュール基板32のデータ系配線UD0で接続される。メモリインタフェース回路4の下位データ系インタフェースユニットLBIIFとSDRAM3の下位バイトユニット端子群LBPAはモジュール基板32のデータ系配線LD0で接続される。

10

【0049】

メモリインタフェース回路4,5のコマンド及びアドレス系インタフェースユニットCAIFを対応するSDRAM2,3のコマンド及びアドレス系端子群に接続するためのコマンド及びアドレス配線CAは、マイクロコンピュータチップ1Aの一つのコーナー部を基点に前記DDR2-SDRAM2,3の間の領域を通り、途中で分岐して各々の前記DDR2-SDRAM2,3の端子に至る経路を有する。T字形の配線トポロジにより、モジュール基板32上におけるコマンド及びアドレス系配線経路の等長化が容易になる。

20

【0050】

CK0はマイクロコンピュータチップ1Aのメモリインタフェース回路4からSDRAM3のクロック端子CK,CKBに差動クロックを供給する差動クロック配線である。同様に、CK1はマイクロコンピュータチップ1Aのメモリインタフェース回路5からSDRAM2のクロック端子CK,CKBに差動クロックを供給する差動クロック配線である。前記差動クロック配線CK0,CK1は前記主なコマンド及びアドレス配線CAの経路に沿って配置される。クロック信号CLK0,CK1はコマンド及びアドレス信号の取り込みタイミングを規定するからタイミングの整合という点において両者を並走させること、即ち同じトポロジとするのが好都合である。コマンド及びアドレス系のタイミングマージンを大きくすることが容易になる。

30

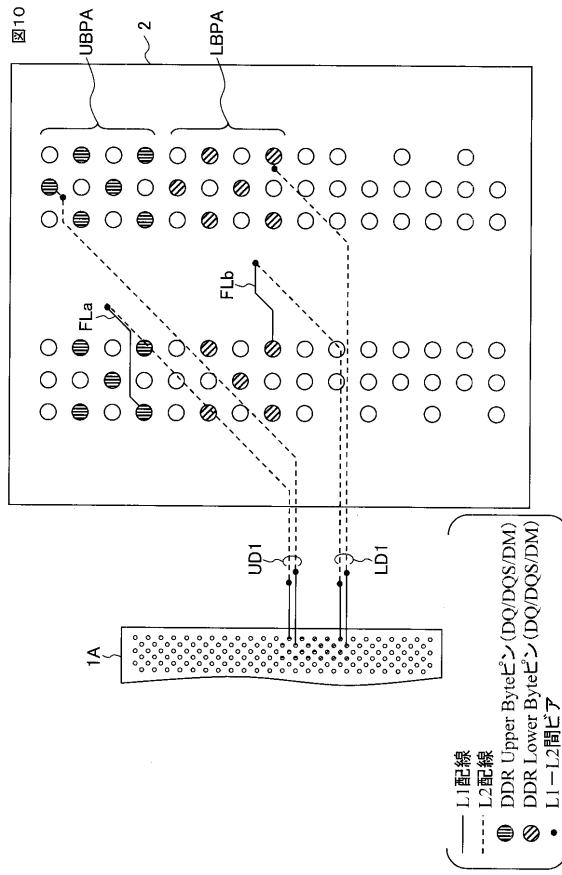

【0051】

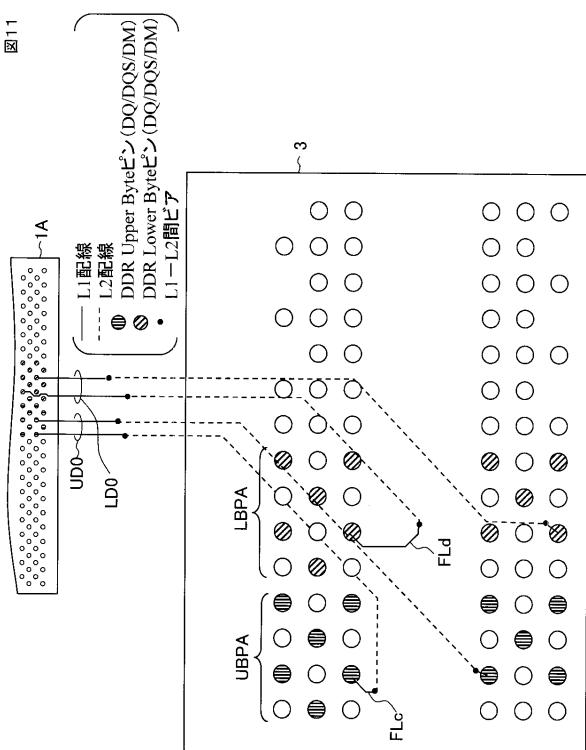

図10にはデータ系配線UD1,LD1に対する等長化経路の例が示される。図10より明らかにSDRAM2のバイトユニット端子群UBPAのボール電極は左右に離間しているから、同一バイト内のデータ及びデータストローブ端子に関し、最も大きな距離のある端子間の配線長に揃えることとし、端子間距離に比べてその配線長が長すぎる端子間配線については、等長化のために同一配線の一部に折り返し経路を形成する。図10には代表的に折り返し経路FLa,FLbが示されている。折り返し経路によってデータ及びデータストローブ信号系配線の等長化が容易になる。図11に例示されるようにマイクロコンピュータチップ1AとSDRAM3との間についてもどうようである。図11には代表的に折り返し経路FLc,FLdが示されている。

40

【0052】

図12にはコマンド及びアドレス系配線CAa~CAdに対する等長化経路の例が示される。T字形トポロジのコマンド及びアドレス系配線において、分岐点より後段には、L2配線の2本セット毎の間に距離DSTを取り、AR1,AR2の位置に代表されるように、信号毎にL1配線とL2配線との間のビア1個と配線1本を通すことができる余地を確保し、PNT1,PNT2に代表されるようにL2配線層の分岐位置を微調整可能にする。分基点以降において、等長化のために同じDDR2-SDRAMへの相互に異なる配線間で伝播方向が逆にされた逆方向経路を一部に有する。図12には代表的に逆方向経路RPa,RPbが示されている。逆方向経路RPa,RPbによってコマンド及びアドレ

50

ス系配線の等長化が容易になる。

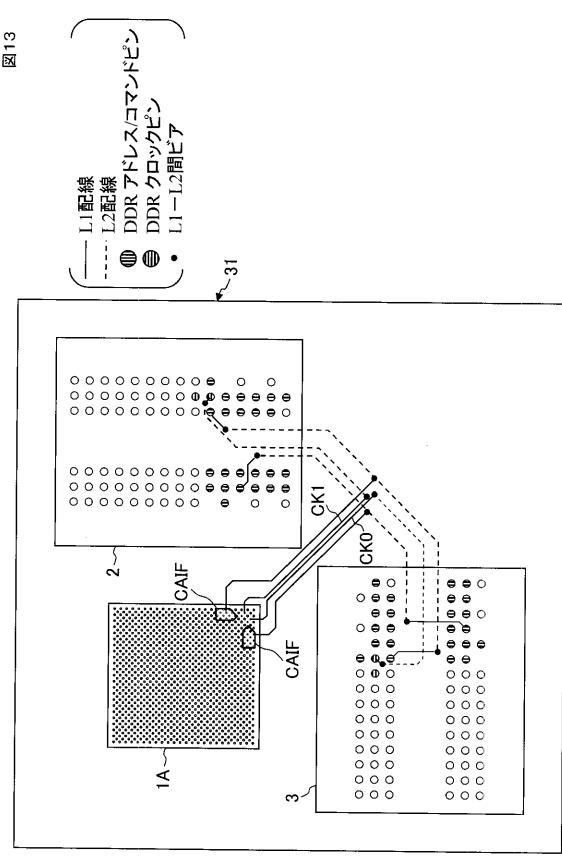

【0053】

図13にはクロック系配線CK0, CK1に対する等長化経路の例が示される。前述の通りクロック系配線CK0, CK1はT形トポロジのコマンド及びアドレス系配線に沿うように配線される。更に、コマンド及びアドレス系配線の真ん中に配置する。これにより、コマンド及びアドレス系配線のマイクロコンピュータとSDRAM間の最長配線と最短配線との各々の差分をそれぞれ均等化し易くなる。これにより、コマンド及びアドレスに関するタイミングマージンの確保が容易になる。

【0054】

《差動信号用ボール電極の配置》

10

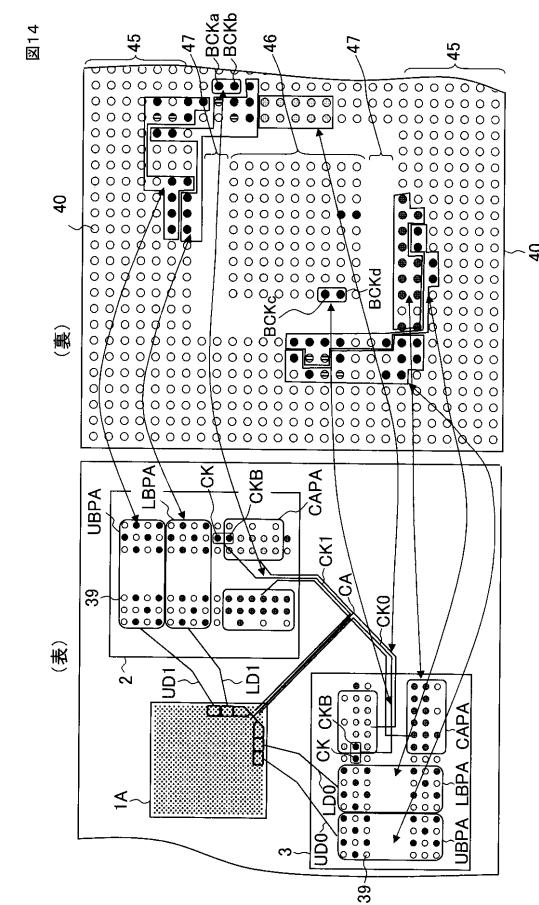

図14にはDDR2-SDRAM2, 3に対するテスト専用端子の配置が例示される。モジュール基板32の裏面に配置されたボール電極40は外周縁に沿って7周配置された周回電極部分45と、中央部の9行9列でマトリクス配置された中央電極部分46とを有する。周回電極部分45と中央電極部分46の間には空白領域47が確保されている。マルチチップモジュール31には、DDR2-SDRAM2, 3をマイクロコンピュータチップ1Aによるアクセス制御とは別に、外部による単独でテスト可能にするテスト用のボール電極が配置される。テスト用のボール電極の領域は、DDR2-SDRAM2, 3のボール電極39との対応が矢印で示されている。図より明らかなように、テスト用のボール電極は周回電極部分の内周寄りに配置されている。マルチチップモジュール31を搭載するマザーボード(プリント配線基板)上にマルチチップモジュール31を搭載するとき、マルチチップモジュール31の下側から側方に向けてPCB配線を引き出す場合、マルチチップモジュール31の周縁に近いほどマザーボード上における配引出しは容易である。したがって、テスト専用ボール電極の如くマザーボード上の配線に接続する必要のない端子は極力、モジュール基板の内側に集めた方が得策だからである。

20

【0055】

ここで、前記差動クロック配線CK1は、SDRAM2のクロック端子CK, CKBの近傍に配置された差動終端抵抗接続用の一対のボール電極BCKa, BCKbを有する。前記ボール電極BCKa, BCKbは、相互に隣接され、且つ、他のモジュール端子が配置されていない領域に隣接し又はテスト専用モジュール端子に隣接して形成されている。SDRAM3のための差動クロック配線CK0についても同様に、差動終端抵抗接続用の一対のボール電極BCKc, BCKdを有する。前記ボール電極BCKc, BCKdも相互に隣接され、且つ、他のモジュール端子が配置されていない領域に隣接し又はテスト専用モジュール端子に隣接して形成されている。

30

【0056】

マルチチップモジュール31が実装されるPCBにはテスト専用モジュール端子に接続されるべき配線は形成されていないから、差動終端抵抗接続用ボール電極BCKaとBCKb、BCKcとBCKdを、他のモジュール端子が配置されていない領域に隣接し又はテスト専用モジュール端子に隣接して形成することにより、当該差動終端抵抗接続用のボール電極BCKaとBCKb、BCKcとBCKdに各々直接終端抵抗を搭載することが容易になる。このことは分岐点から差動終端抵抗までの配線経路を極めて短く且つ等長化するのに好適である。この関係は、LDQSとLDQSb、UDQSとUDQSbのような差動データストローブ信号についても同様に適用すれば有効であるが、JEDDEC標準によれば、それら差動データストローブ信号についても、ODT(On-Die Termination)によるチップ内終端抵抗によって対策されることを期待することができる。差動クロック配線と同様の考慮を払わなくても実質的な問題は少ないと考えられる。

40

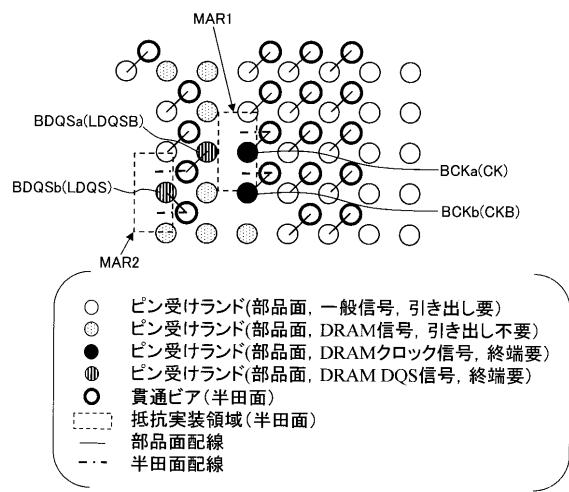

【0057】

図15にはSDRAM2のクロック端子CK, CKBの近傍に配置された差動終端抵抗接続用の一対のボール電極BCKa, BCKbと、差動データストローブ端子LDQS, LDQSbの近傍に配置された差動終端抵抗接続用の一対のボール電極BDQSa, BDQSbとの配置領域の詳細を例示する。差動終端抵抗接続用のボール電極BCKa, BCKb

50

K b は周回電極部分 4 5 の内周縁に配置されていないが、図において左隣には P C B 配線引出し不用のボール電極を配置してあるから、終端抵抗の実装領域 M A R 1 を確保することができる。また、差動終端抵抗接続用のボール電極 B D Q S a , B D Q S b の双方は周回電極部分 4 5 の内周縁に配置されていないが、図において右隣には P C B 配線引出し不用のボール電極を配置し、左側には空白領域 4 7 はあるので、終端抵抗の実装領域 M A R 2 を容易に確保することができる。

【 0 0 5 8 】

《 電源分離 》

D D R 2 - S D R A M 2 , 3 の動作電源は、 V D D Q , V S S Q が外部出力及び外部入出力回路用 ( I / O 用 ) の電源系端子セット、 V D D , V S S がコア回路用の電源系端子セットである。マイクロコンピュータチップ 1 A は、コア回路用と外部インターフェース回路用に別々の電源系端子セットを備える。更に、マイクロコンピュータチップ 1 A は、 S D R A M 2 , 3 にインターフェースされる前記インターフェース回路 4 , 5 の動作電源として V C C d d r 、 V S S d d r の電源系端子セットを有する。電源端子 V D D , V D D Q 、 V C C d d r の電源電圧は例えば 1 . 8 V である。グランド端子 V S S 、 V S S Q 、 V S S d d r のグランド電圧は 0 V である。特に制限されないが、マイクロコンピュータチップ 1 A のコア回路用電源セットは固有の電源系端子による 1 . 0 V と 0 V であり、その他の外部インターフェース回路用の電源セットはそれ固有の電源系端子による 3 . 3 V と 0 V である。

【 0 0 5 9 】

モジュール基板において、マイクロコンピュータチップ 1 A と D D R 2 - S D R A M 2 , 3 との間では動作電源経路が分離され、個別テストの便に供することができるようになっている。更に、 D D R 2 - S D S R A M アクセスに際して電源系ノイズが回り込みことを防止する観点より、 D D R 2 - S D R A M 2 , 3 の I / O 用電源端子 V D D Q とコア回路用電源端子 V D D とは相互に電気的に分離された固有の電源経路を経て接続された電源ボール電極が割り当てられる。 V S S 、 V S S Q 、 V S S d d r に接続するボール電極は電気的に分離されていない。 E S D 耐性の確保と電気的基準の安定化を確保するためである。

【 0 0 6 0 】

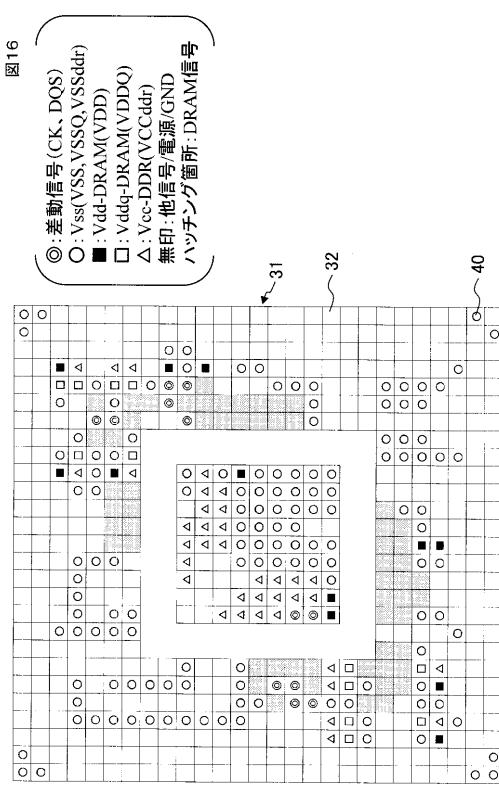

図 16 にはモジュール基板の電源用ボール電極の配置が例示される。 V d d - D R A M は S D R A M 2 , 3 の電源端子 V D D に割り当てられた電源ボール電極、 V d d q - D R A M は S D R A M 2 , 3 の電源端子 V D D Q に割り当てられた電源ボール電極、 V c c - D D R はマイクロコンピュータチップ 1 A の電源端子 V C C d d r に割り当てられた電源ボール電極、 V s s は、 V S S , V S S Q , V S S d d r に割り当てられたグランドボール電極である。

【 0 0 6 1 】

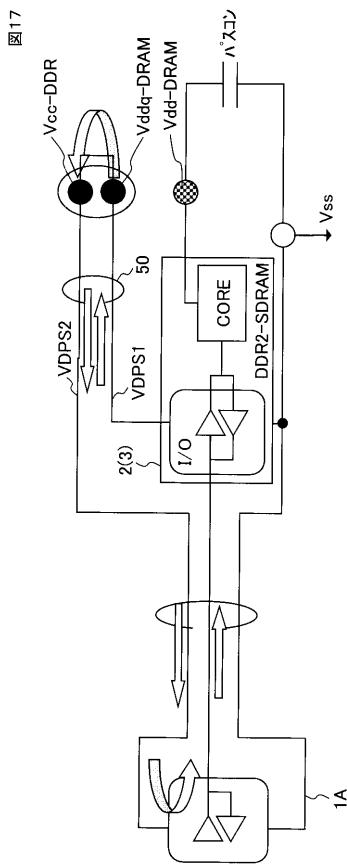

図 17 には M C U - C H P 1 A から D D R - S D R A M 2 に出力される信号の変化に伴う電源系の帰還電流経路が模式的に示される。 V c c - D D R と V d d q - D R A M とが分離されているとき、 M C U - C H P 1 A と D D R 2 - S D R A M 2 との間で信号が充放電されると、その充放電電流のうち電源配線に流れる帰還電流の経路 V D P S 1 と V D P S 2 はモジュール基板 3 2 上において V d d q - D R A M と V c c - D D R とによって分断され、マザーボード上の電源配線若しくは電源プレーンを介して帰還されなければならない。このことが電源系のインピーダンス増加を招くことになるが、これを極力抑制するために、 V c c - D D R と V d d q - D R A M を直近に配置してある。これにより、 5 0 で示されるように V c c - D D R と V d d q - D R A M とを流れる逆方向の電流をカップリングさせて実効インダクタンスを減らすことができる。

【 0 0 6 2 】

《 メモリコアへの給電ビア複数化 》

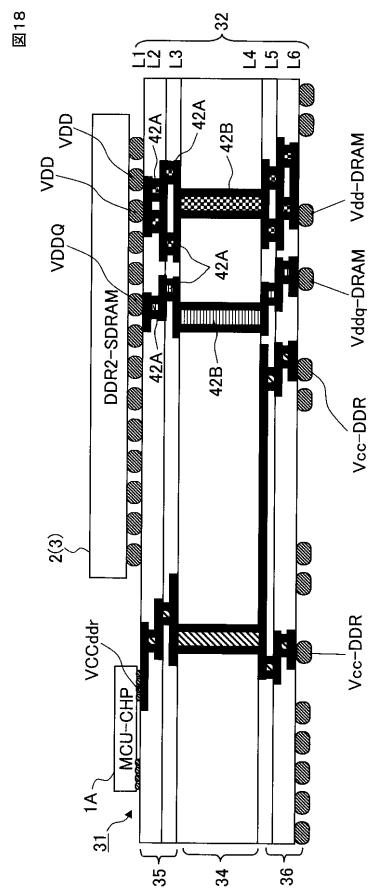

図 18 には主な電源系に着目したときのマルチチップモジュール 3 1 の縦断面構造が例示される。 D D R 2 - S D R A M 2 , 3 は I / O 回路に比べてコア回路の消費電力の方が

10

20

30

40

50

大きい。リフェレッシュ動作時の比較的大きな電力消費を考慮しなければならないからである。ここで、ビルドアップ層 35、36 に形成された 1 個のビア 42A の給電面積はコア層 34 に形成された 1 個のビア 42B の給電面積よりも小さい。このとき、Vdd-DRAM を VDD に接続する給電経路において前記コア層 34 の 1 個のビア 42B に対してビルドアップ層の各層に形成されるビア 42A の数は 2 個とされる。Vddq-DRAM を VDDQ に接続する給電経路において前記コア層 34 の 1 個のビア 42B に対してビルドアップ層 35、36 の各層に形成されるビア 42A の数は 1 個とされる。メモリデバイスのコア回路による消費電力が I/O 回路部分よりも大きくなることを考慮したとき、コア層のビアに比べて導電面積の小さなビルドアップ層のビアによる電流供給能力不足を生じないようにすることができる。

10

#### 【0063】

##### 《グランドスリットによるノイズ対策》

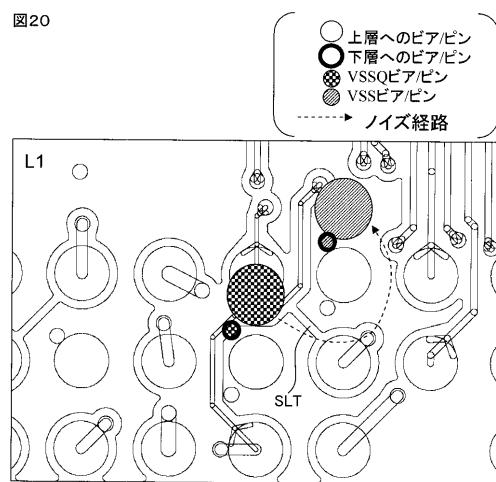

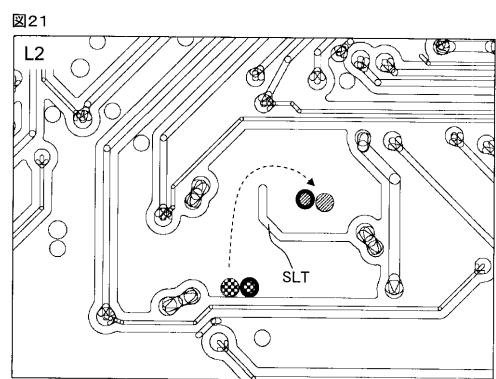

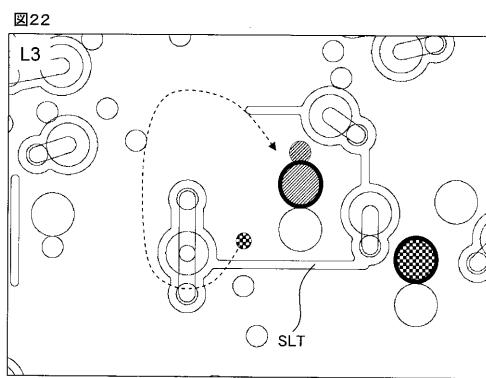

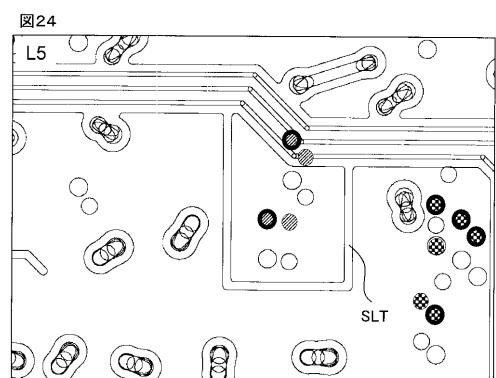

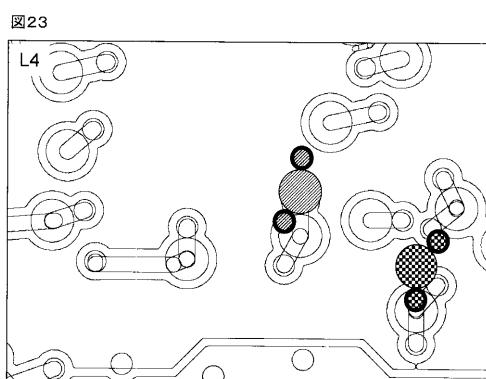

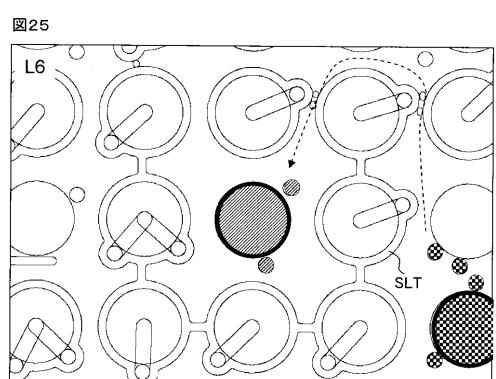

図 19 にはグランド端子 VSS, VSSQ とグランドボール電極 Vss を接続する経路の縦断面構造が例示される。前述のようにデバイス上で分離されているグランド端子 VSS, VSSQ はモジュール基板内では電気的に導通され、電気的に共通のグランドボール電極 Vss に接続される。このとき、前記コア層とビルドアップ層は、グランド端子 VSS, VSSQ 及びグランドボール電極 Vss に導通するグランドパターン GPTN を有し、面積を大きくして極力グランド電位の安定化を図ろうとしている。即ち、グランド端子 VSS, VSSQ 及びグランドボール電極 Vss と、前記コア層及びビルドアップ層のグランドパターン GPTN とは電気的に一体化され、電源系のような分離は行なわれていないから、ESD (Electrostatic Discharge) 耐性の低下、リターンパス経路の阻害に寄る電気的特性の劣化、グランドレベルのずれ等の問題を生じ難い。一方、グランドを DC 的に全て共通化すると、VSS と VSSQ のような異種グランド間でのノイズ回り込みの虞を生ずる。これに対し、前記グランドパターン GPTN は、デバイスグランド端子 VSS に接続するパッド又はビアと、前記デバイスグランド端子 VSSQ に接続するパッド又はビアとを結ぶ線分の間にスリット SLT を有する。図 20 乃至図 25 には各配線層 L1 ~ L6 の状態が例示される。ここでは L4 配線層は基本的に電源プレーンに利用されるのでグランドパターンは存在していない。

20

#### 【0064】

前記スリット SLT がグランドパターン GPTN 上で異種グランドのビアやパッド間の電気的導通経路を長くする。要するに、グランドパターン GPTN の平面上において異種グランド間の電気的導通経路が長くなる。これにより、実装基板上でグランドビア 52G と電源ビア 52V との間に搭載されたバスコン 53 への縦方向の電気的導通経路に A/C 的なノイズが誘導され易くなるから、結果として、異種グランド間でのグランドノイズの回り込みを抑制若しくは緩和することができる。

30

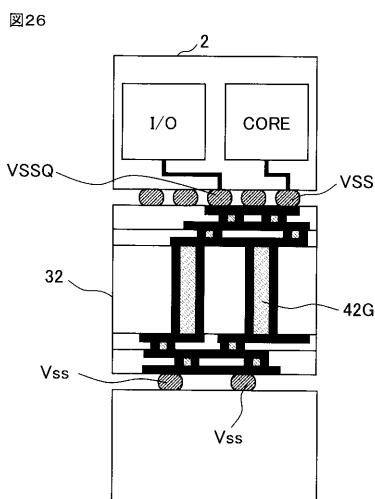

#### 【0065】

図 26 にはスリット SLT を形成しない場合の比較例が示される。VSS と VSSQ の間では L1 層のグランパターン GPTN を介して異種電源の回り込みを生ずる。

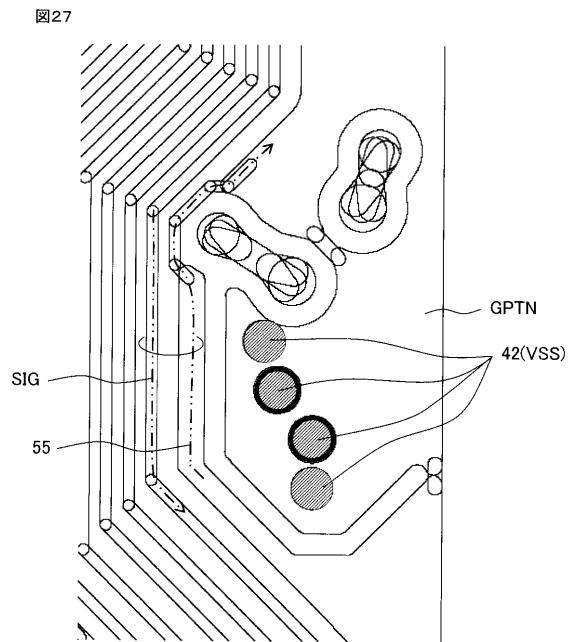

#### 【0066】

図 27 には信号配線のガードに利用されるグランドプレーンの縁辺部分にスリットを適用した例が示される。例えばグランド端子 VSS に接続するビア 42G (VSS) グランドプレーン GPTN に着目すると、このグランドプレーン GPTN の縁辺部分 55 が信号配線 SIG に対向するグランドガードとし利用されているとき、前記グランドプレーンの縁辺部分 55 とビア 42G (VSS) との間に、スリット SLT を形成する。信号配線のガードに利用されるグランドプレーンの縁辺部分 55 には信号配線 SIG に並行してリターン電流が流れるが、スリット SLT は前記信号配線 SIG に隣接する縁辺部分 55 に対してリターンパスを確保するように作用し、且つ、リターンパスを流れる電流がノイズとしてデバイス 2 のグランド端子 VSS に回り込むのを抑制することができる。スリットを形成する時に考慮すべきビアやパッドは VSSQ に接続するものであってもよい。

40

#### 【0067】

50

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0068】

例えば、DDR2-SDRAMの並列データ入出力ビット数は×8等であってもよい。マイクロコンピュータは汎用コントローラに限定されず、グラフィックコントローラ、符号化・複合処理を行なうコントローラなどであってよい。

【図面の簡単な説明】

【0069】

【図1】本発明に係るマイクロコンピュータにおけるメモリインターフェース形態を例示する説明図である。

【図2】×16のデータ入出力を行なうDDR2-SDRAMの端子配列を例示する説明図である。

【図3】マイクロコンピュータのメモリインターフェース回路におけるデータ系ユニットのインターフェース機能を例示する平面図である。

【図4】図3のデータ系単位ユニットLBIFF,UBIFFにおけるインターフェース機能の配置を採用する理由を示す説明図である。

【図5】マイクロコンピュータのボール電極配置を例示する平面図である。

【図6】マイクロコンピュータとDDR2-SDRAMをPCBに実装したときの縦断面図である。

【図7】メモリインターフェース回路のデータ系単位ユニットLBIFF,UBIFFの一例を示すブロック図である。

【図8】本発明に係る半導体装置の一例であるマルチチップモジュールの縦断面図である。

【図9】図8のマルチチップモジュールの平面なレイアウト構成を例示する平面図である。

【図10】SDRAMとの間のデータ系配線に対する等長化経路の例を示す平面図である。

【図11】SDRAMとの間のデータ系配線に対する等長化経路の別の例を示す平面図である。

【図12】SDRAMとの間のコマンド及びアドレス系配線に対する等長化経路の例を示す平面図である。

【図13】SDRAMとの間のクロック系配線に対する等長化経路の例を示す平面図である。

【図14】DDR2-SDRAMに対するテスト専用端子の配置を例示する平面図である。

【図15】SDRAMのクロック端子CK,CKBの近傍に配置された差動終端抵抗接続用の一対のボール電極と、差動データストローブ端子の近傍に配置された差動終端抵抗接続用の一対のボール電極との配置領域の詳細を例示する平面図である。

【図16】モジュール基板の電源用ボール電極の配置を例示する平面図である。

【図17】MCU-CHPからDDR-SDRAMに出力される信号の変化に伴う電源系の帰還電流経路を模式的に示す説明図である。

【図18】主な電源系に着目したときのマルチチップモジュールの縦断面構造を例示する断面図である。

【図19】グランド端子とグランドボール電極を接続する経路の縦断面構造を例示する断面図である。

【図20】モジュール基板のL1配線層におけるグランドパターンのスリットを例示する平面図である。

【図21】モジュール基板のL2配線層におけるグランドパターンのスリットを例示する平面図である。

10

20

30

40

50

【図22】モジュール基板のL3配線層におけるグランドパターンのスリットを例示する平面図である。

【図23】モジュール基板のL4配線層における電源プレーンとグランドビアとに関係を例示する平面図である。

【図24】モジュール基板のL5配線層におけるグランドパターンのスリットを例示する平面図である。

【図25】モジュール基板のL6配線層におけるグランドパターンのスリットを例示する平面図である。

【図26】グランドプレーンにスリットを形成しない場合の比較例を示す断面図である。

【図27】信号配線のガードに利用されるグランドプレーンの縁辺部分にスリットを適用した例を示す平面図である。 10

【符号の説明】

【0070】

1 マイクロコンピュータ (MCU)

2, 3 DDR2 - SDRAM

4, 5 メモリインターフェース回路

1A マイクロコンピュータチップ (MCU\_CHP)

DQ0 ~ DQ15 データ入出力端子

LDQS, LDQS\_B 下位バイトデータに対する差動データストローブ端子

UDQS, UDQS\_B 上位バイトデータに対する差動データストローブ端子

A0 ~ A15 アドレス入力端子

BA0 ~ BA2 バンクアドレス入力端子

RASB, CASB, WEB コマンド入力端子

Csb チップ選択端子

CK, CKB 差動のクロック入力端子

LDM 下位バイトデータに対するデータマスク端子

UDM 上位バイトデータに対するデータマスク端子

VDD, VDDQ メモリ電源端子

VSS, VSSQ グランド端子

VCCddr MCUのメモリインターフェース回路用電源端子

UBCL 上位バイトユニット系PCB配線

LBCL 下位バイトユニット系PCB配線

CACL コマンド及びアドレス系PCB配線

CAPA コマンド及びアドレス系端子群

LBPA CAPA、下位バイトユニット端子群

UBPA 上位バイトユニット端子群

CAIF コマンド及びアドレス系インターフェースユニット

UBIF 上位データ系インターフェースユニット

LBIF 下位データ系インターフェースユニット

10 データ入出力回路

11 データマスク信号回路

12 反転データストローブ信号回路

13 非反転データストローブ信号回路

14 データ入出力回路14

20 入出力バッファ

21 出力バッファ

22 出力ラッチ

26 メモリコントローラ (MCNT) 26

27 中央処理装置 (CPU)

32 モジュール基板

10

20

30

40

50

【図3】

【図4】

【 図 5 】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

図15

【図16】

図16

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図24】

【図23】

【図25】

【図26】

【図27】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 21/822 (2006.01) H 01 L 27/04 D

(72)発明者 松井 重純

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 杉田 憲彦

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 福島 義治

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

審査官 内田 正和

(56)参考文献 国際公開第2005/091367 (WO, A1)

特開2004-030641 (JP, A)

特開2001-094032 (JP, A)

特開2005-032417 (JP, A)

特開2005-340247 (JP, A)

特開2000-174505 (JP, A)

特開平11-67970 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |          |

|--------|----------|

| G 06 F | 1 / 18   |

| G 06 F | 12 / 00  |

| G 06 F | 13 / 16  |

| G 06 F | 15 / 78  |

| H 01 L | 21 / 822 |

| H 01 L | 27 / 04  |