(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-86752

(P2007-86752A)

(43) 公開日 平成19年4月5日(2007.4.5)

| (51) Int.C1.                | F 1                          | テーマコード (参考)                           |

|-----------------------------|------------------------------|---------------------------------------|

| <b>G09G 5/00</b> (2006.01)  | G09G 5/00                    | 520V 5C058                            |

| <b>G09G 5/391</b> (2006.01) | G09G 3/20                    | 650M 5C080                            |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20                    | 650A 5C082                            |

| <b>G09G 3/30</b> (2006.01)  | G09G 3/20                    | 650B                                  |

| <b>G09G 5/02</b> (2006.01)  | G09G 3/30                    | H                                     |

|                             |                              | 審査請求 未請求 請求項の数 26 O L (全 69 頁) 最終頁に続く |

| (21) 出願番号                   | 特願2006-223585 (P2006-223585) | (71) 出願人 000153878                    |

| (22) 出願日                    | 平成18年8月18日 (2006.8.18)       | 株式会社半導体エネルギー研究所                       |

| (31) 優先権主張番号                | 特願2005-240506 (P2005-240506) | 神奈川県厚木市長谷398番地                        |

| (32) 優先日                    | 平成17年8月22日 (2005.8.22)       | (72) 発明者 小山 潤                         |

| (33) 優先権主張国                 | 日本国 (JP)                     | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内       |

|                             |                              | (72) 発明者 傅保 洋樹                        |

|                             |                              | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内       |

|                             |                              | (72) 発明者 木村 肇                         |

|                             |                              | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内       |

|                             |                              | F ターム (参考) 5C058 AA11 AA18 BB25       |

|                             |                              | 最終頁に続く                                |

(54) 【発明の名称】表示装置及びその駆動方法

## (57) 【要約】

【課題】ビデオ信号として輝度信号、及び色差信号が入力されても、R、G、Bの三原色信号が入力されても正しいビデオ信号がディスプレイに入力され、且つビデオ信号がデジタル信号の場合にも対応した表示装置を提供することを目的とする。

【解決手段】発色が異なる複数のピクセルで画素が構成される表示パネルと、輝度情報と色差情報を含む輝度色差信号が入力され、該輝度色差信号をピクセルの発光色に応じたR G B信号に変換するビデオフォーマット変換回路と、R G B信号が入力され駆動タイミングに合わせて該R G B信号を表示パネルに出力するコントローラとを表示装置に設ける。ビデオフォーマット変換回路により、R G B信号と輝度色差信号とを切り替えて表示することができ、コントラストが改善され画質を良くすることができる。ビデオ信号の処理系統をフルデジタル化することができ、ノイズに強い回路構成とすることができます。

【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

発色が異なる複数のピクセルで画素が構成される表示パネルと、

ビデオフォーマット変換回路とを有する表示装置であって、

輝度情報と色差情報を含む輝度色差信号が前記ビデオフォーマット変換回路に入力され、

前記ビデオフォーマット変換回路は該輝度色差信号を前記ピクセルの発光色に応じた、前

記表示パネルのための R G B 信号に変換すること

を特徴とする表示装置。

**【請求項 2】**

発色が異なる複数のピクセルで画素が構成される表示パネルと、

ビデオフォーマット変換回路と、

D / A 変換回路とを有する表示装置であって、

輝度情報と色差情報を含む輝度色差信号が前記ビデオフォーマット変換回路に入力され、

前記ビデオフォーマット変換回路は該輝度色差信号を前記ピクセルの発光色に応じたデジ

タル形式の R G B 信号に変換し、

前記 D / A 変換回路は前記デジタル形式の R G B 信号を、前記表示パネルのためのアナロ

グ形式の R G B 信号に変換すること

を特徴とする表示装置。

**【請求項 3】**

発色が異なる複数のピクセルで画素が構成される表示パネルと、

ビデオフォーマット変換回路と、

入力切替回路とを有する表示装置であって、

前記ビデオフォーマット変換回路は、輝度情報と色差情報を含む輝度色差信号が入力され

るとき、画像信号が R G B 信号又は輝度色差信号のどちらであるかを示すモード信号に応

じて、該輝度色差信号を前記ピクセルの発光色に応じた R G B 信号に変換し、

前記モード信号と、 R G B 信号又は前記ビデオフォーマット変換回路から出力された R G

B 信号とが前記入力切替回路に入力され、前記入力切替回路は該モード信号に応じて、前

記表示パネルのための、 R G B 信号又は輝度色差信号から変換された R G B 信号の一方を

出力すること

を特徴とする表示装置。

**【請求項 4】**

発色が異なる複数のピクセルで画素が構成される表示パネルと、

信号判別回路と、

ビデオフォーマット変換回路と、

入力切替回路とを有する表示装置であって、

前記信号判別回路は、入力信号が乗せられているバスラインの本数から入力信号が R G B

信号と、輝度情報と色差情報を含む輝度色差信号のどちらであるかを判別してモード信号

を生成し、

前記ビデオフォーマット変換回路は前記モード信号に応じて輝度色差信号を R G B 信号に

変換し、

モード信号と、 R G B 信号又はビデオフォーマット変換回路から出力された R G B 信号と

が前記入力切替回路に入力され、前記入力切替回路は、前記モード信号に応じて、前記表示

パネルのための、 R G B 信号又は輝度色差信号から変換された R G B 信号の一方を出力

すること

を特徴とする表示装置。

**【請求項 5】**

複数のピクセルで画素が構成される表示パネルと、

前記表示パネルに接続されたビデオフォーマット変換回路と、

前記ビデオフォーマット変換回路に接続された入力切替回路とを有すること

を特徴とする表示装置。

10

20

30

40

50

**【請求項 6】**

複数のピクセルで画素が構成される表示パネルと、

前記表示パネルに接続された信号判定回路と、

前記信号判定回路に接続されたビデオフォーマット変換回路と、

前記ビデオフォーマット変換回路に接続された入力切替回路とを有すること

を特徴とする表示装置。

**【請求項 7】**

発色が異なる複数のピクセルで画素が構成される表示パネルを有する表示装置の駆動方法

であって、

輝度情報と色差情報を含む輝度色差信号がビデオフォーマット変換回路に入力されるとき

、画像信号が R G B 信号又は輝度色差信号のどちらであるかを示すモード信号に応じて、

前記ビデオフォーマット変換回路にて該輝度色差信号を前記ピクセルの発光色に応じた R

G B 信号に変換し、

前記モード信号と、 R G B 信号又は前記ビデオフォーマット変換回路から出力された R G

B 信号を、前記ビデオフォーマット変換回路から前記入力切替回路に入力し、

該モード信号に応じて、前記表示パネルのための、 R G B 信号又は輝度色差信号から変換

された R G B 信号の一方を前記入力切替回路から出力すること

を特徴とする表示装置の駆動方法。

**【請求項 8】**

発色が異なる複数のピクセルで画素が構成される表示パネルを有する表示装置の駆動方法

であって、

信号判別回路に信号を入力し、

前記信号判別回路にて入力信号が乗せられているバスラインの本数から入力信号が R G B

信号と、輝度情報と色差情報を含む輝度色差信号のどちらであるかを判別し、

前記信号判別回路にてモード信号を生成し、

前記ビデオフォーマット変換回路にて前記モード信号に応じて輝度色差信号を R G B 信号

に変換し、

モード信号と、 R G B 信号又はビデオフォーマット変換回路から出力された R G B 信号と

を前記入力切替回路に入力し、

前記モード信号に応じて、前記表示パネルのための、 R G B 信号又は輝度色差信号から変

換された R G B 信号の一方を前記入力切替回路から出力すること

を特徴とする表示装置の駆動方法。

**【請求項 9】**

請求項 1 において、

コントローラを有し、

前記 R G B 信号は前記ビデオフォーマット変換回路から前記コントローラに入力され、前

記コントローラは、前記表示パネルに前記 R G B 信号を出力すること

を特徴とする表示装置。

**【請求項 10】**

請求項 2 において、

コントローラを有し、

前記アナログ形式の R G B 信号は前記コントローラに入力され、前記コントローラは、前

記表示パネルに前記アナログ形式の R G B 信号を出力すること

を特徴とする表示装置。

**【請求項 11】**

請求項 3 において、

コントローラを有し、

前記 R G B 信号又は輝度色差信号から変換された R G B 信号が前記入力切替回路から前記

コントローラに入力され、前記コントローラは該 R G B 信号を前記表示パネルに出力する

こと

10

20

30

40

50

を特徴とする表示装置。

【請求項 1 2】

請求項 4 において、

コントローラを有し、

前記 R G B 信号又は輝度色差信号から変換された R G B 信号が前記入力切替回路から前記コントローラに入力され、前記コントローラは該 R G B 信号を前記表示パネルに出力すること

を特徴とする表示装置。

【請求項 1 3】

請求項 5 において、

コントローラを有し、

前記コントローラは前記入力切替回路に接続されていることを特徴とする表示装置。

【請求項 1 4】

請求項 6 において、

コントローラを有し、

前記コントローラは前記入力切替回路に接続されていることを特徴とする表示装置。

【請求項 1 5】

請求項 1 において、

前記ビデオフォーマット変換回路が一つの I C チップに配置されていることを特徴とする表示装置。

【請求項 1 6】

請求項 2 において、

前記ビデオフォーマット変換回路が一つの I C チップに配置されていることを特徴とする表示装置。

【請求項 1 7】

請求項 3 において、

前記ビデオフォーマット変換回路及び前記入力切替回路が一つの I C チップに配置されていることを特徴とする表示装置。

【請求項 1 8】

請求項 4 において、

前記ビデオフォーマット変換回路及び前記入力切替回路が一つの I C チップに配置されていることを特徴とする表示装置。

【請求項 1 9】

請求項 5 において、

前記ビデオフォーマット変換回路及び前記入力切替回路が一つの I C チップに配置されていることを特徴とする表示装置。

【請求項 2 0】

請求項 6 において、

前記ビデオフォーマット変換回路及び前記入力切替回路が一つの I C チップに配置されていることを特徴とする表示装置。

【請求項 2 1】

請求項 1 において、

前記表示パネルはデジタル階調方式で表示を行うこと

を特徴とする表示装置。

10

20

30

40

50

**【請求項 2 2】**

請求項 3 において、

前記表示パネルはデジタル階調方式で表示を行うことを特徴とする表示装置。

**【請求項 2 3】**

請求項 4 において、

前記表示パネルはデジタル階調方式で表示を行うことを特徴とする表示装置。

**【請求項 2 4】**

請求項 1 において、

前記輝度色差信号及び R G B 信号はデジタル信号であることを特徴とする表示装置。

**【請求項 2 5】**

請求項 3 において、

前記輝度色差信号及び R G B 信号はデジタル信号であることを特徴とする表示装置。

**【請求項 2 6】**

請求項 4 において、

前記輝度色差信号及び R G B 信号はデジタル信号であることを特徴とする表示装置。

10

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、カラー表示を行う表示装置であって、特に色空間変換機能を備えた表示装置に関する。

**【背景技術】****【0 0 0 2】**

液晶、エレクトロルミネセンス等の表示パネルに画像を表示させるには、走査信号と同期するビデオ信号が必要である。ビデオ信号は明るさと色の情報を持つものである。ビデオ信号としては、符号化された信号の他に、符号化されていないビデオ信号が用いられる場合がある。これらのビデオ信号は、輝度信号及び色差信号で構成されている。そして、ビデオ信号として符号化されていない画像データを入力した場合は、赤( R )、緑( G )、青( B )の三原色信号に変換され、ビデオ信号として符号化画像データを入力した場合は複合手段によって複合され、その後赤( R )、緑( G )、青( B )の三原色信号に変換されている( 例えば、特許文献 1 参照 )。

30

**【0 0 0 3】**

また、C R T 用の画像信号を用いて、液晶表示装置( L C D )において表示を行うことが検討されている。その場合、輝度信号及び色差信号から構成され、且つ C R T 用のガンマ係数によって補正されたビデオ信号を入力し、R、G、B の三原色信号に変換してから逆ガンマ変換を行う。さらに、センサによって得られた外光色温度に合わせて、逆ガンマ変換されたビデオ信号に対して液晶パネルに最適なカラーバランス調整が行われ、アナログ駆動回路を介して液晶パネルへ出力していた( 例えば、特許文献 2 参照 )。

40

**【特許文献 1】特開平 5 - 1 9 7 3 5 3 号公報****【特許文献 2】特開平 7 - 2 5 5 0 6 3 号公報****【発明の開示】****【発明が解決しようとする課題】****【0 0 0 4】**

従来の技術によれば、表示装置に入力されるビデオ信号は輝度信号及び色差信号が入力されることを前提としている。しかしながら、ビデオ信号は輝度信号及び色差信号とは限らず、赤( R )、緑( G )、青( B )の三原色信号( R G B 信号 )の場合もある。その場合

50

、表示装置の信号処理回路がそのビデオ信号のフォーマットに対応していないと、画像を表示することが出来ないこととなる。また、アナログ階調方式を用いて表示することを前提としているため、アナログ信号がノイズの影響を受けてしまう。

#### 【0005】

本発明はこのような問題点に鑑み、ビデオ信号として輝度信号及び色差信号が入力されても、RGB信号が入力されても画像を表示することのできる表示装置を提供すること目的とする。

#### 【課題を解決するための手段】

#### 【0006】

本発明は、ビデオ信号の種類に応じてフォーマットを変換して画像表示を行うことのできる表示装置である。すなわち、RGB信号と輝度色差信号とを切り替えて画像表示を行うことのできる表示装置である。また、デジタルの輝度色差信号を用いてデジタル階調方式で表示を行う表示装置である。

#### 【0007】

本発明の一は、発色が異なる複数のピクセルで画素が構成される表示パネルと、輝度情報と色差情報を含む輝度色差信号が入力され、該輝度色差信号をピクセルの発光色に応じたRGB信号に変換するビデオフォーマット変換回路と、RGB信号が入力され駆動タイミングに合わせて該RGB信号を表示パネルに出力するコントローラとを有する表示装置である。

#### 【0008】

本発明の一は、発色が異なる複数のピクセルで画素が構成される表示パネルと、輝度情報と色差情報を含む輝度色差信号が入力され、該輝度色差信号をピクセルの発光色に応じたデジタル形式のRGB信号に変換するビデオフォーマット変換回路と、デジタル形式のRGB信号をアナログ形式のRGB信号に変換するD/A変換回路と、アナログ形式のRGB信号が入力され駆動タイミングに合わせて該アナログ形式のRGB信号を出力するコントローラとを有する表示装置である。

#### 【発明の効果】

#### 【0009】

本発明によれば、ビデオフォーマット変換回路を備えることにより、RGB信号と輝度色差信号とを切り替えて表示することができる。それによりコントラストが改善され画質を良くすることができる。また、ビデオ信号の処理系統をフルデジタル化することができ、ノイズに強い回路構成とすることができます。さらに、表示装置を小型化することができるので、低消費電力化を図ることができる。

#### 【発明を実施するための最良の形態】

#### 【0010】

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って本実施の形態の記載内容に限定して解釈されるものではない。

#### 【0011】

#### (実施の形態1)

本実施形態は、入力信号として輝度色差信号を用いて表示を行うことのできる表示装置について説明する。

#### 【0012】

ビデオフォーマットとしては、光の三原色に対応した赤(R)、緑(G)、青(B)の各色信号を成分とするRGB方式と、輝度信号及び色差信号を用いる輝度色差方式とがある。RGB方式の場合、全ての色成分に対して同等の処理を行うため画質が優れている。しかしその分、多くの信号量が必要となってしまう。そのため、信号の伝送や処理の負担が大きくなってしまう。

#### 【0013】

10

20

30

40

50

一方、輝度色差方式の場合、例えば、色差の情報量を1/2に削減することで、RGB方式に比べて2/3の信号量で処理することができる。この場合、実質的に画質が劣化するが、実用的には何ら問題も生じない。これは人間の視覚が、輝度の変化には敏感であるが、色差つまり色の変化には鈍感であることに基づいている。

【0014】

このように、輝度色差信号を用いて表示を行うことにより、信号量が低減できるため、信号転送量が少なくなり、信号の処理や伝送が容易に行えるようになる。

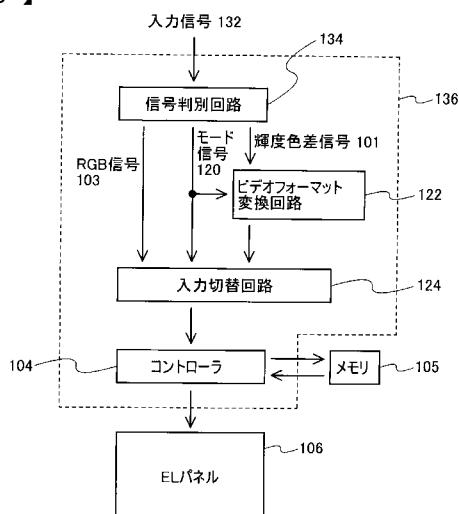

【0015】

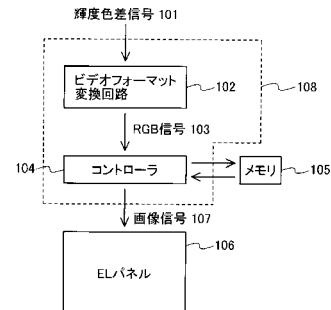

図1に本実施の形態に係る表示装置の構成を示す。この表示装置は、ディスプレイ106を有している。ディスプレイ106はRGB信号に応じて表示が制御される仕様となっている。この表示装置にビデオ信号として、輝度色差信号101がビデオフォーマット変換回路102に入力される。ビデオフォーマット変換回路102において、輝度色差信号101をRGB信号103に変換する。RGB信号103は、コントローラ104に入力される。コントローラ104では、メモリ105に信号を入力する。なお、メモリ105は時間階調方式を用いる場合、1フレーム期間を複数のサブフレーム期間に分割する必要があるため用いられる。メモリ105に保存された信号は、コントローラ104によって、駆動タイミングに合わせてディスプレイ106に画像信号107として入力される。コントローラ104は、ディスプレイ106で表示をするために必要な信号（クロック信号やスタートパルス信号などの同期信号や、各種の制御信号など）も生成し、画像信号107と一緒にディスプレイ106に出力する。画像信号107が入力されたディスプレイ106では、その画像信号107や同期信号や制御信号に応じて表示が行われる。

【0016】

この場合において、ディスプレイ106がデジタル階調方式で表示を行う場合には、輝度色差信号101から画像信号107までを全てデジタル信号として処理することができる。それにより、ノイズに強い回路構成とすることができます。また、表示装置の小型化、低消費電力化を図ることができる。

【0017】

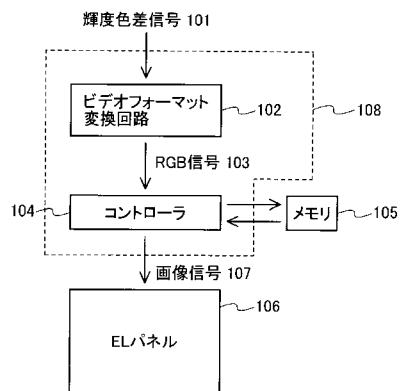

図2は、表示装置がアナログ階調方式で表示を行う場合の構成を示す図である。この場合、ディスプレイ106がアナログ階調方式で表示を行うので、RGB信号103としてアナログ信号を入力する必要がある。アナログ階調方式の場合は、1フレーム期間を複数のサブフレーム期間に分割する、などの操作が必要ないため、コントローラ114の信号を一時的に保存するメモリを省略することができる。ビデオフォーマット変換回路102から出力されたRGB信号103は、DA変換回路110に入力されアナログ形式のRGB信号112に変換される。RGB信号112はコントローラ114に入力され、駆動タイミングに合わせてディスプレイ106に画像信号116として入力される。コントローラ114は、ディスプレイ106で表示をするために必要な信号（クロック信号やスタートパルス信号などの同期信号や、各種の制御信号など）も生成し、画像信号116と一緒にディスプレイ106に出力する。画像信号116が入力されたディスプレイ106では、その画像信号116や同期信号や制御信号に応じて表示が行われる。

【0018】

なお、図1において、ビデオフォーマット変換回路102とコントローラ104を別ブロックで示したが、図中に示す点線枠のように、コントローラ108として、その中にビデオフォーマット変換回路の機能を含ませても良い。同様に、図2において点線枠で示すように、コントローラ118として、その中にビデオフォーマット変換回路及びDA変換回路の機能を含ませても良い。

【0019】

このような表示装置の構成として、1つのICチップの中にコントローラが配置されており、かつ、ビデオフォーマット変換回路が配置されていても良い。同様にメモリ105もコントローラの中に形成されていても良い。この場合、そのICチップは、ディスプレイ106上にCOG（チップオングラス）などにより実装されていても良い。このように実

装することにより、パネルを小型化することに寄与する。

【0020】

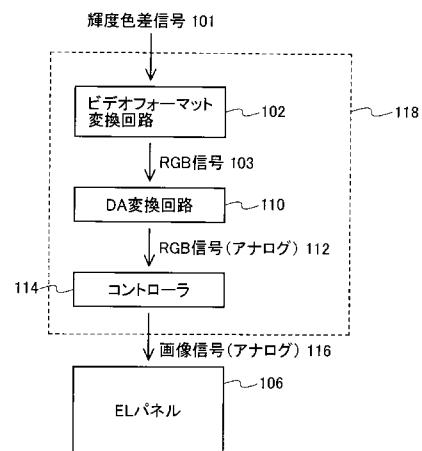

図3に示す表示装置は、輝度色差信号101とRGB信号103を外部回路から入力し、この両信号を適宜切り替えて表示をする構成を示す。ビデオフォーマット変換回路122及び入力切替回路124に入力するモード信号120は、輝度色差信号101とRGB信号103の入力を選択するための信号である。例えば、RGB信号103を入力する場合のモード信号120はL信号となり、輝度色差信号101を入力する場合のモード信号120はH信号となる。モード信号120がH信号の場合、ビデオフォーマット変換回路122は、入力された輝度色差信号101の処理を行う。一方、モード信号120がL信号の場合、ビデオフォーマット変換回路122は変換動作を実行しない。これにより、表示装置の消費電力を低減することが出来る。

10

20

30

入力切替回路124は、モード信号120と、RGB信号103又はビデオフォーマット変換回路122から出力されたRGB信号103が入力される。入力切替回路124は、モード信号120の値に応じてコントローラ104にどちらかのRGB信号103を出力する。例えば、モード信号120がL信号の場合、RGB信号103が入力されているので、それをコントローラ104に出力し、モード信号120がH信号の場合は、輝度色差信号101が入力されているので、ビデオフォーマット変換回路122でRGB信号に変換した後、コントローラ104に出力する。コントローラ104では、メモリ105に信号を入力する。メモリ105に保存された信号は、コントローラ104によって、駆動タイミングに合わせてディスプレイ106に画像信号107として入力される。コントローラ104は、ディスプレイ106で表示をするために必要な信号（クロック信号やスタートパルス信号などの同期信号や、各種の制御信号など）も生成し、画像信号107と一緒にディスプレイ106に出力する。画像信号107が入力されたディスプレイ106では、その画像信号107や同期信号や制御信号に応じて表示が行われる。この場合において、ディスプレイ106がデジタル階調方式で表示を行う場合には、輝度色差信号101、RGB信号103、画像信号107をデジタル信号として処理することができる。それにより、ノイズに強い回路構成とすることができます。また、表示装置の小型化、低消費電力化を図ることができる。

30

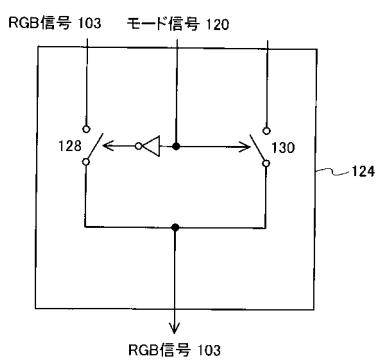

【0021】

図4は入力切替回路124の一構成例であり、モード信号120によりオンオフ動作するスイッチ128及びスイッチ130により、出力する信号を切り替えることができる。図4では、スイッチ128にはインバータを介してモード信号120が与えられるので、スイッチ130と逆のタイミングでオンオフ動作をするように構成している。

40

【0022】

なお、図3において、ビデオフォーマット変換回路122、入力切替回路124、コントローラ104を別ブロックで示したが、図中に示す点線枠のように、コントローラ126として、その中にビデオフォーマット変換回路や入力切替回路の機能を含ませても良い。

【0023】

このような表示装置の構成として、1つのICチップの中にコントローラが配置されており、かつ、ビデオフォーマット変換回路や入力切替回路が配置されていても良い。同様にメモリ105もコントローラの中に含まれていても良い。この場合、そのICチップは、ディスプレイ106上にCOG（チップオングラス）などにより実装されていても良い。このように実装することにより、パネルを小型化することに寄与する。

50

【0024】

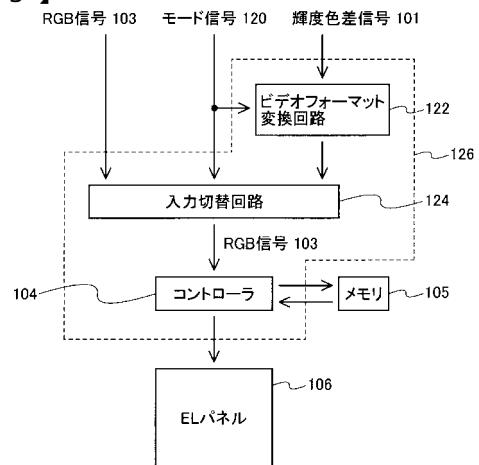

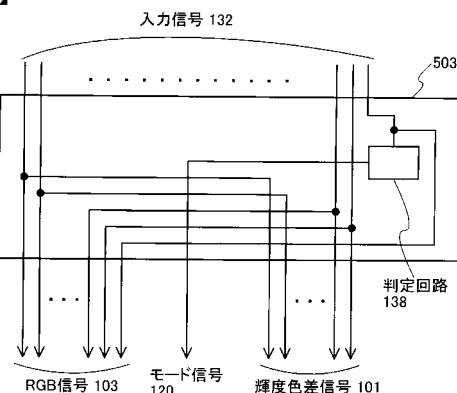

図3は、RGB信号103と輝度色差信号101が、異なるバスラインで表示装置に入力される構成を示している。これに対し、RGB信号103と輝度色差信号101を同一のバスラインで入力する構成を図5に示す。図5では、RGB信号又は輝度色差信号であるものを入力信号132として示している。RGB信号と輝度色差信号とでは、バスラインで信号を送るために必要な信号線の本数が異なっており、通常は輝度色差信号の方がRG

B 信号よりも必要な信号線の本数が少なくて済む。すなわち、入力信号 132 が輝度色差信号である場合、物理的に同じバスラインを使う限り何本かの信号線には信号が入力されないこととなる。この特性を利用することにより、信号判別回路 134 において、入力信号 132 が R G B 信号であるのか輝度色差信号であるのかを判別することができる。例えば、バスラインの特定の信号線に対して、信号の有無をモニタすることにより入力信号 132 の種類を判別することができる。さらに、信号判別回路 134 は、その判別結果を用いてモード信号 120 を生成し、ビデオフォーマット変換回路 122 及び入力切替回路 124 に出力する。

#### 【0026】

図 6 に信号判別回路 134 の構成を示す。入力信号 132 は、複数の信号線を有するバスラインで入力されるものとして示している。入力信号 132 として、R G B 信号 103 又は輝度色差信号 101 を選択することが可能であるが、この場合、それらの信号を伝送するのに必要なバスラインの本数が異なっている。図 6 では、R G B 信号を伝送するときに用いる信号線がバスラインに含まれていることを示している。その R G B 信号を伝送するときに用いる信号線は、判定回路 138 にも入力されている。判定回路 138 では、信号の有無によって、入力信号 132 が、R G B 信号であるのか輝度色差信号であるのかを判断し、その結果に応じてモード信号 120 を出力する。

#### 【0027】

図 6 では、モード信号 120 の値にかかわらず、R G B 信号 103、輝度色差信号 101 を出力するようになっているが、これに限定されない。モード信号 120 の値に応じて、R G B 信号 103 又は輝度色差信号 101 信号を出力しても良い。

#### 【0028】

なお、図 5 において、コントローラ 104、ビデオフォーマット変換回路 122、入力切替回路 124、信号判別回路 134 を別ブロックで示したが、図中に示す点線枠のように、コントローラ 136 として、その中にビデオフォーマット変換回路や入力切替回路の機能を含ませても良い。同様に、メモリ 105 もコントローラの中に含まれていても良い。この場合、その I C チップは、ディスプレイ 106 上に C O G (チップオングラス) などにより実装されていても良い。このように実装することにより、パネルを小型化することに寄与する。

#### 【0029】

図 5 では、輝度色差信号 101、R G B 信号 103、画像信号 107 をデジタル信号として処理することが出来る。図 3 及び図 5 では、デジタル階調方式の場合を例示しているが、図 2 で説明したように D A 変換回路を配置することによりアナログ階調方式とすることもできる。

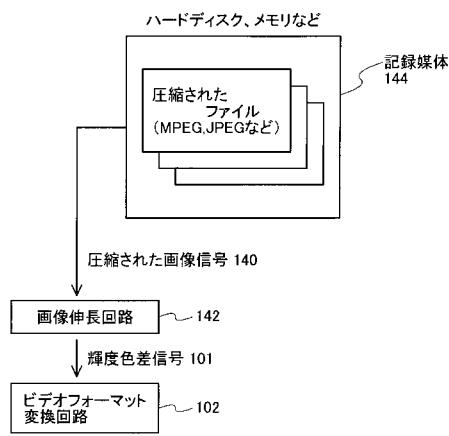

#### 【0030】

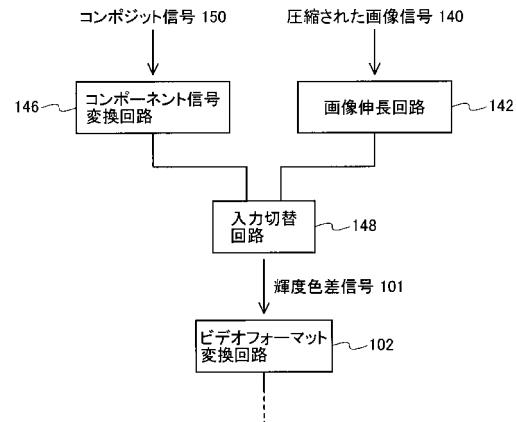

次に、圧縮された画像信号の取り扱いについて図 7 を参照して説明する。圧縮されたファイルは、ハードディスクや半導体メモリなどの記録媒体 144 に記録されている。このファイルは、M P E G 方式や J P E G 方式や、デジタルビデオ規格である D V 方式などの画像若しくは映像ファイルである。これらの圧縮ファイルは、輝度色差信号の状態で圧縮されている。このファイルを読み出して、画像伸長回路 142 に圧縮画像信号 140 を入力する。画像伸長回路 142 では、圧縮されていたファイルを元の状態に戻す動作を行う。このとき、画像伸長回路 142 からは、輝度色差信号のままで出力されるようになる。元々、圧縮されていた状態において、輝度色差信号になっていたため、輝度色差信号のまま画像伸長を行う。その結果、画像伸長回路 142 の負担を軽くすることができる。すなわち、画像伸長回路 142 の回路規模を小型化することができ、処理速度を高速化する必要が無い。輝度色差信号のまま、図 1 乃至図 6 で示すビデオフォーマット変換回路 102 や信号判別回路 134 などに入力することができる。

#### 【0031】

表示部を備えた電子機器類において、ハードディスクや半導体メモリに圧縮保存されている画像若しくは映像ファイルを表示部に表示させる場合、画像伸長回路の構成を簡単にで

10

20

30

40

50

きるので、図7で示す構成は好適である。携帯電話に代表されるように電子機器が備える表示部は、操作メニュー画面などのように、特定の画像を表示させる場合と、圧縮された任意の画像情報を表示させる場合がある。特定の画像を表示させる場合は、RGB方式になっていることが多いため、図3や図5のように、RGB方式と輝度色差方式とを切り替えることができるようにしておくことが好適である。

#### 【0032】

ビデオ信号には、輝度信号と色差信号を一つにまとめたコンポジット信号と、色差信号をさらに青の色差と赤の色差に分離したコンポーネント信号がある。通常のテレビジョン放送はコンポジット信号である。コンポジット信号を扱う場合には、図8で示すようにコンポーネント信号変換回路146を用いて、コンポジット信号150からコンポーネント信号へ変換する。そして、入力切替回路148を用いて信号を切り替えて出力することにより、テレビなどのコンポジット信号も表示させることができる。

#### 【0033】

図8で示すコンポーネント信号変換回路146を備えることにより、ハードディスクや半導体メモリに圧縮されて記憶されている画像若しくは映像ファイルと、テレビジョン放送の双方を切り替えて表示する表示装置を提供することができる。また、操作メニュー画面などのように、特定の画像を表示させる場合は、RGB方式になっていることが多い。そのため、図3や図5で示すように、RGB方式と輝度色差方式とを切り替えることは、表示装置の操作性を向上させる上で有効である。

#### 【0034】

輝度色差信号は、ITU-R BT.601形式、BTAS-001B形式、YCbCr形式、YPbPr形式、YUV形式、YIQ形式、YCC形式など、各種フォーマットに対応させることができる。

#### 【0035】

輝度色差信号を入力しているが、RGB信号以外の信号であれば、輝度色差信号以外の形式の信号でもよい。例えば、CMYK形式やHSV形式のデータの場合であっても、輝度色差信号の場合と同様に構成することができる。なお、CMYKは、シアン(cyan, 青緑)、マゼンタ(magenta, 赤紫)、イエロー(yellow, 黄)、ブラック(black, 墨、Kは、key colorのKで鍵になる色)の頭文字を取った物である。また、HSVは、色相(Hue)、彩度(Saturation)、明度(Value)を意味する。

#### 【0036】

本実施の形態に係る表示装置において、表示部における画素の構成に特段の限定はない。デジタル階調方式を用いている表示装置であれば様々な表示装置に本実施の形態の構成を適用することができる。例えば、表示部が、EL素子で画素を形成するELディスプレイ、PDP(プラズマディスプレイ)、DMD(デジタルマイクロミラーデバイス)を用いたDLP(デジタルライトプロセッシング)などであっても良い。

#### 【0037】

本実施の形態によれば、ビデオフォーマット変換回路を備えることにより、RGB信号と輝度色差信号とを切り替えて表示することができる。それによりコントラストが改善され画質を良くすることができる。また、ビデオ信号の処理系統をフルデジタル化することができ、ノイズに強い回路構成とすることができます。さらに、表示装置を小型化することができるので、低消費電力化を図ることができる。

#### 【0038】

##### (実施の形態2)

本実施の形態では、表示装置を構成するディスプレイの構成と、階調の表現方法について説明する。

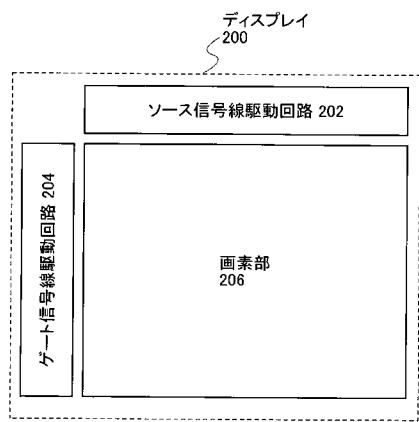

#### 【0039】

表示装置は、表示パネルと、それにビデオ信号等を入力する駆動回路によって構成されている。図9は、そのような表示パネルの一構成例を示している。ディスプレイ200は、

10

20

30

40

50

ソース信号線駆動回路 202、ゲート信号線駆動回路 204、画素部 206 によって構成されている。画素部はマトリクス状に画素が配置された構成となっている。

【0040】

画素部 206 の代表的な構成として、各画素にスイッチング素子を配置したアクティブマトリクス方式のものがある。以下に、画素毎に 2 つの薄膜トランジスタ ( TFT ) を配置し、各画素の発光素子の発光を制御する手法について説明する。

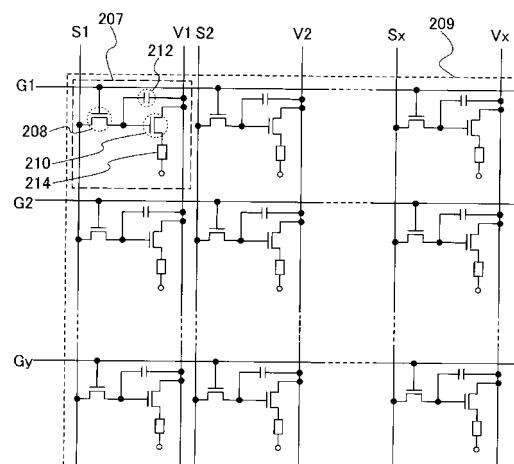

【0041】

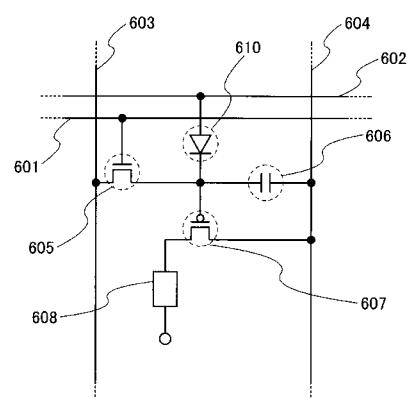

図 10 に表示パネルの画素部の構成を示す。画素部 209 にはソース信号線  $S_1 \sim S_x$ 、ゲート信号線  $G_1 \sim G_y$ 、電源線  $V_1 \sim V_x$  が配置され、 $x$  ( $x$  は自然数) 列  $y$  ( $y$  は自然数) 行の画素が配置されている。画素 207 は、選択 TFT 208、駆動 TFT 210 10、保持容量 212、発光素子 214 を有している。

【0042】

図 10 における画素 207 の詳細を図 11 に示す。選択 TFT 208 のゲート電極はゲート信号線  $G$  に接続されている。選択 TFT 208 のソース領域及びドレイン領域の一方はソース信号線  $S$  に接続され、他方は駆動 TFT 210 のゲート電極及び保持容量 212 の一方の電極に接続されている。駆動 TFT 210 のソース領域及びドレイン領域の一方は電源線  $V$  に接続され、他方は発光素子 214 の陽極又は陰極に接続されている。保持容量 212 の 2 つの電極の内、駆動 TFT 210 及び選択 TFT 208 に接続されていない側は電源線  $V$  に接続されている。

【0043】

本明細書においては、駆動 TFT 210 のソース領域又はドレイン領域が発光素子 214 の陽極と接続されている場合、発光素子 214 の陽極を画素電極と呼び陰極を対向電極と呼ぶこととする。一方、駆動 TFT 210 のソース領域又はドレイン領域が発光素子 214 の陰極と接続されている場合、発光素子 214 の陰極を画素電極と呼び陽極を対向電極と呼ぶこととする。また、電源線  $V$  に与えられる電位を電源電位といい、対向電極に与えられる電位を対向電位と呼ぶこととする。

【0044】

選択 TFT 208 及び駆動 TFT 210 は、P チャネル型 TFT 及び N チャネル型 TFT から選択することができる。保持容量は必要に応じて適宜設ければ良い。例えば、駆動 TFT 210 として用いる N チャネル型 TFT が、ゲート絶縁膜を介してゲート電極に重なるように設けられた LDD 領域を有している場合、この重なり合った領域にはゲート容量と呼ばれる寄生容量が形成される。この寄生容量を、駆動 TFT 210 のゲート電極にかかる電圧を保持するための保持容量として用いることも可能である。

【0045】

以下に上記構成の画素を用いて画像を表示する場合の駆動方法について説明する。

【0046】

ゲート信号線  $G$  に走査信号が入力されると選択 TFT 208 は、ゲート電極の電位が変化してオン、すなわち導通状態となる。それにより、この画素にビデオ信号が入力されることがある。これは、ソース信号線  $S$  から、選択 TFT 208 を介して、駆動 TFT 210 のゲート電極にビデオ信号に基づく電位が印加される状態である。また、同時に保持容量 212 にビデオ信号に応じて電荷が保持される。駆動 TFT 210 のゲート電極に印加される電圧によって、駆動 TFT 210 は導通状態となり、電源線  $V$  の電位が駆動 TFT 210 を介して、発光素子 214 の画素電極に与えられる。それにより、発光素子 214 は発光する。

【0047】

次に、このような構成の画素を用いて、画像を表示する際における階調表現について説明する。

【0048】

階調表現の方法を大別すると、アナログ方式とデジタル方式とが知られている。アナログ方式と比べてデジタル方式は、画素を構成する TFT のばらつきに対して影響を受けにく

10

20

30

40

50

いという特徴がある。また、デジタル方式は多階調表示に向いている。

【0049】

デジタル方式の階調表現方法の一例として、時間階調方式が知られている。この方式の駆動方法は、表示装置の各画素が発光する期間を制御することによって、階調を表現する手法である。

【0050】

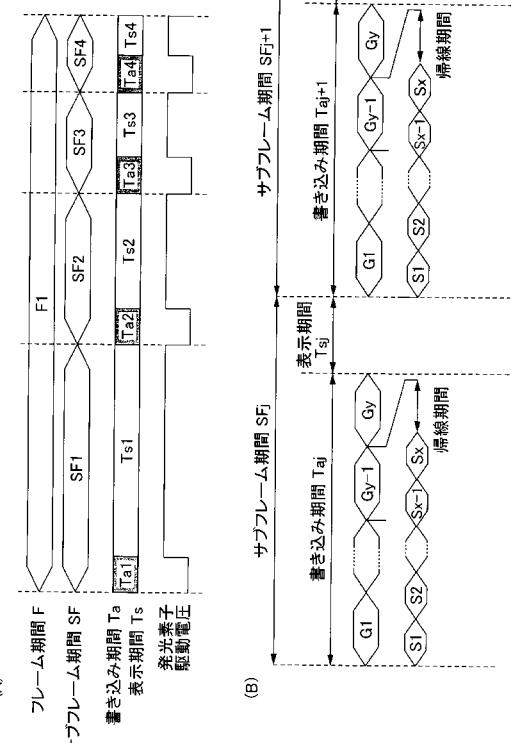

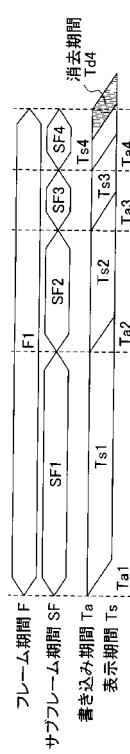

時間階調方式では、1フレーム期間を複数のサブフレーム期間に分割している。

そして、サブフレーム期間毎に灯若しくは非点灯を選択し、1フレーム期間当たりに発光素子が発光する期間を制御して階調を表現している。

【0051】

この時間階調方式の駆動方法について、図12のタイミングチャートを用いて詳しく説明する。図12では一例として、4ビットのデジタル映像信号を用いて階調を表現する場合を示す。画素及び画素部の構成としては、図10及び図11に示したものを参照する。ここで、対向電位は、外部に接続される電源によって、電源線V1～Vxの電位（電源電位）と同じ程度の電位か、電源線V1～Vxの電位との間に、発光素子214が発光する程度の電位差を有するように切り換えることができる。

【0052】

図12(A)において1フレーム期間F1は、複数のサブフレーム期間SF1～SF4に分割される。第1のサブフレーム期間SF1において、はじめにゲート信号線G1が選択される。そして、ゲート信号線G1にゲート電極が接続された選択TFT208を有する画素において、ソース信号線S1～Sxからデジタル映像信号が入力される。入力されたデジタル映像信号によって、各画素の駆動TFT210はオンの状態若しくはオフの状態となる。

【0053】

ここで、TFTがオンの状態とは、あるゲート電圧が印加されたことによって、ソースとドレイン間が導通状態であることを示すものとする。また、TFTがオフの状態とは、あるゲート電圧が印加されたことによって、ソースとドレイン間が非導通状態であることを示すものとする。

【0054】

このとき、発光素子214の対向電位は、電源線V1～Vxの電位（電源電位）とほぼ等しく設定されているので、駆動TFT210がオンの状態となった画素においても発光素子214は発光しない。

【0055】

図12(B)は、各画素の駆動TFT210にデジタル映像信号を入力する動作を示すタイミングチャートである。図12(B)では、各ソース信号線に対応する信号をソース信号線駆動回路がサンプリングする期間を、S1～Sxで示している。サンプリングされた信号は、図中に示す帰線期間において、全てのソース信号線に同時に出力される。こうして出力された信号は、ゲート信号線が選択した画素において、駆動TFT210のゲート電極に入力される。

【0056】

全てのゲート信号線G1～Gyについて以上の動作を繰り返し、書き込み期間Ta1が終了する。ここで、第1のサブフレーム期間SF1の書き込み期間をTa1と呼ぶ。一般に第j(jは自然数)のサブフレーム期間の書き込み期間をTa jと呼ぶことにする。

【0057】

書き込み期間Ta1が終了すると、対向電位が電源電位との間に発光素子214が発光する程度の電位差を有するように変化する。こうして点灯期間Ts1が始まる。なお、第1のサブフレーム期間SF1の点灯期間をTs1と呼ぶ。第j(jは自然数)のサブフレーム期間の点灯期間をTs jと呼ぶことにする。点灯期間Ts1において、各画素の発光素子214は、入力された信号に応じて、発光若しくは非発光の状態となる。

【0058】

10

20

30

40

50

上記動作を全てのサブフレーム期間 S F 1 ~ S F 4 について繰り返し、1フレーム期間 F 1 が終了する。階調は、サブフレーム期間 S F 1 ~ S F 4 の点灯期間 T s 1 ~ T s 4 の長さを適宜設定し、1フレーム期間 F 1 当たり、発光素子 2 1 4 が発光したサブフレーム期間の点灯期間の累計によって表現する。つまり、1フレーム期間中の点灯時間の総和をもって階調を表現する。

【0059】

$n$  ビットのデジタルビデオ信号を入力して、 $2^n$  階調を表現する手法について説明する。例えば、1フレーム期間を  $n$  個のサブフレーム期間 S F 1 ~ S F  $n$  に分割し、各サブフレーム期間 S F 1 ~ S F  $n$  の点灯期間 T s 1 ~ T s  $n$  の長さの比が、 $T s 1 : T s 2 : \dots : T s n - 1 : T s n = 2^0 : 2^{-1} : \dots : 2^{-(n-2)} : 2^{-(n-1)}$  となるように設定する。なお、書き込み期間 T a 1 ~ T a  $n$  の長さは同じである。 10

【0060】

1フレーム期間中に発光素子 2 1 4 において、発光状態が選択された点灯期間 T s の総和を求ることによって、そのフレーム期間におけるその画素の階調が決まる。例えば、 $n = 8$  のとき、全部の点灯期間で画素が発光した場合の輝度を 100% とすると、T s 8 と T s 7 において画素が発光した場合には 1% の輝度が表現でき、T s 6 と T s 4 と T s 1 を選択した場合には 60% の輝度が表現できる。

【0061】

なお、一つのサブフレーム期間をさらに複数のサブフレーム期間に分割しても良い。

【0062】

時間階調方式を用いて階調を表現する場合、サブフレームの数は任意に設定することができる。また、各サブフレーム期間の点灯期間の長さや、どのサブフレームを点灯させるか、すなわち、サブフレームの選択方法についても、特に限定されない。 20

【0063】

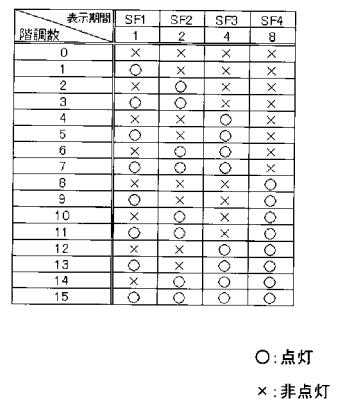

例えば、16階調を表現する場合を図 13 に示す。1フレーム期間を 4 個のサブフレーム ( S F 1 ~ S F 4 ) に分割し、S F 1 ~ S F 4 の点灯期間 T s 1 : T s 2 : T s 3 : T s 4 の比を  $2^0 : 2^1 : 2^2 : 2^3$  としても良い。

【0064】

また、階調の表現方法として、1フレームを分割してできた一部若しくは全部のサブフレームにおける点灯期間を順次足し合わせていくことにより、階調を表現しても良い。つまり、階調が大きくなるにしたがって、点灯するサブフレームが増えていくようにしても良い。この場合、低階調で点灯しているサブフレームは、高階調においても点灯していることになる。このような階調方式を、本明細書中では、重ね合わせ時間階調方式と呼ぶことにする。例えば、16階調を表現する場合に、重ね合わせ時間階調方式を適用した例を図 14 に示す。 30

【0065】

図 14 ( A ) では、1フレーム期間を 5 個のサブフレーム ( S F 1 ~ S F 5 ) に分割し、S F 1 ~ S F 5 の点灯期間 T s 1 : T s 2 : T s 3 : T s 4 : T s 5 の比を  $2^0 : 2^1 : 2^2 : 2^2 : 2^2$  とし、点灯期間の長さが等しい S F 3 ~ S F 5 に対して、重ね合わせ時間階調方式を適用している。また、図 14 ( B ) では、1フレーム期間を 5 個のサブフレーム ( S F 1 ~ S F 5 ) に分割し、S F 1 ~ S F 5 の点灯期間 T s 1 : T s 2 : T s 3 : T s 4 : T s 5 の比を  $2^2 : 2^1 : 2^0 : 2^2 : 2^2$  とし、点灯期間の長さが等しい S F 1 、 S F 4 、 S F 5 に対して、重ね合わせ時間階調方式を適用している。なお、重ね合わせ時間階調方式を適用すると、擬似輪郭を低減することができる。 40

【0066】

なお、重ね合わせ時間階調方式を適用するサブフレームは、点灯期間が等しいものに限定されない。また、サブフレームの出現順序については、これに限定されない。

【0067】

本発明の表示装置のディスプレイが有する画素部の構成としては、図 10 で示した構成の画素以外の公知の構成の画素も、自由に用いることができる。また、発明の表示装置のデ 50

ディスプレイが有するソース信号線駆動回路及びゲート信号線駆動回路についても、公知の構成の回路を自由に用いることができる。さらに、本発明は、発光素子として、発光素子を用いた表示装置だけでなく、FED、PDP等その他の自発光型表示装置などについても適用が可能である。

#### 【0068】

本実施の形態によれば、時間階調方式を用いる場合であっても、ビデオフォーマット変換回路を備えることにより、RGB信号と輝度色差信号とを切り替えて表示することができる。それによりコントラストが改善され画質を良くすることができる。また、ビデオ信号の処理系統をフルデジタル化することができ、ノイズに強い回路構成とすることができる。さらに、表示装置を小型化することができるので、低消費電力化を図ることができる。

10

#### 【0069】

(実施の形態3)

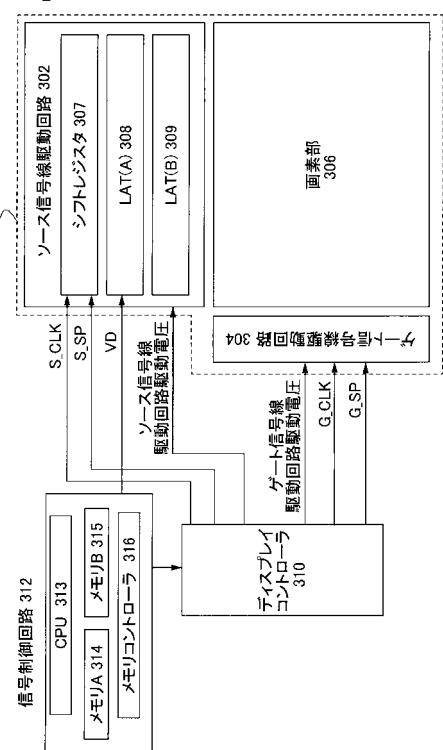

本実施形態は、時間階調方式の駆動方法を行うための信号を、ディスプレイのソース信号線駆動回路及びゲート信号線駆動回路に入力する回路について、図15を用いて説明する。本実施の形態は、4ビットのデジタルビデオ信号を入力して、画像を表示する表示装置を例に説明する。

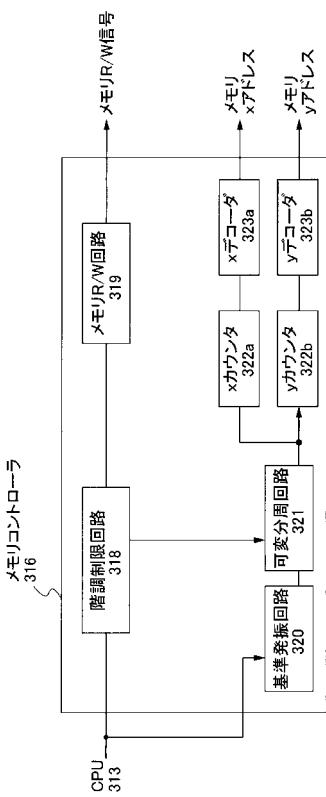

#### 【0070】

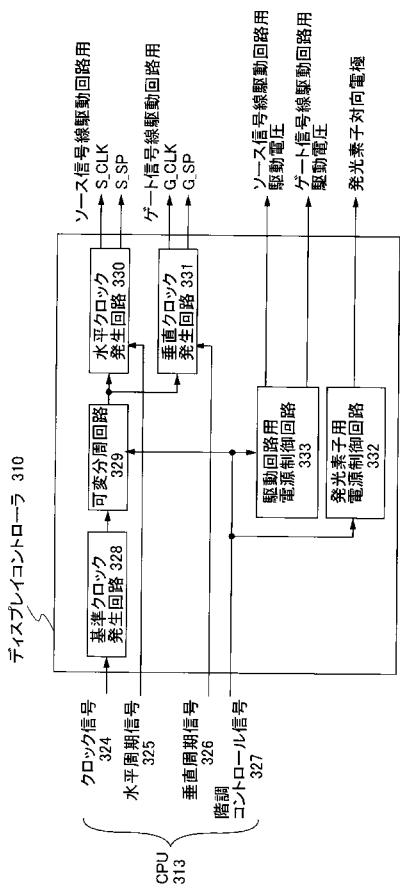

信号制御回路312にデジタルビデオ信号(ディスプレイに入力される映像信号をいう。)が読み込まれ、ディスプレイ300にデジタル映像信号(VD)を出力する。信号制御回路312においてデジタルビデオ信号を編集し、ディスプレイに入力する信号に変換したものと、ここでは「デジタル映像信号」と呼ぶ。

20

#### 【0071】

ディスプレイ300の、ソース信号線駆動回路302及びゲート信号線駆動回路304を駆動するための信号及び駆動電圧は、ディスプレイコントローラ310によって入力されている。ディスプレイ300のソース信号線駆動回路302は、シフトレジスタ307、LAT(A)308、LAT(B)309によって構成される。この他に、ソース信号線駆動回路302にレベルシフタやバッファ等を設けても良い。

#### 【0072】

信号制御回路312は、CPU313、メモリ(A)314、メモリ(B)315及びメモリコントローラ316によって構成されている。

30

#### 【0073】

信号制御回路312に入力されたデジタルビデオ信号は、メモリコントローラ316によって制御され、メモリ(A)314に入力される。ここで、メモリ(A)314は、ディスプレイ300の画素部306の全画素分の4ビットのデジタルビデオ信号を記憶可能な容量を有する。メモリ(A)314に1フレーム期間分の信号が記憶されると、メモリコントローラ316によって、各ビットの信号が順に読み出され、デジタル映像信号VDとして、ソース信号線駆動回路に入力される。

#### 【0074】

メモリ(A)314に記憶された信号の読み出しが始まると、メモリコントローラ316を介して次のフレーム期間に対応するデジタルビデオ信号が入力され、メモリ(B)315にそのデジタルビデオ信号が記憶される。メモリ(B)315もメモリ(A)314と同様に、表示装置の全画素分の4ビットのデジタルビデオ信号を記憶可能な容量を有するとする。

40

#### 【0075】

信号制御回路312は、それぞれ1フレーム期間分の4ビットのデジタルビデオ信号を記憶することができるメモリ(A)314及びメモリ(B)315を有している。このメモリ(A)314とメモリ(B)315とを交互に用いて、デジタルビデオ信号をサンプリングする。

#### 【0076】

信号制御回路312は、複数フレーム分の情報を記憶することができるメモリ容量を有し

50

、1フレーム期間毎のビデオ信号の記憶と読み出しを上記のように行う機能を備えていれば良いので、図15の構成に限定されるものではない。

【0077】

上記動作を行う、表示装置のブロック図を図16に示す。表示装置は、信号制御回路312と、ディスプレイコントローラ310と、ディスプレイ300によって構成されている。

【0078】

ディスプレイコントローラ310は、ディスプレイ300に、スタートパルスSPやクロックパルスCLK、駆動電圧を供給している。

【0079】

図16では、4ビットのデジタルビデオ信号を入力し、第1の表示モードにおいて、4ビットのデジタル映像信号を用いて階調を表現する表示装置を例に示している。メモリ(A)314は、デジタルビデオ信号の第1のビット～第4のビットの情報をそれぞれ記憶するメモリ(A)314a～314dによって構成されている。同様にメモリ(B)315も、デジタルビデオ信号の第1のビット～第4のビットの情報をそれぞれ記憶するメモリ(B)315a～315dによって構成されている。これらの各ビットに対応するメモリはそれぞれ、1ビット分の信号を、1画面を構成する画素数分記憶可能な数の記憶素子を有している。

【0080】

一般に、nビットのデジタル映像信号を用いて階調を表現することが可能な表示装置において、メモリ(A)314は、第1のビット～第nのビットの情報をそれぞれ記憶するメモリ(A)314a～314dによって構成される。同様に、メモリ(B)315も、第1のビット～第nのビットの情報をそれぞれ記憶するメモリ(B)315a～315dによって構成される。これらの各ビットに対応するメモリは、それぞれ1ビット分の信号を、1画面を構成する画素数分記憶可能な容量を有している。

【0081】

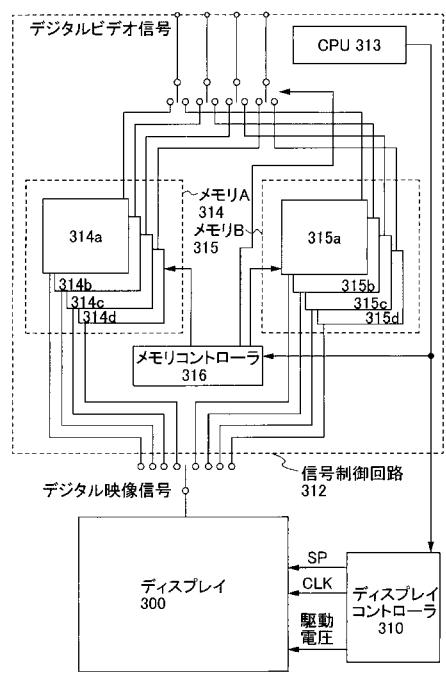

メモリコントローラ316の構成を、図17に示す。図17において、メモリコントローラ316は、階調制限回路318、メモリ制御回路319、基準発振回路320、可変分周回路321、xカウンタ322a、yカウンタ322b、xデコーダ323a、yデコーダ323bによって構成されている。

【0082】

図15、図16等において記したメモリ(A)314及びメモリ(B)315等のメモリの両方をまとめてメモリと表記する。また、メモリは、複数の記憶素子によって構成される。これらの記憶素子は、(x, y)のアドレスによって選択されるものとする。

【0083】

CPU313からの信号が、階調制限回路318を介して、メモリ制御回路319に入力される。階調制限回路318では、第1の表示モード若しくは第2の表示モードのいずれかに応じて、信号をメモリ制御回路319に入力する。メモリ制御回路319は、階調制限回路318の信号に応じて、各ビットに対応するデジタルビデオ信号それぞれを、メモリに書き込むかどうかを選択する。同様に、メモリに書き込まれたデジタル映像信号を読み出す動作を選択する。

【0084】

CPU313からの信号は、基準発振回路320に入力される。基準発振回路320からの信号は、可変分周回路321に入力され、適当な周波数の信号に変換される。ここで、可変分周回路321には、第1の表示モード若しくは第2の表示モードのいずれかに応じた階調制限回路318からの信号が入力されている。この信号によって、可変分周回路321からの信号は、xカウンタ322a及びxデコーダ323aを介してメモリのxアドレスを選択する。同様に、可変分周回路からの信号は、yカウンタ322b及びyデコーダ323bに入力され、メモリのyアドレスを選択する。

【0085】

10

20

30

40

50

このような構成のメモリコントローラ 316 を用いることで、高階調表示が必要ない場合に、信号制御回路に入力されるデジタルビデオ信号のうち、メモリに書き込まれ、またメモリから読み出される信号の情報量を抑えることができる。また、メモリから信号を読み出す周波数を変化させることができる。

【0086】

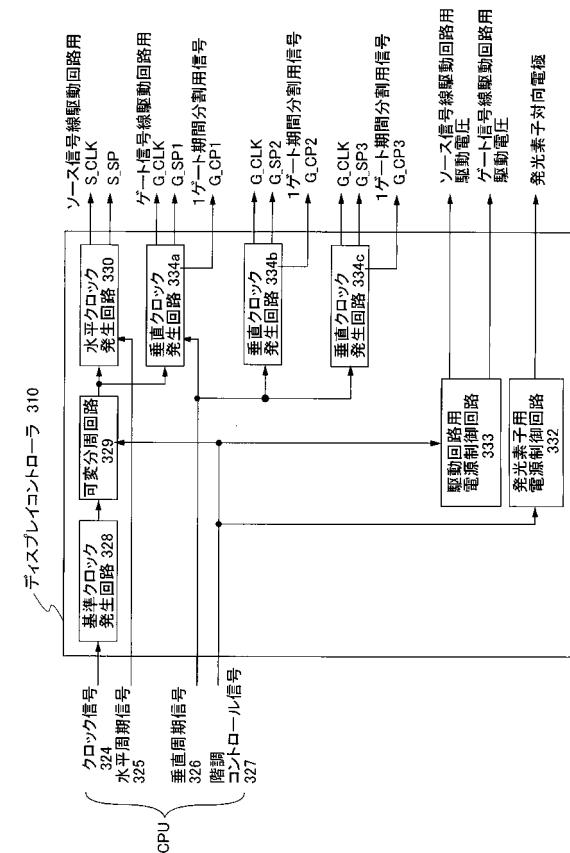

ディスプレイコントローラ 310 の構成について、以下に説明する。図 18 は、本発明のディスプレイコントローラの構成を示した図である。ディスプレイコントローラ 310 は、基準クロック発生回路 328 、可変分周回路 329 、水平クロック発生回路 330 、垂直クロック発生回路 331 、発光素子用電源制御回路 332 、駆動回路用電源制御回路 333 によって構成されている。

10

【0087】

CPU 313 から入力されるクロック信号 324 は、基準クロック発生回路 328 に入力され、基準クロックを発生する。この基準クロックは、可変分周回路 329 を介して、水平クロック発生回路 330 及び垂直クロック発生回路 331 に入力される。可変分周回路 329 には、階調コントロール信号 327 が入力される。この信号によって、基準クロックの周波数を変化させる。

【0088】

可変分周回路 329 において基準クロックの周波数を変化させる度合いは、実施者が適宜定めることができる。

【0089】

水平クロック発生回路 330 には、CPU 313 から水平周期を定める、水平同期信号 325 が入力され、ソース信号線駆動回路用のクロックパルス S\_CLK 及び、スタートパルス S\_SP が出力されている。同様に、垂直クロック発生回路 331 には、CPU 313 から垂直周期を定める垂直同期信号 326 が入力され、ゲート信号線駆動回路用のクロックパルス G\_CLK 及びスタートパルス G\_SP が出力されている。

20

【0090】

こうして、信号制御回路のメモリコントローラにおいて、メモリからの下位ビットの信号の読み出しを無くし、また、メモリからの信号の読み出しの周波数を小さくする。この動作に対応して、ディスプレイコントローラは、各駆動回路（ソース信号線駆動回路及びゲート信号線駆動回路）に入力するサンプリングパルス S\_P 及びクロックパルス C\_LK の周波数を小さくし、画像を表現するサブフレーム期間の書き込み期間及び点灯期間を長く設定することができる。

30

【0091】

本実施の形態では、1 フレーム期間を 4 つのサブフレーム期間に分割して、4 ビットのデジタル映像信号を用いて、 $2^4$  の階調をしたが、ひとつのサブフレーム期間をさらに複数のサブフレーム期間で構成しても良い。例えば、1 フレーム期間を 6 つのサブフレーム期間に分割しても良い。

40

【0092】

発光素子用電源制御回路 332 は、発光素子の対向電極の電位（対向電位）を、書き込み期間中は電源電位とほぼ同じ電位に保たれるようにし、点灯期間においては電源電位との間に発光素子が発光する程度の電位差を有するように、制御している。ここで、発光素子用電源制御回路 332 にも、階調コントロール信号 327 が入力される。これによって、発光状態を選択された画素において、発光素子が発光する期間が長くなった分、発光素子の両電極間にかける電圧が小さくなるように、発光素子の対向電極の電位を変化させる。

【0093】

駆動回路用電源制御回路 333 は、各駆動回路に入力される電源電圧を制御する。ここで、駆動回路用電源制御回路 333 にも、階調コントロール信号 327 が入力されることで、出力される駆動回路用電源電圧を変更する。

【0094】

なお、駆動回路用電源制御回路 333 には、特許第 3110257 号（特開平 8-696

50

90号公報)に開示されている技術など公知の構成のものを用いても良い。

【0095】

前述した信号制御回路312、メモリコントローラ316、CPU313、メモリ(A)314、メモリ(B)315、ディスプレイコントローラ310は、画素と同一基板上に形成しても良いし、LSIチップで形成しディスプレイ300の基板上にCOGで貼り付けを行なっても良い。また、基板上にTABをもちいて貼り付けを行なっても良いし、ディスプレイとは別の基板上に形成し、電気配線にて接続を行なっても良い。

【0096】

本実施の形態に係る表示装置を実施の形態1又は実施の形態2に組み合わせることにより、同様な効果を奏することができる。

10

【0097】

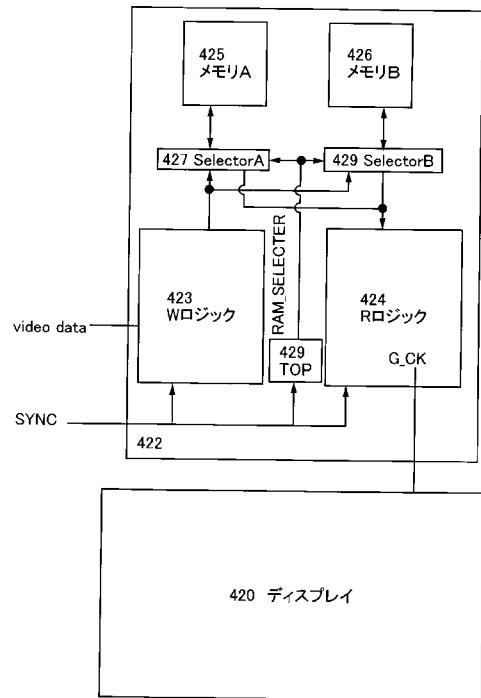

(実施の形態4)

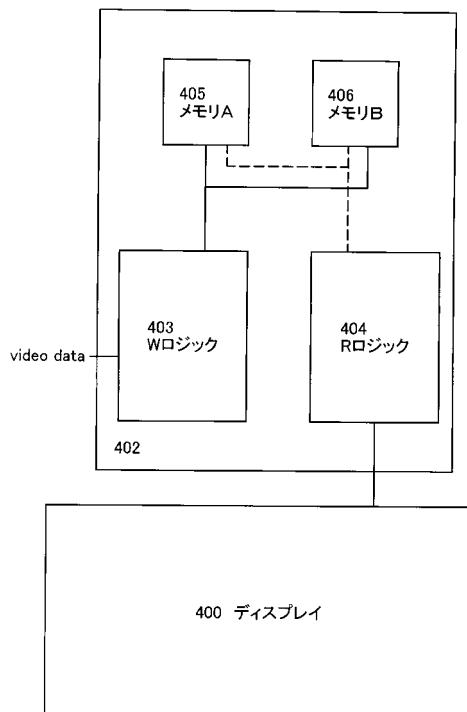

本実施の形態では、表示装置の駆動回路について説明する。時間階調を用いて表示を行なうためには、時間階調用に信号を変換する回路が必要である。時間階調用に信号を変換する回路として、例えば図19のように表される制御回路を用いることができる。制御回路402はデータを記憶するメモリ(A)405及びメモリ(B)406、データを読み取り、メモリへの書き込みを行う論理回路(Wロジック403)、メモリからの読み取りを行い、ディスプレイ400に出力を行う論理回路(Rロジック404)から構成される。

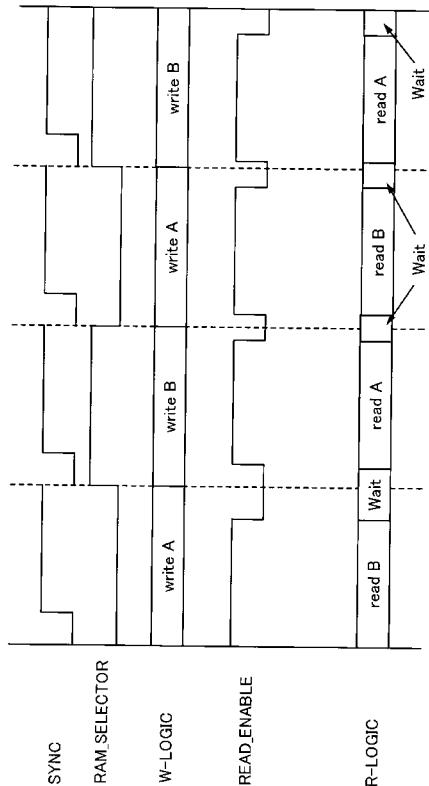

【0098】

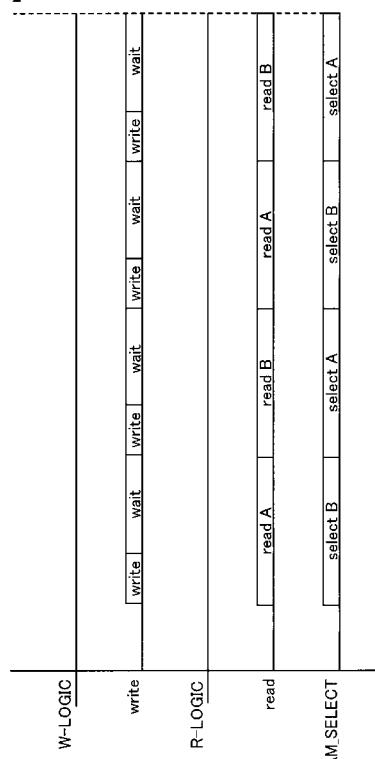

図20に本実施の形態の制御回路のタイミングチャートを示す。Wロジック403に入力されたデジタルデータを時間階調方式に合わせたデータにするために、メモリ(A)405及びメモリ(B)406を使って、交互にデータの書き込み及び読み取りを行う。

20

【0099】

Rロジック404がメモリ(A)405に記憶された信号の読み出しを行うと、同時にメモリ(B)406にWロジック403を介して次のフレーム期間に対応するデジタルビデオ信号が入力されて記憶され始める。

【0100】

このように、制御回路402は、1フレーム期間分ずつのデジタルビデオ信号を記憶することができるメモリ(A)405及びメモリ(B)406を有し、このメモリ(A)405とメモリ(B)406とを交互に用いて、デジタルビデオ信号をサンプリングする。

30

【0101】

このとき、メモリ(A)405又はメモリ(B)406に書き込んだ後、再び読み取り信号が来るまでWait(待機)状態に置かれる。また、メモリ(A)405及びメモリ(B)406の書き込みと読み取りの機能変換は、より時間のかかる読み取り側にタイミングを合わせて行う。

【0102】

また、書き込み信号の周期毎に、2つのメモリの割り当てを決め、書き込み開始信号と水平方向同期信号を通じて読み込み開始を決定するようにしても良い。それにより、フレーム周波数が落ちてしまうことを防止することができる。

40

【0103】

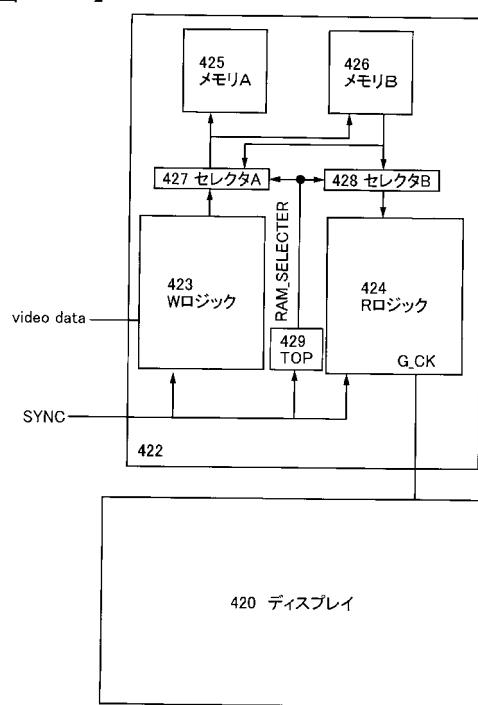

図21に、本実施の形態における別の構成を示すブロック図を示す。

【0104】

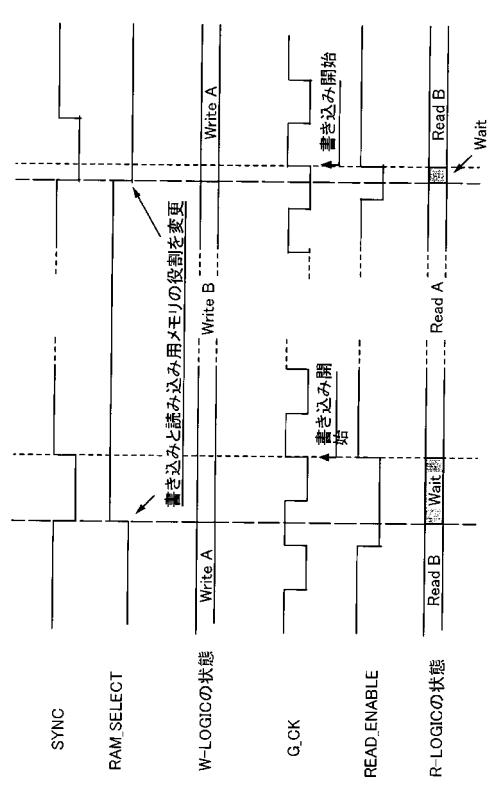

制御回路422はメモリ(A)425及びメモリ(B)426、メモリ書き込み又は読み込み用を選択するセレクタ(A)427、セレクタ(B)428、メモリへの書き込みを行う論理回路(Wロジック423)、メモリからの読み取りを行いディスプレイ420に出力を行う論理回路(Rロジック424)、垂直方向同期信号(SYNC)の開始点を判定する回路(TOP429)から構成される。

【0105】

同期をとる方法として、SYNC、G\_CK、RAM\_SELECTOR、READ\_ENABLEの信号を新たに導入する。

50

## 【0106】

RAM\_SECTOR は SYNC 信号が入力されるたびに反転し、メモリ (A) 425 及びメモリ (B) 426 の書き込み用読み取り用の役目をセレクタ (A) 427、セレクタ (B) 428 によって決定される。

## 【0107】

図 22 に TOP 429、W ロジック、R ロジック、の動作を示すタイミングチャートを示す。SYNC 信号が入力されると RAM セレクタは反転し、2 つのメモリ (A) 425 とメモリ (B) 426 の書き込みと読み取りの役目が入れ替わる。また、同時に W-LOGIC は書き込みを行い R-LOGIC は読み込みを開始し、READ\_ENABLE 信号が H レベル (又は、L レベル) になる。

10

## 【0108】

図 23 に書き込み、読み取りのタイミングと同期の取り方のタイミングチャートを示す。垂直方向同期信号 (SYNC) によって RAM\_SECTOR は反転し、書き込み用メモリと読み取り用メモリの役目が入れ替わる。よって W-LOGIC はデータの書き込みに図 21 に示したメモリ (A) 425 とメモリ (B) 426 を交互に使用する。

## 【0109】

READ\_ENABLE は、H レベルのとき R-LOGIC が読み込み開始可能状態を表し、L レベルのときは待機状態 (Wait) を表す信号とする。

## 【0110】

READ\_ENABLE は RAM\_SECTOR が反転してから水平方向同期信号 (G\_CK) の開始点 (High) から書き込み可能状態 (High) になり R-LOGIC の状態は読み込み待機状態 (Wait) から読み込み開始可能状態になる。なお R-LOGIC の読み込み待機状態 (Wait) は読み込み周期が終わった時点で自動的に読み込み待機状態 (Wait) になる。つまり垂直方向同期信号によって RAM\_SECTOR を反転させ、G\_CK、READ\_ENABLE 信号の各状態から読み込み待機状態 (Wait) 期間を変更させる。なお水平方向同期信号 (G\_CK) の開始と読み込み開始可能状態又は待機状態を示す READ\_ENABLE は、H レベル又は L レベルでも良い。

20

## 【0111】

よって R-LOGIC の待機状態 (Wait) の期間を調整することによって異なる書き込みと読み込み周期の同期が取れる事になる。

30

## 【0112】

本実施の形態では図 21 のブロック図に限られず、図 24 に示したブロック図を用いることができる。図 24 は、図 21 と同様の符号により示されているが、セレクタ (A) 427 とセレクタ (B) 428 の機能が異なっている。セレクタ (A) 427 は R ロジック 424 へのデータ書き込みが可能であり、セレクタ (B) 428 は W ロジックからのデータの読み込みが可能である。これにより、メモリ (A) 425 とメモリ (B) 426 の両者について、データの読み取りと書き込みの機能を入れ替えることができる。

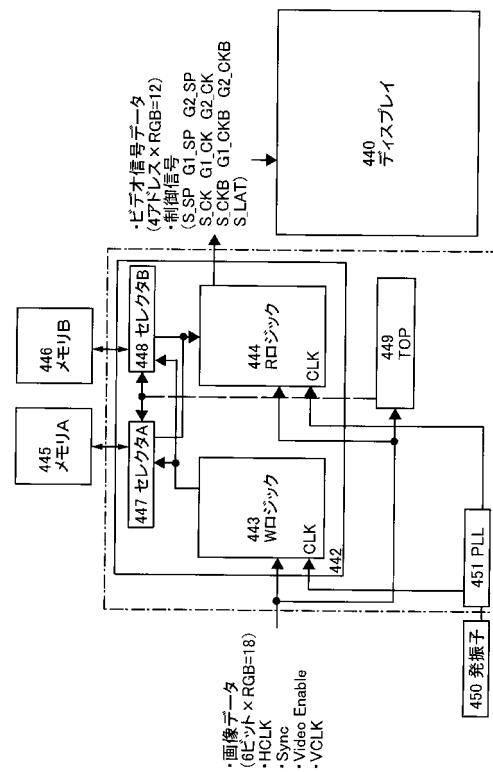

## 【0113】

次に、図 25 を用いて、発光素子を用いた表示用パネルに出力する制御回路の構成の一例を説明する。

40

## 【0114】

制御回路である FPGA 442 には 18 ビット (6 ビット × RGB) の Video\_Data と制御信号が入力される。Video\_Data が入力されてからディスプレイ 440 に出力するまでの動作を説明する。

## 【0115】

各行の読み込みの制御は VCLK (周期 68.6 μsec) で行なわれる。まず SYNC 信号が入力される事で Video\_Data の入力が始まる。SYNC 信号が入力された後一定期間のオフ期間を経て W ロジック 443 に Video\_Data の入力が始まる。VCLK 半周期につき 1 行分の Video\_Data が読み取られる。220 行分の入力

50

が終わると一定期間のオフ期間を経て再び S Y N C 信号が入力され V i d e o \_ D a t a が入力される。全面の入力周期は 1 6 . 6 6 9 8 m s e c ( V C L K 2 4 3 周期分、1 秒間に 60 周期) である。

#### 【 0 1 1 6 】

一行内の各ブロックへの読み込みの制御は H C L K ( 周期 4 0 0 n s ) で行なわれる。 V i d e o \_ E n a b l e が H i g h の期間中 V i d e o \_ D a t a を読み出す。1 行分、すなわち 1 7 6 ブロック分のデータを読み終わると一定期間のオフ期間 ( V i d e o \_ E n a b l e が L レベル) を経て次の行の V i d e o \_ D a t a を読み出す。これを 2 2 0 行分繰り返すことで一画面分のデータとなる。

#### 【 0 1 1 7 】

一方、 F P G A 4 4 2 にはメモリ ( A ) 4 4 5 及びメモリ ( B ) 4 4 6 が接続され、 S Y N C 信号が入力毎に R A M \_ S E L E C T の値を反転させる。

#### 【 0 1 1 8 】

F P G A からの信号 R A M \_ S E L E C T によって、セレクタ ( A ) 4 4 7 、セレクタ ( B ) 4 4 8 を動作させ、どちらのメモリに書き込む、また読み取るかを決定する。

#### 【 0 1 1 9 】

F P G A には  $6 \times 8 \times 3 = 144$  個のフリップフロップによって構成され、各フリップフロップはある点での一色分のデータ ( 6 ビット ) を格納する事ができる。データは H C L K によって順次隣のフリップフロップに移動され、8 ブロック分のデータが揃うと 144 個のレジスタに格納され、 R A M \_ S E L E C T によって決められたメモリに書き込まれる。

#### 【 0 1 2 0 】

ディスプレイ 4 4 0 の表示は時間階調で行うために、メモリ ( A ) 4 4 5 又はメモリ ( B ) 4 4 6 に書き込まれたデータはディスプレイ出力用に並び替えを行い、順次ディスプレイ 4 4 0 に出力される。 R ロジック 4 4 4 はディスプレイ出力用に並び替えられた全面分のデータをメモリ ( A ) 4 4 5 又はメモリ ( B ) 4 4 6 内から読み込み、ディスプレイ 4 0 に出力する。

#### 【 0 1 2 1 】

ディスプレイ 4 4 0 に表示する際には、ビデオ信号データは 4 ( アドレス )  $\times$  R G B ( 3 色 ) = 12 ビット単位で取り扱う。 G 1 \_ C K 、 G 2 \_ C K 、 G 1 \_ C K B 、 G 2 \_ C K B はそれぞれ周期  $12 \mu s$  のクロックである。 G 1 \_ C K 、 G 1 \_ C K B が立ちあがる、又は立ち下がるタイミングでビデオ信号データが入力される行が移動する。

#### 【 0 1 2 2 】

G 1 \_ S P が立ち下がってから 2 周期 (  $24 \mu s$  ) 後に上の行から順に書き込みが行なわれる。2 2 0 行分書き込みが終わると一画面分の表示となるが、次の画面の表示の前に書き込みを遅らせるために 4 周期 (  $48 \mu s$  ) 分のダミーサイクルが入る。また、必要によって書き込みの消去を行うときには G 2 \_ S P を立ちあげる。

#### 【 0 1 2 3 】

S \_ C K 、 S \_ C K B は周期 2 0 0 n s e c のクロックである。 S \_ C K 、 S \_ C K B が立ちあがる、又は立ち下がるタイミングで V i d e o \_ D a t a が入力されるブロックが移動する。 G 1 \_ C L K が立ち上がる若しくは立ち下がってから 4 周期 ( 8 0 0 n s e c ) 後に S \_ L A T が H i g h になって電荷の保持を行い、続いて S \_ S P が H レベルから L レベルになるときにビデオ信号データの入力が始まる。入力は 4 アドレス毎に行うので、4 4 回繰り返す事で 1 行分の書き込みが終了する。

#### 【 0 1 2 4 】

W ロジック 4 4 3 と R ロジック 4 4 4 の動作は発振子 4 5 0 からの P L L 4 5 1 を通したクロックを入力することによって行なっている。また、メモリ ( A ) 4 4 5 及びメモリ ( B ) 4 4 6 への書き込み及び読み取りのタイミングは、 T O P 4 4 9 を通したクロックの立ちあがり及び立ち下がりを使用している。

#### 【 0 1 2 5 】

10

20

30

40

50

W ロジック 4 4 3 及び R ロジック 4 4 4 は L S I を用いても良いし、 F P G A を用いることもできる。

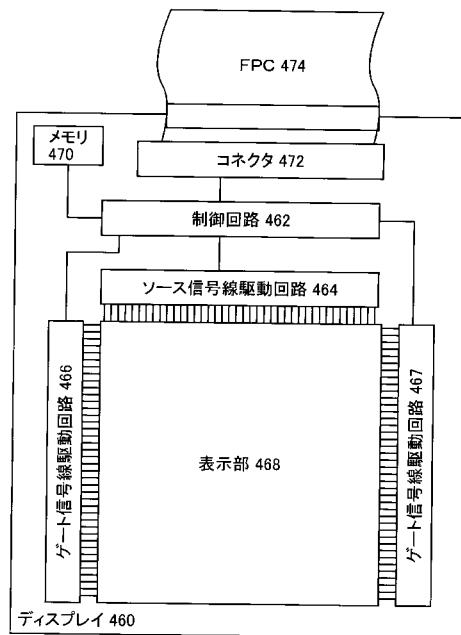

【 0 1 2 6 】

次に、図 2 6 を用いて、制御回路による発光素子を用いた表示装置の一例を示す。

【 0 1 2 7 】

表示装置は、制御回路 4 6 2 、ソース信号線駆動回路 4 6 4 、ゲート信号線駆動回路 4 6 6 及びゲート信号線駆動回路 4 6 7 、表示部 4 6 8 、メモリ 4 7 0 、 F P C 4 7 4 とコネクタ 4 7 2 よりなる。表示装置の各回路はパネル 4 6 0 上に形成若しくは外付けされる。

【 0 1 2 8 】

10 F P C 4 7 4 からコネクタ 4 7 2 を通して送られたデータ及び制御信号は制御回路 4 6 2 に入力され、メモリ 4 7 0 でデータを出力用に並び替えられて再び制御回路 4 6 2 に送られる。制御回路 4 6 2 はデータ及び表示に用いる信号をソース信号線駆動回路 4 6 4 、ゲート信号線駆動回路 4 6 6 、 4 6 7 に送り、発光素子を用いた表示部 4 6 8 で表示を行う。

【 0 1 2 9 】

ソース信号線駆動回路 4 6 4 及びゲート信号線駆動回路 4 6 6 、 4 6 7 は公知のものを用いる事ができる。また、回路の構成によってはゲート信号線駆動回路は一つでも良い。

【 0 1 3 0 】

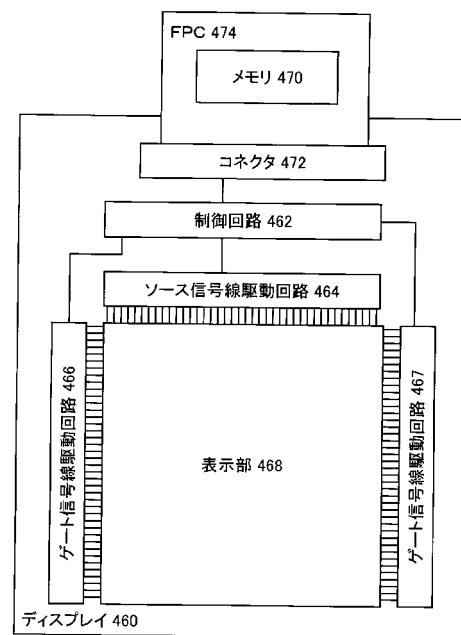

次に、図 2 7 を用いて、制御回路による発光素子を用いた表示装置の別の例を示す。

【 0 1 3 1 】

表示装置は、制御回路 4 6 2 、ソース信号線駆動回路 4 6 4 、ゲート信号線駆動回路 4 6 6 及び 4 6 7 、表示部 4 6 8 、メモリ 4 7 0 、 F P C 4 7 4 よりなるコネクタ 4 7 2 よりなる。表示装置の各回路はパネル 4 6 0 上に形成若しくは外付けされる。

【 0 1 3 2 】

動作の説明を行う。 F P C 4 7 4 からコネクタ 4 7 2 を通して送られたデータ及び制御信号は制御回路 4 6 2 に入力されたのちに、データを F P C 4 7 4 内のメモリ 4 7 0 に戻してデータを出力用に並べ替えられ、再び制御回路 4 6 2 に送られる。制御回路 4 6 2 はデータ及び表示に用いる信号をソース信号線駆動回路 4 6 4 、ゲート信号線駆動回路 4 6 6 、 4 6 7 に送り、発光素子を用いた表示部 4 6 8 で表示を行う。

【 0 1 3 3 】

30 なお、ソース信号線駆動回路 4 6 4 及びゲート信号線駆動回路 4 6 6 、 4 6 7 は公知のものを用いる事ができる。また、回路の構成によってはゲート信号線駆動回路は一つでも良い。

【 0 1 3 4 】

図 2 7 のようにすることで、メモリ 4 7 0 が F P C 4 7 4 内に組み込まれ、表示装置の小型化を図ることができる。

【 0 1 3 5 】

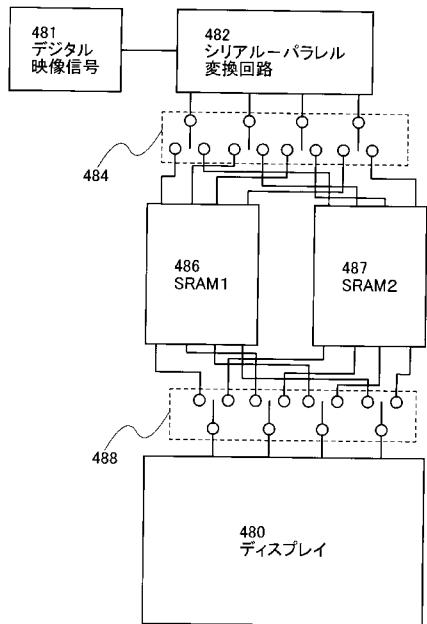

次に、図 2 8 を用いて、別の構成による発光素子を用いたディスプレイに出力する制御回路の一例を説明する。

【 0 1 3 6 】

40 時間階調表示はアナログ表示に比較して、必然的に動作周波数が高くなる。階調数を 1 ビット増やすためには最低 1 サブフレーム追加する必要があり、 8 ビット階調を得るためにサブフレームは 8 以上必要である。さらに、暗部の階調数を増やして自然な画像となるようにガンマ補正を施すには、さらにサブフレーム数を増やす必要があり、サブフレーム数は 10 以上必要となる場合もある。そのため、動作周波数も 10 倍以上にしなければならない。

【 0 1 3 7 】

このような動作周波数で駆動を行うためには使用する S R A M も高速動作が必要であり、高速用の S R A M - I C を使用する必要がある。

【 0 1 3 8 】

ところが、高速用のSRAMは保持時の消費電力が大きく、モバイル機器には適していない。また、低消費電力のSRAMを使用するためには周波数をさらに下げる必要がある。

【0139】

図28に示すように、デジタル映像信号481をSRAM(1)486、SRAM(2)487に書き込みをする前にシリアル・パラレル変換回路482を用いてデジタル映像信号をシリアルからパラレルに変換し、その後でスイッチ484、スイッチ488を介してディスプレイ480に書き込みを行う。

【0140】

このような対策をとることによって、呼び出し時も低周波数でパラレルな呼び出しが可能となるため、低消費電力SRAMが低周波数で使用でき、モバイル機器の電力を下げる事ができる。

【0141】

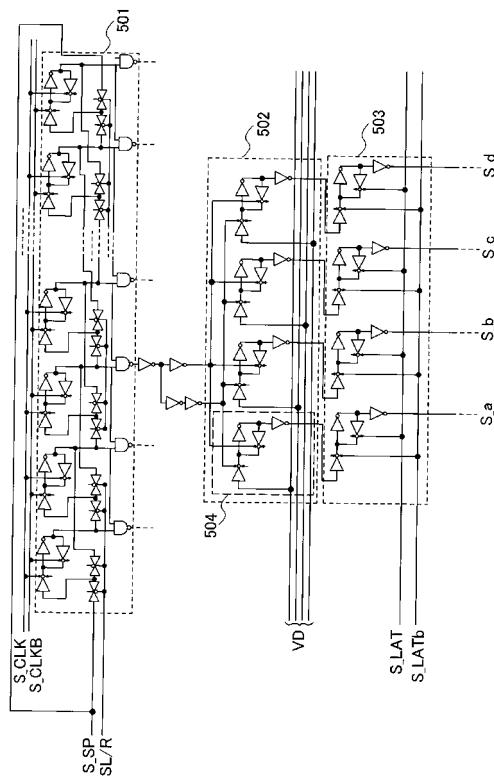

(実施の形態5)

本実施の形態では、本発明に係る表示装置のソース信号線駆動回路の構成例について説明する。ソース信号線駆動回路の構成例を図29に示す。

【0142】

ソース信号線駆動回路は、シフトレジスタ501と、走査方向切り換え回路、LAT(A)502及びLAT(B)503によって構成されている。図29では、シフトレジスタ501からの出力の1つに対応する、LAT(A)502の一部とLAT(B)503の一部のみを図示するが、シフトレジスタ501からの全ての出力に対して、同様の構成のLAT(A)502及びLAT(B)503が対応する。

【0143】

シフトレジスタ501は、クロックドインバータ、インバータ、NAND回路によって構成されている。シフトレジスタ501には、ソース信号線駆動回路用スタートパルスS\_SPが入力され、ソース信号線駆動回路用クロックパルスS\_CLKとその極性が反転した信号であるソース信号線駆動回路用反転クロックパルスS\_CLK\_Bによって、クロックドインバータが導通状態、非導通状態と変化することによって、NAND回路から順に、LAT(A)502にサンプリングパルスを出力する。

【0144】

また、走査方向切り換え回路は、スイッチによって構成され、シフトレジスタ501の走査方向を、図面向かって左右に切り換える働きをする。図29では、左右切り換え信号L/RがLoの信号に対応する場合、シフトレジスタ501は、図面向かって左から右に順にサンプリングパルスを出力する。一方、左右切り換え信号L/RがHレベルの信号に対応する場合、図面向かって右から左に順にサンプリングパルスを出力する。

【0145】

ステージのLAT(A)502は、クロックドインバータと、インバータによってラッチ回路504が構成されている。ここで、各ステージのLAT(A)502とは、1本のソース信号線に入力する映像信号を取り込むLAT(A)502を示すものとする。

【0146】

信号制御回路より出力されたデジタル映像信号はVDは、p分割(pは自然数)されて入力される。つまり、p本のソース信号線への出力に対応する信号が並列に入力される。サンプリングパルスが、バッファを介して、p個のステージのLAT(A)502のクロックドインバータに同時に入力されると、p分割された入力信号はp個のステージのLAT(A)502において、それぞれ同時にサンプリングされる。

【0147】

本実施の形態は、x本のソース信号線に信号電圧を出力するソース信号線駆動回路を例に説明しているので、1水平期間あたり、x/p個のサンプリングパルスが順にシフトレジスタより出力される。各サンプリングパルスに応じて、p個のステージのLAT(A)502は、同時にp本のソース信号線への出力に対応するデジタル映像信号をサンプリングする。

## 【0148】

本明細書中では、このようにソース信号線駆動回路に入力するデジタル映像信号を、p相の並列信号に分割し、p個のデジタル映像信号を1つのサンプリングパルスによって同時に取り込む手法を、p分割駆動と呼ぶことにする。図29では4分割を行なっている。

## 【0149】

上記分割駆動を行うことによって、ソース信号線駆動回路のシフトレジスタのサンプリングにマージンを持たせることができる。こうして表示装置の信頼性を向上させることができる。

## 【0150】

各ステージのLAT(A)502に1水平期間の信号がすべて入力されると、ラッチパルスLS及びその極性が反転した、反転ラッチパルスLSBが入力されて、各ステージのLAT(A)502に入力された信号を各ステージのLAT(B)503へ一斉に出力する。

## 【0151】

なお、ここで各ステージのLAT(B)503とは、各ステージのLAT(A)502からの信号をそれぞれ入力する、LAT(B)503のことと示すとする。

## 【0152】

LAT(B)503の各ステージは、クロックドインバータ及び、インバータによって構成されている。LAT(A)502の各ステージより出力された信号は、LAT(B)503に保持されると同時に、各ソース信号線S1～Sxに出力される。なお、ここでは図示しなかったが、レベルシフタやバッファ等を適宜設けても良い。

## 【0153】

シフトレジスタ501及びLAT(A)502、LAT(B)503に入力されるスタートパルスS\_S\_P、クロックパルスS\_CLK等は、本発明の実施の形態で示したディスプレイコントローラから入力されている。

## 【0154】

本実施の形態では、ビット数の少ないデジタル映像信号を、ソース信号線駆動回路のLAT(A)に入力する動作を信号制御回路によって行い、同時にソース信号線駆動回路のシフトレジスタに入力されるクロックパルスS\_CLKや、スタートパルスS\_S\_P等の周波数を小さくし、ソース信号線駆動回路を動作させる駆動電圧を低くする動作を、ディスプレイコントローラによって行う。

## 【0155】

こうして、第2の表示モードにおいて、ソース信号線駆動回路がデジタル映像信号をサンプリングする動作を少なくして、表示装置の消費電力を抑えることができる。

## 【0156】

本実施の形態の表示装置は、本実施の形態のソース信号線駆動回路の構成に限らず、公知の構成のソース信号線駆動回路を自由に用いることができる。また、ソース信号線駆動回路の構成により、ディスプレイコントローラからソース信号線駆動回路に入力される信号線の数や、駆動電圧の電源線の本数も異なった構成になる。

## 【0157】

本実施の形態は、実施の形態1～実施の形態4と自由に組み合わせて実施することが可能である。

## 【0158】

(実施の形態6)

本実施の形態では、本発明の表示装置のゲート信号線駆動回路の構成例について説明する。

## 【0159】

ゲート信号線駆動回路は、シフトレジスタ、走査方向切り換え回路等によって構成されている。なお、ここでは図示しなかったが、レベルシフタやバッファ等を適宜設けても良い。

10

20

30

40

50

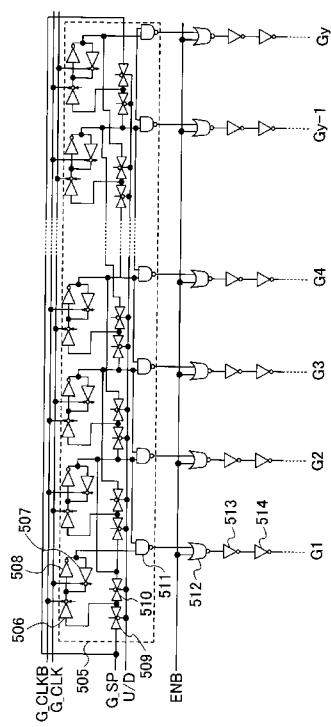

## 【0160】

シフトレジスタには、スタートパルス G\_SP、クロックパルス G\_CLK、駆動電圧等が入力されて、ゲート信号線選択信号を出力している。

## 【0161】

ゲート信号線駆動回路の構成について、図30を用いて説明する。シフトレジスタ505は、クロックドインバータ506、クロックドインバータ507、インバータ508、NAND回路511によって構成されている。シフトレジスタ505には、スタートパルス G\_SPが入力され、クロックパルス G\_CLKとその極性が反転した信号である反転クロックパルス G\_CLKBによって、クロックドインバータ506及び507が導通状態、非導通状態と変化することによって、NAND回路511から順に、サンプリングパルスを出力する。

## 【0162】

また、走査方向切り換え回路は、スイッチ509及びスイッチ510によって構成され、シフトレジスタの操作方向を図面向かって左右に切り換える働きをする。図30では、走査方向切り換え信号 U/D が LO の信号に対応する場合、シフトレジスタは、図面向かって左から右に順に、サンプリングパルスを出力する。一方、走査方向切り換え信号 U/D が H レベルの信号に対応する場合、図面向かって右から左に順にサンプリングパルスを出力する。

## 【0163】

シフトレジスタから出力されたサンプリングパルスは、NOR回路512に入力され、イネーブル信号 ENB と演算される。この演算は、サンプリングパルスのなまりによって、隣り合うゲート信号線が同時に選択される状況を防ぐために行われる。NOR回路512から出力された信号は、バッファ513、バッファ514を介して、ゲート信号線 G1 ~ Gy に出力される。なお、ここでは図示しなかったが、レベルシフタやバッファ等を適宜設けても良い。

## 【0164】

シフタレジスタに入力されるスタートパルス G\_SP、クロックパルス G\_CLK、駆動電圧等は、実施の形態で示したディスプレイコントローラから入力されている。

## 【0165】

なお、本実施の形態の表示装置は、図30で示すゲート信号線駆動回路の構成に限定されず、公知の構成のゲート信号線駆動回路を自由に用いることができる。ゲート信号線駆動回路の構成により、ディスプレイコントローラからゲート信号線駆動回路に入力される信号線の数や、駆動電圧の電源線の本数も異なった構成になる。

## 【0166】

本実施の形態は、実施の形態1～実施の形態5と自由に組み合わせて実施することが可能である。

## 【0167】

## (実施の形態7)

時間階調を用いた表示装置では以上に述べてきた、アドレス期間と点灯期間を分離する方式のほかに、書き込みと表示を同時にを行うような駆動方法も提案されている。例えば、特開2001-343933号公報に開示されている。この方式では従来の選択 TFT、駆動 TFT のほかに消去 TFT を追加し、階調数を向上させることができる。

## 【0168】

具体的には、ゲート信号線駆動回路を複数設けて、第1のゲート信号線駆動回路で書き込みを行い、全ラインが書き込み終わる前に第2のゲート信号線駆動回路で消去を行うものである。4ビット程度では余り効力はないが、階調が6ビット以上になる場合や、擬似輪郭対策でサブフレームを多く増やさねばならない場合には、非常に有効な対策である。本発明はこのような駆動方法をとる表示装置においても適応可能である。

## 【0169】

図31に4ビット階調表示を行う場合のタイミングチャートを示す。図31では4ビッ

10

20

30

40

50

ト目で第2のゲート信号線駆動回路で消去を行って点灯期間を短縮している。

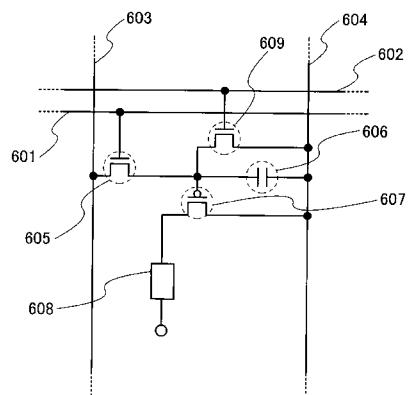

【0170】

この駆動方法を実現するための画素構成の例を図32、図33、図34に示す。図32は、消去TFTを設けた例である。信号の書き込みを行いたい場合は、第1のゲート信号線601の電位を高くすることにより、第1のゲート信号線601を選択し、選択TFT605をオン状態にして、ソース信号線603から信号を保持容量606に入力する。すると、その信号に応じて、駆動TFT607の電流が制御され、電源線604から発光素子608に電流が流れる。

【0171】

信号を消去したい場合は、第2のゲート信号線602の電位を高くすることにより、第2のゲート信号線602を選択し、消去TFT609をオン状態にして、駆動TFT607がオフ状態になるようする。すると、電源線604から発光素子608に電流が流れなくなる。その結果、非点灯期間を作ることができ、点灯期間の長さを自由に制御できるようになる。

【0172】

図32では、消去TFT609を用いていたが、別の方法を用いることも出来る。なぜなら、強制的に非点灯期間を作れば良いので、発光素子608に電流が供給されないようにすれば良いからである。よって、電源線604から発光素子608に電流が流れる経路のどこかに、スイッチを配置して、そのスイッチのオンオフを制御して、非点灯期間を作れば良い。あるいは、駆動TFT607のゲート及びソース間電圧を制御して、駆動TFTが強制的にオフになるようにすれば良い。

【0173】

図33は、駆動TFTを強制的にオフにする場合の例である。選択TFT605、駆動TFT607、消去ダイオード610、発光素子608が配置されている。選択TFT605のソースとドレインは各々、ソース信号線603と駆動TFT607のゲートに接続されている。選択TFT605のゲートは、第1のゲート信号線601に接続されている。駆動TFT607のソースとドレインは各々、電源線604と発光素子608に接続されている。消去ダイオード610は、駆動TFT607のゲートと第2のゲート信号線602に接続されている。

【0174】

保持容量606は、駆動TFT607のゲート電位を保持する役目をしている。よって、駆動TFT607のゲートと電源線604の間に接続されているが、これに限定されない。駆動TFT607のゲート電位を保持できるように配置されていれば良い。また、駆動TFT607のゲート容量などを用いて、駆動TFT607のゲート電位を保持できる場合は、保持容量606を省いても良い。

【0175】

動作方法としては、第1のゲート信号線601の電位を高くすることにより、第1のゲート信号線601を選択し、選択TFT605をオン状態にして、ソース信号線603から信号を保持容量606に入力する。すると、その信号に応じて、駆動TFT607の電流が制御され、電源線604から発光素子608に電流が流れる。

【0176】

信号を消去したい場合は、第2のゲート信号線602の電位を高くすることにより、第2のゲート信号線602を選択し、消去ダイオード610がオンして、第2のゲート信号線602から駆動TFT607のゲートへ電流が流れるようする。その結果、駆動TFT607がオフ状態になる。すると、電源線604から発光素子608に流れなくなる。その結果、非点灯期間を作ることができ、点灯期間の長さを自由に制御できるようになる。

【0177】

信号を保持しておきたい場合は、第2のゲート信号線602を非選択しておく。すると、消去ダイオード610がオフするので、駆動TFT607のゲート電位は保持される。

【0178】

10

20

30

40

50

駆動 T F T 6 0 7 は、整流性がある素子であれば良い。P N型ダイオード、P I N型ダイオード、ショットキー型ダイオード、ツェナー型ダイオードなど様々な整流素子を適用することができる。

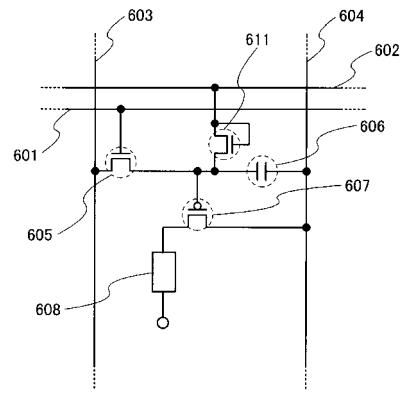

【0179】

また、トランジスタを用いて、ダイオード接続（ゲートとドレインを接続）して、用いても良い。その場合の回路図を図34に示す。消去ダイオード611として、ダイオード接続されたトランジスタを用いている。ここでは、Nチャネル型を用いているが、これに限定されない。Pチャネル型を用いても良い。

【0180】

本実施の形態は実施の形態1～実施の形態6と自由に組み合わせることができる。

10

【0181】

（実施の形態8）

本実施の形態では、実施の形態7と同様に、アドレス期間と点灯期間を同時に行う他の方について説明する。この場合のタイミングチャートを図35に示す。画素構成は図11に示したものと同様である。

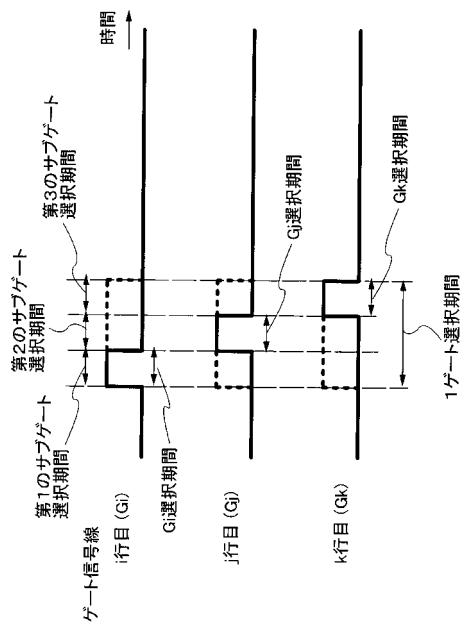

【0182】

図36に示すように、1ゲート選択期間を複数のサブゲート選択期間に分割する（図36の場合は、3つに分割している）。そして、各サブゲート選択期間内で、各々のゲート信号線の電位を高くすることにより、各々のゲート信号線を選択し、その時に対応する信号をソース信号線に入力する。例えば、ある1ゲート選択期間において、第1のサブゲート選択期間ではi行目を選択し、第2のサブゲート選択期間ではj行目を選択し、第3のサブゲート選択期間ではk行目を選択する。そして、次の1ゲート選択期間では、第1のサブゲート選択期間ではi+1行目を選択し、第2のサブゲート選択期間ではj+1行目を選択し、第3のサブゲート選択期間ではk+1行目を選択する。このようにすると、1ゲート選択期間において、あたかも同時に3行分を選択したかのように動作させることができる。

20

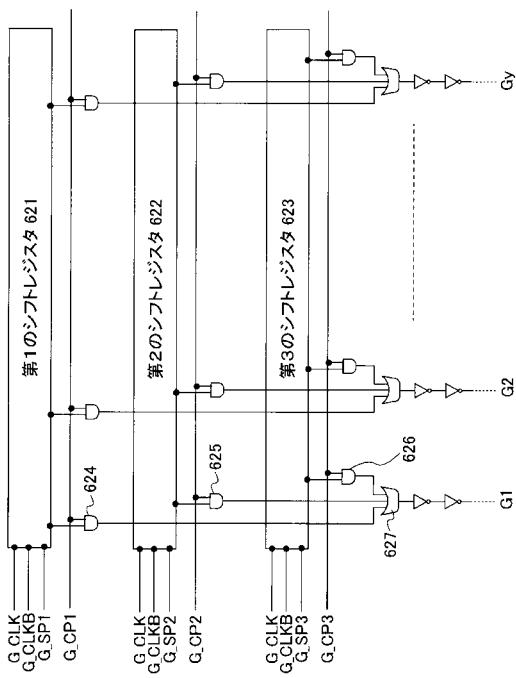

【0183】

この駆動方法を実施するときのゲート信号線駆動回路の構成例を図37に示す。1ゲート選択期間を3つのサブゲート選択期間に分割する場合、第1のシフトレジスタ621、第2のシフトレジスタ622及び第3のシフトレジスタ623を用意する。シフトレジスタについては、例えば、実施の形態6で示したゲート線選択回路（図30）に記載のシフトレジスタ505を用いても良い。第1のシフトレジスタ621、第2のシフトレジスタ622、第3のシフトレジスタ623は、それぞれスタートパルスG\_S P 1、G\_S P 2、G\_S P 3により駆動し、それぞれサンプリングパルスを出力する。次に、それぞれのサンプリングパルスと1ゲート選択期間分割用信号G\_C P 1、G\_C P 2、G\_C P 3をAND回路624、AND回路625、AND回路626に入力し、論理積を計算する。最後に、AND回路624、AND回路625、AND回路626の出力をOR回路627に入力し、論理和を計算する。そして、OR回路627の出力信号がHレベルとなる期間のみ、ゲート信号線が選択される。

30

【0184】

なお、スタートパルスG\_S P 1、G\_S P 2、G\_S P 3、及び1ゲート選択期間分割用信号G\_C P 1、G\_C P 2、G\_C P 3は、ディスプレイコントローラから送られる。本実施の形態におけるディスプレイコントローラの構成例を図38に示す。図38に示した例では、それぞれのシフトレジスタに対するスタートパルス及び1ゲート選択期間分割用信号を生成する垂直クロック発生回路334a、334b、334cを設けている。これにより、それぞれのシフトレジスタを独立に駆動できるようになる。

40

【0185】

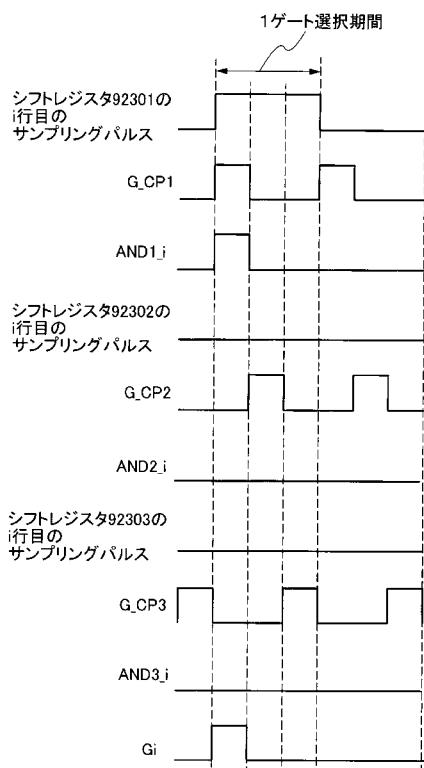

次に、本実施の形態のゲート線選択回路のタイミングチャートを図39、に示す。図39は、第1のシフトレジスタ621を用いて、i行目のゲート線を選択する場合を示している。

50

## 【0186】

1ゲート選択期間分割用信号は、1ゲート選択期間を1周期とする信号とし、1ゲート選択期間分割用信号G\_C\_P1は、1ゲート選択期間の最初の1/3期間のみHレベルの信号で、残りの2/3期間はLoの信号とする。同様に、1ゲート選択期間分割用信号G\_C\_P2は、1ゲート選択期間の真ん中の1/3期間のみHレベルの信号で、残りの2/3期間はLoの信号とし、1ゲート選択期間分割用信号G\_C\_P3は、1ゲート選択期間の最後の1/3期間のみHレベルの信号で、残りの2/3期間はLoの信号とする。

## 【0187】

例えば、第1のシフトレジスタ621のi行目のサンプリングパルスのみがHレベルの信号となる場合を考える。ここで、各シフトレジスタのi行目のサンプリングパルスと1ゲート選択期間分割用信号に対するAND回路の出力信号をAND1\_i、AND2\_i、AND3\_iに示す。第1のシフトレジスタ621のi行目のサンプリングパルスのみがHレベルの信号となっているため、1ゲート選択期間分割用信号G\_C\_P1との論理積を計算すると、1ゲート選択期間の最初の1/3期間のみHレベルとなる信号が得られる。また、第2のシフトレジスタ622、第3のシフトレジスタ623のi行目のサンプリングパルスはLoの信号となっているため、1ゲート選択期間分割用信号との論理積を計算すると、1ゲート選択期間中Loとなる信号が得られる。最後にAND1\_i、AND2\_i、AND3\_iの論理和を計算すると、1ゲート選択期間の最初の1/3期間のみHレベルとなる信号が得られる。したがって、i行目のゲート信号線が1ゲート選択期間の最初の1/3期間のみ選択される。

10

20

30

40

## 【0188】

同様に、第2のシフトレジスタ622のj行目のサンプリングパルスのみがHレベルの信号となる場合には、1ゲート選択期間分割用信号G\_C\_P2を用いることにより、j行目のゲート信号線を1ゲート選択期間の真ん中の1/3期間のみ選択することができる。また、例えば、第3のシフトレジスタ623のk行目のサンプリングパルスのみがHレベルの信号となる場合には、1ゲート選択期間分割用信号G\_C\_P3を用いることにより、k行目のゲート信号線を1ゲート選択期間の最後の1/3期間のみ選択することができる。

## 【0189】

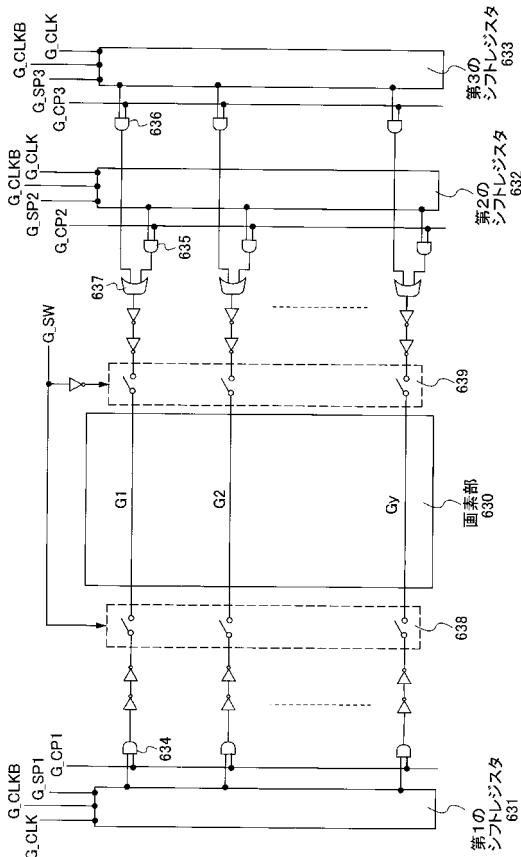

ゲート信号線選択回路の別の構成例を図40に示す。1ゲート選択期間を3つのサブゲート選択期間に分割する場合、第1のシフトレジスタ631、第2のシフトレジスタ632及び第3のシフトレジスタ633を用意し、第1のシフトレジスタ631と、第2のシフトレジスタ632及び第3の633とを、画素部630の両側に配置する。第1のシフトレジスタ631については、その出力であるサンプリングパルスと1ゲート選択期間分割用信号G\_C\_P1をAND回路634に入力する。そして、AND回路634の出力信号がHレベルとなる期間のみ、ゲート信号線が選択される。一方、第2のシフトレジスタ632、第3のシフトレジスタ633については、それぞれのシフトレジスタが出力するサンプリングパルスと1ゲート選択期間分割用信号G\_C\_P2、G\_C\_P3をそれぞれAND回路635、AND回路636に入力し、これらの出力をOR回路637に入力する。そして、OR回路637の出力信号がHレベルとなる期間のみ、ゲート信号線が選択される。なお、AND回路634及びOR回路637の出力線とゲート信号線の間には、スイッチ638、スイッチ639が接続されている。これらのスイッチは、ディスプレイコントローラから送られるスイッチ制御信号G\_SWによって制御され、AND回路634及びOR回路637の出力信号がHレベルとなるゲート信号線に接続されるスイッチをオンにすることにより、ゲート信号線が選択される。

## 【0190】

各行のゲート信号線の両側に接続されている一対のスイッチ638、スイッチ639は、排他的に動作するよう制御する。第1のシフトレジスタ631を用いて、i行目のゲート信号線を選択する場合、i行目のゲート信号線に接続されているスイッチのうち、スイッチ638をオンにし、スイッチ639をオフにする。これにより、第1のシフトレジスタ631の出力のみがi行目のゲート信号線に入力される。また、第2のシフトレジスタ

50

632を用いて、j行目のゲート信号線を選択する場合、j行目のゲート信号線に接続されているスイッチのうち、スイッチ639をオンにし、スイッチ638をオフにする。これにより、第2のシフトレジスタ632の出力のみがj行目のゲート信号線に入力される。

【0191】

このように、本実施の形態のゲート信号線選択回路を用いることによって、1ゲート選択期間中に3行分のゲート信号線を選択することが可能となる。

【0192】

なお、1ゲート選択期間をa個(aは2以上の自然数)のサブゲート選択期間に分割する場合は、シフトレジスタをa段用意し、本実施の形態と同様の方法でゲート信号線選択回路を構成すれば良い。

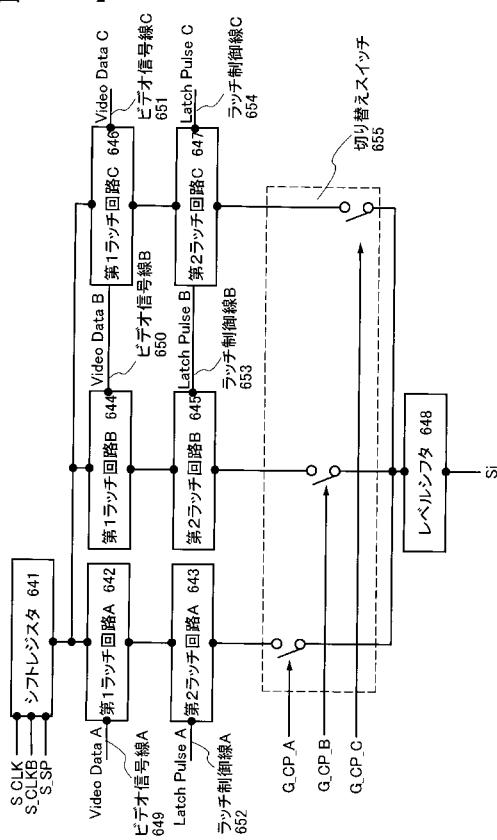

【0193】

次に、この駆動方法を実施するときのソース信号線駆動回路の構成例を図41に示す。図41は、i列目のソース信号線駆動回路について示している。1ゲート選択期間を3つのサブゲート選択期間に分割する場合、シフトレジスタ641の後段に、第1の及び第2のラッチ回路を3組用意する。第1及び第2のラッチ回路の各組では、それぞれ異なる行のビデオ信号を保持する。例えば、第1のラッチ回路(A)642、第2のラッチ回路(A)643では、ビデオ信号線(A)649で入力されるi行目のビデオ信号を保持し、第1のラッチ回路(B)644、第2のラッチ回路(B)645ではビデオ信号線(B)650で入力されるj行目のビデオ信号を保持し、第1のラッチ回路(C)646、第2のラッチ回路(C)647では、ビデオ信号線(C)651で入力されるk行目のビデオ信号を保持する。ラッチ制御線(A)652、ラッチ制御線(B)653、ラッチ制御線(C)654は、それぞれ第2のラッチ回路(A)643、第2のラッチ回路(B)645、第2のラッチ回路(C)647を制御する。そして、どの行のビデオ信号をi列目のソース信号線に入力するかを切り替えスイッチ655により選択し、レベルシフタ648を介して入力する。なお、切り替えスイッチの動作は、3個のサブゲート選択期間ごとに異なるスイッチがオンするように制御すれば良い。例えば、図37で示したゲート信号線駆動回路で用いた1ゲート選択期間分割用信号G\_C\_Pを用い、1ゲート選択期間の最初の1/3期間は、第1のラッチ回路(A)642、第2のラッチ回路(A)643に保持したi行目のビデオ信号だけをソース信号線に入力すれば良い。同様に、1ゲート選択期間の真ん中の1/3期間は、第1のラッチ回路(B)644、第2のラッチ回路(B)645に保持したj行目のビデオ信号だけをソース信号線に入力し、1ゲート選択期間の最後の1/3期間は、第1のラッチ回路(C)646、第2のラッチ回路(C)647に保持したk行目のビデオ信号だけをソース信号線に入力すれば良い。

【0194】

このようなソース信号線駆動回路を用いることによって、1ゲート選択期間内に3行分のビデオ信号をソース信号線に入力することができる。このソース信号線駆動回路と、図37で示したゲート信号線駆動回路を併用することにより、1ゲート選択期間内に複数のゲート信号線を選択するという駆動方法を実施することができる。

【0195】

このような駆動方法を用いると、1フレーム期間あたりの発光素子の点灯期間を多くとることができるために、輝度を向上させることができるとなる。また、各駆動回路(ソース信号線駆動回路及びゲート信号線駆動回路)のシフトレジスタに入力されるクロックパルスやスタートパルス等の周波数を小さくし、各駆動回路を動作させる駆動電圧を低くすることができる。さらに、回路構成が簡単にできるため、廉価版の表示装置に適応が可能である。

【0196】

なお、このような駆動方法の詳細については、例えば、特開2001-324958号公報(米国公開2001/0022565)等に記載されており、その内容を本願と組み合わせて適用することが出来る。

10

20

30

40

50

## 【0197】

なお、本実施の形態は実施の形態1～実施の形態8と自由に組み合わせることができる。

## 【0198】

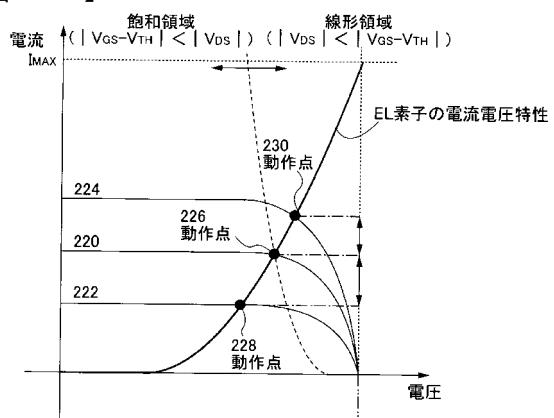

## (実施の形態9)

本実施の形態は、画素における駆動TFTを飽和状態で動作させることにより、駆動TFTを電流源として用いる定電流駆動法について説明する。図42に示すのは、駆動TFTの動作点226、228、230である。定電流駆動をおこなう場合には動作点228があるような飽和領域で、定電圧駆動を行う場合には動作点230があるような線型領域で動作をおこなう。

## 【0199】

定電流駆動法においても、駆動TFTの動作期間を制御することにより、時間階調による表示が可能となる。それについての記述は特開2002-108285号公報(米国公開2002/0047568)に記載されているが、本発明はこのような定電流時間階調についても、適応が可能である。すなわち、実施の形態1～実施の形態8で示す画素を用いて、定電流駆動法で時間階調による階調表示を行うことができる。定電流駆動法を用いることで、発光素子が劣化して発光特性が変化した場合でも、画質の劣化を抑制することができる。

## 【0200】

## (実施の形態10)

実施の形態1～実施の形態9では、時間階調方式を用いる表示装置について説明したが、本発明に係る表示装置は、他の階調方式を適用することができる。例えば、面積階調方式を用いた駆動方法でも適用できる。面積階調方式を適用する場合の画素構成の一例を、図43、図44に示す。面積階調を行う画素の特徴としては、ひとつの画素に、独立に制御できる複数の発光素子があることである。図43、図44における発光素子671、691は、共に、3個の発光素子をもち、そのうち2個を独立に制御できる。独立に制御できる2個の発光素子は、相対的にみて、一方が1の輝度、もう一方が2の輝度を発光することができる。このようにすれば、発光素子を発光若しくは非発光の2値で駆動する場合にも、ひとつの画素内で、0、1、2、3の輝度を表現できることになる。

## 【0201】

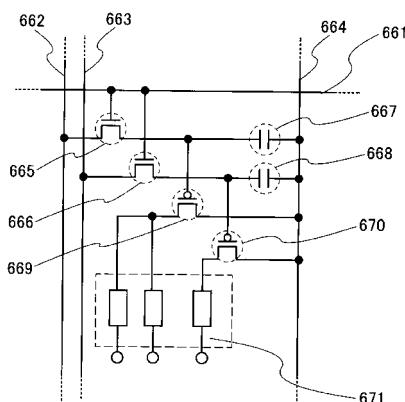

図43は、ソース信号線を複数設け、どのソース信号線にどのような信号を入力するかを制御して、発光させる発光素子の数を変えることにより、階調を表現する場合の構成例である。図43では、ゲート信号線661の電位を高くすることにより、ゲート信号線661を選択し、第1の選択TFT665、第2の選択TFT666をオン状態にして、第1のソース信号線662、第2のソース信号線663から信号を第1の保持容量667、第2の保持容量668にそれぞれ入力する。すると、その信号に応じて、第1の駆動TFT669、第2の駆動TFT670の電流が制御され、電源線664から発光素子671に電流が流れる。

## 【0202】

このとき、第1及び第2のソース信号線に入力する信号によって、発光する発光素子671の数が変化する。例えば、第1のソース信号線662にHレベルの信号を入力し、第2のソース信号線663にL0の信号を入力すると、第1の駆動TFT669のみがオン状態となるため、2個の発光素子が発光する。一方、第1のソース信号線662にL0の信号を入力し、第2のソース信号線663にHレベルの信号を入力すると、第2の駆動TFT670のみがオン状態となるため、1個の発光素子が発光する。また、第1のソース信号線662、第2のソース信号線663にHレベルの信号を入力すると、第1の駆動TFT669、第2の駆動TFT670が共にオン状態となるため、3個の発光素子が発光する。

## 【0203】

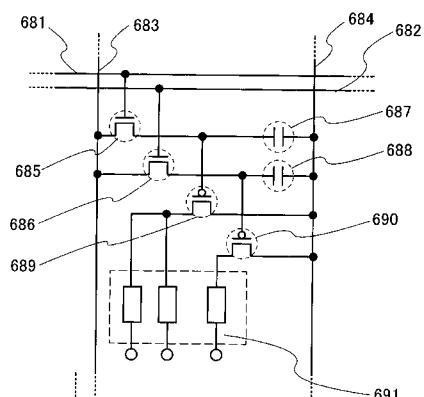

図44は、ゲート信号線を複数設け、どのゲート信号線を選択するかを制御して、発光させる発光素子の数を変えることにより、階調を表現する場合の構成例である。図44では

10

20

30

40

50

、第1のゲート信号線681、第2のゲート信号線682の電位を高くすることにより、第1のゲート信号線681、第2のゲート信号線682を選択し、第1の選択TFT685、第2の選択TFT686をオン状態にして、ソース信号線683から信号を第1の保持容量687、第2の保持容量688にそれぞれ入力する。すると、その信号に応じて、第1の駆動TFT689、第2の駆動TFT690の電流が制御され、電源線684から発光素子691に電流が流れる。

【0204】

このとき、第1及び第2のゲート信号線のうち、どのゲート信号線を選択するかによって、発光する発光素子691の数が変化する。例えば、第1のゲート信号線681のみを選択した場合は、第1の選択TFT685のみがオン状態となり、第1の駆動TFT689のみの電流が制御されるため、2個の発光素子が発光する。一方、第2のゲート信号線682のみを選択した場合は、第2の選択TFT686のみがオン状態となり、第2の駆動TFT690のみの電流が制御されるため、1個の発光素子が発光する。また、第1のゲート信号線681、第2のゲート信号線682の両方を選択すると、第1の選択TFT685、第2の選択TFT686がオン状態となり、第1の駆動TFT689、第2の駆動TFT690の電流が制御されるため、3個の発光素子が発光する。

【0205】

このような画素回路を用いることにより、本発明を面積階調方式に適用することが可能となる。

【0206】

本実施の形態は、実施の形態1～実施の形態9と自由に組み合わせて実施することが可能である。

【0207】

(実施の形態11)

本明細書において、発光素子は、電界が生じると発光するEL層を、陽極及び陰極で挟んだ構造を有する素子を示すものとしている。発光素子とは、一重項励起子から基底状態に遷移する際の発光(蛍光)を利用するものと、三重項励起子から基底状態に遷移する際の発光(燐光)を利用するものの両方を示すものとしている。

【0208】

EL層としては、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等が挙げられる。発光素子は、基本的に、陽極/発光層/陰極の順に積み重ねた構造で示される。この他に、陽極/正孔注入層/発光層/電子注入層/陰極の順に積み重ねた構造や、陽極/正孔注入層/正孔輸送層/発光層/電子輸送層/電子注入層/陰極の順に積み重ねた構造などがある。

【0209】

EL層は、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等が、明確に区別された積層構造を有するものに限定されない。つまり、EL層は、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等を構成する材料が、混合した層を有する構造であっても良い。また、無機物が混合されていても良い。

【0210】

発光素子のEL層としては、低分子有機材料、高分子有機材料、中分子有機材料のいずれの材料であっても良い。また、有機無機複合材料が含まれていても良い。なお、本明細書中において、中分子材料とは、分子数が20以下又は連鎖する分子の長さが10μm以下で、昇華性を有さないものとする。

【0211】

また、発光層は有機材料に限定されず、無機材料を用いて形成することもできる。発光層を形成する母体材料として、無機材料を用いることができる。無機材料としては、亜鉛、カドミウム、ガリウムなど金属材料の硫化物、酸化物、窒化物を用いることが好ましい。例えば、硫化物として、硫化亜鉛(ZnS)、硫化カドミウム(CdS)、硫化カルシウム(CaS)、硫化イットリウム(Y<sub>2</sub>S<sub>3</sub>)、硫化ガリウム(Ga<sub>2</sub>S<sub>3</sub>)、硫化スト

10

20

30

40

50

ロンチウム (SrS)、硫化バリウム (BaS)などを用いることができる。酸化物としては、酸化亜鉛 (ZnO)、酸化イットリウム (Y<sub>2</sub>O<sub>3</sub>)などを用いることができる。また、窒化物としては、窒化アルミニウム (AlN)、窒化ガリウム (GaN)、窒化インジウム (InN)などを用いることができる。さらに、セレン化亜鉛 (ZnSe)、テルル化亜鉛 (ZnTe)なども用いることができ、硫化カルシウム - ガリウム (CaGa<sub>2</sub>S<sub>4</sub>)、硫化ストロンチウム - ガリウム (SrGa<sub>2</sub>S<sub>4</sub>)、硫化バリウム - ガリウム (BaGa<sub>2</sub>S<sub>4</sub>)、などの3元系の混晶であってもよい。

#### 【0212】

不純物元素としては、金属イオンの内殻電子遷移を利用した発光中心を形成するものとして、マンガン (Mn)、銅 (Cu)、サマリウム (Sm)、テルビウム (Tb)、エルビウム (Er)、ツリウム (Tm)、ユーロピウム (Eu)、セリウム (Ce)、プラセオジウム (Pr)などの金属元素を用いることができる。なお、電荷補償として、フッ素 (F)、塩素 (Cl)などのハロゲン元素が添加されていてもよい。

#### 【0213】

また、ドナー - アクセプタ再結合を利用した発光中心として、第一の不純物元素及び第二の不純物元素を含む発光材料を用いることができる。第一の不純物元素としては、例えば、銅 (Cu)、銀 (Ag)、金 (Au)、白金 (Pt)などの金属元素、珪素 (Si)などを用いることができる。第二の不純物元素は、例えば、フッ素 (F)、塩素 (Cl)、臭素 (Br)、ヨウ素 (I)、ホウ素 (B)、アルミニウム (Al)、ガリウム (Ga)、インジウム (In)、タリウム (Tl)などを用いることができる。

#### 【0214】

発光材料は固相反応、すなわち、母体材料及び不純物元素を秤量し、乳鉢で混合、電気炉で加熱して反応させる方法により、母体材料に不純物元素を含有させる。例えば、母体材料と、第一の不純物元素又は第一の不純物元素を含む化合物と、第二の不純物元素又は第二の不純物元素を含む化合物をそれぞれ秤量し、乳鉢で混合した後、電気炉で加熱、焼成を行う。焼成温度は、700～1500が好ましい。温度が低すぎる場合は固体反応が進まず、温度が高すぎる場合は母体材料が分解してしまうからである。なお、粉末状態で焼成を行ってもよいが、ペレット状態で焼成を行うことが好ましい。

#### 【0215】

また、固相反応を利用する場合の不純物元素として、第一の不純物元素と第二の不純物元素で構成される化合物を組み合わせて用いてもよい。この場合、不純物元素が拡散されやすく固相反応が進みやすくなるため、均一な発光材料を得ることができる。さらに余分な不純物元素が入らないため、純度の高い発光材料を得ることができる。第一の不純物元素と第二の不純物元素で構成される化合物としては、例えば、フッ化銅 (CuF<sub>2</sub>)、塩化銅 (CuCl)、ヨウ化銅 (CuI)、臭化銅 (CuBr)、窒化銅 (Cu<sub>3</sub>N)、リン化銅 (Cu<sub>3</sub>P)、フッ化銀 (CuF)、塩化銀 (CuCl)、ヨウ化銀 (CuI)、臭化銀 (CuBr)、塩化金 (AuCl<sub>3</sub>)、臭化金 (AuBr<sub>3</sub>)、塩化白金 (PtCl<sub>2</sub>)などを用いることができる。また、第二の不純物元素の代わりに第三の不純物元素を含んだ発光材料を用いてもよい。

#### 【0216】

第三の不純物元素は、例えば、リチウム (Li)、ナトリウム (Na)、カリウム (K)、ルビジウム (Rb)、セシウム (Cs)、窒素 (N)、リン (P)、ヒ素 (As)、アンチモン (Sb)、ビスマス (Bi)などを用いることができる。これらの不純物元素の濃度は、母体材料に対して0.01～10mol%であれば良く、好ましくは0.1～5mol%の範囲である。

#### 【0217】

高い電気導電性を有する発光材料としては、母体材料として、上述した材料を用い、上述した第一の不純物元素及び第二の不純物元素及び第三の不純物元素を含む発光材料を添加した発光材料を用いることができる。これらの不純物元素の濃度は、母体材料に対して0.01～10mol%であれば良く、好ましくは0.1～5mol%の範囲であれば良い

10

20

30

40

50

。

## 【0218】

第二の不純物元素と第三の不純物元素で構成される化合物としては、例えば、フッ化リチウム(LiF)、塩化リチウム(LiCl)、ヨウ化リチウム(LiI)、臭化銅(CuBr)、塩化ナトリウム(NaCl)などのハロゲン化アルカリ、窒化ホウ素(BN)、窒化アルミニウム(AlN)、アルミニウムアンチモン(AlSb)、ガリウムリン(GaP)、ガリウムヒ素(GaAs)、インジウムリン(InP)、インジウムヒ素(InAs)、インジウムアンチモン(InSb)などを用いることができる。

## 【0219】

母体材料として、上述した材料を用い、上述した第一の不純物元素及び第二の不純物元素及び第三の不純物元素を含む発光材料を用いた発光層は、高電界により加速されたホットエレクトロンを必要とすることなく、発光することが可能である。つまり、発光素子に高電圧を印加する必要がなくなるため、低駆動電圧で動作可能な発光素子を得ることができる。また、低駆動電圧で発光可能であるため、消費電力も低減された発光素子を得ることができる。また、さらに他の発光中心となる元素が含まれていてもよい。

## 【0220】

また、母体材料として上述した材料を用い、第二の不純物元素及び第三の不純物元素及び上述した金属イオンの内殻電子遷移を利用した発光中心を含む発光材料を用いることができる。この場合、発光中心となる金属イオンは、母体材料に対して0.05~5原子%であることが好ましい。また、第二の不純物元素の濃度は、母体材料に対して0.05~5原子%であることが好ましい。また、第三の不純物元素の濃度は、母体材料に対して0.05~5原子%であることが好ましい。このような構成の発光材料は、低電圧で発光可能である。よって、低駆動電圧で発光可能な発光素子を得ることができるために、消費電力が低減された発光素子を得ることができる。また、さらに他の発光中心となる元素が含まれていてもよい。このような発光材料を用いることにより、発光素子の輝度劣化を抑制することができる。また、トランジスタを用いて低電圧で駆動することができる。

## 【0221】

本実施の形態で示す発光素子を、本発明に係る表示装置に適用することにより、コントラストを改善し、画質の向上を図ることができる。また、低消費電力化を図ることができる。

## 【0222】

本実施の形態は、実施の形態1~実施の形態10と自由に組み合わせて実施することができる。

## 【0223】

## (実施の形態12)

本実施の形態では、表示装置を構成するトランジスタの構造について説明する。トランジスタの半導体層にアモルファスシリコン(a-Si:H)膜を用いた場合について説明する。図45にはトップゲートのトランジスタ、図46及び図47にはボトムゲートのトランジスタの場合について示す。

## 【0224】

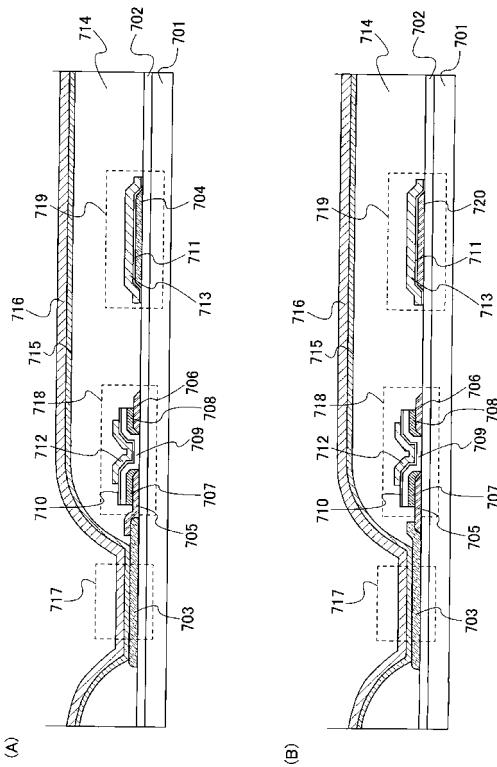

アモルファスシリコンを半導体層に用いたトップゲート構造のトランジスタの断面を図45(A)に示す。図45(A)に示すように、基板701上に下地絶縁膜702が形成されている。さらに下地絶縁膜702上に画素電極703が形成されている。また、画素電極703と同層に同じ材料からなる第1の電極704が形成されている。

## 【0225】

基板はガラス基板、石英基板、セラミック基板などを用いることができる。また、下地絶縁膜702としては、窒化アルミ(AlN)や酸化シリコン(SiO<sub>2</sub>)、酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)などの単層やこれらの積層を用いることができる。

## 【0226】

下地絶縁膜702上に配線705及び配線706が形成され、画素電極703の端部が配

10

20

30

40

50

線 705 で覆われている。配線 705 及び配線 706 の上部に N 型の導電型を有する N 型半導体層 707 及び N 型半導体層 708 が形成されている。また、配線 705 と配線 706 の間であって、下地絶縁膜 702 上に半導体層 709 が形成されている。

【 0227 】

半導体層 709 の一部は N 型半導体層 707 及び N 型半導体層 708 上にまで延長されている。なお、この半導体層はアモルファスシリコン (a-Si:H)、微結晶半導体 ( $\mu$ c-Si:H) 等の非結晶性を有する半導体膜で形成されている。半導体層 709 上にゲート絶縁膜 710 が形成されている。ゲート絶縁膜 710 と同層の同じ材料からなる絶縁膜 711 が第 1 の電極 704 上にも形成されている。なお、ゲート絶縁膜 710 としては酸化シリコン膜や窒化シリコン膜などが用いられる。

10

【 0228 】

ゲート絶縁膜 710 上に、ゲート電極 712 が形成されている。ゲート電極と同層に同じ材料でなる第 2 の電極 713 が第 1 の電極 704 上に絶縁膜 711 を介して形成されている。第 1 の電極 704 及び第 2 の電極 713 で絶縁膜 711 を挟まれた容量素子 719 が形成されている。また、画素電極 703 の端部、駆動トランジスタ 718 及び容量素子 719 を覆い、層間絶縁膜 714 が形成されている。

【 0229 】

層間絶縁膜 714 及びその開口部に位置する画素電極 703 上に発光層 715 及び対向電極 716 が形成され、画素電極 703 と対向電極 716 とで発光層 715 が挟まれた領域では発光素子 717 が形成されている。

20

【 0230 】

図 45 (A) に示す第 1 の電極 704 を図 45 (B) に示すように第 1 の電極 720 で形成しても良い。第 1 の電極 720 は配線 705 及び 706 と同層の同一材料で形成されている。

20

【 0231 】

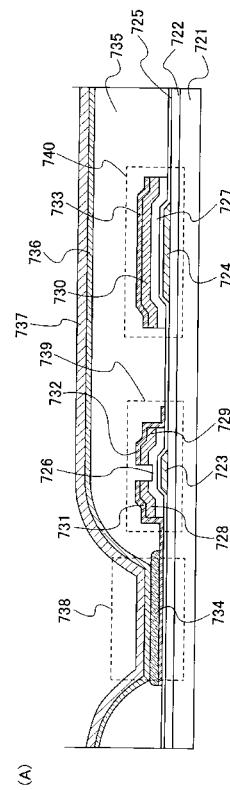

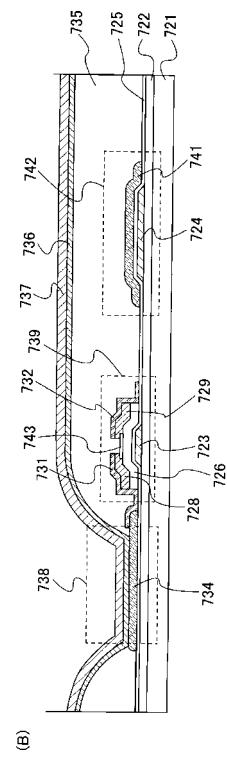

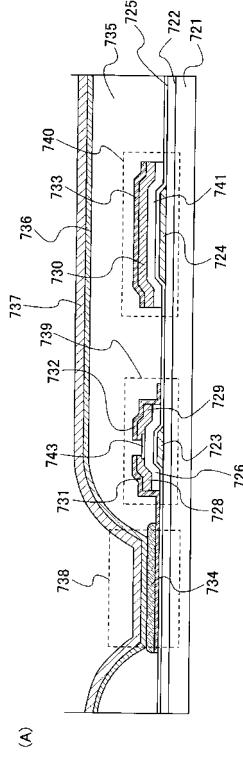

アモルファスシリコンを半導体層に用いたボトムゲート構造のトランジスタを用いた表示装置のパネルの部分断面を図 46 に示す。基板 721 上に絶縁膜 722 が形成されている。さらに絶縁膜 722 上にゲート電極 723 が形成されている。ゲート電極と同層に同じ材料からなる第 1 の電極 724 が形成されている。ゲート電極 723 の材料にはリンが添加された多結晶シリコンを用いることができる。多結晶シリコンの他に、金属とシリコンの化合物であるシリサイドでも良い。

30

【 0232 】

ゲート電極 723 及び第 1 の電極 724 を覆うようにゲート絶縁膜 725 が形成されている。ゲート絶縁膜 725 としては酸化シリコン膜や窒化シリコン膜などが用いられる。

【 0233 】

ゲート絶縁膜 725 上に、半導体層 726 が形成されている。また、半導体層 726 と同層に同じ材料からなる半導体層 727 が形成されている。

【 0234 】

基板はガラス基板、石英基板、セラミック基板などを用いることができる。また、絶縁膜 722 としては、窒化アルミ (AlN) や酸化シリコン (SiO<sub>2</sub>)、酸化窒化シリコン (SiO<sub>x</sub>N<sub>y</sub>) などの単層やこれらの積層を用いることができる。

40

【 0235 】

半導体層 726 上には N 型の導電性を有する N 型半導体層 728、729 が形成され、半導体層 727 上には N 型半導体層 730 が形成されている。N 型半導体層 728、729 上にはそれぞれ配線 731、732 が形成され、N 型半導体層 730 上には配線 731 及び 732 と同層の同一材料からなる導電層 733 が形成されている。

【 0236 】

半導体層 727、N 型半導体層 730 及び導電層 733 からなる第 2 の電極が構成される。なお、この第 2 の電極と第 1 の電極 724 でゲート絶縁膜 725 を挟み込んだ構造の容量素子 740 が形成されている。

50

**【 0 2 3 7 】**

配線 731 の一方の端部は延在し、その延在した配線 731 上部に接して画素電極 734 が形成されている。画素電極 734 の端部、駆動トランジスタ 739 及び容量素子 740 を覆うように絶縁層 735 が形成されている。

**【 0 2 3 8 】**

画素電極 734 及び絶縁層 735 上には発光層 736 及び対向電極 737 が形成され、画素電極 734 と対向電極 737 とで発光層 736 が挟まれた領域では発光素子 738 が形成されている。

**【 0 2 3 9 】**

容量素子の第 2 の電極の一部となる半導体層 727 及び N 型半導体層 730 は設けなくても良い。つまり第 2 の電極は導電層 733 とし、第 1 の電極 724 と導電層 733 でゲート絶縁膜が挟まれた構造の容量素子としても良い。

**【 0 2 4 0 】**

図 46 (A) において、配線 731 を形成する前に画素電極 734 を形成することで、図 46 (B) に示すような、画素電極 734 と同じ材料からなる第 2 の電極 741 と第 1 の電極 724 でゲート絶縁膜 725 が挟まれた構造の容量素子 742 を形成することができる。

**【 0 2 4 1 】**

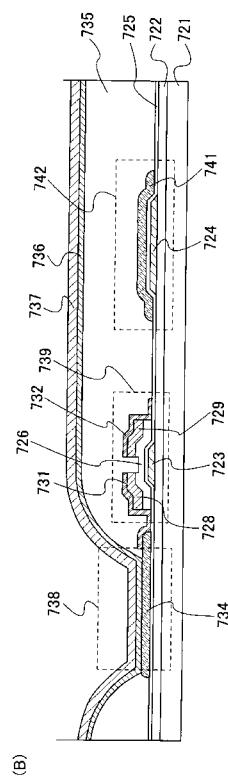

チャネル保護構造のトランジスタの場合について、図 47 (A)、(B) を用いて説明する。図 47 (A) に示すチャネル保護型構造のトランジスタは、図 46 (A) に示したチャネルエッチ構造の駆動トランジスタ 739 の半導体層 726 のチャネルが形成される領域上に絶縁層 743 が設けられている点で異なっている。絶縁層 743 は、ソース及びドレインをエッチングするときのマスクとして利用している。なお、図 46 (A) と共に通する要素は、同じ符号を用いて示している。

**【 0 2 4 2 】**

図 47 (B) に示すチャネル保護型構造のトランジスタは、図 46 (B) に示したチャネルエッチ構造の駆動トランジスタ 739 の半導体層 726 のチャネルが形成される領域上に絶縁層 743 が設けられている点で異なっている。絶縁層 743 は、ソース及びドレインをエッチングするときのマスクとして利用している。なお、図 46 (B) と共に通する要素は、同じ符号を用いて示している。

**【 0 2 4 3 】**

本発明の画素を構成するトランジスタの半導体層（チャネル形成領域やソース領域やドレイン領域など）にアモルファスシリコンを用いることで、製造コストを削減することができる。

**【 0 2 4 4 】**

本発明の画素構成の適用することができるトランジスタの構造や、容量素子の構造は上述した構成に限られず、さまざまな構成のトランジスタの構造や、容量素子の構造のものを用いることができる。

**【 0 2 4 5 】**

本実施の形態で述べた内容は、実施の形態 1 ~ 実施の形態 11 で述べた内容と自由に組み合わせて実施することができる。

**【 0 2 4 6 】****( 実施の形態 13 )**

本実施の形態では、実施の形態 1 ~ 実施の形態 10 で示す表示装置の主要な要素であるトランジスタの作製方法について説明する。特にプラズマ処理を用いてトランジスタを作製する方法について説明する。

**【 0 2 4 7 】**

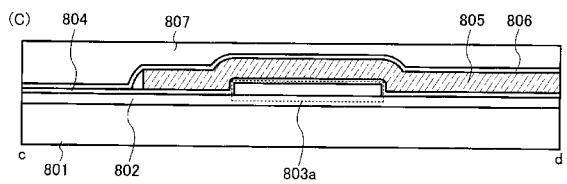

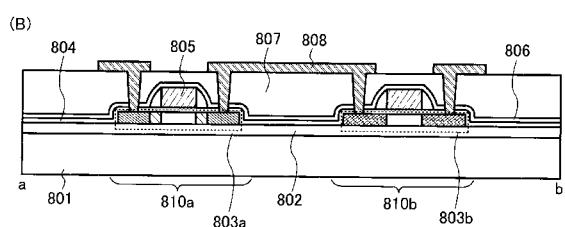

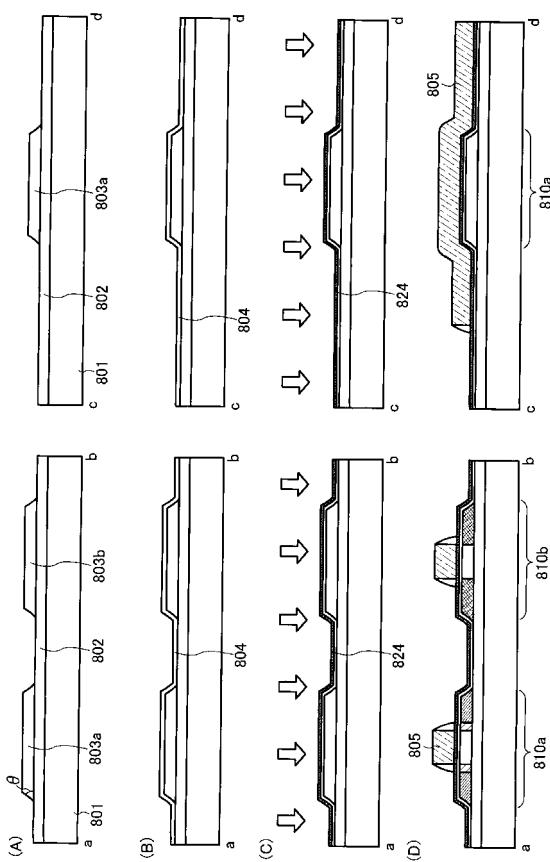

図 48 は、トランジスタ構造例を示した図である。なお、図 48 において、図 48 (B) は図 48 (A) の a - b 間の断面図に相当し、図 48 (C) は図 48 (A) の c - d 間の断面図に相当する。

10

20

30

40

50

## 【0248】

図48は、基板801上に絶縁膜802を介して半導体膜803a、803bが設けられている。当該半導体膜803a、803b上には、ゲート絶縁膜804を介してゲート電極805が設けられている。ゲート電極805を覆って絶縁膜806、807が設けられている。半導体膜803a、803bには、ソース領域及びドレイン領域が形成されており、絶縁膜807に形成されたコンタクトホールによって、導電膜808と接続されている。

## 【0249】

図48においては、半導体膜803aの一部をチャネル領域として用いたNチャネル型トランジスタ810aと半導体膜803bの一部をチャネル領域として用いたPチャネル型トランジスタ810bとを設けた場合を示しているが、この構成に限られない。例えば、Nチャネル型トランジスタ810aにLDD領域を設け、Pチャネル型トランジスタ810bにはLDD領域を設けていないが、両方に設けた構成としても良いし両方に設けない構成とすることも可能である。

10

## 【0250】

本実施の形態では、基板801、絶縁膜802、半導体膜803a及び803b、ゲート絶縁膜804、絶縁膜806又は絶縁膜807のうち少なくともいすれか一層に、プラズマ処理を用いて酸化又は窒化を行うことにより半導体膜又は絶縁膜を酸化又は窒化する工程を含んでいる。プラズマ処理を用いて半導体膜又は絶縁膜を酸化又は窒化することによって、当該半導体膜又は絶縁膜の表面を改質し、CVD法やスパッタ法により形成した絶縁膜と比較してより緻密な絶縁膜を形成することができるため、ピンホール等の欠陥を抑制しトランジスタの特性等を向上させることが可能となる。

20

## 【0251】

本実施の形態では、図48における半導体膜803a、803b又はゲート絶縁膜804にプラズマ処理を行い、当該半導体膜803a、803b又はゲート絶縁膜804を酸化又は窒化することによってトランジスタを作製する方法について図面を参照して説明する。

30

## 【0252】

はじめに、基板上に設けられた島状の半導体膜において、当該島状の半導体膜の端部を直角に近い形状で設ける場合について示す。

## 【0253】

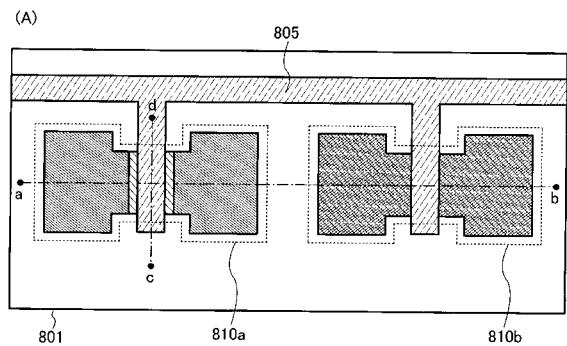

基板801上に島状の半導体膜803a、半導体膜803bを形成する(図49(A))。島状の半導体膜803a、半導体膜803bは、基板801上にあらかじめ形成された絶縁膜802上にスパッタ法、LPCVD法、プラズマCVD法等を用いてシリコン(Si)を主成分とする材料(例えばSi<sub>1-x</sub>Ge<sub>1-x</sub>等)等を用いて非晶質半導体膜を形成し、当該非晶質半導体膜を結晶化させ、半導体膜を選択的にエッチングすることにより設けることができる。なお、非晶質半導体膜の結晶化は、レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法又はこれら方法を組み合わせた方法等の結晶化法により行うことができる。なお、図49では、島状の半導体膜803a、半導体膜803bの端部を直角に近い形状(=85~100°)で設ける。

40

## 【0254】

次に、プラズマ処理を行い半導体膜803a、803bを酸化又は窒化する。それにより、当該半導体膜803a、803bの表面にそれぞれ酸化膜又は窒化膜など(以下、絶縁膜821a、絶縁膜821bとも記す)を形成する(図49(B))。例えば、半導体膜803a、803bとしてSiを用いた場合、絶縁膜821a及び絶縁膜821bとして、酸化シリコン(SiO<sub>x</sub>)又は窒化シリコン(SiN<sub>x</sub>)が形成される。また、プラズマ処理により半導体膜803a、803bを酸化させた後に、再度プラズマ処理を行うことによって窒化させても良い。この場合、半導体膜803a、803bに接して酸化シリコン(SiO<sub>x</sub>)が形成され、当該酸化シリコンの表面に窒化酸化シリコン(SiN<sub>x</sub>O)が形成される。

50

$y$ ) ( $x > y$ ) が形成される。なお、プラズマ処理により半導体膜を酸化する場合には、酸素雰囲気下(例えば、酸素( $O_2$ )と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下又は酸素と水素( $H_2$ )と希ガス雰囲気下又は一酸化二窒素と希ガス雰囲気下)でプラズマ処理を行う。一方、プラズマ処理により半導体膜を窒化する場合には、窒素雰囲気下(例えば、窒素( $N_2$ )と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下又は窒素と水素と希ガス雰囲気下又は $NH_3$ と希ガス雰囲気下)でプラズマ処理を行う。希ガスとしては、例えばArを用いることができる。また、ArとKrを混合したガスを用いても良い。そのため、絶縁膜821a、821bは、プラズマ処理に用いた希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)を含んでおり、Arを用いた場合には絶縁膜821a、821bにArが含まれている。

#### 【0255】

また、プラズマ処理は、上記ガスの雰囲気中において、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下であり、プラズマの電子温度が $0.5 \text{ eV}$ 以上 $1.5 \text{ eV}$ 以下で行う。プラズマの電子密度が高密度であり、基板801上に形成された被処理物(ここでは、半導体膜803a、803b)付近での電子温度が低いため、被処理物に対するプラズマによる損傷を防止することができる。また、プラズマの電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上と高密度であるため、プラズマ処理を用いて、被照射物を酸化又は窒化することによって形成される酸化膜又は窒化膜は、CVD法やスパッタ法等により形成された膜と比較して膜厚等が均一性に優れ、且つ緻密な膜を形成することができる。また、プラズマの電子温度が $1 \text{ eV}$ 以下と低いため、従来のプラズマ処理や熱酸化法と比較して低温度で酸化又は窒化処理を行うことができる。たとえば、ガラス基板の歪点温度よりも $100$ 度以上低い温度でプラズマ処理を行っても十分に酸化又は窒化処理を行うことができる。なお、プラズマを形成するための周波数としては、マイクロ波( $2.45 \text{ GHz}$ )等の高周波を用いることができる。なお、以下に特に断らない場合は、プラズマ処理として上記条件を用いて行うものとする。

#### 【0256】

次に、絶縁膜821a、821bを覆うようにゲート絶縁膜804を形成する(図49(C))。ゲート絶縁膜804はスパッタ法、LPCVD法、プラズマCVD法等を用いて、酸化シリコン( $SiO_x$ )、窒化シリコン( $SiNx$ )、酸化窒化シリコン( $SiO_xNy$ )( $x > y$ )、窒化酸化シリコン( $SiNxOy$ )( $x > y$ )等の酸素又は窒素を有する絶縁膜の単層構造、又はこれらの積層構造で設けることができる。例えば、半導体膜803a、803bとして $Si$ を用い、プラズマ処理により当該 $Si$ を酸化させることによって当該半導体膜803a、803b表面に、絶縁膜821a、821bとして酸化シリコンを形成した場合、当該絶縁膜821a、821b上にゲート絶縁膜として酸化シリコン( $SiO_x$ )を形成する。また、上記図49(B)において、プラズマ処理により半導体膜803a、803bを酸化又は窒化することによって形成された絶縁膜821a、821bの膜厚が十分である場合には、当該絶縁膜821a、821bをゲート絶縁膜として用いることも可能である。

#### 【0257】

次に、ゲート絶縁膜804上にゲート電極805等を形成することによって、島状の半導体膜803a、803bをチャネル領域として用いたNチャネル型トランジスタ810a、Pチャネル型トランジスタ810bを作製することができる(図49(D))。

#### 【0258】

このように、半導体膜803a、803b上にゲート絶縁膜804を設ける前に、プラズマ処理により半導体膜803a、803bの表面を酸化又は窒化することによって、チャネル領域の端部851a、851b等におけるゲート絶縁膜804の被覆不良に起因するゲート電極と半導体膜のショート等を防止することができる。つまり、島状の半導体膜の端部が直角に近い形状( $\theta = 85 \sim 100^\circ$ )を有する場合には、CVD法やスパッタ法等により半導体膜を覆うようにゲート絶縁膜を形成した際に、半導体膜の端部においてゲ

10

20

30

40

50

ート絶縁膜の段切れ等による被覆不良の問題が生じる恐れがあるが、あらかじめ半導体膜の表面にプラズマ処理を用いて酸化又は窒化しておくことによって、半導体膜の端部におけるゲート絶縁膜の被覆不良等を防止することが可能となる。

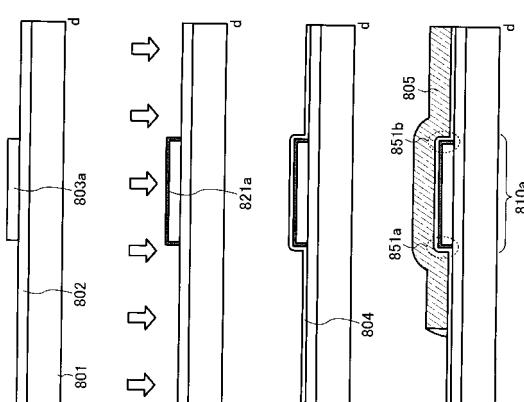

【0259】

図49において、ゲート絶縁膜804を形成した後にプラズマ処理を行うことによって、ゲート絶縁膜804を酸化又は窒化させても良い。この場合、半導体膜803a、803bを覆うように形成されたゲート絶縁膜804(図50(A))にプラズマ処理を行い、ゲート絶縁膜804を酸化又は窒化することによって、ゲート絶縁膜804の表面に酸化膜又は窒化膜(以下、絶縁膜823とも記す)を形成する(図50(B))。プラズマ処理の条件は、図49(B)と同様に行うことができる。また、絶縁膜823は、プラズマ処理に用いた希ガスを含んでおり、例えばArを用いた場合には絶縁膜823にArが含まれている。

【0260】

図50(B)において、一旦酸素雰囲気下でプラズマ処理を行うことによりゲート絶縁膜804を酸化させた後に、再度窒素雰囲気下でプラズマ処理を行うことにより窒化させても良い。この場合、半導体膜803a、803b上に酸化シリコン(SiO<sub>x</sub>)又は酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)(x>y)が形成され、ゲート電極805に接して窒化酸化シリコン(SiN<sub>x</sub>O<sub>y</sub>)(x>y)が形成される。その後、絶縁膜802上にゲート電極805等を形成することによって、島状の半導体膜803a、803bをチャネル領域として用いたNチャネル型トランジスタ810a、Pチャネル型トランジスタ810bを作製することができる(図50(C))。このように、ゲート絶縁膜にプラズマ処理を行うことにより、当該ゲート絶縁膜の表面を酸化又は窒化することによって、ゲート絶縁膜の表面を改質し緻密な膜を形成することができる。プラズマ処理を行うことによって得られた絶縁膜は、CVD法やスパッタ法で形成された絶縁膜と比較して緻密でピンホール等の欠陥も少ないため、トランジスタの特性を向上させることができる。

【0261】

なお、図50においては、あらかじめ半導体膜803a、803bにプラズマ処理を行うことによって、当該半導体膜803a、803bの表面を酸化又は窒化させた場合を示したが、半導体膜803a、803bにプラズマ処理を行わずにゲート絶縁膜804を形成した後にプラズマ処理を行う方法を用いても良い。このように、ゲート電極を形成する前にプラズマ処理を行うことによって、半導体膜の端部においてゲート絶縁膜の段切れ等による被覆不良が生じた場合であっても、被覆不良により露出した半導体膜を酸化又は窒化することができるため、半導体膜の端部におけるゲート絶縁膜の被覆不良に起因するゲート電極と半導体膜のショート等を防止することができる。

【0262】

このように、島状の半導体膜の端部を直角に近い形状で設けた場合であっても、半導体膜又はゲート絶縁膜にプラズマ処理を行い、当該半導体膜又はゲート絶縁膜を酸化又は窒化することによって、半導体膜の端部におけるゲート絶縁膜の被覆不良に起因するゲート電極と半導体膜のショート等を防止することができる。

【0263】

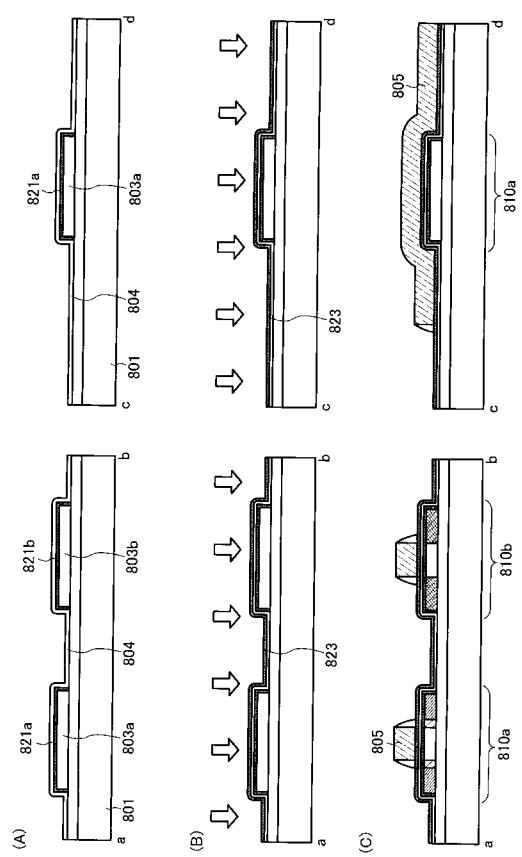

次に、基板上に設けられた島状の半導体膜において、当該島状の半導体膜の端部をテーパー形状(θ=30°～85°)で設ける場合について示す。

【0264】

まず、基板801上に島状の半導体膜803a、803bを形成する(図51(A))。島状の半導体膜803a、803bは、基板801上にあらかじめ形成された絶縁膜802上にスパッタ法、LPCVD法、プラズマCVD法等を用いてシリコン(Si)を主成分とする材料(例えばSi<sub>x</sub>Ge<sub>y</sub>等)等を用いて非晶質半導体膜を形成し、当該非晶質半導体膜をレーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法などの結晶化法により結晶化させ、選択的に半導体膜をエッチングして除去することにより設けることができる。なお、図51では、島

10

20

30

40

50

状の半導体膜の端部をテーバー形状(= 30 ~ 85°)で設ける。

【0265】

半導体膜803a、803bを覆うようにゲート絶縁膜804を形成する(図51(B))。ゲート絶縁膜804はスパッタ法、LPCVD法、プラズマCVD法等を用いて、酸化シリコン(SiO<sub>x</sub>)、窒化シリコン(SiN<sub>x</sub>)、酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)(x > y)、窒化酸化シリコン(SiN<sub>x</sub>O<sub>y</sub>)(x > y)等の酸素又は窒素を有する絶縁膜の単層構造、又はこれらの積層構造で設けることができる。

【0266】

次に、プラズマ処理を行いゲート絶縁膜804を酸化又は窒化することによって、当該ゲート絶縁膜804の表面にそれぞれ酸化膜又は窒化膜(以下、絶縁膜824とも記す)を形成する(図51(C))。なお、プラズマ処理の条件は上記と同様に行うことができる。例えば、ゲート絶縁膜804として酸化シリコン(SiO<sub>x</sub>)又は酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)(x > y)を用いた場合、酸素雰囲気下でプラズマ処理を行いゲート絶縁膜804を酸化することによって、ゲート絶縁膜の表面にはCVD法やスパッタ法等により形成されたゲート絶縁膜と比較してピンホール等の欠陥の少ない緻密な膜を形成することができる。一方、窒素雰囲気下でプラズマ処理を行いゲート絶縁膜804を窒化することによって、ゲート絶縁膜804の表面に絶縁膜824として窒化酸化シリコン(SiN<sub>x</sub>O<sub>y</sub>)(x > y)を設けることができる。また、一旦酸素雰囲気下でプラズマ処理を行うことによりゲート絶縁膜804を酸化させた後に、再度窒素雰囲気下でプラズマ処理を行うことにより窒化させても良い。また、絶縁膜824は、プラズマ処理に用いた希ガスを含んでおり、例えばArを用いた場合には絶縁膜824中にArが含まれている。

【0267】

ゲート絶縁膜804上にゲート電極805等を形成することによって、島状の半導体膜803a、803bをチャネル領域として用いたNチャネル型トランジスタ810a、Pチャネル型トランジスタ810bを作製することができる(図51(D))。

【0268】

このように、ゲート絶縁膜にプラズマ処理を行うことにより、ゲート絶縁膜の表面に酸化膜又は窒化膜からなる絶縁膜を設け、ゲート絶縁膜の表面の改質をすることができる。プラズマ処理を行うことによって酸化又は窒化された絶縁膜は、CVD法やスパッタ法で形成されたゲート絶縁膜と比較して緻密でピンホール等の欠陥も少ないため、トランジスタの特性を向上させることができる。また、半導体膜の端部をテーバー形状とすることによって、半導体膜の端部におけるゲート絶縁膜の被覆不良に起因するゲート電極と半導体膜のショート等を抑制することができるが、ゲート絶縁膜を形成した後にプラズマ処理を行うことによって、より一層ゲート電極と半導体膜のショート等を防止することができる。

【0269】

次に、図51とは、異なるトランジスタの作製方法に関して図面を参照して説明する。具体的には、テーバー形状を有する半導体膜の端部に選択的にプラズマ処理を行う場合に関して示す。

【0270】

まず、基板801上に島状の半導体膜803a、803bを形成する(図52(A))。島状の半導体膜803a、803bは、基板801上にあらかじめ形成された絶縁膜802上にスパッタ法、LPCVD法、プラズマCVD法等を用いてシリコン(Si)を主成分とする材料(例えばSi<sub>x</sub>Ge<sub>y</sub>等)等を用いて非晶質半導体膜を形成し、当該非晶質半導体膜を結晶化させ、レジスト825a、825bをマスクとして半導体膜を選択的にエッチングすることにより設けることができる。なお、非晶質半導体膜の結晶化は、レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法又はこれら方法を組み合わせた方法等の結晶化法により行うことができる。

【0271】

次に、半導体膜のエッチングのために使用したレジスト825a、825bを除去する前

に、プラズマ処理を行い島状の半導体膜 803a、803b の端部を選択的に酸化又は窒化することによって、当該半導体膜 803a、803b の端部にそれぞれ酸化膜又は窒化膜（以下、絶縁膜 826 とも記す）を形成する（図 52（B））。プラズマ処理は、上述した条件下で行う。また、絶縁膜 826 は、プラズマ処理に用いた希ガスを含んでいる。

【0272】

半導体膜 803a、803b を覆うようにゲート絶縁膜 804 を形成する（図 52（C））。ゲート絶縁膜 804 は、上記と同様に設けることができる。

【0273】

ゲート絶縁膜 804 上にゲート電極 805 等を形成することによって、島状の半導体膜 803a、803b をチャネル領域として用いた N チャネル型トランジスタ 810a、P チャネル型トランジスタ 810b を作製することができる（図 52（D））。

【0274】

半導体膜 803a、803b の端部をテーパー形状に設けた場合、半導体膜 803a、803b の一部に形成されるチャネル領域の端部 852a、852b もテーパー形状となり半導体膜の膜厚やゲート絶縁膜の膜厚が中央部分と比較して変化するため、トランジスタの特性に影響を及ぼす場合がある。そのため、ここではプラズマ処理によりチャネル領域の端部を選択的に酸化又は窒化して、当該チャネル領域の端部となる半導体膜に絶縁膜を形成することによって、チャネル領域の端部に起因するトランジスタへの影響を低減することができる。

【0275】

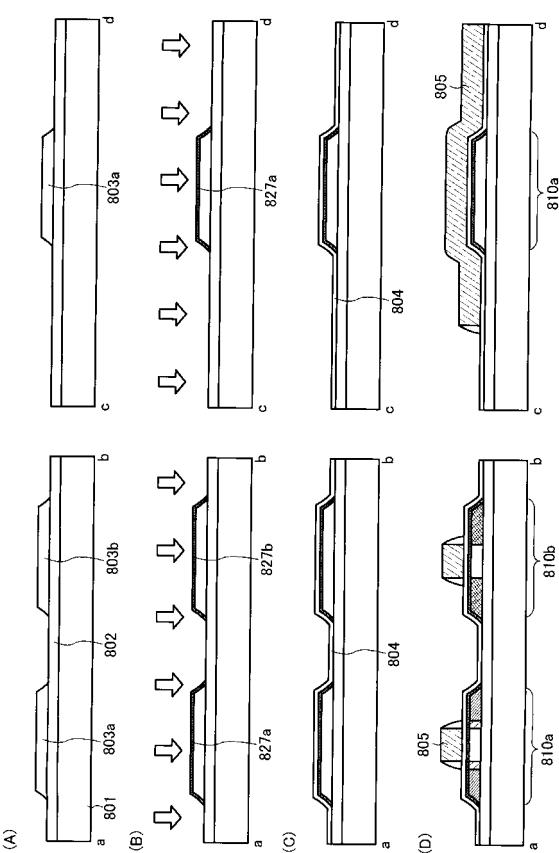

図 52 では、半導体膜 803a、803b の端部に限ってプラズマ処理により酸化又は窒化を行った例を示したが、もちろん上記図 51 で示したようにゲート絶縁膜 804 にもプラズマ処理を行って酸化又は窒化させることも可能である（図 54（A））。

【0276】

次に、上記とは異なるトランジスタの作製方法に関して図面を参照して説明する。具体的には、テーパー形状を有する半導体膜にプラズマ処理を行う場合に関して示す。

【0277】

まず、基板 801 上に上記と同様に島状の半導体膜 803a、803b を形成する（図 53（A））。

【0278】

プラズマ処理を行い半導体膜 803a、803b を酸化又は窒化することによって、当該半導体膜 803a、803b の表面にそれぞれ酸化膜又は窒化膜（以下、絶縁膜 827a、絶縁膜 827b とも記す）を形成する（図 53（B））。プラズマ処理は上述した条件下で同様に行うことができる。例えば、半導体膜 803a、803b として Si を用いた場合、絶縁膜 827a 及び絶縁膜 827b として、酸化シリコン（SiO<sub>x</sub>）又は窒化シリコン（SiN<sub>x</sub>）が形成される。また、プラズマ処理により半導体膜 803a、803b を酸化させた後に、再度プラズマ処理を行うことによって窒化させても良い。この場合、半導体膜 803a、803b に接して酸化シリコン（SiO<sub>x</sub>）又は酸化窒化シリコン（SiO<sub>x</sub>N<sub>y</sub>）（x > y）が形成され、当該酸化シリコンの表面に窒化酸化シリコン（SiN<sub>x</sub>O<sub>y</sub>）（x > y）が形成される。そのため、絶縁膜 827a、827b は、プラズマ処理に用いた希ガスを含んでいる。なお、プラズマ処理を行うことにより半導体膜 803a、803b の端部も同時に酸化又は窒化される。

【0279】

次に、絶縁膜 827a、827b を覆うようにゲート絶縁膜 804 を形成する（図 53（C））。ゲート絶縁膜 804 はスパッタ法、LPCVD 法、プラズマ CVD 法等を用いて、酸化シリコン（SiO<sub>x</sub>）、窒化シリコン（SiN<sub>x</sub>）、酸化窒化シリコン（SiO<sub>x</sub>N<sub>y</sub>）（x > y）、窒化酸化シリコン（SiN<sub>x</sub>O<sub>y</sub>）（x > y）等の酸素又は窒素を有する絶縁膜の単層構造、又はこれらの積層構造で設けることができる。例えば、Si を用いた半導体膜 803a、803b をプラズマ処理により酸化させることによって、当該半導体膜 803a、803b 表面に絶縁膜 827a、827b として酸化シリコンを形成し

10

20

30

40

50

た場合、当該絶縁膜 827a、827b 上にゲート絶縁膜として酸化シリコン (SiO<sub>x</sub>) を形成する。

【0280】

ゲート絶縁膜 804 上にゲート電極 805 等を形成することによって、島状の半導体膜 803a、803b をチャネル領域として用いたNチャネル型トランジスタ 810a、Pチャネル型トランジスタ 810b を作製することができる (図 53 (D))。

【0281】

半導体膜の端部をテーパー形状に設けた場合、半導体膜 803a、803b の一部に形成されるチャネル領域の端部もテーパー形状となるため、半導体素子の特性に影響を及ぼす場合がある。そのため、プラズマ処理により半導体膜を酸化又は窒化することによって、結果的にチャネル領域の端部も酸化又は窒化されるため半導体素子への影響を低減することができる。

【0282】

なお、図 53 では、半導体膜 803a、803b に限ってプラズマ処理により酸化又は窒化を行った例を示したが、もちろん上記図 51 で示したようにゲート絶縁膜 804 にプラズマ処理を行って酸化又は窒化させることも可能である (図 54 (B))。この場合、一旦酸素雰囲気下でプラズマ処理を行うことによりゲート絶縁膜 804 を酸化させた後に、再度窒素雰囲気下でプラズマ処理を行うことにより窒化させても良い。この場合、半導体膜 803a、803b 上に酸化シリコン (SiO<sub>x</sub>) 又は酸化窒化シリコン (SiO<sub>x</sub>N<sub>y</sub>) (x > y) が形成され、ゲート電極 805 に接して窒化酸化シリコン (SiN<sub>x</sub>O<sub>y</sub>) (x > y) が形成される。

【0283】

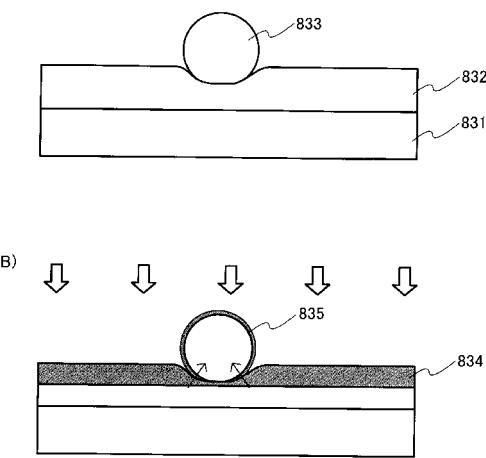

また、上述したようにプラズマ処理を行うことによって、半導体膜や絶縁膜に付着したゴミ等の不純物の除去を容易に行うことができる。一般的に、CVD法やスパッタ法等により形成された膜にはゴミ (パーティクルともいう) が付着していることがある。例えば、図 55 (A) に示すように、絶縁膜又は導電膜又は半導体膜等の膜 831 上にCVD法やスパッタ法等により形成された絶縁膜 832 上にゴミ 833 が形成される場合がある。このような場合であっても、プラズマ処理を行い絶縁膜 832 を酸化又は窒化することによって、絶縁膜 832 の表面に酸化膜又は窒化膜 (以下、絶縁膜 834 ともいう) が形成される。絶縁膜 834 は、ゴミ 833 が存在しない部分のみならず、ゴミ 833 の下側の部分にも回り込むように酸化又は窒化されることによって、絶縁膜 834 の体積が増加する。一方、ゴミ 833 の表面もプラズマ処理によって酸化又は窒化され絶縁膜 835 が形成され、その結果ゴミ 833 の体積も増加する (図 55 (B))。

【0284】

このとき、ゴミ 833 は、ブラシ洗浄等の簡単な洗浄により、絶縁膜 834 の表面から容易に除去される状態になる。このように、プラズマ処理を行うことによって、当該絶縁膜又は半導体膜に付着した微細なゴミであっても当該ゴミの除去が容易になる。なお、これはプラズマ処理を行うことによって得られる効果であり、本実施の形態のみならず、他の実施の形態においても同様のことがいえる。

【0285】

このように、プラズマ処理を行い半導体膜又はゲート絶縁膜を酸化又は窒化して表面を改質することにより、緻密で膜質の良い絶縁膜を形成することができる。また、絶縁膜の表面に付着したゴミ等を洗浄によって、容易に除去することが可能となる。その結果、絶縁膜を薄く形成する場合であってもピンホール等の欠陥を防止し、トランジスタ等の半導体素子の微細化及び高性能化を実現することができる。

【0286】

なお、本実施の形態では、図 48 における半導体膜 803a 及び 803b 又はゲート絶縁膜 804 にプラズマ処理を行い、当該半導体膜 803a 及び 803b 又はゲート絶縁膜 804 を酸化又は窒化を行ったが、プラズマ処理を用いて酸化又は窒化を行う層は、これに限定されない。例えば、基板 801 又は絶縁膜 802 にプラズマ処理を行っても良いし、

10

20

30

40

50

絶縁膜 806 又は絶縁膜 807 にプラズマ処理を行っても良い。

【0287】

本実施の形態では基板上にトランジスタを作製する方法について示しているが、このようなトランジスタを用いて、実施の形態 1 ~ 実施の形態 10 の表示装置を作製することができる。すなわち、実施の形態 1 ~ 実施の形態 10 で述べた内容と自由に組み合わせて実施することができる。

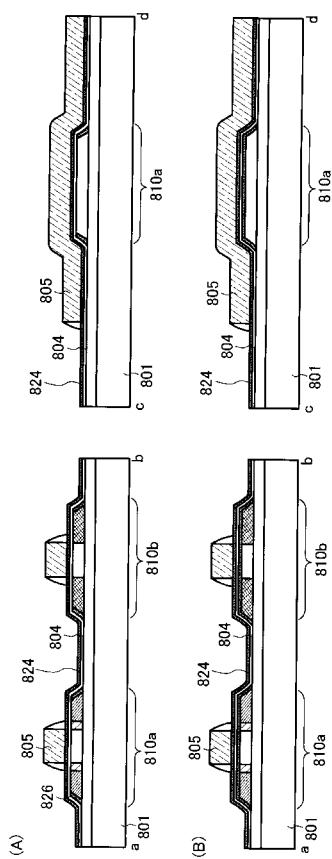

【0288】

(実施の形態 14)

本実施の形態では、実施の形態 1 ~ 実施の形態 10 で示す表示装置の主要な要素であるトランジスタの作製方法について説明する。特にハーフトーン露光方式を用いてトランジスタを作製する方法について説明する。

【0289】

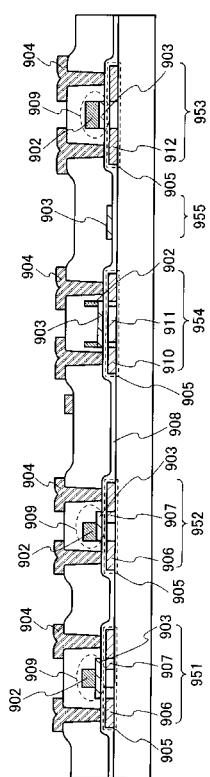

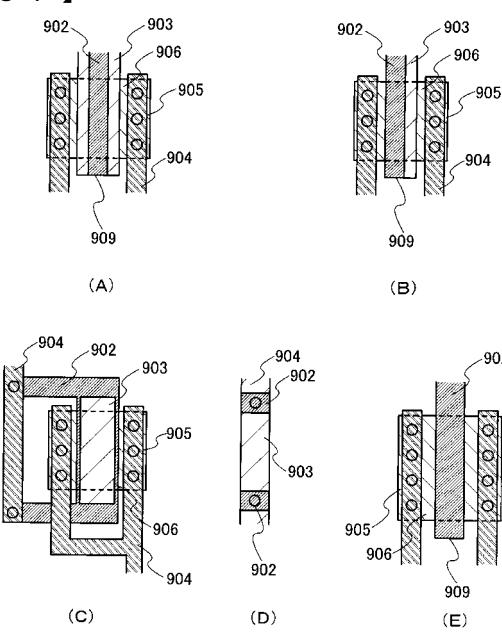

図 56 はトランジスタの他に、同じ工程で作製することのできる容量素子、抵抗素子の断面構造を示す図である。図 56 は、N チャネル型トランジスタ 951、N チャネル型トランジスタ 952、容量素子 954、抵抗素子 955、P チャネル型トランジスタ 953 が示されている。各トランジスタは半導体層 905、絶縁層 908、ゲート電極 909 を備えている。ゲート電極 909 は、第 1 導電層 903 と第 2 導電層 902 の積層構造で形成されている。また、図 57 (A) ~ (E) は、図 56 で示すトランジスタ、容量素子、抵抗素子に対応する上面図であり、合わせて参照することができる。

【0290】

図 56 において、N チャネル型トランジスタ 951 は、チャネル長方向 (キャリアの流れる方向) において、チャネル形成領域の両側に低濃度ドレイン (LDD) とも呼ばれ、配線 904 とコンタクトを形成するソース及びドレイン領域を形成する不純物領域 906 の不純物濃度よりも低濃度にドープされた不純物領域 907 が半導体層 905 に形成されている。不純物領域 906 と不純物領域 907 には、N チャネル型トランジスタ 951 を構成する場合、N 型を付与する不純物としてリンなどが添加されている。LDD はホットエレクトロン劣化や短チャネル効果を抑制する手段として形成される。

【0291】

図 57 (A) で示すように、N チャネル型トランジスタ 951 のゲート電極 909 において、第 1 導電層 903 は、第 2 導電層 902 の両側に広がって形成されている。この場合において、第 1 導電層 903 の膜厚は、第 2 導電層の膜厚よりも薄く形成されている。第 1 導電層 903 の厚さは、10 ~ 100 kV の電界で加速されたイオン種を通過させることができた厚さに形成されている。不純物領域 907 はゲート電極 909 の第 1 導電層 903 と重なるように形成されている。すなわち、ゲート電極 909 とオーバーラップする LDD 領域を形成している。この構造は、ゲート電極 909 において、第 2 導電層 902 をマスクとして、第 1 導電層 903 を通して一導電型の不純物を添加することにより、自己整合的に不純物領域 907 を形成している。すなわち、ゲート電極とオーバーラップする LDD を自己整合的に形成している。

【0292】

図 56 において、N チャネル型トランジスタ 952 は、ゲート電極の片側に不純物領域 906 の不純物濃度よりも低濃度にドープされた不純物領域 907 が半導体層 905 に形成されている。図 57 (B) で示すように、N チャネル型トランジスタ 952 のゲート電極 909 において、第 1 導電層 903 は、第 2 導電層 902 の片側に広がって形成されている。この場合も同様に、第 2 導電層 902 をマスクとして、第 1 導電層 903 を通して一導電型の不純物を添加することにより、自己整合的に LDD を形成することができる。

【0293】

片側に LDD を有するトランジスタは、ソース及びドレイン電極間に正電圧のみ、若しくは負電圧のみが印加されるトランジスタに適用すれば良い。具体的には、インバータ回路、NAND 回路、NOR 回路、ラッチ回路といった論理ゲートを構成するトランジスタや、センスアンプ、定電圧発生回路、VCO といったアナログ回路を構成するトランジスタ

10

20

30

40

50

に適用すれば良い。

【0294】

図56において、容量素子954は、第1導電層903と半導体層905とで絶縁層908を挟んで形成されている。容量素子954を形成する半導体層905には、不純物領域910と不純物領域911を備えている。不純物領域911は、半導体層905において第1導電層903と重なる位置に形成される。また、不純物領域910は配線904とコンタクトを形成する。不純物領域911は、第1導電層903を通して一導電型の不純物を添加することができるので、不純物領域910と不純物領域911に含まれる不純物濃度は同じにすることもできるし、異ならせることも可能である。いずれにしても、容量素子954において、半導体層905は電極として機能させるので、一導電型の不純物を添加して低抵抗化しておくことが好ましい。また、第1導電層903は、図57(C)に示すように、第2導電層902を補助的な電極として利用することにより、電極として十分に機能させることができる。このように、第1導電層903と第2導電層902を組み合わせた複合的な電極構造とすることにより、容量素子954を自己整合的に形成することができる。

【0295】

図56において、抵抗素子955は、第1導電層903によって形成されている。第1導電層903は30~150nm程度の厚さに形成されるので、その幅や長さを適宜設定して抵抗素子を構成することができる。

【0296】

抵抗素子は、高濃度に不純物元素を含む半導体層や、膜厚の薄い金属層によって構成すれば良い。抵抗値が膜厚、膜質、不純物濃度、活性化率などに依存する半導体層に対して、金属層は、膜厚、膜質で抵抗値が決定するため、ばらつきが小さく好ましい。抵抗素子955の上面図を図57(D)に示す。

【0297】

図56において、Pチャネル型トランジスタ953は、半導体層905に不純物領域912を備えている。この不純物領域912は、配線904とコンタクトを形成するソース及びドレイン領域を形成する。ゲート電極909の構成は第1導電層903と第2導電層902が重畠した構成となっている。Pチャネル型トランジスタ953はLDDを設けないシングルドレイン構造のトランジスタである。Pチャネル型トランジスタ953を形成する場合、不純物領域912にはP型を付与する不純物として硼素などが添加される。一方、不純物領域912にリンを添加すればシングルドレイン構造のNチャネル型トランジスタとすることもできる。Pチャネル型トランジスタ953の上面図を図57(E)に示す。

【0298】

半導体層905及びゲート絶縁層908の一方若しくは双方に対してマイクロ波で励起され、電子温度が2eV以下、イオンエネルギーが5eV以下、電子密度が $10^{11} \sim 10^{13} / \text{cm}^3$ 程度である高密度プラズマ処理によって酸化又は窒化処理しても良い。このとき、基板温度を300~450とし、酸化雰囲気(O<sub>2</sub>、N<sub>2</sub>Oなど)又は窒化雰囲気(N<sub>2</sub>、NH<sub>3</sub>など)で処理することにより、半導体層905とゲート絶縁層908の界面の欠陥準位を低減することができる。ゲート絶縁層908に対してこの処理を行うことにより、この絶縁層の緻密化を図ることができる。すなわち、荷電欠陥の生成を抑えトランジスタのしきい値電圧の変動を抑えることができる。また、トランジスタを3V以下の電圧で駆動させる場合には、このプラズマ処理により酸化若しくは窒化された絶縁層をゲート絶縁層908として適用することができる。また、トランジスタの駆動電圧が3V以上の場合には、このプラズマ処理で半導体層905の表面に形成した絶縁層とCVD法(プラズマCVD法若しくは熱CVD法)で堆積した絶縁層とを組み合わせてゲート絶縁層908を形成することができる。また、同様にこの絶縁層は、容量素子954の誘電体層としても利用することができる。この場合、このプラズマ処理で形成された絶縁層は、1~10nmの厚さで形成され、緻密な膜であるので、大きな電荷容量を持つ容量素子を形

10

20

30

40

50

成することができる。

【0299】

図56及び図57を参照して説明したように、膜厚の異なる導電層を組み合わせることにより、さまざまな構成の素子を形成することができる。第1導電層のみが形成される領域と、第1導電層と第2導電層が積層されている領域は、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスク又はレチクルを用いて形成することができる。すなわち、フォトリソグラフィー工程において、フォトレジストを露光する際に、フォトマスクの透過光量を調節して、現像されるレジストマスクの厚さを異ならせる。この場合、フォトマスク又はレチクルに解像度限界以下のスリットを設けて上記複雑な形状を有するレジストを形成しても良い。また、現像後に約200のペークを行ってフォトレジスト材料で形成されるマスクパターンを変形させても良い。

10

【0300】

また、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスク又はレチクルを用いることにより、第1導電層のみが形成される領域と、第1導電層と第2導電層が積層されている領域を連続して形成することができる。図57(A)に示すように、第1導電層のみが形成される領域を半導体層上に選択的に形成することができる。このような領域は、半導体層上において有効であるが、それ以外の領域(ゲート電極と連続する配線領域)では必要がない。このフォトマスク若しくはレチクルを用いることにより、配線部分は、第1導電層のみの領域を作らないで済むので、配線密度を実質的に高めることができる。

20

【0301】

図56及び図57の場合には、第1導電層はタンゲステン(W)、クロム(Cr)、タンタル(Ta)、窒化タンタル(TaN)又はモリブデン(Mo)などの高融点金属、又は高融点金属を主成分とする合金若しくは化合物を30~50nmの厚さで形成する。また、第2導電層はタンゲステン(W)、クロム(Cr)、タンタル(Ta)、窒化タンタル(TaN)又はモリブデン(Mo)などの高融点金属、又は高融点金属を主成分とする合金若しくは化合物で300~600nmの厚さに形成する。例えば、第1導電層と第2導電層をそれぞれ異なる導電材料を用い、後に行うエッチング工程でエッチングレートの差が生じるようにする。一例として、第1導電層をTaNを用い、第2導電層としてタンゲステン膜を用いることができる。

30

【0302】

本実施の形態では、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスク又はレチクルを用いて、電極構造の異なるトランジスタ、容量素子、抵抗素子を、同じパターニング工程によって作り分けることができる事を示している。これにより、回路の特性に応じて、形態の異なる素子を、工程を増やすことなく作り込み、集積化することができる。

40

【0303】

本実施の形態では基板上にトランジスタを作製する方法について示しているが、このようなトランジスタを用いて、実施の形態1~実施の形態10の表示装置を作製することができる。すなわち、実施の形態1~実施の形態10で述べた内容と自由に組み合わせて実施することができる。

40

【0304】

(実施の形態15)

本実施の形態では、トランジスタを作製する際のマスクパターンの例について、図58~図60を参照して説明する。

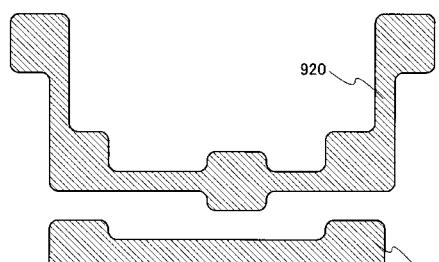

【0305】

図58(A)で示す半導体層920、921は、シリコン若しくはシリコンを成分とする半導体で形成することが好ましい。例えば、シリコン膜をレーザアニールなどによって結晶化された多結晶シリコン、単結晶シリコンなどが適用される。その他にも半導体特性を示す、金属酸化物半導体、アモルファスシリコン、有機半導体を適用することも可能であ

50

る。

【0306】

半導体層920、921は、基板上に成膜した半導体層を、フォトリソグラフィー工程とエッチング工程により形成される。フォトリソグラフィー工程は、半導体層上にマスクパターンを形成する。エッチング工程は、そのマスクパターンを利用して基板上に成膜した半導体層を選択的に除去する。半導体層920、921の形状は、作製すべきトランジスタの特性や、回路のレイアウトを考慮して決められている。

【0307】

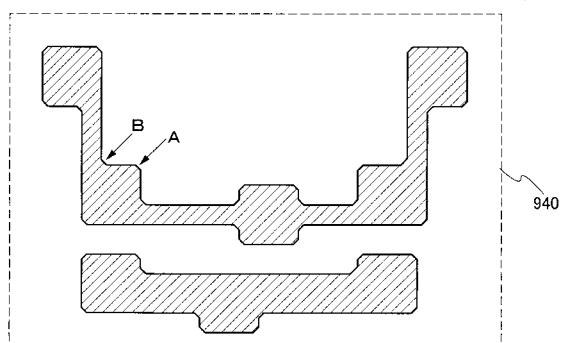

一例として、図58(A)で示す半導体層920、921を形成するためのフォトマスクは、図58(B)に示すマスクパターン940を備えている。このマスクパターン940は、フォトリソグラフィー工程で用いるレジストがポジ型かネガ型かで異なる。ポジ型レジストを用いる場合には、図58(B)で示すマスクパターン940は、遮光部として作製される。マスクパターン940は、多角形の頂部Aを切り欠いた形状となっている。また、屈曲部Bにおいては、その角部が直角で屈曲しないように複数段に渡って屈曲する形状としている。

【0308】

図58(B)で示すマスクパターン940は、その形状が図58(A)で示す半導体層920、921に反映される。その場合、マスクパターン940と相似の形状が転写されても良いが、マスクパターン940の角部がさらに丸みを帯びるように転写されても良い。すなわち、マスクパターン940よりもさらにパターン形状をなめらかにした、丸め部を設けても良い。

【0309】

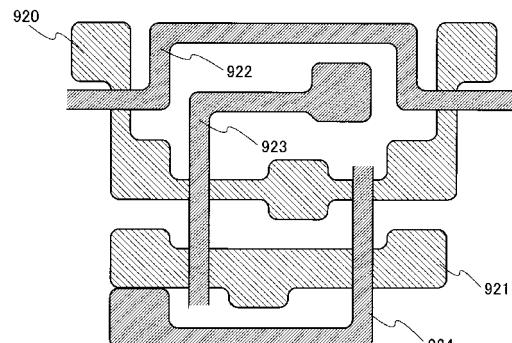

半導体層920、921の上には、酸化シリコン若しくは窒化シリコンを少なくとも一部に含む絶縁層を形成する。この絶縁層を形成する目的の一つはゲート絶縁層である。そして、図59(A)で示すように、半導体層と一部が重なるようにゲート配線922、923、924を形成する。ゲート配線922は半導体層920に対応して形成される。ゲート配線923は半導体層920、921に対応して形成される。また、ゲート配線924は半導体層920、921に対応して形成される。ゲート配線は、金属層又は導電性の高い半導体層を成膜し、フォトリソグラフィー技術によってその形状を絶縁層上に作り込む。

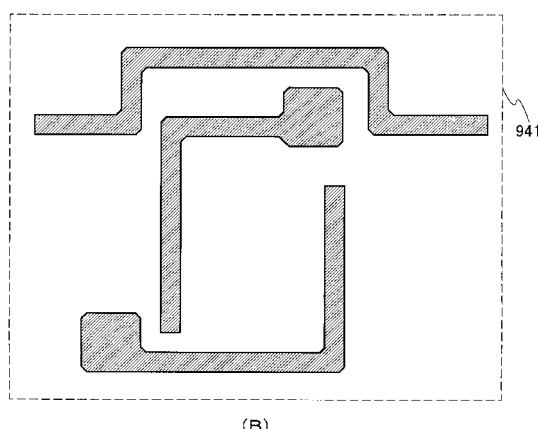

【0310】

ゲート配線922、923、924を形成するためのフォトマスクのパターンを図59(B)に示す。マスクパターン941は、コーナー部の外側が直角に折れ曲がらないように切り欠いた形状としている。また、コーナー部の内側は、直角で屈曲しないように複数段に渡って折れ曲がる形状としている。切り欠きの大きさは、配線幅に基づいて決めれば良い。例えば、配線幅の1/2から1/5の長さで、コーナー部の外側頂部に切り欠きを形成すれば良い。図59(B)で示すマスクパターン941は、その形状が、図59(A)で示すゲート配線922、923、924に反映される。その場合、マスクパターン941と相似の形状が転写されても良いが、マスクパターン941の角部がさらに丸みを帯びるように転写されても良い。すなわち、マスクパターン941よりもさらにパターン形状をなめらかにした、丸め部を設けても良い。コーナー部に丸みをおびさせることによって、プラズマによるドライエッチの際、異常放電による微粉の発生を抑えることができる。凹部のコーナー部に丸みをおびさせることによって、たとえ洗浄のときにできた微粉であっても、それが角に集まりやすいのを洗い流す結果として歩留まり向上が甚だしく期待できるという効果を有する。

【0311】

層間絶縁層はゲート配線922、923、924の次に形成される層である。層間絶縁層は酸化シリコンなどの無機絶縁材料若しくはポリイミドやアクリル樹脂などを使った有機絶縁材料を使って形成する。この層間絶縁層とゲート配線922、923、924の間には窒化シリコン若しくは窒化酸化シリコンなどの絶縁層を介在させても良い。また、層間絶縁層

10

20

30

40

50

層上にも窒化シリコン若しくは窒化酸化シリコンなどの絶縁層を設けても良い。この絶縁層は、外因性の金属イオンや水分などTFTにとっては良くない不純物により半導体層やゲート絶縁層を汚染するのを防ぐことができる。

【0312】

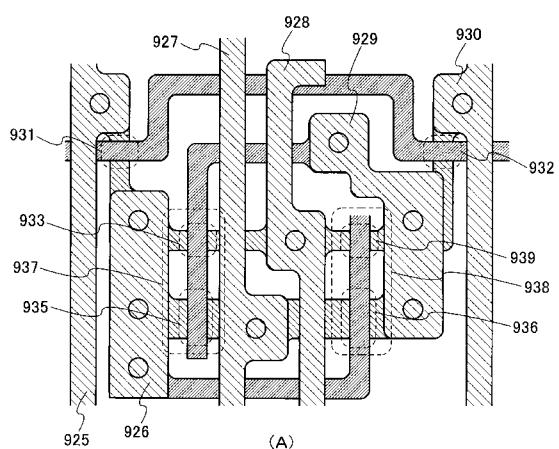

層間絶縁層には所定の位置に開孔が形成されている。例えば、下層にあるゲート配線や半導体層に対応して設けられる。金属若しくは金属化合物の一層若しくは複数層で形成される配線層は、フォトリソグラフィー技術によってマスクパターンが形成され、エッチング加工により所定のパターンに形成される。そして、図60(A)で示すように、半導体層と一部が重なるように配線925～930を形成する。配線はある特定の素子間を連結する。配線は特定の素子と素子の間を直線で結ぶのではなく、レイアウトの制約上屈曲部が含まれる。また、コンタクト部やその他の領域において配線幅が変化する。コンタクト部では、コンタクトホールが配線幅と同等若しくは大きい場合には、その部分で配線幅が広がるよう変化する。

【0313】

この配線925～930を形成するためのフォトマスクのパターンを図60(B)に示す。マスクパターン939は、コーナー部の外側が直角に折れ曲がらないように切り欠いた形状としている。また、コーナー部の内側は、直角で屈曲しないように複数段に渡って折れ曲がる形状としている。切り欠きの大きさは、配線幅に基づいて決めれば良い。例えば、配線幅の1/2から1/5の長さで、コーナー部の外側頂部に切り欠きを形成すれば良い。図60(B)で示すマスクパターン939は、その形状が、図60(A)で示す配線925～930に反映される。その場合、マスクパターン939と相似の形状が転写されても良いが、マスクパターン939の角部がさらに丸みを帯びるように転写されても良い。すなわち、マスクパターン939よりもさらにパターン形状をなめらかにした、丸め部を設けても良い。コーナー部に丸みをおびさせることによって、プラズマによるドライエッチの際、異常放電による微粉の発生を抑えることができる。凹部のコーナー部に丸みをおびさせることによって、たとえ洗浄のときにできた微粉であっても、それが角に集まりやすいのを洗い流す結果として歩留まり向上が甚だしく期待できるという効果を有する。

【0314】

図60(A)には、Nチャネル型トランジスタ931、932、933、939、Pチャネル型トランジスタ935、936が形成されている。Nチャネル型トランジスタ933とPチャネル型トランジスタ935及びNチャネル型トランジスタ939とPチャネル型トランジスタ936はインバータ937、938を構成している。なお、この6つのトランジスタを含む回路はSRAMを形成している。これらのトランジスタの上層には、窒化シリコンや酸化シリコンなどの絶縁層が形成されていても良い。

【0315】

本実施の形態で述べた内容は、実施の形態1～実施の形態14で述べた内容と自由に組み合わせて実施することができる。

【0316】

(実施の形態16)

本実施の形態では、本発明の表示装置を利用した電子機器について図61を用いて説明する。

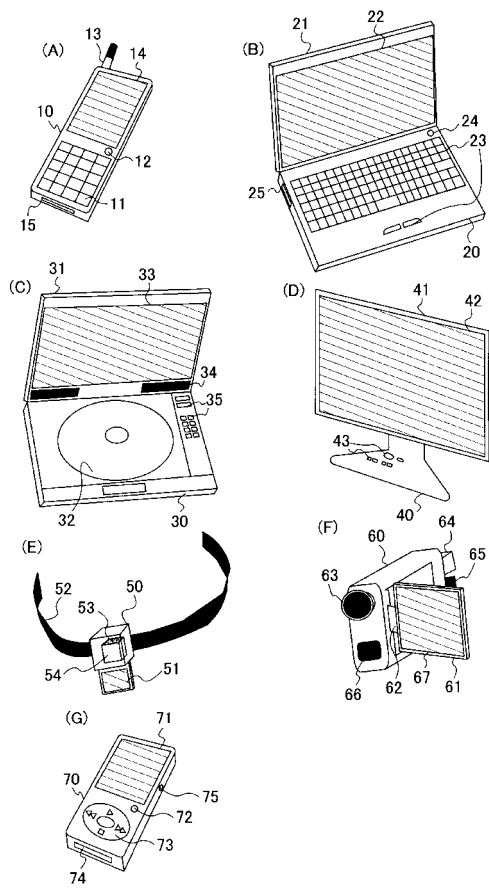

【0317】

図61(A)に本発明の表示装置を用いた携帯情報端末の模式図を示す。携帯情報端末は、本体10、操作スイッチ11、電源スイッチ12、アンテナ13、表示部14、外部入力ポート15によって構成されている。本発明の表示装置は、表示部14に用いることができる。

【0318】

図61(B)に本発明の表示装置を用いたパーソナルコンピュータの模式図を示す。パーソナルコンピュータは、本体20、筐体21、表示部22、操作スイッチ23、電源スイ

10

20

30

40

50

ツチ 24、外部入力ポート 25 によって構成されている。本発明の表示装置は、表示部 22 に用いることができる。

【0319】

図 61 (C) に本発明の表示装置を用いた画像再生装置の模式図を示す。画像再生装置は、本体 30、筐体 31、記録媒体 32、表示部 33、音声出力部 34、操作スイッチ 35 によって構成されている。本発明の表示装置は、表示部 33 に用いることができる。

【0320】