【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第3区分

【発行日】平成27年4月2日(2015.4.2)

【公開番号】特開2014-150482(P2014-150482A)

【公開日】平成26年8月21日(2014.8.21)

【年通号数】公開・登録公報2014-044

【出願番号】特願2013-19290(P2013-19290)

【国際特許分類】

H 03 K 5/08 (2006.01)

H 04 N 5/66 (2006.01)

G 09 G 3/20 (2006.01)

G 09 G 3/30 (2006.01)

【F I】

H 03 K 5/08 N

H 04 N 5/66 1 0 3

G 09 G 3/20 6 1 1 A

G 09 G 3/20 6 2 4 B

G 09 G 3/20 6 4 1 A

G 09 G 3/30 J

【手続補正書】

【提出日】平成27年2月13日(2015.2.13)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】0036

【補正方法】変更

【補正の内容】

【0036】

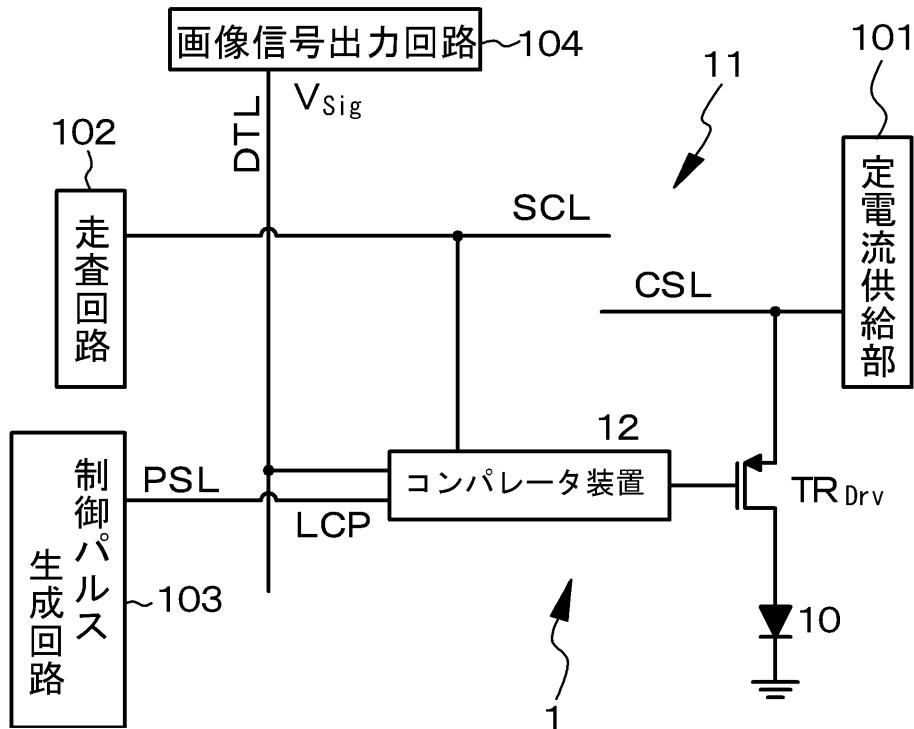

発光部駆動用トランジスタTR<sub>Drv</sub>のゲート電極は、インバータ回路30の出力端に接続されている。また、発光部駆動用トランジスタTR<sub>Drv</sub>の一方のソース／ドレイン電極は、電流供給線CSLを介して、表示装置に備えられた定電流供給部101に接続されている。更には、発光部駆動用トランジスタTR<sub>Drv</sub>の他方のソース／ドレイン電極は、発光部10に接続されている。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0038

【補正方法】変更

【補正の内容】

【0038】

容量部C<sub>1</sub>の他端は、インバータ回路30の入力端(入力ノード)に接続されている。また、発光部10は発光ダイオードから成る。尚、定電流供給部101、走査回路102、制御パルス生成回路103、画像信号出力回路104等は、表示装置に配設されていてもよいし、外部に配設されていてもよい。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0059

【補正方法】変更

【補正の内容】

【0059】

また、走査線 S C L を通して与えられる走査信号が高レベルになるときには、インバータ 1 4 を介した走査信号の反転信号に応答して、制御部 3 5 を構成する第 2 スイッチ回路 ( p チャネル型電界効果トランジスタ T R<sub>18</sub> ) がオン状態になる。これにより、1 段目の C M O S インバータ 3 1 が第 2 スイッチ回路 ( p チャネル型電界効果トランジスタ T R<sub>18</sub> ) を通して 高電位側 の電源 V<sub>dd</sub> に接続されるため、コンパレータ装置 1 2 が作動状態となる。その結果、制御パルス L C P の高レベル区間であっても、コンパレータ装置 1 2 を作動させる必要があるときには、コンパレータ装置 1 2 を確実に作動状態とすることができる。

#### 【手続補正 4】

【補正対象書類名】明細書

【補正対象項目名】0 0 6 7

【補正方法】変更

【補正の内容】

#### 【0 0 6 7】

定電流源 4 2 は、例えば p チャネル型電界効果トランジスタ T R<sub>27</sub> によって構成されている。 p チャネル型電界効果トランジスタ T R<sub>27</sub> のゲート電極に、定電圧回路 4 3 で生成される一定の電圧が印加されることで、定電流源 4 2 は差動回路 4 1 に対して定電流を供給する。定電圧回路 4 3 は、例えば、高電位側 の電源 V<sub>dd</sub> と低電位側の電源 G N D との間に直列に接続された、 p チャネル型電界効果トランジスタ T R<sub>31</sub> , T R<sub>32</sub> 、及び、 n チャネル型電界効果トランジスタ T R<sub>33</sub> , T R<sub>34</sub> から成る。尚、 p チャネル型電界効果トランジスタ T R<sub>32</sub> 及び n チャネル型電界効果トランジスタ T R<sub>33</sub> , T R<sub>34</sub> は、ゲート電極とドレイン電極とが共通に接続されたダイオード接続構成となっている。

#### 【手続補正 5】

【補正対象書類名】明細書

【補正対象項目名】0 0 6 8

【補正方法】変更

【補正の内容】

#### 【0 0 6 8】

差動回路 4 1 において、 p チャネル型電界効果トランジスタ T R<sub>22</sub> のドレイン電極と n チャネル型電界効果トランジスタ T R<sub>24</sub> のドレイン電極との共通接続点 ( ノード ) が、出力端 ( 出力ノード ) となる。この出力端には、ソース接地回路 4 4 の入力端が接続されている。ソース接地回路 4 4 は、高電位側 の電源 V<sub>dd</sub> と低電位側の電源 G N D との間に直列に接続された、 p チャネル型電界効果トランジスタ T R<sub>25</sub> と、 n チャネル型電界効果トランジスタ T R<sub>26</sub> とから成り、電界効果トランジスタ T R<sub>25</sub> のゲート電極には定電圧回路 4 3 から一定の電圧が印加され、電界効果トランジスタ T R<sub>26</sub> のゲート電極が差動回路 4 1 の出力端に接続されている。

#### 【手続補正 6】

【補正対象書類名】明細書

【補正対象項目名】0 0 9 4

【補正方法】変更

【補正の内容】

#### 【0 0 9 4】

図 1 0 に示した例において、信号電圧書き込み期間にあっては、制御パルス L C P の電圧は、例えば、3 ボルト以上である。従って、信号電圧書き込み期間にあっては、コンパレータ装置 1 2 , 1 2 ' は、出力部から第 2 の所定電圧 ( H ) を出力するので、発光部駆動用トランジスタ T R<sub>Drv</sub> はオフ状態にある。画素ブロック発光期間において、制御パルス L C P の電圧が下降し始め、制御パルス L C P の鋸波形の電圧が信号電圧 V<sub>Sig</sub> に基づく電位以下になると、コンパレータ装置 1 2 , 1 2 ' は、出力部から第 1 の所定電圧 ( L ) を出力する。その結果、発光部駆動用トランジスタ T R<sub>Drv</sub> はオン状態となり、電流供給線 C S L から発光部 1 0 に電流が供給され、発光部 1 0 が発光する。制御パルス L C P の電

圧は約 1 ボルトまで下降し、次いで、上昇に転じる。そして、制御パルス L C P の鋸波形の電圧が信号電圧  $V_{sig}$  に基づく電位を超えると、コンパレータ装置 12, 12' は、出力部から第 2 の所定電圧 (H) を出力する。その結果、発光部駆動用トランジスタ T R<sub>D<sub>r</sub></sub> はオフ状態となり、電流供給線 C S L から発光部 10 への電流の供給が遮断され、発光部 10 は発光を中止する。即ち、信号電圧 (発光強度信号)  $V_{sig}$  に基づく電位が制御パルス L C P の鋸波形を切り取る時間の間のみ、発光部 10 を発光させることができる。そして、このときの発光部 10 の輝度は、切り取られる時間の長短に依存する。

#### 【手続補正 7】

【補正対象書類名】明細書

【補正対象項目名】0110

【補正方法】変更

【補正の内容】

#### 【0110】

尚、本開示は以下のような構成を取ることもできる。

##### [A 01] 《コンパレータ装置》

制御パルスと信号電圧に基づく電位とを比較する比較部、及び、

制御パルスによって比較部の作動 / 不作動を制御する制御部、

を備えるコンパレータ装置。

##### [A 02] 《コンパレータ装置：第 1 の構成》

比較部は、

信号電圧が入力される信号書き込みトランジスタ、

制御パルスが入力され、信号書き込みトランジスタと逆相の信号でオン / オフ動作を行う

制御パルス用トランジスタ、

インバータ回路、並びに、

信号書き込みトランジスタ及び制御パルス用トランジスタに一端が接続され、他端がインバータ回路に接続され、信号書き込みトランジスタの作動に基づき、信号電圧に基づく電位を保持する容量部、

を有する [A 01] に記載のコンパレータ装置。

##### [A 03] 制御パルスは、鋸波形の電圧変化を有し、

制御部は、インバータ回路に対して直列に接続され、制御パルスの鋸波形の電圧に応じてオン / オフ動作を行うスイッチ回路を有する [A 02] に記載のコンパレータ装置。

[A 04] 制御部は、スイッチ回路に対して並列に接続され、コンパレータ装置の作動期間でオン状態になる第 2 スイッチ回路を有する [A 03] に記載のコンパレータ装置。

[A 05] 制御部は、インバータ回路に対して直列に接続された抵抗要素を有する [A 03] 又は [A 04] に記載のコンパレータ装置。

[A 06] 制御部は、インバータ回路に対して直列に接続され、インバータ回路に流れる電流を抑える定電流源を有する [A 03] 乃至 [A 05] のいずれか 1 項に記載のコンパレータ装置。

[A 07] インバータ回路は、インバータが、少なくとも 2 段継続接続されて成り、

定電流源は、1 段目のインバータに対して高電位側 / 低電位側の電源の一方の側に接続され、2 段目のインバータに対して高電位側 / 低電位側の電源の他方の側に接続されている [A 06] に記載のコンパレータ装置。

##### [A 08] 《コンパレータ装置：第 2 の構成》

比較部は、

信号電圧と制御パルスとを 2 入力とする差動回路、及び、

差動回路に定電流を供給する定電流源、

を有する [ A 0 1 ] に記載のコンパレータ装置。

[ A 0 9 ] 比較部は、更に、

信号電圧が入力される信号書き込みトランジスタ、及び、

信号書き込みトランジスタに接続され、信号書き込みトランジスタの作動に基づき、信号電圧に基づく電位を保持する容量部、

を有する [ A 0 8 ] に記載のコンパレータ装置。

[ A 1 0 ] 制御パルスは、鋸波形の電圧変化を有し、

制御部は、定電流源に対して直列に接続され、制御パルスの鋸波形の電圧に応じてオン／オフ動作を行うスイッチ回路を有する [ A 0 8 ] 又は [ A 0 9 ] に記載のコンパレータ装置。

[ A 1 1 ] 制御部は、定電流源を構成するトランジスタのゲート電極に定電圧を与える定電圧回路に対して直列に接続され、制御パルスの鋸波形の電圧に応じてオン／オフ動作を行う第 2 スイッチ回路を有する [ A 1 0 ] に記載のコンパレータ装置。

[ B 0 1 ] 《表示装置》

発光部、及び、発光部を駆動する駆動回路から構成された画素が、複数、2 次元マトリクス状に配列されて成り、

各駆動回路は、

制御パルスと信号電圧に基づく電位とを比較し、比較結果に基づく所定電圧を出力する

コンパレータ装置、並びに、

コンパレータ装置からの所定電圧に応じて発光部に電流を供給し、発光部を発光させる

発光部駆動用トランジスタ、

を備えており、

コンパレータ装置は、

制御パルスと信号電圧に基づく電位とを比較する比較部、及び、

制御パルスによって比較部の作動／不作動を制御する制御部、

を備えている表示装置。

[ B 0 2 ] 複数の画素は、第 1 の方向及び第 2 の方向に 2 次元マトリクス状に配列され、

画素群は第 1 の方向に沿って P 個の画素ブロックに分割されており、

第 1 番目の画素ブロックに属する画素を構成する発光部から、第 P 番目の画素ブロック

に属する画素を構成する発光部まで、画素ブロック毎に、順次、一斉に発光させ、且つ、

一部の画素ブロックに属する画素を構成する発光部を発光させているとき、残りの画素ブ

ロックに属する画素を構成する発光部を発光させないように構成された [ B 0 1 ] に記載

の表示装置。

[ B 0 3 ] 複数の制御パルスに基づき、発光部が、複数回、発光する [ B 0 1 ] 又は [ B 0 2 ] に記載の表示装置。

[ B 0 4 ] 複数の制御パルスの時間間隔は一定である [ B 0 3 ] に記載の表示装置。

[ B 0 5 ] 1 表示フレーム内における制御パルスの数よりも、1 表示フレーム内における

駆動回路に供給される制御パルスの数は少ない [ B 0 1 ] 乃至 [ B 0 4 ] のいずれか 1 項

に記載の表示装置。

[B06] 1表示フレームにおいて、常に、いずれかの画素ブロックが発光している[B01]乃至[B05]のいずれか1項に記載の表示装置。

[B07] 1表示フレームにおいて、発光していない画素ブロックが存在する[B01]乃至[B05]のいずれか1項に記載の表示装置。

[B08] 鋸波形の電圧変化を有する制御パルスを生成する制御パルス生成回路を1つ備えている[B01]乃至[B07]のいずれか1項に記載の表示装置。

[B09] 1つの制御パルスの電圧の絶対値は、時間の経過と共に、増加し、次いで、減少する[B01]乃至[B08]のいずれか1項に記載の表示装置。

[B10] 時間の経過と共に変化する制御パルスの電圧によってガンマ補正がなされる[B09]に記載の表示装置。

[B11] 時間を変数とした制御パルスの電圧の変化率の絶対値は、定数2.2に比例する[B10]に記載の表示装置。

[B12] 発光部は発光ダイオードから構成されている[B01]乃至[B11]のいずれか1項に記載の表示装置。

[B13] 《表示装置：第1の構成》

比較部は、

信号電圧が入力される信号書き込みトランジスタ、

制御パルスが入力され、信号書き込みトランジスタと逆相の信号でオン／オフ動作を行う制御パルス用トランジスタ、

インバータ回路、並びに、

信号書き込みトランジスタ及び制御パルス用トランジスタに一端が接続され、他端がインバータ回路に接続され、信号書き込みトランジスタの作動に基づき、信号電圧に基づく電位を保持する容量部、

を有する[B01]乃至[B12]のいずれか1項に記載の表示装置。

[B14] 制御パルスは、鋸波形の電圧変化を有し、

制御部は、インバータ回路に対して直列に接続され、制御パルスの鋸波形の電圧に応じてオン／オフ動作を行うスイッチ回路を有する[B13]に記載の表示装置。

[B15] 制御部は、スイッチ回路に対して並列に接続され、コンパレータ装置の作動期間でオン状態になる第2スイッチ回路を有する[B14]に記載の表示装置。

[B16] 制御部は、インバータ回路に対して直列に接続された抵抗要素を有する[B14]又は[B15]に記載の表示装置。

[B17] 制御部は、インバータ回路に対して直列に接続され、インバータ回路に流れる電流を抑える定電流源を有する[B14]乃至[B16]のいずれか1項に記載の表示装置。

[B18] インバータ回路は、インバータが、少なくとも2段継続接続されて成り、

定電流源は、1段目のインバータに対して高電位側／低電位側の電源の一方の側に接続され、2段目のインバータに対して高電位側／低電位側の電源の他方の側に接続されてい

る [ B 1 7 ] に記載の表示装置。

[ B 1 9 ] 《表示装置：第 2 の構成》

比較部は、

信号電圧と制御パルスとを 2 入力とする差動回路、及び、

差動回路に定電流を供給する定電流源、

を有する [ B 0 1 ] 乃至 [ B 1 2 ] のいずれか 1 項に記載の表示装置。

[ B 2 0 ] 比較部は、更に、

信号電圧が入力される信号書き込みトランジスタ、及び、

信号書き込みトランジスタに接続され、信号書き込みトランジスタの作動に基づき、信号電圧に基づく電位を保持する容量部、

を有する [ B 1 9 ] に記載の表示装置。

[ B 2 1 ] 制御パルスは、鋸波形の電圧変化を有し、

制御部は、定電流源に対して直列に接続され、制御パルスの鋸波形の電圧に応じてオン／オフ動作を行うスイッチ回路を有する [ B 1 9 ] 又は [ B 2 0 ] に記載の表示装置。

[ B 2 2 ] 制御部は、定電流源を構成するトランジスタのゲート電極に定電圧を与える定電圧回路に対して直列に接続され、制御パルスの鋸波形の電圧に応じてオン／オフ動作を行う第 2 スイッチ回路を有する [ B 2 1 ] に記載の表示装置。

[ B 2 3 ] 各画素ブロックにおいて、第 2 の方向に配列された 1 列に属する全ての画素における信号書き込みトランジスタは、一齊に作動状態となる [ B 1 3 ] 乃至 [ B 2 2 ] のいずれか 1 項に記載の表示装置。

[ B 2 4 ] 各画素ブロックにおいて、第 2 の方向に配列された 1 列に属する全ての画素における信号書き込みトランジスタが一齊に作動状態となる動作が、第 1 の方向に配列された第 1 行目に属する全ての画素における信号書き込みトランジスタから最終行に属する全ての画素における信号書き込みトランジスタまで、順次、行われる [ B 2 3 ] に記載の表示装置。

[ B 2 5 ] 各画素ブロックにおいて、第 2 の方向に配列された 1 列に属する全ての画素における信号書き込みトランジスタが一齊に作動状態となる動作が、第 1 の方向に配列された第 1 行目に属する全ての画素における信号書き込みトランジスタから最終行に属する全ての画素における信号書き込みトランジスタまで、順次、行われた後、該画素ブロックに制御パルスが供給される [ B 2 4 ] に記載の表示装置。

[ B 2 6 ] 第 2 の方向に配列された 1 列に属する画素は、制御パルス線に接続されており、

制御パルス線には、所定の間隔で、ボルテージフォロワー回路（バッファ回路）が配設されている [ B 0 1 ] 乃至 [ B 2 5 ] のいずれか 1 項に記載の表示装置。

[ C 0 1 ] 《表示装置の駆動方法》

発光部、及び、発光部を駆動する駆動回路から構成された画素が、複数、2 次元マトリクス状に配列されて成り、

各駆動回路は、

制御パルスと信号電圧に基づく電位とを比較し、比較結果に基づく所定電圧を出力するコンパレータ装置、並びに、

コンパレータ装置からの所定電圧に応じて発光部に電流を供給し、発光部を発光させる

発光部駆動用トランジスタ、

を備えている表示装置の駆動方法であって、

制御パルスによってコンパレータ装置の作動／不作動を制御する表示装置の駆動方法。

【手続補正8】

【補正対象書類名】図面

【補正対象項目名】図2

【補正方法】変更

【補正の内容】

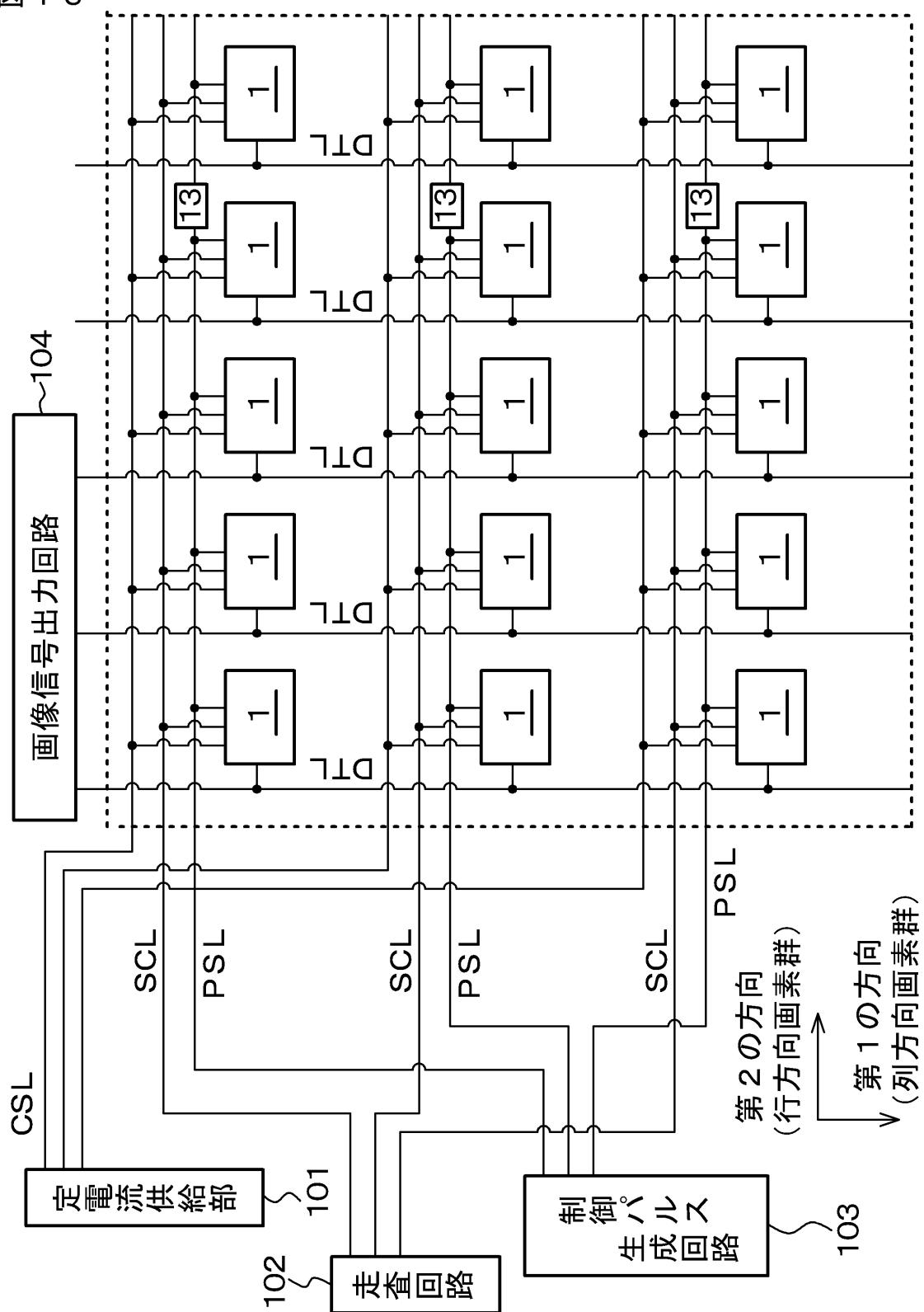

【図2】

図2

【手続補正9】

【補正対象書類名】図面

【補正対象項目名】図3

【補正方法】変更

【補正の内容】

【図3】

図3

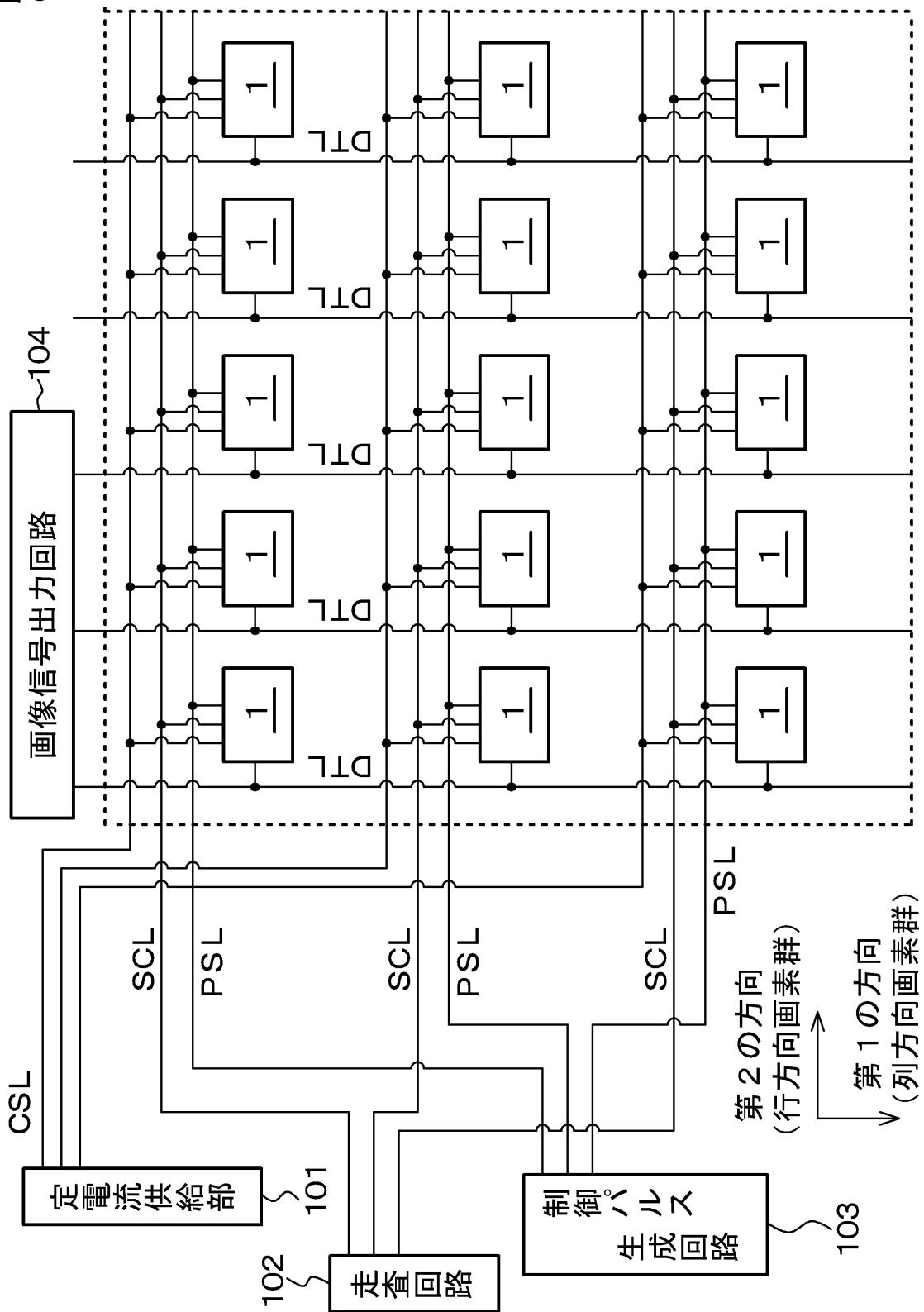

【手続補正10】

【補正対象書類名】図面

【補正対象項目名】図 1 3

【補正方法】変更

【補正の内容】

【図13】

図 1 3