【公報種別】特許公報の訂正

【部門区分】第6部門第1区分

【発行日】令和2年9月2日(2020.9.2)

【特許番号】特許第6736552号(P6736552)

【登録日】令和2年7月17日(2020.7.17)

【特許公報発行日】令和2年8月5日(2020.8.5)

【年通号数】特許・実用新案公報2020-032

【出願番号】特願2017-530001(P2017-530001)

【訂正要旨】特許権者の住所の誤載により下記のとおり全文を訂正する。

【国際特許分類】

G 01 B 7/28 (2006.01)

G 06 T 1/00 (2006.01)

【F I】

G 01 B 7/28 A

G 06 T 1/00 400 G

【記】別紙のとおり

(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6736552号

(P6736552)

(45) 発行日 令和2年8月5日(2020.8.5)

(24) 登録日 令和2年7月17日(2020.7.17)

(51) Int.Cl.

F 1

G 0 1 B 7/28 (2006.01)

G 0 6 T 1/00 (2006.01)G 0 1 B 7/28 A

G 0 6 T 1/00 4 0 0 G

請求項の数 19 (全 21 頁)

(21) 出願番号 特願2017-530001 (P2017-530001)

(86) (22) 出願日 平成27年12月15日 (2015.12.15)

(65) 公表番号 特表2018-500555 (P2018-500555A)

(43) 公表日 平成30年1月11日 (2018.1.11)

(86) 國際出願番号 PCT/SE2015/051345

(87) 國際公開番号 WO2016/105261

(87) 國際公開日 平成28年6月30日 (2016.6.30)

審査請求日 平成30年10月24日 (2018.10.24)

(31) 優先権主張番号 1451633-0

(32) 優先日 平成26年12月22日 (2014.12.22)

(33) 優先権主張国・地域又は機関

スウェーデン(SE)

(73) 特許権者 317002755

フィンガープリント カーズ アクティエ

ボラーグ

スウェーデン国, 4 1 1 1 9 ヨーテボ

リ, クングスガタン 20

(74) 代理人 100099759

弁理士 青木 篤

(74) 代理人 100092624

弁理士 鶴田 準一

(74) 代理人 100114018

弁理士 南山 知広

(74) 代理人 100141254

弁理士 榎原 正巳

最終頁に続く

(54) 【発明の名称】タイミング回路構成を備える感知素子を有する容量性指紋センサ

## (57) 【特許請求の範囲】

## 【請求項 1】

指(31)の指紋パターンを感知する容量性指紋感知装置であって、

前記容量性指紋感知装置は複数の感知素子(8)を備え、各感知素子は、

前記指(31)による接触対象である保護誘電最上層(30)の一部と、

前記最上層(30)の前記一部の下に配置される導電性感知構造(32)と、

電荷測定回路構成(50)であって、前記感知構造に接続されて、少なくとも第一の

測定状態と第二の測定状態との間を連続的に遷移して測定シーケンスを実行し、前記指と

前記感知構造との間の電位差の変化に起因して前記感知構造が帯びる電荷に生じる変化を

示す出力信号を前記電荷測定回路構成から発信する、電荷測定回路構成と、

前記電荷測定回路構成に接続されて前記測定状態の少なくとも一つのタイミングを制

御するタイミング回路構成(51)と、

を備え、

前記タイミング回路構成は、第一の事象と前記第一の事象に関する時間遅延とによって

規定される遷移時間で前記第一の測定状態から前記第二の測定状態に遷移するように前記

電荷測定回路構成を制御するように構成され、

前記タイミング回路構成は、前記第一の事象を規定する第一の信号を受信する入力と、

前記第一の事象に対して遅延する第二の事象を規定する第二の信号を供給する出力と、を

有する第一の遅延素子を備え、

前記タイミング回路構成は、前記第一の遅延素子の出力と第二の遅延素子の入力との間

10

20

に連結される少なくとも一つの論理ゲートを更に備える、

容量性指紋感知装置。

【請求項 2】

前記第二の事象は、前記第一の測定状態から第二の測定状態への遷移を含む、請求項1に記載の容量性指紋感知装置。

【請求項 3】

前記第一の遅延素子の出力は、前記電荷測定回路構成に連結されて、前記第二の信号によって前記電荷測定回路構成の動作を制御できるようにする、請求項1又は請求項2に記載の容量性指紋感知装置。

【請求項 4】

前記タイミング回路構成は、前記第一の遅延素子の出力に連結される入力と、前記第二の事象に対して遅延する第三の事象を規定する第三の信号を供給する出力と、を有する第二の遅延素子を更に備える、請求項1から請求項3までのいずれか一項に記載の容量性指紋感知装置。

【請求項 5】

前記第二の遅延素子の出力は、前記電荷測定回路構成に連結されて、前記第三の信号によって前記電荷測定回路構成の動作を制御できるようにする、請求項4に記載の容量性指紋感知装置。

【請求項 6】

前記タイミング回路構成は、それぞれが入力及び出力を有する複数の遅延素子を備え、前記遅延素子は、連続する遅延素子の配列の形状に配置され、連続する遅延素子の前記配列では前記遅延素子のそれぞれの出力が次の素子の入力に連結されるようになる、請求項1から請求項5までのいずれか一項に記載の容量性指紋感知装置。

【請求項 7】

前記配列は閉ループ配列である、請求項6に記載の容量性指紋感知装置。

【請求項 8】

前記第一の事象は、前記感知素子の外側で生成される起動信号によってもたらされる、請求項1から請求項7までのいずれか一項に記載の容量性指紋感知装置。

【請求項 9】

前記測定シーケンスは、前記電荷測定回路構成の出力での電位が前記感知構造の電位を基準とするリセット状態を少なくとも含む、請求項1から請求項8までのいずれか一項に記載の容量性指紋感知装置。

【請求項 10】

前記電荷測定回路構成は、

電荷増幅器であって、

前記感知構造に接続される負の入力と、

正の入力と、

出力と、

前記負の入力と前記出力との間に接続される帰還コンデンサと、

前記正及び負の入力と前記出力との間の少なくとも一つの増幅器段と、

を備える電荷増幅器を備え、

前記電荷増幅器は、前記負の入力での電位が前記正の入力での電位を実質的に追従するよう構成される、

請求項1から請求項9までのいずれか一項に記載の容量性指紋感知装置。

【請求項 11】

前記容量性指紋感知装置は、

励起信号供給回路構成であって、前記正の入力に接続されて、前記正の入力での電位を第一の電位から第二の電位に変化させ、これにより前記感知構造の電位を変化させ、これにより前記指と前記感知構造との間の電位差の前記変化をもたらすように構成される励起信号供給回路構成、

10

20

30

40

50

を更に備える、請求項1\_0に記載の容量性指紋感知装置。

【請求項1\_2】

前記タイミング回路構成は、前記励起信号供給回路構成に接続されて、

第一の励起制御信号を前記励起信号供給回路構成に供給して、第一の励起遷移時間での第一の電位から第二の電位への電位の前記変化を引き起こし、

第二の励起制御信号を前記励起信号供給回路構成に供給して、第二の励起遷移時間での第二の電位から第一の電位に戻る電位の変化を引き起こす、

請求項1\_1に記載の容量性指紋感知装置。

【請求項1\_3】

指の指紋パターンを感知する容量性指紋感知装置であって、

前記容量性指紋感知装置は複数の感知素子を備え、各感知素子は、

前記指による接触対象である保護誘電最上層の一部と、

前記最上層の前記一部の下に配置される導電性感知構造と、

電荷測定回路構成であって、前記感知構造に接続されて、少なくとも第一の測定状態と第二の測定状態との間を連続的に遷移して測定シーケンスを実行し、前記指と前記感知構造との間の電位差の変化に起因して前記感知構造が帯びる電荷に生じる変化を示す出力信号を前記電荷測定回路構成から発信する、電荷測定回路構成と、

前記電荷測定回路構成に接続されて前記測定状態の少なくとも一つのタイミングを制御するタイミング回路構成と、

を備え、

前記指紋感知装置は、前記指の電位に対して第一の電位から第二の電位に変わり第一の電位に戻る循環変化を含み時間的に変化する励起電位を示す励起信号を供給する励起信号供給回路構成を更に備え、

前記感知素子のそれぞれは、復調回路構成であって、前記電荷測定回路構成に接続されて、前記電荷測定回路構成からの前記出力信号及びタイミングに関連する復調信号を前記励起信号に結合し、前記感知構造が帯びる電荷の前記変化を示すDC信号成分を含む結合信号を供給する復調回路構成を更に備え、

前記指紋感知装置は、読み出し回路構成であって、前記感知素子のそれぞれに接続されて、前記感知素子のそれからの前記DC信号成分に基づく前記指紋パターンの表示を供給する読み出し回路構成を更に備える、

容量性指紋感知装置。

【請求項1\_4】

前記復調回路構成は、前記出力信号を前記復調信号とともに遅倍する信号遅倍回路構成を備える、請求項1\_3に記載の容量性指紋感知装置。

【請求項1\_5】

前記復調回路構成は、高周波化した周波数成分を除去しながら前記DC信号成分が通過できるようにするローパスフィルタを更に備える、請求項1\_3又は請求項1\_4に記載の容量性指紋感知装置。

【請求項1\_6】

前記電荷測定回路構成は、

サンプリング回路構成であって、

前記指と前記感知構造との間の電位差の前記変化の前の第一のサンプリング時間に、前記感知構造が帯びる電荷を示す信号をサンプリングし、

前記指と前記感知構造との間の電位差の前記変化の後の第二のサンプリング時間に、前記感知構造が帯びる電荷を示す前記信号をサンプリングする、

サンプリング回路構成、

を備える、請求項1から請求項1\_5までのいずれか一項に記載の容量性指紋感知装置。

【請求項1\_7】

前記タイミング回路構成は、前記サンプリング回路構成に接続されて、

第一のサンプリング制御信号を、前記第一のサンプリング時間に第一の信号のサンプリ

10

20

30

40

50

ングを実施する前記サンプリング回路構成に供給し、

第二のサンプリング制御信号を、前記第二のサンプリング時間に第二の信号のサンプリングを実施する前記サンプリング回路構成に供給する、

請求項1\_6に記載の容量性指紋感知装置。

【請求項1\_8】

前記感知素子のそれぞれに接続され、前記感知素子のそれぞれからの前記出力信号に基づく前記指紋パターンの表示を供給するように構成される読み出し回路構成、を更に備える、請求項1から請求項1\_7までのいずれか一項に記載の容量性指紋感知装置。

【請求項1\_9】

電子装置であって、

請求項1\_8に記載の指紋感知装置と、

処理回路構成であって、

指紋感知装置からの前記指紋パターンの前記表示を取得し、

前記表示に基づいてユーザを認証し、

前記表示に基づいて前記ユーザが認証された場合にのみ少なくとも一つのユーザ要求処理を実施する、

ように構成される処理回路構成と、

を備える電子装置。

【発明の詳細な説明】

【技術分野】

10

【0001】

本発明は、容量性指紋感知装置及び指紋パターンの感知方法に関する。

【背景技術】

【0002】

様々なタイプの生体認証システムが、安全性を向上するため、及び／又はユーザの利便性を高めるために、用いられることが多くなっている。

【0003】

特に、指紋感知システムは、その小さな形状因子、高い性能及びユーザ受け入れのため、例えば家電装置に採用されている。

【0004】

20

(例えば静電容量式、光学式、熱式のような)様々な利用可能な指紋感知原理の中でも、静電容量感知が最も一般的に用いられており、特に、大きさ及び消費電力が重要な課題である適用例に用いられている。

【0005】

あらゆる容量性指紋センサは、いくつかの感知構造と、指紋センサの表面に置かれるか指紋センサの表面を横切って動く指と、の間の静電容量を示す測定値を供給する。

【0006】

いくつかの容量性指紋センサは、感知構造と指との間の静電容量を受動的に読み取る。しかし、これには、感知構造のそれぞれと指との間の比較的大きな静電容量を必要とする。このため、そのような受動的な静電容量センサは概して、感知構造を覆う非常に薄い保護層を備える。このため、そのようなセンサは引っかき傷及び／又はESD(静電放電)に対していくらか敏感になる。

【0007】

米国特許U.S.7,864,992は、センサアレイの近傍に配置された導電構造をパルス操作して、センサアレイの感知構造が帯びる電荷の結果変化を測定することによって、駆動信号が指に注入される指紋感知システムを開示する。

【0008】

このタイプのいわゆる能動的指紋感知システムは、上記の受動的システムよりもかなり高い信号対雑音比で静電容量及び感知構造の測定を概ね可能にする。次に、これにより保護被覆を大幅に厚くすることができるため、いっそう頑強な容量性指紋センサを、かなり

30

40

50

の摩耗にさらされる携帯電話のようなアイテムに組み入れることができる。

【0009】

しかし、更に向上の余地がある。特に、厚みが更に増した保護被覆を介して指紋を感知すること及び／又は信号対雑音比の点で更に性能を向上させることができることが望ましいであろう。

【発明の概要】

【0010】

上記の欠点をはじめとする先行技術の欠点に鑑みて、本発明の目的は、改良した容量性指紋感知装置、特に、きわめて厚い保護被覆を通しての感知性能が向上した容量性指紋感知装置を得ることである。

【0011】

10

このため、本発明の第一の態様によれば、指の指紋パターンを感知する容量性指紋感知装置が提供される。容量性指紋センサは複数の感知素子を備え、各感知素子は、指による接触対象である保護誘電最上層と、最上層の下に配置される導電性感知構造と、電荷測定回路構成であって、感知構造に接続されて、少なくとも第一の測定状態と第二の測定状態との間を連続的に遷移して測定シーケンスを実行し、指と感知構造との間の電位差の変化に起因して感知構造が帯びる電荷に生じる変化を示す出力信号を電荷測定回路構成から発信する、電荷測定回路構成と、前記電荷測定回路構成に接続されて前記測定状態の少なくとも一つのタイミングを制御するタイミング回路構成と、を備える。

【0012】

20

感知構造は、ある種の平行板コンデンサが感知構造（感知板）、指表面の一部及び保護被覆（及び指表面の一部と保護被覆との間に部分的に存在する可能性のある任意の空気）によって形成されるように、金属板の形態で有利に設けられてもよい。

【0013】

保護被覆は、少なくとも $20\text{ }\mu\text{m}$ の厚さと、指紋感知装置の基底構造を摩耗及び断裂のほかE S Dからも保護する高い絶縁耐力を有利に有してもよい。その上更に有利なことは、保護被覆は少なくとも $50\text{ }\mu\text{m}$ の厚さであってもよい。実施形態では、保護被覆は数百 $\mu\text{m}$ の厚さであってもよい。

【0014】

30

「電荷測定回路構成」は、感知構造が帯びる電荷の変化を示す出力信号を供給することができる任意の回路構成である。出力信号はアナログであってもデジタルであってもよい。例として、出力信号は基準電位に対する電位の形態で供給されてもよい。種々の実施形態では、電荷測定回路構成は電荷増幅器を備えてもよい。

【0015】

電荷測定回路構成は、所定の順序での異なる測定状態間の遷移に及ぶ所定の測定シーケンスを実行するように制御可能であってもよい。測定状態を電荷測定回路構成に供給される制御信号の特定の結合によって規定してもよい。

【0016】

なお、本発明の実施形態による容量性指紋感知装置の各感知素子又は感知素子群は、電荷測定回路構成の測定状態の少なくとも一つのタイミング制御が各感知素子又は感知素子群で局所的に制御されるように、タイミング回路構成を備える。

40

【0017】

言い換えると、少なくとも一つの測定状態の時点及び持続時間の少なくともいずれかが各感知素子又は感知素子群で局所的に制御される。このため、タイミング回路構成は、非同期か同期又はその組み合わせであってもよい局所状態機械として機能するといえる。

【0018】

本発明は、感知素子の動作を高速化すると、各感知素子からの多重的な読み出しが可能になり、ひいては、例えば、信号対雑音比及び同相モードノイズの低減の観点から静電容量測定／感知性能を向上させるであろうという認識に基づくものである。

【0019】

本発明者はこのほか、感知素子又は感知素子群でのタイミングを局所化することによつ

50

て、感知素子の動作の高速化が所望通りに可能になるか大幅に促進されることを理解していた。

【0020】

測定状態間の少なくとも最も緊急を要する一つ（あるいは複数の）遷移のタイミングを局所化することにより、測定時間を減少させたり、及び／又は容量性指紋感知装置の設計を容易にしたりできる。例として、一定のタイミング制御信号の各感知素子へのルート設定を慎重に実施する必要はないであろうが、特定の感知素子又は感知素子群を選択する外部信号によってタイミングを開始することができる。

【0021】

なお、容量性指紋感知装置は少なくとも100個のオーダーでというような多数の感知素子を備えてもよい。容量性指紋感知装置のあるものは、少なくとも10,000個というようなかなり多数の感知素子を備えてもよい。読み出し周波数がおよそ1MHzからおよそ20MHzに増大した場合、異なる感知素子への伝導時間の差は、測定に関するタイミング必要条件を外部の集中タイミング制御を用いて満たすことを難しくするか、実際には不可能にする可能性さえある。

【0022】

このため、本発明の実施形態では、読み出し周波数が高くなり、ひいては測定性能を向上させることができ、更に多重出力信号同士の結合（一種のフィルタリングと称されることがある）を可能にすることにより、同相モードノイズを減少させ、信号対雑音比を増大させることができる。

【0023】

これは次に、ボタン又は携帯電話のような電子装置のカバーの一部など、更に厚めの被覆を通した測定を可能にする。その上、指紋センサのエネルギー消費及び／又は指紋表示（画像）を取得するのに必要な時間を減少させることができる可能性がある。

【0024】

実施形態によれば、各感知素子のタイミング回路構成は、少なくとも一つの追加感知素子に更に接続され、この少なくとも一つの追加感知素子の状態を追加的に制御する。例として、タイミング回路構成は、隣接する感知素子を制御して、適切な電圧レベルをそれぞれの感知構造に供給してもよい。

【0025】

本発明の種々の実施形態によれば、タイミング回路構成は、電荷測定回路構成を制御して、第一の事象と第一の事象に対する時間遅延とによって規定される遷移時間で第一の測定状態から第二の測定状態に遷移するように構成されてもよい。

【0026】

第一の事象は、タイミング回路構成によって独立に供給されてもよく、あるいは、感知素子の外部の回路構成によって供給されてもよい。

【0027】

種々の実施形態によれば、タイミング回路構成は、第一の事象を規定する第一の信号を受信する入力と、第一の事象に対して遅延する第二の事象を規定する第二の信号を供給する出力と、を有する第一の遅延素子を有利に備えてもよい。

【0028】

第一の信号は時間的に変化する電圧であってもよい。第一の事象は、例として、第一の信号の立ち上がり面又は立ち下がり面によって規定されてもよい。

【0029】

第一の信号は、感知素子の内部で生成されてもよい。あるいは、種々の実施形態によれば、感知素子の外部で生成され、例えば、起動信号と称されることのある信号として供給されてもよい。

【0030】

第二の信号は、第一の信号の遅延バージョンとしてもよい。しかし、遅延以外の変換を第一の信号に付与して第二の信号を形成してもよいことを理解すべきである。例として、

10

20

30

40

50

第一の信号を、追加的に増幅及び／又は減衰及び／又は反転して第二の信号を形成してもよい。

【0031】

第一の遅延素子は、一つ以上の論理ゲートのような半導体回路構成を有利に備えてもよい。

【0032】

第二の信号によって規定される第二の事象は、第一の測定状態から第二の測定状態への上記の遷移を有利に含んでもよい。

【0033】

種々の実施形態によれば、第一の遅延素子の出力は、電荷測定回路構成に連結されて、第二の信号によって電荷測定回路構成の動作を制御できるようにしてよい。 10

【0034】

第一の遅延素子の出力は、電荷測定回路構成に直接接続されてもよい。あるいは、第一の遅延素子と電荷測定回路構成との間に追加回路構成があつてもよい。例として、上記の第二の信号及び追加信号を論理ゲートに入力してもよい。論理ゲートの出力を用いて電荷測定回路構成の動作を制御してもよい。

【0035】

その上、タイミング回路構成は、第一の遅延素子の出力に連結される入力と、第二の事象に対して遅延する第三の事象を規定する第三の信号を供給する出力と、を有する第二の遅延素子を追加的に備えてもよい。 20

【0036】

この第三の事象は、電荷測定回路構成を制御して上記の第二の測定状態から第三の測定状態に遷移するようにすることに及んでもよい。

【0037】

そのため、第二の遅延素子の出力は、電荷測定回路構成に連結されて、第三の信号によって電荷測定回路構成の動作を制御できるようにする。

【0038】

種々の実施形態によれば、その上、タイミング回路構成は、第一の遅延素子の出力と前記第二の遅延素子の入力との間に連結される少なくとも一つの論理ゲートを更に備えてもよい。ここで、第二の遅延素子によって遅延する信号は、上記の第二の信号及び感知素子の内部で生成されるか感知素子の外部の回路構成から供給されることがある追加制御信号の論理関数になってもよい。このため、このような実施形態は上記の第二の事象の条件付き制御を可能にするであろう。 30

【0039】

上記の測定シーケンスは、電荷測定回路構成の構成によっては、異なる数の測定状態を含んでもよい。タイミング回路構成は、同一配列の一つの遅延素子の出力が次の遅延素子の入力に連結されているデイジーチェーン構成に複数の遅延素子を配置することにより、測定状態の数に有利に適合させてもよい。遅延素子の数は、測定状態の数に適合させてもよいが、測定シーケンスの測定状態の数に直接一致する必要はない。

【0040】

タイミング回路構成は、一つ又はいくつかの遅延素子を用いる代替物又は補完物として、一つ又はいくつかの論理ゲートと組み合わせて一つ又はいくつかのフィードフォワード及び／又はフィードバックループを備えてもよい。これにより、タイミング回路構成を物理的に小さくすることが可能になり、そのため指紋感知装置の設計が容易になったり、及び／又は感知素子を小さくすることが可能になる可能性がある。 40

【0041】

実施形態では、遅延素子の配列は、外部信号によって制御されることもあればないこともある閉ループ配列であつてもよい。実施形態では、感知素子が、指と感知構造との間の容量結合を示す信号を出力する前又は出力中に、いくつかの測定周期を自動的に「一通り実行する」ことができるようにするのは有利なことであると思われる。 50

## 【0042】

種々の実施形態では、第一の感知素子又は感知素子群が第二の感知素子又は感知素子群の測定シーケンスを開始できるように容量性指紋感知装置を構成するのが有利であってもよい。例として、指紋感知装置の行又は列の各感知素子又は感知素子群は、測定シーケンスの実行を互いに連続的に始動してもよい。これにより、例えば、列又は行全体のクイックスキャンが可能になり、列又は行全体からの平均値信号が高速になることがあるであろう。そのような平均値信号が、例として、雑音消去などに有用であることがある。

## 【0043】

種々の実施形態によれば、上記の測定シーケンスは、電荷測定回路構成の出力での電位が感知構造の電位を基準としているリセット状態を少なくとも含んでもよい。

10

## 【0044】

電荷測定回路構成は、電荷増幅器であって、感知構造に接続される負の入力と、正の入力と、出力と、負の入力と出力との間に接続される帰還コンデンサと、正及び負の入力と出力との間の少なくとも一つの増幅器段と、を備える電荷増幅器を備え、電荷増幅器は、負の入力での電位が正の入力での電位を実質的に追従するように構成される。

## 【0045】

このような実施形態では、電荷測定回路構成は、負の入力と出力とを伝導的に接続して帰還コンデンサを放電するように制御可能であるリセット回路構成を更に備えてもよい。

## 【0046】

リセット回路構成は、感知素子に含まれるタイミング回路構成に連結されてもよい。タイミング回路構成は、リセット回路構成を制御して帰還コンデンサを放電することにより、電荷測定回路構成を上記のリセット状態に遷移させてもよい。

20

## 【0047】

続いて、タイミング回路構成は、リセット回路構成を負の入力が出力から外れるように制御することにより、帰還コンデンサが電荷を保持できるようにしてもよい。この事象は、電荷測定回路構成をリセット状態から、感知構造が帯びる電荷を、電荷増幅器を用いて測定できる測定レディ状態に遷移させるであろう。

## 【0048】

実施形態によれば、指紋感知装置は、指の電位に対して第一の電位から第二の電位に変わり第一の電位に戻る循環変化を含み時間的に変化する励起電位を示す励起信号を供給する励起信号供給回路構成を更に備えてもよい。感知素子のそれぞれは、復調回路構成であって、電荷測定回路構成に接続されて、電荷測定回路構成からの出力信号及びタイミングに関連する復調信号を励起信号に結合し、感知構造が帯びる電荷の変化を示すDC信号成分を含む結合信号を供給する復調回路構成を更に備えてもよい。指紋感知装置は、読み出し回路構成であって、感知素子のそれぞれに接続されて、感知素子のそれぞれからのDC信号成分に基づく指紋パターンの表示を供給する読み出し回路構成を更に備えてもよい。

30

## 【0049】

よって、時間的に変化する電位とは、基準電位に対して時間の経過とともに変化する大きさを有する電位を意味すると理解する必要がある。時間的に変化する励起電位は、例として、一つのパルス繰り返し周波数又は各種パルス繰り返し周波数の組み合わせを有するパルス列として供給されてもよい。そのようなパルス列の各種パルスは、例えば、矩形波パルスであってもよい。これとは別に、時間的に変化する励起電位は、一つの正弦波又は各種正弦波の組み合わせとして供給されてもよい。

40

## 【0050】

本発明者は、感知信号の望ましい情報内容（感知構造が帯びる電荷の上記の変化）がDC信号又はDC信号に近い信号（指紋感知システムの基準電位に対して一定の電圧）によって示されるように、感知素子又は感知素子群内に局在する感知信号を少なくとも部分的に復調することによって、電力消費量の対応する増大を生じさせることなく、感知素子の動作の望ましい高速化を達成できることを理解している。

## 【0051】

50

D C 信号成分としての感知構造が帯びる電荷の変化を各感知素子から出力することによって、読み出しラインの寄生容量に対して電位の読み出しラインを上下に移動させる必要がなくなり、読み出し事象当たりのエネルギー消費が大幅に減少するようになるであろう。

【 0 0 5 2 】

種々の実施形態によれば、容量性指紋感知装置は、励起信号供給回路構成であって、正の入力に接続されて、正の入力での電位を第一の電位から第二の電位に変化させ、これにより感知構造の電位を変化させ、これにより指と感知構造との間の電位差の変化をもたらすように構成される励起信号供給回路構成を、更に備えてよい。

【 0 0 5 3 】

励起信号供給回路構成は、異なるライン上の二つ以上の異なる電位間を切り替わるよう構成されるスイッチング回路構成であることがある。これとは別に、あるいはこれと併せて、励起信号供給回路構成は、波電圧信号又は正弦波電圧信号のような時変電位を供給するように構成される少なくとも一つの信号源を備えてよい。

【 0 0 5 4 】

実施形態によれば、各感知素子は、その特定の感知素子に対する励起信号供給回路構成を備えてよい。

【 0 0 5 5 】

その上、各感知素子について、タイミング回路構成は、励起信号供給回路構成に接続されて、第一の励起制御信号を励起信号供給回路構成に供給して、第一の励起遷移時間での第一の電位から第二の電位への電位の変化を引き起こし、第二の励起制御信号を励起信号供給回路構成に供給して、第二の励起遷移時間での第二の電位から第一の電位に戻る電位の変化を引き起こしてもよい。

【 0 0 5 6 】

種々の実施形態によれば、電荷測定回路構成は、サンプリング回路構成であって、指と感知構造との間の電位差の変化の前の第一のサンプリング時間に、感知構造が帯びる電荷を示す信号をサンプリングし、指と感知構造との間の電位差の変化の後の第二のサンプリング時間に、感知構造が帯びる電荷を示す信号をサンプリングするサンプリング回路構成を備える。

【 0 0 5 7 】

サンプリング回路構成は、第一及び第二のサンプリングコンデンサと、感知構造が帯びる電荷を示す上記の信号を第一のサンプリング時間で第一のサンプリングコンデンサに供給し、信号を第二のサンプリング時間で第二のサンプリングコンデンサに供給するように制御可能なスイッチング回路構成と、を備えてよい。

【 0 0 5 8 】

感知信号を第一及び第二のサンプリング時間でサンプリングする手順は、相関二重サンプリングと一般に呼ばれ、指紋感知装置がさらされることがある同相モードノイズのオフセット成分のほか少なくとも低周波成分の大部分も除去する。

【 0 0 5 9 】

タイミング回路構成は、サンプリング回路構成に有利に接続されて、第一のサンプリング制御信号を、第一のサンプリング時間に第一の信号のサンプリングを実施するサンプリング回路構成に供給し、第二のサンプリング制御信号を、前記第二のサンプリング時間に前記第二の信号のサンプリングを実施するサンプリング回路構成に供給する。

【 0 0 6 0 】

このような種々の実施形態では、本発明の容量性指紋感知装置は、感知素子のそれぞれに接続され、感知素子のそれぞれからの出力信号に基づく指紋パターンの表示を供給するように構成される読み出し回路構成を有利に更に備えてよい。

【 0 0 6 1 】

指紋パターンの表示は、読み出し回路構成によって、容量性指紋感知装置の外部にある他の回路構成に供給されてもよい。

10

20

30

40

50

## 【0062】

本発明の種々の実施形態による容量性指紋感知装置は、電子装置に有利に含まれてもよい。この電子装置は、処理回路構成であって、指紋感知装置からの指紋パターンの表示を取得し、この表示に基づいてユーザを認証し、この表示に基づいてユーザが認証された場合にのみ少なくとも一つのユーザ要求処理を実施する、ように構成される処理回路構成、を更に備える。電子装置は、例えば、携帯電話又はタブレットのような携帯用通信装置、コンピュータ、あるいは腕時計又はそれに類似する装置のような装着型電子部品であってもよい。

## 【0063】

本発明の第二の態様によれば、複数の感知素子を備える容量性指紋センサを用いて指の指紋パターンを感知する方法が提供される。各感知素子は、指による接触対象である保護誘電最上層と、最上層の下に配置される導電性感知構造と、電荷測定回路構成であって、感知構造に接続されて少なくとも第一の測定状態と第二の測定状態との間を連続的に遷移して測定シーケンスを実行し、指と感知構造との間の電位差の変化に起因して感知構造が帯びる電荷に生じる変化を示す出力信号を電荷測定回路構成から発信する、電荷測定回路構成と、を備える。この方法は、感知素子のそれぞれに対して、第一の事象を規定する第一の信号を供給する工程と、第一の信号を遅延させて、第一の事象に対して時間的に遅延する第二の事象を規定する第二の信号を供給する工程と、制御信号としての第二の信号を用いて、電荷測定回路構成を、第一の測定状態から第二の測定状態に遷移するように制御する工程と、を含む。

10

## 【0064】

遅延させる工程は、第一の信号に遅延素子を通過させる工程を有利に含んでもよい。

## 【0065】

種々の実施形態によれば、前記容量性指紋感知装置は、電荷測定装置の出力信号をサンプリングするサンプリング回路構成と、指と感知構造との間の電位差の変化をもたらす励起信号供給回路構成と、感知素子のそれぞれに接続され、感知素子のそれぞれからの出力信号に基づく指紋パターンの表示を供給するように構成される読み出し回路構成と、を備える。この方法は、感知素子を選択する選択信号を供給する工程と、選択信号を遅延させてリセット信号を供給する工程と、リセット信号を電荷測定回路構成に供給して、電荷測定回路構成をリセット状態に遷移させる工程と、リセット信号を遅延させて測定レディ信号を供給する工程と、測定レディ信号を電荷測定回路構成に供給してリセット状態を終了させ、測定レディ状態に遷移する工程と、測定レディ信号を遅延させて、第一のサンプリング制御信号を供給する工程と、第一のサンプリング制御信号をサンプリング回路構成に供給して、感知構造が帯びる電荷を示す第一の信号の第一のサンプリング時間でのサンプリングを始動させる工程と、第一のサンプリング制御信号を遅延させて第一の励起制御信号を供給する工程と、第一の励起制御信号を励起信号供給回路構成に供給して指と感知構造との間の電位差の変化を達成する工程と、第一の励起制御信号を遅延させて第二のサンプリング制御信号を供給する工程と、第二のサンプリング制御信号をサンプリング回路構成に供給して、感知構造が帯びる電荷を示す第二の信号の第二のサンプリング時間でのサンプリングを始動させる工程と、を含む。

20

30

## 【0066】

本発明のこれ以外の実施形態及び本発明の第二の態様から得られる効果は、本発明の第一の態様に対するこれまでの記載と大部分類似している。

## 【図面の簡単な説明】

## 【0067】

上記の態様をはじめとする本発明の態様を、本発明の例示的な実施形態を示す添付の図面を参照して、更に詳細に以下に説明する。

## 【0068】

【図1】図1は、本発明の例示的実施形態による指紋感知システムを備える携帯電話の概略図である。

40

50

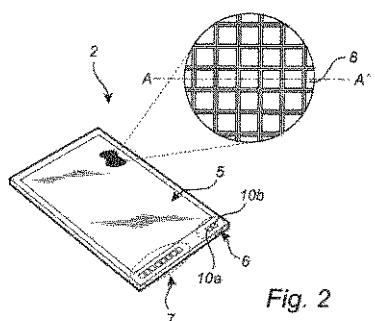

【図2】図2は、図1の指紋感知装置の概略図である。

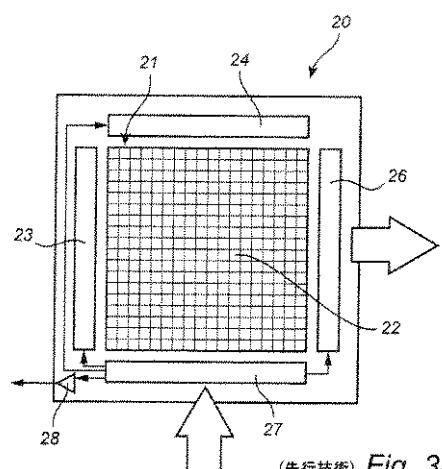

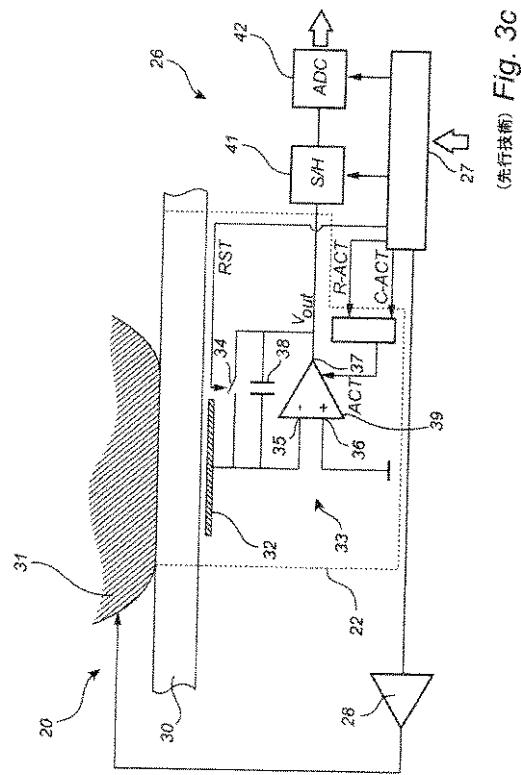

【図3a】図3a bは、従来の指紋感知装置の概略ブロック図である。

【図3b】図3a bは、従来の指紋感知装置の概略ブロック図である。

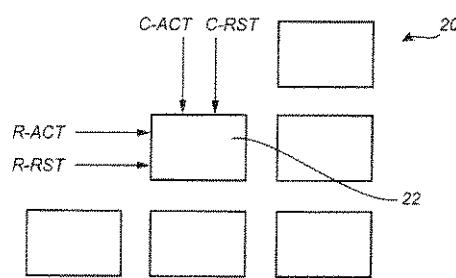

【図3c】図3a bの指紋感知装置の動作を概略的に図示する回路図である。

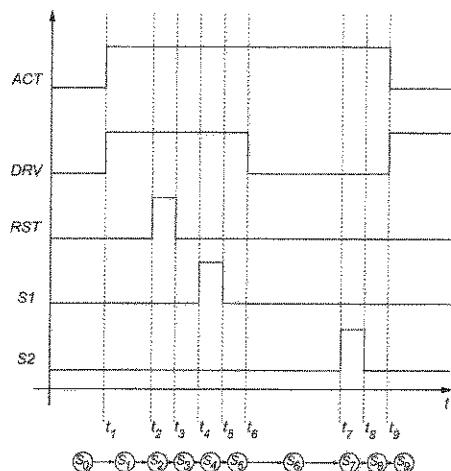

【図4】図4は、本発明の実施形態による容量性指紋感知装置のほか、図3cの従来の指紋感知装置のための測定シーケンスの例を図示するタイミング図である。

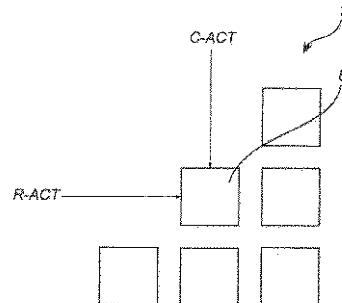

【図5a】図5a bは、本発明の実施形態による指紋感知装置に含まれる感知素子の概略図である。

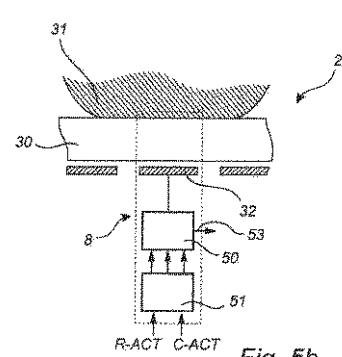

【図5b】図5a bは、本発明の実施形態による指紋感知装置に含まれる感知素子の概略図である。

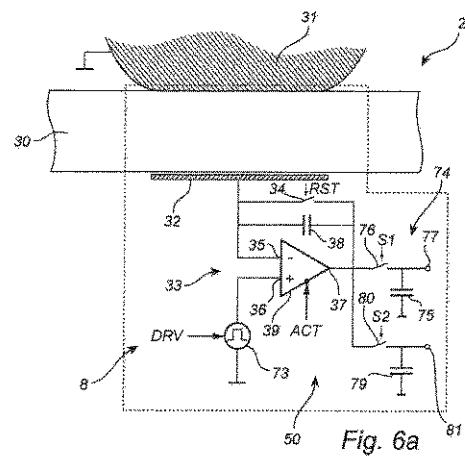

【図6a】電荷測定回路構成を含み、図5bの感知素子の一部を示す概略回路図である。

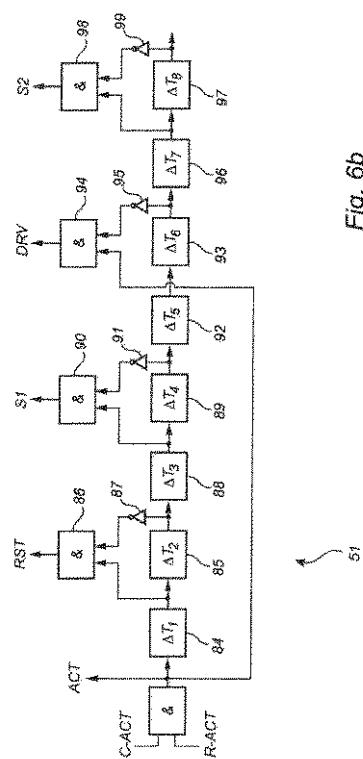

【図6b】図6aの電荷測定回路構成によって実施される測定シーケンスのタイミングを制御するタイミング回路の概略図である。

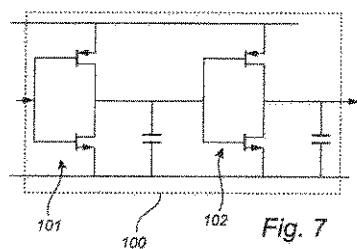

【図7】図6bのタイミング回路に含まれる遅延素子の回路図である。

【発明を実施するための形態】

【0069】

この詳細な説明では、本発明による指紋感知装置及び指紋感知方法の種々の実施形態が容量性指紋感知装置を参照して主に説明される。この容量性指紋感知装置では、各感知素子が、感知構造が帯びる電荷を測定する電荷増幅器を含む電荷測定回路構成と、励起信号又は駆動信号を感知構造に供給する励起信号供給回路構成と、電荷増幅器及び励起信号供給回路構成の制御動作のための複数の遅延素子を備えるタイミング回路構成と、を備える。更に、容量性指紋感知装置は、静止した指から指紋表示を獲得するように寸法が決められ構成されるタッチセンサとして図示される。

【0070】

なお、このことは、決して本発明の範囲を限定せず、例えば、指と感知構造との間の電位差の変化に起因して感知構造が帯びる電荷に生じる変化を測定する別の回路構成を含む容量性指紋感知装置を同じように良好に含む。更に、本発明は、この電位差の変化を感知素子の感知構造を駆動することによって達成する容量性指紋感知装置に限定されるものではない。代わりに、電位差は、励起信号を指に直接送るか、感知用に現時点で選択されているいくつかの感知素子以外の感知素子を介して送ることによって達成されてもよい。そのような他の感知素子は、駆動素子として機能するようにプログラムされてもよい。動く指から指紋表示を獲得するための、いわゆるスワイプセンサ（又はラインセンサ）のような他のセンサアレイ構成もまた、添付の請求の範囲で定義されるように、本発明の範囲内である。

【0071】

図1は、本発明の例示的実施形態による指紋感知装置の適用例を指紋感知装置2が組み込まれた携帯電話1の形態で概略的に示す。指紋感知装置2は、例えば、携帯電話1のロックを解除するため、及び／又は携帯電話を用いて実行される処理を認証するため等に用いられてもよい。

【0072】

図2は、図1の携帯電話1に含まれる指紋感知装置2を概略的に示す。図2に示すように、指紋感知装置2は、センサアレイ5、電源インターフェース6及び通信インターフェース7を備える。センサアレイ5は、多数の感知素子8（図面が乱雑になるのを避けるために、一つの感知素子のみに参照記号を付して示す）を備える。感知素子8はそれぞれ、感知素子8に含まれる感知構造（天板）とセンサアレイ5の上面に接触する指の表面との距離を感知するよう制御可能である。

【0073】

電源インターフェース6は、接着パッドとして示され、供給電圧V<sub>supply</sub>を指紋センサ2に接続する第一の接触パッド10a及び第二の接触パッド10bを備える。

【0074】

10

20

30

40

50

通信インターフェース 7 は、指紋センサ 2 の制御を可能にし、指紋センサ 2 から指紋データを取得する多数の接着パッドを備える。

【0075】

ここで、本発明の実施形態の理解を助けるために、既知の容量性指紋センサの例を図 3 a から図 3 c を参照して示す。

【0076】

図 3 a は、先行技術による容量性指紋センサ 20 の概略ブロック図である。図 3 a を参考すると、指紋センサ 20 は、容量性感知素子 22 のアレイ 21、行選択回路構成 23、列選択回路構成 24、読み出し回路構成 26、状態機械 27 及び励起信号増幅器 28 を備える。

10

【0077】

状態機械 27 は、状態機械 27 の方を指すブロック矢印 29 で図示されるように指令を受信し、受信した指令に基づいて、行選択回路構成 23、列選択回路構成 24 及び読み出し回路構成 26 を制御する。また、状態機械 27 は励起信号を供給して、励起信号増幅器 28 を介して駆動パルスを指に送る。

【0078】

図 3 b に概略的に示すように行選択回路構成 23 及び列選択回路構成 24 を制御して特定の感知素子 22 を選択した後、状態機械 27 はこのほか、タイミング制御信号を感知素子 22 に含まれる電荷測定回路構成と、感知素子 22 が供給した感知信号を読み出す読み出し回路構成と、に供給する。特に、状態機械 27 は、感知素子 22 及び読み出し回路構成 26 を制御して、複数の順次測定状態間の遷移を含む測定シーケンスを実行する。このことを図 3 c と、図 4 の例示タイミング図とを参照して以下に更に詳細に説明する。

20

【0079】

図 3 c には、図 3 a 及び図 3 b に示す指紋感知装置 20 の感知素子 22 のひとつの概略断面図の部分と、状態機械 27 による制御時の指紋感知装置 20 の動作を図示する機能ブロック図とがある。

【0080】

図 3 c を参照すると、感知素子 22 は、指 31 が触れる保護誘電最上層 30 (図 3 c は指紋の単一隆線の断面を概略的に示す)、導電性感知構造 (板) 32 及び電荷増幅器 33 を備える。電荷増幅器 33 は、負の入力 35、正の入力 36、出力 37、帰還コンデンサ 38 及び増幅器 39 を備える。

30

【0081】

負の入力 35 は感知構造 (板) 32 に接続され、正の入力 36 は接地され、出力 37 は読み出し回路構成 26 に接続される。

【0082】

帰還コンデンサ 38 は負の入力 35 と出力 37 との間に接続され、電荷増幅器 33 の増幅を規定する。感知素子 22 は、帰還コンデンサ 38 と並列なりセットスイッチ 34 を更に備える。

【0083】

感知素子 22 の外側では、図 3 c のブロック図は状態機械 27 と、励起信号増幅器 28 と、サンプルホールド回路 (S / H 回路) 41 及びアナログ・デジタル変換器 (ADC) 42 を備える読み出し回路構成 26 とを概略的に示す。

40

【0084】

指紋感知装置 20 の作動中に、状態機械 27 は、図 3 a から図 3 c のほか、図 4 を参照して以下に記載するように、電荷増幅器 33 及び読み出し回路構成 26 のタイミングを制御する。

【0085】

図 4 は、先行技術による指紋センサ 20 のほか、本発明の種々の実施形態による指紋センサ 2 に対する測定シーケンスの例を図示する。以下の記載から明らかなように、先行技術の指紋センサ 20 と本発明の実施形態による指紋センサとの主な差は、図 4 に図示する

50

測定シーケンス又は別の適切な測定シーケンスを更にかなり速く実行することができ、いつそう速い読み出し及び／又は各感知素子からの複数回の読み取りが可能になるため、測定性能が向上することになる点である。

【0086】

図4を参照すると、その図に示されるタイミング図は、上から下に向かって、起動信号A C T、駆動（励起）信号D R V、リセット信号R S T、第一のサンプリング制御信号S 1及び第二のサンプリング制御信号S 2を備える。

【0087】

タイミング図の下には、上記の測定シーケンスとともに形成する測定状態S<sub>0</sub>～S<sub>9</sub>のシーケンスが概略的に示される。

10

【0088】

図3a及び図3bの感知素子22の起動のために、感知素子22を示す行選択信号及び列選択信号が典型的に供給されてもよい。図4の簡素かつ概略的なタイミング図では、そのような選択信号を単一の起動信号A C Tによって表す。

【0089】

第一の時間t<sub>1</sub>では、感知素子22は起動信号A C Tの低から高への遷移によって起動される。これは、例えば、増幅器39の起動にまで及んでもよい。時間t<sub>1</sub>と実質的に同一の時点では、状態機械27によって励起信号増幅器28を介して指31に供給される駆動（励起）信号D R Vは低から高へ向かうように制御される。駆動信号D R Vは、例えば、少なくとも部分的に指紋センサ20を取り囲むベゼル（図示しない）などの指電極へのガルバニック接続を介して指に供給される。これとは別に、駆動信号D R Vは、例えば、現時点では感知状態ではないが駆動状態である一つまたはいくつかの感知素子に駆動信号を印加することによって指31に容量結合されてもよい。

20

【0090】

このため、時間t<sub>1</sub>では、測定シーケンスの「休止」状態S<sub>0</sub>から第一の測定状態S<sub>1</sub>への遷移がみられる。

【0091】

駆動信号D R Vを指31に印加すると、感知構造32が帯びる電荷が変化することになる。電荷増幅器からの出力信号が安定することが可能になるある程度の時間が経過したのち、時間t<sub>2</sub>にリセット信号R S Tを供給してリセットスイッチ34を閉じることにより、帰還コンデンサを放電し、電荷増幅器33の出力37での電位の基準を感知構造（板）32の電位とする。

30

【0092】

リセット信号の第一の立ち上がりを設けることにより、第一の測定状態S<sub>1</sub>から第二の測定状態S<sub>2</sub>（リセット状態）に遷移する。

【0093】

リセットスイッチ34は時間t<sub>3</sub>で解除（再度開放を許可）され、これにより、第三の測定状態S<sub>3</sub>（測定レディ状態）に遷移する。

【0094】

時間t<sub>4</sub>では、第四の測定状態S<sub>4</sub>への遷移が認められる。ここでは、第一のサンプリング制御信号S 1が低から高に変わり、電荷増幅器33の出力37での感知信号をサンプリングするようにサンプルホールド回路41を制御する。

40

【0095】

時間t<sub>5</sub>では、第五の測定状態S<sub>5</sub>への遷移が認められ、第一のサンプリング制御信号S 1が高から低に変わる。

【0096】

次に、時間t<sub>6</sub>では、駆動信号D R Vは高から低に変わり、指31と感知構造32との間の電位差を変化させる。これは、図4に概略的に示すように、第六の測定状態S<sub>6</sub>への遷移もある。

【0097】

50

時間  $t_7$  では、第七の測定状態  $S_7$  への遷移が認められる。ここでは、第二のサンプリング制御信号  $S_2$  は低から高に変わり、電荷増幅器 33 の出力 37 での感知信号を二度サンプリングするようにサンプルホールド回路 41 を制御する。

【0098】

時間  $t_8$  では、第八の測定状態  $S_8$  への遷移が認められ、第二のサンプリング制御信号  $S_2$  が高から低に変わる。

【0099】

最後に、時間  $t_9$  では、第九の測定状態  $S_9$  への遷移が認められる。ここでは、感知素子 22 は停止され、駆動信号 D R V が再度低から高に変わる。第九の測定状態  $S_9$  は初期の「休止」状態  $S_0$  と同一である。

10

【0100】

図 4 のタイミング図には図示しないが、測定シーケンスは、S / H 41 の出力を指 31 と感知構造 32 との間を結合する静電容量を表すデジタル値に変換するように A D C 42 を制御することを含んでもよい。

【0101】

図 3a 及び図 3b に示される先行技術の指紋感知システムでは、測定状態間の遷移のタイミングは大域状態機械によって感知素子 22 のそれぞれに対して制御される。状態遷移のタイミングは、例えば、信号線の感知素子 22 への経路指定に起因して、感知素子ごとにいくぶん異なるものであってもよい。例えば、リセット信号 R S T のタイミングは感知素子ごとに異なるものであってもよい。第二の時間  $t_2$  でのリセット状態  $S_2$  への遷移の前及び / 又は第三の時間  $t_3$  でのリセット状態  $S_2$  から測定レディ状態  $S_3$  への遷移の後に充分な時間があれば、測定は成功するであろう。しかし、測定周波数が上がることにより、測定周期に費やされる合計時間が減少するのであれば、大域的に制御された測定状態間の遷移のタイミングの変動が大きくなりすぎて、測定が影響を受けるという状況になる可能性がある。

20

【0102】

この状況は、更に以下に記載するように、改善することができ、更に高い周波数で実施される容量指紋測定を本発明の実施形態を通して提供する。

【0103】

図 5a 及び図 5b は、本発明の実施形態による容量性指紋感知装置に含まれる感知素子を概略的に図示する。

30

【0104】

まず、図 5a を参照すると、図 2 のセンサアレイ 5 からの一つの感知素子 8 がその周囲の素子とともに示される。図 3a から図 3c で先行技術の容量性指紋感知装置 20 を参照して上記に記載したように、一つ（または複数）の感知素子、その感知構造と指 31 との間の容量結合を感知するための感知素子は、行選択回路構成及び列選択回路構成からの起動信号を用いて選択されてもよい。そのような起動信号は R A C T 及び C A C T として図 5a に示される。また、このような起動信号を供給して上記の先行技術による指紋感知装置 20 の特定の感知素子 22 を選択する。その指紋感知装置 20 では、上記にも記載したように、追加タイミング制御信号が状態機械 27 から各感知素子 22 に送られる。図 3a から図 3c の指紋センサ 20 では、このような追加タイミング制御信号は、図 4 を参照して上記に記載されるように、リセット信号 R S T として、状態機械 27 から各感知素子に供給され、測定シーケンスの少なくとも一部の集中タイミング制御を提供する。

40

【0105】

下記に記載するように、本発明の実施形態による容量性指紋感知装置は、対照的に、各感知素子 8 又は感知素子群での測定シーケンスの状態遷移に対して局所的にタイミング制御信号を供給する。これには、例えば、上記のリセット制御信号 R S T のような制御信号の更に均一かつ正確なタイミングによるタイミング制御の向上という効果がある。

【0106】

図 5b を参照すると、容量性指紋感知装置 2 の各感知素子 8 は電荷測定回路構成 50 及

50

びタイミング回路構成 5 1 を備える。

【 0 1 0 7 】

電荷測定回路構成 5 0 は感知構造（板）3 2 に接続され、指 3 1 と感知構造 3 2 との間の電位差の変化に起因して感知構造 3 2 が帯びる電荷に生じる変化を測定する。この測定は、図 4 を参照して上記に説明したように、一連の測定状態を経る遷移を含む測定シーケンスを実行することによって実施される。電荷測定回路構成 5 0 は、感知構造 3 2 の電位と指 3 1 の電位との間の電位差の変化に起因して感知構造 3 2 が帯びる電荷に生じる変化を示す信号を供給する出力 5 3 を有する。

【 0 1 0 8 】

タイミング回路構成 5 1 は電荷測定回路構成 5 0 に接続されて、各種測定状態の少なくとも一つのタイミングを制御する。 10

【 0 1 0 9 】

タイミング回路構成は、図 5 b に概略的に図示するように、感知素子 8 の測定動作を始動させる一つ又はいくつかの制御信号を受信してもよい。例として、上記の行起動信号 R A C T 及び列起動信号 C A C T はタイミング回路構成 5 0 によって受信されてもよい。その後、タイミング回路構成 5 0 は、図 5 b の矢印によって概略的に示すように、種々のタイミング制御信号を独立して電荷測定回路構成 5 0 に供給してもよい。

【 0 1 1 0 】

図 4 からの測定状態表示 S<sub>0</sub> ~ S<sub>9</sub> を用いるここに提示した例では、感知素子 8 に含まれるタイミング回路構成 5 1 は、上に述べたように、図 4 に示す測定状態の少なくとも一つのタイミングを制御する。 20

【 0 1 1 1 】

測定シーケンスに含まれる測定状態の少なくとも一つのタイミングのこの局所的制御を経て、測定状態間の遷移のタイミングは、更に正確及び／又は均一に制御されることから、遷移間の時間が更に短縮され、ひいては測定周波数が上がるという効果がある。

【 0 1 1 2 】

ここで、図 5 b の電荷測定回路構成 5 0 の例示的実施形態を図 6 a を参照して説明する。

【 0 1 1 3 】

図 6 a の電荷測定回路構成 5 0 は、電荷増幅器 3 3 と、ここでは制御可能電源 7 3 によって表される励起信号供給回路構成と、サンプルホールド回路構成 7 4 とを備える。 30

【 0 1 1 4 】

図 3 b の感知素子 2 2 について上記で説明したように、図 6 a の電荷増幅器の電荷測定回路構成 5 0 は、負の入力 3 5 、正の入力 3 6 、出力 3 7 、帰還コンデンサ 3 8 及び増幅器 3 9 を備える。

【 0 1 1 5 】

負の入力 3 5 は感知構造（板）3 2 に接続され、出力 3 7 は感知素子 8 に含まれるサンプルホールド回路構成 7 4 に接続される。

【 0 1 1 6 】

帰還コンデンサ 3 8 は、負の入力 3 5 と出力 3 7 との間に接続され、電荷増幅器 3 3 の增幅を規定する。感知素子 2 2 は、帰還コンデンサ 3 8 と並列のリセットスイッチ 3 4 を更に備える。 40

【 0 1 1 7 】

正の入力 3 6 は、直接接地されるか別の基準電位に接続されるのではなく、制御可能電源 7 3 に接続される。

【 0 1 1 8 】

サンプルホールド回路構成 7 4 は、第一のサンプリングコンデンサ 7 5 、第一のサンプリングスイッチ 7 6 及び第一の出力 7 7 、第二のサンプリングコンデンサ 7 9 、第二のサンプリングスイッチ 8 0 及び第二の出力 8 1 を備える。

【 0 1 1 9 】

電荷測定回路構成 5 0 は、図 6 a の矢印によって概略的に示すように、上記の各種制御信号（起動信号 A C T、リセット信号 R S T、駆動制御信号 D R V、第一のサンプリング制御信号 S 1 及び第二のサンプリング制御信号 S 2）を用いて図 4 を参照して上記で説明した測定シーケンスを実行するように制御される。図 4 を参照して記載される測定シーケンスが実行されている場合、サンプルホールド回路 7 4 の第一の出力 7 7 と第二の出力 8 1 との間の電位差は、感知構造 3 2 と指 3 1 との間の容量結合を示すであろう。

#### 【 0 1 2 0 】

なお、図 6 a の回路図は、本発明の実施形態の説明を容易にするために簡略化されている。例として、感知素子 8 の出力でのレベルシフトが省略されている。もっとも、レベルシフトの実行は当業者にとって容易なことである。

10

#### 【 0 1 2 1 】

電荷増幅器は、負の入力 3 5 での電位が正の入力 3 6 での電位に実質的に追従（いわゆる仮想接地）するように構成されるため、感知構造（板）3 2 での電位は、容量性指紋感知装置 2 を備える電子装置の基準電位と比較して時間的に変化し、制御可能電源 7 3 の制御を経て正の入力 3 6 に供給される電位に実質的に追従するであろう。

#### 【 0 1 2 2 】

指 3 1 の電位は、（例えば、電子装置とユーザの手との間の電気的接続を介して）電子装置の基準電位に対して実質的に一定であるため、電荷増幅器 3 3 の正の入力 3 6 での電位の時間による変動は、指 3 1 と感知構造 3 2 との間の電位差の変化をもたらし、ひいては指 3 1 と感知構造（板）3 2 との間の容量結合を示す感知構造 3 2 が帯びる電荷の変化をもたらすであろう。

20

#### 【 0 1 2 3 】

指 3 1 の指紋パターンを示す指紋パターン信号の指紋センサ 2 からの出力を促進するために、サンプルホールド回路 7 4 の出力間の電圧 V S H は、図 3 a から図 3 c に概略的に示すようなセンサアレイの外側に設けてもよいアナログ・デジタル変換器を用いてデジタル形式に変換してもよい。

#### 【 0 1 2 4 】

ここで、図 6 b を参照して、図 5 b のタイミング回路 5 1 の構成例を説明する。図 6 b に示すように、タイミング回路 5 1 は、第一の A N D ゲート 8 3、第一の遅延素子 8 4、第二の遅延素子 8 5、第二の A N D ゲート 8 6、第一のインバータ 8 7、第三の遅延素子 8 8、第四の遅延素子 8 9、第三の A N D ゲート 9 0、第二のインバータ 9 1、第五の遅延素子 9 2、第六の遅延素子 9 3、第四の A N D ゲート 9 4、第三のインバータ 9 5、第七の遅延素子 9 6、第八の遅延素子 9 7、第五の A N D ゲート 9 8 及び第四のインバータ 9 9 を備える。

30

#### 【 0 1 2 5 】

図 5 1 に概略的に示すように、行起動信号 R A C T 及び列起動信号 C A C T は第一の論理 A N D ゲート 8 3 に入力される。また、図 6 a を参照すると、第一の A N D ゲート 8 3 の出力は、上記の起動信号 A C T として電荷測定回路構成 5 0 の増幅器 3 9 に供給され、第一の遅延素子 8 4 の入力に供給され、第四の A N D ゲート 9 4 に入力される。第一の遅延素子 8 4 の出力は、第二の A N D ゲート 8 6 に供給され、第二の遅延素子 8 5 の入力に供給される。第二の遅延素子 8 5 の出力は第一のインバータ 8 7 を介して第二の A N D ゲート 8 6 に供給され、第三の遅延素子 8 8 の入力に供給される。第三の遅延素子 8 8 の出力は第三の A N D ゲート 9 0 の入力に供給され、第四の遅延素子 8 9 の入力に供給される。第四の遅延素子 8 9 の出力は第二のインバータ 9 1 を介して第三の A N D ゲート 9 0 に供給され、第五の遅延素子 9 2 の入力に供給される。第五の遅延素子 9 2 の出力は第六の遅延素子 9 3 の入力に供給される。第六の遅延素子 9 3 の出力は第三のインバータ 9 5 を介して第四の A N D ゲート 9 4 に供給され、第七の遅延素子 9 6 の入力に供給される。第七の遅延素子 9 6 の出力は第八の遅延素子 9 7 の入力及び第五の A N D ゲート 9 8 の入力に供給される。最後に、第八の遅延素子 9 7 の出力は第四のインバータ 9 9 を介して第五の A N D ゲート 9 8 の入力に供給される。

40

50

## 【0126】

起動信号 R A C T も列起動信号 C A C T もともに高に設定することによって図 6 a の電荷測定回路構成 50 及び図 6 b のタイミング回路 51 を備える感知素子 8 を選択する場合、感知素子 8 に対する起動信号 A C T は（図 4 を参照する時間  $t_1$  では）高になる。第一の A N D ゲート 83 からの出力は、第一の遅延素子 84 を通過し、第一の時間遅延  $t_1$  だけ遅延して、起動信号 A C T の第一の遅延バージョンを第二の A N D ゲート 86 に供給する。

## 【0127】

第一の時間遅延  $t_1$  は図 4 の  $t_2 - t_1$  に相当し、第一の測定状態  $S_1$  の持続時間を規定する。

10

## 【0128】

また、第一の遅延素子 84 からの出力は、第二の遅延素子 85 の入力に供給され、遅延して起動信号 A C T の第二の遅延バージョンを供給する。

## 【0129】

起動信号 A C T の第二の遅延バージョンは、第一のインバータ 87 を介して第二の A N D ゲート 86 の入力に供給され、第二の A N D ゲート 86 の出力にリセット制御信号 R S T をもたらす。

## 【0130】

第二の時間遅延  $t_2$  は、図 4 の  $t_3 - t_2$  に相当し、第二の測定状態  $S_2$ （ここではリセット制御信号 R S T は高）の持続時間を規定する。

20

## 【0131】

タイミング回路 51 の残りの部分は同一の方法で動作し、このとき遅延素子は図 4 のタイミング図に示される制御信号が達成されるように構成される。

## 【0132】

このため、第三の時間遅延  $t_3$  は図 4 の  $t_4 - t_3$  に相当し、第三の測定状態  $S_3$  の持続時間を規定する。第四の時間遅延  $t_4$  は図 4 の  $t_5 - t_4$  に相当し、第四の測定状態  $S_4$  などの持続時間を規定する。

## 【0133】

なお、タイミング回路 51 は、遅延素子と、感知素子に含まれる電荷測定回路構成の測定状態のタイミングを局地的に制御する論理ゲートとの併用の動作原理を図示する簡略化された例である。タイミング回路構成は、実際の実装状態によっては、信号整形及び／又はタイミングなどのための追加または他の回路構成を備えてよい。当業者は、本明細書の記載に基づいて、不当な負担なく、タイミング回路の適切な実装を設計することができるであろう。

30

## 【0134】

なお、特定の実施形態によっては、更に少ないか追加のタイミング制御信号をタイミング回路構成 51 から電荷測定回路構成 50 に独立して供給してもよい。

## 【0135】

図 7 は、図 6 a のタイミング回路構成 51 に含まれる可能性のある遅延素子 100 の説明に役立つ実例を示す。

40

## 【0136】

遅延素子 100 は、第一の C M O S インバータ 101 と、直列に接続される第二の C M O S インバータ 102 とを備える。この遅延素子の時間遅延は、遅延素子 100 に含まれる構成要素の寸法設定に左右されるため、遅延素子の設計時に設定できるであろう。遅延時間を更にかなり長くすることが望まれるのであれば、更に C M O S インバータを直列に連結できる。

## 【0137】

当業者は、本発明が決して上記の好適な実施形態に限定されるものではないことを理解している。それどころか、添付請求項に記載の範囲内で多くの修正及び変更が可能である。

50

## 【0138】

請求の範囲では、「備える」という文言は他の要素又は工程を除外するものではなく、不定冠詞「a」又は「an」は複数を除外するものではない。単一のプロセッサをはじめとする装置が、請求項に記載のいくつかの特徴の各種機能を発揮する可能性がある。単に特定の手段が相互に異なる従属項に記載されているというだけでは、このような手段の組み合わせを有利に用いることができないことを示すことにはならない。コンピュータプログラムを、他のハードウェアとともに、あるいはその一部として供給される光学記憶媒体又は固体媒体のような適切な媒体に保存／分配してもよいが、ほかにも、インターネットあるいは有線又は無線電気通信システムを介してというような他の形態で分配してもよい。請求項に記載のいかなる参照符号も請求の範囲を限定するものと解釈すべきではない。

10

【図1】

Fig. 1

【図2】

Fig. 2

【図3a】

(先行技術) Fig. 3a

【図 3 b】

(先行技術) Fig. 3b

【図 3 c】

(先行技術) Fig. 3c

【図 4】

Fig. 4

【図 5 a】

Fig. 5a

【図 5 b】

Fig. 5b

【図 6 a】

【図 6 b】

【図 7】

---

フロントページの続き

(72)発明者 フランク リーデイク

オランダ国, 2613 テーゼット デルフト, フーゴ デ フロートストラート 156

審査官 九鬼 一慶

(56)参考文献 特表2008-502989 (JP, A)

特開平09-178407 (JP, A)

特開2000-213908 (JP, A)

米国特許第05953441 (US, A)

特開2003-148906 (JP, A)

特開2003-028607 (JP, A)

特開平09-251530 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G01B 7/28

G06T 1/00