(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

24 February 2011 (24.02.2011)

(10) International Publication Number

**WO 2011/022040 A1**

(51) International Patent Classification:

*G06F 17/30* (2006.01)   *G06F 9/455* (2006.01)

*G06F 21/00* (2006.01)

(74) Agent: **WAGNER, Robyn**; Van Pelt, Yi & James LLP,

10050 N. Foothill Blvd., Suite 200, Cupertino, CA 95014

(US).

(21) International Application Number:

PCT/US2010/002214

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(22) International Filing Date:

11 August 2010 (11.08.2010)

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

61/234,604      17 August 2009 (17.08.2009)      US

12/580,891      16 October 2009 (16.10.2009)      US

61/257,043      2 November 2009 (02.11.2009)      US

61/286,369      14 December 2009 (14.12.2009)      US

12/714,547      1 March 2010 (01.03.2010)      US

(71) Applicant (for all designated States except US):

**FATSKUNK, INC.** [US/US]; 590 Mariposa Ave.,

Mountain View, CA 94041 (US).

Published:

— with international search report (Art. 21(3))

(72) Inventors: **JAKOBSSON, Bjorn Markus**; 590 Mariposa Ave., Mountain View, CA 94041 (US). **JOHANSSON, Karl-Anders, R.**; 590 Mariposa Ave., Mountain View, CA 94041 (US).

(54) Title: AUDITING A DEVICE

**FIG. 1**

(57) **Abstract:** The auditing of a device that includes a physical memory is disclosed. One or more hardware parameters that correspond to a hardware configuration is received. Initialization information is also received. The physical memory is selectively read and at least one result is determined. The result is provided to a verifier.

## AUDITING A DEVICE

### CROSS REFERENCE TO OTHER APPLICATIONS

[0001] This application claims priority to U.S. Provisional Patent Application No. 61/234,604 entitled DETECTION OF MALWARE filed August 17, 2009, U.S. Provisional Patent Application No. 61/257,043 entitled AUDITING A DEVICE filed November 2, 2009, and U.S. Provisional Patent Application No. 61/286,369 entitled AUDITING A DEVICE filed December 14, 2009, each of which is incorporated herein, in its entirety, by reference for all purposes.

### BACKGROUND OF THE INVENTION

[0002] Existing techniques for detecting the presence of unauthorized programs are typically resource-intensive. For example, they generally require constant updates (e.g., of blacklists) and periodic or continuous scans for problems. The situation is exacerbated if the device being protected by such techniques has limited resources, such as limited memory, or by being powered by a battery. As one example, a device with limited resources may not be able to store definitions for detecting all known unauthorized programs. As another example, scanning for unauthorized programs is typically a power-intensive act, and may quickly deplete the battery of a battery-powered device. In some environments, a central authority is used to facilitate the discovery of unauthorized programs. One drawback of this approach is that it typically requires that the device being protected compile detailed logs of device activities. Generating such logs is resource-intensive (e.g., requiring large amounts of disk storage; processing power to assemble the log data; and the bandwidth to deliver the log data to the central authority) and can also present privacy problems.

[0003] Existing techniques for detecting the presence of unauthorized programs are also generally vulnerable to attempts by such programs to cause incorrect reporting. For example, a rootkit can “listen in” to requests by applications to the operating system, and may modify these requests and their responses. If an application requests information about what processes are running, a malicious rootkit application can avoid detection by removing information about itself from the report that is returned by the operating system.

[0004] Existing techniques for screening against the installation or execution of unauthorized programs are also known to be vulnerable to new instances of malware that may not immediately be detectable due to a lack of information about their structure and functionality. Therefore, and irrespective of the resources available to the device, if the unauthorized program is sufficiently sophisticated and/or has not previously been encountered, it can evade detection and cause undetected harm. And, if the unauthorized program has intentionally been installed by the user to bypass detection (e.g., to facilitate software piracy), traditional techniques may fail to locate the unauthorized program, or any other unauthorized activities.

### **BRIEF DESCRIPTION OF THE DRAWINGS**

[0005] Various embodiments of the invention are disclosed in the following detailed description and the accompanying drawings.

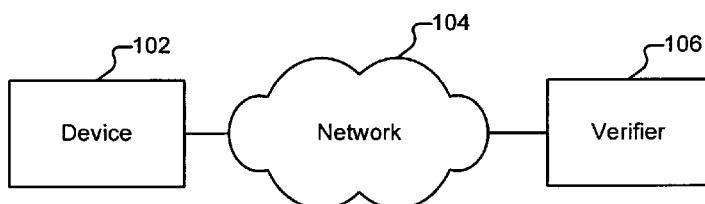

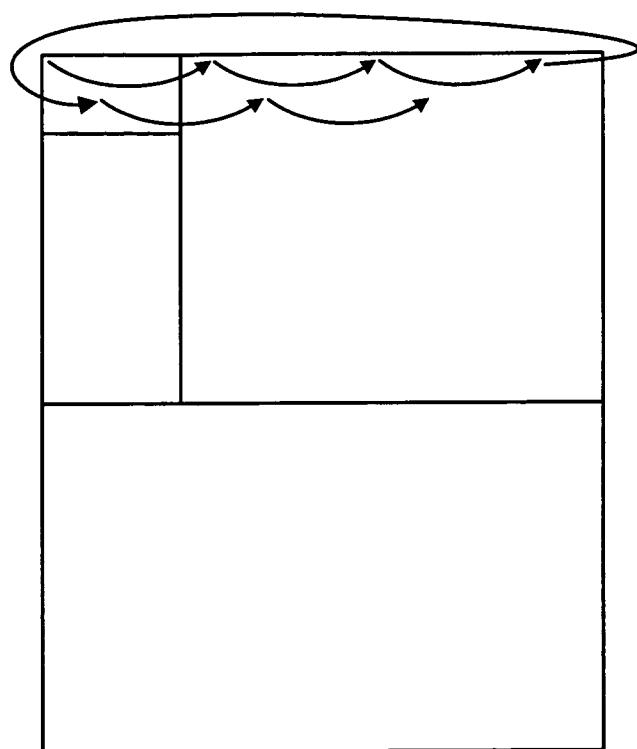

[0006] Figure 1 illustrates an embodiment of an environment in which device auditing is provided.

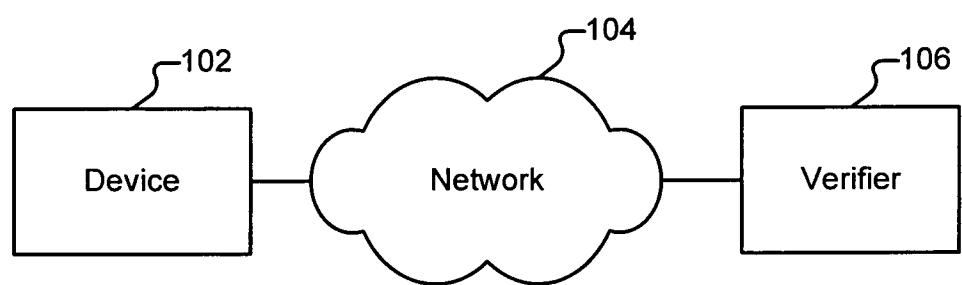

[0007] Figure 2 illustrates an embodiment of a device.

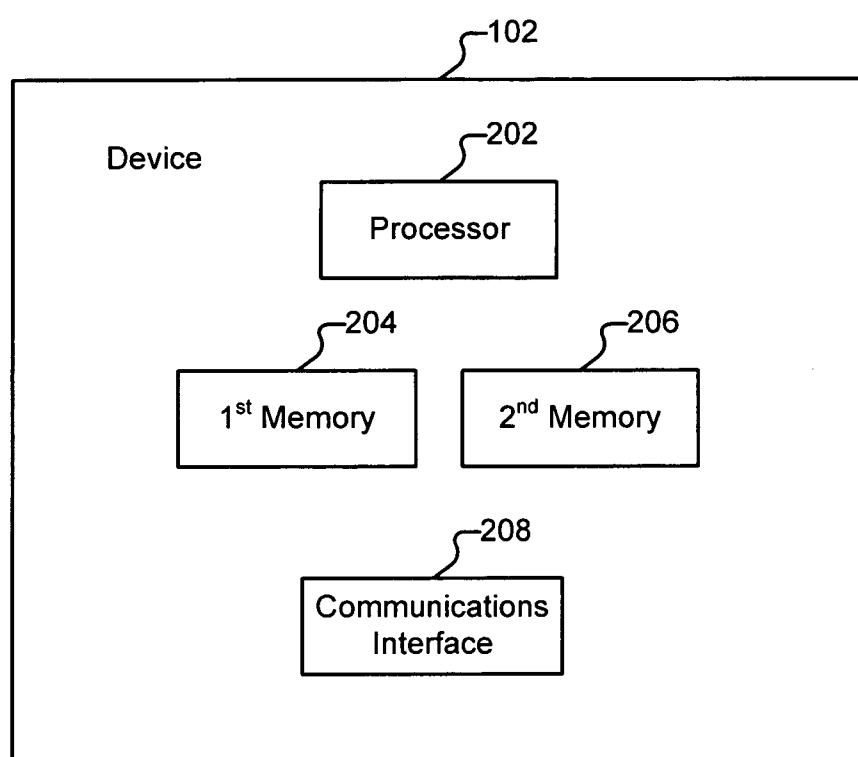

[0008] Figure 3 illustrates an embodiment of a process for performing a device audit.

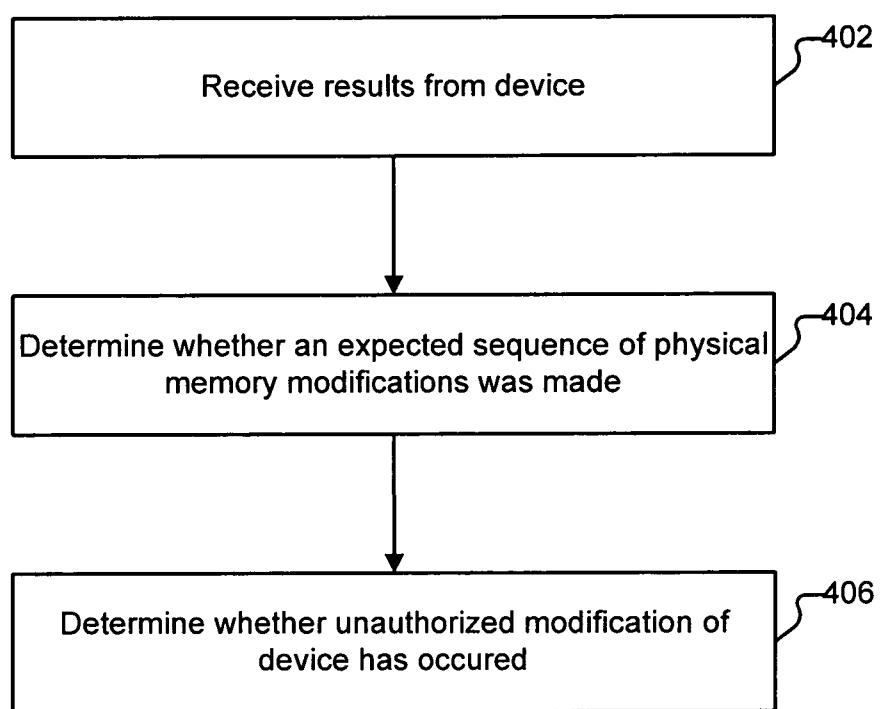

[0009] Figure 4 illustrates an embodiment of a process for performing a device audit.

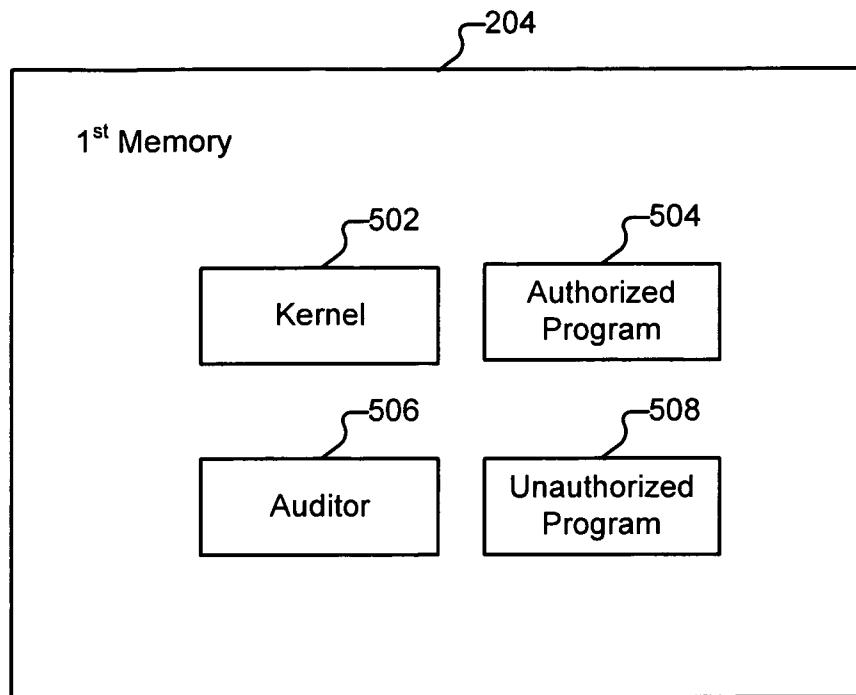

[0010] Figure 5A illustrates a representation of a memory prior to an execution of the process shown in Figure 3.

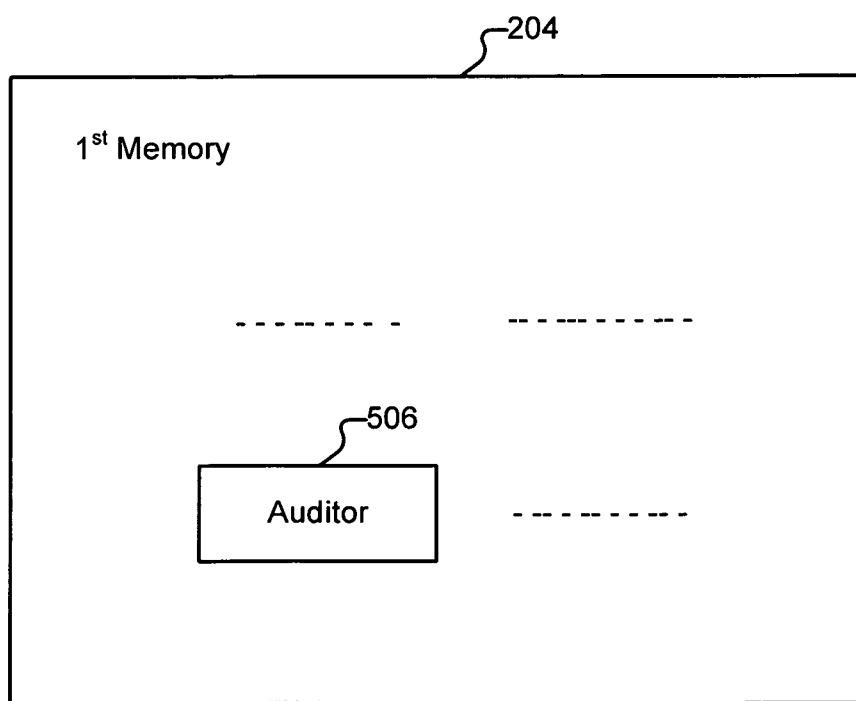

[0011] Figure 5B illustrates a representation of a memory while the process shown in Figure 3 is occurring.

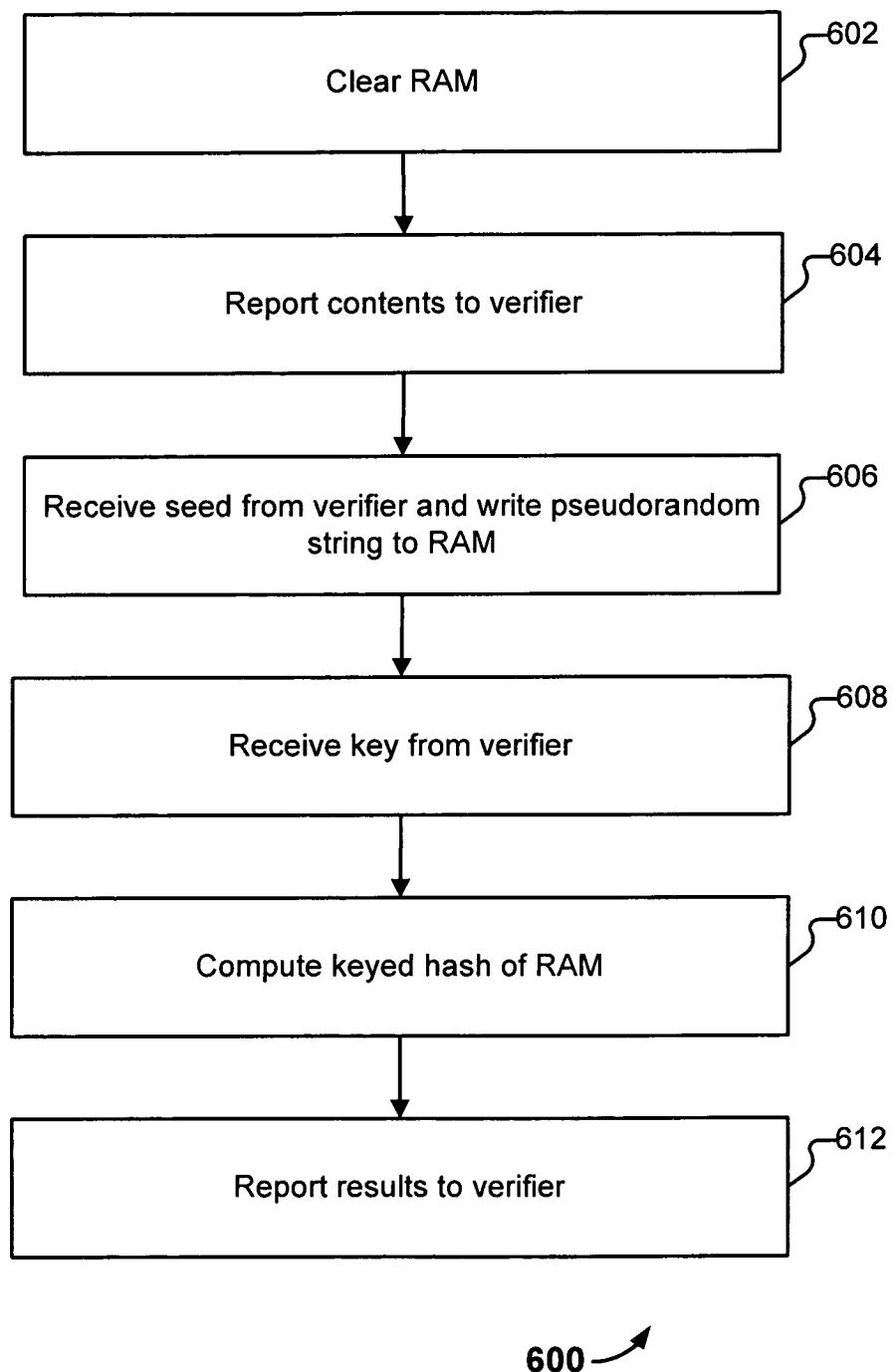

[0012] Figure 6 illustrates an embodiment of a process for performing a device audit.

[0013] Figure 7 illustrates an example of pseudo code for use in conjunction with auditing a device.

[0014] Figure 8 illustrates an example of a process for performing a device audit.

[0015] Figure 9 illustrates an embodiment of an environment in which device auditing is provided.

[0016] Figure 10 illustrates an embodiment of a portion of a device.

[0017] Figure 11 illustrates an embodiment of a process for performing a device audit.

[0018] Figure 12 illustrates a portion of memory being read in accordance with a step.

[0019] Figure 13 illustrates an embodiment of an implementation of a process for selectively reading memory.

[0020] Figure 14 illustrates an embodiment of an implementation of a process for timing a portion of a device audit.

### **DETAILED DESCRIPTION**

[0021] The invention can be implemented in numerous ways, including as a process; an apparatus; a system; a composition of matter; a computer program product embodied on a computer readable storage medium; and/or a processor, such as a processor configured to execute instructions stored on and/or provided by a memory coupled to the processor. In this specification, these implementations, or any other form that the invention may take, may be referred to as techniques. In general, the order of the steps of disclosed processes may be altered within the scope of the invention. Unless stated otherwise, a component such as a processor or a memory described as being configured to perform a task may be implemented as a general component that is temporarily configured to perform the task at a given time or a specific component that is manufactured to perform the task. As used herein, the term 'processor' refers to one or more devices, circuits, and/or processing cores configured to process data, such as computer program instructions.

[0022] A detailed description of one or more embodiments of the invention is provided below along with accompanying figures that illustrate the principles of the invention. The invention is described in connection with such embodiments, but the invention is not limited to any embodiment. The scope of the invention is limited only by the claims and the invention encompasses numerous alternatives, modifications and equivalents. Numerous specific details are set forth in the following description in order to provide a

thorough understanding of the invention. These details are provided for the purpose of example and the invention may be practiced according to the claims without some or all of these specific details. For the purpose of clarity, technical material that is known in the technical fields related to the invention has not been described in detail so that the invention is not unnecessarily obscured.

**[0023]** Figure 1 illustrates an embodiment of an environment in which device auditing is provided. In the example shown, device 102 is a cellular telephone. Device 102 is in communication (e.g. via network 104) with verifier 106. In Figure 1, device 102 communicates with verifier 106 via a 3G network. Verifier 106 is under the control of a carrier, such as a provider of telephony service to device 102. Verifier 106 includes a database of hardware configuration information, including an entry corresponding to device 102 and the amount of RAM included on device 102.

**[0024]** As will be explained in more detail below, device 102 can be audited such that any evasive programs (e.g., malware) present on the device can be detected and/or removed. In some embodiments this is accomplished through the undertaking of a sequence of modifications to physical memory included on device 102. Results associated with the performance of the memory modifications are verified by verifier 106. Once device 102 is determined to be free of influence of such evasive programs, additional scans can be performed, which are also described in more detail below. For example, in addition to detecting malware (e.g., software installed without a user's knowledge and/or consent), the techniques described herein can detect "jailbreaking" actions (e.g., privilege escalations) taken by the user, such as to circumvent digital rights management installed by a carrier or hardware manufacturer.

**[0025]** A variety of devices can be used in conjunction with the techniques described herein. For example, in some embodiments device 102 is a video game console. The video game console is configured to communicate with a verifier under the control of the manufacturer of the game console via the Internet (104). If the owner of device 102 makes an unauthorized change to device 102 (e.g., by using a modification chip), verifier 106 will be able to detect the modification accordingly.

**[0026]** Other examples of devices that can be used in conjunction with the techniques described herein include desktop computers, notebook computers, netbooks, personal digital

assistants, video playback devices (e.g. televisions, DVD players, portable video players), routers, access points, settop boxes, medical devices, and virtually any other device that includes a processor and a memory.

[0027] In various embodiments, verifier 106 is controlled by a user of device 102, instead of by a separate entity. For example, a desktop computer owned by the user of device 102 can be configured to provide verification services to device 102. In that scenario, device 102 can be configured to communicate with the verifier via a local network. Device 102 can also be configured to communicate with verifier 106 directly (e.g., via a dedicated cable) and network 104 is omitted as applicable.

[0028] In some embodiments a verifier is collocated with or otherwise directly coupled to device 102. For example, a subscriber identity module (“SIM”) card inserted into a cellular phone can be configured to provide the functionality of verifier 106 to the cellular phone. As another example, the functionality of verifier 106 can be integrated into a power cord used to charge a cellular phone. In such embodiments, an external verifier can either be omitted, or can be used in addition to the verification services provided by the collocated/coupled verifier. As one example, suppose device 102 is a personal video player with integrated WiFi capabilities. A power cord used to charge the device can be configured to provide verification services to the device each time it is charged. In addition, if the WiFi radio is active, the device can be configured to communicate periodically with a verifier provided by the manufacturer of the device. As another example, a verifier 106 can be included on a USB device that is periodically inserted by a user into a laptop 102. In addition, whenever a user of laptop 102 attempts to conduct banking transactions with an online bank, the bank can also provide verification services to the laptop 102 prior to granting access to the user’s account. As yet another example, a network operator or service provider can require a user to have his or her machine audited before he or she is allowed on the network or allowed to access a service. User can also initiate an audit, for example, after realizing that he or she has been exposed to a potentially risky situation. One way a user can initiate an audit is to select a menu option on the device. Another example way is for the user to request an audit from verifier 106 (e.g., by submitting an online request through a web form).

[0029] Figure 2 illustrates an embodiment of a device. In the example shown, device 102 includes a processor 202, a first memory 204, a second memory 206, and a

communications interface 208. As one example, device 102 includes a 528 Mhz ARM processor (202), 128MB of RAM (204), a micro SD card slot into which a user has inserted a 1GB micro SD card (206), and a 3G modem (208). Memory 204 is also referred to herein as “fast” memory. Memory 206 is also referred to herein as “slow” memory. However, memories 204 and 206 need not be different speeds. Other components may also be included in device 102, such as a GPS receiver (not shown). Elements, such as second memory 206, may also be omitted as applicable. One may refer to RAM that can contain active programs as fast, and consider RAM that can only store data as slow.

[0030] Using the auditing techniques described herein, the absence of active processes in fast memory can be verified. And, after that verification has been completed, all memory (e.g., both fast and slow) can be scanned to identify, classify, report and potentially modify the contents of the fast and slow memory, or portions thereof. The distinction between fast and slow memory can be made in a variety ways. For example, on a device with RAM, flash memory and a hard drive, it is possible to treat only the RAM as fast memory and flash memory and the hard drive as slow memory. It is also possible to treat both the RAM and the flash memories as fast memory and the hard drive as slow memory. It is also possible to consider all memory physically located on a given device as being fast, and all external memory accessible (or potentially accessible) by the device as slow. The turnaround time to communicate to external components will cause such external accesses to be slower, irrespective of the type and actual local access speed of the external memory. Depending of what types of memory are treated as fast vs. slow, the selection of parameters would be done accordingly.

[0031] As will be described in more detail below, the existence of unauthorized modifications to device 102 can be detected by configuring device 102 to run a series of modifications to memory 204 and examining the results. If for example, the time it takes to perform the modifications exceeds a tolerance of a predetermined length of time, or if a result determined in conjunction with the modifications does not match an expected result, the presence of an evasive program may be indicated. In various embodiments, the memory modifications are performed across all memory on a device (e.g. both memory 204 and memory 206), instead of being run only on fast memory such as memory 204.

[0032] Figure 3 illustrates an embodiment of a process for performing a device audit. In various embodiments, the process shown in Figure 3 is performed by device 102. The

process shown in Figure 3 can be initiated in a variety of ways. For example, the process can be initiated every time the user charges the device (e.g., by configuring the device to initiate the process when it detects a power supply). The process can also be initiated in response to the occurrence of a particularly large or unusual transaction, in response to a concern that the user is at risk (e.g., in response to the carrier receiving notification that a new vulnerability has been released by a nefarious individual), in response to the elapsing of a certain amount of time, etc. Additional examples of events that can trigger the initiation of the process shown in Figure 3 include an attempt by the user of device 102 to make a payment or otherwise engage in a financial transaction, an authentication attempt (e.g., the user of the device attempting to access to a bank account), and an access request being performed (e.g., a request for the download of a movie to the device).

**[0033]** The process begins at 302 when one or more hardware parameters that correspond to a hardware configuration is received. Example hardware parameters include the amount and the speed of fast memory 204. For example, in the case of the device shown in Figure 2, the hardware parameters would include “amount=128M” and “speed= 300Mhz.” Additional parameters that can be used include the number of cores, the type of bus, etc.

**[0034]** The hardware parameters can be received in a variety of ways. As one example, the SIM of a cellular phone can be configured to detect the amount and speed of installed memory. As another example, if a proprietary cable is used to connect device 102 to a power source (or to a computer or other device), the parameters may be known (and thus “received”) by virtue of the cable only working in conjunction with a device having a specific amount and speed of memory. As yet another example, a serial number of a device may indicate the amount and speed of fast memory 204 installed on a device. In various embodiments, the user (or a representative thereof) is requested to input memory parameters in a web form or a configuration file. Assumptions can also be made about the likely memory configuration of the device and a benchmarking program can be run to confirm whether the assumption is likely to be correct.

**[0035]** At 304, a sequence of modifications to a physical memory is performed. Examples of ways in which such modifications can be performed are described in more detail below. In some embodiments the sequence of modifications to be performed is determined by the verifier. The set of modifications to be made can be provided to the device in a variety of ways. For example, the sequence can be constructed on the device based on a seed value.

The sequence can be pre-loaded onto the device at time of manufacture, at time of delivery to the supplier or carrier, or at the time of purchase. It can also be loaded by user choice or by a service provider at any time after purchase (e.g., as an over-the-update or as a firmware update), or when needed to perform an audit. The parameterization can be performed by the manufacturer or supplier or carrier, given known specifications. It can also be performed through a lookup, e.g., of serial number, by a user or service provider. The parameters can be associated with the model or device name. If the device is reconfigured, e.g., by replacement or addition of components, then these new components can carry information about the new or additional parameterization. The components can also carry the entire set of instructions, instead of just the parameters. Alternatively, the serial numbers, names, or types of components can indicate the needed change in parameters. If it is believed that the client device is secure at the time of installation of the algorithm or a new component, then the client machine can also inquire what components are installed (as is typically done as a system is booted up), and set the parameters accordingly.

**[0036]** In various embodiments, device manufacturers offer to preload non-activated auditing software at no cost, and later request payment to activate auditing services (and/or the additional scanning services described in more detail below. The auditing software can subsequently be activated by carriers, on request by end users or service providers. The carrier collects payment for the activation and optionally forwards portions of the payment to the handset manufacturer, providers of auditing software, providers of additional scanning software (e.g., antivirus detection services), and any other parties involved in the transaction.

**[0037]** At 306, one or more results of the portion of the process performed at 304 are reported to a verifier. In some embodiments results are provided to proxy 906, which timestamps the results and provides them to the verifier. As will be described in conjunction with Figure 5, in some embodiments multiple iterations of modifications to the memory and communications with the verifier are made, and the processes shown in Figures 3 and 4 are adapted accordingly.

**[0038]** Figure 4 illustrates an embodiment of a process for performing a device audit. In various embodiments, the process shown in Figure 4 is performed by verifier 106. As explained above, in some embodiments the process shown in Figure 4 is performed by an entity separate from device 102 (such as on a verifier controlled by a carrier). In other

embodiments the process is performed by a verifier located on or otherwise physically coupled to device 102.

**[0039]** The process begins at 402 when results are received. For example, when device 102 reports results at 306, those results are received by a verifier at 402.

**[0040]** At 404, a determination is made as to whether the results received at 404 indicate that an expected sequence of physical modifications was made. Verifier 106 is configured with information such as the amount of time the execution of a sequence of memory modifications should take on device 106 (assuming no authorized modifications have been made). In some embodiments verifier 106 is also be configured to store additional information, such as seed values and the results of computations performed by device 102.

**[0041]** If the expected sequence of physical memory modifications is determined to have been made (e.g., device 106 performed the sequence of memory modifications), it is concluded (406) that no unauthorized modifications have been made to the device. And, any evasive processes that might previously have been active on device 102 have been neutralized. If the expected sequence of physical memory modifications is determined to have not been made (e.g., because the amount of time to perform the sequence is off, or computed results are incorrect), it is concluded (406) that an unauthorized modification has been made to the device. (e.g., that an evasive process is present on the device and is attempting to avoid detection). In various embodiments, error correcting codes are used to avoid errors due to network noise. Message-authentication codes and other authentication techniques can be used to avoid active tampering with contents. Encryption techniques can be used to obfuscate contents and make it impossible for eavesdroppers to determine the plaintext messages being transmitted.

**[0042]** Figure 5A illustrates a representation of a memory prior to an execution of the process shown in Figure 3. In the example shown, kernel 502, authorized program 504, unauthorized program (e.g., a malware agent) 508, and an auditor program 506 are loaded in RAM. Typically, in order to remain resident on a device, an evasive program needs to do one of two things. It must either remain active in RAM (or swap space), or it must modify a legitimate program, data, or configuration of the device to allow the malware agent to gain control after a scan has been performed. As will be explained in more detail below, using the techniques described herein, the presence of the malware agent can be detected, irrespective

of the techniques it employs to evade detection. In addition, using the techniques described herein, the presence of the malware agent can be detected even if auditor 506 is loaded after malware agent 504.

**[0043]** Figure 5B illustrates a representation of a memory while the process shown in Figure 3 is occurring. As will be explained in more detail below, auditor 506 is configured to clear memory RAM (and any swap space) except for the space used by auditor 506. In various embodiments, a minimalistic set of other services is also permitted to occupy RAM. For example, if device 102 supports 3G communications, the area of RAM occupied by a 3G driver/module is not cleared, so that auditor 506 can use the 3G modem to communicate with verifier 106. As another example, in some embodiments a microkernel is permitted to occupy a portion of RAM while auditor 506 clears the remainder of the RAM.

**[0044]** Figure 6 illustrates an embodiment of a process for auditing a device. The process begins at 602 when an auditor process running on device such as device 102 clears all portions of memory 204 (and any swap space) that is not claimed for use by the auditor. In some embodiments, this includes unloading the kernel, various drivers, and all other processes. In various embodiments, the unclaimed memory space is overwritten by a sequence instead of being cleared (e.g., with zeros). One example sequence is a pseudo-random sequence that is combined with the original memory contents, such as by using the XOR operation. This allows the unclaimed memory space to later be reconstituted by the repeated combination with a pseudo-random sequence that complements or equals the previously used pseudo-random sequence. The unclaimed memory space can also be overwritten with contents in a way that clears it, but which does not correspond to the typical erasing operation of the device. For example, it is possible to clear unclaimed memory by writing a sequence of 01010101 to it, or any other appropriate sequence.

**[0045]** In some embodiments, the auditor code comprises two components: a loader and a variable algorithm segment. The task of the loader is to load algorithm segments from non-RAM storage (e.g., something other than memory 204), and hand over control to the loaded algorithm segment. After an algorithm segment has completed, it hands back the control to the loader.

[0046] At 604, contents of memory 204 are reported to verifier 106. In some embodiments the entire contents are reported. In other embodiments, only descriptions of changes since the last audit are communicated.

[0047] At 606, the device receives a cryptographic seed from the verifier. The seed is expanded to a pseudorandom string and the string is written to RAM. An example technique for writing a string to RAM in accordance with portion 606 of process 600 is provided below.

[0048] At 608, the device receives a cryptographic key from the verifier.

[0049] At 610, the device uses the received key to compute a keyed hash of the entire contents of the device's RAM.

[0050] At 612, the device reports the resulting value to the verifier. Verifier 106 evaluates the results, e.g., according to the process shown in Figure 4.

[0051] In various embodiments, device 102 reports state information from computations at 606 and 610 at time intervals set by verifier 106. The use of such intervals provides assurance that the computations performed by device 102 are being performed within memory 204 (and not, e.g. a portion of memory 206).

[0052] Device 102 obtains updates, from verifier 106, of the seed and respective key on an as-needed basis. The use of updates provides assurance that device 102 is not outsourcing computation to an external fast resource. For example, in order to outsource the computation, an evasive program would have to forward the seed and key updates to the external device, which would introduce a measurable delay.

[0053] Verifier 106 verifies that both the final function value and partial results are correct and are reported by device 102 to the verifier within acceptable time bounds. An example technique for evaluating the time it takes an auditor to perform its tasks is provided below. As mentioned above, in some embodiments verifier 106 is external to device 102 and is operated by a party other than the owner of the device. In other embodiments, verifier 106 is under the control of the user of device 102.

[0054] After the process shown in Figure 6 has been completed, auditor 506 can restore the contents of the device, whether fully or partially, and return control to previously active processes or to a process performing further scans of memory contents. The contents

of the fast memory can be restored if they were swapped out to slow memory prior to the execution of the timed computation, or if the original contents were combined with a string, the latter allowing a similar combination to be performed, thereby recovering the previous state. It is also possible to restart the device by loading a “starting” state. It is further possible to first hand over control to a process that scans, reviews, reports and modifies the contents of memory, or any subset of these operations (described in more detail below). The reporting can be presented to verifier 106, or to a third party, such as one in charge of managing the processing of memory contents. In the latter case, verifier 106 may be in charge of assuring that there is no active malicious process, and the second verifier could be in charge of processing the memory of the device to determine whether it complies with a particular policy, which may be related to malware detection, digital rights management, or another policy identifying what device memory contents are desirable.

**[0055]        Example Adversarial Strategies**

**[0056]**        In order for an evasive program to avoid being detected, e.g., during portion 604 of the process shown in Figure 6, it must be active in RAM, either as a unique process (504) or as part of a corrupted version of auditor 506. The following are six example ways in which an evasive program such as malware agent 504 can attempt to remain active:

**[0057]        Strategy 1: Outsource storage.**

**[0058]**        The malware agent can stay active in RAM and attempt to remain undetected by causing auditor 106 to not clear the appropriate space (e.g., at 602) and rely on non-RAM storage or external storage to store the corresponding portion of the pseudo-random string generated at 606. The computation at 610 would then be modified to use the outsourced storage instead of the space where the malware agent resides.

**[0059]        Strategy 2: Compute missing data.**

**[0060]**        Instead of outsourcing storage of portions of the pseudo-random string, the malware agent can store a modified representation of the string (e.g., a compressed version, or a version that is missing portions), and reconstitute relevant portions of the string as they are needed during the computation of the keyed hash at 610. Since the malware agent has the seed from which the pseudo-random string is generated, it can use this – or later states of the pseudo-random generator – to regenerate required portions of data.

[0061] **Strategy 3: Outsource computation.**

[0062] The malware agent can forward relevant data to an external device (assuming the necessary communications infrastructure, such as a WiFi connection is still enabled). The external device receives data from device 102 and computes the values needed to report to verifier 106, feeding these values to the malware agent on device 102.

[0063] **Strategy 4: Modify detection code.**

[0064] The malware agent can attempt to replace the code of auditor 506 with modified code. This replacement code may be designed to suppress reports of compromised memory contents, or contain a hook for malware code to be loaded after the audit completes. The malware agent can attempt to incorporate such changes to auditor 506 without taking up more space by swapping out or compressing portions of the auditor code and loading or unpacking it again as it is needed.

[0065] **Filling Fast Memory**

[0066] This section describes an example technique that can be used in conjunction with portion 606 of the process shown in Figure 6.

[0067] Figure 7 illustrates an example of pseudo code for use in conjunction with auditing a device. In the example shown, the subroutine *get\_permutation* returns a vector indicating a random permutation of *number\_blocks* items, ranging from 0 to *number\_blocks*–1, where *number\_blocks* is the number of portions of size equal to a flash block that the RAM comprises, minus those needed by the auditor. The subroutine *next\_string\_chunk* returns a pseudo-randomly generated chunk of bits; the term *chunk* is used to refer to the amount of data that can be sent on the memory bus. As one example, for an Android G1 phone, a chunk is 32 bits.

[0068] Both *get\_permutation* and *next\_string\_chunk* use the most recently provided seed as input. The pseudo-random string can be computed as  $segment_i \leftarrow hash(segment_{i-1})$ , i.e., in a way that *cannot* be computed using random access. One example is a function based on iterated application of the hash function, given the non-homomorphic properties of hash functions. A variety of hash functions may be used. One example is MD6 in 512-bit mode.

[0069] The constant *rounds* is the number of times a pseudo-random chunk is XORed into the contents of a cell, using the function *modify\_memory*. The choice of *rounds* controls the amount of work an adversary has to perform to carry out the second adversarial strategy (computing missing data), while also incurring an increasing cost to the honest execution of the algorithm for large values. In the example shown, *rounds* = 2, which results in a noticeably greater cost to the adversary than *rounds* = 1, since the value of each cell will come to depend on two other cells. This can confound memory management strategies of an adversary. In the example shown, *chunks\_per\_block* is the number of chunks contained in a flash block, equaling 32768 (=128kB/ 32 bits) for an example G1 phone, while *number\_blocks* = 1024 (= 128 MB / 128kB).

[0070] The function *modify\_memory(pos, string)* XORs the contents of position *pos* with the value *string*, where *pos* = 0 describes the first chunk of RAM to be operated on, and *pos* = *number\_blocks* × *chunks\_per\_block* - 1 is the last chunk.

[0071] The memory access structure described in conjunction with Figure 7 causes accesses to individual pages of randomly ordered blocks, if forced to use flash (e.g., memory 206) instead of RAM (204). This will cause the flash to be cleared with an overwhelming probability, and the pseudo-random access order prevents the adversary from scheduling the memory accesses to avoid this drawback. The cost of a flash-bound computation in comparison to the RAM-bound alternative available to the honest execution of the algorithm is noticeably more time consuming.

[0072] In some embodiments, one hash function application is used to generate several invocations of *next\_string\_chunk*. This reduces the computational burden associated with the auditing process, which emphasizes the contribution of the memory access in terms of the time to perform the task.

[0073] In various embodiments the input to the hash function is a constant number of previous outputs; this complicates storage for a malware agent wishing to reconstitute the state of a given portion of the pseudo-random generator, and is thus useful to further frustrate any attempt to use strategy 2 (compute missing data).

[0074] **Performing Timing**

[0075] This section describes an example technique that can be used for timing the execution of auditing tasks. For example, in some embodiments the technique is employed by verifier 106 as described in conjunction with the text corresponding to Figure 6.

[0076] Verifier 106 is configured to time the execution of portions 606 and 610 of the process shown in Figure 6, e.g., to identify attempts to outsource storage; compute missing data; and outsource computation.

[0077] In some embodiments verifier 106 is configured to obtain state information from device 102 at frequent intervals (e.g., that are set by verifier 106). One example of state information is the memory contents of the memory chunk that was last updated, which vouches for that device 102 has reached this stage of the computation. Verifier 106 sends update requests to device 102 at regular intervals. In some embodiments the update requests correspond to updates of the state of the pseudo-random generator used to compute the output of the subroutine *next\_string\_chunk*. If the output of the subroutine *next\_string\_chunk* is generated by selecting an unused portion from an already generated pseudo-random string, the string can be cleared at the same time, thus forcing the new seed to affect the state immediately.

[0078] An evasive program employing adversarial strategy 3 (i.e., outsourcing computation), must transmit the update of the pseudo-random string to the external device that performs the computation, after which the external device has to compute the resulting next value to be reported by device 102 to verifier 106 and transmit this to the evasive program. This incurs a round-trip delay. If the round-trip delay exceeds the time between timing checkpoints, the cheating will be detected. Here, an assumption is made that seeds and keys, along with other status information, is communicated securely between the client device and the verifier. Various cryptographic techniques can be used to achieve this.

[0079] In various embodiments, the device-specific time between checkpoints is chosen so that there is not enough time to outsource computation using communications equipment (e.g., WiFi) included on device 102, pessimistically assuming congestion-free environments.

[0080] The execution time of *modify\_memory* is determined by the parameter selections described above and what hash function to use to compute *next\_string\_chunk*. For

example, the MD6 hash function can be configured to different output sizes, from 224 to 512 bits. As explained above, in some embodiments a 512-bit version is used. The time per invocation of *modify\_memory* is noticeably less than the time between checkpoints determined above.

**[0081] Examples of Detecting Various Evasive Programs**

**[0082]** The following section provides examples of how evasive programs employing the various strategies described above can be detected using the techniques described herein.

**[0083] Defending against adversarial strategy 1 – outsource storage.**

**[0084]** Assume an empty SD card has been inserted into device 102. The corresponding write speed could reach up to 5MB/s. The size of a block processed by *modify\_memory* as described above is chosen, in this example, to be 128kB. The time to write the data to the SD card would be 25ms. In comparison, suppose RAM on device 102 has a write speed of 100MB/s. The corresponding write time would be 1.25ms. The additional delay can be readily detected. And, if multiple accesses to the SD card are made between two checkpoints, the additional delay will be even more readily detected.

**[0085] Defending against adversarial strategy 2 – compute missing data.**

**[0086]** As mentioned above, the pseudo-random string can be computed in a way that cannot be computed using random access. To compute the value of a certain output, the corresponding input needs to be computed from stored data. Since *rounds* > 1, the data stored in RAM is not this needed state, but a combination of the states of the two or more rounds. The state needs to be explicitly stored (in RAM) by the malware agent, as part of its code space, and the needed state computed from this. This forces the malware agent to compute at least (and in fact, *much* more) than *rounds* × *number\_blocks* × *chunks\_per\_block* hash operations during the execution of portion 610 of the process shown in Figure 6, in addition to the computation it needs to perform to “legitimate” computation. For the selected parameter choices, that is more than 100 million hash operations. Given an approximate time of 10  $\mu$ s for computing a hash function invocation, this is about 1000 s, which is approximately 3 orders of magnitude more than the expected and can be detected accordingly.

[0087] A sample proof corresponding to the defense against strategy 2 will now be provided. Assume that an evasive program resides in memory 204 and takes up at least portions of some  $c$  32-bit chunks for itself and its variables. A pessimistic assumption can be made that *all* of this space can effectively be used to store variables, which is not possible, but which gives a lower bound on the amount of work that the malware has to perform to remain undetected. In reality, its effort is greater as not all  $c$  chunks can be used for storage, but some are needed to store its code.

[0088] For each one of the  $c$  hits to RAM chunks that do not contain the values needed to compute the function, the malware agent has to compute the expected contents. It is assumed in this example that the original contents – before the RAM-filling was performed – were zero. If this is not so, the effort of the malware agent would be greater, so making this assumption establishes a lower bound on the effort of the malware agent. To compute the expected updates to this cell that would have been performed by the RAM-filling algorithm, the malware agent needs to compute the values for all the *rounds* passes on the memory chunk in question. The values XORed in to memory come from a pseudo-random sequence. And, it is only possible to reconstitute the state of the chain in the cell where it is missing by computing the value *next\_string\_chunk* from a value that is stored by the malware agent in part of the  $c$  chunks of storage. It is assumed that the variables are stored solely in RAM, or the malware agent needs to *also* succeed with strategy 1 (outsource storage).

[0089] As explained above, the pseudo-random generator cannot be computed using a random-access approach. It is the case that  $L = 16$  chunks is needed to store a state, given a chunk size of 32 bits and a state size (= MD6 output size) of 512 bits. The malware agent has to recompute the sequence of hash function invocations from a position of RAM associated with this state (which does not have to be where the malware agent *stored* this state.)

[0090] Given the random permutation over cells during the writing of the memory (the order which cannot be anticipated by the malware agent), the expected length of the run to the string position corresponding to the stored state is at least  $rounds \times n / (c / L)$ , where  $n = number\_blocks \times chunks\_per\_block$  corresponds to the number of chunks that RAM consist of,  $rounds \times n$  is the length of the pseudo-random string, and where  $c / L$  are the number of pseudo-random states stored by the malware agent. Thus, for each hit to a “bad” cell, the malware agent has to perform an expected  $rounds \times n \times L / c$  invocations of

*next\_string\_chunk*, which corresponds to  $rounds \times n \times c$ . There are  $c$  such hits, not counting hits to “bad” cells that occur as the malware agent attempts to compute one of the expected states. Therefore, the malware agent has to perform at least  $rounds \times n$  hash operations to compute the contents of the  $c$  bad blocks from the stored contents. The approximate time to do this (according to an example implementation) is at least between 100,000-1,000,000 times slower than the legitimate client which indicates that any attempt to compute missing data will be detected.

[0091] If the computation of the chain causes the access to a cell that has been used to store a value for another pass of the computation, then this causes another hit to be incurred. It would happen with an approximate probability

$(c - c / rounds) / c \times c / number\_blocks = (c - c / number\_blocks) / number\_blocks \approx c / number\_blocks$  for each memory access, and therefore, with approximate probability

$1 - (1 - c / number\_blocks)^{number\_blocks \times rounds^2 / c}$  for a given first bad cell hit, as described above. A rough approximation of this quantity is  $1 - e^{-rounds^2}$ . For  $rounds = 2$ , this is more than 98% probability. This additional cost would increase with increasing values of  $c$ . An adversary would therefore do best to make  $c$  small.

[0092] In the following, assume that the adversary uses  $c = L = 16$  cells only, all 16 to store one value. With this configuration, the adversary would fail to compute the value (unless using external memory) in those situations where the chain leads in a direction that does not make it possible to compute the value corresponding to the “programcell” from the value in the “storage cell”. For  $rounds = 2$ , this failure occurs with probability 75%. In the remaining 25% of the cases, the adversary would simply be slowed down. (To always succeed to compute the value, the adversary needs to store at least  $round = 2$  values, each 512 bits long.

[0093] **Defending against adversarial strategy 3 – outsource computation.**

[0094] In some embodiments the time between checkpoints is chosen so that there is no time to outsource computation using the communications equipment on the device. The time between checkpoints can be chosen by verifier 106 in a way that makes this immediately detectable. A strategy involving outsourcing of computation will fail, as the roundtrip has to be completed between two checkpoints for the right value to be provided by the adversary.

This is independent of the speed of communication between the client device and the verifying party.

**[0095] Defending against adversarial strategy 4 – modify detection code.**

**[0096]** Suppose unauthorized program 508 corrupts the execution of some steps (e.g., as described in conjunction with Figure 6), then willingly loads legitimate code and removes itself. Such an adversary could potentially corrupt portions 602 and 604 of the process, but will not be able to corrupt portion 606. Specifically, it needs to corrupt portion 602 of the process (clearing swap space and RAM) in order to maintain active. It can then cause a misreporting of state at 604. However, this will be detected when the keyed hash of the memory contents are computed (610). This is both due to the assumed collision-freeness of the hash function used, and the fact that the key is not disclosed to the device until 608. Portion 608 cannot be corrupted without being active during 606, which in turn would cause detection, as described above. And, the evasive program will be unable to compute the correct values to be reported at 612 without executing portion 606 of the process shown in Figure 6.

**[0097]** Combinations of the four adversarial strategies will also fail, since each of them will be detected and combinations of them do not change the underlying device-specific limitations.

**[0098] Additional Processing**

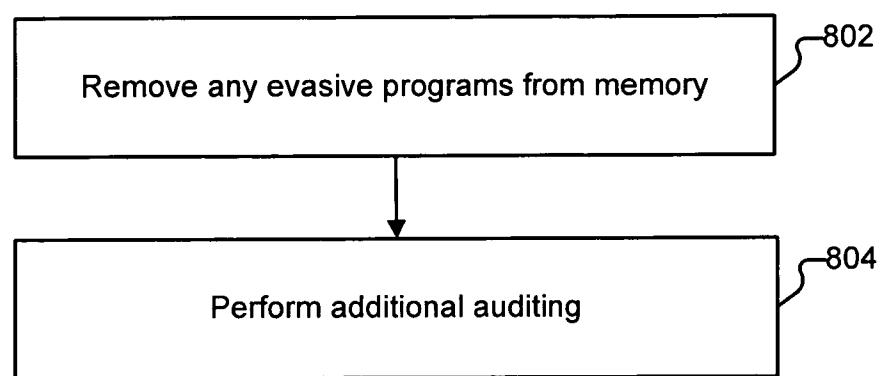

**[0099]** Figure 8 illustrates an example of a process for performing a device audit. In various embodiments, the auditing processes described above form one phase (802) of a two (or more) phase process. Once the techniques described above have been employed with respect to a device such as device 102, an assumption can be made that no evasive software is active in the RAM of the device. Arbitrary additional processing can then be performed on the device (804). Examples of additional processing that can be performed are described below.

**[00100] Example: Malware**

**[00101]** After the processing of 802 is performed, at 804, device 102 performs traditional antivirus software to identify known bad software, such as may be stored in

memory 206. At 804 device 102 can also be configured to report the entire contents of memory 206 or portions of memory to verifier 106 or to another device.

**[00102] Example: Jailbreaking**

**[00103]** After the processing of 802 is performed, at 804 device 102 determines whether its operating system loader has a particular hash, and/or otherwise determines whether the operating system loader has been altered away from a desirable state.

**[00104] Example: Phone Unlocking**

**[00105]** After the processing of 802 is performed, at 804 device 102 determines whether its operating system loader has been altered and also determines whether any information associated with a service provider has been altered.

**[00106] Example: Software Piracy**

**[00107]** After the processing of 802 is performed, at 804 device 102 determines whether any software included in memory 206 has been modified from an expected configuration, ascertains any associated serial numbers for the software, and/or otherwise determines whether the included software is being used in an unauthorized/unlicensed manner. In some embodiments device 102 reports the contents of memory 206 or portions thereof to verifier 106.

**[00108] Example: Media Piracy**

**[00109]** Suppose that media files (e.g., music, video, or image files) are customized using watermarks during distribution, and that these watermarks are cryptographically authenticated, e.g., using a MAC or digital signature. At 804 it can be determined which files present on device 102 have legitimate watermarks, and whether these contain valid authenticators. The determination can be made either locally to device 102 or centrally (e.g., on verifier 106).

**[00110]** In various embodiments, applications (such as a music player installed on device 102) record usage and other data (forming a log of activity) and associate the information with the appropriate media (e.g., song file). The logs can be read by the verifier 106 at 804.

**[00111] Example: Chains of Custody / Usage Logs**

[00112] Suppose an application (or data file) has an associated log file that is used to record transactions. One example is a log file that records the occurrence of financial transactions, including stored-value information. The legitimacy of changes made to the log file can be verified as follows. First, the processing of 802 is performed. Then, at 804 a determination can be made (e.g., by comparing hashes of program images) as to whether or not the application (or data file) has been altered, and thus, whether the log file is genuine.

[00113] One approach to the processing performed at 804 in this example is as follows: First, memory 206 is scanned and a list of applications and data files associated with the applications is created. Next, a list of descriptors for the applications and data files is determined. An example of a descriptor is a hash of the file, along with the name and type of file, and an identifier stating what string sequence(s) it matched. Next, a second list of any descriptions of applications or data that is not already reported on in the first list is made. The description created here may include all or parts of the code for an application, or of a description of what type of input files it processes and output files it produces. The second list is transmitted to an external party, such as verifier 106, where it is verified. The second list can also be processed locally using any policy obtained from a policy verification server.

[00114] The outcome of the verification can be used to affect the permissions to the applications and data, and can be used to control how external servers interact with the device, including whether it is granted access to network resources (such as the Internet, 3G networks, corporate networks, etc.). As another example, the software allowed to run on the device can be restricted, and notify the user of lack of compliance, attempt to remove or repair or otherwise modify files, etc.

**[00115] Example: Parental Control Filters and other Monitoring Features**

[00116] After the processing of 802 is performed, in various embodiments, additional middleware is installed that can be configured to log (and/or block) various events associated with the device. Examples include:

[00117] (a) determining what photos were generated on the device and later transmitted out (e.g., to prevent “sexting”).

[00118] (b) determining (e.g., based on device activity and GPS changes) whether the device was used (e.g., for texting or watching video clips) while travelling at a speed greater than 20 miles per hour.

[00119] (c) determining (e.g., based on installation activity) whether alternative applications (such as a second instant messaging program in addition to a default program) has been installed, and then creating a log file for the alternative application.

[00120] (d) determining (e.g., based on browser history information) what URLs a user has visited including which URLs were manually navigated to and which URLs were referred to in other HTML documents that were accessed. One benefit of this logging is to identify whether a person is likely to have fallen victim to phishing; has visited a web site known to distribute unwanted content, including malware; and whether the device is likely to be involved in click-fraud. Such abuse is possible to achieve without infection of the device itself, e.g., by use of JavaScript, cascading style sheets, and/or other related scripting languages.

[00121] **Example: Additional Applications**

[00122] In addition to the above examples, yet more uses of the techniques described herein are possible. For example, device auditing can be used in vehicular black-boxes for metering usage, purposes of insurance, tariffs, taxes, tolls, etc. - both to identify malware and intentional tampering.

[00123] The device auditing technique can be included as a component in other applications, allowing these applications to temporarily suspend themselves to perform the scan, and later be given control again, in the known clean state.

[00124] As yet another example, the techniques can be used in medical devices, to determine that they are free from infection, correctly configured and maintained, and in order to audit usage in special cases when it becomes valuable to know who had access to data and equipment. The devices in question may log usage information at all time, in a way that preloaded application cannot interfere with; the audit process would include a memory-printing scan to assert that the preloaded applications are still in a good state, and that no conflicting applications or configurations are present.

[00125] Finally, the techniques can be used for detection of malware in situations where there is no need to remediate, or where that is not the primary goal. One such context is for online games, to detect the absence of modules to cheat in the games.

[00126] **Preserving Privacy**

[00127] In some embodiments descriptions of all state (e.g., the contents of memory 204) is communicated to the verifier 106. However, some data should preferably not be transferred off device 102, such as private keys and non-executable private data. In the following section, techniques preserving the privacy of such data are described.

[00128] Assume that a first random number is called  $x$ , and that it is selected from some space of possible values,  $1 \dots \text{max}_x$ . It is possible that  $x$  encodes malware apart from providing an input to the auditing process for which it was intended. A legitimate program computes a one-way function value  $y$  from the input data  $x$  and some system parameters, which is called  $(g_1, n_1)$ . One example way of doing this is by computing  $y = g_1^x \text{ modulo } n_1$ , where  $g_1$  generates a large subgroup of  $G_{n1}$ .

[00129] Let the program then compute a second one-way function value  $z$  from the value  $y$  and some system parameters, which is called  $(g_2, n_2)$ . One example way of doing this is by computing  $z = g_2^y \text{ modulo } n_2$ , where  $g_2$  generates a large subgroup of  $G_{n2}$ .

[00130] Next, it is assumed that the client machine proves (e.g., using a zero-knowledge proof) that there is a value  $x$  such that  $z = g_2^{g_1^x \text{ modulo } n_1} \text{ modulo } n_2$ , where  $(z, g_1, g_2, n_1, n_2)$  are known by the verifier, but  $(z, x)$  are not. The device (the “prover”) then erases the value  $x$  but stores  $(y, z)$  and the parameters  $(g_1, g_2, n_1, n_2)$ .

[00131] At later times, the device has to prove that the value  $y$  that it stores, but which is secret, corresponds to the value  $z$ . (Here,  $z$  can be stored on device 102, but can also be stored by verifier 106.) One example proof that can be used is a zero-knowledge proof.

[00132] If the second proof concludes and verifier 106 accepts it, then the verifier knows that the unknown value  $z$  that the client stores is of a format that cannot be used to hide a significant amount of data of value to a malware agent.

[00133] Here,  $z$  can be used to encrypt some other data, which is referred to as  $m$ , and whose ciphertext is referred to as  $c$ . Thus,  $c = E_z(m)$  for an encryption algorithm  $E$ . Assuming

symmetric encryption,  $m=D_z(c)$  for some decryption algorithm  $D$ . The device contents can be verified, but  $m$  remains unknown by the party receiving  $c$ . This party would not know  $z$ , but only that  $z$  is of some acceptable form that cannot hide large amounts of malware data. Since the auditing process described herein allows the verifier party to be assured that only legitimate programs exist in the RAM of the client device, it can be known that the programs – using the secret value  $z$  – can access  $m$ , given  $c$ . However, the verifier cannot.

[00134] Since it is known that the accessing program is legitimate, it is also known that  $m$  will only be accessed in an approved manner. For example, if  $m$  is data and not code, then it is the case that the accessing program will not try to execute the data.

[00135] **Using A Pseudo Random String Generator**

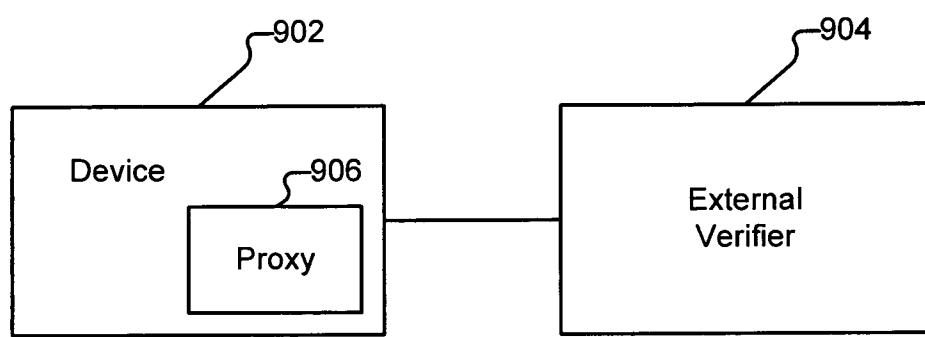

[00136] Figure 9 illustrates an embodiment of an environment in which device auditing is provided. In the example shown, device 902 includes, in addition to the components illustrated in Figure 2, a SIM configured to serve as a proxy (906) for external verifier 904. As will be described in more detail below, a monolith kernel stored in the instruction cache of device 102 (where it fits in its entirety) swaps out all other processes (excepting any processes it chooses to except) when it is activated, and performs an auditing process. The monolith kernel has an associated working space that is located in the data cache (and registers). The cache is typically implemented using RAM, and is considered as being part of it herein. As used herein, “free RAM” is the portion of RAM which ought to be free after all applications – including the regular kernel – have been swapped out. In some embodiments, “free RAM” is defined as the segment of RAM that is not taken up by a set of approved routines and data. For example, the regular kernel may be an approved routine, as may common and whitelisted applications. Moreover, approved data may correspond to data that is known by the external verifier, and may be of any format, as long as it is whitelisted (i.e., believed to be safe.). In such cases, the approved programs need not be swapped out to secondary storage (as described in more detail below) but may instead remain resident during the memory reading portion of the audit (e.g., 1108).

[00137] In some embodiments the monolith kernel corresponds to a program  $F_\varepsilon$ , parameterized for a known execution environment  $\varepsilon$ . As explained above, the execution environment corresponds to a hardware configuration of the device. Executing  $F_\varepsilon$  on input  $x$  produces a sequence of outputs  $F_{\varepsilon i}(F_\varepsilon, x)$ , each within a time  $t_i(F_\varepsilon, x)$  from the start of the

execution and produces an ending state  $s(F_\epsilon, x)$ . In this example,  $x \in X$ , where  $X$  is the set of all legitimate inputs.

[00138] Proxy 906 is used to reduce latency variance from the device, and in various embodiments is implemented as a tethered cellular phone, a cell phone tower, etc., instead of or in addition to a SIM. In some embodiments external verifier 904 performs an initial computation (described in more detail below) and communicates (e.g., via a secure channel), part of the information to proxy 906, using device 902 as an intermediary. Proxy 906 times computations performed by the monolith kernel and reports the timing measures back to external verifier 904. In some embodiments, external devices, such as tethered cell phones or computers, base stations, or additional external verifiers are used instead of or in addition to proxy 906. It is also possible to use software proxies that are believed to be tamper resistant, or to use special-purpose hardware proxies.

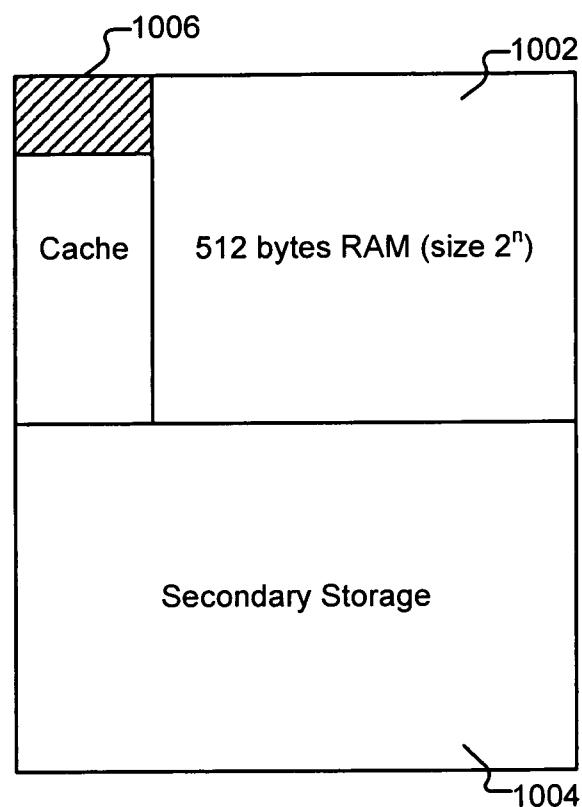

[00139] Figure 10 illustrates an embodiment of a portion of a device. As mentioned above, “free” RAM is defined as being the portion of RAM that ought to be free after all applications and the standard kernel have been swapped out. The width of the bus is a word. The size of memory is also describable in words. For example, a 512 byte memory page as shown in Figure 10 has a size 128 words on a standard handset, where a word is 32 bits. As used herein, a “chunk” is the length of the cache line. In the example shown, the cache line corresponds to 8 words, each of which is 32 bits, and the chunk is 256 bits accordingly.

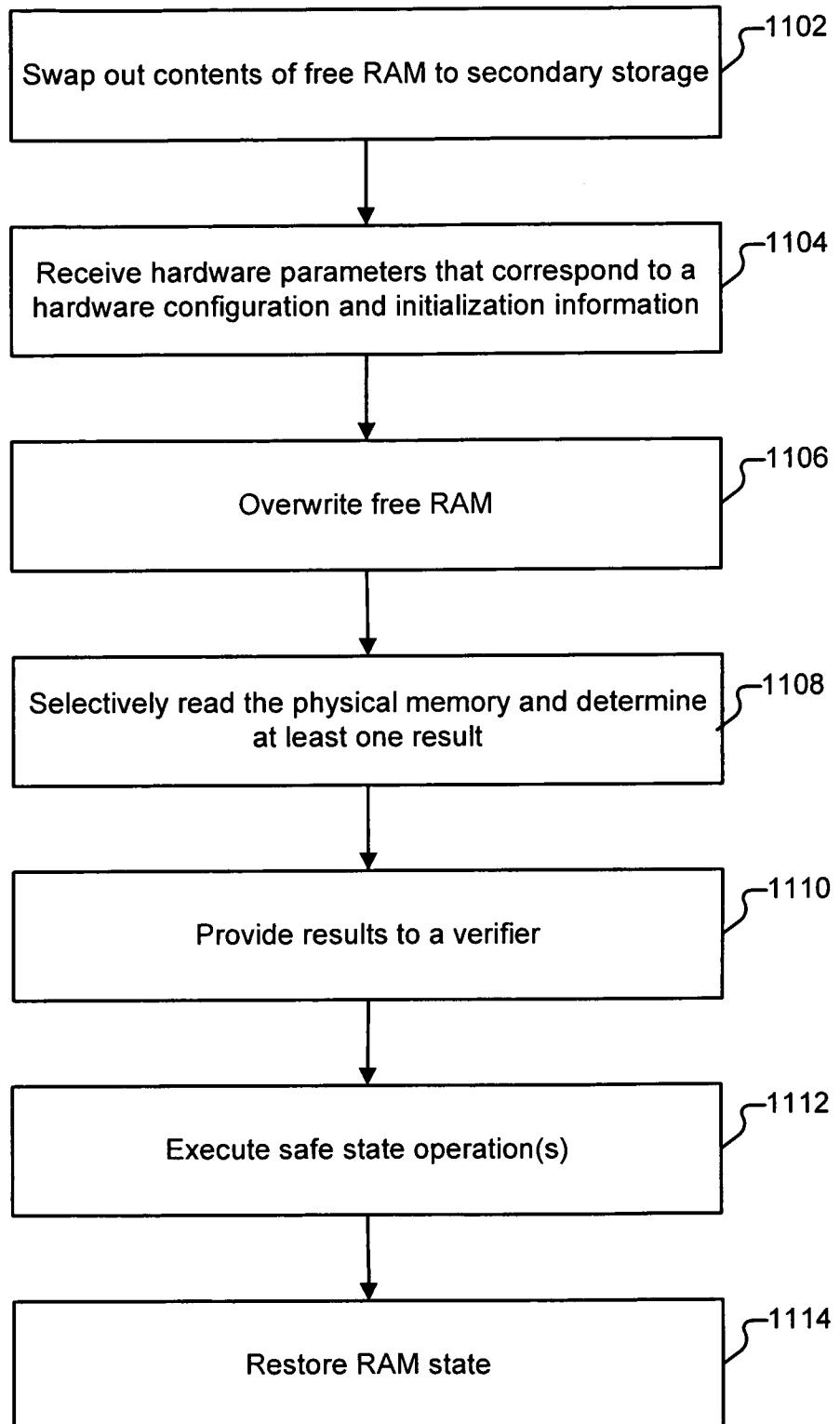

[00140] Figure 11 illustrates an embodiment of a process for performing a device audit. In various embodiments, the process shown in Figure 11 is performed by device 902. The process is configured such that its computations are expected to complete in a particular amount of time. Any change to the amount of free RAM evaluated and any attempts to access secondary storage 1004 will result in an observable lengthening of the amount of time the computations take to complete. Similarly, changing the contents of any of the whitelisted programs or associated data will cause a delay or the computation of the incorrect responses.

[00141] The process shown in Figure 11 can be initiated in a variety of ways, such as the ways described in conjunction with the process shown in Figure 3. As additional examples, the audit process can be included in a shutdown or boot route. It is also possible for an application to initiate the audit process. The application would be deactivated, the processing would be performed, and control would be handed back to the application when

complete. In some embodiments an application queries a central authority (or the device) for information about how recent the last scan was performed. The SIM card can store information about when a scan was performed. If the SIM card has the functionality that allows it to constantly measure time, it can give an actual time as the answer. Otherwise, it can give a time estimate based on the number of seen transactions, many of which will be known to be periodic. Such information can be used to assess the duration since the last scan.

**[00142]** The process begins at 1102 when contents of memory 1002, except monolith kernel 1006 (and any processes it deems acceptable to retain) are swapped to secondary storage 1004. In some embodiments portion 1102 of the process includes swapping out the normal kernel, or parts thereof. Crucial features, such as device drivers for serial communication, are re-implemented in monolith kernel 1106. In various embodiments, the contents are swapped out verbatim, or compact descriptions of the contents are swapped out or stored on the proxy, external verifier, or other trusted device, or stored in RAM in a state that cannot be used for active code. (E.g., it is possible to store instructions in a portion of cache not intended for instructions, but only data.) In some embodiments, no “free” space exists and portion 1102 of the process shown in Figure 11 is omitted.

**[00143]** At 1104, one or more hardware parameters that correspond to a hardware configuration are received. This portion of the process is similar to portion 302 of the process shown in Figure 3. Also at 1104, initialization information, such as a seed that can be used to generate a pseudo-random string, is received. Other examples of initialization information include a step value and a key value, as described in more detail below.

**[00144]** At 1106, the free RAM is overwritten. In some embodiments the output of a pseudorandom string generated using the seed is used to overwrite the free RAM. One technique for overwriting the free RAM is to generate an  $n^2$ -bit pseudorandom string with the particular property that the computation of any one of the output bits will take at least half as long as the computation of the entire block of bits or at least 512 applications of MD6 in 512 bit mode. The technique uses three phases, and repeats (with different values of aux) until the output strings fill the entire free RAM:

**[00145]** 1. Generating: Using a hash function  $h$  (e.g., MD6) with an output size of “ $n$ ” bits, generate the value  $x_i = h(seed, i, aux)$  for  $0 \leq i \leq n-1$ , and some value aux. This generates  $n^2$  pseudorandom bits.

[00146] 2. Shuffling: Compute  $y_j = \prod_{i=0}^j 2^i \text{BIT}_j(x_i)$ ,  $0 \leq j \leq n-1$ , where  $\text{BIT}_j$  is a function that returns the  $j^{\text{th}}$  most significant bit of the input. This shuffles the bits in a manner that requires computation of all  $n$  hash function applications to reconstitute any one of the values.

[00147] 3. Blending: Compute  $z_j = h(y_j)$ , for  $0 \leq j \leq n-1$ . This assures that each bit of the output is a function of all the  $n$  input bits, each one of which required one hash function evaluation to compute.

[00148] In various embodiments, additional shuffling and blending is performed to further increase the cost of computing any part of the final string. In addition, other techniques for overwriting free RAM can be used instead of the example technique described in conjunction with portion 1106 of the process shown in Figure 11.

[00149] At 1108, memory 1002 (or portions thereof) is read in a manner determined by the “step” value. Results are accumulated and the computation is keyed using a key. In various embodiments, the processing of portion 1108 is performed by a memory access scheduler and an accumulator, each of which will now be described in more detail.

[00150] **Memory Access Scheduler**

[00151] Let “sRAM” be the size of RAM 1002, measured in its entirety, in chunks. External verifier 904 will select a random value step in the range  $page < step < sRAM - page$ , such that “step” is an odd value. Here, “page” denotes the size of one memory page in secondary storage, also measured in chunks. In the case where there are several page sizes (e.g., if there are several components that constitute secondary storage), in various embodiments the largest of the page sizes is used.

[00152] Performing the processing of 1108 includes a loop in which memory is accessed and the results combined to form a keyed memory checksum. For each iteration of the loop, the access location is increased by the value step, modulo sRAM. Because “step” and sRAM are relatively prime, all RAM memory locations will be accessed exactly once. Further, the access order will be unknown to an adversary until the value “step” is disclosed. An illustration of memory 1002 being read in accordance with a “step” is provided in Figure 12.

[00153] In the example shown in Figure 9, device 902 includes a single, single-core CPU. In systems such as laptop computers that include multi-core processors and/or multiple processors, the processing of 1108 can be constructed in a way that is either inherently serial (and which will therefore obstruct the use of multiple processors) or adapted to take advantage of multiple processors. As one example of the latter, several computations can be started with offsets such that each thread corresponds to a different portion of memory, and where there are no collisions.

[00154] **Accumulator**

[00155] Memory contents can be accumulated in a register using a simple non-linear function that combines the previous register contents (referred to herein as a “state”) with the newly read memory contents (data), one by one. Examples of accumulating functions include hash functions (e.g., MD6); a non-linear shift-back register; and simpler functions.

[00156] One example of a simpler function is  $\text{state} \leftarrow \text{ROR}(\text{state} + \text{data})$ . The latter function corresponds to a function  $\text{ROR}(\dots(\text{ROR}(\text{state}_0 + \text{data}_1) + \text{data}_2) \dots + \text{data}_n)$ , where “+” refers to regular addition, and “ROR” rotates the contents of the register one bit to the right. In this case, the function itself may not be nonlinear, but when combined with the a priori unknown step size and the tight timing requirements, it is nonetheless sufficient to satisfy the processing requirements needed.

[00157] As mentioned above, in various embodiments, the accumulation process is keyed. One way to accomplish this is to offset the value “state” with a new value “key” (obtained from the external verifier or the proxy) at regular intervals. The offset can be performed by adding the current value state to the new value key.

[00158] Further, while the process described in conjunction with 1108 is based on reading memory, in some embodiments a write operation is included to cause further flash-based slowdowns. As one example, sequences of “1”s are written, as causing an erase of the entire block, should the data be stored in flash. To simplify the scheduling of where to write (and with it the monolith kernel), the location can be obtained from the proxy at the same time a new key value is obtained.

[00159] Various other sequences of memory accesses can also be performed at 1108. For example, it is possible to use two step values instead of one, where these step values may

both be even numbers, but where they cause mostly all of the space to be covered. It is also possible to use a collection of numbers or parameters that determine a function that selects the sequence of locations. It is possible to think of this as a maximum-length sequence, where the outputs are locations, and the maximum-length sequence includes all values in a given range, corresponding to memory positions. It is possible to offset such values to avoid accessing certain areas (e.g., the monolith kernel), should that be desirable. In the case of a maximum-length sequence, the key provided by the external verifier or proxy can be the initial state, or the weights associated with the various cells of the LFSR.

**[00160]** At 1110, the keyed computation is provided to an external verifier 904. If the external verifier approves of the results, device 902 is deemed to be in a safe state.

**[00161]** At 1112, device 902 executes any functions that are to be executed in a safe state. Examples include setting up an SSL connection, casting a vote, entering a password, scanning secondary storage for malicious/unwanted programs, etc. In various embodiments, if the code of the safe-state function is in secondary storage (i.e. it is not part of the monolith kernel), a digest of the function is compared to a value stored in the monolith kernel (or on the proxy). The function is activated only if the values match. In various embodiments, if the proxy can perform the message digest computation, the monolith kernel need not contain code to do the same.

**[00162]** At 1114, the state of RAM 1002 is restored by loading contents (swapped out at 1102) of secondary storage 1004.

**[00163]** A large portion of the potential load of the process shown in Figure 11 involves swapping out applications and data from RAM to secondary storage, and swapping it back. It is possible to avoid doing this, e.g., in order to save time. This could be done by killing the applications. If an external verifier or other resource knows what applications are running, and potentially also their state or parts thereof, it is possible for this party to assist in restarting selected applications after the auditing process has run. It is possible for secondary storage or a SIM card or other on-board unit to maintain some of this information. It is possible to identify applications and data not by their full strings, but by shorter identifiers to save space and time. It is possible to have approximate algorithms that largely re-generate the same state after the detection algorithm has run. For example, this may restart a browser, but fail to recover the browser contents.

**[00164]** Further, it is not necessary to swap out active applications if they only take up some portion of RAM. For example, suppose they only take up the lower half of RAM. For each cell (number  $i$ ) in free RAM, copy the contents of that cell to a position higher up (position  $2i$ ). This is preferably done starting from the end (higher numbered positions.) This effectively slices the applications, and makes them reside only in even positions. Now pseudorandom values need only be written into the odd-numbered positions, and only need to perform the nonlinear accumulation of the odd-numbered cells. Note that it is not possible for any functional malware to remain active. It is possible for malware to exist, but only if its instructions are “jump to next open space” and that is where the next instruction is. Since all the space that is not overwritten by pseudorandom material will be jumps only (there is not space for more in consecutive space), it is knowable that the malware cannot achieve anything. It is possible to make the distance between slices larger, especially if the space is not predictable by an adversary. The distance may be predicted by a sequence generator, for example, where different distances are different length. The spreading out of data and programs within the RAM can be combined with offsetting these with random strings. The microkernel (the program in charge of the malware detection)—would not be spread out in this manner, as it needs to remain in a state that allows it to execute.

**[00165]** In conjunction with Figure 11, a description was made as to how RAM could be read using a step size that is not a priori known. It is also possible to write (free) RAM using a step size other than one, where the step size may be unknown a priori. One effect of this is that it causes writes to secondary storage for an attacker wishing to store information in secondary storage. These delays are greater than read delays if secondary storage uses flash. It is possible to use a simple step increment modulo an integer corresponding to the range to be written -- plus an offset if the monolith kernel does not reside in high addresses. It is also possible to use no particular modulo for the arithmetic -- which corresponds to using a modulo corresponding to the addressable RAM space -- and to identify whether the cell to be written is in a range that should not be written.

**[00166]** Figure 13 illustrates an embodiment of an implementation of a process for selectively reading memory. In some embodiments Figure 13 is used to implement a portion of portion 1108 of the process shown in Figure 11.

**[00167]** In some embodiments, full use of the data cache is made. Specifically, data is processed in chunks the width of the cache line, whose size typically ranges from 8 to 512

bytes. In the following, the parameter “ $\alpha$ ” denotes the width of the cache line, in words. The parameter “period” corresponds to the length of the timing periods. This is set to correspond to a time that is shorter than an optimistic roundtrip latency from device 902 to a potential external helper. The reported values, and the time at which they are reported, are recorded by proxy 906.

**[00168] Examples of Detecting Various Evasive Programs**

**[00169]** The following section provides examples of how evasive programs employing the various strategies described above can be detected using the techniques described herein. To succeed in evading detection, an adversary has to provide the correct responses  $F_{\epsilon_i}(x)$  within the expected time  $t_i(F_{\epsilon}, x) + \delta$ . There are various ways this can be attempted by an adversary, each of which will now be described.

**[00170] Defending against adversarial strategy 1 – external support.**

**[00171]** The values “key” and “step” are communicated to the proxy over a secure channel. The value of “state” is reported for each iteration of the outer loop. The computation of this value depends on the value “key.” Therefore, it is not possible for an external device to help with the generation of the responses if the roundtrip latency (from sending out the value key to receiving the result of the computation) exceeds the time threshold  $t_i(F_{\epsilon}, x) + \delta$ , where  $t_i(F_{\epsilon}, x)$  is the time for  $F_{\epsilon}$  to generate the response.

**[00172] Defending against adversarial strategy 2 – using secondary storage.**