(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7002378号

(P7002378)

(45)発行日 令和4年1月20日(2022.1.20)

(24)登録日 令和4年1月4日(2022.1.4)

(51)国際特許分類

|         |                |         |       |

|---------|----------------|---------|-------|

| H 0 3 K | 5/131(2014.01) | H 0 3 K | 5/131 |

| H 0 3 K | 5/133(2014.01) | H 0 3 K | 5/133 |

| H 0 3 K | 5/135(2006.01) | H 0 3 K | 5/135 |

F I

請求項の数 4 (全12頁)

|          |                             |          |                    |

|----------|-----------------------------|----------|--------------------|

| (21)出願番号 | 特願2018-51613(P2018-51613)   | (73)特許権者 | 000003078          |

| (22)出願日  | 平成30年3月19日(2018.3.19)       |          | 株式会社東芝             |

| (65)公開番号 | 特開2019-165330(P2019-165330) |          | 東京都港区芝浦一丁目1番1号     |

|          | A)                          | (74)代理人  | 100091487          |

| (43)公開日  | 令和1年9月26日(2019.9.26)        |          | 弁理士 中村 行孝          |

| 審査請求日    | 令和1年8月19日(2019.8.19)        | (74)代理人  | 100107582          |

| 審判番号     | 不服2021-1889(P2021-1889/J1)  |          | 弁理士 関根 賀           |

| 審判請求日    | 令和3年2月10日(2021.2.10)        | (74)代理人  | 100118843          |

|          |                             |          | 弁理士 赤岡 明           |

|          |                             | (74)代理人  | 100103263          |

|          |                             |          | 弁理士 川崎 康           |

|          |                             | (72)発明者  | 吉岡 健太郎             |

|          |                             |          | 東京都港区芝浦一丁目1番1号 株式会 |

|          |                             |          | 社東芝内               |

|          |                             | 合議体      |                    |

最終頁に続く

(54)【発明の名称】 デジタル時間変換器及び情報処理装置

## (57)【特許請求の範囲】

## 【請求項1】

起動信号に同期して発振動作を行う発振器と、

前記起動信号が入力されたタイミングで前記発振器の発振回数のカウントを開始し、前記発振器から出力された発振信号をデジタル入力信号に応じた基準発振回数に到達するまでカウントし、前記基準発振回数に到達するタイミングに同期して前記起動信号を遅延させた第1遅延起動信号を出力するカウント回路と、

前記第1遅延起動信号を前記デジタル入力信号に応じた遅延時間分遅延させた第2遅延起動信号を出力する遅延付加回路と、

前記起動信号と前記第2遅延起動信号とに基づいて、前記デジタル入力信号に応じたパルス幅のパルス信号を出力するパルス出力回路と、

前記起動信号を、前記発振器及び前記カウント回路に基づく信号遅延と、前記遅延付加回路に基づく信号遅延と、に応じて遅延させる遅延調整回路と、を備え、

前記カウント回路は、前記デジタル入力信号の上位側ビットに基づいて前記基準発振回数を設定し、

前記遅延付加回路は、前記デジタル入力信号の少なくとも下位側ビットに応じた遅延時間分前記第1遅延起動信号を遅延させた前記第2遅延起動信号を出力し、

前記パルス出力回路は、前記遅延調整回路にて前記起動信号を遅延させた信号と前記第2遅延起動信号とに基づいて、前記パルス信号を出力し、

前記第2遅延起動信号は、前記起動信号を前記デジタル入力信号に応じた遅延時間分遅延

させた信号であるデジタル時間変換器。

【請求項 2】

前記遅延付加回路は、それぞれ遅延量が相違し直列接続される複数の遅延回路を有し、前記直列接続された複数の遅延回路のうち初段の遅延回路には前記第1遅延起動信号が入力され、

前記下位側ビットに基づいて、前記複数の遅延回路のそれぞれで遅延させるか否かが選択される、請求項1に記載のデジタル時間変換器。

【請求項 3】

前記発振器は、リング状に縦続接続される複数の第1論理反転素子を有し、

前記遅延付加回路は、前記複数の第1論理反転素子と同一の遅延時間を有する2以上の第2論理反転素子を有する、請求項1又は2に記載のデジタル時間変換器。

10

【請求項 4】

請求項1又は2に記載のデジタル時間変換器と、

前記パルス信号のパルス幅の期間に発振動作を行い、前記期間が終わった時点の位相状態を保持する選択的発振器と、

前記位相状態を含むデジタル出力信号を出力する読出部と、を備える、情報処理装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、デジタル時間変換器及び情報処理装置に関する。

20

【背景技術】

【0002】

デジタル入力信号に応じたパルス幅のパルス信号を出力するデジタル時間変換器が知られている。この種のデジタル時間変換器では、それぞれ遅延時間が異なる複数の遅延回路を直列接続し、各遅延回路を動作させるか否かをデジタル入力信号により選択している。

【0003】

しかしながら、この種のデジタル時間変換器では、デジタル入力信号のビット数が増えると、遅延回路の数が指数関数的に増えて、回路規模が急激に大きくなるという問題がある。

【先行技術文献】

【特許文献】

30

【0004】

【文献】米国特許8,988,262公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の一態様は、デジタル入力信号のビット数が増えても、回路規模が急激に大きくならないようにしたデジタル時間変換器及び情報処理装置を提供するものである。

【課題を解決するための手段】

【0006】

本実施形態によれば、発振動作を行う発振器と、

40

起動信号が入力されたタイミングで前記発振器の発振回数のカウントを開始し、前記タイミングから、カウントされた発振回数がデジタル入力信号に応じた基準発振回数に到達するまでの期間、前記起動信号を遅延させた第1遅延起動信号を出力するカウント回路と、を備える、デジタル時間変換器が提供される。

【図面の簡単な説明】

【0007】

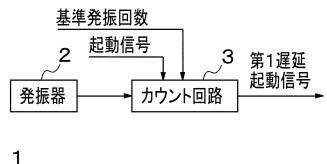

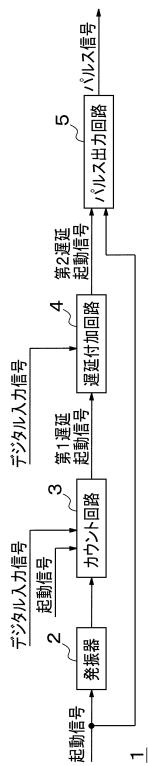

【図1】第1の実施形態によるデジタル時間変換器1の概略構成を示すブロック図。

【図2】図1のデジタル時間変換器1のタイミング図。

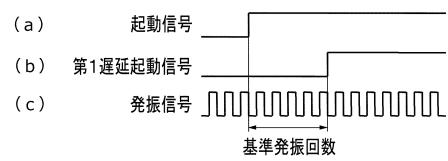

【図3】図1の第1変形例によるデジタル時間変換器の概略構成を示すブロック図。

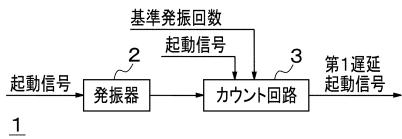

【図4】図1の第2変形例によるデジタル時間変換器の概略構成を示すブロック図。

50

【図 5】図 1 の第 3 変形例によるデジタル時間変換器の概略構成を示すブロック図。

【図 6】図 5 のデジタル時間変換器を具体化した回路図。

【図 7】リング発振器の一変形例を示す回路図。

【図 8】デジタル遅延回路の内部構成の一例を示すブロック図。

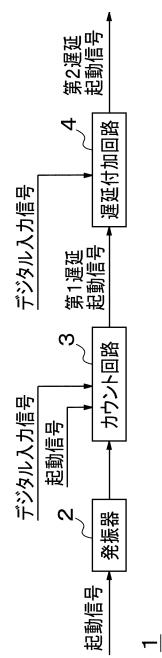

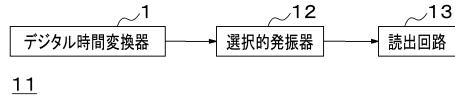

【図 9】第 2 の実施形態によるデジタル時間変換器を備えた情報処理装置の概略構成を示すブロック図。

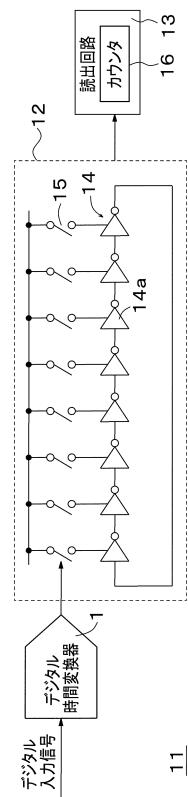

【図 10】選択的発振器の内部構成の一例を示す図。

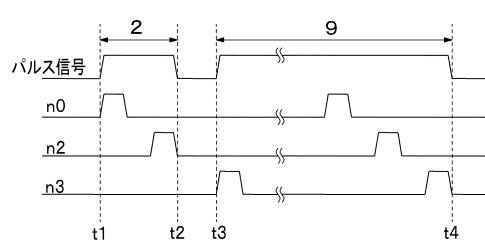

【図 11】図 9 の情報処理装置に  $N = 2$  個のデジタル入力信号を順に入力した場合のタイミング図。

【発明を実施するための形態】

【0008】

10

以下、図面を参照して実施の形態について説明する。なお、本件明細書と添付図面においては、理解のしやすさと図示の便宜上、一部の構成部分を省略、変更または簡易化して説明および図示しているが、同様の機能を期待し得る程度の技術内容も、本実施の形態に含めて解釈することとする。

【0009】

20

(第 1 の実施形態)

図 1 は第 1 の実施形態によるデジタル時間変換器 1 の概略構成を示すブロック図である。

図 1 のデジタル時間変換器 1 は、発振器 2 と、カウント回路 3 とを備えている。

【0010】

発振器 2 は、発振動作を行って、所定の発振周波数の発振信号を出力する。発振器 2 は、電源電圧が供給されている間は、継続して発振動作を行ってもよいし、外部から起動信号が入力された場合のみ発振動作を行ってもよい。発振器 2 は、後述するように、例えば複数の論理反転素子（インバータ）をリング状に継続接続したリング発振器で構成されてもよい。ここで、起動信号（トリガ信号）が入力されるとは、起動信号が特定の論理になることを意味し、例えば、起動信号がロウレベルからハイレベルに変化したタイミングで、起動信号が入力されたものとして扱う。

【0011】

発振器 2 から出力された発振信号はカウント回路 3 に入力される。この他、カウント回路 3 には、起動信号と基準発振回数が入力される。カウント回路 3 は、起動信号が入力されたタイミングで発振器 2 の発振回数のカウントを開始し、カウントされた発振回数がデジタル入力信号に応じた基準発振回数に到達するまでの期間、起動信号を遅延させた第 1 遅延起動信号を出力する。カウント回路 3 に入力される基準発振回数は、例えばデジタル入力信号の少なくとも一部のビット列にて指定することができる。

30

【0012】

図 1 のデジタル時間変換器 1 は、デジタル入力信号によって、起動信号を遅延させるための任意の遅延時間を設定できる。デジタル入力信号のビット数を増やすことで、起動信号の遅延時間を細かく設定できる。すなわち、デジタル入力信号のビット数によって、起動信号の遅延時間の分解能を調整できる。

【0013】

40

図 2 は図 1 のデジタル時間変換器 1 のタイミング図である。図 2 からわかるように、カウント回路 3 は、起動信号を、発振器 2 から出力された発振信号の基準発振回数分だけ遅延させた第 1 遅延起動信号を出力する。

【0014】

図 3 は図 1 の第 1 変形例によるデジタル時間変換器 1 の概略構成を示すブロック図である。図 3 は、カウント回路 3 だけでなく、発振器 2 にも起動信号が入力されている点で図 1 のデジタル時間変換器 1 とは異なっている。図 3 の発振器 2 は、起動信号に同期して発振動作を行う。すなわち、図 3 の発振器 2 は、起動信号が入力されたとき（例えば、起動信号がハイレベルのとき）に発振動作を行い、起動信号が入力されないと（例えば、起動信号がロウレベルのとき）には発振動作を停止する。図 3 のカウント回路 3 は、発振器 2

50

から出力された発振信号を基準発振回数に到達するまでカウントし、基準発振回数に到達するタイミングに同期して第1遅延起動信号を出力する。図3のデジタル時間変換器1は、起動信号が入力されているときのみ、発振器2が発振動作を行うため、発振器2の消費電力を抑制できる。

【0015】

図4は図1の第2変形例によるデジタル時間変換器1の概略構成を示すブロック図である。図4のデジタル時間変換器1は、図3のデジタル時間変換器1に遅延付加回路4を追加した構成を備えているが、図1のデジタル時間変換器1に遅延付加回路4を追加してもよい。

遅延付加回路4は、第1遅延起動信号をデジタル入力信号に応じた遅延時間分遅延させた第2遅延起動信号を出力する。遅延付加回路4は、デジタル入力信号の少なくとも下位側ビット(LSB:Least Significant Bit)に応じた遅延時間分第1遅延起動信号を遅延させた第2遅延起動信号を出力する。また、遅延付加回路4は、カウント回路3に入力されるデジタル入力信号の上位側ビット(MSB:Most Significant Bit)のうち少なくとも一部のビットを含めたデジタル入力信号の下位側ビットに基づいて、第2遅延起動信号の遅延時間を設定してもよい。

【0016】

例えば、デジタル入力信号の上位側ビットをカウント回路3に入力して基準発振回数を設定し、デジタル入力信号の下位側ビットを遅延付加回路4に入力して第1遅延起動信号の遅延時間を設定してもよい。これにより、カウント回路3により起動信号のおおまかな遅延時間を設定でき、遅延付加回路4により起動信号の遅延時間の微調整を行うことができる。

【0017】

図5は図1の第3変形例によるデジタル時間変換器1の概略構成を示すブロック図である。図5のデジタル時間変換器1は、図4のデジタル時間変換器1にパルス出力回路5を追加した構成を備えている。パルス出力回路5は、起動信号と第2遅延起動信号に基づいて、デジタル入力信号に応じたパルス幅のパルス信号を出力する。例えば、パルス出力回路5は、図2に示すように、起動信号の立ち上がりエッジから、第2遅延起動信号の立ち上がりエッジまでのパルス幅を有するパルス信号を出力する。このように、図5のデジタル時間変換器1は、デジタルパルス変換器として動作する。

【0018】

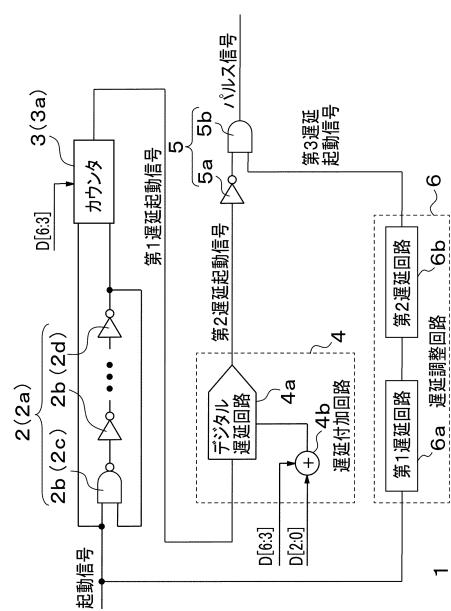

図6は図5のデジタル時間変換器1を具体化した回路図である。図6のデジタル時間変換器1は、発振器2と、カウント回路3と、遅延付加回路4と、パルス出力回路5と、遅延調整回路6とを備えている。

【0019】

図6の発振器2は、例えばリング発振器2aである。このリング発振器2aは、複数の論理反転素子2bをリング状に継続接続したものである。図6のリング発振器2aは、初段の論理反転素子2bを2入力のNANDゲート2cとし、二段目以降の論理反転素子2bをインバータ2dとしているが、論理反転素子2bを構成する具体的な回路素子は任意である。図6のNANDゲート2cは、起動信号と最終段のインバータ2dの出力信号との否定論理積演算を行う。起動信号がロウレベルのときは、NANDゲート2cの出力はハイ固定になるため、リング発振器2aは発振動作を停止する。起動信号がハイレベルになると、NANDゲート2cは論理反転素子2bとして機能し、NANDゲート2cとインバータ2dを合わせた段数に応じた周波数で発振動作を行う。リング発振器2aにおける継続接続された複数の論理反転素子2bの段数と各論理反転素子2bの信号遅延時間によって、発振周波数が決定される。例えば、複数の論理反転素子2bの段数をm(mは2以上の整数)、各論理反転素子2bの信号遅延時間がいずれも $t_{inv}$ とすると、発振周波数 $f = 2m \times t_{inv}$ となる。

【0020】

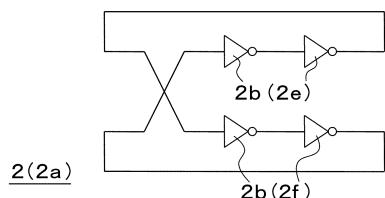

リング発振器2aにおける論理反転素子2bの段数は奇数個でもよいし、偶数個でもよい

10

20

30

40

50

。奇数個の場合は、図 6 に示すように、最終段の論理反転素子 2 b の出力信号を初段の論理反転素子 2 b に入力するだけでよいが、偶数段の場合には、例えば図 7 に示すように、縦続接続された複数の論理反転素子 2 b からなる第 1 論理反転素子群 2 e と、縦続接続された複数の論理反転素子 2 b からなる第 2 論理反転素子群 2 f とを備え、第 1 論理反転素子群 2 e 内の最終段の論理反転素子 2 b の出力信号を第 2 論理反転素子群 2 f 内の初段の論理反転素子 2 b に入力し、かつ第 2 論理反転素子群 2 f 内の最終段の論理反転素子 2 b の出力信号を第 1 論理反転素子群 2 e 内の初段の論理反転素子 2 b に入力する。リング発振器 2 a を図 7 のような偶数段の論理反転素子 2 b で構成すると、論理反転素子 2 b の総数は奇数段のときよりも増えるものの、発振信号の発振周波数を 2 のべき乗で調整できことから、2 進数で遅延時間を調整できることになり、デジタル時間変換器 1 の設計が容易になる。

10

#### 【 0 0 2 1 】

図 6 のカウント回路 3 は、カウンタ 3 a を有する。カウンタ 3 a でカウント可能なビット数が多いほど、遅延設定の分解能を高くすることができる。カウンタ 3 a には、デジタル入力信号の上位側ビット D [ 6 : 3 ] が入力されており、この上位側ビットにて、基準発振回数が設定される。図 6 の例では、デジタル入力信号 D [ 6 : 0 ] の総ビット数が 7 ビットであり、そのうちの上位側ビット D [ 6 : 3 ] をカウンタ 3 a に入力する例を示している。カウンタ 3 a に入力される上位側ビットのビット数が大きいほど、カウンタ 3 a のビット数を増やす必要がある。カウンタ 3 a は、シフトレジスタを主な回路部品としており、ビット数を増やすとしてもそれほど回路規模は増えない。

20

#### 【 0 0 2 2 】

カウンタ 3 a は、発振器 2 から出力された発振信号に同期してカウント動作を行い、カウント数が基準発振回数に到達すると、カウンタ 3 a がカウント動作を行っていた期間分、起動信号を遅延させた第 1 遅延起動信号を出力する。

#### 【 0 0 2 3 】

リング発振器 2 a 内の論理反転素子 2 b の接続段数が例えば 7 段で、各論理反転素子 2 b の信号遅延時間が  $t_{inv}$  の場合、リング発振器 2 a の発振周波数は、 $7 \times 2 \times t_{inv} = 14 t_{inv}$  で表される。よって、基準発振回数が  $m$  回 ( $m$  は 1 以上の整数) であれば、カウンタ 3 a は、起動信号を、 $14 t_{inv} \times m$  だけ遅延させた第 1 遅延起動信号を出力する。

30

#### 【 0 0 2 4 】

図 6 の遅延付加回路 4 は、デジタル遅延回路 4 a と、遅延制御回路 4 b とを有する。デジタル遅延回路 4 a は、遅延制御回路 4 b から出力された遅延制御信号に応じた遅延時間分、第 1 遅延起動信号を遅延させた第 2 遅延起動信号を出力する。

#### 【 0 0 2 5 】

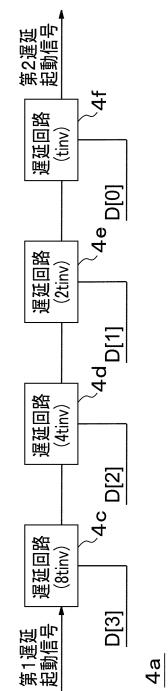

図 8 はデジタル遅延回路 4 a の内部構成の一例を示すブロック図である。図 8 のデジタル遅延回路 4 a は、それぞれ遅延時間が異なる複数の遅延回路 4 c, 4 d, 4 e, 4 f を直列接続した構成を有する。初段の遅延回路 4 c には、カウント回路 3 から出力された第 1 遅延起動信号が入力される。図 8 の例では、初段の遅延回路 4 c の遅延時間を  $8 t_{inv}$ 、二段目の遅延回路 4 d の遅延時間を  $4 t_{inv}$ 、三段目の遅延回路 4 e の遅延時間を  $2 t_{inv}$ 、最終段の遅延回路 4 f の遅延時間を  $t_{inv}$  としているが、これは一例であり、必ずしも 2 のべき乗の遅延時間の違いを設ける必要はない。また、図 8 の例では、リング発振器 2 a 内の各論理反転素子 2 b の信号遅延時間を  $t_{inv}$  としたときに、この信号遅延時間の倍数となるように各遅延回路 4 c の遅延時間を設定している。これは、遅延時間の誤差を少なくするためである。

40

#### 【 0 0 2 6 】

各遅延回路 4 c ~ 4 f には、遅延制御回路 4 b から出力された遅延制御信号を構成するビット列のうち、対応するビットが入力される。例えば、遅延制御信号が 4 ビットのビット列 D [ 3 : 0 ] の場合、最上位ビット D [ 3 ] は初段の遅延回路 4 c に入力され、D [ 2 ] は二段目の遅延回路 4 d に入力され、D [ 1 ] は三段目の遅延回路 4 e に入力され、D [ 0 ] は最終段の遅延回路 4 f に入力される。各遅延回路 4 c ~ 4 f は、遅延制御信号の

50

対応するビットが 1 の場合は、入力信号を遅延させて出力し、ビットが 0 の場合は、入力信号を遅延させずにそのまま出力する。

【 0 0 2 7 】

遅延制御回路 4 b は、デジタル入力信号の上位側ビット D [ 6 : 3 ] と下位側ビット D [ 2 : 0 ] をビット加算することにより、遅延制御信号を生成する。例えば D [ 6 : 3 ] = 0 0 0 1 で、D [ 2 : 0 ] = 0 0 0 の場合、遅延制御回路 4 b は、遅延制御信号として 0 0 1 を出力する。

【 0 0 2 8 】

図 6 の遅延調整回路 6 は、カウント回路 3 での信号遅延時間だけ起動信号を遅延させる第 1 遅延回路 6 a と、デジタル遅延回路 4 a での信号遅延時間だけ起動信号を遅延させる第 2 遅延回路 6 b とを有する。図 6 の遅延調整回路 6 は、起動信号を、カウント回路 3 とデジタル遅延回路 4 a での信号遅延時間だけ遅延させた第 3 遅延起動信号を出力する。

10

【 0 0 2 9 】

パルス出力回路 5 は、デジタル遅延回路 4 a から出力された第 2 遅延起動信号と、遅延調整回路 6 から出力された第 3 遅延起動信号とに基づいて、パルス信号を生成して出力する。図 6 のパルス出力回路 5 は、第 2 遅延起動信号の論理を反転させるインバータ 5 a と、インバータ 5 a の出力と第 3 遅延起動信号との論理積信号を出力する AND ゲート 5 b とを有するが、パルス出力回路 5 の具体的な回路構成は任意である。これにより、パルス出力回路 5 は、デジタル入力信号に応じたパルス幅のパルス信号を出力する。

20

【 0 0 3 0 】

このように、第 1 の実施形態によるカウント回路 3 は、デジタル入力信号の上位側ビットに応じた遅延時間分、起動信号を遅延させた第 1 遅延起動信号を生成する。遅延付加回路 4 は、デジタル入力信号の上位側ビット及び下位側ビットに応じた遅延時間分、第 1 遅延起動信号を遅延させた第 2 遅延起動信号を生成する。遅延調整回路 6 は、カウント回路 3 と遅延付加回路 4 の信号遅延時間分、起動信号を遅延させた第 3 遅延起動信号を生成する。パルス出力回路 5 は、第 2 遅延起動信号と第 3 遅延起動信号とに基づいて、パルス信号を生成する。

20

【 0 0 3 1 】

第 1 の実施形態によれば、デジタル入力信号のビット数が増えても、カウント回路 3 内のカウンタ 3 a のビット数が増えるだけであり、全体的な回路規模はそれほど増えない。また、本実施形態では、カウント回路 3 にて起動信号のおおまかな遅延時間を設定し、遅延付加回路 4 にて起動信号の遅延時間を精度よく設定するため、遅延時間の精度を落とさずに回路規模の増大を抑制できる。

30

【 0 0 3 2 】

( 第 2 の実施形態 )

上述した図 5 又は図 6 のデジタル時間変換器 1 は、デジタル入力信号の積和演算処理に用いることができる。

【 0 0 3 3 】

図 9 は第 2 の実施形態によるデジタル時間変換器 1 を備えた情報処理装置 1 1 の概略構成を示すブロック図である。図 9 の情報処理装置 1 1 は、図 5 又は図 6 のデジタル時間変換器 1 と、選択的発振器 1 2 と、読出回路 1 3 とを備えている。

40

【 0 0 3 4 】

選択的発振器 1 2 は、パルス信号がパルスを出力している最中に発振動作を行い、パルスの出力が停止した時点の発振動作状態を保持する。図 1 0 は選択的発振器 1 2 の内部構成の一例を示す図である。選択的発振器 1 2 は、リング発振器 1 4 と、複数の切替器 1 5 とを有する。リング発振器 1 4 は、リング状に接続された複数の遅延素子 1 4 a を有し、初期パルス信号を複数の遅延素子 1 4 a にて順繰りに伝送する。各遅延素子 1 4 a は、例えばインバータで構成可能である。

【 0 0 3 5 】

複数の切替器 1 5 のそれぞれは、複数の遅延素子 1 4 a のそれぞれに対応して設けられて

50

いる。各切替器 15 は、対応する遅延素子 14a に遅延動作を行わせるか否かを切り替える。例えば、各遅延素子 14a は、対応する切替器 15 がオンの場合には、前段の遅延素子 14a の出力信号を遅延させて出力し、対応する切替器 15 がオフの場合には、信号の伝搬遅延動作を停止する。すべての切替器 15 は同期してオンまたはオフする。

#### 【 0 0 3 6 】

読み出回路 13 は、初期パルス信号がリング発振器 14 を一回りするたびにカウントアップするカウンタ 16 を有する。読み出部 13 は、カウンタ 16 のカウント値によって発振回数を検出するとともに、リング発振器 14 内のどの遅延素子 14a が初期パルス信号を保持しているかを示す位相状態を検出する。そして、読み出部 13 は、発振回数と位相状態を含むデジタル出力信号を生成して出力する。

10

#### 【 0 0 3 7 】

図 11 は図 9 の情報処理装置 11 に  $N = 2$  個のデジタル入力信号を順に入力した場合のタイミング図である。図 11 は、デジタル入力信号として、2 と 9 が順に入力された例を示している。ここで、選択的発振器 12 は所望の状態に初期化されているとし、発振状態のデューティは無視し簡単のため位相状態をパルスに置き換えて説明する。リング発振器 14 は、最初のデジタル入力信号が入力される前にいったんリセットされ、初段の遅延素子 14a に所定のパルス長の初期パルス信号が入力される。最初のデジタル入力信号 ( $= 2$ ) がデジタル - パルス変換器に入力されると (時刻  $t_1$ )、デジタル - パルス変換器は、遅延素子 14a の遅延量の 2 個分のパルス長のパルスを含むパルス信号を出力する。このパルス長のパルスが出力されている最中は、すべての切替器 15 がオンして、すべての遅延素子 14a に電源電圧が供給される。初期状態では、初段の遅延素子 14a の入力端子に初期パルス信号が入力されるため、この初期パルス信号は、左から 2 つ目の遅延素子 14a の出力端子まで伝搬される。デジタル - パルス変換器から出力されたパルス信号が時刻  $t_2$  でロウレベルに落ちると、すべての切替器 15 はオフし、左から 2 段目の遅延素子 14a は、その直前の信号レベルであるハイレベルを保持する。

20

#### 【 0 0 3 8 】

その後、2 個目のデジタル入力信号 ( $= 9$ ) が入力されると (時刻  $t_3$ )、デジタル - パルス変換器は、遅延素子 14a の遅延量の 9 個分のパルス長のパルスを含むパルス信号を出力する。このパルス長のパルスが出力されている最中は、すべての切替器 15 がオンして、すべての遅延素子 14a に電源電圧が供給される。よって、左から 2 番目の遅延素子 14a が保持していた初期パルス信号は、9 個の遅延素子 14a 分だけ順に伝搬される。2 番目の遅延素子 14a から一番右の遅延素子 14a までに 6 個の遅延素子 14a があるため、一番右の遅延素子 14a から一番左の遅延素子 14a まで伝搬された初期パルス信号は、さらに左から 3 番目の遅延素子 14a まで伝搬された時点  $t_4$  で、すべての切替器 15 がオフになる。よって、初期パルス信号は左から 3 番目の遅延素子 14a が保持することになる。

30

#### 【 0 0 3 9 】

このように、図 9 の情報処理装置 11 は、単一の選択的発振器 12 を用いることで、簡易な回路構成にて複数のデジタル入力信号の積分処理を行うことができる。また、図 9 の情報処理装置 11 では、同一の選択的発振器 12 を用いて複数の積分および和演算を行えるため、演算対象のデジタル入力信号の数が増えても、情報処理装置 11 の構成が複雑化することなく、多数のデジタル入力信号の積分および和演算を簡易な回路構成の情報処理装置 11 にて行うことができる。

40

#### 【 0 0 4 0 】

また、デジタル入力信号に対して重み信号を付与することで、積和演算を行うことができる。人工知能 (A I : Artificial Intelligence) の演算処理では、多数の積和演算を行う必要があるため、図 9 の情報処理装置 11 を適用することで、A I の演算処理をハードウェアにて高速に行うことができる。

#### 【 0 0 4 1 】

以上では、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提

50

示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0042】

1 デジタル時間変換器、2 発振器、2 a リング発振器、2 b 論理反転素子、2 e 第1論理反転素子群、2 f 第2論理反転素子群、3 カウント回路、4 遅延付加回路、5 パルス出力回路、6 遅延調整回路、11 情報処理装置、12 選択的発振器、13 読出回路、14 リング発振器、14 a 遅延素子、15 切替器

10

20

30

40

50

【図面】

【図 1】

【図 2】

10

【図 3】

【図 4】

20

30

40

50

【図 5】

【図 6】

10

20

30

40

【図 7】

【図 8】

50

【図 9】

【図 10】

【図 11】

---

フロントページの続き

審判長 伊藤 隆夫

審判官 吉田 隆之

衣鳩 文彦

(56)参考文献 特開平6-77791 (JP, A)

米国特許出願公開第2004/0263266 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

H03K