#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

### (19) World Intellectual Property Organization

International Bureau

### (43) International Publication Date 2 February 2012 (02.02.2012)

### (10) International Publication Number WO 2012/014786 A1

(51) International Patent Classification:

H01L 29/786 (2006.01)

H01L 27/108 (2006.01)

H01L 21/28 (2006.01)

H01L 27/115 (2006.01)

H01L 21/336 (2006.01)

H01L 29/423 (2006.01)

H01L 21/8234 (2006.01)

H01L 29/49 (2006.01)

H01L 21/8247 (2006.01)

H01L 29/788 (2006.01)

H01L 21/8247 (2006.01)

H01L 29/792 (2006.01)

(21) International Application Number:

H01L 27/088 (2006.01)

PCT/JP2011/066622

English

(22) International Filing Date:

14 July 2011 (14.07.2011)

(25) Filing Language:

(26) Publication Language: English

(30) Priority Data:

2010-171597 30 July 2010 (30.07.2010) JJ

(71) Applicant (for all designated States except US): SEMI-CONDUCTOR ENERGY LABORATORY CO., LTD. [JP/JP]; 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

- (72) Inventor; and

- (75) Inventor/Applicant (for US only): YAMAZAKI, Shunpei [JP/JP]; c/o SEMICONDUCTOR ENERGY LABO-

RATORY CO., LTD., 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

— with international search report (Art. 21(3))

#### (54) Title: SEMICONDCUTOR DEVICE AND MANUFACTURING METHOD THEREOF

(57) Abstract: A method for manufacturing a semiconductor device, which enables miniaturization and reduction of defect, is provided. It includes forming an oxide semiconductor layer, and source and drain electrodes in contact with the oxide semiconductor layer, over an insulating surface; forming insulating layers over the source electrode and the drain electrode; forming a gate insulating layer over the oxide semiconductor layer, the source and drain electrodes, and the insulating layer; forming a conductive layer over the gate insulating layer; forming an insulating film covering the conductive laver: processing the insulating film so that at least part of a region of the conductive layer, which overlaps with the source electrode or the drain electrode, is exposed; and etching the exposed region of the conductive layer to form a gate electrode overlapping with at least part of the region sandwiched between the source electrode and the drain electrode, in a self-aligned manner.

#### DESCRIPTION

#### SEMICONDCUTOR DEVICE AND MANUFACTURING METHOD THEREOF

#### TECHNICAL FIELD

[0001]

The present invention relates to semiconductor devices. Here, semiconductor devices refer to general elements and devices which function utilizing semiconductor characteristics.

10

15

20

25

30

5

#### **BACKGROUND ART**

[0002]

There are a wide variety of metal oxides and such metal oxides are used for various applications. Indium oxide is a well-known material and has been used for transparent electrodes required in liquid crystal display devices or the like.

[0003]

Some metal oxides have semiconductor characteristics. The examples of such metal oxides having semiconductor characteristics are, for example, tungsten oxide, tin oxide, indium oxide, and zinc oxide. Thin film transistors in which channel formation regions are formed using such metal oxides are already known (for example, see Patent Documents 1 to 4, Non-Patent Document 1, and the like).

[0004]

As metal oxides, not only single-component oxides but also multi-component oxides are known. For example,  $InGaO_3(ZnO)_m$  (m: natural number) having a homologous phase is known as a multi-component oxide semiconductor containing In, Ga, and Zn (for example, see Non-Patent Documents 2 to 4 and the like). [0005]

Furthermore, it is confirmed that an oxide semiconductor containing such an In-Ga-Zn-based oxide is also applicable to a channel formation region of a thin film transistor (for example, see Patent Document 5, Non-Patent Documents 5 and 6, and the like).

[Reference]

PCT/JP2011/066622

[0006]

[Patent Document 1] Japanese Published Patent Application No. S60-198861

[Patent Document 2] Japanese Published Patent Application No. H8-264794

[Patent Document 3] Japanese Translation of PCT International Application No.

5 H11-505377

[Patent Document 4] Japanese Published Patent Application No. 2000-150900

[Patent Document 5] Japanese Published Patent Application No. 2004-103957 [0007]

[Non-Patent Document 1] M. W. Prins, K. O. Grosse-Holz, G. Muller, J. F. M. Cillessen,

J. B. Giesbers, R. P. Weening, and R. M. Wolf, "A ferroelectric transparent thin-film transistor", *Appl. Phys. Lett.*, 17 June 1996, Vol.68, pp.3650-3652

[Non-Patent Document 2] M. Nakamura, N. Kimizuka, and T. Mohri, "The Phase Relations in the In<sub>2</sub>O<sub>3</sub>-Ga<sub>2</sub>ZnO<sub>4</sub>-ZnO System at 1350 °C", *J. Solid State Chem.*, 1991, Vol.93, pp.298-315

[Non-Patent Document 3] N. Kimizuka, M. Isobe, and M. Nakamura, "Syntheses and Single-Crystal Data of Homologous Compounds, In<sub>2</sub>O<sub>3</sub>(ZnO)<sub>m</sub> (m = 3, 4, and 5), InGaO<sub>3</sub>(ZnO)<sub>3</sub>, and Ga<sub>2</sub>O<sub>3</sub>(ZnO)<sub>m</sub> (m = 7, 8, 9, and 16) in the In<sub>2</sub>O<sub>3</sub>-ZnGa<sub>2</sub>O<sub>4</sub>-ZnO System", J. Solid State Chem., 1995, Vol.116, pp.170-178

[Non-Patent Document 4] M. Nakamura, N. Kimizuka, T. Mohri, and M. Isobe,

"Syntheses and crystal structures of new homologous compounds, indium iron zinc oxides (InFeO<sub>3</sub>(ZnO)<sub>m</sub>) (m: natural number) and related compounds", KOTAI BUTSURI (SOLID STATE PHYSICS), 1993, Vol. 28, No. 5, pp. 317-327

[Non-Patent Document 5] K. Nomura, H. Ohta, K. Ueda, T. Kamiya, M. Hirano, and H. Hosono, "Thin-film transistor fabricated in single-crystalline transparent oxide semiconductor", *SCIENCE*, 2003, Vol. 300, pp. 1269-1272

[Non-Patent Document 6] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors", *NATURE*, 2004, Vol.432, pp.488-492

# 30 DISCLOSURE OF INVENTION [0008]

25

Also in the case of a transistor including an oxide semiconductor, it is important to miniaturize the transistor in order to achieve high-speed operation, low power consumption, cost reduction, or the like of the transistor.

[0009]

5

10

Meanwhile, however, a defect caused when a transistor is miniaturized is a major problem. For example, such a problem due to miniaturization of a transistor is that a mask used in processing a conductive layer into a wiring or an electrode is misaligned, so that a transistor cannot be manufactured according to designed dimension. Particularly when a gate electrode is formed in manufacture of a top-gate transistor, it is preferable to form the gate electrode in a region which is over an oxide semiconductor layer and sandwiched between a source electrode and a drain electrode; however, it is difficult to form the gate electrode precisely in the region because the region is significantly narrowed by miniaturization of the transistor.

[0010]

15

When a wide gate electrode is formed so as to sufficiently overlap with a region which is over an oxide semiconductor layer and sandwiched between a source electrode and a drain electrode, a region where the gate electrode overlaps with the source electrode or the drain electrode of the transistor is excessively large. Thus, parasitic capacitance might be increased.

20 [0011]

25

30

It is known that a transistor including an oxide semiconductor has a lower off-state current than a transistor including silicon at room temperature. However, when a gate electrode is misaligned or parasitic capacitance of a transistor is increased as described above, it is not possible to make use of characteristics of a transistor including an oxide semiconductor, which is typified by a low off-state current. On the contrary, performance and yield of a semiconductor device using the transistor might be decreased.

[0012]

In view of the above, it is an object of one embodiment of the disclosed invention to provide a method for manufacturing a semiconductor device, which enables miniaturization and reduction of defects.

[0013]

One embodiment of the disclosed invention is a method for manufacturing a semiconductor device, which includes the following steps. An oxide semiconductor layer, a source electrode and a drain electrode which are in contact with the oxide semiconductor layer, an insulating layer over the source electrode, and an insulating layer over the drain electrode are formed over an insulating surface. A gate insulating layer is formed over the oxide semiconductor layer, the source electrode, the drain electrode, and the insulating layer. A conductive layer is formed over the gate insulating layer so as to overlap with at least part of a region sandwiched between the source electrode and the drain electrode. An insulating film is formed so as to cover the conductive layer. The insulating film is processed so that at least part of a region of the conductive layer, which overlaps with the source electrode or the drain electrode, is exposed. The exposed region of the conductive layer is etched to form a gate electrode overlapping with at least part of the region sandwiched between the source electrode and the drain electrode, in a self-aligned manner.

[0014]

5

10

15

20

25

30

In the above, it is preferable that a portion of the gate electrode, which is over the uppermost surface of the gate insulating layer, do not overlap with the source electrode and the drain electrode.

[0015]

Another embodiment of the disclosed invention is a method for manufacturing a semiconductor device, which includes the following steps. An oxide semiconductor layer, a source electrode and a drain electrode which are in contact with the oxide semiconductor layer, an insulating layer over the source electrode, and an insulating layer over the drain electrode are formed over an insulating surface. A gate insulating layer is formed over the oxide semiconductor layer, the source electrode, the drain electrode, and the insulating layer. A conductive layer is formed over the gate insulating layer so as to overlap with at least part of a region sandwiched between the source electrode and the drain electrode. The conductive layer is processed so that at least part of a region of the gate insulating layer, which overlaps with the source electrode or the drain electrode, is exposed in order to form a gate electrode overlapping with at least part of the region sandwiched between the source electrode and the drain electrode, in a self-aligned manner.

[0016]

In the above, the top surface of the gate electrode is preferably at a level lower than that of the uppermost surface of the gate insulating layer.

[0017]

5

10

15

20

25

30

The source electrode and the drain electrode may be in contact with at least part of the top surface of the oxide semiconductor layer, or the oxide semiconductor layer may be in contact with at least parts of the top surfaces of the source electrode and the drain electrode. Further, part of the conductive layer, which is left in formation of the gate electrode, may be processed to form a wiring. The distance between the edges of the source electrode and the drain electrode is preferably greater than or equal to 10 nm and less than or equal to 200 nm.

[0018]

Note that semiconductor devices herein refer to general devices which function by utilizing semiconductor characteristics. For example, a display device, a storage device, an integrated circuit, and the like are included in the category of the semiconductor device.

[0019]

In the above semiconductor devices, a semiconductor is not limited to an oxide semiconductor. For example, an amorphous semiconductor, a microcrystalline semiconductor, a polycrystalline semiconductor, a single crystal semiconductor, or the like made of silicon, germanium, silicon germanium, silicon carbide, gallium arsenide, or the like may be used.

[0020]

In this specification and the like, the terms "over" and "below" do not necessarily mean "directly on" and "directly under", respectively, in the description of a positional relationship between components. For example, the expression "a gate electrode over a gate insulating layer" can mean the case where there is an additional component between the gate insulating layer and the gate electrode.

[0021]

In addition, in this specification and the like, the term such as an "electrode" or a "wiring" does not limit a function of a component. For example, an "electrode" is

used as part of a "wiring" in some cases, and vice versa. Furthermore, the term "electrode" or "wiring" can include the case where a plurality of "electrodes" or "wirings" are formed in an integrated manner.

[0022]

5

10

15

20

30

Functions of a "source" and a "drain" are sometimes replaced with each other when a transistor of opposite polarity is used or when the direction of flow of current is changed in circuit operation, for example. Therefore, the terms "source" and "drain" can be used to denote the drain and the source, respectively, in this specification.

[0023]

Note that in this specification and the like, the expression "electrically connected" includes the case where components are connected through an "object having any electric function". There is no particular limitation on an "object having any electric function" as long as electric signals can be transmitted and received between components that are connected through the object. Examples of an "object having any electric function" are a switching element such as a transistor, a resistor, an inductor, a capacitor, and elements with a variety of functions as well as an electrode and a wiring.

[0024]

According to one embodiment of the disclosed invention, in a miniaturized transistor, a gate electrode can be formed in a region which is over an oxide semiconductor layer and sandwiched between a source electrode and a drain electrode precisely and easily and the gate electrode can be prevented from overlapping with the source electrode and the drain electrode, so that an increase in parasitic capacitance can be suppressed.

25 [0025]

With such an effect, a problem accompanied with miniaturization can be solved. As a result, the size of a transistor can be sufficiently reduced. When the size of the transistor is sufficiently reduced, an area occupied by a semiconductor device is also reduced, which leads to an increase in the number of semiconductor devices manufactured from one substrate. Accordingly, the manufacturing cost of the semiconductor device can be reduced. Further, since the semiconductor device is

downsized, a semiconductor device which is substantially the same as a conventional semiconductor device in size and has a further improved function can be realized. Furthermore, effects of high-speed operation, low power consumption, and the like of a transistor can be obtained in accordance with a reduction in channel length. Thus, miniaturization of a transistor including an oxide semiconductor can be achieved according to one embodiment of the disclosed invention, and various effects accompanied with the miniaturization can be obtained.

[0026]

As described above, according to one embodiment of the disclosed invention, a method for manufacturing a semiconductor device, which enables miniaturization and reduction of defects, can be provided.

## BRIEF DESCRIPTION OF DRAWINGS [0027]

5

10

15

20

25

30

In the accompanying drawings:

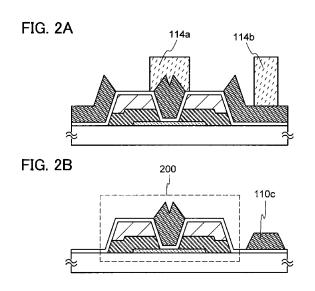

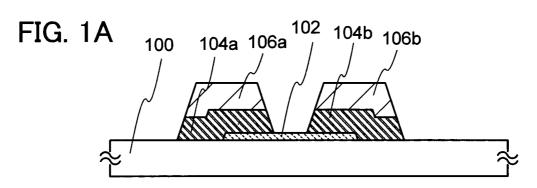

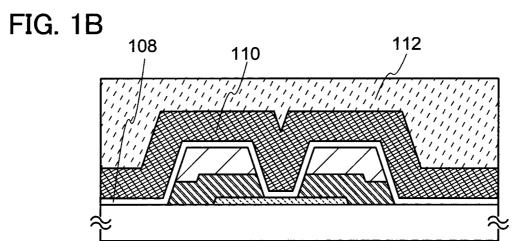

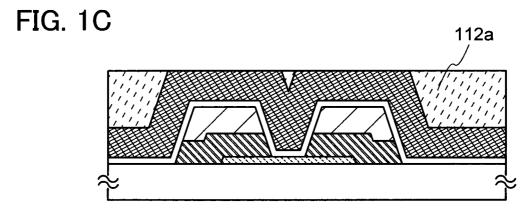

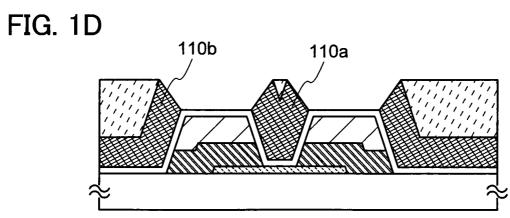

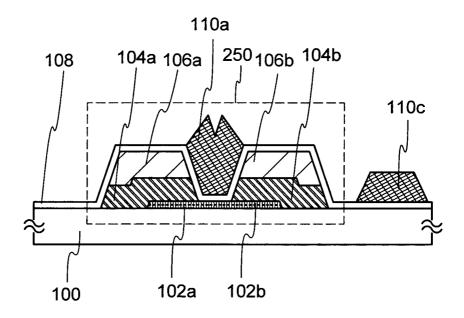

FIGS. 1A to 1D are cross-sectional views relating to manufacturing steps of a semiconductor device;

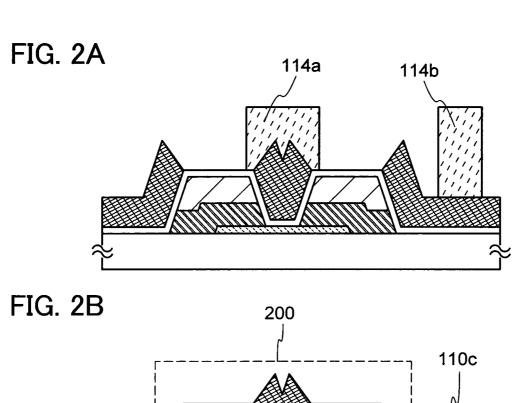

FIGS. 2A and 2B are cross-sectional views relating to manufacturing steps of a semiconductor device;

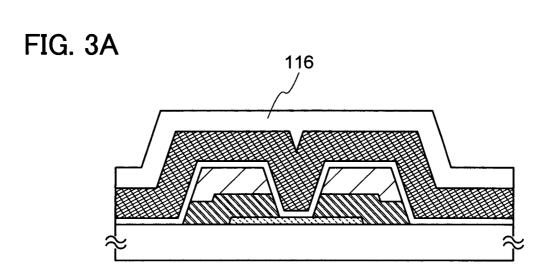

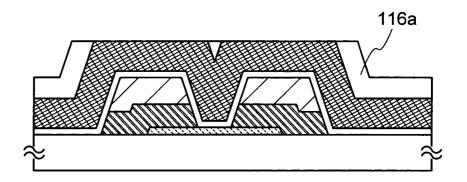

FIGS. 3A and 3B are cross-sectional views relating to manufacturing steps of a semiconductor device;

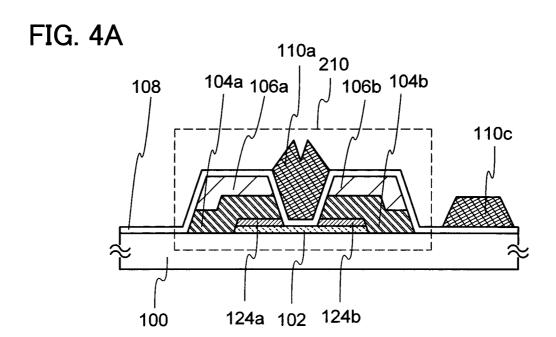

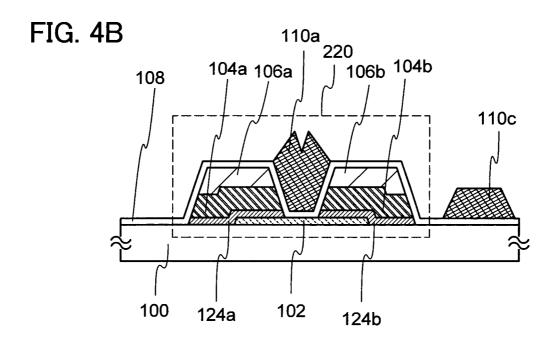

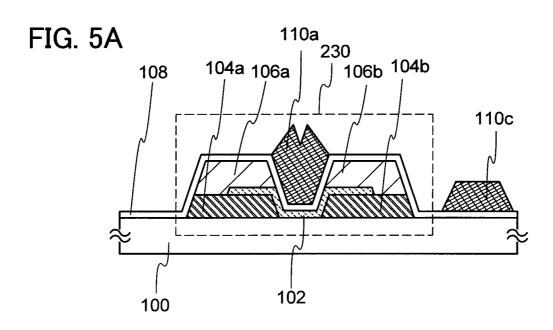

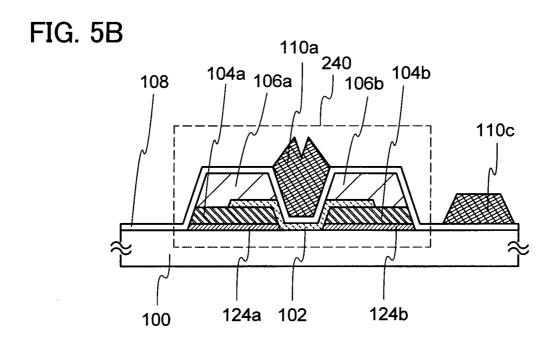

FIGS. 4A and 4B are cross-sectional views of semiconductor devices;

FIGS. 5A and 5B are cross-sectional views of semiconductor devices;

FIGS. 6A to 6C are cross-sectional views relating to manufacturing steps of a semiconductor device;

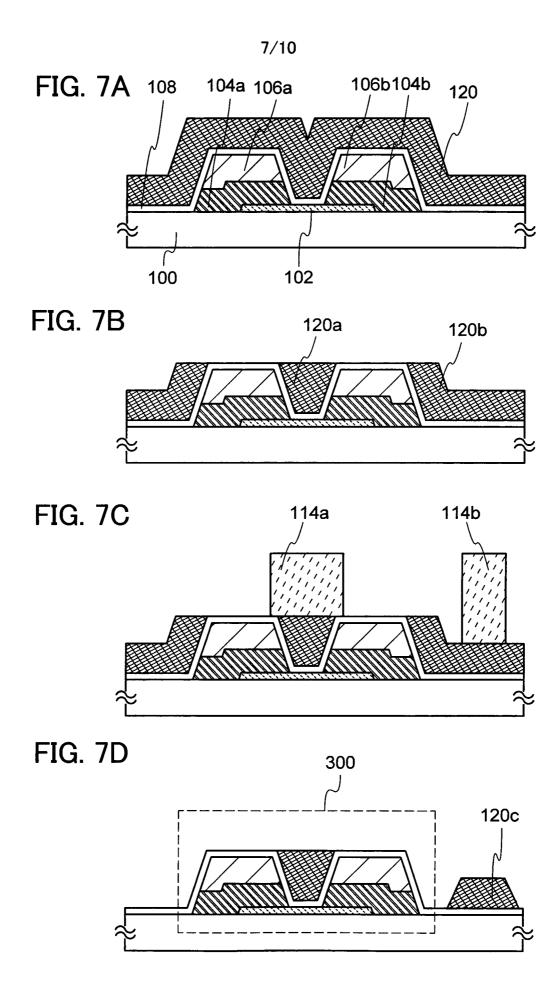

FIGS. 7A to 7D are cross-sectional views relating to manufacturing steps of a semiconductor device;

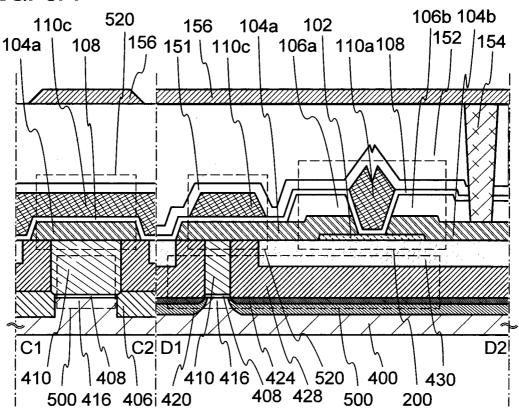

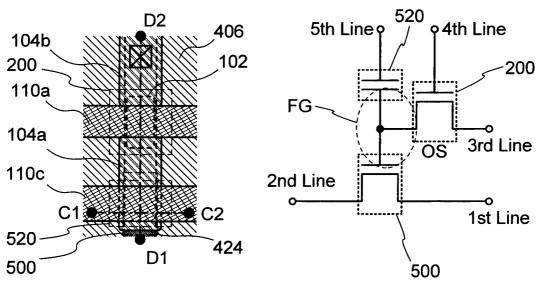

FIGS. 8A, 8B, and 8C are a cross-sectional view, a top view, and a circuit diagram of a semiconductor device, respectively;

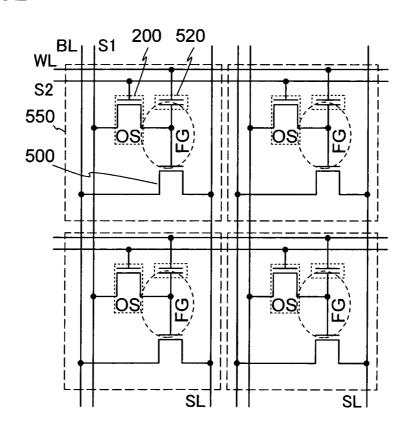

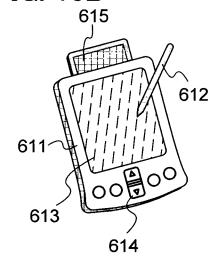

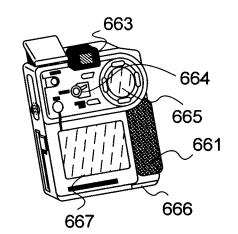

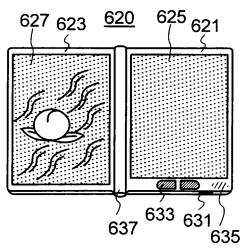

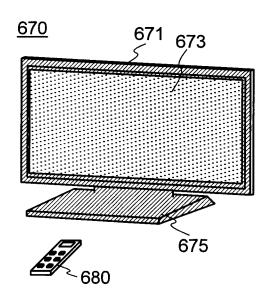

FIGS. 9A and 9B are circuit diagrams of semiconductor devices; and FIGS. 10A to 10F are examples of electronic devices.

## BEST MODE FOR CARRYING OUT THE INVENTION [0028]

Hereinafter, embodiments of the present invention will be described with reference to the drawings. Note that the present invention is not limited to the following description and it will be readily appreciated by those skilled in the art that modes and details can be modified in various ways without departing from the spirit and the scope of the present invention. Therefore, the present invention should not be construed as being limited to the description in the following embodiments.

[0029]

Note that the position, the size, the range, or the like of each structure illustrated in drawings and the like is not accurately represented in some cases for simplification. Therefore, the disclosed invention is not necessarily limited to the position, the size, the range, or the like disclosed in the drawings and the like.

[0030]

In this specification and the like, ordinal numbers such as "first", "second", and "third" are used in order to avoid confusion among components, and the terms do not mean limitation of the number of components.

[0031]

5

10

15

20

25

30

(Embodiment 1)

In this embodiment, embodiments of a semiconductor device and a method for manufacturing the semiconductor device will be described with reference to FIGS. 1A to 6C.

[0032]

[0033]

FIGS. 1A to 1D, FIGS. 2A and 2B, and FIGS. 3A and 3B are cross-sectional views illustrating manufacturing steps of a transistor 200 as an example of a method for manufacturing a semiconductor device according to one embodiment of the disclosed invention. Here, the transistor 200 in FIG. 2B includes, over a substrate 100, an oxide semiconductor layer 102, a source electrode 104a, a drain electrode 104b, an insulating layer 106a, an insulating layer 106b, a gate insulating layer 108, and a gate electrode 110a. In addition, a wiring 110c including the same material as the gate electrode 110a is formed over the gate insulating layer 108.

Here, the channel length L of the transistor 200 is preferably greater than or equal to 10 nm and less than or equal to 200 nm, more preferably greater than or equal to 20 nm and less than or equal to 100 nm. Thus, the channel length L is made small in order to miniaturize the transistor, so that an increase in operation speed and a reduction in power consumption of the transistor can be achieved. Note that in this specification, the channel length L depends on the distance between the edges of the source electrode 104a and the drain electrode 104b.

[0034]

5

10

15

20

25

30

The gate electrode 110a provided over the gate insulating layer 108 overlaps with at least part of a region which is over the oxide semiconductor layer 102 and sandwiched between the source electrode 104a and the drain electrode 104b. Further, it is preferable that a portion of the gate electrode 110a, which is over the uppermost surface of the gate insulating layer 108, do not overlap with the source electrode 104a and the drain electrode 104b. With such a structure, the gate electrode 110a can be precisely formed in the region which is over the oxide semiconductor layer 102 and sandwiched between the source electrode 104a and the drain electrode 104b, and an increase in parasitic capacitance can be suppressed. Therefore, the transistor 200 can have desired transistor characteristics as designed. Note that in this specification, the uppermost surface of a gate insulating layer refers to part of a surface of the gate insulating layer, which overlaps with a source electrode or a drain electrode and is parallel with a substrate. In the case where each of the source electrode 104a, the drain electrode 104b are tapered, and a portion of the gate electrode 110a, which is below the uppermost surface of the gate insulating layer 108, is inversely tapered, the inverse tapered portion of the gate electrode 110a, which is below the uppermost surface of the gate insulating layer 108, may overlap with the source electrode 104a and the drain electrode 104b. In that case, the portion of the gate electrode 110a, which is over the uppermost surface of the gate insulating layer 108, may overlap with the source electrode 104a and the drain electrode 104b.

[0035]

An example of a manufacturing process of the transistor 200 in FIG. 2B will be described with reference to FIGS. 1A to 1D, FIGS. 2A and 2B, and FIGS. 3A and 3B. [0036]

First, the oxide semiconductor layer 102 and the source electrode 104a and the drain electrode 104b which are in contact with the oxide semiconductor layer 102 are formed over the substrate 100 having an insulating surface (see FIG. 1A). In the structure illustrated in FIG. 1A, after the oxide semiconductor layer 102 is formed over the substrate 100, a conductive layer is formed and etched to form the source electrode 104a and the drain electrode 104b so that they are partly in contact with parts of the top surface of the oxide semiconductor layer 102.

[0037]

5

10

15

20

25

30

Although there is no particular limitation on a material or the like of the substrate 100, it is necessary that the substrate have at least heat resistance to heat treatment performed later. For example, a glass substrate, a ceramic substrate, a quartz substrate, or a sapphire substrate can be used as the substrate 100. Alternatively, a single crystal semiconductor substrate or a polycrystalline semiconductor substrate made of silicon, silicon carbide, or the like, a compound semiconductor substrate made of silicon germanium or the like, an SOI substrate, or the like may be used as the substrate 100. Still alternatively, any of these substrates further provided with a semiconductor element may be used as the substrate 100.

[0038]

A flexible substrate may alternatively be used as the substrate 100. In the case where the transistor is provided over a flexible substrate, for example, the transistor can be directly formed over the flexible substrate.

[0039]

Here, a base insulating layer is preferably formed over the substrate 100 before the oxide semiconductor layer 102 is formed. The base insulating layer can be formed using a material and a method similar to those of the gate insulating layer 108 to be described later.

[0040]

As a material used for the oxide semiconductor layer 102, any of the following materials can be used: a four-component metal oxide such as an In-Sn-Ga-Zn-O-based material; three-component metal oxides such as an In-Ga-Zn-O-based material, an In-Sn-Zn-O-based material, an In-Al-Zn-O-based material, an Sn-Ga-Zn-O-based material;

two-component metal oxides such as an In-Zn-O-based material, a Sn-Zn-O-based material, an Al-Zn-O-based material, a Zn-Mg-O-based material, a Sn-Mg-O-based material, an In-Mg-O-based material, and an In-Ga-O-based material; and single-component metal oxides such as an In-O-based material, a Sn-O-based material, and a Zn-O-based material. In addition, the above material may contain SiO<sub>2</sub>. Here, for example, an In-Ga-Zn-O-based material refers to an oxide film containing indium (In), gallium (Ga), and zinc (Zn), and there is no particular limitation on the composition ratio. Further, the In-Ga-Zn-O-based material may contain an element other than In, Ga, and Zn.

10 [0041]

5

The oxide semiconductor layer 102 may be a thin film including a material expressed by the chemical formula,  $InMO_3(ZnO)_m$  (m > 0). Here, M represents one or more metal elements selected from Ga, Al, Mn, and Co. For example, M may be Ga, Ga and Al, Ga and Mn, Ga and Co, or the like.

15 [0042]

The thickness of the oxide semiconductor layer 102 is desirably greater than or equal to 3 nm and less than or equal to 30 nm. This is because the transistor might possibly be normally on when the oxide semiconductor layer 102 is too thick (e.g., the thickness is 50 nm or more).

20 [0043]

25

30

The oxide semiconductor layer is preferably formed by a method in which impurities such as hydrogen, water, a hydroxyl group, and hydride are less likely to enter the oxide semiconductor layer. For example, a sputtering method can be used.

[0044]

In this embodiment, the oxide semiconductor layer is formed by a sputtering method using an In-Ga-Zn-O-based oxide semiconductor deposition target.

[0045]

As the In-Ga-Zn-O-based oxide semiconductor deposition target, for example, an oxide semiconductor deposition target with the following composition ratio can be used: the composition ratio of In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO is 1:1:1 [molar ratio]. Note that it is not necessary to limit the material and the composition of the oxide semiconductor deposition target to the above. For example, an oxide semiconductor deposition target

with the following composition ratio may alternatively be used: the following composition ratio of In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO is 1:1:2 [molar ratio]. [0046]

In the case where an In-Zn-O-based material is used for the oxide semiconductor, a target with the following composition ratio is used: the composition ratio of In:Zn is 50:1 to 1:2 in an atomic ratio (In<sub>2</sub>O<sub>3</sub>:ZnO = 25:1 to 1:4 in a molar ratio), preferably 20:1 to 1:1 in an atomic ratio (In<sub>2</sub>O<sub>3</sub>:ZnO = 10:1 to 1:2 in a molar ratio), more preferably 15:1 to 1.5:1 in an atomic ratio (In<sub>2</sub>O<sub>3</sub>:ZnO = 15:2 to 3:4 in a molar ratio). For example, a target used for the formation of an In-Zn-O-based oxide semiconductor has the following atomic ratio: the atomic ratio of In: Zn: O is X:Y:Z, where Z > 1.5X + Y.

[0047]

5

10

15

20

25

30

The fill rate of the oxide semiconductor deposition target is higher than or equal to 90 % and lower than or equal to 100 %, preferably higher than or equal to 95 % and lower than or equal to 99.9 %. This is because with the use of the oxide semiconductor deposition target with a high fill rate, a dense oxide semiconductor layer can be formed.

[0048]

The deposition atmosphere may be a rare gas (typically argon) atmosphere, an oxygen atmosphere, or a mixed atmosphere containing a rare gas and oxygen. Further, in order to prevent impurities such as hydrogen and water from entering the oxide semiconductor layer, it is preferable to use an atmosphere of a high-purity gas in which impurities such as hydrogen and water are sufficiently removed.

[0049]

For example, the oxide semiconductor layer can be formed as follows. [0050]

First, the substrate 100 is placed in a deposition chamber kept under reduced pressure, and heating is performed so that the substrate temperature is higher than 200 °C and lower than or equal to 500 °C, preferably higher than 300 °C and lower than or equal to 500 °C, more preferably higher than or equal to 350 °C and lower than or equal to 450 °C.

[0051]

5

10

15

20

25

Then, a high-purity gas in which impurities such as hydrogen and water are sufficiently removed is introduced into the deposition chamber from which remaining moisture is being removed, and the oxide semiconductor layer is formed over the substrate 100 with the use of the oxide semiconductor deposition target. To remove moisture remaining in the deposition chamber, an entrapment vacuum pump such as a cryopump, an ion pump, or a titanium sublimation pump is desirably used. Further, an evacuation means may be a turbo pump provided with a cold trap. In the deposition chamber which is evacuated with the cryopump, impurities such as hydrogen and water (more preferably, also a compound containing a carbon atom), and the like are removed, whereby the concentration of impurities such as hydrogen and water in the oxide semiconductor layer formed in the deposition chamber can be reduced.

[0052]

PCT/JP2011/066622

When the substrate temperature is low (e.g., lower than or equal to 100 °C) during deposition, impurities such as hydrogen and water might enter the oxide semiconductor layer; therefore, the substrate 100 is preferably heated at the above temperature. When the oxide semiconductor layer is formed with the substrate 100 heated at the above temperature, the substrate temperature is increased; thus, hydrogen bonds are cut due to heat and are less likely to be taken into the oxide semiconductor layer. Therefore, the oxide semiconductor layer is formed with the substrate 100 heated at the above temperature, whereby the concentration of impurities such as hydrogen and water in the oxide semiconductor layer can be sufficiently reduced. Moreover, damage due to sputtering can be reduced.

Note that, as a method for measuring the amount of water in the oxide semiconductor layer, thermal desorption spectroscopy (TDS) is given. For example, when the temperature is increased from room temperature to approximately 400 °C, elimination of water, hydrogen, a hydroxyl group, and the like in the oxide semiconductor layer can be observed in the range of approximately 200 °C to 300 °C.

30 [0054]

An example of the deposition condition is as follows: the distance between the

substrate and the target is 60 mm, the pressure is 0.4 Pa, the direct-current (DC) power is 0.5 kW, the substrate temperature is 400 °C, and the deposition atmosphere is an oxygen atmosphere (the flow rate of the oxygen is 100 %). Note that a pulse direct current power source is preferably used because powdery substances (also referred to as particles or dust) generated in deposition can be reduced and the film thickness can be even.

[0055]

5

10

Note that before the oxide semiconductor layer is formed by a sputtering method, powdery substances (also referred to as particles or dust) attached on a surface of the substrate 100 are preferably removed by reverse sputtering in which an argon gas is introduced and plasma is generated. The reverse sputtering refers to a method in which a voltage is applied to a substrate side to generate plasma in the vicinity of the substrate to modify a surface. Note that instead of argon, a gas such as nitrogen, helium, or oxygen may be used.

15 [0056]

The oxide semiconductor layer can be processed by being etched after a mask having a desired shape is formed over the oxide semiconductor layer. The mask can be formed by a method such as photolithography or an ink-jet method. For the etching of the oxide semiconductor layer, either wet etching or dry etching may be employed. It is needless to say that both of them may be employed in combination.

[0057]

20

25

30

The oxide semiconductor layer 102 formed in such a manner may be subjected to heat treatment. Impurities such as hydrogen and water in the oxide semiconductor layer 102 are further reduced through the heat treatment, so that the structure of the oxide semiconductor layer 102 is modified and defect levels in an energy gap can be reduced.

[0058]

The heat treatment is performed in an inert gas atmosphere at higher than or equal to 250 °C and lower than or equal to 700 °C, preferably higher than or equal to 450 °C and lower than or equal to 600 °C or lower than the strain point of the substrate. As the inert gas atmosphere, an atmosphere that contains nitrogen or a rare gas (e.g.,

helium, neon, or argon) as its main component and does not contain impurities such as hydrogen and water is desirably used. For example, the purity of nitrogen or a rare gas such as helium, neon, or argon introduced into a heat treatment apparatus is 6N (99.9999 %) or higher, preferably 7N (99.99999 %) or higher (that is, the impurity concentration is 1 ppm or lower, preferably 0.1 ppm or lower).

[0059]

5

10

15

20

25

30

The heat treatment can be performed in such a manner that, for example, an object to be heated is introduced into an electric furnace in which a resistance heating element or the like is used, and heated in a nitrogen atmosphere at 450 °C for an hour. The oxide semiconductor layer 102 is not exposed to the air during the heat treatment so that entry of impurities such as hydrogen and water can be prevented.

[0060]

The above heat treatment can be referred to as dehydration treatment, dehydrogenation treatment, or the like because of its advantageous effect of removing impurities such as hydrogen and water. The heat treatment can be performed at the timing, for example, after the oxide semiconductor layer is formed. Such dehydration treatment or dehydrogenation treatment may be conducted once or plural times. [0061]

Next, treatment for supplying oxygen (also referred to as oxygen doping treatment, or the like) is desirably performed on the oxide semiconductor layer 102. As the treatment for supplying oxygen, heat treatment in an oxygen atmosphere, treatment with oxygen plasma, and the like are given. Alternatively, oxygen may be added by performing exposure to an oxygen ion accelerated by an electric field. [0062]

Note that an electric bias may be applied to the substrate in order to add oxygen more favorably.

[0063]

By performing oxygen doping treatment on the oxide semiconductor layer 102, the oxygen can be contained either or both in the oxide semiconductor layer 102 or/and in the vicinity of the interface of the oxide semiconductor layer 102. In that case, the oxygen content is desirably approximately higher than that in the stoichiometric ratio of

the oxide semiconductor layer.

[0064]

Note that heat treatment may be performed on the oxide semiconductor layer 102 which has been subjected to the oxygen doping treatment. The heat treatment is performed at a temperature higher than or equal to 250 °C and lower than or equal to 700 °C, preferably higher than or equal to 400 °C and lower than or equal to 600 °C or lower than the strain point of the substrate.

[0065]

5

10

15

20

30

Through the heat treatment, water, a hydroxide (OH), and the like generated by reaction between oxygen and hydrogen contained in the oxide semiconductor layer can be removed from the oxide semiconductor layer. Further, through this heat treatment, hydrogen or the like that has entered the oxide semiconductor layer 102 or the like during the above oxygen doping treatment can also be removed. The heat treatment may be performed in an atmosphere of nitrogen, oxygen, an ultra-dry air (an air where the moisture content is 20 ppm (-55 °C by conversion into a dew point) or less, preferably 1 ppm or less, more preferably 10 ppb or less when measurement is performed using a dew-point instrument of a cavity ring-down spectroscopy (CRDS) system), a rare gas (e.g., argon or helium), or the like in which water, hydrogen, and the like are sufficiently reduced. In particular, the heat treatment is preferably performed in an atmosphere containing oxygen. The purity of nitrogen, oxygen, or the rare gas which is introduced into the heat treatment apparatus is set to preferably 6N (99.9999 %) or higher (that is, the impurity concentration is 1 ppm or lower), more preferably 7N (99.99999 %) or higher (that is, the impurity concentration is 0.1 ppm or lower).

25 [0066]

Note that the timing of the oxygen doping treatment is not limited to the timing described above. However, the oxygen doping treatment is desirably performed after the heat treatment for dehydration or the like.

[0067]

The source electrode 104a and the drain electrode 104b are formed in such a manner that a conductive layer is formed over the oxide semiconductor layer 102 by a

sputtering method, a vacuum evaporation method, or the like and processed. The source electrode 104a and the drain electrode 104b are thus formed, thereby being in contact with parts of the top surface of the oxide semiconductor layer 102. When the thicknesses of the source electrode 104a and the drain electrode 104b are increased, there are not only an effect of reducing the resistance of the electrodes and wirings thereof but also an effect of reducing the resistance of the gate electrode 110a because the thickness of the gate electrode 110a can also be increased as described later. Meanwhile, parasitic capacitance between the gate electrode 110a and the source and drain electrodes 104a and 104b increases. Thus, here, the thicknesses of the source electrode 104a and the drain electrode 104b are each greater than or equal to 50 nm and less than or equal to 500 nm, for example.

Note that the channel length L of the transistor depends on the distance between the edges of the source electrode 104a and the drain electrode 104b which are formed here. The channel length L of the transistor is preferably greater than or equal to 10 nm and less than or equal to 200 nm, more preferably greater than or equal to 20 nm and less than or equal to 100 nm.

[0069]

[0068]

5

10

15

20

25

As the conductive layer used for the source electrode 104a and the drain electrode 104b, for example, a metal film containing an element selected from aluminum, chromium, copper, tantalum, titanium, molybdenum, and tungsten, or a metal nitride film containing any of the above elements as its component (e.g., a titanium nitride film, a molybdenum nitride film, or a tungsten nitride film) can be used. The source electrode 104a and the drain electrode 104b may be formed to have a single-layer structure or a layered structure. Alternatively, a structure may be employed in which a high-melting-point metal film of titanium, molybdenum, tungsten, or the like or a metal nitride film of any of these elements (a titanium nitride film, a molybdenum nitride film, or a tungsten nitride film) may be provided over and/or below a metal film of aluminum, copper, or the like.

30 [0070]

Alternatively, the conductive layer used for the source electrode 104a and the drain electrode 104b may be formed using a conductive metal oxide. As the

conductive metal oxide, indium oxide (In<sub>2</sub>O<sub>3</sub>), tin oxide (SnO<sub>2</sub>), zinc oxide (ZnO), an indium oxide-tin oxide alloy (In<sub>2</sub>O<sub>3</sub>-SnO<sub>2</sub>, which is abbreviated to ITO), an indium oxide-zinc oxide alloy (In<sub>2</sub>O<sub>3</sub>-ZnO), or any of these metal oxide materials containing silicon oxide can be used.

5 [0071]

The conductive layer can be processed by being etched after a mask having a desired shape is formed over the conductive layer. As the above mask, a resist mask or the like can be used. Ultraviolet light, KrF laser light, ArF laser light, or the like is preferably used for light exposure in formation of the resist mask.

10 [0072]

15

20

25

30

In the case where the channel length L is less than 25 nm, the light exposure at the time of forming the resist mask is preferably performed using, for example, extreme ultraviolet light having an extremely short wavelength of several nanometers to several tens of nanometers. In the light exposure with extreme ultraviolet light, the resolution is high and the focus depth is large. Thus, the channel length L of the transistor can be reduced, and the operation speed of a circuit can be increased.

An etching step may be performed with the use of a resist mask formed using a so-called multi-tone mask. A resist mask formed using a multi-tone mask has a plurality of thicknesses and can be further changed in shape by ashing; thus, such a resist mask can be used in a plurality of etching steps for different patterns. Therefore, a resist mask for at least two kinds of patterns can be formed using a multi-tone mask, resulting in simplification of the process.

[0074]

Either wet etching or dry etching may be employed for the etching of the conductive layer to be the source electrode 104a and the drain electrode 104b; dry etching is preferably employed in terms of microfabrication. The etching conditions (e.g., an etching gas or an etching solution, etching time, and temperature) are set as appropriate depending on the material so that the conductive layer can be etched to have a desired shape. In the case where the conductive layer to be the source electrode 104a and the drain electrode 104b is etched by dry etching, chlorine (Cl<sub>2</sub>), boron trichloride (BCl<sub>3</sub>), silicon tetrachloride (SiCl<sub>4</sub>), tetrafluoromethane (CF<sub>4</sub>), sulfur hexafluoride (SF<sub>6</sub>),

nitrogen trifluoride (NF<sub>3</sub>), or the like can be used as an etching gas. Further, a mixed gas containing some of the above gases may be used. Furthermore, a rare gas (helium (He) or argon (Ar)), oxygen, or the like may be added to the above gas.

[0075]

As illustrated in FIG. 1A, the source electrode 104a and the drain electrode 104b may be tapered. The taper angle is larger than or equal to 45° and smaller than 90° and can preferably be larger than or equal to 60° and smaller than or equal to 80°. When the source electrode 104a and the drain electrode 104b are tapered as described above, coverage of the source electrode 104a and the drain electrode 104b with the gate insulating layer 108 which is formed later can be improved and disconnection of the gate insulating layer 108 can be prevented. Note that the taper angle refers to a tilt angle formed by a side surface and the bottom surface of a layer having a tapered shape (e.g., the source electrode 104a or the drain electrode 104b) in the case where the layer is observed from a direction perpendicular to a cross section thereof.

[0076]

5

10

15

20

25

30

Note that in the etching of the conductive layer, part of the oxide semiconductor layer 102 is etched, so that the oxide semiconductor layer 102 having a groove (recessed portion) is formed in some cases.

[0077]

After that, by plasma treatment using a gas such as  $N_2O$ ,  $N_2$ , or Ar, impurities such as hydrogen and water attached to a surface of an exposed portion of the oxide semiconductor layer 102 may be removed.

[0078]

Next, an insulating layer is formed so as to cover the oxide semiconductor layer 102, the source electrode 104a, and the drain electrode 104b and processed using a photomask, so that an insulating layer 106a and an insulating layer 106b are formed over the source electrode 104a and the drain electrode 104b, respectively (see FIG. 1A). [0079]

Here, the insulating layer 106a and the insulating layer 106b can be formed using a material such as silicon oxide, silicon nitride, silicon oxynitride, or silicon nitride oxide by a CVD method, a sputtering method, or the like. The thicknesses of

the insulating layer 106a and the insulating layer 106b are each preferably greater than or equal to 10 nm and less than or equal to 500 nm.

The insulating layer 106a and the insulating layer 106b are formed in such a manner that a resist mask is formed over an insulating layer and etching is performed using the resist mask. The resist mask can be formed by the same method as the method employed for formation of the source electrode 104a and the drain electrode 104b, and it is preferable to use the photomask used for formation of the source electrode 104a and the drain electrode 104b. Either wet etching or dry etching may be employed for the etching of the insulating layer; dry etching is preferably employed in terms of microfabrication. The etching conditions (e.g., an etching gas or an etching solution, etching time, and temperature) are set as appropriate depending on the material so that the insulating layer can be etched to have a desired shape. Note that dry etching is preferably employed in terms of reduction in channel length (L) of the transistor. As an etching gas used in dry etching, for example, a gas containing fluorine such as sulfur hexafluoride (SF<sub>6</sub>), nitrogen trifluoride (NF<sub>3</sub>), trifluoromethane (CHF<sub>3</sub>), or octafluorocyclobutane (C<sub>4</sub>F<sub>8</sub>), a mixed gas of tetrafluoromethane (CF<sub>4</sub>) and hydrogen, or the like can be used. Furthermore, a rare gas (e.g., helium (He), argon (Ar), or xenon (Xe)), carbon monoxide, carbon dioxide, or the like may be added to the above gas.

[0081]

[0080]

5

10

15

20

25

30

By thus forming the insulating layer 106a and the insulating layer 106b, a recessed portion in a region sandwiched between the source electrode 104a and the drain electrode 104b can be deep, so that the gate electrode 110a which is formed later can be sufficiently thick. Thus, loss of the gate electrode 110a which is formed later or significant reduction in thickness of the gate electrode 110a can be prevented. Accordingly, sufficient conductivity of the gate electrode 110a can be maintained. [0082]

Note that the insulating layer 106a and the insulating layer 106b are not necessarily formed. For example, in the case where the source electrode 104a and the drain electrode 104b are sufficiently thick, the insulating layer 106a and the insulating layer 106b are not necessarily formed because even when the insulating layer 106a and

the insulating layer 106b are not formed, the gate electrode 110a can be sufficiently thick.

[0083]

5

10

15

20

25

30

Note that the method is described here in which the source electrode 104a and the drain electrode 104b are formed and then the insulating layer 106a and the insulating layer 106b are formed; however, this embodiment is not limited thereto. For example, in the case where the source electrode 104a and the drain electrode 104b are formed in contact with parts of the top surface of the oxide semiconductor layer 102, after a conductive layer is formed over the oxide semiconductor layer 102 and an insulating layer is formed over the conductive layer, the insulating layer and the conductive layer are processed using one resist mask so that the insulating layer 106a, the insulating layer 106b, the source electrode 104a, and the drain electrode 104b can be formed. By forming the insulating layer 106a, the insulating layer 106b, the source electrode 104a, and the drain electrode 104b in such a manner, the edges of the insulating layer 106a and the insulating layer 106b can be substantially aligned with the edges of the source electrode 104a and the drain electrode 104b, respectively. Thus, misalignment between the insulating layer 106a and the source electrode 104a and between the insulating layer 106b and the drain electrode 104b can be prevented. Further, the number of photomasks can be reduced, resulting in cost reduction of the semiconductor device. Note that the expression "substantially aligned" does not always refer to exact alignment. For example, the expression "substantially aligned" includes a degree of alignment in a shape obtained by etching a plurality of layers with the use of one mask. [0084]

Next, the gate insulating layer 108 is formed over the oxide semiconductor layer 102, the source electrode 104a, the drain electrode 104b, the insulating layer 106a, and the insulating layer 106b (see FIG. 1B).

[0085]

For example, the gate insulating layer 108 is formed using a material such as silicon oxide, silicon nitride, silicon oxynitride, or silicon nitride oxide. The gate insulating layer 108 may be formed using a material containing gallium oxide. The material containing gallium oxide may further contain aluminum oxide; that is, a material containing aluminum gallium oxide or gallium aluminum oxide, or the like

may be used. Here, aluminum gallium oxide refers to a material in which the aluminum content is higher than the gallium content in atomic percent, and gallium aluminum oxide refers to a material in which the gallium content is higher than or equal to the aluminum content in atomic percent. Further, a material having a high dielectric constant, such as hafnium oxide, tantalum oxide, yttrium oxide, hafnium silicate (HfSi<sub>x</sub>O<sub>y</sub> (x > 0, y > 0)), hafnium silicate (HfSi<sub>x</sub>O<sub>y</sub> (x > 0, y > 0)) to which nitrogen is added, or hafnium aluminate (HfAl<sub>x</sub>O<sub>y</sub> (x > 0, y > 0)) to which nitrogen is added may be used. The gate insulating layer 108 can be formed to have a single-layer structure or a layered structure using any of the above materials.

10 [0086]

5

15

20

25

In the case where a gallium oxide film is used for the gate insulating layer 108, the composition of the gallium oxide film is preferably  $Ga_2O_{3+\alpha}$  ( $\alpha>0$ ). It is preferable that  $\alpha$  be greater than or equal to 3.04 and less than or equal to 3.09. Alternatively, in the case where an aluminum gallium oxide film is used for the gate insulating layer 108, the composition of the aluminum gallium oxide film is preferably  $Al_xGa_{2-x}O_{3+\alpha}$  (1< x< 2,  $\alpha>0$ ). Still alternatively, in the case where a gallium aluminum oxide film is used for the gate insulating layer 108, the gallium aluminum oxide film preferably has a composition of  $Al_xGa_{2-x}O_{3+\alpha}$  ( $0< x\le 1$ ,  $\alpha>0$ ) by being doped with oxygen.

In many cases, an oxide semiconductor material used for the oxide semiconductor layer contains gallium. Therefore, in the case where the gate insulating layer 108 is formed in contact with the oxide semiconductor layer with the use of a material containing gallium oxide, a favorable condition can be maintained at the interface between the oxide semiconductor layer and the gate insulating layer 108. For example, when the oxide semiconductor layer and an insulating layer containing gallium oxide are provided in contact with each other, an accumulation of hydrogen at the interface between the oxide semiconductor layer and the insulating layer can be reduced. This is because a material containing gallium oxide is compatible with an oxide semiconductor material.

30 [0088]

Note that, in the case where an element belonging to the same group as a

constituent element of the oxide semiconductor is used for the gate insulating layer 108, a similar effect can be obtained. That is, it is also effective to additionally use a material containing aluminum oxide or the like in formation of the gate insulating layer 108. Note that water is not likely to permeate aluminum oxide; therefore, it is preferable to use aluminum oxide in terms of preventing water from entering the oxide semiconductor layer. For example, the above material such as aluminum gallium oxide (or gallium aluminum oxide) containing gallium and aluminum may be used for the gate insulating layer 108. In that case, both the effect resulting from containing gallium and the effect resulting from containing aluminum can be obtained, which is preferable. For example, by providing an insulating layer containing aluminum gallium oxide in contact with the oxide semiconductor layer, water can be prevented from entering the oxide semiconductor layer and an accumulation of hydrogen at an interface between the oxide semiconductor layer and the insulating layer can be sufficiently reduced.

15 [0089]

5

10

20

25

30

The gate insulating layer 108 is preferably formed by a method with which impurities such as hydrogen and water do not enter the gate insulating layer 108. This is because when an impurity such as hydrogen or water is contained in the gate insulating layer 108, the impurity such as hydrogen or water enters the oxide semiconductor layer or oxygen in the oxide semiconductor layer is extracted by the impurity such as hydrogen or water, so that the oxide semiconductor layer might have lower resistance (have n-type conductivity). Therefore, the gate insulating layer 108 is preferably formed so as to contain as few impurities such as hydrogen and water as possible. For example, the gate insulating layer 108 is preferably formed by a sputtering method, and a high-purity gas in which impurities such as hydrogen and water are removed is preferably used as a sputtering gas used for deposition.

As a sputtering method, a DC sputtering method in which a direct current power source is used, a pulsed DC sputtering method in which a direct current bias is applied in a pulsed manner, an AC sputtering method, or the like can be employed.

[0091]

After formation of the gate insulating layer 108, heat treatment is desirably

performed in an inert gas atmosphere or an oxygen atmosphere. The temperature of the heat treatment is set to higher than or equal to 200 °C and lower than or equal to 450 °C, desirably higher than or equal to 250 °C and lower than or equal to 350 °C. For example, the heat treatment may be performed at 250 °C for an hour in a nitrogen atmosphere. By performing the heat treatment, variation in electrical characteristics of the transistor can be reduced. In the case where the gate insulating layer 108 contains oxygen, oxygen can be supplied to the oxide semiconductor layer 102 so that oxygen vacancies in the oxide semiconductor layer 102 are filled. In this sense, the heat treatment can also be referred to as heat treatment for supply of oxygen.

10 [0092]

[0093]

5

15

20

30

Note that in this embodiment, the heat treatment for supply of oxygen is performed after the gate insulating layer 108 is formed; however, the timing of the heat treatment for supply of oxygen is not limited thereto. For example, the heat treatment for supply of oxygen may be performed after the gate electrode 110a is formed. The heat treatment for supply of oxygen may be performed following heat treatment for dehydration or dehydrogenation.

As described above, the heat treatment for dehydration or dehydrogenation, and the oxygen doping treatment or the heat treatment for supply of oxygen are performed to reduce impurities and fill oxygen vacancies in the oxide semiconductor layer 102, whereby the oxide semiconductor layer 102 can be highly purified so as to contain elements (impurity elements) that are not main components of the oxide semiconductor layer 102 as few as possible. The oxide semiconductor layer 102 which has been highly purified contains extremely few carriers derived from donors.

25 [0094]

Next, a conductive layer 110 is formed over the gate insulating layer 108 so as to overlap with at least part of a region sandwiched between the source electrode 104a and the drain electrode 104b (see FIG. 1B).

[0095]

The conductive layer 110 is used to form the gate electrode 110a and the wiring 110c in a later step. The conductive layer 110 can be formed using a material similar

to that used for the conductive layer for formation of the source electrode 104a and the drain electrode 104b. Further, the conductive layer 110 can be formed by a PVD method or a CVD method and is formed such that part of the conductive layer fills a recessed portion sandwiched between the insulating layer 106a and the source electrode 104a, and the insulating layer 106b and the drain electrode 104b.

[0096]

Then, an insulating film 112 is formed so as to cover the conductive layer 110 (see FIG. 1B). The insulating film 112 functions as a mask used in etching the conductive layer 110. Processed in a later step so that the uppermost surface of the conductive layer 110 is exposed, the insulating film 112 is preferably a planarization insulating film having the top surface parallel to the substrate 100. Note that in this specification, the uppermost surface of the conductive layer 110 refers to part of a surface of the conductive layer 110, which overlaps with the source electrode 104a or the drain electrode 104b and is parallel to the substrate 100.

15 [0097]

5

10

20

25

The planarization insulating film used as the insulating film 112 can be formed using an organic material such as polyimide, an acrylic resin, a benzocyclobutene resin, polyamide, or an epoxy resin. Other than such organic materials, it is also possible to use a low-dielectric constant material (a low-k material), a siloxane-based resin, PSG (phosphosilicate glass), BPSG (borophosphosilicate glass), or the like. There is no particular limitation on the method of forming the insulating film 112, and the following method or means can be employed depending on the material: a method such as a sputtering method, an SOG method, a spin coating method, a dipping method, a spray coating method, or a droplet discharge method (e.g., an ink-jet method, screen printing, or offset printing), or a tool such as a doctor knife, a roll coater, a curtain coater, or a knife coater. Note that a siloxane-based resin is a resin including a Si-O-Si bond formed using a siloxane-based material as a starting material. The siloxane-based resin may include an organic group (e.g., an alkyl group or an aryl group) or a fluoro group as a substituent. Moreover, the organic group may include a fluoro group.

30 [0098]

Note that the insulating film functioning as a mask used in etching the conductive layer 110 is not necessarily a planarization insulating film. For example, in

the case where the insulating film is processed by CMP treatment or the like in a later step, an insulating film 116 which is not planarized may be formed over the conductive layer 110 as illustrated in FIG. 3A. The insulating film 116 can be formed using a material including an inorganic insulating material such as silicon oxide or silicon oxynitride.

[0099]

5

15

20

25

30

Then, the insulating film 112 is processed so that at least part of a region of the conductive layer 110, which overlaps with the source electrode 104a or the drain electrode 104b, is exposed. Thus, insulating film 112a is formed (see FIG. 1C).

10 [0100]

Here, from the entire top surface of the insulating film 112, the insulating film 112 is partly removed at an even rate. When the uppermost surface of the conductive layer 110 is exposed (or when a small portion of the conductive layer 110 is removed after the uppermost surface of the conductive layer 110 is exposed), this operation is stopped. Thus, the insulating film 112a can be formed. Such processing of the insulating film 112 can be performed by ashing treatment, etching treatment, or polishing treatment; the processing method may be selected as appropriate depending on the material of the insulating film 112.

[0101]

For the ashing treatment of the insulating film 112, for example, oxygen plasma ashing can be employed. The ashing treatment using oxygen plasma is performed in an oxygen atmosphere in such a manner that oxygen is made to be plasma by high frequency power or the like and the insulating film 112 is decomposed and removed by the oxygen made to be plasma. Thus, from the entire top surface of the insulating film 112, the insulating film 112 can be partly removed at an even rate. Further, when the insulating film 112 is partly removed in such a manner, generation of a residue of the insulating film 112 or a reaction product of the residue can be avoided. [0102]

Either wet etching or dry etching may be employed for the etching of the insulating film 112. The etching conditions (e.g., an etching gas or an etching solution, etching time, and temperature) are set as appropriate depending on the material so that the insulating film 112 can be etched to have a desired shape. In particular, the etching

conditions are set so that the etching selectivity of the insulating film 112 to the conductive layer 110 is sufficiently high.

[0103]

5

10

15

20

25

30

As the polishing treatment of the insulating film 112, for example, a chemical mechanical polishing (CMP) treatment can be employed. Here, the CMP treatment is treatment of planarizing a surface of an object to be processed by a combination of chemical and mechanical actions using the surface as a reference. In general, the CMP treatment is a method in which a polishing cloth is attached to a polishing stage, and the polishing stage and the object to be processed are each rotated or swung while a slurry (an abrasive) is supplied between the object to be processed and the polishing cloth, whereby the surface of the object to be processed is polished by chemical reaction between the slurry and the surface of the object to be processed and by action of mechanical polishing of the object to be processed with the polishing cloth.

In the case where the insulating film 116 which is not planarized is formed over the conductive layer 110 as illustrated in FIG. 3A, the insulating film 116 may be processed by the CMP treatment. When the insulating film 116 is processed by the CMP treatment, an insulating film 116a can be formed so that the uppermost surface of the conductive layer 110 is exposed as illustrated n FIG. 3B. Note that a step performed after the step in FIG. 3B can also be performed in a manner similar to that in formation of the insulating film 112.

[0105]

Then, an exposed region of the conductive layer 110 is etched to form the gate electrode 110a which overlaps with at least part of the region sandwiched between the source electrode 104a and the drain electrode 104b, in a self-aligned manner (see FIG. 1D). Here, besides the gate electrode 110a, the conductive layers 110b remain in portions covered with the insulating film 112a.

[0106]

The conductive layer 110 can be etched in a manner similar to that of the source electrode 104a and the drain electrode 104b, and either wet etching or dry etching may be employed; dry etching is preferably employed in terms of microfabrication. Further, the etching conditions are set as appropriate so that the

etching selectivity of the conductive layer 110 to the gate insulating layer 108 is sufficiently high, and etching is performed. In that manner, the conductive layer 110 is etched until the uppermost surface of the gate insulating layer 108 is exposed.

[0107]

In general, in the case of forming a gate electrode of a transistor with the use of a photomask in such a manner, the gate electrode is misaligned by approximately several nanometers to several hundred nanometers in some cases. When the channel length of the transistor is greater than or equal to 1  $\mu$ m, a significant problem does not occur. However, in the case of reducing the size of the transistor as in this embodiment, such misalignment might possibly be a defect which severely influences transistor characteristics. However, by forming the gate electrode 110a in a self-aligned manner as described above, the gate electrode 110a can be formed precisely and easily in the region which is over the oxide semiconductor layer 102 and sandwiched between the source electrode 104a and the drain electrode 104b.

[0108]

5

10

15

20

25

30

Further, in the portion of the gate electrode 110a, which is over the uppermost surface of the gate insulating layer 108, does not overlap with the source electrode 104a and the drain electrode 104b, which leads to suppression of an increase in parasitic capacitance between the gate electrode 110a and the source and drain electrodes 104a and 104b. Thus, a transistor having desired transistor characteristics as designed can be manufactured. Note that in the case where each of the source electrode 104a and the drain electrode 104b are tapered, and the portion of the gate electrode 110a, which is below the uppermost surface of the gate insulating layer 108, is inversely tapered, the inverse tapered portion of the gate electrode 110a, which is below the uppermost surface of the gate insulating layer 108, may overlap with the source electrode 104a and the drain electrode 104b. In that case, the portion of the gate electrode 110a, which is over the uppermost surface of the gate insulating layer 108, may overlap with the source electrode 104a and the drain electrode 104b.

[0109]

Since the gate electrode 110a can be formed without using a photomask, the number of photomasks used in the whole manufacturing process can be reduced. Accordingly, the cost of the semiconductor device can be reduced.

[0110]

Next, a resist mask 114a is formed so as to cover the gate electrode 110a, and a resist mask 114b is formed over part of the conductive layer 110b (see FIG. 2A). After that, the conductive layer 110b is processed using the resist mask 114a and the resist mask 114b to form the wiring 110c (see FIG. 2B).

[0111]

5

The resist mask 114a and the resist mask 114b can be formed in such a manner that a material such as photosensitive resin is deposited by a spin coating method or the like and then, photolithography is performed using a photomask.

10 [0112]

Then, etching is performed in a manner similar to that of the gate electrode 110a, so that the wiring 110c can be formed. Thus, the wiring 110c can be formed utilizing part of the conductive layer 110b left when the gate electrode 110a is formed, resulting in reduction in cost of the semiconductor device.

15 [0113]

Through the above process, the transistor 200 can be manufactured in which the gate electrode 110a overlaps with the region which is over the oxide semiconductor layer 102 and sandwiched between the source electrode 104a and the drain electrode 104b, while miniaturization thereof is achieved (see FIG. 2B).

20 [0114]

25

30

As described above, the oxide semiconductor layer 102 used in the transistor 200 is desirably a highly purified oxide semiconductor layer formed by sufficiently removing impurities such as hydrogen and water and sufficiently supplying oxygen. Specifically, the concentration of hydrogen in the oxide semiconductor layer 102 is lower than or equal to  $5 \times 10^{19}$  atoms/cm³, desirably lower than or equal to  $5 \times 10^{18}$  atoms/cm³, more desirably lower than or equal to  $5 \times 10^{17}$  atoms/cm³, for example. Note that the concentration of hydrogen in the oxide semiconductor layer 102 is measured by secondary ion mass spectrometry (SIMS). The oxide semiconductor layer 102 which is highly purified by sufficient reduction in hydrogen concentration and is reduced in defect level in energy gap due to oxygen deficiency by sufficient supply of oxygen has a carrier concentration of less than  $1 \times 10^{12}$  /cm³, desirably less than  $1 \times$

$10^{11}$  /cm<sup>3</sup>, more desirably less than  $1.45 \times 10^{10}$  /cm<sup>3</sup>. For example, the off-state current (here, a current per micrometer ( $\mu$ m) of channel width) at room temperature (25 °C) is lower than or equal to 100 zA (1 zA (zeptoampere) is  $1 \times 10^{-21}$  A), desirably lower than or equal to 10 zA. In this manner, by using an i-type (intrinsic) or substantially i-type oxide semiconductor, the transistor having favorable electrical characteristics can be obtained.

[0115]

5

10

Hereinafter, a method for manufacturing a semiconductor device, which is different from the method for manufacturing a semiconductor device in FIGS. 1A to 1D, FIGS. 2A and 2B, and FIGS. 3A and 3B, will be described with reference to FIGS. 4A and 4B, FIGS. 5A and 5B, and FIGS. 6A to 6C. Note that in FIGS. 4A and 4B, FIGS. 5A and 5B, and FIGS. 6A to 6C, portions corresponding to those in FIGS. 1A to 1D, FIGS. 2A and 2B, and FIGS. 3A and 3B are denoted by the same reference signs, and specific description thereof will be omitted.

15 [0116]

In the method for manufacturing a semiconductor device in FIGS. 1A to 1D, FIGS. 2A and 2B, and FIGS. 3A and 3B, the source electrode 104a and the drain electrode 104b are formed on and in direct contact with the oxide semiconductor layer 102; however, one embodiment of the disclosed invention is not limited thereto.

20 [0117]

25

30

For example, as illustrated in FIG. 4A, a transistor 210 may be manufactured in which an n<sup>+</sup> layer 124a and an n<sup>+</sup> layer 124b are formed over the top surface of the oxide semiconductor layer 102, and the source electrode 104a and the drain electrode 104b are formed over the n<sup>+</sup> layer 124a and the n<sup>+</sup> layer 124b, respectively. Here, the n<sup>+</sup> layer 124a and the n<sup>+</sup> layer 124b function to reduce contact resistance between the oxide semiconductor layer 102 and the source electrode 104a and contact resistance between the oxide semiconductor layer 102 and the drain electrode 104b, respectively. The n<sup>+</sup> layer 124a and the n<sup>+</sup> layer 124b can be formed using an In-Zn-O-based material, an In-Sn-O-based material, or a Sn-O-based material. Further, the above material may contain SiO<sub>2</sub>. The thicknesses of the n<sup>+</sup> layer 124a and the n<sup>+</sup> layer 124b are each preferably greater than or equal to 1 nm and less than or equal to 10

nm; in this embodiment, the n<sup>+</sup> layer 124a and the n<sup>+</sup> layer 124b each having a thickness of 5 nm are used.

[0118]

5

10

15

20

25

30

In the case of the transistor 210 described above, a film functioning as an oxide semiconductor layer and a film functioning as an n<sup>+</sup> layer are successively formed and then processed at the same time to form the oxide semiconductor layer 102 and a film functioning as an island-shaped n<sup>+</sup> layer in the manufacturing process of the transistor 200. Further, in forming the source electrode 104a and the drain electrode 104b, the film functioning as an island-shaped n<sup>+</sup> layer is processed to form the n<sup>+</sup> layer 124a and the n<sup>+</sup> layer 124b. Note that after formation of the source electrode 104a and the drain electrode 104b, the same steps as those in FIGS. 1A to 1D, FIGS. 2A and 2B, and FIGS. 3A and 3B are performed, so that the transistor 210 can be manufactured.

In the transistor 210 in FIG. 4A, the n<sup>+</sup> layer 124a and the n<sup>+</sup> layer 124b are formed only over the top surface of the oxide semiconductor layer 102; however, one embodiment of the disclosed invention is not limited thereto. As illustrated in FIG. 4B, a transistor 220 may be manufactured in which the n<sup>+</sup> layer 124a and the n<sup>+</sup> layer 124b further cover side surfaces of the oxide semiconductor layer 102. In that case, unlike in the method for manufacturing the transistor 210, after the island-shaped oxide semiconductor layer 102 is formed, a film functioning as an n<sup>+</sup> layer and a conductive film functioning as the source electrode 104a and the drain electrode 104b are successively formed. Then, these films are processed at the same time into island shapes to form the source electrode 104a, the drain electrode 104b, the n<sup>+</sup> layer 124a, and the n<sup>+</sup> layer 124b. Note that after formation of the source electrode 104a and the drain electrode 104b, the same steps as those in FIGS. 1A to 1D, FIGS. 2A and 2B, and FIGS. 3A and 3B are performed, so that the transistor 220 can be manufactured.

When the n<sup>+</sup> layer 124a and the n<sup>+</sup> layer 124b are thus formed between the oxide semiconductor layer 102 and the source and drain electrode layers 104a and 104b, the contact resistance therebetween can be lower than the contact resistance between the oxide semiconductor layer 102 and the source electrode 104a and the contact resistance

between the oxide semiconductor layer 102 and the drain electrode 104b. By forming the n<sup>+</sup> layer 124a and the n<sup>+</sup> layer 124b, parasitic capacitance can be reduced and further, the amount of change in on-state current between before and after application of negative gate stress can be reduced (Ion deterioration can be suppressed) when bias-temperature stress test (BT test) is performed.

[0121]

5

10

15

20

25

30

In the method for manufacturing a semiconductor device in FIGS. 1A to 1D, FIGS. 2A and 2B, and FIGS. 3A and 3B, the transistor 200 is formed such that the source electrode 104a and the drain electrode 104b are formed in contact with parts of the top surface of the oxide semiconductor layer 102; however, one embodiment of the disclosed invention is not limited thereto.

[0122]

For example, as illustrated in FIG. 5A, a transistor 230 may be manufactured in which the oxide semiconductor layer 102 is in contact with parts of the top surfaces of the source electrode 104a and the drain electrode 104b. In that case, unlike in the method for manufacturing the transistor 200, the source electrode 104a and the drain electrode 104b are formed over the substrate 100 having an insulating surface and then, the oxide semiconductor layer 102 is formed in contact with the parts of the top surfaces of the source electrode 104a and the drain electrode 104b. After that, the insulating layer 106a and the insulating layer 106b are formed over the source electrode 104a and the drain electrode 104b, respectively. Here, the oxide semiconductor layer 102, the source electrode 104a, the drain electrode 104b, the insulating layer 106a, and the insulating layer 106b can be formed by a method similar to the method illustrated in FIGS. 1A to 1D, FIGS. 2A and 2B, and FIGS. 3A and 3B. Note that after formation of the insulating layer 106a and the insulating layer 106b, the same steps as those in FIGS. 1A to 1D, FIGS. 2A and 2B, and FIGS. 3A and 3B are performed, so that the transistor 230 can be manufactured.

[0123]

Further, as illustrated in FIG. 5B, a transistor 240 may be manufactured, which is different from the transistor 230 in that the n<sup>+</sup> layer 124a and the n<sup>+</sup> layer 124b are provided below the source electrode 104a and the drain electrode 104b, respectively.

In the transistor 240, side surfaces of the n<sup>+</sup> layer 124a and the n<sup>+</sup> layer 124b are in contact with the oxide semiconductor layer 102; therefore, the contact resistance therebetween can be lower than the contact resistance between the oxide semiconductor layer 102 and the source electrode 104a and the contact resistance between the oxide semiconductor layer 102 and the drain electrode 104b.

[0124]

5

10

15

20

25

30

Further, examples of a structure and a manufacturing method of the oxide semiconductor layer 102, which are different from those illustrated in FIGS. 1A to 1D, FIGS. 2A and 2B, and FIGS. 3A and 3B, will be described with reference to FIGS. 6A to 6C.

[0125]

First, a first oxide semiconductor layer is formed to a thickness of 1 nm or more and 10 nm or less over the substrate 100 having an insulating surface. Note that a base insulating layer is preferably formed over the substrate 100 before the first oxide semiconductor layer is formed. The base insulating layer can be formed using a material and a method similar to those of the gate insulating layer 108.

[0126]

In the method for manufacturing a semiconductor device, which is illustrated in FIGS. 6A to 6C, the first oxide semiconductor layer is formed to a thickness of 5 nm in an oxygen atmosphere, an argon atmosphere, or a mixed atmosphere of argon and oxygen under the following conditions: a target for an oxide semiconductor (a target for an In-Ga-Zn-O-based oxide semiconductor containing In<sub>2</sub>O<sub>3</sub>, Ga<sub>2</sub>O<sub>3</sub>, and ZnO at a ratio of 1:1:2 [molar ratio]) is used; the distance between the substrate and the target is 170 mm; the substrate temperature is 400 °C; the pressure is 0.4 Pa; and the direct current (DC) power is 0.5 kW.

[0127]

Then, first heat treatment is performed with the substrate placed in an atmosphere of nitrogen or dry air. The first heat treatment is performed at a temperature higher than or equal to 450 °C and lower than the strain point of the substrate, preferably higher than or equal to 400 °C and lower than or equal to 650 °C. Through the first heat treatment, a first crystalline oxide semiconductor layer 102a is

formed (see FIG. 6A).

[0128]

Next, a second oxide semiconductor layer is formed to a thickness greater than 10 nm over the first crystalline oxide semiconductor layer 102a.

5 [0129]

10

15

25

30

In this embodiment, the second oxide semiconductor layer is formed to a thickness of 25 nm in an oxygen atmosphere, an argon atmosphere, or a mixed atmosphere of argon and oxygen under the following conditions: a target for an oxide semiconductor (a target for an In-Ga-Zn-O-based oxide semiconductor containing In<sub>2</sub>O<sub>3</sub>, Ga<sub>2</sub>O<sub>3</sub>, and ZnO at a ratio of 1:1:2 [molar ratio]) is used; the distance between the substrate and the target is 170 mm; the substrate temperature is 400 °C; the pressure is 0.4 Pa; and the direct current (DC) power is 0.5 kW.