(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4780098号

(P4780098)

(45) 発行日 平成23年9月28日(2011.9.28)

(24) 登録日 平成23年7月15日(2011.7.15)

(51) Int.Cl.

G06F 1/04 (2006.01)

G06F 15/78 (2006.01)

F 1

G06F 1/04 301C

G06F 15/78 510P

G06F 15/78 510E

請求項の数 6 (全 40 頁)

(21) 出願番号 特願2007-322364 (P2007-322364)

(22) 出願日 平成19年12月13日 (2007.12.13)

(62) 分割の表示 特願2002-380002 (P2002-380002)

原出願日 平成14年12月27日 (2002.12.27)

(65) 公開番号 特開2008-123538 (P2008-123538A)

(43) 公開日 平成20年5月29日 (2008.5.29)

審査請求日 平成19年12月13日 (2007.12.13)

前置審査

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74) 代理人 100123191

弁理士 伊藤 高順

(74) 代理人 100138542

弁理士 井口 亮祉

(74) 代理人 100096998

弁理士 碓水 裕彦

(72) 発明者 手嶋 芳徳

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

(72) 発明者 松岡 俊彦

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

最終頁に続く

(54) 【発明の名称】マイクロコンピュータ

## (57) 【特許請求の範囲】

## 【請求項1】

内部状態を保持したまま動作を一時的に停止する低消費電力モードの設定が可能に構成されるCPUと、

前記低消費電力モードを周期的に解除するための解除タイマと、

前記低消費電力モードが設定されている期間内に、外部信号出力端子のレベルを変化させる信号レベル変化手段とを備えて構成され、

前記信号レベル変化手段は、

前記外部信号出力端子のレベルを変化させるタイミングを設定するためのレジスタと、

前記CPUが低消費電力モードに移行した時点からカウント動作を開始するレベル変化用タイマと、

前記レベル変化用タイマのカウント値と前記レジスタの値とを比較して、両者が一致するとトリガ信号を出力する比較回路とを備え、前記トリガ信号が出力されると、前記外部信号出力端子のレベルを変化させるように構成されていることを特徴とするマイクロコンピュータ。

## 【請求項2】

前記レジスタは、前記CPUによって任意のデータ値が設定可能に構成されていることを特徴とする請求項1記載のマイクロコンピュータ。

## 【請求項3】

前記信号レベル変化手段によって変化された外部信号出力端子のレベルは、前記低消費

電力モードが解除されると、前記 C P U によってリセットすることが可能に構成されていることを特徴とする請求項 1 または 2 記載のマイクロコンピュータ。

【請求項 4】

前記低消費電力モードは、前記解除タイマ以外の解除要因が発生した場合も解除されるように設定されており、

前記信号レベル変化手段が前記外部信号出力端子のレベルを変化させた後、前記解除要因の発生によって低消費電力モードが解除されると、前記解除タイマによって前記低消費電力モードが解除される予定のタイミングで、前記 C P U に対して割り込み要求を発生させる割り込み発生手段を備えたことを特徴とする請求項 3 記載のマイクロコンピュータ。

【請求項 5】

前記レベル変化用タイマは、前記解除タイマと共に構成されていることを特徴とする請求項 1 乃至 4 の何れかに記載のマイクロコンピュータ。

【請求項 6】

前記解除タイマは、前記 C P U の動作を監視するためのウォッチドッグタイマ、若しくは前記 C P U の動作用クロックとは独立にカウント動作するフリーランタイマと共に構成されていることを特徴とする請求項 1 乃至 4 の何れかに記載のマイクロコンピュータ。

10

【発明の詳細な説明】

【技術分野】

【0001】

20

本発明は、内部状態を保持したまま動作を一時的に停止する低消費電力モードの設定が可能に構成される C P U を備えてなるマイクロコンピュータに関する。

【背景技術】

【0002】

マイクロコンピュータにおいては、C P U が処理を行なう必要がない状態となった場合に、その内部状態を保持しつつクロック信号の発振動作を停止させることで電力消費を低減する低消費電力モードに移行することが可能に構成されているものがある（例えば、特許文献 1）。

また、マイクロコンピュータは、外部信号出力端子のレベルを変化させることで、その端子に接続されている外部デバイスの制御を行う。この場合、端子の出力レベルと、その端子をアクティブにする期間とはプログラムによって設定される。

30

【0003】

特にバッテリを動作用電源として構成されるマイクロコンピュータでは、C P U が処理を行なう必要がない状態となった場合に、その内部状態を保持しつつクロック信号の発振動作を停止することで電力消費を低減する低消費電力モードに移行することが可能に構成されているものがある。その場合、マイコンの内部処理や外部デバイスの制御などについては、例えば図 37 に示すように、低消費電力モードと通常モードとを交互に移行することで、定期的に実行されるようにスケジューリングすることが可能である。

或いは、マイコンの外部で発生する何らかのイベントに応じて不定期に処理を行なう必要がある場合は、そのイベントを低消費電力モードの解除要因として、イベントの発生に応じて通常モードに移行させ、処理を実行させることも可能である。

40

【特許文献 1】特開平 11 - 305888 号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献 1 のような従来のマイクロコンピュータでは、低消費電力モードに移行している期間において外来ノイズが印加されると、外部出力端子の出力レベルが変化してしまうおそれがあった。例えば、マイコンがモータを駆動する制御するように構成されていると、低消費電力モードに移行する場合はモータの回転を停止させるように外部出力端子のレベルを制御する。その状態で、外来ノイズの影響で外部出力端子の出力レ

50

ベルが変化すると、モータが回転してしまうことになる。

#### 【0005】

また、例えば、通常モードにおいてプログラムが実行されている場合は、そのプログラムにおいて外部出力端子のレベルを設定し(例えば、H)、出力期間の間はそのレベルを保持し、出力期間が終了すると前記レベルを元に戻すように設定する(例えば、L)。そして、上記出力期間を把握するために、プログラムはCPUの動作クロック(マシンクロック)などに基づいて動作するタイマを使用する。

また、プログラムは、上記出力期間中においては、他の処理も並行して実行することが可能であるが、そのように並行して実行可能な処理が常に存在するとは限らない。その場合は、結果として、単に端子の出力レベルを保持するためだけにCPUが起動していることになる。そして、その期間中は動作クロックが発振し続けるため、消費電流が増大するという問題があった。10

#### 【0006】

本発明は上記事情に鑑みてなされたものであり、その目的は、低消費電力モードの設定が可能に構成される場合に、外来ノイズの影響を極力低減することができるマイクロコンピュータ、また、低消費電力モードに移行している状態においても、外部出力端子のレベル設定を行うことが可能なマイクロコンピュータを提供することにある。

#### 【課題を解決するための手段】

#### 【0009】

請求項1記載のマイクロコンピュータによれば、信号レベル変化手段は、CPUが低消費電力モードに設定されている期間内に、外部信号出力端子のレベルを変化させる。従って、CPUは、外部信号出力端子のレベルを変化させるためだけに通常の動作モードを継続する必要がないので、消費電力を低減することができる。20

#### 【0010】

請求項1記載のマイクロコンピュータによれば、信号レベル変化手段は、レベル変化用タイマのカウント値とレベル変化タイミングが設定されているレジスタの値とを比較回路が比較し、両者が一致することでトリガ信号が出力されると外部信号出力端子のレベルを変化させる。従って、レジスタに設定されるタイミングで、出力端子のレベルを変化させることができる。

#### 【0011】

請求項2記載のマイクロコンピュータによれば、レジスタは、CPUによって任意のデータ値が設定可能に構成されるので、ユーザプログラムによってレベル変化タイミングを任意に設定することができる。30

#### 【0012】

請求項3記載のマイクロコンピュータによれば、外部信号出力端子のレベルは、低消費電力モードが解除されるとCPUによってリセットすることが可能に構成されるので、CPUが必要な処理を行った時点で出力端子のレベルを直ちにリセットすることができる。

#### 【0013】

請求項4記載のマイクロコンピュータによれば、割り込み発生手段は、信号レベル変化手段が外部信号出力端子のレベルを変化させた後、解除要因の発生によって低消費電力モードが解除されると、解除タイマによって低消費電力モードが解除される予定のタイミングでCPUに対して割り込み要求を発生させる。40

#### 【0014】

即ち、信号レベル変化手段が変化させた外部信号出力端子のレベルについては、そのレベルを最低限維持するように要求される場合がある(例えば、その外部信号出力端子が接続されている外部デバイスに対する制御に係る要請などによる)。その場合、前記レベルの維持期間は、低消費電力モードが設定されている期間との関係に応じて定められているため、解除要因の発生によって低消費電力モードが予定よりも早く解除されると、CPUは、本来の信号レベルの維持期間が判らなくなってしまう。

そこで、割り込み発生手段が上記のタイミングでCPUに対して割り込み要求を発生さ50

せれば、CPUは前記維持期間を認識できるようになり、その割り込み要求を認識した後に、必要に応じて出力端子のレベルをリセットすることができる。

#### 【0015】

請求項5記載のマイクロコンピュータによれば、レベル変化用タイマを解除タイマと共に通にしてより簡単に構成することができる。

請求項6記載のマイクロコンピュータによれば、解除タイマを、CPUの動作を監視するためのウォッチドッグタイマ、若しくは、CPUの動作用クロックとは独立にカウント動作するフリーランタイマと共に通としてより簡単に構成することができる。

#### 【発明を実施するための最良の形態】

##### 【0016】

10

###### (第1実施例)

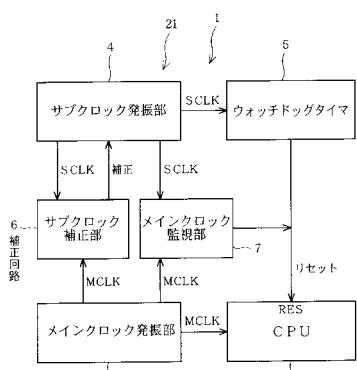

以下、本発明をマイクロコンピュータに適用した場合の第1実施例について図1乃至図4を参照して説明する。図1は、マイクロコンピュータ(マイコン)1の電気的構成を示す機能ブロック図である。マイコン1は、CPU2を中心として構成され、そのCPU2には、メインクロック発振部(発振回路)3によって発振出力されるメインクロック信号MCLK(例えば、周波数4MHz, 第1クロック信号)が動作用クロック信号として供給されるようになっている。メインクロック発振部3は、具体的には図示しないが、水晶発振子を用いて構成されている。

##### 【0017】

20

また、マイコン1は、CR発振回路で構成されるサブクロック発振部(CR発振回路)4を備えている。サブクロック発振部4によって発振出力されるサブクロック信号SCLK(例えば、周波数25kHz, 第2クロック信号)は、ウォッチドッグタイマ5にカウント用クロック信号として供給されるようになっている。

ウォッチドッグタイマ5は、周知のようにCPU2の暴走監視機能をなすものであり、CPU2によって周期的なクリア動作が実行されなくなるとオーバーフローしてCPU2にリセット信号を出力する。また、本実施例におけるウォッチドッグタイマ5は、クリア動作画行なわれる時点でタイマ5のカウント値が現地を超えていない場合にもリセット信号を出力するように構成されている。

##### 【0018】

30

サブクロック補正部(補正回路)6は、メインクロック信号MCLKを用いてサブクロック信号SCLKの発振周波数補正を行なうように構成されている。一方、メインクロック監視部(監視回路)7は、サブクロック信号SCLKを用いてメインクロック信号MCLKの監視を行なうように構成されており、メインクロック信号MCLKの異常を検出すると、CPU2にリセット信号を出力するようになっている。

##### 【0019】

40

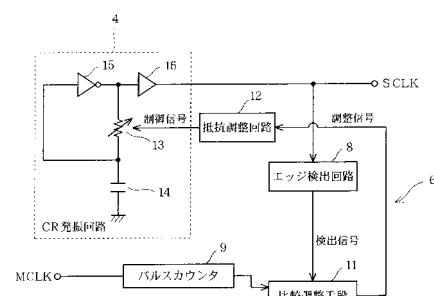

図2は、サブクロック補正部6を中心とする詳細な構成を示すものである。サブクロック補正部6は、エッジ検出回路8、パルスカウンタ9、カウント数設定レジスタ10、比較調整手段11および抵抗調整回路12を備えている。また、サブクロック発振部4は、抵抗調整回路6からの制御信号により抵抗値が可変な可変抵抗器としてのラダー抵抗13、コンデンサ14、インバータ15およびバッファ16で構成されている。

##### 【0020】

サブクロック補正部6のエッジ検出回路8は、サブクロック発振部4からの発振出力のエッジを検出して検出信号を生成する。パルスカウンタ9は、メインクロック信号MCLKの出力パルスを計数するデジタルカウンタである。また、カウント数設定レジスタ10は、サブクロック信号SCLKの一周期に相当すべきMCLKパルスの適正なカウント数が格納されるレジスタである。すなわち、カウント数設定レジスタ10に設定されるカウント数には、MCLKパルスがそのカウント数だけ発生する時間に応じて、サブクロック信号SCLKの発振周期が調整されるべき数値が設定される。

##### 【0021】

比較調整手段11は、エッジ検出回路8からエッジ検出信号を受け取ると、パルスカウ

50

ンタ 9 によるパルスのカウント数とレジスタ 4 に格納されたカウント数とを比較し、両カウント数の比較結果に基づいて、サブクロック信号 S C L K の発振周期を調整するための調整信号を出力するように構成されている。

抵抗調整回路 1 2 は、比較調整手段 1 1 からの調整信号に基づいて制御信号を生成し、この制御信号をもってサブクロック発振部 4 のラダー抵抗 1 3 の抵抗値を調整する回路である。

#### 【 0 0 2 2 】

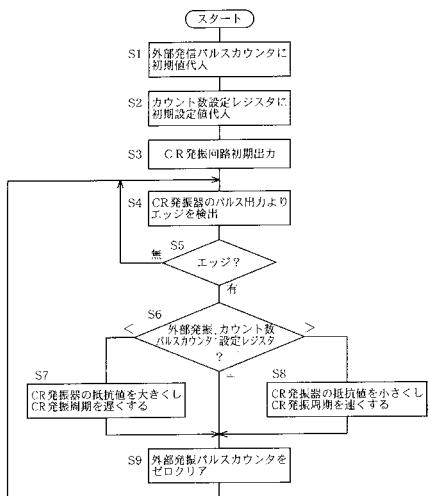

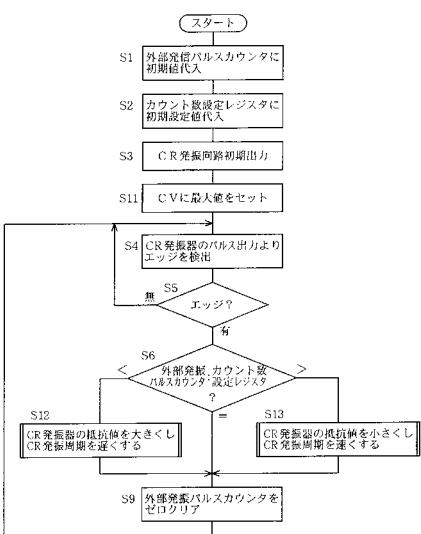

尚、サブクロック補正部 6 の動作については、特開 2 0 0 1 - 1 1 1 3 8 9 号公報に詳細に開示されているが、以下、その概略について述べる。サブクロック信号 S C L K の一周期が経過して、そのクロックパルスのエッジがエッジ検出回路 8 によって検出されると、検出信号が比較調整手段 1 1 に出力される。すると、比較調整手段 1 1 は、パルスカウンタ 9 で積算されている前回の検出信号から積算されたパルスのカウント数と、カウント数設定レジスタ 1 0 に設定されているカウント数とを読み出して両者を比較する。10

#### 【 0 0 2 3 】

ここで、レジスタ 1 0 に設定されているカウント数は、サブクロック信号 S C L K の一周期に相当すべきパルスの適正な積算値である。そこで、比較調整手段 1 1 は、M C L K パルスがサブクロック信号 S C L K の一周期のうちにいくつ積算されたかをもって、サブクロック信号 S C L K の一周期が適正な設定値よりもどの程度大きいかあるいは小さいかを判定することができる。比較調整手段 1 1 は、その判定結果に基づいて、サブクロック信号 S C L K の発振周期を調整するための調整信号を生成し、抵抗調整回路 1 2 は、この調整信号に基づいて制御信号を生成出力してラダー抵抗 1 3 の抵抗値を調整する。尚、図 3 は、以上の補正処理を示すフローチャートである。20

#### 【 0 0 2 4 】

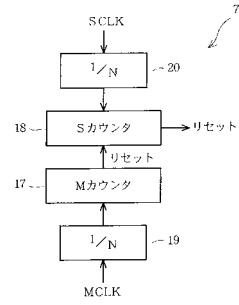

図 4 は、メインクロック監視部 7 の詳細な構成を示すものである。メインクロック監視部 7 は、M カウンタ 1 7 及び S カウンタ 1 8 を中心として構成されている。M カウンタ 1 7 は、1 / N 分周器 1 9 を介して与えられるメインクロック信号 M C L K のパルスをカウントするカウンタであり、S カウンタ 1 8 は、1 / N 分周器 2 0 を介して与えられるサブクロック信号 S C L K のパルスをカウントするカウンタである。そして、S カウンタ 1 8 は、M カウンタ 1 7 におけるカウントデータの M S B が立つとリセットされると共に、リセットされずにオーバーフローすると C P U 2 にリセット信号を出力するように構成されている。30

尚、1 / N 分周器 1 9 , 2 0 の分周値は、C P U 2 のプログラムによってセット可能に構成されている。また、分周器 1 9 , 2 0 については、クロック信号を分周することなくそのまま出力することも可能に構成されている。

#### 【 0 0 2 5 】

即ち、メインクロック監視部 7 においては、メインクロック信号 M C L K の周波数が適正であれば、サブクロック信号 S C L K の出力パルスをカウントする S カウンタ 1 8 がオーバーフローする前に M カウンタ 1 7 におけるカウントデータの M S B が立つことで、S カウンタ 1 8 はリセットされるように設定されている。そして、メインクロック信号 M C L K の周波数が低下した場合は、M カウンタ 1 7 の M S B が立つ前に S カウンタ 1 8 がオーバーフローするので、C P U 2 はリセットされる。40

#### 【 0 0 2 6 】

また、メインクロック監視部 7 における S カウンタ 1 8 のオーバーフロー周期は、ウォッチドッグタイマ 5 のオーバーフロー周期よりも短くなるように構成されている。

尚、メインクロック発振部 3 、サブクロック発振部 4 、サブクロック補正部 6 及びメインクロック監視部 7 は、クロック制御回路装置 2 1 を構成している。また、マイコン 1 としては、具体的には図示しないが、その他、R O M 、R A M や I / O , A / D 変換部などの周辺回路を備えている。

#### 【 0 0 2 7 】

そして、クロック制御回路装置 2 1 のサブクロック補正部 6 及びメインクロック監視部50

7、並びにウォッチドッグタイマ5の機能を組み合わせることで、総合的に以下のような監視形態がとられることになる。

(1) MCLK : 正常 , SCLK : 周波数低下

サブクロック補正部6の範囲内で補正され、その補正範囲を超える場合は、ウォッチドッグタイマ5によりCPU2にリセットがかかる。

(2) MCLK : 正常 , SCLK : 周波数上昇

サブクロック補正部6の範囲内で補正され、その補正範囲を超える場合は、メインクロック監視部7によりCPU2にリセットがかかる。

(3) MCLK : 周波数低下 , SCLK : 正常

相対的にSCLKが速くなることから、メインクロック監視部7によりCPU2にリセットがかかる。 10

(4) MCLK : 周波数上昇 , SCLK : 正常

相対的にSCLKが遅くなることから、ウォッチドッグタイマ5によりCPU2にリセットがかかる。

#### 【0028】

以上のように構成された本実施例によれば、クロック制御回路装置21のサブクロック補正部6は、メインクロック信号MCLKに基づいてサブクロック信号SCLKの発振周波数を補正し、メインクロック監視部7は、サブクロック信号SCLKに基づいてメインクロック信号MCLKの発振状態を監視する。従って、メイン、サブの2つのクロック信号によって互いに補正、監視を行なうので、発振動作の信頼性を総合的に向上させることができる。 20

#### 【0029】

また、本実施例によれば、メインクロック監視部7によるメインクロック信号MCLKの監視を行なう周期は、ウォッチドッグタイマ5の周期よりも短くなるように設定される。従って、メインクロック監視部7は、ウォッチドッグタイマ5の監視周期では検出することができない異常の発生を検出することが可能となる。即ち、メインクロック信号MCLKが遅くなった場合は、ウォッチドッグタイマ5によるリセットがかかる前にメインクロック監視部7によってリセットをかけることができる。

そして、サブクロック信号SCLKを補正することで、CPU2は、設計通りにウォッチドッグタイマ5をリセットすることができる。 30

#### 【0030】

<以下は参考>

A . 発振子を使用して第1クロック信号を発振する発振回路と、

前記第1クロック信号よりも低い周波数の第2クロック信号を発振し、その発振周波数が調整可能に構成されるCR発振回路と、

前記第1クロック信号に基づいて、前記第2クロック信号の発振周波数を補正する補正回路と、

前記第2クロック信号に基づいて、前記第1クロック信号の発振状態を監視する監視回路とを備えて構成されることを特徴とするクロック制御回路装置。

上記Aのクロック制御回路装置によれば、補正回路は、第1クロック信号に基づいて第2クロック信号の発振周波数を補正し、監視回路は、第2クロック信号に基づいて第1クロック信号の発振状態を監視する。即ち、第1, 第2の2つのクロック信号によって互いに補正、監視を行なうので、発振動作の信頼性を向上させることができる。 40

#### 【0031】

B . 上記A記載のクロック制御回路装置と、

前記第1クロック信号に基づいて生成される動作クロック信号が供給されるCPUと、

前記第2クロック信号に基づいて前記CPUの動作を監視するウォッチドッグタイマとを備え、

前記監視回路による第1クロック信号の監視を行なう周期は、前記ウォッチドッグタイマ周期よりも短くなるように構成されていることを特徴とするマイクロコンピュータ。 50

上記Bのマイクロコンピュータによれば、監視回路による第1クロック信号の監視を行なう周期は、ウォッチドッグタイマ周期よりも短くなるように設定される。従って、監視回路は、ウォッチドッグタイマの監視周期では検出することができない異常の発生を検出することが可能となる。

#### 【0032】

##### (第2実施例)

図5乃至図8は本発明の第2実施例を示すものであり、第1実施例と同一部分には同一符号を付して説明を省略以下異なる部分についてのみ説明する。第2実施例における構成は基本的に第1実施例と同様であり、比較調整手段11による調整動作が若干異なっている。10

即ち、図5に示すフローチャートでは、ステップS3,S4の間に「CVに最大値をセット」の処理ステップS11が挿入されている。また、ステップS7,S8は、ステップS12,S13に置き換わっている。ここで、「CV」とは、比較調整手段11が出力する調整信号データである。

即ち、図5に示すフローチャートの実行が開始されるのは(スタート)、CPU2のリセットや、スリープモードなどの低消費電力モードが解除された場合の起動時である。その場合に、ステップS11において補正データの初期値が最大値(max)にセットされることになる。

#### 【0033】

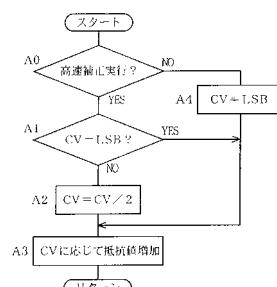

図6は、ステップS12における処理内容を示すものである。先ず、比較調整手段11は、高速補正を行なうか否かを判断する(ステップA0)。この設定はユーザによって行われるようになっており、例えばユーザプログラム中や、基板上に設けられたディップスイッチなどで設定される。高速補正を行うように設定されていない場合('NO')、比較調整手段11は、調整信号データCVを補正データの最小単位(LSB)に設定し(ステップA4)、それからステップA3に移行する。この場合は、補正が最小単位で行なわれるため、第1実施例と同様の低速補正となる。ステップA3では、調整信号データCVを抵抗調整回路12に出力することで、データCVに応じてラダー抵抗13の抵抗値を増加させる。20

#### 【0034】

一方、ステップA0において、高速補正を行うように設定されている場合('YES')、比較調整手段11は、調整信号データCVがその時点で最小単位になっているか否かを判断する(ステップA1)。そして、データCVが最小単位に等しければ('YES')ステップA3に移行する。30

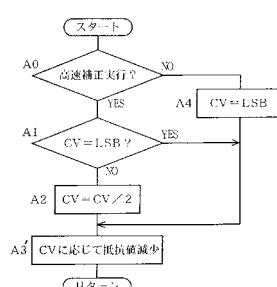

また、ステップA1において、データCVが最小単位に等しくなければ('NO')、比較調整手段11は、調整信号データCVを1/2にしてから(ステップA2)ステップA3に移行する。尚、図7に示すステップS13における処理では、ステップA3'の処理が、ステップA3の「増加」を「減少」に変更したものである。

#### 【0035】

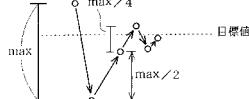

ここで、図8には、高速補正動作が行なわれる状態(即ち、ステップS12についてはステップA3を実行する場合)の概念的な説明図を示す。即ち、最初の補正是調整範囲の最大値maxによって行なわれ、例えば、サブクロック信号SCLKの周期データがレジスタ10の設定値よりも大きい(周波数が低い)場合は、周期が短くなる方向に最大値maxで振る。40

その次の補正では、周期が短くなったため、周期が長くなる方向に最大値maxの1/2で振る。更に、その次の補正では周期が未だ短いため、更に周期が長くなる方向にmax/4で振る。すると、今度は目標値を超えたため、次の補正では周期が長くなる方向にmax/8で振るようにする。

#### 【0036】

以上のように、最大値maxで補正を開始して、絶対値が1/2, 1/4, 1/8と漸減していくように補正を行なう。即ち、データ検索方式でいえば、所謂バイナリサーチを50

同じ概念である。即ち、C P U 2 のリセット解除時や、低消費電力モードから通常モードに移行した場合のような起動時には、サブクロック発振部 4 の発振状態はかなり不安定となり、その発振周波数は、設定された周波数から大きく外れた状態にあると推定される。従って、その期間における調整動作についてはバイナリサーチ方式で行うことで、サブクロック信号 S C L K の周期データがより速くレジスタ 1 0 の設定値に等しくなるように（狙い周波数に収束するように）補正される。

そして、調整信号データ C V を 1 / 2 にすることを繰り返すと、最終的にはデータの最小値（L S B）に到達する（ステップ A 1、「Y E S」）。それ以降は、その最小値によって補正が継続されることになる。

#### 【 0 0 3 7 】

10

また、ステップ A 0 において、高速補正を行なうか否かを選択可能としたのは、以下の理由による。即ち、C P U 2 が低消費電力モードを実行可能に構成されている場合、高速補正を行なっている途中で低消費電力モードに移行すると、サブクロック発振部 4 の発振周波数が設定周波数と大きく離れた状態のままで移行してしまうおそれがある。従って、低消費電力モードへの移行周期の設定に応じて調整方式を選択することで、ユーザの設計意図に応じた調整が可能となる。

#### 【 0 0 3 8 】

以上のように第 2 実施例によれば、サブクロック補正部 6 の比較調整手段 1 1 は、C P U 2 が起動した直後に、サブクロック発振部 4 の発振周波数を調整する場合は、調整範囲の最大値より開始して、その絶対値を調整周期毎に 1 / 2 ずつ減少させるようにした。従って、サブクロック信号 S C L K の周波数を、設定周波数により速く収束させることができるとなる。

20

そして、比較調整手段 1 1 は、調整信号レベルの絶対値が最小値（L S B）に達するとい降はその最小値によって調整を継続するので、発振周波数が設定周波数の近傍に近付いた状態になれば調整を精密に行なうことが可能となる。更に、比較調整手段 1 1 は、C P U 2 が起動した直後の調整動作においては、高速補正を行なうか否かを選択可能とするので、ユーザの意図に沿うように調整を行なわせることができる。

#### 【 0 0 3 9 】

< 以下は参考 >

C . 発振子を使用して第 1 クロック信号を発振する発振回路と、

前記第 1 クロック信号に基づいて生成される動作クロック信号が供給される C P U と、

前記第 1 クロック信号よりも低い周波数の第 2 クロック信号を発振し、その発振周波数

が調整可能に構成される C R 発振回路と、

30

前記第 1 クロック信号に基づいて、前記第 2 クロック信号の発振周波数を補正する補正回路とを備え、

前記補正回路は、前記第 2 クロック信号のエッジを検出するエッジ検出回路と、前記第 1 クロック信号に基づいてカウント動作を行なうパルスカウンタと、前記第 2 クロック信号の一周期に相当すべき前記パルスカウンタのカウント数が格納されるカウント数設定レジスタと、前記エッジ検出回路からエッジ検出信号を受け取ると、前記パルスカウンタのカウント数と前記カウント数設定レジスタに格納されたカウント数とを比較し、両者の差に基づいて前記 C R 発振回路の発振周波数を調整するための調整信号を生成する比較調整手段と、前記調整信号に基づいて、前記 C R 発振回路の発振周波数を調整する調整回路とを備えて構成され、

40

前記比較調整手段は、前記 C P U が起動した直後の調整動作においては、前記調整信号レベルの絶対値を調整周期毎に漸減させるように構成されていることを特徴とするマイクロコンピュータ。

#### 【 0 0 4 0 】

上記 C のマイクロコンピュータによれば、比較調整手段は、C P U が起動した直後に、C R 発振回路の発振周波数を調整する場合は、調整信号レベルの絶対値を調整周期毎に漸減させる。即ち、C P U のリセット解除時や、低消費電力モードから通常モードに移行し

50

た場合のような起動時には、C R 発振回路の発振状態はかなり不安定となり、その発振周波数は、設定された周波数から大きく外れた状態にあると推定される。従って、その期間における調整動作については、調整信号レベルの絶対値を、調整周期毎に大きな値から小さな値に漸減させるように調整を行なえば、設定周波数により速く収束させることが可能となる。

#### 【0041】

D . 前記比較調整手段は、前記調整動作においては、調整範囲の最大値より開始して、その絶対値を調整周期毎に 1 / 2 ずつ減少させることを特徴とする上記 C のマイクロコンピュータ。

上記 D のマイクロコンピュータによれば、比較調整手段は、調整動作においては、調整範囲の最大値より開始して、その絶対値を調整周期毎に 1 / 2 ずつ減少させる。即ち、データ検索における所謂バイナリサーチと同様の方式によることで、C R 発振回路の発振周波数を設定周波数により速く収束させることが可能となる。

#### 【0042】

E . 前記比較調整手段は、前記調整信号レベルの絶対値が最小値に達すると、以降はその最小値によって調整を継続することを特徴とする上記 C または D のマイクロコンピュータ。

上記 E のマイクロコンピュータによれば、比較調整手段は、調整信号レベルの絶対値が最小値に達すると以降はその最小値によって調整を継続するので、発振周波数が設定周波数の近傍に近付いた状態になれば調整を精密に行なうことが可能となる。

#### 【0043】

F . 前記比較調整手段は、前記 C P U が起動した直後の調整動作においては、前記調整信号レベルの絶対値を調整周期毎に漸減させる調整動作を行なうか否かを選択可能に構成されていることを特徴とする上記 C ~ E の何れかのマイクロコンピュータ。

上記 F のマイクロコンピュータによれば、比較調整手段は、C P U が起動した直後の調整動作においては、調整信号レベルの絶対値を調整周期毎に漸減させる調整動作を行なうか否かを選択可能に構成される。即ち、C P U が低消費電力モードを実行可能に構成されている場合、調整周期毎に漸減させる調整動作を行なっている途中で低消費電力モードに移行すると、C R 発振回路の発振周波数が設定周波数と大きく離れた状態のままで移行してしまうおそれがある。従って、低消費電力モードへの移行周期の設定に応じて調整方式を選択できるようにすれば、ユーザの意図に沿うように調整を行なわせることができる。

#### 【0044】

C' . 発振子を使用して第 1 クロック信号を発振する発振回路と、前記第 1 クロック信号に基づいて生成される動作クロック信号が供給される C P U と、前記第 1 クロック信号よりも低い周波数の第 2 クロック信号を発振し、その発振周波数が調整可能に構成される C R 発振回路と、前記第 1 クロック信号に基づいて、前記第 2 クロック信号の発振周波数を補正する補正回路とを備えて構成されるマイクロコンピュータについて、前記第 2 クロック信号の発振周波数を調整する発振周波数の調整方法であって、

前記補正回路は、前記第 2 クロック信号のエッジを検出し、前記第 1 クロック信号に基づいてカウント動作を行ない、前記第 2 クロック信号の一周期に相当すべきカウント数を保持し、前記エッジ検出信号を受け取ると、前記カウント動作によって示されるカウント数と前記保持されたカウント数とを比較し、両者の差に基づいて前記 C R 発振回路の発振周波数を調整するための調整信号を生成し、前記調整信号に基づいて、前記 C R 発振回路の発振周波数を調整し、

前記 C P U が起動した直後の調整動作においては、前記調整信号レベルの絶対値を調整周期毎に漸減させることを特徴とするクロック信号の発振周波数調整方法。

#### 【0045】

D' . 前記調整動作においては、調整範囲の最大値より開始して、その絶対値を調整周期毎に 1 / 2 ずつ減少させることを特徴とする上記 C' のクロック信号の発振周波数調整方法。

10

20

30

40

50

E' . 前記調整信号レベルの絶対値が最小値に達すると、以降はその最小値によって調整を継続することを特徴とする上記C' またはD' のクロック信号の発振周波数調整方法。

F' . 前記CPUが起動した直後の調整動作においては、前記調整信号レベルの絶対値を調整周期毎に漸減させる調整動作を行なうか否かが選択可能であることを特徴とするC' ~ E' のクロック信号の発振周波数調整方法。

#### 【0046】

(第3実施例)

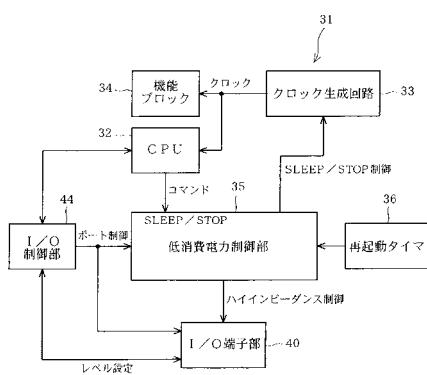

図9乃至図13は本発明の第3実施例を示すものである。図9は、マイクロコンピュータ(マイコン)31の構成を示す機能ブロック図である。マイコン31は、CPU32を中心として構成されている。そのCPU32には、クロック生成回路33より生成出力されるクロック信号が動作用クロック信号として供給されるようになっている。また、前記クロック信号は、その他周辺回路などの機能ブロック34にも供給されている。

10

#### 【0047】

低消費電力制御部(端子制御手段)35は、CPU32によって与えられる制御コマンドに応じて所謂スリープ/ストップモードなどの低消費電力モードに関する制御を行うものである。ここで、スリープモードとは、クロック生成回路33の動作を停止させることでCPU32に対する動作用クロック信号の供給を停止させ、CPU32は、内部レジスタのデータ値などを保持した状態で処理を一時的に停止するモードである。スリープモードは、設定された時間間隔で周期的に解除(ウェイクアップ)されるようになっている。

20

一方、ストップモードは、CPU32が処理を停止する点についてはストップモードと同様であるが、周期的に解除されることはなく、CPU32が処理すべき何らかのイベントが発生した場合にのみ解除されるモードである。

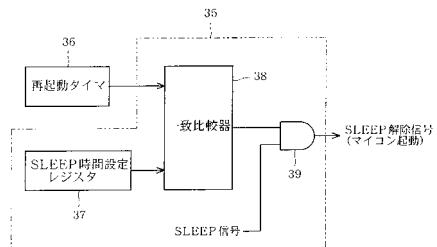

#### 【0048】

図10は、低消費電力制御部35が、スリープモードについて制御を行う機能部分の構成を示すものである。即ち、低消費電力制御部35は、例えばCR発振回路で構成される再起動タイマ36のカウント値と、内部のSLEEP時間設定レジスタ37の設定データ値とを一致比較器38によって比較し、両者が一致するとハイレベルの一致信号をANDゲート39の一方の入力端子に出力する。ANDゲート39の他方の入力端子には、SLEEP信号が与えられる。

30

従って、ハイレベルのSLEEP信号が与えられている期間において一致比較器38が一致信号を出力すると、ANDゲート39はハイレベルのSLEEP解除信号を出力する。この時、再起動タイマ36はリセットされる。

#### 【0049】

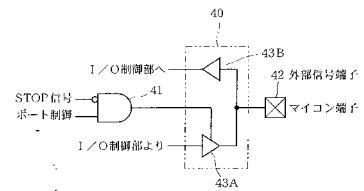

一方、図11は、低消費電力制御部35が、ストップモードが設定された場合にI/O端子部40の制御を行う機能部分の構成を示すものである。即ち、低消費電力制御部35のANDゲート41の負論理入力端子と正論理入力端子には、夫々STOP信号、ポート制御信号が与えられるようになっている。そして、ANDゲート41はI/O端子部40にハイインピーダンス制御信号を出力する。

I/O端子部40は、出入力端子(外部信号端子)42にバッファ43A, 43Bが双方接続された構成である。そして、出力バッファ43Aは、ANDゲート41によって出力されるハイインピーダンス制御信号によって制御される。また、I/O端子部40は、I/O制御部44によって出入力切替え制御(ポート制御)と出力レベル制御が行われるようになっている。前記ポート制御信号は、I/O制御部44によって出力される。

40

#### 【0050】

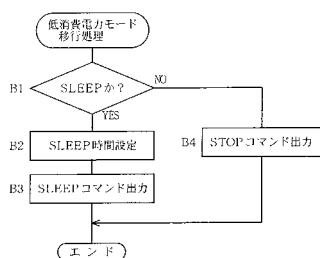

次に、第3実施例の作用について図12及び図13を参照して説明する。図12は、CPU32が低消費電力モードに移行する場合の処理を示すフローチャートである。CPU32は、低消費電力モードが「スリープ」であるか否かを判断する(ステップB1)。そして、「スリープ」である場合は('YES')、SLEEP時間設定レジスタ37にスリープモードの移行期間データを設定する(ステップB2)。それから、低消費電力制御部

50

35に対してSLEEPコマンドを出力すると(ステップB3)処理を終了する。この場合、低消費電力制御部35の図9に示す構成部分がアクティブとなり、スリープモードの移行期間の計測が開始され、その期間が終了するとスリープモードは解除される。

#### 【0051】

一方、低消費電力モードが「STOP」である場合(ステップB1、「NO」)、CPU32は、低消費電力制御部35に対してSTOPコマンドを出力する(ステップB4)。そして、処理を終了する。この場合、低消費電力制御部35の図11に示す構成部分が作用する。即ち、STOP信号がハイレベルとなり、ANDゲート41の出力レベルはロウとなることで、出力バッファ43Aの出力端子はハイインピーダンス状態となる。

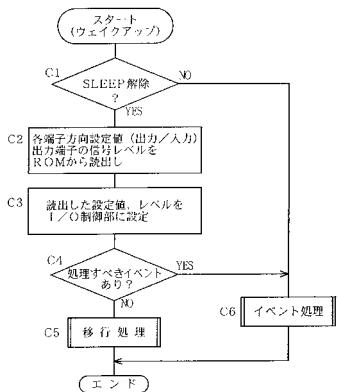

#### 【0052】

また、図13は、低消費電力モードが解除されて、CPU32が起動(ウェイクアップ)する場合の処理を示すフローチャートである。CPU32は、解除されたのがスリープモードか否かを判断し(ステップC1)、スリープモードであれば('YES')、その時点における各端子の方向(入力/出力)設定値、及び出力端子の信号レベル設定を、データとして保持しているROM(図示せず)などから読み出す(ステップC2)。そして、読み出した設定値やレベルの設定をI/O制御部44に再設定することで、各入出力端子42等における出力信号レベルを再設定する(ステップC3)。

#### 【0053】

それから、その時点で他に処理すべきイベントが発生しているか否かを判断し(ステップC4)、発生していれば('YES')そのイベントの処理を行なった後(ステップC6)、図12に示した低消費電力モードへの移行処理を行なう(ステップC5)。一方、ステップC4において処理すべきイベントが発生していないければ('NO')、そのままステップC5に移行する。

#### 【0054】

以上のように第3実施例によれば、マイコン31のCPU32は、スリープモードが再起動タイマ36によって周期的に解除される毎に、入出力端子42の信号出力レベルを再設定してからスリープモードに移行するようにした。従って、CPU32が、たとえ、スリープモード移行中に外来ノイズの影響を受けることで入出力端子42の信号出力レベルが変化したとしても、その出力レベルはスリープモードが周期的に解除される毎に再設定されるので、マイコン31の信頼性を向上させることができる。

#### 【0055】

また、マイコン31の低消費電力制御部35は、CPU32が低消費電力モードに移行する場合、入出力端子42をハイインピーダンス状態に設定するようにした。従って、CPU32が、例え、STOPモードの移行中に上述と同様に外来ノイズの影響を受けたとしても、入出力端子42がハイインピーダンス状態であるから、その端子42によってマイコン31に接続されている外部デバイスが駆動されることなく、信頼性を向上させることができる。

#### 【0056】

##### (第4実施例)

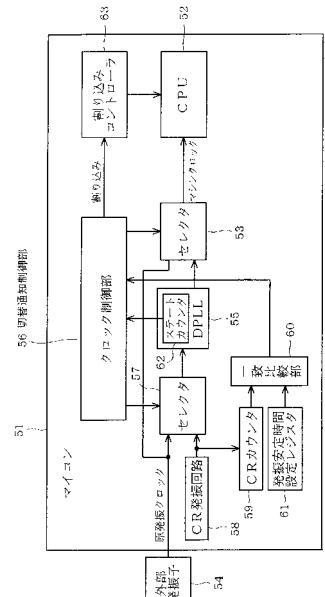

図14乃至図17は本発明の第4実施例を示すものである。図14は、マイクロコンピュータ51のクロック制御に関する機能部分を示すブロック図である。マイコン51は、CPU52を中心として構成されている。そのCPU52は、セレクタ53を介して動作用クロック(マシンクロック)信号が選択的に与えられるようになっている。

セレクタ53には、マイコン51に外付けされる外部発振子54による原発振信号と、DPLL(Digital Phase Locked Loop)回路55によって出力される遅倍クロック信号とが与えられている。そして、セレクタ53の切替えは、クロック制御部(切替通知制御部)56によって行われるようになっている。

#### 【0057】

また、DPLL回路(周波数遅倍回路)55の基準クロック信号もセレクタ57を介して与えられるようになっており、そのセレクタ57には、外部発振子54による原発振信

10

20

30

40

50

号と、C R 発振回路 5 8 によって出力される C R クロック信号とが与えられている。そして、セレクタ 5 7 の切替えもクロック制御部 5 6 によって行われるようになっている。例えば、原発振信号は周波数 4 M H z , C R クロック信号は周波数 2 5 k H z である。尚、クロック制御部 5 6 は、C R クロック信号を D P L L 回路 5 5 のクロックソースとして選択する場合は、外部発振子 5 4 の発振動作を停止させるように構成されている。

#### 【 0 0 5 8 】

C R クロック信号は、C R カウンタ 5 9 にもカウント用クロックとして与えられている。一致比較部 6 0 には、C R カウンタ 5 9 のカウントデータと、発振安定時間設定レジスタ 6 1 の設定データが与えられている。その設定データは、電源投入時にはハードウェアによって初期値がセットされるが、C P U 5 2 が実行するユーザプログラムによってもセット可能となっている。一致比較部 6 0 は、両者のデータ値を比較して一致すると、一致信号をクロック制御部 5 6 に出力するようになっている。10

#### 【 0 0 5 9 】

即ち、設定レジスタ 6 1 に、外部発振子 5 4 の発振安定時間に相当するデータをセットすれば、前記一致信号が出力されるタイミングによってその発振安定時間の経過が判る。また、クロック制御部 5 6 は、D P L L 回路 5 5 が内蔵しており内部の発振動作シーケンスを制御するために用いられるステートカウンタ（シーケンス制御手段）6 2 のカウンタ値を参照することで、D P L L 回路 5 5 の発振安定時間の経過を知ることも可能となっている。

#### 【 0 0 6 0 】

尚、ここでのステートカウンタ 6 2 は、例えば第 5 実施例における制御回路 2 0 と同様のものであり、例えば、外部発振子 5 4 の出力クロックを基準クロック信号とする場合、その 8 カウントを 1 制御周期とするようになっている。従って、遅倍動作開始時においては、その 1 制御周期が経過した時点で最初の演算結果としての遅倍クロック信号が出力されることになり、その期間が発振安定期間となる。20

#### 【 0 0 6 1 】

そして、クロック制御部 5 6 は、それらの検出タイミングにおいて、C P U 5 2 の割り込みコントローラ 6 3 にクロック切替え完了割り込み信号を出力するようになっている。割り込みコントローラ 6 3 は、その他の割り込み要因も含めてイネーブル制御やマスク制御などを行い、適切な割り込み信号を C P U 5 2 に出力するようになっている。30

#### 【 0 0 6 2 】

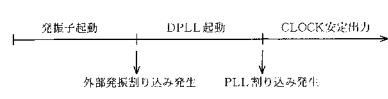

次に、第 4 実施例の作用について図 1 5 乃至図 1 7 を参照して説明する。図 1 5 は、電源投入時や、スリープ / ストップモードから C P U 5 2 が起動したウェイクアップ時におけるクロック信号の遷移状態を示すものである。即ち、スリープ / ストップモードに遷移した場合は、C R 発振回路 5 8 を除いてクロック信号の発振動作は停止される。先ず、外部発振子 5 4 が電源投入によって発振動作を開始する。発振開始の初期においてはその発振動作即ち発振周波数が不安定であるから、C P U 5 2 は D P L L 回路 5 5 の動作を禁止している。

#### 【 0 0 6 3 】

そして、C R カウンタ 5 9 のカウンタ値が発振安定時間設定レジスタ 6 1 の設定データに一致し、一致比較部 6 0 が一致信号をクロック制御部 5 6 に出力すると、クロック制御部 5 6 は、それを受け割り込み信号を、割り込みコントローラ 6 3 を介して C P U 5 2 に出力する。すると、C P U 5 2 は、その割り込み信号によって外部発振子 5 4 の発振動作が安定したことを認識し、D P L L 回路 5 5 に周波数遅倍動作を開始させる。40

そして、クロック制御部 5 6 は、今度は D P L L 回路 5 5 のステートカウンタ 6 2 のカウンタ値を参照し、D P L L 回路 5 5 の動作が安定するまで待機し、動作が安定した状態になった時点で割り込み信号を出力する。従って、C P U 5 2 はその割り込みによって D P L L 回路 5 5 の動作が安定したこと認識できる。

#### 【 0 0 6 4 】

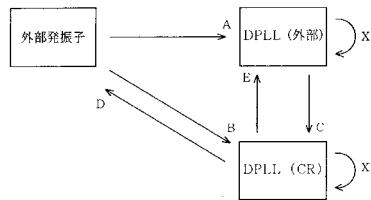

また、図 1 6 は、C P U 5 2 が通常の動作を行なっている状態において、ユーザプログ50

ラムによりマシンクロックの切替を行なう場合のダイヤグラムである。この場合、クロックソースとしては、外部発振子 54, DPLL 回路 55 (外部発振子 54 がソース), DPLL 回路 55 (CR 発振回路 58 がソース) の 3 種類があり、これらの間でクロック信号の選択切替が行なわれる。また、DPLL 回路 55 は、CPU52 が遅倍又は分周データを設定することでクロックソースの周波数を遅倍または分周可能であるから、DPLL 回路 55 単体においても周波数切替が行なわれる。これらのパターンを下記に示す。

- A : 外部発振子 DPLL 回路 (外部ソース)

- B : 外部発振子 DPLL 回路 (CR ソース)

- C : DPLL 回路 (外部ソース) DPLL 回路 (CR ソース)

- D : DPLL 回路 (CR ソース) 外部発振子

- E : DPLL 回路 (CR ソース) DPLL 回路 (外部ソース)

- X : DPLL 回路における周波数変更

10

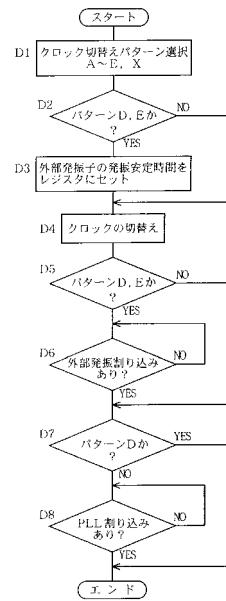

#### 【0065】

図 17 は、CPU52 が、図 16 に示すダイヤグラムに基づいてマシンクロック信号の切替を行なう場合の処理を示すフローチャートである。CPU52 は、先ず、クロック信号の切替えパターンを上記 A ~ E, X の中から選択する (ステップ D1)。そして、パターン D, E であれば (ステップ D2, 「YES」)、外部発振子 54 の発振安定時間データを設定レジスタ 61 にセットし (ステップ D3)、パターンに応じたクロック切替を行なう (ステップ D4)。

クロック切替は、CPU52 がクロック制御部 56 の内部にある設定レジスタにデータを書き込むことで、セレクタ 53, 57 を切替えて行なう。また、ステップ D2 において切替えパターンが D, E 以外であれば ('NO')、そのままステップ D4 に移行する。

20

#### 【0066】

続いて、CPU52 は、ステップ D2 と同様に切替えパターンが D, E か否かを判断し (ステップ D5)、パターン D, E であれば ('YES') 外部発振割り込みが発生するまで待機する (ステップ D6)。そして、割り込みが発生すると ('YES') ステップ D7 に移行する。また、ステップ D5 においてパターン D, E 以外の場合もステップ D7 に移行する。

#### 【0067】

ステップ D7 において、CPU52 は、切替えパターン D か否かを判断し、パターン D でなければ ('NO') PLL 割り込みが発生するのを待って (ステップ D8, 「YES」) 処理を終了する。また、ステップ D7 においてパターン D であれば ('YES') そのまま処理を終了する。即ち、CPU52 は、パターン E の場合は外部発振割り込み, PLL 割り込み双方の発生を待つことでクロック安定を認識する。パターン D の場合は外部発振割り込みのみ、その他のパターンでは PLL 割り込みのみの発生を待つことでクロック安定を認識することになる。

30

#### 【0068】

以上のように第 4 実施例によれば、マイコン 51 のクロック制御部 56 は、DPLL 回路 55 の発振動作をスタートカウンタ 62 によって監視し、遅倍クロック信号の周波数が切替えられた場合は、その切替えに伴う発振動作が安定したタイミングで CPU52 に対して割り込み要求を発生させるようにした。

40

従って、CPU52 は、冗長な待機時間を設定する必要がなくなり、処理効率を向上させることができる。そして、クロック制御部 56 は、シーケンスカウンタ 62 を参照することで DPLL 回路 55 の発振動作が安定したことを明確に認識することができる。

#### 【0069】

また、CPU52 の動作用クロック信号を、セレクタ 53, 57 によって複数のクロック信号の内から選択可能としたので、より多様なクロック信号を選択することによって、制御範囲を広げることができる。

そして、クロック制御部 56 は、外部発振子 54 の発振動作も監視し、その動作切替えに伴う発振動作が安定したタイミングでも CPU52 に対して割り込み要求を発生させる

50

ので、C P U 5 2 は、その割り込み要求の発生によってD P L L 回路5 5 の動作を開始させるのに適切なタイミングを知ることが可能となる。

#### 【 0 0 7 0 】

<以下は参考>

G . 基準クロック信号の周波数を遅倍して出力する周波数遅倍回路と、

この周波数遅倍回路によって出力される遅倍クロック信号が動作用クロック信号として供給可能であるC P U と、

前記周波数遅倍回路の発振動作を監視し、前記遅倍クロック信号の周波数が切替えられた場合は、その切替えに伴う発振動作が安定したタイミングで前記C P U に対して割り込み要求を発生させる切替通知制御部とを備えて構成されることを特徴とするマイクロコンピュータ。

10

上記G のマイクロコンピュータによれば、切替通知制御部は、周波数遅倍回路の発振動作を監視し、遅倍クロック信号の周波数が切替えられた場合は、その切替えに伴う発振動作が安定したタイミングでC P U に対して割り込み要求を発生させる。従って、C P U は、遅倍クロック信号の周波数を切替えた場合に、その発振動作が安定したことを割り込みによって知ることができるので、冗長な待機時間を設定する必要がなくなり、処理効率を向上させることができる。

#### 【 0 0 7 1 】

H . 前記周波数遅倍回路は、前記基準クロック信号に基づいて、発振動作シーケンスを制御するための制御信号を出力するシーケンス制御手段を備え、

20

前記切替通知制御部は、前記制御信号に基づいて前記周波数遅倍回路の発振動作を監視することを特徴とする上記G のマイクロコンピュータ。

上記H のマイクロコンピュータによれば、切替通知制御部は、周波数遅倍回路の発振動作シーケンスを制御するシーケンス制御手段によって出力される制御信号に基づいて、当該周波数遅倍回路の発振動作を監視するので、発振動作が安定したことを制御信号によって明確に認識することができる。

#### 【 0 0 7 2 】

I . 前記動作用クロック信号として供給可能なクロック信号が、前記遅倍クロック信号の他にも1つ以上存在し、

前記動作用クロック信号は、それら複数のクロック信号の内から選択可能に構成されていることを特徴とする上記G またはH のマイクロコンピュータ。

30

上記I のマイクロコンピュータによれば、C P U の動作用クロック信号は、遅倍クロック信号を含む複数のクロック信号の内から選択可能に構成されるので、そのような構成においても上記H と同様の作用効果を得ることができる。

#### 【 0 0 7 3 】

J . 前記切替通知制御部は、前記動作用クロック信号として供給可能なクロック信号を出力する外部発振子の発振動作も監視し、その動作切替えに伴う発振動作が安定したタイミングでも前記C P U に対して割り込み要求を発生させることを特徴とする上記I のマイクロコンピュータ。

上記J のマイクロコンピュータによれば、切替通知制御部は、外部発振子の発振動作も監視し、その動作切替えに伴う発振動作が安定したタイミングでもC P U に対して割り込み要求を発生させる。従って、外部発振子によって出力されるクロック信号が周波数遅倍回路の基準クロック信号となる場合、C P U は、前記割り込み要求の発生によって周波数遅倍回路の動作を開始させるのに適切なタイミングを知ることが可能となる。

40

#### 【 0 0 7 4 】

(第5実施例)

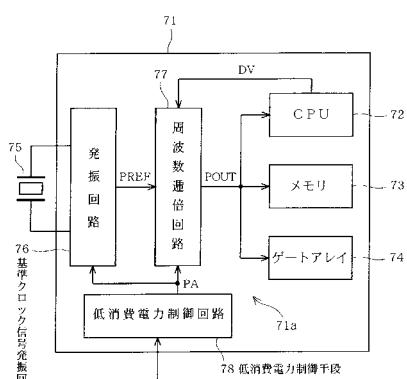

図18乃至図23は、本発明を車両用E C U(Electronic Control Unit)に適用した場合の第5実施例を示すものである。尚、以下に述べる構成の基本的部分は特開2000-357947号公報に開示されているので、以下では概略的に説明する。図18は、E C U(マイクロコンピュータ)71の電気的構成を示す機能ブロック図である。E C U 71

50

は、半導体集積回路（ I C ）として構成されており、その内部回路として、 C P U 7 2 , メモリ 7 3 及びゲートアレイ 7 4 などのクロック同期回路を有している。 E C U 7 1 には、水晶発振子 7 5 に外付けされており、発振回路（基準クロック発振回路） 7 6 は、水晶発振子 7 5 にバイアスを与えて周波数 1 6 K H z の基準クロック信号 P R E F を出力するようになっている。

#### 【 0 0 7 5 】

その基準クロック信号 P R E F は周波数遅倍回路 7 7 に与えられており、周波数遅倍回路 7 7 は、その基準クロック信号 P R E F を 5 1 2 遅倍した周波数 8 M H z 遅倍クロック信号 P O U T を生成して、 C P U 7 2 , メモリ 7 3 及びゲートアレイ 7 4 のクロック入力端子に出力するようになっている。周波数遅倍回路 7 7 は、所謂 D P L L (Digital Phase Locked Loop) 回路として構成されるものであり、前記遅倍数は、 C P U 7 2 より与えられる遅倍数設定データ D V の値に応じて設定される。

10

また、周波数遅倍回路 7 7 には、低消費電力制御回路（低消費電力制御手段） 7 8 によって E C U 7 1 の動作モードを低消費電力モードとスタンバイモードとに切換えるためのモード制御信号 P A ( 停止制御 ) が出力されるようになっている。

#### 【 0 0 7 6 】

キー検出スイッチ 7 9 は、自動車のキーがキーシリンダ（何れも図示せず）に挿入されているか否かを検出するスイッチである。そして、キー検出スイッチ 7 9 がキー検出信号を低消費電力制御回路 7 8 に出力していなければ、低消費電力制御回路 7 8 は、モード制御信号 P A をロウレベルにすることで E C U 7 1 を低消費電力モード（スリープ / ストップ）に維持するようになっている。

20

また、キー検出スイッチ 7 9 がキー検出信号を出力した場合、低消費電力制御回路 7 8 は、モード制御信号 P A をハイレベルにして、 E C U 7 1 を低消費電力モードからスタンバイモードに切換える。尚、周波数遅倍回路 7 7 及び低消費電力制御回路 7 8 は、クロック制御回路（発振回路装置） 7 1 a を構成している。

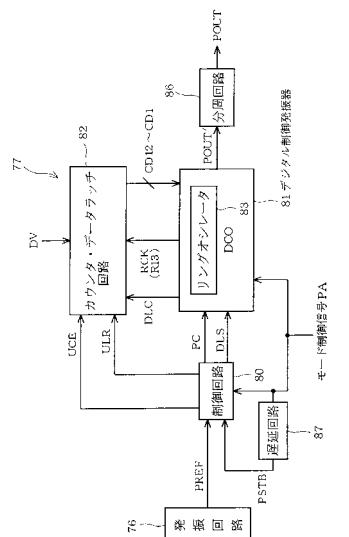

#### 【 0 0 7 7 】

図 1 9 は、周波数遅倍回路 7 7 の概略構成を示す機能ブロック図である（尚、詳細な構成については、更に特開平 8 - 2 6 5 1 1 1 号公報を参照）。制御回路（シーケンス制御手段） 8 0 には、発振回路 7 6 より出力される基準クロック信号 P R E F が与えられている。そして、制御回路 8 0 は、3 個のフリップフロップ（図示せず）で構成されるシーケンスカウンタを内蔵している。

30

そして、このシーケンスカウンタによって基準クロック信号 P R E F の入力パルス数をカウントして基準クロック信号 P R E F の 8 周期を 1 シーケンス制御周期とし、基準クロック信号 P R E F に同期して各種の制御タイミング信号を D C O ( Digital Controlled Oscillator , デジタル制御発振器 ) 8 1 及びカウンタ・データラッチ回路 8 2 に出力する。

#### 【 0 0 7 8 】

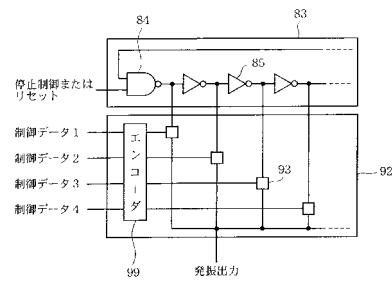

D C O 8 1 は、内部にリングオシレータ（多相クロック信号出力手段） 8 3 を備えている。リングオシレータ 8 3 は、図 2 1 に示すように、論理反転回路として N A N D ゲート 8 4 と複数個の I N V ( インバータ ) ゲート 8 5 とを備えて構成されている。これらの I N V ゲート 8 4 は、各出力端子が次段の入力端子へとリング状に接続されており、 N A N D ゲート 8 5 の一方の入力端子は最終段の I N V ゲート（図示せず）の出力端子に接続され、他方の入力端子には外部からの停止制御信号が与えられている。そして、 I N V ゲート 8 4 の各出力端子からは、夫々多相クロック信号 R 1 ~ R 1 6 が出力される。

40

#### 【 0 0 7 9 】

再び、図 1 9 を参照して、カウンタ・データラッチ回路 8 2 には、制御回路 8 0 より出力される制御タイミング信号 U C E 及び C L R が与えられるようになっている。これらの制御タイミング信号 U C E 及び C L R は、基準クロック信号 P R E F 1 周期に相当するパルス幅を有しており、制御回路 8 0 におけるシーケンス制御周期の第 3 及び第 7 周期に夫々出力される信号である。

#### 【 0 0 8 0 】

また、カウンタ・データラッチ回路82には、リングオシレータ83より出力されるクロック信号R13がRCKとして与えられ、そのクロック信号RCKによって内部のアップカウンタ(16ビット)によるカウント動作を行う。そして、カウンタ・データラッチ回路82は、制御タイミング信号UCエ出力されている間、カウンタにアップカウント動作を行わせることで、基準クロック信号PREF1周期に相当する時間をクロック信号RCKによってカウントする。

そのカウントデータは、制御回路80よりシーケンス制御周期の第5周期で出力される制御タイミング信号DLSがDCO81を介して与えられるラッチ信号 DLCのタイミングでラッチされ、制御タイミング信号CLRが出力されるとラッチされたデータはクリアされる。

10

#### 【0081】

カウンタ・データラッチ回路82は、カウントした16ビットのデータDT16～DT1を、CPU72により与えられる遅倍数設定データDVに応じてデータビットを右シフトし、そのシフト後のデータの12ビットをラッチする。そして、ラッチされた12ビットのデータは、CD12～CD1としてDCO81に出力される。DCO81が出力する遅倍クロック信号POUTは、デューティ比を調整するための分周回路86を介して2分周されて、遅倍クロック信号POUTとして出力される。

また、モード制御信号PAは、制御回路80にも与えられていると共に、例えば、基準クロック信号PREF1周期分程度の遅延時間を与える遅延回路87を介して、制御回路80に動作開始信号PSTBとしても与えられるようになっている。

20

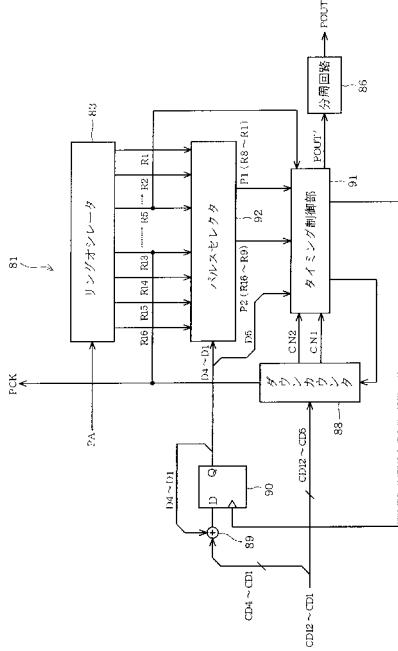

#### 【0082】

図20は、DCO81の詳細な構成を示す機能ブロック図である。カウンタ・データラッチ回路82より与えられるラッチデータCD12～CD1の内、上位側の8ビットであるCD12～CD5は、ダウンカウンタ88のカウントデータとして所定のタイミングでロードされるようになっている。そして、ダウンカウンタ88は、リングオシレータ83より出力されるクロック信号R13によってロードされたカウントデータをダウンカウントするようになっている。

#### 【0083】

また、ラッチデータCD12～CD1の内、下位側の4ビットであるCD4～CD1は、加算器89を介してレジスタ90のデータ入力端子Dに与えられるようになっている。レジスタ90は、タイミング制御部91より出力されるタイミング信号によって加算器89の出力データを5ビットのデータD5～D1として出力するようになっており、その内の下位3ビットデータD4～D1は、パルスセレクタ92に与えられると共に、加算器89に被加算値として入力されるようになっている。また、レジスタ90より出力されるデータD5は、加算器89における加算に応じて発生するキャリー信号に相当するものであり、タイミング制御部91に与えられるようになっている。

30

#### 【0084】

パルスセレクタ92には、リングオシレータ83より出力される多相クロック信号R16～R1が与えられており、それらの多相クロック信号R16～R1の内、レジスタ90より出力されるデータD4～D1の値(10進数値+1)に相当する番号)に対応するものを1つ選択して、出力端子P1(R8～R1), P2(R16～R9)の何れか一方からタイミング制御部91に出力するようになっている。タイミング制御部91には、リングオシレータ83より出力されるクロック信号R5が与えられている。

40

また、ダウンカウンタ88は、ロードされたカウントデータをダウンカウントして行き、そのカウント値が“2”になると出力信号CN2をハイレベルにし、カウント値が“1”になると出力信号CN1をハイレベルにしてタイミング制御部91に出力するようになっている。

#### 【0085】

以上の動作の概略は以下のようになる。即ち、基準クロック信号PREFの8周期毎に、基準クロック信号PREFの1周期相当のカウントデータDT16～DT1がカウントされ

50

、その内遅倍データ D v に応じてビット右シフトされた 12 ビットデータ C D 12 ~ C D 1 が D C O 8 1 に与えられる。そして、上位 8 ビットの C D 12 ~ C D 5 がダウンカウントされると、レジスタ 9 0 より与えられる下位データ D 4 ~ D 1 の値 (+ 1) に対応する多相クロック信号 R 16 ~ R 1 の何れか 1 つが選択されて遅倍クロック信号 P OUT として出力される。

#### 【 0 0 8 6 】

そして、図 2 1 に示すように、パルスセレクタ 9 2 の内部では、各多相クロック信号 R 1 ~ R 16 に対応してアナログスイッチ 9 3 が配置されている。そして、複数のアナログスイッチ 9 3 の内何れかを制御データ D 1 ~ D 4 に基づいてエンコーダ 9 9 によりエンコードし逐一的にオンすることで、多相クロック信号 R 1 ~ R 16 の内 1 つをタイミング制御部 9 1 に出力するようになっている。10

#### 【 0 0 8 7 】

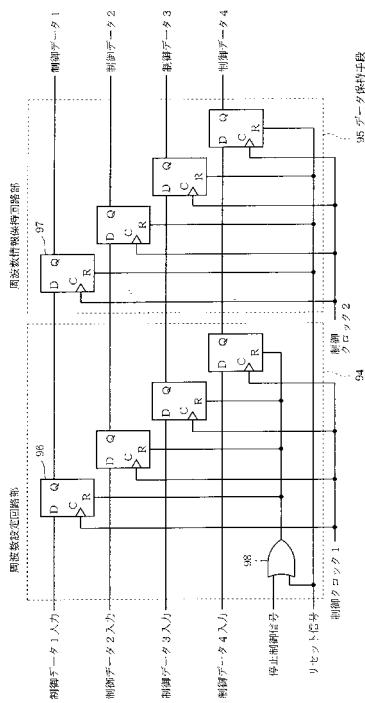

図 2 2 は、カウンタ・データラッチ回路 8 2 の内部構成の一部を示すものである。即ち、制御データ C D 12 ~ C D 1 は( 図示は C D 4 ~ C D 1 のみ )、周波数設定回路部 9 4 、周波数情報保持回路部( データ保持手段 ) 9 5 によるダブルラッチ構成で保持されるようになっている。これらの回路部 9 4 , 9 5 は、夫々フリップフロップ 9 6 , 9 7 で構成されており、クロック入力端子には制御クロック 1 , 2 が与えられている。

そして、周波数設定回路部 9 4 を構成するフリップフロップ 9 6 のリセット端子にはリセット信号が与えられている。一方、周波数情報保持回路部 9 5 を構成するフリップフロップ 9 6 のリセット端子には、OR ゲート 9 8 を介してリセット信号と、低消費電力モード時の停止制御信号が与えられている。20

#### 【 0 0 8 8 】

尚、周波数情報保持回路部 9 5 は、通常動作時においては、周波数設定回路部 9 4 によって制御クロック 1 により同期化され保持された制御データ 1 ~ 4 を、制御クロック 2 によって再同期化するために使用されているものであり、それと同様の機能を有するものは、特開 2000 - 357947 においても存在している( 但し、低消費電力モードに移行すると、そのデータはリセットされて消失するようになっていた )。

#### 【 0 0 8 9 】

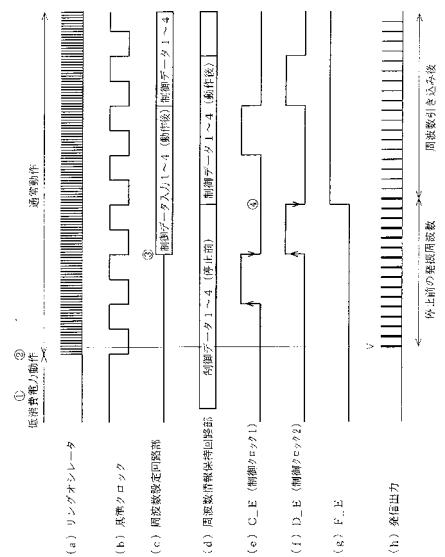

次に、第 5 実施例の作用について図 2 3 を参照して説明する。図 2 3 は、周波数遅倍回路 7 7 が低消費電力モードにある状態から、起動して発振動作を行なう場合を示すタイミングチャートである。( 1 ) の低消費電力モードにおいては、リングオシレータ 8 3 及び発振回路 7 6 の発振動作は停止した状態にある。そして、( 2 ) において低消費電力モードが解除されると、それらは発振動作を開始する。30

また、低消費電力モード中に、周波数設定回路部 9 4 のデータはリセットされているが、周波数情報保持回路部 9 5 のデータは保持されている。この保持されているデータは、( 1 ) の低消費電力モードに移行する前に、周波数遅倍回路 7 7 が行なっていた発振動作に使用されたデータ( 発振制御条件 )であり、リングオシレータ 8 3 のクロック信号によって発振回路 7 6 の基準クロック信号の周期を計測したデータである。

#### 【 0 0 9 0 】

従って、( 2 ) で低消費電力モードが解除されると、周波数遅倍回路 7 7 は、基準クロック信号周期の計測を再度行なわずとも、周波数情報保持回路部 9 5 に保持されているデータに基づいて直ちに発振動作を開始することができる。そして、( 3 ) で制御クロック 1 が立ち下がると、周波数設定回路部 9 4 は、ウェイクアップ後の C P U 7 2 によって新たに設定された制御データ入力 1 ~ 4 を出力し、周波数情報保持回路部 9 5 は、制御クロック 2 の立ち上がりでその制御データ入力 1 ~ 4 をラッチして、( 4 ) の立下りで新たに設定された制御データ 1 ~ 4 を出力する。また、( 4 ) では、遅倍クロック信号出力( 発振出力 )のイネーブル信号である F\_E がアクティブとなり、クロック信号 P OUT が C P U 7 2 に出力される。40

#### 【 0 0 9 1 】

以上のように第 5 実施例によれば、デジタル制御方式の D P L L 回路として構成される50

周波数遅倍回路 77 の発振動作を低消費電力モード移行することで一時的に停止させる場合に、その時点で設定されている制御データ C D 1 2 ~ C D 1 を周波数情報保持回路部 95 によって保持し、その保持した制御データ C D 1 2 ~ C D 1 に基づいて発振動作を再開させるようにした。従って、従来とは異なり、発振動作を再開させる際に発振制御条件を再度設定し直す必要がないので、再開時における発振状態をより速く安定させることができる。そして、更に低消費電力化を図ることができる。

#### 【 0 0 9 2 】

また、周波数遅倍回路 77 を、複数個の論理反転回路がリング状に接続されてなるリングオシレータ 83 を備えて構成したので、デジタル制御方式の発振動作に必要な多相クロック信号を得る構成をより少ないゲート数で実現することができる。更に、低消費電力制御回 78 は、クロック同期回路の動作を停止させて低消費電力モードに移行させる場合にリングオシレータ 83 の発振動作を停止させるので、一層の低消費電力化を図ることができる。そして、周波数遅倍回路 77 は、発振回路 76 によって出力される基準クロック信号 P REF の周波数を  $n$  遅倍した  $n$  遅倍クロック信号を生成して出力する D C O 81 を備えるので、デジタル制御方式で高精度の発振動作を行なわせることができる。

10

#### 【 0 0 9 3 】

ここで、周波数遅倍回路 77において、制御データを設定し直すことを想定すると、それに応じて基準クロック信号 P REF の周期を多相クロック信号の周期に基づいて計測し、その計測値に基づいて遅倍動作をやり直すことになる。それに対して、制御データを保持する構成とすれば、基準クロック信号 P REF の周期計測をやり直す必要がなくなるため、発振動作を極めて高速に安定化させることができるとなる。

20

#### 【 0 0 9 4 】

また、従来のアナログ方式の P L L 回路 200において、同様に発振動作を一時的に停止させる場合を想定すると、位相比較器 201 が出力する電圧信号を、一旦 A / D 変換してそのデジタルデータをラッピングなどして保持し、発振動作を再開させる場合は、保持したデジタルデータを D / A 変換して出力させる、という構成にならざるを得ない。それに対して、第 5 実施例のようにデジタル制御方式の周波数遅倍回路 77 であれば、制御データは一貫してデジタル形式であるから、データの保持を極めて容易に行なうことができるので、アナログ方式に比較しても有利である。

30

#### 【 0 0 9 5 】

< 以下は参考 >

K . 設定された発振制御条件に応じて定まる周波数で発振動作が可能であると共に、前記発振動作が一時的に停止可能に構成されるデジタル制御方式の発振回路装置において、

発振動作を一時的に停止させる際に、その時点で設定されている発振制御条件が保持可能に構成され、保持された発振制御条件に基づいて発振動作を再開させるように構成されていることを特徴とする発振回路装置。

上記 K の発振回路装置によれば、デジタル制御方式の発振動作を一時的に停止させる場合はその時点で設定されている発振制御条件が保持され、その保持された発振制御条件に基づいて発振動作を再開させる。従って、従来とは異なり、発振動作を再開させる際に発振制御条件を再度設定し直す必要がないので、再開時における発振状態をより速く安定させることができる。そして、更に低消費電力化を図ることができる。

40

#### 【 0 0 9 6 】

L . 複数個の論理反転回路がリング状に接続されてなるリングオシレータを備えて構成されていることを特徴とする上記 K の発振回路装置。

上記 L の発振回路装置によれば、複数個の論理反転回路がリング状に接続されてなるリングオシレータを備えて構成されるので、デジタル制御方式の発振動作に必要な多相クロック信号を得る構成をより少ないゲート数で実現することができ、一層の低消費電力化を図ることができる。

M . 前記発振制御条件を、発振動作を再開させる以前に変更可能に構成されていることを特徴とする上記 K または L の発振回路装置。

50

上記Mの発振回路装置によれば、発振制御条件が、発振動作を再開させる以前に変更可能に構成されるので、発振動作を再開させる際に発振周波数を切替えることができる。

#### 【0097】

##### (第6実施例)

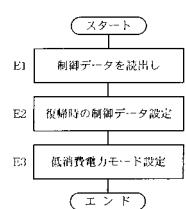

図24は、本発明の第6実施例を示すものである。第6実施例では、CPU52が、低消費電力モードが解除されると同時に、周波数遅倍回路77によるn遅倍クロック信号の周波数を変化させるように処理する例を示す。即ち、周波数情報保持回路部95の保持データは、CPU72によって読み出し及び書き込みが可能となるように構成されている。

図24に示すフローチャートにおいて、CPU72は、先ず、周波数情報保持回路部95の保持データを読み出す(ステップE1)。すると、そのデータに応じて次回の起動時における遅倍率を決定し、起動時における周波数に応じたデータを周波数情報保持回路部95に書き込む(ステップE2)。それから、低消費電力モードに移行する(ステップE3)。

#### 【0098】

以上のように第6実施例によれば、制御データCD12～CD1が、現在の発振動作を停止させる以前に変更可能に構成されるので、例えば、CPU52が発振動作を制御すると共に発振制御条件を設定する構成の場合、CPU52が発振動作を停止させる前の段階で、次回に動作を再開させる場合の発振周波数を変更したい場合には、予めそれに応じた発振制御条件を設定しておくことができる。

#### 【0099】

##### <以下は参考>

N. 前記発振制御条件を、現在の発振動作を停止させる以前に変更可能に構成されていることを特徴とする上記Mの発振回路装置。

上記Nの発振回路装置によれば、発振制御条件を、現在の発振動作を停止させる以前に変更可能に構成されるので、例えば、CPUが発振動作を制御すると共に発振制御条件を設定する構成の場合、CPUが発振動作を停止させる前の段階で、次回に動作を再開させる場合の発振周波数を変更したい場合には、予めそれに応じた発振制御条件を設定しておくことができる。

#### 【0100】

O. 所定の位相差を有する多相クロック信号をデジタル制御による発振動作で生成して出力する多相クロック信号出力手段を備え、基準クロック発振回路によって出力される基準クロック信号の周期を前記多相クロック信号の周期に基づいて計測し、その計測値に基づき前記基準クロック信号の周波数を前記多相クロック信号の位相差を分解能としてn遅倍したn遅倍クロック信号を生成して出力する周波数遅倍回路を備えて構成されていることを特徴とする上記K～Lの何れかの発振回路装置。

上記Oの発振回路装置によれば、多相クロック信号出力手段を備え、基準クロック発振回路によって出力される基準クロック信号の周波数をn遅倍したn遅倍クロック信号を生成して出力する周波数遅倍回路を備えて構成されるので、デジタル制御方式で高精度の発振動作を行なわせることができる。

そして、上記の周波数遅倍回路を備える構成において発振制御条件を設定し直すことを想定すると、それに応じて基準クロック信号の周期を多相クロック信号の周期に基づいて計測し、その計測値に基づいて遅倍動作をやり直すことになる。それに対して、発振制御条件を保持する構成とすれば、基準クロック信号の周期計測をやり直す必要がなくなるため、発振動作を極めて高速に安定化させることが可能となる。

#### 【0101】

P. 前記周波数遅倍回路によって出力されるn遅倍クロック信号がクロック入力端子に与えられて動作するクロック同期回路の動作を停止させて低消費電力モードに移行させる場合に、前記多相クロック信号出力手段の発振動作を停止させる低消費電力制御手段と、

前記発振制御条件として、前記基準クロック信号の周期測定データを保持するデータ保持手段とを備えたことを特徴とする上記Oの発振回路装置。

10

20

30

40

50

上記 P の発振回路装置によれば、低消費電力制御手段は、クロック同期回路の動作を停止させて低消費電力モードに移行させる場合に多相クロック信号出力手段の発振動作を停止させ、データ保持手段は、基準クロック信号の周期測定データを保持する。従って、低消費電力モードが解除された場合には、データ保持手段によって保持されている周期測定データに基づく発振動作を直ちに行なわせることができる。

#### 【0102】

(第7実施例)

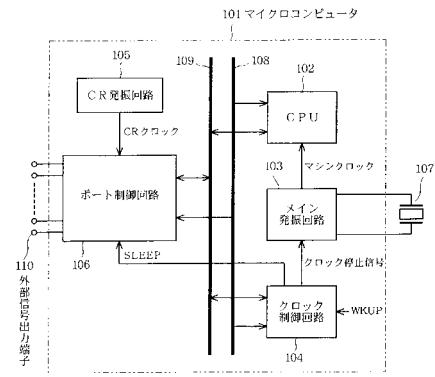

図25乃至図28は、本発明の第7実施例を示すものである。図25は、例えば車両用のボディECU(Electronic Control Unit)などに使用されるシングルチップマイクロコンピュータ(マイコン)の一構成例を示すものである。マイコン101は、CPU102を中心として、その周辺にメイン発振回路103、クロック制御回路104、CR発振回路105、ポート制御回路(信号レベル変化手段)106などを備えている。

10

#### 【0103】

メイン発振回路103は、マイコン101の外部に接続される水晶発振子107を発振させてCPU102に動作用のクロック信号(マシンクロック或いはシステムクロック)を供給するものである。クロック制御回路104は、CPU102によりアドレスバス108及びデータバス109を介してスリープ/ストップモードを開始させる指令が与えられると、メイン発振回路103に対してクロック停止信号を出力し、メイン発振回路103によるクロック信号の出力を停止させ、CPU102(若しくは、CPU102を含むマイコン101全体)をスリープ/ストップモードに設定する。

20

#### 【0104】

ここで、スリープモードとは、一旦移行するとクロック制御回路104に内蔵されているタイマで所定時間が経過した時点で自動的に解除されるモードを言うものとし、ストップモードとは、一旦移行すると外部においてウェイクアップ要因(後述するウェイクアップ信号など)が発生するまで解除されないモードを言うものとする。即ち、これらは、CPU102の動作状態を通常時よりも低下させることで消費電力の低下を図るモードである。

#### 【0105】

そして、クロック制御回路104は、ウェイクアップ要因の発生に応じてウェイクアップ信号WKUPが出力されると、クロック停止信号の出力を中止してメイン発振回路103によるクロック信号の出力を再開させるようになっている。尚、スリープモードにあっても、ウェイクアップ信号WKUPの出力によって当該モードは解除されるようになっている。

30

例えば、メイン発振回路103の発振周波数は4MHz程度であり、CR発振回路105の発振周波数は25kHz程度である。また、CPU102は、周波数4MHzのクロックを、内蔵するPLL発振回路(図示せず)で4倍して16MHzのクロック周波数で動作するようになっている。

#### 【0106】

ポート制御回路106は、CPU102が内部のレジスタに行う設定に応じて、マイコン101の出力端子(外部信号出力端子)110のレベル制御を行う回路である。また、ポート制御回路106には、クロック制御回路104によってスリープモード中に出力されるSLEEP信号が与えられている。

40

尚、具体的には図示しないが、マイコン101は、その他、割込みコントローラ、DMAコントローラ、ウォッチドッグタイマー、A/Dコンバータ、D/Aコンバータやシリアル通信回路などの周辺回路を備えている。

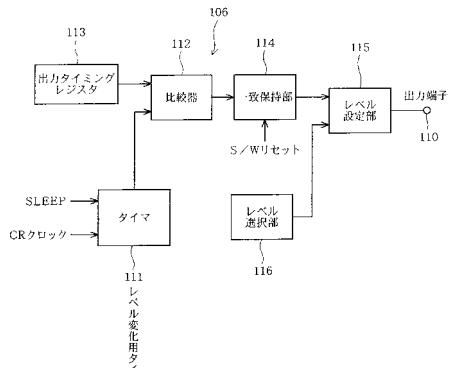

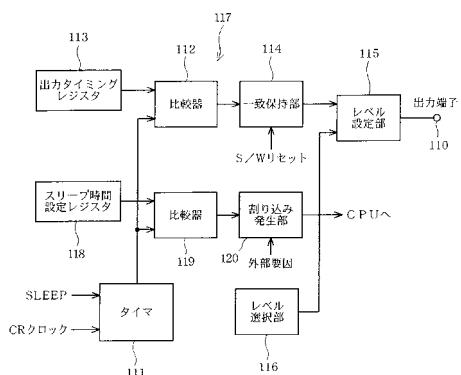

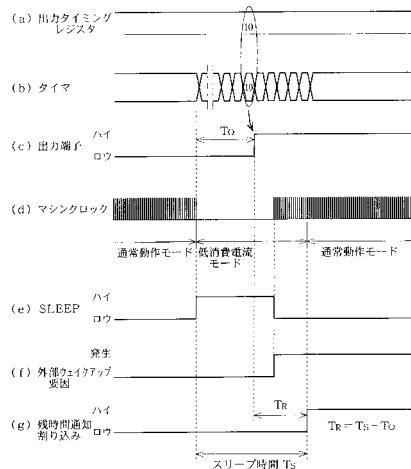

#### 【0107】

図26は、ポート制御回路106の内部構成を示す機能ブロック図である。タイマ(レベル変化用タイマ)111は、CR発振回路105によって出力されるCRクロック信号に基づいてカウント動作を行なうものであり、そのカウントデータは比較器(比較回路)112に与えられている。尚、タイマ111は、SLEEP信号がアクティブの場合カウ

50

ント動作がイネーブルとなる。

#### 【0108】

比較器112には、出力タイミングレジスタ113の設定データも与えられており、比較器112は、両者のデータ値が一致すると、一致信号を一致保持部114を介してレベル設定部115に出力する。出力タイミングレジスタ113は、CPU102によるデータの書き込みが可能に構成されたレジスタである。また、一致保持部114は、比較器112によって出力された一致信号のアクティブ状態を保持するフリップフロップである。

#### 【0109】

レベル設定部115には、レベル選択部116において設定されたレベルの信号を、一致保持部114を介して与えられる一致信号をトリガとしてマイコン101の出力端子110に出力するものである。レベル選択部116は、出力タイミングレジスタ113と同様に、CPU102によるデータの書き込みが可能に構成されたレジスタである。また、一致保持部114の出力状態は、CPU102が別途設けられているリセットレジスタに書き込みを行なうことで、リセットする(S/Wリセット)ことが可能に構成されている。

10

#### 【0110】

尚、このポート制御回路106の機能は、以下のように動作させることを目的としたものである。即ち、CPU102がスリープモードからウェイクアップした場合に、マイコン101の端子に接続されている制御対象等の外部デバイスについて、何らかの処理を行なう必要があるとする。その時に、処理の前段階として、当該外部デバイスの機能をアクティブにする(例えば、動作用電源を投入する)ことが要求される場合に、CPU102がウェイクアップしてから全ての手順を踏むと、その処理が完了するまでに長い時間を要する。

20

そこで、第7実施例では、CPU102がスリープモードに移行している場合においても、その解除前の段階で出力端子110のレベルをハードウェア的に制御し、外部デバイスの機能を予めアクティブにすることを目的とする。

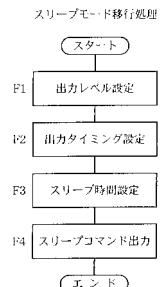

#### 【0111】

次に、第7実施例の作用について図27及び図28を参照して説明する。図27は、CPU102によるスリープモード移行処理の内容を示すフローチャートである。先ず、CPU102は、レベル選択部116に書き込みを行なうことで、スリープモード中に変化させる出力端子110のレベルを設定する(例えば、L→H, ステップF1)。続いて、出力タイミングレジスタ113に書き込みを行なうことで、スリープモード中のどのタイミングで出力端子110のレベルを変化させるかを設定する(ステップF2)。

30

#### 【0112】

それから、CPU102は、クロック制御回路104の図示しない内部レジスタに書き込みを行なうことで、スリープモードの継続時間を設定すると(ステップF3)、クロック制御回路104に対してスリープコマンドを発行する(ステップF4)。すると、クロック制御回路104は、それを受けたメイン発振回路103に対してクロック停止信号を出力して発振動作を停止させる。並行して、クロック制御回路104は、ポート制御回路106に対してSLEEP信号を出力する。

40

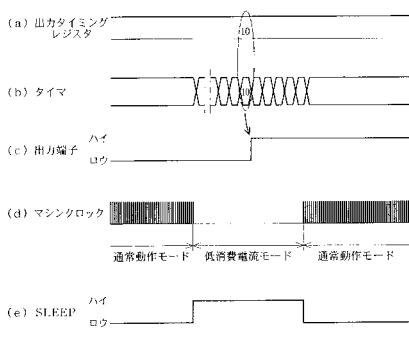

#### 【0113】

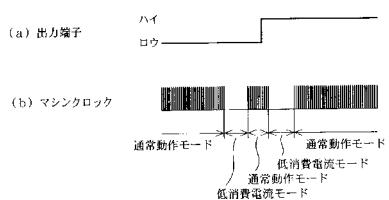

図28は、スリープモード移行中のタイミングチャートである。SLEEP信号がアクティブ(ハイ)になると(e)、メイン発振回路103によって出力されるマシンクロックは停止する(d)。そして、ポート制御回路106のタイマ111が、SLEEP信号の立ち上がりからカウント動作を開始する(b)。出力タイミングレジスタ113には、例えば設定データ「10」がセットされており(a)、タイマ111のカウント値が「10」に達すると、比較器112は一致信号を出力する。

#### 【0114】

すると、その時点で、レベル設定部115は出力端子110の信号レベルをL(ロウ)からH(ハイ)に変化させる。ここで、出力端子110の信号レベルがハイに変化したことで、その出力端子110に接続されている外部デバイスはアクティブ状態となる。その

50

後、設定されたスリープ継続期間が経過してCPU102がウェイクアップすると、CPU102は、当該外部デバイスに対して直ちに必要な処理を行うことが可能となる。そして、その処理を実行した後は、一致保持部114をS/Wリセットすることで、出力端子110の信号レベルを元に戻す。

#### 【0115】

以上のように第7実施例によれば、マイコン101のポート制御回路106は、CPU102がスリープモードに設定されている期間内に、出力端子110のレベルを変化させるようにした。従って、CPU102は、出力端子110のレベルを変化させるためだけに通常の動作モードを継続する必要がないので、消費電力を低減することができる。

そして、ポート制御回路106は、タイマ111のカウント値と出力タイミングレジスタ113のレジスタ値とを比較器112が比較し、両者が一致することでトリガ信号が出力されると出力端子110のレベルを変化させるので、レジスタ113に設定されるタイミングで、出力端子110のレベルを変化させることができる。また、そのレジスタ113は、CPU102によって任意のデータ値が設定可能に構成されるので、ユーザプログラムによってレベル変化タイミングを任意に設定することができる。

#### 【0116】

加えて、出力端子のレベル110は、スリープモードが解除されるとCPU102によってリセットすることが可能に構成されるので、CPU102が必要な処理を行った時点で出力端子のレベルを直ちにリセットすることができる。

#### 【0117】

##### (第8実施例)

図29及び図30は、本発明の第8実施例を示すものであり、第7実施例と同一部分には同一符号を付して説明を省略し、以下異なる部分についてのみ説明する。第8実施例におけるポート制御回路117は、第7実施例の構成に機能を追加したものである。即ち、スリープ時間設定レジスタ118が追加されており、そのレジスタ118の設定データは、比較器119によってタイマ111のカウント値と比較される。

#### 【0118】

比較器119は、両者が一致した時点で一致信号を割り込み発生部120に出力する。但し、割り込み発生部120は、比較器119によって一致信号が出力される以前に外部ウェイクアップ要因が発生し、スリープモードが解除された場合に、前記一致信号を受けてCPU102に割り込み要求を発生させるようになっている。即ち、タイマ111、スリープ時間設定レジスタ118、比較器119及び割り込み発生部120は、割り込み発生手段121を構成している。

#### 【0119】

次に、第8実施例の作用について図30をも参照して説明する。先ず、割り込み発生手段121の機能目的について述べる。スリープモードは、スリープ時間が経過する以前であっても外部要因の発生によって解除されるが、第7実施例の機能によってポート制御回路106が出力端子110のレベルを変化させた後に、外部要因の発生によって解除が行なわれると、次のような問題が発生する。

即ち、第7実施例において述べたように、ポート制御回路106が出力端子110のレベルを変化させる目的は、スリープモードが解除されると、CPU102が直ちに外部デバイスに対する処理を実行できるようにするためである。従って、出力端子110のレベルが変化した時点から、スリープモードがタイマによって解除されるまでの時間は、通常、外部デバイスをアクティブにするために必要最小限の時間に設定される。何故なら、この時間に冗長性を持たせると電流消費量が増加するからである。

#### 【0120】

そのような事情において、スリープモードが、スリープ時間の経過前に解除されると、CPU102が起動した時点では、出力端子110のレベルを変化させてから必要な時間が経過していないため、外部デバイスが未だインアクティブ状態となっているおそれがある。そして、CPU102は、起動した時点では、本来の必要な時間が後どれ位なのかを

10

20

30

40

50

知る手段がない。

#### 【0121】

そこで、第8実施例では、CPU102に対して本来必要であった時間を割り込みによって通知することを目的とする。即ち、図30に示すように、ポート制御回路117は、第7実施例と同様に出力端子110のレベルを変化させた後、外部要因の発生によって(f)スリープモードが早期解除されると(d,e)、割り込み発生部120がアクティブとなる。そして、本来のスリープ時間が経過して比較器119が一致信号を出力すると、その時点でCPU102に対して割り込みを発生させる。

従って、CPU102は、その割り込み信号によって、外部デバイスがアクティブとなつことが認識可能となり、必要な処理を行なった後に、出力端子110のレベルをS/Wリセットする。

#### 【0122】

以上のように第8実施例によれば、割り込み発生手段121は、ポート制御回路117信号が出力端子110のレベルを変化させた後、解除要因の発生によってスリープモードが解除されると、図示しない解除タイマによってスリープモードが解除される予定のタイミングでCPU102に対して割り込み要求を発生させるようにした。したがって、CPU102は出力端子110について変化させた信号レベルの維持期間を把握できるようになり、その割り込み要求を認識した後、必要に応じて出力端子110のレベルをリセットすることができる。

#### 【0123】

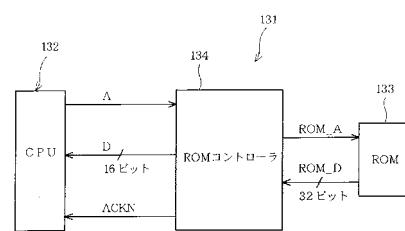

##### (第9実施例)

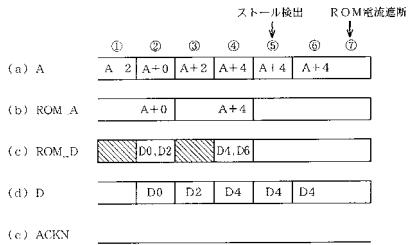

図31乃至図34は本発明の第9実施例を示すものである。マイクロコンピュータ131の構成を示す図31において、CPU132は、データバスが例えば16ビット構成であり、ROM133に記憶されているプログラムやデータを読み出して実行するようになっている。ROM133は、例えばフラッシュROMで構成されており、データバス幅はCPU132の2倍の32ビット構成となっている。

#### 【0124】

そして、両者の間にはROMコントローラ(メモリインターフェイス回路装置)134が介在しており、CPU132は、ROMコントローラ134を介してROM133よりデータを読み出すようになっている。ROMコントローラ134は、CPU132によって出力された読み出しアドレスAについて所定の操作を行なったアドレスROM\_Aを出力してROM133よりデータROM\_Dを読み出す。そのデータを適切なタイミングでCPU132側のデータバス上にデータDとして出力するようになっている。

即ち、マイコン101においては、フラッシュROMで構成されるROM133の読み出し速度はCPU132の処理速度に比較して遅いため、ROM133側のデータバス幅をCPU132の2倍として、両者の間の調停制御をROMコントローラ134が行なうように構成されている。

#### 【0125】

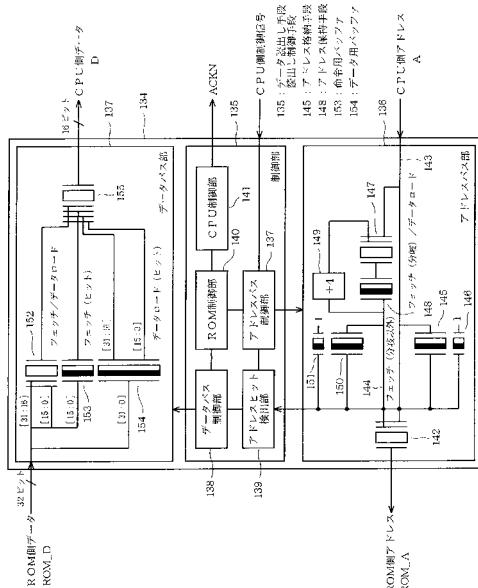

図32は、ROMコントローラ134の内部構成を示すブロック図である。ROMコントローラ134は、制御部(データ読み出し手段、読み出し制御手段)135、アドレスバス部136、データバス部(読み出し制御手段)137によって構成されている。制御部135は、アドレスバス制御部137、データバス制御部138、アドレスヒット検出部139、ROM制御部140及びCPU制御部141を備えている。

#### 【0126】

アドレスバス制御部137、データバス制御部138は、夫々アドレスバス部136、データバス部137の制御を行う。アドレスヒット検出部139は、アドレスバス部136が保持しているアドレスと、CPU132によって出力されたアドレスとの一致(ヒット)を検出するものである。CPU制御部141は、CPU132に対して読み出し制御信号(アクノリッジ信号ACKN)を出力する。尚、読み出し制御信号ACKNは、CPU132に対してROMデータ読み出しをウェイトさせる場合にハイレベルとなり、ロウレ

10

20

30

40

50

ベルではアクノリッジがアクティブであることを示している。そして、ROM制御部140は、これらを統括的に制御するようになっている。

#### 【0127】

アドレスバス部136は、ROM133に対してマルチプレクサ(MUX)142を介してアドレスを出力するようになっている。そのMUX142の一方の入力側には、CPU132側のアドレスバスに直結されるスルーパス143が接続されており、他方の入力側にはカウンタ側バス144が接続されている。

スルーパス143には、バッファ(ラッチ)145の入力側も接続されており、バッファ(アドレス格納手段)145の出力側は、アドレスヒット検出部139に接続されている。バッファ145は、CPU132がデータ読み出しサイクルを実行した場合に出力されたアドレスが格納される。

#### 【0128】

また、ビット出力部146は、ROM133のデータ読み出し対象アドレスと、そのアドレスに応じたデータがバッファ145、及び後述するデータ用バッファ154に格納されている場合に、ROM読み出しイネーブルを示すビット(バリッドビット)がセットされるように構成されており、その出力側もアドレスヒット検出部139に接続されている。尚、ビット出力部146のリセットは、ハードウェアによって行われる。

#### 【0129】

一方、カウンタ側バス144側には、MUX147、カウンタバッファ(アドレス保持手段)148及びカウンタ(+4)149が配置されている。MUX147の一方の入力側にはスルーパス143が接続されており、他方の入力側には、カウンタ149の出力側が接続されている。そして、MUX147の出力端子は、カウンタバッファ148を介してカウンタ149の入力側及びカウンタ側バス144に接続されている。

また、カウンタ側バス144には、スルーパス143側と同様にバッファ150の入力側も接続されており、バッファ150の出力側は、アドレスヒット検出部139に接続されている。また、ビット出力部151の出力側もアドレスヒット検出部139に接続されている。

#### 【0130】

ビット出力部151は、ビット出力部146と同様に、ROM133の命令読み出し対象アドレスと、そのアドレスに応じた命令がバッファ148、及び後述する命令用バッファ153に格納されている場合に、ROM読み出しイネーブルを示すビットがセットされるように構成されている。そして、CPU132による命令読み出しが連続したアドレスで行われている場合には、ROMコントローラ153、ROM133との間ににおける1サイクル毎に、ビット出力部151及び153とCPU132側のアドレスAからヒット、ミスヒットを交互に検出することになる。

#### 【0131】

データバス部137は、MUX152、命令用バッファ153、データ用バッファ154及びMUX155で構成されている。MUX152の入力側には、32ビットのROM-Dの内、上位16ビット[31:16]、下位16ビット[15:0]が夫々接続されている。命令用バッファ153は、CPU132がROM133に対して命令読み出し(インストラクションフェッチ)サイクルを実行した場合に、下位16ビットデータが格納される。

#### 【0132】

データ用バッファ154は、CPU132がROM133に対してデータ読み出し(データロード)サイクルを実行した場合に、32ビットデータが格納される。そして、MUX155は、MUX152、命令用バッファ153、データ用バッファ154の上位側、下位側の何れかを選択してCPU132側のデータバスに出力するようになっている。

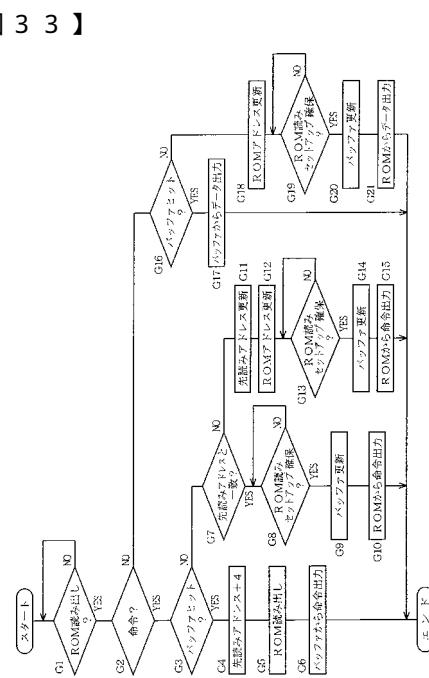

#### 【0133】

図33は、CPU132がROM133に対する読み出しサイクルを実行する場合におけるROMコントローラ134の制御内容を示すフローチャートである。また、図34は

10

20

30

40

50

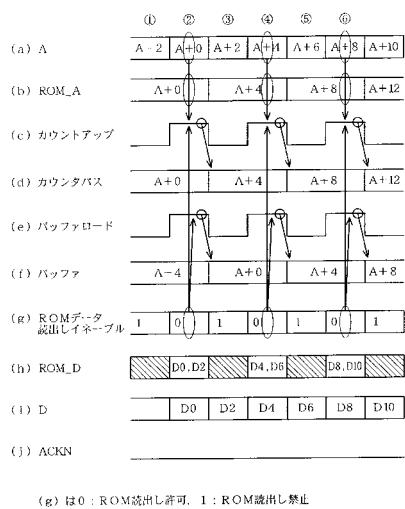

、 C P U 1 3 2 が命令読み出しサイクルを連続的に実行した場合のタイミングチャートである。尚、 R O M コントローラ 1 3 4 は純粹にハードウェアのみで構成されており、 図 3 3 のフロー チャートは、 そのハードウェアの動作を表したものである。

#### 【 0 1 3 4 】

図 3 4 における動作概要を説明すると、 C P U 1 3 2 は、 命令読み出しを 1 6 ビット ( 2 バイト ) 単位で行う ( a ) 。 その場合、 R O M コントローラ 1 3 4 は、 自身がバッファ 1 4 8 に保持しているアドレスを、 R O M 1 3 3 のデータバス幅 3 2 ビットに合わせて「 4 」ずつ増加させ、 命令を 3 2 ビット ( 4 バイト ) 単位で読み出すようになっている ( b ) 。

そして、 R O M コントローラ 1 3 4 は、 同時に読み出した 3 2 ビットの命令の内、 上位 1 6 ビットは読み出しと同時に C P U 1 3 2 側のデータバスに出力し、 下位 1 6 ビットは一旦バッファ 1 5 3 に格納する ( h ) 。 そして、 C P U 1 3 2 が次の読み出しサイクルを実行した場合に、 バッファ 1 5 3 に格納した命令を前記データバスに出力する ( i ) 。

#### 【 0 1 3 5 】

また、 制御部 1 3 5 は、 C P U アドレス A と、 カウンタバッファ 1 4 8 が保持しているアドレスとが一致すると、 その次のサイクルにおいてアドレスを「 4 」増加させるためのカウントアップ信号を出力する ( c ) 。 同時に、 カウンタバッファ 1 4 8 が保持しているアドレスをバッファ 1 5 0 に、 また、 R O M 1 3 3 より読み出されたデータをバッファ 1 5 3 にロードするためのロード信号を出力する ( e ) 。

#### 【 0 1 3 6 】

図 3 3 において、 制御部 1 3 5 は、 外部の図示しないデコーダによるデコード信号の出力状態によって R O M 1 3 3 に対する読み出しサイクルが発生するまで待機している ( ステップ G 1 ) 。 そして、 前記読み出しサイクルが発生すると ( 「 Y E S 」 ) 、 その読み出しサイクルが「 命令読み出し 」であるか否かを判断する ( ステップ G 2 ) 。

#### 【 0 1 3 7 】

##### A . < 命令読み出し : アドレス連続 >

制御部 1 3 5 は、 C P U 1 3 2 が出力する制御信号におけるアクセスコード等を参照し、「 命令読み出し 」であると判断すると ( ステップ G 2 , 「 Y E S 」 ) 、 次に、 そのアドレスが命令用バッファ 1 5 3 にヒットしているか否かを判断する ( ステップ G 3 ) 。

前記アドレスに対応する命令が命令用バッファ 1 5 3 に格納されていればヒットであるから ( 「 Y E S 」 ) 、 制御部 1 3 5 は、 カウンタ 1 4 9 によって「 4 」が加算されたアドレスにより ( MUX 1 4 7 を介して ) バッファ 1 4 8 の値を更新させる ( ステップ G 4 ) 。 尚、 制御部 1 3 5 は、 ビット出力部 1 5 1 が「 1 」を出力している場合で、 且つ、 バッファ 1 5 0 に格納されているアドレスと C P U 1 3 2 側のアドレス A とが一致した場合に、 命令の内下位 1 6 ビットがヒットしていると判断する。

#### 【 0 1 3 8 】

それから、 MUX 1 4 2 を介して R O M 1 3 3 側のアドレスバスに前記アドレスを出力させ、 4 バイト分の命令読み出しを行う ( ステップ G 5 ) 。 続いて、 制御部 1 3 5 は、 データバス部 1 3 7 の命令用バッファ 1 5 3 にヒットしている命令を、 当該バッファ 1 5 3 より C P U 1 3 2 側のデータバスに出力させる。

#### 【 0 1 3 9 】

ここで、 図 3 4 を参照する。 上記のケースは、 例えば、 サイクル ( 3 ) に対応する。 即ち、 C P U 1 3 2 がアドレス ( A + 2 ) を出力すると、 そのアドレスに対応する命令 D 2 は、 R O M コントローラ 1 3 4 がその前のサイクル ( 1 ) , ( 2 ) で行った読み出しにおいて命令用バッファ 1 5 3 に格納されている。 従って、 この場合はバッファヒットとなり、 命令 D 2 はバッファ 1 5 3 より出力される。

それと同時に、 バッファヒットとなった場合は、 次回も命令が連続して ( A + 4 ) 読み出される蓋然性が高いので、 次回の命令読み出しに備えてアドレス ( A + 4 ) による命令読み出しを予め行なっておく。

#### 【 0 1 4 0 】

10

20

30

40

50

再び、図33を参照する。ステップG3において、バッファヒットとならなかった場合（「NO」）、制御部135は、その時のアドレスが、現在読み出しを行なっているアドレスに一致しているか否かを判断する（ステップG7）。そして、両者が一致している場合は（「YES」）、その時点で行われている読み出しが完了するまでのセットアップ時間が経過するまで待機し（ステップG8、「YES」）、読み出されたデータの下位側16ビットでバッファ153の内容を更新する（ステップG9）。また、読み出されたデータの上位側16ビットは、そのままCPU132側のデータバスに出力する（ステップG10）。

#### 【0141】

上記のケースは、例えば、図34のサイクル（4）に対応する。即ち、CPU132がアドレス（A+4）を出力すると、そのアドレスに対応する命令D4はバッファ153に格納されておらずバッファミスとなるが、アドレス（A+4）は、サイクル（3），（4）で行なっている読み出しのアドレス（先読みアドレス）と一致している。従って、制御部135は、サイクル（4）で読み出されたデータの上位側D4をCPU132側のデータバスに出力し、下位側D6はバッファ153に格納する。10

#### 【0142】

##### B. <命令読み出し:分岐>

また、ステップG7において、その時のアドレスが先読みアドレスに一致しなかった場合は（「NO」）、プログラムにおいて分岐命令が実行された場合である。この時、制御部135は、先読みアドレス（カウンタバッファ148）を更新すると共に（ステップG11）、MUX142をスルーパス143側に切替えることでROMアドレスを更新する（ステップG12）。そして、ステップG8～G10と同様の処理を行なう（ステップG13～G15）。20

#### 【0143】

##### C. <データ読み出し>

ステップG2において、制御部135が「NO」と判断してステップG16に移行するケースは、CPU132がROM133に対してデータ読み出しサイクルを行った場合である。CPU132がデータロードを行う場合、バイトアクセス、ワード（16ビット）アクセスの2つのケースがあるが、ROMコントローラ134は、何れであるかにかかわらず、読み出し対象データが属する32ビット分のデータをROM133より同時に読み出すようになっている。また、その場合の読み出しアドレスは、バッファ145に格納される。30

そして、その32ビットデータは常にデータ用バッファ154に格納されると共に、CPU132の読み出し対象データが属する上位、下位16ビットの何れかは、MUX152, 155を介してデータバスに出力される。

#### 【0144】

即ち、制御部135は、ステップG16において、読み出しアドレスがデータ用バッファ154にヒットしたか否かを、バッファ145に格納されたアドレスとビット出力部146のビットに基づいて判断する。そして、ヒットした場合は（「YES」）データ用バッファ154よりヒットした側の16ビットデータをMUX155により選択してCPU132側のデータバスに出力する（ステップG17）。また、ステップG16において、読み出しアドレスがデータ用バッファ154にヒットしなかった場合は（「NO」）、データについてステップG12～G15と同様の処理を行なう（ステップG18～G21）。40

#### 【0145】

以上のように第9実施例によれば、ROMコントローラ134の制御部135は、バッファ148に保持されたアドレスに対して、CPU132が命令読み出しサイクルで出力したアドレスが一致すると、バッファ148に保持されたアドレス値を増加させてその次のサイクルでROM133よりデータを読み出す。そして、命令用バッファ153は、制御部135が読み出したデータをCPU132のバス幅を超えて分だけ格納し、制御部135は、CPU132が次回に連続するアドレスでROM133に対する命令読み出しサイクルを実行すると、命令用バッファ153が保持しているデータをCPU132の50

データバスに出力するようにした。

**【0146】**

即ち、ROM133の読み出し速度が遅い場合でも、CPU132が連続するアドレス（CPU132のデータバス幅に応じた増分のアドレス）で命令読み出しを行う場合は、次回以降に読み出そうとする命令は今回の読み出しで同時に読み出されて命令用バッファ153に格納され、次の読み出しでは命令用バッファ153より命令が読み出される。従って、CPU132がROM133からの読み出しを行うために従来必要であったウエイトサイクルを削減することができ、処理効率を向上させることができる。

**【0147】**

また、CPU132がROM133に対するデータ読み出しサイクルを実行した場合は、読み出されたデータをデータ用バッファ154に格納し、制御部135は、CPU132が、次回にデータ読み出しサイクルを実行した場合にその読み出しあドレスがデータ用バッファ154にヒットすれば、バッファ154に格納されているデータをCPU132のデータバスに出力する。即ち、データ用バッファ154は所謂データキャッシュとして作用することになるので、CPUは、データの読み出し効率を向上させることができるとなる。

**【0148】**

<以下は参考>

Q. CPUと、このCPUよりも広いデータバス幅を構成する1つ以上のROMとの間に接続され、前記CPUが前記ROMよりデータを読み出そうとする場合に、その読み出しを制御するメモリインターフェイス回路装置であって、

アドレス値を保持する命令用アドレス保持手段と、

このアドレス保持手段に保持されたアドレスと、前記CPUが前記ROMに対する命令読み出しサイクルを実行するために出力したアドレスとを比較し、両者が一致した場合は、前記アドレス保持手段に保持されたアドレス値を、前記ROMのバス幅が前記CPUのバス幅を超えている分だけ増加させて、前記ROMよりデータを読み出すデータ読み出し手段と、

前記データ読み出し手段が読み出したデータを、前記ROMのバス幅が前記CPUのバス幅を超えている分だけ格納する命令用バッファと、

前記CPUが、次回に連続するアドレスで前記ROMに対する命令読み出しサイクルを実行すると、前記命令用バッファが保持しているデータを前記CPUのデータバスに出力させるように制御する読み出し制御手段とを備えることを特徴とするメモリインターフェイス回路装置。

**【0149】**

上記Qのメモリインターフェイス回路装置によれば、データ読み出し手段は、アドレス保持手段に保持されたアドレスと、CPUが命令読み出しサイクルで出力したアドレスとが一致すると、アドレス保持手段に保持されたアドレス値を増加させてROMよりデータを読み出す。そして、命令用バッファは、データ読み出し手段が読み出したデータをCPUのバス幅を超えている分だけバッファリングし、読み出し制御手段は、CPUが次回に連続するアドレスでROMに対する命令読み出しサイクルを実行すると、命令用バッファが保持しているデータをCPUのデータバスに出力する。

**【0150】**

即ち、ROMの読み出し速度が遅い場合でも、CPUが連続するアドレスで命令読み出しを行う場合は、CPUが次回以降に読み出そうとする命令は今回の読み出しで同時に読み出されて命令用バッファに保持され、次の読み出しでは命令用バッファより命令が読み出される。従って、CPUがROMからの読み出しを行うために従来必要であったウエイトサイクルを削減することができ、処理効率を向上させることができる。

**【0151】**

R. 前記CPUが前記ROMに対するデータ読み出しサイクルを実行した場合に、前記データ読み出し手段が前記ROMより読み出したデータを、前記ROMのバス幅が前記CPUのバス幅を超えている分だけ格納するデータ用バッファと、

10

20

30

40

50

前記アドレスを格納するためのアドレス格納手段とを備え、

前記読み出し制御手段は、前記アドレス格納手段に格納されているアドレスに基づいて、

前記CPUが次回に前記ROMに対するデータ読み出しサイクルを実行した場合に、その

読み出しあдресに対応するデータが前記データ用バッファに格納されていると判断する

と、前記データを前記CPUのデータバスに出力させるように制御することを特徴とする

上記Qのメモリインターフェイス回路装置。

#### 【0152】

上記Rのメモリインターフェイス回路装置によれば、CPUがデータ読み出しサイクル

を実行した場合にROMより読み出されたデータを、ROMのバス幅がCPUのバス幅を

超えている分だけデータ用バッファに格納する。また、この時、前記読み出しあдресはア

ドレス格納手段に格納される。そして、読み出し制御手段は、CPUが次回にデータ読み出

しサイクルを実行した場合に、その読み出しあdressに対応するデータがデータ用バッ

ファに格納されていると判断すると、そのデータをCPUのデータバスに出力させる。

10

即ち、データ用バッファは所謂データキャッシュとして作用するので、データの読み出

しアドレスがデータ用バッファにヒットした場合、CPUはそのデータを高速に読み出すこ

とができる。従って、データの読み出し効率を向上させることが可能となる。

#### 【0153】

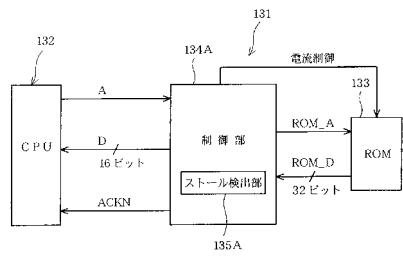

##### (第10実施例)

図35及び図36は本発明の第10実施例を示すものであり、第9実施例と異なる部分

についてのみ説明する。図35に示すように、第10実施例では、ROMコントローラ1

34Aの制御部135Aは、CPU132がストール状態となったことを検出する機能を

有しており、その場合に、ROM133の電流を遮断する制御を行うように構成されてい

る。

20

#### 【0154】

図36に示すタイミングチャートにおいて、制御部135Aは、CPU132の動作に

ストールが発生したことを、例えばアドレス値(A+4)が2サイクル続けて同じ値である

ことによってサイクル(5)のタイミングで検出する。

その後、CPU132のストール状態が例えば更に2サイクル継続すると、制御部13

5Aは、ROM133の消費電流をカットするように制御する。尚、ここで言う「ストー

ル」とは、一般的な意味におけるCPU132内部の演算処理の停止に加えて、ROM1

33に対するアクセスが行われない状態(例えば、RAMやI/O等の他のリソースに対

してアクセスを行っている場合)も含むものとする。その場合は、外部のデコーダのデコ

ード信号によってROM133がセレクトされなくなることで判定できる。例えば、図3

3のステップG1において、「NO」と判断している期間を計測して判定することが可能

である。

30

#### 【0155】

以上のように第10実施例によれば、ROMコントローラ134Aの制御部135Aは

、CPU132がストール状態となったことを検出するとROM133からのデータ読み

出しを停止させる。そして、CPU132のストール状態が所定期間継続すると、ROM

133における消費電流を遮断するようにした。従って、無駄な電力消費を低減するこ

とができる。

40

#### 【0156】

##### <以下は参考>

S. 前記読み出し制御手段は、前記CPUの動作にストールが発生したことを検出可能に

構成され、

前記データ読み出し手段は、前記ストールが発生したことが検出された場合に、前記R

OMに対するデータの読み出しが実行中である場合は、その読み出し処理を継続して完了

させることを特徴とする上記Q, R, 下記Uの何れかのメモリインターフェイス回路装置

。

上記Sのメモリインターフェイス回路装置によれば、データ読み出し手段は、CPUの

50

動作にストールが発生したことが検出された場合でも、ROMに対するデータの読み出しが実行中である場合は、その読み出し処理を継続して完了させる。即ち、ストールが発生した時点で直ちに読み出しを中止する事がないので、読み出し効率を向上させることができる。

#### 【0157】

T. 前記読み出し制御手段は、前記CPUの動作にストールが発生したことを検出し、そのストール状態が所定期間継続すると、前記ROMにおける消費電流を遮断するように制御することを特徴とする上記Q, R, 下記Uの何れかのメモリインターフェイス回路装置。

上記Tのメモリインターフェイス回路装置によれば、読み出し制御手段は、CPUのストール状態が所定期間継続すると、ROMにおける消費電流を遮断するように制御するので、無駄な電力消費を低減することができる。 10

#### 【0158】

本発明は上記し且つ図面に記載した実施例にのみ限定されるものではなく、以下のような変形または拡張が可能である。

第1実施例において1/N分周器19, 20は必要に応じて設ければ良い。

第2実施例において、メインクロック監視部7は削除しても良い。

また、第2実施例においてステップA0, A4は削除して実施しても良い。

また、第2実施例において、高速補正動作は、必ずしもバイナリサーチ方式で行なうものに限らず、比較的大なる調整信号データから開始して、その絶対値が次第に小さくなるようにして行けば良い。 20

第5実施例において、発振回路装置の発振動作を停止させる場合は、低消費電力モードの実行に伴うものに限ることはない。即ち、発振回路装置が出力するクロック信号は、CPUの動作用クロック信号として供給されるものに限らず、どのような用途であっても良い。従って、その用途に応じてクロック信号の出力を一時的に停止させた後、出力を再開させる必要があるものであれば、広く適用が可能である。

#### 【0159】

第7実施例において、出力タイミングレジスタ113に設定されるデータは、ハードウェア的に固定されているように構成しても良い。

第8実施例において、レベル変化用タイマを解除タイマと共にすれば、より簡単に構成することができる。 30

また、第8実施例において、割り込み発生用のタイマを、レベル変化用タイマと独立に備えても良い。

また、マイコン101に、CPU102の動作を監視するためのウォッチドッグタイマ、若しくは、CPU102の動作用クロックとは独立にカウント動作するフリーランタイマなどを備えている場合、レベル変化用タイマを、それら他のタイマと共にすることで、構成をより簡単にすることができる。但し、この場合、レベル変化用タイマとして使用する場合は、そのタイマ動作の開始時点におけるウォッチドッグタイマ等のカウント値を読み出し、出力タイミングに相当するカウント値を加算したものを出力タイミングレジスタに設定する。そして、タイマを共通にすることで、ソフトウェアの作成管理が容易となり、バグが発生する可能性を低下させることができる。 40

#### 【0160】

第9実施例において、メモリインターフェイス回路装置が内蔵するバッファのバス幅を、ROMのデータバス幅よりも広くするように構成しても良い。斯様に構成すれば、データ読み出し手段がROMに対する読み出しを複数回行なって、前記バッファにデータを格納することでより多くのデータについてその先読みを行なうことができる。

第9または第10実施例において、ROMを、16ビットバス構成のマットを2個並べて同様に実施しても良い。また、その場合、ROMコントローラ134による読み出し対象となっていないマットのROMについては消費電流を遮断するように構成しても良い。斯様に構成しても、ROMが複数マットで構成されている場合に、無駄な電力消費を低減す 50

ることができる。

#### 【0161】

更に、第10実施例において、CPU132がスリープ／ストップなどの低消費電力モードに移行した場合は、ROMの全ての消費電流を遮断するように構成しても良い。斯様に構成すれば、無駄な電力消費を低減することができる。

また、第10実施例において、ROMコントローラ134Aを、CPU132のストール検出タイミングが例えばサイクル(4)でアドレス(A+2)が継続した場合に、その時点でROM133に対して実行中である命令のデータD2, D4の読み出しがその他の条件により続行可能であれば、続行して完了させるようにする。斯様に構成すれば、ROMコントローラ134Aは、ストール状態を検出しても直ちにROM133に対する読み出しを停止することができないので、読み出し効率を向上させることができる。10

#### 【0162】

<以下は参考>

U. 前記バッファのバス幅は、前記ROMのデータバス幅よりも広く構成されていることを特徴とする請求項30または31記載のメモリインターフェイス回路装置。

上記Uのメモリインターフェイス回路装置によれば、バッファのバス幅を、ROMのデータバス幅よりも広くするので、データ読み出し手段が読み出しを複数回行なって、前記バッファにデータを格納すれば、より多くのデータについてその先読みを行なうことができる。

#### 【0163】

V. 前記ROMが、複数マットで構成されている場合、

前記読み出し制御手段は、前記データ読み出し手段による読み出し対象となっているROM以外の消費電流を遮断するように制御することを特徴とする請求項34記載のメモリインターフェイス回路装置。

上記Vのメモリインターフェイス回路装置によれば、読み出し制御手段は、データ読み出し手段による読み出し対象となっているROM以外の消費電流を遮断するので、ROMが複数マットで構成されている場合に、無駄な電力消費を低減することができる。

#### 【0164】

W. 前記読み出し制御手段は、前記CPUが、内部状態を保持したまま動作を一時的に停止する低消費電力モードに移行した場合は、前記ROMの全ての消費電流を遮断するように制御することを特徴とする上記S又はTのメモリインターフェイス回路装置。30

上記Wのメモリインターフェイス回路装置によれば、読み出し制御手段は、CPUが低消費電力モードに移行した場合は、ROMの全ての消費電流を遮断するので、無駄な電力消費を低減することができる。

#### 【図面の簡単な説明】

#### 【0165】

【図1】本発明をマイクロコンピュータに適用した場合の第1実施例であり、マイクロコンピュータの電気的構成を示す機能ブロック図

【図2】サブクロック補正部を中心とする詳細な構成を示す図

【図3】サブクロック補正部による補正処理を示すフロー・チャート40

【図4】メインクロック監視部の詳細な構成を示す

【図5】本発明の第2実施例を示す図3相当図

【図6】ステップS12における処理内容を示すフロー・チャート

【図7】ステップS13における処理内容を示すフロー・チャート

【図8】高速補正動作が行なわれる状態の概念的な説明図

【図9】本発明の第3実施例であり、マイクロコンピュータの構成を示す機能ブロック図

【図10】低消費電力制御部が、スリープモードについて制御を行う機能部分の構成を示す図

【図11】低消費電力制御部が、ストップモードが設定された場合にI/O端子部の制御を行う機能部分の構成を示す図50

- 【図12】C P Uが低消費電力モードに移行する場合の処理を示すフローチャート

【図13】低消費電力モードが解除されて、C P Uが起動（ウェイクアップ）する場合の処理を示すフローチャート

【図14】本発明の第4実施例であり、マイクロコンピュータのクロック制御に関する機能部分を示すブロック図

【図15】電源投入時や、スリープ／ストップモードからC P Uが起動したウェイクアップ時ににおけるクロック信号の遷移状態を示す図

【図16】C P Uが通常の動作を行なっている状態において、ユーザプログラムによりマシンクロックの切替えを行なう場合のダイヤグラム

【図17】C P Uが、図16に示すダイヤグラムに基づいてマシンクロック信号の切替えを行なう場合の処理を示すフローチャート

10

【図18】本発明の第5実施例であり、E C Uの電気的構成を示す機能ブロック図

【図19】周波数倍回路の概略構成を示す機能ブロック図

【図20】D C Oの詳細な構成を示す機能ブロック図

【図21】リングオシレータの構成を示す図

【図22】カウンタ・データラッチ回路の内部構成の一部を示す図

【図23】周波数倍回路が低消費電力モードにある状態から、起動して発振動作を行なう場合を示すタイミングチャート

【図24】本発明の第6実施例を示すC P Uのフローチャート

20

【図25】本発明の第7実施例であり、シングルチップマイクロコンピュータの一構成例を示す図

【図26】ポート制御回路の内部構成を示す機能ブロック図

【図27】C P Uによるスリープモード移行処理の内容を示すフローチャート

【図28】スリープモード移行中のタイミングチャート

【図29】本発明の第8実施例を示す図26相当図

【図30】図28相当図

【図31】本発明の第9実施例であり、マイクロコンピュータの構成を示す図

【図32】R O Mコントローラの内部構成を示すブロック図

【図33】C P UがR O Mに対する読み出しサイクルを実行する場合におけるR O Mコントローラの制御内容を示すフローチャート

30

【図34】C P Uが命令読み出しサイクルを連続的に実行した場合のタイミングチャート

【図35】本発明の第10実施例を示す図31相当図

【図36】図33相当図

【図37】従来技術を示す図28相当図

【符号の説明】

【0166】

1はマイクロコンピュータ、2はC P U、3はメインクロック発振部（発振回路）、4はサブクロック発振部（C R発振回路）、5はウォッチドッグタイマ、6はサブクロック補正部（補正回路）、7はメインクロック監視部（監視回路）、8はエッジ検出回路8、9はパルスカウンタ、10カウント数設定レジスタ、11は比較調整手段、13はラダー抵抗（可変抵抗器）、21はクロック制御回路装置、31はマイクロコンピュータ、32はC P U、35は低消費電力制御部（端子制御手段）、42は入出力端子（外部信号端子）、51はマイクロコンピュータ、52はC P U、54は外部発振子、55はD P L L回路（周波数倍回路）、56はクロック制御部（切替通知制御部）、62はステートカウンタ（シーケンス制御手段）、71はE C U（マイクロコンピュータ）、71aはクロック制御回路（発振回路装置）、76は発振回路、77は周波数倍回路、78は低消費電力制御回路（低消費電力制御手段）、80は制御回路（シーケンス制御手段）、81はD C O、83はリングオシレータ（多相クロック信号出力手段）、95は周波数情報保持回路部（データ保持手段）、101はシングルチップマイクロコンピュータ、102はC P U、106はポート制御回路（信号レベル変化手段）、110は出力端子（外部信号出力手段）

40

端子)、111はタイマ(レベル変化用タイマ)、112は比較器(比較回路)、113は出力タイミングレジスタ、117はポート制御回路、121は割り込み発生手段、131はマイクロコンピュータ、132はCPU、133はROM、134, 134AはROMコントローラ(メモリインターフェイス回路装置)、135, 135Aは制御部(データ読み出し手段、読み出し制御手段)、137はデータバス部(読み出し制御手段)、145はバッファ(アドレス格納手段)、148はカウンタバッファ(アドレス保持手段)、153は命令用バッファ、154はデータ用バッファを示す。

【図1】

4 : CR発振回路

7 : 監視回路

21 : クロック制御回路装置

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 10】

【図 9】

【図 11】

35 : 端子制御手段

【図 12】

【図 14】

55 : 周波数検出回路

62 : シーケンス制御手段

【図 13】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【 図 2 1 】

【 図 2 2 】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図3-2】

【図34】

【図35】

【図36】

【図37】

---

フロントページの続き

(72)発明者 野田 真一

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 鶴田 前

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 藤井 裕志

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 石原 秀昭

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

審査官 小林 正明

(56)参考文献 特開2002-202830(JP,A)

特開平05-073349(JP,A)

特開平01-137355(JP,A)

特開平09-006750(JP,A)

特開2002-063150(JP,A)

特開平11-095864(JP,A)

特開平09-034867(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 1 / 04

G 06 F 15 / 78