(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6635653号

(P6635653)

(45) 発行日 令和2年1月29日(2020.1.29)

(24) 登録日 令和1年12月27日(2019.12.27)

(51) Int.Cl.

H04L 1/22 (2006.01)

F 1

H04L 1/22

|                    |                               | 請求項の数 18 (全 20 頁) |                                                                                    |

|--------------------|-------------------------------|-------------------|------------------------------------------------------------------------------------|

| (21) 出願番号          | 特願2014-261431 (P2014-261431)  | (73) 特許権者         | 390041542<br>ゼネラル・エレクトリック・カンパニイ<br>アメリカ合衆国、ニューヨーク州 123<br>45、スケネクタディ、リバーロード、1<br>番 |

| (22) 出願日           | 平成26年12月25日(2014.12.25)       | (74) 代理人          | 100105588<br>弁理士 小倉 博                                                              |

| (65) 公開番号          | 特開2015-130668 (P2015-130668A) | (74) 代理人          | 100129779<br>弁理士 黒川 俊久                                                             |

| (43) 公開日           | 平成27年7月16日(2015.7.16)         | (72) 発明者          | リチャード・ジョセフ・グローサー、ジュ<br>ニア<br>アメリカ合衆国、ヴァージニア州、セイラ<br>ム、ロアノーク・ブルヴァード、150<br>1番       |

| 審査請求日              | 平成29年12月12日(2017.12.12)       |                   |                                                                                    |

| (31) 優先権主張番号       | 14/145,636                    |                   |                                                                                    |

| (32) 優先日           | 平成25年12月31日(2013.12.31)       |                   |                                                                                    |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |                   |                                                                                    |

| 前置審査               |                               | 最終頁に続く            |                                                                                    |

(54) 【発明の名称】送信システムエラー検出および訂正のシステムおよび方法

## (57) 【特許請求の範囲】

## 【請求項 1】

データ送信サブシステムを備え、1以上の装置に通信接続するように構成された工業用制御システムであって、

前記データ送信サブシステムが、

プログラマブルロジックデバイスを備え、前記プログラマブルロジックデバイスが、

第1のシリアルリンクに通信可能に結合されるように構成された第1のシリアルポートであって、第1の複数のビットを含む第1の送信信号を前記第1のシリアルリンクから受信するように構成された第1のシリアルポートと、

第2のシリアルリンクに通信可能に結合されるように構成された第2のシリアルポートであって、前記第2のシリアルポートが第2の複数のビットを含む第2の送信信号を前記第2のシリアルリンクから受信するように構成され、前記第1のシリアルリンクおよび前記第2のシリアルリンクが互いに並行に配置され、前記第1の複数のビットおよび前記第2の複数のビットが同一の情報を表す、第2のシリアルポートと、

回路と、

を備え、

前記回路が、

前記第1の複数のビットと前記第2の複数のビットを比較する、第1の比較を実行し、

前記第1の比較に少なくとも部分的に基づいて、前記第1の送信信号にエラーが存在

10

20

するか否かを決定し、存在する場合にはそのエラーのタイプ及び、そのエラーが前記第2の複数のビットを使用してリアルタイムで訂正できるか否かを決定し、

前記エラーのタイプに少なくとも部分的に基づいて、前記第1の複数のビットを前記第2の複数のビットを使用して調整することにより、リアルタイムで前記エラーを訂正して、前記工業用制御システムが、前記第1の複数のビットに少なくとも部分的に基づいて、前記1以上の装置の動作を制御するように構成される、工業用制御システム。

#### 【請求項2】

前記回路が、前記第1の送信信号内のビットを前記第2の送信信号からのビットで置き換えること、または前記第1の送信信号、前記第2の送信信号もしくはその両方を無視することによって、リアルタイムで前記エラーを訂正するように構成された、請求項1記載の工業用制御システム。 10

#### 【請求項3】

前記回路が、前記エラーが訂正可能かどうかをエラータイプおよびエラーの大きさに少なくとも部分的に基づいて判定し、前記第1の送信信号と前記第2の送信信号の前記比較および前記エラータイプに少なくとも部分的に基づいてリアルタイムで前記エラーを訂正するように構成された、請求項1または2に記載の工業用制御システム。

#### 【請求項4】

前記第2の複数のビットは、前記第1の複数のビットが逆転されたものであり、前記回路が、エラー訂正に際し、前記第1の複数のビットの最上位ビットを前記第2の複数のビットの最下位ビットで置き換える、請求項1乃至3のいずれかに記載の工業用制御システム。 20

#### 【請求項5】

前記回路が、フィールドプログラマブルゲートアレイ、プログラマブルアレイロジック、プログラマブルロジックアレイ、汎用アレイロジック、特定用途向け集積回路、またはそれらの任意の組合せを備える、請求項1乃至4のいずれかに記載の工業用制御システム。

#### 【請求項6】

前記第1の送信信号にエラーが存在するか否かの決定が、

前記回路を、

前記第1の送信信号と前記第2の送信信号の間でビット単位の一致を検査すること、

前記第1の送信信号もしくは前記第2の送信信号でコード化された順序番号を判定すること。 30

前記第1の送信信号もしくは前記第2の送信信号でコード化されたタイミングデータを判定すること、

前記第1の送信信号もしくは前記第2の送信信号でコード化された送信者IDを判定すること、

前記第1の送信信号もしくは前記第2の送信信号でエラー検査技法を実行し、前記エラー検査技法の結果を判定すること、または、

それらの任意の組合せを行なうように構成することを含む、請求項1乃至5のいずれかに記載の工業用制御システム。

#### 【請求項7】

工業用制御システムに通信接続する1以上の装置を制御する方法であって、

前記工業用制御システムの第1のプログラマブルロジックデバイスを使用して、第1のシリアルリンクを介して第2のプログラマブルロジックデバイスから第1の複数のビットを含む第1の送信信号を受信するステップと、

前記第1のプログラマブルロジックデバイスを使用して、前記第2のプログラマブルロジックデバイスから第2のシリアルリンクを介して第2の複数のビットを含む第2の送信信号を受信するステップであって、前記第1のシリアルリンクおよび前記第2のシリアルリンクが互いに並行に配置され、前記第1の複数のビットおよび前記第2の複数のビットが同一の情報を表す、ステップと、

前記第1のプログラマブルロジックデバイスを使用して、前記第1の複数のビットと前 50

記第2の複数のビットを比較する、第1の比較を実行するステップと、

前記第1のプログラマブルロジックデバイスを使用して、前記第1の比較に少なくとも部分的に基づいて、前記第1の送信信号にエラーが存在するか否かを決定し、存在する場合にはそのエラーのタイプ及び、そのエラーが前記第2の複数のビットを使用してリアルタイムで訂正できるか否か決定するステップと、

前記第1のプログラマブルロジックデバイスを使用して、前記エラーのタイプに少なくとも部分的に基づいて、前記第1の複数のビットを前記第2の複数のビットを使用して調整することにより、リアルタイムで前記エラーを訂正して、前記工業用制御システムが、前記第1の複数のビットに少なくとも部分的に基づいて、前記1以上の装置の動作を制御するステップと

を含む、方法。

**【請求項8】**

前記第1の送信信号と前記第2の送信信号を比較するステップが、エラーのタイプおよびエラーの大きさに少なくとも部分的に基づいて前記エラーが訂正可能かどうかを判定するステップを含み、リアルタイムで前記エラーを訂正するステップが、前記比較および前記エラータイプに少なくとも部分的に基づく、請求項7記載の方法。

**【請求項9】**

前記第2の複数のビットは、前記第1の複数のビットが逆転されたものであり、前記第1のプログラマブルロジックデバイスが、エラー訂正に際し、前記第1の複数のビットの最上位ビットを前記第2の複数のビットの最下位ビットで置き換えるステップを含む、請求項7または8に記載の方法。

**【請求項10】**

前記第1の送信信号と前記第2の送信信号を比較するステップが、前記第1の送信信号と前記第2の送信信号の間でビット単位の一致を検査するステップを含む、請求項7乃至9のいずれかに記載の方法。

**【請求項11】**

リアルタイムで前記エラーを訂正するステップが、前記第1の送信信号内のビットを前記第2の送信信号からのビットで置き換えるステップ、または前記第1の送信信号、前記第2の送信信号、もしくはその両方を無視するステップを含む、請求項7乃至10のいずれかに記載の方法。

**【請求項12】**

リアルタイムで訂正できるか否か決定する前記ステップが、

前記第1の送信信号または前記第2の送信信号でコード化されたタイミングデータを判定するステップを含む、請求項7乃至11のいずれかに記載の方法。

**【請求項13】**

リアルタイムで訂正できるか否か決定する前記ステップが、

前記第1の送信信号または前記第2の送信信号でコード化された順序番号を判定するステップを含む、請求項7乃至12のいずれかに記載の方法。

**【請求項14】**

リアルタイムで訂正できるか否か決定する前記ステップが、

前記第1の送信信号または前記第2の送信信号でコード化された送信者IDを判定するステップを含む、請求項7乃至13のいずれかに記載の方法。

**【請求項15】**

リアルタイムで訂正できるか否か決定する前記ステップが、

前記第1の送信信号または前記第2の送信信号でエラー検査技法を実行するステップと、

前記エラー検査技法の結果を判定するステップと

を含む、請求項7乃至14のいずれかに記載の方法。

**【請求項16】**

前記エラー検査技法が、巡回冗長検査を含む、請求項15に記載の方法。

**【請求項17】**

10

20

30

40

50

前記第1の送信信号と前記第2の送信信号を比較するステップが、ソフトウェア監視なしに前記第1のプログラマブルロジックデバイス内のハードウェアのみを使用して実行される、請求項7乃至16のいずれかに記載の方法。

【請求項18】

前記1以上の装置が、タービン、発電機、コンプレッサ、コンバスタ、センサ、ポンプのいずれかである野外装置である、請求項1乃至6のいずれかに記載の工業用制御システム。

【発明の詳細な説明】

【技術分野】

【0001】

10

本明細書で開示される主題は、送信システムに関し、より具体的には、データ送信システムのためのハードウェアシリアルリンク故障検出システムに関する。

【背景技術】

【0002】

一般に、データ送信システムは、ある入力／出力(I/O)デバイスから別のI/Oデバイスにデータを転送するために使用され得る。たとえば、送信システムは、タービン、発電機、コンプレッサ、コンバスタなどの様々なデバイスとインターフェースをとり、制御する様々な工業用コントローラの間の通信を円滑化するために、工業用制御システムで使用され得る。より具体的には、送信システムは、コントローラが制御コマンドなどのデータを互いに通信することを可能にすることができる。たとえば、第1のコントローラは、第2のコントローラに制御コマンドを送信して送信システムを介してタービンの稼働を開始することができる。したがって、送信システムの信頼性を向上させることは有益であることになる。

20

【先行技術文献】

【特許文献】

【0003】

【特許文献1】米国特許第7642748号公報

【発明の概要】

【課題を解決するための手段】

【0004】

30

出願時に特許請求された発明の範囲に準じたある種の実施形態が、以下に要約される。これらの実施形態は、特許請求されている発明の範囲を限定するものではなく、そうではなくて、これらの実施形態は、本発明の起り得る形の簡潔な概要を提供することのみを意図されている。実際、本発明は、以下に記載の実施形態と同様のまたはそれらとは異なり得る様々な形を包含し得る。

【0005】

第1の実施形態は、第2のプログラマブルロジックデバイスから第1のシリアルリンクを介して第1のプログラマブルロジックデバイスで第1の通信信号を受信するステップと、第2のプログラマブルロジックデバイスから第2のシリアルリンクを介して第1のプログラマブルロジックデバイスで第2の信号を受信するステップとを含むデータ送信システムでのリアルタイムエラー訂正のための方法であって、第1のシリアルリンクおよび第2のシリアルリンクが互いに並行に配置され、単一のルートを介して通信するように構成され、第1の通信信号および第2の通信信号が同一の情報を表す、方法が説明される。本方法は、第1のプログラマブルロジックデバイスにおいて第1の通信信号と第2の通信信号を比較して第1の通信信号、第2の通信信号、またはその両方でデータ内のエラーを検出するステップと、エラーが検出されたときに、第1の通信信号と第2の通信信号の比較に少なくとも部分的に基づいて第1のプログラマブルロジックデバイスでリアルタイムでエラーを訂正するステップとをさらに含む。

40

【0006】

第2の実施形態は、プログラマブルロジックデバイスを含むデータ送信システムを説明

50

する。そのプログラマブルロジックデバイスは、第1のシリアルポートが第1のシリアルリンクから第1の送信信号を受信する、第1のシリアルリンクに通信可能に結合された第1のシリアルポートと、第2のシリアルポートが第2のシリアルリンクから第2の送信信号を受信する、第2のシリアルリンクに通信可能に結合された第2のシリアルポートとを含む。第1のシリアルリンクおよび第2のシリアルリンクは、互いに並行に配置され、单一のルートを介して通信し、第1の通信信号および第2の通信信号は同一の情報を表す。そのプログラマブルロジックデバイスは、第1の通信信号と第2の通信信号を比較して第1の通信信号、第2の通信信号、またはその両方に含まれるデータ内のエラーを検出するために、エラーが検出されたときに、第1の通信信号と第2の通信信号の比較に少なくとも部分的に基づいてリアルタイムでエラーを訂正するために、回路を含む。

10

#### 【0007】

第3の実施形態は、送信された第1の通信信号と第2の通信信号を比較することによってプログラマブルロジックデバイスで第1の通信信号、第2の通信信号、またはその両方ににおいて表されたデータ内のエラーを検出するステップを含む、データ送信システムを動作させるための方法を説明し、第1の通信信号および第2の通信信号はプログラマブルロジックデバイスによって並行して受信され、第1の通信信号および第2の通信信号は同一の情報を表し、エラーの検出はそのプログラマブルロジックデバイス内のハードウェア検出のみを含む。本方法は、エラーが検出された場合に、そのエラーのタイプを判定するステップと、エラーのタイプ、第1の通信信号、第2の通信信号、またはそれらの任意の組合せに少なくとも部分的に基づいて、プログラマブルロジックデバイスでエラーを訂正するステップとをさらに含む。

20

#### 【0008】

本発明のこれらのおよび他の特徴、態様、および利点は、以下のような、同様の文字が図面を通して同様の部分を表す、添付の図面を参照して、以下の詳細な説明が読まれるときに、よりよく理解されよう。

#### 【図面の簡単な説明】

#### 【0009】

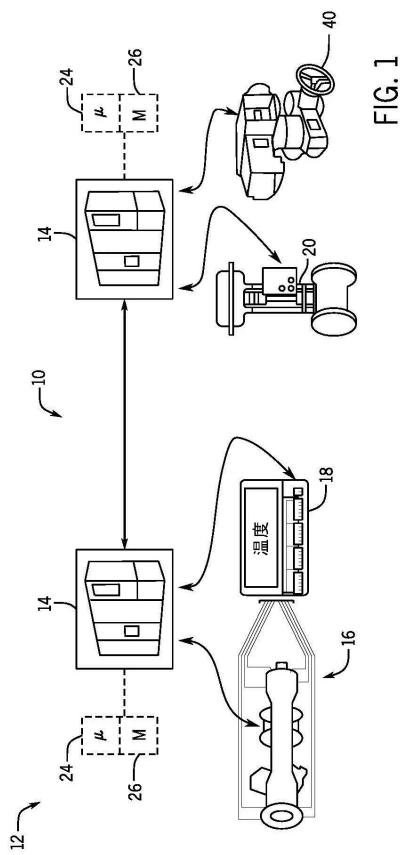

【図1】一実施形態による、データ送信システムの概略図である。

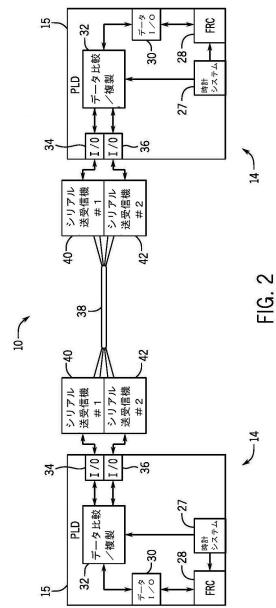

【図2】一実施形態による、図1に示すデータ送信システム内のコントローラのブロック図である。

30

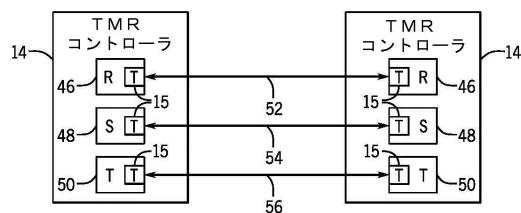

【図3】一実施形態による、三重モジュール式冗長コントローラのブロック図である。

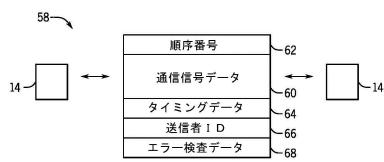

【図4】一実施形態による、通信信号のブロック図である。

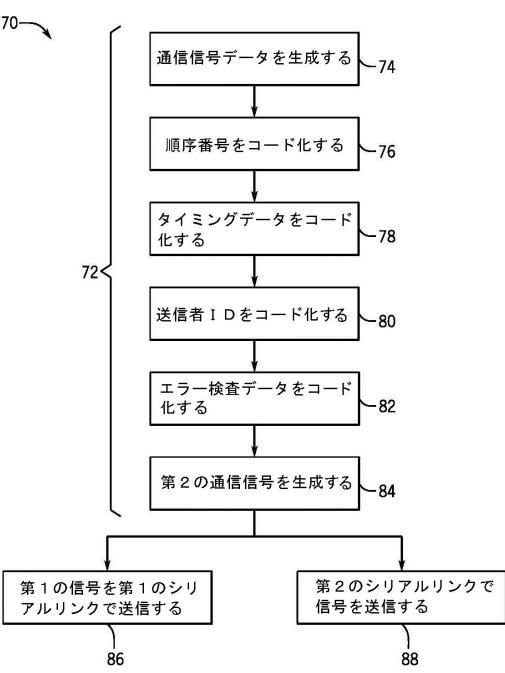

【図5】一実施形態による、通信信号をデータ送信システムに送信するためのプロセスを示す流れ図である。

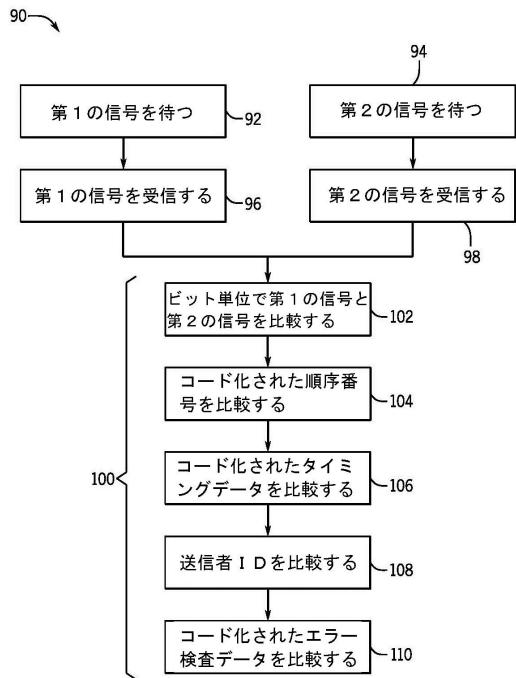

【図6】一実施形態による、通信信号をデータ送信システムから受信するためのプロセスを示す流れ図である。

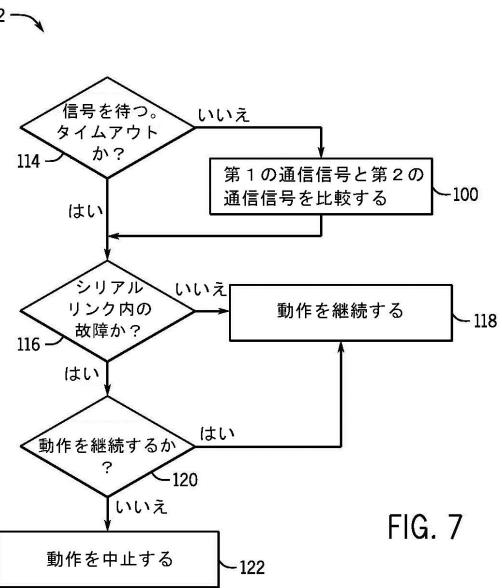

【図7】一実施形態による、シリアルリンクにおいて故障を検出するためのプロセスを示す流れ図である。

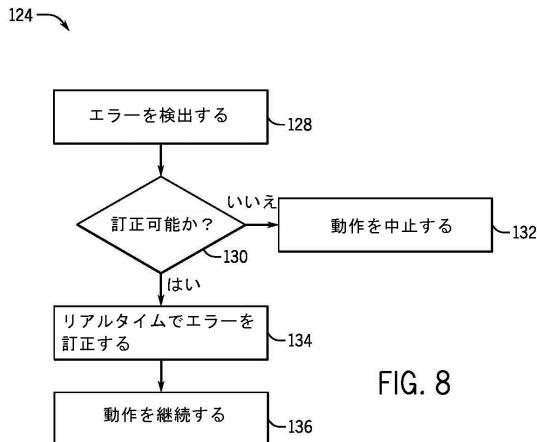

【図8】一実施形態による、受信された通信信号内のエラーを検出および訂正するためのプロセスを示す流れ図である。

40

#### 【発明を実施するための形態】

#### 【0010】

本発明の1つまたは複数の特定の実施形態が、以下に説明される。これらの実施形態の簡潔な説明を提供することを目的として、実際の実装形態のすべての特徴は本明細書には記載されないことがある。任意のそのような実際の実装形態の開発では、いずれの工学または設計プロジェクトでもそうであるように、多数の実装形態特有の決定が、実装形態によって変わり得るシステム関連およびビジネス関連の制約の順守などの開発者の特有の目的を達成するために行われるべきあることを理解されたい。さらに、そのような開発の努力は、複雑で、時間を要することがあるが、それでもなお、本開示の利益を有する当業者の設計、製作、および製造の通常業務となろうことを理解されたい。

50

**【 0 0 1 1 】**

本発明の様々な実施形態の要素を紹介するとき、「1つの（a、an）」、「その（the）」および「前記（said）」という冠詞は、1つまたは複数のその要素が存在することを意味するものである。「備える」、「含む」、および「有する」という用語は、包括的であり、挙げられた要素以外の追加の要素が存在し得ることを意味するものである。

**【 0 0 1 2 】**

データ送信システムは、しばしば、工業用制御システムおよび自動化システムなどのシステム内で使用されてそのシステム内の様々な入力／出力（I／O）デバイス間の通信を円滑化する。たとえば、データ送信システムは、様々なコントローラが互いにデータを通信することを可能にすることができる。一般に、コントローラは、タービン、発電機、コンプレッサ、コンバスタ、センサ、ポンプ、バルブ、他の野外装置などの様々なデバイスとインターフェースをとり、制御する。したがって、コントローラによって通信されるデータは、制御されたデバイスによって集められたデータ、制御コマンド、デバイス状況などを含み得る。データ送信システムを使用し得るシステムの特質により、そのようなデータ送信システムの信頼性を向上させることは有益となろう。10

**【 0 0 1 3 】**

データ送信システムの信頼性を向上させるための1つの技法は、プロセス制御のためのオブジェクトのリンクと埋め込み（Object Linking and Embedding for Process Control、OPC）、モdbus（Modbus）、ファウンデーションフィールドバス、プロセスフィールドバス、および／またはBACnetなどの様々な通信プロトコルの使用を含み得る。一般に、これらの通信プロトコルは、何らかのソフトウェア監視および処理を使用し得る。たとえば、ファウンデーションフィールドバスを使用するとき、ある一定のレベルの処理が、データを送信および受信するための機能ブロックを実行するために使用され得る。しかし、いくつかのI／Oデバイスは、そのようなプロトコルのための所望の処理能力を含まないことがあるので、本開示は処理能力にかかわらずI／Oデバイスのための送信システムの信頼性を向上させるための実施形態を含む。したがって、本明細書に記載の技法は、安全システム適用例を含む、様々な適用例における通信のための低レベルのシリアルリンクを実現する。低レベルのシリアルリンクは、より少ない処理および資源（たとえば、ソフトウェアおよびハードウェア資源）を使用し、その上で、SIL1、2、3、および／または4を含む所望の安全完全性レベル（SIL）証明を満たすために適切な動作を提供することができる。ある種の実施形態において、低レベルのシリアルリンクは、ハードウェア故障検出方式を適用して、処理および他の資源の使用を低減するのに適した所望の安全証明を実現することができる。20

**【 0 0 1 4 】**

したがって、第1の実施形態は、プログラマブルロジックデバイスを含むフォールトレアント送信システムを示す。そのプログラマブルロジックデバイスは、第1のシリアルポートが第1のシリアルリンクから第1の送信信号を受信する、第1のシリアルリンクに通信可能に結合された第1のシリアルポートと、第2のシリアルポートが第2のシリアルリンクから第2の送信信号を受信する、第2のシリアルリンクに通信可能に結合された第2のシリアルポートとを含む。第1のシリアルリンクおよび第2のシリアルリンクは、互いに並行に配置され、第1の単一のルートを介して通信し、第1の通信信号および第2の通信信号は同一の情報を表す。そのプログラマブルロジックデバイスは、第1の通信信号と第2の通信信号を比較することによって第1のシリアルリンク、第2のシリアルリンク、またはその両方で故障を検出し、故障が検出された場合には、送信システムがその故障にかかわらず動作を継続することができるかどうかを判定する、回路をさらに含む。言い換えれば、同情報を表すパラレル通信信号の受信は、様々なデバイス間の通信リンク（たとえば、シリアルリンク）における故障の検出を可能にする。さらに、本送信システムは、検出された故障に知的に反応することによって、よりフォールトレアントであり得る304050

。

#### 【0015】

したがって、第2の実施形態は、プログラマブルロジックデバイスを含むデータ送信システムを示す。そのプログラマブルロジックデバイスは、第1のシリアルポートが第1のシリアルリンクから第1の送信信号を受信する、第1のシリアルリンクに通信可能に結合された第1のシリアルポートと、第2のシリアルポートが第2のシリアルリンクから第2の送信信号を受信する、第2のシリアルリンクに通信可能に結合された第2のシリアルポートとを含む。第1のシリアルリンクおよび第2のシリアルリンクは、互いに並行に配置され、単一のルートを介して通信し、第1の通信信号および第2の通信信号は同一の情報を表す。そのプログラマブルロジックデバイスは、第1の通信信号と第2の通信信号を比較して第1の通信信号、第2の通信信号、またはその両方に含まれるデータ内のエラーを検出し、エラーが検出されたときには、第1の通信信号と第2の通信信号の比較に少なくとも部分的に基づいてリアルタイムでエラーを訂正するために、回路をさらに含む。言い換えれば、同情報を表すパラレル通信信号の受信は、通信信号のエラーの検出およびリアルタイム訂正を可能にする。本明細書では、「リアルタイム」は、先行するステップに直ちに続くことを意味するものである。たとえば、エラー訂正是、エラーが検出されるとすぐに開始し得る。10

#### 【0016】

以下にさらに詳しく説明するように、いくつかの実施形態では、データ送信システムは、ソフトウェア監視を殆どまたは全く有さずにハードウェアを使用して送信システムの信頼性を向上させることができる。その結果、データ送信システムの信頼性の向上が、プロセッサを有するI/Oデバイスおよびプロセッサを有しないI/Oデバイスに実現され得る。さらに、本明細書に記載の技法は、I/Oデバイスが国際電気標準会議（International Electrotechnical Commission、IEC）61508に準拠することを可能にし、いくつかの実施形態では、SIL1、2、3、および／または4証明を満たすことを可能にする。20

#### 【0017】

前置きとして、図1は、工業用制御システム12内に配置されたデータ送信システム10の一実施形態を示す。工業用制御システム12は、工業用制御システム12内の様々なデバイスと各々がインターフェースをとり、制御することができる複数のコントローラ14を含む。図示するように、第1のコントローラは、タービン16（たとえば、ガスタービン、蒸気タービン、水力タービン）に結合され、制御し、センサ18に通信可能に結合され、第2のコントローラは、バルブ20およびポンプ22に結合され、それを制御する。他の実施形態では、コントローラ14は、コンバスタ、発電機、および他のターボ機械など、工業用制御システム12内の他のデバイスに結合され、制御することができる。30

#### 【0018】

さらに、図示するように、コントローラ14は、データ送信システム10を介して互いに通信することができる。工業用制御システム12のいくつかの実施形態では、データ送信システム10は、高速イーサネット（登録商標）（HSE）ネットワークまたはH1ネットワークを含み得る。しかし、以下にさらに詳しく説明するように、本明細書に記載の技法は、任意の直列二地点間構造を使用することができる。データ送信システム10を使用することによって、コントローラ14は、接続されたデバイスの状況、収集された測定結果、および制御コマンドなどの様々なタイプのデータを通信することができる。たとえば、第1のコントローラは、データ送信システム10を介して第2のコントローラにセンサ18によって収集された測定結果を送信することができる。それに応答して、第2のコントローラは、タービン16の動作を修正するように第1のコントローラに命令する制御コマンドを送信することができる。したがって、通信、接続されたデバイスの制御、およびコントローラの他の様々な機能を円滑化するために、コントローラ14は、1つまたは複数のプロセッサ24と、1つまたは複数のプロセッサ24によって実行可能な非一時的機械可読命令を記憶することができるメモリ26とを含む。40

## 【0019】

データ送信システム10の一実施形態の詳細な表示が、図2に示される。図示するよう に、各コントローラ14は、データ送信サブシステム15を含む。いくつかの実施形態では、データ送信サブシステム15は、フィールドプログラマブルゲートアレイ、プログラ マブルアレイロジック、プログラマブルロジックアレイ、汎用アレイロジック、またはそれらの任意の組合せなど、プログラマブルロジックデバイスでもよい。他の実施形態では、サブシステム15は、特定用途向け集積回路でもよい。加えて、データ送信サブシステム15は、各コントローラ14のハードウェアサブシステムとして（たとえば、ホットス ワップ可能なカードとして）含まれ得る。サブシステム15を含み得るコントローラ14 の一例は、ニューヨークのGeneral Electric Company of Schenectadyによって入手可能にされたMark VIeコントロールシステムである。10

## 【0020】

図示された実施形態では、データ送信サブシステム15によって実行される機能は、コントローラプロセッサ24および/またはメモリ26によって実行することができる機能 ブロックとして表される。図示するように、サブシステム15は、時計システム（機能ブ ロック27）、フリーランニングカウンタ（FRC）（機能ブロック28）、データI / O（機能ブロック30）、データ比較/複製（機能ブロック32）、および、コントロー ラ14をデータ送信システム10に結合させるパラレルI / Oポート（機能ブロック34 および36）を含む。以下にさらに詳しく説明するように、FRC28は、タイミングデ タを生成して通信信号の時刻同期を可能にすることができる、データI / O30は通信信 号を生成することができ、データ比較/複製32は、通信信号を複製し、通信リンク（た とえば、シリアルリンク）内の故障を検出し、受信された通信信号内のエラーを検出/訂 正することができる。20

## 【0021】

さらに、図示するように、送信システム10は、単一のルート（たとえば、ケーブル） 38と、ルート38のいずれかの末端部に結合されたパラレルシリアル送受信機40およ び42とを含む。より具体的には、シリアル送受信機40および42は、I / Oポート3 4および36とインターフェースし、コントローラ14がサブシステム15を介して他の コントローラ14と通信することを可能にする。シリアル送受信機40および42は、RS - 232送受信機、RS - 485送受信機、差動バス送受信機、シングルエンド送受信 機、または他の低レベルのシリアル送受信機でもよい。いくつかの実施形態では、1つのみのケーブル（たとえば、キャット5、キャット5e、またはキャット6）が使用されて 、2つのサブシステム15を接続し、それによってルートおよび関連機器を最小限に抑える。他の実施形態では、複数のケーブルが使用され得る。いくつかの実施形態では、シリアル送受信機40および42は、無線周波数よりも低い周波数で通信信号を送信して、無 線周波数に起因する信号内のノイズの量を最小限に抑えることができる。たとえば、シリアル送受信機40および42は、1~20MHz、20~30MHz、30~40MHz 、40~50MHz、50~60、60~100MHz、またはそれらの任意の組合せの 間で通信して、1~20Mbit/s、20~30Mbit/s、30~40Mbit/s、40~50Mbit/s、50~60Mbit/s、60~100Mbit/sまたはそれらの任意の組合せの間のデータ送信を可能にす ることができる。3040

## 【0022】

明確に図示されていないが、単一のルート38は、シリアル送受信機40を結合する第 1のシリアルリンクと、並行してシリアル送受信機42を結合させる第2のシリアルリンクとを含む。より具体的には、第1のおよび第2のシリアルリンクは、コントローラ14 間の通信信号のパラレル送信を可能にすることができます。たとえば、第1の通信信号は第 1のシリアルリンクを介して送信することができ、第2の通信信号は、並行して、そして ほぼ同時に、第2のシリアルリンクを介して送信することができる。以下にさらに詳しく述べるように、第1の通信信号および第2の通信は、同情報を表すことができ、シリアル50

ルリンク内の故障の検出および通信信号内のエラーの検出／訂正を円滑化する。いくつかの実施形態では、適切なルート38は、4つのワイヤを第1のシリアルリンクのために使用することおよび4つのワイヤを第2のシリアルリンクのために使用することを可能にする8つのシリアルワイヤを含むので、適切なルート38は、カテゴリ5（キャット5）ケーブルでもよい。他の実施形態では、第1のシリアルリンクおよび第2のシリアルリンクは、別個のルートで含まれ得る。さらに、図示するように、単一のルート38は、1つのコントローラを別のコントローラに結合させ、それによって、直列二地点間構造をセットする。本明細書では、「二地点間構造」は、1つのデバイスが別のデバイスに直接に結合される場合を述べている。言い換えれば、いくつかの実施形態では、コントローラ14は、ルート38を介してのみ通信することができ、他方のコントローラ14の識別、通信信号の送信時間、通信信号の順序、またはそれらの任意の組合せを両方のコントローラ14が予定する（たとえば、予想するまたは期待する）ことを可能にする。そのような構造は、1～10メートル離れて、10～20メートル離れて、20～30メートル離れて、30～40メートル離れて、40～100メートル離れて、またはそれらの任意の組合せで置かれたデバイスの間の通信に適切であり得る。

#### 【0023】

いくつかの実施形態では、コントローラ14は、図3に示すような三重モジュール式冗長（TMR）コントローラ14でもよい。一般に、TMRコントローラ14は、3つのコアを使用することによって、信頼性を向上させることができる。より具体的には、図示するように、TMRコントローラ14は、各々がほぼ同じに機能するRコア46、Sコア48、およびTコア50を含む。それにより、TMRコントローラ14は、投票方式を介して動作して、正常に動作しないコア（たとえば、46、48、または50）の影響を低減する。

#### 【0024】

図示するように、TMRコントローラ14内のRコア46は第1の送信システム52によって結合され、Sコア48は第2の送信システム54によって結合され、Tコースは第3の送信システム56によって結合される。より具体的には、いくつかの実施形態では、各々の送信システム（たとえば、52、54、および56）は、たとえば、データ送信サブシステム15を含むこと、および、互いにほぼ独立して動作することによって、前述のデータ送信システム10と同様に機能することができる。より具体的には、各送信システム（たとえば、52、54、および56）は、各ペアのコアの間の通信信号のパラレル送信を可能にするために、第1のおよび第2のシリアルリンク（または、サブシステム15の任意の他の構成要素）を含み得る。言い換えれば、第1の送信システム52はRコア46間でパラレル通信信号（たとえば、2つ以上の同一のデータ送信）を送信することができ、第2の送信システム54はSコア48間でパラレル通信信号を送信することができ、第3の送信システム56はTコア50間でパラレル通信信号を送信することができる。加えて、前述のように、第1のおよび第2のシリアルリンクは、単一のまたは2つの別個のルート内に含まれ得る。したがって、図3に示す実施形態では、3つの別個のルートまたは6つの別個のルートが使用され得る。別法として、すべての6つのシリアルリンクが、単一のルートに含まれ得る。

#### 【0025】

データ送信システム10を介してコントローラ14間で送信され得る通信信号58の一実施形態が、図4に示される。図示するように、通信信号58は、通信信号データ60、順序番号62、タイミングデータ64、送信者ID66、および、エラー検査データ68を含む。通信信号データ60は、コントローラ14間で通信されることを意図されたデータを含み得る。たとえば、通信信号データ60は、制御コマンド、ログインデータ、認証データ、投票データ、測定データ、デバイス状況などを含み得る。

#### 【0026】

順序番号62は、通信信号58が送信された順番を表すことができる。いくつかの実施形態では、順序番号62は、通信信号58のヘッダ内に含まれ得る。したがって、順序番

10

20

30

40

50

号 5 8 は、受信コントローラ 1 4 が通信信号 5 8 が送信された順番を判定することを可能にすることができる。

#### 【 0 0 2 7 】

前述のように、タイミングデータ 6 4 は、通信信号 5 8 の時刻同期を可能にするために、F R C 2 8 によって生成され得る。たとえば、いくつかの実施形態では、タイミングデータ 6 4 は、F R C 2 8 でのカウントを表す一意の文字でもよい。それにより、送信および受信コントローラ 1 4 内のF R C 2 8 が同期される場合、タイミングデータ 6 4 は通信信号 5 8 がいつ送信されたかを受信コントローラ 1 4 が判定することを可能にする。

#### 【 0 0 2 8 】

送信者 I D 6 6 は、送信コントローラ 1 4 を識別することができる。たとえば、いくつかの実施形態では、送信者 I D は、媒体アクセス制御（M A C）アドレス、所有権を主張できる一意のモジュール I D コード、または他の同様の一意の識別子でもよい。いくつかの実施形態では、所有権を主張できる一意のモジュール I D コードは、データコードを含む一意の通し番号を含み得る。したがって、送信者 I D 6 6 は、受信コントローラ 1 4 が送信コントローラ 1 4 の識別を判定することを可能にすることができる。10

#### 【 0 0 2 9 】

エラー検査データ 6 8 は、巡回冗長検査、チェックサム、暗号学的ハッシュ関数、または同様のものなどのエラー検査技法を円滑化するデータを含み得る。たとえば、巡回冗長検査が使用される場合、エラー検査データ 6 8 は、通信信号 5 8 の多項式除法の余りを含み得る。動作中、送信コントローラ 1 4 は、エラー検査技法を実行し、通信信号 5 8 でエラー検査データ 6 8 （たとえば、チェックサム）をコード化することができる。その結果、受信コントローラ 1 4 は、エラー検査技法を繰り返すこと、およびその結果をエラー検査データ 6 8 と突き合わせること（たとえば、新たにチェックサムを計算すること、および、送信されたチェックサムで計算を確認すること）によって、エラー／故障を検出することができる。20

#### 【 0 0 3 0 】

前述のように、送信システム 1 0 は、コントローラ 1 4 間で通信信号 5 8 を送信することを可能にする。図 5 は、パラレル通信信号を送信するために、送信コントローラ 1 4 、および、より具体的には、データ送信サブシステム 1 5 （たとえば、プログラマブルロジックデバイス）によって使用され得る、プロセス 7 0 の一実施形態を示す。プロセス 7 0 は、メモリ 2 6 に記憶されたおよびプロセッサ 2 4 によって実行される非一時的機械可読命令またはコードによって、実装され得る。図示された実施形態では、プロセス 7 0 は、通信信号データを生成すること（プロセスブロック 7 4 ）、順序番号をコード化すること（プロセスブロック 7 6 ）、タイミングデータをコード化すること（プロセスブロック 7 8 ）、送信者 I D をコード化すること（プロセスブロック 8 0 ）、およびエラーデータをコード化すること（プロセスブロック 8 2 ）を含む第 1 の通信信号の生成（大括弧 7 2 ）によって、開始する。プロセス 7 0 は、第 2 の通信信号を生成すること（プロセスブロック 8 4 ）、および第 1 のシリアルリンクで第 1 の通信信号を（プロセスブロック 8 6 ）そして第 2 のシリアルリンクで第 2 の通信信号を（プロセスブロック 8 8 ）並行して送信することによって、継続する。30

#### 【 0 0 3 1 】

より具体的には、第 1 の通信信号は、データ I / O 3 0 によって生成され得る。通信信号データ 6 0 を生成するために（プロセスブロック 7 4 ）、データ I / O 3 0 は、第 1 の通信信号で送信するためのデータを収集することができる。たとえば、デバイス状況が送信されようとするとき、データ I / O 3 0 は、その状況について接続されたデバイス（たとえば、1 6、2 0 または 2 2 ）をポーリングすること、または、デバイスを監視するセンサ（たとえば、1 8 ）から測定結果を検索することができる。順序番号 6 2 をコード化するために（プロセスブロック 7 6 ）、データ I / O 3 0 は、各通信信号が送信されると値を増加させる逐次カウンタを含み得る。それにより、カウンタからのカウントが、通信信号 5 8 が送信される順番を表すために、順序番号 6 2 として含まれ得る。送信者 I D40

50

66をコード化するために(プロセスブロック80)、データI/O30は、送信コントローラのメモリ26からその送信コントローラを識別する記憶された一意の識別子を検索することができる。

#### 【0032】

タイミングデータ64をコード化するために(プロセスブロック78)、データI/O30は、FRC28からタイミングデータ64を受信することができる。より具体的には、FRC28は、システム時計27から受信されたタイミング信号に基づいて、タイミングデータ64を生成することができる。たとえば、FRC28は、そのタイミング信号に基づいてカウントアップし、それが特定のカウントに到達した後は、カウントをリセットすることができる。通信信号58が送信されようとするときのカウントに基づいて、FRC28は、そのカウントを表す一意の文字を出力することができる。それにより、通信信号58が受信されるとき、受信コントローラは、それ自体のFRC28内のカウントとその一意の文字を比較して、いつ送信信号58が送信されたかを判定することができる。10

#### 【0033】

エラー検査データ68をコード化するために(プロセスブロック82)、データI/O30は、巡回冗長検査、チェックサム、暗号学的ハッシュ関数、または同様のものなどのデータ検査方法を実行することができる。たとえば、巡回冗長検査が使用される場合、データI/O30は、通信信号58、またはより具体的には通信信号データ60、で多項式除法を実行し、その多項式除法の余りをエラー検査データ68としてコード化することができる。それにより、受信コントローラ14は、そのエラー検査技法を繰り返すことおよびその結果をエラー検査データ68と突き合わせることによって、エラーを検出することができる。他の実施形態では、順序番号62をコード化すること(プロセスブロック76)、タイミングデータ64をコード化すること(プロセスブロック76)、送信者ID66をコード化すること(プロセスブロック76)、およびエラー検査データ68をコード化すること(プロセスブロック76)は、任意の順序で実行され得る。20

#### 【0034】

第1の通信信号は、次いで、データI/O30からデータ比較／複製32に渡されて、第2の通信信号を生成することができる(プロセスブロック84)。より具体的には、データ比較／複製32は、たとえば第1の通信信号を複製することによって、同情情報を第1の通信信号として表すために、第2の通信信号を生成することができる。加えてまたは別法として、第2の通信信号を生成するために、データ比較／複製32は、第1の通信信号を反転されること(たとえば、「1」を「0」に、またはその逆に変更する)、または第1の通信信号を逆転させること(たとえば、第1の通信信号の最上位ビットを第2の通信信号の最下位ビットとして置くことなど)ができる。たとえば、第1の通信信号が「10011100」である場合、逆転された第2の通信信号は「00111001」でもよく、反転された第2の信号は「01100011」でもよい。30

#### 【0035】

第1の通信信号の逆転および/または反転は、シリアルリンクにおける故障の検出および/または送信されるデータにおけるエラーの検出/訂正を円滑化することができる。たとえば、通信信号が反転される場合、それらの通信信号のうちの1つの通信信号内のエラーは、第1の通信信号と第2の通信信号内のビットが両方とも「高い」または両方とも「低い」とときに検出され得る。また、第2の通信信号が逆転される場合、エラーは、第1の通信信号の最上位ビットが第2の通信信号の最下位ビットと一致しないときに検出され得る。さらに、エラーは、第1の通信信号の誤りのあるビットを第2の通信信号からの誤りのないビットで置き換えることによって、訂正され得る。40

#### 【0036】

第1の通信信号は、データ比較／複製32から第1のI/Oポート34に渡されて第1のシリアルリンクを介して送信することができ(プロセスブロック86)、第2の通信信号は、第2のシリアルリンクを介してデータ比較／複製32から第2のI/Oポート36に渡すことができる(プロセスブロック88)。以下にさらに詳しく説明するように、シ50

リアルリンク故障検出およびデータエラー検出／訂正を円滑化するために、第1の通信信号および第2の通信信号は、並行して、ほぼ同時に、送信され得る。

#### 【0037】

送信システム10の受信側では、送信された通信信号58が、受信コントローラ14によって受信される。図6は、たとえば単一のルート（たとえば、キャット5ケーブル）で、パラレル通信信号58を受信するために、受信コントローラ14、より具体的にはデータ送信サブシステム15（たとえば、プログラマブルロジックデバイス）、によって使用され得るプロセス90の一実施形態を示す。プロセス90は、メモリ26に記憶された、プロセッサ24によって実行される非一時的機械可読命令またはコードによって、実装され得る。図示するように、プロセス90は、第1の通信信号を待つこと（プロセスブロック92）および第2の通信信号を待つこと（プロセスブロック94）によって、開始する。第1の通信信号が受信され（プロセスブロック96）、第2の通信信号が受信される（プロセスブロック98）場合、第1の通信信号と第2の通信信号が比較され（大括弧100）、これは、ビット単位の一致について第1の通信信号と第2の通信信号を比較すること（プロセスブロック102）、コード化された順序番号を比較すること（プロセスブロック104）、コード化されたタイミングデータを比較すること（プロセスブロック106）、送信者IDを比較すること（プロセスブロック108）、および、コード化されたエラー検査データを比較すること（プロセスブロック110）を含み得る。10

#### 【0038】

より具体的には、データ比較／複製32は、第1のI/Oポート34を介する第1の通信信号の受信を待つこと（プロセスブロック92）、および第2のI/Oポート36を介する第2の通信信号の受信を待つこと（プロセスブロック94）を待つことができる。いくつかの実施形態では、これは、定期的にスケジュールされた通信信号58のウォッチドッグタイムアウトを使用することを含み得る。言い換えれば、データ比較／複製32は、スケジュールされた通信信号58の期待される到達時間など、所定の時間待つことができ、通信信号58がその時間内に受信されない場合には、データ比較／複製信号58は、タイムアウト信号を出力することができる。いくつかの実施形態では、前述のように、二地点間構造の使用は、コントローラ14が前の通信信号58の実際の到達時間を調べることを可能にすることができるので、期待される到達時間は、受信コントローラ14によって予定することができる。したがって、図2に示すように、データ比較／複製32は、時計システム27に結合されてタイミング信号を受信する。いくつかの実施形態では、通信信号58は、1～5ミリ秒、5～8ミリ秒、8～10ミリ秒、10～12ミリ秒、12～15ミリ秒、15～30ミリ秒、またはそれらの任意の組合せごとに期待される。したがって、タイムアウト信号の出力は、通信信号58が削除されたまたは遅れたことを指示し得る。2030

#### 【0039】

第1の通信信号および第2の通信信号の両方が受信された後は、データ比較／複製32は、第1の通信信号と第2の通信信号の比較を開始することができ（大括弧100）、シリアルリンク内の故障の検出および送信されたデータにおけるエラーの検出／訂正を円滑化することができる。より具体的には、前述のように、第2の通信信号は第1の通信信号の逆転または反転されたバージョンでもよいので、ビット単位の一致について第1の通信信号と第2の通信信号を比較するために（プロセスブロック102）、データ比較／複製32は、第2の通信信号を第1の通信信号と比較する前に、第2の通信信号を反転または逆転させることができる。したがって、ビット単位の比較は、通信信号58内のビットが削除された、挿入された、または破損したことを指示し得る。加えて、以下に詳しく説明するように、ビット単位の比較は、通信信号58内のビットのリアルタイム訂正を円滑化することができる。40

#### 【0040】

コード化された順序番号62を比較するために（プロセスブロック104）、データ比較／複製32は、通信信号58のヘッダから順序番号62を検索することができ、コント50

ローラ 1 4 が通信信号 5 8 が送信された順番を判定することを可能にする。より具体的には、データ比較 / 複製 3 2 は、第 1 の通信信号と第 2 の通信信号のうちの一方または両方でコード化された順序番号 6 2 を予期した順序番号 6 2 と比較することができる。たとえば、通信信号 5 8 でコード化された順序番号 6 2 が前のペアの通信信号と同じである場合、繰返しエラーが検出され得る。加えて、通信信号 5 8 でコード化された順序番号 6 2 が予期した順序番号とは異なる場合、削除、挿入または並べ直しエラーが検出され得る。エラーが存在しない場合、受信された各通信信号 5 8 でコード化された順序番号 6 2 は、前に受信された通信信号 5 8 でコード化された順序番号 6 2 と所定の関係を有することになるので、いくつかの実施形態では、前述のように、二地点間直列構造の使用は、受信コントローラ 1 4 が予期した順序番号を維持することを可能にできる。したがって、順序番号 6 2 の比較は、通信信号 5 8 の一方または両方が繰り返された、削除された、挿入された、または並べ直されたことを指示し得る。

#### 【 0 0 4 1 】

コード化されたタイミングデータ 6 4 を比較するために（プロセスブロック 1 0 6）、データ比較 / 複製 3 2 は、第 1 の通信信号および第 2 の通信信号の一方または両方を時刻同期させることができる。いくつかの実施形態では、これは、通信信号 5 8 でコード化されたタイミングデータ 6 4 を受信コントローラ 1 4 で F R C 2 8 によって生成されたメモリ 2 6 内の記憶されたタイミングデータ 6 4 と突き合わせることによって、通信信号 5 8 が送信された時間を判定することを含み得る。たとえば、送信および受信コントローラの両方で F R C 2 8 は、午後 3 時を示すための一意の文字「X」を生成することができる。加えて、通信信号 5 8 でコード化されたタイミングデータ 6 4 が、前に受信された通信信号 5 8 でコード化されたタイミングデータ 6 4 と同じである場合、繰返しエラーが検出され得る。さらに、通信信号 5 8 でコード化されたタイミングデータが、前に受信された通信信号 5 8 でコード化されたタイミングデータ 6 4 よりも早い場合、並べ直しまたは遅延エラーが検出され得る。したがって、コード化されたタイミングデータ 6 4 の比較は、通信信号 5 8 の一方または両方が繰り返された、並べ直された、または遅れたことを指示し得る。

#### 【 0 0 4 2 】

送信者 I D 6 6 を比較するために（プロセスブロック 1 0 8）、データ比較 / 複製 3 2 は、送信コントローラ 1 4 の識別を判定することができる。より具体的には、これは、第 1 の通信信号および第 2 の通信信号の一方または両方でコード化された送信者 I D 6 6 をメモリ 2 6 内に記憶された送信者 I D 6 6 と突き合わせることを含み得る。たとえば、コントローラメモリ 2 6 は、コントローラが通信信号 5 8 をそこから受信することを期待するデバイスに対応する送信者 I D 6 6 のリストを記憶することができる。いくつかの実施形態では、前述のように、二地点間直列構造の使用は、受信コントローラ 1 4 が、どのデバイスにコントローラ 1 4 が結合されるかを予め定め、それらのデバイスに関連する送信者 I D を記憶することを可能にできる。したがって、コード化された送信者 I D 6 6 が、コントローラ 1 4 がそこから通信信号 5 8 を受信することを期待しないデバイスに対応する場合に、コード化された送信者 I D 6 6 の比較は、通信信号 5 8 の一方または両方が挿入されたことを指示し得る。

#### 【 0 0 4 3 】

コード化されたエラー検査データ 6 8 を比較するために（プロセスブロック 1 1 0）、データ比較 / 複製 3 2 は、第 1 の通信信号および第 2 の通信の一方または両方で、巡回冗長検査（C R C）などのエラー検査技法を実行して、受信された通信信号 5 8 が破損しているかどうかを判定することができる。より具体的には、データ比較 / 複製 3 2 は、送信コントローラ 1 4 で実行されたエラー検査技法を複製し、その結果をコード化されたエラー検査データ 6 8 と比較することができる。その結果、コード化されたエラー検査データ 6 8 の比較は、通信信号 5 8 の一方または両方が破損している、または他の方法で互いと一致しないことを指示し得る。

#### 【 0 0 4 4 】

10

20

30

40

50

他の実施形態では、ピット単位で通信信号を比較すること（プロセスブロック 102）、コード化された順序番号 62 を比較すること（プロセスブロック 104）、コード化されたタイミングデータ 64 を比較すること（プロセスブロック 106）、送信者 ID 66 を比較すること（プロセスブロック 108）、および、エラー検査データ 68 を比較すること（プロセスブロック 110）は、任意の順序で実行され得る。さらに、ある種の実施形態において、挿入、削除、遅延、またはそれらの任意の組合せの検出は、なりすましを指示し得る。本明細書では、なりすましは、送信システム 10 への認証されていない侵入を表すものである。たとえば、通信信号 58 が挿入された、削除された、または遅れているときに、これは、認証されていないデバイス（たとえば、コントローラ 14）が送信システム 10 にアクセスし、通信信号 58 を変更していることを指示し得る。

10

#### 【0045】

前述のように、それぞれ第 1 のおよび第 2 のシリアルリンクを介して並行してほぼ同一の情報を表す第 1 の通信信号および第 2 の通信信号を送信することは、第 1 のシリアルリンク、第 2 のシリアルリンク、またはその両方での故障および／またはなりすましの検出を可能にする。シリアルリンクにおいて故障を検出するために使用され得るプロセス 112 の一実施形態が、図 7 に示される。プロセス 112 は、メモリ 26 に記憶された、プロセッサ 24 によって実行される非一時的機械可読命令またはコードによって、実装され得る。図示するように、プロセス 112 は、第 1 の通信信号と第 2 の通信信号を待つこと（決定ブロック 114）によって、開始し得る。両方の通信信号が受信された場合、第 1 の通信信号と第 2 の通信信号が比較され得る（プロセスブロック 100）。タイムアウト信号が出力されたかどうかおよび／または通信信号の比較に基づいて、シリアルリンクにおける故障が検出され得る（決定ブロック 116）。シリアルリンクで故障が検出されない場合、送信システム 10 は動作を継続する（プロセスブロック 118）。一方、故障が検出された場合、送信システム 10 がその検出された故障にかかわらず動作を継続するべきか（プロセスブロック 118）または動作を中止するべきか（プロセスブロック 122）が判定され得る（決定ブロック 120）。

20

#### 【0046】

より具体的には、前述のように、データ比較／複製 32 は、通信信号 58 のために通信信号フレームなどの指定された時間待つことができる（プロセスブロック 114）。通信信号 58 の一方または両方が受信されない場合、データ比較／複製 32 は、通信信号 58 の一方または両方がタイムアウトされたことを指示するタイムアウト信号を出力することができる。一方、両方の信号 58 が指定された時間内に受信された場合、データ比較／複製 32 は通信信号 58 を比較することができ（プロセスブロック 100）、これは、ピット単位の一致について第 1 の通信信号と第 2 の通信信号 58 を比較すること（プロセスブロック 102）と、コード化された順序番号を比較すること（プロセスブロック 104）と、コード化されたタイミングデータを比較すること（プロセスブロック 106）と、送信者 ID を比較すること（プロセスブロック 108）と、コード化されたエラー検査データを比較すること（プロセスブロック 110）とを含み得る。前述のように、その通信信号の比較は、通信信号で送信されるデータにおけるエラーの検出を円滑化することができる。

30

#### 【0047】

通信信号 58 の比較および／またはタイムアウト信号が出力されたかどうかに基づいて、データ比較／複製 32 は、故障が第 1 のシリアルリンク、第 2 のシリアルリンク、またはその両方内に存在するかどうかを判定することができる（決定ブロック 116）。たとえば、第 1 の通信信号がタイムアウトしたが、第 2 の通信信号はしていない場合、データ比較／複製 32 は、第 1 のシリアルリンクが故障を有すると判定することができる。加えて、任意のエラー（たとえば、繰返し、削除、挿入、並べ直し、破損、遅延、またはなりすまし）は、シリアルリンクのうちの 1 つまたは複数における故障を指示し得る。たとえば、第 1 の通信信号 58 に破損があるが第 2 の通信信号 58 には破損がないことは、第 1 のシリアルリンクでの絶縁が弱くなり、浮遊電磁波などの外部干渉を受けやすいことを指

40

50

示し得る。

#### 【0048】

さらに、いくつかの実施形態では、シリアルリンク内の故障が検出された場合、シリアルリンクの状況が、その故障に基づいて更新され得る。たとえば、故障が検出される前に、第1のシリアルリンクおよび第2のシリアルリンクの状況は「良好」に設定されるが、第1のシリアルリンク内の故障が検出された場合、第1のシリアルリンクの状況は「不良」に更新され得る。以下にさらに説明するように、他の実施形態では、その状況は、送信システム10が動作をより賢明に管理することを可能にするために、中間状況を含み得る。たとえば、シリアルリンクは、単一のエラーのみが検出された場合、またはエラーが単に周期的に検出される場合（たとえば、送信されるあらゆる通信信号でではなく）、「部分的に不良」または「潜在的に不良」の状況を有し得る。たとえば、第1のエラーが検出された場合には、状況は「機能している」から「潜在的に不良」に更新することができ、第2のエラーが3つの通信信号の後に検出された場合には、状況は再び「不良」に更新され得る。10

#### 【0049】

故障が検出された場合、データ比較／複製32は、その故障に関連する状況に基づいて送信システムの動作を中止するか継続するかをより賢明に判定することができる（決定ブロック120）。言い換えれば、送信システム10は、よりフォールトトレラントになり、シリアルリンク内の故障が検出されるたびに直ぐにシャットダウンしないことが可能になる。いくつかの実施形態では、動作を継続するかどうかの決定は、シリアルリンクの状況と通信信号58に含まれる情報とに依存し得る。たとえば、第1のシリアルリンクが「機能している」が第2のシリアルリンクは「不良」であり、通信信号58は温度測定結果を単に通信する場合、送信システム10は、第1のシリアルリンクを介して受信された通信信号58に単に基づいて動作を継続することができる。そのような一実施形態では、コントローラ14は、センサ18の測定結果の送信および受信を継続することを決定することができるが、制御コマンドの送信／受信を中止することを決定することが可能である。20

#### 【0050】

加えて、送信システム10の動作を継続するかどうかの決定に影響を及ぼす他の要因は、送信システム10を使用するシステムの特質と、通信信号内のエラーの履歴とを含み得る。たとえば、キャンディ製造工場内の送信システム10は原子力発電所よりもフォールトトレラントであることがある、1つの「機能している」シリアルリンクおよび1つの「潜在的に不良」リンクで動作することを選択することができるが、原子力発電所は2つの「機能している」シリアルリンクでのみ動作し得る。加えて、エラーの履歴がなかった場合、送信システム10は、エラーが異常に起因するものと考え、次のエラーが検出されるまで動作を継続することができる。そのような実施形態では、送信システム10は、不良シリアルリンクを訂正するための機会をオペレータに与えるために、設定された期間の動作を継続することを決定することができるが、故障が設定された期間の後に訂正されていない場合には動作を中止することができる。30

#### 【0051】

さらに、動作を継続するかどうかの決定は、エラーがリアルタイムで訂正可能であるかどうかに依存し得る。たとえば、エラーが削除である、または通信信号58およびその通信信号の両方で最上位ビットの破損が逆転された場合、送信システム10は、訂正された通信信号58に基づいて動作を継続することを選択することができる。通信信号58中のエラーの訂正可能性が、以下にさらに詳細に説明される。40

#### 【0052】

前述の例に基づいて、動作を継続するか中止するかの決定は、送信システム10を使用するシステムの特質、シリアルリンクの状況、通信信号58内のエラーがリアルタイムで訂正可能かどうか、通信信号58で送信される情報の特質、エラーの履歴など、様々な要因のうちの1つまたは複数に基づいてカスタマイズされ得ることを理解されたい。そのような判定のために使用される機能は、データ比較／複製32あるいはプロセッサ24およ50

び／またはメモリ 2 6 の他のシステムによって実行され得る。

#### 【 0 0 5 3 】

リアルタイムでエラーを訂正するためのプロセス 1 2 4 の一実施形態が、図 8 に示される。プロセス 1 2 4 は、メモリ 2 6 に記憶された、プロセッサ 2 4 によって実行される非一時的機械可読命令またはコードによって、実装され得る。図示するように、エラーが検出された場合（プロセスブロック 1 2 6 ）、そのエラー訂正が可能であるかどうかの判定が行われる（決定ブロック 1 2 8 ）。エラーが訂正不可能である場合、送信システム 1 0 は、動作を中止することができる（プロセスブロック 1 3 2 ）。そのエラーが訂正可能である場合、エラーはリアルタイムで訂正され（プロセスブロック 1 3 4 ）、送信システム 1 0 は動作を継続する（プロセスブロック 1 3 6 ）。

10

#### 【 0 0 5 4 】

より具体的には、データ比較／複製 3 2 は、エラーのタイプおよびエラーの大きさなどの様々な要因に基づいて、エラーが訂正可能であるかどうかを判定することができる。たとえば、前述の例で、エラーが単に各通信信号 5 8 の最上位ビットを破損し、通信信号 5 8 が逆転された場合、データ比較／複製 3 2 は、第 1 の通信信号の最上位ビットを第 2 の通信信号の最下位ビットで置き換えることおよびその逆によって、エラーを訂正することができる。加えて、検出されたエラーが繰返しである場合、送信システム 1 0 は、単に、前に受信された通信信号を実行することおよび次に受信された通信信号を無視することによって、エラーを訂正することができる。同様に、検出されたエラーが挿入である場合、送信システムは、挿入された通信信号 5 8 を単に無視し、エラーを訂正することができる。一方、検出されたエラーがなりすましである場合、エラーは、訂正可能ではないことがあり、送信システム 1 0 は、送信システム 1 0 への侵入が検出されたので動作を中止することを選択することができる。

20

#### 【 0 0 5 5 】

前述の例に基づいて、データ比較／複製 3 2 は、第 1 の通信信号内の誤りのあるビットを第 2 の通信信号からの誤りのないビットで置き換えることによって、リアルタイムで第 1 の通信信号の 1 つまたは複数のビットに影響を及ぼすエラーを訂正することができる。加えて、データ比較／複製 3 2 は、第 1 の通信信号を無視することによって、第 1 の通信信号に影響を及ぼすが第 2 の通信信号には影響を及ぼさないエラーを訂正することができる。さらに、データ比較／複製 3 2 は、第 1 の通信信号および第 2 の通信信号の両方を無視することによって、第 1 の通信信号および第 2 の通信信号の両方に影響を及ぼすエラーを訂正することができる。検出されたエラーの訂正可能性は、事実に固有することがあることを理解されたい。そのような判定のために使用される機能は、データ比較／複製 3 2 あるいはプロセッサ 2 4 および／またはメモリ 2 6 の他の部分によって、実行され得る。

30

#### 【 0 0 5 6 】

さらに、本明細書に記載の技法は、エラーが検出されるとすぐに訂正される、またはそのエラーがリアルタイムで訂正されることを可能にする。たとえば、前述の例で、第 1 の通信信号の最上位ビットと第 2 の通信信号の最下位ビットがビット単位で比較される際、第 1 の通信信号の最上位ビットは第 2 の通信信号の最下位ビットで置き換えることが可能であり、前に受信された通信信号 5 8 は受信時に実行することができ、次に受信された通信信号は受信時に無視してもよく、挿入された通信信号 5 8 は受信時に無視することができる。

40

#### 【 0 0 5 7 】

前述は 2 つのパラレルシリアルリンクを説明するが、他の実施形態は、3 つ以上のパラレルシリアルリンク（たとえば、3 つのまたは 4 つのパラレルシリアルリンク）を含み得る。3 つ以上のパラレルシリアルリンクの使用は、一般に、前述の技法を使用してデータ送信システム 1 0 の信頼性を向上させることができることが、理解されよう。

#### 【 0 0 5 8 】

記載された実施形態の技術的効果は、データ送信システム 1 0 の信頼性を増すことを含む。より具体的には、データ送信システム 1 0 の信頼性は、並行して同情報を表す通信信

50

号 5 8 を各々送信するパラレルシリアルリンクを使用することによって、向上させることができる。パラレル通信信号 5 8 の受信および比較に基づいて、シリアルリンク内の故障および通信信号内のエラーが検出され得る。その結果、送信システム 1 0 の信頼性は、送信システム 1 0 をよりフォールトトレラントにすることおよびリアルタイムでエラーを訂正することによって、向上させることができる。加えて、いくつかの実施形態では、故障およびエラーの検出および／または訂正是、処理能力にかかわらず、すべてのデバイスに実現される信頼性の向上を可能にする、ハードウェアの使用のみで実現され得る。

#### 【 0 0 5 9 】

本明細書は、最良の形態を含めて本発明を開示するために、さらには任意のデバイスまたはシステムの製造および使用と任意の組み込まれた方法の実行とを含めて、当業者が本発明を実施することを可能にするために、例を使用する。本発明の特許性のある範囲は、本特許請求の範囲によって定義され、当業者が気が付く他の例を含み得る。そのような他の例は、それらが本特許請求の範囲の文言と異ならない構造的要素を有する場合、またはそれらが本特許請求の範囲の文言とごくわずかな差を有する同等の構造的要素を含む場合、本特許請求の範囲内にあるものとする。

10

#### 【 符号の説明 】

#### 【 0 0 6 0 】

|     |              |    |

|-----|--------------|----|

| 1 0 | データ送信システム    |    |

| 1 2 | 工業用制御システム    |    |

| 1 4 | コントローラ       | 20 |

| 1 5 | データ送信サブシステム  |    |

| 1 6 | タービン         |    |

| 1 8 | センサ          |    |

| 2 0 | バルブ          |    |

| 2 2 | ポンプ          |    |

| 2 4 | プロセッサ        |    |

| 2 6 | メモリ          |    |

| 3 0 | データ I / O    |    |

| 3 2 | データ比較／複製     |    |

| 3 4 | I / O ポート    | 30 |

| 3 6 | I / O ポート    |    |

| 3 8 | ルート          |    |

| 4 0 | パラレルシリアル送受信機 |    |

| 4 2 | パラレルシリアル送受信機 |    |

| 4 6 | R コア         |    |

| 4 8 | S コア         |    |

| 5 0 | T コア         |    |

| 5 2 | 第 1 の送信システム  |    |

| 5 4 | 第 2 の送信システム  |    |

| 5 6 | 第 3 の送信システム  | 40 |

| 5 8 | 通信信号         |    |

| 6 0 | 通信信号データ      |    |

| 6 2 | 順序番号         |    |

| 6 4 | タイミングデータ     |    |

| 6 6 | 送信者 ID       |    |

| 6 8 | エラー検査データ     |    |

【図1】

【図2】

【図3】

FIG. 3

【図5】

【図4】

FIG. 4

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

---

フロントページの続き

(72)発明者 マイケル・グリン・ワイズ

アメリカ合衆国、ヴァージニア州、セイラム、ロアノーク・ブルーヴァード、1501番

(72)発明者 スティーブン・ジェイムズ・シュミット

アメリカ合衆国、ヴァージニア州、セイラム、ロアノーク・ブルーヴァード、1501番

審査官 川口 貴裕

(56)参考文献 国際公開第2012/144068 (WO, A1)

米国特許第07870299 (US, B1)

特開2012-119813 (JP, A)

特開2006-165656 (JP, A)

特開昭57-042244 (JP, A)

特開2011-146953 (JP, A)

特開2011-176718 (JP, A)

米国特許出願公開第2011/0209021 (US, A1)

特開2006-319520 (JP, A)

特開2013-046230 (JP, A)

特開2011-068351 (JP, A)

特開昭63-031241 (JP, A)

米国特許第04633473 (US, A)

米国特許出願公開第2012/0191888 (US, A1)

(58)調査した分野(Int.Cl., DB名)

H04L 1/00

H04L 1/22

H03K 19/173