### (10) **DE 698 39 192 T2** 2009.02.26

#### •

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 040 587 B1

(21) Deutsches Aktenzeichen: 698 39 192.6

(86) PCT-Aktenzeichen: PCT/US98/26051

(96) Europäisches Aktenzeichen: 98 962 004.2

(87) PCT-Veröffentlichungs-Nr.: WO 1999/030428

(86) PCT-Anmeldetag: 08.12.1998

(87) Veröffentlichungstag

der PCT-Anmeldung: 17.06.1999

(97) Erstveröffentlichung durch das EPA: 04.10.2000

(97) Veröffentlichungstag

der Patenterteilung beim EPA: **27.02.2008** (47) Veröffentlichungstag im Patentblatt: **26.02.2009**

(30) Unionspriorität:

987306 09.12.1997 US

(73) Patentinhaber:

Qualcomm Inc., San Diego, Calif., US

(74) Vertreter:

WAGNER & GEYER Partnerschaft Patent- und Rechtsanwälte, 80538 München

(51) Int Cl.<sup>8</sup>: *H04B 1/16* (2006.01)

H03M 3/02 (2006.01)

(84) Benannte Vertragsstaaten:

DE, DK, ES, FI, FR, GB, SE

(72) Erfinder:

BAZARJANI, Seyfollah S., San Diego, CA 92 121-1714, US; CICCARELLI, Steven C., San Diego, CA 92 121-1714, US; YOUNIS, Saed G., San Diego, CA 92130, US; BUTTERFIELD, Daniel K., San Diego, CA 92130, US

(54) Bezeichnung: FUNKEMPFÄNGER MIT EINEM SIGMA-DELTA-DIGITAL/ANALOG-WANDLER

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelegt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

#### **Beschreibung**

Hintergrund der Erfindung

I. Gebiet der Erfindung

**[0001]** Die vorliegende Erfindung bezieht sich auf Kommunikationen. Im besonderen bezieht sich die vorliegende Erfindung auf einen neuartigen und verbesserten Empfänger, der einen Sigma-Delta-Analog-zu-Digital-Wandler umfasst.

II. Beschreibung der verwandten Technik

[0002] In vielen modernen Kommunikationssystemen wird die digitale Sendung aufgrund der verbesserten Effizienz und der Fähigkeit verwendet, Sendefehler zu erfassen und zu korrigieren. Beispielhafte digitale Sendeformate beinhalten Binär-Phasenumtastung (BSPK = binary phase shift keying), Quadraturphasenumtastung (QPSK = quarternary phase shift keying), Quadratur-Offset-Phasenumtastung (OQPSK = offset quarternary phase shift keying), m-wertige Phasenumtastung (m-PSK = m-ary phase shift keying) und Quadratur-Amplitudemodulation (QAM = quarternary amplitude modulation). Beispielhafte Kommunikationssysteme, die digitale Sendung verwenden, beinhalten Codemultiplexvielfachzugriff-(CDMA = code division multiple access)Kommunikationssysteme und Fernsehsysteme hoher Auflösung (HDTV = high definition television system). Die Verwendung von CDMA-Techniken in einem Vielfachzugriff-Kommunikationssystem wird in dem US-Patent Nummer 4,901,307 mit dem Titel "Spread Spectrum Multiple Access Communication System Using Satellite Or Terrestrial Repeaters" und in dem US-Patent Nummer 5,103,459 mit dem Titel "System And Method for Generating Waveforms In A CDMA Cellular Telephone System" offenbart, wobei beide Patente dem Rechtsnachfolger der vorliegenden Erfindung zugewiesen sind. Ein beispielhaftes HDTV-System wird in dem US-Patent mit der Nummer 5,452,104, dem US-Patent mit der Nummer 5,107,345 und dem US-Patent mit der Nummer 5,021,891, alle drei mit dem Titel "Adaptive Block Size Image Compression Method And System" und in dem US-Patent mit der Nummer 5,576,767 mit dem Titel "Interframe Video Encoding And Decoding System" offenbart, wobei alle vier Patente dem Rechtsnachfolger der vorliegenden Erfindung zugewiesen sind.

**[0003]** In dem CDMA-System kommuniziert eine Basisstation mit einer oder mehreren entfernten Stationen. Die Basisstation befindet sich typischerweise an einem festen Standort. Deshalb ist der Energieverbrauch, was die Konstruktion der Basisstation angeht, weniger wichtig. Die entfernten Stationen sind typischerweise Verbrauchereinheiten, die in großer Anzahl existieren. Deshalb sind wegen der Anzahl

von produzierten Einheiten Kosten und Verlässlichkeit wichtige Entwurfskriterien. Weiterhin ist in einigen Anwendungen wie zum Beispiel einem mobilen

CDMA-Kommunikationssystem der Energieverbrauch wegen der Tragbarkeit der entfernten Station

entscheidend. Gewöhnlich werden Kompromisse

zwischen Performance, Kosten und Energieverbrauch bei dem Entwurf der mobilen Stationen eingegangen.

**[0004]** Bei digitaler Sendung werden die digitalisierten Daten dazu verwendet, um einen sinusförmigen Träger zu modulieren, indem eines der oben aufgelisteten Formate verwendet wird. Die modulierte Wellenform wird weiterhin verarbeitet (z. B. gefiltert, verstärkt und aufwärtskonvertiert) und an die entfernte Station gesendet. Bei der entfernten Station wird das gesendete HF-Signal empfangen und von einem Empfänger demoduliert.

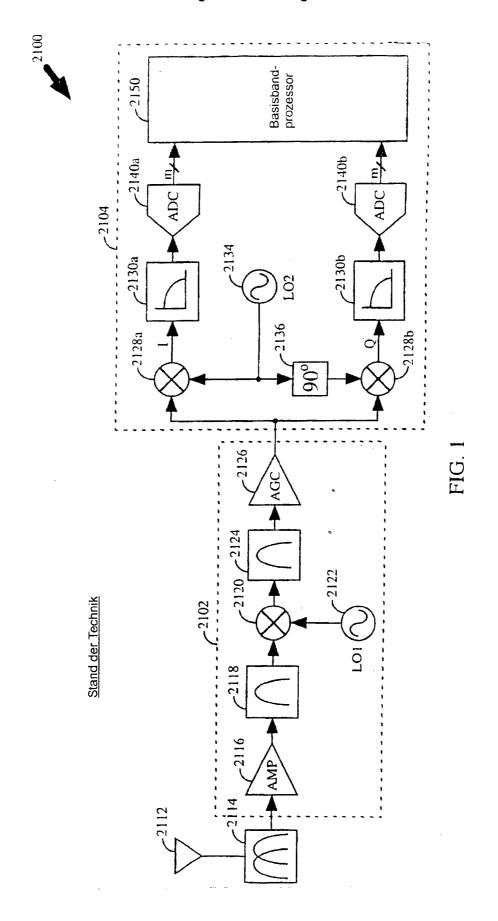

[0005] Ein Blockdiagramm eines beispielhaften Super-Heterodyne-Empfängers 2100 nach dem bisherigen Standes der Technik, die für Quadraturdemodulation eines QSPK-, OQPSK- und QAM-Signals verwendet wird, ist dargestellt in Fig. 1. Empfänger 2100 kann bei der Basisstation oder der entfernten Station verwendet werden. Innerhalb des Empfängers 2100 wird das gesendete HF-Signal von Antenne 2112 empfangen, durch Duplexer 2114 geleitet und an Frontend 2102 geliefert. Innerhalb des Frontends 2102 verstärkt Verstärker (AMP = amplifier) 2116 das Signal und liefert das Signal an Bandpassfilter 2118, der das Signal filtert, um ungewünschte Signale zu entfernen. In dieser Spezifikation umfassen ungewünschte Signale Rauschen, Spurensignale, ungewünschte Bilder, Interferenz und Störsender. Das gefilterte HF-Signal wird an den Mischer 2120 geliefert, der das Signal auf eine feste mittlere Frequenz (IF = intermediate frequency bzw. Zwischenfrequenz) mit der Sinuswellenform von lokalem Oszillator (101 = local oscillator 1) 2122 abwärtskonvertiert. Das IF-Signal von dem Mischer 2120 wird von dem Bandpassfilter 2124 gefiltert und durch den Verstärker 2126 mit automatischer Verstärkungssteuerung (AGC = automatic gain control) verstärkt, um die erforderliche Signalamplitude bei dem Eingang des Analog-zu-Digital-Wandlers (ADC = analog-to-digital- converter) 2140 zu erzeugen. Das verstärkungsgesteuerte Signal wird an den Demodulator 2104 geliefert. Innerhalb des Demodulators 2104 herabkonvertieren zwei Mischer 2128a und 2128b das Signal auf die Basisband-I und -Q-Signale jeweils mit der Sinuswellenform, die von dem lokalen Oszillator (LO2 = local oscillator 2) und Phasenverschieber 2136 vorgesehen wird. Die Basisband-I und -Q-Signale werden jeweils an die Tiefpassfilter 2130a und 2130b geliefert, die Optimalfilterung, Ablehnung eines benachbarten Kanals und/oder Anti-Alias-Filtern der Basisbandssignale vorsehen. Die gefilterten Signale werden an die ADCs 2140a und 2140b geliefert, die Signale abtasten, um die digitalisierten Basisbandabtastungen zu erzeugen. Die Abtastungen werden an den Basisbandprozessor **2150** für die weitere Verarbeitung geliefert (zum Beispiel Fehlererfassung, Fehlerkorrektur und Dekompression), um rekonstruierte Abschätzungen der gesendeten Daten zu erzeugen.

[0006] Die erste Frequenz-Abwärtskonvertierung mit dem Mischer 2120 gestattet es dem Empfänger 2100, Signale bei mehreren HF-Frequenzen auf eine feste IF-Frequenz abwärtszukonvertieren, wo mehr Signalverarbeitung durchgeführt werden kann. Die feste IF-Frequenz gestattet es dem Bandpassfilter 2124, in einem festen Bandpassfilter implementiert zu sein wie zum Beispiel ein Filter akustischer Oberflächenwellen (SAW = surface acoustic wave), um ungewünschte Signale aus den IF-Signal zu entfernen. Die Entfernung ungewünschter Signale ist wichtig, weil diese Signale in dem Signalband (z. B. das Band, in dem das Eingangssignal vorhanden ist) bei der zweiten Frequenz-Abwärtskonvertierungsstufe als Faltungskomponente auftreten können. Weiterhin können die ungewünschten Signale die Amplitude des Signals in mehreren aktiven Komponenten wie zum Beispiel den Verstärkern und Mischern signifikant vergrößern, was einen höheren Pegel von Intermodulationsprodukten durch die Nichtlinearität der aktiven Komponenten hervorrufen kann. Ungewünschte Signale und die Intermodulationsprodukte können eine Verschlechterung der Performance des Kommunikationssystems verursachen.

[0007] Der Quadratur-Demodulator nach dem bisherigen Stand der Technik besitzt mehrere schwerwiegende Nachteile. Erstens kann die notwendige Filterung durch den Bandpassfilter 2124 und/oder durch die Tiefpassfilter 2130 komplex sein. Diese Filter können ein flaches Passband, eine hohe Dämpfung in dem Stoppband und ein scharfes Roll-off in dem Übergangsband erfordern. Diese Filter werden mit analogen Schaltungen implementiert. Die Komponententoleranz von analogen Schaltungen ist schwierig aufrecht zu erhalten und kann zu Verzerrung der Frequenzantwort dieser Filter führen. Die Performance von Empfänger 2100 kann sich als Ergebnis der Verzerrung verschlechtern. Zweitens ist es wegen der Komponententoleranz in Phasen-Splitter 2136, den Mischern 2128, Tiefpassfilter 2130 und ADCs 2140 schwierig, die Quadraturbalance über viele Erzeugungseinheiten aufrecht zu erhalten. Jede Fehlabstimmung zwischen den beiden Signalpfaden resultiert in einer mangelnden Quadraturbalance und Verschlechterung der Performance des Empfängers 2100. Eine Pfad-Fehlabstimmung resultiert in dem Übersprechen des I-Signals in das Q-Signal und umgekehrt. Das Signal des Übersprechens verhält sich wie zusätzliches Rauschen in dem gewünschten Signal und resultiert in einer schlechten Erfassung des gewünschten Signals. Drittens besitzt die Empfängerarchitektur nach dem bisherigen Stand der Technik einen Gleichspannungs-Offset, weil die analogen Filter sich auf dem Basisband befinden. Und viertens können die ADCs **2140** eine Verschlechterung der Performance des Empfängers **2100** aufgrund mehrerer Gründe, die im folgenden beschrieben werden, verursachen.

[0008] In den meisten Demodulatoren werden ein oder mehrere ADCs benötigt, um eine analoge Wellenform in fortlaufender Zeit in diskrete Abtastungen bei Zeitintervallen regelmäßigen Abstandes zu konvertieren. Einige wichtige Performanceparameter eines ADCs beinhalten dynamischen Bereich, Linearität und Gleichspannungs-Offset. Jeder dieser Parameter kann die Performance des Kommunikationssystems beeinträchtigen. Der dynamische Bereich kann die Bit-Fehler-Raten-(BER = bit-error-rate)Performance des Empfängers beeinträchtigen, weil das Rauschen von dem ADC die Fähigkeit des ADCs verschlechtert, das Eingangssignal sauber zu erfassen. Die Linearität bezieht sich auf die Differenz zwischen einer tatsächlichen Transfer-Kurve (zum Beispiel digitale Ausgabe gegen analoge Eingabe) und der idealen Transfer-Kurve. Es ist schwieriger, eine gute Linearität zu erhalten, wenn sich die Anzahl von Bits in dem ADC vergrößert. Eine schlechte Linearität kann die Fehlererfassung/den Korrekturvorgang verschlechtern. Und ein Gleichspannungs-Offset kann die Performance der phasenverriegelten Schleife bzw. phase locked loop in dem Empfänger und des Fehlerkorrektur-Decodierers wie zum Beispiel dem Viterbi-Decodierer verschlechtern.

[0009] Nach dem bisherigen Stand der Technik werden Flash-ADCs oder ADCs mit sukzessiver Approximation verwendet, um die Basisbandssignale abzutasten. Innerhalb des Flash-ADCs wird das Eingangssignal durch eine resistive Leiter getrennt, um L-1 Vergleichsignale zu erzeugen, wobei L = 2<sup>m</sup> und m die Anzahl von Bits in dem ADC ist. Die Vergleichssignale werden mit L-1 Referenzspannungen verglichen, die durch eine zweite resistive Leiter erzeugt werden, von L-1 Komparatoren. Flash-ADCs sind sperrig und verbrauchen viel Energie, weil L-1 Komparatoren und 2 L Widerstände benötigt werden. Flash-ADCs können eine schlechte Linearität und schlechte Gleichspannungs-Offset-Charakteristiken besitzen, wenn die Widerstände in der resistiven Leiter nicht aufeinander abgestimmt sind. Flash-ADCs sind jedoch wegen ihrer hohen Betriebsgeschwindigkeit beliebt.

**[0010]** ADCs mit sukzessiver Approximation sind für Kommunikationssysteme ebenfalls beliebt. Diese ADCs minimieren die Komplexität, indem Approximationen des Eingangssignal über zwei oder mehrere Stufen durchgeführt werden. Diese ADCs können jedoch ebenfalls eine schlechte Linearität und schlechte Gleichspannungs-Offset-Charakteristiken ähnlich denen von Flash-ADCs zeigen. Somit sind

Flash-ADCs und ADCs mit sukzessiver Approximation keine idealen Kandidaten für die Verwendung in vielen Kommunikationsanwendungen.

[0011] Sigma-Delta-Analog-Zu-Digital-Wandler (ΣΔADCs) besitzen eine bessere Performance als Flash-ADCs und ADCs mit sukzessiver Approximation wegen der inhärenten Architektur des  $\Sigma\Delta$ ADC. Der ΣΔADC führt eine Analog-Zu-Digital-Konvertierung des Eingangssignals durch, indem sukzessive Ein-Bit-Approximationen des Eingangssignals bei einer Abtastungsfrequenz durchgeführt werden, die um ein Vielfaches größer ist als die Bandbreite des Eingangssignals. Die Ausgabe-Abtastungen umfassen das Eingangssignal und das Quantisierungsrauschen. Der ΣΔADC kann jedoch so entworfen werden, dass das Quantisierungsrauschen in dem Signalband (z. B. das Band, in dem das Signal vorhanden ist) auf eine Frequenz außerhalb des Bandes (oder geformt wie Rauschen) gedrückt wird, wo eine Filterung einfacher durchgeführt wird. Das Quantisierungsrauschen außerhalb des Bandes ist normalerweise keine zusätzliche Angelegenheit, weil eine Filterung typischerweise in Kommunikationsgeräten durchgeführt wird, um ungewünschte Signale wie zum Beispiel Störsender zu entfernen.

[0012] Der  $\Sigma\Delta$ ADC kann einen hohen dynamischem Bereich, gute Linearität und einen geringen Gleichspannungs-Versatz aufgrund des ΣΔADC liefern. Zum Beispiel kann ein hoher dynamischer Bereich erreicht werden, indem ein ausreichendes Überabtastungverhältnis (OSR = oversampling ratio) und die richtige Rauschformungsfiltercharakteristik ausgewählt wird. Für Bandpassabtastungen ist das Überabtastungverhältnis definiert als die Abtastungsfrequenz geteilt durch die zweiseitige Bandbreite der Eingabe. Zusätzlich kann wegen des einfachen Ein-Bit-Quantisierers innerhalb des ΣΔADCs eine gute Linearität erreicht werden. Für einen Bandpassabtastungs-ΣΔADC ist ein Gleichspannungs-Offset immer noch vorhanden, befindet sich aber entfernt von dem gewünschten Signal.

[0013] Weil ein hohes Überabtastungverhältnis für eine hohe Performance benötigt wird, wurden ΣΔADCs traditionell auf Anwendungen beschränkt, wo das Eingangssignal ein Signal geringer Bandbreite wie zum Beispiel bei Audio-Anwendungen ist. Mit dem Aufkommen von Hochgeschwindigkeitsanalogschaltungen können ΣΔADCs so implementiert werden, dass sie bei hoher Geschwindigkeit arbeiten. Hochgeschwindigkeits-Bandpassund -Implementierungen band-ΣΔADC-Entwürfe und werden im Detail offenbart in der anhängenden **US-Patent-Anmeldung** der Seriennummer mit 08/928,874 und dem Titel "Bandpass Sigma-Delta Analog-To-Digital-Converter", erteilt am 12.9.1997 und dem Rechtsnachfolger der vorliegenden Erfindung zugewiesen.

[0014] Weitere Aufmerksamkeit soll auf das Dokument WO 93/07679 A gelenkt werden, das sich auf einen NMR-Empfänger bezieht, der das Sigma-Delta-Modulationsverfahren verwendet, das in dem Analog-zu-Digital-Wandler-Gerät implementiert ist, um die Verwendung von analogen Anti-Aliasing-Filtern zu ermöglichen, die eine größere Bandbreite besitzen. Die analogen Filter erzeugen keine Phasenverzerrung des Signals in der Betriebsfrequenz und dies beseitigt die Notwendigkeit für eine Phasenkorrektur erster Ordnung durch den Digital-Signalprozessor. Der digitale Dezimierungsfilter, der innerhalb des Analog-zu-Digital-Wandler-Gerätes enthalten ist, verhält sich als ein digitaler Tiefpassfilter.

#### Zusammenfassung der Erfindung

**[0015]** Gemäß der vorliegenden Erfindung wird ein Empfänger zur Demodulierung eines HF-Signals gemäß Anspruch 1 und Anspruch 23 vorgesehen. Ausführungsbeispiele der vorliegenden Erfindung werden in den Unteransprüchen geltend gemacht.

[0016] Die vorliegende Erfindung ist ein neuartiger und verbesserter Empfänger, der einen Sigma-Delta-Analog-Zu-Digital-Wandler (ΣΔADC) umfasst. Die vorliegende Erfindung kann in einer von vier Konfigurationen verwendet werden, nämlich als ein Unterabtastungsbandpassempfänger, ein Unterabtastungsbasisbandempfänger, ein Nyquist-Abtastungsbandpassempfänger oder ein Nyquist-Abtastungsbasisbandempfänger. Für Unterabtastungs-ΣΔ-Empfänger ist die Abtastungsfrequenz kleiner als die doppelte Zentrums- bzw. Mittenfrequenz des Eingangssigden  $\Sigma\Delta ADC$ . Für Nyquist-Abtastungs-ΣΔ-Empfänger ist die Abtastungsfreguenz mindestens doppelt so groß wie die höchste Frequenz des Eingangssignals in den ΣΔADC. Für Basisband-ΣΔ-Empfänger ist die Zentrumsfrequenz des Ausgangssignals aus dem ΣΔADC ungefähr null oder ein Gleichspannungssignal. Für Bandpass-ΣΔ-Empfänger ist die Zentrumsfrequenz des Ausgangssignals aus dem ΣΔADC größer als null. Vorzugsweise wird die Zentrumsfrequenz des Eingangssignals in den ΣΔADC für Bandpass-ΣΔ-Empfänger so gewählt, dass die Zentrumsfrequenz des Ausgangssignals aus dem ΣΔADC ungefähr 0,25 f<sub>s</sub>. ist, wobei  $f_s$  die Abtastungsfrequenz des  $\Sigma\Delta$ ADC ist. Diese 0,25·f<sub>s</sub> – Zentrumsfrequenz vereinfacht die In-Phase- und Quadraturseparation und sieht die maximale Separation zwischen den Alias vor, ist aber kein notwendiges Erfordernis. Die Abtastungsfrequenz kann weiterhin basierend auf der Bandbreite des Eingangssignals ausgewählt werden, um den Entwurf der digitalen Schaltungen zu vereinfachen, die verwendet werden, um die Ausgabeabtastungen auf dem ΣΔADC zu verarbeiten. Weiterhin kann die Zentrumsfrequenz des Eingabesignals basierend auf der Abtastungsfrequenz und der Bandbreite des Eingangssignals ausgewählt werden.

[0017] Es ist eine Aufgabe der vorliegenden Erfindung, einen Unterabtastungs-ΣΔ-Empfänger zur Demodulierung von digitalen und analogen Modulationsformaten vorzusehen. Die Verwendung eines Unterabtastungs-ΣΔADCs innerhalb des Empfängers sieht viele Vorteile vor, einschließlich (1) der Eliminierung einer Abwärtskonvertierungsstufe analoger Frequenz, die vorgesehen wird durch die Unterabtastung des Eingabesignals und die Aliasing-Eigenschaft der Abtastung, (2) der Reduktion der analogen Filterungsanforderungen durch Taktung des ΣΔADCs bei einem hohen Überabtastungverhältnis und dem Entwurf des ΣΔADCs mit zusätzlichen Auflösungsbits, die dazu verwendet werden können, ungewünschte Signale zu handhaben, (3) der Verbesserung der Zuverlässigkeit und Erhöhung der Flexibilität durch die Verwendung von digitaler Demodulation für die Ausgabeabtastungen von dem  $\Sigma\Delta ADC$ , (4) der Eliminierung eines Quadratur-Ungleichgewichts durch den Entwurf der digitalen Schaltungen mit dem erforderlichen Quadratur-Gleichgewicht, (5) Verbesserung des dynamischen Bereichs, Linearität und Gleichspannungs-Offset durch die Verwendung eines ΣΔADCs und (6) der Reduktion des Energiever-

[0018] Es ist eine weitere Aufgabe der vorliegenden Erfindung, einen Nyquist-Abtastungs- $\Sigma\Delta$ -Empfänger für die Demodulation von digitalen und analogen Modulationsformaten vorzusehen. Die Verwendung des Nyquist-Abtastungs- $\Sigma\Delta$ ADCs sieht viele Vorteile wie zum Beispiel einen verbesserten dynamischem Bereich, erhöhte Linearität, reduzierten Gleichspannungs-Offset und einen minimalen Energieverbrauch vor.

#### Kurze Beschreibung der Zeichnungen

**[0019]** Die Merkmale, Aufgaben und Vorteile der vorliegenden Erfindung werden aus der folgenden detaillierten Beschreibung in Verbindung mit den Zeichnungen klar hervorgehen, in denen gleiche Bezugszeichen durchgehend gleiches identifizieren, wobei:

**[0020]** Fig. 1 ein Blockdiagramm eines beispielhaften Super-Heterodyne-Empfängers nach dem bisherigen Stand der Technik ist;

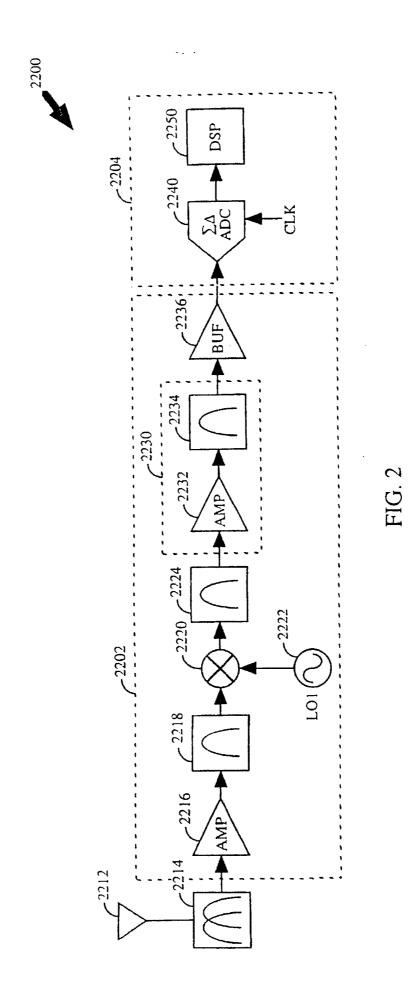

[0021] Fig. 2 ein Blockdiagramm eines beispielhaften Unterabtastungs- $\Sigma\Delta$ -Empfängers der vorliegenden Erfindung ist;

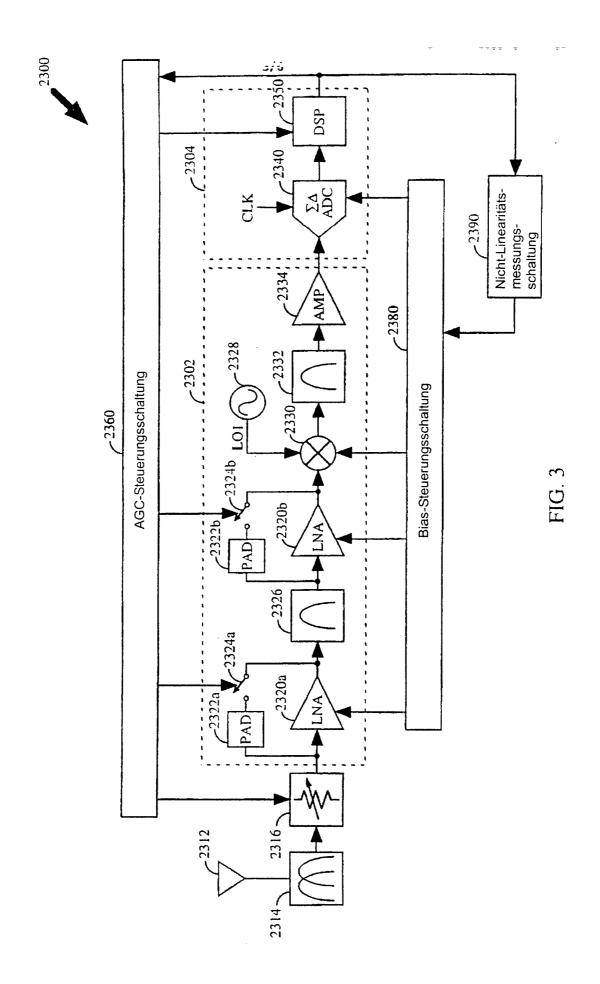

[0022] Fig. 3 ein Blockdiagramm eines beispielhaften alternativen Unterabtastungs- $\Sigma\Delta$ -Empfängers der vorliegenden Erfindung ist;

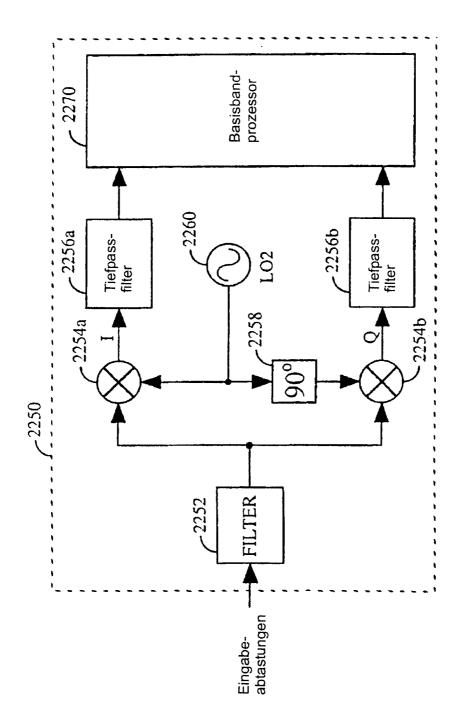

**[0023]** Fig. 4 ein Blockdiagramm eines beispielhaften digitalen Signalprozessors der vorliegenden Erfindung ist, der für Quadratur-Demodulation verwen-

det wird;

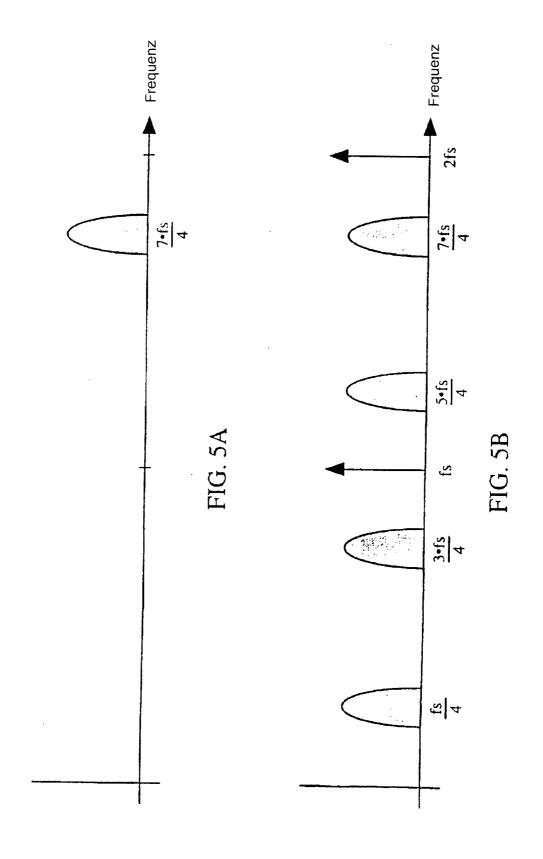

[0024] Fig. 5A–Fig. 5B jeweils Diagramme des Frequenzspektrums der IF-Eingabe- und des Frequenzspektrums der Ausgabe-Abtastungen von dem  $\Sigma\Delta$ ADC für einen Unterabtastungs-Bandpass- $\Sigma\Delta$  Empfänger sind und

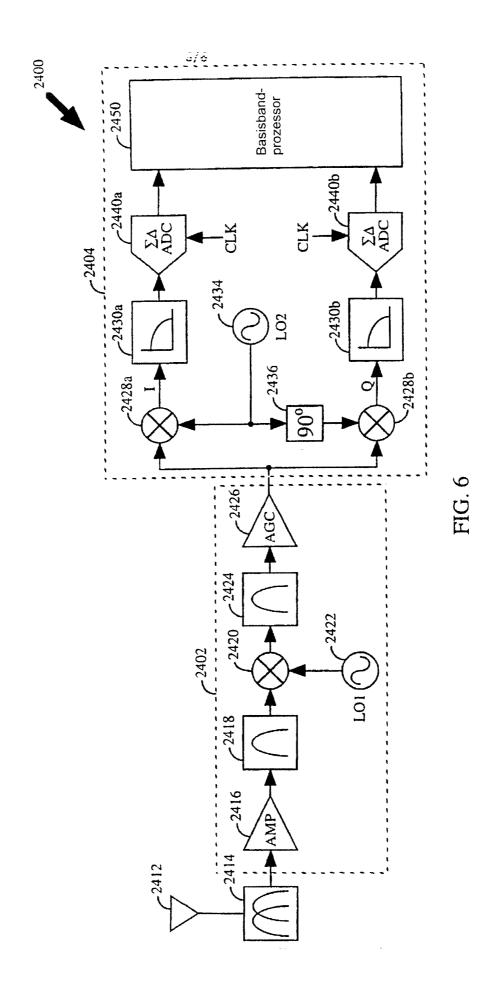

[0025] Fig. 6 ein Blockdiagramm für einen beispielhaften Nyquist-Abtastungs-Basisband-ΣΔ-Empfänger der vorliegenden Erfindung ist.

Detaillierte Beschreibung der bevorzugten Ausführungsbeispiele

[0026] Die vorliegende Erfindung verwendet die überlegene Performance eines Hochgeschwindigkeits-Sigma-Delta-Analog-Zu-Digital-Wandlers (ΣΔADC), um die erforderliche Analog-zu-Digital-Wandlung einer analogen Wellenform durchzuführen. Beispielhafte Anwendungen beinhalten CD-MA-Kommunikationssysteme und HDTV-Signale. In dem Unterabtastungs-ΣΔ-Empfänger-Ausführungsbeispiel der vorliegenden Erfindung ist das Eingangssignal bei einer mittleren Frequenz (if = intermediate frequency) anstatt eines Basisbandes zentriert. In dieser Spezifikation bezeichnet Unterabtastung, dass die Abtastungsfrequenz des ΣΔADCs kleiner als die doppelte Zentrumsfrequenz des Eingangssignals in den  $\Sigma\Delta$ ADC ist. Die Abtastung eines Signals, das sich bei einer IF-Frequenz befindet, erlaubt die Eliminierung einer Frequenz-Abwärtskonvertierungsstufe in dem Empfänger und vereinfacht damit den Hardware-Entwurf und verbessert die Zuverlässigkeit. Der Rauschformer innerhalb des ΣΔADCs kann so entworfen werden, dass das Quantisierungsrauschen um das Signalband außerhalb des Bandes (oder rauschgeformt) gedrückt wird, wo eine Filterung leichter durchgeführt wird. Für Unterabtastungs-ΣΔ-Empfänger kann der ΣΔADC ein Bandpass- $\Sigma\Delta$ ADC oder ein Basisband- $\Sigma\Delta$ ADC sein und zwar abhängig von der Anwendung und den Anforderungen. In dieser Spezifikation bezeichnet Basisband-Abtastung (oder Basisband-ΣΔADC), dass das Ausgangssignal von dem ΣΔADC bei ungefähr null oder Gleichspannung zentriert ist und Bandpass-Abtastung (oder Bandpass-ΣΔADC) bezeichnet, dass das Ausgangssignal aus dem ΣΔADC bei einem größeren Wert als Gleichspannung zentriert ist. Die Verwendung eines ΣΔADCs sieht viele Vorteile gegenüber konventionellen (zum Beispiel Flash-ADCs und ADCs mit sukzessiver Approximation) ADCs wie im folgenden beschrieben vor. In dem Nyquist-Abtastungs-ΣΔ-Empfänger-Ausführungsbeispiel der vorliegenden Erfindung kann sich das Eingabesignal bei dem Basisband oder einer IF-Frequenz befinden und ein Basisband oder ein Basisband-ΣΔADC kann jeweils dazu verwendet werden, das Eingangssignal abzutasten. In dieser Spezifikation bezeichnet Nyquist-Abtastung, dass die Abtastungsfrequenz des  $\Sigma\Delta$ ADCs mindestens bei der doppelten der höchsten Frequenz des Eingabesignals in den  $\Sigma\Delta$ ADC liegt.

[0027] Der  $\Sigma\Delta$ ADC tastet eine analoge Wellenform in kontinuierlicher Zeit ab, um diskrete Abtastungen bei Intervallen gleichmäßigen Abstandes vorzusehen. Der  $\Sigma\Delta$ ADC besitzt die ff. Transferfunktion:

$$Y(z) = STF(z) \cdot X(z) + NTF(z) \cdot E(z), \tag{1},$$

wobei Y(z) die Ausgabe aus dem ADC in dem z-Transformierungsraum, X(z) die Eingabe in den ADC, STF(z) die Signaltransferfunktion von der Eingabe zu der Ausgabe des ADC, E(z) das Quantisierungsrauschen und NTF(z) die Rausch-Transferfunktion von dem Quantisierer zu der Ausgabe des ADC ist. Somit umfasst das ADC-Ausgabe-Y(z) das Eingabesignal X(z), das von der Signaltransferfunktion STF(z) geformt wird, plus dem Quantisierungsrauschen E(z), das von der Rausch-Transferfunktion NTF(z) geformt wird. Um eine Verzerrung des Eingabesignals X(z) zu vermeiden, ist die Signaltransferfunktion STF(z) typischerweise so entworfen, dass sie innerhalb des gewünschten Grads an erforderlicher Genauigkeit frequenzunabhängig von dem vorliegenden Band ist. Zum Beispiel kann STF(z) eine Allpass-Funktion sein, die eine feste Verstärkung (A<sub>1</sub>) und Verzögerungselemente (z-1) wie zum Beispiel  $A_{1.7}^{-k}$  umfasst. Das Quantisierungsrauschen E(z) kann durch die Rausch-Transferfunktion NTF(z) so geformt werden, dass das Quantisierungsrauschen in dem Signalband außerhalb des Bandes gedrückt wird, wo eine Filterung einfacher durchgeführt wird. Die Charakteristik der Rausch-Transferfunktion NTF(z) wird basierend auf der Anwendung ausgewählt, für die der ADC verwendet wird und wird so entworfen, dass sie die erforderliche Performance vorsieht.

# I. Subsampling- bzw. Unterabtastungs- $\Sigma\Delta$ -Empfänger

[0028] In Fig. 2 wird ein beispielhafter Unterabtastungs-ΣΔ-Empfänger dargestellt. Empfänger 2200 kann verwendet werden, um BPSK, QPSK, OQPSK, QAM und andere digitale und analoge Modulationsformate zu demodulieren. Innerhalb des Empfängers 2200 wird das gesendete Signal durch Antenne 2212 empfangen, durch den Duplexer 2214 geleitet und an den Frontend 2202 geliefert. Innerhalb des Frontends **2202** verstärkt der Verstärker (AMP = amplifier) das Signal und liefert das verstärkte Signal an den Bandpassfilter 2218, der das Signal filtert, um ungewünschte Signale zu entfernen. In dem beispielhaften Ausführungsbeispiel ist der Bandpassfilter 2218 ein Filter akustischer Oberflächenwellen (SAW = surface acoustic wave), wobei die Implementierung hiervon nach dem Stand der Technik bekannt ist. Das gefilterte Signal wird an den Mischer 2220 geliefert, der das Signal mit der Sinuswellenform des lokalen Oszillators (LO1) **2222** abwärtskonvertiert. Das IF-Signal von dem Mischer **2220** wird an den Bandpassfilter **2224** geliefert, der das Signal weiterhin filtert. In dem beispielhaften Ausführungsbeispiel ist der Bandpassfilter **2224** ein anderer SAW-Filter, der ungewünschte Signale entfernt, die ein Aliasing in dem Band von Interesse verursachen, und den erforderlichen dynamischen Bereich reduziert, indem Störsender gefiltert werden.

[0029] In einigen Anwendungen wie zum Beispiel einem CDMA-Kommunikationssystem, das bei dem Personal-Communication-System-(PCS = personal communication system)Band arbeitet, wird das gefilterte Signal von dem Bandpassfilter 2224 an den IF-Prozessor 2230 geliefert. Innerhalb des IF-Prozessors 2230 wird das gefilterte Signal durch den Verstärker 2232 verstärkt und durch den Bandpassfilter 2234 gefiltert, um weiter ungewünschte Signale zu entfernen. Der Bandpassfilter 2234 ist beinhaltet, um eine weitere Anti-Alias-Filterung vorzusehen. Das gefilterte Signal wird an den Puffer (BUF = buffer) 2236 geliefert, die Verstärkung und/oder Pufferung des Signals vorsieht. In anderen Anwendungen, wie dem CDMA-Kommunikationssystem, das bei dem 900 MHz-Zellularband arbeitet, ist die Verstärkung und Filterung durch den IF-Prozessor 2230 nicht notwendig. In diesem Fall wird das Signal von dem Bandpassfilter 2224 direkt an den Puffer 2236 geliefert. Das gepufferte Signal wird an den Demodulator 2204 geliefert. Innerhalb des Demodulators 2204 tastet der ΣΔADC 2240 das gepufferte Signal bei einer hohen Abtastungsfrequenz ab, die durch das CLK-Signal bestimmt wird, und liefert die Abtastungen an den digitalen Signalprozessor (DSP = digital signal processor) 2250. Der digitale Signalprozessor 2052 wird im folgenden im Detail beschrieben.

[0030] Der Empfänger 2200 umfasst die grundlegenden Funktionalitäten, die von den meisten Empfängern benötigt werden. Die Anordnung der Verstärker 2216 und 2233, der Bandpassfilter 2218, 2224 und 2234 und des Mischers 2220 kann neu angeordnet werden, um die Performance des Empfängers 2200 für spezifische Anwendungen zu optimieren. Zum Beispiel kann der Bandpassfilter 2218 zwischen dem Duplexer 2214 und dem Verstärker 2216 eingesetzt werden, um ungewünschte Signale vor der ersten Verstärkerstufe herauszufiltern. Der Verstärker 2216 kann mit einem Verstärker mit geringem Rauschen (LNA = low noise amplifier) oder einen Verstärker mit automatischer Verstärkungssteuerung (AGC = automatic gain control) ausgetauscht werden, um die erforderliche Verstärkung und AGC-Steuerung vorzusehen. Zusätzliche Frequenz-Abwärtskonvertierungsstufen können ebenfalls innerhalb des Empfängers 2200 je nach Erfordernis hinzugefügt werden. Verschiedene Anordnungen der hier gezeigten Funktionalitäten sind denkbar und befinden sich innerhalb des Umfangs der vorliegenden Erfindung.

Weiterhin sind andere Anordnungen der hier gezeigten Funktionalitäten in Kombination mit anderen Empfänger-Funktionalitäten, die nach dem Stand der Technik bekannt sind, denkbar und befinden sich innerhalb des Umfangs der vorliegenden Erfindung.

[0031] Ein Blockdiagramm eines alternativen Unterabtastungs-ΣΔ-Empfängers der vorliegenden Erfindung wird in Fig. 3 dargestellt. Der Empfänger 2300 sieht die Vorteile des Unterabtastungs-ΣΔ-Empfängers 2200 zusätzlich zu den Vorteilen eines programmierbaren linearen Empfängers vor, wie offenbart in der anhängenden US-Patent-Anmeldung mit der Seriennummer 08/928,874. Innerhalb des Empfängers 2300 wird das gesendete HF-Signal von der Antenne 2312 empfangen, durch den Duplexer 2314 geleitet und an den Dämpfer 2316 geliefert. Der Dämpfer 2316 dämpft das HF-Signal, um ein Signal bei der erforderlichen Amplitude vorzusehen, und liefert das gedämpfte Signal an den Frontend 2302. Innerhalb des Frontends 2302 wird das gedämpfte Signal an Pad 2322a und an den Verstärker mit geringem Rauschen (LNA = low noise amplifier) 2320a geliefert. Der LNA 2320a verstärkt das HF-Signal und liefert das verstärkte Signal an den Bandpassfilter 2326. Das Pad 2322a sieht einen vorbestimmten Dämpfungspegel vor und ist mit dem Schalter 2324a in Reihe geschaltet. Der Schalter 2324a sieht eine Überbrückung um den LNA 2320a vor, wenn die Verstärkung des LNA 2320a nicht benötigt wird. Der Bandpassfilter 2326 filtert das Signal, um ungewünschte Signale zu entfernen, die Intermodulationsprodukte in den nachfolgenden Signalverarbeitungsstufen verursachen können. Das gefilterte Signal wird an Pad 2322b und an den Verstärker mit geringem Rauschen (LNA) 2320b geliefert. LNA 2023b verstärkt das gefilterte Signal und liefert das Signal an den Mischer 2330. Pad 2322b sieht einen vorbestimmten Dämpfungspegel vor und ist in Reihe mit dem Schalter 2324b geschaltet. Der Schalter 2324b sieht eine Überbrückung um den LNA 2320b vor, wenn die Verstärkung des LNA 2320b nicht benötigt wird. Der Mischer 2330 abwärtskonvertiert das Signal auf eine IF-Frequenz mit der Sinuswellenform von dem lokalen Oszillator (LO1) 2328. Das IF-Signal wird an den Bandpassfilter 2332 geliefert, der ungewünschte Signale und Produkte der Abwärtskonvertierung außerhalb des Bandes herausfiltert. Das gefilterte IF-Signal wird an den Verstärker (AMP) 2334 geliefert, der das Signal verstärkt. Das verstärkte IF-Signal wird an den Demodulator 2304 geliefert, der das Signal gemäß dem Modulationsformat demoduliert, das bei dem Sender verwendet wird. Der Demodulator 2304 ist identisch mit dem Demodulator 2204 (siehe Fig. 2), der im Folgenden beschrieben wird. In diesem und ähnlichen Empfängerentwürfen kann ein Teil der Verstärkungssteuerung (oder ein beliebiger AGC-Bereich) durch den Verstärker 2334 vorgesehen werden, der als ein Spannungssteuerungsverstärker (VGA = voltage control amplifier), digitaler Signalprozessor (DSP) **2350** innerhalb des Demodulators **2304**, die Referenzspannung innerhalb des  $\Sigma\Delta$ ADCs **2440** oder Kombinationen derer implementiert werden.

[0032] Für Anwendungen, für die Quadratur-Demodulation erforderlich ist, wie zum Beispiel QPSK, OQPSK und QAM wird ein Bandpass- $\Sigma\Delta$ ADC verwendet.

[0033] Der Bandpass-ΣΔADC kann auf die Weise entworfen und implementiert werden, die in der anhängenden US-Patentanmeldung mit der Seriennummer 08/928,874 beschrieben wird. Der Bandpass-ΣΔADC tastet das IF-Signal von dem Verstärker 2334 ab und liefert die IF-Abtastungen an den digitalen Signalprozessor 2250.

[0034] In Fig. 4 wird ein beispielhaftes Blockdiagramm eines digitalen Signalprozessors 2250 dargestellt, der für Quadratur-Demodulation verwendet wird. Die quantisierten IF-Abtastungen von ΣΔADC 2240 werden an einen Filter 2252 geliefert, der IF-Abtastungen filtert und dezimiert. Die gefilterten Abtastungen werden an die Multiplizierer 2254a und 2254b geliefert, die die gefilterten Abtastungen auf die Basisband-I- und -Q-Abtastungen mit den In-Phasenund Quadratur-Sinuswellenformen des lokalen Oszillators (LO2) 2560 und Phasenverschiebers 2258 jeweils abwärtskonvertieren. Der Phasenverschieber bzw. -umtaster 2258 sieht eine Phasenverschiebung bzw. Umtastung von 90° für die Quadratur-Sinuswellenform vor. Die Basisband-I- und -Q-Abtastungen werden jeweils an den Tiefpassfilter 2256a und 2256b geliefert, der die Abtastungen filtert, um die Iund Q-Daten vorzusehen. Die I- und Q-Daten werden an den Basisband-Prozessor 2270 geliefert, der eine zusätzliche Signalverarbeitung durchführt wie zum Beispiel Fehlererfassung/-Korrektur und Dekompression. In dem beispielhaften Ausführungsbeispiel sehen die Filter 2252 und/ oder die Tiefpassfilter 2256 ebenfalls die Skalierung der Abtastungen vor, um den digitalen Signalprozessor 2250 zu befähigen, Basisband-Daten bei unterschiedlicher Amplitude vorzusehen. Andere Implementierungen des digitalen Signalprozessors 2250 können entworfen werden, um Quadratur-Demodulation durchzuführen und befinden sich innerhalb des Umfangs der vorliegenden Erfindung.

[0035] Für Anwendungen, bei denen Quadratur-Demulation nicht benötigt wird, wie zum Beispiel BPSK und FM kann ein Basisband- $\Sigma\Delta$ ADC verwendet werden.

[0036] Der Basisband-ΣΔADC kann auf die Weise entworfen und implementiert werden, die in der anhängenden US-Patentanmeldung mit der Seriennummer 08/9,28,874 beschrieben wird. Für den Unterabtastungs-Basisband-ΣΔ-Empfänger befindet

sich das IF-Signal bei  $f_{\rm iF}=n\cdot f_{\rm s}$ , wobei n eine ganze Zahl größer als eins ist. Diese IF-Frequenz resultiert in einem Bild des gewünschten Signals bei Gleichspannung.

[0037] Unterabtastungs-ΣΔ-Empfänger die Empfänger 2200 und 2300 haben viele Vorteile gegenüber dem Super-Heterodyne-Empfänger 2100 nach dem bisherigen Stand der Technik. Erstens wird die zweite analoge Frequenz-Abwärtskonvertierungsstufe (z. B. die Mischer 2128 in Fig. 1) vollständurch die Verwendung der Unterabtastungs-ΣΔ-Empfänger eliminiert. Zweitens erfordern Unterabtastungs-ΣΔ-Empfänger wegen des hohen Überabtastungverhältnisses und hohen dynamischen Bereichs des ΣΔADC eine weniger strenge Anti-Alias-Analogfilterung. Diese Charakteristiken erlauben es, den Hauptteil der Filterungsfunktion in die nachfolgenden digitalen Filter zu verlagern. Drittens kann die digitale Signalverarbeitung nach dem ΣΔADC mit der erforderlichen Präzision und mit verbesserter Zuverlässigkeit der analogen Verarbeitung nach dem bisherigen Stand der Technik durchgeführt werden. Viertens entfernt die digitale Demodulation der IF-Abtastungen das Quadratur-Ungleichgewicht. das mit dem Super-Heterodyne-Empfänger 2100 nach dem bisherigen Stand der Technik üblich ist. Und fünftens kann der ΣΔADC der vorliegenden Erfindung einen verbesserten dynamischem Bereich, Linearität und Gleichspannungs-Offset gegenüber den konventionellen ADCs nach dem bisherigen Stand der Technik vorsehen. Diese Vorteile werden im Folgenden im Detail diskutiert.

[0038] Der erste Hauptvorteil der Unterabtastungs-ΣΔ-Empfänger der vorliegenden Erfindung ist die Eliminierung einer analogen Frequenz-Abwärtskonvertierungsstufe. Die Diagramme des Frequenzspektrums der IF-Eingabe und des Frequenzspektrums der IF-Abtastungen von dem ΣΔADC für einen Unterabtastungs-Bandpass-ΣΔ-Empfänger werden jeweils in Fig. 5A-Fig. 5B dargestellt. Für den Unterabtastungs-Bandpass-ΣΔ-Empfänger befindet sich das IF-Signal bei  $f_{IF} = 0.25 \cdot (2n + 1) \cdot f_s$ , wobei n eine ganze Zahl größer als eins und fs die Abtastungsfrequenz des ΣΔADC ist. In dem beispielhaften Ausführungsbeispiel ist n gleich drei und die Frequenz des IF-Signals in den ΣΔADC ist zentriert bei  $f_{IF}$  = 1.75· $f_s$ . Die Zentrumsfrequenz des IF-Signals kann durch die Änderung der Frequenz des lokalen Oszillators innerhalb des Frontends gesteuert werden (z. B. lokaler Oszillator 2222 in Fig. 2). Wenn das IF-Signal bei einer Unterabtastungsfrequenz abgetastet wird, erscheinen die IF-Signal-Alias und -Bilder des IF-Signals bei  $0.25 \cdot f_s$ ,  $0.75 \cdot f_s$ ,  $1.25 \cdot f_s$ ,  $1.75 \cdot f_s$  usw. (siehe Fig. 5B). Unterabtastung bezeichnet, dass die Abtastungsfrequenz kleiner als das Doppelte der höchsten Frequenz des IF-Signals ist. Indem die Aliasing-Eigenschaften der Abtastungen verwendet werden, wird das IF-Signal bei 1.75·f<sub>s</sub> in wirksamer Weise ohne die Verwendung einer analogen Abwärtskonvertierungsstufe auf  $0.25 \cdot f_s$  abwärtskonvertiert. Das Signal bei  $0.25 \cdot f_s$  wird anschließend durch den digitalen Signalprozessor verarbeitet.

[0039] Für Unterabtastungs-Bandpass-ΣΔ-Empfänger ist der ΣΔADC ein Bandpass-ΣΔ-ADC, der das Quantisierungsrauschen gemäß der anhängenden US-Patentanmeldung mit der Seriennummer 08/928,874 formt. Für einen Bandpass-ΣΔ-ADC wird das Quantisierungsrauschen um  $0.25 \cdot f_s$  auf Gleichspannung und  $0.50 \cdot f_s$  gedrückt, wo die Filterung des Quantisierungsrauschens einfacher durchzuführen ist. In dem beispielhaften Ausführungsbeispiel wird die Zentrumsfrequenz des IF-Signals so ausgewählt, dass ein Bild bei  $0.25 \cdot f_s$  erscheint, die Frequenz, wo das Quantisierungsrauschen minimal ist.

[0040] Für den Quadratur-Demodulator 2250, der in Fig. 4 gezeigt wird, werden die Abtastungen von dem Filter 2252 durch die Multiplizierer 2254a und 2254b jeweils mit den In-Phasen- und Quadratur-Sinuswellenformen des lokalen Oszillators 2260 und Phasen-Splitters 2258 auf das Basisband abwärtskonvertiert. Für eine saubere Auswahl der Freguenzen der Abtastungen von dem Filter 2252 für den ΣΔADC ist die Frequenz-Abwärtskonvertierungsstufe trivial. Die Abtastungen von dem ΣΔADC werden an den Filter 2252 geliefert, der die IF-Abtastungen filtert und um N dezimiert, um dezimierte Abtastungen bei der dezimierten Frequenz f<sub>d</sub> zu erzeugen. Wenn die dezimierte Frequenz f<sub>d</sub> so ausgewählt wird, dass sie 1/4 der Abtastungsfrequenz beträgt, also d = f<sub>s</sub>/4, die Quadratur-Abwärtskonvertierung durch die Multiplizierer **2254a** und **2254b** durchgeführt werden, indem die dezimierten Abtastungen von dem Filter 2252 jeweils mit den Sequenzen (1, 0, -1, 0, 1, 0, -1, ...) und (0, 1, 0, -1, 0, 1, 0, ...) multipliziert werden. Somit können die Multiplizierer 2254a und 2254b mit einfachen digitalen Schaltungen implementiert werden.

[0041] In dem beispielhaften Ausführungsbeispiel wird der Unterabtastungs-ΣΔ-Empfänger der vorliegenden Erfindung verwendet, um CDMA-Signale zu demodulieren, die eine zweiseitige Bandbreite von 1,2288 MHz besitzen. In dem beispielhaften Ausführungsbeispiel wird die dezimierte Frequenz f<sub>d</sub> so ausgewählt, dass sie Chip × 8 (9,83 MHz) und damit dem achtfachen der zweiseitigen Bandbreite des CD-MA-Signals entspricht, zur einfachen Implementierung der Quadratur-Abwärtskonvertierungsstufe und der nachfolgenden Signalverarbeitungsstufen. In dem beispielhaften Ausführungsbeispiel wird die Abtastungsfrequenz so ausgewählt, dass sie 66,6 MHz entspricht und dass die Zentrumsfrequenz des IF-Signals in den  $\Sigma\Delta$ ADC 116,5 MHz und damit  $f_{IF} = 1.75 \cdot f_{s}$ entspricht. Diese Frequenzen werden so ausgewählt, um minimale ungewünschte Signale und Intermodulationsprodukte in dem Signalband zu verursachen. Andere Abtastungs- und IF-Frequenzen können

ebenfalls verwendet werden und befinden sich innerhalb des Umfangs der vorliegenden Erfindung. Das Verhältnis der Abtastungsfrequenz durch die dezimierte Frequenz beträgt 6,77 (66,6 MHz/9,83 MHz), welches keine ganze Zahl ist. In dem beispielhaften Ausführungsbeispiel wird ein Datenraten-Konvertierer verwendet, um die IF-Abtastungen erneut bei f<sub>s</sub> in konvertierte Abtastungen bei einer konvertierten Frequenz f<sub>c</sub> abzutasten. Die konvertierte Frequenz f<sub>c</sub> wird so ausgewählt, dass sie einem ganzzahligen Vielfachen der dezimierten Frequenz entspricht und somit f<sub>c</sub> = M·f<sub>d</sub>. Der Datenraten-Konvertierer kann gemäß dem bisherigen Stand der Technik, wie zum Beispiel als ein linearer Interpolator oder ein quadratischer Interpolator wie im Detail in 08/928,874 beschrieben wird, implementiert werden. In einigen Anwendungen, wo der Frequenzplan eine Abtastung bei einer Abtastungsfrequenz erlaubt, die dem p-fachen der dezimierten Frequenz f<sub>d</sub> entspricht, wobei p eine ganze Zahl ist, wird der Datenraten-Konvertierung nicht benötigt.

[0042] Der zweite große Vorteil der Unterabtastungs-ΣΔ-Empfänger sind weniger strenge Anforderungen an die analogen Filter. Innerhalb des Frontend des Unterabtastungs-ΣΔ-Empfängers ist nur einfaches Anti-Alias-Filtern notwendig, um ungewünschte Signale aus dem Ausgangssignal von dem ersten Mischer (z. B. Mischer 2220) vor der Abtastung durch den ΣΔADC zu entfernen. Die anspruchsvollen analogen Optimalfilter, die in dem Empfänger 2100 benötigt werden, werden mit digitalen Filtern innerhalb des digitalen Signalprozessors implementiert.

[0043] Anspruchsvolle analoge Filter können in dem Empfänger 2100 auch benötigt werden, um ungewünschte Signale zu unterdrücken. Für eine CD-MA-Anwendung können sich ungewünschte Signale großer Amplitude (zum Beispiel einschließlich Störsender) sehr nahe bei der Bandkante des gewünschten Signals (zum Beispiel des CDMA-Signals) befinden. Die Störsender können eine weitaus größere Amplitude als das gewünschte Signale besitzen. Nach dem bisherigen Stand der Technik werden scharfe analoge Filter benötigt, um die Störsender auf eine kleine Amplitude zu drücken, so dass die ADCs nicht abgeschnitten werden, da ein Abschneiden der ADCs Intermodulationsprodukte verursacht, die das gewünschte Signal verschlechtern. Das ΣΔADC in der vorliegenden Erfindung kann mit zusätzlichen Auflösungsbits entworfen werden, die dazu verwendet werden können, die Störsendern ohne ein Abschneiden des ΣΔADCs zu quantisieren. Die zusätzlichen Bits befähigen den ΣΔADC, Störsender höherer Amplitude zu tolerieren, wobei dies die Anforderungen an die analogen Filter vor dem ΣΔADC lockert.

[0044] Der dritte große Vorteil des Unterabtas-

tungs-ΣΔ-Empfängers ist, dass die Quadratur-Demodulation der IF-Abtastungen von dem ΣΔADC mit der benötigten Präzision und mit verbesserter Zuverlässigkeit verglichen mit der analogen Quadratur-Demodulation nach dem bisherigen Stand der Technik durchgeführt werden kann. Bezüglich Fig. 4 können der Filter 2252 und die Tiefpassfilter 2256a und 2256b so entworfen werden, um die erforderliche Abstimmungsfilterung des Eingangssignals vorzusehen, die typischerweise durch einen Demodulator für eine optimale Performance erforderlich ist. Die Implementierung der Filter mit digitalen Filtern wie Filter mit finiter Impulsantwort (FIR = finite impulse response), Filter mit infiniter Impulsantwort (IIR = infinte impulse response) oder Polyphasen-Filter erlaubt eine höhere Performance und erhöhte Zuverlässigkeit. Die digitalen Filter können ebenfalls so entworfen werden, dass die erforderliche Präzision erreicht wird, während die Schaltungskomplexität minimiert wird. Digitale Filter können ebenfalls eine verbesserte Performance vorsehen, da die Frequenzantwort der digitalen Filter für alle erzeugten Einheiten identisch ist. Gleichheit ist für Empfänger wichtig, die in großer Menge hergestellt werden.

[0045] Digitale Demodulation bietet auch große Flexibilität und geringere Kosten. Die digitalen Filter können so entworfen werden, dass sie beliebige erforderliche Spezifikationen erfüllen (zum Beispiel jede beliebige erforderliche Frequenzantwort). Die digitalen Filter können ebenfalls mit der Flexibilität entworfen werden, um die optimale Frequenzantwort basierend auf den Erfordernissen der Anwendung vorzusehen. Zum Beispiel können die FIR-Filter mit Filter-Tap-Koeffizienten entworfen werden, die von einem Kontroller geladen werden können. Die Frequenzantwort der FIR-Filter kann dann dynamisch für verschiedene Betriebsmodi variiert werden. Zusätzlich können die digitalen Filter in Stufen entworfen werden und einige Stufen können überbrückt werden, wenn sie nicht benötigt werden, um den Energieverbrauch zu minimieren.

[0046] Digitale Quadratur-Demodulation kann mit digitalen Schaltungen implementiert werden, die eine oder mehrere integrierte Schaltungen (ICs = integrated circuits) integriert werden können, um die Komponentenanzahl zu minimieren, Kosten zu drücken und die Zuverlässigkeit zu verbessern. Zusätzlich können digitale Schaltungen einfach während der Herstellungsphase und/oder der Betriebsphase getestet werden. Nach dem bisherigen Stand der Technik wird Quadratur-Demodulation mit analogen Schaltungen implementiert. Schlechte Komponententoleranz in analogen Schaltungen kann darin resultieren, dass der Empfänger die erforderlichen Performance-Spezifikationen nicht erfüllt. Ebenfalls umfassen analoge Schaltungen viele Komponenten, die die Zuverlässigkeit des Empfängers verschlechtern können und die Kosten erhöhen. Zusätzlich müssen die analogen Schaltungen nach dem bisherigen Stand der Technik für jeden der Vielzahl von Standards neu entworfen werden, zum Beispiel um den IS-95-Standard, dem koreanischen Standard und den japanischen Standard zu erfüllen.

[0047] Der vierte große Vorteil des Unterabtastungs-ΣΔ-Empfängers ist die Eliminierung der Quadratur-Fehlanpassung. In der vorliegenden Erfindung wird die Quadratur-Unausgeglichenheit, die man in einem analogen Quadratur-Demodulator vorfindet, eliminiert, weil die Signalverarbeitung nach dem ΣΔADC digital durchgeführt wird. In dem beispielhaften Ausführungsbeispiel sind die Multiplizierer 2254 und die Tiefpassfilter 2256 so entworfen, dass sie identisch sind. Weiterhin werden jeweils die In-Phasen- und Quadratur-Sinuswellenformen von dem lokalen Oszillator 2260 und dem Phasenverschieber 2258 von verschiedenen Werten aus erzeugt (zum Beispiel 1, 0 oder –1), die mit demselben Taktsignal assoziiert sind und keinen Phasenfehler besitzen. Für den digitalen Quadratur-Demodulator werden die beiden Signalpfade aufeinander abgestimmt und zwar in exakter Quadratur zueinander.

[0048] In dem analogen Quadraturdemodulator nach dem bisherigen Stand der Technik (siehe Fig. 1) werden zwei Signalpfade verwendet, um die Basisband-I- und -Q-Signale zu verarbeiten. Jede Fehlanpassung der beiden Signalpfade (z. B. Fehler in dem Phasensplitter 2136 und/oder Fehlanpassung in den Mischern 2128, Tiefpassfilter 2130 und ADCs 2140) resultiert in einem Übersprechen des I-Signals in das Q-Signal und umgekehrt. Das Übersprechen resultiert in der Verschlechterung der BER-Performance des analogen Quadratur-Demodulators.

[0049] Der fünfte große Vorteil des Unterabtastungs- $\Sigma\Delta$ -Empfängers ist, dass der  $\Sigma\Delta$ ADC so entworfen werden kann, um den dynamischem Bereich, die Linearität und den Gleichspannungs-Offset gegenüber den konventionellen ADCs (z. B. Flash oder nachfolgende Approximation) nach dem bisherigen Stand der Technik zu verbessern. Das Formen des Rauschens des Quantisierungsrauschens durch den ΣΔADC sieht einen verbesserten dynamischen Bereich gegenüber konventionellen ADCs vor, weil der Betrag an Quantisierungsrauschen in dem Signal-Band reduziert wird. Für konventionelle ADCs ist das Quantisierungsrauschen über das Ausgabespektrum von Gleichspannung bis zur Abtastungsfrequenz weiß. Für den ΣΔADC ist das Quantisierungsrauschen in dem Signalband durch einen sauberen Entwurf des Rauschformers innerhalb des ΣΔADC minimal. Der Rauschformer kann so entworfen werden, dass er die Charakteristika des IF-Signals und die Performance-Anforderungen erfüllt.

[0050] Der verbesserte dynamische Bereich, den der  $\Sigma\Delta$ ADC bietet, resultiert auch aus der hohen

Überabtastung des Eingabesignals. Für einen Bandpass-ΣΔADC ist das Überabtastungverhältnis definiert als die Abtastungsfrequenz geteilt durch die doppelte beidseitige Bandbreite des Eingabesignals und damit OSR =  $f_s/2f_{bw}$ . Die Ausgabe des  $\Sigma\Delta$ ADC kann 1-bit oder m-bit sein, abhängig davon, ob eine einschleifige Architektur oder eine MASH-(Multi-stAge noise SHaper) Architektur verwendet wird und ob ein Einzel-Bit- oder Mehrfach-Bit-Quantisierer verwendet wird. Die Abtastungsfrequenz wird so ausgewählt, dass sie viel größer ist als die Signalbandbreite. Deshalb ist das Quantisierungsrauschen über ein weiteres Spektrum von Gleichspannung bis zur Abtastungsfrequenz gespreizt. Anschließende Filterung und Dezimierung der Abtastungen von dem ΣΔADC entfernt Rauschen außerhalb des Bandes, während das gewünschte Signal erhalten bleibt, wodurch der dynamische Bereich verbessert wird. Ein exemplarischer ΣΔADC-Entwurf, der einen dynamischem Bereich von 12 Bits vorsieht, ist im Detail in der anhängenden US-Patentanmeldung mit der Seriennummer 08/928,874 offenbart.

[0051] In dem beispielhaften Ausführungsbeispiel kann der ΣΔADC 12 oder mehr Auflösungsbits besitzen. Die Auflösung kann durch geeignete Auswahl des Überabtastungverhältnisses, des Rauschformers und der Ordnung des ΣΔADC entworfen werden. Das IF-Signal in den ΣΔADC umfasst typischerweise das gewünschte Signale plus ungewünschte Signale, die Störsender beinhalten können. Die Amplitude der Störsender kann viel größer als die Amplitude des gewünschten Signals sein. Um ein Abschneiden der ADC-Eingabe zu verhindern, was In-Band-Intermodulationsprodukte erzeugen kann, wird das IF-Signal so skaliert, dass es in den gesamten Bereich der Eingabe des ADCs passt. Da die Amplitude der Störsender zunimmt, wird aus dem gewünschten Signal ein kleinerer Prozentsatz des Eingabe-IF-Signals. Mehr Auflösungsbits werden von dem ADC benötigt, um das gewünschte Signal passend zu quantisieren.

[0052] In dem analogen Quadratur-Demodulator nach dem bisherigen Stand der Technik wird die Amplitude der Störsender minimiert, indem das analoge Signal mit komplexen Filtern gefiltert wird, bevor es von den ADCs abgetastet wird. Da die Störsender sich nahe bei dem Signalband befinden (z. B. 900 kHz entfernt von der Zentrumsfrequenz des CD-MA-Signals), werden scharfe Roll-off-Filter wie zum Beispiel SAW-Filter und elliptische Filter hoher Ordnung benötigt, um die Amplitude der Störsender zu minimieren. Diese scharfen Roll-off-Filter können im Entwurf komplex, schwierig herzustellen und kostspielig sein.

[0053] Die zusätzliche Anzahl von Auflösungsbits, die von dem  $\Sigma\Delta$ ADC der vorliegenden Erfindung vorgesehen werden, entspricht einem höheren dynami-

#### DE 698 39 192 T2 2009.02.26

schem Bereich und gestattet Störsender mit größerer Amplitude in dem IF-Signal ohne die Verschlechterung des gewünschten Signals. Die höhere Auflösung erlaubt dem  $\Sigma\Delta$ ADC das gewünschte Signale sauber zu Quantisierern, sogar wenn es nur ein kleiner Bruchteil des Eingabe-IF-Signals ist. In dem beispielhaften Ausführungsbeispiel werden nur vier Auflösungsbits für eine saubere Demodulation des gewünschten Signals benötigt. Wird ein 12-Bit- $\Sigma\Delta$ ADC verwendet, können die acht verbleibenden Bits dazu verwendet werden, Störsender zu behandeln und/oder Verstärkungssteuerung vorzusehen.

[0054] Der ΣΔADC der vorliegenden Erfindung sieht ebenfalls eine verbesserte Linearität und Gleichspannungs-Offset-Charakteristik gegenüber konventionellen ADCs nach dem bisherigen Stand der Technik vor. Für den Flash-ADC nach dem bisherigen Stand der Technik ist die Linearität abhängig von der Abstimmung der Widerstände in den zwei resistiven Leitern, die verwendet werden, um das Eingangssignal und die Referenzspannung wie oben beschrieben zu teilen. Die Anzahl der Widerstände in einer Leiter ist 2<sup>m</sup> wobei m die Anzahl der Bits in dem ADC ist. Wenn m ansteigt, ist es wegen der Anzahl der Widerstände, die abgestimmt werden müssen, schwieriger, die die Linearität aufrechtzuerhalten. Im Gegensatz dazu ist die Linearität für den ΣΔADC einfacher erreichbar, weil ein Einzel-Bit-Quantisierer verwendet werden kann. Solange die hohen und niedrigen Rückkopplungsspannungen innerhalb des ΣΔADC bei einem konstanten Pegel gehalten werden, bleibt die Linearität erhalten.

[0055] Nichtlinearität kann die Performance des Empfängers verschlechtern wie zum Beispiel die Bit-Fehler-Rate (BER = bit-error-rate) oder die Rahmen-Fehler-Rate (FER = frame-error-rate). Nichtlinearität kann ebenfalls die Performance der Vielzahl von Schleifen innerhalb des Empfängers verschlechtern wie zum Beispiel die Trägerverfolgungsschleife bzw. carrier-tracking loop und die Bit-Timing-Schleife bzw bit-timing loop. Die Trägerverfolgungsschleife verfolgt die Frequenz/Phase des Eingangs-HF-Signals und die Bit-Timing-Schleife verfolgt die Symbolrate des Eingangssignals. Nichtlinearität kann ebenfalls die Messung des Signalpegels beeinträchtigen, der in der Schaltung mit automatischer Verstärkungssteuerung (AGC = automatic gain control) und der Vorspannungssteuerungschaltung bzw. biss control circuit verwendet wird, die verwendet werden, um die Performance des eingabebezogenen Intermodulationsprodukts dritter Ordnung (IIP3 = input-referred third order intermodulation product) zu verbessern.

[0056] Der  $\Sigma\Delta$ ADC besitzt ebenfalls eine verbesserte Gleichspannungs-Offsetcharakteristik gegenüber dem konventionellen ADC nach dem bisherigen Stand der Technik. Für den Basisband- $\Sigma\Delta$ ADC wird der Gleichspannungs-Offset verbessert, weil die ana-

logen Filter nach dem bisherigen Stand der Technik, die die Gleichspannung verstärken, nicht mehr in der vorliegenden Erfindung vorhanden sind. Für den Bandpass-ΣΔADC ist der Gleichspannungs-Offset nicht von Belang, weil diese spektrale Komponente sich außerhalb des Bandes befindet. Jeder beliebige Gleichspannungs-Offset kann herausgefiltert werden und trägt wenig zu den Ausgabe-Abtastungen bei.

[0057] Gleichspannungs-Offset ist besonders wichtig für ein digitales Kommunikationssystem, weil dieser Parameter die BER-Performance und die Performance der Schleifen mit fester Phase innerhalb des Empfängers verschlechtern kann. Der Gleichspannungs-Offset verzerrt die Quantisierung ADC-Ausgabe-Abtastungen und kann in einer fehlerhaften Erfassung des Eingabesignals resultieren. Ein Gleichspannungs-Offset kann ebenfalls die Performance des Viterbi-Dekodierungsvorgangs verschlechtern, der gewöhnlich in digitalen Kommunikationssystemen verwendet wird. Zusätzlich kann der Gleichspannungs-Offset die Performance der Trägerverfolgungsschleifen und der Bit-Timing-Schleifen beeinträchtigen. Ein Gleichspannungs-Offset führt zu einer Gleichvorspannung in den Schleifen, was die Aquisitions-Performance der Schleifen verschlechtert. Die Gleichvorspannung belastet ebenfalls die Schleifen, wobei die Verfolgungs-Performance der Schleifen verschlechtert wird. In vielen Kommunikationssystemen ist der Gleichspannungs-Offset ein wichtiger Entwurfs- und Herstellungsgesichtspunkt, der mit einer oder einer Kombination von Maßnahmen angegangen wird. Der Gleichspannungs-Offset von jedem ADC kann vorsichtig bis zu bestimmten Grenzen überwacht werden. Ebenfalls können spezielle Ausgleichschleifen entworfen werden, um den Gleichspannungs-Offset jedes ADCs abzuschätzen und auszulesen.

[0058] Der Entwurf des  $\Sigma\Delta$ ADCs wie in der anhängenden US-Patentanmeldung mit der Seriennummer 08/928,874 beschrieben, liefert zusätzliche Vorteile, wenn er innerhalb des Empfängers der vorliegenden Erfindung verwendet wird. Der  $\Sigma\Delta$ ADC kann während des Betriebs neu konfiguriert werden, so dass Teile des  $\Sigma\Delta$ ADC ausgeschaltet werden können, um Energie zu sparen, wenn eine hohe Performance nicht benötigt wird. Zum Beispiel kann der  $\Sigma\Delta$ ADC mit einer Zweischleifen-MASH-Architektur und eine Schleife kann AUS-geschaltet werden, wenn ein hoher dynamischer Bereich nicht benötigt wird.

[0059] Ein weiterer Vorteil des  $\Sigma\Delta ADC$  ist die Vereinfachung der Schnittstelle zwischen dem  $\Sigma\Delta ADC$  und anderen Schaltkreisen innerhalb des Empfängers.

[0060] Der  $\Sigma\Delta$ ADC gibt bei jedem Abtastungs-Taktzyklus nur einen oder wenige Bits aus, auch wenn der  $\Sigma\Delta$ ADC eventuell mehr Auflösungsbits besitzt.

Somit besitzt der  $\Sigma\Delta ADC$  wenige Eingabe/Ausgabe-(I/O)Pins beziehungsweise Kontakte. Weiterhin wird nur ein  $\Sigma\Delta ADC$  für Unterabtastungs- $\Sigma\Delta$ -Empfänger benötigt. Weniger ADC- und I/O-Pins vereinfachen die Signalweitergabe zwischen dem  $\Sigma\Delta ADC$  und anderen Schaltungen innerhalb des Empfängers. Für konventionelle ADCs wird typischerweise ein I/O-Pin für jedes Auflösungsbit benötigt. Weiterhin werden zwei konventionelle ADCs für einen Quadratur-Demodulator, wie in Fig. 1 gezeigt, benötigt. Die große Anzahl von ADCs und I/O-Pins kann das Layout und die Signalweitergabe schwieriger gestalten.

[0061] Die Empfänger 2200 und 2300 sind zwei beispielhafte Empfängerarchitekturen, die Unterabtastungs- $\Sigma\Delta$ -Analog-Zu-Digital-Konvertierung des IF-Signals unterstützen. Andere Empfängerarchitekturen können entworfen werden, um die notwendige Frontend-Verarbeitung basierend auf den Erfordernissen der Anwendung, für die der Empfänger verwendet wird, vorzusehen. Weiterhin können andere digitale Signalprozessoren entworfen werden, um die Demodulation der IF-Abtastungen durchzuführen. Somit befinden sich verschiedene Empfängerarchitekturen, die einen Unterabtastungs- $\Sigma\Delta$ ADC umfassen, innerhalb des Umfangs der vorliegenden Erfindung.

#### II. Nyquist-Abtastungs-ΣΔ-Empfänger

[0062] In dem ersten Ausführungsbeispiel der vorliegenden Erfindung umfasst der Empfänger einen Unterabtastungs-ΣΔADC. Diese Architektur sieht wie oben beschrieben zahlreiche Vorteile vor. In dem zweiten Ausführungsbeispiel der vorliegenden Erfindung umfasst der Empfänger einen Nyquist-Abtastungs-ΣΔADC. Diese Architektur sieht viele der Vorteile des ΣΔADC vor, im besonderen den hohen dynamischem Bereich, verbesserte Linearität, niedrigen Gleichspannungs-Offset und minimalen Energieverbrauch. Für einen Nyquist-Abtastungs-ADC beträgt die Abtastungsfrequenz mindestens das Doppelte der höchsten Frequenz des Eingabesignals in den ADC, so dass Aliasing verhindert anstatt verwendet wird.

[0063] Ein Blockdiagramm eines beispielhaften Nyquist-Abtastungs-ΣΔ-Empfängers, für den Quadratur-Demodulation verwendet wird, wird in Fig. 6 dargestellt. Der Empfänger 2400 kann dazu verwendet werden, BPSK, QPSK, OQPSK, QAM und digitale und analoge Modulationsformate zu demodulieren. Innerhalb des Empfängers 2400 wird das gesendete Signal von der Antenne 2412 empfangen durch den Duplexer 2414 geleitet und an das Frontend 2402 geliefert. Innerhalb des Frontends 2402 verstärkt der Verstärker (AMP = amplifier) 2416 das Signal und liefert das verstärkte Signal an den Bandpassfilter 2418, der das Signal filtert, um ungewünschte Signale zu entfernen. In dem beispielhaften Ausführungs-

beispiel ist der Bandpassfilter **2418** ein Filter mit akustischen Oberflächenwellen (SAW = surface acoustic wave). Das gefilterte Signal wird an den Mischer **2420** geliefert, der das Signal mit der Sinuswellenform von dem lokalen Oszillator (LO1) **2422** abwärtskonvertiert. Das IF-Signal von dem Mischer **2420** wird von dem Bandpassfilter **2424** gefiltert und von dem Verstärker mit automatischer Verstärkungssteuerung (AGC = automatic gain control) **2426** verstärkt, um die erforderliche Signalamplitude an dem Ausgang der  $\Sigma\Delta$ ADCs **2440** zu erzeugen. In dem beispielhaften Ausführungsbeispiel ist der Bandpassfilter **2424** ebenfalls ein SAW-Filter. Das AGC-verstärkte Signal wird an den Demodulator **2404** geliefert.

[0064] Der Demodulator 2404 sieht eine Quadratur-Demodulation vor, die Nyquist-Abtastungs-Basisband-ΣΔADCs verwendet. Innerhalb des Demodulators 2404 abwärtskonvertieren zwei Mischer 2428a und 2428b das Signal auf die Basisband-I- und -Q-Signale mit der Sinuswellenform, die jeweils von dem lokalen Oszillator (LO2) 2434 und dem Phasenverschieber 2436 vorgesehen wird. Die Basisband-Iund -Q-Signale werden jeweils an die Tiefpassfilter 2430a und 2430b geliefert, die eine Abstimmungsfilterung und/oder Anti-Alias-Filterung der Basisbandssignale vorsehen. Die gefilterten Signale werden an die ΣΔADCs 2440a und 2440b geliefert, die die Signale abtasten, um digitalisierte Basisband-Abtastungen zu erzeugen. Die Abtastungen werden an den Basisbandprozessor 2450 für die weitere Verarbeitung (zum Beispiel Fehlererfassung und/oder -korrektur, Dekompression) geliefert.

[0065] In dem beispielhaften Ausführungsbeispiel sind die ΣΔADCs 2440 Nyquist-Abtastungs-Basisband-ΣΔADCs, die in der Weise implementiert werden können, wie sie in der anhängenden US-Patentanmeldung mit der Seriennummer 08/928,874 offenbart wird. Der Basisband-ΣΔADC bewegt das Quantisierungsrauschen um die Gleichspannung zu einer höheren Frequenz, wo eine Filterung einfacher durchgeführt werden kann. Der Nyquist-Abtastungs- $\Sigma\Delta$ -Empfänger kann so entworfen werden, dass digitale Quadratur-Demodulation ähnlich den Unterabtastungs-ΣΔ-Empfängern 2200 und 2300 durchgeführt wird. In diesem Ausführungsbeispiel sind die Unterabtastungs- $\Sigma\Delta$ -Empfänger 2200 und 2300 so entworfen, dass sich die Zentrumsfrequenz des IF-Signals in den Bandpass-ΣΔADC bei einer IF-Frequenz befindet. Vorzugsweise wird die IF-Frequenz als 0.25·fs ausgewählt. Diese IF-Frequenz kann erhalten werden, indem die Frequenz des ersten lokalen Oszillators (zum Beispiel LO1 2222) angepasst wird oder durch eine zweite Frequenz-Abwärtskonvertierungsstufe, die zwischen die erste Frequenz-Abwärtskonvertierungsstufe (z. B. Mischer **2200**) und den Basisband- $\Sigma\Delta$ ADC angeordnet ist.

[0066] Die obige Beschreibung der bevorzugten

#### DE 698 39 192 T2 2009.02.26

Ausführungsbeispiele wird vorgesehen, um jeden Fachmann in die Lage zu versetzen, die vorliegende Erfindung zu verstehen und zu verwenden. Die zahlreichen Modifikationen dieser Ausführungsbeispiele sind für den Fachmann vollständig offensichtlich und die darin enthaltenen grundlegenden Prinzipien können ohne die Verwendung erfinderischer Fähigkeiten auf andere Ausführungsbeispiele angewandt werden.

#### Patentansprüche

1. Ein Empfänger (2300) zum Demodulieren eines HF-Signals, der Folgendes aufweist:

Ein Front-End (2302) zum Empfangen des HF-Signals und zum Herunterkonvertieren des HF-Signals in ein Zwischen- bzw. IF-Signal (IF = intermediate frequency bzw. Zwischenfrequenz), wobei das IF-Signal eine Mittenfrequenz und eine zweiseitige Bandbreite hat;

wenigstens ein  $\Sigma\Delta$ -ADC (**2340**) zum Empfangen eines Signals von dem Front-End (**2302**) und zum Abtasten des Signals, um Samples bzw. Abtastungen zu erzeugen, wobei der  $\Sigma\Delta$ -ADC (**2340**) mit einer Abtastfrequenz getaktet wird:

ein Digital-Signal-Prozessor (2350), der mit dem  $\Sigma\Delta$ -ADC (2340) verbunden ist, und zwar zum Empfangen der Samples und zum Demodulieren der Samples gemäß einem Modulationsformat, das benutzt wird, um das HF-Signal zu erzeugen;

wobei der  $\Sigma\Delta$ -ADC (**2340**) mehrere Schleifen aufweist, wobei jede Schleife ein- oder ausgeschaltet werden kann, abhängig von einer spezifizierten Anforderung.

- 2. Empfänger (**2300**) gemäß Anspruch 1, wobei der  $\Sigma\Delta$ -ADC (**2340**) ein Unterabtastungsbandpass- $\Sigma\Delta$ -ADC ist.

- 3. Empfänger (2300) gemäß Anspruch 1, wobei der  $\Sigma\Delta$ -ADC (2340) ein Unterabtastungsbasisband- $\Sigma\Delta$ -ADC ist.

- 4. Empfänger (2300) gemäß Anspruch 1, wobei der  $\Sigma\Delta$ -ADC (2340) ein Nyquist-Abtastungsbandpass- $\Sigma\Delta$ -ADC ist.

- 5. Empfänger (2300) gemäß Anspruch 1, wobei der  $\Sigma\Delta$ -ADC (2340) ein Nyquist-Abtastungsbasisband- $\Sigma\Delta$ -ADC ist.

- 6. Empfänger (**2300**) gemäß Anspruch 2, wobei die Mittenfrequenz des IF-Signals gleich (0,25·(2n + 1))-mal die Abtastfrequenz ist, wobei n ein ganze Zahl ist, die größer als 1 ist.

- 7. Empfänger (2300) gemäß Anspruch 6, wobei n gleich zwei ist.

- 8. Empfänger (2300) gemäß Anspruch 2, wobei

- die Mittenfrequenz des IF-Signals gleich 0,25·(2n)-mal die Abtastfrequenz ist, wobei n eine ganze Zahl größer als 1 ist.

- 9. Empfänger (2300) gemäß Anspruch 8, wobei n gleich zwei ist.

- 10. Empfänger (2300) gemäß Anspruch 2, wobei die Abtastfrequenz ausgewählt wird, basierend auf der zweiseitigen Bandbreite des IF-Signals.

- 11. Empfänger (**2300**) gemäß Anspruch 2, wobei das IF-Signal ein CDMA-Signal aufweist.

- 12. Empfänger (**2300**) gemäß Anspruch 11, wobei die Mittenfrequenz des IF-Signals bei 116,5 MHz liegt.

- 13. Empfänger (**2300**) gemäß Anspruch 12, wobei die Abtastfrequenz 66,6 MHz ist.

- 14. Empfänger (2300) gemäß Anspruch 1, wobei der digitale Signalprozessor (2350) Folgendes aufweist:

ein digitales Filter zum Empfangen der IF-Samples und zum Vorsehen von gefilterten Samples, wobei das digitale Filter die IF-Samples mit einer Frequenzantwort filtert und die gefilterten Samples durch ein Dezimierungsverhältnis dezimiert.

- 15. Empfänger (**2300**) gemäß Anspruch 14, wobei die Frequenzantwort des digitalen Filters angepasst werden kann, und zwar basierend auf einen Betriebsmodus des Empfängers.

- 16. Empfänger (2300) gemäß Anspruch 14, wobei die Abtastfrequenz ausgewählt wird, basierend auf dem Dezimierungsverhältnis des digitalen Filters und der zweiseitigen Bandbreite des IF-Signals.

- 17. Empfänger (2300) gemäß Anspruch 1, wobei der  $\Sigma\Delta$ -ADC (2340) vier oder mehr Bits an Auflösung vorsieht.

- 18. Empfänger (2300) gemäß Anspruch 1, wobei der  $\Sigma\Delta$ -ADC (2340) bei einem Überabtastungsverhältnis von 16 oder größer getaktet wird.

- 19. Empfänger (2300) gemäß Anspruch 1, wobei der  $\Sigma\Delta$ -ADC (2340) ein einschleifiger  $\Sigma\Delta$ -ADC ist.

- 20. Empfänger (2300) gemäß Anspruch 1, wobei der  $\Sigma\Delta$ -ADC (2340) ein MASH- $\Sigma\Delta$ -ADC ist.

- 21. Empfänger (**2300**) gemäß Anspruch 20, wobei der MASH- $\Sigma\Delta$ -ADC ein MASH-4-4- $\Sigma\Delta$ -ADC ist.

- 22. Empfänger (**2400**) gemäß Anspruch 1, der weiterhin Folgendes aufweist:

Einen Quadratur-Demodulator (2404), verbunden mit

dem Front-End (**2402**) zum Empfangen des IF-Signals und zum Herunterkonvertieren des IF-Signals in Basisband-I- und -Q-Signale;

wobei der wenigstens eine  $\Sigma\Delta$ -ADC zwei  $\Sigma\Delta$ -ADCs (2440a, 2440b) verbunden mit dem Quadratur-Demodulator (2404) aufweist, wobei ein  $\Sigma\Delta$ -ADC (2440a) zum Empfangen des Basisband-I-Signals und ein  $\Sigma\Delta$ -ADC (2440b) zum Empfangen des Basisband-Q-Signals dient, wobei die  $\Sigma\Delta$ -ADCs (2440a, 2440b) die Basisband-I- und -Q-Signale abtasten, um Basisband-Samples zu erzeugen.

- 23. Empfänger (**2400**) gemäß Anspruch 22, wobei die  $\Sigma\Delta$ -ADCs Nyquist-Abtastungs-Basisband- $\Sigma\Delta$ -ADCs sind.

- 24. Empfänger (**2400**) gemäß Anspruch 23, wobei die  $\Sigma\Delta$ -ADCs MASH- $\Sigma\Delta$ -ADCs sind.

- 25. Empfänger (**2400**) gemäß Anspruch 24, wobei die ΣΔ-ADCs MASH-4-4-ΣΔ-ADCs sind.

Es folgen 6 Blatt Zeichnungen

# DE 698 39 192 T2 2009.02.26

## Anhängende Zeichnungen

FIG. 4