(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6092483号

(P6092483)

(45) 発行日 平成29年3月8日(2017.3.8)

(24) 登録日 平成29年2月17日(2017.2.17)

(51) Int.CI.

G 11 C 17/12 (2006.01)

F 1

G 11 C 17/00 304 Z

請求項の数 13 (全 15 頁)

(21) 出願番号 特願2016-531772 (P2016-531772)

(86) (22) 出願日 平成26年7月24日 (2014.7.24)

(65) 公表番号 特表2016-528660 (P2016-528660A)

(43) 公表日 平成28年9月15日 (2016.9.15)

(86) 國際出願番号 PCT/US2014/048061

(87) 國際公開番号 WO2015/017253

(87) 國際公開日 平成27年2月5日 (2015.2.5)

審査請求日 平成28年11月22日 (2016.11.22)

(31) 優先権主張番号 13/953,511

(32) 優先日 平成25年7月29日 (2013.7.29)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】セキュリティが強化されたマスクプログラム読取り専用メモリ

## (57) 【特許請求の範囲】

## 【請求項 1】

ビット線と相補ビット線とを含むカラム線ペアと、複数のメモリセルと、ここにおいて、各メモリセルが、前記ビット線に結合された第1のトランジスタと、前記相補ビット線に結合された第2のトランジスタとを備えるトランジスタのペアを含み、ここにおいて、トランジスタの各ペアについて、前記第1および第2のトランジスタのうちの1つが低しきい値電圧(低V<sub>t</sub>)トランジスタであり、前記第1および第2のトランジスタのうちの残りの1つが高しきい値電圧(高V<sub>t</sub>)トランジスタである、

前記ビット線と前記相補ビット線との間の電圧差を検知するように構成されたセンス増幅器と、

接地と前記第1および第2のトランジスタの各々のソースとの間に結合されたチョークデバイスと、ここにおいて、前記チョークデバイスが、漏れ電流を抑制するために前記第1および第2のトランジスタの前記各々のためのゲートソース間電圧を低減するように構成される、

前記相補ビット線に結合されたそのゲートと、前記ビット線に結合されたドレインとを有する第1のPMOSトランジスタと、

前記ビット線に結合されたそのゲートと、前記相補ビット線に結合されたドレインとを有する第2のPMOSトランジスタと

を備えるマスクプログラムROM(MROM)。

10

20

## 【請求項 2】

前記第1のトランジスタおよび前記第2のトランジスタがN M O Sトランジスタである、請求項1に記載のM R O M。

## 【請求項 3】

前記チヨークデバイスが、電源に結合されたゲートと、接地に結合されたソースと、前記第1および第2のトランジスタの前記ソースに結合されたドレインとを有するN M O Sトランジスタを備える、請求項1に記載のM R O M。

## 【請求項 4】

前記第1のP M O Sトランジスタのためのソースと前記第2のP M O Sトランジスタのためのソースとが両方とも電源に結合された、請求項1に記載のM R O M。 10

## 【請求項 5】

前記カラム線ペアの両端間のコモンモード電圧降下を減少させるように構成されたキーパーデバイスのペアをさらに備える、請求項1に記載のM R O M。

## 【請求項 6】

前記カラム線ペアをプリチャージするように構成されたプリチャージトランジスタのペアをさらに備える、請求項1に記載のM R O M。

## 【請求項 7】

ビット線と相補ビット線とを含むカラム線のペアをプリチャージすることと、

前記ビット線に結合された第1のトランジスタと、前記相補ビット線に結合された第2のトランジスタとを含むメモリセルにアクセスするためにワード線をアサートすることと、ここにおいて、前記第1および第2のトランジスタのうちの1つが低V<sub>t</sub>トランジスタであり、ここにおいて、前記第1および第2のトランジスタのうちの残りの1つが高V<sub>t</sub>トランジスタである、 20

前記ワード線のアサーションに応答して、前記アクセスされたメモリセルに記憶された2進値を検知するために、前記第1および第2のトランジスタのうちのどの1つが前記低V<sub>t</sub>トランジスタであるか、および、前記第1および第2のトランジスタのうちのどの1つが前記高V<sub>t</sub>トランジスタであるかを決定するために、カラム線の前記プリチャージされたペアの両端間の電圧差を検知することと、

漏れ電流を抑制するために、チヨークデバイスを通して接地に前記第1のトランジスタのためのソースを結合し、前記チヨークデバイスを通して接地に前記第2のトランジスタのソースを結合することと、 30

キーパーデバイスを通して前記ビット線と前記相補ビット線とを弱くチャージすることによって、前記カラム線のペアについてのコモンモード電圧降下を減少させることとを備える、方法。

## 【請求項 8】

前記低V<sub>t</sub>トランジスタが、前記プリチャージされたカラム線のうちの1つを、前記プリチャージされたカラム線のうちの残りの1つよりも低い電圧までディスチャージしたことに応答して、前記プリチャージされたカラム線の前記残りの1つを電源電圧までチャージするためにトランジスタをオンにすることをさらに備える、請求項7に記載の方法。 40

## 【請求項 9】

センス增幅器において前記電圧差を検知することをトリガするために、前記電圧差の発生の後にセンスイネーブル信号をアサートすることをさらに備える、請求項7に記載の方法。

## 【請求項 10】

ビット線と相補ビット線とを含むカラム線ペアと、

チヨークデバイスと、

複数のメモリセルと、ここにおいて、各メモリセルが、前記ビット線に結合された第1のトランジスタと、前記相補ビット線に結合された第2のトランジスタとを備えるトランジスタのペアを含み、ここにおいて、トランジスタの各ペアについて、前記第1および第2のトランジスタのうちの1つが、前記チヨークデバイスを通して接地に結合されたソー 50

スを有する低しきい値電圧（低V<sub>t</sub>）トランジスタであり、前記第1および第2のトランジスタのうちの残りの1つが、前記チョークデバイスを通して接地に結合されたソースを有する高しきい値電圧（高V<sub>t</sub>）トランジスタであり、ここにおいて、前記チョークデバイスが、前記第1および第2のトランジスタの各々のためのゲートソース間電圧を低減するように構成される。

前記メモリセルのうちのアクセスされた1つのメモリセルにおいて前記第1および第2のトランジスタのうちのいずれが高V<sub>t</sub>トランジスタまたは低V<sub>t</sub>トランジスタであるかを決定するために前記ピット線と前記相補ピット線との間の電圧差を検知するための手段と、

前記相補ピット線に結合されたそのゲートと、前記ピット線に結合されたドレインとを有する第1のPMOSトランジスタと

前記ピット線に結合されたそのゲートと、前記相補ピット線に結合されたドレインとを有する第2のPMOSトランジスタと

を備えるマスクプログラムドROM(MROM)。

【請求項11】

前記手段は、前記メモリセルのうちの前記アクセスされた1つのメモリセルにおいて前記第1および第2のトランジスタのうちのいずれが高V<sub>t</sub>トランジスタまたは低V<sub>t</sub>トランジスタであるかを決定するために、前記カラム線ペアの両端間の電圧差を検出するように構成された、請求項10に記載のMROM。

【請求項12】

前記手段は、前記メモリセルのうちの前記アクセスされた1つのメモリセルにおいて前記第1および第2のトランジスタのうちのいずれが高V<sub>t</sub>トランジスタまたは低V<sub>t</sub>トランジスタであるかの前記決定に応答してピット判定を行うようにさらに構成された、請求項11に記載のMROM。

【請求項13】

前記第1のトランジスタおよび前記第2のトランジスタがNMOSトランジスタである、請求項10に記載のMROM。

【発明の詳細な説明】

【技術分野】

【0001】

関連出願の相互参照

[0001]本出願は、その全体が参照により本明細書に組み込まれる、2013年7月29日に出願された米国非仮出願第13/953,511号の優先権を主張する。

【0002】

[0002]本出願は、マスクプログラムド(mask-programmed)読み取り専用メモリ(ROM)に關し、より詳細には、その記憶されたデータへの無許可のアクセス(unauthorized access)に対するセキュリティが強化されたマスクプログラムドROMに関する。

【背景技術】

【0003】

[0003]マスクプログラムドROM(MROM:a mask-programmed ROM)中の記憶されたデータは、暗号化コードまたは動作パラメータに關係する高度に機密のデータであり得る。たとえば、MROMは、重要なプログラムコード、メインプロセッサのための基本ブートストラップファームウェア、またはグラフィックカード、ハードディスク、DVDドライブ、およびTFTスクリーンなどの内蔵型のデバイス(self-contained devices)を内部で制御するために必要とされるファームウェアを記憶し得る。したがって、MROMが、その記憶されたデータへの無許可のアクセスに対して比較的セキュアであることが望ましい。

【0004】

[0004]MROMにおけるマスクプログラミングステップ(mask programming step)のタイプはそのデータセキュリティに影響を及ぼす。たとえば、MROMの1つのタイプ

10

20

30

40

50

は金属層プログラミングステップ (a metal layer programming step) の使用を伴う。金属層プログラミングは極めて普及しているが、高度なユーザは、記憶されたデータを回復する (recover) ために金属層プログラミングを容易にリバースエンジニアリングし得る。たとえば、埋込みM R O Mを含むシステムオンチップ (S O C : a system on a chip) ダイは、一般に、パッケージ基板上に取り付けられたフリップチップである。したがって、その隣接する金属層をもつダイのためのアクティブ表面はパッケージ基板に面するが、ダイの裏面はモールド化合物 (a mold compound) を用いてカプセル化される。その場合、リバースエンジニアは、ダイの裏面を露出させるためにモールド化合物を容易に除去し、金属層プログラミングを読み取り、記憶されたデータを決定するために、電子顕微鏡を使用して、露出したダイを通して撮像し得る。ヒューズベースR O M中の金属層ヒューズの状態も、この走査電子顕微鏡技法を使用して回復され得る。

10

#### 【0005】

[0005]別のタイプのM R O Mは、対応するメモリセルトランジスタにチャネルインプラント (channel implant) を選択的に与えるためにチャネルプログラミングステップ (a channel programming step) を使用する。チャネルインプラントの存在に応じて、メモリセルトランジスタは高しきい値電圧トランジスタ (a high threshold voltage transistor) または低しきい値電圧トランジスタ (a low threshold voltage transistor) のいずれかを備える。理想的には、低しきい値電圧トランジスタメモリセルは、その対応するワード線 (word line) のアサーションに応答して導通するが、高しきい値電圧トランジスタは導通しない。チャネルインプラントは、金属層プログラミングを検査するために使用されるリバースエンジニアリングのタイプに対してロバストであるが、トランジスタディメンジョンがディープサブミクロンレジーム (deep sub-micron regime) に押し進む (push into) ので、高しきい値電圧と低しきい値電圧との間の差はわずか 1 0 0 ミリボルトまで低減する。それにより、低しきい値電圧トランジスタと高しきい値電圧トランジスタの両方が高度プロセスノードにおいてワード線のアサーションに応答し、したがって、高しきい値電圧メモリセルを低しきい値メモリセルと区別するために別個の基準回路が必要とされ、これは、密度を低減し、システム複雑さを増加させる。さらに、チャネルインプラントプログラムドM R O M (channel-implant-programmed MROMs) 中の低しきい値電圧メモリセルトランジスタは過大な漏れ電流 (leakage current) に悩まされる。

20

#### 【0006】

[0006]したがって、当技術分野において、無許可のアクセスに対してロバストであり、しかも密度の増加と電力消費の低減とを達成するマスクプログラマブルR O Mが必要である。

30

#### 【発明の概要】

#### 【0007】

[0007]当技術分野において、密度の増加と電力消費の低減とを達成しながらセキュリティが強化されたマスクプログラムドR O Mの必要性を満たすために、カラム線 (column lines) またはビット線 (bit lines) のペアを含むマスクプログラムドR O M (M R O M) が開示される。各カラム線ペアはビット線と相補ビット線 (a complement bit line) とを含む。M R O Mは、各カラム線ペアについて複数のメモリセルを含む。各メモリセルはトランジスタのペアを備える。各トランジスタペア中の第1のトランジスタはビット線に結合するが、残りの第2のトランジスタは相補ビット線に結合する。各メモリセルのためのマスクプログラミングステップにおける選択的チャネルインプラントがそれの2進値 (論理 1 または論理 0) を決定する。各トランジスタペア中の第1または第2のトランジスタのいずれかはチャネルインプラントを受け取るが、そのペア中のトランジスタのうちの残りの1つはチャネルインプラントを受け取らない。チャネルインプラントの存在 (またはそれの欠如) がメモリセルの第1および第2のトランジスタのためのしきい値電圧を決定する。マスクプログラミングは、各トランジスタペア中のトランジスタのうちの1つが高しきい値電圧 (a high threshold voltage) (高V t (high Vt)) トランジスタであり、各ペア中のトランジスタのうちの残りの1つが低しきい値電圧 (a low threshold

40

50

voltage) (低  $V_t$  (low  $V_t$ )) トランジスタであるように、各メモリセルに関して相補的である。

【0008】

[0008] チャネルインプラントのタイプは、メモリセルトランジスタが低  $V_t$  トランジスタであるのか高  $V_t$  トランジスタであるのかを決定する。たとえば、アクセプタドーパント (acceptor dopants) がN M O Sトランジスタのチャネルに注入された (implanted) 場合、しきい値電圧は増加される。逆に、ドナードーパント (donor dopants) がN M O Sトランジスタのチャネルに注入された場合、しきい値電圧は低減される。したがって、一実施形態では、メモリセルは、高  $V_t$  トランジスタ (a high  $V_t$  transistor) になるよう 10 に第1のトランジスタのしきい値電圧を上げるために第1のトランジスタをチャネル注入すること (channel implanting) によって、第1の2進値 (論理高 (logic high) または論理低のいずれか) を記憶するようにマスクプログラムされ (mask programmed) 得る。残りの第2のトランジスタは、チャネルインプラントを受け取らないようにマスキングされ、したがって低  $V_t$  トランジスタ (a low  $V_t$  transistor) を備えるであろう。その 20 ような実施形態では、メモリセルは、第2のトランジスタが高  $V_t$  トランジスタを備えるように第2のトランジスタをチャネル注入することによって、第1の2進値のコンプリメント (complement) である第2の2進値を記憶するようにマスクプログラムされ得る。残りの第1のトランジスタは、それが低  $V_t$  トランジスタを備えるように、チャネルインプラントからマスキングされるであろう。しかし、上記で説明したように、チャネルインプラントの存在はしきい値電圧を代わりに下げ得ることを諒解されよう。チャネルインプラントがしきい値電圧を上げるのか下げるのかにかかわらず、各メモリセル中の第1および第2のトランジスタのうちの1つは高  $V_t$  トランジスタであるが、残りのトランジスタは低  $V_t$  トランジスタであるように、マスキングステップは相補的である。したがって、メモリセルの2進値は、第1および第2のトランジスタのうちのいずれが高  $V_t$  トランジスタまたは低  $V_t$  トランジスタであるかに依存する。

【0009】

[0009] 複数のワード線がカラム線ペアとの交差部 (intersections) を形成するように配置される。各カラム線ペアのためのメモリセルは、各メモリセルが、対応するワード線と対応するカラム線ペアとの交差点 (a cross point) または交差部に位置するように、ワード線ごとに配置される。メモリセルのワード線はトランジスタペアのゲートに結合する。したがって、対応するワード線が、その電圧を上げることによってアサートされた (asserted) 場合、ペア中の両方のトランジスタがオンになる。しかし、低  $V_t$  トランジスタは高  $V_t$  トランジスタよりも大きい程度までオンになる。 30

【0010】

[0010] 高  $V_t$  トランジスタによって通される電流の量と、低  $V_t$  トランジスタによって通される電流の量との間のこの差が以下のように読み取り動作中に使用される。特定のメモリセルに記憶されたビット値を読み取るために、最初に、対応するカラム線ペアがプリチャージ電圧 (a precharge voltage) までプリチャージされる。次に、対応するワード線を、たとえば電源電圧  $V_{DD}$  までチャージすることによって、対応するワード線が高にアサートされる。次いで、トランジスタペア中の両方のトランジスタが導通する。しかし、低  $V_t$  トランジスタに結合されたカラム線の電圧は、しきい値電圧の差のために、高  $V_t$  トランジスタに結合された残りの線よりも多くディスチャージされる。したがって、センス增幅器を使用してカラム線ペアの両端間の電圧降下差 (the voltage drop difference across the column line pair) を検査することによって、第1のトランジスタが高  $V_t$  トランジスタであるのか低  $V_t$  トランジスタであるのか、または同等に、第2のトランジスタが低  $V_t$  トランジスタであるのか高  $V_t$  トランジスタであるのかが決定され得る。センス增幅器がそのような決定を行うと、センス增幅器は、対応する出力ビットを生成する。たとえば、センス增幅器が、第1のトランジスタは高  $V_t$  トランジスタである (または同等に、第2のトランジスタは低  $V_t$  トランジスタである) と決定した場合、センス增幅器は、第1の2進値に等しい出力ビットを生成し得る。第1の2進値が2進1値であるの 40 50

か 2 進 0 値であるのかは設計選択である。逆に、センス増幅器が、第 1 のトランジスタは低  $V_t$  トランジスタである（または同等に、第 2 のトランジスタは高  $V_t$  トランジスタである）と決定した場合、センス増幅器は、第 1 の 2 進値のコンプリメントである第 2 の 2 進値に等しい出力ビットを生成し得る。

【図面の簡単な説明】

【0011】

【図 1】[0011] 本開示の一実施形態による、マスクプログラムド ROM (MROM) 中のカラムの概略図。

【図 2】[0012] 図 2 の MROM における様々な信号のための波形を示す図。

【図 3】[0013] 本開示の一実施形態による、チョークデバイス (choke devices) を含む MROM 中のカラムの概略図。

10

【図 4】[0014] 図 3 の MROM における様々な信号のための波形を示す図。

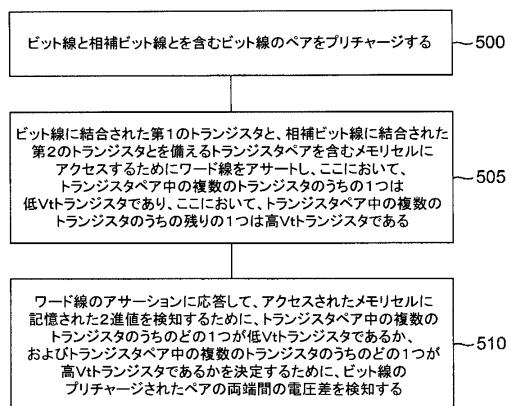

【図 5】[0015] 本開示の一実施形態による、MROM のための例示的な動作方法のためのフロー チャート。

【詳細な説明】

【0012】

[0016] 各メモリセルがトランジスタのペアを含む、マスクプログラムド ROM (MROM) が開示される。各ペア中の第 1 のトランジスタはビット線に結合する。したがって、第 1 のトランジスタはビット線トランジスタとして示されることもある。各ペア中の残りの第 2 のトランジスタは相補ビット線に結合し、したがって、第 2 のトランジスタは相補ビット線トランジスタとして示されることもある。各ペア中のトランジスタのためのしきい値電圧は、複数のトランジスタのうちの 1 つ（ビット線トランジスタまたは相補ビット線トランジスタのいずれか）が低  $V_t$  トランジスタであり、残りのトランジスタが高  $V_t$  トランジスタであるように、相補的である。メモリセルトランジスタのしきい値電圧は、製造プロセス中に、対応する（1 つまたは複数の）マスクステップを通して、メモリセルトランジスタがマスキングされたか否かに応じてチャネルインプラントを受け取るように構成される。各トランジスタペアについて、複数のトランジスタのうちの 1 つは、残りのトランジスタがチャネルインプラントを受け取る間、マスキングされる。以下の説明では、チャネルインプラントがしきい値電圧を増加させることを仮定するが、チャネルインプラントは、しきい値電圧を低減するようにも構成され得ることが、諒解されよう。メモリセルは、各メモリセルがワード線とカラム線ペアとの交差点または交差部に位置するように、ワード線ごとに配置される。各カラム線ペアはビット線と相補ビット線とを含む。

20

【0013】

[0017] 第 1 の 2 進値を記憶するようにメモリセルをマスクプログラムするために、メモリセルのビット線トランジスタは、それが、チャネルインプラントから遮蔽され、低  $V_t$  トランジスタとして構成されるように、マスキングされる。逆に、マスキングされていない相補ビット線トランジスタは、それが高  $V_t$  トランジスタとして構成されるように、チャネルインプラントを受け取る。同様に、第 1 の 2 進値のコンプリメントである第 2 の 2 進値を記憶するようにメモリセルをマスクプログラムするために、ビット線トランジスタは高  $V_t$  トランジスタとして構成されるが、相補ビット線トランジスタは低  $V_t$  トランジスタとして構成されるように、チャネルインプラントおよびマスキングが実行される。したがって、各マスクプログラムドメモリセルの 2 進状態は、有利なことにどの金属層構成にも依存しない。言い換えれば、本明細書で開示する MROM のための金属層のどんな目視検査 (visual examination) も、MROM 内の記憶されたデータに関する情報を与えない。このようにして、従来技術の金属層プログラムド ROM と比較してセキュリティが大幅に強化される。その上、各メモリセル中の高  $V_t$  トランジスタと低  $V_t$  トランジスタとの相補的使用は、従来のチャネルインプラントプログラムド ROM (channel-implant-programmed ROMS) の設計を複雑にする別個の基準回路の必要性をなくす。さらに、従来のチャネルインプラントプログラムド ROM を悩ました漏れ電流が、本明細書でさらに説明するように急激に低減される。次に、いくつかの例示的な実施形態について説明する。

30

40

50

## 【0014】

## 例示的な実施形態

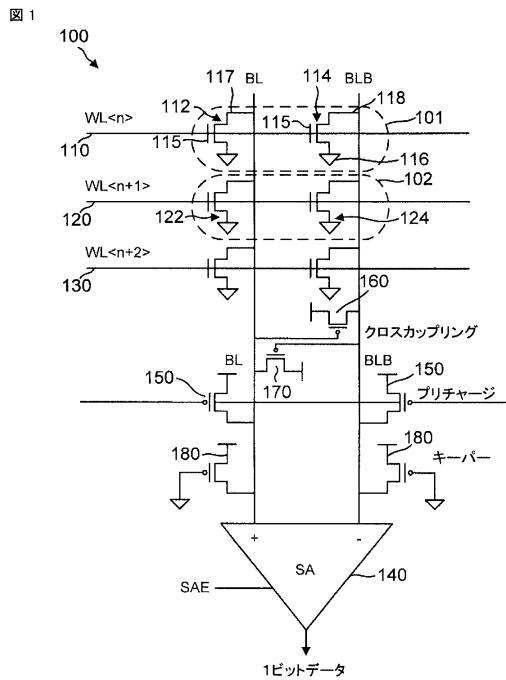

[0018] 次に図面を参照すると、図1は、メモリセル101および102などの複数のメモリセルを含むMR ROM100を示している。各メモリセルは、ビット線(BL)に結合された第1のN MOSトランジスタと、相補ビット線(BLB:a complement bit line)に結合された第2のN MOSトランジスタとを含む。ビット線BLおよびBLBはカラム線ペアを形成する。したがって、カラム線ペアに結合されたメモリセルはMR ROM100においてメモリセルのカラムを形成する。各第1のトランジスタおよび各第2のトランジスタのためのしきい値電圧が各メモリセルの2進状態を決定する。メモリセル101では、第1のトランジスタは、ビット線BLに結合されたドレイン117を有する低Vtトランジスタ112である。逆に、第2のトランジスタは、相補ビット線BLBに結合されたドレイン118を有する高Vtトランジスタ114である。10

## 【0015】

[0019] MR ROM100は、ワード線110、120、および130などの複数のロウワード線(row word lines)を含む。ワード線110はMR ROMのためのn番目のワード線であり、ただし、nは任意の正の整数である。同様に、ワード線120は(n+1)番目のワード線であり、ワード線130は(n+2)番目のワード線である。説明の明快のために、MR ROM100中の残りのワード線は図示されていない。トランジスタ112および114のためのゲート115はワード線110に電気的に接続されるが、トランジスタ112および114のためのソースは接地116に結合する。しかしながら、以下でさらに説明するように、トランジスタ112および114のためのソースは、漏れ電流を制限するために代替実施形態ではショートデバイスに結合し得る。センス增幅器140は、カラム線ペアの両端間の電圧差を検知することによってビット判定を行う(make a bit decision)ように構成される。低Vtトランジスタ112は、電源電圧VDDへのワード線110の上昇に応答してより十分にオンになる傾向があるが、高Vtトランジスタ114はそれほどロバストにオンにならない。したがって、ビット線BLは、ワード線110がアサートされたとき(ワード線110上の電圧が電源電圧VDDまで上げられたとき)、相補ビット線BLBよりも速く接地へディスチャージすることになる。一実施形態では、センス增幅器140は、メモリセルのうちのアクセスされた1つのメモリセルにおいて第1および第2のトランジスタのうちのいずれが高Vtトランジスタまたは低Vtトランジスタであるかを決定するための手段を備える。20

## 【0016】

[0020] MR ROM100中のメモリセルのプログラミングは、各メモリセルトランジスタペア中の第1および第2のトランジスタのためのしきい値電圧に依存する。それらのしきい値電圧は、トランジスタペア中の複数のトランジスタのうちの1つが低Vtトランジスタであり、複数のトランジスタのうちの残りの1つが高Vtトランジスタであるという点で相補的である。たとえば、メモリセル102では、第1のトランジスタは高Vtトランジスタ122であるが、第2のトランジスタは低Vtトランジスタ124である。したがって、メモリセル102のマスクプログラミングはメモリセル101のためのマスクプログラミングと相補関係にある。たとえば、第1のトランジスタが低Vtトランジスタである場合、および第2のトランジスタが高Vtトランジスタである場合、論理0値がメモリセルに記憶されると見なされ得る。逆に、第1のトランジスタが高Vtトランジスタである場合、および第2のトランジスタが低Vtトランジスタである場合、論理1値がメモリセルに記憶されると見なされ得る。第1のトランジスタが高Vtトランジスタである場合、および第2のトランジスタが低Vtトランジスタである場合、代わりに論理1値がメモリセルに記憶されると見なされ得るように、2進値の割当ては任意であることを諒解することができよう。(n+1)番目のワード線120はメモリセル102中のトランジスタ122および124のゲートに結合する。ワード線120がアサートされたとき、相補ビット線BLBは、したがって、ビット線BLと比較してより速く接地へディスチャージされることになる。30

## 【0017】

[0021]概して、MROM100中の特定のメモリセルのための読み取り動作は以下の通りである。アクセスされたメモリセルに記憶されたビット値を読み取る第1のステップは、プリチャージPMOSトランジスタ150のゲートを駆動するプリチャージ信号のアサーション（アクティブ低）に応答してプリチャージPMOSトランジスタ150のペアをオンにすることによってなど、ビット線BLと相補ビット線BLLとをプリチャージすることを備える。各プリチャージトランジスタ150は、電源VDDに結合されたそのソースを有する。1つのプリチャージトランジスタ150は、ビット線BLに連結された（tied）そのドレインを有するが、残りのプリチャージトランジスタ150は、相補ビット線BLLに連結されたそのドレインを有する。MROM100はワード線ごとに連続的に読み取られるので、同じワード線によってアクセスされるすべてのメモリセルがワード線のアサーション時に読み取られ得る。プリチャージ電圧は、一実施形態では0.8ボルト（V）から1.2Vにわたり得る電源電圧VDDに依存する。プリチャージステージ中に、ワード線はアサートされない。同様に、センス增幅器140も、この時点でオフにされるかまたはカラム線ペアから切り離される。カラム線ペアがプリチャージされると、ビット線BLおよび相補ビット線BLLが浮動するように、プリチャージトランジスタ150はオフにされる。

## 【0018】

[0022]ワード線は複数のカラム線ペアにわたって延びる。説明の明快のために、図1には単一のカラム線ペアのみが示されている。ターゲットにされるワード線は、VDDまで上げられることによってアサートされ、したがって、アサートされたワード線によって横断される様々なカラム線ペアにおいてメモリセル中の第1および第2のトランジスタをオンにし得る。アクセスされたメモリセルに結合されたビット線BLおよび相補ビット線BLLのための電圧は、次いで、どのカラム線が低Vtトランジスタに結合するか、およびどのカラム線が高Vtトランジスタに結合するかに応じて応答する。この電圧差の発生の後に、センス增幅器140は、ビット判定を行うことを可能にされる。一実施形態では、電源電圧VDDは1Vであるが、高電圧しきい値は摂氏25度において約400mVであり、低電圧しきい値は摂氏25度において約300mVである。したがって、高Vtトランジスタと低Vtトランジスタの両方が、対応するワード線のアサーションに応答してオンになるが、低Vtトランジスタはより速くオンになり始める。オンになると、両方のトランジスタは、それらのそれぞれのチャネル中で電流を導通するように働き、これは、高Vtトランジスタの応答パターンと低Vtトランジスタの応答パターンとが異なるので、異なる量だけカラム線をディスチャージする。NMOSトランジスタのチャネル中で生成される電流の大きさは、ゲートソース間電圧（gate-to-source voltage）としきい値電圧との間の差に依存するので、高Vtトランジスタ中で生成される電流と比較して、より大きい電流が低Vtトランジスタのチャネル中で生成される。したがって、低Vtトランジスタに結合されたカラム線（ビット線BLまたは相補ビット線BLLのいずれか）のための電圧は、高Vtトランジスタに結合されたカラム線の電圧よりも速く低下することになる。

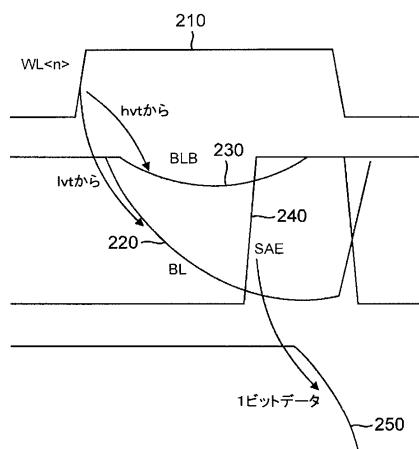

## 【0019】

[0023]図2に、ワード線110上にアサートされた電圧210に応答したカラム線ペア上の時間的な電圧変化を示す。メモリセル101中の低Vtトランジスタ112がオンになるにつれて、プリチャージされたビット線BL上の電圧220が最初に低下し始め、少し後に、高Vtトランジスタ114がオンになり始めるにつれて、相補ビット線BLL上の電圧230が低下することがわかり得る。しかし、ビット線BL電圧220は相補ビット線BLL電圧230よりも速く低下する。ビット線BLと相補ビット線BLLとの間にこの電圧差が発生するのに十分な量の時間の後、センス增幅器イネーブル（SAE:sense amplifier enable）信号240がアサートされ、したがって、センス增幅器140は、ビット線BL電圧220が相補ビット線BLL電圧230よりも高いのか低いのかを決定することによって、メモリセル101に記憶された2進値を検知し得る。たとえば、メモ

10

20

30

40

50

リセル 102 が読み取り動作においてアクセスされた場合、メモリセル 102 では高  $V_t$  トランジスタ 122 がビット線 BL に結合するので、センス増幅器 140 は、ビット線 BL 電圧 220 が相補ビット線 BLB 電圧 230 よりも高いままであると決定するであろう。カラム線ペアについての電圧差に基づいて、センス増幅器 140 は、アクセスされたメモリセルに記憶された論理値を決定し、データバスまたは出力に送出されるべき対応するデータビット 250 を生成することができる。センス増幅器 140 による、カラム線ペアの両端間の電圧差の検知と、そこからのデータビットの生成とは、メモリ技術において知られているセンス増幅器 140 における従来のラッチングプロセス (latching process) によって達成され得る。

## 【0020】

10

[0024] 電圧差を強調する (accentuate) ために、カラム線ペアはクロスカップリングされ (cross-coupled) 得る。たとえば、PMOS トランジスタ 160 および 170 のペアが、図 1 に示されているようにこのクロスカップリング (cross-coupling) を実装するために使用され得る。PMOS トランジスタ 160 のゲートはビット線 BL 上の電圧によって駆動されるが、PMOS トランジスタ 170 のゲートは相補ビット線 BLB 上の電圧によって駆動される。PMOS トランジスタ 160 のドレインは相補ビット線 BLB に結合するが、PMOS トランジスタ 170 のドレインはビット線 BL に結合する。トランジスタ 160 および 170 のためのソースは、電源電圧 VDD を与える電源に結合する。このクロスカップリングが与えられれば、カラム線ペアの両端間の電圧差は強調される。たとえば、万ービット線 BL 上の電圧が最初に降下した場合、トランジスタ 160 は、相補ビット線 BLB のための電圧を VDD までプルするためにオンになる傾向がある。逆に、万一相補ビット線 BLB 上の電圧が最初に降下した場合、トランジスタ 170 は、ビット線 BL 上の電圧を VDD までプルするためにオンになる傾向がある。図 2 は、ビット線電圧 220 がワード線アサーションに応答して最初に降下する、メモリセル 101 などのメモリセルについての電圧発生を示しているので、相補ビット線電圧 230 は、ビット線電圧 220 が減少するにつれて跳ね上がることが示されている。このようにして、PMOS トランジスタ 160 および 170 からのクロスカップリングは、センス増幅器 140 がビット判定を行うのを支援する。

20

## 【0021】

[0025] また、弱いキーパー PMOS トランジスタ (a weak keeper PMOS transistor) 180 が、コモンモード電圧降下 (a common mode voltage drop) を減速するために各カラム線に結合され得る。そのようなデバイスがなければ、各カラム線上のコモンモード降下が、高  $V_t$  および低  $V_t$  トランジスタが導通し始めたことに応答してあまりにも速く生じことがある。その場合、センス増幅器 140 は、そのような速いディスチャージにより、どのカラム線電圧が最も多くディスチャージしたかを見分けることができないことがある。各キーパー PMOS トランジスタ 180 は、常時オンであるが、弱いように構成される。各カラム線のための電圧を弱くプルアップすることによって、キーパートランジスタ (keeper transistors) 180 は、カラム線ディスチャージを減速するように働く。キーパートランジスタ 180 の効果は、電圧 220 および 230 が比較的徐々に下降するという点で図 2 に示されている。

30

## 【0022】

40

[0026] ROM 100 に関する 1 つの問題は漏れ電流の量である。特に、低  $V_t$  トランジスタからの漏れ電流は、高  $V_t$  トランジスタからのそれと比較して比較的高い。これらのトランジスタを通した接地への生じたディスチャージは、バッテリー電源式デバイスについてより速いバッテリー消耗を生じる。その上、ワード線の数が増加するにつれて、各カラム線に結合された低  $V_t$  トランジスタの数は増加する傾向がある。各カラム線に結合された、この増加した数の低  $V_t$  トランジスタは、アクセスされたメモリセルにおいてオンにされている低  $V_t$  トランジスタからのディスチャージに等しいまたはそれよりもさらに大きい量だけ各カラム線をディスチャージし得る。したがって、カラム線ペア中のどのカラム線がより低い電圧を有するかは、アクセスされたメモリセル中の第 1 のトランジ

50

タおよび第2のトランジスタのためのしきい値電圧にもはや依存しないので、センス増幅器140は、カラム線ペア中のどのカラム線がより低い電圧を有するかを正しく決定することができないであろう。代わりに、カラム線のディスチャージは、アクセスされないメモリセルにおける漏れ電流によって生成されたそれによって支配され得る。

#### 【0023】

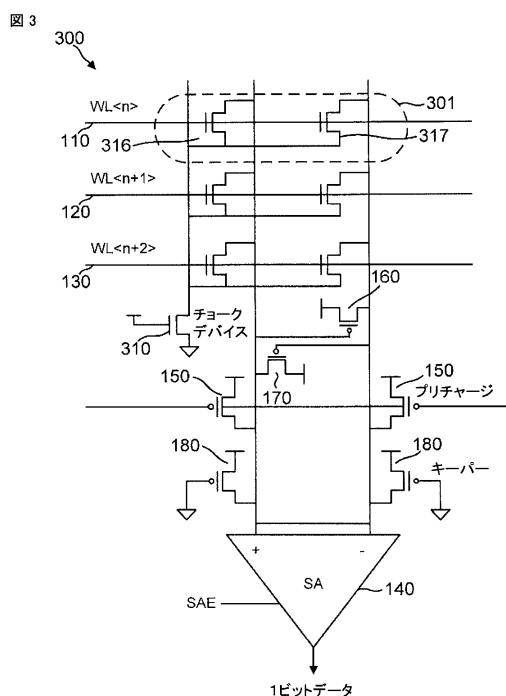

[0027]この漏れ電流を抑制するために、メモリセルトランジスタドレインは、図3のMR ROM300について示されているように、対応するチョークトランジスタ310を通して接地に結合し得る。チョークトランジスタ310はメモリセルトランジスタと比較して比較的弱い。MR ROM300では、チョークトランジスタ310は、永続的にオンになるように、V DDに連結されたそのゲートを有するNMOSトランジスタである。チョークトランジスタ310のためのソースは接地に結合するが、そのドレインは、対応するカラム線ペアに結合された、すべての低V tトランジスタのためのソースと、すべての高V tトランジスタのためのソースとに（または少なくとも低V tおよび高V tトランジスタのサブセットに）結合する。チョークトランジスタ310は比較的弱いので、それは、漏洩低V tトランジスタ（leaking low Vt transistors）からのすべての漏れ電流を導通することはできず、したがって、そのドレインの電圧がV DDへ上がり始める。チョークトランジスタ310上のドレイン電圧のこの上昇は、アサート解除された（de-asserted）ワード線を有するオフにされた低V tトランジスタについてゲートソース間電圧が減少し、したがって、これらの低V tトランジスタについて負になることを意味する。漏れ電流はゲートソース間電圧の指數関数であるので、チョークトランジスタ310は、アクセスされない低V tトランジスタにおける漏れ電流を急激に低減する。チョークトランジスタ310は、このようにして漏れ電流を低減するだけでなく、それはまた、高V tトランジスタのゲートソース間電圧が、オンになるために高しきい値電圧を超えるなければならないので、アクセスされたメモリセルにおいて高V tトランジスタをオフに保つを助ける。しかし、ソース電圧はチョークトランジスタ310の効果により上昇するので、高V tトランジスタは、対応するワード線のアサーションに応答してオンになるのを抑制されることになる。その結果、高V tトランジスタに結合されたカラム線上の電圧は、対応するワード線のアサーションに応答して降下しない（または、ごくわずかしか降下しない）。

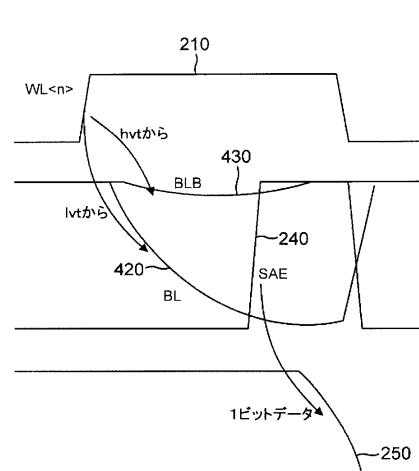

#### 【0024】

[0028]図4に、図3のメモリセル301のための読み取り動作に関するチョークトランジスタ310の効果を示す。メモリセル301では、低V tトランジスタ316は、ビット線B Lに結合する第1のトランジスタであるが、高V tトランジスタ317は、相補ビット線B L Bに結合する第2のトランジスタである。したがって、チョークトランジスタ310はトランジスタ316および317のためのソースに結合する。高V tトランジスタ317上のソース電圧の増加により、相補ビット線電圧430は、ワード線110のためのワード線電圧210のアサーションに応答してごくわずかしか降下しない。したがって、チョークトランジスタ310は、アクセスされないメモリセル中の低V tトランジスタからの漏れを低減することによってだけでなく、カラム線ペアの両端間の電圧差をさらに発生させるために、アクセスされたメモリセル中の高V tトランジスタがオンになるのを抑制することによっても、センス増幅器140による信号読み取りおよび区別を向上させる。次に、例示的な動作方法について説明する。

#### 【0025】

##### 例示的な動作方法

[0029]例示的な読み取り動作のためのフローチャートを図5に示す。読み取り動作は、ビット線と相補ビット線（a complementary bit line）とを含むカラム線のペアをプリチャージする行為500から始まる。読み取り動作は、ビット線に結合された第1のトランジスタと、相補ビット線に結合された第2のトランジスタとを備えるトランジスタペアを含むメモリセルにアクセスするためにワード線をアサートする行為505を続け、ここにおいて、トランジスタペア中の複数のトランジスタのうちの1つは低V tトランジスタであり、

10

20

30

40

50

ここにおいて、トランジスタペア中の複数のトランジスタのうちの残りの1つは高V<sub>t</sub>トランジスタである。読み取り動作は、ワード線アサーションに応答して、アクセスされたメモリセルに記憶された2進値を検知するために、トランジスタペア中の複数のトランジスタのうちのどの1つが低V<sub>t</sub>トランジスタであるか、およびトランジスタペア中の複数のトランジスタのうちのどの1つが高V<sub>t</sub>トランジスタであるかを決定するための、カラム線ペアの両端間の電圧差を検知する行為510で終わる。

【0026】

[0030]当業者が今や諒解するように、および目下の特定の適用例に応じて、本開示の趣旨および範囲から逸脱することなく、本開示のデバイスの材料、装置、構成および使用方法においておよびそれへの多くの変更、置換および変形が行われ得る。これに照らして、本明細書で例示し、説明した特定の実施形態は本開示のいくつかの例にすぎないので、本開示の範囲は、それらの実施形態の範囲に限定されるべきでなく、むしろ、以下に添付された特許請求の範囲およびそれらの機能的等価物の範囲に十分に相応すべきである。

以下に、本願出願の当初の特許請求の範囲に記載された発明を付記する。

[C1] ビット線と相補ビット線とを含むカラム線ペアと、

複数のメモリセルと、ここにおいて、各メモリセルが、前記ビット線に結合された第1のトランジスタと、前記相補ビット線に結合された第2のトランジスタとを備えるトランジスタのペアを含み、ここにおいて、トランジスタの各ペアについて、前記第1および第2のトランジスタのうちの1つが低しきい値電圧(低V<sub>t</sub>)トランジスタであり、前記第1および第2のトランジスタのうちの残りの1つが高しきい値電圧(高V<sub>t</sub>)トランジスタである、

を備えるマスクプログラムドROM(MROM)。

[C2] 前記第1のトランジスタおよび前記第2のトランジスタがNMOSトランジスタである、C1に記載のMROM。

[C3] 各第1のトランジスタおよび各第2のトランジスタが、接地されたソースを含み、ここにおいて、各第1のトランジスタのためのドレインが前記ビット線に結合し、各第2のトランジスタのためのドレインが前記相補ビット線に結合する、C2に記載のMROM。

[C4] 前記第1および第2のトランジスタの各々のソースに結合されたチャーチデバイスをさらに備え、ここにおいて、前記チャーチデバイスが、前記第1および第2のトランジスタの前記各々のためのゲートソース間電圧を低減するように構成された、C1に記載のMROM。

[C5] 前記チャーチデバイスが、電源に結合されたゲートと、接地に結合されたソースと、前記第1および第2のトランジスタの前記ソースに結合されたドレインとを有するNMOSトランジスタを備える、C4に記載のMROM。

[C6] 前記相補ビット線に結合されたそのゲートと、前記ビット線に結合されたドレインとを有する第1のPMOSトランジスタと、

前記ビット線に結合されたそのゲートと、前記相補ビット線に結合されたドレインとを有する第2のPMOSトランジスタと、

をさらに備える、C1に記載のMROM。

[C7] 前記第1のPMOSトランジスタのためのソースと前記第2のPMOSトランジスタのためのソースとが両方とも電源に結合された、C6に記載のMROM。

[C8] 前記カラム線ペアの両端間のコモンモード電圧降下を減少させるように構成されたキーパーデバイスのペアをさらに備える、C1に記載のMROM。

[C9] 前記カラム線ペアをプリチャージするように構成されたプリチャージトランジスタのペアをさらに備える、C1に記載のMROM。

[C10] ビット線と相補ビット線とを含むカラム線のペアをプリチャージすること、

前記ビット線に結合された第1のトランジスタと、前記相補ビット線に結合された第2のトランジスタとを含むメモリセルにアクセスするためにワード線をアサートすることと

10

20

30

40

50

、ここにおいて、前記第1および第2のトランジスタのうちの1つが低V<sub>t</sub>トランジスタであり、ここにおいて、前記第1および第2のトランジスタのうちの残りの1つが高V<sub>t</sub>トランジスタである、

前記ワード線のアサーションに応答して、前記アクセスされたメモリセルに記憶された2進値を検知するために、前記第1および第2のトランジスタのうちのどの1つが前記低V<sub>t</sub>トランジスタであるか、および、前記第1および第2のトランジスタのうちのどの1つが前記高V<sub>t</sub>トランジスタであるかを決定するために、カラム線の前記プリチャージされたペアの両端間の電圧差を検知することとを備える、方法。

[C11] 前記低V<sub>t</sub>トランジスタが、前記プリチャージされたカラム線のうちの1つを、前記プリチャージされたカラム線のうちの残りの1つよりも低い電圧までディスチャージしたことに応答して、前記プリチャージされたカラム線の前記残りの1つを電源電圧までチャージするためにトランジスタをオンにすることとをさらに備える、C10に記載の方法。

[C12] キーパーデバイスを通して前記ビット線と前記相補ビット線とを弱くチャージすることによって、前記カラム線のペアについてのコモンモード電圧降下を減少させることをさらに備える、C10に記載の方法。

[C13] 漏れ電流を抑制するために前記第1および第2のトランジスタの各々のためのソース電圧を上げることをさらに備える、C10に記載の方法。

[C14] 前記第1および第2のトランジスタの各々のための前記ソース電圧を上げることが、前記第1および第2のトランジスタからの漏れ電流をN MOSトランジスタを通して接地に導通することを備える、C13に記載の方法。

[C15] センス増幅器において前記電圧差を検知することをトリガするために、前記電圧差の発生の後にセンスイネーブル信号をアサートすることをさらに備える、C10に記載の方法。

[C16] ビット線と相補ビット線とを含むカラム線ペアと、複数のメモリセルと、ここにおいて、各メモリセルが、前記ビット線に結合された第1のトランジスタと、前記相補ビット線に結合された第2のトランジスタとを備えるトランジスタのペアを含み、ここにおいて、トランジスタの各ペアについて、前記第1および第2のトランジスタのうちの1つが低しきい値電圧(低V<sub>t</sub>)トランジスタであり、前記第1および第2のトランジスタのうちの残りの1つが高しきい値電圧(高V<sub>t</sub>)トランジスタである、

前記メモリセルのうちのアクセスされた1つのメモリセルにおいて前記第1および第2のトランジスタのうちのいずれが高V<sub>t</sub>トランジスタまたは低V<sub>t</sub>トランジスタであるかを決定するための手段と

を備えるマスクプログラムドROM(MROM)。

[C17] 前記手段は、前記メモリセルのうちの前記アクセスされた1つのメモリセルにおいて前記第1および第2のトランジスタのうちのいずれが高V<sub>t</sub>トランジスタまたは低V<sub>t</sub>トランジスタであるかを決定するために、前記カラム線ペアの両端間の電圧差を検出するように構成された、C16に記載のMROM。

[C18] 前記手段は、前記メモリセルのうちの前記アクセスされた1つのメモリセルにおいて前記第1および第2のトランジスタのうちのいずれが高V<sub>t</sub>トランジスタまたは低V<sub>t</sub>トランジスタであるかの前記決定に応答してビット判定を行うように構成された、C17に記載のMROM。

[C19] 前記第1のトランジスタおよび前記第2のトランジスタがN MOSトランジスタである、C16に記載のMROM。

[C20] 前記第1および第2のトランジスタの各々のソースに結合されたチョークデバイスをさらに備え、ここにおいて、前記チョークデバイスが、前記第1および第2のトランジスタの各々のためのゲートソース間電圧を低減するように構成された、C16に記載のMROM。

10

20

30

40

50

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

## 【図5】

図5

FIG. 5

---

フロントページの続き

- (72)発明者 ユン、セイ・スン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

- (72)発明者 ジュン、チュルミン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

- (72)発明者 タージオグル、イージン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

- (72)発明者 ミレンドルフ、スティーブン・マーク

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 後藤 彰

- (56)参考文献 特開平7-105694 (JP, A)

特開平1-100797 (JP, A)

特開2013-143161 (JP, A)

米国特許出願公開第2008/0008019 (US, A1)

特開2000-299394 (JP, A)

米国特許第6016277 (US, A)

米国特許第6473334 (US, B1)

米国特許第5959467 (US, A)

米国特許第4599704 (US, A)

- (58)調査した分野(Int.Cl., DB名)

G11C 17/12