## (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**HO2M 7/493** (2007.01) **HO2M 7/5387** (2007.01) **HO2M 7/5395** (2006.01)

(52) CPC특허분류

**HO2M 7/493** (2013.01) **HO2M 7/5387** (2013.01)

(21) 출원번호 **10-2018-0016504**

(22) 출원일자 **2018년02월09일** 심사청구일자 **2018년02월09일**

(56) 선행기술조사문헌

JP2016082661 A

KR101704377 B1

US05822199 A

US20030048006 A1

(45) 공고일자 2018년04월06일

(11) 등록번호 10-1846212

(24) 등록일자 2018년04월02일

(73) 특허권자

## 국제전기 주식회사

충청북도 음성군 금왕읍 신개촌로 98

(72) 발명자

#### 김정호

경기도 구리시 동구릉로66번길 14, 101동 101호( 인창동, 우림필유)

## 심현섭

경기도 용인시 기흥구 금화로11번길 10, 310동 306호(상갈동, 금화마을주공3단지아파트)

(74) 대리인

이원섭

전체 청구항 수 : 총 7 항

심사관 : 최창락

## (54) 발명의 명칭 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치 및 제어 방법

#### (57) 요 약

본 발명에 따른 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치는 2개 이상의 인버터 가 병렬 연결되었을 때 각각의 인버터가 서로 균등한 전력으로 부하를 분담하도록 하여 각 인버터 간 유효 전력 편차나 무효 전력의 편차로 인해 인버터간 순환 전류가 발생 됨을 방지하고, 상기 각 인버터에는 상기 인버터에 (뒷면에 계속)

## 대표도

내부 장착되어 H-브릿지(Bridge) 회로를 이용하여 직류 전원을 교류 전원으로 변환하는 IGBT 전력 변환부(3)와. 상기 IGBT 전력 변환부(3)로부터 출력된 PWM 펄스 신호를 필터링(Filtering)하여 정현파 형태로 변환하는 LC 필 터부(5)가 갖추어진 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치에 있어서, 상기 LC 필터부(5)의 출력단에 연결되어 인버터가 정상 가동될 때에는 스위치 온(On)되어 부하로 전류를 흘려보내는 반면, 인버터에 고장이 발생되었을 때에는 스위치 오프(Off)되어 전류 흐름을 끊는 인버터 스위치(Inverter Switch)(1)와; 상기 인버터 스위치(1)의 출력단에 연결되어 인버터가 정상 가동될 때에는 스위치 오프(Off)되는 반면, 인버터에 고장이 발생되었을 때에는 스위치 온(On)되어 바이패스(Bypass) 선로로부터 입력된 3상 교류 전 원을 부하측으로 공급하는 바이패스 스위치(Bypass Switch)(4); 상기 인버터 스위치(1)가 스위치 온(On)되고 바 이패스 스위치(4)가 스위치 오프(Off)된 상태에서 상기 IGBT 전력 변환부(3)로부터 출력되는 인버터 전류와, LC 필터부(5)로부터 인버터 스위치(1)로 전달되는 3상 부하 전압과 3상 부하 전류 그리고 바이패스 선로(6)로부터 출력된 3상 바이패스 전압을 동기 신호 발생부(7)로부터 제공된 동기 신호에 맞춰 DQ 변환하여 DQ 동기 좌표 변 환 값으로 변환하는 DQ 변환부(9); 메모리에 저장된 파라미터로부터 제공된 전류 위상각 보상값을 이용하여 상 기 DQ 변환부(9)로부터 입력받은 3상 부하 전류의 위상각을 보상하고 상기 위상각이 보상된 3상 부하 전류와 상 기 DQ 변환부(9)로부터 전달된 3상 부하 전압을 이용하여 새로운 유효 전력 레퍼런스(Reference) 값(Pref)과 무 효 전력 레퍼런스(Reference) 값(Qref)을 계산하고, 인버터의 유효 전력이 증가하면 상기 유효 전력 레퍼런스 값(Pref)을 이용하여 인버터로부터 출력되는 전압 주파수를 낮추기 위한 유효 전력 드룹(Droop) 신호를 생성하고, 인버터의 무효 전력이 증가하면 상기 무효 전력 레퍼런스 값을 이용하여 인버터로부터 출력되는 전압을 낮 추기 위한 무효 전력 드룹 신호를 생성하는 V/F(Voltage/Frequency) 병렬 드룹(Droop) 제어부; 상기 V/F 병렬 드룹 제어부(11)로부터 출력된 무효 전력 드룹 신호가 증가하면 인버터로부터 출력되는 전압을 낮추기 위한 제 어 신호를 DQ 역변환부(13)에 전달하는 전압 전류 제어부(15); 상기 DQ 변환부(9)에 의해 변환된 3상 바이패스 전압의 Q축 전압 신호와 동상인 동기 신호를 발생하는 동기 신호 발생부(7); 상기 V/F 병렬 드룹 제어부(11)로 부터 출력된 유효 전력 드룹 신호가 증가하면 인버터로부터 출력되는 전압 주파수를 낮추기 위한 제어 신호를 DQ 역변환부(13)에 전달하는 주파수 제어부(17); 상기 전압 전류 제어부(15)와 주파수 제어부(17)의 제어 신호 에 따라 인버터의 출력 전압과 주파수를 조정하기 위한 지령 신호를 발생하는 DQ 역변환부(13); 및 상기 DQ 역 변환부(13)로부터 출력된 지령 신호를 IGBT 전력 변환부(3)의 IGBT(Insulated Gate Bipolar Transistor)를 스위 칭시키기 위한 공간 벡터 펄스 폭 변조 신호(SV PWM: Space Vector Pulse Width Modulation)로 변환하는 SV PWM 변환부(19)로 이루어져, 인버터의 유효 전력이 증가하면 증가된 유효 전력을 낮추기 위해 인버터의 출력 전압 주파수를 낮추고 인버터의 무효 전력이 증가하면 증가된 무효 전력을 낮추기 위해 인버터의 출력 전압을 낮춤으 로써 병렬 연결된 2개 이상의 인버터가 부하를 균등하게 분담하도록 한다.

#### (52) CPC특허분류

**HO2M 7/5395** (2013.01)

## 명 세 서

## 청구범위

#### 청구항 1

2개 이상의 인버터가 병렬 연결되었을 때 각각의 인버터가 서로 균등한 전력으로 부하를 분담하도록 하여 각 인버터 간 유효 전력 편차나 무효 전력의 편차로 인해 인버터간 순환 전류가 발생 됨을 방지하고, 상기 각 인버터에는 상기 인버터에 내부 장착되어 H-브릿지(Bridge) 회로를 이용하여 직류 전원을 교류 전원으로 변환하는 IGBT 전력 변환부(3)와, 상기 IGBT 전력 변환부(3)로부터 출력된 PWM 펄스 신호를 필터링(Filtering)하여 정현파 형태로 변환하는 LC 필터부(5)가 갖추어진 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터제어 장치에 있어서,

상기 LC 필터부(5)의 출력단에 연결되어 인버터가 정상 가동될 때에는 스위치 온(On)되어 부하로 전류를 흘려보내는 반면, 인버터에 고장이 발생되었을 때에는 스위치 오프(Off)되어 전류 흐름을 끊는 인버터 스위치 (Inverter Switch)(1)와;

상기 인버터 스위치(1)의 출력단에 연결되어 인버터가 정상 가동될 때에는 스위치 오프(Off)되는 반면, 인버터에 고장이 발생되었을 때에는 스위치 온(On)되어 바이패스(Bypass) 선로(6)로부터 입력된 3상 교류 전원을 부하측으로 공급하는 바이패스 스위치(Bypass Switch)(4);

상기 인버터 스위치(1)가 스위치 온(On)되고 바이패스 스위치(4)가 스위치 오프(Off)된 상태에서 상기 IGBT 전력 변환부(3)로부터 출력되는 인버터 전류와, LC 필터부(5)로부터 인버터 스위치(1)로 전달되는 3상 부하 전압과 3상 부하 전류 그리고 바이패스 선로(6)로부터 출력된 3상 바이패스 전압을 동기 신호 발생부(7)로부터 제공된 동기 신호에 맞춰 DQ 변환하여 DQ 동기 좌표 변환 값으로 변환하는 DQ 변환부(9);

메모리에 저장된 파라미터로부터 제공된 전류 위상각 보상값을 이용하여 상기 DQ 변환부(9)로부터 입력받은 3상부하 전류의 위상각을 보상하고 상기 위상각이 보상된 3상부하 전류와 상기 DQ 변환부(9)로부터 전달된 3상부하 전압을 이용하여 새로운 유효 전력 레퍼런스(Reference) 값(Pref)과 무효 전력 레퍼런스(Reference) 값(Qref)을 계산하고, 인버터의 유효 전력이 증가 되었을 때 상기 유효 전력 레퍼런스 값(Pref)을 이용하여 인버터로부터 출력되는 전압 주파수를 낮추기 위한 유효 전력 드룹(Droop) 신호를 생성하고, 인버터의 무효 전력이 증가 되었을 때 상기 무효 전력 레퍼런스 값을 이용하여 인버터로부터 출력되는 전압을 낮추기 위한 무효 전력 드룹 신호를 생성하는 V/F(Voltage/Frequency) 병렬 드룹(Droop) 제어부(11);

상기 V/F 병렬 드룹 제어부(11)로부터 출력된 무효 전력 드룹 신호가 증가 하면 인버터로부터 출력되는 전압을 낮추기 위한 제어 신호를 DQ 역변환부(13)에 전달하는 전압 전류 제어부(15);

상기 DQ 변환부(9)에 의해 변환된 3상 바이패스 전압의 Q축 전압 신호와 동상인 동기 신호를 발생하는 동기 신호 발생부(7);

상기 V/F 병렬 드룹 제어부(11)로부터 출력된 유효 전력 드룹 신호가 증가 하면 인버터로부터 출력되는 전압 주파수를 낮추기 위한 제어 신호를 DQ 역변환부(13)에 전달하는 주파수 제어부(17);

상기 전압 전류 제어부(15)와 주파수 제어부(17)의 제어 신호에 따라 인버터의 출력 전압과 주파수를 조정하기 위한 지령 신호를 발생하는 DQ 역변환부(13);

및 상기 DQ 역변환부(13)로부터 출력된 지령 신호를 IGBT 전력 변환부(3)의 IGBT(Insulated Gate Bipolar Transistor)를 스위칭시키기 위한 공간 벡터 펄스 폭 변조 신호(SV PWM: Space Vector Pulse Width Modulation)로 변환하는 SV PWM 변환부(19)로 이루어져,

인버터의 유효 전력이 증가하면 증가된 유효 전력을 낮추기 위해 인버터의 출력 전압 주파수를 낮추고 인버터의 무효 전력이 증가하면 증가된 무효 전력을 낮추기 위해 인버터의 출력 전압을 낮춤으로써 병렬 연결된 2개 이상 의 인버터가 부하를 균등하게 분담하도록 하는 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치.

#### 청구항 2

제1 항에 있어서,

상기 V/F 병렬 드룹(Droop) 제어부(11)는 상기 DQ 변환부(9)로부터 3상 부하 전압과 3상 부하 전류에 대한 DQ 동기 좌표 변환 값을 입력받아 부하에 공급되는 유효 전력(P)과 무효 전력(Q)값을 계산하는 PQ 변환부(21)와,

병렬 드룹(Droop) 제어 신호를 만들기 위해 메모리에 저장된 파라미터로부터 제공된 전류 위상각 보상값을 이용하여 상기 DQ 변환부(9)로부터 입력받은 3상 부하 전류의 위상각을 보상하고 상기 위상각이 보상된 3상 부하 전류와 상기 DQ 변환부(9)로부터 전달된 3상 부하 전압를 이용하여 새로운 유효 전력 레퍼런스(Reference) 값(Pref)과 무효 전력 레퍼런스(Reference) 값(Qref)을 계산하는 V/F 드룹(Droop) 위상 오차 보상부(23),

상기 인버터로부터 출력되는 유효 전력이 증가하면, 인버터로부터 출력되는 전압 주파수가 일정 비율로 감소 되도록 제어하기 위해 상기 V/F 드룹 위상 오차 보상부(23)에 의해 계산된 유효 전력 레퍼런스 값(Pref)과 드룹 계수(Kp)를 곱한 값에 현재(n) 샘플링(Sampling)된 유효 전력 레퍼런스 값과 현재 이전(n-1)에 샘플링된 유효 전력 레퍼런스 값 사이의 변화분인 유효 전력 레퍼런스 값 변화분(dPref)과 변화분 드룹 계수(Kpd)를 곱한 값을 더하여 유효 전력 드룹 신호(Pdrp)를 생성하는 유효 전력 드룹(Droop) 신호 생성부(25),

상기 인버터로부터 출력되는 무효 전력이 증가되면, 인버터로부터 출력되는 전압이 일정 비율로 감소 되도록 제어하기 위해 상기 V/F 드룹 위상 오차 보상부(23)에 의해 계산된 무효 전력 레퍼런스 값(Qref)과 드룹 계수(Kq)를 곱한 값에 현재(n) 샘플링(Sampling)된 무효 전력 레퍼런스 값과 현재 이전(n-1)에 샘플링된 무효 전력 레퍼런스 값 사이의 변화분인 무효 전력 레퍼런스 값 변화분(dQref)과 변화분 드룹 계수(Kqd)를 곱한 값을 더하여 무효 전력 드룹 신호(Qdrp)를 생성하는 무효 전력 드룹(Droop) 신호 생성부(27)를 포함하는 것을 특징으로 하는 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치.

#### 청구항 3

제1 항에 있어서,

상기 전압 전류 제어부(15)는 인버터 출력전압 D축 레퍼런스 신호(Vref(d))와 무효 전력 드룹 신호 생성부(27)에서 생성된 무효 전력 드룹 신호(Qdrp) 사이의 오차를 계산하는 제1 D축 오차 계산기(29)와,

상기 제1 D축 오차 계산기(29)의 출력 신호와 DQ 변환부(9)에 의해 변환된 3상 부하 전압의 D축 전압 신호 (Vlde) 사이의 오차를 계산하는 제2 D축 오차 계산기(31),

상기 제2 D축 오차 계산기(31)로부터 출력된 신호를 비례 적분제어하여 인버터 전류 D축 레퍼런스 신호를 생성하는 D축 전압 제어부(33)와,

현재 타임(Time)에 IGBT 전력 변환부(3)의 출력단으로부터 샘플링(Sampling)된 3상 인버터 전압의 D축 전압 평균값에 게인(Gain)값을 곱한 D축 전향 보상값을 저장하고, 현재 타임(Time)의 한 주기 또는 반 주기 이전에 저장된 D축 전향 보상값을 호출하여 D축 가감산부(36)로 출력하는 D축 반복 제어부(35),

상기 D축 전압 제어부(33)로부터 출력된 신호에 D축 반복 제어부(35)로부터 출력된 신호를 가산한 다음, DQ 변환부(9)에 의해 변환된 3상 인버터 전류의 D축 전류 신호(Iide)를 감산하는 D축 가감산부(36),

상기 D축 가감산부(36)로부터 출력된 신호를 비례 적분제어하여 보상 값을 얻는 D축 전류 제어부(39),

상기 인버터 출력전압 D축 레퍼런스 신호(Vref(d))와 D축 전류 제어부(39)로부터 출력된 보상값을 가산하여 최종 D축 전압 제어 신호(Vdref)를 생성하는 D축 가산기(41),

상기 인버터 출력전압 Q축 레퍼런스 신호(Vref(q))와 DQ 변환부(9)에 의해 변환된 3상 부하 전압의 Q축 전압 신호(Vlqe) 사이의 오차를 계산하는 제1 Q축 오차 계산기(43),

상기 제1 Q축 오차 계산기(43)로부터 출력된 신호를 비례 적분제어하여 인버터 전류 Q축 레퍼런스 신호를 생성하는 Q축 전압 제어부(45),

현재 타임(Time)에 IGBT 전력 변환부(3)의 출력단으로부터 샘플링(Sampling)된 3상 인버터 전압의 Q축 전압 평균값에 게인(Gain)값을 곱한 Q축 전향 보상값을 저장하고, 현재 타임(Time)의 한 주기 또는 반 주기 이전에 저

장된 Q축 전향 보상값을 호출하여 Q축 가감산부(48)로 출력하는 Q축 반복 제어부(47),

상기 Q축 전압 제어부(45)로부터 출력된 신호에 Q축 반복 제어부(47)로부터 출력된 신호를 가산한 다음, DQ 변환부(9)에 의해 변환된 3상 인버터 전류의 Q축 전류 신호(Iide)를 감산하는 Q축 가감산부(48),

상기 Q축 가감산부(48)로부터 출력된 신호를 비례 적분제어하여 최종 Q축 전압 제어 신호(Vqref)를 생성하는 Q축 전류 제어부(51)를 포함하는 것을 특징으로 하는 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치.

#### 청구항 4

제3 항에 있어서,

상기 D축 전류 제어부(39)의 출력단에는 LC 필터부(5)의 공진 이득을 상쇄시키기 위해 LC 필터부(5)의 공진 극점 이득과 서로 반대가 되는 주파수 특성을 이용하여 D축 전류 제어부(39)의 출력단으로부터 출력되는 LC 필터부(5)의 공진 주파수를 억제하는 D축 노치 필터(55)(Notch Filter)가 부가 장착되고,

상기 Q축 전류 제어부(51)의 출력단에는 LC 필터부(5)의 공진 이득을 상쇄시키기 위해 LC 필터부(5)의 공진 극점 이득과 서로 반대되는 주파수 특성을 이용하여 Q축 전류 제어부(51)의 출력단으로부터 출력되는 LC 필터부(5)의 공진 주파수를 억제하는 Q축 노치 필터(57)(Notch Filter)를 더 포함하는 것을 특징으로 하는 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치.

#### 청구항 5

2개 이상의 인버터가 병렬 연결되었을 때 각각의 인버터가 서로 균등한 전력으로 부하를 분담하도록 하여 각 인 버터 간 유효 전력 편차나 무효 전력의 편차로 인해 인버터간 순환 전류가 발생됨을 방지하고,

상기 각 인버터에는 상기 인버터에 내부 장착되어 H-브릿지(Bridge) 회로를 이용하여 직류 전원을 교류 전원으로 변환하는 IGBT 전력 변환부(3)와,

상기 IGBT 전력 변환부(3)로부터 출력된 PWM 펄스 신호를 필터링(Filtering)하여 정현파 형태로 변환하는 LC 필터부(5),

상기 LC 필터부(5)의 출력단에 연결되어 인버터가 정상 가동될 때에는 스위치 온(On)되어 부하로 전류를 흘려보내는 반면, 인버터에 고장이 발생되었을 때에는 스위치 오프(Off)되어 전류 흐름을 끊는 인버터 스위치 (Inverter Switch)(1),

상기 인버터 스위치(1)의 출력단에 연결되어 인버터가 정상 가동될 때에는 스위치 오프(Off)되는 반면, 인버터에 고장이 발생되었을 때에는 스위치 온(On)되어 바이패스(Bypass) 선로로부터 입력된 3상 교류 전원을 부하측으로 공급하는 바이패스 스위치(Bypass Switch)(4)가 구비된 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬운전 인버터 제어 방법에 있어서,

상기 인버터 스위치(1)가 스위치 온(0n)되고 바이패스 스위치(4)가 스위치 오프(0ff)된 상태에서 상기 인버터에 설치된 DQ 변환부(9)가 상기 IGBT 전력 변환부(3)로부터 출력되는 인버터 전류와, LC 필터부(5)로부터 인버터 스위치(1)로 전달되는 3상 부하 전압과 3상 부하 전류 그리고 바이패스 선로(6)로부터 출력된 3상 바이패스 전압을 동기 신호 발생부(7)로부터 제공된 동기 신호에 맞춰 DQ 변환하여 DQ 동기 좌표 변환 값으로 변환하는 단계(S1)와;

상기 인버터에 설치된 V/F(Voltage/Frequency) 병렬 드룹(Droop) 제어부(11)가 메모리에 저장된 파라미터로부터 제공된 전류 위상각 보상값을 이용하여 상기 DQ 변환부(9)로부터 입력받은 3상 부하 전류의 위상각을 보상하고 상기 위상각이 보상된 부하 전류와 상기 DQ 변환부(9)로부터 전달된 3상 부하 전압을 이용하여 새로운 유효 전력 레퍼런스(Reference) 값(Pref)과 무효 전력 레퍼런스(Reference) 값(Qref)을 계산하고, 인버터의 유효 전력 이 증가하면 상기 유효 전력 레퍼런스 값(Pref)을 이용하여 인버터로부터 출력되는 전압 주파수를 낮추기 위한 유효 전력 드룹(Droop) 신호를 생성하고, 인버터의 무효 전력이 증가하면 상기 무효 전력 레퍼런스 값을 이용하여 인버터로부터 출력되는 전압을 낮추기 위한 무효 전력 드룹 신호를 생성하는 단계(S2);

상기 인버터에 설치된 전압 전류 제어부(15)가 상기 V/F 병렬 드룹 제어부(11)로부터 출력된 무효 전력 드룹 신호가 증가하면 인버터로부터 출력되는 전압을 낮추기 위한 제어 신호를 DQ 역변환부(13)에 전달하는 단계(S3);

상기 인버터에 설치된 동기 신호 발생부(7)가 상기 DQ 변환부(9)에 의해 변환된 3상 바이패스 전압의 Q축 전압 신호와 동상인 동기 신호를 발생하는 단계(S4);

상기 인버터에 설치된 주파수 제어부(17)가 상기 V/F 병렬 드룹 제어부(11)로부터 출력된 유효 전력 드룹 신호가 증가하면 인버터로부터 출력되는 전압 주파수를 낮추기 위한 제어 신호를 DQ 역변환부(13)에 전달하는 단계(S5);

상기 DQ 역변환부(13)가 상기 전압 전류 제어부(15)와 주파수 제어부(17)의 제어 신호에 따라 인버터의 출력 전 압과 주파수를 조정하기 위한 지령 신호를 발생하는 단계(S6);

상기 인버터에 설치된 SV PWM 변환부(19)가 상기 DQ 역변환부(13)로부터 출력된 지령 신호를 IGBT 전력 변환부(3)의 IGBT(Insulated Gate Bipolar Transistor)를 스위칭시키기 위한 공간 벡터 펼스 폭 변조 신호(SV PWM: Space Vector Pulse Width Modulation)로 변환하는 단계(S7)로 이루어져,

인버터의 유효 전력이 증가하면 증가된 유효 전력을 낮추기 위해 인버터의 출력 전압 주파수를 낮추고, 인버터의 무효 전력이 증가하면 증가 된 무효 전력을 낮추기 위해 인버터의 출력 전압을 낮춤으로써 병렬 연결된 2개이상의 인버터가 부하를 균등하게 분담하도록 하는 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 방법.

#### 청구항 6

제 5항에 있어서,

상기 인버터에 설치된 V/F(Voltage/Frequency) 병렬 드룹(Droop) 제어부(11)가 메모리에 저장된 파라미터로부터 제공된 전류 위상각 보상값을 이용하여 상기 DQ 변환부(9)로부터 입력받은 3상 부하 전류의 위상각을 보상하고 상기 위상각이 보상된 3상 부하 전류와 상기 DQ 변환부(9)로부터 전달된 3상 부하 전압을 이용하여 새로운 유효 전력 레퍼런스(Reference) 값(Pref)과 무효 전력 레퍼런스(Reference) 값(Qref)을 계산하고, 인버터의 유효 전력이 증가하면 상기 유효 전력 레퍼런스 값(Pref)을 이용하여 인버터로부터 출력되는 전압 주파수를 낮추기 위한 유효 전력 드룹(Droop) 신호를 생성하고, 인버터의 무효 전력이 증가하면 상기 무효 전력 레퍼런스 값을 이용하여 인버터로부터 출력되는 전압을 낮추기 위한 무효 전력 드룹 신호를 생성하는 단계(S2)는

상기 V/F 병렬 드룹(Droop) 제어부(11)에 갖추어진 PQ 변환부(21)가 상기 DQ 변환부(9)로부터 3상 부하 전압과 3상 부하 전류에 대한 DQ 동기 좌표 변환 값을 입력받아 부하에 공급되는 유효 전력(P)과 무효 전력(Q)값을 계산하는 단계와;

상기 V/F 병렬 드룹(Droop) 제어부(11)에 갖추어진 V/F 드룹(Droop) 위상 오차 보상부(23)가 병렬 드룹(Droop) 제어 신호를 만들기 위해 메모리에 저장된 파라미터로부터 제공된 전류 위상각 보상값을 이용하여 상기 DQ 변환부(9)로부터 입력받은 3상 부하 전류의 위상각을 보상하고 상기 위상각이 보상된 부하 전류와 상기 DQ 변환부(9)로부터 전달된 3상 부하 전압을 이용하여 새로운 유효 전력 레퍼런스(Reference) 값(Pref)과 무효 전력 레퍼런스(Reference) 값(Qref)을 계산하는 단계;

상기 V/F 병렬 드룹(Droop) 제어부(11)에 갖추어진 유효 전력 드룹(Droop) 신호 생성부(25)가 상기 인버터로부터 출력되는 유효 전력이 증가하면, 인버터로부터 출력되는 전압 주파수가 일정 비율로 감소 되도록 제어하기 위해 상기 V/F 드룹 위상 오차 보상부(23)에 의해 계산된 유효 전력 레퍼런스 값(Pref)과 드룹 계수(Kp)를 곱한 값에 현재(n) 샘플링(Sampling)된 유효 전력 레퍼런스 값과 현재 이전(n-1)에 샘플링된 유효 전력 레퍼런스 값 사이의 변화분인 유효 전력 레퍼런스 값 변화분(dPref)과 변화분 드룹 계수(Kpd)를 곱한 값을 더하여 유효 전력 드룹 신호(Pdrp)를 생성하는 단계;

상기 V/F 병렬 드룹(Droop) 제어부(11)에 갖추어진 무효 전력 드룹(Droop) 신호 생성부(27)가 상기 인버터로부터 출력되는 무효 전력이 증가되면, 인버터로부터 출력되는 전압이 일정 비율로 감소 되도록 제어하기 위해 상기 V/F 드룹 위상 오차 보상부(23)에 의해 계산된 무효 전력 레퍼런스 값(Qref)과 드룹 계수(Kq)를 곱한 값에 현재(n) 샘플링(Sampling)된 무효 전력 레퍼런스 값과 현재 이전(n-1)에 샘플링된 무효 전력 레퍼런스 값 사이의 변화분인 무효 전력 레퍼런스 값 변화분(dQref)과 변화분 드룹 계수(Kqd)를 곱한 값을 더하여 무효 전력 드

룹 신호(Qdrp)를 생성하는 단계로 이루어진 것을 특징으로 하는 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 방법.

#### 청구항 7

제5 항에 있어서,

상기 인버터에 설치된 전압 전류 제어부(15)가 상기 V/F 병렬 드룹 제어부(11)로부터 출력된 무효 전력 드룹 신호가 증가하면 인버터로부터 출력되는 전압을 낮추기 위한 제어 신호를 DQ 역변환부(13)에 전달하는 단계(S3)는

상기 전압 전류 제어부(15)에 갖추어진 제1 D축 오차 계산기(29)가 인버터 출력전압 D축 레퍼런스 신호 (Vref(d))와 무효 전력 드룹 신호 생성부(27)에서 생성된 무효 전력 드룹 신호(Qdrp) 사이의 오차를 계산하는 단계와;

상기 전압 전류 제어부(15)에 갖추어진 제2 D축 오차 계산기(31)가 상기 제1 D축 오차 계산기(29)의 출력 신호 와 DQ 변환부(9)에 의해 변환된 3상 부하 전압의 D축 전압 신호(Vlde) 사이의 오차를 계산하는 단계;

상기 전압 전류 제어부(15)에 갖추어진 D축 전압 제어부(33)가 상기 제2 D축 오차 계산기(31)로부터 출력된 신호를 비례 적분제어하여 인버터 전류 D축 레퍼런스 신호를 생성하는 단계;

상기 전압 전류 제어부(15)에 갖추어진 D축 반복 제어부(35)가 현재 타임(Time)에 IGBT 전력 변환부(3)의 출력 단으로부터 샘플링(Sampling)된 3상 인버터 전압의 D축 전압 평균값에 게인(Gain)값을 곱한 D축 전향 보상값을 저장하고, 현재 타임(Time)의 한 주기 또는 반 주기 이전에 저장된 D축 전향 보상값을 호출하여 D축 가감산부(36)로 출력하는 단계;

상기 전압 전류 제어부(15)에 갖추어진 D축 가감산부(36)가 상기 D축 전압 제어부(33)로부터 출력된 신호에 D축 반복 제어부(35)로부터 출력된 신호를 가산한 다음, DQ 변환부(9)에 의해 변환된 3상 인버터 전류의 D축 전류 신호(Iide)를 감산하는 단계;

상기 전압 전류 제어부(15)에 갖추어진 D축 전류 제어부(39)가 상기 D축 가감산부(36)로부터 출력된 신호를 비례 적분제어하여 보상값을 얻는 단계;

상기 전압 전류 제어부(15)에 갖추어진 D축 가산기(41)가 상기 인버터 출력전압 D축 레퍼런스 신호(Vref(d))와 D축 전류 제어부(39)로부터 출력된 보상값을 가산하여 최종 D축 전압 제어 신호(Vdref)를 생성하는 단계;

상기 전압 전류 제어부(15)에 갖추어진 제1 Q축 오차 계산기(43)가 상기 인버터 출력전압 Q축 레퍼런스 신호 (Vref(q))와 DQ 변환부(9)에 의해 변환된 3상 부하 전압의 Q축 전압 신호(Vlqe) 사이의 오차를 계산하는 단계;

상기 전압 전류 제어부(15)에 갖추어진 Q축 전압 제어부(45)가 상기 제1 Q축 오차 계산기(43)로부터 출력된 신호를 비례 적분제어하여 인버터 전류 Q축 레퍼런스 신호를 생성하는 단계;

상기 전압 전류 제어부(15)에 갖추어진 Q축 반복 제어부(47)가 현재 타임(Time)에 IGBT 전력 변환부(3)의 출력 단으로부터 샘플링(Sampling)된 3상 인버터 전압의 Q축 전압 평균값에 게인(Gain)값을 곱한 Q축 전향 보상값을 저장하고, 현재 타임(Time)의 한 주기 또는 반 주기 이전에 저장된 Q축 전향 보상값을 호출하여 Q축 가감산부(48)로 출력하는 단계;

상기 전압 전류 제어부(15)에 갖추어진 Q축 가감산부(48)가 상기 Q축 전압 제어부(45)로부터 출력된 신호에 Q축 반복 제어부(47)로부터 출력된 신호를 가산한 다음, DQ 변환부(9)에 의해 변환된 3상 인버터 전류의 Q축 전류 신호(Iide)를 감산하는 단계;

상기 전압 전류 제어부(15)에 갖추어진 Q축 전류 제어부(51)가 상기 Q축 가감산부(48)로부터 출력된 신호를 비례 적분제어하여 최종 Q축 전압 제어 신호(Vqref)를 생성하는 단계로 이루어진 것을 특징으로 하는 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 방법.

### 발명의 설명

#### 기술분야

[0001] 본 발명은 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치 및 제어 방법에 관한 것으

로, 보다 상세하게는, 2개 이상의 인버터들을 병렬 연결하였을 때 각 인버터들 간 부하 분담률을 1대1로 자동조정함으로써 각 인버터들 간 유효 전력과 무효 전력 편차를 없애 인버터 간 전력 편차로 인해 발생 될 수 있는 순환 전류를 억제할 수 있는 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치 및 제어 방법에 관한 것이다.

## 배경기술

- [0003] 일반적으로, 인버터의 용량을 확대하기 위한 방법으로는 인버터 내 파워 소자의 전압 및 전류 용량을 증대하여 새로운 제품을 설계하는 방법과 기존에 개발된 인버터를 병렬 구성하여 설계하는 방법이 있다.

- [0004] 산업용 인버터의 경우 파워소자의 제한된 전압 및 전류 용량으로 인해 대용량 인버터를 개발하는 것에는 한계가 있으므로, 최근 병렬 구조 인버터가 많이 설계되는 추세이다.

- [0005] 상기 2개 이상의 인버터를 병렬 연결하는 방식은 필요에 따라 인버터를 추가하거나 변경 또는 제거함으로써 전력 변환 용량을 조절할 수 있고, 인버터에 장애가 발생 되었을 때에는 고장이 난 인버터를 교체하여 전력 시스템을 정상화할 수도 있다.

- [0006] 한편, 상기 인버터로부터 출력되는 교류 전원에는 고조파 성분이 포함될 수 있는데, 종래의 인버터는 상기 고조파 성분을 감쇄하기 위해 고조파 분석법을 이용하여 고조파 성분을 분석한 다음, 고조파 보상 제어 방법을 이용하여 고조파를 감쇄하고 있다.

- [0007] 상기 고조파 보상 제어 방법은 각 고조파 차수별로 고조파 크기와 위상을 구한 다음, 각 고조파를 영('0')으로 제어하는 방법이다.

- [0008] 하지만, 상기 고조파 보상 제어 방법은 고조파를 감쇄하는 제어기 개수가 고조파 차수별로 구성되어야 함으로 계산량이 많고, 인버터에 연결되는 부하 특성에 따라 왜란으로부터 민감하게 동작할 수 있어, 고조파 보상 계수 가 부하특성에 의해 변화되어야 한다는 문제점이 있었다.

- [0009] 한편, 종래의 인버터는 인버터의 출력단에 설치된 LC 필터부의 커패시터 전류를 센싱(Sensing)한 다음, 센싱 결과에 따라 인버터 출력 전압이나 출력 전류를 보상 제어해야 함으로 LC 필터부에 전류 센싱 모듈이 추가되어야한다는 문제점도 있었다.

- [0010] 또한, 상기 인버터를 2개 이상 병렬 연결하였을 때에는 각 인버터마다 인버터 구성 부품의 특성 편차가 존재할 수 있고, 부하 특성에 영향을 받는 전력 라인의 임피던스 영향, 그리고, 각 구성 부품의 온도 변화 특성의 상이 함으로 인해 각 인버터들이 부하로 공급되는 유효 전력과, 무효 전력을 1 대 1로 균등하게 분담할 수 없다는 문제점이 있었다.

- [0011] 이때, 각 인버터들간에 유효 전력과 무효 전력 편차가 발생 되면 인버터 상호간 순환 전류가 발생 되고 상기 순환 전류로 인해 인버터로부터 과전류가 발생될 수 있다는 문제점이 있었다.

- [0012] 한편, 2개 이상이 병렬 연결된 인버터 간 유효 전력과 무효 전력 편차를 최소화하기 위해 V/F 드룹 기반의 인버터 병렬 운전이 개발되었는데, 상기 V/F(Voltage/Frequency) 드룹(Droop) 기반의 인버터 병렬 운전은 단지 부하 측으로부터 계산된 전압 값과 전류 값을 이용하여 유효 전력과 무효 전력 편차를 보상함으로써 병렬 연결된 인버터 간 파워 정보 교환 없이도 병렬 운전이 가능한 방식이다.

- [0013] 하지만, 종래의 V/F 드룹 기반의 인버터 병렬 운전은 각 인버터 별 유효 전력과 무효 전력 편차를 보상하기 위해 부하측으로부터 계산된 전압 값과 전류 값을 그대로 이용할 경우 각 인버터별 유효 전력과 무효 전력 편차가일어난 시간부터 유효 전력과 무효 전력 편차가 보상되기까지의 시간이 오래 걸려 인버터의 병렬 운전 상태가불안정하다는 문제점이 있었다.

- [0014] 한편, 본 발명의 선행 기술로는 특허등록번호 "10-1639825"호의 "인버터의 전류 제어 장치"가 출원되어 등록되었는데, 상기 인버터의 전류 제어 장치는 계통의 3상 전압을 D축 전압 및 Q축 전압으로 변환하고, 상기 변환된 D축 전압 및 Q축 전압을 계통 전압의 주파수에 따라 회전 변환하여 제1 D축 전압 및 제1 Q축 전압을 출력하는 제1 회전 변환기와; 상기 제1 회전 변환기에 의해 출력되는 제1 D축 전압 과 제1 Q축 전압으로부터 고조파 신호를 제거하여 제2 D축 전압과 제2 Q축 전압을 출력하는 저역 통과 필터; 상기 d-q 변환 및 회전 변환기와 저역통과필터의 출력 신호를 감산하는 감산기; 상기 감산기의 출력 신호에 대해 정회전 및 역회전 변환하여 위상 지연만큼 앞선 위상을 갖는 제3 D축 전압 및 제3 Q축 전압을 검출하는 제2 회전 변환기; 상기 제2 및 3 D축 전압을 이용하여 D축 계통 전압을 검출하고, 상기 검출된 D축 계통 전압을 이용하여 부하로 공급될 D축 구동 전압을 생

성하는 D축 전류 제어기; 및 상기 제2 및 3 Q축 전압을 이용하여 Q축 계통 전압을 검출하고, 상기 검출된 Q축 계통 전압을 이용하여 부하로 공급될 Q축 구동 전압을 생성하는 Q축 전류 제어기를 포함한다.

### 선행기술문헌

### 특허문헌

[0016] (특허문헌 0001) 대한민국 특허등록번호 10-1639825 (2016.07.14)

(특허문헌 0002) 대한민국 특허등록번호 10-1763071 (2017.07.31)

## 발명의 내용

[0018]

[0020]

## 해결하려는 과제

[0017] 이에 본 발명은 상기 문제점을 해결하기 위하여 종래보다 간단한 제어 방법으로 인버터로부터 출력되는 각 차수의 고조파 성분을 감쇄함과 동시에 2개 이상의 인버터가 병렬 연결된 상태에서 구동될 때 부하 불평형으로 인한부하 전압의 불균형 현상을 보상할 수 있고, V/F 드룹(Voltage/Frequency Droop) 제어시 유효 전력과 무효 전력의 편차를 보다 빠르게 보상하여 인버터의 부하 분담 특성을 향상시킬 수 있는 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치 및 제어 방법을 제공하는데 본 발명의 목적이 있다.

또한, 본 발명의 또 다른 목적은 여러 대의 인버터가 병렬 운전시 각 인버터로부터 발생될 수 있는 유효 전력과 무효 전력 편차를 보다 빠르게 보상함으로써 인버터의 병렬 운전 상태를 보다 안정화시킬 수 있는 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치 및 제어 방법을 제공하는 것이다.

#### 과제의 해결 수단

상기 목적을 달성하기 위한 본 발명에 따른 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제 어 장치는 2개 이상의 인버터가 병렬 연결되었을 때 각각의 인버터가 서로 균등한 전력으로 부하를 분담하도록 하여 각 인버터 간 유효 전력 편차나 무효 전력의 편차로 인해 인버터간 순환 전류가 발생 됨을 방지하고, 상기 각 인버터에는 상기 인버터에 내부 장착되어 H-브릿지(Bridge) 회로를 이용하여 직류 전원을 교류 전원으로 변 환하는 IGBT 전력 변환부(3)와, 상기 IGBT 전력 변환부(3)로부터 출력된 PWM 펼스 신호를 필터링(Filtering)하 여 정현파 형태로 변환하는 LC 필터부(5)가 갖추어진 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치에 있어서, 상기 LC 필터부(5)의 출력단에 연결되어 인버터가 정상 가동될 때에는 스위치 온 (On)되어 부하로 전류를 흘려보내는 반면, 인버터에 고장이 발생되었을 때에는 스위치 오프(Off)되어 전류 흐름 을 끊는 인버터 스위치(Inverter Switch)(1)와; 상기 인버터 스위치(1)의 출력단에 연결되어 인버터가 정상 가 동될 때에는 스위치 오프(Off)되는 반면, 인버터에 고장이 발생되었을 때에는 스위치 온(On)되어 바이패스 (Bypass) 선로로부터 입력된 3상 교류 전원을 부하측으로 공급하는 바이패스 스위치(Bypass Switch)(4); 상기 인버터 스위치(1)가 스위치 온(On)되고 바이패스 스위치(4)가 스위치 오프(Off)된 상태에서 상기 IGBT 전력 변 환부(3)로부터 출력되는 인버터 전류와, LC 필터부(5)로부터 인버터 스위치(1)로 전달되는 3상 부하 전압과 3상 부하 전류 그리고 바이패스 선로(6)로부터 출력된 3상 바이패스 전압을 동기 신호 발생부(7)로부터 제공된 동기 신호에 맞춰 DQ 변환하여 DQ 동기 좌표 변환 값으로 변환하는 DQ 변환부(9); 메모리에 저장된 파라미터로부터 제공된 전류 위상각 보상값을 이용하여 상기 DQ 변환부(9)로부터 입력받은 3상 부하 전류의 위상각을 보상하고 상기 위상각이 보상된 3상 부하 전류와 상기 DQ 변환부(9)로부터 전달된 3상 부하 전압을 이용하여 새로운 유효 전력 레퍼런스(Reference) 값(Pref)과 무효 전력 레퍼런스(Reference) 값(Qref)을 계산하고, 인버터의 유효 전 력이 증가하면 상기 유효 전력 레퍼런스 값(Pref)을 이용하여 인버터로부터 출력되는 전압 주파수를 낮추기 위 한 유효 전력 드룹(Droop) 신호를 생성하고, 인버터의 무효 전력이 증가하면 상기 무효 전력 레퍼런스 값을 이 용하여 인버터로부터 출력되는 전압을 낮추기 위한 무효 전력 드룹 신호를 생성하는 V/F(Voltage/Frequency) 병 렬 드룹(Droop) 제어부(11); 상기 V/F 병렬 드룹 제어부(11)로부터 출력된 무효 전력 드룹 신호가 증가하면 인 버터로부터 출력되는 전압을 낮추기 위한 제어 신호를 DQ 역변환부(13)에 전달하는 전압 전류 제어부(15); 상기 DQ 변환부(9)에 의해 변환된 3상 바이패스 전압의 Q축 전압 신호와 동상인 동기 신호를 발생하는 동기 신호 발 생부(7); 상기 V/F 병렬 드룹 제어부(11)로부터 출력된 유효 전력 드룹 신호가 증가하면 인버터로부터 출력되는 전압 주파수를 낮추기 위한 제어 신호를 DQ 역변환부(13)에 전달하는 주파수 제어부(17); 상기 전압 전류 제어

부(15)와 주파수 제어부(17)의 제어 신호에 따라 인버터의 출력 전압과 주파수를 조정하기 위한 지령 신호를 발생하는 DQ 역변환부(13); 및 상기 DQ 역변환부(13)로부터 출력된 지령 신호를 IGBT 전력 변환부(3)의 IGBT(Insulated Gate Bipolar Transistor)를 스위칭시키기 위한 공간 벡터 펄스 폭 변조 신호(SV PWM: Space Vector Pulse Width Modulation)로 변환하는 SV PWM 변환부(19)로 이루어져, 인버터의 유효 전력이 증가하면 증가된 유효 전력을 낮추기 위해 인버터의 출력 전압 주파수를 낮추고 인버터의 무효 전력이 증가하면 증가된 무효 전력을 낮추기 위해 인버터의 출력 전압을 낮춤으로써 병렬 연결된 2개 이상의 인버터가 부하를 균등하게 분담하도록 한다.

#### 발명의 효과

- [0022] 이러한 구조로 이루어진 본 발명에 따른 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치 및 제어 방법은 2개 이상의 인버터가 병렬 연결되고 2개 이상의 인버터에 부하가 공통으로 연결되었을 때, 인버터의 유효 전력이 증가하면 인버터로부터 출력되는 전압 주파수를 낮춰 증가된 유효 전력을 낮추고, 인버터의 무효 전력이 증가하면 인버터로부터 출력되는 전압을 낮춰 증가된 무효 전력을 낮추게 된다.

- [0023] 결과적으로, 인버터의 유효 전력과 무효 전력을 일정하게 유지함으로써 인버터간 유효 전력 편차와 무효 전력 편차로 인해 발생 될 수 있는 순환 전류에 의해 인버터로부터 과전류가 출력됨을 억제할 수 있다.

- [0024] 따라서, 본 발명에 따른 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치 및 제어 방법은 2개 이상의 인버터가 병렬 연결된 상태에서 운전될 때 부하 불평형으로 인한 부하 전압의 불균형 현상을 보상할 수 있고, V/F 드룹(Voltage/Frequency Droop) 제어시 유효 전력과 무효 전력의 편차를 보상하여 인버터의 부하 분담 특성을 향상시킬 수 있다.

- [0025] 또한, 본 발명은 여러 대의 인버터가 병렬 운전시 각 인버터로부터 발생 될 수 있는 유효 전력과 무효 전력 편 차를 보다 빠르게 보상함으로써 인버터의 병렬 운전 상태를 보다 안정화시킬 수 있다.

#### 도면의 간단한 설명

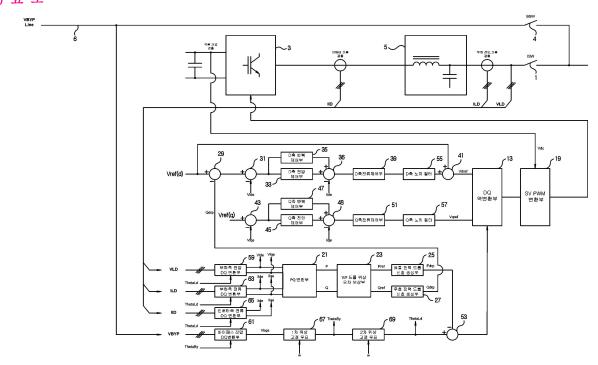

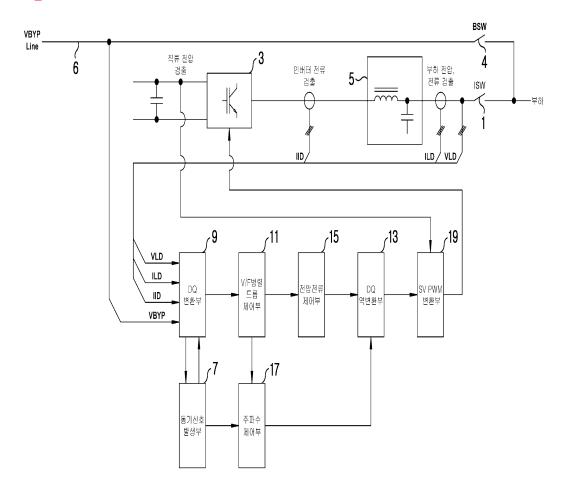

[0027] 도면 1은 본 발명에 따른 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치의 제어 블록도.

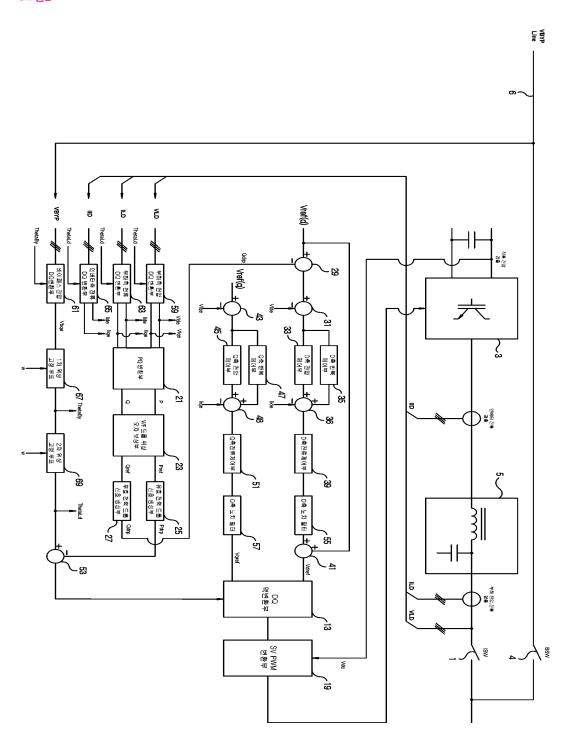

도면 2는 도면 1에 도시한 각 구성 요소를 구체화한 제어 블록도,

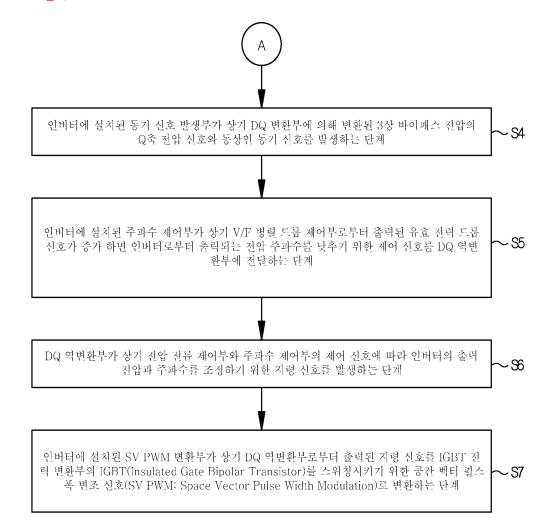

도면 3a 내지 도면 3b는 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 방법의 제어 흐름도,

## 발명을 실시하기 위한 구체적인 내용

- [0028] 이하, 첨부된 도면을 참조하여 본 발명을 자세히 설명한다.

- 본 발명에 따른 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치는 도면 1에 도시한 [0029] 바와 같이, 2개 이상의 인버터가 병렬 연결되었을 때 각각의 인버터가 서로 균등한 전력으로 부하를 분담하도록 하여 각 인버터 간 유효 전력 편차나 무효 전력의 편차로 인해 인버터간 순환 전류가 발생됨을 방지하고, 상기 각 인버터에는 상기 인버터에 내부 장착되어 H-브릿지(Bridge) 회로를 이용하여 직류 전원을 교류 전원으로 변 환하는 IGBT 전력 변환부(3)와, 상기 IGBT 전력 변환부(3)로부터 출력된 PWM 펄스 신호를 필터링(Filtering)하 여 정현파 형태로 변환하는 LC 필터부(5)가 갖추어진 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치에 있어서, 상기 LC 필터부(5)의 출력단에 연결되어 인버터가 정상 가동될 때에는 스위치 온 (On)되어 부하로 전류를 흘려보내는 반면, 인버터에 고장이 발생되었을 때에는 스위치 오프(Off)되어 전류 흐름 을 끊는 인버터 스위치(Inverter Switch)(1)와; 상기 인버터 스위치(1)의 출력단에 연결되어 인버터가 정상 가 동될 때에는 스위치 오프(Off)되는 반면, 인버터에 고장이 발생되었을 때에는 스위치 온(On)되어 바이패스 (Bypass) 선로로부터 입력된 3상 교류 전원을 부하측으로 공급하는 바이패스 스위치(Bypass Switch)(4); 상기 인버터 스위치(1)가 스위치 온(On)되고 바이패스 스위치(4)가 스위치 오프(Off)된 상태에서 상기 IGBT 전력 변 환부(3)로부터 출력되는 인버터 전류와, LC 필터부(5)로부터 인버터 스위치(1)로 전달되는 3상 부하 전압과 3상 부하 전류 그리고 바이패스 선로(6)로부터 출력된 3상 바이패스 전압을 동기 신호 발생부(7)로부터 제공된 동기 신호에 맞춰 DQ 변환하여 DQ 동기 좌표 변환 값으로 변환하는 DQ 변환부(9); 메모리에 저장된 파라미터로부터 제공된 전류 위상각 보상값을 이용하여 상기 DQ 변환부(9)로부터 입력받은 3상 부하 전류의 위상각을 보상하고

상기 위상각이 보상된 3상 부하 전류와 상기 DQ 변환부(9)로부터 전달된 3상 부하 전압을 이용하여 새로운 유효

전력 레퍼런스(Reference) 값(Pref)과 무효 전력 레퍼런스(Reference) 값(Qref)을 계산하고, 인버터의 유효 전 력이 증가하면 상기 유효 전력 레퍼런스 값(Pref)을 이용하여 인버터로부터 출력되는 전압 주파수를 낮추기 위 한 유효 전력 드룹(Droop) 신호를 생성하고, 인버터의 무효 전력이 증가하면 상기 무효 전력 레퍼런스 값을 이 용하여 인버터로부터 출력되는 전압을 낮추기 위한 무효 전력 드룹 신호를 생성하는 V/F(Voltage/Frequency) 병 렬 드룹(Droop) 제어부(11); 상기 V/F 병렬 드룹 제어부(11)로부터 출력된 무효 전력 드룹 신호가 증가하면 인 버터로부터 출력되는 전압을 낮추기 위한 제어 신호를 DQ 역변환부(13)에 전달하는 전압 전류 제어부(15); 상기 DQ 변환부(9)에 의해 변환된 3상 바이패스 전압의 Q축 전압 신호와 동상인 동기 신호를 발생하는 동기 신호 발 생부(7); 상기 V/F 병렬 드룹 제어부(11)로부터 출력된 유효 전력 드룹 신호가 증가하면 인버터로부터 출력되는 전압 주파수를 낮추기 위한 제어 신호를 DQ 역변환부(13)에 전달하는 주파수 제어부(17); 상기 전압 전류 제어 부(15)와 주파수 제어부(17)의 제어 신호에 따라 인버터의 출력 전압과 주파수를 조정하기 위한 지령 신호를 발 생하는 DQ 역변환부(13); 및 상기 DQ 역변환부(13)로부터 출력된 지령 신호를 IGBT 전력 변환부(3)의 IGBT(Insulated Gate Bipolar Transistor)를 스위칭시키기 위한 공간 벡터 펄스 폭 변조 신호(SV PWM: Space Vector Pulse Width Modulation)로 변환하는 SV PWM 변환부(19)로 이루어져, 인버터의 유효 전력이 증가하면 증가된 유효 전력을 낮추기 위해 인버터의 출력 전압 주파수를 낮추고 인버터의 무효 전력이 증가하면 증가된 무효 전력을 낮추기 위해 인버터의 출력 전압을 낮춤으로써 병렬 연결된 2개 이상의 인버터가 부하를 균등하게 분담하도록 한다.

[0030] 상기 V/F 병렬 드룹(Droop) 제어부(11)는 도면 2에 도시한 바와 같이, 상기 DQ 변환부(9)로부터 3상 부하 전압 과 3상 부하 전류에 대한 DQ 동기 좌표 변환 값을 입력받아 부하에 공급되는 유효 전력(P)과 무효 전력(Q)값을 계산하는 PQ 변환부(21)와, 병렬 드룹(Droop) 제어 신호를 만들기 위해 메모리에 저장된 파라미터로부터 제공된 전류 위상각 보상값을 이용하여 상기 DQ 변환부(9)로부터 입력받은 3상 부하 전류의 위상각을 보상하고 상기 위 상각이 보상된 3상 부하 전류와 상기 DQ 변환부(9)로부터 전달된 3상 부하 전압를 이용하여 새로운 유효 전력 레퍼런스(Reference) 값(Pref)과 무효 전력 레퍼런스(Reference) 값(Qref)을 계산하는 V/F 드룹(Droop) 위상 오차 보상부(23), 상기 인버터로부터 출력되는 유효 전력이 증가하면, 인버터로부터 출력되는 전압 주파수가 일 정 비율로 감소 되도록 제어하기 위해 상기 V/F 드룹 위상 오차 보상부(23)에 의해 계산된 유효 전력 레퍼런스 값(Pref)과 드룹 계수(Kp)를 곱한 값에 현재(n) 샘플링(Sampling)된 유효 전력 레퍼런스 값과 현재 이전(n-1)에 샘플링된 유효 전력 레퍼런스 값 사이의 변화분인 유효 전력 레퍼런스 값 변화분(dPref)과 변화분 드룹 계수 (Kpd)를 곱한 값을 더하여 유효 전력 드룹 신호(Pdrp)를 생성하는 유효 전력 드룹(Droop) 신호 생성부(25), 상 기 인버터로부터 출력되는 무효 전력이 증가되면, 인버터로부터 출력되는 전압이 일정 비율로 감소 되도록 제어 하기 위해 상기 V/F 드룹 위상 오차 보상부(23)에 의해 계산된 무효 전력 레퍼런스 값(Qref)과 드룹 계수(Kq)를 곱한 값에 현재(n) 샘플링(Sampling)된 무효 전력 레퍼런스 값과 현재 이전(n-1)에 샘플링된 무효 전력 레퍼런 스 값 사이의 변화분인 무효 전력 레퍼런스 값 변화분(dQref)과 변화분 드룹 계수(Kqd)를 곱한 값을 더하여 무 효 전력 드룹 신호(Qdrp)를 생성하는 무효 전력 드룹(Droop) 신호 생성부(27)로 이루어질 수 있다.

[0031]

상기 전압 전류 제어부(15)는 도면 2에 도시한 바와 같이, 인버터 출력전압 D축 레퍼런스 신호(Vref(d))와 무효 전력 드룹 신호 생성부(27)에서 생성된 무효 전력 드룹 신호(Qdrp) 사이의 오차를 계산하는 제1 D축 오차 계산 기(29)와, 상기 제1 D축 오차 계산기(29)의 출력 신호와 DQ 변환부(9)에 의해 변환된 3상 부하 전압의 D축 전압 신호(Vide) 사이의 오차를 계산하는 제2 D축 오차 계산기(31), 상기 제2 D축 오차 계산기(31)로부터 출력된 신 호를 비례 적분제어하여 인버터 전류 D축 레퍼런스 신호를 생성하는 D축 전압 제어부(33)와, 현재 타임(Time)에 IGBT 전력 변환부(3)의 출력단으로부터 샘플링(Sampling)된 3상 인버터 전압의 D축 전압 평균값에 게인(Gain)값 을 곱한 D축 전향 보상값을 저장하고, 현재 타임(Time)의 한 주기 또는 반 주기 이전에 저장된 D축 전향 보상값 을 호출하여 D축 가감산부(36)로 출력하는 D축 반복 제어부(35), 상기 D축 전압 제어부(33)로부터 출력된 신호 에 D축 반복 제어부(35)로부터 출력된 신호를 가산한 다음, DQ 변환부(9)에 의해 변환된 3상 인버터 전류의 D축 전류 신호(Iide)를 감산하는 D축 가감산부(36), 상기 D축 가감산부(36)로부터 출력된 신호를 비례 적분제어하여 보상값을 얻는 D축 전류 제어부(39), 상기 인버터 출력전압 D축 레퍼런스 신호(Vref(d))와 D축 전류 제어부(3 9)로부터 출력된 보상값을 가산하여 최종 D축 전압 제어 신호(Vdref)를 생성하는 D축 가산기(41), 상기 인버터 출력전압 Q축 레퍼런스 신호(Vref(q))와 DQ 변환부(9)에 의해 변환된 3상 부하 전압의 Q축 전압 신호(Vlqe) 사 이의 오차를 계산하는 제1 Q축 오차 계산기(43), 상기 제1 Q축 오차 계산기(43)로부터 출력된 신호를 비례 적분 제어하여 인버터 전류 Q축 레퍼런스 신호를 생성하는 Q축 전압 제어부(45), 현재 타임(Time)에 IGBT 전력 변환 부(3)의 출력단으로부터 샘플링(Sampling)된 3상 인버터 전압의 Q축 전압 평균값에 게인(Gain)값을 곱한 Q축 전 향 보상값을 저장하고, 현재 타임(Time)의 한 주기 또는 반 주기 이전에 저장된 Q축 전향 보상값을 호출하여 Q 축 가감산부(48)로 출력하는 Q축 반복 제어부(47), 상기 Q축 전압 제어부(45)로부터 출력된 신호에 Q축 반복 제

어부(47)로부터 출력된 신호를 가산한 다음, DQ 변환부(9)에 의해 변환된 3상 인버터 전류의 Q축 전류 신호 (Iide)를 감산하는 Q축 가감산부(48), 상기 Q축 가감산부(48)로부터 출력된 신호를 비례 적분제어하여 최종 Q축 전압 제어 신호(Vqref)를 생성하는 Q축 전류 제어부(51)로 이루어질 수 있다.

- [0032] 상기 D축 반복 제어부(35)와 Q축 반복 제어부(47)는 현재 샘플링 타임의 60Hz의 한 주기 전 또는 60Hz 반 주기 전 IGBT 전력 변환부(3)의 출력단으로부터 출력된 3상 인버터 전압을 3회 이상 샘플링하여 메모리에 저장해두었다가 현재 샘플링 타임에 한주기, 또는 반주기 이전 값을 참조하여 보상값을 계산하여 전향 보상한다.

- [0033] 현재 타임(Time)의 한 주기 또는 반 주기 이전에 저장된 D축 전향 보상값 또는 Q축 전향 보상값은 현재 타임 (Time)의 한 주기 또는 반 주기 이전에 IGBT 전력 변환부(3)의 출력단으로부터 샘플링(Sampling)된 3상 인버터 전압의 D축 전압 평균값 또는 Q축 전압 평균값에 게인(Gain)값을 곱한 값이다.

- [0034] 상기 D축 반복 제어부(35)와 Q축 반복 제어부(47)에 의한 고조파 보상 방법은 단지, D축과 Q축에 장착된 D축 반복 제어부(35)와 Q축 반복 제어부(47)를 이용하여 각 차수의 고조파를 모두 보상할 수 있고, 동시에 부하 불평형으로 나타나는 부하 전압의 불균형 보상 효과와, 인버터 병렬 V/F 드룹 제어 운전시 유효 전력, 무효 전력 편차 보상 효과 등으로 인해 인버터가 2개 이상 병렬 연결되어 운용시 우수한 병렬 운전 부하 분담 특성을 가지도록 한다.

- [0035] 상기 주파수 제어부(17)는 도면 2에 도시한 바와 같이, 상기 동기 신호 발생부(7)로부터 출력된 동기 신호에서 상기 유효 전력 드룹 신호 생성부(25)로부터 출력된 유효 전력 드룹 신호(Pdrp)를 감산하는 주파수 감산기(53)를 포함한다.

- [0036] 상기 DQ 역변환부(13)는 도면 2에 도시한 바와 같이, 상기 D축 가산기(41)로부터 출력된 최종 D축 전압 제어 신호(Vdref)와 상기 Q축 전류 제어부(51)로부터 출력된 최종 Q축 전압 제어 신호(Vqref)를 DQ 역변환하여 3상 인버터 전류 지령 신호를 생성하고, 상기 주파수 감산기(53)로부터 출력된 위상각 신호 주파수에 따라 3상 인버터 전류 지령 신호 주파수를 조정한다.

- [0037] 상기 D축 전류 제어부(39)의 출력단에는 도면 2에 도시한 바와 같이, LC 필터부(5)의 공진 이득을 상쇄시키기 위해 LC 필터부(5)의 공진 극점 이득과 서로 반대 되는 주파수 특성을 이용하여 D축 전류 제어부(39)의 출력단으로부터 출력되는 LC 필터부(5)의 공진 주파수를 억제하는 D축 노치 필터(55)(Notch Filter)가 부가 장착된다.

- [0038] 또한, 상기 Q축 전류 제어부(51)의 출력단에는 도면 2에 도시한 바와 같이, LC 필터부(5)의 공진 이득을 상쇄시키기 위해 LC 필터부(5)의 공진 극점 이득과 서로 반대가 되는 주파수 특성을 이용하여 Q축 전류 제어부(51)의 출력단으로부터 출력되는 LC 필터부(5)의 공진 주파수를 억제하는 Q축 노치 필터(57)(Notch Filter)를 더 포함한다.

- [0039] 상기 D축 노치 필터(55)와 Q축 노치 필터(57)는 노치 필터의 주파수 특성을 이용하여 상기 LC 필터부(5)의 공진 주파수를 상쇄시킨다.

- [0040] 상기 D축 노치 필터(55)와 Q축 노치 필터(57)는 추가 부품 없이 단지 필터 주파수와 이득을 조정함으로써 인버 터 전압을 매우 안정되게 제어할 수 있다.

- [0041] 또한, 인버터 출력 전압의 전반적인 제어 과정을 단, 한 샘플 타임 주기에 가능해지도록 함으로써 부하 과도 응답 동특성에서도 우수한 성능을 나타낼 수 있다.

- [0042] 상기 DQ 변환부(9)는 도면 2에 도시한 바와 같이, 상기 인버터의 LC 필터부(5)로부터 부하로 공급되는 3상 부하 전압을 DQ 변환하여 DQ 동기 좌표 변환값(Vlde,Vlqe)으로 변환하는 부하측 전압 DQ 변환부(59)와, 상기 바이패스 선로(6)로부터 바이패스(Bypass)된 3상 바이패스 전압을 DQ 변환하여 DQ 동기 좌표 변환값(Vbqe)으로 변환하는 바이패스(Bypass) 전압 DQ 변환부(61), 상기 인버터의 LC 필터부(5)로부터 부하로 공급되는 3상 부하 전류를 DQ 변환하여 DQ 동기 좌표 변환값(Ilde,Ilqe)으로 변환하는 부하측 전류 DQ 변환부(63), 및 상기 IGBT 전력 변환부(3)로부터 출력되는 3상 인버터 전류를 DQ 변환하여 DQ 동기 좌표 변환값(Iide,Iiqe)으로 변환하는 인버터 측 전류 DQ 변환부(65)를 포함한다.

- [0043] 상기 동기 신호 발생부(7)는 도면 2에 도시한 바와 같이, 상기 DQ 변환부(9)에 의해 변환된 3상 바이패스 전압의 Q축 전압 신호와 동기된 1차 바이패스 동기 신호를 출력하는 1차 위상 고정 루프(67)(PLL: Phase Locked Loop)와; 상기 1차 위상 고정 루프(67)로부터 출력된 1차 바이패스 동기 신호와 이중화 동기된 2차 바이패스 동기 신호를 출력하는 2차 위상 고정 루프(69)를 포함한다.

[0044]

한편, 본 발명에 따른 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 방법은 도면 3a 내 지 도면 3b에 도시한 바와 같이, 2개 이상의 인버터가 병렬 연결되었을 때 각각의 인버터가 서로 균등한 전력으 로 부하를 분담하도록 하여 각 인버터 간 유효 전력 편차나 무효 전력의 편차로 인해 인버터간 순환 전류가 발 생됨을 방지하고, 상기 각 인버터에는 상기 인버터에 내부 장착되어 H-브릿지(Bridge) 회로를 이용하여 직류 전 원을 교류 전원으로 변환하는 IGBT 전력 변환부(3)와, 상기 IGBT 전력 변환부(3)로부터 출력된 PWM 펄스 신호를 필터링(Filtering)하여 정현파 형태로 변환하는 LC 필터부(5), 상기 LC 필터부(5)의 출력단에 연결되어 인버터 가 정상 가동될 때에는 스위치 온(On)되어 부하로 전류를 흘려보내는 반면, 인버터에 고장이 발생되었을 때에는 스위치 오프(Off)되어 전류 흐름을 끊는 인버터 스위치(Inverter Switch)(1), 상기 인버터 스위치(1)의 출력단 에 연결되어 인버터가 정상 가동될 때에는 스위치 오프(Off)되는 반면, 인버터에 고장이 발생되었을 때에는 스 위치 온(On)되어 바이패스(Bypass) 선로로부터 입력된 3상 교류 전원을 부하측으로 공급하는 바이패스 스위치 (Bypass Switch)(4)가 구비된 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 방법에 있어 서, 상기 인버터 스위치(1)가 스위치 온(On)되고 바이패스 스위치(4)가 스위치 오프(Off)된 상태에서 상기 인버 터에 설치된 DQ 변환부(9)가 상기 IGBT 전력 변환부(3)로부터 출력되는 인버터 전류와, LC 필터부(5)로부터 인 버터 스위치(1)로 전달되는 3상 부하 전압과 3상 부하 전류 그리고 바이패스 선로(6)로부터 출력된 3상 바이패 스 전압을 동기 신호 발생부(7)로부터 제공된 동기 신호에 맞춰 DQ 변환하여 DQ 동기 좌표 변환 값으로 변환하 는 단계(S1)와; 상기 인버터에 설치된 V/F(Voltage/Frequency) 병렬 드룹(Droop) 제어부(11)가 메모리에 저장 된 파라미터로부터 제공된 전류 위상각 보상값을 이용하여 상기 DQ 변환부(9)로부터 입력받은 3상 부하 전류의 위상각을 보상하고 상기 위상각이 보상된 3상 부하 전류와 상기 DQ 변환부(9)로부터 전달된 3상 부하 전압을 이 용하여 새로운 유효 전력 레퍼런스(Reference) 값(Pref)과 무효 전력 레퍼런스(Reference) 값(Qref)을 계산하고, 인버터의 유효 전력이 증가하면 상기 유효 전력 레퍼런스 값(Pref)을 이용하여 인버터로부터 출력되 는 전압 주파수를 낮추기 위한 유효 전력 드룹(Droop) 신호를 생성하고, 인버터의 무효 전력이 증가하면 상기 무효 전력 레퍼런스 값을 이용하여 인버터로부터 출력되는 전압을 낮추기 위한 무효 전력 드룹 신호를 생성하는 단계(S2); 상기 인버터에 설치된 전압 전류 제어부(15)가 상기 V/F 병렬 드룹 제어부(11)로부터 출력된 무효 전 력 드룹 신호가 증가하면 인버터로부터 출력되는 전압을 낮추기 위한 제어 신호를 DQ 역변환부(13)에 전달하는 단계(S3); 상기 인버터에 설치된 동기 신호 발생부(7)가 상기 DQ 변환부(9)에 의해 변환된 3상 바이패스 전압의 Q축 전압 신호와 동상인 동기 신호를 발생하는 단계(S4); 상기 인버터에 설치된 주파수 제어부(17)가 상기 V/F 병렬 드룹 제어부(11)로부터 출력된 유효 전력 드룹 신호가 증가하면 인버터로부터 출력되는 전압 주파수를 낮 추기 위한 제어 신호를 DQ 역변환부(13)에 전달하는 단계(S5); 상기 DQ 역변환부(13)가 상기 전압 전류 제어부 (15)와 주파수 제어부(17)의 제어 신호에 따라 인버터의 출력 전압과 주파수를 조정하기 위한 지령 신호를 발생 하는 단계(S6); 상기 인버터에 설치된 SV PWM 변환부(19)가 상기 DQ 역변환부(13)로부터 출력된 지령 신호를 IGBT 전력 변환부(3)의 IGBT(Insulated Gate Bipolar Transistor)를 스위칭시키기 위한 공간 벡터 펄스 폭 변 조 신호(SV PWM: Space Vector Pulse Width Modulation)로 변환하는 단계(S7)로 이루어져, 인버터의 유효 전력 이 증가하면 증가된 유효 전력을 낮추기 위해 인버터의 출력 전압 주파수를 낮추고, 인버터의 무효 전력이 증가 하면 증가 된 무효 전력을 낮추기 위해 인버터의 출력 전압을 낮춤으로써 병렬 연결된 2개 이상의 인버터가 부 하를 균등하게 분담하도록 한다.

[0045]

상기 인버터에 설치된 V/F(Voltage/Frequency) 병렬 드룹(Droop) 제어부(11)가 메모리에 저장된 파라미터로부터 제공된 전류 위상각 보상값을 이용하여 상기 DQ 변환부(9)로부터 입력받은 3상 부하 전류의 위상각을 보상하고 상기 위상각이 보상된 3상 부하 전류와 상기 DQ 변환부(9)로부터 전달된 3상 부하 전압을 이용하여 새로운 유효 전력 레퍼런스(Reference) 값(Pref)과 무효 전력 레퍼런스(Reference) 값(Qref)을 계산하고, 인버터의 유효 전력이 증가하면 상기 유효 전력 레퍼런스 값(Pref)을 이용하여 인버터로부터 출력되는 전압 주파수를 낮추기 위한 유효 전력 드룹(Droop) 신호를 생성하고, 인버터의 무효 전력이 증가하면 상기 무효 전력 레퍼런스 값을 이용하여 인버터로부터 출력되는 전압을 낮추기 위한 무효 전력 드룹 신호를 생성하는 단계(S2)는 상기 V/F 병렬 드룹(Droop) 제어부(11)에 갖추어진 PQ 변환부(21)가 상기 DQ 변환부(9)로부터 3상 부하 전압과 3상 부하 전류에 대한 DQ 동기 좌표 변환 값을 입력받아 부하에 공급되는 유효 전력(P)과 무효 전력(Q)값을 계산하는 단계와; 상기 V/F 병렬 드룹(Droop) 제어부(11)에 갖추어진 V/F 드룹(Droop) 위상 오차 보상부(23)가 병렬 드룹(Droop) 제어 신호를 만들기 위해 메모리에 저장된 파라미터로부터 제공된 전류 위상각 보상값을 이용하여 상기 DQ 변환부(9)로부터 입력받은 3상 부하 전류의 위상각을 보상하고 상기 위상각이 보상된 부하 전류와 상기 DQ 변환부(9)로부터 전달된 3상 부하 전압을 이용하여 새로운 유효 전력 레퍼런스(Reference) 값(Pref)과 무효 전력 레퍼런스(Reference) 값(Qref)을 계산하는 단계; 상기 V/F 병렬 드룹(Droop) 제어부(11)에 갖추어진 유효 전력 드룹(Droop) 신호 생성부(25)가 상기 인버터로부터 출력되는 유효 전력이 증가하면, 인버터로부터 출력되는 전압 주

파수가 일정 비율로 감소 되도록 제어하기 위해 상기 V/F 드룹 위상 오차 보상부(23)에 의해 계산된 유효 전력 레퍼런스 값(Pref)과 드룹 계수(Kp)를 곱한 값에 현재(n) 샘플링(Sampling)된 유효 전력 레퍼런스 값과 현재 이전(n-1)에 샘플링된 유효 전력 레퍼런스 값 사이의 변화분인 유효 전력 레퍼런스 값 변화분(dPref)과 변화분 드룹 계수(Kpd)를 곱한 값을 더하여 유효 전력 드룹 신호(Pdrp)를 생성하는 단계; 상기 V/F 병렬 드룹(Droop) 제어부(11)에 갖추어진 무효 전력 드룹(Droop) 신호 생성부(27)가 상기 인버터로부터 출력되는 무효 전력이 증가되면, 인버터로부터 출력되는 전압이 일정 비율로 감소 되도록 제어하기 위해 상기 V/F 드룹 위상 오차 보상부(23)에 의해 계산된 무효 전력 레퍼런스 값(Qref)과 드룹 계수(Kq)를 곱한 값에 현재(n) 샘플링(Sampling)된 무효 전력 레퍼런스 값과 현재 이전(n-1)에 샘플링된 무효 전력 레퍼런스 값 사이의 변화분인 무효 전력 레퍼런스 값 변화분(dQref)과 변화분 드룹 계수(Kqd)를 곱한 값을 더하여 무효 전력 드룹 신호(Qdrp)를 생성하는 단계로 이루어질 수 있다.

- [0046] 상기 인버터에 설치된 전압 전류 제어부(15)가 상기 V/F 병렬 드룹 제어부(11)로부터 출력된 무효 전력 드룹 신 호가 증가하면 인버터로부터 출력되는 전압을 낮추기 위한 제어 신호를 DO 역변환부(13)에 전달하는 단계(S3)는 상기 전압 전류 제어부(15)에 갖추어진 제1 D축 오차 계산기(29)가 인버터 출력전압 D축 레퍼런스 신호 (Vref(d))와 무효 전력 드룹 신호 생성부(27)에서 생성된 무효 전력 드룹 신호(Qdrp) 사이의 오차를 계산하는 단계와; 상기 전압 전류 제어부(15)에 갖추어진 제2 D축 오차 계산기(31)가 상기 제1 D축 오차 계산기(29)의 출 력 신호와 DQ 변환부(9)에 의해 변환된 3상 부하 전압의 D축 전압 신호(Vlde) 사이의 오차를 계산하는 단계; 상 기 전압 전류 제어부(15)에 갖추어진 D축 전압 제어부(33)가 상기 제2 D축 오차 계산기(31)로부터 출력된 신호 를 비례 적분제어하여 인버터 전류 D축 레퍼런스 신호를 생성하는 단계; 상기 전압 전류 제어부(15)에 갖추어진 D축 반복 제어부(35)가 현재 타임(Time)에 IGBT 전력 변환부(3)의 출력단으로부터 샘플링(Sampling)된 3상 인버 터 전압의 D축 전압 평균값에 게인(Gain)값을 곱한 D축 전향 보상값을 저장하고, 현재 타임(Time)의 한 주기 또 는 반 주기 이전에 저장된 D축 전향 보상값을 호출하여 D축 가감산부(36)로 출력하는 단계; 상기 전압 전류 제 어부(15)에 갖추어진 D축 가감산부(36)가 상기 D축 전압 제어부(33)로부터 출력된 신호에 D축 반복 제어부(35) 로부터 출력된 신호를 가산한 다음, DQ 변환부(9)에 의해 변환된 3상 인버터 전류의 D축 전류 신호(lide)를 감 산하는 단계; 상기 전압 전류 제어부(15)에 갖추어진 D축 전류 제어부(39)가 상기 D축 가감산부(36)로부터 출력 된 신호를 비례 적분제어하여 보상값을 얻는 단계; 상기 전압 전류 제어부(15)에 갖추어진 D축 가산기(41)가 상 기 인버터 출력전압 D축 레퍼런스 신호(Vref(d))와 D축 전류 제어부(39)로부터 출력된 보상값을 가산하여 최종 D축 전압 제어 신호(Vdref)를 생성하는 단계; 상기 전압 전류 제어부(15)에 갖추어진 제1 Q축 오차 계산기(43) 가 상기 인버터 출력전압 Q축 레퍼런스 신호(Vref(q))와 DQ 변환부(9)에 의해 변환된 3상 부하 전압의 Q축 전압 신호(Vlqe) 사이의 오차를 계산하는 단계; 상기 전압 전류 제어부(15)에 갖추어진 Q축 전압 제어부(45)가 상기 제1 Q축 오차 계산기(43)로부터 출력된 신호를 비례 적분제어하여 인버터 전류 Q축 레퍼런스 신호를 생성하는 단계; 상기 전압 전류 제어부(15)에 갖추어진 Q축 반복 제어부(47)가 현재 타임(Time)에 IGBT 전력 변환부(3)의 출력단으로부터 샘플링(Sampling)된 3상 인버터 전압의 Q축 전압 평균값에 게인(Gain)값을 곱한 Q축 전향 보상 값을 저장하고, 현재 타임(Time)의 한 주기 또는 반 주기 이전에 저장된 0축 전향 보상값을 호출하여 0축 가감 산부(48)로 출력하는 단계; 상기 전압 전류 제어부(15)에 갖추어진 Q축 가감산부(48)가 상기 Q축 전압 제어부 (45)로부터 출력된 신호에 Q축 반복 제어부(47)로부터 출력된 신호를 가산한 다음, DQ 변환부(9)에 의해 변환된 3상 인버터 전류의 Q축 전류 신호(Iide)를 감산하는 단계; 상기 전압 전류 제어부(15)에 갖추어진 Q축 전류 제 어부(51)가 상기 Q축 가감산부(48)로부터 출력된 신호를 비례 적분제어하여 최종 Q축 전압 제어 신호(Vqref)를 생성하는 단계로 이루어질 수 있다.

- [0047] 상기 인버터에 설치된 주파수 제어부(17)가 상기 V/F 병렬 드룹 제어부(11)로부터 출력된 유효 전력 드룹 신호가 증가하면 인버터로부터 출력되는 전압 주파수를 낮추기 위한 제어 신호를 DQ 역변환부(13)에 전달하는 단계(S5)는 상기 주파수 제어부(17)가 주파수 감산기(53)를 이용하여 상기 동기 신호 발생부(7)로부터 출력된 동기신호에서 상기 유효 전력 드룹 신호 생성부(25)로부터 출력된 유효 전력 드룹 신호(Pdrp)를 감산하는 단계와; 상기 주파수 감산기(53)로부터 출력된 위상각 신호의 주파수가 낮아지면, DQ 역변환부(13)는 인버터의 출력 전압 주파수를 낮추기 위한 지령 신호를 출력하는 단계를 포함한다.

- [0048] 이러한 구조로 이루어진 본 발명에 따른 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치 및 제어 방법은 2개 이상의 인버터가 병렬 연결되고 2개 이상의 인버터에 부하가 공통으로 연결되었을 때, 인버터의 유효 전력이 증가하면 인버터로부터 출력되는 전압 주파수를 낮춰 증가된 유효 전력을 낮추고, 인버터의 무효 전력이 증가하면 인버터로부터 출력되는 전압을 낮춰 증가된 무효 전력을 낮추게 된다.

- [0049] 결과적으로, 인버터의 유효 전력과 무효 전력을 일정하게 유지함으로써 인버터간 유효 전력 편차와 무효 전력

편차로 인해 발생 될 수 있는 순환 전류에 의해 인버터로부터 과전류가 발생됨을 방지할 수 있다.

- [0050] 따라서, 본 발명에 따른 능동 댐핑과 반복 제어 보상 기반의 V/F 드룹 병렬 운전 인버터 제어 장치 및 제어 방법은 2개 이상의 인버터가 병렬 연결된 상태에서 운전될 때 부하 불평형으로 인한 부하 전압의 불균형 현상을 보상할 수 있고, V/F 드룹(Voltage/Frequency Droop) 제어시 유효 전력과 무효 전력의 편차를 보상하여 인버터의 부하 분담 특성을 향상시킬 수 있다.

- [0051] 또한, 본 발명은 여러 대의 인버터가 병렬 운전시 각 인버터로부터 발생 될 수 있는 유효 전력과 무효 전력 편 차를 보다 빠르게 보상함으로써 인버터의 병렬 운전 상태를 보다 안정화시킬 수 있다.

## 부호의 설명

- [0053] 1. 인버터 스위치

- 4. 바이패스 스위치

- 6. 바이패스 선로

- 9. DQ 변환부

- 13. DQ 역변환부

- 17. 주파수 제어부

- 21. PQ 변환부

- 25. 유효 전력 드룹 신호 생성부

- 29. 제1 D축 오차 계산기

- 33. D축 전압 제어부

- 36. D축 가감산부

- 41. D축 가산기

- 45. Q축 전압 제어부

- 48. Q축 가감산부

- 53. 주파수 감산기

- 57. Q축 노치 필터

- 61. 바이패스 전압 DQ 변환부

- 65. 인버터측 전류 DQ 변환부

- 69. 2차 위상 고정 루프

- 3. IGBT 전력 변환부

- 5. LC 필터부

- 7. 동기 신호 발생부

- 11. V/F 병렬 드룹 제어부

- 15. 전압 전류 제어부

- 19. SV PWM 변환부

- 23. V/F 드룹 위상 오차 보상부

- 27. 무효 전력 드룹 신호 생성부

- 31. 제2 D축 오차 계산기

- 35. D축 반복 제어부

- 39. D축 전류 제어부

- 43. 제1 Q축 오차 계산기

- 47. Q축 반복 제어부

- 51. Q축 전류 제어부

- 55. D축 노치 필터

- 59. 부하측 전압 DQ 변환부

- 63. 부하측 전류 DQ 변환부

- 67. 1차 위상 고정 루프

# 도면

## 도면1

# 도면2

~ S1

- S3

#### 도면3a

인버터 스위치가 스위치 온(On)되고 바이패스 스위치가 스위치 오프(Off)된 상태에서 상기 인비터에 설치된 DQ 변환부가 상기 IGBT 전력 변환부로부터 출력되는 인버터 전류와, LC 필터부로부터 인버터 스위치로 전달되는 3상 부하 전압과 3상 부하 전류 그리고 바이패스 선로로부터 출력된 3상 바이패스 전압을 동기 신호 발생부로부터 제공된 동기 신호에 맞춰 DQ 변환하여 DQ 동기 좌표 변환 값으로 변환하는 단계

인버터에 설치된 V/F(Voltage/Frequency) 병렬 드륨(Droop) 제어부가 메모리에 저장된 파라미터로부터 제공된 전류 위상각 보상값을 이용하여 상기 DQ 변환부로부터 입력받은 3상 부하 전류의 위상각을 보상하고 상기 위상각이 보상된 부하 전류와 상기 DQ 변환부로부터 전달된 3상 부하 전압을 이용하여 새로운 유효전력 레퍼런스(Reference) 값(Pref)과 무효 전력 레퍼런스(Reference) 값(Qref)을 계산하고, 인버터의 유효 전력이 증가 하면 상기 유효 전력 레퍼런스 값(Pref)을 이용하여 인버터로부 출력되는 전압 주파수를 낮추기 위한 유효 전력 레퍼런스 값을 이용하여 인버터로부터 출력되는 전압을 낮추기 위한 무효 전력 레퍼런스 값을 이용하여 인버터로부터 출력되는 전압을 낮추기 위한 무효 전력 드륨 신호를 생성하는 단계

인버터에 설치된 전압 전류 제어부가 상기 V/F 병렬 드룹 제어부로부터 출력된 무효 전력 드룹 신호가 증가 하면 인버터로부터 출력되는 전압을 낮추기 위한 제어 신호를 DQ 역변환부에 전달하는 단계

$\bigwedge$

#### 도면3b