(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5031976号

(P5031976)

(45) 発行日 平成24年9月26日(2012.9.26)

(24) 登録日 平成24年7月6日(2012.7.6)

(51) Int.Cl.

HO4N 7/26 (2006.01)

F 1

HO4N 7/13

Z

請求項の数 31 (全 15 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2003-550513 (P2003-550513)  |

| (86) (22) 出願日 | 平成14年12月3日 (2002.12.3)        |

| (65) 公表番号     | 特表2006-501697 (P2006-501697A) |

| (43) 公表日      | 平成18年1月12日 (2006.1.12)        |

| (86) 國際出願番号   | PCT/US2002/038666             |

| (87) 國際公開番号   | W02003/049454                 |

| (87) 國際公開日    | 平成15年6月12日 (2003.6.12)        |

| 審査請求日         | 平成17年12月1日 (2005.12.1)        |

| 審判番号          | 不服2010-24944 (P2010-24944/J1) |

| 審判請求日         | 平成22年11月5日 (2010.11.5)        |

| (31) 優先権主張番号  | 10/006,044                    |

| (32) 優先日      | 平成13年12月4日 (2001.12.4)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595020643<br>クアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                                                        |

| (74) 代理人  | 100091351<br>弁理士 河野 哲                                                                                         |

| (74) 代理人  | 100088683<br>弁理士 中村 誠                                                                                         |

| (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                                                        |

最終頁に続く

(54) 【発明の名称】デジタルビデオデータの処理

## (57) 【特許請求の範囲】

## 【請求項 1】

ビデオデータを記憶するための線形アドレス指定可能記憶装置をもつメモリと、

ビデオデータの多次元ブロックを指定する命令に応答して、メモリの記憶装置にアクセスし、命令に応答して、メモリの多数の非連続行からビデオデータの多次元ブロックをフェッチするためのプログラマブルビデオ直接メモリアクセス(video direct memory access, VDMA)制御装置とを含み、命令はビデオデータのブロックの各行間の記憶装置の個数を示すジャンプパラメータを指定する、システム。

## 【請求項 2】

命令が、ビデオデータブロックの行番号および列番号を指定する請求項1記載のシステム。10

## 【請求項 3】

VDMA制御装置が、命令に応答して、メモリから宛先メモリへビデオデータをコピーする請求項1記載のシステム。

## 【請求項 4】

命令が、メモリ内のビデオブロックの開始アドレスと宛先メモリ内の開始アドレスとを指定する請求項3記載のシステム。

## 【請求項 5】

第1のバスを介してVDMA制御装置へ命令を発行するためのプロセッサと、

第2のバスを介してVDMA制御装置へ命令を発行するためのディジタル信号プロセ20

ッサとをさらに含む請求項 1 記載のシステム。

**【請求項 6】**

内部メモリを含む動き推定装置と、ビデオデータブロック間の歪みメトリックを計算するための差分計算器とをさらに含み、V D M A 制御装置が、命令に応答して、メモリから、動き推定装置の内部キャッシュへ、ビデオデータブロックをコピーする請求項 1 記載のシステム。

**【請求項 7】**

プロセッサから直接メモリアクセス (direct memory access, DMA) 命令を受信して、ビデオデータの多次元ブロックを転送し、命令はビデオデータのブロックの各行間の記憶装置の個数を示すジャンプパラメータを指定することと、10

命令に応答して、ビデオデータの多次元ブロックのためのソースアドレスの組と宛先アドレスの組とを生成し、ソースアドレスの組が、ソースメモリの多数の非連続行に対応することと、

命令に応答して、ソースアドレスおよび宛先アドレスにしたがって、ソースメモリから宛先メモリへビデオデータをコピーすることとを含む方法。

**【請求項 8】**

ソースメモリおよび宛先メモリの各々が、線形アドレス指定可能記憶装置をもつ請求項 7 記載の方法。

**【請求項 9】**

命令が、ビデオデータブロックの行番号および列番号を指定し、アドレスの組を生成することが、行番号および列番号の関数として、ソースアドレスおよび宛先アドレスを計算することを含む請求項 7 記載の方法。20

**【請求項 10】**

アドレスの組を生成することが、ジャンプパラメータの関数として、ソースアドレスおよび宛先アドレスを計算することを含む請求項 7 記載の方法。

**【請求項 11】**

命令が、ソースメモリ内のビデオブロックの開始ソースアドレスと宛先メモリ内の開始宛先アドレスとを指定する請求項 7 記載の方法。

**【請求項 12】**

ビデオデータをコピーすることが、命令に応答して、多数の行をもつビデオデータのブロック全体をフェッチすることを含む請求項 7 記載の方法。30

**【請求項 13】**

命令を受信することが、第 1 のバスを介して命令を受信することを含む方法であって、ディジタル信号プロセッサから第 2 のバスを介して第 2 の命令を受信することをさらに含む請求項 7 記載の方法。

**【請求項 14】**

ビデオデータをコピーすることが、命令に応答して、ビデオデータを、動き推定装置の内部キャッシュへコピーすることを含む請求項 7 記載の方法。

**【請求項 15】**

符号化される候補のビデオブロックを記憶するための第 1 のメモリと、40

符号化される候補のビデオブロックを含むビデオデータブロックの組を記憶するための第 2 のメモリと、

候補のビデオブロックとビデオブロックの組との差分メトリックを計算するための差分計算器と、

候補のビデオブロックとビデオブロックの組とをビデオメモリから第 1 のメモリおよび第 2 のメモリにそれぞれコピーするためのプログラマブルビデオ直接メモリアクセス (V D M A ) 制御装置であって、ビデオメモリ内に多数の非連続行で記憶されているビデオデータの多次元サーチ空間を特定する 1 つの直接メモリアクセス (D M A ) 命令に応答して、ブロックの組を第 2 のメモリにコピーする V D M A 制御装置とを含み、命令はビデオデータのブロックの各行間の記憶装置の個数を示すジャンプパラメータを指定する、装置50

。

【請求項 1 6】

第 2 のメモリによって記憶されるビデオデータブロックの組が、完全なビデオデータフレームを含む請求項 1 5 記載の装置。

【請求項 1 7】

差分計算器が、第 1 のメモリから候補のビデオブロックを、第 2 のメモリからビデオブロックの組の中の 1 つ以上のビデオブロックを読み出すためのアドレス生成論理を含む請求項 1 5 記載の装置。

【請求項 1 8】

差分計算器が、第 1 のメモリから候補のビデオブロックを、第 2 のメモリからビデオブロックの組の中の 1 つ以上のビデオブロックを並列に読み出す請求項 1 7 記載の装置。 10

【請求項 1 9】

命令が、ビデオデータのサーチ空間の行番号および列番号を指定する請求項 1 5 記載の装置。

【請求項 2 0】

ビデオメモリが、ビデオデータを記憶するための複数の線形アドレス指定可能記憶装置を含む請求項 1 5 記載の装置。

【請求項 2 1】

命令が、ビデオメモリ内のサーチ空間の開始ソースアドレスと第 2 のメモリ内の開始宛先アドレスとを指定する請求項 1 5 記載の装置。 20

【請求項 2 2】

第1のバスを介して V D M A 制御装置へ命令を発行するためのプロセッサと、

第 2 のバスを介して V D M A 制御装置へ命令を発行するためのディジタル信号プロセッサ ( D S P ) とをさらに含む請求項 1 5 記載の装置。

【請求項 2 3】

差分計算器が、サーチ命令に応答して、差分メトリックを計算し、各サーチ命令が、第 2 のメモリ内に記憶されているビデオデータの多次元領域を指定する請求項 1 5 記載の装置。

【請求項 2 4】

サーチ命令を記憶し、かつサーチ命令を差分計算器へ送るための命令緩衝器をさらに含む請求項 2 3 記載の装置。 30

【請求項 2 5】

プロセッサから直接メモリアクセス ( D M A ) 命令を受信して、ビデオデータの多次元ブロックを転送するための手段であって、命令はビデオデータのブロックの各行間の記憶装置の個数を示すジャンプパラメータを指定する、手段と、

命令に応答して、ビデオデータの多次元ブロックのソースアドレスの組と宛先アドレスの組とを生成するための手段であって、ソースアドレスの組がソースメモリの多数の非連続行に対応する手段と、

ソースアドレスおよび宛先アドレスにしたがって、ソースメモリから宛先メモリへビデオデータをコピーするための手段とを含む装置。 40

【請求項 2 6】

ソースメモリおよび宛先メモリの各々が、線形アドレス指定可能記憶装置をもつ請求項 2 5 記載の装置。

【請求項 2 7】

命令が、ビデオデータブロックの行番号および列番号を指定し、生成手段が、行番号および列番号の関数として、ソースアドレスおよび宛先アドレスを計算するための手段を含む請求項 2 5 記載の装置。

【請求項 2 8】

生成手段が、ジャンプパラメータの関数として、ソースアドレスおよび宛先アドレスを計算するための手段を含む請求 2 5 記載の装置。 50

**【請求項 29】**

命令が、ソースメモリ内のビデオブロックの開始ソースアドレスと、宛先メモリ内の開始宛先アドレスとを指定する請求項 25 記載の装置。

**【請求項 30】**

受信手段が、第 1 のバスを介して命令を、ディジタル信号プロセッサから第 2 のバスを介して第 2 の命令を受信する請求項 25 記載の装置。

**【請求項 31】**

コピー手段が、命令に応答して、ビデオデータを、動き推定装置の内部キャッシュへコピーするための手段を含む請求項 25 記載の装置。

**【発明の詳細な説明】**

10

**【技術分野】****【0001】**

本発明は、ディジタルビデオデータの符号化または復号のような、ディジタルビデオデータの処理に関する。

**【背景技術】****【0002】**

コンピュータ処理能力の最近の向上と、手頃な価格設定とのために、フルモーションディジタルビデオ受信機がより普及してきている。とくに、ディジタルビデオの能力は、ディジタルテレビジョン、ディジタル直接放送システム、無線通信装置、ポータブルディジタルアシスタント (portable digital assistant, PDA)、ラップトップコンピュータ、およびデスクトップコンピュータを含む幅広い範囲の装置に取り入れられた。これらの装置は、フルモーションビデオ系列の生成、変更、伝送、記憶、および再生において従来のアナログビデオシステムよりも相当に向上している。

20

**【0003】**

ディジタルビデオ系列と通信するための種々のビデオ圧縮の標準規格または処理が設定された。例えば、MPEG (Moving Picture Experts Group) (MPEG - 1, MPEG - 2、およびMPEG - 4を含む) は、多数の標準規格を開発した。他の標準規格は、Apple Computer(Cupertino California)によって開発されたQuickTime(商標)技術、Microsoft Corporation(Redmond, Washington)によって開発されたVideo for Windows(商標)、Intel Corporationによって開発されたIndeo (商標)、RealNetworks, Inc(Seattle, Washington)からのRealVideo(商標)、およびSuperMac Inc. によって開発されたCinepak (商標)を含む。

30

**【0004】**

これらの標準規格の多くは、データ圧縮を用いることによって、より高い伝送レートを達成する。例えば、MPEG の標準規格は、ビデオおよび画像をより狭い帯域幅で伝送するように設計されたグラフィックおよびビデオ圧縮アルゴリズムを使用する。とくに、MPEG の標準規格は、連続する画像フレーム間の類似性 (時間またはフレーム間相関と呼ばれる) を使用し、フレーム間圧縮を行なうビデオ圧縮技術を取り入れている。フレーム間圧縮技術は、画像フレームの画素ベースの表現を、動き表現に変換することによって、フレーム全体におけるデータの冗長性を用いる。さらに加えて、ビデオ圧縮技術では、画像フレーム内の類似性 (空間またはフレーム内相関と呼ばれる) を使用し、フレーム内圧縮をする。フレーム内圧縮では、画像フレーム内の動き表現を圧縮することができる。フレーム内圧縮は、一般に、離散コサイン変換 (discrete cosine transform, DCT) 符号化のような、静止画像を圧縮するための従来の処理に基づく。

40

**【0005】**

圧縮技術を支援するために、多くのディジタルビデオ装置は、ディジタルビデオ系列を圧縮および逆圧縮するための符号器 / 復号器 (encoder/decoder, CODEC) を含む。CODEC は、ビデオ画像系列内の画素ブロックを処理する。例えば、MPEG では、CODEC は、一般に、伝送されるビデオ画像フレームを、より小さい画像ブロックから成るマクロブロックへ分割する。画像フレーム内の各マクロブロックごとに、CODEC は、直前

50

のビデオフレームをサーチして、最も類似したマクロブロックを識別し、伝送するマクロブロック間の差を、符号化に使用された前のフレームからマクロブロックを示す動きベクトルと共に符号化する。復号器は、動きベクトルおよび符号化されたビデオデータを受信し、動き補償を行って、ビデオ系列を生成する。

【発明の開示】

【課題を解決するための手段】

【0006】

概して、本発明は、ディジタルビデオデータの符号化または復号のような、ディジタルビデオデータの処理に関する。1つの実施形態では、本発明は、ビデオデータを記憶するための複数の線形アドレス指定可能な記憶装置をもつメモリと、ビデオデータの多次元ブロックを指定する命令に応答して、メモリの記憶装置にアクセスするためのプログラマブルビデオ直接メモリアクセス (video direct memory access, VDMA) 制御装置とを含むシステムに関する。命令は、例えば、ビデオデータブロックの行番号および列番号と、ビデオブロックの各列間の記憶装置番号を示すジャンプパラメータとを指定する。このようにして、VDMA制御装置は、1つの直接メモリアクセス (direct memory access, DMA) 命令に応答して、多数の不連続行をもつビデオデータのブロック全体をフェッチすることができる。したがって、マイクロプロセッサは、より少ないアドレス計算数で、ビデオデータのブロックにアクセスすることができる。

【0007】

別の実施形態において、本発明は、プロセッサから直接メモリアクセス (DMA) 命令を受信して、ビデオデータの多次元ブロックを転送することと、命令に応答して、1組のソースアドレスおよび1組の宛先アドレスを生成することとを含む方法に関する。この方法は、ソースアドレスおよび宛先アドレスにしたがって、ソースメモリから宛先メモリへビデオデータをコピーすることも含む。

【0008】

別の実施形態において、本発明は、ディジタルビデオデータを処理するための装置に関する。装置は、符号化される候補のビデオブロックを記憶するための第1のメモリと、符号化される候補のビデオブロックを含むビデオデータブロックの組を記憶するための第2のメモリとを含む。装置は、候補のビデオブロックとビデオブロックの組との差分メトリックを計算するための差分計算器も含む。

【0009】

本発明の1つ以上の実施形態の詳細は、添付の図面および以下の説明において示される。本発明の他の特徴、目的、および長所は、説明および図面、並びに特許請求項から明らかになるであろう。

【発明を実施するための最良の形態】

【0010】

本発明は、概して、ディジタルビデオデータの符号化または復号のような、ディジタルビデオデータの処理に関する。符号器、復号器、または符号器 / 復号器 (CODEC) のような装置は、組込まれたプロセッサ、ディジタル信号プロセッサ、および専用のハードウェア間で機能を分割して、向上した性能を実現する革新的なアーキテクチャを含む。さらに加えて、装置のこれらの、および他の構成要素は、ビデオデータのブロックに直接にアクセスするための命令を支援する固有のメモリ構造を使用する。

【0011】

組込まれたプロセッサ、ディジタル信号プロセッサ、および専用ハードウェア間で符号化および復号機能を分割することによって、装置は、高速の符号化および復号を実現することができる。さらに加えて、組込まれたプロセッサおよびディジタル信号プロセッサ (digital signal processor, DSP) は、個々の圧縮標準規格に特定の全機能を実行し、一方で専用ハードウェアは、大抵の標準規格に共通する特定の計算を実行するように最適化される。このようにして、装置は高性能を実現するが、将来のビデオ圧縮の標準規格を支援するために、依然として、容易にアップグレードすることができる。

10

20

30

40

50

## 【0012】

さらに加えて、ビデオデータのブロックに直接にアクセスするための命令を支援するプログラマブルビデオ直接メモリアクセス(video direct memory access, VDMA)制御装置を使用することによって、構成要素は、多数のアドレス計算を行う必要なく、ビデオデータのブロックにアクセスすることができる。言い換えると、構成要素は、従来の線形記憶アドレスの代わりに、ビデオデータのブロックを指定する命令を使用して、メモリ構造へデータを書き込み、かつそこからデータを読み出すことができる。したがって、通常はビデオデータが順次に記憶されないために、ビデオデータにアクセスするのに通常必要とされる多数のアドレス計算を行う必要なく、構成要素は、ビデオデータのブロックにアクセスすることができる。

10

## 【0013】

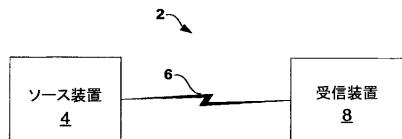

図1は、ソース装置4がビデオデータ6の符号化された系列を受信装置8へ送信する例示的なシステム2を示すブロック図である。とくに、ソース装置4は、種々のビデオ圧縮の標準規格の1つを使用して、ビデオデータ6を符号化して、送信する。このような標準規格の例は、Moving Picture Experts Groupによって開発されたMPEG、Apple Computer(Cupertino California)によって開発されたQuickTime(商標)、Microsoft Corporation(Redmond, Washington)によって開発されたVideo for Windows(商標)、Intel Corporationによって開発されたIndeo(商標)、およびSuperMac Inc.によって開発されたCinepak(商標)を含む。

20

## 【0014】

ソース装置4は、ビデオデータ6を符号化して、送信することができる装置である。同様に、受信装置8は、ビデオデータ6を受信して、復号することができる装置である。ソース装置4および受信装置8の装置は、例えば、コンピュータネットワーク上に位置するサーバ、ワークステーションまたは他のデスクトップコンピュータ、およびラップトップコンピュータのようなモバイルコンピュータを含む。他の例は、ディジタルテレビジョン放送衛星および受信装置、例えば、ディジタルテレビジョン、ディジタルビデオカメラまたは他の記録装置、ディジタルビデオ電話装置、無線ビデオ装置、等を含む。

## 【0015】

したがって、ソース装置4および受信装置8の各々は、一般に、ディジタルビデオデータ6を符号化および復号するための符号器/復号器(CODEC)(図示されていない)を含む。例えば、ソース装置4のCODECは、ビデオ画像系列内の画素ブロックを処理して、ビデオデータを符号化する。とくに、ソース装置4のCODECは、伝送されるビデオ画像フレームを、多数のより小さい画像ブロックから成るマクロブロックへ分割する。画像フレーム内の各マクロブロックごとに、ソース装置4のCODECは、既に伝送された前のビデオフレームをサーチして、最も類似したマクロブロックを識別し、マクロブロック間の差を、符号化に使用された前のフレームからマクロブロックを識別する動きベクトルと共に符号化する。受信装置8のCODECは、動きベクトルおよび符号化されたビデオデータを受信し、動き補償を行って、ユーザに表示するためのビデオ系列を生成する。ソース装置4および受信装置8の各々は、CODECを含む必要はない。例えば、ソース装置4が符号器を含み、受信装置8が復号器を含んでもよい。

30

## 【0016】

ソース装置4のCODEC、受信装置8のCODEC、またはこの両者は、ビデオデータを符号化および復号するための革新的なアーキテクチャを含む。したがって、本発明は、符号化されたビデオデータを送信するための装置、または符号化されたビデオデータを受信するための装置に制限されない。符号化および復号の機能は、組込まれたプロセッサ、ディジタル信号プロセッサ、および専用ハードウェア間で分割される。さらに加えて、CODECのこれらの、および他の構成要素は、ビデオデータのブロックに直接にアクセスするための命令を支援する固有のメモリ構造を使用する。言い換えると、構成要素は、従来の線形記憶アドレスの代わりに、ビデオデータのブロックを指定する命令を使用して、メモリ構造へデータを書き込み、かつそこからデータを読み出すことができる。したが

40

50

って、通常はビデオデータが順次に記憶されないために、ビデオデータにアクセスするのに通常必要とされる多数のアドレス計算を行う必要なく、構成要素は、ビデオデータのブロックにアクセスすることができる。

#### 【 0 0 1 7 】

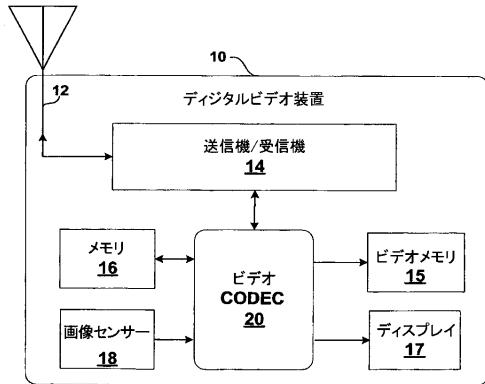

図2は、ソース装置4または受信装置6のような、例示的なディジタルビデオ装置10を示すブロック図であって、本発明の原理にしたがってディジタルビデオ系列を圧縮および逆圧縮するビデオ符号器／復号器(CODEC)20が組込まれている。例示的なディジタルビデオ装置10は、モバイルコンピュータ、パーソナルディジタルアシスタント(PDA)、無線通信装置、等のような無線装置として示される。しかしながら、本発明の原理は無線装置に制限されず、他のディジタルビデオ装置へ直ちに適用される。さらに加えて、本発明は、CODECに関連して示されているが、これに制限されず、符号器および復号器へ直ちに適用される。10

#### 【 0 0 1 8 】

ディジタルビデオ装置10は、アンテナ12および送信機／受信機14を介して圧縮されたディジタルビデオ系列を受信する。CODEC20は、ビデオ系列を復号し、ビデオ系列をビデオメモリ15に記憶する。CODEC20は、復号されたビデオ系列をディスプレイ17上に表示する。ディスプレイ17は、液晶ディスプレイ(liquid crystal display, LCD)または他の出力装置を含む。さらに加えて、CODEC20は、画像センサー18によって取り込まれたディジタルビデオ系列を符号化する。CODEC20は、符号化されたディジタルビデオ系列を、送信機／受信機14およびアンテナ12を介して送信する前に、ビデオメモリ15内で緩衝する。メモリ16は、CODEC20が使用する指令およびデータを記憶する。メモリ15、16は、同期ダイナミックランダムアクセスメモリ(synchronous dynamic random access memory, SDRAM)、等を含む。20

#### 【 0 0 1 9 】

別途詳しく記載するように、CODEC20は、ビデオデータを符号化および復号するための革新的なアーキテクチャを含む。したがって、ディジタルビデオ装置10は、1.5メガビット／秒以上のような、ビデオデータの高速転送を実現する。

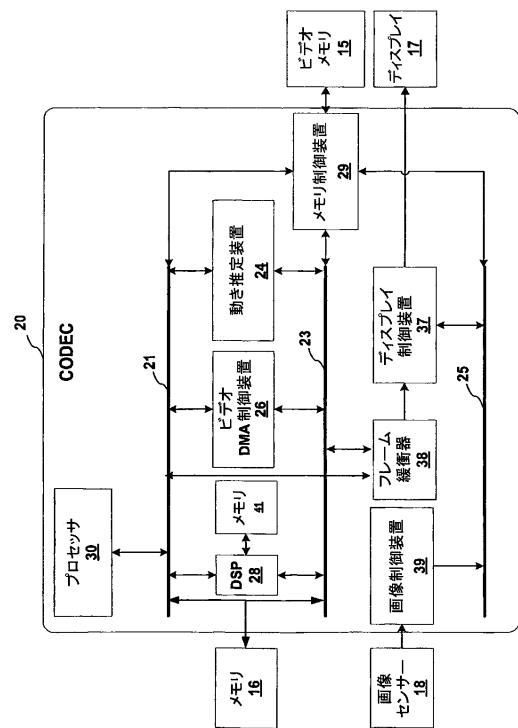

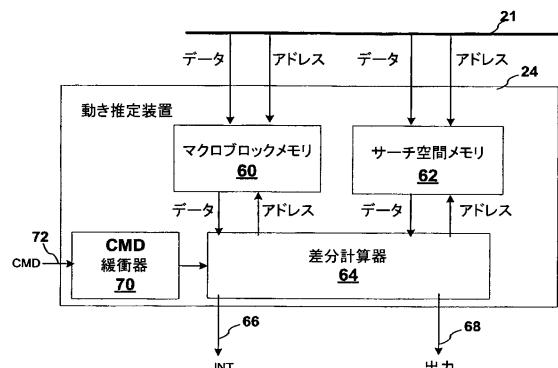

図3は、ディジタルビデオ装置10のCODEC20の例示的な実施形態をさらに詳しく示すブロック図である。概して、CODEC20は、組込まれたプロセッサ30、ディジタル信号プロセッサ(digital signal processor, DSP)28、および動き推定装置24間で、符号化および復号のタスクを分割する。多数の構成要素を含む1つの特定用途向け集積回路(application-specific integrated circuit, ASIC)として図示されているが、多数のディスクリートな構成要素を使用して、本明細書に記載されている原理を直ちに実行することができる。30

#### 【 0 0 2 0 】

プロセッサ30は、CODEC20の全構成要素に対して主要な制御を与え、ディジタルビデオ装置10の他の構成要素との通信を調整する。プロセッサ30は、ディジタルビデオ系列を符号化および復号するのに必要な多数の計算を行う集中的なタスクを実行するよう、DSP28へ命令する。また、幾つかのタスクにおいて、DSP28は動き推定装置24に関係する。動き推定装置24は、動き推定を行うための専用ハードウェアも含む。既に記載したように、メモリ16は、プロセッサ30によって使用するための指令およびデータを記憶し、一方で、ビデオメモリ15はビデオデータを記憶する。図示されているように、メモリ15、16は、CODEC20の外部にあり、プロセッサバス21を介してプロセッサ30に接続される。40

#### 【 0 0 2 1 】

プロセッサ30は、プロセッサバス21を介して、DSP28を構成し、制御する。DSP28は、指令およびデータを記憶するための専用メモリ41をもつが、DSPバス23を介してメモリ15、16へアクセスすることもできる。異なるDSPバス23を使用すると、DSP28およびプロセッサ30は、CODEC20の種々の構成要素に同時にアクセスすることができ、したがってディジタルビデオ装置10の全バンド幅が増す。例えば、DSP28がビデオメモリ15、16へ同時にアクセスする。50

リ15にアクセスし、一方で、プロセッサ30がメモリ16にアクセスすることができる。メモリ制御装置29は、プロセッサバス21、DSPバス23、および入力／出力(input/output, I/O)バス25間で、ビデオメモリ15へのアクセスを調停する。

#### 【0022】

I/Oバス25は、プロセッサ30およびDSP28を、ディスプレイ17および画像センサー18のような多数の異なる周辺装置へ接続する。プロセッサ30およびDSP28は、例えば、復号されたビデオデータをフレーム緩衝器38へ供給し、ディスプレイ制御装置37を介してディスプレイ17へ出力する。さらに加えて、プロセッサ30は、画像センサー18からビデオデータを取り込むように画像制御装置39に命令したり、ビデオメモリ15内にビデオデータを記憶したりする。

10

#### 【0023】

プロセッサ30およびDSP28は、ビデオダイナミックメモリアクセス(VDMA)制御装置26を使用して、ビデオデータの効率的な符号化および復号を容易にする。とくに、プロセッサ30およびDSP28は、VDMA制御装置26に、ビデオデータの多次元ブロックを指定するアクセス命令を発行し、VDMA制御装置26は、それを一次元の記憶アドレスへ変換する。VDMA制御装置26は、プロセッサバス21およびDSPバス23の両者の上に位置し、外部メモリ16、ビデオメモリ15、DSPメモリ41、動き推定装置24内のメモリ(図示されていない)を含むCODEC20のメモリ間でデータを転送できるようとする。例えば、DSP28からの命令に応答して、VDMA制御装置26は、ビデオメモリ15から動き推定装置24へビデオデータの1つ以上のブロックをコピーする。

20

#### 【0024】

一度にメモリの一行を読み出す従来のDMA制御装置とは異なり、VDMA制御装置26は、行の間でプログラムし直す必要なく、フレームの多次元ビデオブロックをフェッチする。さらに加えて、VDMA制御装置26は、ビデオデータの非正方形のブロックをフェッチすることができる。このようにして、VDMAは、プロセッサ30、DSP28、およびCODEC20の他の構成要素が多数のアドレス計算をする必要を省いている。このような多数のアドレス計算は、通常はビデオデータが順次に記憶されないために、ビデオデータにアクセスするのに通常必要とされる。

#### 【0025】

プロセッサ30およびDSP28は、転送するブロックを指定する1組のパラメータを含む命令を発行することによって、VDMA制御装置26をプログラムする。例えば、1つの命令は、次のパラメータを指定する。

30

ビデオブロック幅 - バイトで表わされるデータブロックの幅(列数)。

ビデオブロック長 - バイトで表わされるデータブロック長(行数)。

ソースメモリ開始アドレス - ソースメモリからデータを読み出すための開始アドレスであり、一般に、転送されるブロック内の左上の画素。

宛先メモリ開始アドレス - 宛先メモリ内にデータを書込むための開始アドレス。

ジャンプ間隔 - ある行の最後と次の行の最初との間のアドレスの個数をバイトで示すアドレスジャンプパラメータ。

ソースメモリワード幅 - ソースメモリ内の1ワード当たりのバイト数。

40

宛先メモリワード幅 - 宛先メモリ内の1ワード当たりのバイト数。

ゼロパッドフラグ - データをゼロで埋めるかどうかを制御するプールフラグ。

#### 【0026】

上述のパラメータリストにおいて、ビデオブロック幅およびビデオブロック長は、バイトで表わされる希望の長方形のブロックの次元を定めるのに使用される。ソースメモリワード幅および宛先メモリワード幅により、VDMA制御装置26は、データを転送するときに、データパッキングが必要かどうかを判断することができる。例えば、ソースメモリが8ビット幅であり、宛先メモリが64ビット幅であるとき、VDMA制御装置26は、ソースメモリから8バイトを読み出し、それらを64ビットワードへパックし、宛先メモリへ書込む。

50

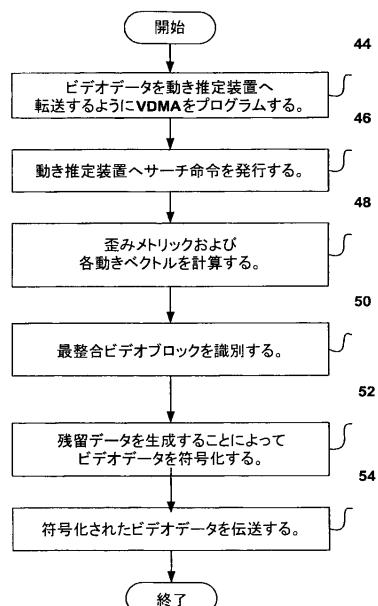

## 【0027】

図4は、フレーム間で時間的な冗長を取り除くことによって、ビデオ系列を符号化する処理を示すフローチャートである。DSP28は、プロセッサ30の指示を受けて、ビデオメモリ15からビデオデータをフェッチして、動き推定装置24へ送るように、VDMA制御装置26をプログラムする(44)。とくに、DSP28は、ビデオメモリ15内のビデオデータの1つ以上のブロックを指定するビデオブロック移動命令を、VDMA制御装置26へ発行する。応答して、VDMA制御装置26は、不連続のビデオデータを、ビデオメモリ15から動き推定装置24の内部メモリへ転送するのに必要な全てのアドレス計算を行う。例えば、DSP28によって発行される命令に応答して、VDMA制御装置26は、伝送される現在のビデオブロックと、既に伝送されたビデオフレームとを、ビデオメモリ15から動き推定装置24へ転送する。

10

## 【0028】

符号化処理は、DSP28と動き推定装置24との間で分割される。とくに、DSP28は、符号化アルゴリズムを実行するが、一般的なデータ処理機能を実行するには動き推定装置24を使用する。したがって、全サーチアルゴリズムが専用ハードウェア装置内で実行される従来のアプローチとは異なり、DSP28上で実行するソフトウェアは、動き推定装置24に変更を要求することなく、直ちに変更される。

## 【0029】

例えば、符号化処理中に、DSP28は、既に伝送されたビデオフレームをサーチして、符号化される現在のビデオブロックに最も類似したビデオブロックを識別する命令を、動き推定装置24へ発行する(46)。この命令は、現在のブロックを選択し、かつ前のビデオフレームのブロックと比較するのに必要な全情報を指定する。さらに加えて、命令は、一般的のフォーマットにしたがっており、従来のサーチングアルゴリズムで直ちに使用される。例えば、命令は、サーチ空間の左上角部の(X, Y)座標、サーチ空間の右下角部の(X, Y)座標、およびある行の最後と次の行の最初との距離をバイトで示すジャンプ値を指定する。

20

## 【0030】

命令に応答して、動き推定装置24は、符号化される現在のビデオブロックと、前のフレームのブロックとを比較して、ブロックの歪みメトリックの組と、各動きベクトルとを出力する(48)。歪みメトリックは、伝送されるブロックと、前のフレームの種々のブロックとの差を相対的に示す。動き推定装置24は、並行して計算を行い、サーチ空間内の各ブロック歪みメトリックを生成する。

30

## 【0031】

歪みメトリックを計算するために、動き推定装置24は、既に伝送されたビデオフレームと、符号化される現在のブロックとを使用して、多数のアルゴリズムの1つを実行する。動き推定装置24は、符号化されるブロックと、前のビデオフレーム内のブロックとにおいて、例えば、絶対差の和(Sum of Absolute the Difference, SAD)または平方差の和(Sum of the Squared Difference, SSD)を計算する。その代りに、動き推定装置24は、ビデオデータ間の平均平方誤差(Mean Square Error, MSE)を計算するか、または正規化相互相關関数(Normalized Cross Correlation Function, NCCF)を実行してもよい。

40

## 【0032】

DSP28は、歪みメトリックに基づいて、サーチ空間内の1つまたは複数の最整合ブロックを識別する(50)。DSP28は、例えば、MPEGの符号化されたビデオデータにおいて、最も近いマクロブロックを示す1つの動きベクトルか、または4つのブロックを示す4つの動きベクトルを選択する。DSP28は、最整合ブロックを判断すると、データを符号化するための多数の画像処理機能を実行する(52)。例えば、DSP28は、転送されるブロックから、選択されたブロックを減算することによって動き補償を行う。さらに加えて、DSP28は、離散コサイン変換(DCT)を実行して、信号エネルギーを係数および量子化ヘパックし、符号化するビット数を低減する。プロセッサ30は、伝送のために二次元の係数データを一次元へ変換するための走査と、ヘッダおよび圧縮パラメータを追加

50

するためのビットストリームの符号化とを行なう。最後に、プロセッサ30は、送信機／受信機14と対話して、DSP28によって生成された符号化されたデータを伝送する(54)。

#### 【0033】

このようにして、CODEC20は、プロセッサ30、DSP28、および動き推定装置24の間で、動き推定およびビデオ圧縮タスクを分割する。とくに、プロセッサ30は、高レベルの監視役で働き、DSP28は、非常に多くの計算を行なう符号化アルゴリズムを処理し、動き推定装置24は、専用ハードウェアを使用して、高速のサーチを行なう。CODEC20は、この分割により高い性能を実現できるが、将来のビデオ圧縮の標準規格を支援するために、依然として容易にアップグレード可能である。さらに加えて、組込まれたプロセッサがサーチング技術を全体的に実行する従来のアプローチよりも、プロセッサ30の計算の負荷およびCODEC20の電力消費量を相当に低減することができる。10

#### 【0034】

図5は、動き推定装置24の例示的な実施形態をさらに詳しく示すブロック図である。動き推定装置24は、符号化される現在のブロックをキャッシュするための2つの内部高速メモリ60、62と、現在のブロックを差別的に符号化するのに使用するためのビデオデータとを含む。とくに、動き推定装置24は、符号化される現在のブロックを記憶するためのブロックメモリ60を含む。さらに加えて、動き推定装置24は、既に伝送された最も近いビデオブロックを識別するデータを含む全データを記憶するためのサーチ空間メモリ62を含む。例えば、MPEGを支援する実施形態において、ブロックメモリ60は、伝送されるマクロブロックを記憶し、一方でサーチ空間メモリ62は、既に伝送されたビデオフレームのような、複数の既に伝送されたマクロブロックを記憶する。この構成では、通常のブロックは $8 \times 8$ バイトから成り、マクロブロックは $16 \times 16$ バイトから成り、サーチ空間は $48 \times 48$ バイトから成る。20

#### 【0035】

差分計算器64は、メモリ60、62からビデオデータを検索するためのアドレス生成論理を含む。符号化処理中に、VDMA制御装置26は、ビデオメモリ15から現在のブロックをフェッチし、現在のブロックをメモリ60内に記憶する。さらに加えて、VDMA制御装置26は、前のビデオフレーム内のサーチ空間をフェッチし、サーチ空間メモリ62内にビデオデータを記憶する。したがって、DSP28は、指定されたビデオデータを、動き推定装置24の各内部メモリ60、62へ転送するように、VDMA制御装置26をプログラムする。とくに、DSP28は、ビデオブロック移動命令をビデオVDMA制御装置26へ発行し、ビデオメモリ15内の不連続のビデオデータブロックと、メモリ15、60、62のワード幅のような他の必要なパラメータとを指定し、VDMA制御装置26がメモリ15、60、62間で不連続のビデオデータを正しく転送できるようにする。30

#### 【0036】

差分計算器64は、DSP28からサーチ命令72を受信すると、メモリ60、62内に記憶されているビデオデータを検索し、ビデオデータ間で画素に関する比較を行って、1つ以上の差分メトリックを計算する。各サーチ命令72は、差分メトリックを生成するのに使用するための、メモリ62内のビデオデータの多次元領域を指定する。例として、各サーチ命令72は、メモリ62内の領域の左上角部と右下角部とを指定する。40

#### 【0037】

したがって、DSP28は、動き推定アルゴリズムの実行中に、メモリ60、62によって記憶されたビデオデータを何度も使用するように、差分計算器64に命令する。符号化される現在のブロックおよび全サーチ空間をメモリ60、62内にそれぞれ内部キャッシュすることによって、動き推定装置24は、サーチ間に、ビデオメモリ15にアクセスする必要がなくなる。したがって、CODEC20は、従来のアーキテクチャに関係する符号化速度を増すことができる。

#### 【0038】

差分メトリックを計算するために、差分計算器64は、多数のアルゴリズムの1つを実行し、メモリ60内に記憶されている現在のブロックと、サーチ空間メモリ62内の種々のブロ50

ックとの差を示す出力を生成する。既に記載したように、差分計算器64は、符号化されるブロックと前のビデオフレーム内のブロックとの絶対差の和（S A D）または平方差の和（S S D）を実行する。その代りに、差分計算器64は、平均平方誤差（M S E）または正規化相互相關関数（N C C F）を実行してもよい。

#### 【0039】

差分測定値および動きベクトルを計算するとき、差分計算器64は、中断（interrupt, I N T）66をアサートし、保留中の結果についてD S P 28に知らせる。中断数を低減するために、動き推定装置24は、命令（command, CMD）緩衝器70を含み、D S P 28から受信したサーチ命令72を記憶する。C M D 緩衝器70は、例えば、受信した命令を緩衝するための先入れ先出し（first-in first-out, FIFO）待ち行列を含む。したがって、D S P 28は、結果を報告する前に、動き推定装置24によって実行される複数のサーチを指定することができる。10

#### 【0040】

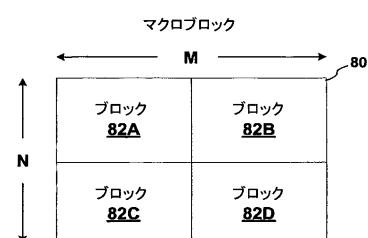

図6は、メモリ60内に記憶される例示的なマクロブロック80を示す。既に記載したように、この実行は、M P E G、およびマクロブロックを使用する他のビデオ圧縮方式において有益である。とくに、マクロブロック80は、ビデオデータの4つのブロック82Aないし82Dを含む。この実施形態では、差分計算器64のアドレス生成論理は、4つのブロック82の何れかにアクセスするように構成されている。各ブロック82が8バイト（M / 2）の幅と8バイト（N / 2）の長さとをもち、マクロブロック60が8バイトのワード幅をもつ例示的な構成について検討する。この構成では、メモリ60内において、ブロック82Aおよび82Bの行は交互になり、ブロック82Cおよび82Dの交互の行が続く。したがって、各ブロック82の差分メトリックを計算するために、差分計算器64のアドレス生成論理は、直列または並列に、個々のブロック82をフェッチするアドレスを生成する。20

#### 【0041】

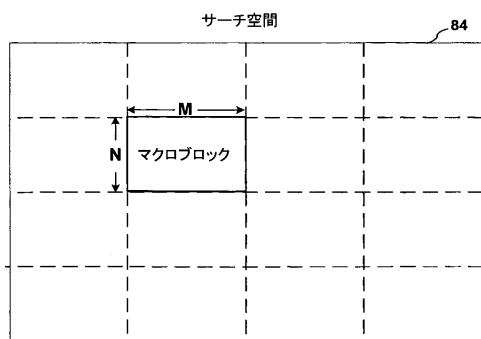

図7は、M P E Gおよび他のビデオ圧縮方式で使用するのに有益なサーチ空間メモリ62内に記憶される例示的なサーチ空間84を示す。とくに、サーチ空間84は、ビデオデータを記憶し、その一部は差の計算に使用される。

1つの構成において、差分計算器64のアドレス生成論理は、サーチ空間メモリ62からM × 4の連続するバイトをフェッチするためのアドレスを生成する。したがって、多数の候補のブロックの差分メトリックを並列に計算することができる。30

#### 【0042】

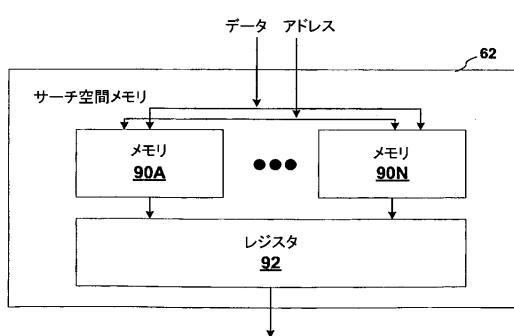

図8は、図7に示されているようなM × N次元のマクロブロックを含むサーチ空間を記憶するためのサーチ空間メモリ62の例示的な構成を示す。とくに、サーチ空間メモリ62は、Mバイト幅のメモリ90を含む。1サイクルにおいて、レジスタ92はメモリ90からMバイトを受信し、バイトを連結してから、検索されたデータを差分計算器64へ送る。したがって、差分計算器64は、1クロックサイクルにおいて、マクロブロック内のブロックの1つからビデオデータの行全体をフェッチすることができる。ブロックの連続する行は、メモリ90内で隣り合っていないので、差分計算器64のアドレス生成論理は、ブロック全体をフェッチするために、アクセスのたびにアドレスをジャンプする。

#### 【0043】

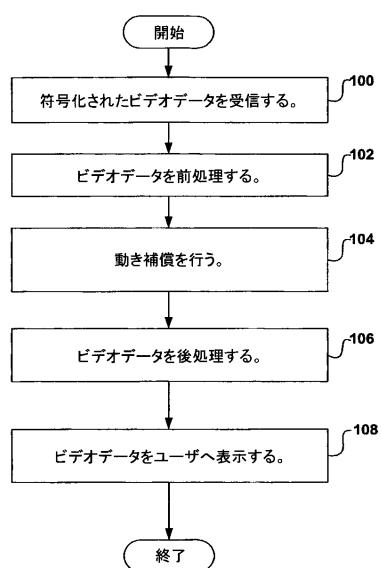

図9は、本発明の原理にしたがって、ビデオ系列を復号する処理を示すフローチャートである。プロセッサ30またはC O D E C 20は、送信機／受信機14およびアンテナ12を介して、符号化されたビデオ系列を受信する（100）。その後で、プロセッサ30は、受信ビットストリームをアンパックして、逆量子化および逆離散コサイン変換（inverse discrete cosine transformation, IDCT）を行うことによって、ビデオデータを前処理する（102）。

#### 【0044】

次に、プロセッサ30は、受信した動きベクトルが、もしあれば、それを、既に受信したビデオデータへ適用することによって動き補償を行う（104）。この処理中に、プロセッサ30は、V D M A 制御装置26を使用して、ブロック命令を用いて、既に伝送されたデータ4050

をビデオメモリ15から検索する。同様に、プロセッサ30は、生成されたビデオデータをビデオメモリ15へ転送するように、V D M A 制御装置26に命令する。

【 0 0 4 5 】

次に、プロセッサ30は、圧縮アルゴリズムによって取入れられるブロッキング効果を除去し、かつ必要な色変換を行う後処理をビデオデータに行うように、D S P 28に命令する(106)。D S P 28は、V D M A を使用して、ビデオメモリ15からビデオデータを検索し、後処理されたビデオデータをビデオメモリ15へ記憶する。

【 0 0 4 6 】

最後に、プロセッサ30は、ユーザが見るために、復号されたビデオデータをディスプレイ17に表示するように、ディスプレイ制御装置37に命令する。とくに、プロセッサ30は、V D M A 制御装置26を呼出して、復号されたビデオデータをビデオメモリ15からフレーム緩衝器38へ転送する。

10

【 0 0 4 7 】

本発明の種々の実施形態を記載した。これらの、および他の実施形態は、特許請求項の技術的範囲内である。

【 図面の簡単な説明 】

【 0 0 4 8 】

【図1】ソース装置がビデオデータの符号化された系列を受信装置へ伝送する例示的なシステムを示すブロック図。

20

【図2】本発明の原理にしたがって、ディジタルビデオ系列を圧縮および逆圧縮するビデオ符号器／復号器(C O D E C)を取り入れた例示的なディジタルビデオ装置を示すブロック図。

【図3】C O D E C の例示的な実施形態をさらに詳しく示すブロック図。

【図4】本発明の原理にしたがってビデオ系列を符号化する処理を示すフローチャート。

【図5】動き推定装置の例示的な実施形態を示すブロック図。

【図6】メモリ内に記憶されているビデオデータの例示的なマクロブロックを示す図。

【図7】メモリ内に記憶されている例示的なサーチ空間を示す図。

【図8】M × N 次元のマクロブロックをもつサーチ空間を記憶するためのメモリの例示的な構成を示す図。

【図9】本発明の原理にしたがって、ビデオ系列を符号化する処理を示すフローチャート。

30

。

【 符号の説明 】

【 0 0 4 9 】

2 · · · システム、6 · · · ビデオデータ、2 1 · · · プロセッサバス、2 3 · · · D S P バス、2 5 · · · 入力／出力(I / O)バス。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100101812

弁理士 勝村 紘

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(74)代理人 100127144

弁理士 市原 卓三

(74)代理人 100141933

弁理士 山下 元

(72)発明者 シュ、ギルバート・シー

アメリカ合衆国、カリフォルニア州 92129、サン・ディエゴ、ピピット・プレイス 780

4

(72)発明者 ティアン、ユシ

アメリカ合衆国、カリフォルニア州 92131、サン・ディエゴ、カミニト・アルカダ 111

43

## 合議体

審判長 奥村 元宏

審判官 千葉 輝久

審判官 藤内 光武

(56)参考文献 國際公開第00/36841(WO,A1)

特開2000-175199(JP,A)

特開平11-316708(JP,A)

特開2001-218215(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N7/26-50