(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3825949号

(P3825949)

(45) 発行日 平成18年9月27日(2006.9.27)

(24) 登録日 平成18年7月7日(2006.7.7)

(51) Int.C1.

F 1

|             |              |                  |      |       |      |

|-------------|--------------|------------------|------|-------|------|

| <b>H03M</b> | <b>1/10</b>  | <b>(2006.01)</b> | H03M | 1/10  | B    |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | G02F | 1/133 | 505  |

| <b>G09F</b> | <b>9/35</b>  | <b>(2006.01)</b> | G09F | 9/35  | 305  |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20  | 611H |

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | G09G | 3/20  | 623F |

請求項の数 7 (全 8 頁) 最終頁に続く

(21) 出願番号 特願2000-30625 (P2000-30625)

(22) 出願日 平成12年2月8日 (2000.2.8)

(65) 公開番号 特開2000-307424 (P2000-307424A)

(43) 公開日 平成12年11月2日 (2000.11.2)

審査請求日 平成16年6月21日 (2004.6.21)

(31) 優先権主張番号 特願平11-37319

(32) 優先日 平成11年2月16日 (1999.2.16)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100065385

弁理士 山下 橋平

(72) 発明者 吉田 大介

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 清水 稔

最終頁に続く

(54) 【発明の名称】電子回路およびそれを用いた液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

デジタルデータを記憶する記憶手段と、

入力されたデジタル信号と、前記記憶手段から読み出された前記デジタルデータとを加算又は減算する演算手段と、

前記演算手段から出力された演算されたデジタル信号を入力し、アナログ信号に変換して出力するDAコンバータと、を有するユニットを、

複数備えた電子回路であって、

更に、第2の演算手段と、第2のDAコンバータと、前記各ユニットの前記DAコンバータからの出力と前記第2のDAコンバータの出力を比較する比較器と、前記比較器からのアナログ出力を前記デジタルデータにエンコードするエンコーダと、を有しており、各ユニットに、対応する前記DAコンバータからの出力と前記デジタル信号に基づく前記第2のDAコンバータの出力を比較して、各DAコンバータ固有のオフセット量を測定し、

各ユニットの前記記憶手段は、同ユニット内の前記DAコンバータ固有の前記オフセット量を前記デジタルデータとして記憶しており、当該デジタルデータを基に前記DAコンバータ固有の前記オフセット量が補正された、アナログ信号を出力することを特徴とする電子回路。

## 【請求項 2】

順次オンされるスイッチを介して前記各ユニットの前記DAコンバータからのアナログ

信号を入力して、前記各ユニットの前記オフセット量を測定する、前記各ユニットに共通の回路を有する請求項 1 に記載の電子回路。

【請求項 3】

デジタルデータを記憶する記憶手段と、

入力されたデジタル信号と、前記記憶手段から読み出された前記デジタルデータとを加算又は減算する演算を行う演算手段と、

前記演算手段から出力された演算されたデジタル信号を入力し、アナログ信号に変換して出力する D A コンバータと、を有するユニットを、複数備え、

各ユニットの前記記憶手段は、同ユニット内の前記 D A コンバータ固有の前記オフセット量を前記デジタルデータとして記憶しており、当該デジタルデータを基に前記 D A コンバータ固有の前記オフセット量が補正された、アナログ信号を出力する電子回路であって

10

前記各ユニットの前記 D A コンバータは、

前記入力されたデジタル信号の上位ビットをデコードすることにより選択された基準電圧と、

前記入力されたデジタル信号の下位ビットと前記記憶手段に記憶された前記デジタルデータの上位ビットとを演算して得られたデータと、

前記記憶手段に記憶された前記デジタルデータの下位ビットと、を入力することを特徴とする電子回路。

【請求項 4】

前記各ユニットは、前記入力されたデジタル信号の上位ビットをデコードし、前記デコーダの出力に応じて前記 D A コンバータに供給する基準電圧を選択する請求項 1 乃至 3 のいずれか 1 項に記載の電子回路。

20

【請求項 5】

前記各ユニットの前記演算手段は、前記入力されたデジタル信号の下位ビットと前記記憶手段に記憶された前記デジタルデータの上位ビットとを演算する請求項 1 乃至 3 のいずれか 1 項に記載の電子回路。

【請求項 6】

前記各ユニットは、前記入力されたデジタル信号の上位ビットをデコードし、前記デコーダの出力に応じて前記 D A コンバータに供給する 2 つの基準電圧を選択し、前記入力されたデジタル信号の下位ビットによって前記 2 つの基準電圧の間を更に分割する請求項 4 に記載の電子回路。

30

【請求項 7】

画像表示装置において、

請求項 1 乃至 6 に記載の電子回路と、

前記電子回路に接続された信号線を有するアクティブマトリクス回路基板と、

を具備することを特徴とする画像表示装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、複数の D A コンバータからなる電子回路及びそれを用いた液晶表示装置に関するもので、特に、D A コンバータは各々にオフセット量を補正するためのデジタルデータを記憶する手段を有し、デジタルの入力信号に対し前記オフセット量を補正するためのデジタルデータを加算又は減算する手段を有する D A コンバータからなる電子回路及びそれを用いた液晶表示装置に関するもの。

40

【0002】

【従来の技術】

従来、複数の D A コンバータを使用した回路としては、図 7 に示したようにデータラッチ回路と D A コンバータのみで構成されている。このような回路を液晶表示装置に応用した場合、図 8 に示すようになる。図においては複数の垂直信号線に映像信号を転送する手段

50

として、複数のDAコンバータを用いている。

#### 【0003】

##### 【発明が解決しようとする課題】

しかし、上記した従来技術には以下に述べる問題点があった。すなわち、各々のDAコンバータは少なからず特性にばらつきがあり、特に出力段のアナログバッファ回路にCMOS構成のアンプを用いた場合、DCオフセットが各アンプ毎に大きく異なってしまう。ある垂直信号線には必ず1つのDAコンバータから信号が書き込まれるため、DAコンバータの特性ばらつきがそのまま画像表示のばらつきとして視認され、より具体的には、DAコンバータのブロック毎に縦の帯状のパターンが視認され、表示品位を低下させるという問題点があった。

10

#### 【0004】

そこで、本発明は、DAコンバータのオフセットばらつきがあっても、これを補正することができるであり、全DAコンバータの特性を同一にすることが可能な回路を提供することを課題としている。さらに、本発明は、これを液晶表示装置に応用することにより、全体にはばらつきのない均一な表示特性の液晶表示装置を実現することを課題としている。

#### 【0005】

##### 【課題を解決するための手段】

上記の課題を解決するための本発明の電子回路は、デジタルデータを記憶する記憶手段と、入力されたデジタル信号と、前記記憶手段から読み出された前記デジタルデータとを加算又は減算する演算を行う演算手段と、前記演算手段から出力された演算されたデジタル信号を入力し、アナログ信号に変換して出力するDAコンバータと、を有するユニットを、複数備えた電子回路であって、更に、第2の演算手段と、第2のDAコンバータと、前記各ユニットの前記DAコンバータからの出力と前記第2のDAコンバータの出力とを比較する比較器と、前記比較器からのアナログ出力を前記デジタルデータにエンコードするエンコーダと、を有しており、各ユニットの前記記憶手段は、同ユニット内の前記DAコンバータ固有の前記オフセット量を前記デジタルデータとして記憶しており、当該デジタルデータを基に前記DAコンバータ固有の前記オフセット量が補正された、アナログ信号を出力することを特徴とする。

20

#### 【0006】

##### 【発明の実施の形態】

30

以下、図面を参照して、本発明の実施の形態について説明する。

#### 【0007】

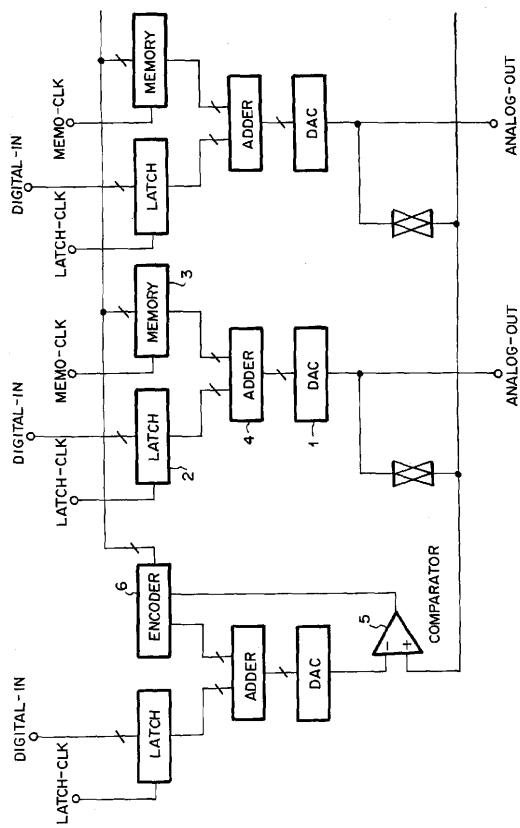

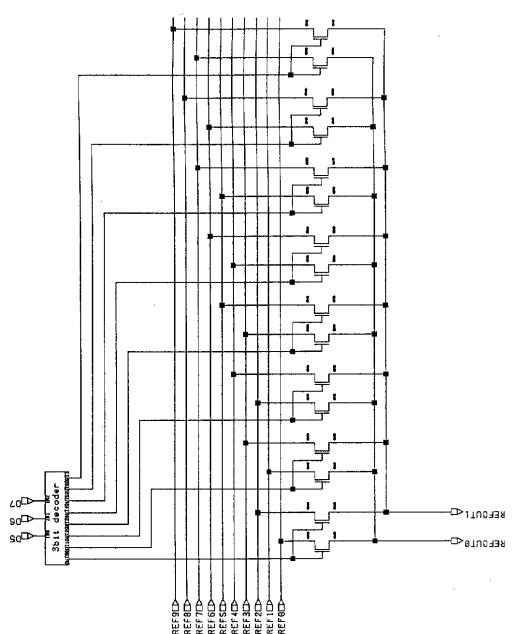

図1は本発明の電子回路のブロック図である。図においてDAコンバータ1は図の水平方向に複数配されており、各々にデジタル信号を記憶するラッチ回路2、オフセット補正データを記憶するメモリ回路3、前記デジタル信号に前記オフセット補正データを加算する加算回路4を有している。また、図の左端に示す回路は、各DAコンバータのオフセット量を測定し、前記オフセット量をデジタルデータに変換する回路であり、デジタル信号を記憶するラッチ回路2とデジタルデータをアナログ信号に変換するDAコンバータ1と水平方向に配されたDAコンバータ1のアナログ出力と前記オフセット量測定回路中のDAコンバータのアナログ出力を比較する比較器5の出力によってデジタルのオフセット補正データを発生するエンコーダ回路6から成っている。

40

#### 【0008】

次に、本発明回路の動作について説明する。まず各データラッチ回路に同レベルのデジタルデータを転送する。このとき各オフセット補正データを記憶するメモリ回路は所定のレベルにリセットする。各DAコンバータには同一レベルのデジタル信号が転送されるが、各DAコンバータのアナログ出力は、各々のDAコンバータに固有のオフセット量が上乗せされているため、各々のアナログ出力値が異なっている。ここで各DAコンバータの出力に接続されたスイッチを順次オンしていく。そして各々のDAコンバータのアナログ出力はオフセット補正データ発生ADコンバタ回路内のDAコンバータのアナログ出力と比較され、各DAコンバータのアナログ出力の、オフセット補正ADコンバータ内のDA

50

コンバータのアナログ出力に対するオフセット量が測定され、このオフセット量はエンコーダ回路によってデジタルデータとして出力され、各々の D A コンバータ毎に配されたメモリ回路に順次書き込まれる。

【 0 0 0 9 】

以上の動作により各 D A コンバータ毎に配されたオフセット補正用メモリ回路に各 D A コンバータ毎のオフセット量に対応するデータが記憶された状態となり、全 D A コンバータはこれ以降同等の特性を得られるようになる。

【 0 0 1 0 】

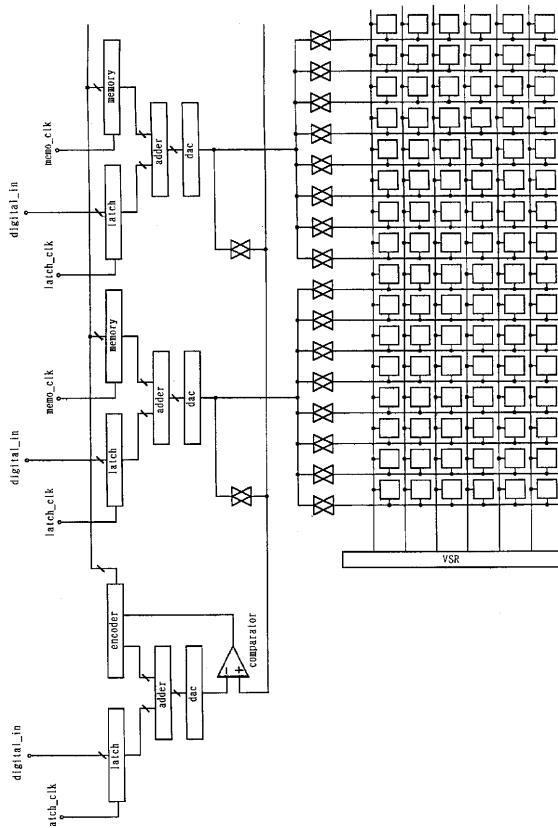

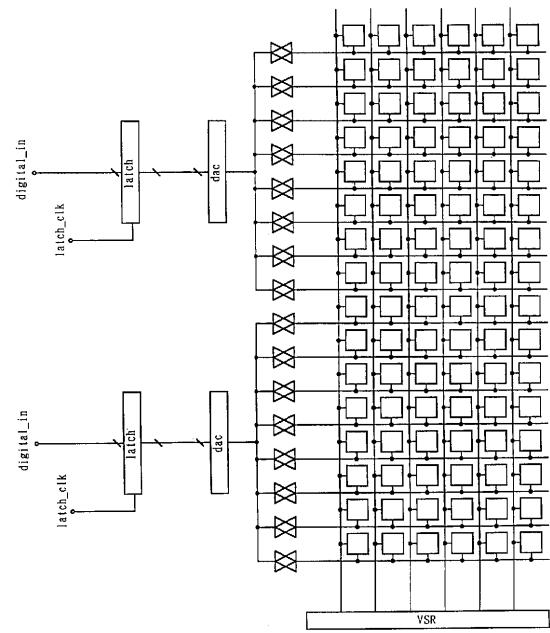

図 2 は本発明の電子回路を液晶表示装置に応用した実施形態を示したブロック図である。

図において、D A コンバータのアナログ出力は信号転送スイッチを介して垂直信号線に転送される。画素部は画素トランジスタ、付加容量、液晶からなり、垂直シフトレジスタの出力によって順次走査線が選択され、該画素トランジスタがオン状態となり、画素電極に信号が書き込まれる。先に述べたオフセット補正のための動作は電源投入時に行えばよく、さらに望ましくは 1 フィールド毎のブランкиング期間に行えばよい。

10

【 0 0 1 1 】

以上により、D A コンバータの特性ばらつきがあってもそれぞれに関して補正されているので、全体として均一な表示が得られる。

【 0 0 1 2 】

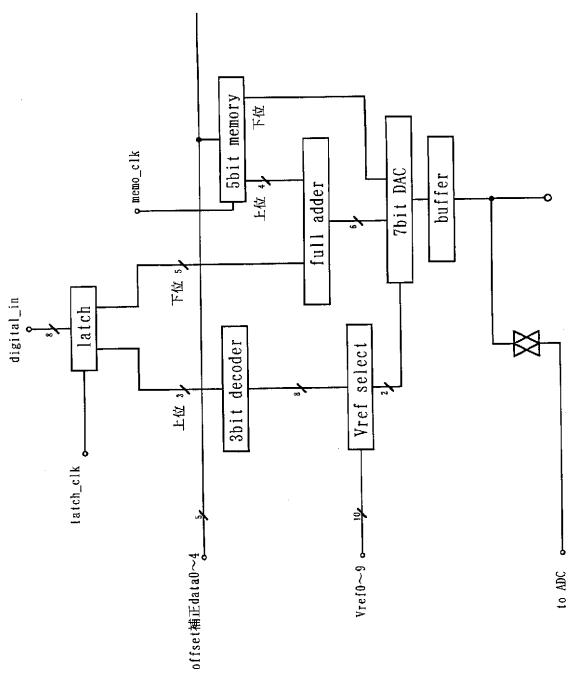

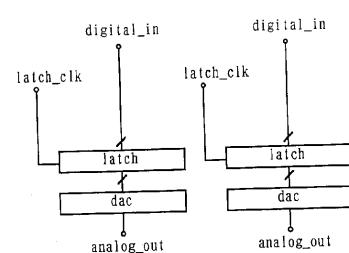

図 3、図 4、図 5 は本発明の電子回路の D A コンバータのブロック図である。図においては、デジタル入力信号が 8 ビットであり、上位 3 ビットと下位 5 ビットを分離して D A 変換を行う例を示している。本実施形態ではオフセット補正はデジタル入力信号の ( 1 / 2 ) L S B まで可能である。

20

【 0 0 1 3 】

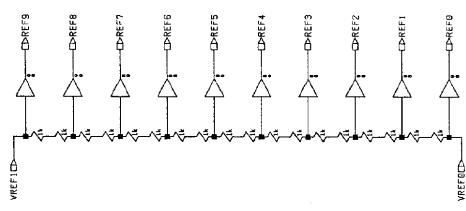

図 4 の回路で直列の抵抗分割とバッファ回路によって 10 ヶの基準電圧を発生させる。

【 0 0 1 4 】

そして図 5 の回路において、デジタル信号の上位 3 ビットをデコードして前記 10 ヶの基準電圧源のうち 1 つ間をおいた 2 ヶを選択する。

【 0 0 1 5 】

次にデジタル入力信号の下位 5 ビットと、5 ビットのオフセット補正信号のうち上位 4 ビットとを加算し 6 ビットのデータを発生させる。先に選択された 2 ヶの基準電圧は図示の 7 ビット D A 変換器に入力され、この 2 ヶの基準電圧のレンジ内を D A 変換する。ここでは前記デジタル入力信号の下位 5 ビットとオフセット補正デジタル信号の上位 4 ビットを加算した結果である 6 ビットのデータを、前記 7 ビット D A コンバータの上位 6 ビットに入力し、前記オフセット補正信号の最下位 1 ビットを前記 7 ビット D A コンバータの最下位 1 ビットに入力する。以上によりオフセット補正はデジタル入力信号の 1 / 2 L S B の精度で可能であり、補正レンジとしては入力デジタル信号の 15 L S B まで可能となる。

30

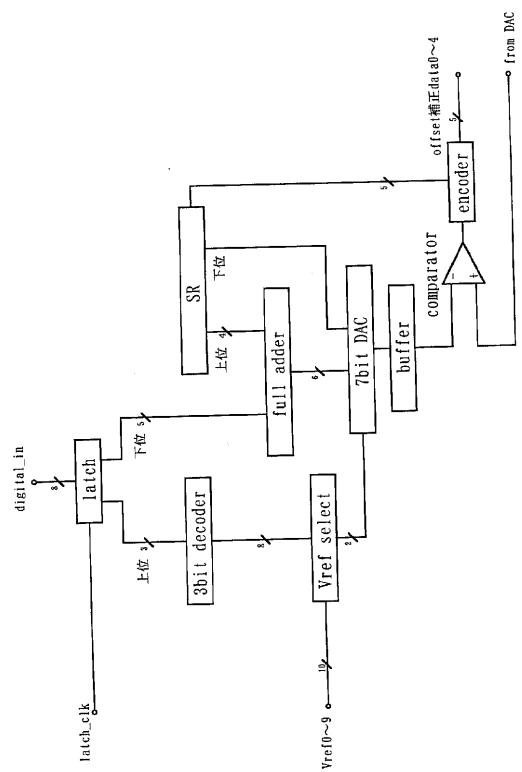

【 0 0 1 6 】

図 6 は本発明の電子回路の A D コンバータ回路のブロック図である。本実施形態ではシフトレジスタ回路の出力を最上位ビットから順次入力し、このデータとデジタル入力データを加算したデータを D A 変換し、このアナログ出力を不図示の D A コンバータのアナログ出力と逐次比較する。この動作を D A コンバータの最下位ビットまで繰り返すことにより、デジタルの補正データが確定する。この結果をエンコーダ回路によってエンコードし、各々の D A コンバータ毎のメモリに記憶する。

40

【 0 0 1 7 】

以上、本発明の本実施形態について説明したが、本発明は液晶表示装置への適用に限らず、音声処理用回路、画像処理回路等に適用してもよい。

【 0 0 1 8 】

【 発明の効果 】

以上説明した本発明によれば、D A コンバータのオフセット量にはらつきがあっても各々に関して固有の補正が可能であるため、全ての D A コンバータは結果的に同一の特性が得

50

られ、このような回路を液晶表示装置に応用した場合、全体にわたって均一な表示が得られる。

【図面の簡単な説明】

【図1】本発明に係る電子回路の実施形態を示した回路ブロック図である。

【図2】本発明に係る液晶表示装置の実施形態を示したブロック図である。

【図3】本発明に係るDAコンバータを示した回路ブロック図である。

【図4】本発明に係るDAコンバータを示した回路ブロック図である。

【図5】本発明に係るDAコンバータを示した回路ブロック図である。

【図6】本発明に係るADコンバータ回路部の実施形態を示した回路図である。

【図7】従来技術のDAコンバータを用いた回路を示したブロック図である。

【図8】従来技術の回路を液晶表示装置に応用した場合を示したブロック図である。

10

【符号の説明】

- 1 DAコンバータ

- 2 ラッチ回路

- 3 メモリ回路

- 4 加算回路

- 5 比較器

- 6 エンコーダ回路

【図1】

【図2】

【図3】

【 図 6 】

【 図 4 】

【 図 5 】

【 四 7 】

【図8】

---

フロントページの続き

(51)Int.Cl. F I

**H 03M 1/66 (2006.01)** G 09G 3/36

H 03M 1/66

C

(56)参考文献 特開平05-265405 (JP, A)

特表平10-503292 (JP, A)

特開平04-135323 (JP, A)

国際公開第03/017243 (WO, A1)

特開平04-142591 (JP, A)

## (58)調査した分野(Int.Cl., DB名)

H03M 1/10

G02F 1/133

G09F 9/35

G09G 3/20

G09G 3/36

H03M 1/66