(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-227495

(P2008-227495A)

(43) 公開日 平成20年9月25日(2008.9.25)

(51) Int.Cl.

H01L 29/861 (2006.01)

F 1

H01L 29/91

テーマコード (参考)

L

審査請求 未請求 請求項の数 36 O L (全 14 頁)

(21) 出願番号 特願2008-59321 (P2008-59321)

(22) 出願日 平成20年3月10日 (2008.3.10)

(31) 優先権主張番号 11/684, 261

(32) 優先日 平成19年3月9日 (2007.3.9)

(33) 優先権主張国 米国(US)

(71) 出願人 508073601

ダイオーズ ファブテック インコーポレ

イテッド

アメリカ合衆国 ミズーリ州 64086

リーズ サミット ノースウェスト ブ

ルー パークウェイ 777 スイート

350

(74) 代理人 100082005

弁理士 熊倉 槟男

(74) 代理人 100067013

弁理士 大塚 文昭

(74) 代理人 100086771

弁理士 西島 孝喜

(74) 代理人 100109070

弁理士 須田 洋之

最終頁に続く

(54) 【発明の名称】高効率整流器

## (57) 【要約】

【課題】電力半導体整流デバイス及びそれを製造する方法を提供する。

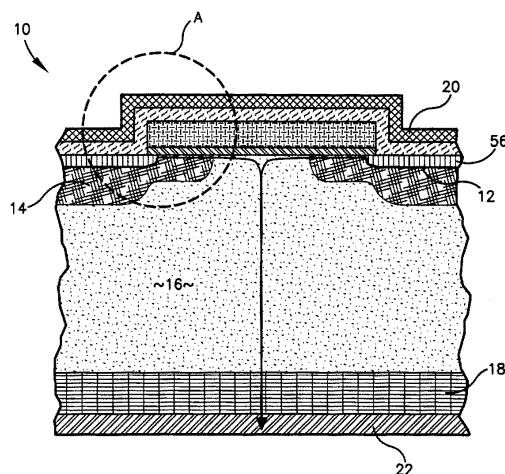

【解決手段】P++層(12)、P-ボディ(14)、N-ドリフト領域(16)、N+基板(18)、アノード(20)、及びカソード(22)を含む高効率電力半導体整流デバイス(10)が開示される。デバイス(10)を製造する方法は、N+基板(18)上にN-ドリフト領域(16)を堆積させる段階と、N+ドリフト領域(16)内にホウ素を注入してP-ボディ領域(14)を作成する段階と、P-ボディ領域(14)上にチタンシリサイドの層(56)を形成する段階と、注入ホウ素の一部分をチタンシリサイドの層(56)とP-ボディ領域(14)の間のインターフェース領域で濃縮し、過飽和P-ドープシリコンのP++層(12)を作成する段階とを含む。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

第1の導電型のドーパントにより過飽和された過飽和シリコンの層と、

実質的に前記過飽和シリコンの層の下方に該層に隣接して配置された前記第1の導電型

のボディ領域と、

実質的に前記ボディ領域の下方に該領域に隣接して配置された第2の導電型のドリフト

領域と、

実質的に前記ドリフト領域の下方に配置された前記第2の導電型の基板と、

を具備することを特徴とする半導体整流デバイス。

**【請求項 2】**

10

実質的に前記過飽和シリコンの層の上方に該層に隣接して配置され高次シリサイドを含

むシリサイド領域、を更に具備する、請求項1に記載の半導体整流デバイス。

**【請求項 3】**

P++層と、

実質的に前記P++層の下方に該層に隣接して配置されたP-ボディと、

実質的に前記P-ボディ領域の下方に該領域に隣接して配置されたN-ドリフト領域と

、

実質的に前記N-ドリフト領域の下方に配置されたN+基板と、

を具備することを特徴とする半導体整流デバイス。

**【請求項 4】**

20

実質的に前記P++層の上方に配置されたアノードと、

実質的に前記N+基板の下方に配置されたカソードと、を更に具備する、請求項3に記

載の半導体整流デバイス。

**【請求項 5】**

前記P++層は、P-ドープシリコンの過飽和領域を含みかつ約数個の原子層の厚み

を有する、請求項3に記載の半導体整流デバイス。

**【請求項 6】**

前記N-ドリフト領域が、約0.4オーム・センチメートルの抵抗率及び約3マイクロ

メートルの厚みを有する、請求項3に記載の半導体整流デバイス。

**【請求項 7】**

30

前記N+基板が約 $5 \times 10^{-3}$ オーム・センチメートル以下の抵抗率を有する、請求項3

に記載の半導体整流デバイス。

**【請求項 8】**

前記N+基板がヒ素によりドープされる、請求項7に記載の半導体整流デバイス。

**【請求項 9】**

前記N+基板が燐によりドープされる、請求項7に記載の半導体整流デバイス。

**【請求項 10】**

実質的に前記P++層の上方に該層に隣接して配置された高次シリサイドの領域を更

に具備する、請求項3に記載の半導体整流デバイス。

**【請求項 11】**

40

前記N-ドリフト領域、前記P-ボディ、前記P++層、及び、前記チタンシリサイ

ドの領域のうちの1つ以上の実質的に上方に隣接して配置され、ゲート誘電体として機能

する酸化物の層を更に具備する、請求項10に記載の半導体整流デバイス。

**【請求項 12】**

前記酸化物が約85の厚みを有する、請求項11に記載の半導体整流デバイス。

**【請求項 13】**

実質的に前記酸化物の層の上方に該層に隣接して配置されたポリシリコンの層を更に具

備する、請求項11に記載の半導体整流デバイス。

**【請求項 14】**

前記ポリシリコンの層が約40keVのエネルギーでヒ素を注入される、請求項13に記

50

載の半導体整流デバイス。

【請求項 15】

実質的に前記ポリシリコンの層の上方に該層に隣接して配置されたチタンの層を更に具備する、請求項13に記載の半導体整流デバイス。

【請求項 16】

前記チタンが約300 の厚みを有する、請求項15に記載の半導体整流デバイス。

【請求項 17】

実質的に前記チタンの層の上方に該層に隣接して配置された窒化チタンの層を更に具備する、請求項15に記載の半導体整流デバイス。

【請求項 18】

前記窒化チタンの層が約500 の厚みを有する、請求項16に記載の半導体整流デバイス。

【請求項 19】

半導体整流デバイスを製造する方法であって、

(a) 第2の導電型のドリフト領域を該第2の導電型の基板上に堆積させる段階と、

(b) 前記ドリフト領域内に第1の導電型のドーパントを注入して該第1の導電型のボディ領域を作成する段階と、

(c) 前記ボディ領域上に高次シリサイドの層を形成する段階と、

(d) 前記注入ドーパントの一部分を前記高次シリサイドの層と前記ボディ領域の間のインターフェース領域で濃縮し、前記第1の導電型の該ドーパントで過飽和されたシリコンの層を作成する段階と、

を含むことを特徴とする方法。

【請求項 20】

前記高次シリサイドの層がチタンシリサイドを含む、請求項19に記載の方法。

【請求項 21】

半導体整流デバイスを製造する方法であって、

(a) N+基板上にN-ドリフト領域を堆積させる段階と、

(b) 前記N-ドリフト領域内にホウ素を注入してP-ボディ領域を作成する段階と、

(c) 前記P-ボディ領域上にチタンシリサイドの層を形成する段階と、

(d) 前記注入ホウ素の一部分を前記チタンシリサイドの層と前記P-ボディ領域の間のインターフェース領域で濃縮し、過飽和P-ドープシリコンのP++層を作成する段階と、

を含むことを特徴とする方法。

【請求項 22】

前記P++層が約数個の原子層の厚みを有する、請求項21に記載の方法。

【請求項 23】

半導体整流デバイスを製造する方法であって、

(a) シリコンN+基板上にN-層を堆積させる段階と、

(b) 前記N-層の上に酸化シリコンの層を成長させる段階と、

(c) 前記酸化シリコンの層の第1の部分を除去することにより、保護リングを形成する第1のフォトリソグラフィ段階を実行する段階と、

(d) 前記保護リング内にホウ素を注入してホウ素注入領域を作成する段階と、

(e) 前記ホウ素注入領域を拡散させる段階と、

(f) 前記ホウ素注入領域の上に前記酸化シリコンの層の前記第1の部分を再成長させる段階と、

(g) 前記酸化シリコンの層の第2の部分を除去して活性区域を開放する第2のフォトリソグラフィ段階を実行する段階と、

(h) 前記活性区域にゲート酸化物を成長させる段階と、

(i) 前記ゲート酸化物上にポリシリコンの層を堆積させる段階と、

(j) 前記ポリシリコンの層にヒ素を注入する段階と、

10

20

30

40

50

(k) 前記ポリシリコンの層を部分酸化し、酸化ポリシリコンの層と非酸化ポリシリコンの層とを作成し、結果としてNドープポリシリコンゲートをもたらす段階と、

(l) 前記ポリシリコンゲートを更に形成する第3のフォトリソグラフィ段階を実行する段階と、

(m) 反応性イオンエッティング処理を用いて前記酸化ポリシリコンの層をエッティングする段階と、

(n) 前記N-ドリフト領域内にホウ素を注入してP-ボディ領域を作成する段階と、

(o) フォトレジストを除去する段階と、

(p) 前記酸化ポリシリコンの層と前記ゲート酸化物の上面とをエッティングする段階と、

(q) 前記酸化ポリシリコンの層と前記ゲート酸化物の上にチタンの層を堆積させ、かつ該チタンの層の上に窒化チタンの層を堆積させる段階と、

(r) 前記酸化ポリシリコンの層の一部分を少なくとも約650の温度に露出することによって前記P-ボディ領域と前記チタンの層の間にチタンシリサイドの層を形成し、結果としてホウ素をインタフェースまで移動させ、該チタンシリサイドの層と該P-ボディ領域の間に過飽和P-ドープシリコンのP++層を作成する段階と、

を含むことを特徴とする方法。

#### 【請求項24】

段階(b)の前記酸化シリコンが約0.5マイクロメートルから1.0マイクロメートルの厚みに成長させられる、請求項23に記載の方法。

#### 【請求項25】

段階(h)の前記ゲート酸化物が約85の厚みに成長させられる、請求項23に記載の方法。

#### 【請求項26】

段階(i)の前記ポリシリコンが約1500の厚みに成長させられる、請求項23に記載の方法。

#### 【請求項27】

段階(j)において、前記ヒ素が約40keVのエネルギーで注入される、請求項23に記載の方法。

#### 【請求項28】

前記非酸化ポリシリコンの層が約800の厚みを有する、請求項23に記載の方法。

#### 【請求項29】

段階(o)において、前記ホウ素が約80keVのエネルギーで注入される、請求項23に記載の方法。

#### 【請求項30】

段階(q)において、前記ホウ素が約30keVのエネルギーで注入される、請求項23に記載の方法。

#### 【請求項31】

段階(q)において、前記チタンの層が300の厚みを有し、前記窒化チタンの層が500の厚みを有する、請求項23に記載の方法。

#### 【請求項32】

段階(t)において、前記P++層が約数個の原子層の厚みを有する、請求項23に記載の方法。

#### 【請求項33】

アノードを堆積させる段階を更に含む、請求項23に記載の方法。

#### 【請求項34】

前記アノードをエッティングする第4のフォトリソグラフィ処理を実行する段階を更に含む、請求項23に記載の方法。

#### 【請求項35】

前記N+基板を薄くする段階を更に含む、請求項23に記載の方法。

10

20

30

40

50

**【請求項 3 6】**

カソードを堆積させる段階を更に含む、請求項 2 3 に記載の方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、半導体デバイス及びそれを製造する方法に関する。より詳細には、本発明は、電力半導体整流デバイス及びそれを製造する方法に関する。

**【背景技術】****【0 0 0 2】**

最新の電力回路は、改善した電力スイッチング性能を有する電力整流器を必要とする。

高電圧の用途については、高い絶縁破壊電圧及び高い作動温度が望ましい時、高いスイッチング速度を有する P + / N 整流器が使用されることが多い。低電圧の用途については、高いスイッチング速度及び非常に低い順方向電圧低下が望ましい時、ショットキー障壁整流器が使用されることが多い。ショットキー障壁整流器は、回復中の逆方向電流フローを殆ど許さない多数キャリアデバイスである。残念なことに、ショットキー障壁整流器は、高温で作動する時の不必要に高い逆方向漏れ電流を欠点として有する。

10

**【0 0 0 3】**

ショットキー整流器の遮断機能を改善するために、いくつかの改良が導入された。1つのこうした改良は、接合障壁ショットキー (JBS) 整流器であり、これは、P / N 接合グリッドを、P + / N 接合グリッドからの拡大空間電荷領域が映像電荷によって引き起こされたショットキー障壁低下の除去をもたらすほど十分に小さいショットキー障壁領域に結合させる。JBS 整流器は、同じチップ面積及び順方向電圧低下について漏れ電流の約 50 % の正味の低下を提供する。これは、50 % 負荷サイクルで作動するダイオードに関するワット損曲線における約 11 ケルビン度の改善と同等である。

20

**【0 0 0 4】**

別のこうした改良はトレンチ・ショットキーであり、これは、順方向電圧低下が 0.7 ボルトを超過し、JBS 整流器が多数キャリアデバイスとして作動することを停止するより高電圧の用途に有用である。例えば、トレンチ MOS 障壁制御ショットキー (T-MBS) 整流器は、250 Vまでの絶縁破壊電圧に対して P - i - N 整流器よりも低い順方向電圧低下を有し、依然として多数キャリアデバイスとして作動する。

30

**【0 0 0 5】**

これらの高電圧の用途に加え、従来型のトレンチ・ショットキーが十分に適切とは言えない低電圧用途に対する需要が増大している。トレンチ・ショットキーは、遮断状態において、内側トレンチが十分に接近して離間され、かつボディ部分の隣接領域が十分に低い濃度にドープされており、それによってボディ部分内に形成された空乏層が、絶縁破壊電圧よりも低い電圧でトレンチ間のボディ部分の中間領域を空乏化させることを必要とする。このようにして、逆方向電圧遮断特性が改善される。残念なことに、それは、トレンチが、チップ上の利用可能な面積の 50 % ほども消費する場合があるので、ショットキー障壁に利用可能な面積の有意な減少もたらす。

40

**【発明の開示】****【発明が解決しようとする課題】****【0 0 0 6】**

米国特許第 6,979,861 号は、MOS パートの垂直構造及び順方向電流フローパターンは、この特許の図 2 に示されている。このデバイスは二端子デバイスであり、すなわち、上部電極は、N+ ソース、ゲート電極、及び P - ボディとの直接接触を提供し、一方で下部電極は、ドレイン電極である。順方向伝導は、正電圧が上部電極に印加された時に得られる。ゲートへの正バイアスは、ゲートの下の P - ボディを順方向電流が流れることを可能にする N - チャンネルに反転する。ゲートへの負バイアスは、N - チャンネルを形成させない。P - ベース / N - ドリフト領域は、逆方向バイアスのピンダイオードになり、逆方向電圧をサポートする。

50

残念なことには、このデバイスは、 $dV/dt$ 性能の低下を招くその寄生N+ / P / N双極構造を欠陥として有する。

**【課題を解決するための手段】**

**【0007】**

本発明は、改良された半導体整流デバイスを提供することによって上述の問題及び限界を克服する。広義に特徴付ければ、デバイスは、第1の導電型のドーパントで過飽和されたシリコンの層と、実質的に過飽和シリコンの層の下方にかつ隣接して位置する第1の導電型のボディ領域と、実質的にボディ領域の下方にかつ隣接して位置する第2の導電型のドリフト領域と、実質的にドリフト領域の下方に位置する第2の導電型の基板とを含む。

**【0008】**

広義に特徴付ければ、上述のデバイスを製造する方法は、第2の導電型の基板上に第2の導電型のドリフト領域を堆積させる段階と、ドリフト領域内に第1の導電型のドーパントを注入して第1の導電型のボディ領域を作成する段階と、高次シリサイド、例えばチタンシリサイドの層をボディ領域上に形成する段階と、注入ドーパントの一部分をシリサイドの層とボディ領域の間のインターフェース領域で濃縮し、第1の導電型のドーパントで過飽和されたシリコンの層を作成する段階とを含む。

**【0009】**

一実施形態では、第1の導電型はPであり、第2の導電型はNである。すなわち、この実施形態では、デバイスは、広義的には、P++層、P-ボディ、N-ドリフト領域、N+基板、アノード、及びカソードを含む。この実施形態では、P-ボディは、実質的に

P++層の下方にかつ隣接して位置し、N-ドリフト領域は、実質的にP-ボディの下方にかつ隣接して位置し、N+基板は、実質的にN-ドリフト領域の下方に位置し、アノードは、実質的にP++層の上方に位置し、カソードは、実質的にN+基板の下方に位置する。

**【0010】**

すなわち、この実施形態では、デバイスを製造する方法は、N+基板上にN-ドリフト領域を堆積させる段階と、N+ドリフト領域内にホウ素を注入してP-ボディ領域を作成する段階と、P-ボディ領域上にチタンシリサイドの層を形成する段階と、注入ホウ素の一部分をチタンシリサイドの層とP-ボディ領域の間のインターフェース領域で濃縮し、過飽和P-ドープシリコンのP++層を作成する段階とを含む。

本発明のこれら及び他の特徴は、[発明を実施するための最良の形態]の節で以下に詳細に説明する。

本発明は、明確にするために寸法通りでなく大幅に強調された添付図面を参照して本明細書に説明する。

**【発明を実施するための最良の形態】**

**【0011】**

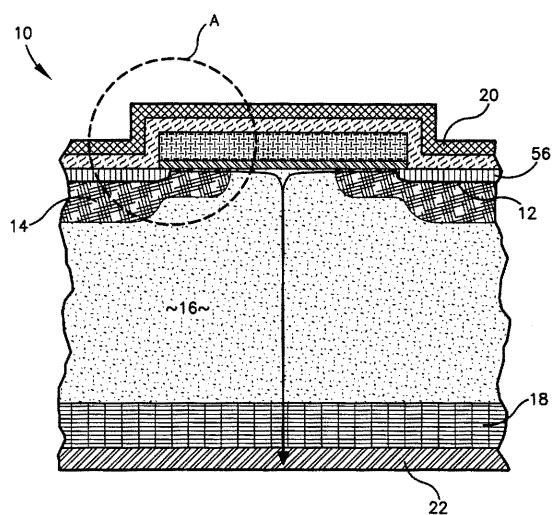

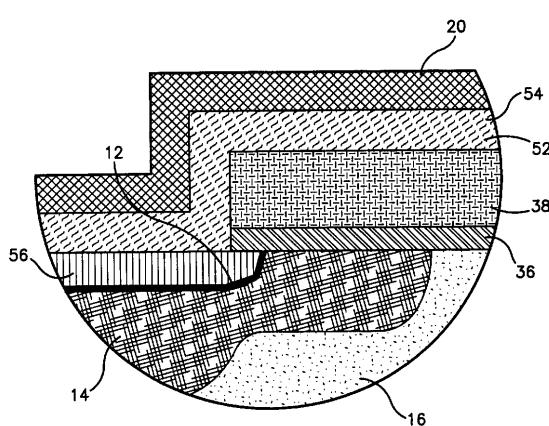

図面を参照して、高効率電力半導体整流デバイス10を本発明の好ましい実施形態を含む様々な実施形態に従って本明細書において説明し、示し、かつその他の方法で開示する。

広義に特徴付ければ、デバイス10は、第1の導電型のドーパントで過飽和されたシリコンの層と、過飽和シリコンの層に実質的に隣接して位置する第1の導電型のボディ領域と、ボディ領域に実質的に隣接して位置する第2の導電型のドリフト領域と、ドリフト領域よりも下方に位置する第2の導電型の基板とを含む。

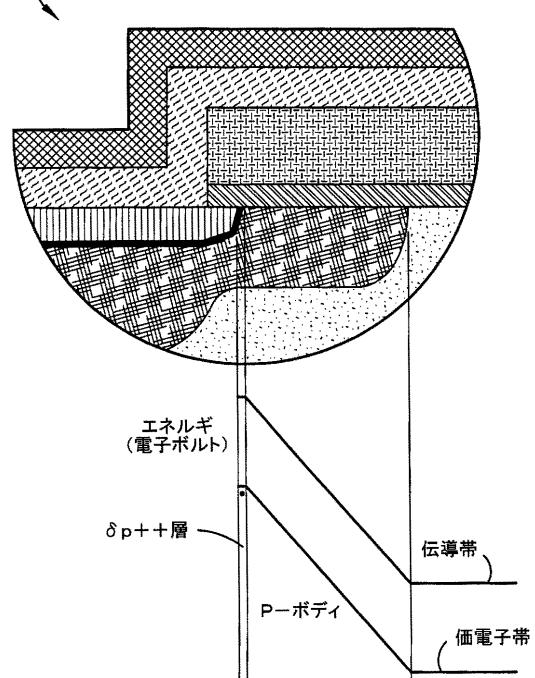

**【0012】**

一実施形態では、第1の導電型はPであり、第2の導電型はNである。すなわち、この実施形態では、広義的には、図1-図4を参照すると、デバイス10は、P++層12、P-ボディ14、N-ドリフト領域16、N+基板18、アノード20、及びカソード22を含む。この実施形態では、P-ボディ16は、P++層12に実質的に隣接して位置し、N-ドリフト領域16は、P-ボディ領域14に実質的に隣接して位置し、N+基板18は、N-ドリフト領域よりも下方に位置し、アノード20は、P++層12よ

10

20

30

40

50

りも上に位置し、カソード 22 は、n+ 基板 18 よりも下方に位置する。本明細書で使用される時の用語「実質的に」は、位置関係用語、例えば、上に、下方に、又は隣接して組み合わせた時に上述の構成要素の相対的位置決めを称し、かつ(A)構成要素の少なくとも大部分が説明された相対位置に適合する複合形状、及び(B)介在構成要素、例えば、領域又は層、特に、製造工程及び/又は構成要素の間の相互作用ために僅かに異なる特性を有する場合があるインターフェース領域のような介在する小さな構成要素の両方を考慮するものである。また、本明細書で使用される時の用語「上に」及び「下方に」は、構成要素のそれぞれの側を称し、すなわち、「上に」は、構成要素の一方の側を称し、「下方に」は、構成要素の反対側を称する。通例、アノード 20 の相対的方向にあるいずれも「上に」あり、一方、カソード 22 の相対的方向にあるいずれも「下方に」ある。しかし、本明細書で使用される時の「上に」及び「下方に」は、主観的に定められており、全体としてデバイス 10 のいかなる特定の向きにも依存しないことに注意されたい。

10

## 【0013】

一実施形態では、P++層 12 は、P-ドープシリコンの過飽和領域であって約数個の原子層の厚みを有し、P-ボディ 14 は、ホウ素注入ポリシリコンであり、N-ドリフト領域 16 は、約 0.4 オーム / センチメートルの抵抗率及び約 3 マイクロメートルの厚みを有し、N+基板 18 は、約  $5 \times 10^{-3}$  オーム / センチメートルに等しいか又はそれ未満の抵抗率を有し、ヒ素又は燐でドープされている。

20

## 【0014】

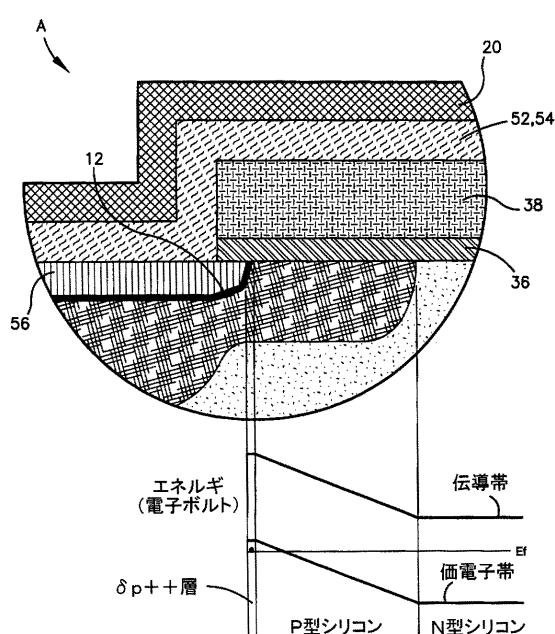

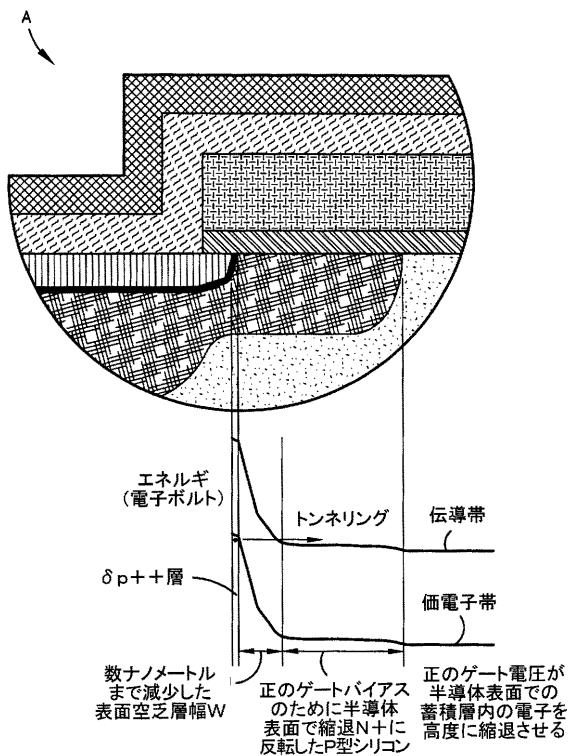

一実施形態では、デバイス 10 は、以下の付加的構成要素を更に含む。すなわち、P++層 12 よりも上にかつ実質的に隣接して位置するチタンシリサイド又は別の高次シリサイドの領域 56 がある。また、N-ドリフト領域 16、P-ボディ 14、P++層 12、及びチタンシリサイドの領域 56 のうちの 1 つ又はそれよりも多くのものよりも上にかつそれと実質的に隣接して位置するゲート誘電体として機能する酸化シリコンの層 36 がある。一実施形態では、ゲート酸化物 36 は、約 85 である。また、酸化シリコンの層 36 の上方にかつ実質的に隣接して位置するポリシリコンの層 38 がある。一実施形態では、ポリシリコン層 38 は、約  $8 \times 10^{-3}$  cm<sup>-2</sup> の線量及び 40 keV のエネルギーでヒ素を注入される。また、ポリシリコンの層 38 の上方にかつ実質的に隣接して位置するチタンの層 52 がある。一実施形態では、チタン 52 は、300 の厚みを有する。また、チタンの層 52 よりも上にかつ実質的に隣接して位置し、かつアノード 20 よりも下方にかつ実質的に隣接して位置する窒化チタンの層 54 がある。一実施形態では、窒化チタン 54 は、500 の厚みを有する。

30

ゲート電圧がなければ、デバイス 10 は、ピンダイオードとしての機能を果たす。正のゲート電圧の印加は、ゲート誘電体の下部の 2 次元電子チャンネルとトンネリング P+/N+ 接合の形成とをもたらす。

40

## 【0015】

P++層 12 への正バイアスの印加は、帯域対帯域トンネリングによる大きい順方向電流フローをもたらす。図 2 は、熱平衡におけるデバイス 10 に関する帯域図を示し、一方で図 3 は、電子電流が 2 次元 MOSFET チャンネルから 3 次元 P++層 12 内に流れるデバイスの半導体表面に関する帯域図を示す。より高い順方向バイアスの印加は、トラップ支援トンネリング電流のために順方向電流を増大させる。

40

逆方向バイアスの印加は、負のゲートバイアスをもたらし、P-ボディ 14 の表面が反転しなくなり、デバイス 10 が P-i-N ダイオードとして機能するようになる。図 4 は、逆方向バイアスダイオードに関するダイオードの半導体表面に対する帯域図を示している。より高い逆方向バイアスは、P-ボディ 14 の表面がより蓄積状態になることをもたらし、次に、そのことが逆方向漏れ電流を低下させる。

## 【0016】

広義に特徴付ければ、デバイス 10 を製造する方法は、第 2 の導電型の基板上に第 2 の導電性のドリフト領域を堆積させる段階と、第 1 の導電型のドーパントをドリフト領域に注入して第 1 の導電型のボディ領域を作成する段階と、高次シリサイド、例えばチタンシ

50

リサイドをボディ領域上に形成する段階と、注入したドーパントの一部分をシリサイドの層とボディ領域の間のインターフェース領域で濃縮し、第1の導電型のドーパントで過飽和されたシリコンの層を作成する段階とを含む。

#### 【0017】

上述のように、一実施形態では、第1の導電型はPであり、第2の導電型はNである。すなわち、この実施形態では、本方法は、N+基板上にN-ドリフト領域を堆積させる段階と、N+ドリフト領域内にホウ素を注入してP-ボディ領域を作成する段階と、チタンシリサイドの層をP-ボディ領域上に形成する段階と、注入ホウ素の一部分をチタンシリサイドの層とP-ボディ領域の間のインターフェース領域で濃縮し、過飽和されたP-ドープシリコンのP++層を作成する段階とを含む。

10

#### 【0018】

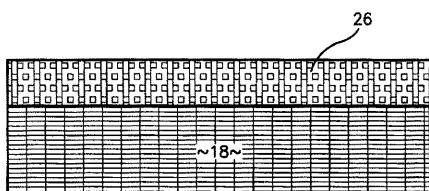

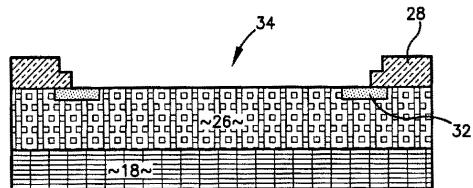

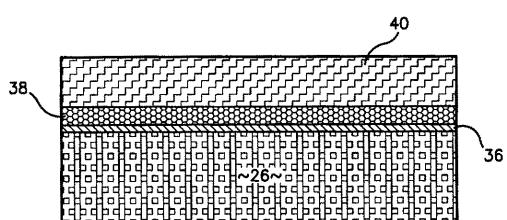

一実施形態では、図5-図20を参照すると、デバイス10は、以下の詳細な段階に従って製造される。

段階1：図5に示すように、N-ドリフト領域16であることになるN-層26が、シリコンN+基板18上にエピタキシャル堆積される。

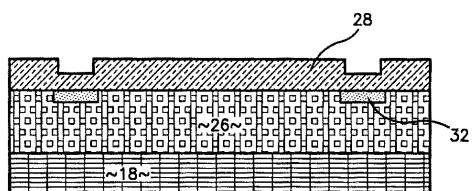

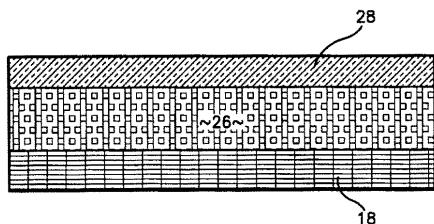

段階2：図6に示すように、初期酸化シリコン層28が、N-層の上に成長する。一実施形態では、酸化シリコン層28は、約0.75マイクロメートルの厚みを有し、別の実施形態では、この厚みは、約0.5マイクロメートルから1.0マイクロメートルである。

20

#### 【0019】

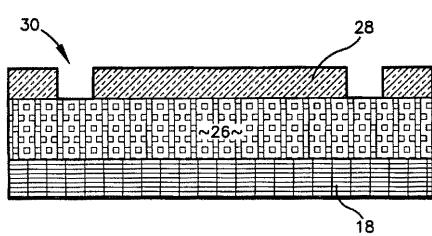

段階3：図7に示すように、保護リング30が、酸化シリコン28のエッチング又は一部の除去によって第1のフォトリソグラフィ段階において形成される。フォトリソグラフィに使用されたフォトレジストが次に剥離される。40V又はそれ未満の比較的低い絶縁破壊電圧を有するダイオードに関しては、この段階及び得られるP+保護リングは省くことができる。更に、深位置ホウ素注入及び浅位置ホウ素注入は、段階6で生成された開放域34に沿った活性区域の周囲で終端するのに十分である。この単純化は、段階6の第2のフォトリソグラフィ段階によって生成された開放域34の周囲を段階11の第3のフォトリソグラフィ段階によって生成された開放域と重複させることによって達成することができる。

30

#### 【0020】

段階4：保護リング30にホウ素が注入されて、ホウ素注入領域32が形成される。ホウ素注入30のための線量及びエネルギーは非常に広範囲とすることができます。一実施形態では、ホウ素注入30の線量は、約3e13cm<sup>-2</sup>であり、エネルギーは、約30keVである。例えば、約40Vに等しいか又はそれ未満である比較的低い絶縁破壊電圧を伴う実施形態では、このホウ素注入並びにそれに関する後段の処置は省くことができる。

#### 【0021】

段階5：図8に示すように、ホウ素注入30が拡散して、薄い酸化シリコン層が、縁部の終端をもたらすようにホウ素注入シリコンの上に再成長する。

40

段階6：図9に示すように、酸化シリコン28が第2のフォトリソグラフィ段階においてチップの中央でエッチングされて、活性区域34が開放される。

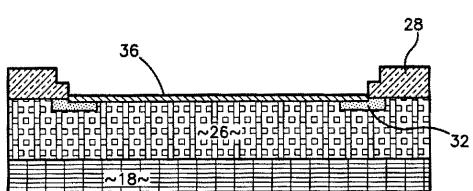

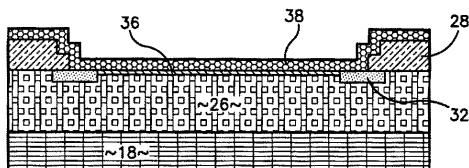

段階7：図10に示すように、ゲート酸化物36が活性区域34内部に成長する。一実施形態では、ゲート酸化物36は、約85の厚みを有する。

段階8：図11に示すように、ポリシリコンが堆積され、ポリシリコン層38が作成される。一実施形態では、ポリシリコン層38は、1500の厚みを有する。

#### 【0022】

段階9：ポリシリコン38にヒ素が注入される。一実施形態では、ヒ素注入のための線量は、約8e15cm<sup>-2</sup>であり、エネルギーは約40keVである。

50

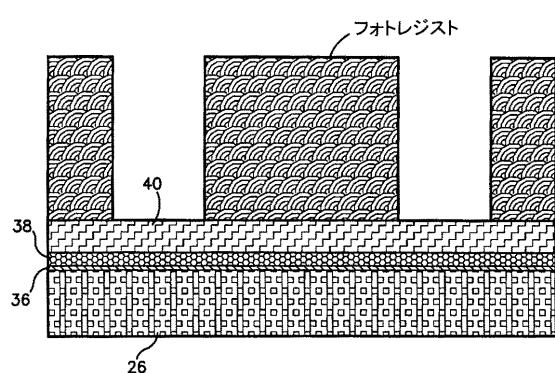

段階10：図12に示すように、ポリシリコン層38が部分的に酸化されて、約800のポリシリコンが酸化されずに残され、高度N-ドープポリシリコンゲート40が作成される。

段階 1 1 : 図 1 3 に示すように、ゲートは、第 3 のリソグラフィ段階においてエッチングされ、すなわち、更に形成される。

#### 【 0 0 2 3 】

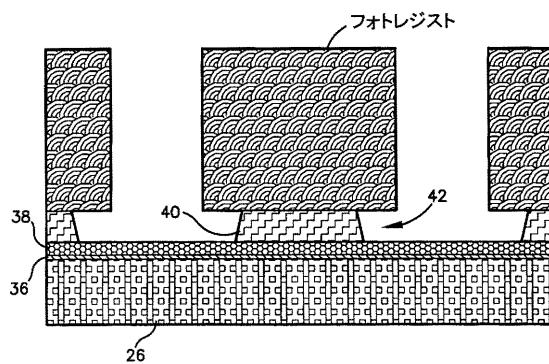

段階 1 2 : 図 1 4 に示すように、酸化シリコン 4 0 がウェットエッチングされ、切り下げ区域 4 2 が作成される。切り下げの量は、このチャンネルの長さを定める。一実施形態では、この段階及び得られる切り下げは省かれる。

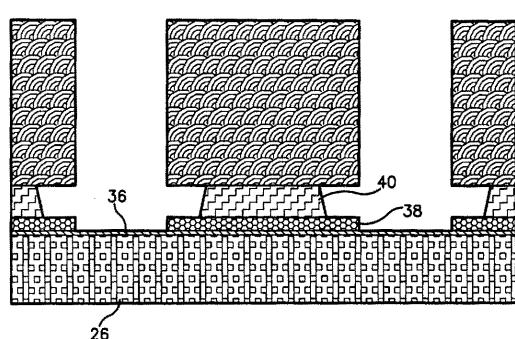

段階 1 3 : 図 1 5 に示すように、ポリシリコン層 3 8 がエッチングされる。一実施形態では、このエッチングは、反応性イオンエッチング法を用いて達成される。

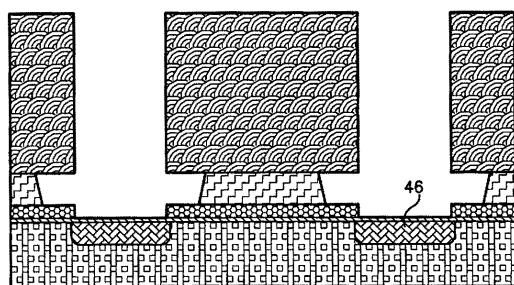

段階 1 4 : 図 1 6 に示すように、ホウ素が N - ドリフト領域に注入され、P - ボディ 1 4 であることになるホウ素注入領域 4 6 が作成される。一実施形態では、ホウ素注入の線量は、約 3 e 1 3 c m - 2 であり、エネルギーは、約 8 0 k e V である。

#### 【 0 0 2 4 】

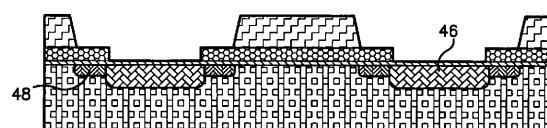

段階 1 5 : 図 1 7 に示すように、段階 1 4 で作成した P - ボディ 1 4 に隣接してチャンネル域 4 8 にホウ素が注入される。一実施形態では、この段階及び得られる付加的ホウ素注入が省かれる。

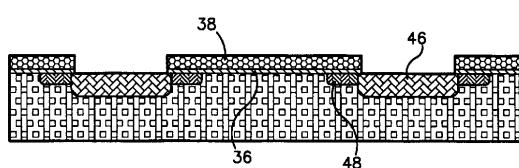

段階 1 6 : 図 1 8 に示すように、上部酸化シリコン 3 8 及びポリシリコン域の外側のゲート酸化物 3 6 が、ゲートポリシリコン、P - ボディ 1 4 、及び段階 1 7 で付加されるチタン / 窒化チタンがスパッタリングされた金属システムの間の良好な接触を保証するためにエッチングされる。

#### 【 0 0 2 5 】

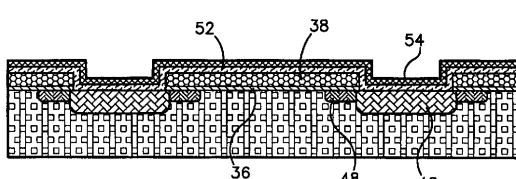

段階 1 7 : 図 1 9 に示すように、チタン 5 2 及び窒化チタン 5 4 が、それぞれスパッタリング及び反応性スパッタリング堆積法を用いて堆積される。一実施形態では、チタン 5 2 は、3 0 0 の厚みを有し、窒化チタン 5 4 は、5 0 0 の厚みを有する。

段階 1 8 : 図 2 0 を参照すると、チタンシリサイドの層 5 6 が形成される。接触域内のある一定の量のシリコンが、6 5 0 又はそれよりも高い温度でチタンシリサイド 5 6 に変換される。接触域内のホウ素は、チタンシリサイドとシリコンの間のインターフェース領域に移動又は「雪かき」され、約数個の原子層の厚みを有する過飽和 P ドープシリコンの P + + 層 1 2 が作成される。

#### 【 0 0 2 6 】

過飽和 P + + 層を作成する他の方法としては、分子ビームエピタキシ ( M B E ) 及び原子層堆積 ( A L D ) が挙げられるが、これらの方法は、高価でありかつ複雑である。本発明の方法は、高次シリサイド、例えばチタンシリサイドの形成を使用する。ホウ素原子は、シリサイド / シリコンインターフェースまで前進するシリサイド相によって押し出されるか又は雪かきされ、シリサイド形成の工程が良好に制御された温度による窒素雰囲気のような非酸化雰囲気内で行われる時、押し出されたホウ素原子は、インターフェース領域内部に残存することになる。この理由は、シリサイドが 1 分間未満に形成され、温度が十分低く、P + + 層が形成されるのを妨げるほど十分に深くホウ素原子がシリコン格子内に浸透することを妨げるからである。

#### 【 0 0 2 7 】

段階 1 9 : アノード 2 0 又は上部金属が、スパッタリング堆積法によるなどで堆積される。金属の種類は、使用される電極接点の種類に依存することになる。ワイヤ結合接点を含む一実施形態では、上部金属は、アルミニウムである。半田付け接点を含む一実施形態では、上部金属は、金又は銀とすることができます。

段階 2 0 : アノードは、第 4 のフォトリソグラフィ段階においてそのパターンを形成するためにエッチングされる。

#### 【 0 0 2 8 】

段階 2 1 : 必要に応じてウェーハは薄くされる。一般的に、カソード又はウェーハの裏面からある一定の量のシリコンが除去され、最終チップの厚みが低減される。

段階 2 2 : カソード 2 2 又は裏面金属が、ウェーハのカソード側に堆積される。使用される金属システムは、例えば、半田又は共晶合金であるカソード接点の種類に依存するこ

とになる。

#### 【0029】

上述の説明から、本発明のデバイスは、順方向電圧低下と逆方向漏れ電流の間の好ましい均衡、迅速なスイッチング機能、及び有利な  $dV/dt$  性能を含む従来技術に勝る有意な利点を提供することが認められるであろう。この改善は、従来技術のデバイスに存在する寄生 N+ / P / N ランジスタの解消によって少なくともある程度達成される。更に、デバイスを製造するのに 4 つのフォト段階を要するのみであり、これは、一部の従来技術のデバイスに必要とされる 5 段階よりも少ない。4 段階から 3 段階への更なる低減は、40V 又はそれ未満の低絶縁破壊電圧の場合に P+ 保護リングを省くことによって可能である。更に、デバイスを生成する工程は、N+ ソース及び重い P- ボディのいずれも注入されなくてもよいという点で有意に単純化される。これは、セルのチャンネル密度及び他の幾何学的形状の縮小を可能にし、チップ寸法の削減をもたらす。チップ寸法の削減は、最新電力整流器デバイスの専有面積を低減し、コストも低下させる。

本発明を様々な特定的な実施形態に関連して開示したが、特許請求の範囲に説明した本発明の範囲を逸脱することなく、本明細書に均等物を用い、かつ置換を行うことができることは理解される。

本発明の好ましい実施形態をこのように説明したが、新規であると主張し、かつ特許証による保護が望ましい事項は、特許請求の範囲に含まれている。

#### 【図面の簡単な説明】

#### 【0030】

【図 1】本発明のデバイスの実施形態の部分断面立面図である。

【図 2】デバイスが熱平衡にある時の図 1 のデバイスの区域 A の部分断面立面図である。

【図 3】デバイスが順方向バイアスをかけられた時の図 1 のダイオードの区域 A の部分断面立面図である。

【図 4】デバイスが逆方向バイアスをかけられた時の図 1 のダイオードの区域 A の部分断面立面図である。

【図 5】デバイス製造法の実施形態の第 1 段階の後でのデバイスの部分断面立面図である。

【図 6】第 2 段階の後でのデバイスの部分断面立面図である。

【図 7】第 3 段階の後でのデバイスの部分断面立面図である。

【図 8】第 5 段階の後でのデバイスの部分断面立面図である。

【図 9】第 6 段階の後でのデバイスの部分断面立面図である。

【図 10】第 7 段階の後でのデバイスの部分断面立面図である。

【図 11】第 8 段階の後でのデバイスの部分断面立面図である。

【図 12】第 10 段階の後でのデバイスの部分断面立面図である。

【図 13】第 11 段階の後でのデバイスの部分断面立面図である。

【図 14】第 12 段階の後でのデバイスの部分断面立面図である。

【図 15】第 13 段階の後でのデバイスの部分断面立面図である。

【図 16】第 14 段階の後でのデバイスの部分断面立面図である。

【図 17】第 15 段階の後でのデバイスの部分断面立面図である。

【図 18】第 16 段階の後でのデバイスの部分断面立面図である。

【図 19】第 17 段階の後でのデバイスの部分断面立面図である。

【図 20】第 18 段階の後でのデバイスの部分断面立面図である。

#### 【符号の説明】

#### 【0031】

10 高効率電力半導体整流デバイス

12 P++層

14 P-ボディ

16 N-ドリフト領域

18 N+基板

10

20

30

40

50

- 2 0 アノード

2 2 カソード

5 6 チタンシリサイドの層

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 8】

【図 6】

【図 9】

【図 7】

【図 10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図 1 7】

【図 1 8】

【図 1 9】

【図 2 0】

---

フロントページの続き

- (72)発明者 ローマン ジェイ ハマースキー

アメリカ合衆国 カンザス州 66085 オーヴァーランド パーク ローズウッド ストリー

ト 16104

- (72)発明者 ゼルイ チエン

カナダ ヴィー3エヌ 5イー3 ブリティッシュ コロンビア バーナビー サウスポイント

ドライヴ 6888 #207

- (72)発明者 ジェイムズ マン ファイ ホン

アメリカ合衆国 カリフォルニア州 94577 サン リアンドロ ベネディクト ドライヴ

2520

- (72)発明者 ジョニー デューク ヴァン キーム

アメリカ合衆国 カリフォルニア州 93012 カマリロ フリン ロード 1561 #43

12

- (72)発明者 クリストファー ディー フルスカ

アメリカ合衆国 ミズーリ州 64015 ブルー スプリングス スティル メドーズ レーン

2509

- (72)発明者 ティモシー イーストマン

アメリカ合衆国 ミズーリ州 64063 リーズ サミット サウスイースト フィフス テラ

ス 1108