(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6439552号

(P6439552)

(45) 発行日 平成30年12月19日(2018.12.19)

(24) 登録日 平成30年11月30日(2018.11.30)

(51) Int.Cl.

F 1

H01L 25/07 (2006.01)

H01L 25/18 (2006.01)

H01L 23/02 (2006.01)H01L 25/04

H01L 23/02C

J

請求項の数 14 (全 23 頁)

(21) 出願番号 特願2015-75251 (P2015-75251)

(22) 出願日 平成27年4月1日 (2015.4.1)

(65) 公開番号 特開2016-195216 (P2016-195216A)

(43) 公開日 平成28年11月17日 (2016.11.17)

審査請求日 平成30年2月14日 (2018.2.14)

(73) 特許権者 000005234

富士電機株式会社

神奈川県川崎市川崎区田辺新田1番1号

(74) 代理人 100092152

弁理士 服部 毅麿

(72) 発明者 稲葉 哲也

神奈川県川崎市川崎区田辺新田1番1号

富士電機株式会社内

(72) 発明者 池田 良成

神奈川県川崎市川崎区田辺新田1番1号

富士電機株式会社内

(72) 発明者 堀 元人

神奈川県川崎市川崎区田辺新田1番1号

富士電機株式会社内

最終頁に続く

(54) 【発明の名称】半導体モジュール及び半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ドレイン板と、

おもて面にゲート電極とソース電極とを備え、裏面にドレイン電極を備え、前記ドレイン板のおもて面に配置され、前記ドレイン電極と前記ドレイン板とが電気的に接続される、半導体素子と、

絶縁板と、前記絶縁板のおもて面に設けられた第1回路板及び第2回路板とを備え、前記ドレイン板のおもて面に配置され、前記第1回路板は前記ゲート電極と電気的に接続され、前記第2回路板は前記ソース電極と電気的に接続された、積層基板と、

前記第1回路板上に配置されたゲート端子と、

前記第2回路板上に配置されたソース端子と、

開口及びガイド溝を備え、前記ドレイン板のおもて面と対向して配置され、前記ゲート端子及び前記ソース端子が前記開口に位置し、前記ガイド溝は前記開口に接して外周部まで延伸されている、蓋と、

を備える半導体モジュール。

## 【請求項 2】

前記ゲート端子と電気的に接続され、前記ガイド溝に沿って外周部に延伸されたゲート板、

をさらに有する請求項1記載の半導体モジュール。

## 【請求項 3】

10

20

前記第2回路板上に配置され、前記開口に位置する補助ソース端子と、

前記補助ソース端子と電気的に接続され、前記ガイド溝に沿って前記ゲート板とは電気的に絶縁されて外周部に延伸された補助ソース板と、

をさらに有する請求項2記載の半導体モジュール。

【請求項4】

前記蓋に設けられた補助ガイド溝と、

前記補助ガイド溝に沿って外周部に延伸された補助ソース板と、

をさらに有し、

前記ガイド溝は前記開口の一方に接して形成され、

前記補助ガイド溝は前記開口の他方に接して形成され、

前記第2回路板と前記補助ソース板との間が、前記ソース端子及び前記蓋を経由して電気的に接続されている、

請求項2記載の半導体モジュール。

10

【請求項5】

前記第2回路板は、前記第1回路板を取り囲んで前記絶縁板のおもて面に配置されている請求項1乃至4のいずれかに記載の半導体モジュール。

【請求項6】

前記ゲート端子は、前記ガイド溝の中間点を直交する線上に位置するように前記第1回路板上に設けられている請求項5記載の半導体モジュール。

【請求項7】

前記ソース端子は、前記第2回路板上に一対設けられ、

前記ゲート端子と、一対の前記ソース端子とは前記ガイド溝と平行に直線状に配置されている請求項6記載の半導体モジュール。

20

【請求項8】

前記ガイド溝の底部が、前記ゲート端子の上端部より上方に位置している、

請求項1から4のいずれか1項に記載の半導体モジュール。

【請求項9】

請求項2記載の前記半導体モジュールを複数備え、

複数の前記半導体モジュールは、前記ガイド溝同士が連結されるように配置され、

当該連結された前記ガイド溝に沿って、一体化された前記ゲート板が配置されている、

半導体装置。

30

【請求項10】

請求項3記載の前記半導体モジュールを複数備え、

複数の前記半導体モジュールは、前記ガイド溝同士が連結されるように配置され、

当該連結された前記ガイド溝に沿って、一体化された前記ゲート板及び一体化された前記補助ソース板が配置されている、

半導体装置。

【請求項11】

請求項4記載の前記半導体モジュールを複数備え、

複数の前記半導体モジュールは、前記ガイド溝同士が連結されるように配置され、前記補助ガイド溝同士が連結されるように配置され、

当該連結された前記ガイド溝に沿って一体化された前記ゲート板が配置され、

当該連結された前記補助ガイド溝に沿って一体化された前記補助ソース板が配置されている、

半導体装置。

40

【請求項12】

請求項1記載の前記半導体モジュールを複数備え、

複数の前記半導体モジュールは、前記半導体モジュールの前記ソース端子と、別の前記半導体モジュールの前記ドレイン板とが電気的に接続されている、

半導体装置。

50

### 【請求項 1 3】

複数の前記半導体モジュールが積層して配置され、

前記半導体モジュールの前記ソース端子と、隣接する前記半導体モジュールの前記ドレン

イン板が電気的に接続されている、

請求項 1 2 記載の半導体装置。

### 【請求項 1 4】

複数の前記半導体モジュールが並んで配置され、

前記半導体モジュールの前記ソース端子と、隣接する前記半導体モジュールの前記ドレン

イン板が導電部材を経由して電気的に接続されている、

請求項1-2記載の半導体装置。

## 【発明の詳細な説明】

## 【技術分野】

[ 0 0 0 1 ]

## 本発明は

背景技术】

【背景技术】

[ 6 6 6 2 ]

半導体装置の一つとして、IGBT (Insulated Gate Bipolar Transistor)、FWD (Free Wheeling Diode) 等の複数の半導体素子を含む半導体モジュールが広く用いられている。例えば、この半導体モジュールを並列接続することで、スイッチング、コンバータ等としての機能が実現される。このような半導体モジュールの内、モジュール内部に絶縁機能を有さない非絶縁型の半導体モジュールは、絶縁型の半導体モジュールに比べ、内部配線のインダクタンスを低減することができる。

【 0 0 0 3 】

### 非絶縁型の

ン端子を備えている。そして、上面からゲート導体とソース導体が一体になったものを配置し、下面にドレイン導体を配置し、それらを上下から圧接することにより、外部と電気的に接続されている（例えば、特許文献 1 参照）。

【先行技術文献】

## 【先行技术文献】

【特許文献】

[ 0 0 0 4 ]

【特許文献1】特開平7-312410号公報

30

## 【発明の概要】

## 【発明が解決しようとする課題】

【 0 0 0 5 】

しかし、特許文献1の半導体モジュールでは、ゲート導体に圧接されたばね板形状のゲート端子は、半導体モジュールの動作中にゲート導体が摺動して、ゲート導体との接触面の電気抵抗が増加する。このため、半導体モジュールに動作不良が生じてしまうおそれがある。

【 0 0 0 6 】

本発明は、このような点を鑑みてなされたものであり、動作不良の発生が抑制された半 40

導体を提供することを目的とす

## 【課題を解決】

50

もて面と対向して配置され、前記ゲート端子及び前記ソース端子が前記開口に位置し、前記ガイド溝は前記開口に接して外周部に延伸されている、蓋と、を備える半導体モジュールが提供される。

【発明の効果】

【0008】

開示の技術によれば、半導体装置の動作不良の発生を防止して、半導体装置の特性の低下を抑制することができるようになる。

【図面の簡単な説明】

【0009】

【図1】第1の実施の形態の半導体モジュールを示す図である。

10

【図2】第1の実施の形態の半導体モジュールの構成を示す図である。

【図3】第1の実施の形態の半導体モジュールの構成を示す図である。

【図4】第1の実施の形態の半導体モジュールの構成を示す図である。

【図5】第1の実施の形態の半導体モジュールの構成を示す図である。

【図6】第1の実施の形態の半導体モジュールの構成を示す図である。

【図7】第1の実施の形態の半導体モジュールの構成を示す図である。

【図8】第1の実施の形態の半導体モジュールの構成を示す図である。

【図9】第1の実施の形態の半導体モジュールの構成を示す図である。

【図10】第1の実施の形態の半導体モジュールの構成を示す図である。

【図11】第2の実施の形態の半導体装置を示す図である。

20

【図12】第2の実施の形態の半導体装置の配線板を示す図である。

【図13】第3の実施の形態の半導体モジュールを示す図である。

【図14】第4の実施の形態の半導体モジュールを示す図である。

【図15】第5の実施の形態の半導体モジュールに用いられるゲート板と補助ソース板とを含むプリント基板を示す図である。

【図16】第6の実施の形態の半導体装置を示す図である。

【図17】第7の実施の形態の半導体モジュールを示す図である。

【図18】第7の実施の形態の半導体モジュールを複数組み合わせた半導体装置を示す図である。

【図19】第8の実施の形態の半導体モジュールを示す図である。

30

【図20】第8の実施の形態の半導体モジュールを複数組み合わせた半導体装置を示す図である。

【図21】第9の実施の形態の半導体装置を示す側面図である。

【図22】第9の実施の形態の半導体装置を示す側面図である。

【発明を実施するための形態】

【0010】

以下、図面を参照して実施の形態について説明する。

[第1の実施の形態]

第1の実施の形態の半導体モジュールについて、図1～図10を用いて説明する。

【0011】

40

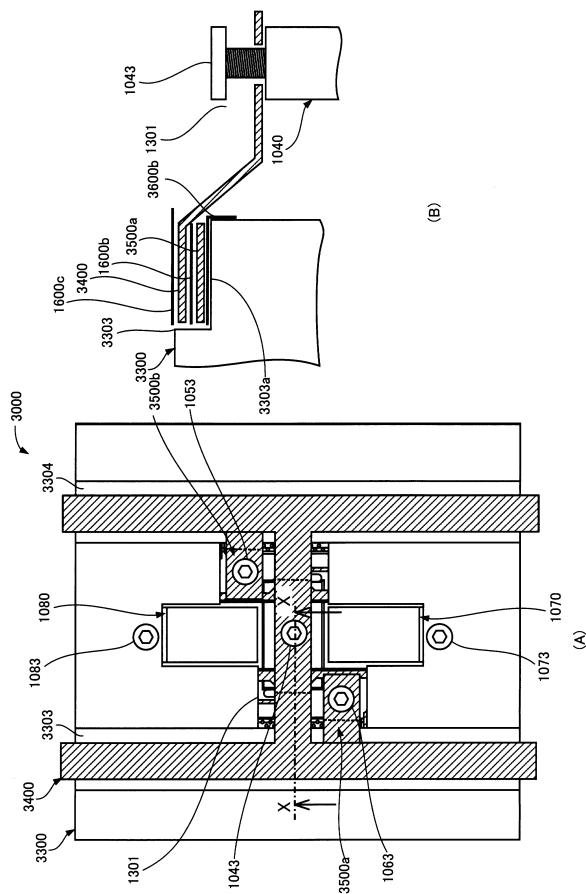

図1は、第1の実施の形態の半導体モジュールを示す図である。

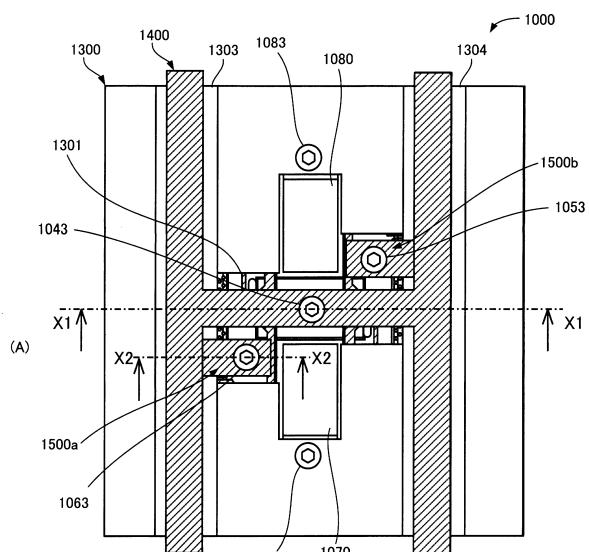

なお、図1(A)は、半導体モジュールの平面図を、図1(B)は、図1(A)の一点鎖線X1-X1の断面図をそれぞれ示している。

【0012】

また、図2～図10は、第1の実施の形態の半導体モジュールの構成を示す図である。

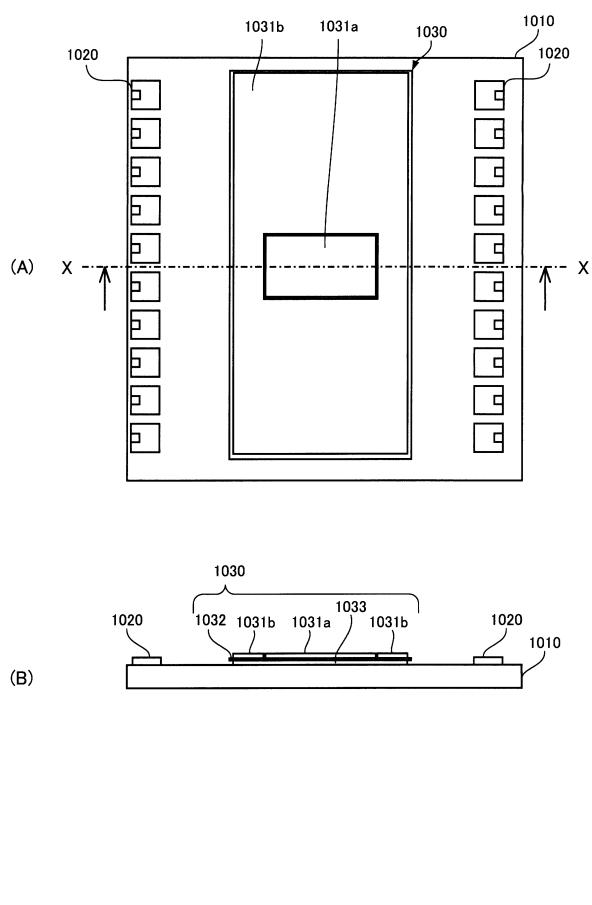

図2(A)は、ドレイン板1010の平面図を、図2(B)は、図2(A)の一点鎖線X-Xにおける断面図をそれぞれ示している。

【0013】

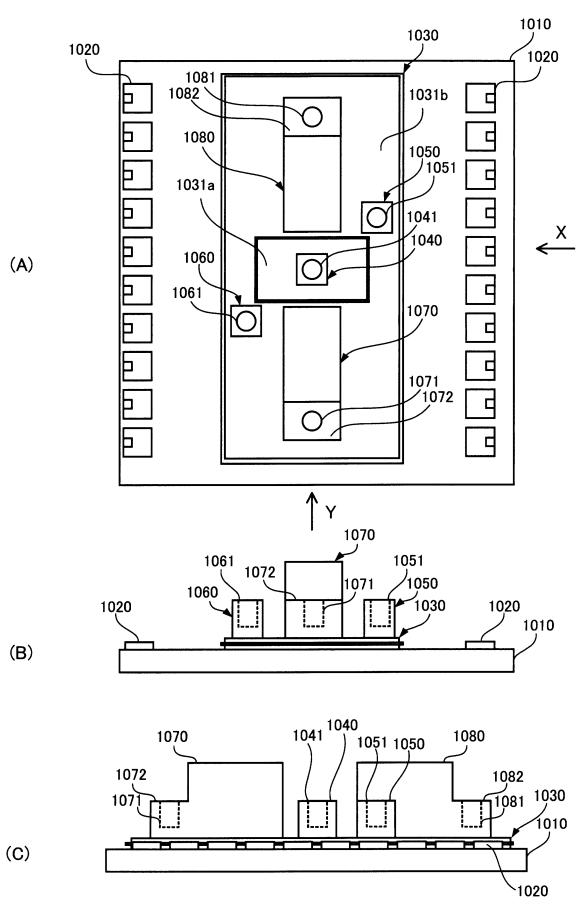

図3(A)は、ドレイン板1010の平面図を、図3(B)は、図3(A)の矢視Yから見た側面図を、図3(C)は、図3(A)の矢視Xから見た側面図をそれぞれ示してい

50

る。

【0014】

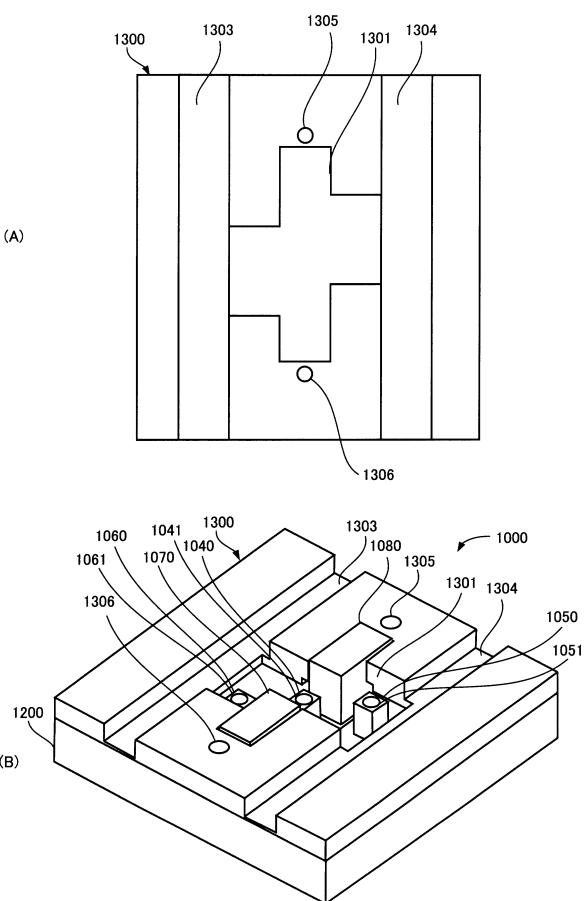

図8(A)は、蓋1300の平面図を、図8(B)は、(ゲート板1400及び補助ソース板1500a, 1500bを配置していない)半導体モジュールの斜視図をそれぞれ示している。

【0015】

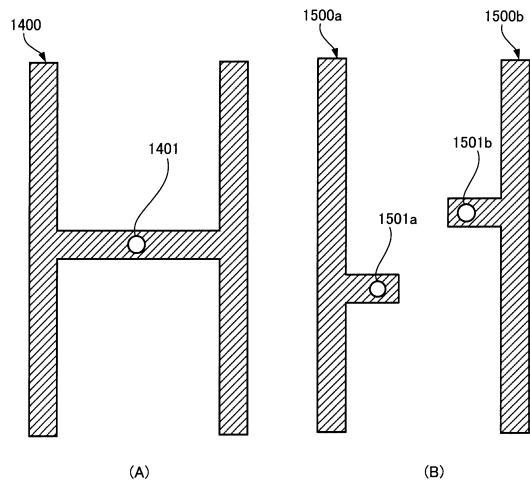

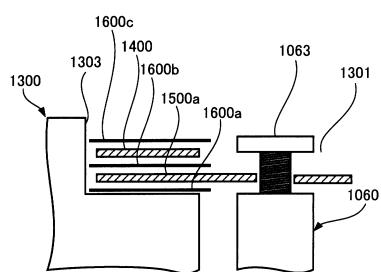

図9(A)は、ゲート板1400の平面図を、図9(B)は、補助ソース板1500a, 1500bの平面図をそれぞれ示している。なお、図10は、図1の一点鎖線X2-X2の断面拡大図を示している。

【0016】

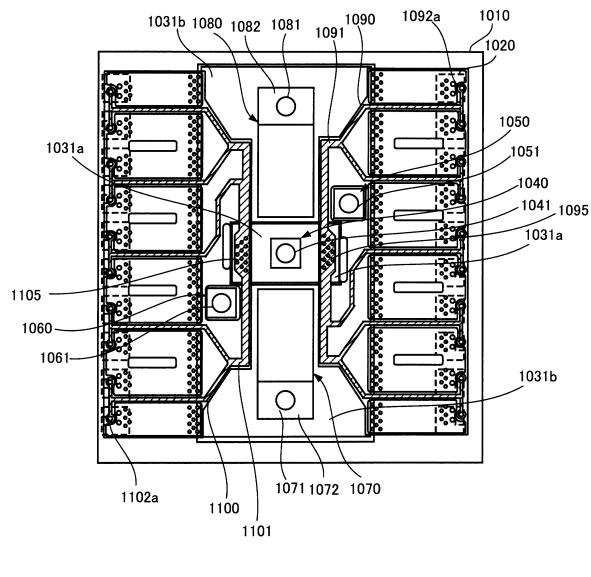

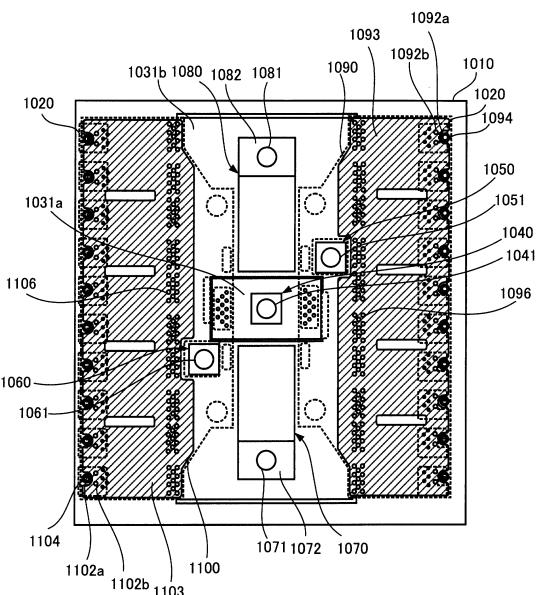

非絶縁型の半導体モジュール1000は、図1に示されるように、ドレイン板1010と、半導体素子1020と、積層基板1030と、ゲート端子1040と、補助ソース端子1050と、蓋1300とを備える。また、半導体モジュール1000は、ゲート板1400と、補助ソース端子1060と、補助ソース板1500a, 1500bと、絶縁性の枠1200をさらに備えている。

【0017】

ドレイン板1010は、銅やアルミ等の導電性材料で構成される。ドレイン板1010のおもて面には半導体モジュール1000の各構成部材が搭載され、裏面に外部電源からの電力が入力される。すなわち、ドレイン板1010は、非絶縁型の半導体モジュール1000のドレイン端子としての機能を有する。

【0018】

半導体素子1020は、パワーMOSFET (Metal Oxide Semiconductor Field Effect Transistor) やIGBT等の縦型のパワー半導体素子である。第1の実施の形態においては、半導体素子1020がパワーMOSFETの場合について説明する。半導体素子1020は、おもて面にゲート電極とソース電極とを備え、裏面にドレイン電極を備える。半導体素子1020は、ドレイン板1010のおもて面に配置される。そして、半導体素子1020の裏面のドレイン電極と、ドレイン板1010が、はんだ等の導電性の接合材により接合され、電気的に接続されている。

【0019】

積層基板1030は、図2に示されるように、絶縁板1032と、第1回路板1031aと、第2回路板1031bとを備える。積層基板1030は、ドレイン板1010のおもて面のうち、半導体素子1020が配置されている箇所とは異なる箇所に配置されている。また、第1回路板1031aと半導体素子1020のゲート電極が電気的に接続され、第2回路板1031bと半導体素子1020のソース電極が電気的に接続されている。これらの接続構成の詳細については後述する。

【0020】

ゲート端子1040は、第1回路板1031a上に配置されている。一対のソース端子1070, 1080は、第2回路板1031b上に配置されている。一対の補助ソース端子1050, 1060は、第2回路板1031b上に配置されている。いずれの端子も銅やアルミなどの導電性材料で構成される。また、いずれの端子も第1回路板1031aもしくは第2回路板1031bと、はんだなどの導電性の接合材により接合され、電気的に接続されている。

【0021】

図8に示すように、蓋1300は、矩形状をなし、ガイド溝1303, 1304を備える。蓋1300は、ドレイン板1010のおもて面に対向して配置されている。そして、開口1301に、ゲート端子1040、ソース端子1070, 1080、及び補助ソース端子1050, 1060が位置している。ガイド溝1303, 1304は開口1301に接し、開口1301に接する箇所から外周部まで延伸されている。蓋1300は、銅やアルミ等の導電性材料で構成されることが好ましい。

【0022】

10

20

30

40

50

なお、蓋 1300 は、ボルト孔 1305, 1306 を用いて、ボルト 1073, 1083 でソース端子 1070, 1080 にねじ止めされ、固定されている。

ゲート板 1400 は、ガイド溝 1303, 1304 に配置され、ゲート端子 1040 と電気的に接続され、ガイド溝 1303, 1304 に沿って外周部に延伸されている。なお、ゲート端子 1040 は、ガイド溝 1303, 1304 の中間点を直交する線上に位置している。

#### 【0023】

補助ソース板 1500a, 1500b は、ガイド溝 1303, 1304 に配置されて、補助ソース端子 1050, 1060 にそれぞれ電気的に接続されている。また、補助ソース板 1500a, 1500b は、ゲート板 1400 とは絶縁層 1600b により絶縁されながら、ガイド溝 1303, 1304 に沿って外周部に延伸されている。 10

#### 【0024】

ゲート板 1400 は、第 1 の実施の形態では、H 字型の形状をなしており、中心部でゲート端子 1040 のボルト孔 1041 にボルト 1043 で固定されている。補助ソース板 1500a, 1500b も、補助ソース端子 1050 及び補助ソース端子 1060 のボルト孔 1051, 1061 にボルト 1053, 1063 で固定されている。

#### 【0025】

このような半導体モジュール 1000において、ドレイン板 1010 にドレイン導体 1800 を押圧し、ソース端子 1070, 1080 にソース導体 1700 を押圧して、上下から圧接する。これにより、外部電源と半導体モジュール 1000 を電気的に接続することができる。また、外周部に延伸され、半導体モジュール 1000 の側部に取り出されたゲート板 1400 に、ゲートドライバユニット(不図示)からゲート電圧を印加する。これにより、半導体素子 1020 のスイッチング動作を制御することができる。 20

#### 【0026】

このような構成を有する半導体モジュールの構成、組み立てについて、以下で説明する。

まず、図 2 に示されるように、ドレイン板 1010 の中央部に積層基板 1030 と、積層基板 1030 の両側に複数の半導体素子 1020 とがそれぞれ配置されている。

#### 【0027】

絶縁板 1032 のおもて面に、第 1 回路板 1031a と第 2 回路板 1031b とが配置されている。第 1 回路板 1031a 及び第 2 回路板 1031b は、銅やアルミ等の導電性材料により構成されている。第 1 回路板 1031a と第 2 回路板 1031b とは、電気的に絶縁されており、第 2 回路板 1031b が第 1 回路板 1031a を取り囲んで配置されている。また、絶縁板 1032 の裏面に、例えば、銅で構成された金属板 1033 を備える。金属板 1033 を配置することにより、ドレイン板 1010 と積層基板 1030 との間を、はんだ付けによる接合が可能となる。なお、ドレイン板 1010 と積層基板 1030 との間を接着剤で接合する場合は、金属板 1033 は無くても良い。 30

#### 【0028】

次いで、図 3 に示されるように、積層基板 1030 の第 1 回路板 1031a の中心部に、柱状であって、上面にボルト孔 1041 が設けられたゲート端子 1040 が設置される。

#### 【0029】

また、第 2 回路板 1031b には、一対のソース端子 1070, 1080 が、第 1 回路板 1031a を挟んで設置される。ソース端子 1070, 1080 には、それぞれ、段差面 1072, 1082 が形成されており、段差面 1072, 1082 には、ボルト孔 1071, 1081 がそれぞれ形成されている。

#### 【0030】

さらに、第 2 回路板 1031b には、補助ソース端子 1050, 1060 が設置される。補助ソース端子 1050, 1060 は、例えば、第 1 回路板 1031a を挟んで、ソース端子 1070, 1080 と並んで設置される。補助ソース端子 1050, 1060 には

10

20

30

40

50

、ボルト孔 1051, 1061 がそれぞれ形成されている。なお、図 3 (A) に示す補助ソース端子 1050, 1060 の設置箇所は、一例であって、第 2 回路板 1031b 上であればどこでも構わない。

#### 【0031】

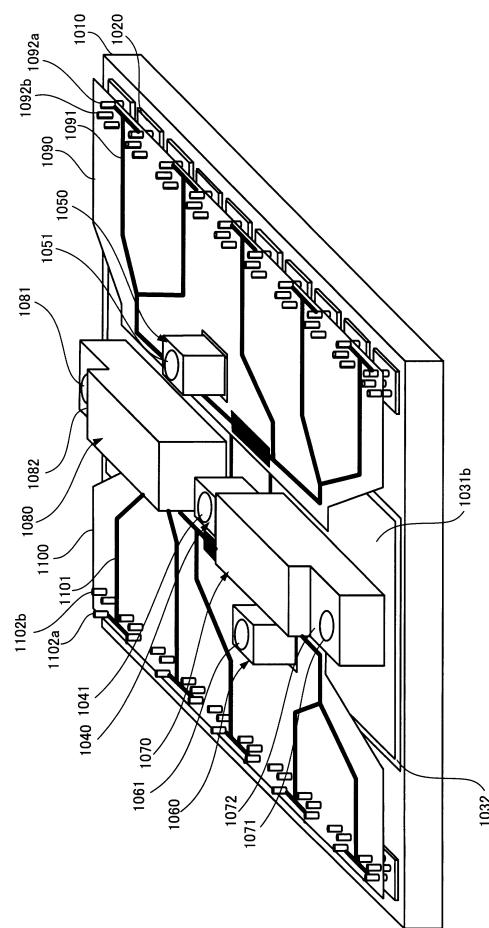

次いで、図 4 ~ 図 6 に示されるように、複数の半導体素子 1020 と、第 1 回路板 1031a 及び第 2 回路板 1031bとの間に、プリント基板 1090, 1100 が設置される。設置の際、プリント基板 1090, 1100 と、補助ソース端子 1050, 1060 が干渉しないように、プリント基板 1090, 1100 のおもて面に配置されたゲート配線層 1091, 1101 と、複数の半導体素子 1020 の各ゲート電極とは、導電ポスト 1092a, 1102a を経由してそれぞれ電気的に接続されている。また、ゲート配線層 1091, 1101 と、積層基板 1030 の第 1 回路板 1031a とは、ゲート接続部 1095, 1105 を経由して電気的に接続されている。

#### 【0032】

また、プリント基板 1090, 1100 の裏面に配置されたソース配線層 1093, 1103 と、複数の半導体素子 1020 の各ソース電極とは、導電ポスト 1092b, 1102b を経由してそれぞれ電気的に接続されている。また、ソース配線層 1093, 1103 と、積層基板 1030 の第 2 回路板 1031b とは、ソース接続部 1096, 1106 を経由して電気的に接続されている。

#### 【0033】

このように、プリント基板 1090, 1100 及び導電ポスト 1092a, 1092b, 1102a, 1102b を用いて、半導体素子 1020 と積層基板 1030 とが電気的に接続される。

#### 【0034】

なお、ソース配線層 1093, 1103 には貫通孔 1094, 1104 が形成されている。プリント基板 1090, 1100 のゲート配線層 1091, 1101 に接続されている導電ポスト 1092a, 1102a は、貫通孔 1094, 1104 に挿通されている。このため、導電ポスト 1092a, 1102a とソース配線層 1093, 1103 とは電気的絶縁性が保たれている。

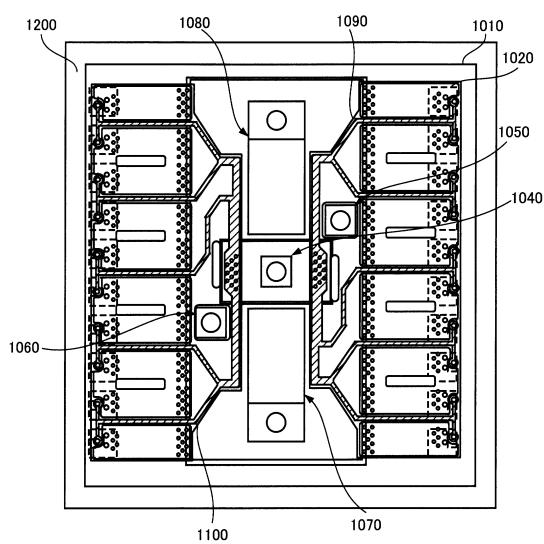

#### 【0035】

このようにして各構成が設置されたドレイン板 1010 を、図 7 に示されるように、四方が覆われた枠 1200 内に設ける。

次いで、枠 1200 に被せる蓋 1300 は、図 8 (A) に示されるように、開口 1301 と、ボルト孔 1305, 1306 とがそれぞれ形成されている。さらに、蓋 1300 は、図中上下方向に直線状のガイド溝 1303, 1304 が開口 1301 に接して、外周部まで延伸されて形成されている。

#### 【0036】

このような蓋 1300 を枠 1200 に被せると、図 8 (B) に示される半導体モジュール 1000 となる。半導体モジュール 1000 では、ゲート端子 1040 と、ソース端子 1070, 1080 と、補助ソース端子 1050, 1060 とが、開口 1301 に位置し、開口 1301 から少なくとも一部が露出するように配置されている。また、ボルト孔 1305, 1306 が、ソース端子 1070, 1080 のボルト孔 1071, 1081 に位置合わせされ、蓋 1300 がボルト 1073, 1083 で固定されている。

#### 【0037】

なお、蓋 1300 に形成されたガイド溝 1303, 1304 の溝の深さは、例えば、ゲート端子 1040 と、補助ソース端子 1050, 1060 との高さと一致するようにしている。

#### 【0038】

次いで、図 9 及び図 10 に示されるように、蓋 1300 のガイド溝 1303 に、絶縁層 1600a を配置して、補助ソース板 1500a を配置する。配置の際には、補助ソース

10

20

30

40

50

板 1500a のボルト孔 1501a が、補助ソース端子 1060 のボルト孔 1061 に位置合わせされ、ボルト 1063 で固定される。補助ソース板 1500b も同様にしてガイド溝 1304 に絶縁層 1600a を介して配置される。この際、補助ソース板 1500b のボルト孔 1501a が、補助ソース端子 1050 のボルト孔 1051 に位置合わせされ、ボルト 1053 で固定される。

#### 【0039】

また、ガイド溝 1303, 1304 に配置された補助ソース板 1500a, 1500b に、絶縁層 1600b を配置し、図 9 (A) に示されるゲート板 1400 を配置する。配置の際には、ゲート板 1400 のボルト孔 1401 が、ゲート端子 1040 のボルト孔 1041 に位置合わせされ、ボルト 1043 で固定される。ゲート板 1400 上にはさらに絶縁層 1600c を配置する。

10

#### 【0040】

すなわち、ガイド溝 1303 において、図 10 に示されるように、絶縁層 1600a、補助ソース板 1500a、絶縁層 1600b、ゲート板 1400、絶縁層 1600c の順で積層される。また、ガイド溝 1304 において、絶縁層 1600a、補助ソース板 1500b、絶縁層 1600b、ゲート板 1400、絶縁層 1600c の順で積層される。

#### 【0041】

このようにして設置された補助ソース板 1500a, 1500b にゲートドライバユニットを接続すると、ゲートドライバユニットは、ゲート電圧に応じたソース電流を計測することができる。

20

#### 【0042】

第 1 の実施の形態の半導体モジュール 1000 では、蓋 1300 にガイド溝 1303, 1304 が設けられることにより、ソース端子 1070, 1080 の上面よりも低い位置にゲート板 1400 を配置することができる。これにより、ゲート板 1400 とゲート端子 1040 を接合する、ボルト 1043 を配置するのに必要なスペースを確保することができる。そして、ボルト 1043 で強固に接合することにより、動作時におけるゲート端子 1040 の摩耗の発生が抑制される。このため、ゲート端子 1040 の電気抵抗の増加、並びに、発熱の発生が抑制されて、半導体モジュール 1000 の動作不良の発生が防止される。

#### 【0043】

30

また、半導体モジュール 1000 では、補助ソース端子 1050, 1060 を設置して、補助ソース端子 1050, 1060 に接合した補助ソース板 1500a, 1500b をガイド溝 1303, 1304 から延伸させるようにした。このため、ゲート電圧に対するソース電流を計測することができ、所望のソース電流が outputされるように印加するゲート電圧を正確に制御することができる。

#### 【0044】

また、ガイド溝 1303, 1304 にゲート板 1400 及び補助ソース板 1500a, 1500b を積層配置している。このため、ゲート配線の配線インダクタンスを低減させることができ、半導体モジュールの高速動作が可能となる。

#### 【0045】

40

また、半導体モジュール 1000 では、半導体素子 1020、積層基板 1030 等が導電性の蓋 1300 により覆われているために、半導体モジュール内部で発生するノイズを遮断することができる。

#### 【0046】

また、半導体モジュール 1000 は、ゲート板 1400 と補助ソース板 1500a, 1500b とがガイド溝 1303, 1304 に収納されるために、コンパクト化される。

なお、第 1 の実施の形態では、ガイド溝 1303, 1304 に補助ソース板 1500a, 1500b を先に配置して、ゲート板 1400 を配置する場合を例に挙げて説明した。この場合に限らず、ゲート板 1400 を先に配置して、補助ソース板 1500a, 1500b を配置することも可能である。

50

## 【0047】

また、第1の実施の形態では、半導体素子1020にパワーMOSFETを用いる場合について説明したが、これに限定されるものではなく、半導体素子1020をIGBTにしてもよい。この場合、上記実施の形態におけるドレイン電極はコレクタ電極に、ソース電極はエミッタ電極にそれぞれ置き換えるべき。また、その他のスイッチング素子を用いてもよい。

## 【0048】

すなわち、第1の出願の明細書及び特許請求の範囲において、「ドレイン電極」とは半導体素子1020の陽極側の電極の総称であり、「ソース電極」とは半導体素子1020の陰極側の電極の総称である。

10

## 【0049】

## [第2の実施の形態]

第2の実施の形態では、第1の実施の形態で示した半導体モジュールを複数組み合わせた半導体装置について、図11及び図12を用いて説明する。

## 【0050】

図11は、第2の実施の形態の半導体装置を示す図である。

また、図12は、第2の実施の形態の半導体装置の配線板を示す図である。

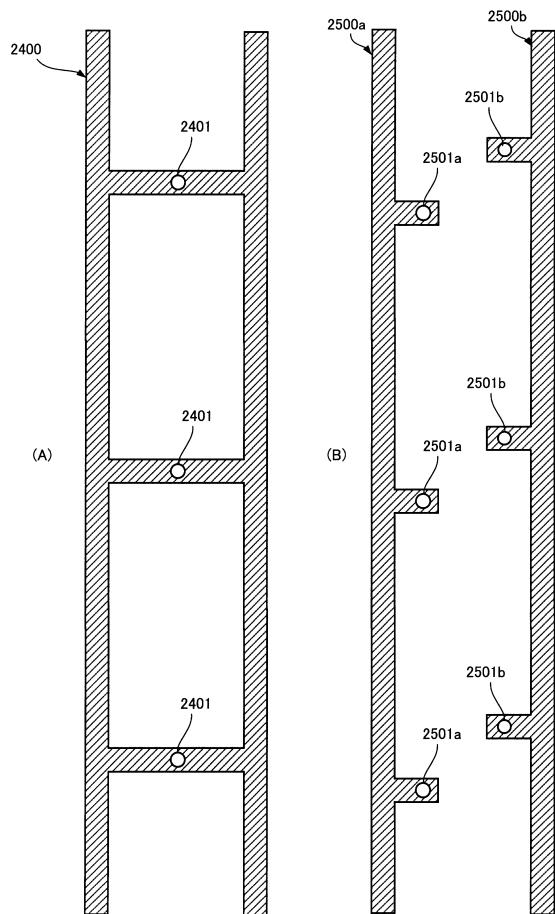

図12(A)はゲート板の平面図、図12(B)は補助ソース板の平面図をそれぞれ示している。

## 【0051】

20

複数(第2の実施の形態では3つ)の半導体モジュール(図8(B))を用意して、ガイド溝1303同士が連結し、またガイド溝1304同士が連結するように配置する。

このようにガイド溝同士を連結した複数の半導体モジュールに対して、図12に示されるような、一体化したゲート板2400と、一体化した補助ソース板2500a, 2500bとを用意する。

## 【0052】

複数を組み合わせた半導体モジュールの連結したガイド溝1303に、絶縁層を介して一体化した補助ソース板2500aを配置する。配置の際には、補助ソース板2500aのボルト孔2501aを、補助ソース端子1060のボルト孔1061に位置合わせする。補助ソース板2500bについても同様に、連結したガイド溝1304に、絶縁層を介して配置する。この際、補助ソース板2500bのボルト孔2501bを、補助ソース端子1050のボルト孔1051に位置合わせする。

30

## 【0053】

続いて、第1の実施の形態と同様、補助ソース板2500a, 2500bの上に、絶縁層を配置する。

さらに、連結したガイド溝1303, 1304の絶縁層を介して、一体化したゲート板2400を配置する。配置の際には、ゲート板2400のボルト孔2401を、ゲート端子1040のボルト孔1041に位置合わせする。

## 【0054】

さらに、図11に示されるように、ゲート板2400が、ボルト1043で固定される。また、補助ソース板2500a, 2500bが、ボルト1053, 1063でそれぞれ固定される。

40

## 【0055】

このようにして組み合わされた半導体装置100の複数のソース端子1070, 1080を、ソース導体(不図示)で押圧する。そして同様に、半導体装置100の複数のドレイン板1010を、ドレイン導体(不図示)で押圧する。これにより、複数の半導体モジュール1000を、容易に並列接続することができる。

## 【0056】

このように、第2の実施の形態においては、複数の半導体モジュール1000について、ガイド溝1303, 1304が連結するように組み合わせて並列接続した、半導体装置

50

100を構成することができる。これにより、半導体装置100の大電流化を容易に図ることができる。

【0057】

[第3の実施の形態]

第3の実施の形態では、補助ソース端子を設けずに、補助ソース電流を得ることができ半導体モジュールについて、図13を用いて説明する。

【0058】

図13は、第3の実施の形態の半導体モジュールを示す図である。

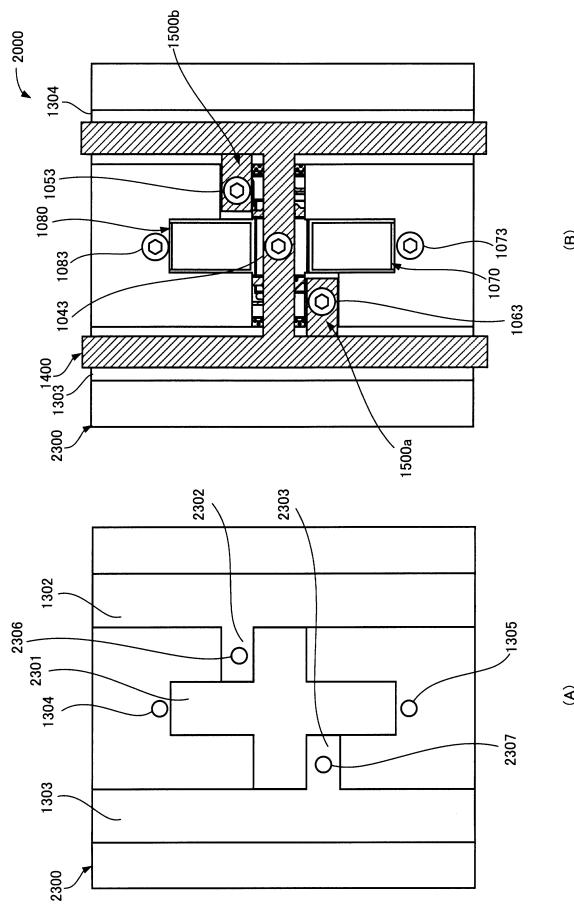

図13(A)は、蓋2300の平面図を、図13(B)は、第3の実施の形態の半導体モジュール2000の平面図をそれぞれ示している。

10

【0059】

半導体モジュール2000では、第1の実施の形態の半導体モジュール1000に示した補助ソース端子1050, 1060を配置していない。また、半導体モジュール2000の蓋2300は、図13(A)に示されるように、ソース端子1070, 1080と、ゲート端子1040を表出する開口2301が形成されている。さらに、蓋2300は、ガイド溝1303, 1304と同じ深さ(高さ)に位置する凹部2302, 2303と、凹部2302, 2303に設けられたボルト孔2306, 2307とを備える。その他は、半導体モジュール1000と同様の構成をなしている。

【0060】

このような蓋2300を、第1の実施の形態と同様に、半導体素子1020、積層基板1030等を収納する枠1200に被せる。ソース端子1070, 1080のボルト孔1071, 1081に位置合わせし、ボルト孔1304, 1305をボルト1083, 1073でねじ止めする。これにより、蓋2300がソース端子1070, 1080に固定される。

20

【0061】

さらに、第1の実施の形態と同様に、補助ソース板1500a, 1500bをガイド溝1303, 1304に絶縁層を介して配置する。そして、補助ソース板1500a, 1500bのボルト孔1501a, 1501bを、ボルト孔2307, 2306に位置合わせする。そして、補助ソース板1500a, 1500bを、ボルト1053, 1063でねじ止めして、蓋2300に固定し、電気的に接続する。ゲート板1400も、第1の実施の形態と同様に、ゲート端子1040のボルト孔1041にボルト孔1401を位置合わせし、ボルト1043でねじ止めして、ゲート端子1040に固定される。

30

【0062】

この際、蓋2300は、ソース端子1070, 1080とは電気的に接続されているために、蓋2300とソース端子1070, 1080とは同電位となっている。この状態において、補助ソース板1500a, 1500bが蓋2300に電気的に接続されているために、補助ソース板1500a, 1500bも、ソース端子1070, 1080と同電位となる。したがって、第2回路板1031bと、補助ソース板1500a, 1500bとの間が、ソース端子1070, 1080及び蓋2300を経由して、電気的に接続されている。これにより、第1の実施の形態と同様に、補助ソース板1500a, 1500bから補助ソース電流を得ることが可能となる。

40

【0063】

第3の実施の形態により、構成部材の増加を抑えて、補助ソース電流を得ることが可能となる。

[第4の実施の形態]

第4の実施の形態では、半導体モジュールのガイド溝の深さをゲート端子並びに補助ソース端子よりも浅くする場合について、図14を用いて説明する。

【0064】

図14は、第4の実施の形態の半導体モジュールを示す図である。

図14(A)は、第4の実施の形態の半導体モジュール3000の平面図、図14(B)

50

) は、図 14 ( A ) の一点鎖線 X - X における断面拡大図をそれぞれ示している。

【 0 0 6 5 】

半導体モジュール 3000 は、ガイド溝 3303, 3304 が、第 1 の実施の形態のガイド溝 1303, 1304 よりも浅く構成されている。なお、半導体モジュール 3000 の他の構成については、第 1 の実施の形態の半導体モジュールと同様の構成をなしている。このため、図 14 ( B ) に示されるように、ガイド溝 3303 の底面 3303a が、ゲート端子 1040 の上端部よりも上方に位置しており、ガイド溝 3303 と、ゲート端子 1040 の上端部とに段差が生じている。

【 0 0 6 6 】

そこで、ガイド溝 3303, 3304 に配置するゲート板 1400 の中心部には、この段差に応じて傾斜が付けられている。この傾斜により、ゲート板 3400 のボルト孔がゲート端子 1040 のボルト孔 1041 に位置合わせされ、ゲート板 3400 がゲート端子 1040 にボルト 1043 で固定される。

10

【 0 0 6 7 】

また、補助ソース板 3500a, 3500b も、図示を省略するものの、ボルト孔が形成されている箇所に、ゲート板 3400 と同様に傾斜が付けられている。

これにより、ゲート板 3400 と補助ソース板 3500a, 3500b とが配置されるガイド溝 3303, 3304 の隙間 ( 空間 ) を小さくすることができる。このために、半導体モジュール 3000 の低インダクタンス化を図ることができる。したがって、ガイド溝 3303, 3304 の深さは、隙間が最も少ない、ゲート板 3400 と、補助ソース板 3500a, 3500b と、絶縁層とを合わせた厚さ程度とすることが望ましい。

20

【 0 0 6 8 】

また、半導体モジュール 3000 は、第 2 の実施の形態の半導体モジュール ( 図 11 ) と同様に、ガイド溝 3303, 3304 が連結するように複数組み合わせることも可能である。

【 0 0 6 9 】

〔 第 5 の実施の形態 〕

第 5 の実施の形態では、第 1 の実施の形態のゲート板 1400 と補助ソース板 1500a, 1500b とをプリント基板にして一体化した場合について、図 15 を用いて説明する。

30

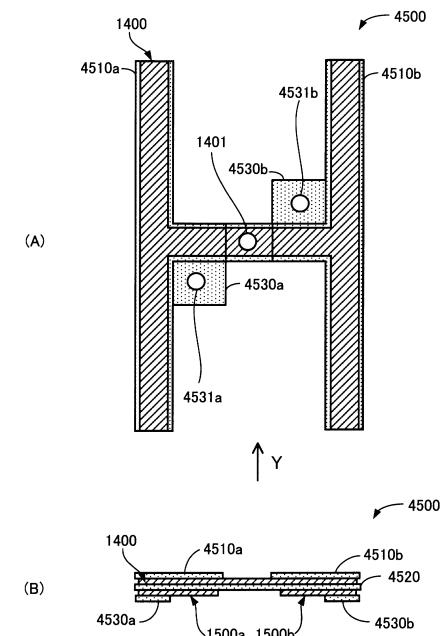

【 0 0 7 0 】

図 15 は、第 5 の実施の形態の半導体モジュールに用いられるゲート板と補助ソース板とを含むプリント基板を示す図である。

図 15 ( A ) は、ゲート板 1400 と補助ソース板 1500a, 1500b とを含むプリント基板の平面図を、図 15 ( B ) は、図 15 ( A ) の矢視 Y から見た側面図をそれぞれ示している。

【 0 0 7 1 】

プリント基板 4500 は、第 1 の実施の形態のゲート板 1400 と、補助ソース板 1500a, 1500b との間に絶縁材料で構成された基材 4520 が挟まれている。ゲート板 1400 上にはレジスト層 4510a, 4510b が形成され、またボルト孔 1041 部分が開口されている。また、補助ソース板 1500a, 1500b には、レジスト層 4510a, 4510b が形成され、ボルト孔 1501a, 1501b に対向する開口 4531a, 4531b が形成されている。

40

【 0 0 7 2 】

そして、第 1 の実施の形態の半導体モジュール 1000 の開口 1301、ガイド溝 1303, 1304 にプリント基板 4500 が嵌めこまれて、ボルト 1043, 1053, 1063 で固定される。

【 0 0 7 3 】

このようなプリント基板 4500 を用いることにより、ゲート板 1400 と、補助ソース板 1500a, 1500b の取り付けが容易になる。

50

なお、複数の半導体モジュールを組み合わせる場合には、例えば、第4の実施の形態に示したゲート板2400と、補助ソース板2500a, 2500bとを、プリント基板として一体化することが可能である。

【0074】

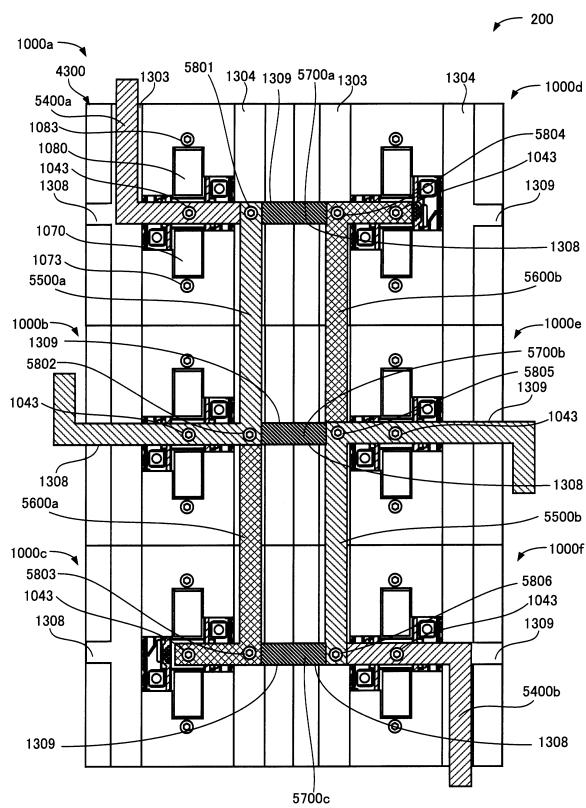

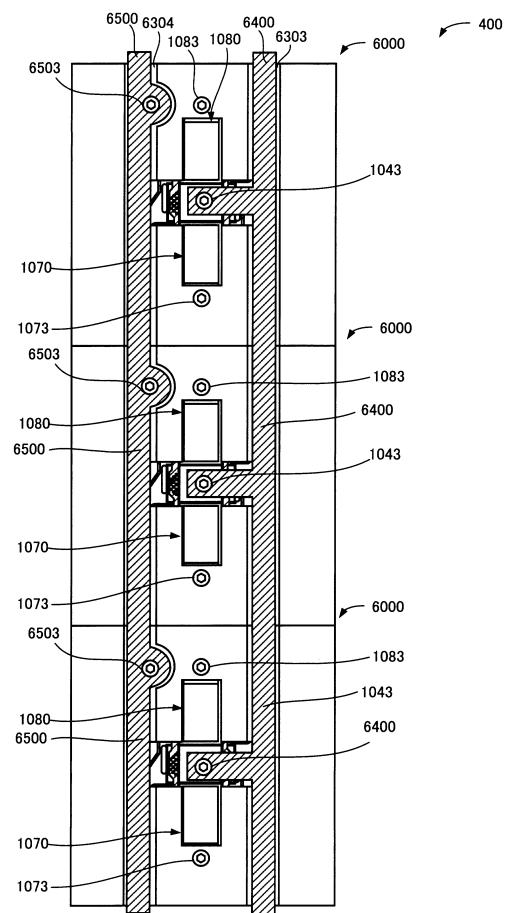

[第6の実施の形態]

第6の実施の形態では半導体モジュールを6つ組み合わせた場合について、図16を用いて説明する。

【0075】

図16は、第6の実施の形態の半導体装置を示す図である。

半導体モジュール1000a～1000fは、半導体モジュール1000と同様の構成をなしている。但し、半導体モジュール1000a～1000fの蓋4300には、ガイド溝1303, 1304の中心部から外周部に通じるガイド溝1308, 1309がさらに形成されている。なお、図16では、半導体モジュール1000aにのみ符号を付しており、半導体モジュール1000b～1000fに対する符号は省略している。

【0076】

このような半導体モジュール1000a～1000fを、図16のように縦3つ、横2つ並列に配置させている。

そして、ゲート板5400aが半導体モジュール1000aのガイド溝1303に配置され、半導体モジュール1000aのゲート端子1040にボルト1043で固定されている。

【0077】

ゲート板5500aは、半導体モジュール1000aのガイド溝1304と、半導体モジュール1000bのガイド溝1304, 1308とに配置され、半導体モジュール1000bのゲート端子1040にボルト1043で固定されている。

【0078】

ゲート板5600aは、半導体モジュール1000bのガイド溝1304と、半導体モジュール1000cのガイド溝1304とに配置され、半導体モジュール1000cのゲート端子1040にボルト1043で固定されている。

【0079】

また、ゲート板5600bは、半導体モジュール1000dのガイド溝1303と、半導体モジュール1000eのガイド溝1303とに配置され、半導体モジュール1000dのゲート端子1040にボルト1043で固定されている。

【0080】

ゲート板5500bは、半導体モジュール1000eのガイド溝1303, 1309と、半導体モジュール1000fのガイド溝1303とに配置され、半導体モジュール1000eのゲート端子1040にボルト1043で固定されている。

【0081】

ゲート板5400bは、半導体モジュール1000fのガイド溝1304に配置され、半導体モジュール1000fのゲート端子1040にボルト1043で固定されている。

接続板5700aが、半導体モジュール1000aのガイド溝1309と半導体モジュール1000dのガイド溝1308とに配置されている。接続板5700aと、ゲート板5400a, 5500aとが、ボルト5801で固定され、接続板5700aと、ゲート板5600bとが、ボルト5804で固定されている。

【0082】

接続板5700bが、半導体モジュール1000bのガイド溝1309と半導体モジュール1000eのガイド溝1308とに配置されている。接続板5700bと、ゲート板5500a, 5600aとが、ボルト5802で固定され、接続板5700bと、ゲート板5600b, 5500bとが、ボルト5805で固定されている。

【0083】

接続板5700cが、半導体モジュール1000cのガイド溝1309と半導体モジュ

10

20

30

40

50

ール 1000f のガイド溝 1308 とに配置されている。接続板 5700c と、ゲート板 5600a とが、ボルト 5803 で固定され、接続板 5700c とゲート板 5500b, 5400b とが、ボルト 5806 で固定されている。

【0084】

このようにして複数の半導体モジュール 1000a ~ 1000f が組み合わされた半導体装置 200 では、裏面のドレイン板 1010 からドレイン電圧が印加される。そして、ゲートドライバユニットからゲート板 5400a, 5500a, 5500b, 5400b にそれぞれゲート電圧が印加されると、各ソース端子 1070, 1080 からソース電流が出力される。

【0085】

このように、半導体モジュールの蓋 4300 に、外周部に通じるガイド溝 1308, 1309 を配置することにより、複数の半導体モジュールの配置パターン数を増加することができる。これにより、より柔軟に半導体装置 200 の大電流化を図ることができる。

【0086】

[第7の実施の形態]

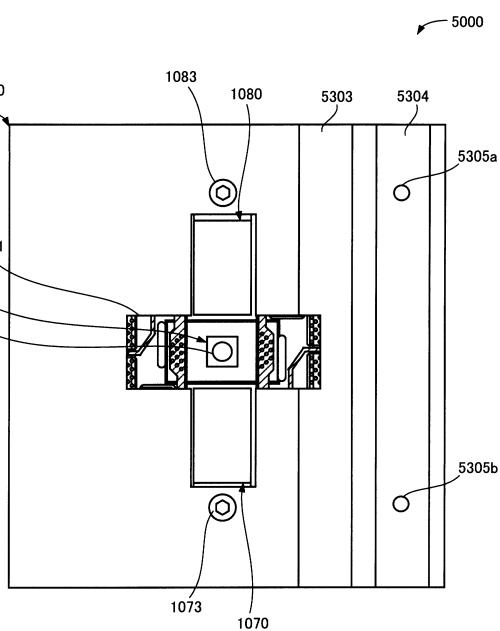

第7の実施の形態では、第1の実施の形態の半導体モジュール 1000 において、補助ソース板が配置されるガイド溝を新たに設けた場合について説明する。

【0087】

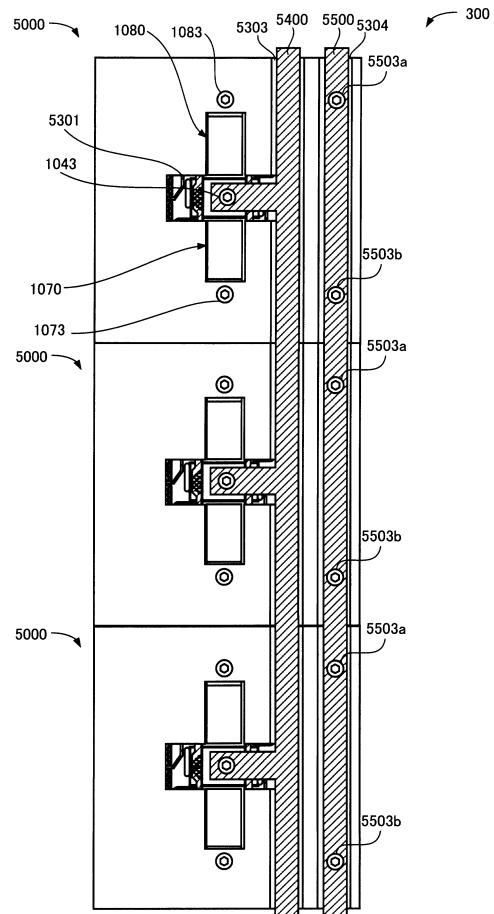

図 17 は、第7の実施の形態の半導体モジュールを示す図である。

半導体モジュール 5000 では、蓋 5300 以外については、半導体モジュール 1000 と同様の構成がなされている。

【0088】

蓋 5300 は、ゲート端子 1040 と隣接し、開口 1301 に接して形成されたガイド溝 5303 を備える。さらに、当該ガイド溝 5303 と平行に配置され、ボルト孔 5305a, 5305b を備えるガイド溝 5304 が形成されている。そして、ガイド溝 5304 に沿って、図示しない補助ソース板が配置され、補助ソース板はボルト孔 5305a, 5305b を用いて固定される。

【0089】

また、蓋 5300 は、ソース端子 1070, 1080 にボルト 1073, 1083 で固定されている。このため、蓋 5300 は、ソース端子 1070, 1080 と同電位である。したがって、第2回路板 1031b と、補助ソース板とを同電位にすることが可能となる。

【0090】

なお、ゲート板が配置されるガイド溝 5303 は、図 17 の形成位置に限らず、第1の実施の形態と同様に、開口 5301 の両側に形成することも、または、開口 5301 の図中左側のみに形成することも可能である。

【0091】

また、半導体モジュール 5000 を複数組み合わせた場合について、図 18 を用いて説明する。

図 18 は、第7の実施の形態の半導体モジュールを複数組み合わせた半導体装置を示す図である。

【0092】

複数（第7の実施の形態では3つ）の半導体モジュール 5000 を用意して、ガイド溝 5303, 5304 がそれぞれ連結するように配置する。

連結したガイド溝 5303 に絶縁層を介して、ゲート板 5400 を配置して、ゲート板 5400 をゲート端子 1040 にボルト 1043 で固定する。

【0093】

同様にして、連結したガイド溝 5304 に絶縁層を介して、補助ソース板 5500 を配置して、補助ソース板 5500 をガイド溝 5304 にボルト 5503a, 5503b で固定する。

10

30

40

50

## 【0094】

このようにして複数の半導体モジュール5000を組み合わせた半導体装置300では、各半導体モジュール5000から出力されるソース電流が合成されて、半導体装置の大電流化を図ることができる。

## 【0095】

## [第8の実施の形態]

第8の実施の形態では、第7の実施の形態の半導体モジュール5000において、補助ソース板が配置されるガイド溝を別の箇所に設けた場合について説明する。

## 【0096】

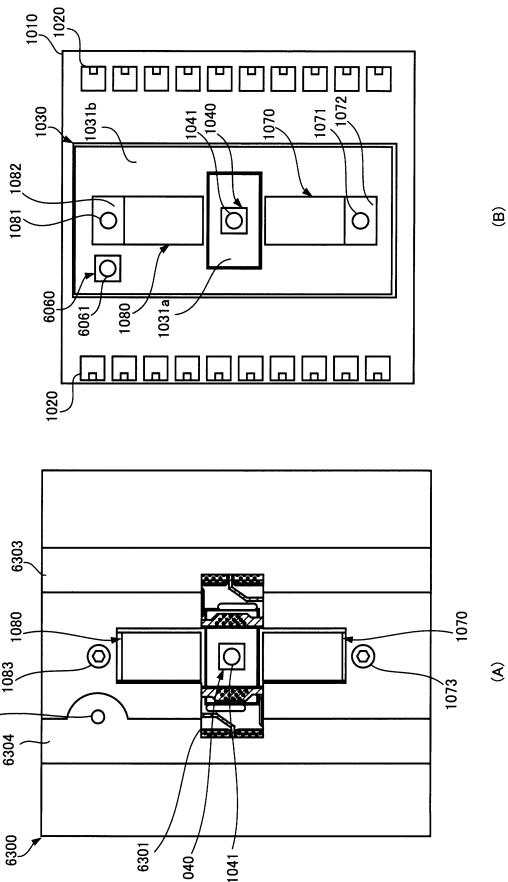

図19は、第8の実施の形態の半導体モジュールを示す図である。

10

図19(A)は、蓋6300が設置された半導体モジュール6000の平面図、図19(B)は、半導体モジュール6000の内部平面図をそれぞれ示している。

## 【0097】

半導体モジュール6000は、蓋6300及び補助ソース端子6060以外については、半導体モジュール1000と同様の構成がなされている。

蓋6300は、ゲート端子1040と隣接し、開口6301に接して形成されたガイド溝6303を備える。さらに、開口6301の図中左側に、ガイド溝6303と平行に配置され、ボルト孔6305aを備える補助ガイド溝6304が形成されている。

## 【0098】

補助ソース端子6060は、第2回路板1031b上に配置されている。蓋6300が枠1200に設置されると、補助ガイド溝6304のボルト孔6305aと、補助ソース端子6060のボルト孔6061とが位置合わせされる。

20

## 【0099】

そして、補助ガイド溝6304に沿って、図示しない補助ソース板が絶縁層を介して配置され、ボルト孔6305aを用いて図示しないボルトにより固定される。

また、このような半導体モジュール6000を複数組み合わせた半導体装置400について、図20を用いて説明する。

## 【0100】

図20は、第8の実施の形態の半導体モジュールを複数組み合わせた半導体装置を示す図である。

30

複数(第8の実施の形態では3つ)の半導体モジュール6000を用意して、ガイド溝6303と補助ガイド溝6304が連結するように配置する。

## 【0101】

そして、連結したガイド溝6303に絶縁層を介してゲート板6400を配置して、ゲート板6400をゲート端子1040にボルト1043で固定する。

同様にして、連結した補助ガイド溝6304に絶縁層を介して、補助ソース板6500を配置して、補助ソース板6500を補助ガイド溝6304のボルト孔6305aに、ボルト6503でねじ止めして固定する。

## 【0102】

このようにして半導体モジュール6000が組み合わされた半導体装置400では、各半導体モジュール6000から出力されるソース電流が合成されて、半導体装置400の大電流化を図ることができる。

40

## 【0103】

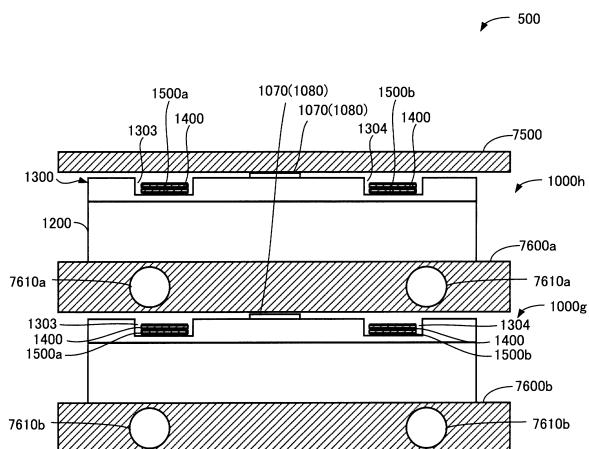

## [第9の実施の形態]

第9の実施の形態では、半導体モジュール1000を直列に組み合わせた場合について図21及び図22を用いて説明する。

## 【0104】

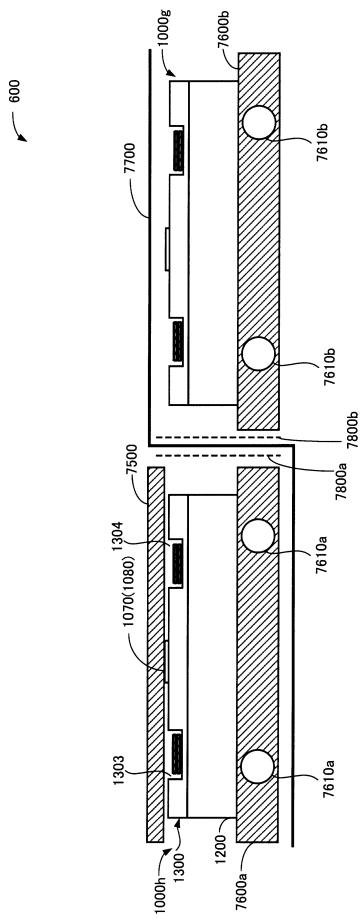

図21及び図22は、第9の実施の形態の半導体装置を示す側面図である。

なお、図21では、複数の半導体モジュールを縦方向に配列して、図22は、複数の半導体モジュールを横方向に配列して、それぞれ直列に組み合わされた半導体装置を示す側面

50

図である。

**【0105】**

図21に示すように、金属製の冷却フィン7600bに、第1の実施の形態の半導体モジュール1000gを載置して、半導体モジュール1000gのドレイン板1010と冷却フィン7600bとを電気的に接続させる。当該半導体モジュール1000g上に冷却フィン7600aを載置して、半導体モジュール1000gのソース端子1070, 1080と冷却フィン7600aとを電気的に接続させる。

**【0106】**

冷却フィン7600aに、さらに、半導体モジュール1000hを載置して、半導体モジュール1000hのドレイン板1010と冷却フィン7600aとを電気的に接続させる。半導体モジュール1000hのソース端子1070, 1080に、ソース板7500を圧接させる。

10

**【0107】**

なお、冷却フィン7600a, 7600bには、水が流れるパイプ7610a, 7610bが内部に形成されている。冷却フィン7600a, 7600bはパイプ7610a, 7610bに水が流れることで、半導体モジュール1000h, 1000gをより効果的に冷却することができる。

**【0108】**

このように半導体モジュール1000h, 1000gを積層させて組み合わせた半導体装置500は、冷却フィン7600bからドレイン電圧を印加して、各半導体モジュール1000g, 1000hのゲート板1400にゲートユニットドライバからゲート電圧を印加する。すると、半導体モジュール1000g、冷却フィン7600a、及び半導体モジュール1000hを経由して出力したソース電流がソース板7500から得られる。すなわち、第9の実施の形態の半導体装置500の定格電圧は、半導体モジュール1000の定格電圧の2倍となる。

20

**【0109】**

なお、第9の実施の形態において、半導体モジュール1000h, 1000gは2つ、すなわち2段に限られず、3段以上であっても積層して直列接続することが可能である。また、第2, 第6の実施の形態のように並列に組み合わせた半導体モジュール1000を、さらに任意の段数直列に設置することも可能である。例えば、直列に3段積層させる場合であって、ドレイン板1010からソース端子1070, 1080に順に半導体モジュール1000を1段目に2並列、2段目に4並列、3段目に3並列、合計9つの半導体モジュール1000を設置することができる。この際の半導体装置の定格電圧、定格電流は9つの半導体モジュール1000で一致する必要はない。定格電圧が一致しない場合、半導体装置の定格電圧は、各段における定格電圧が最低である半導体モジュール1000の3つの和に等しい。また、定格電流が一致しない場合、半導体装置の定格電流は、各段の3つの定格電流のうち、最低となる段の定格電流に等しい。

30

**【0110】**

また、冷却フィン7600a, 7600bに限らず、導電部材を介して積層することや、半導体モジュール1000h, 1000g同士を直接積層することも可能である。

40

次いで、複数の半導体モジュール1000を直列に接続するに当たって、半導体モジュール1000を横方向に配置する場合について、図22を用いて説明する。

**【0111】**

半導体装置600は、図22に示されるように、冷却フィン7600a, 7600bを並列に配置し、冷却フィン7600aに半導体モジュール1000hを配置し、冷却フィン7600bに半導体モジュール1000gを配置する。半導体モジュール1000hのドレイン板と接続された冷却フィン7600aと、半導体モジュール1000gのソース端子1070, 1080とを、金属プレート7700で圧接して電気的に接続する。但し、冷却フィン7600a, 7600bと金属プレート7700との間には絶縁層7800a, 7800bを挟んで電気的に絶縁している。

50

## 【0112】

このようにして半導体モジュール1000を横方向に配列して、直列接続することが可能である。

## 【符号の説明】

## 【0113】

|                                                |          |    |

|------------------------------------------------|----------|----|

| 100                                            | 半導体装置    |    |

| 1000                                           | 半導体モジュール |    |

| 1010                                           | ドレイン板    |    |

| 1020                                           | 半導体素子    |    |

| 1030                                           | 積層基板     | 10 |

| 1031 a                                         | 第1回路板    |    |

| 1031 b                                         | 第2回路板    |    |

| 1032                                           | 絶縁板      |    |

| 1033                                           | 金属板      |    |

| 1040                                           | ゲート端子    |    |

| 1041, 1051, 1061, 1071, 1081, 1305, 1306, 1401 |          |    |

| , 1501 a, 1501 b                               | ボルト孔     |    |

| 1043, 1053, 1063, 1073, 1083                   | ボルト      |    |

| 1050, 1060                                     | 補助ソース端子  |    |

| 1070, 1080                                     | ソース端子    | 20 |

| 1072, 1082                                     | 段差面      |    |

| 1090, 1100                                     | プリント基板   |    |

| 1091, 1101                                     | ゲート配線層   |    |

| 1093, 1103                                     | ソース配線層   |    |

| 1092 a, 1092 b, 1102 a, 1102 b                 | 導電ポスト    |    |

| 1094, 1104                                     | 貫通孔      |    |

| 1095, 1105                                     | ゲート接続部   |    |

| 1096, 1106                                     | ソース接続部   |    |

| 1200                                           | 枠        |    |

| 1300                                           | 蓋        | 30 |

| 1301                                           | 開口       |    |

| 1303, 1304                                     | ガイド溝     |    |

| 1400                                           | ゲート板     |    |

| 1500 a, 1500 b                                 | 補助ソース板   |    |

| 1600 a, 1600 b, 1600 c                         | 絶縁層      |    |

| 1700                                           | ソース導体    |    |

| 1800                                           | ドレイン導体   |    |

【図1】

【図2】

【図3】

【図4】

【 义 5 】

【 义 6 】

【 四 7 】

【 四 8 】

【図9】

(A)

(B)

【図11】

【図10】

【図12】

(A)

(B)

【図13】

(B)

(A)

【図14】

【図15】

【図16】

【図17】

【図18】

【 図 1 9 】

【図20】

【図21】

【図22】

---

フロントページの続き

(72)発明者 君島 大輔

神奈川県川崎市川崎区田辺新田1番1号 富士電機株式会社内

審査官 木下 直哉

(56)参考文献 特開平01-122146 (JP, A)

特開平01-255257 (JP, A)

特開平05-160339 (JP, A)

実開昭62-142856 (JP, U)

(58)調査した分野(Int.Cl., DB名)

H01L 21/54

H01L 23/00-23/04

H01L 23/06-23/10

H01L 23/16-23/26

H01L 23/29

H01L 23/34-23/36

H01L 23/373-23/427

H01L 23/44

H01L 23/467-23/48

H01L 25/00-25/07

H01L 25/10-25/11

H01L 25/16-25/18

H02M 7/42-7/98