(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-186186

(P2004-186186A)

(43) 公開日 平成16年7月2日(2004.7.2)

(51) Int.C1.<sup>7</sup>

H01L 21/338

H01L 29/812

F 1

H01L 29/80

H01L 29/80

テーマコード(参考)

5F1O2

F

審査請求 未請求 請求項の数 4 O L (全 7 頁)

(21) 出願番号

特願2002-347828 (P2002-347828)

(22) 出願日

平成14年11月29日 (2002.11.29)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100081732

弁理士 大胡 典夫

(74) 代理人 100075683

弁理士 竹花 喜久男

(74) 代理人 100084515

弁理士 宇治 弘

(72) 発明者 木村 英樹

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝小向工場内

(72) 発明者 川崎 久夫

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝小向工場内

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【要約】

【課題】ゲート耐圧を確保し、ソース抵抗を低減した半導体装置およびその製造方法を提供すること。

【解決手段】能動層12を有するGaAs基板11と、このGaAs基板11上に設けられたオーム性接触のソース電極Sおよびドレイン電極Dと、ソース電極Sおよびドレイン電極D間に位置する能動層12の上方に堆積された第1絶縁膜14と、この第1絶縁膜14を貫通して能動層12の所定深さ部分にまで形成された溝17の内部に埋め込まれ、その下端部分が能動層12に接触するショットキー接合のゲート電極Gと、このゲート電極Gの下端部分G1よりも上方に位置する上方部分と能動層12からなる溝17の側壁部分との間に挟まれた第2絶縁膜18とを具備している。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

能動層を有する半導体基板と、この半導体基板上に設けられたオーム性接触のソース電極およびドレイン電極と、前記ソース電極および前記ドレイン電極間に位置する前記能動層の上方に堆積された第1絶縁膜と、この第1絶縁膜を貫通して前記能動層の所定深さ部分まで形成された溝内部に埋め込まれ、その下端部分が前記能動層に接触するショットキー接合のゲート電極と、このゲート電極の前記下端部分よりも上方に位置する上方部分と前記能動層からなる前記溝側壁部分との間に挟まれた第2絶縁膜とを具備したことを特徴とする半導体装置。

## 【請求項 2】

能動層およびこの能動層上に位置する $n^+$ 層を有し、前記 $n^+$ 層は前記能動層よりも高濃度に不純物が注入されている半導体基板と、この半導体基板上に設けられたオーム性接触のソース電極およびドレイン電極と、前記ソース電極および前記ドレイン電極間に位置する前記 $n^+$ 層の上方に堆積された第1絶縁膜と、この第1絶縁膜および前記 $n^+$ 層を貫通して前記能動層の所定深さ部分まで形成された溝内部に埋め込まれ、その下端部分が前記能動層に接触するショットキー接合のゲート電極と、このゲート電極の前記下端部分よりも上方に位置する上方部分と前記能動層および前記 $n^+$ 層の両層からなる前記溝側壁部分との間に挟まれた第2絶縁膜とを具備したことを特徴とする半導体装置。

## 【請求項 3】

半導体基板の能動層の上方に、オーム性接触のソース電極およびドレイン電極、ショットキー接合のゲート電極を設けた半導体装置の製造方法において、前記ソース電極および前記ドレイン電極間に位置する前記能動層の上方に第1絶縁膜を堆積する第1工程と、前記第1絶縁膜の所定位置に第1開口を設け、前記第1開口を通してエッチングを行い、前記能動層の所定深さ部分まで溝を形成する第2工程と、この第2工程の後、第2絶縁膜およびレジスト膜を順に堆積する第3工程と、前記能動層に設けられた前記溝上方領域の前記レジスト膜に第2開口を設ける第4工程と、前記第2開口を通して前記第2絶縁膜をエッチングし、前記溝側壁部分に前記第2絶縁膜を残し、かつ、前記溝底面上に位置する前記第2絶縁膜の一部を除去する第5工程と、この第5工程で前記第2絶縁膜が除去された領域の前記能動層を所定の深さまでエッチング除去する第6工程と、この第6工程の後、前記溝内に前記ゲート電極を埋め込み形成する第7工程とからなることを特徴とする半導体装置の製造方法。

## 【請求項 4】

能動層およびこの能動層上に位置し前記能動層よりも不純物が高濃度に注入された $n^+$ 層を有する半導体基板上に、オーム性接触のソース電極およびドレイン電極、ショットキー接合のゲート電極を設けた半導体装置の製造方法において、前記ソース電極および前記ドレイン電極間に位置する前記 $n^+$ 層の上方に第1絶縁膜を堆積する第1工程と、前記第1絶縁膜の所定位置に第1開口を設け、前記第1開口を通してエッチングを行い、前記能動層の所定深さ部分まで溝を形成する第2工程と、この第2工程の後、第2絶縁膜およびレジスト膜を順に堆積する第3工程と、前記能動層に設けられた前記溝の上方領域の前記レジスト膜に第2開口を設ける第4工程と、前記第2開口を通して前記第2絶縁膜をエッチングし、能動層および $n^+$ 層からなる前記溝の側壁部分に前記第2絶縁膜を残し、かつ、前記溝底面上に位置する前記第2絶縁膜の一部を除去する第5工程と、この第5工程で前記第2絶縁膜が除去された領域の前記能動層を所定の深さまでエッチング除去する第6工程と、この第6工程の後、前記溝内に前記ゲート電極を埋め込み形成する第7工程とからなることを特徴とする半導体装置の製造方法。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は、高周波動作に適する半導体装置およびその製造方法に関する。

## 【0002】

10

20

30

40

50

【従来の技術】

GaAsなどの化合物半導体を用いた半導体装置たとえば電界効果型トランジスタ(以下FETと略する)は、優れた高周波特性を有しマイクロ波帯で動作する半導体装置として広く実用化されている。

【0003】

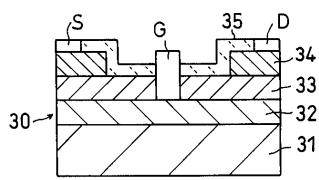

ここで、従来の半導体装置について、FETを例にとり図2を参照して説明する。半導体基板30は半絶縁性半導体のGaAs基板31などから構成されている。GaAs基板31上にショットキー接合を形成する能動層32が設けられている。能動層32上にアンドープのGaAs層33が設けられ、GaAs層33上には良好なオーム性接触を得るためにn<sup>+</sup>層34が設けられている。

10

【0004】

上記した半導体基板30のn<sup>+</sup>層34上にソース電極Sおよびドレイン電極Dが形成されている。アンドープのGaAs層33上に絶縁膜35が堆積され、絶縁膜35に設けられた開口部分を通してゲート電極Gが配置されている。

【0005】

上記したFETは、絶縁膜35と半導体基板30たとえばアンドープのGaAs層33との界面に高密度の表面準位が存在し、この表面準位により形成される表面空乏層がFETの動作に悪影響を与えていた。

20

【0006】

このような表面空乏層の影響を少なくするために、近年、ゲート電極G直下のチャネル部と、絶縁膜35およびGaAs層33の界面とを分離した構造、いわゆる埋め込みゲート電極構造が採用されている。

【0007】

埋め込みゲート電極構造の場合、動作時における十分な耐圧を得るために、図2に示したように、ゲート電極Gが接する溝の側壁部たとえばGaAs層33をアンドープ層にしている。この結果、ソース抵抗が増大し、FETの高性能化を妨げる原因になっている。

【0008】

上記した従来技術に関連する半導体装置およびその製造方法は特許文献1などにも記載されている。

30

【0009】

【特許文献1】

特開平6-232167号公報

【0010】

【発明が解決しようとする課題】

従来の半導体装置たとえば埋め込みゲート電極構造のFETは、十分なゲート耐圧を得るために、埋め込みゲート電極が接する溝の側壁部を絶縁層あるいは低濃度のn層にしている。そのためソース抵抗が増大し、FETの高性能化が困難になっている。

【0011】

本発明は、上記した欠点を解消し、ゲート耐圧を確保し、ソース抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

40

【0012】

【課題を解決するための手段】

本発明は、能動層を有する半導体基板と、この半導体基板上に設けられたオーム性接触のソース電極およびドレイン電極と、前記ソース電極および前記ドレイン電極間に位置する前記能動層の上方に堆積された第1絶縁膜と、この第1絶縁膜を貫通して前記能動層の所定深さ部分まで形成された溝内部に埋め込まれ、その下端部分が前記能動層に接触するショットキー接合のゲート電極と、このゲート電極の前記下端部分よりも上方に位置する上方部分と前記能動層からなる前記溝側壁部分との間に挟まれた第2絶縁膜とを具備したことを特徴とする。

【0013】

50

また、本発明は、半導体基板の能動層の上方に、オーム性接触のソース電極およびドレイン電極、ショットキー接合のゲート電極を設けた半導体装置の製造方法において、前記ソース電極および前記ドレイン電極間に位置する前記能動層の上方に第1絶縁膜を堆積する第1工程と、前記第1絶縁膜の所定位置に第1開口を設け、前記第1開口を通してエッチングを行い、前記能動層の所定深さ部分まで溝を形成する第2工程と、この第2工程の後、第2絶縁膜およびレジスト膜を順に堆積する第3工程と、前記能動層に設けられた前記溝上方領域の前記レジスト膜に第2開口を設ける第4工程と、前記第2開口を通して前記第2絶縁膜をエッチングし、前記溝側壁部分に前記第2絶縁膜を残し、かつ、前記溝底面上に位置する前記第2絶縁膜の一部を除去する第5工程と、この第5工程で前記第2絶縁膜が除去された領域の前記能動層を所定の深さまでエッチング除去する第6工程と、この第6工程の後、前記溝内に前記ゲート電極を埋め込み形成する第7工程とからなることを特徴とする。

10

## 【0014】

## 【発明の実施の形態】

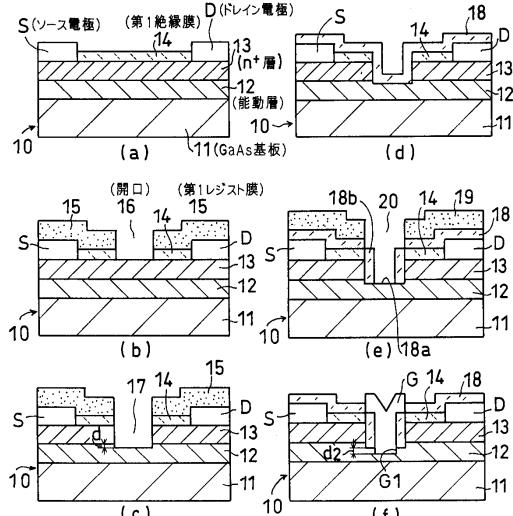

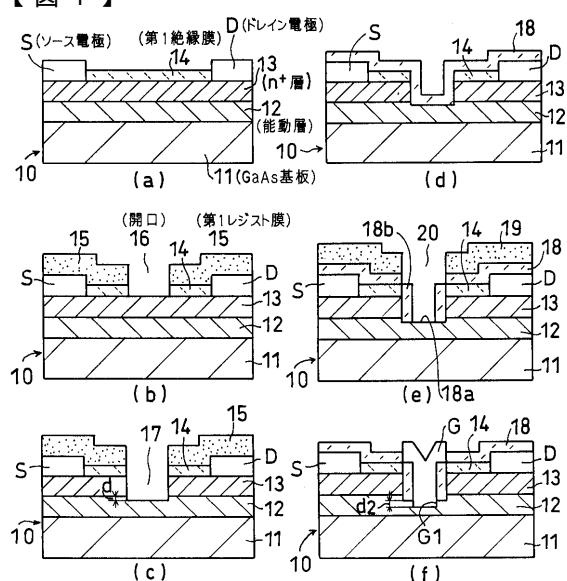

本発明の実施形態について、FETの場合を例にとり図1の工程図を参照して説明する。

## 【0015】

図1(a)に示すように、半導体基板10は半絶縁性半導体基板たとえばGaAs基板11などから構成されている。GaAs基板11上に、ショットキー接合およびチャネルを形成する能動層12が設けられ、能動層12上には良好なオーム性接触を得るためにn<sup>+</sup>層13が設けられている。能動層12およびn<sup>+</sup>層13は、たとえばエピタキシャル結晶成長法によりGaAs基板11上に順に形成される。

20

## 【0016】

半導体基板10のn<sup>+</sup>層13上にソース電極Sおよびドレイン電極Dが形成されている。能動層12の上方たとえばn<sup>+</sup>層13上には、ソース電極Sとドレイン電極Dに挟まれた領域に、たとえばSiO<sub>2</sub>からなる第1絶縁膜14が100nm程度の厚さに堆積されている。

## 【0017】

次に、図1(b)に示すように、第1レジスト膜15を全面に塗布し、その後、第1絶縁膜14上に位置する第1レジスト膜15の所定位置に第1開口16を設ける。その後、さらに第1開口16を通して第1絶縁膜14をたとえばRIE(反応性イオンエッチング)で垂直エッチングし、第1開口16下方領域の第1絶縁膜14を除去する。

30

## 【0018】

次に、図1(c)に示すように、第1開口16および第1絶縁膜14が除去された領域を通して、n<sup>+</sup>層13部分と能動層12の一部、たとえば能動層12の所定深さd1部分までをそれぞれエッチング除去し、n<sup>+</sup>層13部分から能動層12部分にわたって溝17を形成する。

## 【0019】

次に、第1レジスト15を剥離した後、図1(d)に示すように、半導体基板10の全面たとえばソース電極Sやドレイン電極D、第1絶縁膜14それぞれの上面、およびn<sup>+</sup>層13や能動層12部分の一部に設けられた溝17内面を覆うように、たとえばSiNからなる第2絶縁膜18を100nm程度の厚さに堆積する。

40

## 【0020】

次に、図1(e)に示すように、第2レジスト膜19を全面に塗布した後、溝17部分の上方領域に位置する第2レジスト膜19の部分に第2開口20を設け、その後、第2開口20を通して、たとえばRIEにより、第2絶縁膜18に対し100nm程度の厚さ分を垂直エッチングする。

## 【0021】

このエッチングにより、たとえば溝17底部中央の第2絶縁膜18が除去され、その除去部分18aに能動層12が露出する。この場合、溝17の側壁部に堆積した第2絶縁膜18bは、100nm程度の垂直エッチングに対しては十分な厚みを持っている。したがつ

50

て、エッティング後も、溝 17 の側壁部は第 2 絶縁膜 18 で覆われている。

【0022】

また、溝 17 の周辺部も、第 1 絶縁膜 14 および第 2 絶縁膜 18 が重なって堆積され、100 nm 程度の垂直エッティングに対しては十分な厚みを持っている。したがって、第 2 レジスト膜 19 の第 2 開口 20 に位置ずれが生じ、溝 17 周辺部が第 2 開口 20 の下方領域に位置しても、溝 17 の周辺部は第 2 絶縁膜 18 に覆われた状態が確保される。

【0023】

次に、図 1 (f) に示すように、能動層 12 をさらに所定深さ  $d_2$  だけエッティングし、その後、溝 17 を埋め込むようにたとえばリフトオフ法でゲート電極 G を形成し、FET が完成する。

10

【0024】

上記した構成によれば、FET のゲート電極 G は、その下端領域 G1 (図 1 (f))、すなわち図 1 (f) の工程でエッティングされた領域が能動層 12 と接触する。また、下端領域 G1 の上方に位置する上方部分は、 $n^+$  層 13 および能動層 12 からなる溝 17 側壁部との間に第 2 絶縁膜 18 が挟まれた構造になっている。このことにより、FET の動作に必要とされる十分なゲート耐圧が確保されるとともに、アンドープ層を設ける必要がなくなるため、ソース抵抗を低下させることができる。

【0025】

上記の実施形態では、半絶縁性半導体基板たとえば GaAs 基板上に能動層や  $n^+$  層をエピタキシャル結晶成長法で形成している。しかし、この発明は、能動層や  $n^+$  層をイオン注入法で形成した半導体装置に対しても適用できる。

20

【0026】

また、上記の実施形態では  $n^+$  層が設けられている。しかし、 $n^+$  層は必ずしも必要とされず、たとえば  $n^+$  層に代えて、実用上問題のないコンタクト抵抗を得るに足りる電子濃度や膜厚を持った能動層を利用する構造の半導体装置などに対しても適用できる。

30

【0027】

上記した構成によれば、ゲート電極の上方部分は溝の側壁部との間に絶縁膜が挟まれた構造になっている。そのため、アンドープ層を設けることなく、ソース抵抗を低下させ、なおかつ十分なゲート耐圧を確保した半導体装置およびその製造方法が得られ、FET の高性能化が達成される。

【0028】

【発明の効果】

本発明によれば、ゲート耐圧を確保しソース抵抗を低減した半導体装置およびその製造方法を実現できる。

【図面の簡単な説明】

【図 1】本発明の実施形態を説明するための断面で示した工程図である。

【図 2】従来例を説明するための断面図である。

【符号の説明】

10 ... 半絶縁性半導体基板

11 ... GaAs 基板

40

12 ... 能動層

13 ...  $n^+$  層

14 ... 第 1 絶縁膜

15 ... 第 1 レジスト膜

16 ... 第 1 開口

17 ... 溝

18 ... 第 2 絶縁膜

19 ... 第 2 レジスト膜

20 ... 第 2 開口

S ... ソース電極

50

D ... ドレイン電極

G ... ゲート電極

【図1】

【図2】

---

フロントページの続き

F ターム(参考) 5F102 FA01 FA03 GB01 GC01 GD01 GJ05 GL05 GR04 GV06 GV07

GV08 HC01 HC07 HC16 HC18 HC19