前記トレンチの表面に形成されたゲート絶縁膜(8)と、

前記ゲート絶縁膜の表面に形成されたゲート電極(9)と、

前記IGBT部において前記第2導電型領域に電気的に接続されると共に、前記アノード領域に電気的に接続された上部電極(11)と、

前記IGBT部において前記コレクタ領域に電気的に接続されると共に、前記ダイオード部において前記カソード領域と電気的に接続された下部電極(12)と、を備え、

前記IGBT部のうち前記ダイオード部に隣接している部分にも、前記ホール注入低減層が形成され、

該ホール注入低減層は、前記ダイオード部から前記IGBT部の一部にのみはみ出して形成されていることを特徴とする半導体装置。

10

#### 【請求項2】

前記IGBT部には、前記トレンチにて複数に分けられた前記第2導電型領域のうち前記チャネル領域ではない部分によって前記エミッタ領域が形成されていない間引き部が構成されていることを特徴とする請求項1に記載の半導体装置。

#### 【請求項3】

前記間引き部において、前記トレンチの深さ方向において前記第2導電型領域を上下に分割する第1導電型のホールストップ層(30)が形成されていることを特徴とする請求項2に記載の半導体装置。

#### 【請求項4】

前記IGBT部には、前記トレンチにて複数に分けられた前記第2導電型領域のうち前記チャネル領域ではない部分によって前記エミッタ領域が形成されていない間引き部が構成されていると共に、該間引き部において、前記トレンチの深さ方向において前記第2導電型領域を上下に分割する第1導電型のホールストップ層(30)が形成されており、

前記ホールストップ層は、前記間引き部のうち前記ホール注入低減層が形成されている部分には形成されておらず、前記ホール注入低減層が形成されていない部分に形成されていることを特徴とする請求項1に記載の半導体装置。

20

#### 【請求項5】

前記ホール注入低減層は、前記トレンチの底部よりも浅く形成されていることを特徴とする請求項1ないし4のいずれか1つに記載の半導体装置。

30

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、絶縁ゲート型電界効果トランジスタ(以下、IGBTという)とフリーホイールダイオード(以下、単にダイオードという)とが共に1つの基板に形成された半導体装置に関するものである。

#### 【背景技術】

#### 【0002】

従来、例えば特許文献1において、インバータなどの回路に備えられるIGBTとダイオードとが並列して備えられた半導体装置が提案されている。この特許に示される半導体装置では、次のような手法によってライフタイム制御を行っている。

40

#### 【0003】

具体的には、半導体プロセスを経てIGBTおよびダイオードと共に1つの基板に形成したもの用意する。そして、基板表面側からIGBTおよびダイオードの形成位置にイオン注入を行うと共に、基板裏面側からダイオードの形成位置にイオン注入を行い、さらにアニール処理を行う。これにより、イオン注入が行われた部分に欠陥が形成され、ライフタイム制御を行うことが可能となる。

#### 【先行技術文献】

#### 【特許文献】

#### 【0004】

【特許文献1】特開2008-4866号公報

50

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

しかしながら、上記特許文献1に記載のライフタイム制御では、イオン注入が行われる位置にトレニチゲート構造を構成するトレニチが存在すると、トレニチ内壁面に形成されたゲート絶縁膜にイオン注入によるダメージを与えててしまう。このダメージは高温度でのアニール処理を行えば回復可能であるが、ライフタイム制御のために形成した欠陥が380以上アーニール処理で回復してしまうため、380以上のアーニール処理を行うことができない。

**【0006】**

これに対して、従来より、基板裏面側からIGBTおよびダイオードの形成位置の全域にイオン注入を行うことでライフタイム制御を行うことも一般的に行われている。しかしながら、このような手法では、IGBTとダイオードとが同時にライフタイム制御が行われることになり、IGBTとダイオードとのライフタイム制御を個別に最適化して行うことができない。特に、IGBTについては、ライフタイム制御を行うことによる特性劣化が懸念され、ライフタイム制御を最小限に抑える方が好ましい。

**【0007】**

本発明は上記点に鑑みて、ゲート絶縁膜にイオン注入によるダメージを与えることなく、かつ、ライフタイム制御を最小限、好ましくはライフタイム制御を行わなくても、IGBTとダイオードの特性を別々に最適化できる半導体装置およびその製造方法を提供することを目的とする。

**【課題を解決するための手段】****【0008】**

上記目的を達成するため、請求項1ないし5に記載の発明では、IGBTが形成されるIGBT部(100)とダイオードが形成されるダイオード部(200)とが1つの基板に備えられる半導体装置であって、ダイオード部において、ドリフト層(1)の上層部に、ダイオード部における第2導電型領域(5)により構成されるアノード領域(5b)よりも深くて低不純物濃度とされ、かつ、ドリフト層よりも高不純物濃度とされた第1導電型のホール注入低減層(20)を備え、IGBT部のうちダイオード部に隣接している部分にも、ホール注入低減層が形成され、該ホール注入低減層は、ダイオード部からIGBT部の一部にのみはみ出して形成されていることを特徴としている。

**【0009】**

このように、ダイオード部にホール注入低減層を備えている。このため、IGBT動作中にダイオード部を通じて注入されるホールを低減することが可能となる。これにより、スイッチング時のAC損失を低減することが可能となる。また、ホール注入低減層の不純物濃度に応じて、AC損失やAC損失とトレーードオフの関係となるDC損失について調整できる。したがって、ダイオード部にホール注入低減層を備えることによって、AC損失とDC損失を最適に設定できることから、IGBTとダイオードの特性を別々に最適化することが可能となる。

**【0010】**

なお、上記各手段の括弧内の符号は、後述する実施形態に記載の具体的手段との対応関係の一例を示すものである。

**【図面の簡単な説明】****【0011】**

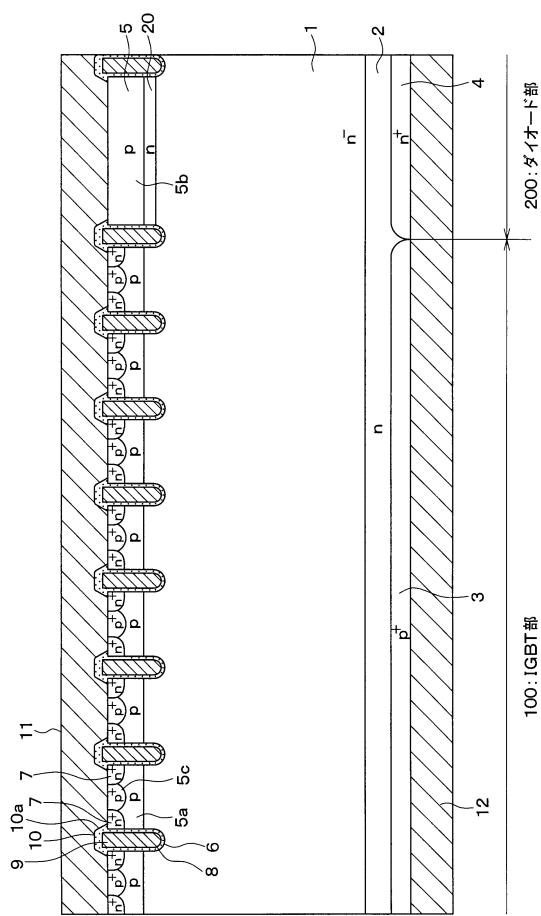

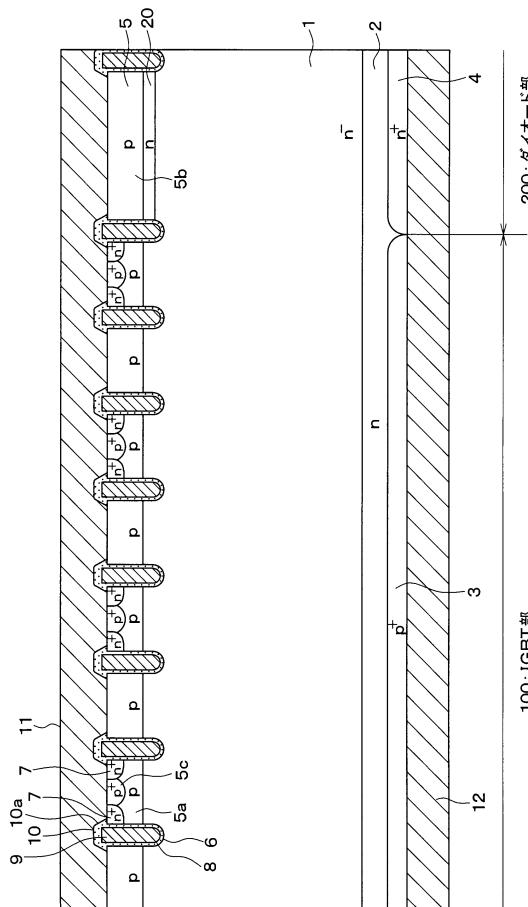

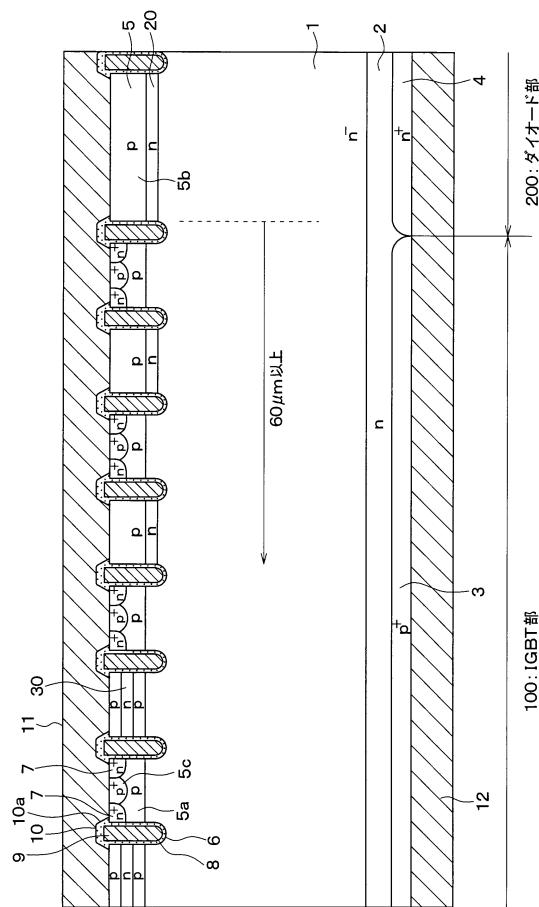

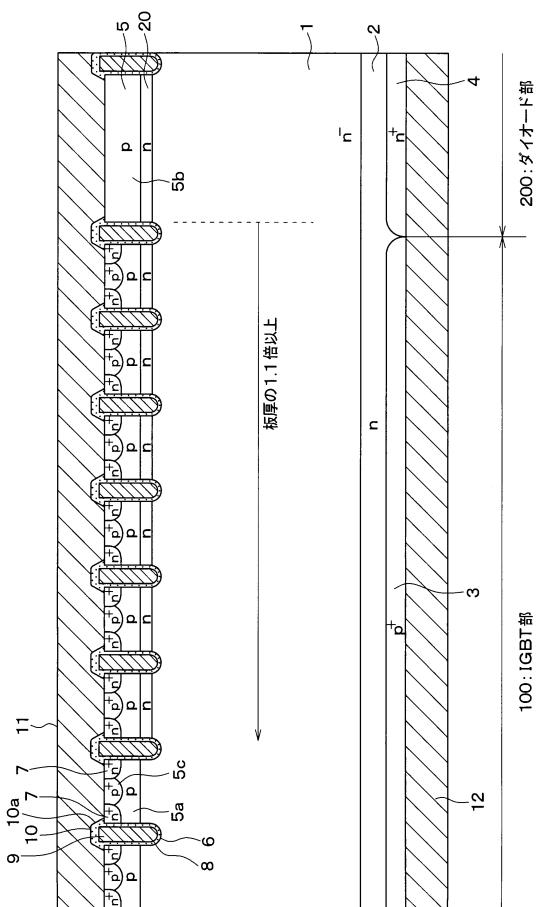

**【図1】**本発明の第1実施形態にかかるIGBTとダイオードを備えた半導体装置の断面図である。

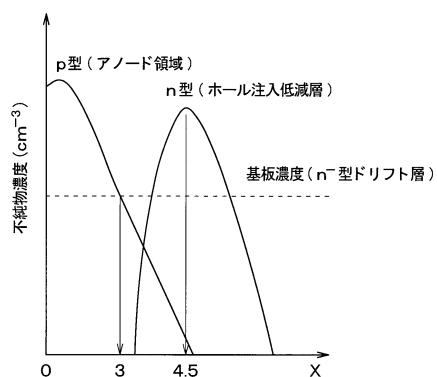

**【図2】**p型領域5とホール注入低減層20の不純物濃度分布を示した図である。

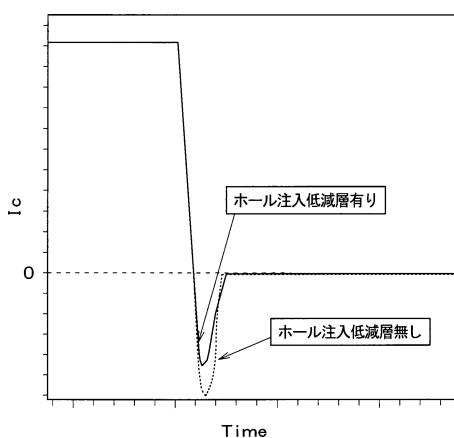

**【図3】**IGBTのオフ時にコレクタ電流Icの変化を測定した結果を示した図である。

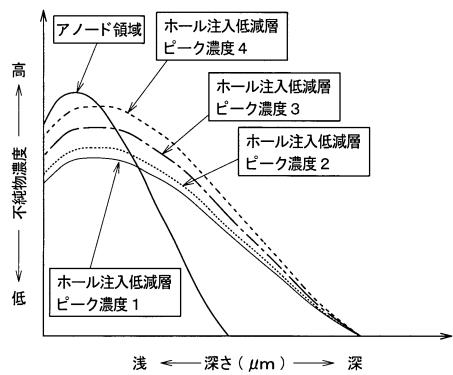

**【図4】**ホール注入低減層20の不純物濃度ピークを変化させたときの各濃度分布を示した図である。

10

20

30

40

50

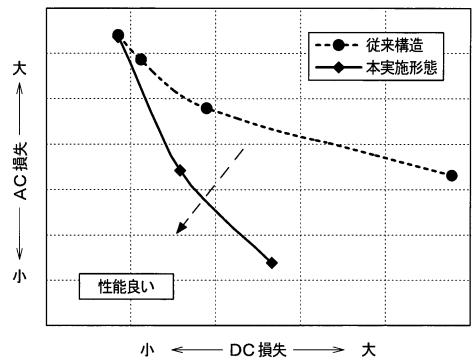

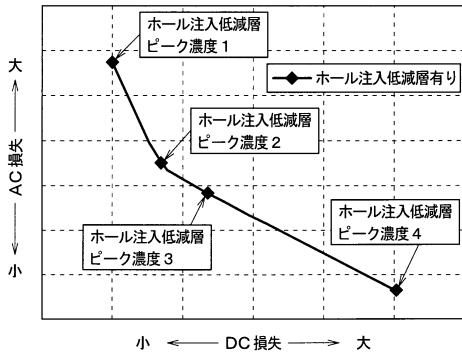

【図5】ホール注入低減層20の不純物濃度ピークを変化させたときのAC損失とDC損失について調べた結果を示す図である。

【図6】ホール注入低減層20が備えられた第1実施形態の構造と備えられていない従来構造それぞれについてAC損失とDC損失の関係について調べた結果を示す図である。

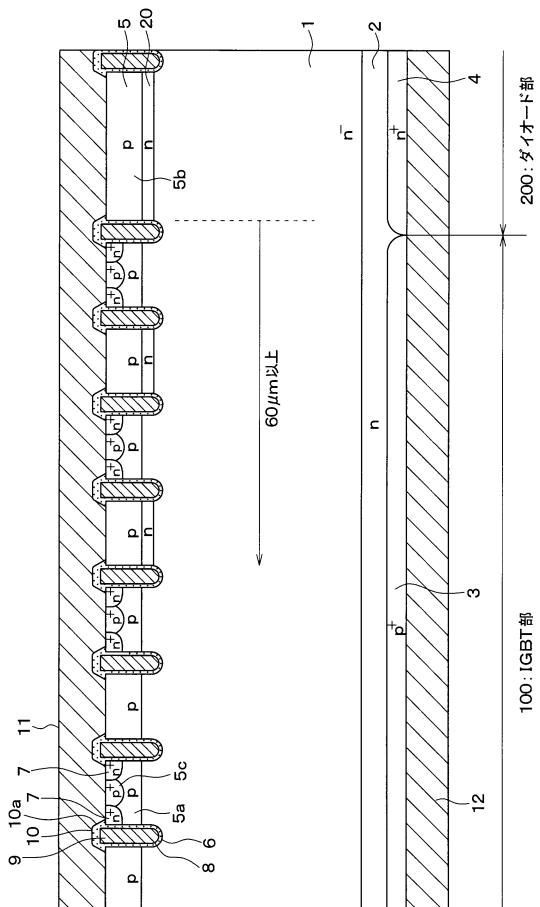

【図7】本発明の第2実施形態にかかるIGBTとダイオードを備えた半導体装置の断面図である。

【図8】本発明の第3実施形態にかかるIGBTとダイオードを備えた半導体装置の断面図である。

【図9】IGBT部100にホール注入低減層20を形成していない場合におけるホール分布を示す図である。 10

【図10】ホール注入低減層20のはみ出し量を変化させた場合のAC損失とDC損失とを調べた結果を示す図である。

【図11】ホール注入低減層20のはみ出し量を変化させた場合のダイオード部200での全損失を調べた結果を示す図である。

【図12】本発明の第4実施形態にかかるIGBTとダイオードを備えた半導体装置の断面図である。

【図13】本発明の第5実施形態にかかるIGBTとダイオードを備えた半導体装置の断面図である。

【図14】IGBT部100にホール注入低減層20を形成していない場合におけるホール分布とIGBT部100とダイオード部200のホール密度の比較結果を示した図である。 20

【図15】ボディp型領域5cの不純物濃度の変化に対するはみ出し量L1と板厚T1との比L1/T1の関係を示した図である。

【図16】板厚T1とホール拡散長との関係をボディp型領域5cの不純物濃度を変えて調べた結果を示す図である。

#### 【発明を実施するための形態】

##### 【0012】

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、同一符号を付して説明を行う。

##### 【0013】 30

###### (第1実施形態)

本発明の第1実施形態について説明する。図1に示すように、本実施形態にかかる半導体装置は、基板厚み方向に電流を流す縦型のIGBTとダイオードとが1つの基板に備えられることにより構成されている。具体的には、本実施形態にかかる半導体装置は以下のように構成されている。

##### 【0014】

図1に示されるように、本実施形態にかかる半導体装置は、IGBTが備えられるIGBT部100と、IGBT部100に沿って備えられ、ダイオードが形成されたダイオード部200とを有した構成とされている。これらIGBT部100やダイオード部200は、例えばチップの中央部のセル領域に形成されており、セル領域の外周、つまりチップの外縁部に図示しない外周耐圧部が配置されることにより、本実施形態にかかる半導体装置が構成されている。 40

##### 【0015】

IGBTおよびダイオードは、n<sup>-</sup>型ドリフト層1を構成する半導体基板を用いて形成されている。IGBT部100およびダイオード部200において、n<sup>-</sup>型ドリフト層1の裏面側におけるn<sup>-</sup>型ドリフト層1の表層部には、n型層によって構成されるフィールドストップ(以下、FSという)層2が形成されている。FS層2は、n<sup>-</sup>型ドリフト層1の裏面から比較的浅い所定深さの位置まで形成され、リン(P)などのn型不純物が注入されることで構成されている。FS層2の不純物濃度や拡散深さについては、要求されるIGBTやダイオードの特性に応じて設定されている。 50

## 【0016】

IGBT部100において、FS層2の表層部に、p<sup>+</sup>型不純物層にて構成されたコレクタ領域3が形成されている。コレクタ領域3は、ボロン等のp型不純物が注入されて形成されている。また、ダイオード部200において、FS層2の表層部に、n<sup>+</sup>型不純物層にて構成されたカソード領域4が形成されている。カソード領域4は、リン等のn型不純物が注入されて形成されている。これらコレクタ領域3やカソード領域4の不純物濃度や拡散深さについては、要求されるIGBTやダイオードの特性に応じて設定されている。

## 【0017】

さらに、IGBT部100およびダイオード部200の両方において、n<sup>-</sup>型ドリフト層1の表面側の表層部にp型領域5が形成されている。このp型領域5を貫通してn<sup>-</sup>型ドリフト層1まで達するように複数個のトレンチ6が形成されており、このトレンチ6によってp型領域5が複数個に分離されている。具体的には、トレンチ6は複数個所定のピッチ(間隔)で形成されており、図1の紙面垂直方向において各トレンチ6が平行に延設されたストライプ構造、もしくは並行に延設されたのちその先端部において引き回されることで環状構造とされている。環状構造とされる場合、例えば各トレンチ6が構成する環状構造は複数本ずつを1組として多重リング構造が構成される。

## 【0018】

トレンチ6によって複数に分割されたp型領域5のうち、IGBT部100に形成された部分は、チャネル領域を構成するチャネルp型領域5aとなる。このチャネルp型領域5aの表層部に、n<sup>+</sup>型不純物層にて構成されたエミッタ領域7が形成されている。

## 【0019】

p型領域5のうち、チャネルp型領域5aの表層部、具体的にはチャネルp型領域5a内の両側に配置されたエミッタ領域7の間に、チャネルp型領域5aのコンタクト部としても機能する高濃度なボディp型領域5cが形成されている。このため、IGBT部100ではp型領域5のp型不純物濃度の表面濃度が高濃度とされている。

## 【0020】

エミッタ領域7は、n<sup>-</sup>型ドリフト層1よりも高不純物濃度で構成され、p型領域5内において終端しており、かつ、トレンチ6の側面に接するように配置されている。より詳しくは、トレンチ6の長手方向に沿って棒状に延設され、トレンチ6の先端よりも内側で終端した構造とされている。

## 【0021】

トレンチ6は、p型領域5よりも深くされており、上述したように図1に示す断面において所定のピッチで配置されている。また、各トレンチ6内は、各トレンチ6の内壁表面を覆うように形成されたゲート絶縁膜8と、このゲート絶縁膜8の表面に形成されたドープトPolycrystalline Silicon等により構成されるゲート電極9とにより埋め込まれている。IGBT部100に形成されたゲート電極9は、図1とは別断面において互いに電気的に接続され、同電位のゲート電圧が印加されるようになっている。

## 【0022】

さらに、エミッタ領域7およびチャネルp型領域5aは、層間絶縁膜10に形成されたコンタクトホール10aを通じて、エミッタ電極を構成する上部電極11と電気的に接続されている。また、図示しないが、上部電極11や配線などを保護するようにパッシバーション膜が形成されている。そして、コレクタ領域3の裏面側にコレクタ電極を構成する下部電極12が形成されることにより、IGBTが構成されている。

## 【0023】

トレンチ6によって複数に分割されたp型領域5のうち、ダイオード部200に形成された部分は、アノード領域5bとされ、表層部が比較的高濃度とされることでコンタクト領域が構成されている。上記した上部電極11はダイオード部200にも延設されており、アノード領域5bにオーミック接続されることでアノード電極としても機能する。さらに、上記した下部電極12もダイオード部200まで延設されており、カソード領域4に

10

20

30

40

50

オーム接觸されられることでカソード電極としても機能する。このような構成により、ダイオードが構成されている。

#### 【0024】

そして、本実施形態では、上記のように構成されたダイオード部200にn型層にて構成されたホール注入低減層20が備えられている。ホール注入低減層20は、n<sup>-</sup>型ドリフト層1の上層部において、アノード領域5bからのホールの注入を低減させる役割を果たし、アノード領域5bよりも深く、かつ、トレンチ6の底部よりも浅い位置に形成されている。ホール注入低減層20の不純物濃度は、n<sup>-</sup>型ドリフト層1の不純物濃度よりも濃く、かつ、図2に示すように、不純物濃度ピーク値がアノード領域5bの不純物濃度ピーク値よりも低く設定されている。例えば、n<sup>-</sup>型ドリフト層1の不純物濃度が $7 \times 10^{11} \sim 8 \times 10^{14} \text{ cm}^{-3}$ 、ホール注入低減層20の不純物濃度が $1 \times 10^{16} \sim 1 \times 10^{17} \text{ cm}^{-3}$ 、アノード領域5bの不純物濃度が $1 \times 10^{17} \text{ cm}^{-3}$ 以上に設定される。ホール注入低減層20の厚みについては任意であるが、例えば1~2μmとされている。10

#### 【0025】

なお、本実施形態では、ホール注入低減層20の底部がトレンチ6の底部よりも浅くなる構成としたが、トレンチ6の底部よりも深くなる構成であっても構わない。

#### 【0026】

以上のようにして、本実施形態にかかるIGBTおよびダイオードを備えた半導体装置が構成されている。このように構成された半導体装置では、ダイオード部200にホール注入低減層20が備えられている。このため、IGBT動作中にダイオード部200を通じて注入されるホールを低減することが可能となる。これにより、IGBTのオフ時に引き抜かなければならないホール量を少なくすることが可能となって、図3に示すように、IGBTのオフ時にコレクタ電流Icが0になるときに、0を下回ってオーバーシュートするときの突き出し量が小さくなる。よって、スイッチング時のAC損失を低減することが可能となる。20

#### 【0027】

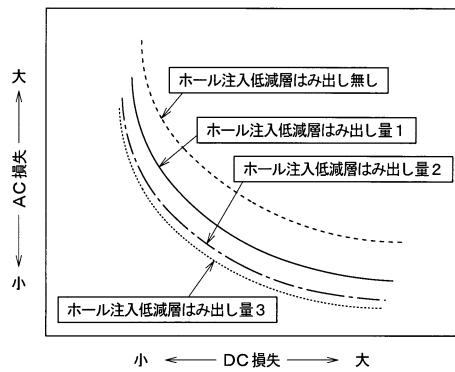

ホール注入量についてはホール注入低減層20の濃度を濃くすればするほど少なくなることから、ホール注入低減層20の不純物濃度ピークを高くすることで、よりAC損失を低減することが可能となる。ただし、スイッチング時のDC損失についてはAC損失とトレードオフの関係となっており、ホール注入低減層20の不純物濃度ピークが高くなるほど、DC損失が大きくなる。例えば、図4に示すように、ホール注入低減層20の不純物濃度ピークを4段階に変化させて、AC損失とDC損失の関係について調べたところ、図5に示す関係が得られた。30

#### 【0028】

このように、AC損失とDC損失にはトレードオフの関係が有り、これらをホール注入低減層20の不純物濃度ピークに応じて調整できる。このため、要求される仕様に応じてホール注入低減層20の不純物濃度ピークを設定すれば、AC損失とDC損失を最適に設定できる。そして、ダイオード部200にホール注入低減層20を備えることによって、AC損失とDC損失を最適に設定できることから、IGBTとダイオードの特性を別々に最適化することが可能となる。40

#### 【0029】

また、本実施形態のようにホール注入低減層20が備えられた構造と備えられていない従来構造それぞれについてAC損失とDC損失の関係について調べたところ、図6に示す結果が得られた。このように、本実施形態の構造の方が従来構造と比較してAC損失を同じ値とした場合のDC損失が改善されており、半導体装置の性能が向上できていることが判る。したがって、本実施形態のように、ホール注入低減層20を備えることにより、半導体装置の性能向上を図ることが可能となる。

#### 【0030】

続いて、このように構成される半導体装置の製造方法について説明する。ただし、本実施形態のような構造の半導体装置については、従来構造の半導体装置とほぼ同様の製造方50

法によって製造可能であるため、従来と異なる部分について主に説明する。

#### 【0031】

まず、 $n^-$ 型ドリフト層1を構成する半導体基板を用意したのち、ダイオード部200におけるホール注入低減層20の形成位置に $n$ 型不純物をイオン注入する。また、IGBT部100およびダイオード部200において、 $n^-$ 型ドリフト層1の表層部に $p$ 型領域5の形成のために $p$ 型不純物をイオン注入する。さらに、IGBT部100におけるボディ $p$ 型領域5cやエミッタ領域7の形成位置にそれぞれ $p$ 型不純物と $n$ 型不純物をイオン注入する。そして、アニール処理による熱拡散工程を行うことで、注入したイオンを熱拡散させ、ホール注入低減層20、 $p$ 型領域5、ボディ $p$ 型領域5cおよびエミッタ領域7を形成する。

10

#### 【0032】

次に、IGBT部100およびダイオード部200において、トレンチゲート構造の形成予定位置が開口するマスク(図示せず)を配置したのち、異方性エッチングを行うことでトレンチ6を形成する。その後、熱酸化によるゲート絶縁膜8の形成工程、ドープトボリシリコンの成膜およびパターニングによるゲート電極9の形成工程を行う。そして、層間絶縁膜10を形成した後、コンタクトホール10aの形成工程を行い、さらにA1などの電極材料をパターニングして上部電極11を形成する。これにより、基板表面側の製造工程が終了する。

#### 【0033】

続いて、 $n^-$ 型ドリフト層1を構成する半導体基板の裏面側を所望厚さとなるまで研削してから必要に応じてエッチングして表面平坦化を行する。その後、FS層2の形成のためのリンのイオン注入、コレクタ領域3の形成のためのボロンのイオン注入およびカソード領域4の形成のためのリンのイオン注入を行う。そして、レーザアニール等によって表面側に影響を与えない局所的な熱処理を行い、注入されたイオンの拡散工程を行う。更に、A1などの電極材料を成膜するなどの下部電極12の形成工程を行う。これにより、基板裏面側の製造工程が終了し、図1に示したIGBTおよびダイオードを備えた半導体装置が完成する。

20

#### 【0034】

このような製造方法においては、ホール注入低減層20を備えることによってダイオードの特性をIGBTの特性と切り離して個別に最適化できる。このため、上記の製造方法においては、トレンチゲート構造を形成してから基板表面側からライフタイム制御のためのイオン注入を行う必要がなくなる。したがって、ゲート絶縁膜8にイオン注入によるダメージを与えることなく、かつ、ライフタイム制御を最小限、好ましくはライフタイム制御を行わなくても、IGBTとダイオードの特性を別々に最適化することが可能となる。

30

#### 【0035】

##### (第2実施形態)

本発明の第2実施形態について説明する。本実施形態は、第1実施形態に対してIGBT部100の構成を変更したものであり、その他については第1実施形態と同様であるため、第1実施形態と異なる部分についてのみ説明する。

40

#### 【0036】

図7に示すように、本実施形態では、IGBT部100において、隣接するトレンチ6によって複数に分割された $p$ 型領域5の一部のみをチャネル $p$ 型領域5aとしている。つまり、 $p$ 型領域5の一部のみに $n^+$ 型不純物にて構成されたエミッタ領域7を形成している。このエミッタ領域7が形成された部分がチャネル $p$ 型領域5aとされることでIGBT動作させられるIGBT動作部となる。また、 $p$ 型領域5のうちのエミッタ領域7が形成されない残りの部分は間引き部となり、IGBT動作は行われないようになっている。

#### 【0037】

このように、IGBT部100の全域をIGBT動作部とせずに、部分的に間引き部が備えられた構成とされていても、ダイオード部200について第1実施形態と同様の構造

50

とすることができる。このような構成としても、第1実施形態と同様の効果を得ることができる。

#### 【0038】

##### (第3実施形態)

本発明の第3実施形態について説明する。本実施形態は、第1、第2実施形態に対してホール注入低減層20の形成位置を増加させたものであり、その他については第1、第2実施形態と同様であるため、第1、第2実施形態と異なる部分についてのみ説明する。なお、ここでは第2実施形態に対してホール注入低減層20の形成位置を増加させた場合について説明するが、第1実施形態に対しても同様の構成を適用できる。

#### 【0039】

図8に示すように、本実施形態では、第2実施形態と同様、p型領域5の一部が間引き部とされているのに加え、IGBT部100のうちダイオード部200の近傍に位置する部分にもホール注入低減層20を備えた構造としている。つまり、ホール注入低減層20をIGBT部100側にはみ出すように形成している。具体的には、IGBT部100のうち、ダイオード部200との境界位置から $60\mu m$ 以上の位置までホール注入低減層20を備えている。

#### 【0040】

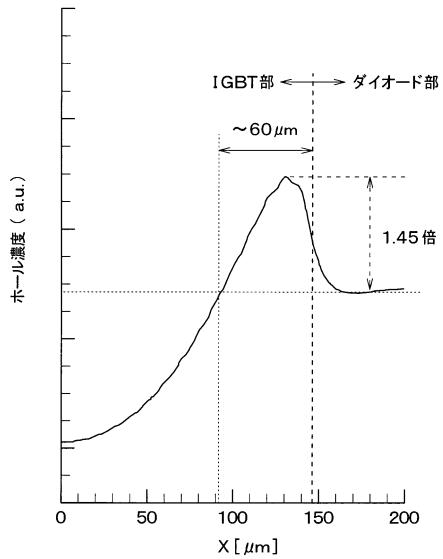

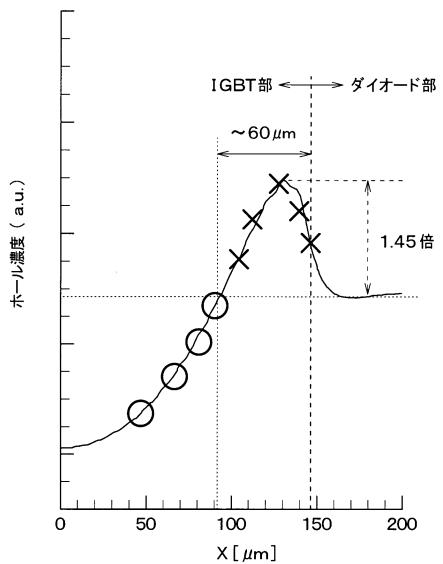

第1実施形態のようにIGBT部100にホール注入低減層20を形成していない場合におけるホール分布、すなわちp型領域5の表面から $10\mu m$ の深さでのホール濃度を調べると、図9に示される結果となった。ここで実験では、半導体基板の板厚、つまり各拡散層を形成する前の状態におけるn<sup>-</sup>型ドリフト層1の厚み(各拡散層の形成後におけるn<sup>-</sup>型ドリフト層1、コレクタ領域3、チャネルp型領域5a、エミッタ領域7のトータルの厚み)を $75\mu m$ とした。また、ボディp型領域5cの不純物濃度(ピーク値)を $3 \times 10^{15} c m^{-3}$ とした。この図より、IGBT部100の中でもダイオード部200の近傍に位置している部分においてホール密度が高まっていることが判る。

#### 【0041】

上記したように、ダイオード部200にホール注入低減層20を形成することによってIGBT動作中にダイオード部200を通じて注入されるホールを低減させ、スイッチング時のAC損失を低減させることが可能となる。しかしながら、実際にはIGBT部100から注入されるホールもAC損失に影響を与え、特にIGBT部100の中でもダイオード部200の近傍に位置する部分からのホール注入が大きな影響を与える。

#### 【0042】

このため、本実施形態では、ダイオード部200よりもホール密度が高くなっている部分、つまりIGBT部100のうち少なくともダイオード部200との境界位置から $60\mu m$ の位置までホール注入低減層20を形成している。これにより、IGBT部100から注入されるホールがAC損失に影響を与えることを抑制することが可能となり、よりAC損失の低減を図ることが可能となる。

#### 【0043】

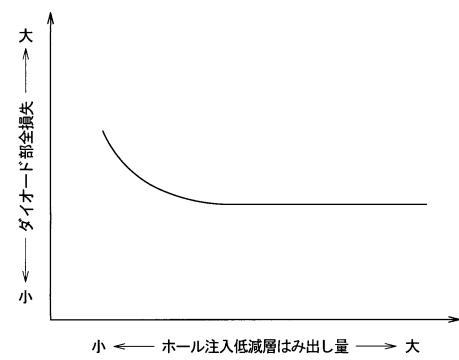

なお、参考として、ホール注入低減層20のはみ出し量を変化させた場合のAC損失とDC損失とを調べると共に、ダイオード部200での全損失を調べた。その結果、図10および図11に示す結果が得られた。図10に示す結果から、はみ出し量が大きくなる程(はみ出し量1<はみ出し量2<はみ出し量3)、性能向上が図っていた。ただし、図11に示すように、はみ出し量が一定量に至ると、ダイオード部200での全損失がほぼ一定値に収まっていた。このことから、ホール注入低減層20をIGBT部100の一部にはみ出すように形成することで、半導体装置の更なる性能向上を図ることが可能になると言える。

#### 【0044】

##### (第4実施形態)

本発明の第4実施形態について説明する。本実施形態は、第2、第3実施形態に対してホールストップ層を備えたものであり、その他については第2、第3実施形態と同様であ

10

20

30

40

50

るため、第2、第3実施形態と異なる部分についてのみ説明する。なお、ここでは第3実施形態に対してホールストップ層を形成した場合について説明するが、第2実施形態に対しても同様の構成を適用できる。

#### 【0045】

図12に示すように、本実施形態でも、第3実施形態と同様、p型領域5の一部を間引き部としているのに加え、IGBT部100のうちダイオード部200の近傍に位置する部分にホール注入低減層20を備えている。さらに、本実施形態では間引き部にホールストップ層30を備えている。

#### 【0046】

ホールストップ層30は、間引き部におけるp型領域5内に形成されており、n<sup>-</sup>型ドリフト層1に注入されたホールが間引き部におけるp型領域5を介して抜け出ることを抑制するためのn型層にて構成されている。ホールストップ層30は、トレンチ6の深さ方向において、間引き部におけるp型領域5を上下に分割するように形成されており、この上下に分割された各領域が電位的に分離された構成とされている。

#### 【0047】

このように、ホールストップ層30を備えた構造とすることもできる。その場合、IGBT部100のうちホール注入低減層20が備えられているダイオード部200の近傍の位置においては、図12に示すように、ホールストップ層30を形成していなくても構わない。

#### 【0048】

(第5実施形態)

本発明の第5実施形態について説明する。本実施形態は、第1～第4実施形態に対してIGBT部100側にはみ出させたホール注入低減層20の形成位置を具体的に特定したものであり、その他については第1～4実施形態と同様であるため、第1～第4実施形態と異なる部分についてのみ説明する。なお、ここでは第1実施形態に対してホール注入低減層20の形成位置を増加させた場合について説明するが、第2～第4実施形態に対しても同様の構成を適用できる。

#### 【0049】

図13に示すように、本実施形態も、第1実施形態と同様、IGBT部100において、各トレンチゲート構造の間のp型領域5の表層部にボディp型領域5cおよびエミッタ領域7が形成され、すべてがIGBT動作部とされている。このような構造において、IGBT部100のうちダイオード部200の近傍に位置する部分にもホール注入低減層20を備えた構造としている。つまり、ホール注入低減層20をIGBT部100にはみ出すように形成している。具体的には、ボディp型領域5cの不純物濃度(ピーク値)が $6 \times 10^{15} \text{ cm}^{-3}$ 以上とされている構造において、IGBT部100のうち、ダイオード部200との境界位置から半導体基板の板厚の1.1倍以上の距離の位置までホール注入低減層20を備えている。

#### 【0050】

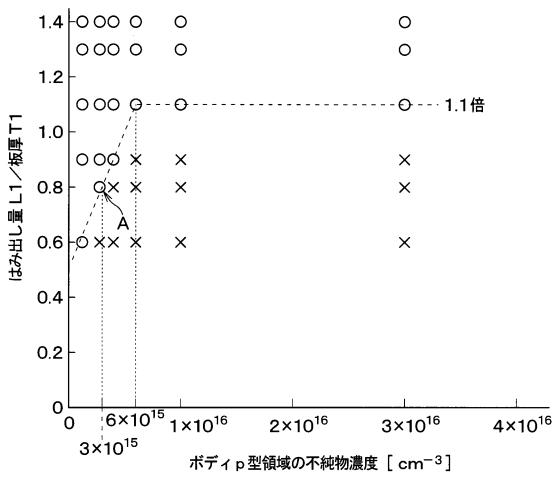

実験により、ホール注入低減層20の形成位置は、ボディp型領域5cの不純物濃度が薄いときには半導体基板の板厚とボディp型領域5cの不純物濃度に依存し、ボディp型領域5cの不純物濃度が濃くなると半導体基板の板厚に依存した値になることが確認された。具体的には、ホール注入低減層20を設けていない構造において、ボディp型領域5cの不純物濃度Paを変化させて、ホールがどの程度IGBT部100側にはみ出しか調べた。つまり、IGBT部100の方がダイオード部200よりもキャリア量が多くなる領域を調べ、その領域のIGBT部100とダイオード部200との境界位置からIGBT部100側へのみ出し量L1がどの程度になるかを調べた。ここでは、図1に示す構造のうちダイオード部200におけるカソード領域4を設けない構造を用いてシミュレーション解析を行い、ホール拡散幅を求めた。そして、図14に示すように、IGBT部100のうちダイオード部200よりもキャリア(ホール密度)が多くなる部分をX、キャリアが少なくなる部分を0として表して、不純物濃度Paの変化に対するみ出し量L

10

20

30

40

50

1と板厚T 1との比との関係を調べた。その結果、図15に示す関係となった。

#### 【0051】

この図に示されるように、ボディp型領域5cの不純物濃度が $6 \times 10^{15} \text{ cm}^{-3}$ 以下のときには、不純物濃度Paに対してIGBT部100とダイオード部200のキャリアの大小が切り替わるはみ出し量L1と板厚T1との比L1/T1が変化する。具体的には、不純物濃度Paが多くなるほど、IGBT部100の方がダイオード部200よりもキャリアが少なくなる比L1/T1の下限値が大きくなる。つまり、不純物濃度Paが多くなるに連れて、はみ出し量L1が大きくなないとIGBT部100のキャリアがダイオード部200のキャリアより少なくならない。

#### 【0052】

しかしながら、ボディp型領域5cの不純物濃度が $6 \times 10^{15} \text{ cm}^{-3}$ 以上になると、不純物濃度Paに対してIGBT部100とダイオード部200のキャリアの大小が切り替わるはみ出し量L1と板厚T1との比L1/T1が一定になる。具体的には、ボディp型領域5cの濃度にかかわらず、比L1/T1 = 1.1以上であれば、IGBT部100の方がダイオード部200よりもキャリアが少なくなる。

#### 【0053】

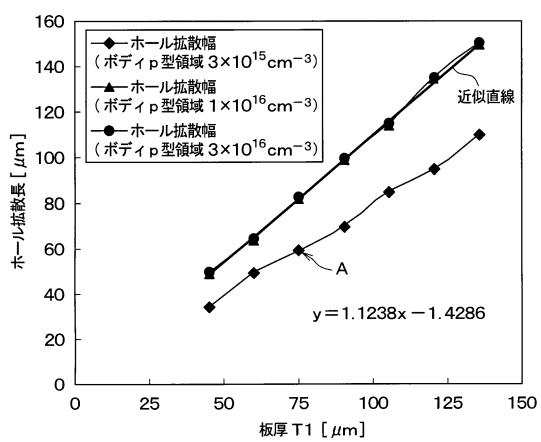

これは、ボディp型領域5cの不純物濃度が薄いときにはホールの拡散が小さくなるが、ある程度濃くなると半導体基板の板厚T1に依存してボディp型領域5cの不純物濃度に依らなくなるためである。図16に示すように、ボディp型領域5cの不純物濃度が $3 \times 10^{15} \text{ cm}^{-3}$ の際には、半導体基板の板厚T1の変化に伴ってホール拡散長が大きくなっているものの、板厚T1に対してホール拡散長が大きくなる割合は、正比例の関係から若干ずれる。これに対して、ボディp型領域5cの不純物濃度が $1 \times 10^{16} \text{ cm}^{-3}$ や $3 \times 10^{16} \text{ cm}^{-3}$ の際には、板厚T1に対してホール拡散長が大きくなる割合が正比例の関係となる。そして、いずれの濃度の場合でも、同じ近似直線（板厚をx、ホール拡散長をyとした場合に $y = 1.1238x - 1.4286$ の直線）で示される線形の関係となっている。これは、ボディp型領域5cの不純物濃度が濃くなると、ホールの拡散が飽和するためである。このため、ホール拡散長が板厚T1に依存することになる。

#### 【0054】

よって、本実施形態では、ボディp型領域5cの不純物濃度が $6 \times 10^{15} \text{ cm}^{-3}$ 以上とされている構造において、はみ出し量L1と半導体基板の板厚T1との比L1/T1が1.1倍以上となる関係を満たすようにホール注入低減層20のはみ出し量Lを設定している。つまり、少なくともホールのIGBT部100側へのはみ出し量L1の長さとなるように、ホール注入低減層20のはみ出し量Lを設定している。これにより、IGBT部100から注入されるホールがAC損失に影響を与えることを抑制することが可能となり、よりAC損失の低減を図ることが可能となる。

#### 【0055】

なお、第3実施形態では、半導体基板の板厚T1を $75 \mu\text{m}$ とし、ボディp型領域5cの不純物濃度を $3 \times 10^{15} \text{ cm}^{-3}$ としているが、これは、図16における点Aの場合に相当している。この条件は、ボディp型領域5cの不純物濃度が $6 \times 10^{15} \text{ cm}^{-3}$ 以下の場合に相当し、ホール注入低減層20のはみ出し量Lと板厚T1の比の関係が図15中の点Aとなればよい。点Aでは、ホール注入低減層20のはみ出し量Lと板厚T1の比L1/T1 = 0.8となっており、板厚T1 =  $75 \mu\text{m}$ のときであれば、ホール注入低減層20のはみ出し量L =  $60 \mu\text{m}$ あれば良いことが分かる。したがって、第3実施形態では、ホール注入低減層20のはみ出し量Lを $60 \mu\text{m}$ 以上としており、これによって上記効果を得ることを可能としている。

#### 【0056】

また、ここでは、ボディp型領域5cの不純物濃度が $6 \times 10^{15} \text{ cm}^{-3}$ 以上とされている構造において、ホール注入低減層20のはみ出し量Lと板厚T1の比が1.1倍以上となるようにした。これに対して、ボディp型領域5cの不純物濃度が $6 \times 10^{15} \text{ cm}^{-3}$ 以下とされる構造において、図15におけるボディp型領域5cの不純物濃度の変化に対す

10

20

30

40

50

る比  $L / T_1$  の関係を表す直線に基づいて、ホール注入低減層 20 のはみ出し量  $L$  を設定しても良い。具体的には、図 15において、ボディ p 型領域 5c の不純物濃度を  $x [1 \times 10^{15} \text{ cm}^{-3}]$  、はみ出し量  $L_1$  と板厚  $T_1$  との比  $L_1 / T_1$  を  $y$  とすると、 $y = 0.1x + 0.5$  の直線を示す関数式となる。したがって、ホール注入低減層 20 のはみ出し量  $L$  と板厚  $T_1$  との比  $L / T_1$  がこの関数式に示される  $y (= L_1 / T_1)$  以上となるように、 $L / T_1 - y = 0.1x + 0.5$  を満たすようにホール注入低減層 20 のはみ出し量  $L$  を設定すれば良い。

#### 【0057】

また、第 2 ~ 第 4 実施形態で示したような間引き部を有する構造においては、間引き部においてホールが低注入となることから、より IGBT 部 100 側の方がダイオード部 200 側よりもホール密度が低くなる。したがって、図 15 に示した関係よりもホール注入低減層 20 のはみ出し量  $L$  と板厚  $T_1$  との比  $L / T_1$  が低くても、IGBT 部 100 の方がダイオード部 200 よりもキャリアを低減できることになる。よって、本実施形態で説明したように、ボディ p 型領域 5c の不純物濃度が  $6 \times 10^{15} \text{ cm}^{-3}$  以上とされている構造において、ホール注入低減層 20 のはみ出し量  $L$  と板厚  $T_1$  の比が 1.1 倍以上となるようすれば、間引き部を有する構造であっても、上記効果が得られる。

#### 【0058】

##### (他の実施形態)

本発明は上記した実施形態に限定されるものではなく、特許請求の範囲に記載した範囲内において適宜変更が可能である。

#### 【0059】

例えば、上記実施形態においてホール注入低減層 20 を含む各部の不純物濃度や厚みの一例を挙げたが、ここに挙げた数値に限るものではなく、適宜変更可能である。つまり、ホール注入低減層 20 の不純物濃度について、n-型ドリフト層 1 の不純物濃度よりも濃く、かつ、不純物濃度ピーク値がアノード領域 5b の不純物濃度ピーク値よりも低く設定されれば良い。特に、ホール注入低減層 20 については、要求される AC 損失と DC 損失との設定に応じて適宜変更され得る。

#### 【0060】

また、上記実施形態では、IGBT 部 100 とダイオード部 200 のトレンチ 6 のピッチを変えているが、同じピッチであっても良い。また、IGBT 部 100 やダイオード部 200 内において、トレンチ 6 のピッチが一定である必要はなく、異なるピッチとされたものがあっても良い。

#### 【0061】

また、ダイオード部 200 にも IGBT 部 100 と同様に、アノード領域 5b とされる p 型領域 5 にエミッタ領域 7 やボディ p 型領域 5c が形成された構造とされていても良い。

#### 【0062】

また、上記各実施形態では、第 1 導電型を n 型、第 2 導電型を p 型とした n チャネルタイプの IGBT を備えた半導体装置を例に挙げて説明したが、各構成要素の導電型を反転させた p チャネルタイプの IGBT としても良い。

#### 【符号の説明】

#### 【0063】

- 1 n-型ドリフト層

- 3 コレクタ領域

- 4 カソード領域

- 5a チャネル p 型領域

- 5b アノード領域

- 6 トレンチ

- 7 エミッタ領域

- 9 ゲート電極

10

20

30

40

50

20 ホール注入低減層

30 ホールストッパ層

100 IGBT部

200 ダイオード部

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図14】

【図15】

【図16】

---

フロントページの続き

(51)Int.Cl.

F I

H 0 1 L 29/78 6 5 3 A

H 0 1 L 29/91 C

(56)参考文献 特開2010-118642(JP,A)

特開2007-134625(JP,A)

特開2008-053648(JP,A)

特開2013-021304(JP,A)

特開2011-216825(JP,A)

特開2008-192737(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 9 / 7 8

H 0 1 L 2 1 / 3 3 6

H 0 1 L 2 9 / 7 3 9

H 0 1 L 2 1 / 3 3 1

H 0 1 L 2 9 / 8 6 1 - 2 9 / 8 8 5

H 0 1 L 2 1 / 3 2 9

H 0 1 L 2 7 / 0 6 - 2 7 / 0 7