(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6497831号

(P6497831)

(45) 発行日 平成31年4月10日(2019.4.10)

(24) 登録日 平成31年3月22日(2019.3.22)

(51) Int.Cl.

F 1

|                        |              |     |

|------------------------|--------------|-----|

| GO6F 12/126 (2016.01)  | GO6F 12/126  | 100 |

| GO6F 12/0862 (2016.01) | GO6F 12/0862 |     |

| GO6F 12/0895 (2016.01) | GO6F 12/0895 | 112 |

| GO6F 12/0897 (2016.01) | GO6F 12/0897 | 105 |

請求項の数 20 (全 16 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2018-511588 (P2018-511588)  |

| (86) (22) 出願日 | 平成27年7月30日 (2015.7.30)        |

| (65) 公表番号     | 特表2018-519614 (P2018-519614A) |

| (43) 公表日      | 平成30年7月19日 (2018.7.19)        |

| (86) 國際出願番号   | PCT/US2015/042792             |

| (87) 國際公開番号   | W02016/182588                 |

| (87) 國際公開日    | 平成28年11月17日 (2016.11.17)      |

| 審査請求日         | 平成30年3月13日 (2018.3.13)        |

| (31) 優先権主張番号  | 14/710,837                    |

| (32) 優先日      | 平成27年5月13日 (2015.5.13)        |

| (33) 優先権主張国   | 米国 (US)                       |

| 早期審査対象出願      |                               |

|                                                                           |                                        |

|---------------------------------------------------------------------------|----------------------------------------|

| (73) 特許権者                                                                 | 318007085<br>アンペア・コンピューティング・エルエル<br>シー |

| アメリカ合衆国・カリフォルニア・950<br>54・サンタ・クララ・グレート・アメリ<br>カ・パークウェイ・4555・シックスス<br>・フロア |                                        |

| (74) 代理人                                                                  | 100108453<br>弁理士 村山 靖彦                 |

| (74) 代理人                                                                  | 100110364<br>弁理士 実広 信哉                 |

| (74) 代理人                                                                  | 100133400<br>弁理士 阿部 達彦                 |

最終頁に続く

(54) 【発明の名称】 追い出しを促すための先読みタグ

## (57) 【特許請求の範囲】

## 【請求項 1】

プロセッサ、共有キャッシュ、およびメインメモリを通信可能に結合するために構成される相互接続と、

データのセットを前記メインメモリから前記相互接続を介してプロセッサキャッシュに格納するために先読みするために構成されるプロセッサキャッシュプリフェッチャであって、前記プロセッサキャッシュは、前記プロセッサに関連付けられており、前記プロセッサキャッシュプリフェッチャは、データの第1の部分が、前記プロセッサにより使用されていない、前記プロセッサによる第1の将来使用の第1の確率を有する、及び前記プロセッサキャッシュから共有キャッシュに送信される、ことを示すために前記データのセットのデータの第1の部分に未使用データとタグを付け、データの第2の部分が、前記プロセッサにより使用されている、及び前記プロセッサキャッシュから前記メインメモリに送信される、ことを示すために前記データのセットに関連するデータの第2の部分に使用済みデータとタグを付け、前記第1の将来使用の前記第1の確率は、前記プロセッサが一定期間内に前記データの第1の部分を使用する確率に基づく、プロセッサキャッシュプリフェッチャと、

未使用データとしてタグ付けされた前記データの第1の部分に基づいて、前記データの第1の部分を前記プロセッサキャッシュから前記共有キャッシュに前記相互接続を介して追い出し、使用済みデータとしてタグ付けされた前記データの第2の部分に基づいて、前記データの第2の部分を前記プロセッサキャッシュから前記メインメモリに前記相互接続

を介して追い出すように構成されるプロセッサキャッシュエビクタとを備える、キャッシュ先読みシステム。

【請求項 2】

前記相互接続は、リング相互接続を備える、請求項1に記載のキャッシュ先読みシステム。

【請求項 3】

前記プロセッサキャッシュは、レベル2キャッシュを備え、前記共有キャッシュは、レベル3キャッシュを備える、請求項1に記載のキャッシュ先読みシステム。

【請求項 4】

前記データのセットは、前記プロセッサによって実行される第1のデータ、および前記第1のデータに関連付けられた第2のデータを含む、請求項1に記載のキャッシュ先読みシステム。

10

【請求項 5】

前記第2のデータは、前記第1のデータに関連する第1のアドレス空間が、前記メインメモリの前記第2のデータに関連する第2のアドレス空間に規定された近接内であることの決定に基づいて前記第1のデータに関連して決定される、請求項4に記載のキャッシュ先読みシステム。

【請求項 6】

前記プロセッサキャッシュプリフェッチャはさらに、前記プロセッサによる前記データの第1の部分の第1の将来使用の第1の確率を示す第1のタグで前記データの第1の部分をタグ付けし、前記プロセッサによる前記データの第2の部分の第2の将来使用の第2の確率を示す第2のタグで前記データの第2の部分をタグ付けするように構成される、請求項1に記載のキャッシュ先読みシステム。

20

【請求項 7】

前記プロセッサキャッシュプリフェッチャはさらに、前記プロセッサキャッシュ内で前記データのセットの少なくとも一部に関連するメモリ位置が特定しないことに応答して、前記プロセッサキャッシュに格納するために前記相互接続を介して前記メインメモリから前記データのセットを先読みするように構成されている、請求項1に記載のキャッシュ先読みシステム。

【請求項 8】

30

前記プロセッサキャッシュプリフェッチャはさらに、前記プロセッサが前記データの第1の部分を要求することに応答して、前記データの第1の部分を前記共有キャッシュから先読みするために構成される、請求項1に記載のキャッシュ先読みシステム。

【請求項 9】

前記共有キャッシュは、前記プロセッサを含む複数のプロセッサにより共有される、請求項1に記載のキャッシュ先読みシステム。

【請求項 10】

プロセッサと、

前記プロセッサによって実行されるときに動作の実施を容易にする実行可能命令を記憶するメモリと

を備え、前記動作が、

40

前記プロセッサに格納するために、システムメモリからデータのセットを先読みするステップと、

前記データのセットに格納するデータの第1の部分に、前記データの第1の部分が、前記プロセッサにより実行されるとともに前記プロセッサキャッシュから前記システムメモリに送信されるべき実行済みデータである、との第1の表示でタグ付けするステップと、

前記データの第2の部分が、前記プロセッサにより使用されておらず、一定期間内に前記プロセッサにより実行されると予想されることを決定することに基づいて、前記データのセットのデータの第2の部分に、第2の表示でタグ付けするステップであって、前記データの第2の部分は、前記一定期間内に前記プロセッサにより実行される所定の確率を有

50

すると決定される、ステップと、

前記データの第2の部分の前記タグ付けに基づいて、前記データの第2の部分を前記プロセッサキャッシュから共有キャッシュに追い出すステップと

を含む、キャッシュ先読みシステム。

【請求項 1 1】

前記動作はさらに、

前記第1の表示に基づいて、前記データの第1の部分を前記プロセッサキャッシュから前記システムメモリに追い出すステップ

を含む、請求項10に記載のキャッシュ先読みシステム。

【請求項 1 2】

前記動作はさらに、

前記データの第2の部分を実行するための要求を前記プロセッサから受け取ることに応答して、前記追い出されたデータの第2の部分を前記共有キャッシュから前記プロセッサキャッシュに先読みするステップ

を含む、請求項10に記載のキャッシュ先読みシステム。

【請求項 1 3】

前記プロセッサ、前記システムメモリ、および前記共有キャッシュは、リング相互接続を介して通信可能に結合される、請求項10に記載のキャッシュ先読みシステム。

【請求項 1 4】

前記共有キャッシュからデータを取り出すための第1のレイテンシは、前記システムメモリからデータを取り出すための第2のレイテンシ未満である、請求項10に記載のキャッシュ先読みシステム。

【請求項 1 5】

前記データの第1の部分がデータ要求において要求され、前記データの第2の部分は前記データ要求で要求されず、前記システムメモリ内の前記データの第1の部分と前記データの第2の部分との論理的近接度および物理的近接度に基づいて、前記データの第1の部分と前記データの第2の部分は、互いに関連していると決定され、前記データの第1の部分と前記データの第2の部分が互いに関連すると決定されることに基づいた前記データ要求に応答して、前記データの第1の部分および前記データの第2の部分が、前記プロセッサキャッシュに格納するために前記システムメモリから先読みされる、請求項10に記載のキャッシュ先読みシステム。

【請求項 1 6】

プロセッサキャッシュに格納するためにシステムメモリからデータのセットを先読みするステップであって、前記プロセッサキャッシュは、プロセッサに関連付けられている、ステップと、

前記データのセットに関連するデータの第1の部分に、前記データの第1の部分は、前記プロセッサにより使用されるとともに前記プロセッサキャッシュから前記システムメモリに通信されるべき使用済みデータであることを示す第1のインジケータでタグ付けするステップと、

前記データのセットのデータの第2の部分に、前記データの第2の部分は、未使用データであり、前記データの第2の部分が、前記プロセッサにより使用されておらず、一定期間内に前記プロセッサにより実行されると予想されることを決定することに基づいて、前記プロセッサキャッシュから共有キャッシュに通信されることを示す第2のインジケータでタグ付けするステップと、

前記データの第2の部分に前記第2のインジケータでタグ付けする前記ステップに基づいて、前記データの第2の部分を前記プロセッサキャッシュから前記共有キャッシュに追い出すステップと

を含む、キャッシング方法。

【請求項 1 7】

前記データの第1の部分に前記第1のインジケータでタグ付けする前記ステップに基づい

10

20

30

40

50

て、前記データの第1の部分を前記プロセッサキャッシュから前記システムメモリに追い出すステップ、

をさらに含む、請求項16に記載のキャッシング方法。

【請求項18】

前記データの第2の部分を実行するための要求を前記プロセッサから受け取ることに応答して、前記追い出されたデータの第2の部分を前記共有キャッシュから前記プロセッサキャッシュに先読みするステップ

をさらに含む、請求項16に記載のキャッシング方法。

【請求項19】

前記先読みするステップおよび前記追い出するステップは、前記プロセッサ、前記システムメモリ、および前記共有キャッシュを結合するリング相互接続を介している、請求項16

に記載のキャッシング方法。 10

【請求項20】

前記データの第1の部分に前記第1のインジケータでタグ付けする前記ステップを容易にするために、第1のインジケータビットを第1の値に設定するステップと、

前記データの第2の部分に前記第2のインジケータでタグ付けする前記ステップを容易にするために、第2のインジケータビットを第2の値に設定するステップと

をさらに含む、請求項16に記載のキャッシング方法。

【発明の詳細な説明】

【技術分野】

20

【0001】

この開示は、データをキャッシュにメインメモリから先読みすること(prefetching)、

およびキャッシュトラッシングを防止するためにデータを追い出すこと(evicting)に関する。

【背景技術】

【0002】

現代のマイクロプロセッサは、プログラムが記憶されるメモリよりもはるかに高速であり、それは、プログラム命令がメインメモリから読み出される場合、マイクロプロセッサをビジー状態に保つことができるほど高速にはその命令を読み出すことができないことを意味する。少量の非常に速いメモリであるキャッシュを各プロセッサに追加することは、必要とされる命令へのより速いアクセスを提供することによって処理時間を短縮することができる。 30

【0003】

先読みは、予想される命令が、プロセッサによって要求される前にキャッシュにロードされるプロセスである。現代のシステムは、各プロセッサ、またはプロセッサの各コアが、各コア/プロセッサに専用の1または2レベルのキャッシュ、およびコア/プロセッサの間で共有される1つまたは複数の追加のキャッシュレベルを有することもある、マルチキャッシュシステムに発展してきた。コア/プロセッサから離れた各連続レベルのキャッシュは、前のキャッシュレベルよりも大きいが、しかし遅いこともある。メインメモリからレベル1またはレベル2キャッシュなどのプロセッサキャッシュに先読みすることは、データへの低レイテンシアクセスを提供することができるが、しかしプロセッサキャッシュのサイズが小さいので、すぐに使用されないデータ、またはキャッシュのサイズよりも大きいデータセットは、リソースの競合および混乱(キャッシュトラッシング)を引き起こす可能性がある。 40

【発明の概要】

【課題を解決するための手段】

【0004】

一実施形態では、キャッシュ先読みシステムは、プロセッサ、共有キャッシュ、およびメインメモリを通信可能に結合するために構成される相互接続を備える。キャッシュ先読みシステムは、データのセットをメインメモリから相互接続を介してプロセッサキャッシュ

50

ユに先読みするために構成されるプロセッサキャッシュブリフェッチャを含むことができ、プロセッサキャッシュは、プロセッサに関連付けられており、プロセッサキャッシュは、そのデータのセットからのデータの第1の部分に未使用とタグを付け、そのデータのセットからのデータの第2の部分に使用済みとタグを付ける。キャッシュ先読みシステムは、データの第1の部分を共有キャッシュに相互接続を介して追い出し、データの第2の部分をメインメモリに相互接続を介して追い出すために構成されるプロセッサキャッシュエビクタを含むことができる。

#### 【0005】

別の実施形態では、キャッシュ先読みシステムは、プロセッサと、プロセッサによって実行されるときに動作の実施を容易にする実行可能命令を記憶するメモリとを含むことができる。動作は、システムメモリから、プロセッサに関連付けられたプロセッサキャッシュに、データのセットを先読みするステップと、そのデータのセットのデータの第1の部分に、データの第1の部分が実行されるデータであるとの表示でタグ付けするステップとを含むことができる。動作は、そのデータのセットのデータの第2の部分に、データの第2の部分が実行されるデータである可能性があるとの表示でタグ付けするステップと、データの第2の部分を共有キャッシュに追い出すステップとを含むことができる。

10

#### 【0006】

別の実施形態では、方法は、システムメモリから、プロセッサに関連付けられたプロセッサキャッシュに、データのセットを先読みするステップを含む。本方法は、そのデータのセットのデータの第1の部分に、データの第1の部分が使用されるデータであるとの表示でタグ付けするステップを含むことができる。本方法は、そのデータのセットのデータの第2の部分に、データの第2の部分が未使用データであるとの表示でタグ付けするステップを含むことができる。本方法は、データの第2の部分を共有キャッシュに追い出すステップを含むことができる。

20

#### 【図面の簡単な説明】

#### 【0007】

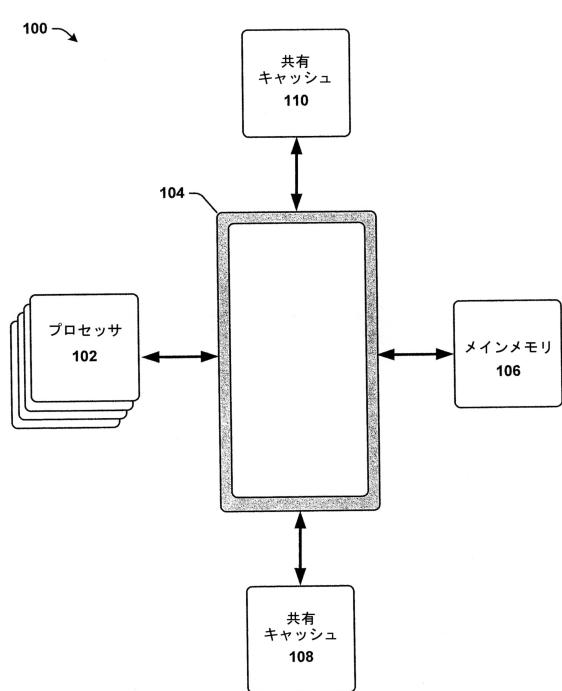

【図1】リングアーキテクチャ相互接続を用いて先読みするためのシステムの一実施形態を例示するブロック図である。

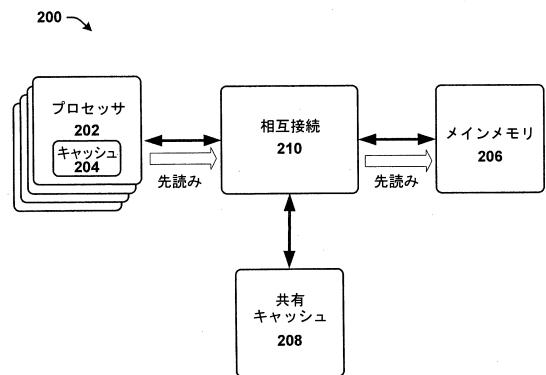

【図2】先読みシステムの一実施形態を例示するブロック図である。

30

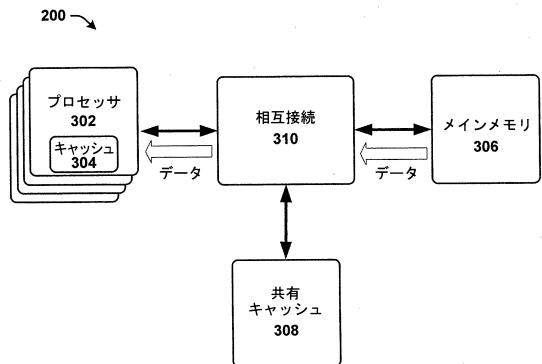

【図3】先読みシステムの一実施形態を例示するブロック図である。

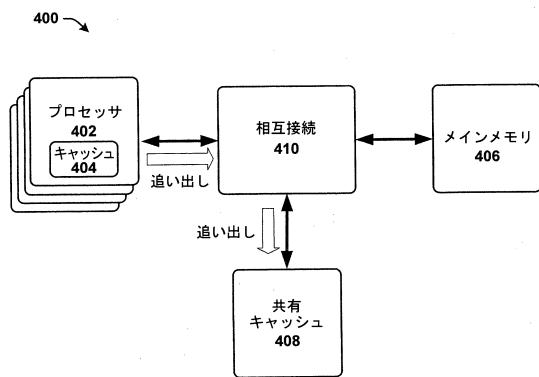

【図4】先読みシステムの一実施形態を例示するブロック図である。

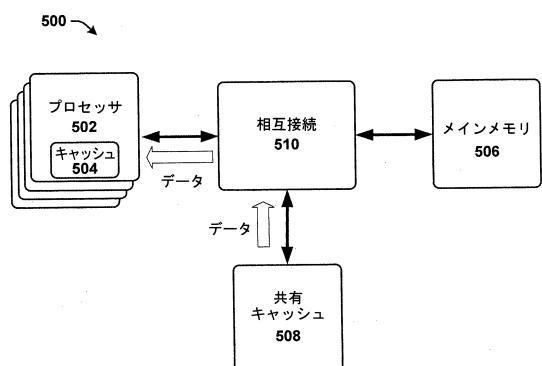

【図5】先読みシステムの一実施形態を例示するブロック図である。

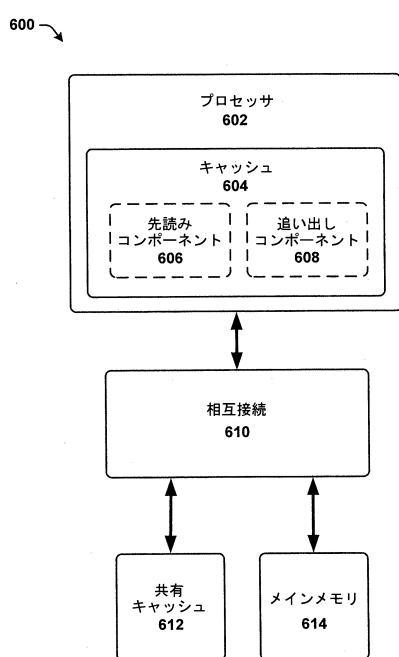

【図6】キャッシュトラッシングを防止するためにデータを追い出す先読みキャッシュシステムを有するプロセッサの一実施形態を例示するブロック図である。

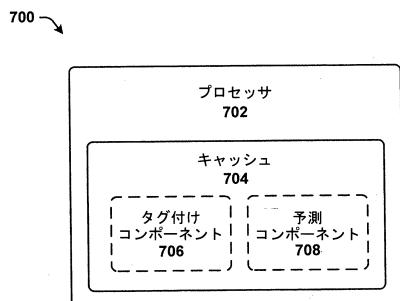

【図7】キャッシュトラッシングを防止するためにデータを追い出す先読みキャッシュシステムを有するプロセッサの一実施形態を例示するブロック図である。

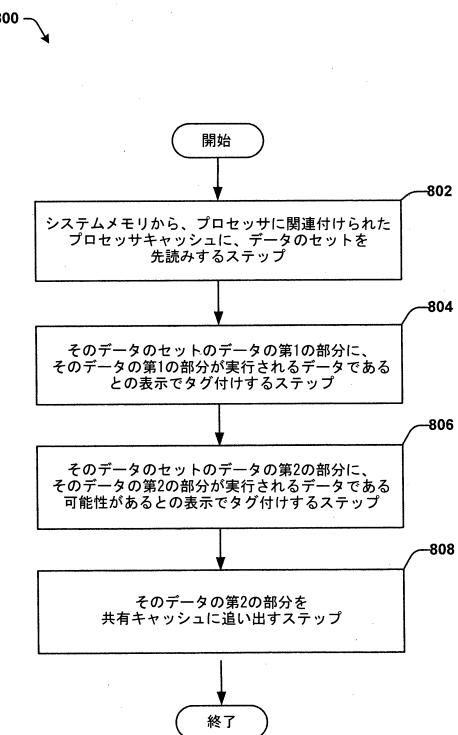

【図8】キャッシュトラッシングを防止するために未使用データを先読みし、追い出すための方法の一実施形態の流れ図を例示する図である。

【図9】例示的な電子コンピューティング環境のブロック図を例示する図である。

【図10】例示的なデータ通信ネットワークのブロック図を例示する図である。

40

#### 【発明を実施するための形態】

#### 【0008】

様々な実施形態は、データをメインメモリからキャッシュに先読みし、次いで未使用データをより低いレベルのキャッシュに追い出すシステムを提供する。先読みシステムは、データをメインメモリからキャッシュに先読みし、すぐに使用できないまたはキャッシュに入れるには大きすぎるデータセットの一部であるデータは、より低いレベルのキャッシュに追い出すためのタグを付けられてもよく、それは、データがメインメモリから再びロードされなければならない場合よりも短いレイテンシでデータを利用可能な状態に保つ。これは、あまりに先んじて使用可能なデータを先読みするコストを低くし、キャッシュトラッシングを防止する。

50

## 【0009】

より遅いメモリ(DDR、ディスク)からのロードは、性質が空間的かつ時間的である傾向があるので、データは、それが使用され得るよりも十分に前に先読みされてもよい。関連データは、プロセッサによって要求されているデータの物理的または論理的に近くに位置することもあるので、先読みは、ロードの空間的性質を利用する。したがって、アドレスの流れについて、メモリアドレスAへのロードのすぐ後に、メモリアドレスA+Nへのロードが続くことになる可能性が高く、ただしNは、どんな任意の整数であってもよく、したがってロードは、アドレスA+N\*mへとストライドで(in strides)行われ、ただし $m$ は、別の任意の符号付き整数である。

## 【0010】

関連データならびに現在要求されるデータを先読みすることによって、メインメモリまたは記憶装置からのデータのさらなるローディングは、回避することができる。レベル2キャッシュなどのプロセッサレベルキャッシュは、あまり大きくないので、データは、実行の次の順番でない限り、またはもうすぐ処理されることにならない限り、そこに記憶されるべきでない。したがって、すぐ次の順番でないデータは、未使用データとタグを付けられてもよく、レベル3キャッシュなどのより低いレベルのキャッシュに追い出されてもよい。レベル3キャッシュは、レベル2キャッシュよりも遅いこともあるが、しかしそれは、はるかにより大きくすることができ、後になって使用されることもあるデータをより実行可能に保有することができる。レベル3キャッシュに追い出されたデータが、次いでプロセッサによって必要とされるとき、レベル2キャッシュは、メインメモリからデータを先読みするよりもはるかに速くそのデータをレベル3キャッシュから先読みすることができる。

10

## 【0011】

図1は、リングアーキテクチャ相互接続を用いて先読みするためのシステム100の実施形態を例示するプロック図である。プロセッサ102は、1つまたは複数のコアを含むことができる(図1では4コアを有して示される)。プロセッサ102はまた、プロセッサレベルキャッシュ、またはプロセッサ102の各コアに関連付けられたキャッシュを含むこともできる。このキャッシュは、いくつかの実施形態ではレベル2キャッシュとすることができる。プロセッサ102はまた、リング相互接続104を介して1つまたは複数の共有キャッシュ108および110、ならびにメインメモリ106に通信可能に結合されてもよい。リング相互接続104などのリング相互接続を有するシステムでは、共有キャッシュ108および110は、各プロセッサに直接結び付けられることなく、1つまたは複数のプロセッサ(例えば、プロセッサ102、その他)の間で共有されてもよい。共有キャッシュ、いくつかの実施形態ではレベル3キャッシュは、したがって多重コアおよび/またはプロセッサの間で分散されてもよい。

20

## 【0012】

一実施形態では、プロセッサ102は、プロセッサ102内の各コア、またはコアの対について、プロセッサレベルキャッシュ、またはレベル2キャッシュを含むことができる。プロセッサ102によって実行されるデータは、レベル2キャッシュからレベル1キャッシュに、さらにはプロセッサ102に関連付けられたレジスタに直接に読み出されてよい。プロセッサ102上のプロセッサレベルキャッシュが、プロセッサ102が実行のために必要とすることになるデータを有することを確実にし、プロセッサがキャッシュ内のメモリ位置を見いだせないキャッシュミスを回避するために、プロセッサキャッシュは、データをメインメモリ106からリング相互接続104を介して先読みすることができる。予測ヒューリスティックスを使用すると、プロセッサキャッシュ内のプリフェッチャは、上で述べられたA+N\*mアルゴリズムを使用してどのデータが次に使用される可能性があるかを予測し、プロセッサ102が、データを必要とするときに、データが、利用可能であるように、データをプロセッサキャッシュにプリロードすることができる。

30

## 【0013】

関連データは、要求されるデータに物理的もしくは論理的に近いか、またはアドレス空間において関連している可能性があることがあるので、関連データは、後になってプロセ

40

50

ツサによって要求されることもあるため、要求されるデータに加えて先読みされてもよい。もしデータセットが、プロセッサ上のレベル2キャッシュにとって大きすぎる、または所定の期間内に使用されないこともあるならば、レベル2キャッシュは、そのデータに「先読みだけ」または「未使用」とマークを付けることができ、それは、データを共有キャッシュ108または110に追い出すことを促すことになる。完全に関係のないこともあるデータは、追い出されてメインメモリ106に戻されてもよいが、しかもしデータがおそらくは、近い将来に、または所定の期間内に使用されることもあるならば、データは、共有キャッシュ108または110に追い出されるべきかどうかに基づいて、インジケータビットをオンまたはオフに設定することによってタグを付けられてもよい。一実施形態では、データは、プロセッサによる将来使用の確率の表示に基づいてタグを付けられてもよい。将来使用の確率に基づいて、レベル3キャッシュ、または共有キャッシュ108もしくは110は、メインメモリ106に追い出す前に所定の長さの時間にわたってデータを保持することができる。同様に、もし所定の期間内での将来使用の確率が、非常に高いならば、プロセッサキャッシュは、データに追い出しのためのタグを付けなくてもよい。

#### 【0014】

そのデータが、後になってプロセッサによって要求されるとき、データを共有キャッシュ108または110から取り戻すためのレイテンシは、データをメインメモリ106から取り戻すレイテンシよりもはるかに短いことになる。

#### 【0015】

レベル2およびレベル3のキャッシュに言及されたけれども、先読みされたデータに階層的により低いキャッシュシステムへの追い出しのためのタグを付ける先読みシステムを述べる本明細書での概念は、他の実施形態において適用されてもよいことを認識すべきである。例えば、データは、レベル1キャッシュに先読みされ、次いでレベル2キャッシュに追い出されてもよく、他の実施形態では、レベル3および4のキャッシュ、またはそれらの様々な組み合わせが、使用されてもよい。

#### 【0016】

図2は、先読みシステム200の実施形態例を示すブロック図を例示する。プロセッサ202は、1つまたは複数のコアを含むことができる(図2では4つのコアを有して示される)。プロセッサ202はまた、プロセッサレベルキャッシュ204も含むことができ、いくつかの実施形態では、各コアは、キャッシュ204に似たキャッシュを含むことができる。キャッシュ204は、いくつかの実施形態ではレベル2キャッシュとすることができます。プロセッサ202はまた、相互接続210に通信可能に結合され、相互接続210を介して共有キャッシュ208およびメインメモリ206に通信可能に結合されてもよい。一実施形態では、共有キャッシュ208は、各プロセッサに直接結び付けられることなく、1つもしくは複数のプロセッサ(例えば、プロセッサ202、その他)および/またはコアの間で共有されてもよい。共有キャッシュ208、いくつかの実施形態ではレベル3キャッシュは、したがって多重コアおよび/またはプロセッサの間で分散されてもよい。

#### 【0017】

プロセッサ202によって実行されるデータは、レベル2キャッシュからレベル1キャッシュに、さらにはプロセッサ202に関連付けられたレジスタに直接に読み出されてもよい。プロセッサ202上のプロセッサレベルキャッシュ204が、プロセッサ202が実行のために必要とすることになるデータを有することを確実にし、プロセッサがキャッシュ内にメモリ位置を見いだせないキャッシュミスを回避するために、プロセッサキャッシュは、データをメインメモリ206から相互接続210を介して先読みすることができる。予測ヒューリスティックスを使用すると、プロセッサキャッシュ内のプリフェッチャは、上で述べられたA+N\*mアルゴリズムを使用してどのデータが次に使用される可能性があるかを予測し、プロセッサ202が、データを必要とするときに、データが、利用可能であるように、データをプロセッサキャッシュ204にプリロードするための要求をメインメモリ206に相互接続210を介して送ることができる。

10

20

30

40

50

## 【0018】

図3は、先読みシステム300の一実施形態のブロック図を例示する。プロセッサ302およびキャッシュ304内のプリフェッチャが、メインメモリ306からプリロードされるべきデータを要求した後、データは、メインメモリ306からプロセッサ302およびキャッシュ304に相互接続310を介して送られてもよい。いくつかの実施形態では、データは、共有キャッシュ308(レベル3キャッシュ)を飛ばして、レベル2キャッシュ304に直接先読みされてもよく、他の実施形態では、データは、最初に共有キャッシュ308に先読みされ、次いで共有キャッシュ308からキャッシュ304に先読みされてもよい。キャッシュ304によって先読みされるデータは、プロセッサ302によって要求されているデータならびに要求されているデータに関連することもある他のデータとすることができる。関連データは、アドレス空間において関連する、または要求されるデータの物理的または論理的に近くに位置するデータとすることができる、すべてのおそらく関連するデータを先読みすることは、多重動作において、要求されるデータを先読みすることよりもより効率的とすることができる。10

## 【0019】

図4は、先読みシステム400の一実施形態の別のブロック図を例示する。プロセッサ402およびキャッシュ404が、一組の関連データをメインメモリ406から先読みした後、キャッシュ404は、データの一部分を共有キャッシュ408に相互接続410を介して追い出すことができる。関連データは、要求されるデータに物理的もしくは論理的に近いか、またはアドレス空間において関連する可能性があることもあるので、関連データは、後になってプロセッサによって要求されることもあってから、要求されるデータに加えて先読みされてもよい。もしデータセットが、プロセッサ402上のキャッシュ404にとって大きすぎる、または所定の期間内に使用されないこともあるならば、キャッシュ404は、そのデータに「先読みだけ」または「未使用」とマークを付けることができ、それは、データを共有キャッシュ408に追い出すことを促すことになる。完全に関係のないこともあるデータは、追い出されてメインメモリ406に戻されてもよいが、しかしもしデータがおそらくは、近い将来に、または所定の期間内に使用されることもあるならば、データは、共有キャッシュ408への追い出しのためのタグを付けられてもよい。データは、共有キャッシュ408に追い出されるべきかどうかに基づいて、インジケータビットをオンまたはオフに設定することによってタグを付けられてもよい。一実施形態では、データは、プロセッサ402による将来使用の確率の表示に基づいてタグを付けられてもよい。将来使用の確率に基づいて、レベル3キャッシュ、または共有キャッシュ408は、メインメモリ406に追い出す前に所定の長さの時間にわたってデータを保持することができる。同様に、もし所定の期間内での将来使用の確率が、非常に高いまたは所定の確率を上回るならば、プロセッサキャッシュ404は、データに追い出しのためのタグを付けなくてもよい。20

## 【0020】

図5は、先読みシステム500の一実施形態のブロック図を例示する。タグを付けられたデータが、共有キャッシュ508に追い出された後、もしプロセッサ502が、追い出されたデータを要求する、またはキャッシュ504上のプリフェッチャが、プロセッサ502がすぐに関連データを処理する/実行することになると決定するならば、データは、共有キャッシュ508から相互接続510を介して取り戻されてもよい。一実施形態では、もしデータが、すでに追い出されてメインメモリ506に戻っているならば、キャッシュ504は、データをメインメモリ506から相互接続510を介してロードすることができる。30

## 【0021】

図6は、キャッシュトラッシングを防止するためにデータを追い出す先読みキャッシュシステム600を有するプロセッサの一実施形態を例示するブロック図を例示する。プロセッサ602は、1つまたは複数のコアおよびキャッシュ604を含むことができる。いくつかの実施形態では、各コア、またはコアの対は、対応するキャッシュを有してもよい。いくつかの実施形態では、キャッシュ604は、レベル2キャッシュとすることができる。プロセッサ602はまた、共有キャッシュ612、およびメインメモリ614(DDR、ディスク、その他)に相互接続610を介して通信可能に結合されてもよい。相互接続610などのリング相互接続を有40

するシステムでは、共有キャッシュ612は、各プロセッサに直接結び付けられることなく、1つまたは複数のプロセッサ(例えば、プロセッサ602、その他)の間で共有されてもよい。共有キャッシュ612、いくつかの実施形態ではレベル3キャッシュは、したがって多重コアおよび/またはプロセッサの間で分散されてもよい。

【0022】

一実施形態では、キャッシュ604は、先読みコンポーネント606(プリフェッチャ)および追い出しコンポーネント608(エビクタ)を含むことができる。先読みコンポーネントは、データのセットをメインメモリ614から相互接続610を介してキャッシュ604に先読みするように構成されてもよく、プロセッサキャッシュ604は、プロセッサ602に関連付けられている。先読みコンポーネント606は、そのデータのセットからのデータの第1の部分に未使用とタグを付け、そのデータのセットからのデータの第2の部分に使用済みとタグを付けることができる。10

【0023】

追い出しコンポーネント608は、データの第1の部分を共有キャッシュ612に相互接続610を介して追い出し、データの第2の部分をメインメモリ614に相互接続610を介して追い出すように構成されてもよい。

【0024】

図7は、キャッシュトラッシングを防止するためにデータを追い出す先読みキャッシュシステム700を有するプロセッサの一実施形態のブロック図を例示する。プロセッサ702は、タグ付けコンポーネント706および予測コンポーネント708を有するキャッシュ704を含むことができる。タグ付けコンポーネント706は、データが、未使用である、または将来に使用される可能性があることを示すためにキャッシュ704によって先読みされるデータにタグを付けることができる。20

【0025】

プロセッサ要求データに関連するデータは、要求されるデータに物理的もしくは論理的に近いか、またはアドレス空間において関連している可能性があることもあるので、関連データは、後になってプロセッサ702によって要求されることもあってから、要求されるデータに加えて先読みされてもよい。もしデータセットが、プロセッサ上のキャッシュ704にとって大きすぎる、または所定の期間内に使用されないこともあるならば、キャッシュ704は、そのデータに「先読みだけ」または「未使用」とタグを付けることができ、それは、データをレベル3キャッシュまたはより低いレベルのキャッシュに追い出すことを促すことになる。完全に関係のないこともあるデータは、追い出されてメインメモリに戻されてもよいが、しかしもしデータがおそらくは、近い将来に、または所定の期間内に使用されることもあるならば、データは、共有キャッシュへの追い出しのためのタグを付けられてもよい。データは、共有キャッシュに追い出されるべきかどうかに基づいて、インジケータビットをオンまたはオフに設定することによってタグ付けコンポーネント706によってタグを付けられてもよい。一実施形態では、データは、プロセッサによる将来使用の確率の表示に基づいてタグを付けられてもよい。予測コンポーネント708は、データが所定期間内にプロセッサ702によって使用されることになる可能性を決定することができ、将来使用の確率に基づいて、レベル3キャッシュ、または共有キャッシュは、メインメモリに追い出す前に所定の長さの時間にわたってデータを保持することができる。タグ付けコンポーネント706はまた、将来使用の相対的または絶対的確率を示すデータにインジケータを設定することもできる。30

【0026】

上で述べられた例示的なシステムを考慮すると、述べられる主題に従って実施されてもよい方法は、図8の流れ図を参照してより良く認識されてもよい。本方法は、一連のブロックとして示され、述べられるが、いくつかのブロックは、本明細書で描かれるものと異なる順番でかつ/または他のブロックと同時に生じてもよいので、特許請求される主題は、ブロックの順番によって限定されない。すべての例示されるブロックが、以下で述べられる方法を実施するために必要とされることもあるとは限らない。40

**【 0 0 2 7 】**

図8は、キャッシュトラッシングを防止するために未使用データを先読みし、追い出すための方法の一実施形態の流れ図である。手順800は、802から始めることができ、そこでは本方法は、システムメモリから、プロセッサに関連付けられたプロセッサキャッシュに、データのセットを先読みするステップを含む。先読みするステップは、いくつかの実施形態ではレベル2キャッシュとすることができますプロセッサキャッシュ内のプリフェッチャによって行われてもよい。先読みするステップは、プロセッサによって指示されるメモリアドレスにおけるデータだけでなく、要求されるデータに関連するメモリアドレスにおけるデータもまたロードする。予測ヒューリスティックスを使用すると、プリフェッチャは、どのデータが将来に使用される可能性があるかを予測することができ、それは、同様のアドレス空間内のデータ、または要求されるデータに物理的もしくは論理的に近いデータを含むことができる。この関連データは、プロセッサによるデータへのより速いアクセスを可能にするためにキャッシュにプリロードされてもよい。

10

**【 0 0 2 8 】**

804において、本方法は、そのデータのセットのデータの第1の部分にデータの第1の部分が使用されるデータであるとの表示でタグ付けするステップを含むことができる。もしデータが、プロセッサによって使用され、かつそれが、近い将来に再び使用される可能性がないならば、データは、メインメモリまたはディスクに追い出して戻すためのタグを付けられてもよい。同様に、806において、本方法は、そのデータのセットのデータの第2の部分にデータの第2の部分が実行されるデータである可能性があるとの表示でタグ付けするステップを含むことができ、808において、本方法は、データの第2の部分を共有キャッシュに追い出すステップを含む。すぐに使用されないが、しかし近い将来に使用されることもあるデータは、共有キャッシュ(例えば、レベル3キャッシュ)に送られてもよい。この共有キャッシュは、メインメモリからよりも迅速なデータへのアクセスを提供し、それを追い出すことで、プロセッサにおけるキャッシュ(レベル2キャッシュ)が追い出されたデータよりも早急にまたはすぐに使用されることもあるデータを保有することを可能にする。

20

**【 0 0 2 9 】**

本明細書で述べられる技法は、キャッシュトラッシングを回避するために先読みするステップおよび追い出すステップの実行を容易にすることが望ましい、任意のデバイスに適用されてもよい。ハンドヘルド、携帯および他のコンピューティングデバイスならびにすべての種類のコンピューティングオブジェクトは、様々な実施形態に関連して、すなわち、デバイスが、コンピューティングリソースを複数のゲストデバイスまたは仮想マシンと共有することを望むこともあるどこかで使用するために熟考される。それに応じて、図9において以下で述べられる以下の汎用リモートコンピュータは、一例であり、開示される主題は、ネットワーク/バス相互運用および相互作用を有する任意のクライアントを用いて実施されてもよい。したがって、開示される主題は、ほんの少しのまたは最小限のクライアントリソースしか関与していないネットワーク化ホスト型サービスの環境、例えば、クライアントデバイスが単に、電化製品内に置かれたオブジェクトなどの、ネットワーク/バスへのインターフェースとしての役割を果たすだけのネットワーク化環境において実施されてもよい。

30

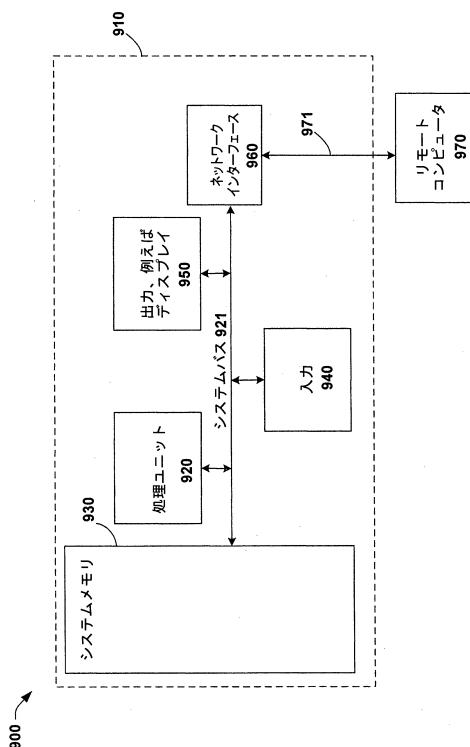

**【 0 0 3 0 】**

図9は、開示される主題のいくつかの態様が、実施されてもよい、コンピューティングシステム環境900の例を示すが、コンピューティングシステム環境900は、デバイスのためのコンピューティング環境の一例である。

**【 0 0 3 1 】**

図9は、開示される主題を実施するための例示的なデバイスであり、コンピュータ910の形の汎用コンピューティングデバイスを含む。コンピュータ910のコンポーネントは、処理ユニット920、システムメモリ930、およびシステムメモリを含む様々なシステムコンポーネントを処理ユニット920に結合するシステムバス921を含んでもよい。

40

50

**【 0 0 3 2 】**

コンピュータ910は、いろいろなコンピュータ可読媒体を含む。コンピュータ可読媒体は、コンピュータ910によってアクセス可能な任意の利用可能な媒体とすることができます。システムメモリ930は、読み出し専用メモリ(ROM)および/またはランダムアクセスメモリ(RAM)などの揮発性および/または不揮発性メモリの形のコンピュータ記憶媒体を含んでもよい。

**【 0 0 3 3 】**

コンピュータ910は、リモートコンピュータ970などの1つまたは複数の他のリモートコンピュータへの論理接続を使用してネットワーク化または分散型環境において動作することができ、それらは次に、デバイス910と異なる媒体能力を有することができます。図9に描かれる論理接続は、ローカルエリアネットワーク(LAN)または広域ネットワーク(WAN)などのネットワーク971を含むが、しかしながら有線かまたは無線の他のネットワーク/バスも含むことができる。LANネットワーキング環境において使用されるとき、コンピュータ910は、ネットワークインターフェースまたはアダプタを通じてLAN971に接続されてもよい。WANネットワーキング環境において使用されるとき、コンピュータ910は典型的には、モデムなどの通信コンポーネント、またはインターネットなどの、WANを通じて通信を確立するための他の手段を含むことができる。

10

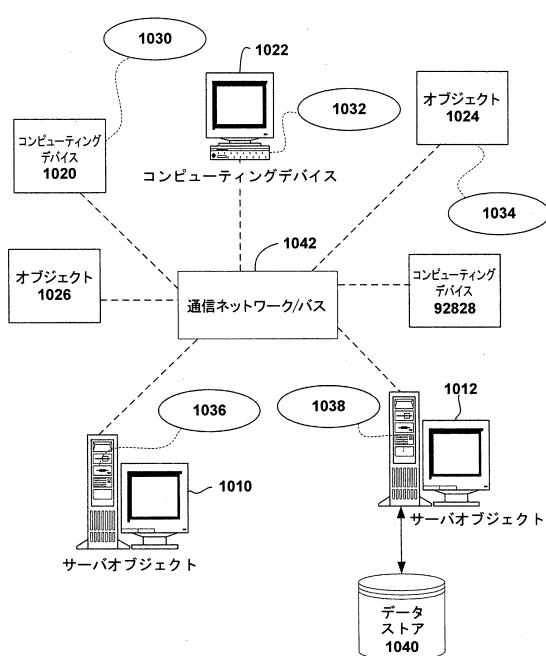

**【 0 0 3 4 】**

図10は、例示的なネットワーク化または分散型コンピューティング環境の概略図である。分散型コンピューティング環境は、コンピューティングオブジェクト1010、1012、その他、およびコンピューティングオブジェクトまたはデバイス1020、1022、1024、1026、1028、その他を備え、それらは、アプリケーション1030、1032、1034、1036、1038およびデータストア1040によって表されるなどの、プログラム、方法、データストア、プログラマブル論理、その他を含んでもよい。

20

**【 0 0 3 5 】**

各コンピューティングオブジェクト1010、1012、その他、およびコンピューティングオブジェクトまたはデバイス1020、1022、1024、1026、1028、その他は、1つまたは複数の他のコンピューティングオブジェクト1010、1012、その他、およびコンピューティングオブジェクトまたはデバイス1020、1022、1024、1026、1028、その他と通信ネットワーク1042を通じて通信することができる。通信ネットワーク1042は、サービスを図10のシステムに提供する他のコンピューティングオブジェクトおよびコンピューティングデバイスを備えててもよく、かつ/または多重相互接続ネットワークを表してもよい。クライアント/サーバ、ピアツーピア、またはハイブリッドアーキテクチャなどの、ネットワーキングプロトコルおよびネットワーク基盤のホストが、利用されてもよい。クライアント/サーバアーキテクチャ、特にネットワーク化システムでは、クライアントは通常、別のコンピュータ、例えばサーバによって提供される共有ネットワークリソースにアクセスするコンピュータである。

30

**【 0 0 3 6 】**

メモリから実行されるプロセスおよびプロセッサの両方は、コンポーネントとすることができます。別の例として、アーキテクチャは、電子ハードウェアの配置(例えば、並列または直列トランジスタ)、処理命令およびプロセッサを含むことができ、それらは、電子ハードウェアの配置に適した仕方で処理命令を実施する。

40

**【 0 0 3 7 】**

開示される主題は、開示される主題を実施するように電子デバイスを制御するためにハードウェア、ファームウェア、ソフトウェア、またはそれらの任意の適切な組み合わせを作成するための典型的な製造、プログラミングまたはエンジニアリング技法を使用する製造の方法、装置、または物品として実施されてもよい。コンピュータ可読媒体は、ハードウェア媒体、ソフトウェア媒体、非一時的媒体、または搬送媒体を含むことができる。

**【 符号の説明 】****【 0 0 3 8 】**

50

|     |                          |    |

|-----|--------------------------|----|

| 100 | 先読みするためのシステム             |    |

| 102 | プロセッサ                    |    |

| 104 | リング相互接続                  |    |

| 106 | メインメモリ                   |    |

| 108 | 共有キャッシュ                  |    |

| 110 | 共有キャッシュ                  |    |

| 200 | 先読みシステム                  |    |

| 202 | プロセッサ                    |    |

| 204 | プロセッサレベルキャッシュ、プロセッサキャッシュ | 10 |

| 206 | メインメモリ                   |    |

| 208 | 共有キャッシュ                  |    |

| 210 | 相互接続                     |    |

| 300 | 先読みシステム                  |    |

| 302 | プロセッサ                    |    |

| 304 | キャッシュ                    |    |

| 306 | メインメモリ                   |    |

| 308 | 共有キャッシュ                  |    |

| 310 | 相互接続                     |    |

| 400 | 先読みシステム                  |    |

| 402 | プロセッサ                    | 20 |

| 404 | キャッシュ                    |    |

| 406 | メインメモリ                   |    |

| 408 | 共有キャッシュ                  |    |

| 410 | 相互接続                     |    |

| 500 | 先読みシステム                  |    |

| 502 | プロセッサ                    |    |

| 504 | キャッシュ                    |    |

| 506 | メインメモリ                   |    |

| 508 | 共有キャッシュ                  |    |

| 510 | 相互接続                     | 30 |

| 600 | 先読みキャッシュシステム             |    |

| 602 | プロセッサ                    |    |

| 604 | キャッシュ                    |    |

| 606 | 先読みコンポーネント               |    |

| 608 | 追い出しコンポーネント              |    |

| 610 | 相互接続                     |    |

| 612 | 共有キャッシュ                  |    |

| 614 | メインメモリ                   |    |

| 700 | 先読みキャッシュシステム             |    |

| 702 | プロセッサ                    | 40 |

| 704 | キャッシュ                    |    |

| 706 | タグ付けコンポーネント              |    |

| 708 | 予測コンポーネント                |    |

| 800 | 手順                       |    |

| 900 | コンピューティングシステム環境          |    |

| 910 | コンピュータ、デバイス              |    |

| 920 | 処理ユニット                   |    |

| 921 | システムバス                   |    |

| 930 | システムメモリ                  |    |

| 970 | リモートコンピュータ               | 50 |

|      |                        |    |

|------|------------------------|----|

| 971  | ネットワーク、LAN             |    |

| 1010 | コンピューティングオブジェクト        |    |

| 1012 | コンピューティングオブジェクト        |    |

| 1020 | コンピューティングオブジェクトまたはデバイス |    |

| 1022 | コンピューティングオブジェクトまたはデバイス |    |

| 1024 | コンピューティングオブジェクトまたはデバイス |    |

| 1026 | コンピューティングオブジェクトまたはデバイス |    |

| 1028 | コンピューティングオブジェクトまたはデバイス |    |

| 1030 | アプリケーション               |    |

| 1032 | アプリケーション               | 10 |

| 1034 | アプリケーション               |    |

| 1036 | アプリケーション               |    |

| 1038 | アプリケーション               |    |

| 1040 | データストア                 |    |

| 1042 | 通信ネットワーク               |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 キエル・スヴェンドセン

アメリカ合衆国・カリフォルニア・94086・サニーヴェール・マングローヴ・アヴェニュー・

905

審査官 後藤 彰

(56)参考文献 特開2014-115851(JP, A)

特表2013-542511(JP, A)

国際公開第2005/091146(WO, A1)

特開平10-320285(JP, A)

米国特許出願公開第2014/0181402(US, A1)

米国特許出願公開第2011/0113199(US, A1)

(58)調査した分野(Int.Cl., DB名)

G06F 12/126

G06F 12/0862

G06F 12/0895

G06F 12/0897