(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 697 21 381 T2 2004.01.15

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 0 811 931 B1

(51) Int Cl.<sup>7</sup>: G06F 13/40

(21) Deutsches Aktenzeichen: 697 21 381.1

(96) Europäisches Aktenzeichen: 97 303 797.1

(96) Europäischer Anmeldetag: 04.06.1997

(97) Erstveröffentlichung durch das EPA: 10.12.1997

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 02.05.2003

(47) Veröffentlichungstag im Patentblatt: 15.01.2004

(30) Unionspriorität:

**658602** 05.06.1996 US

(84) Benannte Vertragsstaaten:

**DE, FR, GB, IT**

(73) Patentinhaber:

**Compaq Computer Corp., Houston, Tex., US**

(72) Erfinder:

**Culley, Paul R., Cypress, US; Goodrum, Alan L., Tomball, Texas 77375, US; Chow, Raymond Y. L., Cypress, Texas 77429, US; Basile, Barry S., Houston, Texas 77084, US**

(74) Vertreter:

**Grünecker, Kinkeldey, Stockmair & Schwanhäusser, 80538 München**

(54) Bezeichnung: **Einsetzen und Entfernen einer Erweiterungskarte**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

- [0001] Die Erfindung bezieht sich auf ein Einsetzen und Entfernen von Erweiterungskarten.

- [0002] Computersysteme besitzen typischerweise Erweiterungskarten-Steckplätze bzw. -Schlitze zum Aufnehmen und elektrischen Verbinden von Erweiterungskarten mit einem Erweiterungsbus des Computersystems. Der Erweiterungsbus kann einer von verschiedenen Typen sein, wie beispielsweise ein Industry Standard Architecture (ISA) Bus, ein Extended Industry Standard Architecture (EISA) Bus oder ein Peripheral Component Interconnect (PCI) Bus.

- [0003] Die EP-A-0 254 456 offenbart eine elektrische Schaltungsleiterplatte, die elektrisch mit einem Bus verbunden ist, entfernbare von dem System und wieder einsetzbar in das System, ohne die Notwendigkeit, andere Schaltungen, verbunden mit dem Bus, zu sperren.

- [0004] IBM Technical Disclosure Bulletin Vol. 29 No. 7 offenbart eine Schaltung, um zu ermöglichen, dass eine Datenkassette in ein Betriebsterminal eingesetzt oder davon entfernt werden kann, ohne die Operation des Terminals zu unterbrechen.

- [0005] Gemäß der vorliegenden Erfindung wird ein Verfahren zur Verwendung in einem Computersystem geschaffen, das eine zentrale Verarbeitungseinheit besitzt, wobei das Verfahren aufweist: Verwenden einer Klemme, um selektiv ein Entfernen einer Schaltungskarte von einem Verbinder zu verhindern, wobei der Verbinder so konfiguriert ist, um die Schaltungskarte aufzunehmen und elektrisch die Schaltungskarte mit der zentralen Verarbeitungseinheit zu verbinden; Überwachen des Eingriffszustands der Klemme; und Zuführen einer Anzeige bzw. Indikation über den Eingriffszustand zu der zentralen Verarbeitungseinheit; und Zuführen einer Unterbrechungs-Anforderung zu der zentralen Verarbeitungseinheit, um anzuzeigen, wenn sich der Eingriffszustand ändert; und gekennzeichnet durch Trennen einer Takteleitung und von anderen Leitungen des Busses, wobei die anderen Leitungen des Busses getrennt werden, bevor die Takteleitung getrennt wird und die Energie weggenommen wird.

- [0006] Vorzugsweise weist das Verfahren weiterhin ein Speichern des Eingriffszustands in einem Speicher, auf den durch die zentrale Verarbeitungseinheit zugreifbar ist, auf.

- [0007] Vorzugsweise weist das Verfahren weiterhin ein Überwachen eines Energie-Zustand-Signals des Verbinder; und Zuführen einer Indikation bzw. Anzeige über das Energie-Zustand-Signal zu der zentralen Verarbeitungseinheit auf.

- [0008] Vorzugsweise wird Energie zu dem Verbinder, wenn die Klemme in Eingriff ist, zugeführt, und Energie wird von dem Verbinder weggenommen, wenn die Klemme nicht in Eingriff ist.

- [0009] Vorzugsweise weist das Verfahren weiterhin ein Bestimmen auf, ob die zentrale Verarbeitungseinheit den Verbinder freigegeben hat, um Energie aufzunehmen, und wobei der Schritt eines Zuführens Energie nur dann zuführt, wenn die zentrale Verarbeitungseinheit den Verbinder freigegeben hat, um Energie aufzunehmen.

- [0010] Vorzugsweise umfasst ein Verbinden der zentralen Verarbeitungseinheit ein elektrisches Verbinden eines Busses mit dem Verbinder, wenn die Klemme in Eingriff ist; und ein elektrisches Isolieren der zentralen Verarbeitungseinheit umfasst ein elektrisches Isolieren des Busses gegen den Verbinder, wenn die Klemme nicht in Eingriff ist.

- [0011] Vorzugsweise umfasst ein elektrisches Verbinden ein Verbinden einer Takteleitung und von anderen Leitungen des Busses, wobei die anderen Leitungen des Busses verbunden werden, nachdem die Energie zugeführt ist und die Takteleitung verbunden ist.

- [0012] Vorzugsweise besitzt das Computersystem einen Schalter, betätigt durch die Klemme, was eine Anzeige der Position des Schalters liefert, und wobei das Verfahren vorzugsweise weiterhin aufweist: Aktualisieren des Eingriffszustands bzw. -status , wenn die Anzeige dieselbe Position für eine vorbestimmte Dauer anzeigt.

- [0013] Weiterhin wird gemäß der vorliegenden Erfindung ein System geschaffen, das aufweist: eine zentrale Verarbeitungseinheit; einen Verbinder zum Aufnehmen einer Schaltungskarte, wobei der Verbinder eine Mehrzahl von externen Verbindungen besitzt; eine Klemme, konfiguriert so, um selektiv ein Entfernen der Schaltungskarte von dem Verbinder, wenn die Klemme in Eingriff ist, zu verhindern; und eine Schaltung, verbunden so, um den Eingriffsstatus der Klemme zu überwachen, und um eine Zufuhr von Energie zu dem Verbinder basierend auf dem Eingriffsstatus der Klemme zu regulieren; und dadurch gekennzeichnet, dass die Schaltung zum Isolieren des Busses Einrichtungen zum Trennen einer Takteleitung und von anderen Leitungen des Busses umfasst, wobei die anderen Leitungen des Busses getrennt werden, bevor die Takteleitung getrennt ist und die Energie entfernt ist.

- [0014] Die Schaltung umfasst vorzugsweise: einen Schalter, betätigt durch die Klemme, was eine Anzeige über die Position des Schalters liefert; und eine Schaltung, verbunden so, um den Eingriffsstatus zu aktualisieren, wenn die Anzeige dieselbe Position für eine vorbestimmte Dauer anzeigt.

- [0015] Die Schaltung kann vorzugsweise so konfiguriert sein, um eine Unterbrechungsanforderung zu der zentralen Verarbeitungseinheit zuzuführen, um anzuzeigen, wenn sich der Eingriffszustand ändert. Sie kann

auch einen Puffer umfassen, zugreifbar durch die zentrale Verarbeitungseinheit, verbunden so, um die Anzeige über den Eingriffszustand zu speichern.

[0016] Vorzugsweise überwacht die Schaltung ein Energie-Status-Signal bzw. -Zustands-Signal des Verbinder und liefert eine Anzeige des Energie-Status-Signals zu der zentralen Verarbeitungseinheit.

[0017] Weiterhin weist das Computersystem eine Schaltung auf, die auf die Schaltung anspricht, verbunden so, um den Eingriffszustand der Klemme zu überwachen, verbunden so, um Energie zu dem Verbinder zuzuführen, wenn die Klemme in Eingriff ist, und so, um Energie von dem Verbinder wegzunehmen, wenn die Klemme nicht in Eingriff ist.

[0018] Die zentrale Verarbeitungseinheit kann selektiv den Verbinder freigeben, um Energie aufzunehmen, und wobei das Computersystem weiterhin aufweisen kann: einen Puffer, verbunden so, um anzuzeigen, wenn die zentrale Verarbeitungseinheit den Verbinder freigegeben hat, um Energie aufzunehmen, und wobei die Schaltung, verbunden so, um nur Energie zuzuführen, Energie dann zuführt, wenn die zentrale Verarbeitungseinheit den Verbinder freigegeben hat, um Energie aufzunehmen.

[0019] Das Computersystem kann weiterhin einen Bus, vorzugsweise einen PCI-Bus, und eine Schaltung, die auf die Schaltung zum Überwachen anspricht, zum Verbinden des Busses mit dem Verbinder, wenn die Klemme in Eingriff ist, und zum elektrischen Isolieren des Busses gegen den Verbinder, wenn die Klemme nicht in Eingriff ist, aufweisen.

[0020] Die zentrale Verarbeitungseinheit kann selektiv den Bus freigeben, um mit dem Verbinder verbunden zu werden, und das Computersystem kann weiterhin aufweisen: einen Puffer, verbunden so, um anzuzeigen, wenn die zentrale Verarbeitungseinheit den Bus freigegeben hat, um mit dem Verbinder verbunden zu werden, und wobei die Schaltung, verbunden so, um nur Energie zuzuführen, den Bus mit dem Verbinder dann verbindet, wenn die zentrale Verarbeitungseinheit den Verbinder freigegeben hat, um mit dem Bus verbunden zu werden.

[0021] Vorzugsweise umfasst die Schaltung zum elektrischen Verbinden des Busses mit dem Verbinder eine Einrichtung zum Verbinden einer Takteleitung und von anderen Leitungen des Busses, wobei die anderen Leitungen des Busses verbunden werden, nachdem die Energie zugeführt ist und die Takteleitung verbunden ist.

[0022] Unter den Vorteilen der Erfindung ist einer oder sind mehrere der Folgenden umfasst. Wenn die Erweiterungskarte verbunden ist, werden Operationen auf der Erweiterungskarte stabilisiert und erreichen Bereitschaftsbedingungen, bevor externe Bussignale zu der Erweiterungskarte zugeführt werden. Wenn heruntergefahren bzw. getrennt wird, werden Operationen auf der Erweiterungskarte in einer geordneten Art und Weise gehalten, bevor die Erweiterungskarte von dem Schlitz entfernt wird, was das Auftreten von nicht erwünschten Signalen auf dem Bus minimiert.

[0023] Andere Vorteile und Merkmale werden aus der nachfolgenden Beschreibung und aus den Zeichnungen ersichtlich werden, in denen:

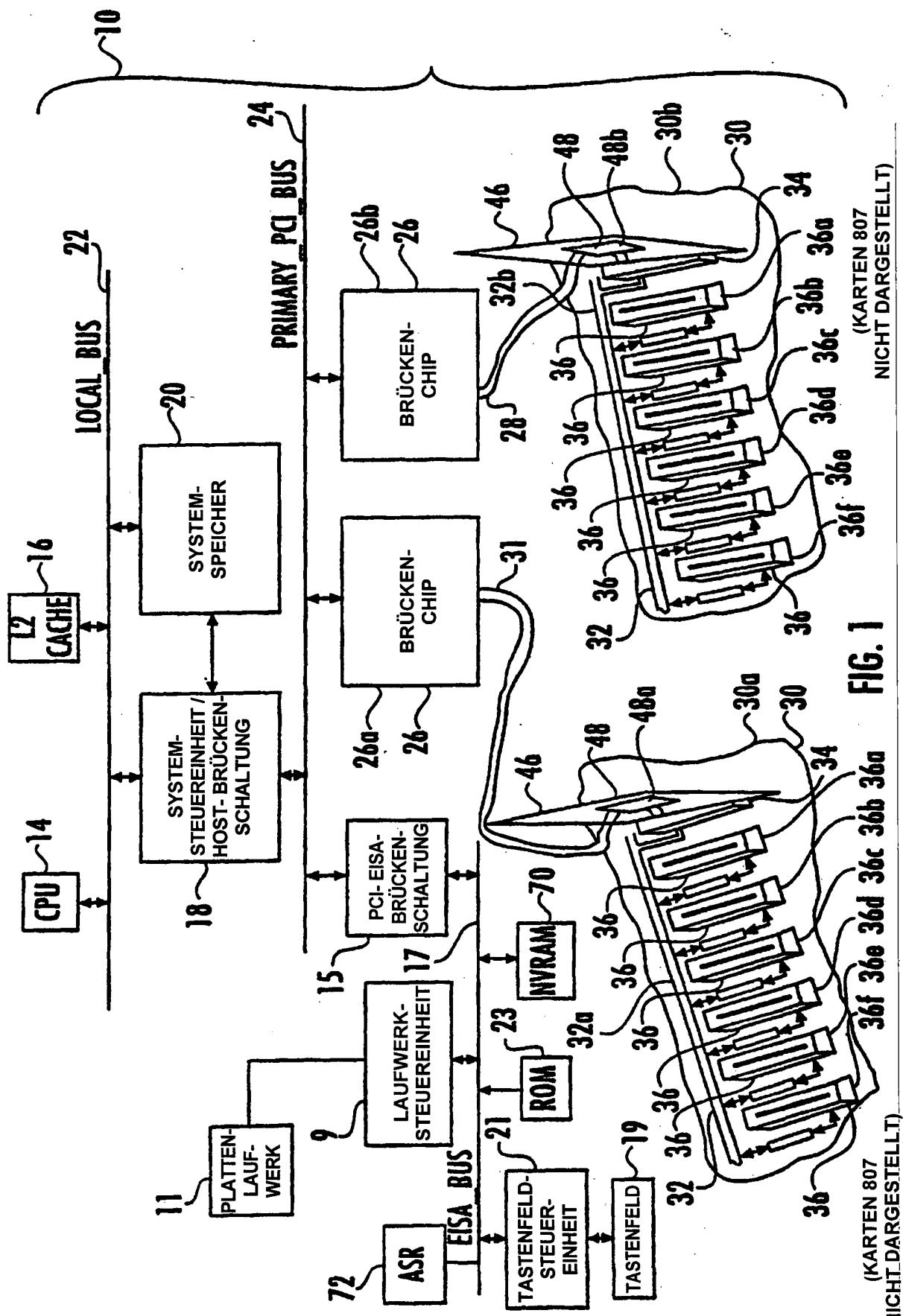

[0024] **Fig. 1** zeigt ein Blockdiagramm eines Computersystems.

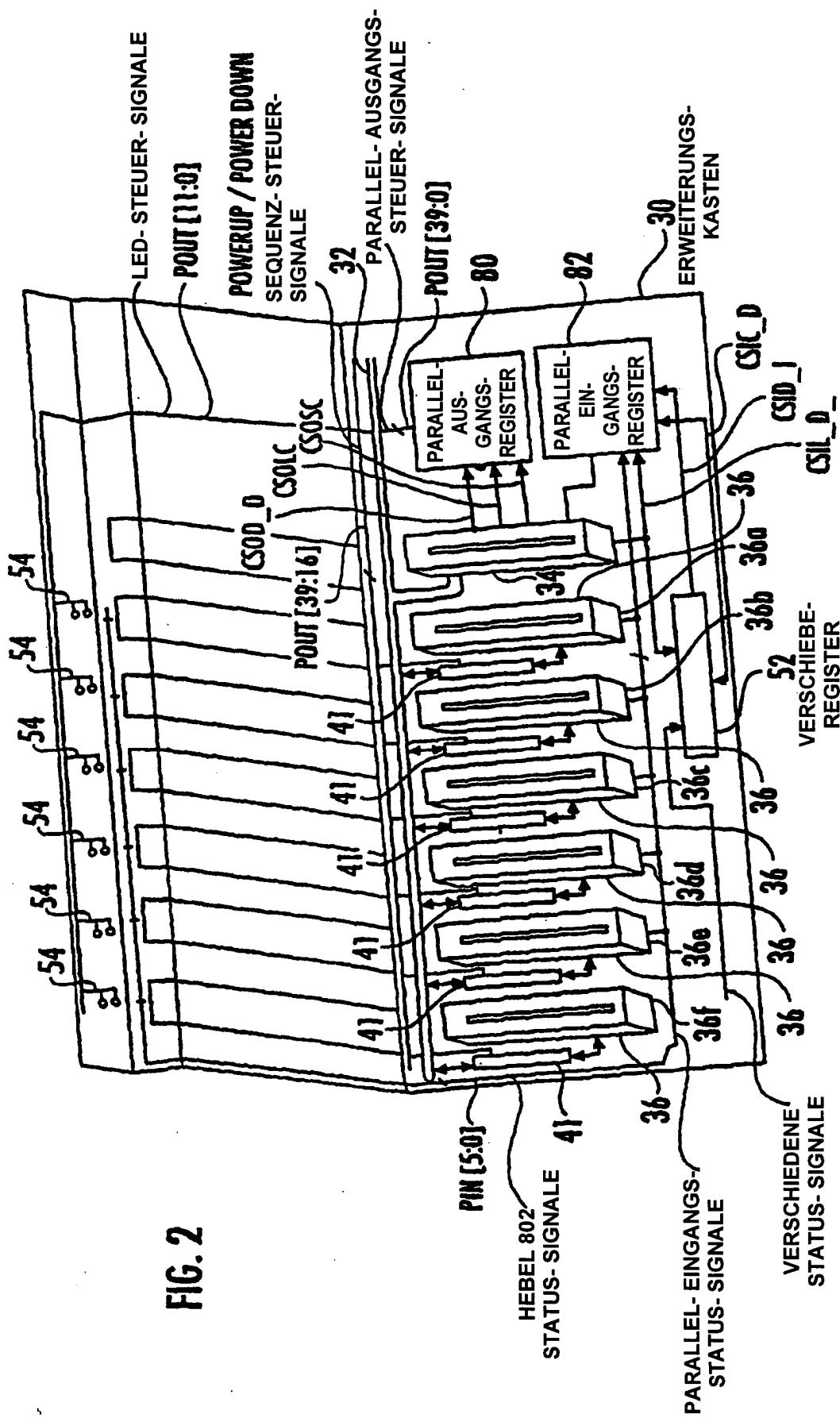

[0025] **Fig. 2** zeigt ein Blockdiagramm eines Erweiterungskastens des Computersystems der **Fig. 1**.

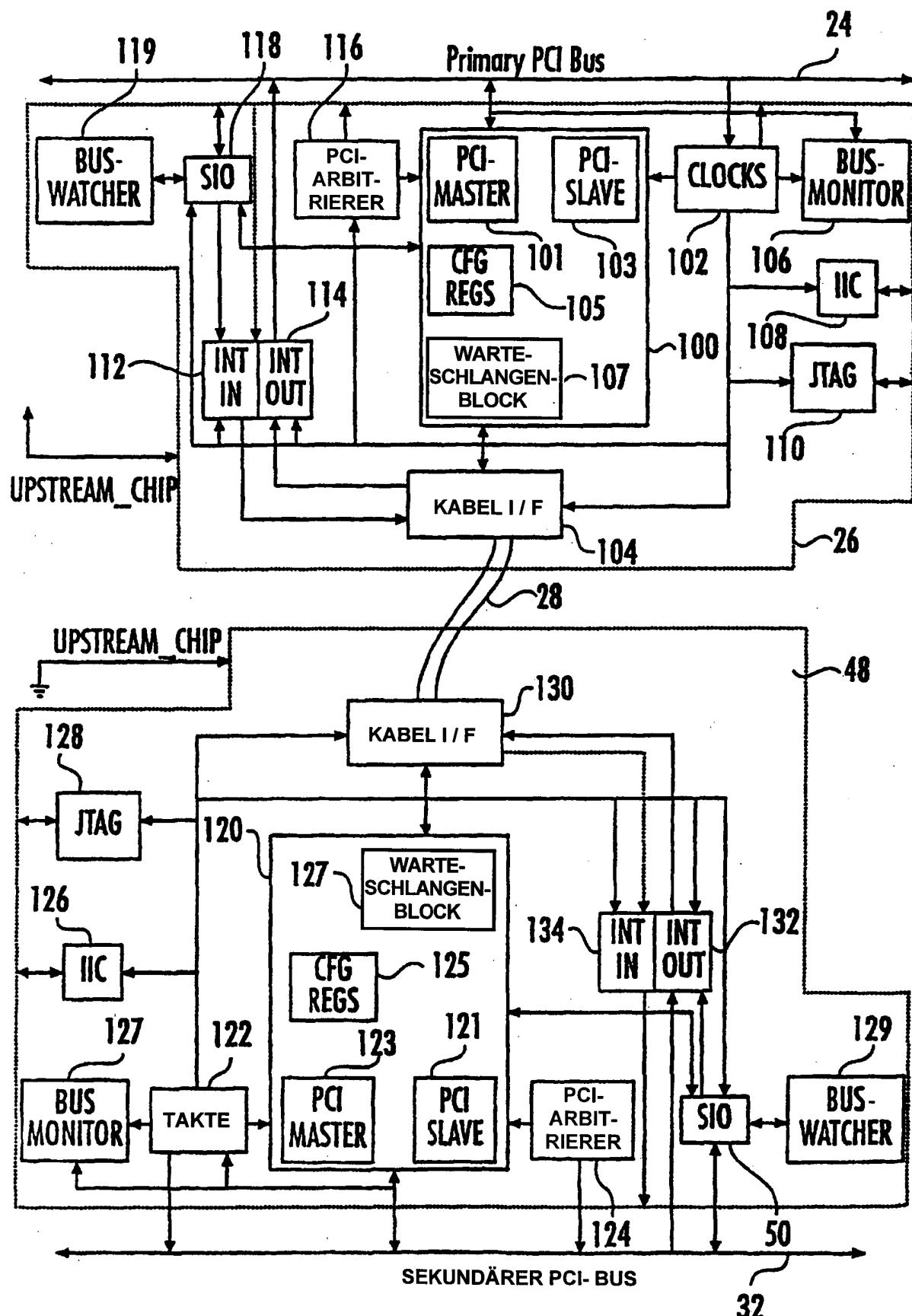

[0026] **Fig. 3** zeigt ein Blockdiagramm der Brücken-Chips in dem Computersystem.

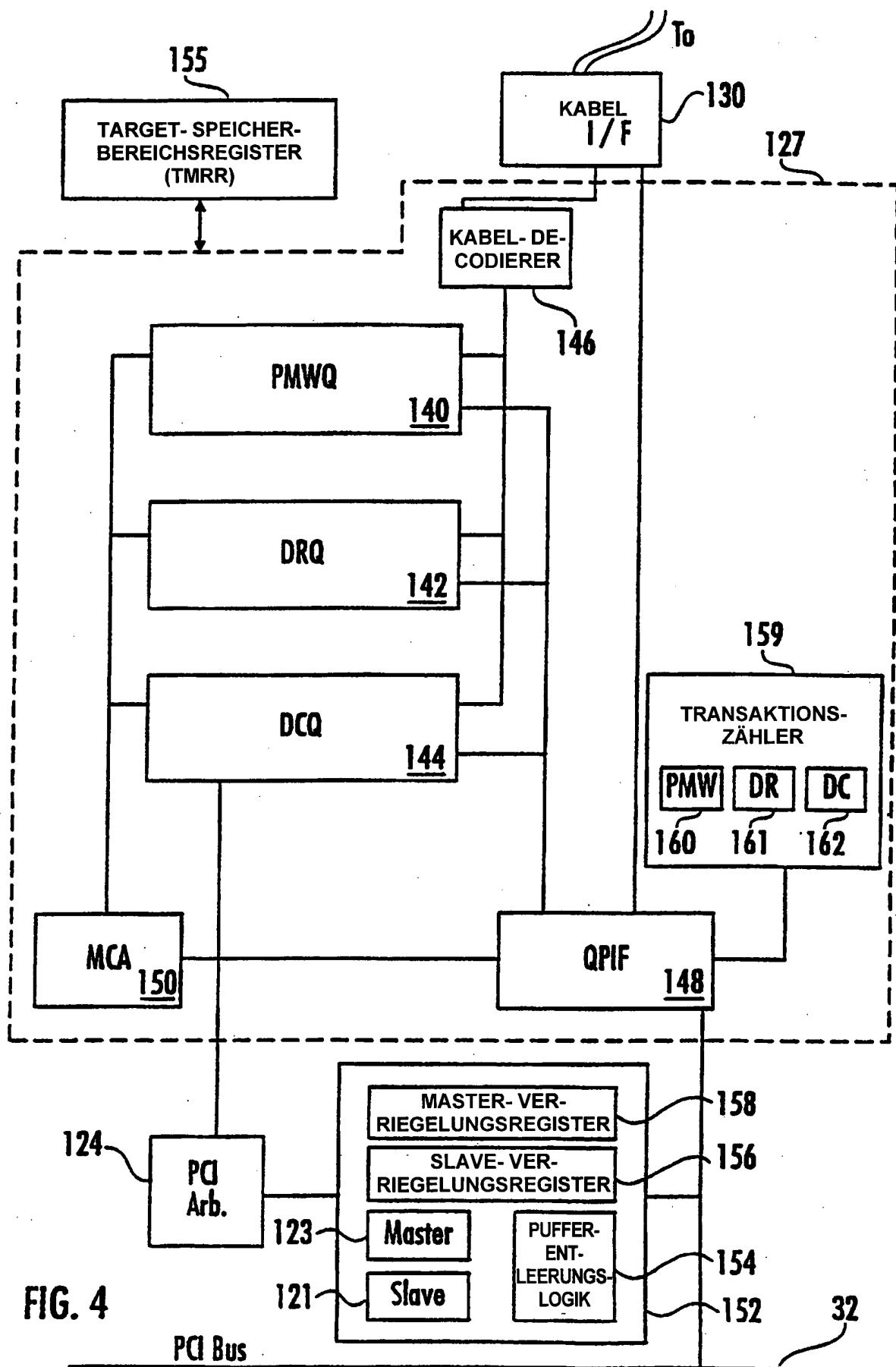

[0027] **Fig. 4** zeigt ein Blockdiagramm eines Warteschlangen-Blocks in jedem der Brücken-Chips.

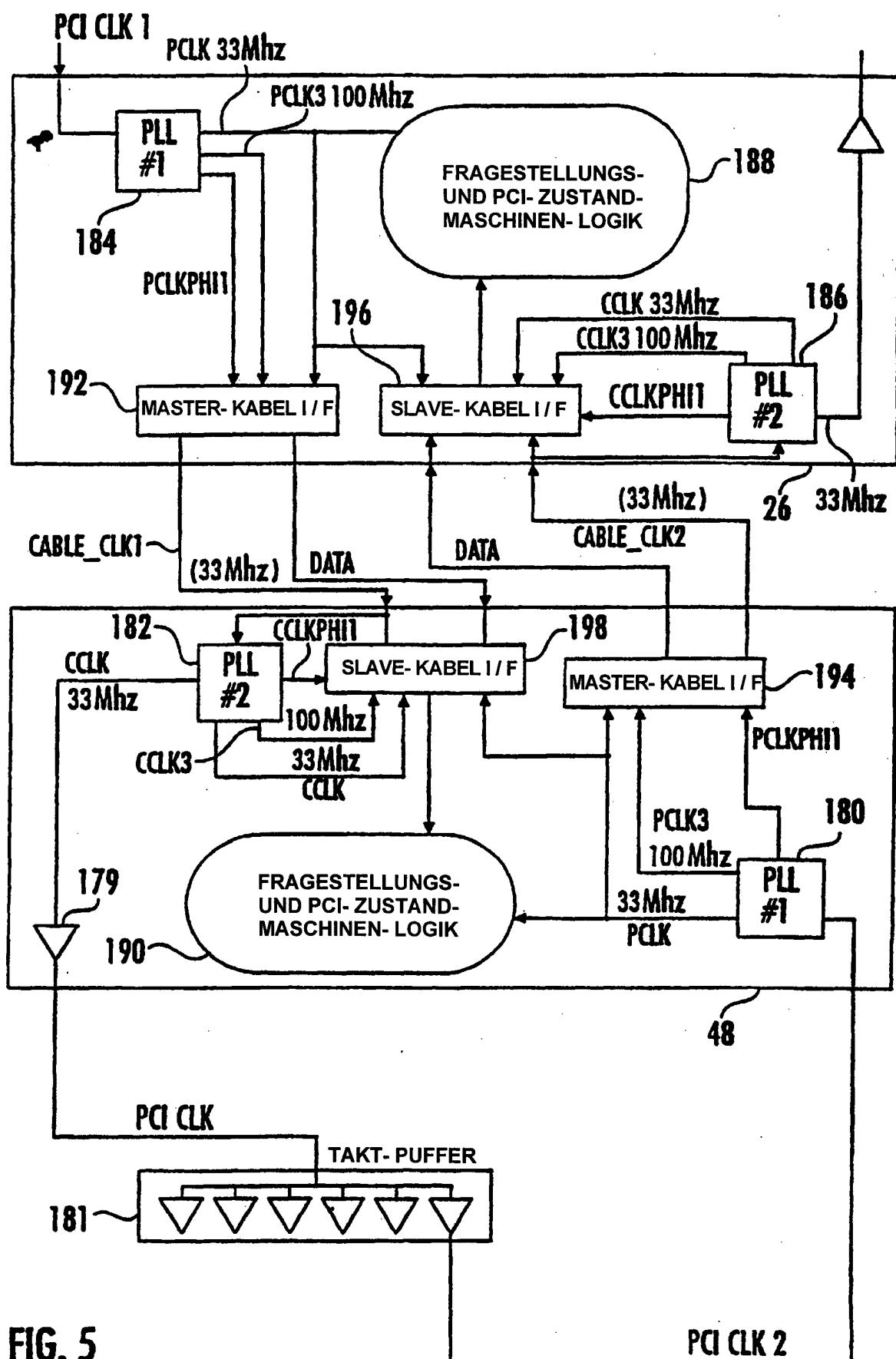

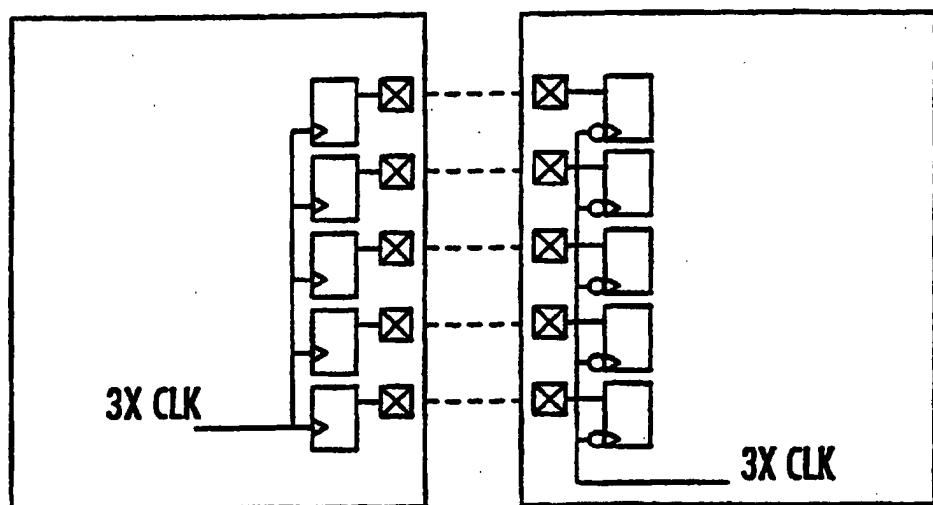

[0028] **Fig. 5** zeigt ein Blockdiagramm des Takt-Routing-Schemas in den Brücken-Chips.

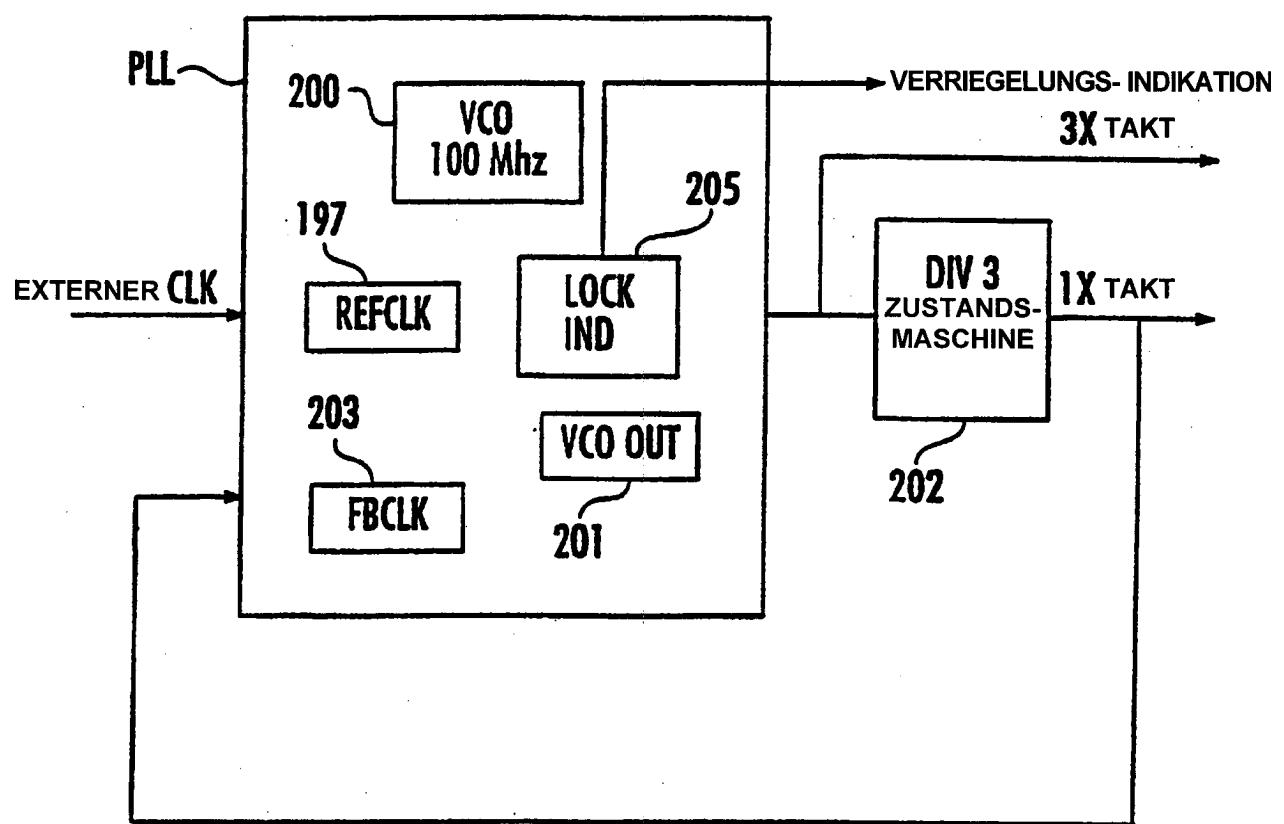

[0029] **Fig. 6** zeigt ein Blockdiagramm eines Taktgenerators in jedem der Brücken-Chips.

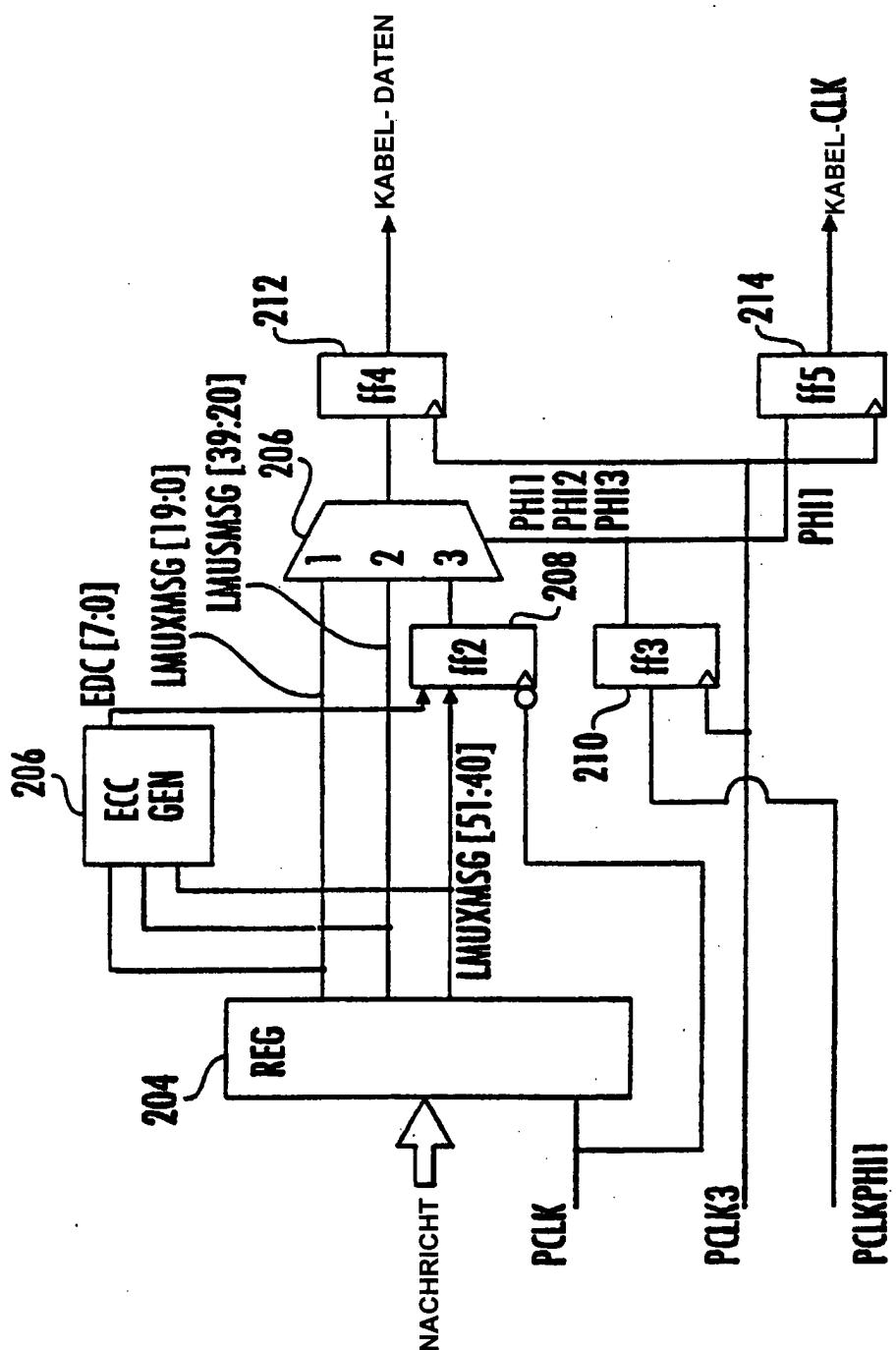

[0030] **Fig. 7** zeigt ein Blockdiagramm einer Master-Kabel-Schnittstelle in jedem der Brücken-Chips zum Übertragen von Daten über ein Kabel, das die Brücken-Chips verbindet.

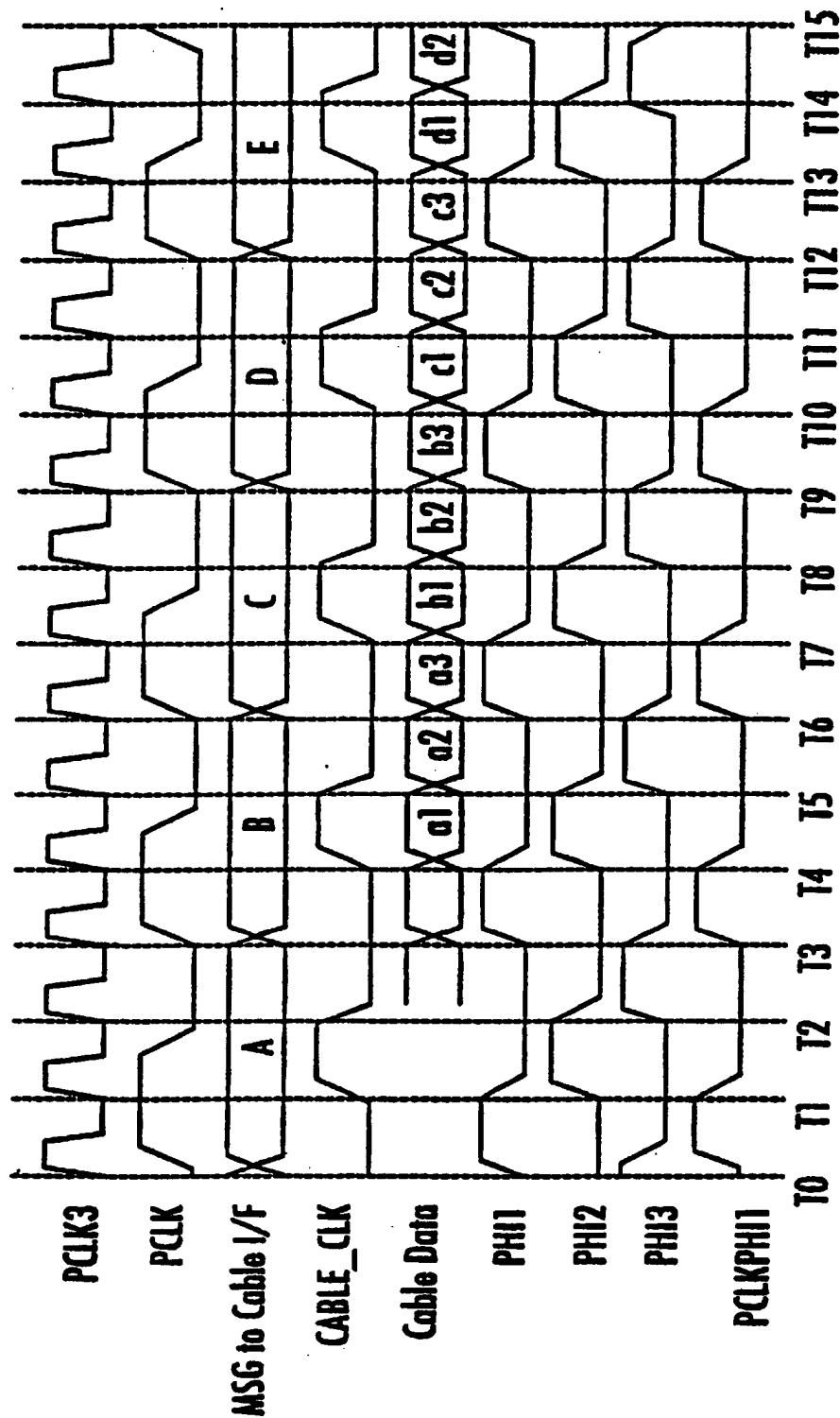

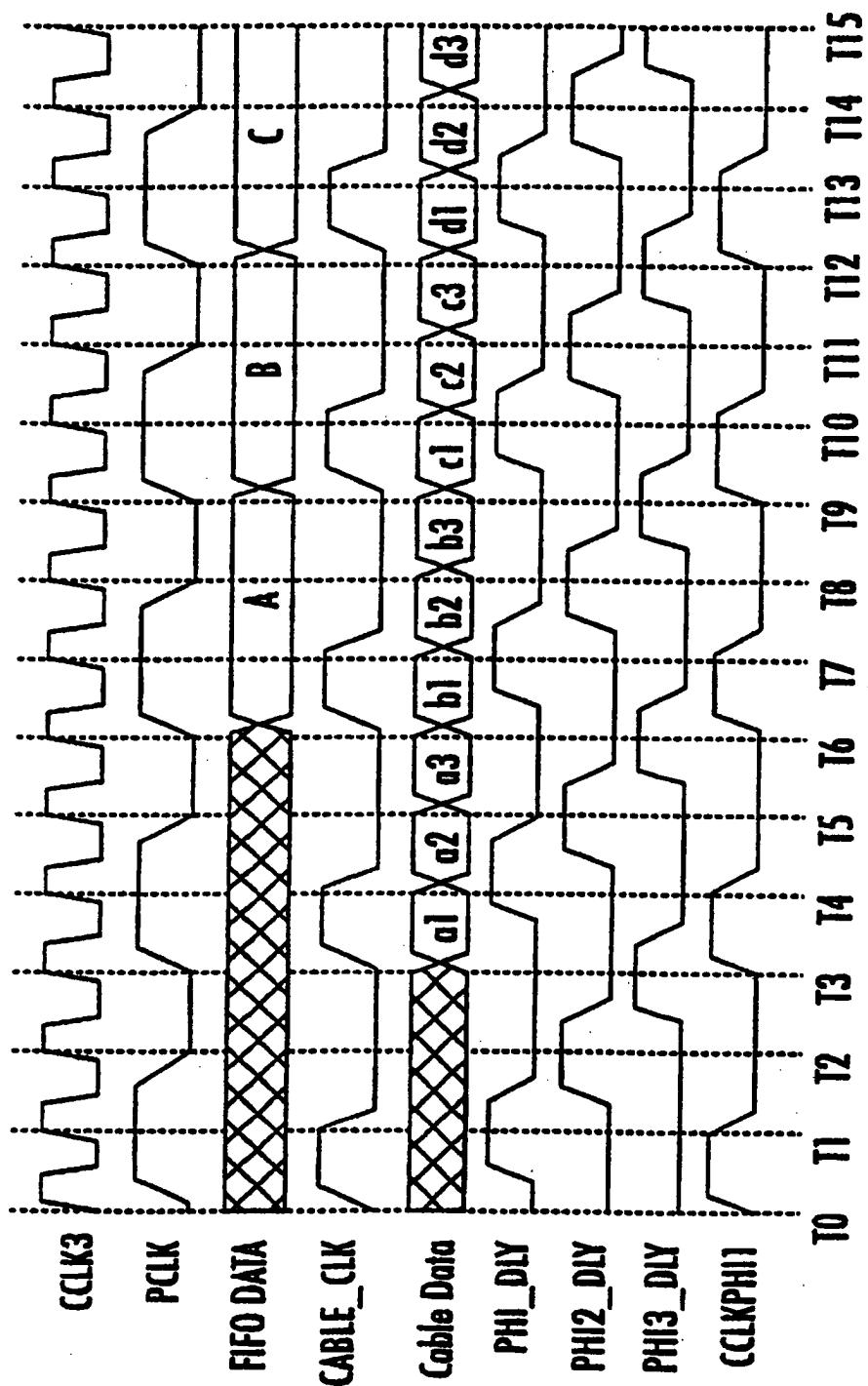

[0031] **Fig. 8** zeigt ein Zeitabstimmungsdiagramm von Signalen in der Master-Kabel-Schnittstelle.

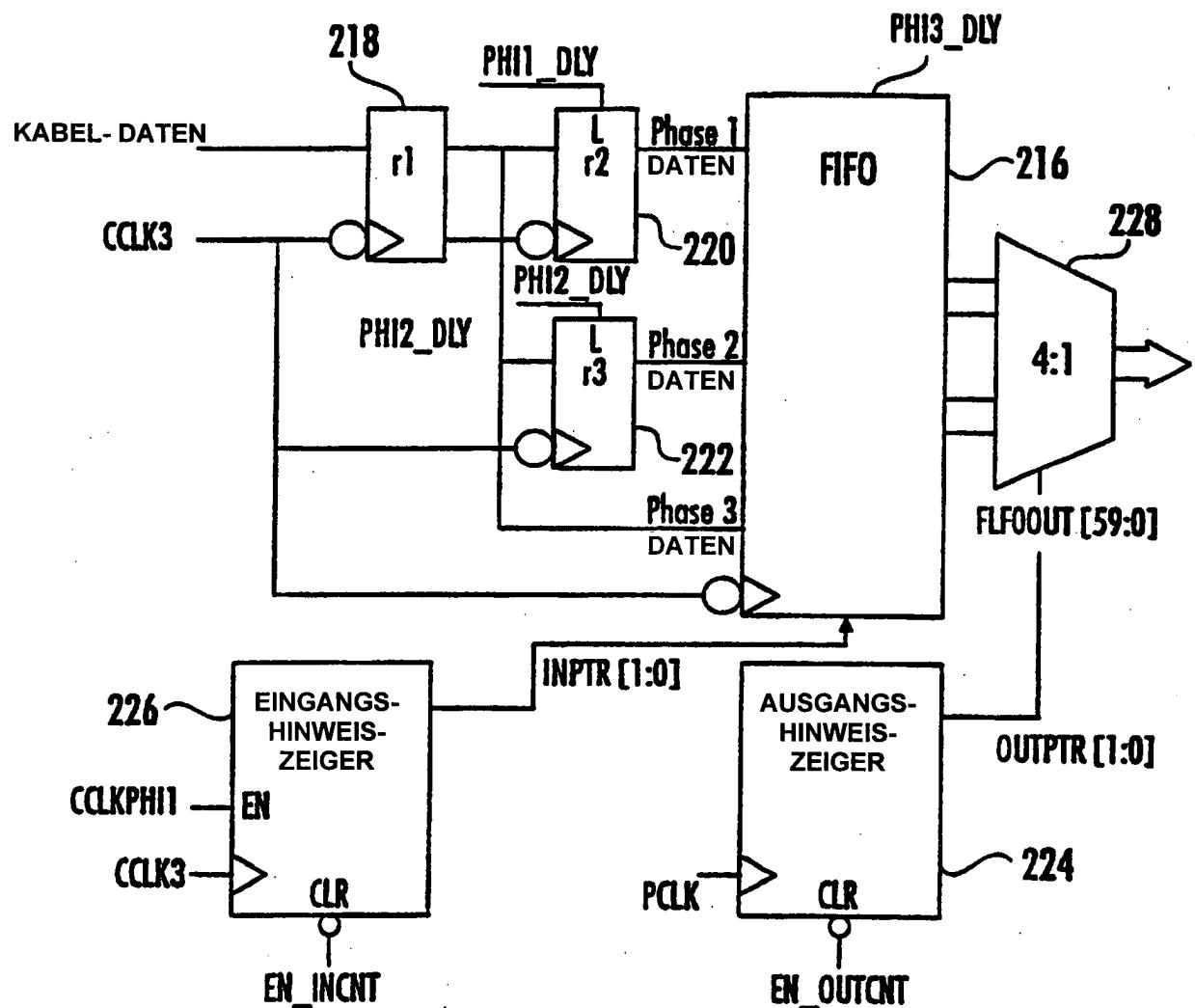

[0032] **Fig. 9** zeigt ein Blockdiagramm einer Slave-Kabel-Schnittstelle in jedem der Brücken-Chips zum Aufnehmen von Daten, übertragen über das Kabel.

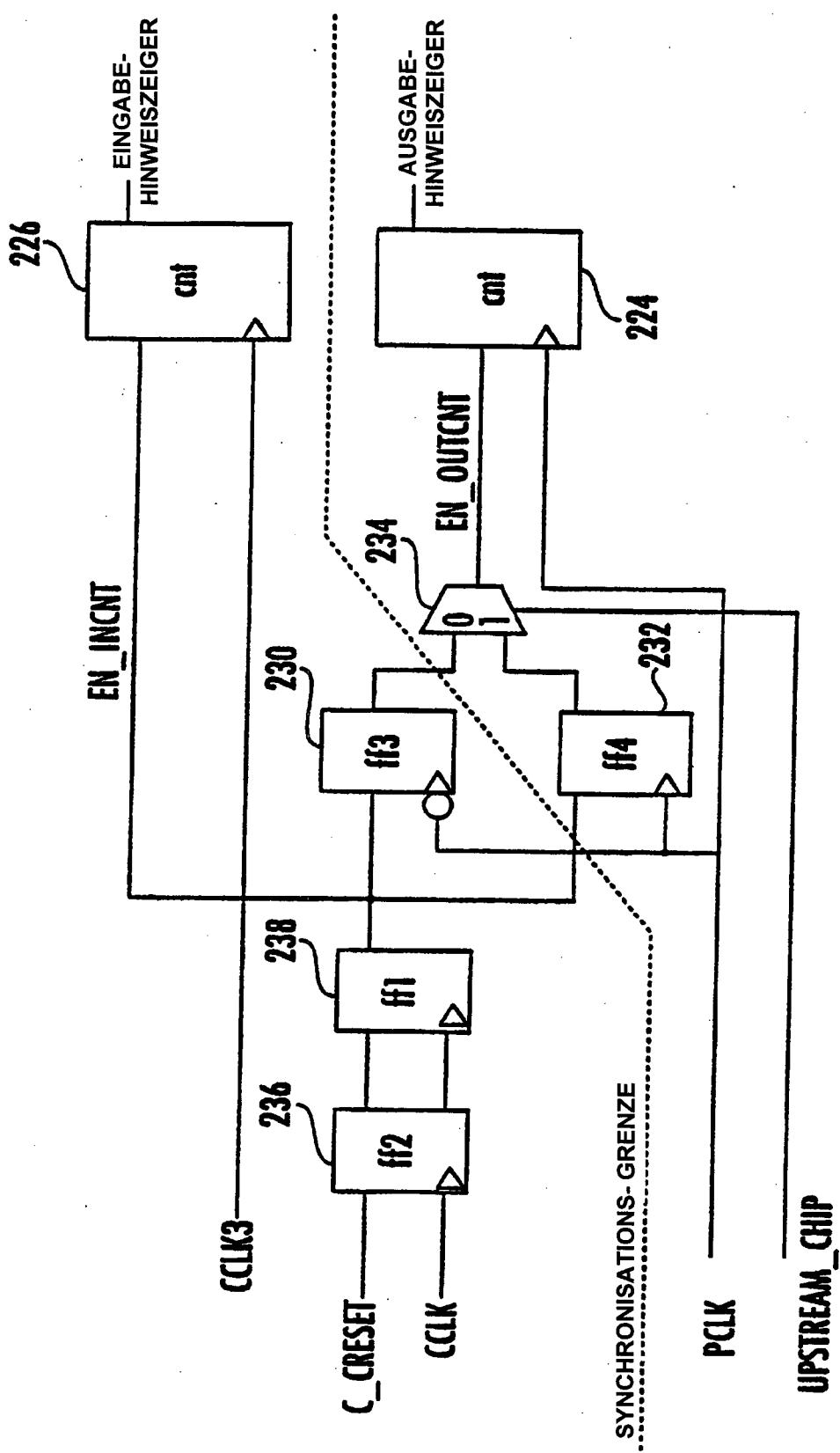

[0033] **Fig. 10** zeigt ein Blockdiagramm von Logik-Erzeugungs-Eingangs- und Ausgangs-Hinweiszeigern für die empfangene Logik in der Slave-Kabel-Schnittstelle.

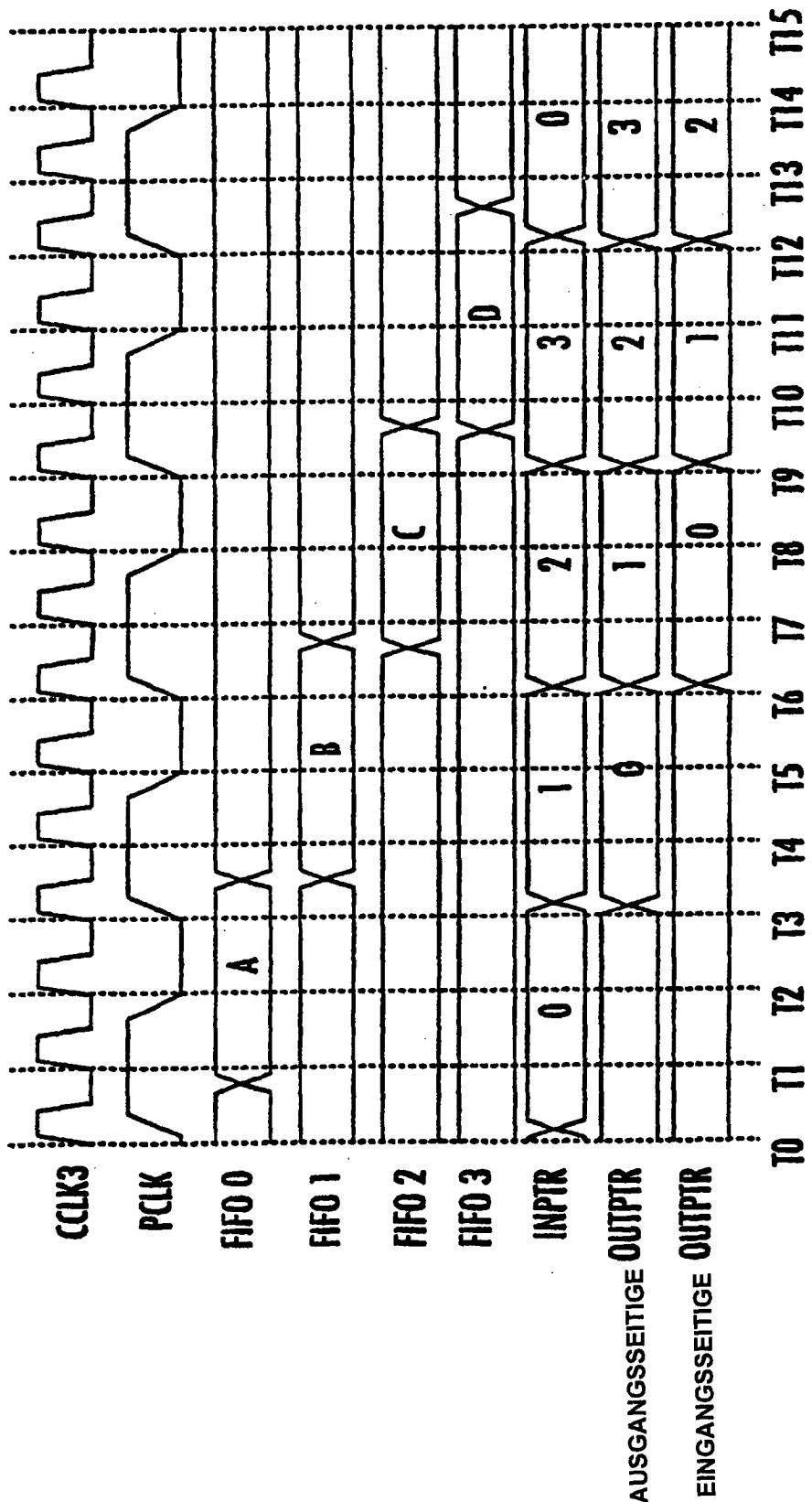

[0034] **Fig. 11** zeigt ein Zeitabstimmungsdiagramm von Signalen in der Slave-Kabel-Schnittstelle.

[0035] **Fig. 12** zeigt ein Zeitabstimmungsdiagramm der Eingangs- und Ausgangs-Hinweiszeiger und deren Beziehung zu den aufgenommenen Kabeldaten.

[0036] **Fig. 13** zeigt ein Blockdiagramm der Plazierung von Flip-Flop's und Eingangs- und Ausgangsanschlüsseflächen in jedem der Brücken-Chips.

[0037] **Fig. 14** zeigt eine Tabelle der Informationen, geführt durch das Kabel.

[0038] **Fig. 15A** zeigt eine Tabelle, die den Typ von Informationen darstellt, geführt durch die Kabelsignale, die Einzel-Adressenzyklus-Transaktionen zugeordnet sind.

[0039] **Fig. 15B** zeigt eine Tabelle, die den Typ von Informationen darstellt, geführt durch die Kabelsignale, zugeordnet zu Dual-Adressen-Zyklus-Transaktionen.

[0040] **Fig. 16** zeigt eine Tabelle von Parametern, zugeordnet zu dem Kabel.

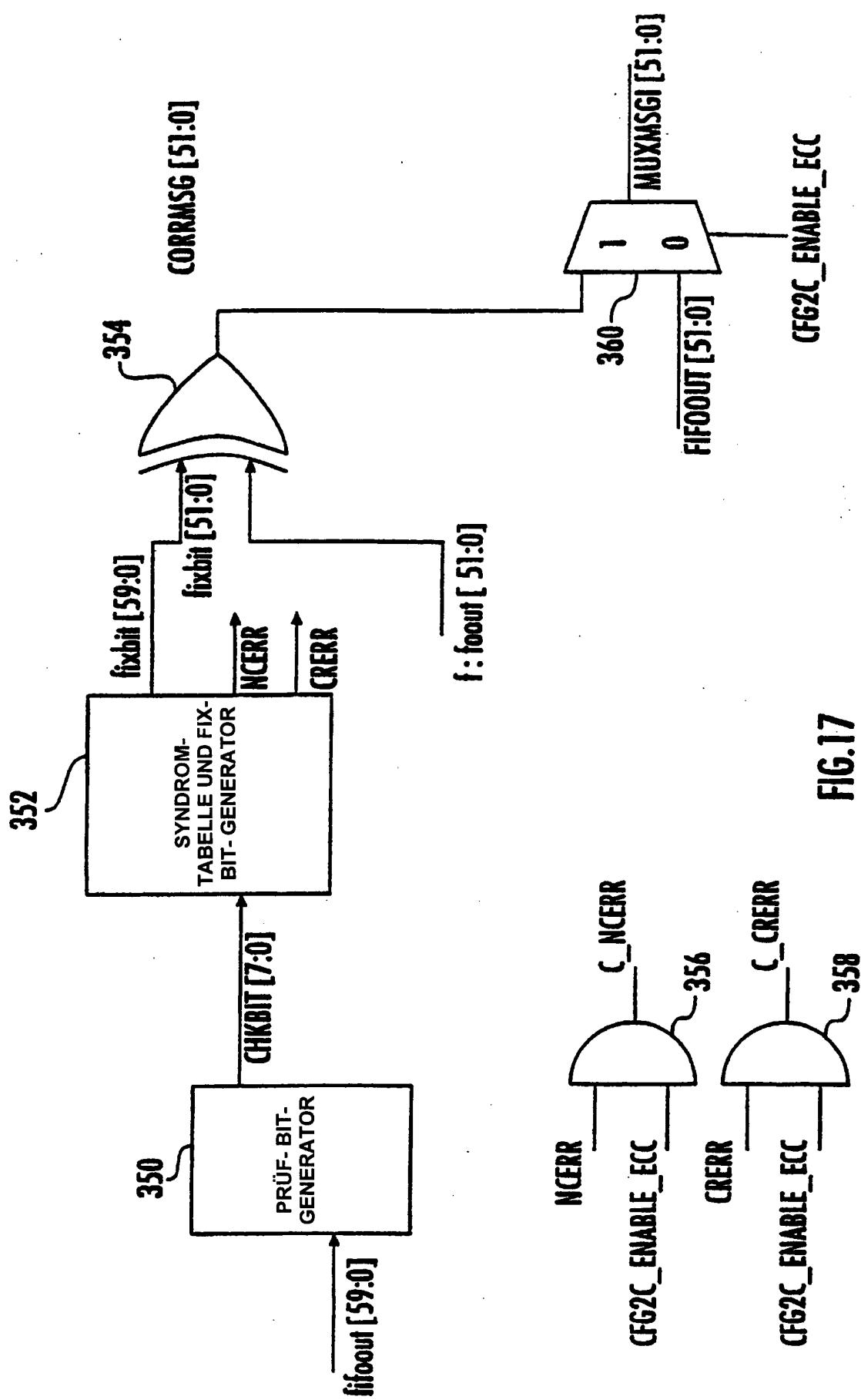

[0041] **Fig. 17** zeigt ein Logikdiagramm einer Fehlererkennungs- und Korrekturschaltung.

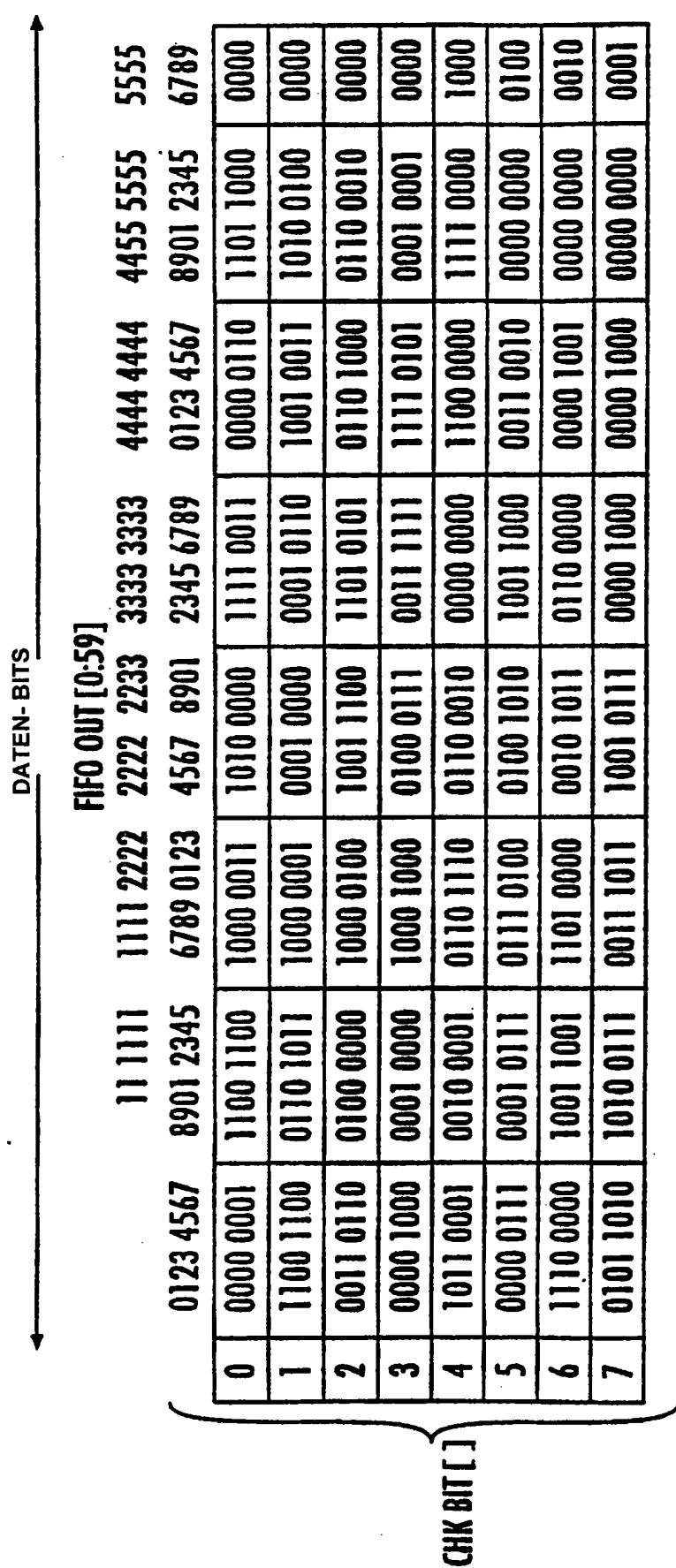

[0042] **Fig. 18** zeigt eine Parität-Prüf-Matrix zum Erzeugen von Prüf-Bits in der Fehlererkennungs- und Kor-

rekturschaltung.

- [0043] Fig. 19 zeigt eine Syndrom-Tabelle zum Erzeugen von Fix-Bits in der Fehlererfassungs- und Korrekturschaltung.

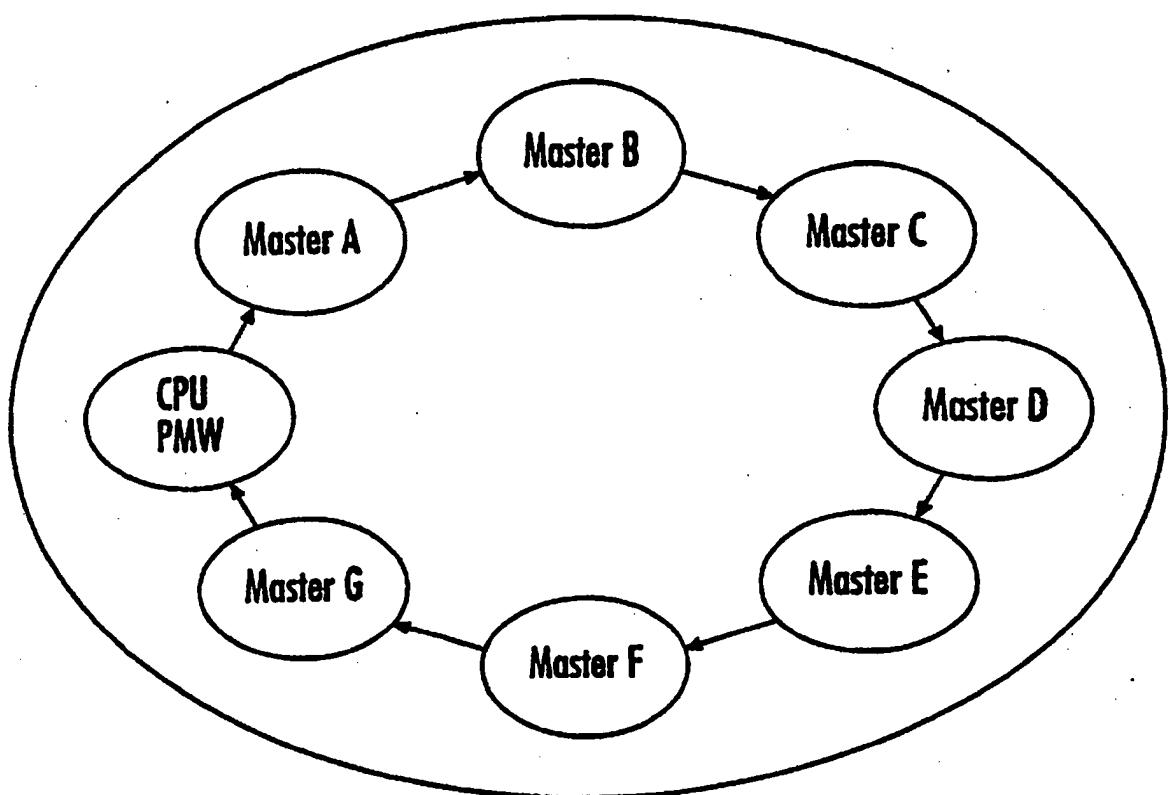

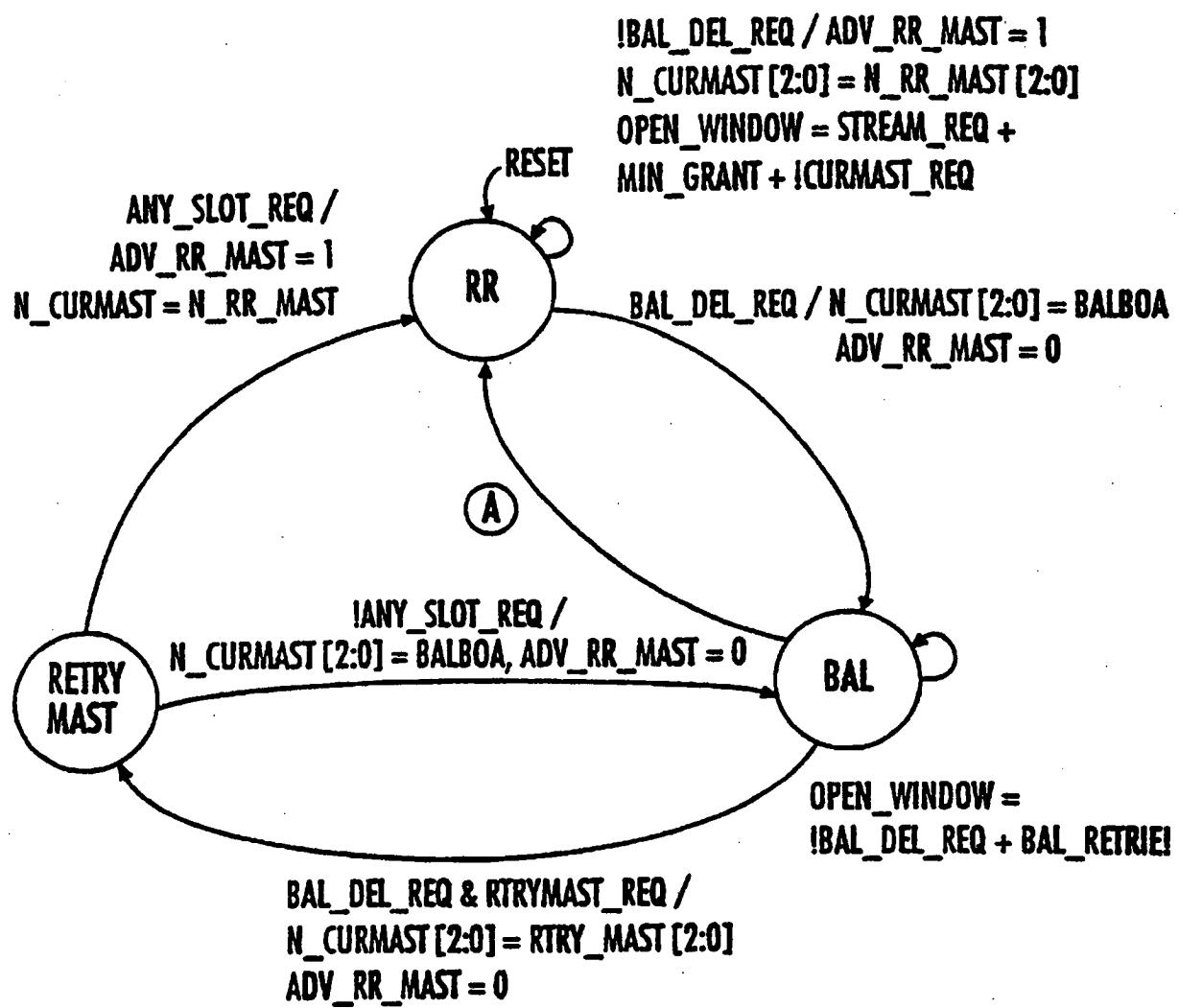

- [0044] **Fig. 20A** zeigt ein Zustand-Diagramm, das ein Round-Robin Arbitrierungs-Schema darstellt.

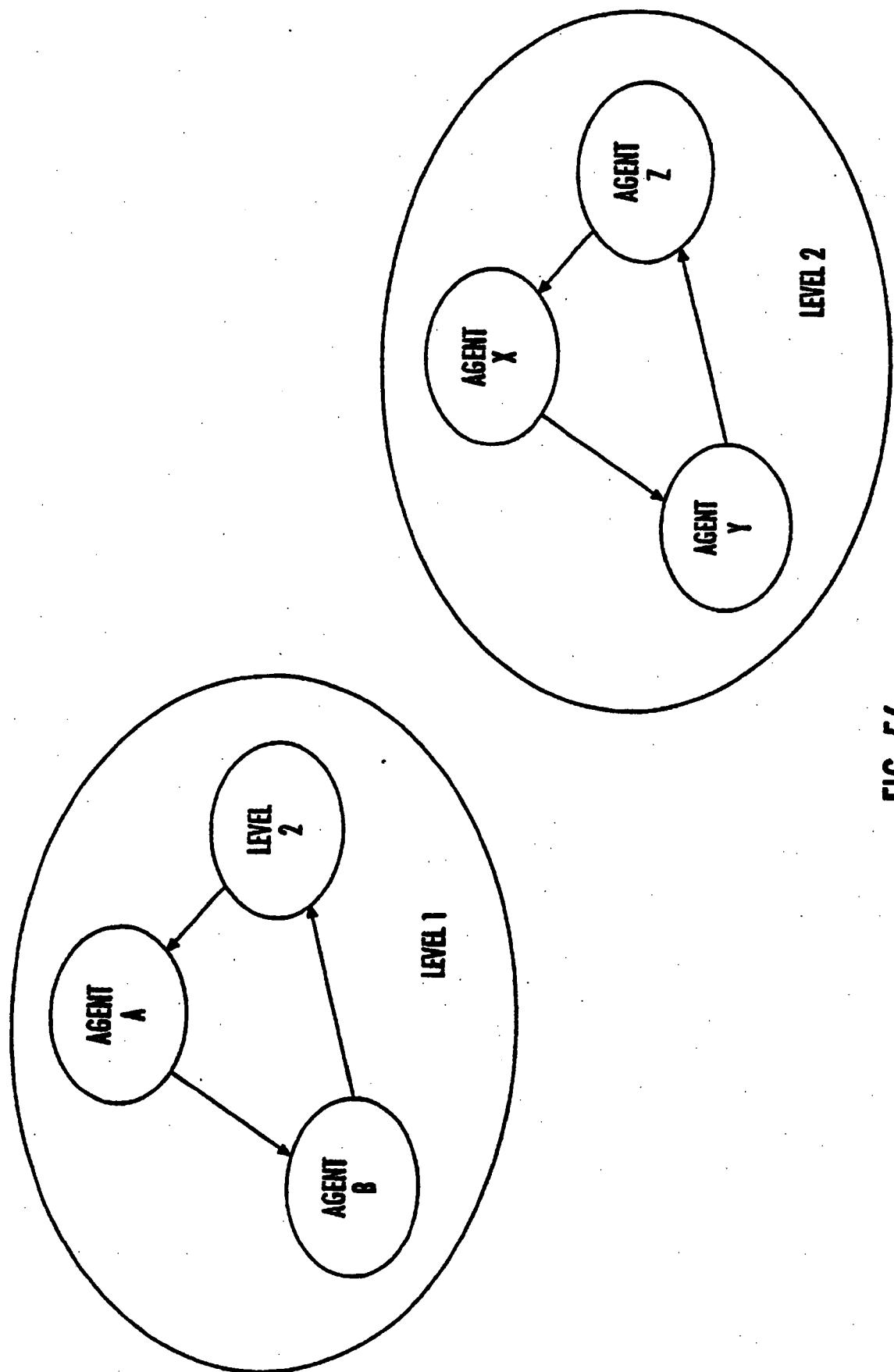

- [0045] **Fig. 20B** zeigt ein Zustandsdiagramm, dass ein Zwei-Niveau-Entscheidungs-Schema darstellt.

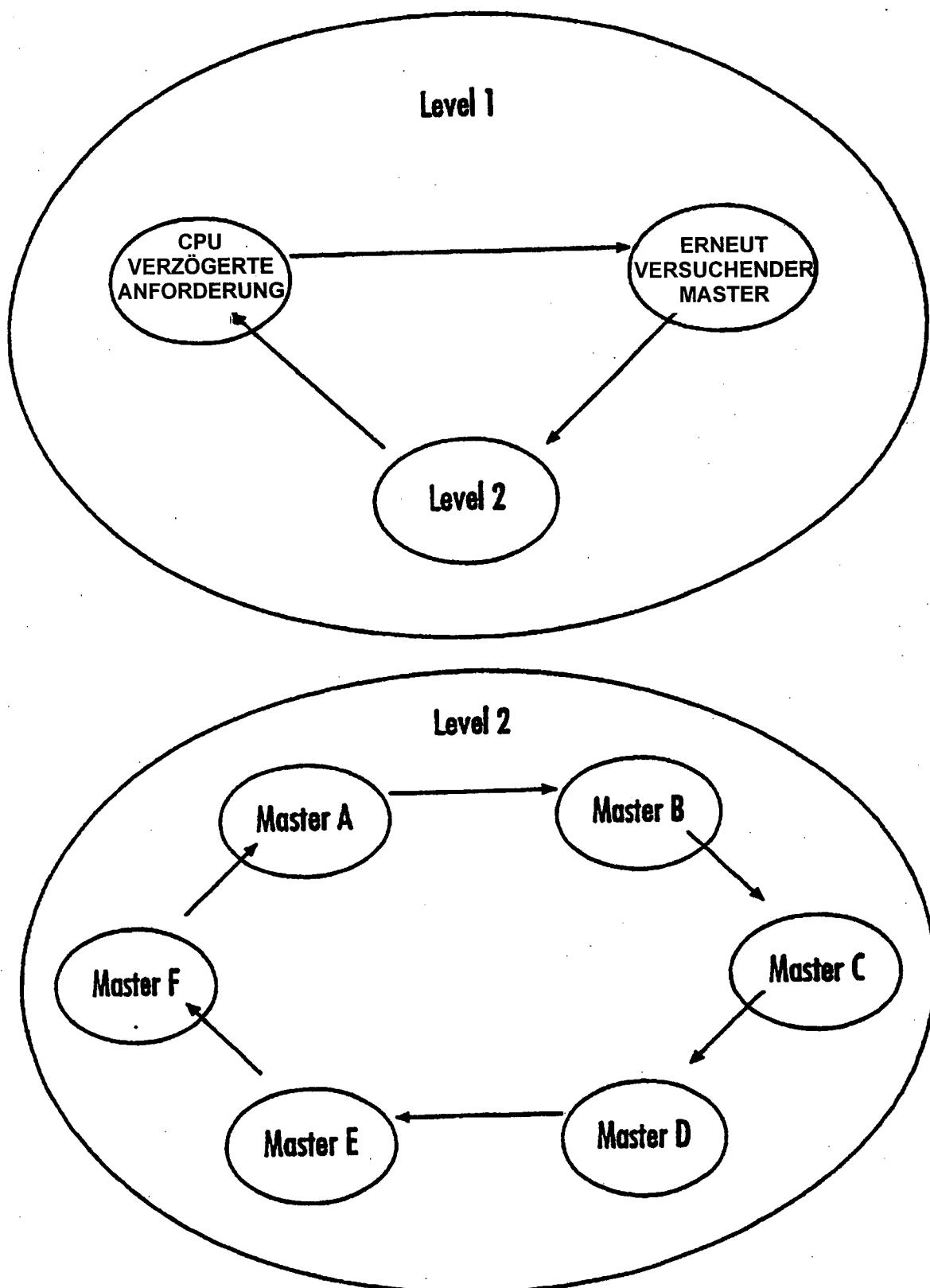

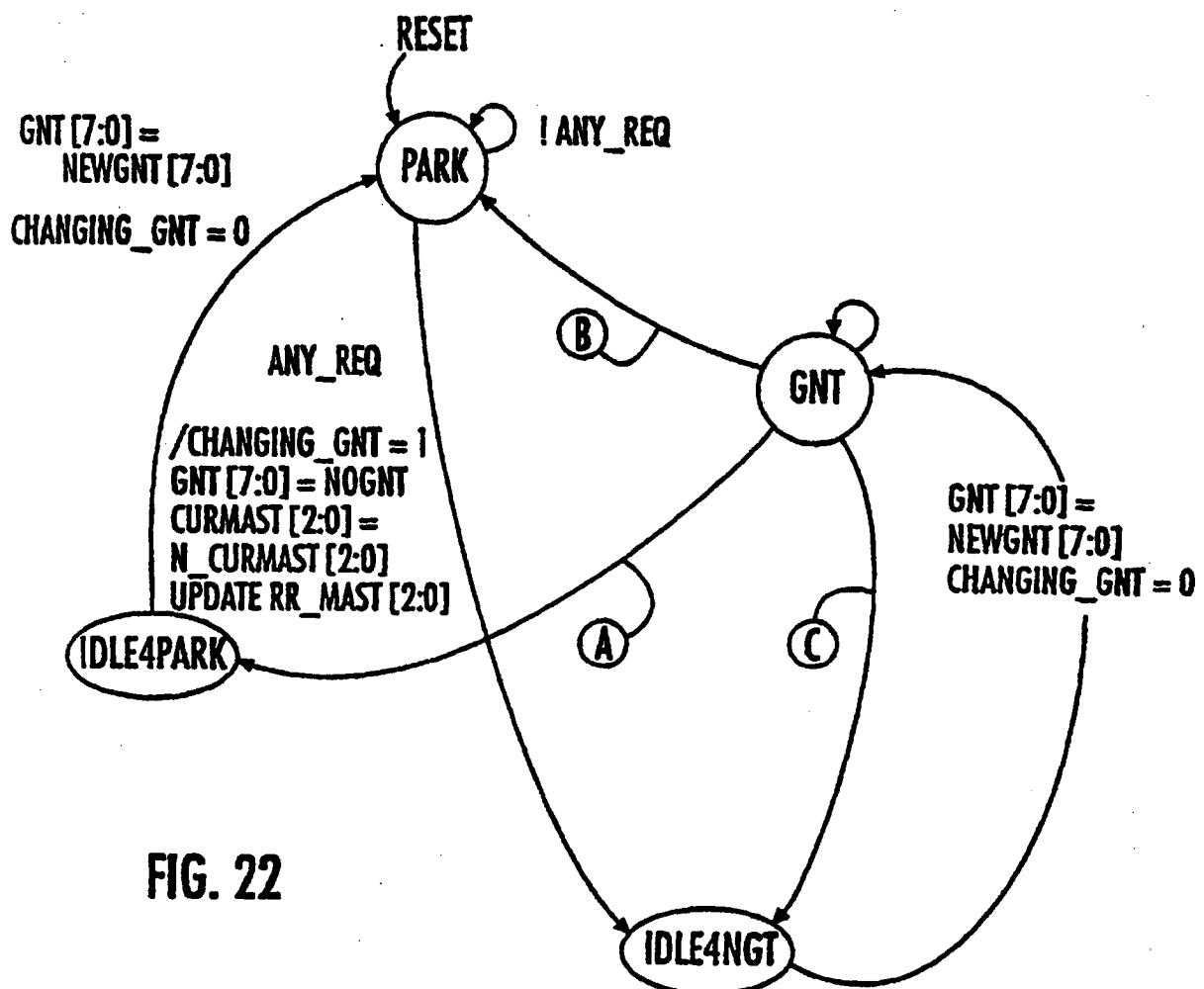

- [0046] **Fig. 21** zeigt ein logisches Diagramm einer Entscheidungseinrichtung in jedem der Brücken-Chips.

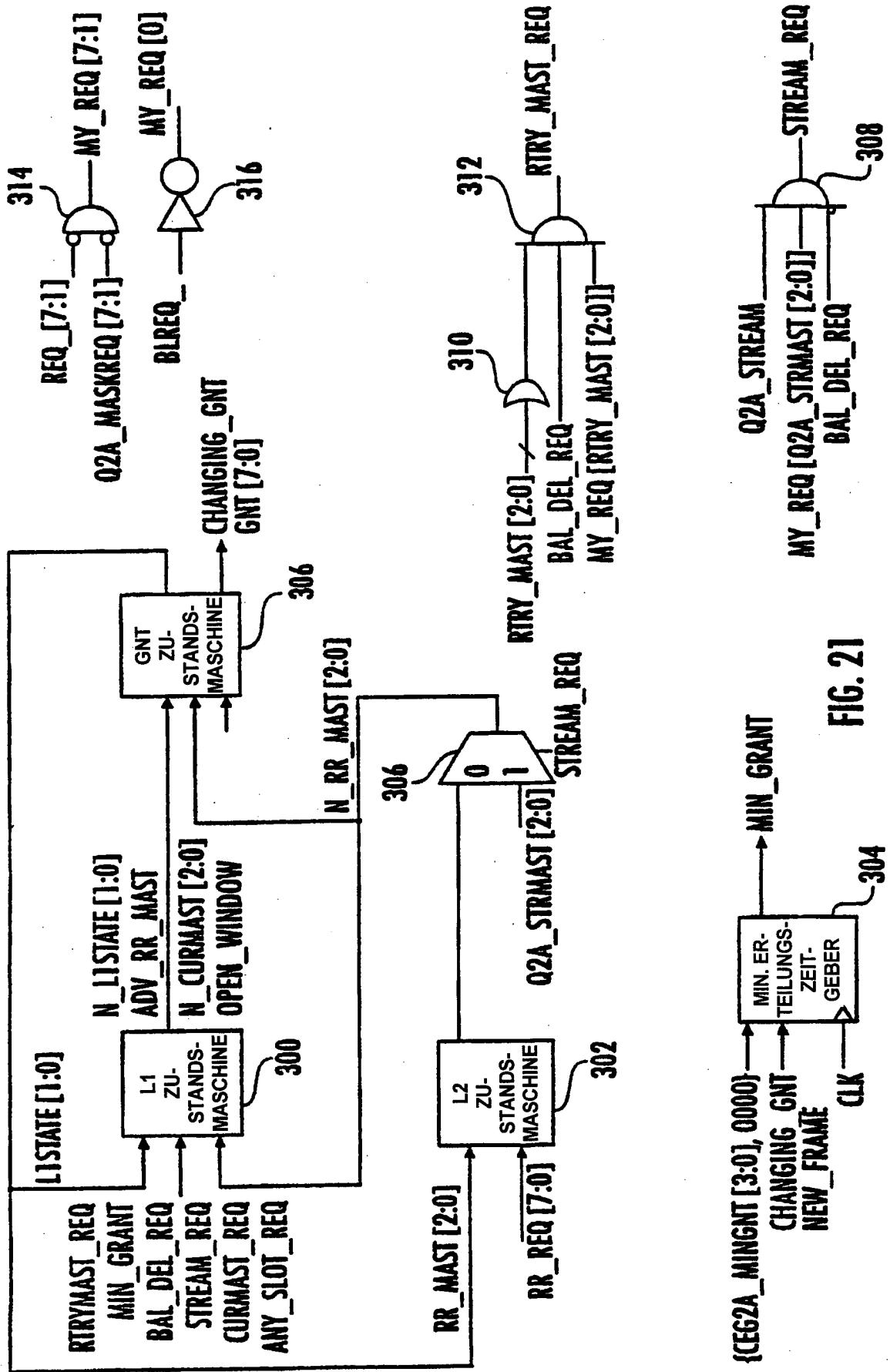

- [0047] **Fig. 22** zeigt ein Zustandsdiagramm einer Erteilungs-Zustand-Maschine in einer Entscheidungseinrichtung.

- [0048] **Fig. 23** zeigt ein Zustandsdiagramm eines Level eins einer Entscheidungs-Zustand-Maschine in der Entscheidungseinrichtung.

- [0049] **Fig. 24** zeigt eine Tabelle, die eine Erzeugung von neuen Erteilungs-Signalen basierend auf dem momentanen Master darstellt.

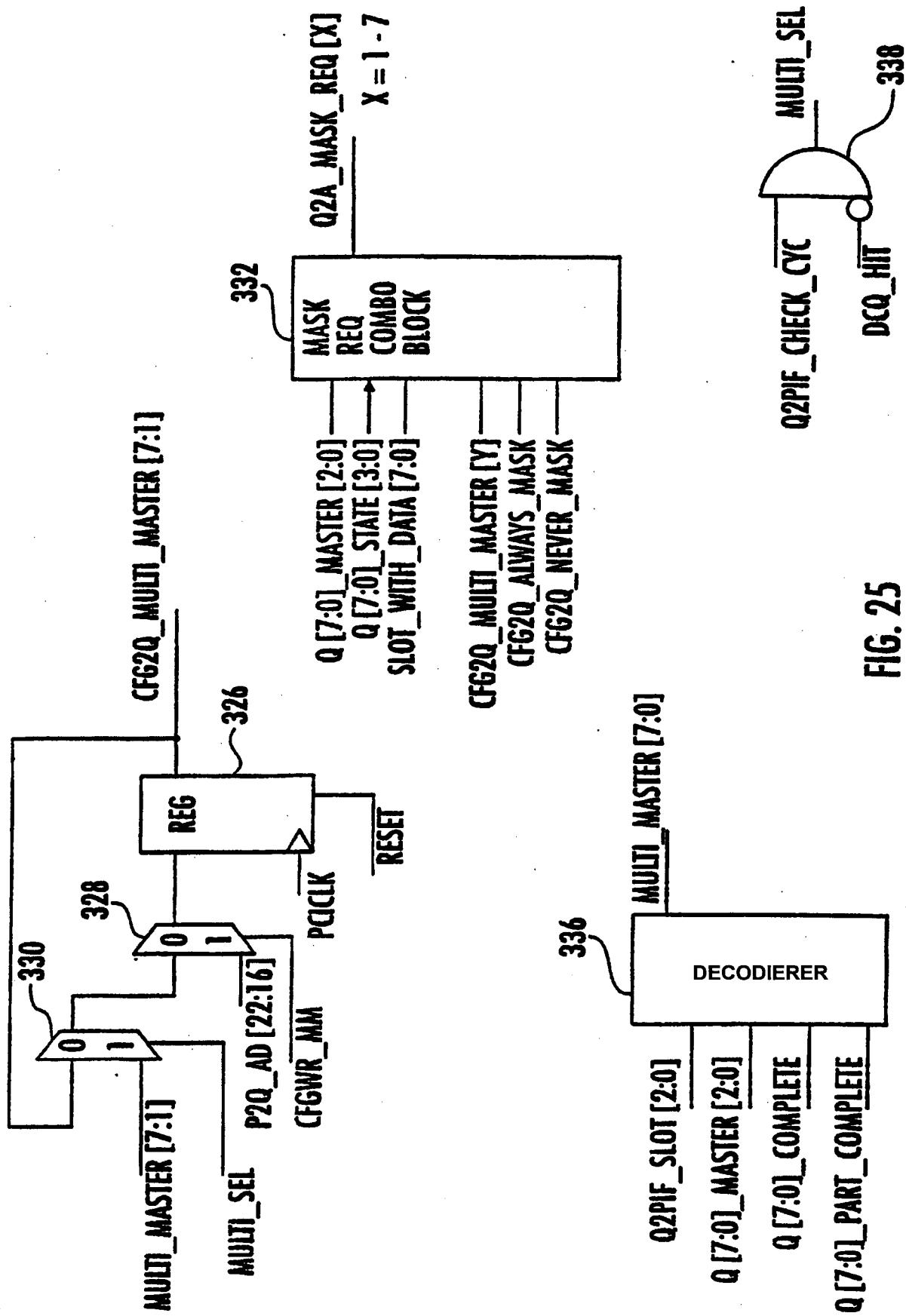

- [0050] **Fig. 25** zeigt ein Blockdiagramm einer Logik zum Erzeugen von Masken-Bits und Master-Indikations-Bits mit Multi-Threading-Fähigkeit.

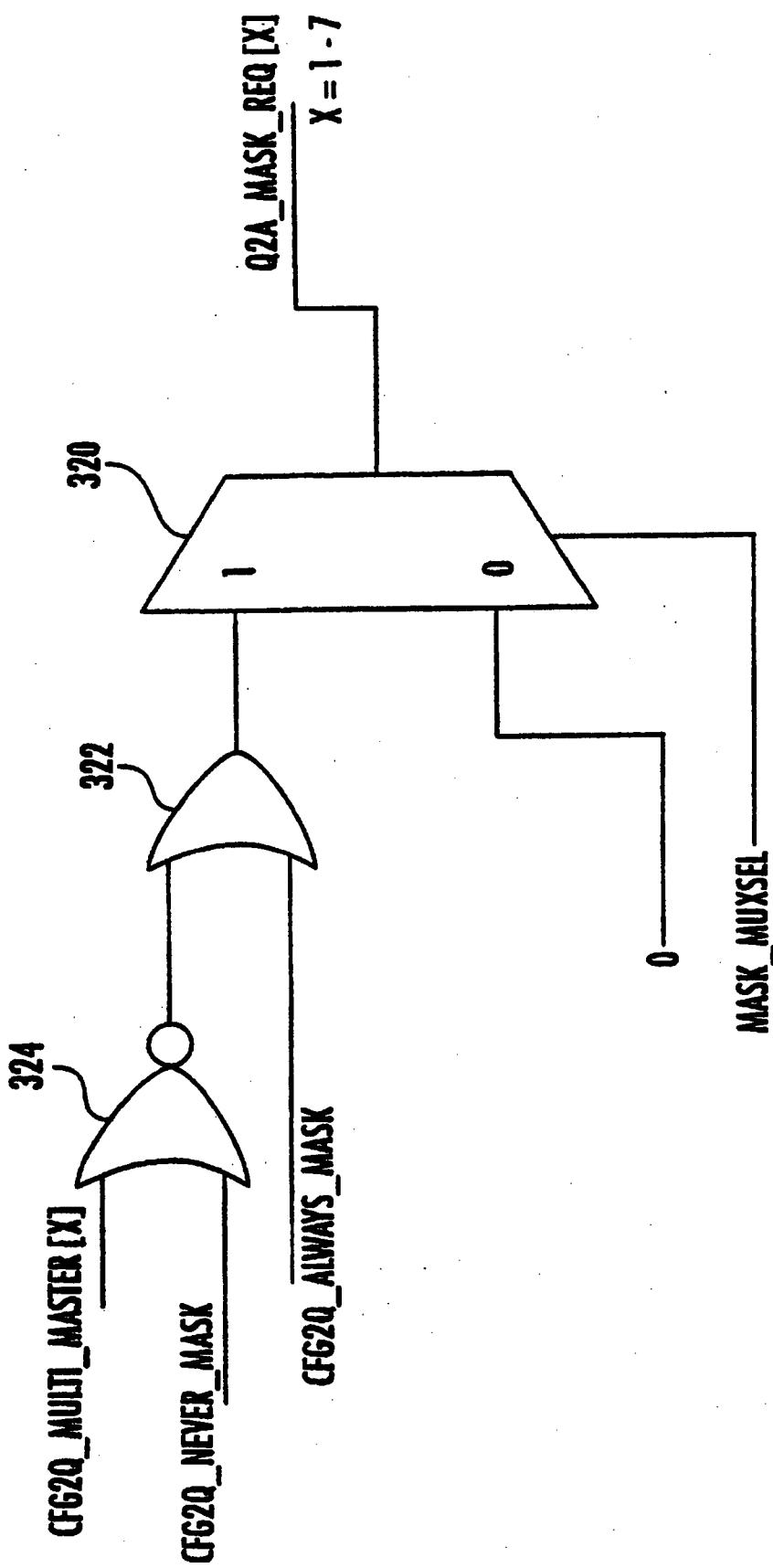

- [0051] **Fig. 26A** zeigt ein logisches Diagramm von Schaltungen zum Erzeugen der maskierten Bits.

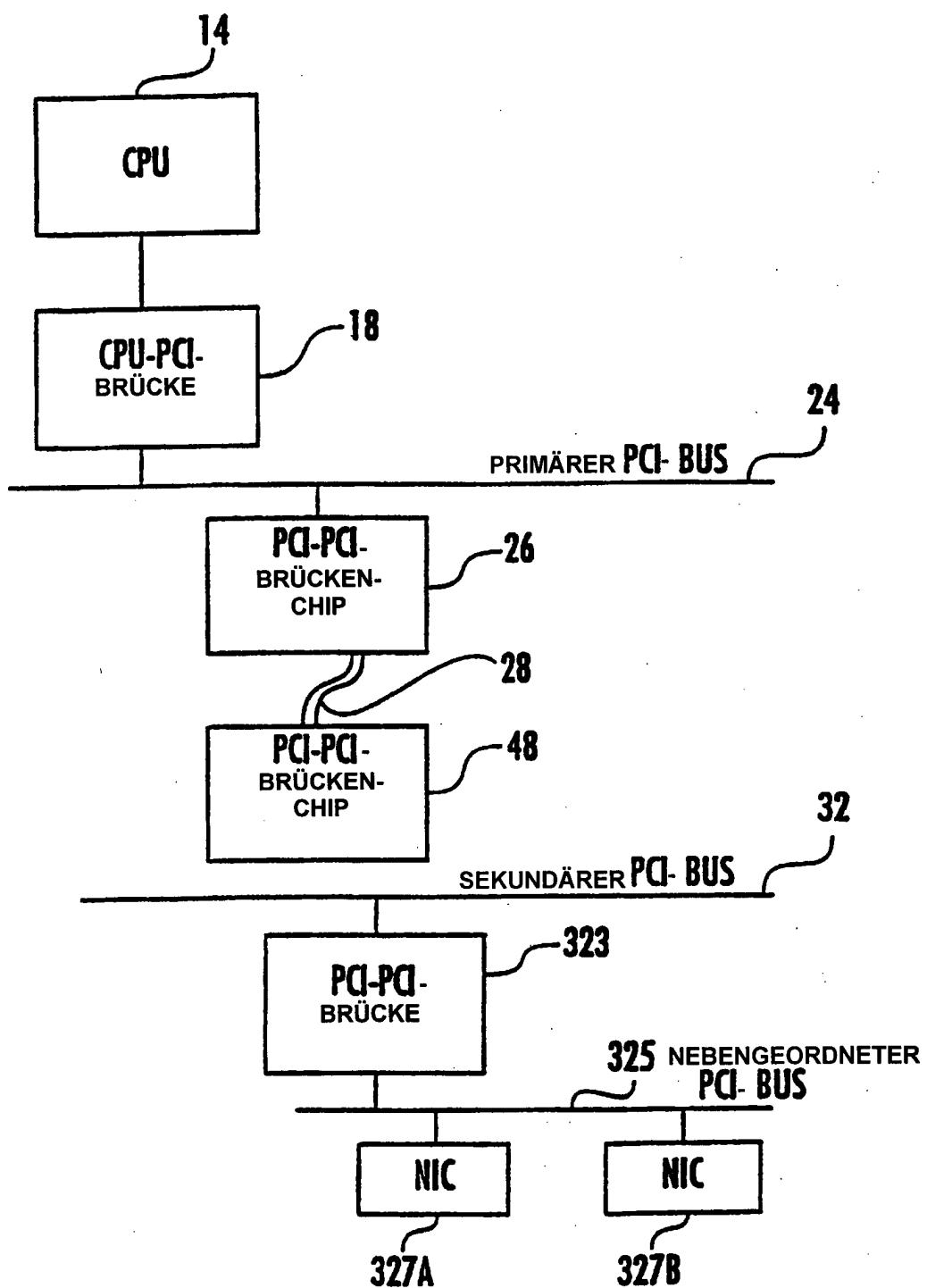

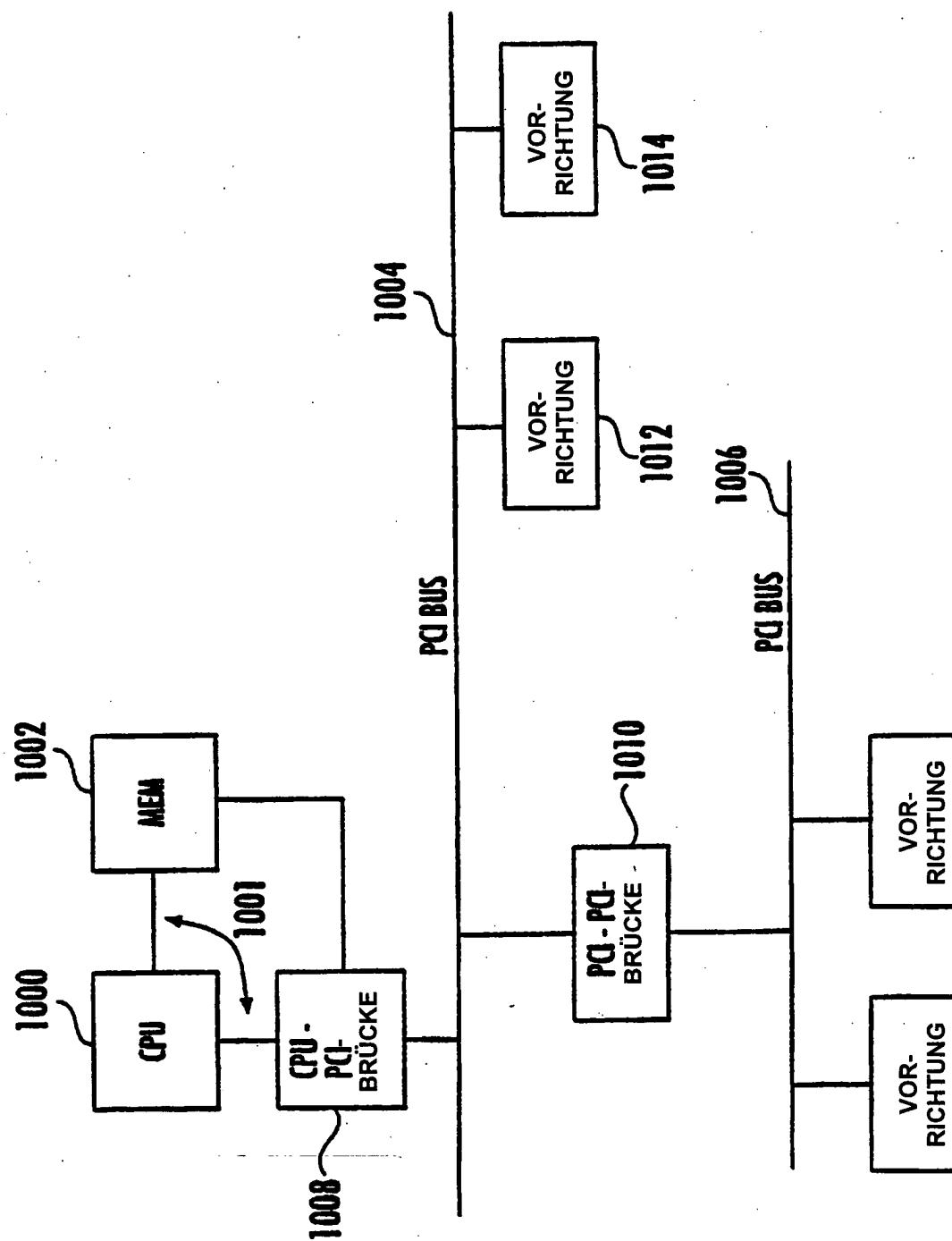

- [0052] **Fig. 26B** zeigt ein Blockdiagramm eines Computersystems mit Mehrfach-Schichten von Bussen.

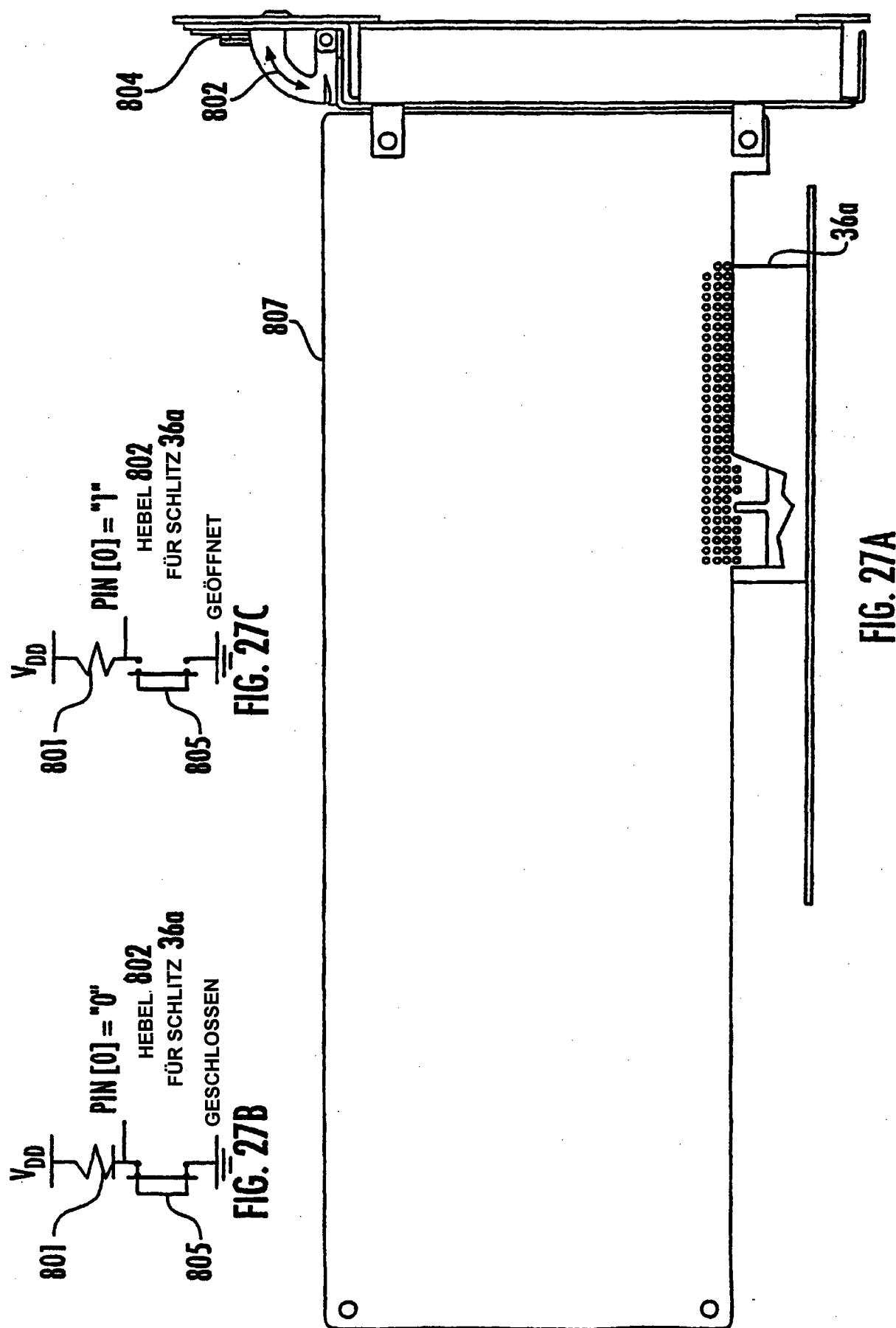

- [0053] **Fig. 27A** zeigt eine Seitenansicht einer Erweiterungskarte, eingesetzt in einen Schlitz.

- [0054] **Fig. 27B-C** zeigen schematische Diagramme einer Hebel-Schaltung.

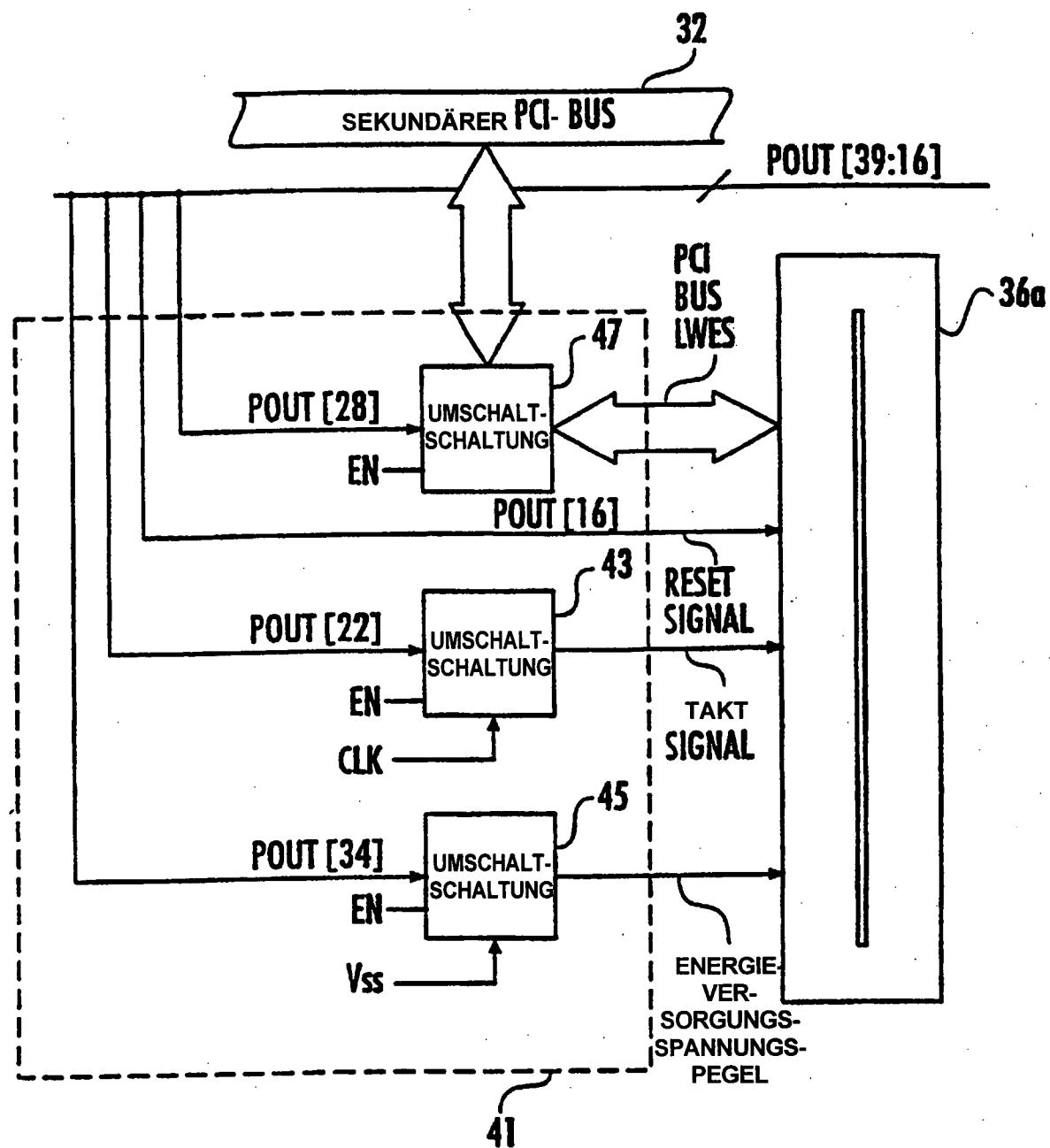

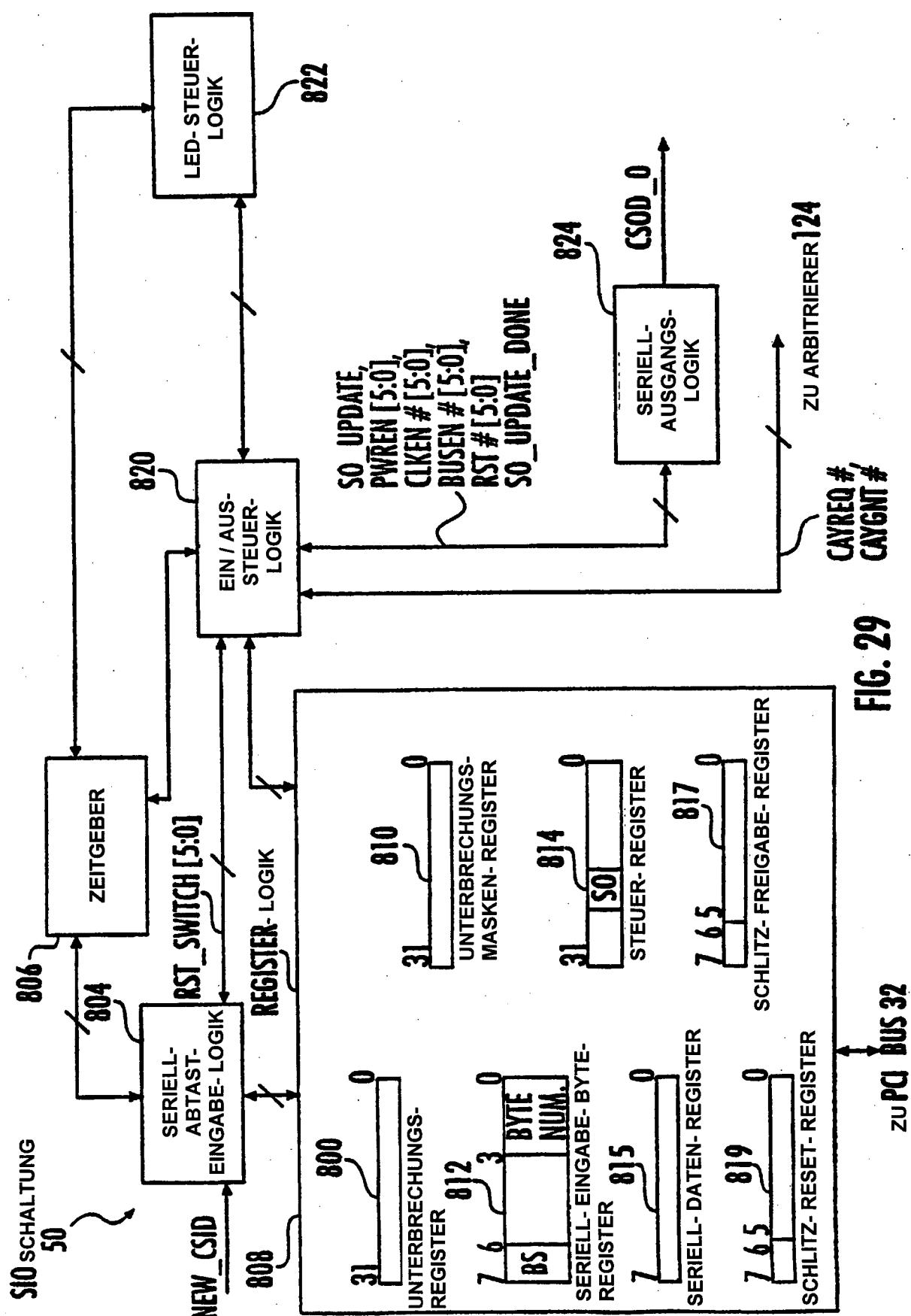

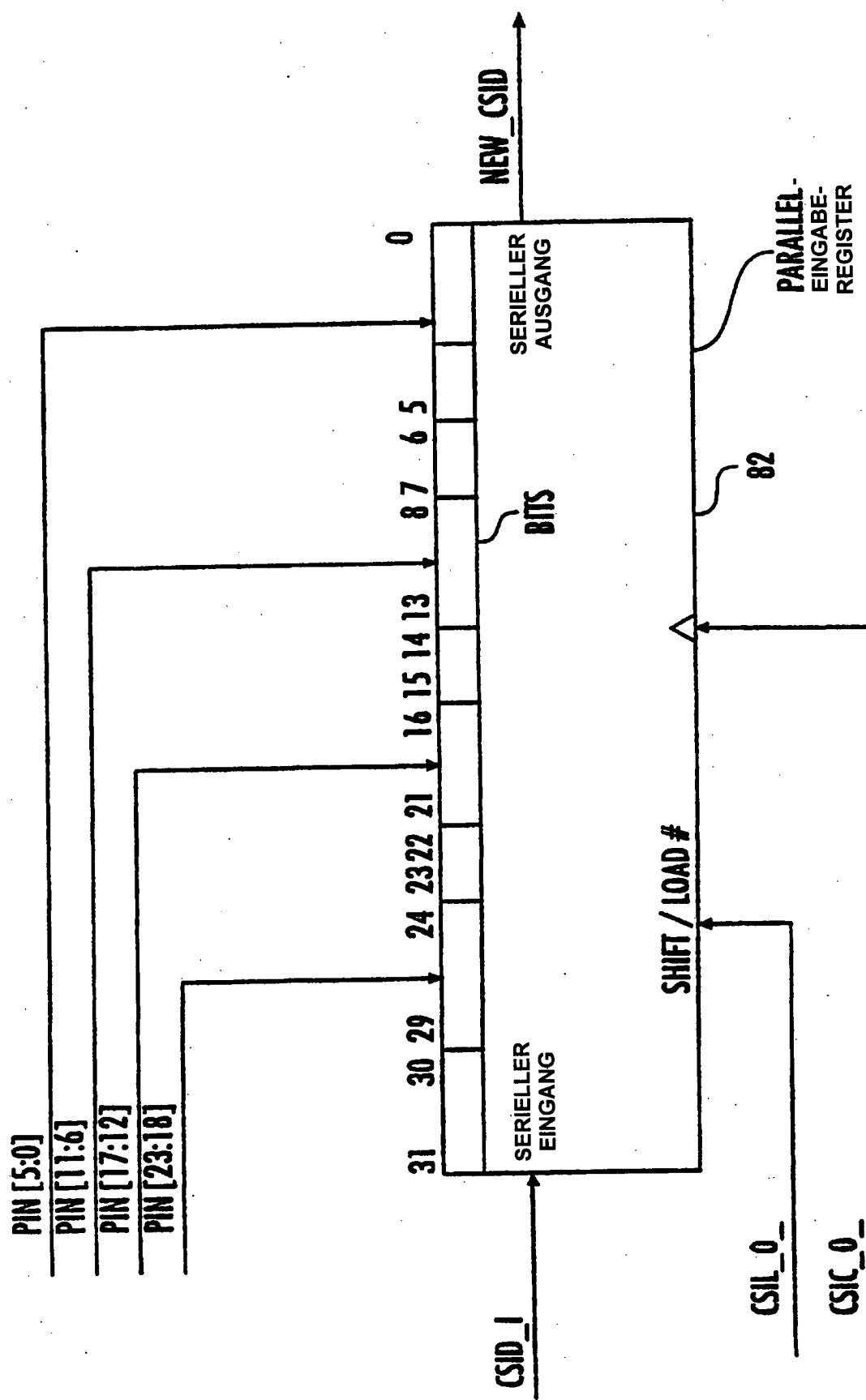

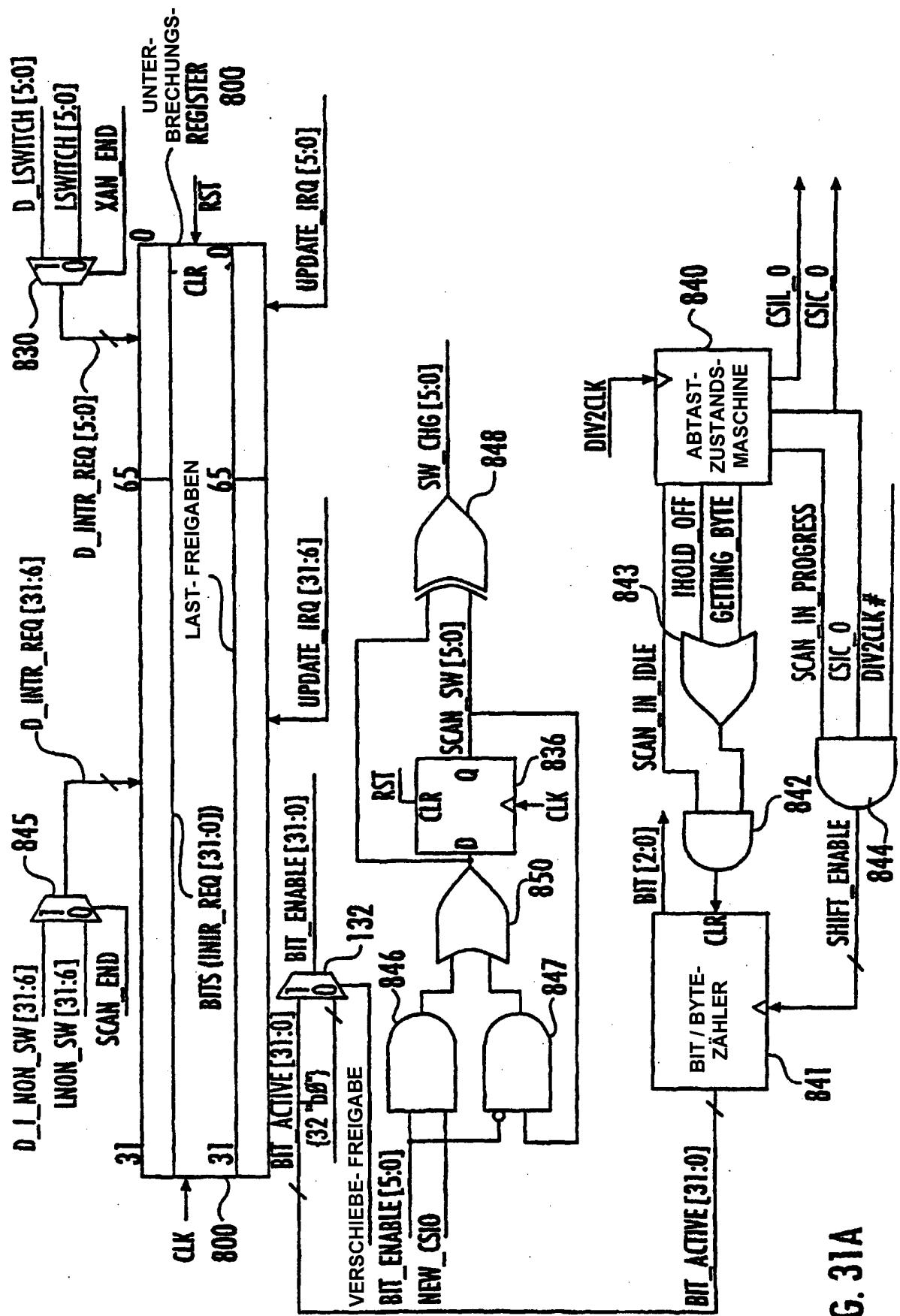

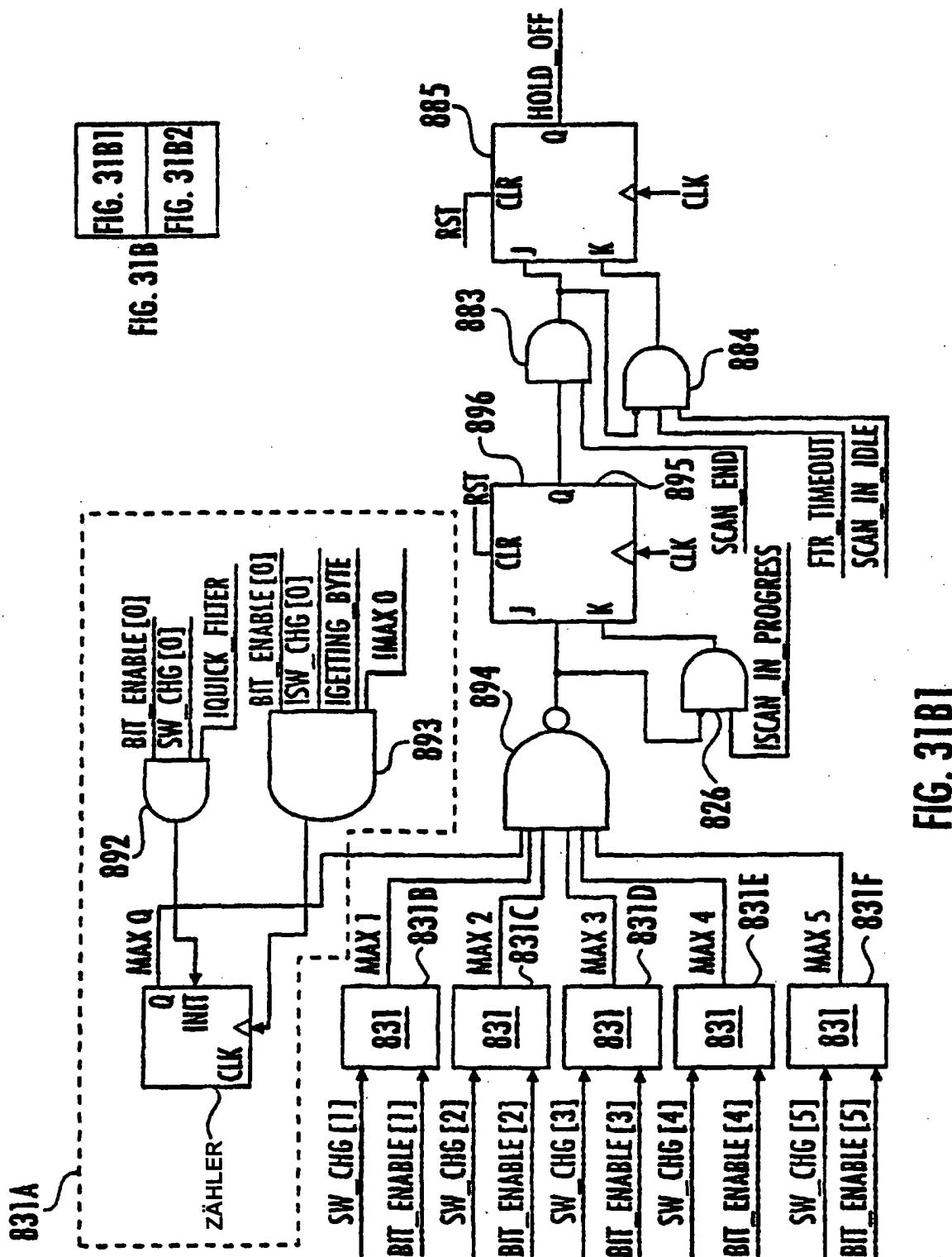

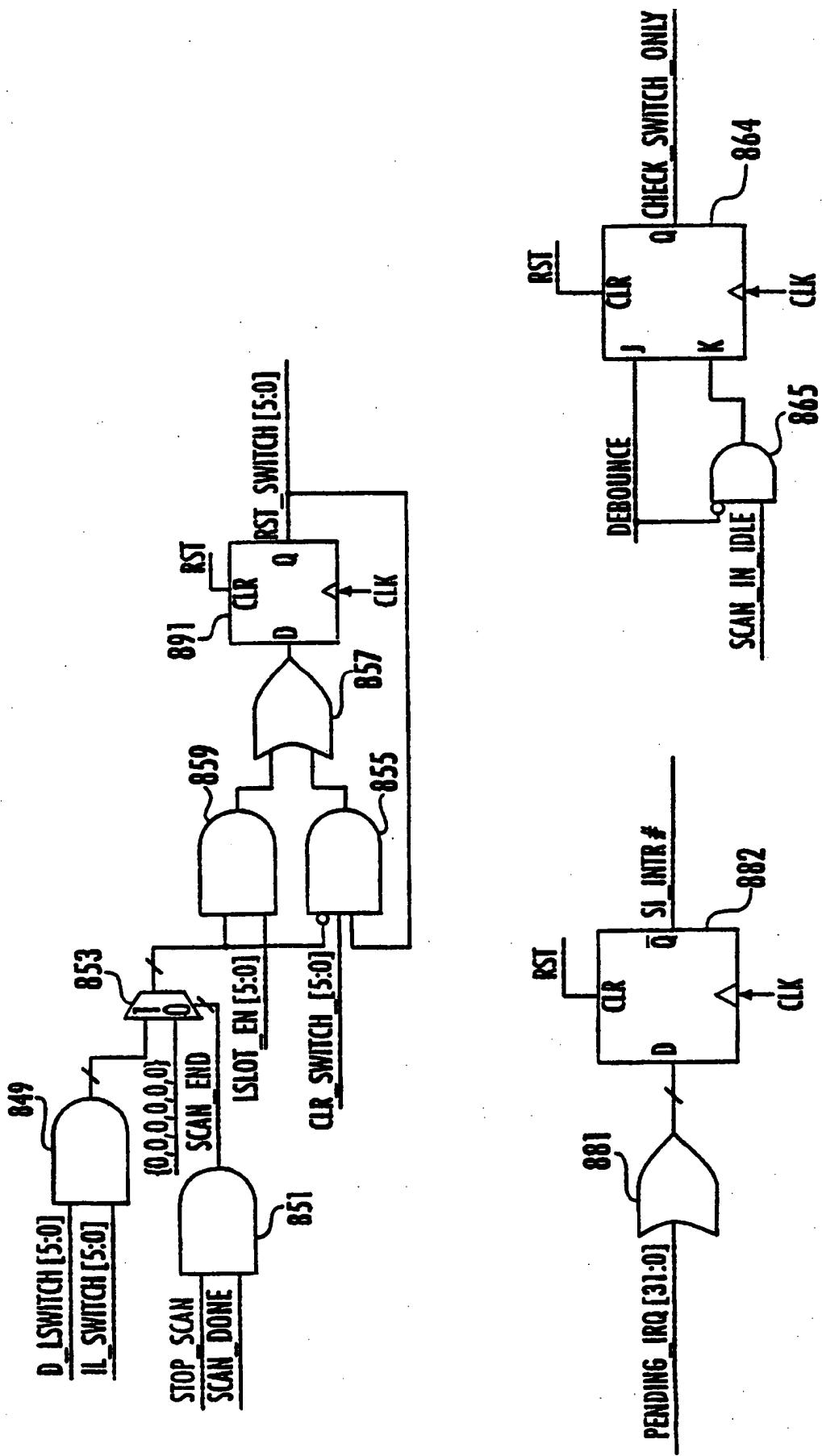

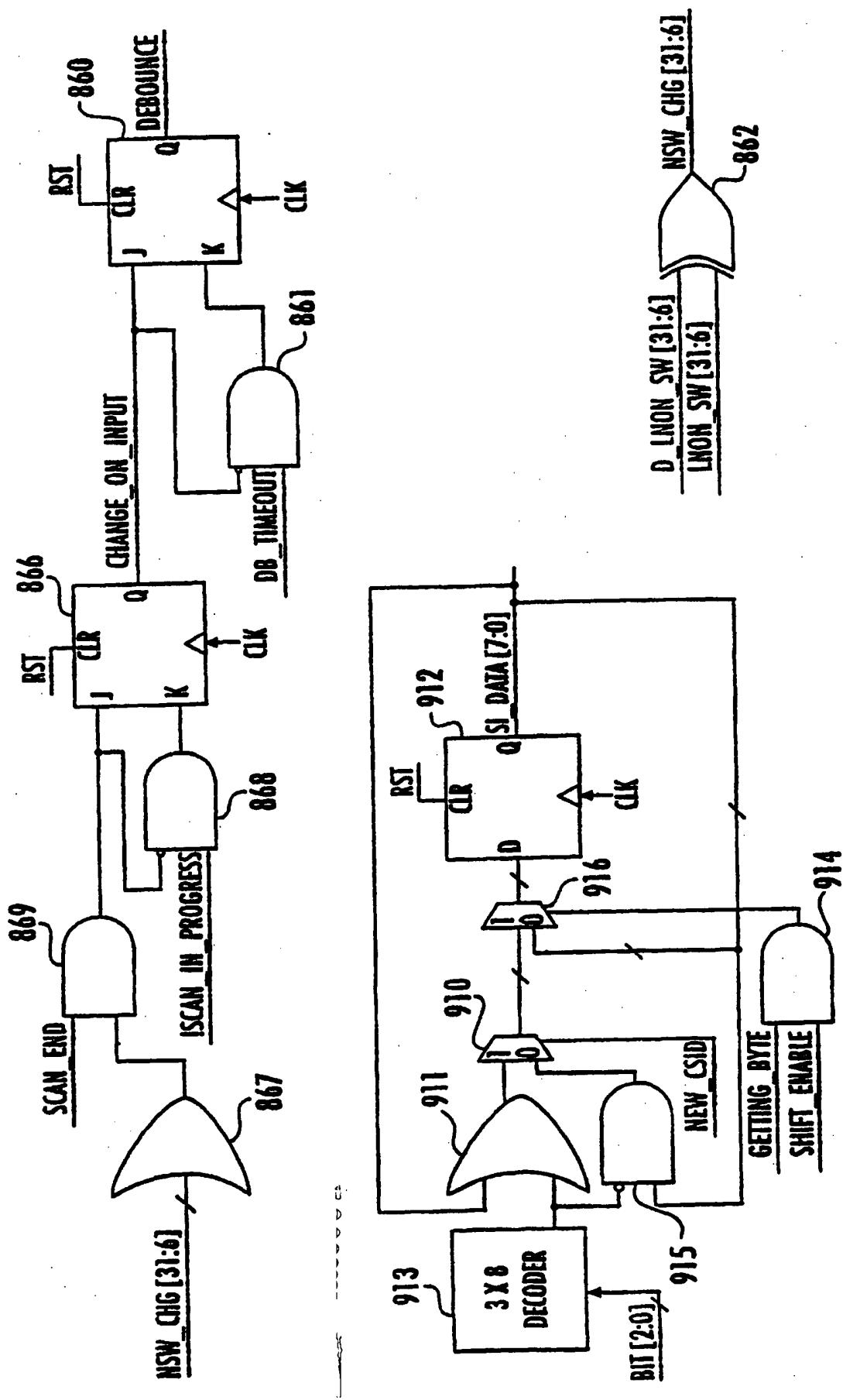

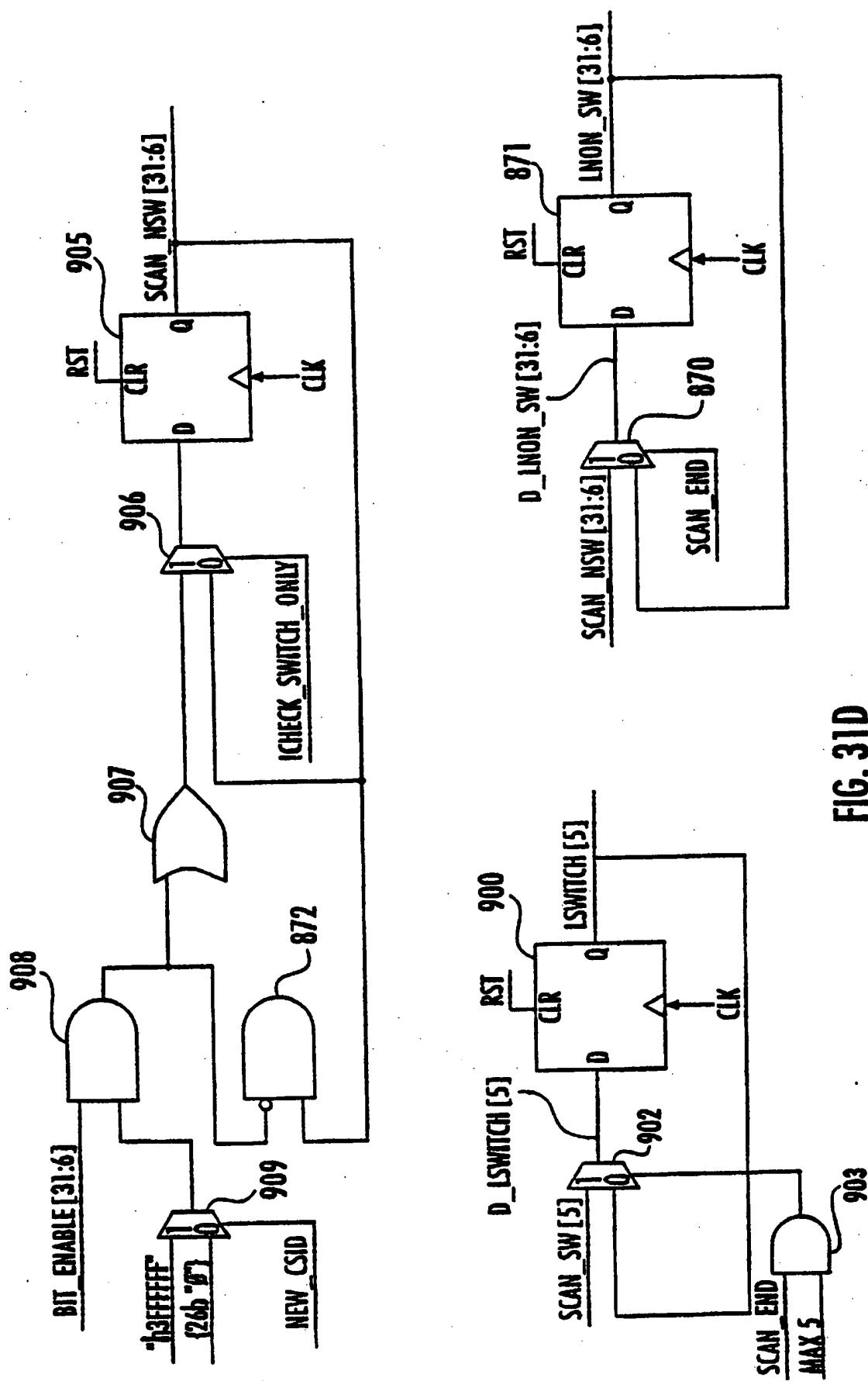

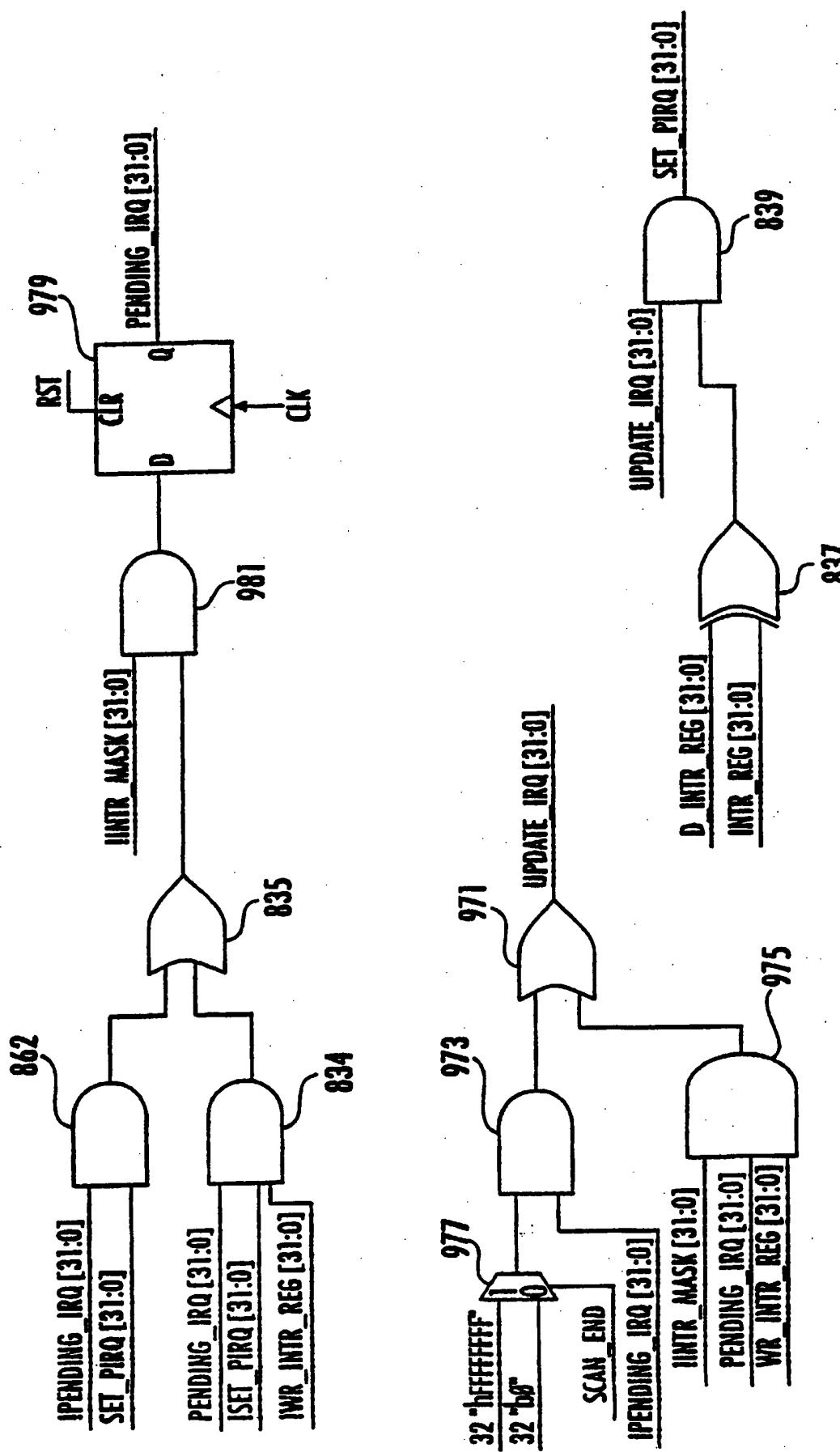

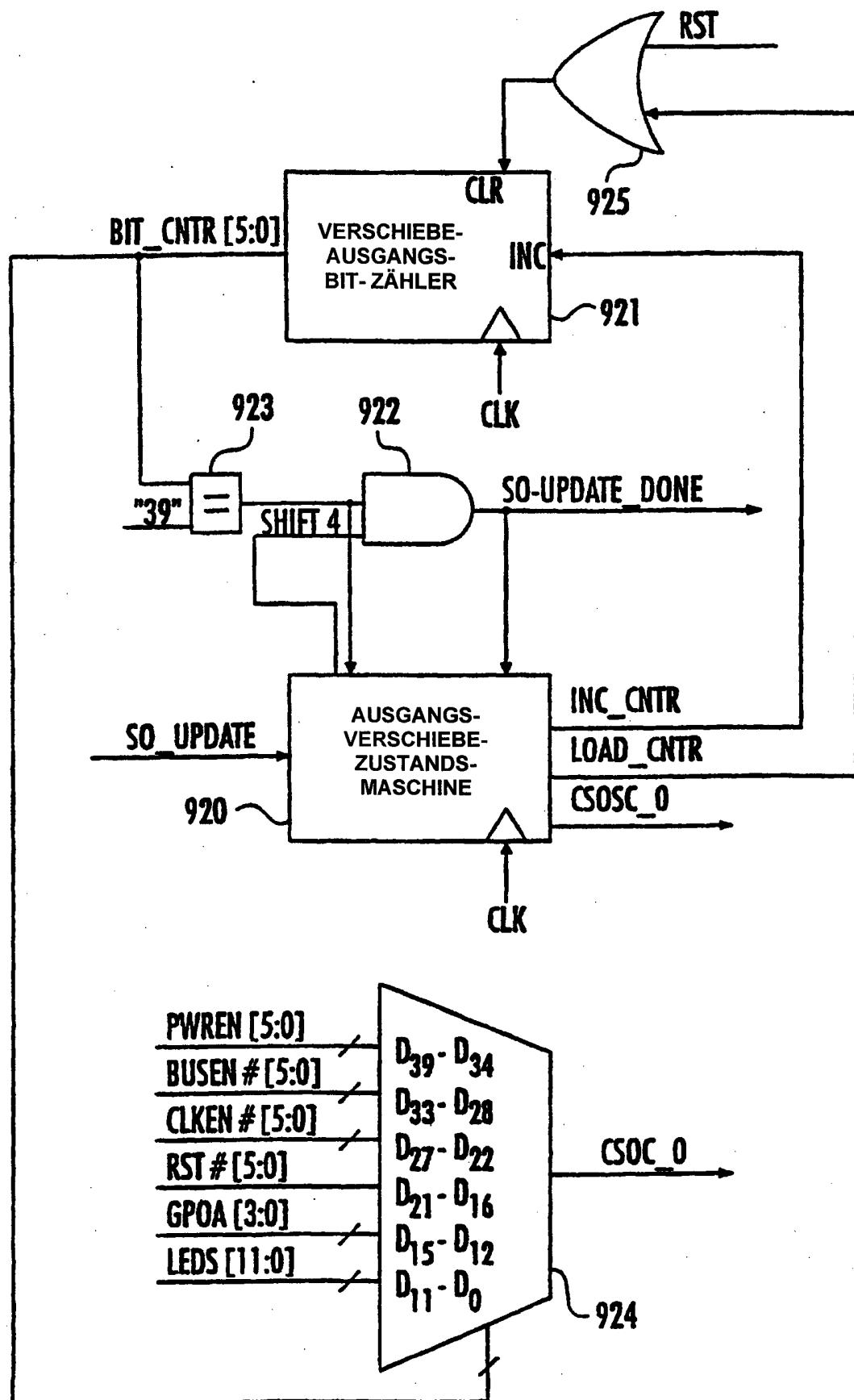

- [0055] Fig. 28–31 zeigen schematische Diagramme einer Schaltung des Erweiterungskastens.

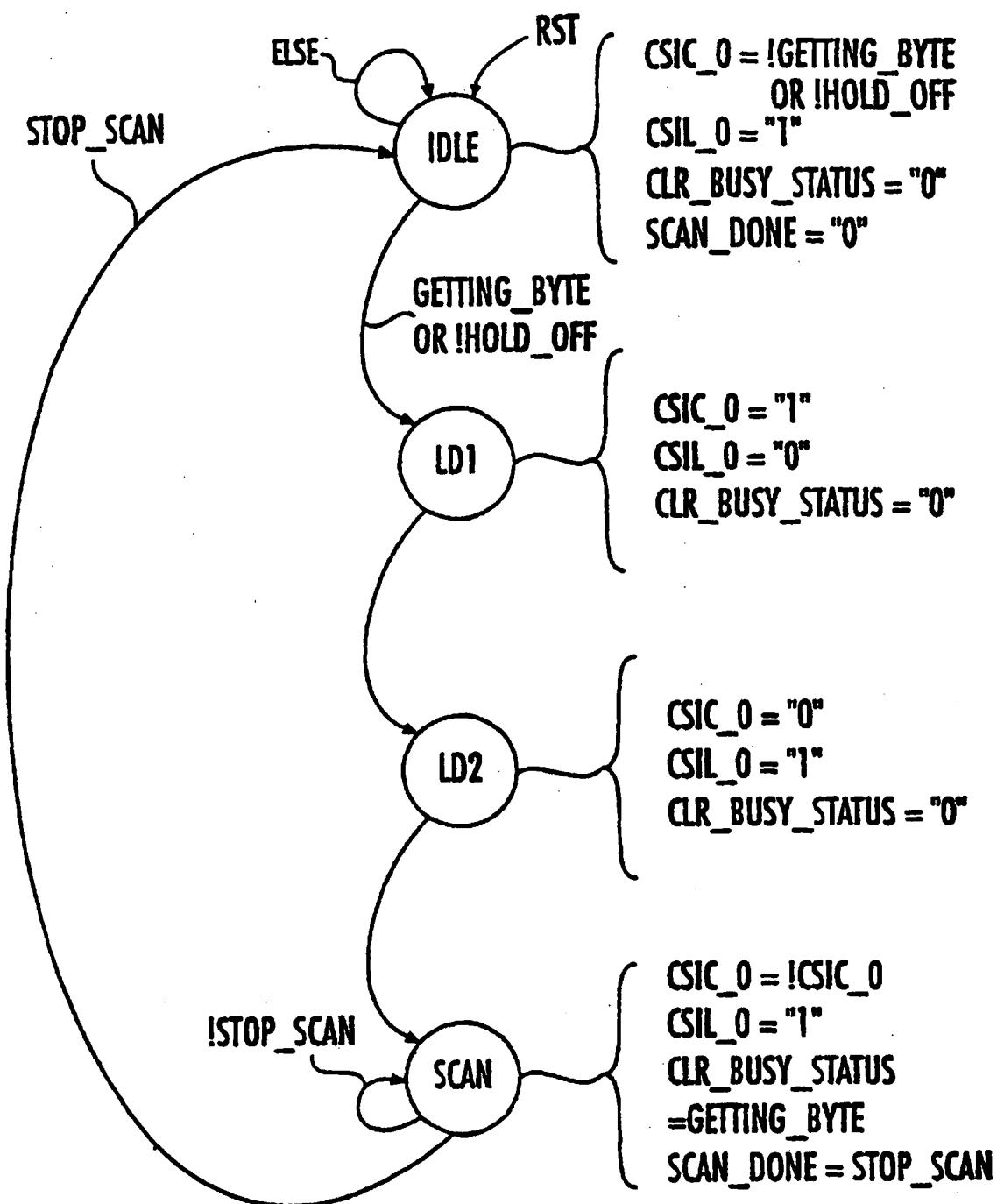

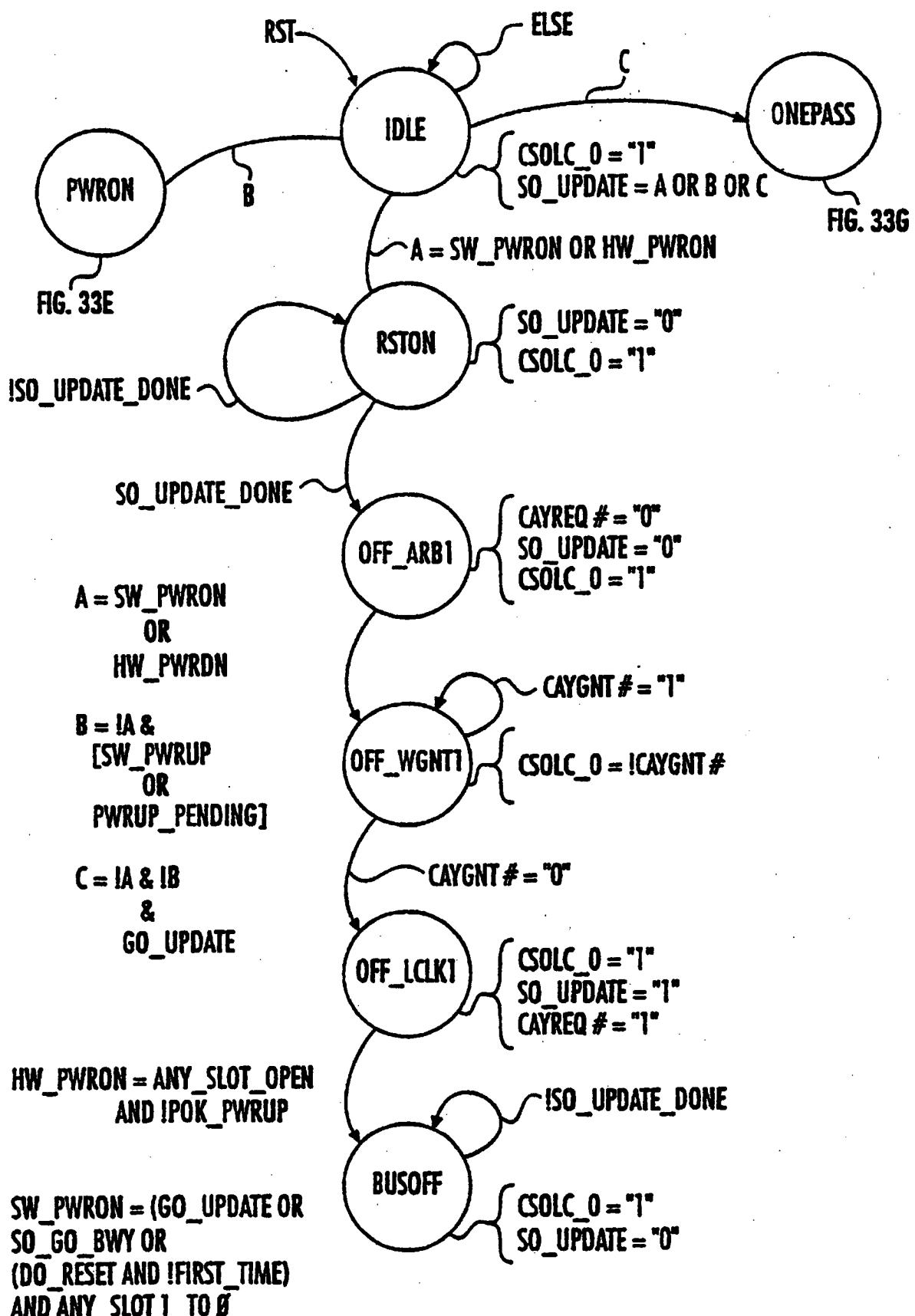

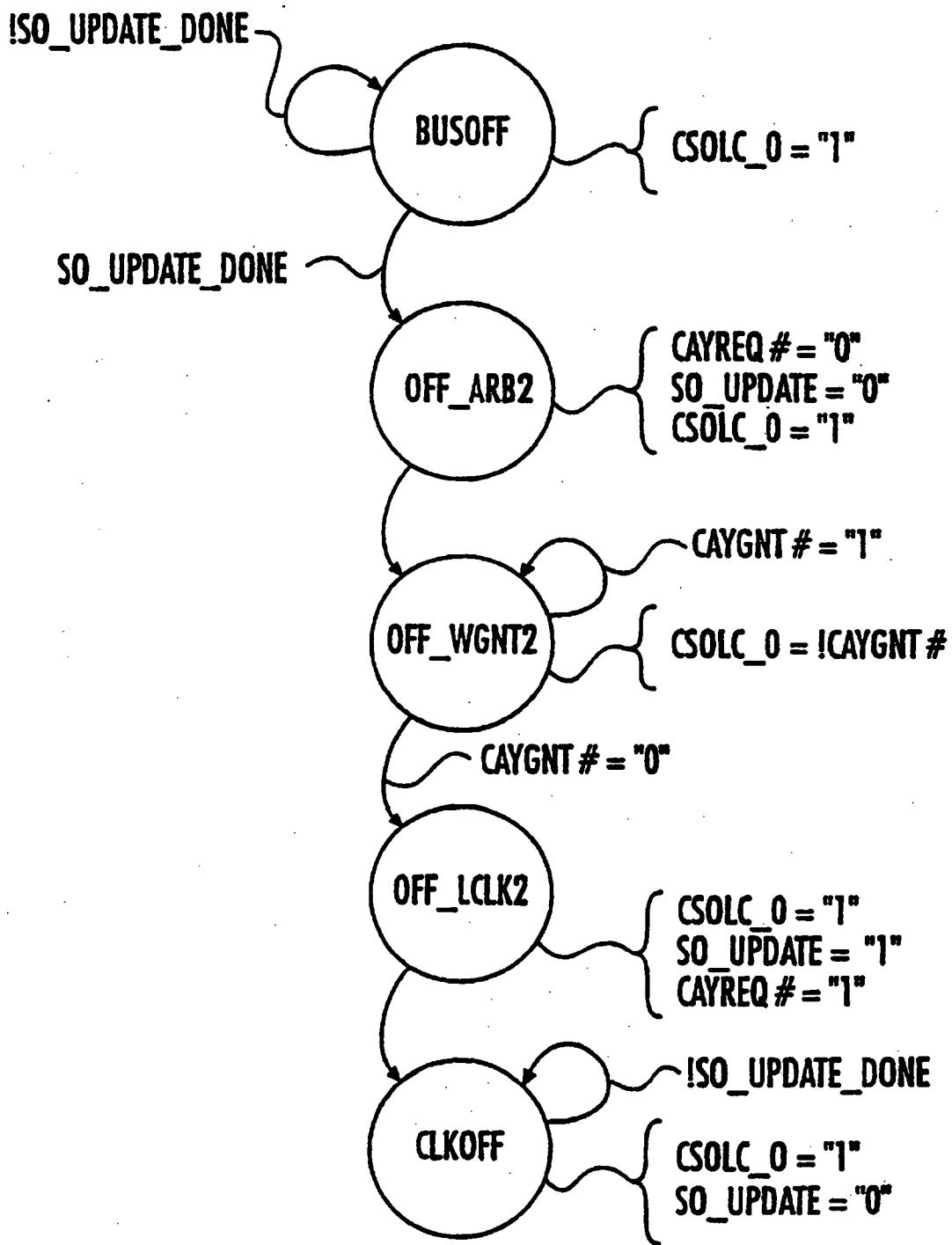

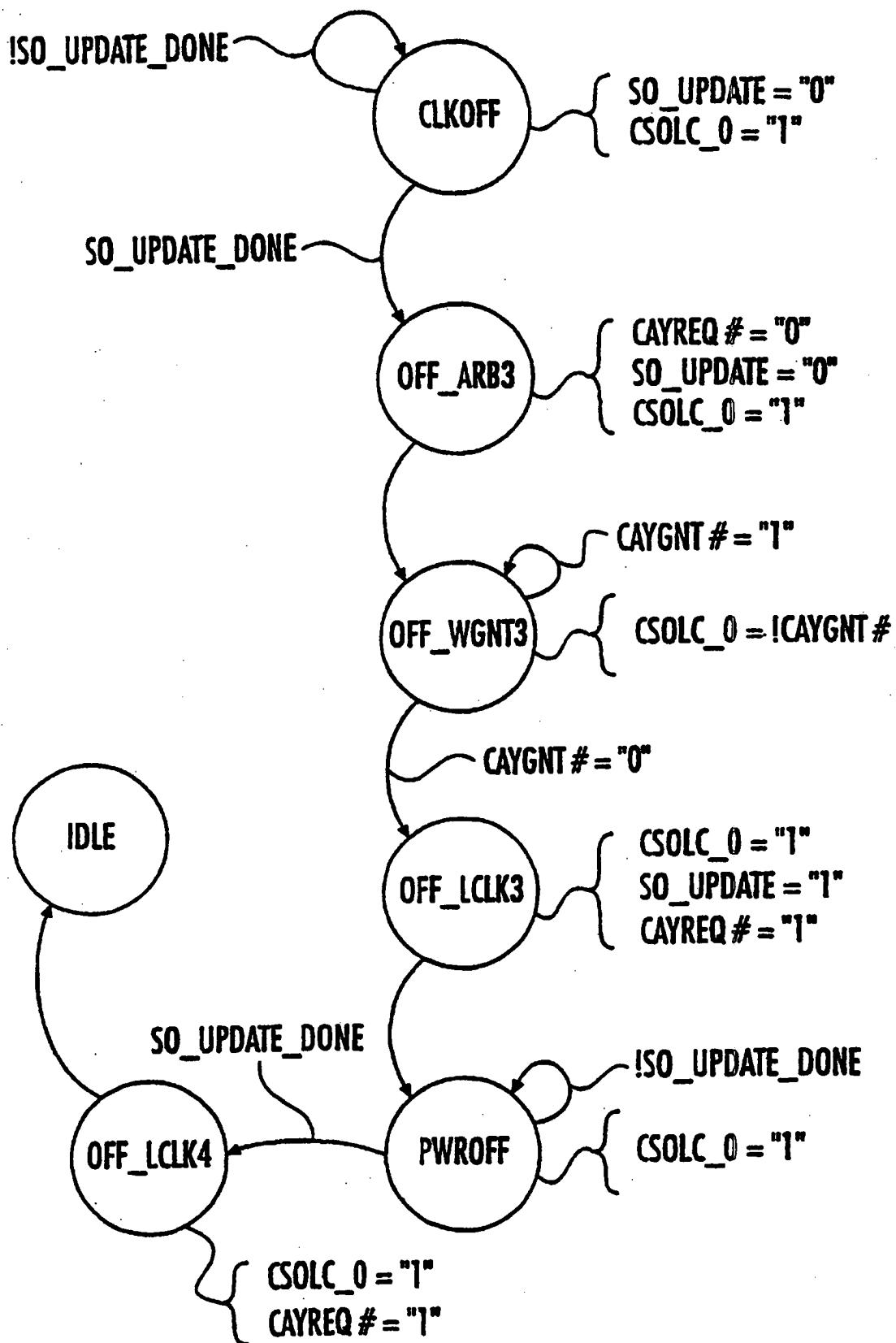

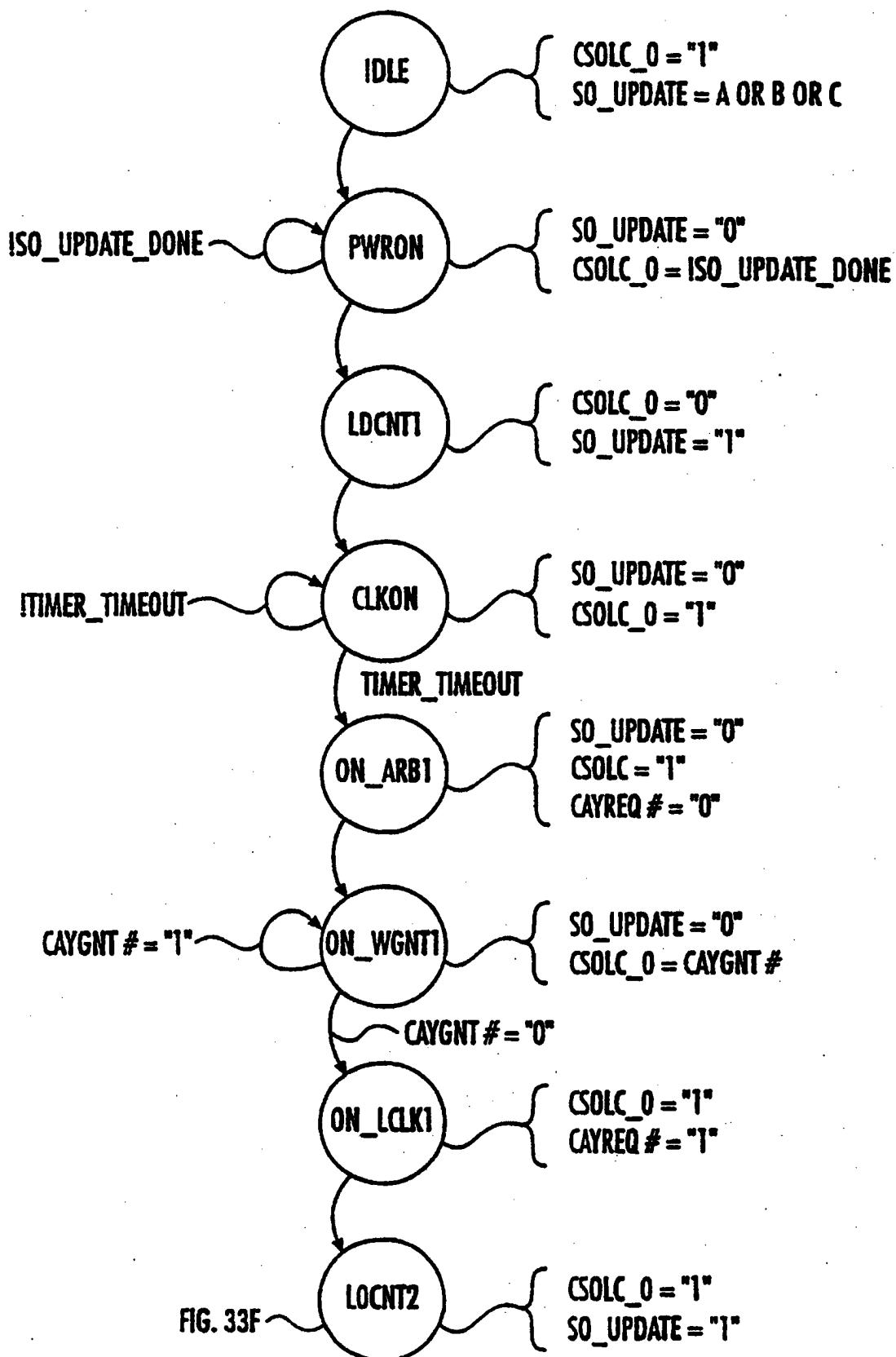

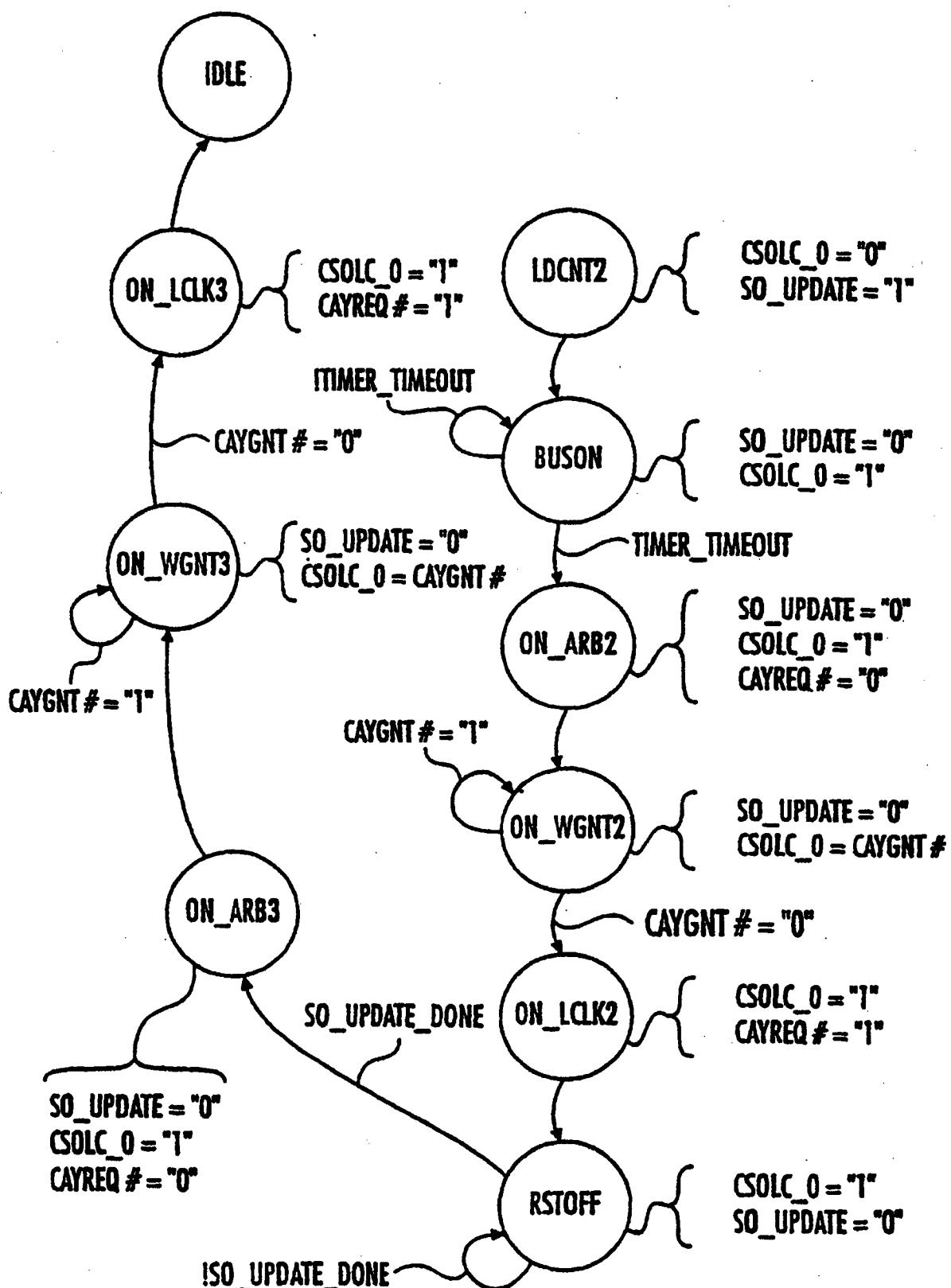

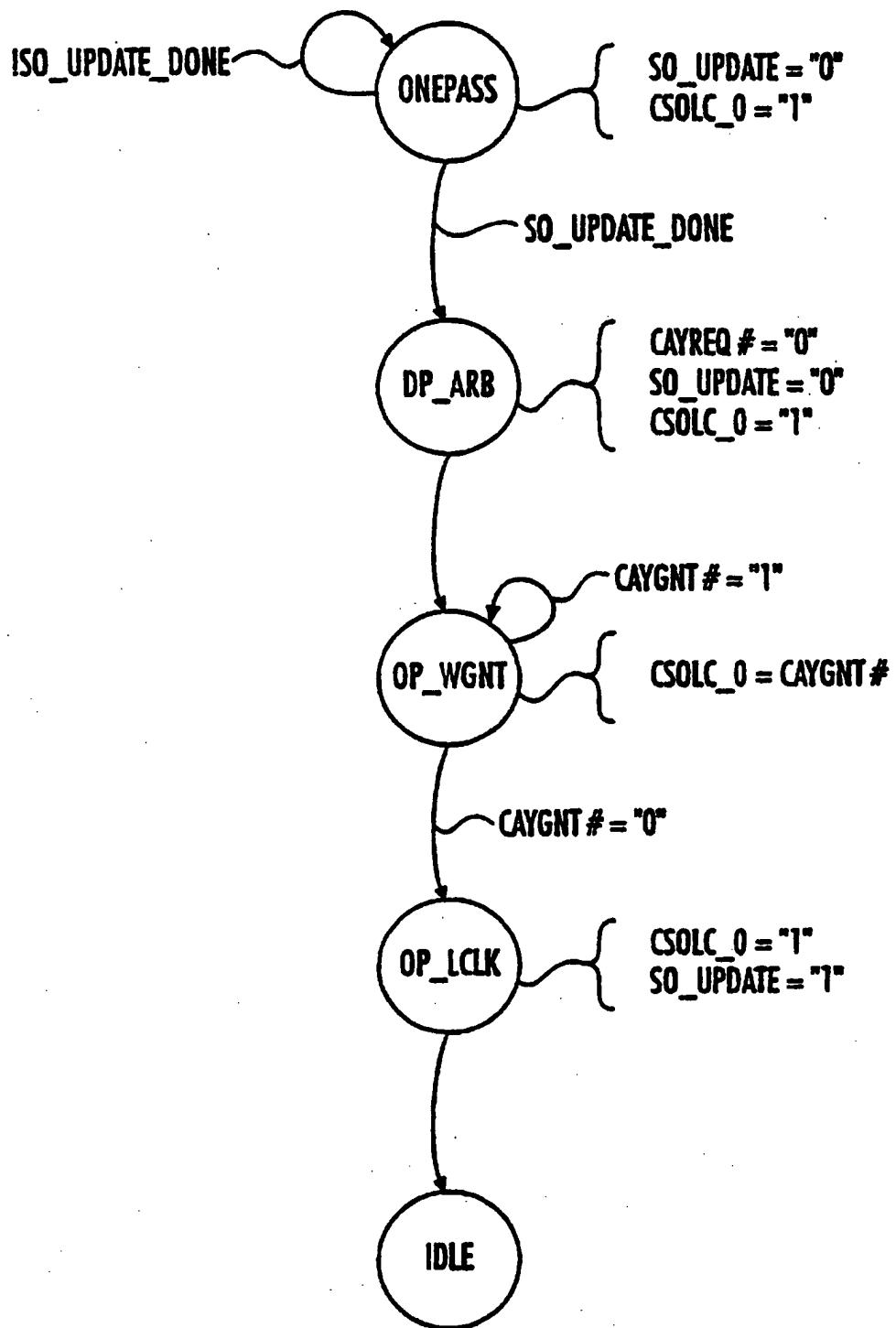

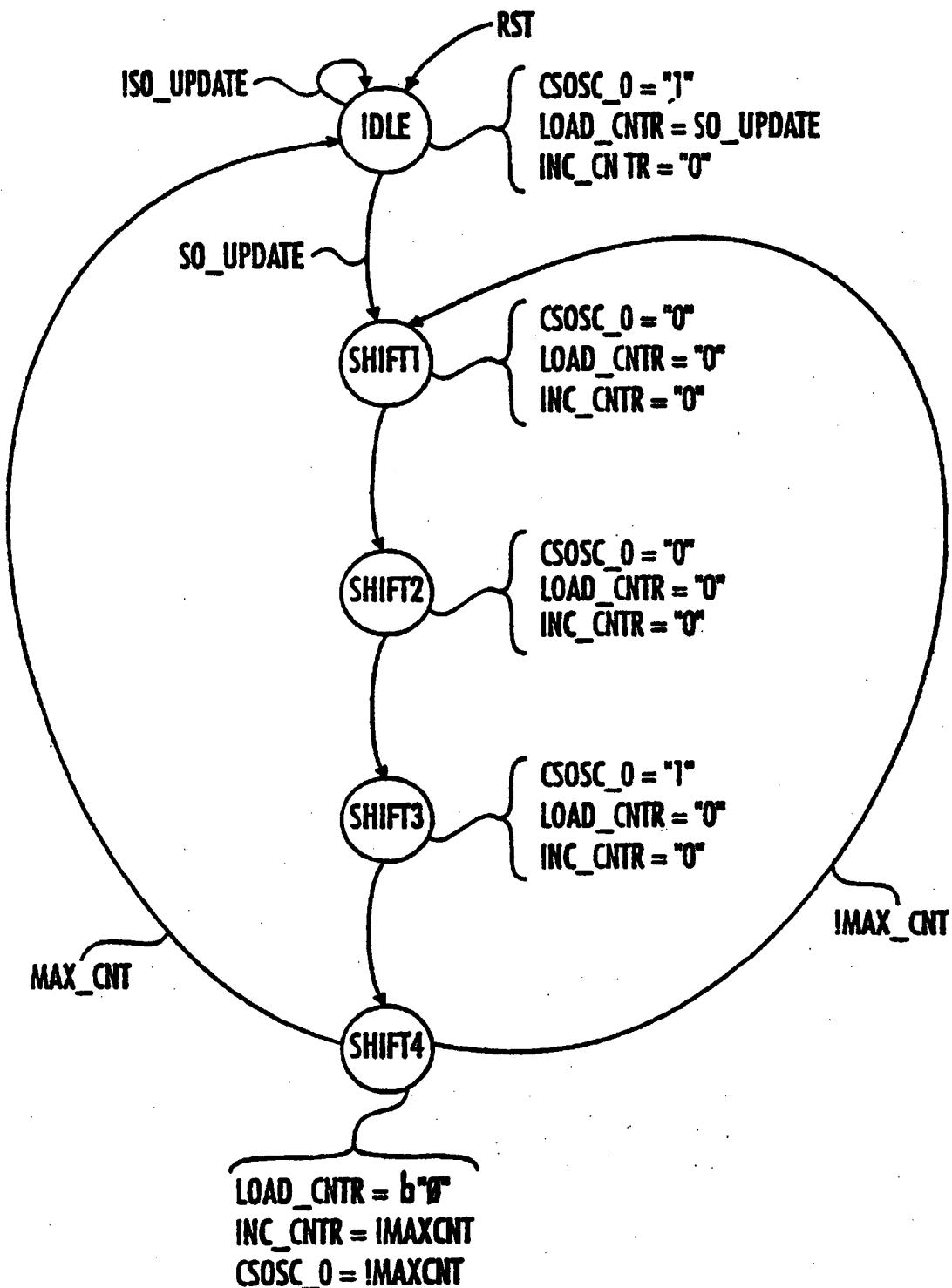

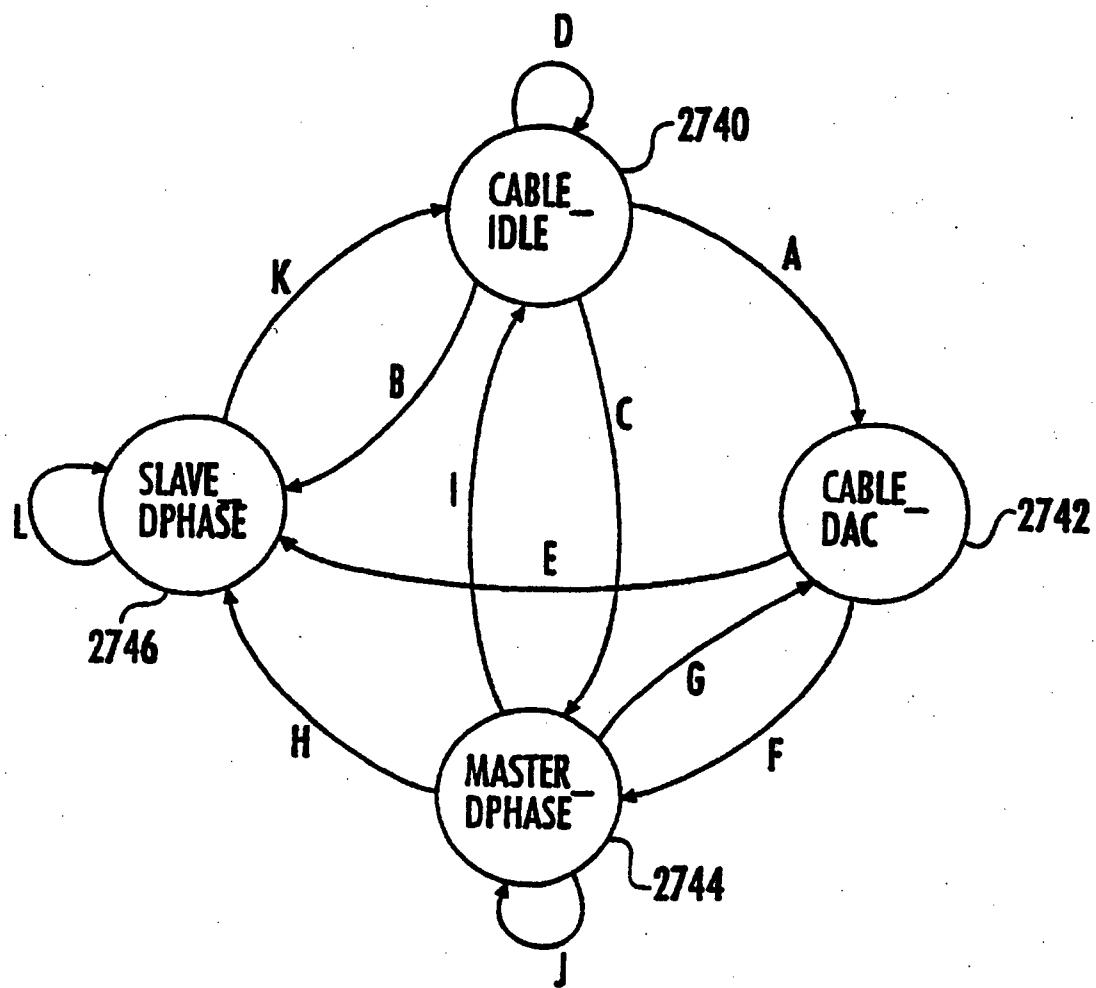

- [0056] **Fig. 32A** zeigt ein Zustandsdiagramm von der Schaltung des Erweiterungskastens.

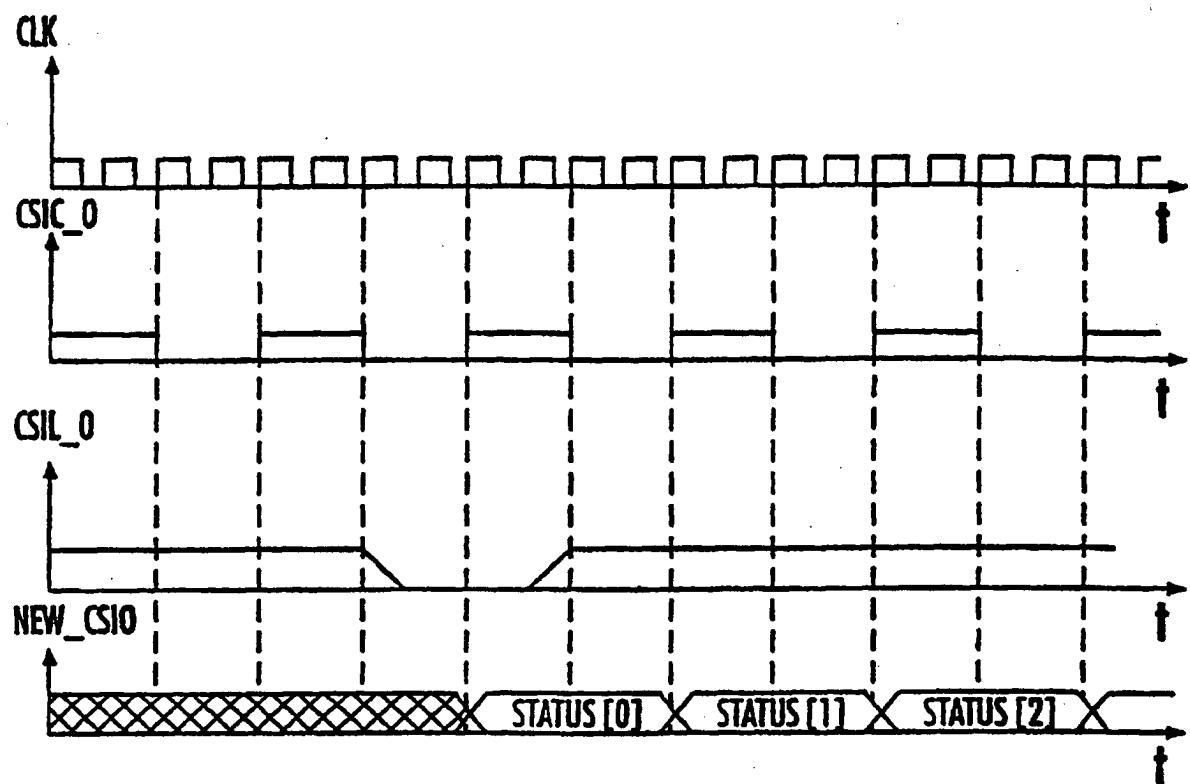

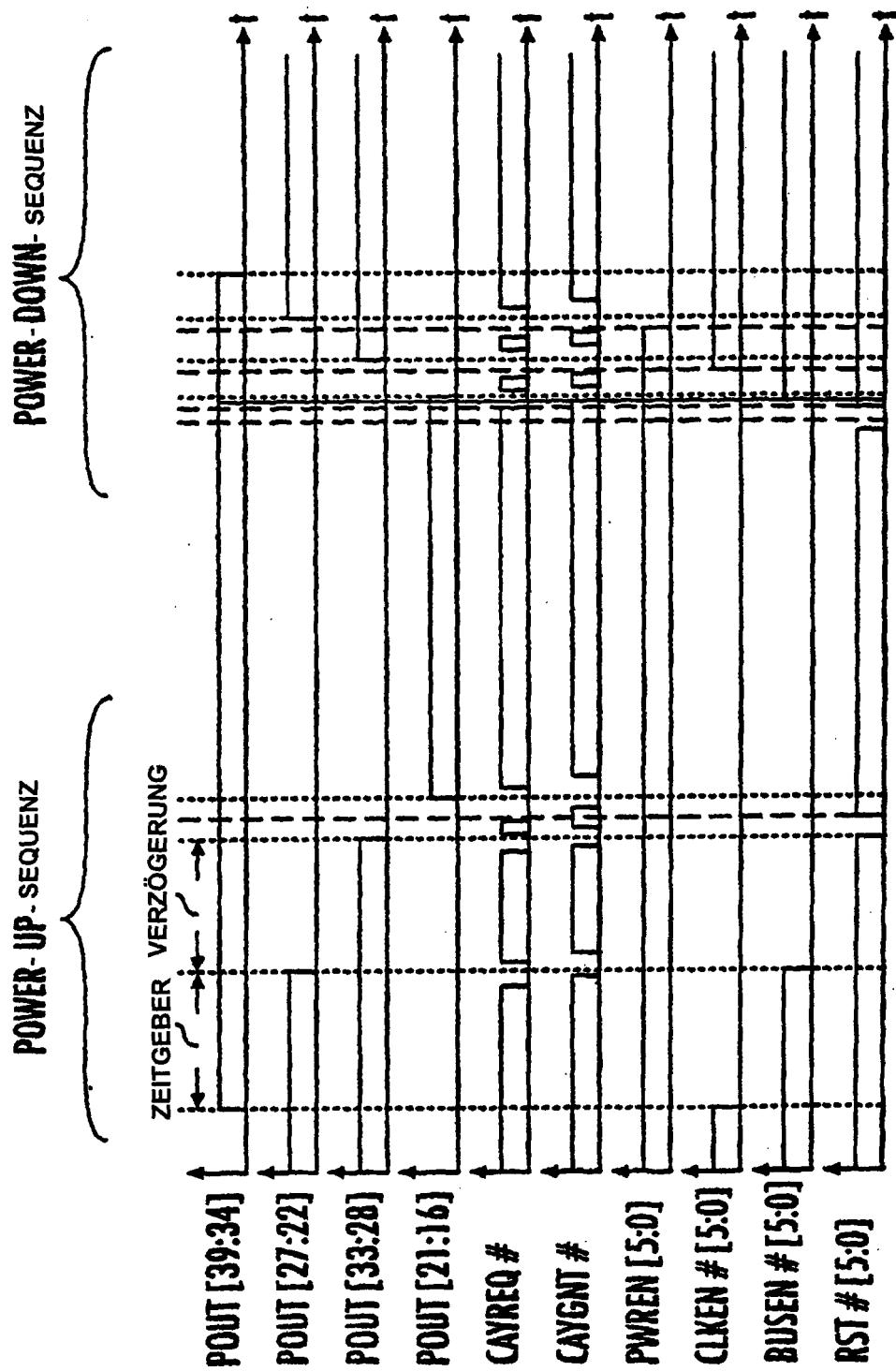

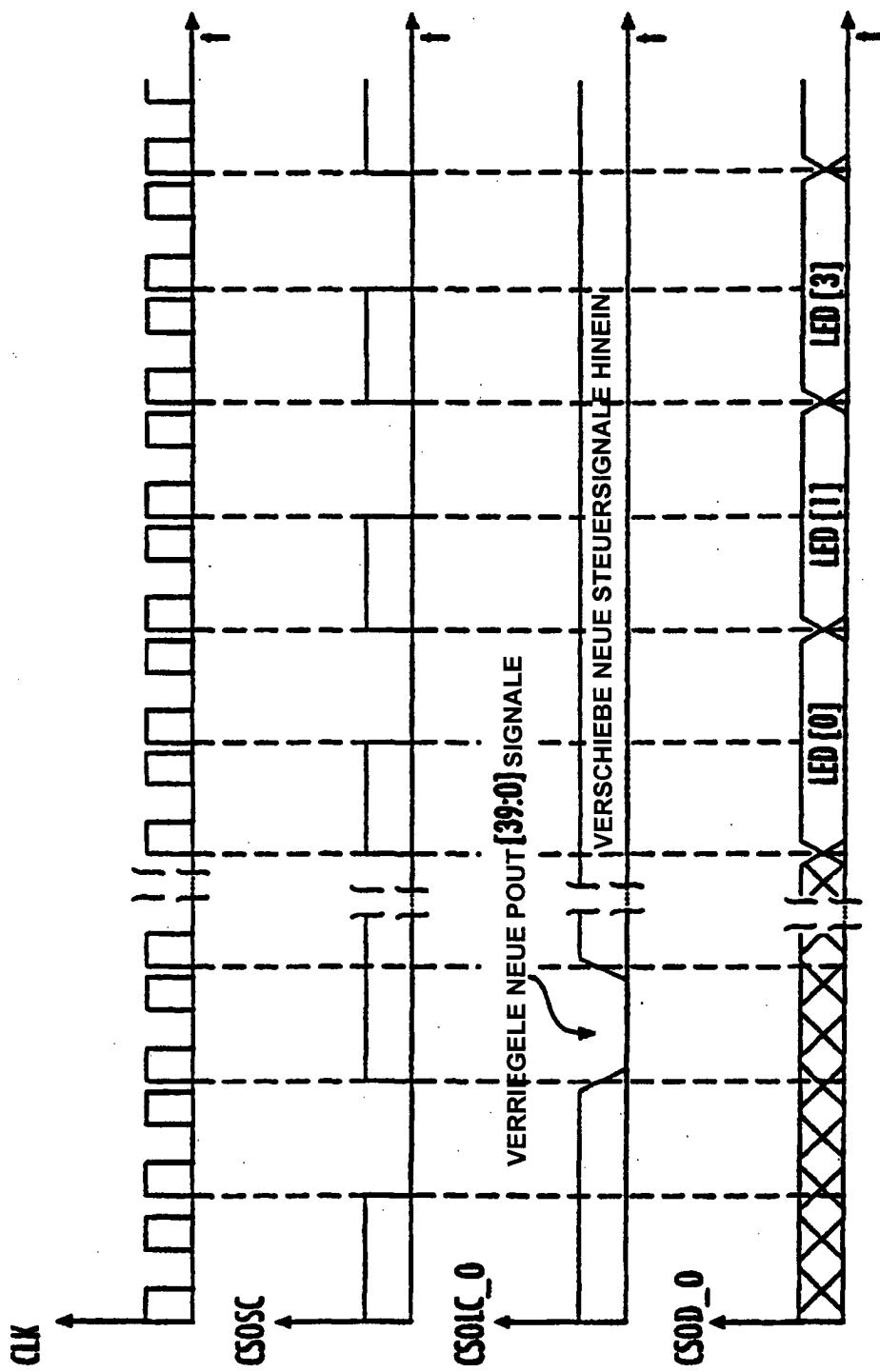

- [0057] **Fig. 32B** zeigt Wellenformen für die Schaltung des Erweiterungskastens.

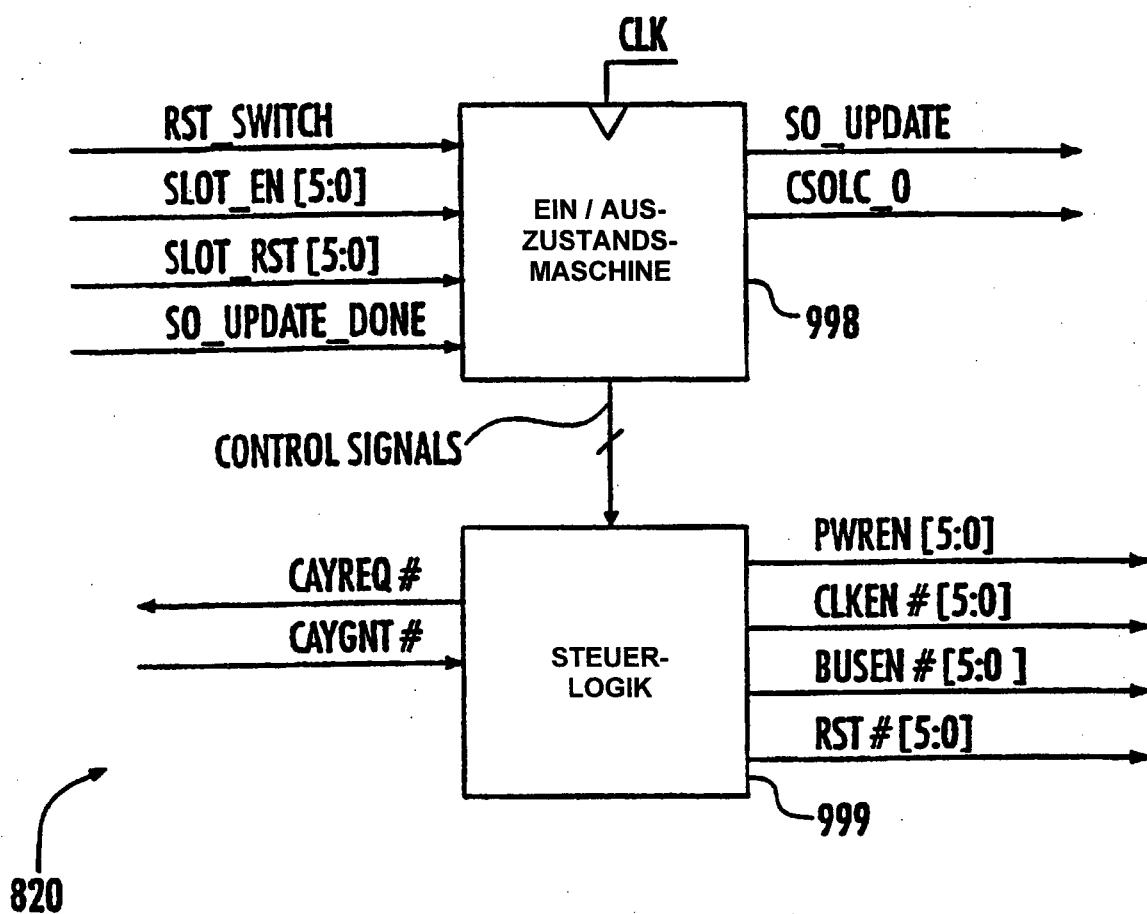

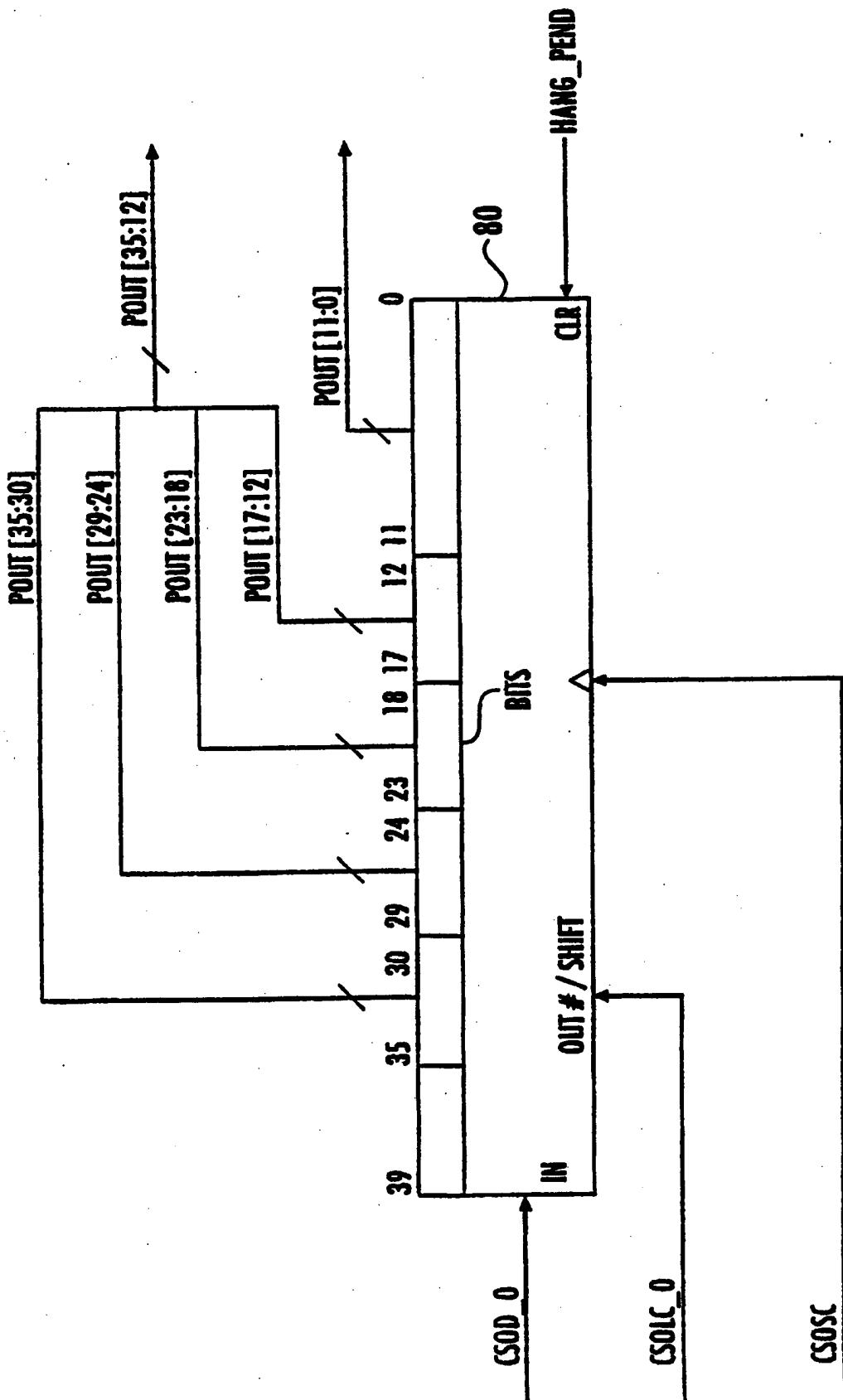

- [0058] **Fig. 33A** zeigt ein schematisches Diagramm einer Schaltung des Erweiterungskastens.

- [0059] **Fig. 33B** zeigt Wellenformen für die Schaltung des Erweiterungskastens.

- [0060] **Fig. 33C-H** zeigen ein Zustandsdiagramm von der Schaltung des Erweiterungskastens.

- [0061] **Fig. 34** zeigt ein schematisches Diagramm einer Schaltung des Erweiterungskastens.

- [0062] **Fig. 35A** zeigt ein Zustandsdiagramm von der Schaltung des Erweiterungskastens.

- [0063] **Fig. 35B** zeigt Wellenformen von der Schaltung des Erweiterungskastens.

- [0064] **Fig. 36** zeigt ein schematisches Diagramm einer Schaltung des Erweiterungskastens.

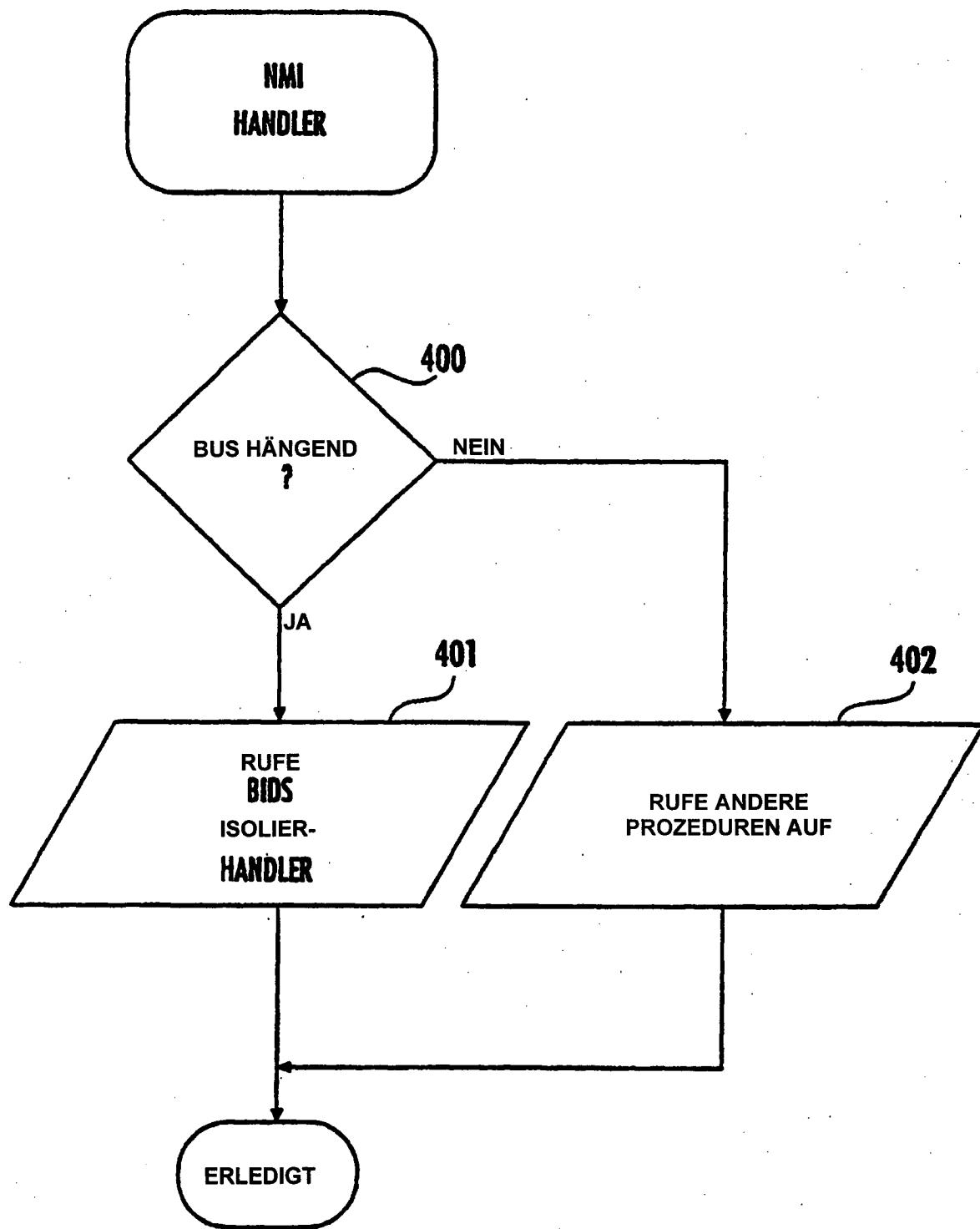

- [0065] **Fig. 37** zeigt ein Flußdiagramm eines nicht-maskierbaren Unterbrecher-Handler's, aufgerufen in Abhängigkeit einer Erfassung eines Bus-Hängend-Zustands in dem Computer-System.

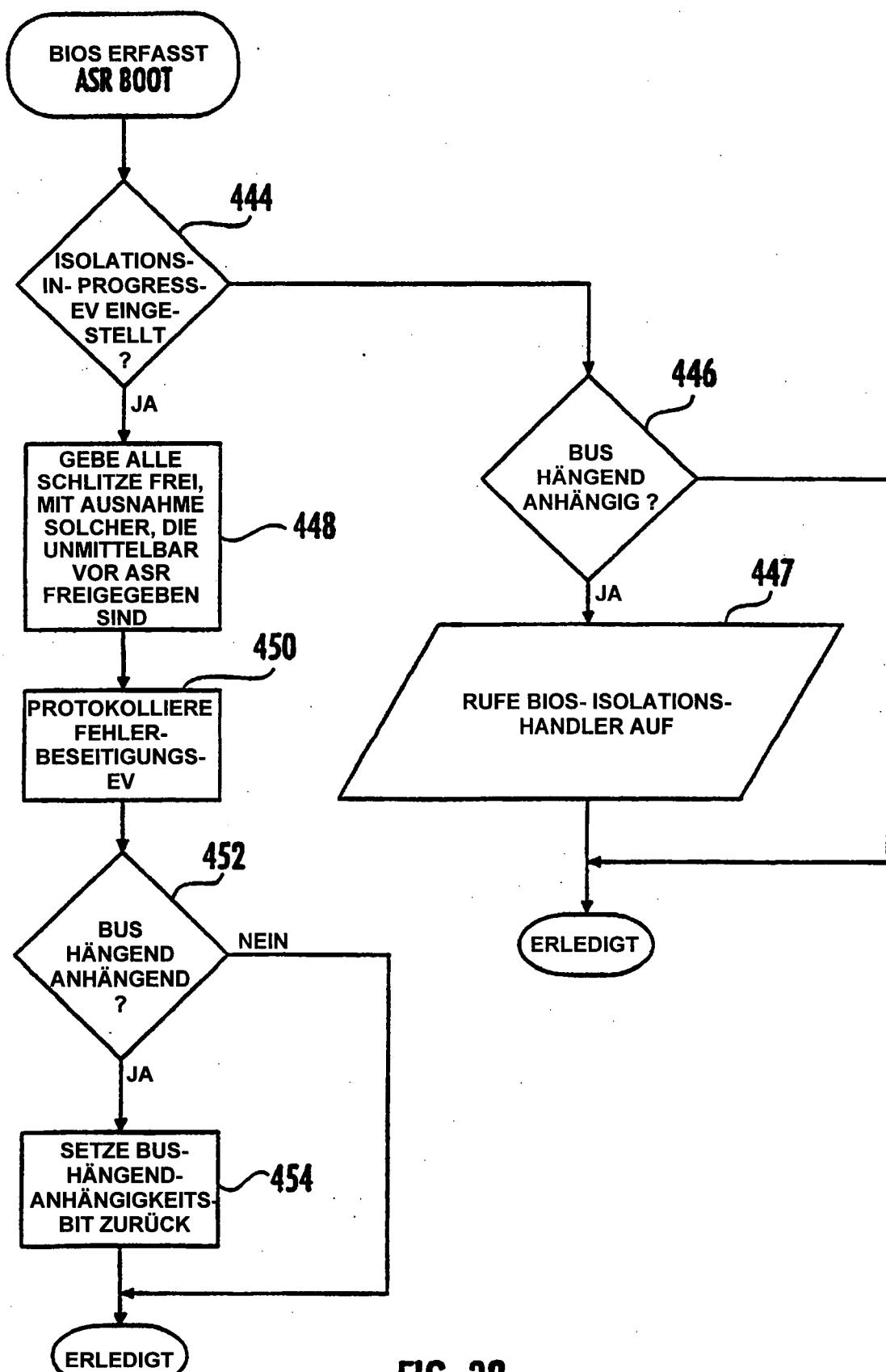

- [0066] **Fig. 38** zeigt ein Fluß-Diagramm eines BIOS-Programms, das durch ein Computersystem-Durchsichts-Ereignis aufgerufen wird.

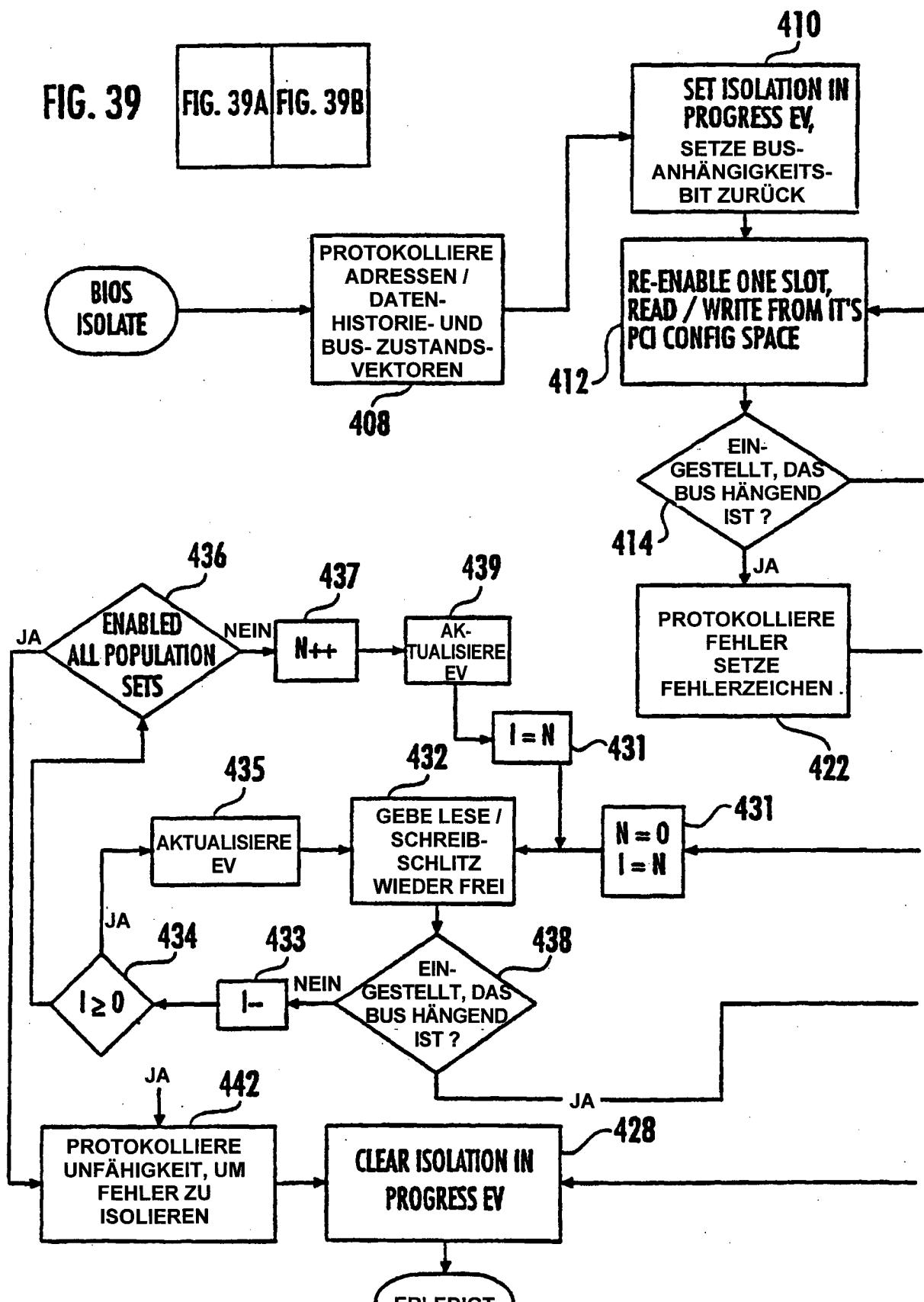

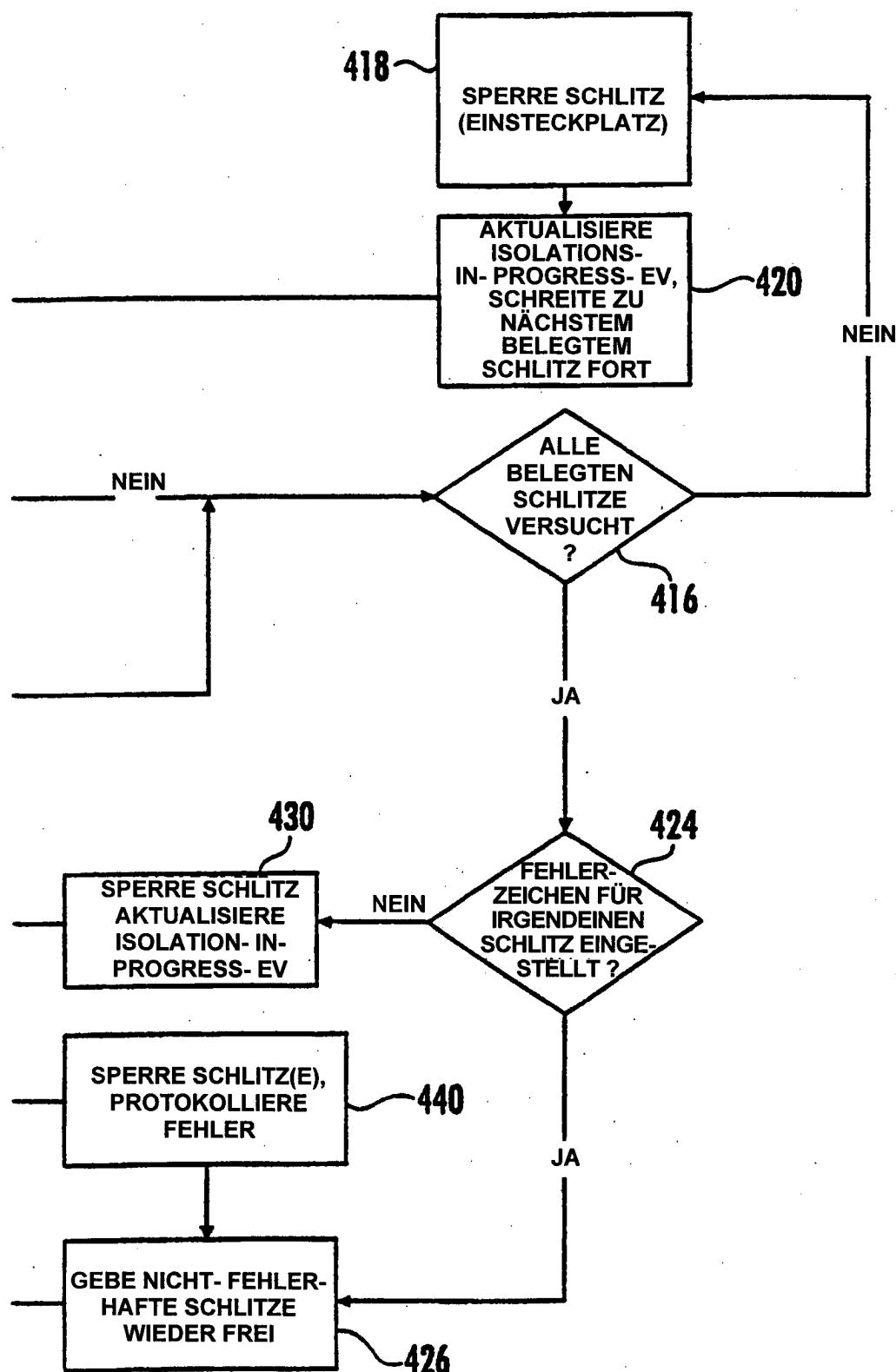

- [0067] **Fig. 39** zeigt ein Fluß-Diagramm eines BIOS-Isolier-Programms, aufgerufen auf einen Bus-Hängend-Zustand oder das Computer-Durchsichts-Ereignis hin.

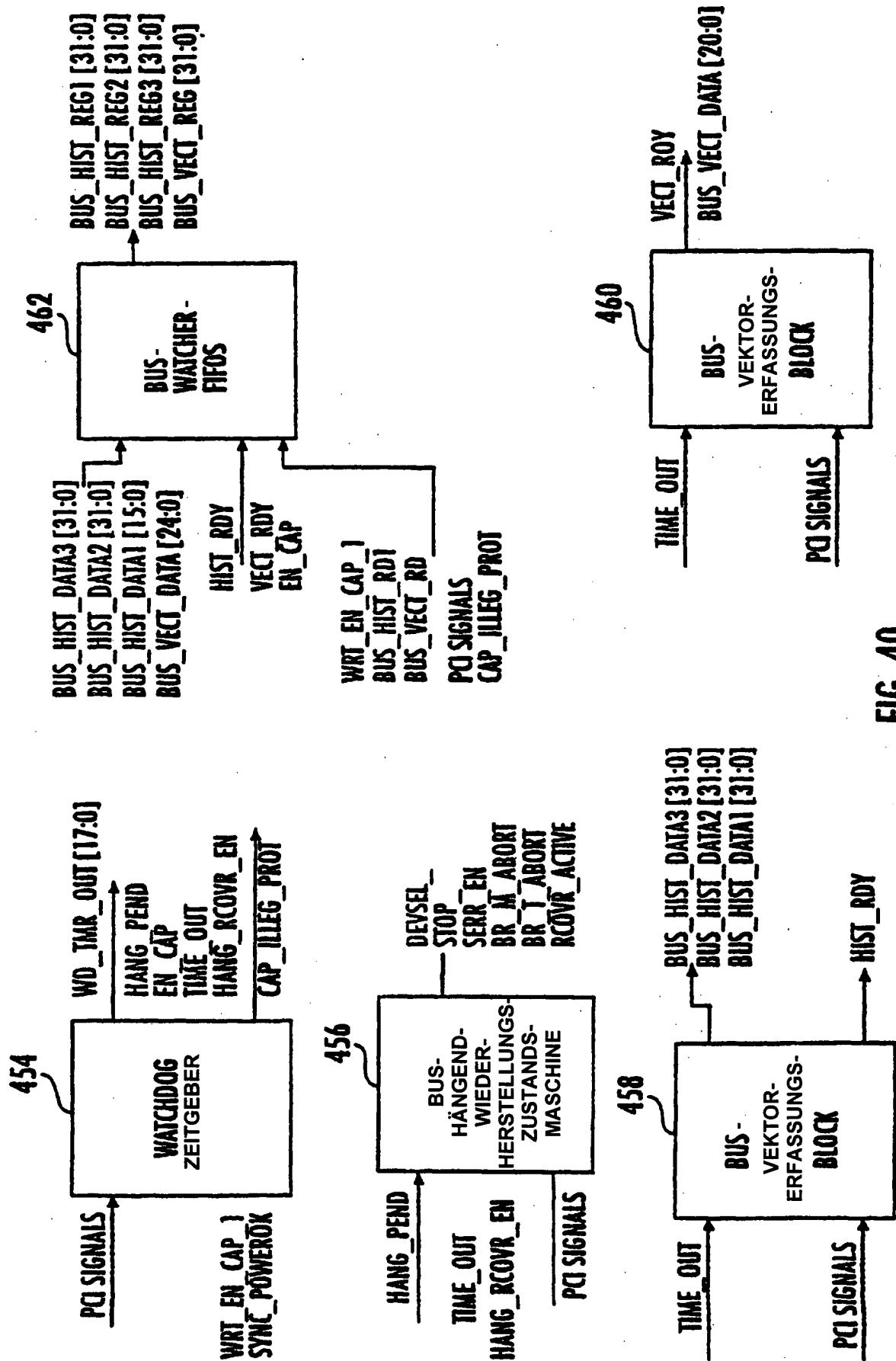

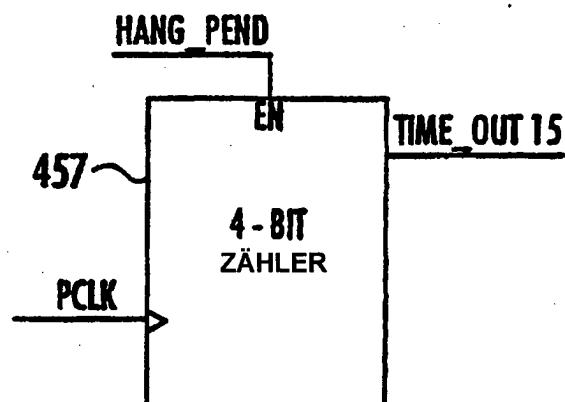

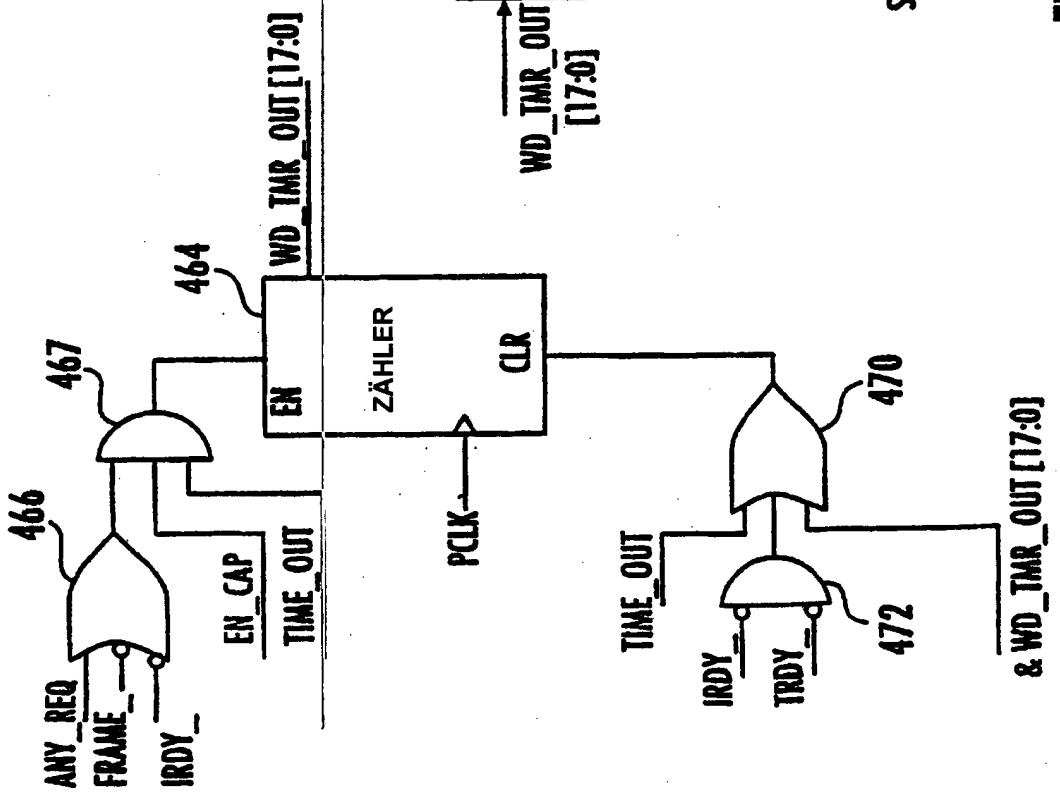

- [0068] **Fig. 40** zeigt ein Blockdiagramm eines Bus-Watcher's in jedem der Brücken-Chips.

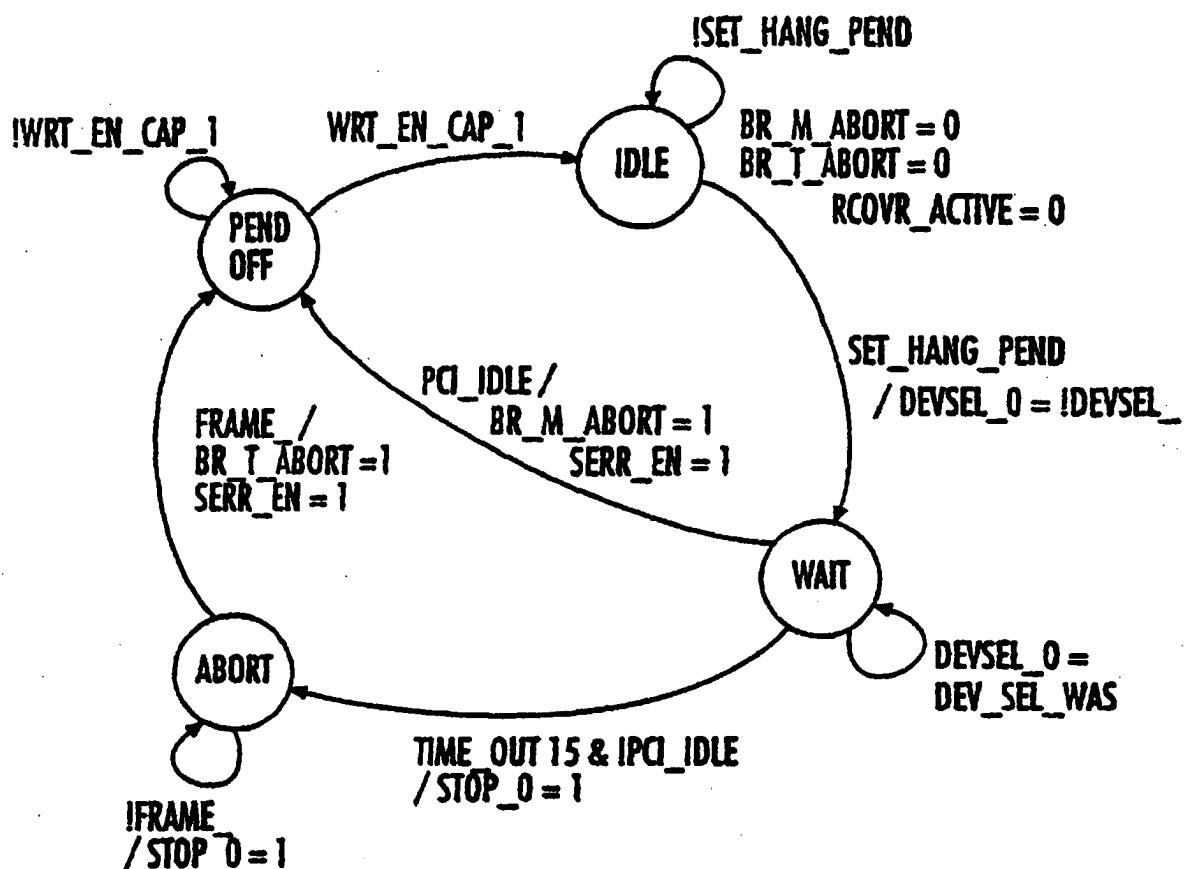

- [0069] **Fig. 41** zeigt ein Zustandsdiagramm einer Logik in dem Bus-Watcher zum Zurückführen des Busses zu einem Leerlaufzustand.

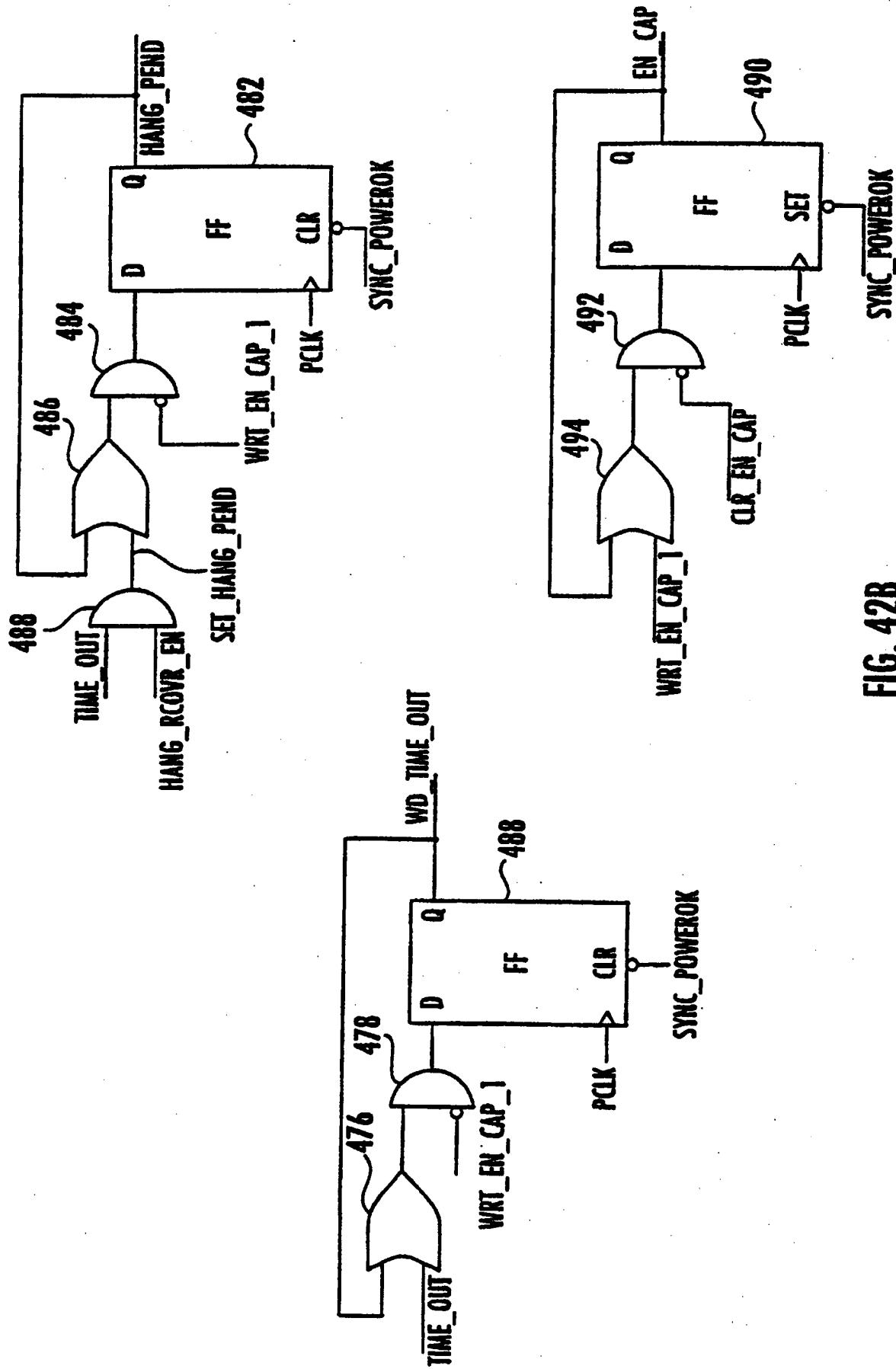

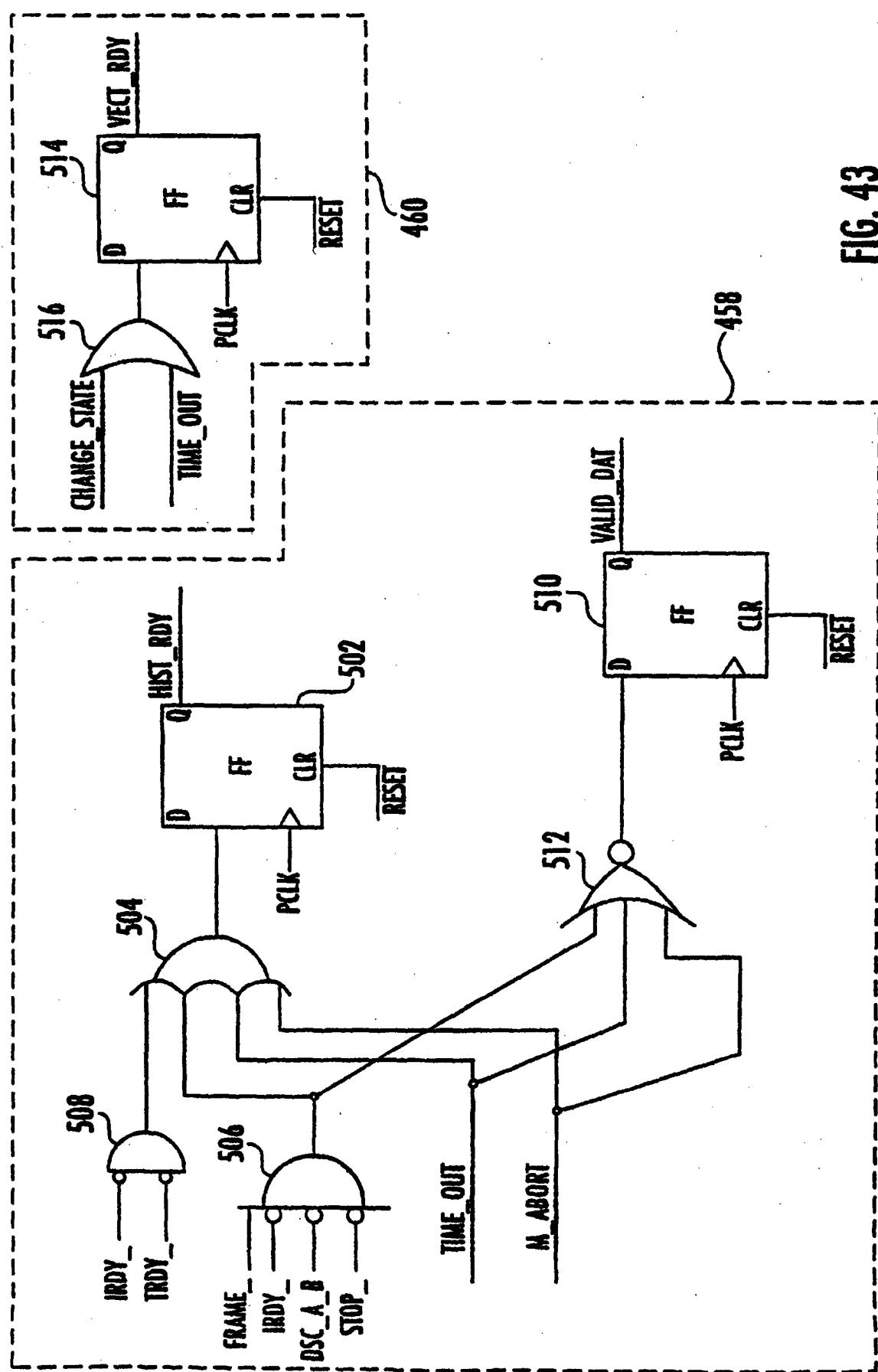

- [0070] **Fig. 42** zeigt ein logisches Diagramm von Status-Signalen in dem Bus-Watcher. **Fig. 43** zeigt ein logisches Diagramm von Bus-Historie-FIFOs und Bus-Zustand-Vektor-FIFOs in der Fehler-Isolations-Schaltung.

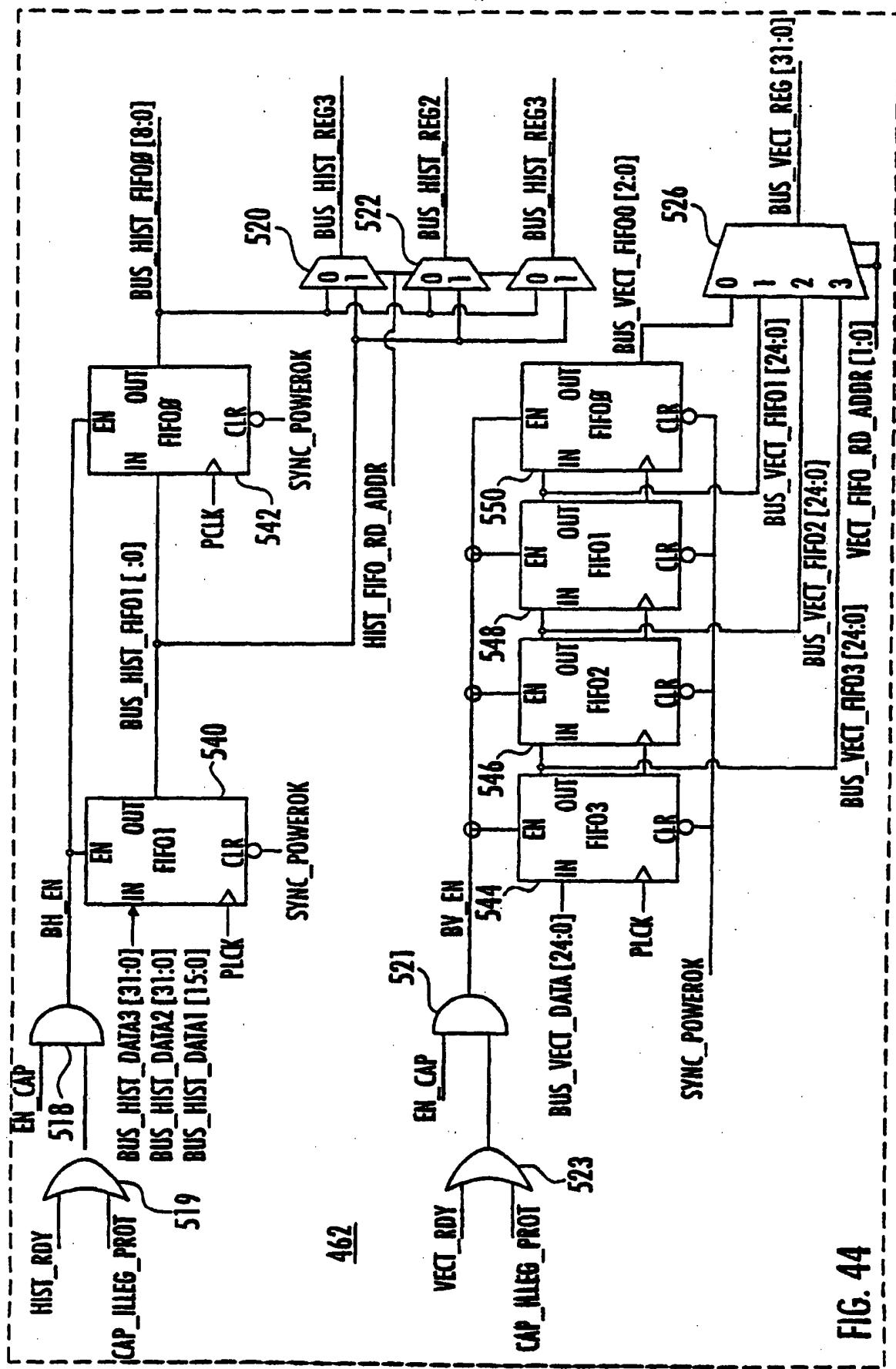

- [0071] **Fig. 44** zeigt ein logisches Diagramm einer Schaltung zum Erzeugen von Bereitschafts-Signalen zum Anzeigen, wenn die Bus-Historie- und Zustand-Vektor-Informationen verfügbar sind.

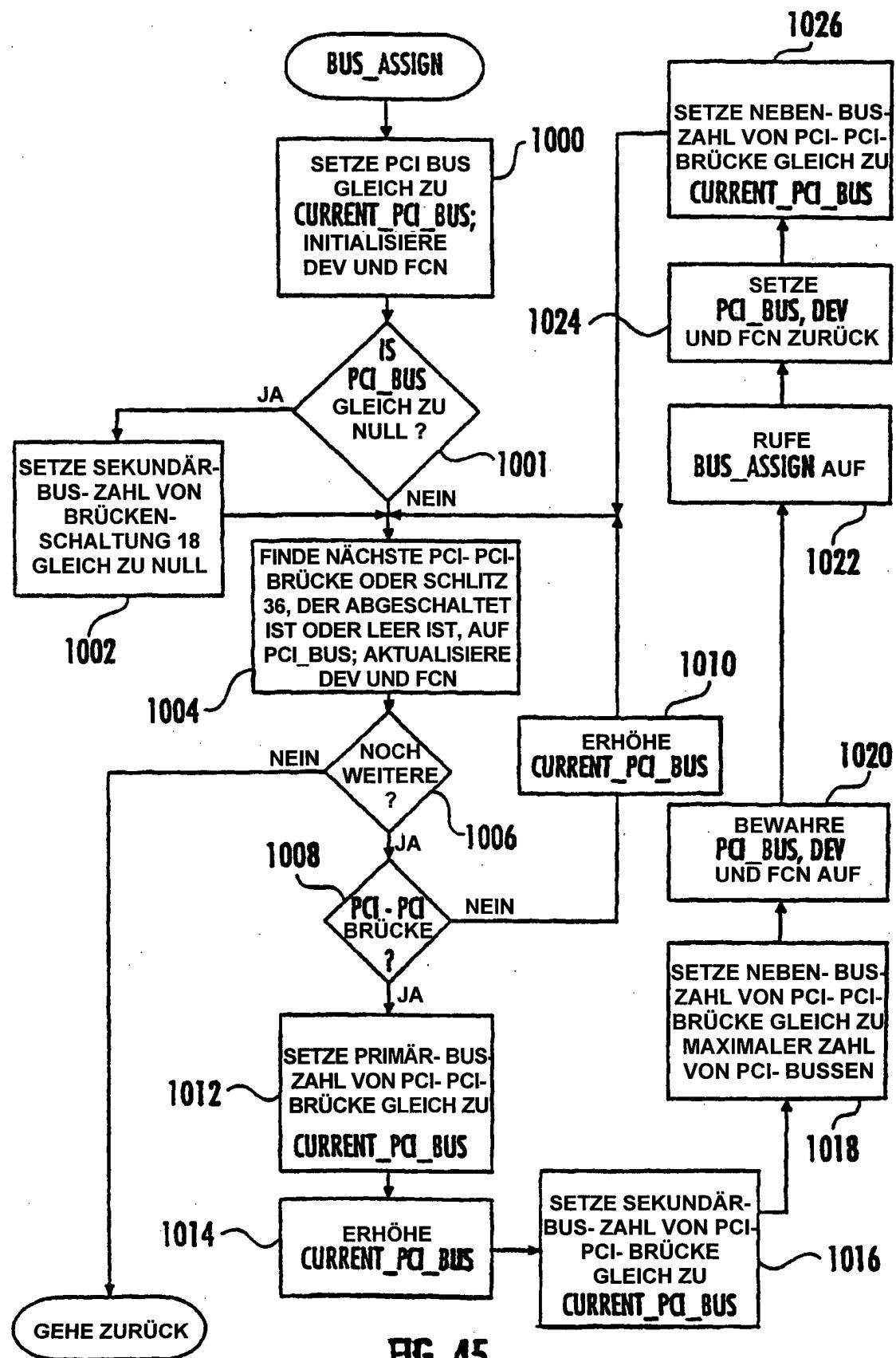

- [0072] **Fig. 45** zeigt ein Flußdiagramm eines Programms zum Zuordnen einer Bus-Zahl zu einem eingeschalteten oder leeren Schlitz.

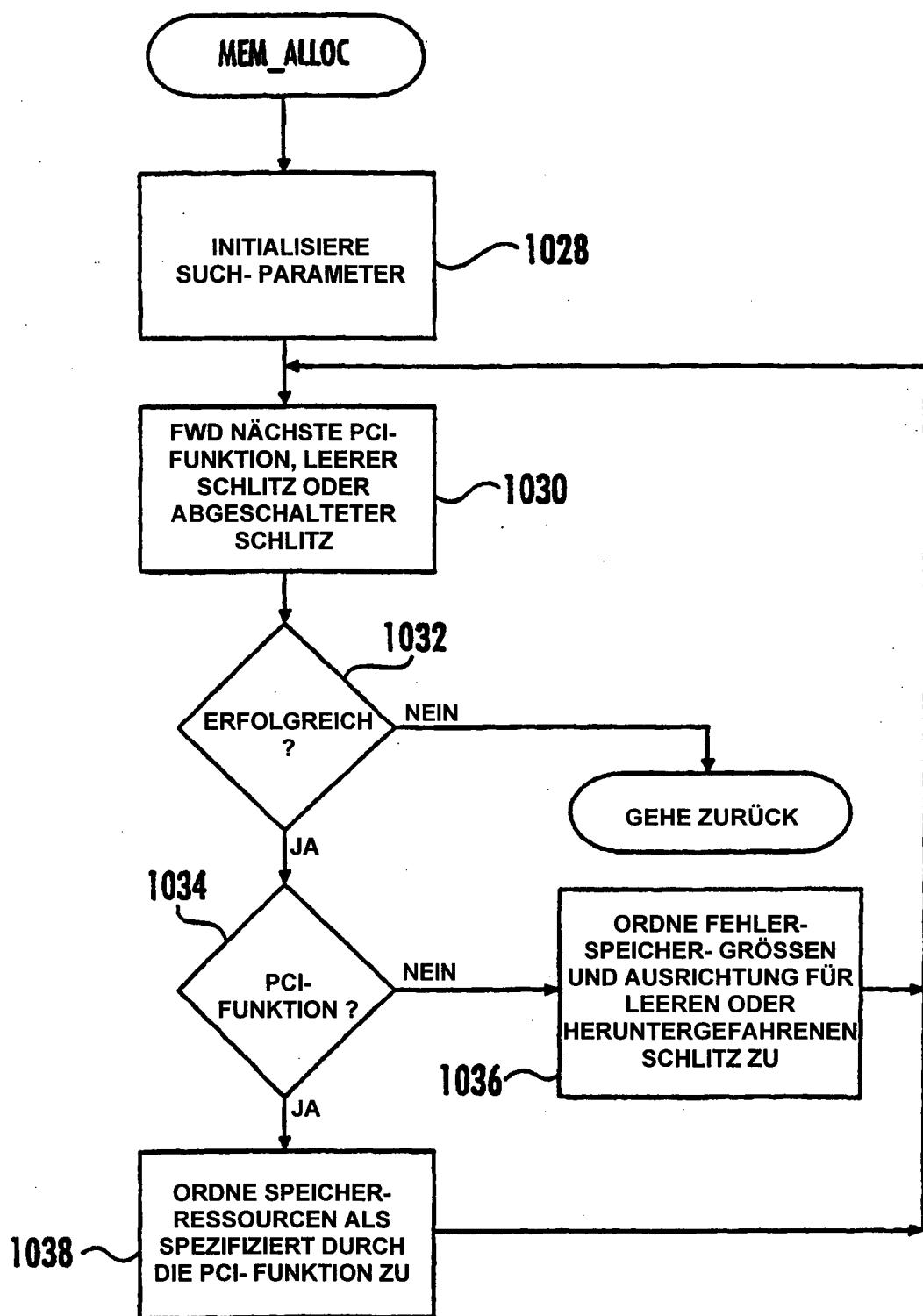

- [0073] **Fig. 46** zeigt ein Flußdiagramm eines Programms zum Zuordnen von Speicherraum für das Computersystem.

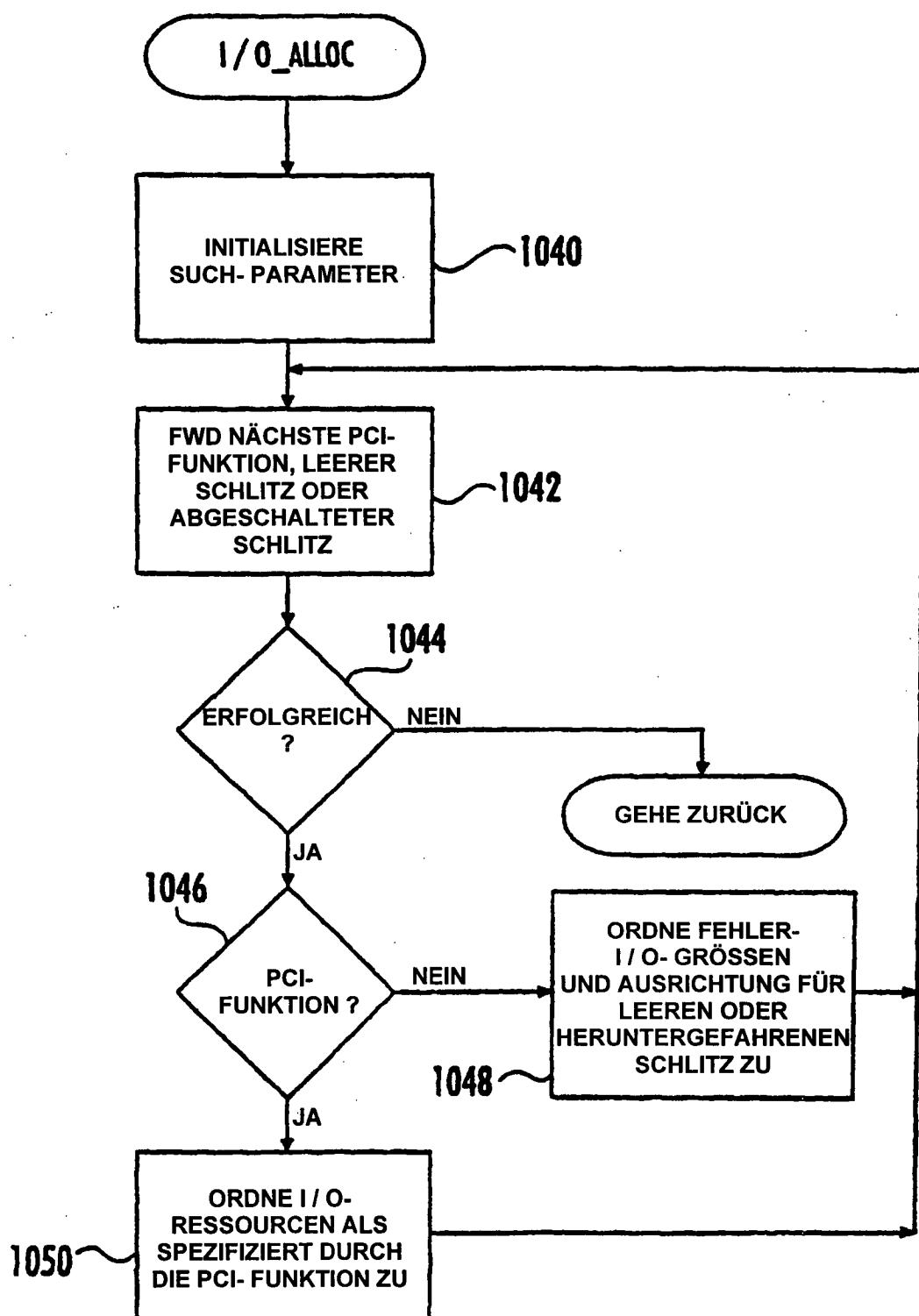

- [0074] **Fig. 47** zeigt ein Flußdiagramm eines Programms zum Zuordnen eines I/O-Raums für das Computersystem.

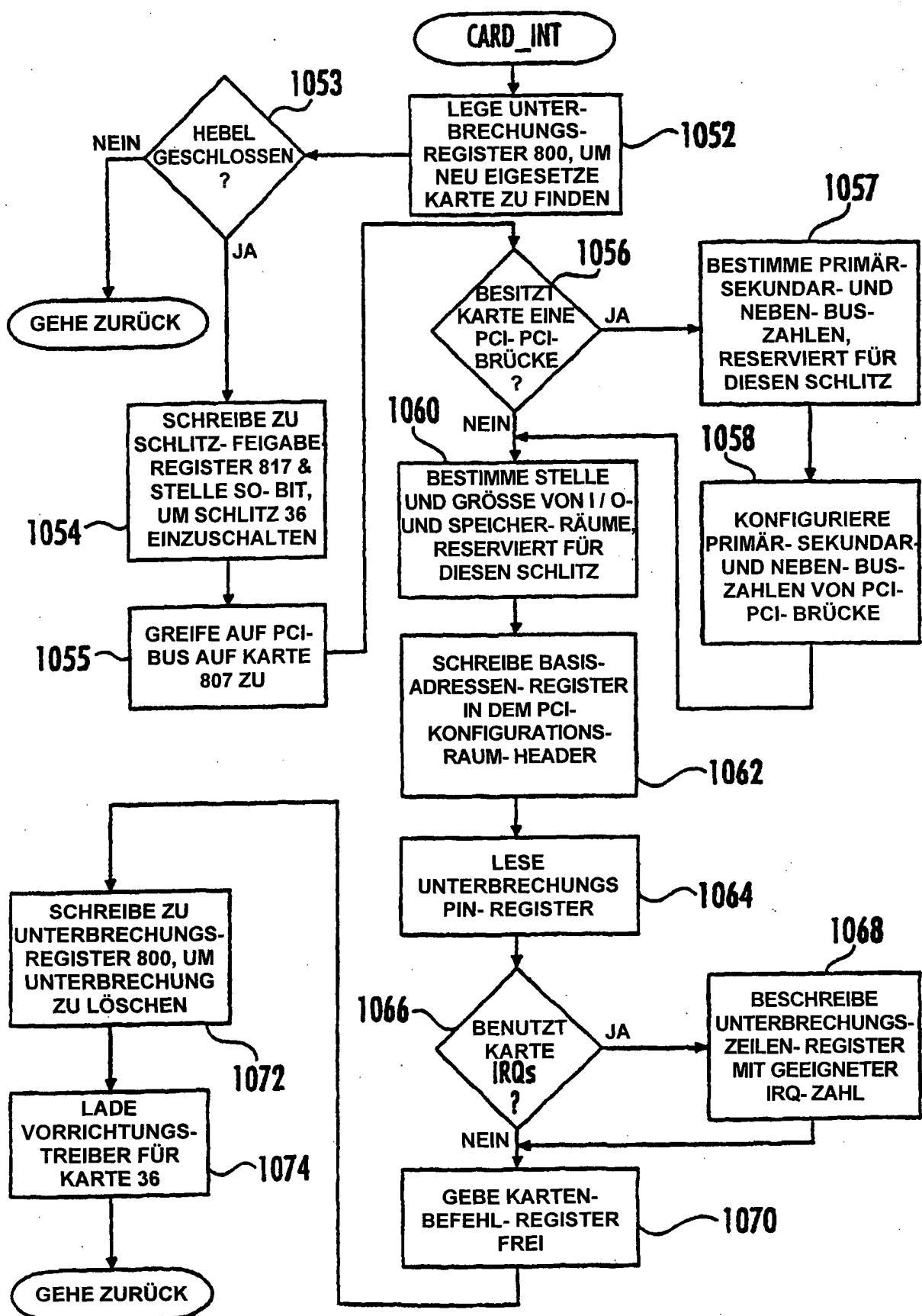

- [0075] **Fig. 48** zeigt ein Flußdiagramm eines Programms zum Handhaben einer neu eingeschalteten Karte.

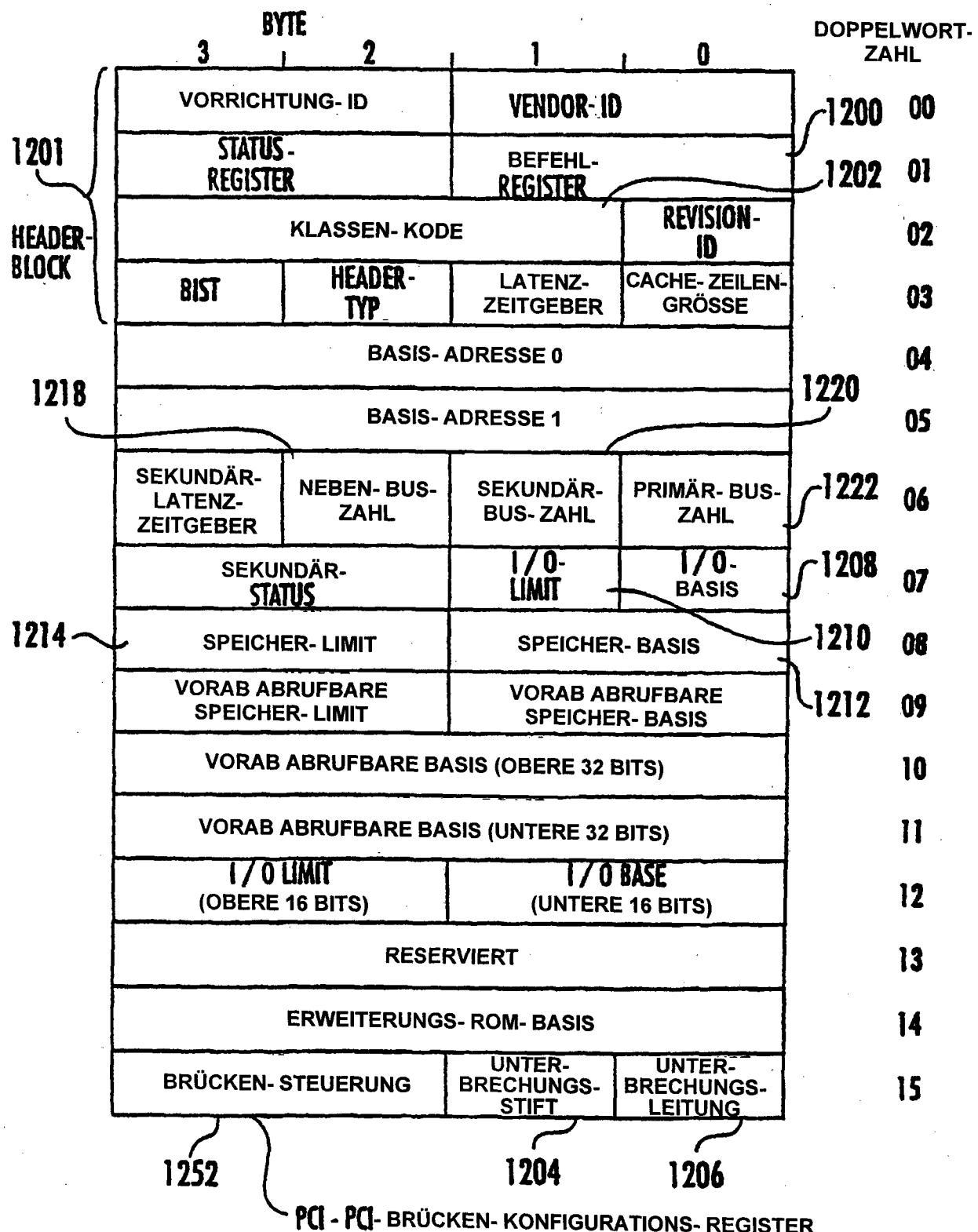

- [0076] **Fig. 49** zeigt ein Blockdiagramm eines Konfigurationsraums für eine PCI-Brückenschaltung.

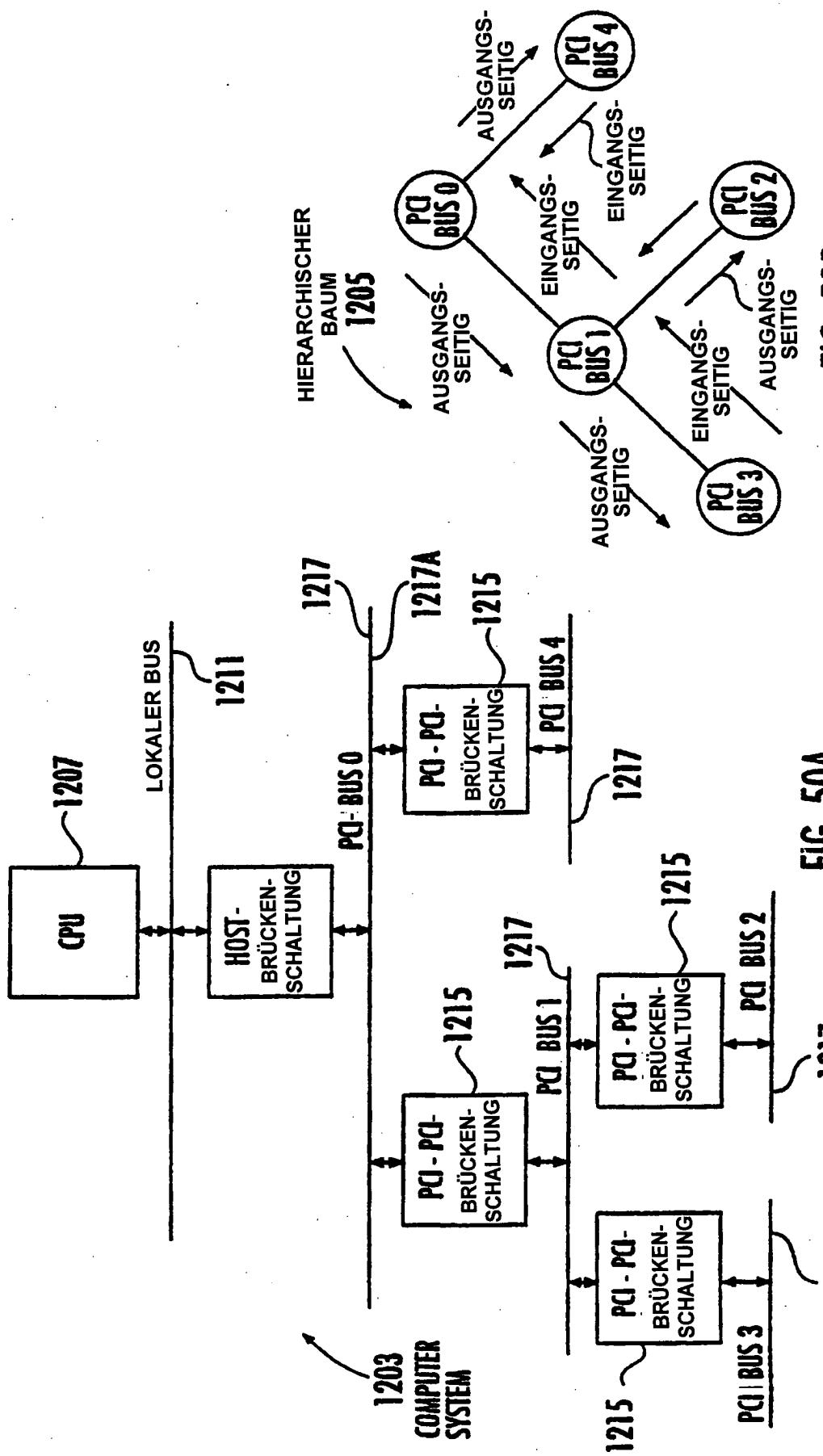

- [0077] **Fig. 50A** zeigt ein Blockdiagramm eines Computersystems.

- [0078] **Fig. 50B** zeigt einen Bus-Zahl-Zuordnungs-Baum.

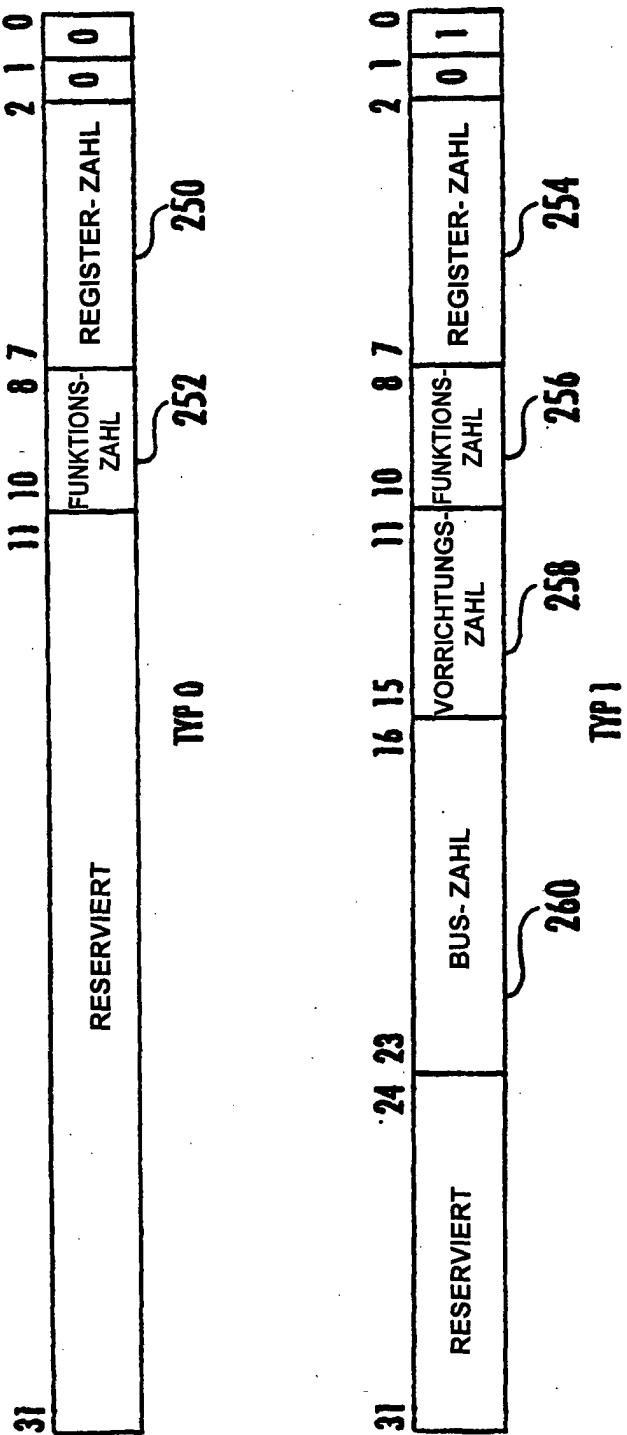

- [0079] **Fig. 51** zeigt ein Blockdiagramm, das Konfigurations-Transaktionen vom Typ 0 und Typ 1 darstellt.

- [0080] **Fig. 52** zeigt eine Tabelle, die eine Auflistung einer Adresse von einem primären Bus zu einem sekundären Bus aufweist.

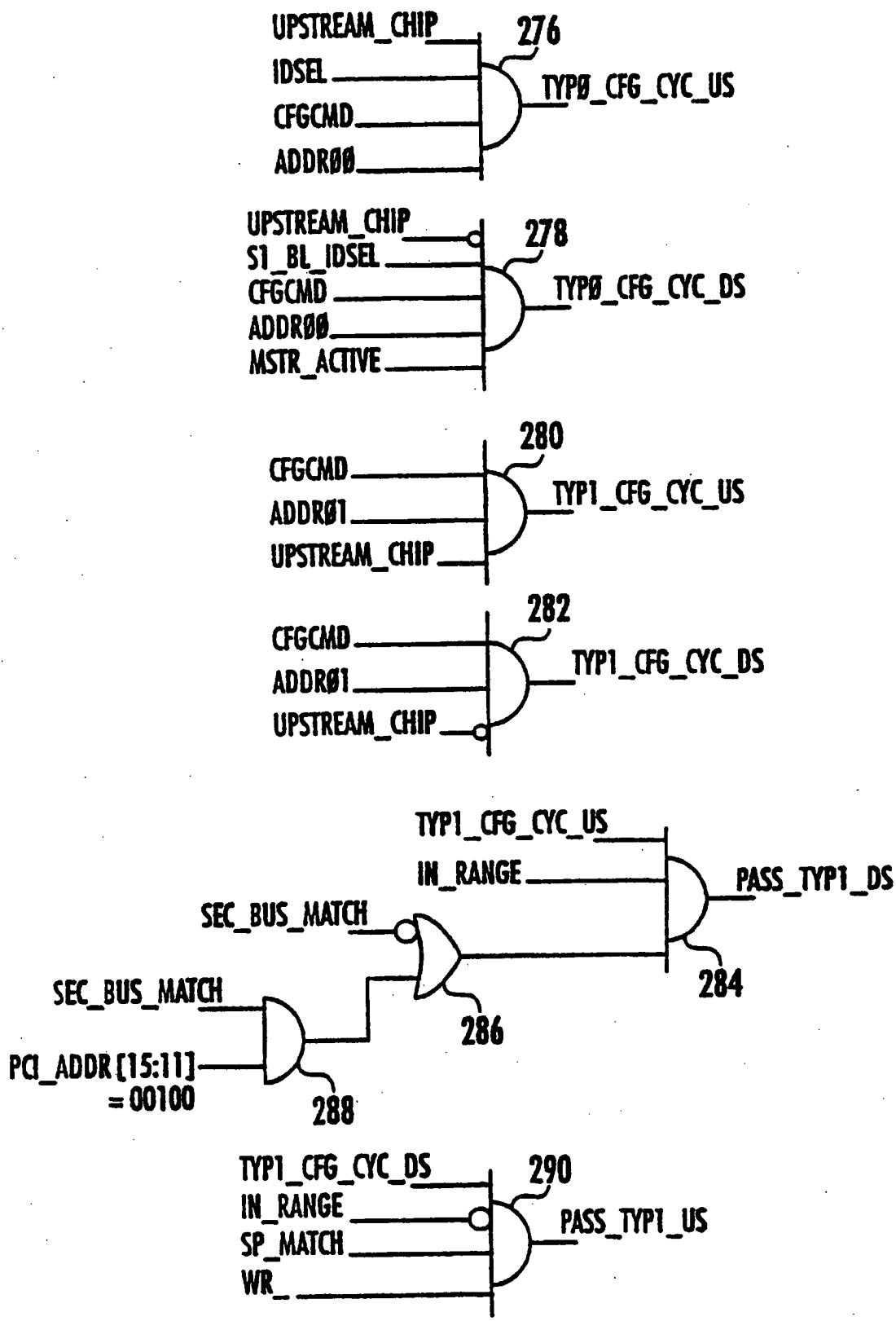

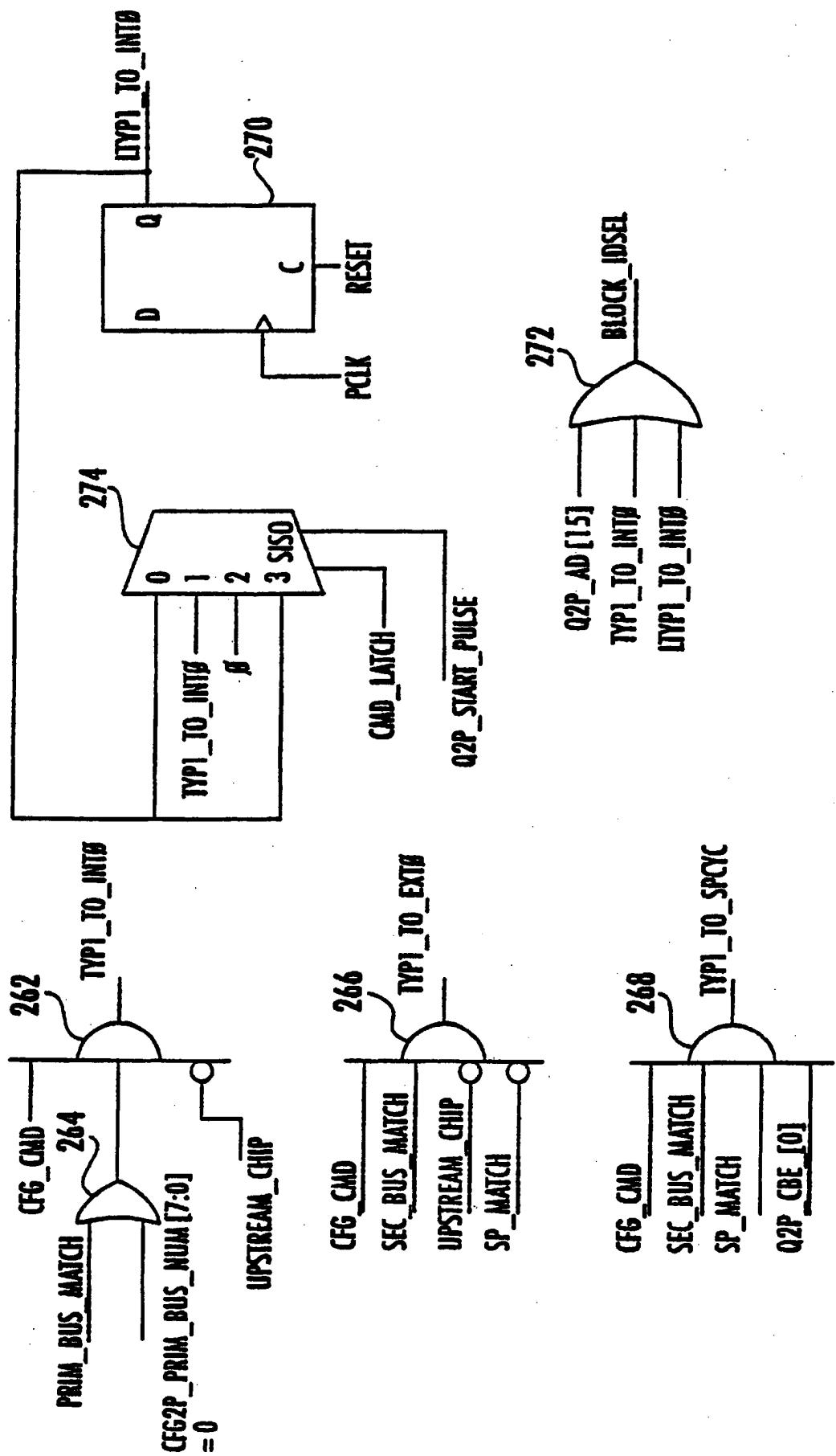

- [0081] **Fig. 53A** und **53B** zeigen ein logisches Diagramm einer Schaltung zum Handhaben von Konfigurations-Zyklen vom Typ 0 und Typ 1.

- [0082] **Fig. 54A** zeigt ein Blockdiagramm einer Schaltung zum Speichern von Informationen, um eine Berechnung von Bus-Funktions-Parametern zu ermöglichen.

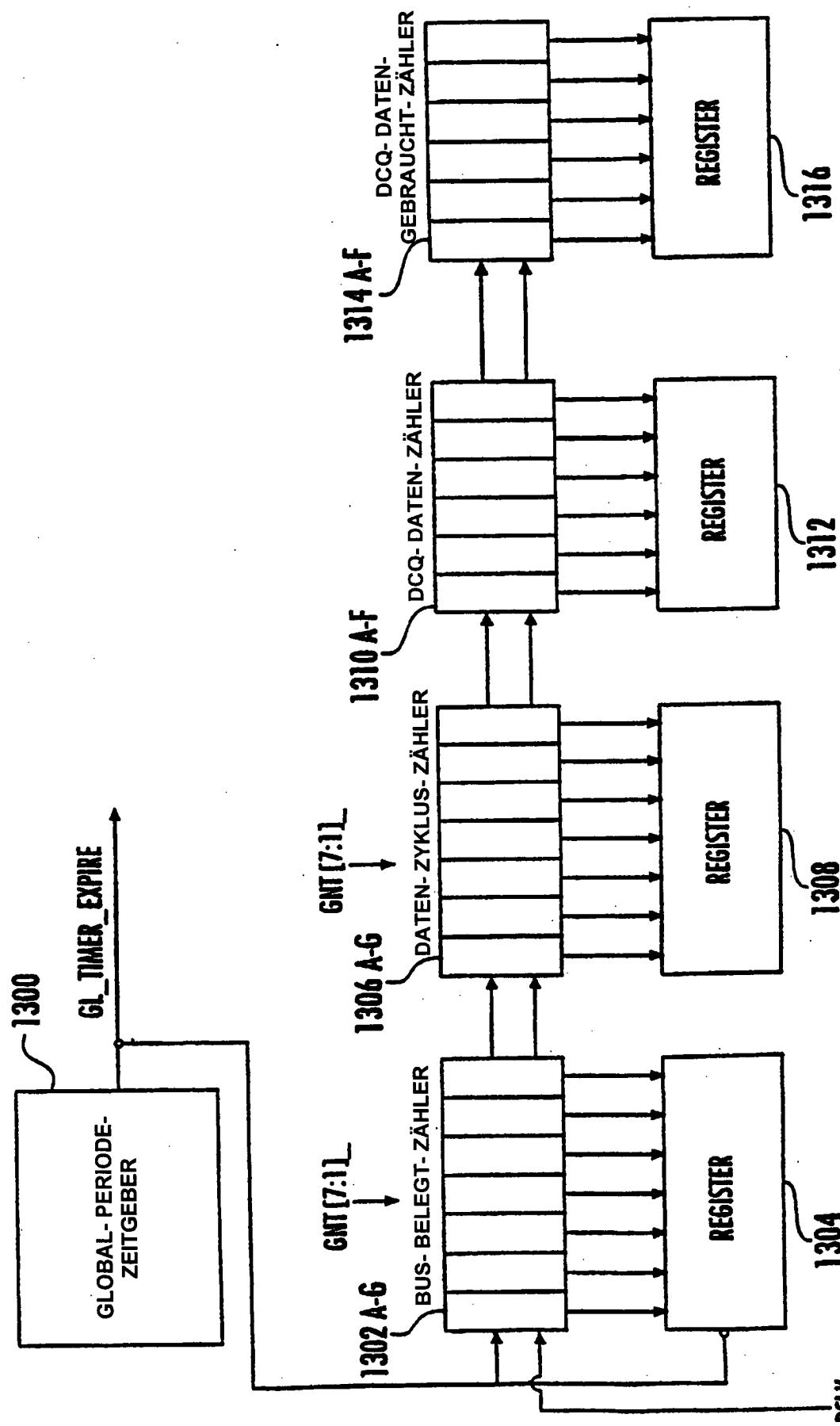

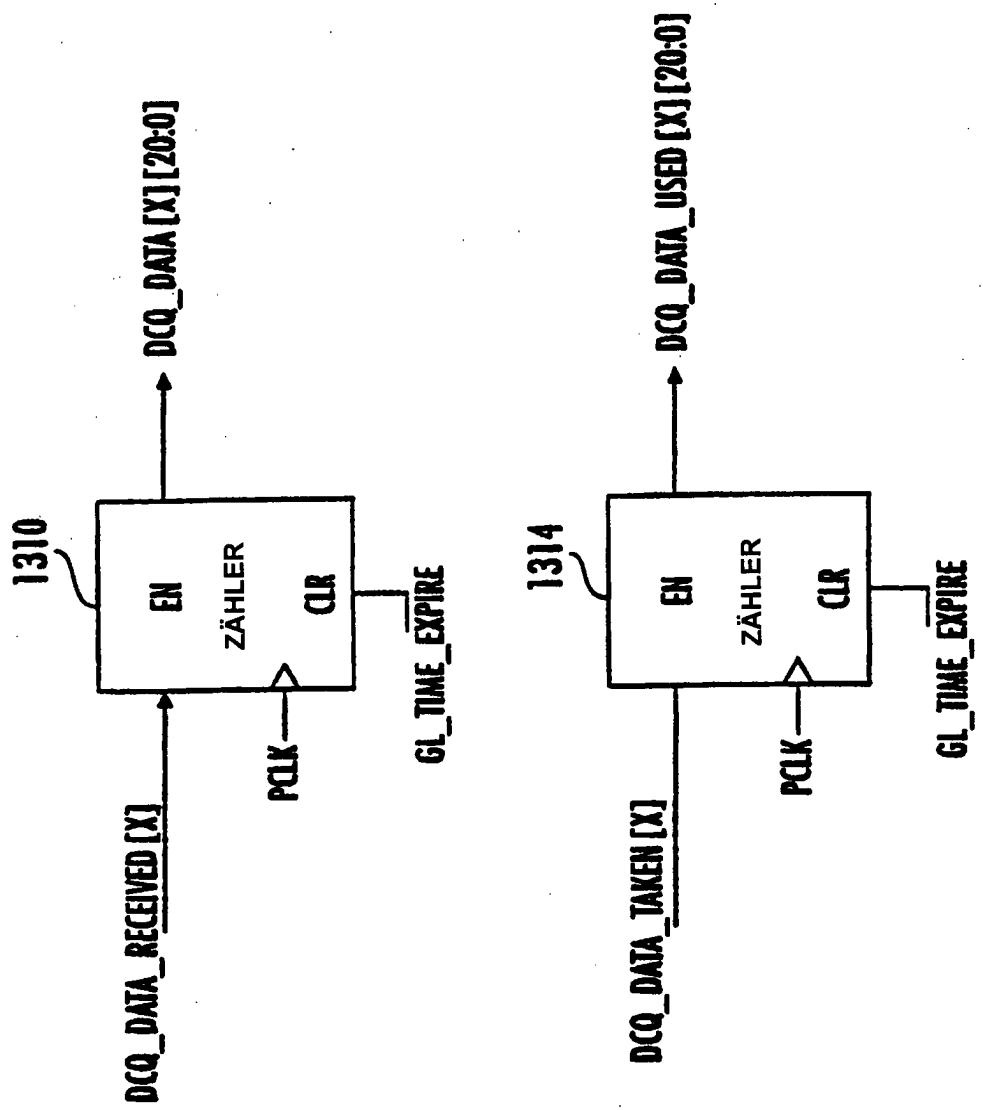

- [0083] **Fig. 54B** zeigt ein Blockdiagramm von Vorabruf-Zählern.

- [0084] **Fig. 55** zeigt ein Blockdiagramm eines Computersystems.

- [0085] **Fig.** 56 zeigt ein Blockdiagramm eines PCI-Entscheidungs-Schemas.

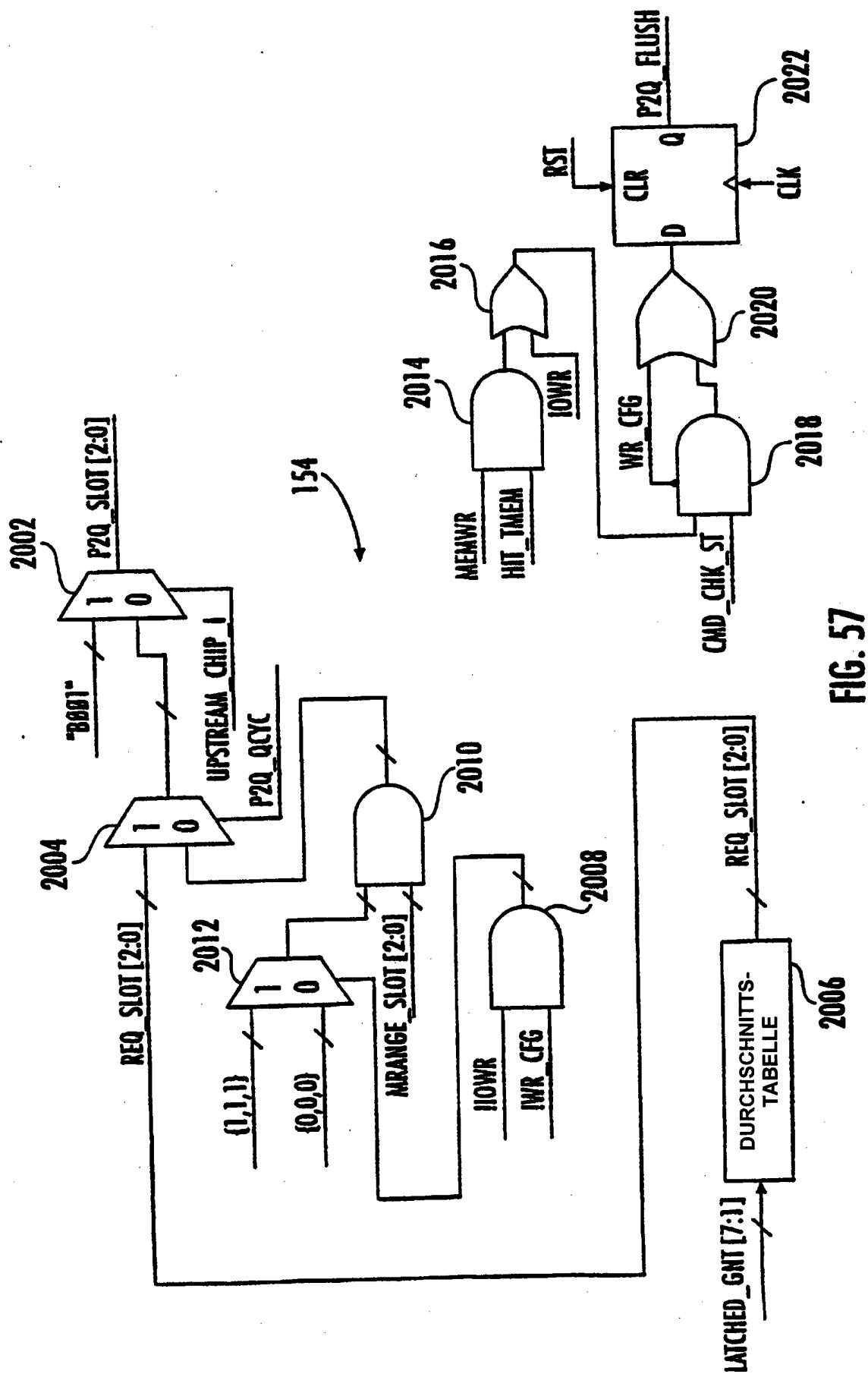

- [0086] **Fig.** 57 zeigt ein schematisches Diagramm eines Puffer-Entleerungs-Logik-Blocks.

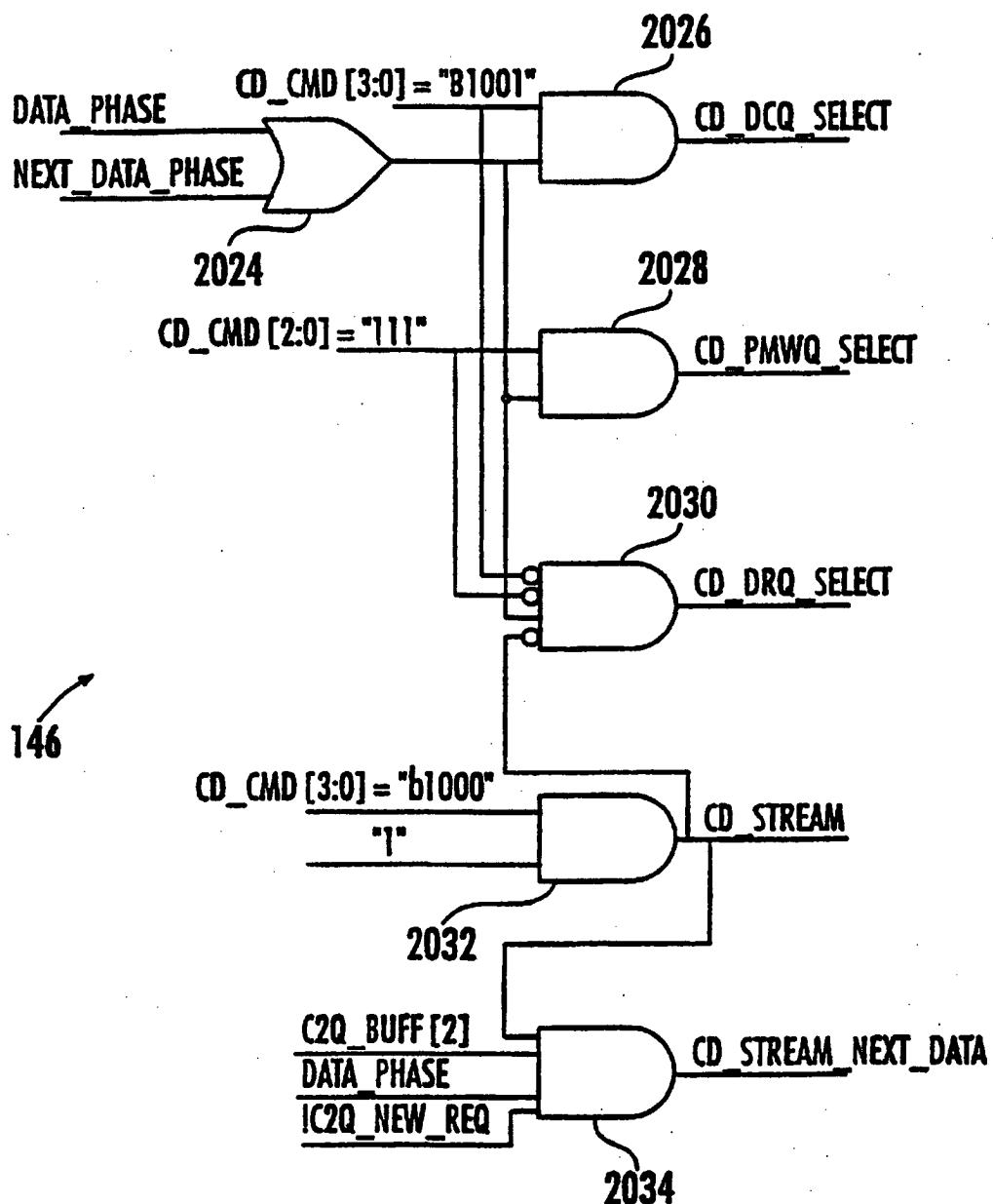

- [0087] **Fig.** 58 zeigt ein schematisches Diagramm eines Kabel-Decodierers.

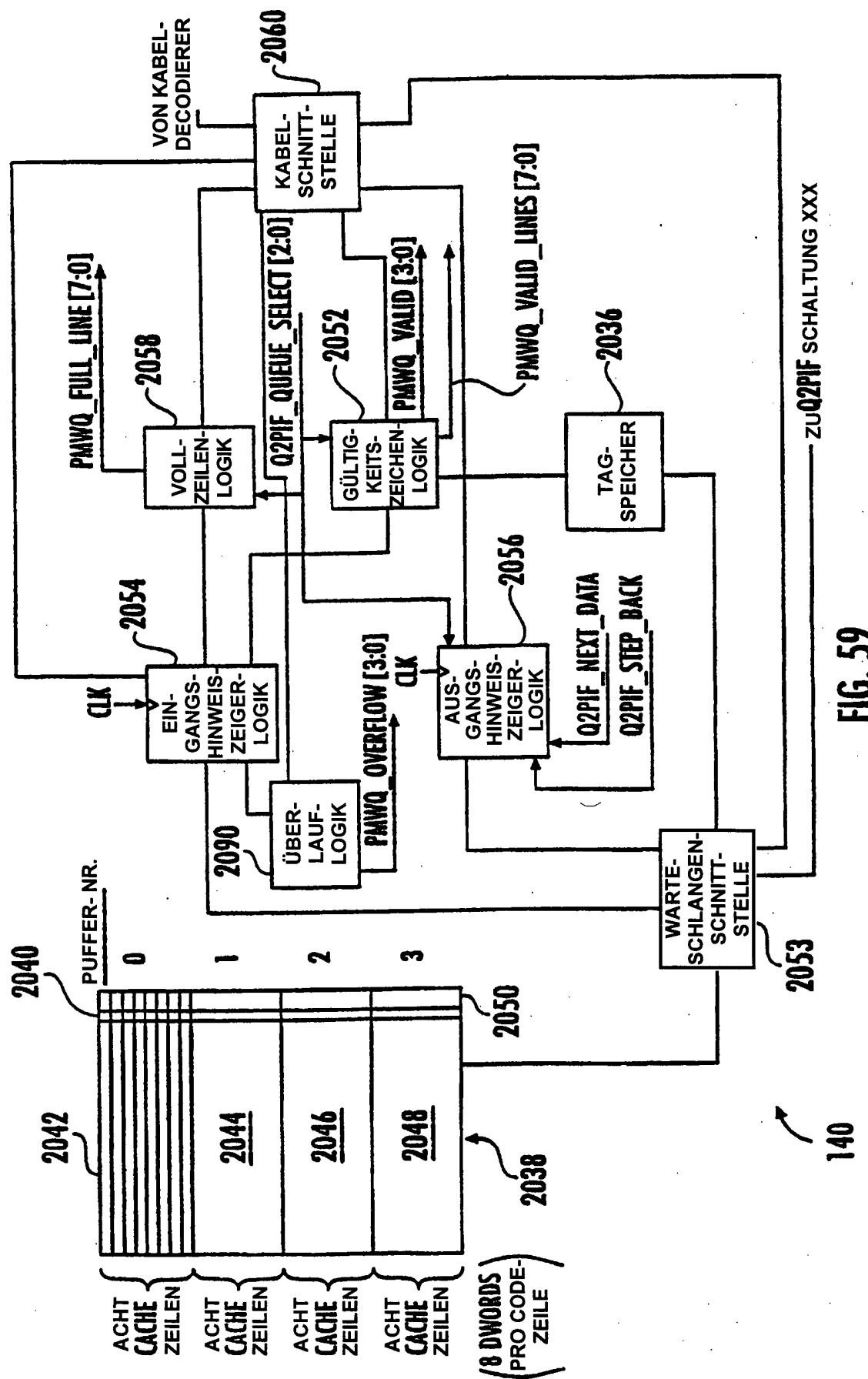

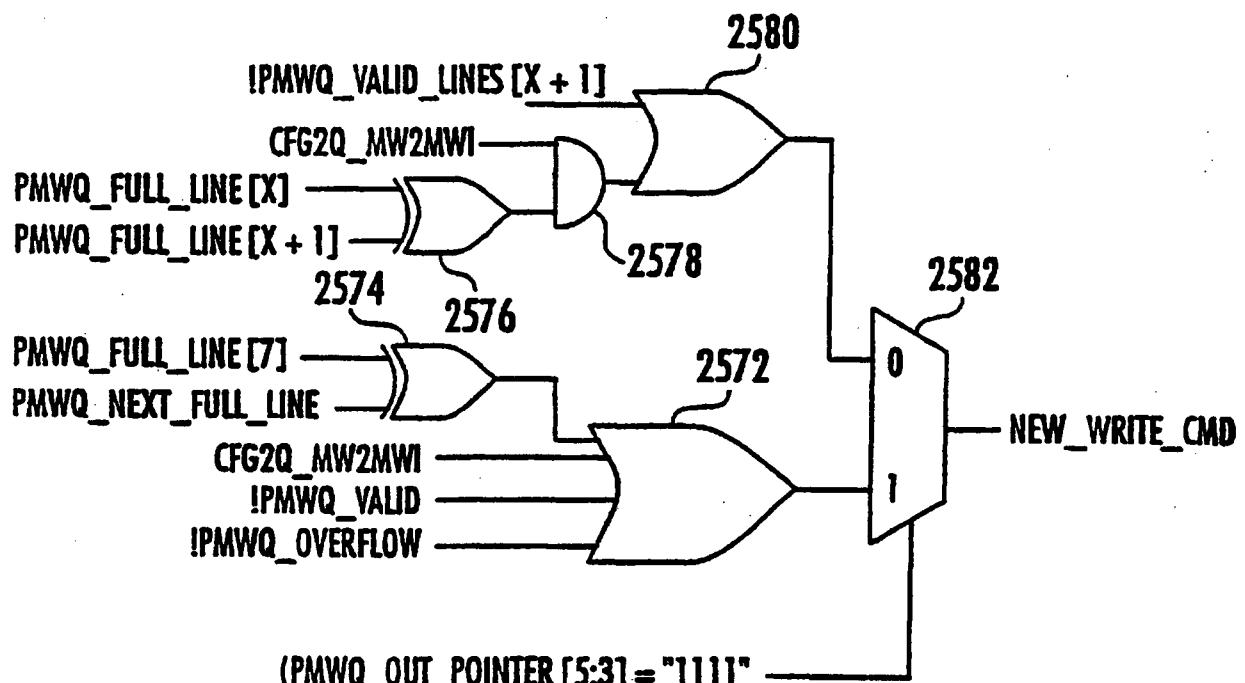

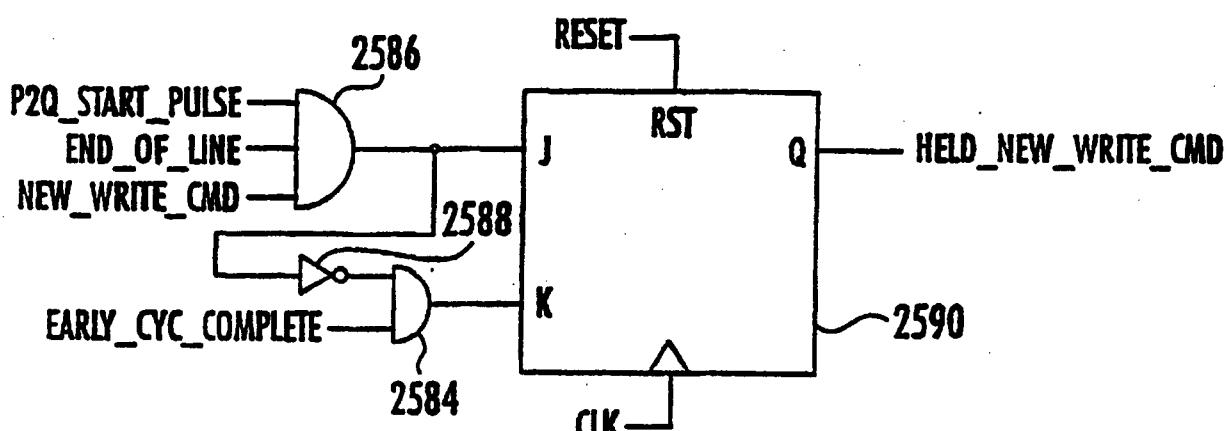

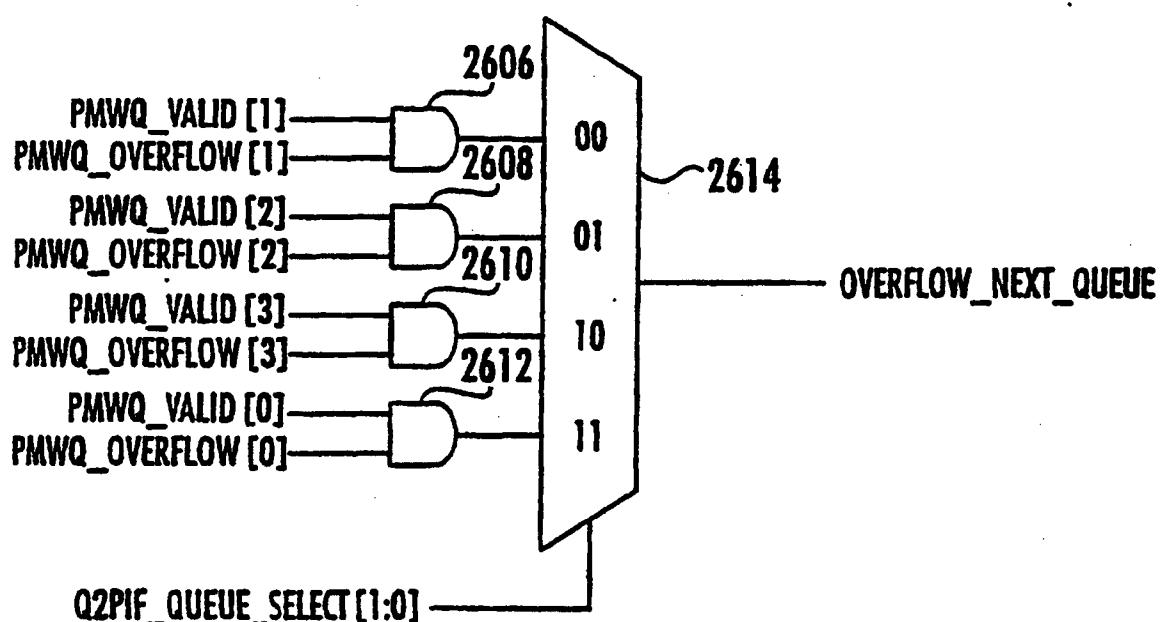

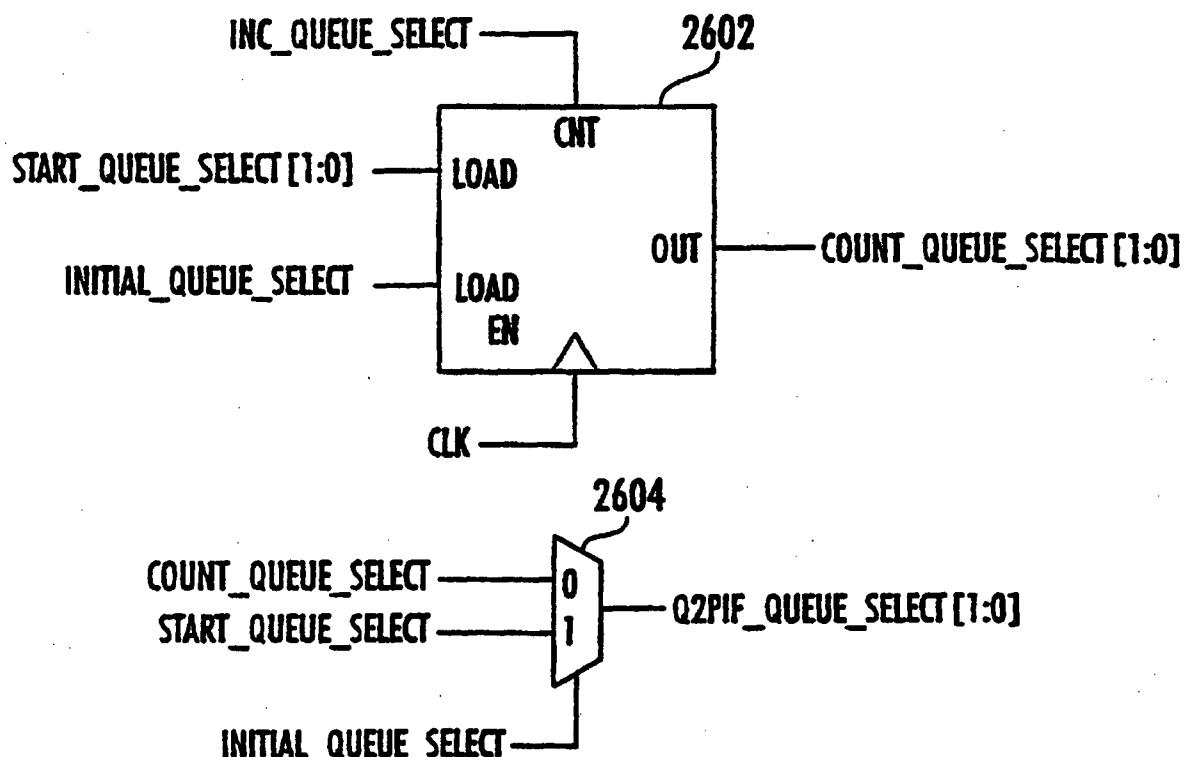

- [0088] **Fig.** 59–62 zeigen schematische Diagramme einer geposteten Speicher-Schreib-Warteschlange, umfassend eine Steuerlogik.

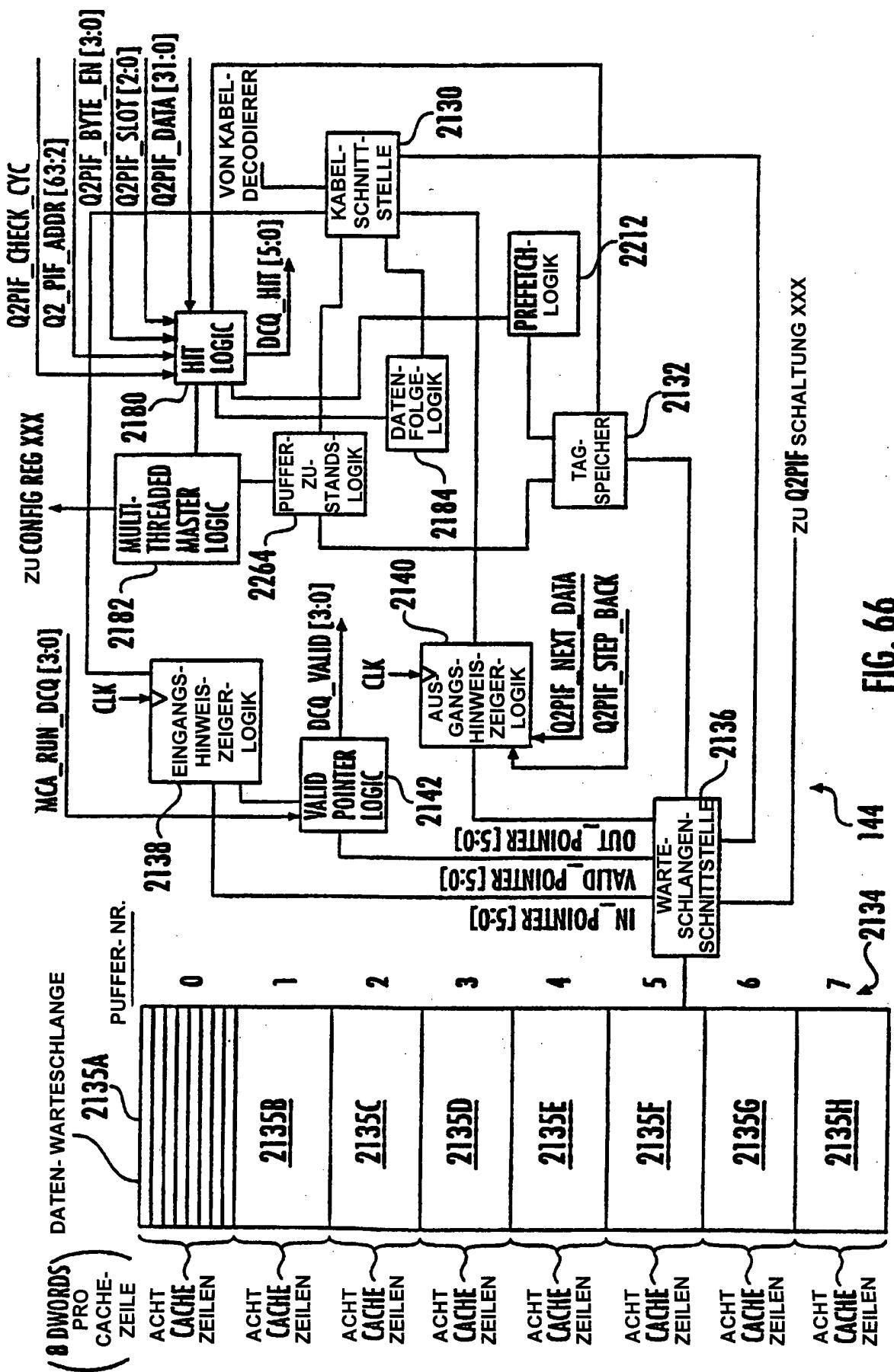

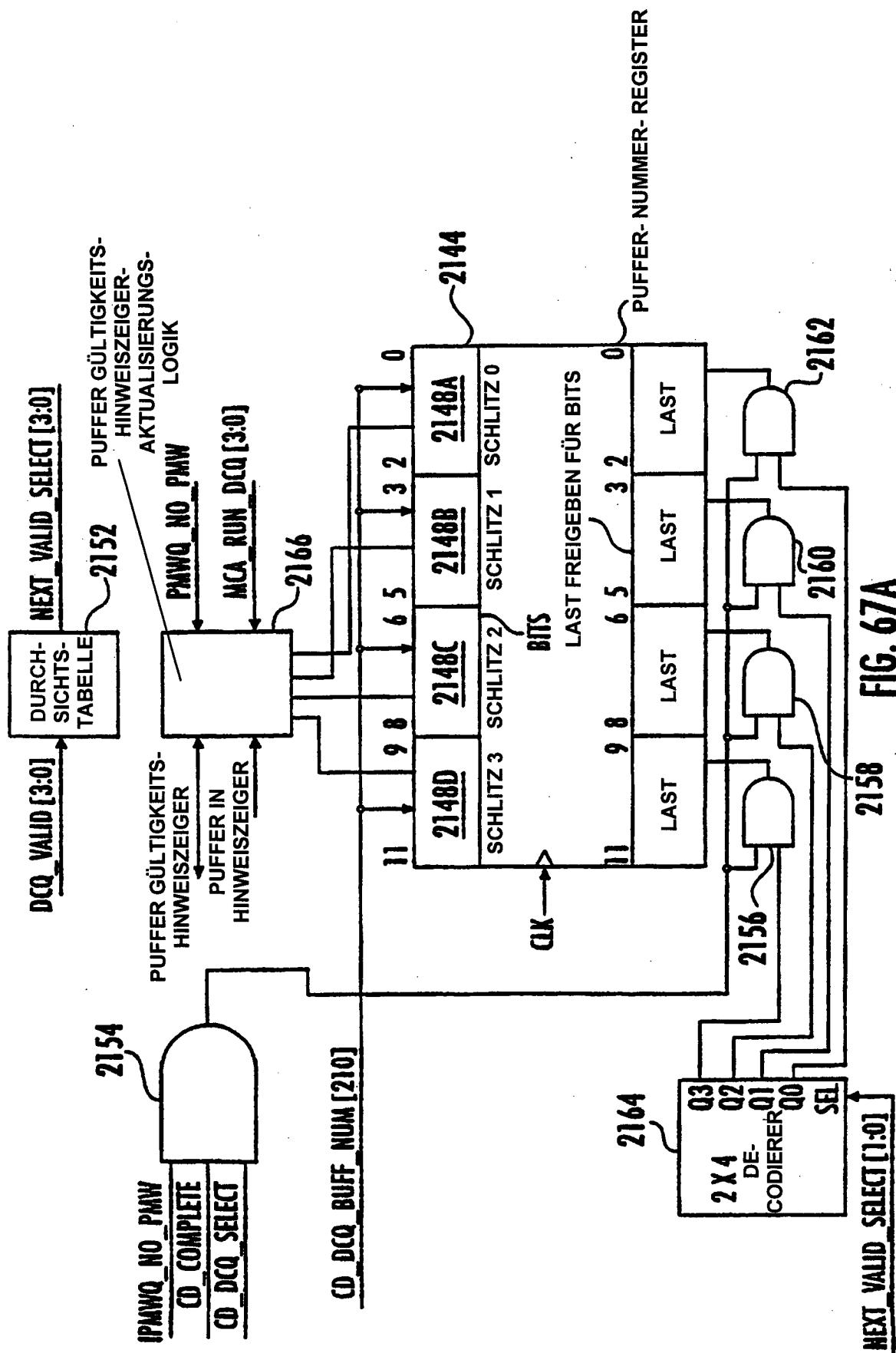

- [0089] **Fig.** 63–65 zeigen schematische Diagramme einer verzögerten Anforderungs-Warteschlange, umfassend eine Steuerlogik.

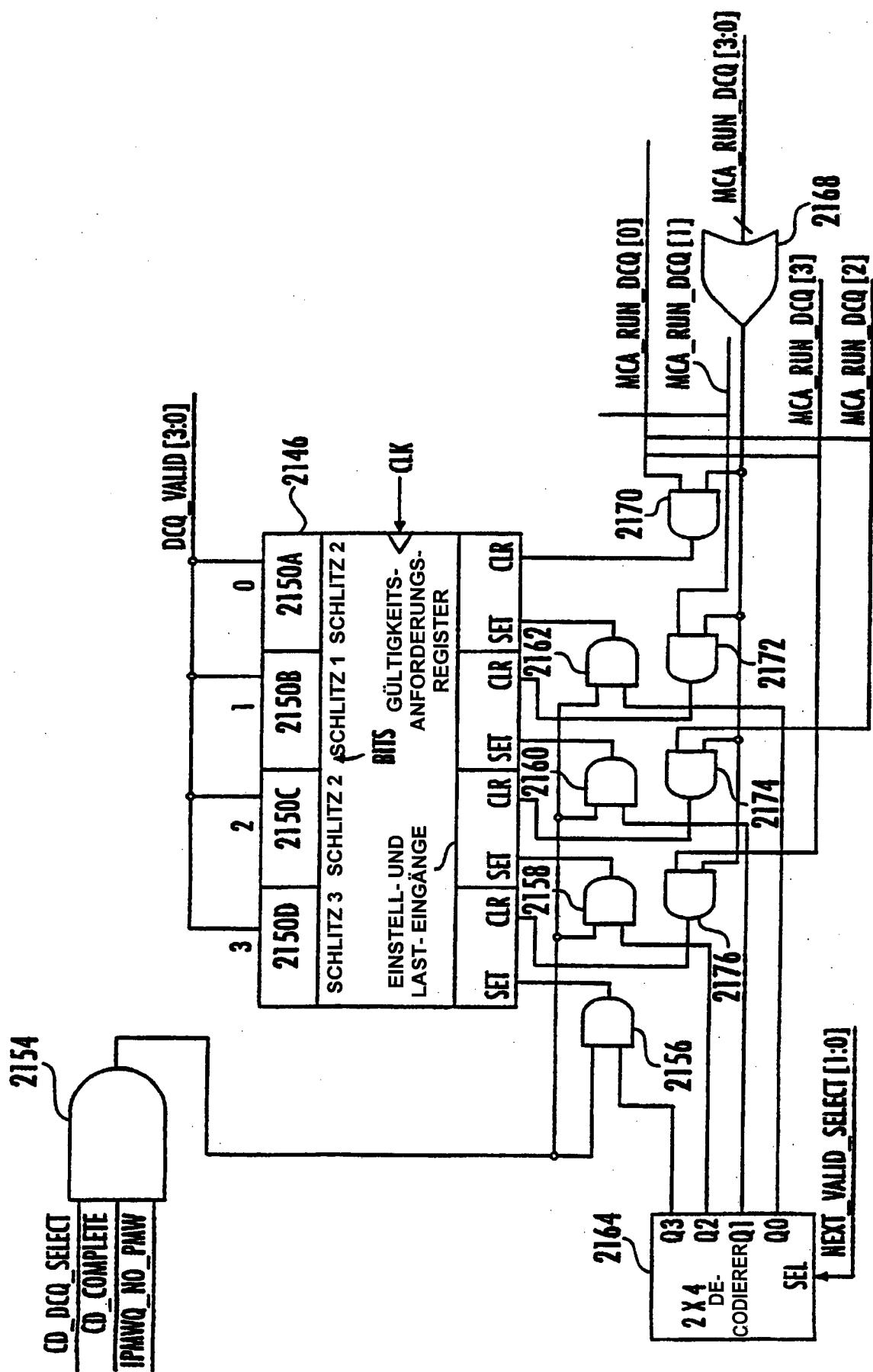

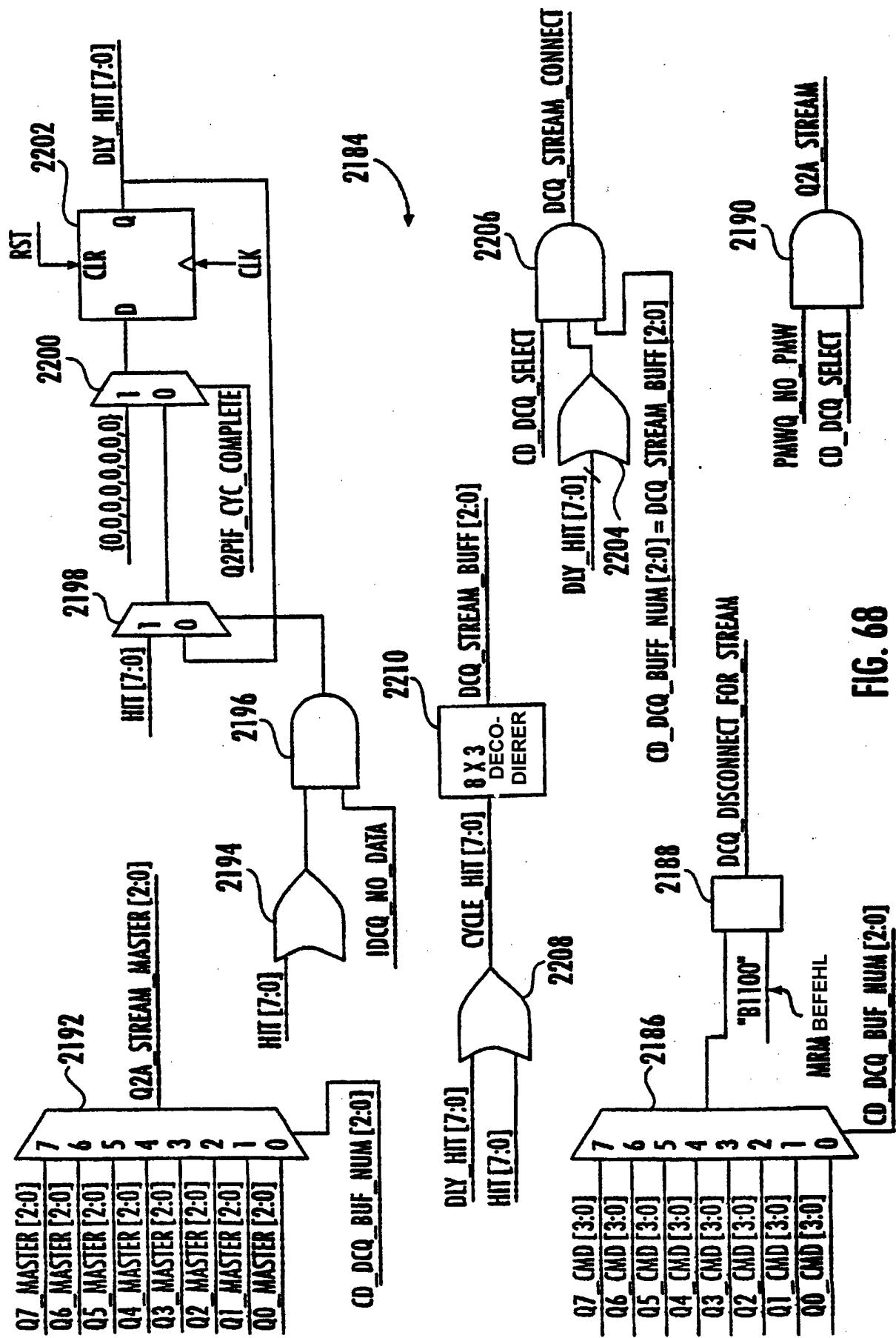

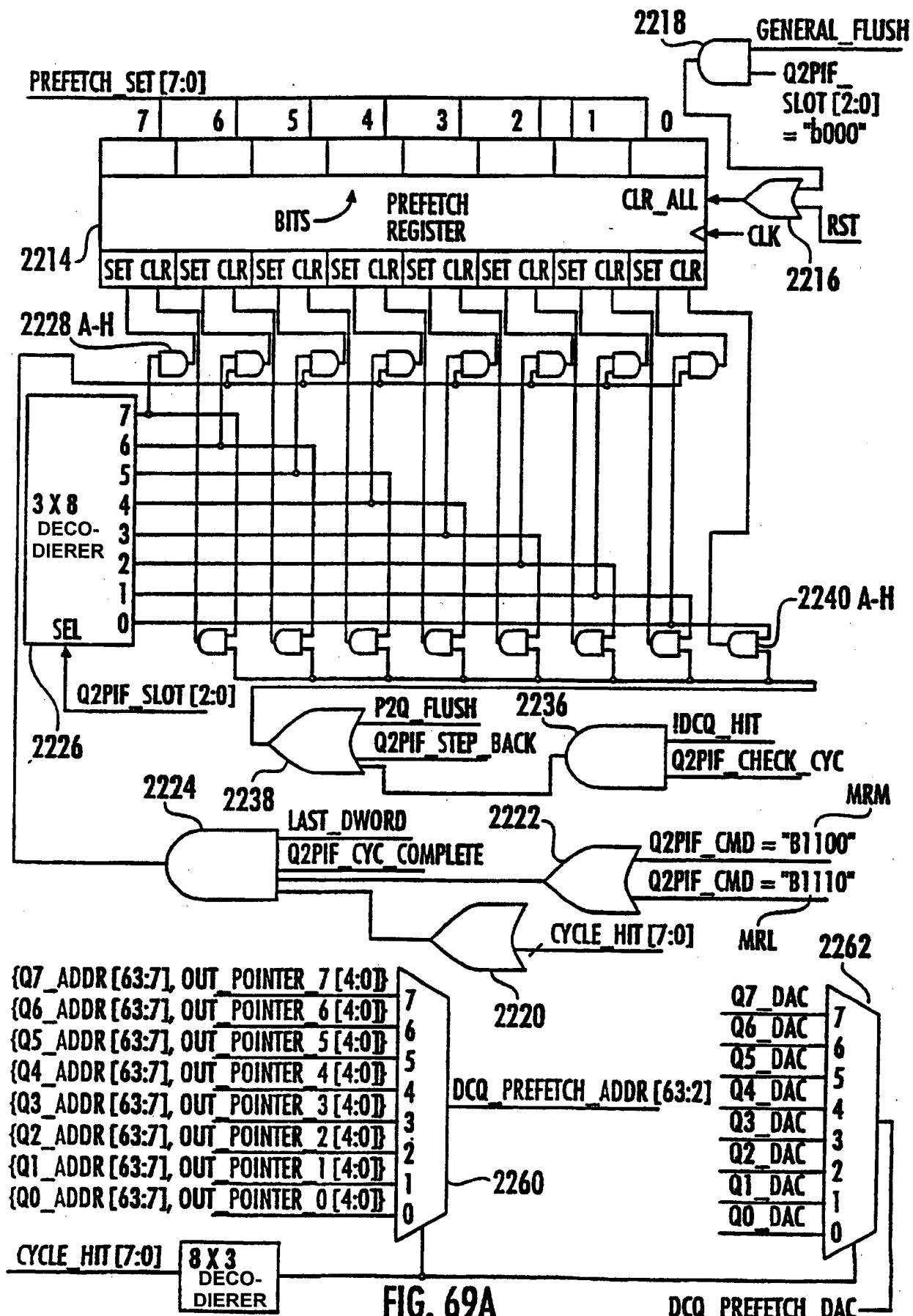

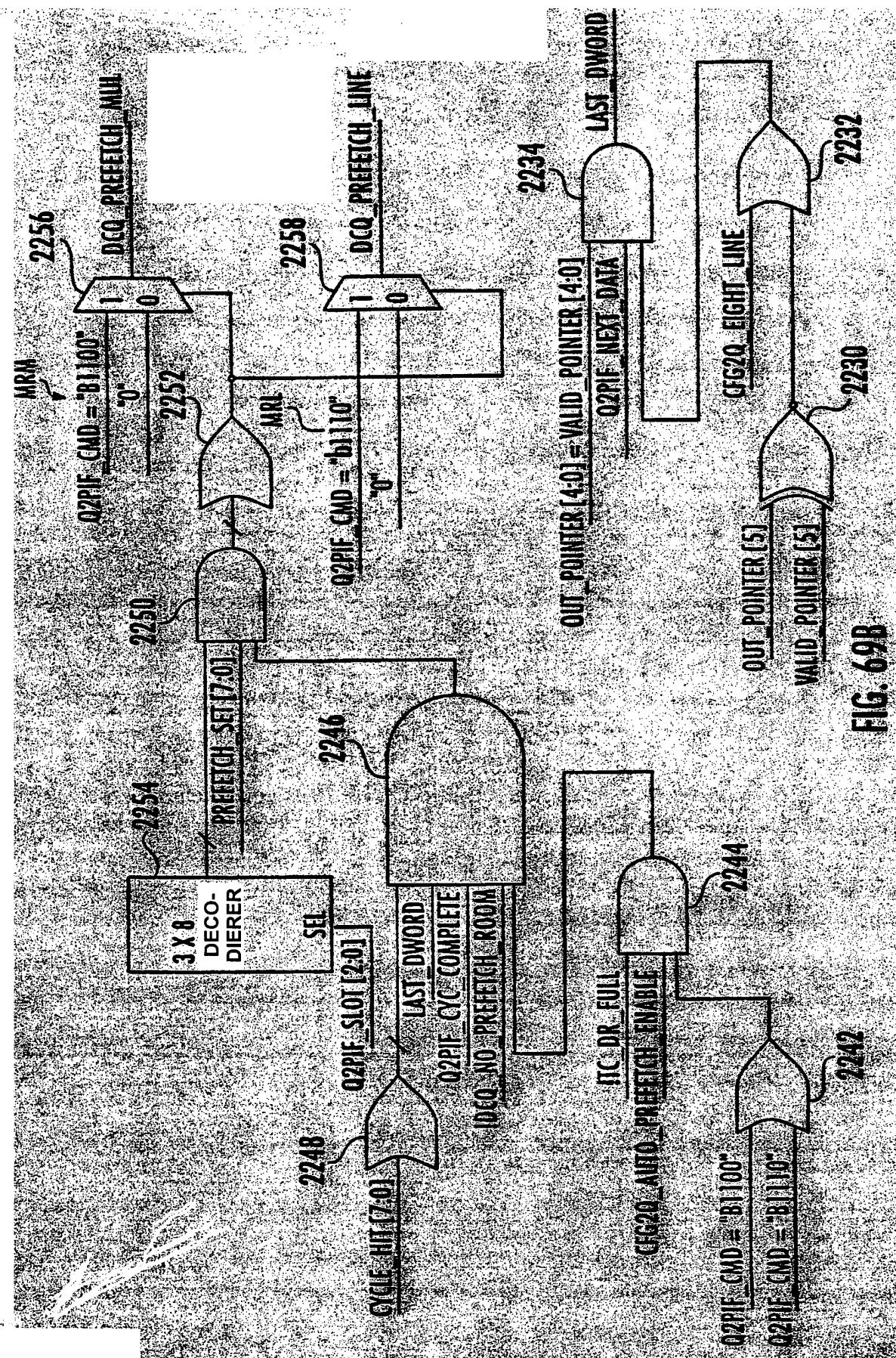

- [0090] **Fig.** 66–69b zeigen schematische Diagramme einer verzögerten Abschluss-Warteschlange, umfassend eine Steuerlogik.

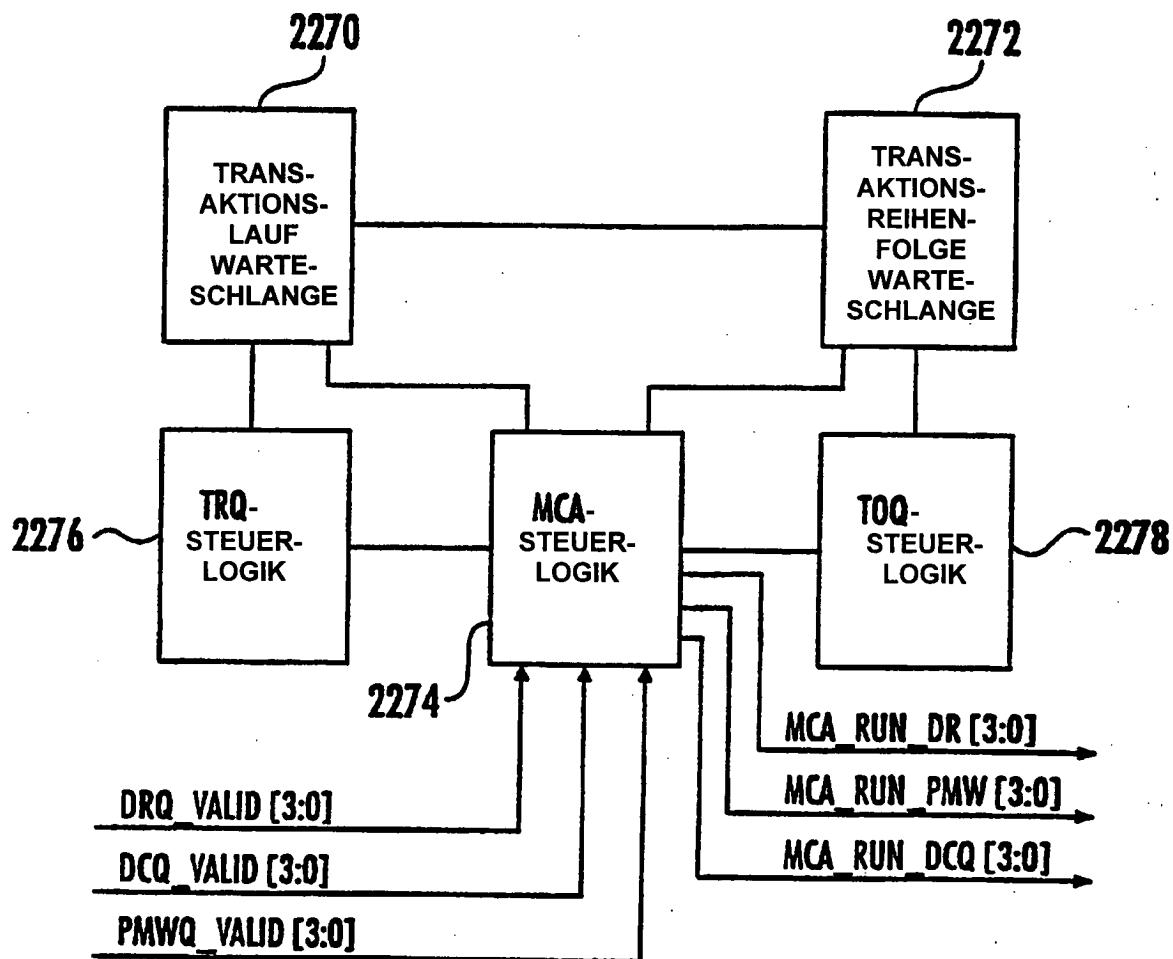

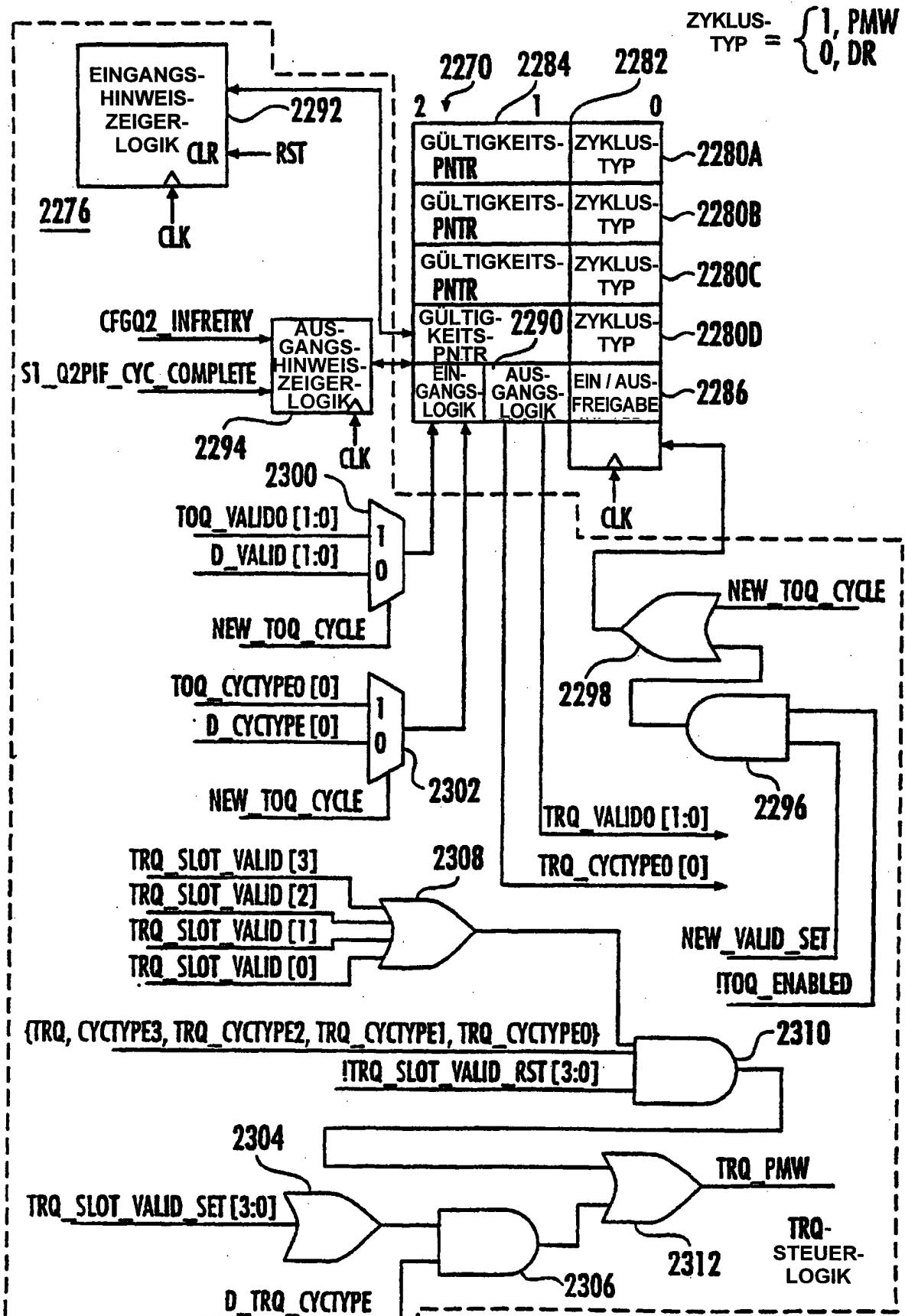

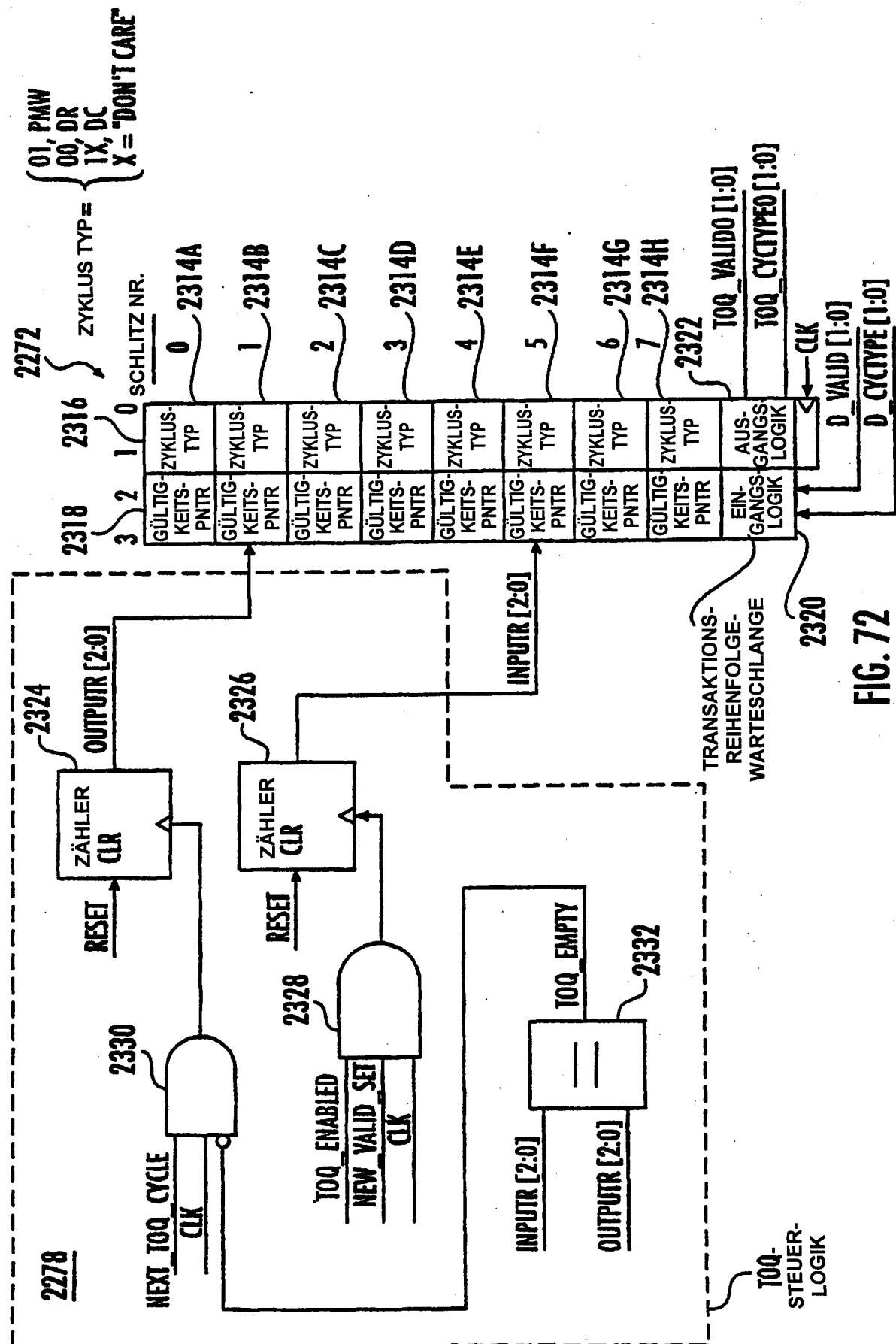

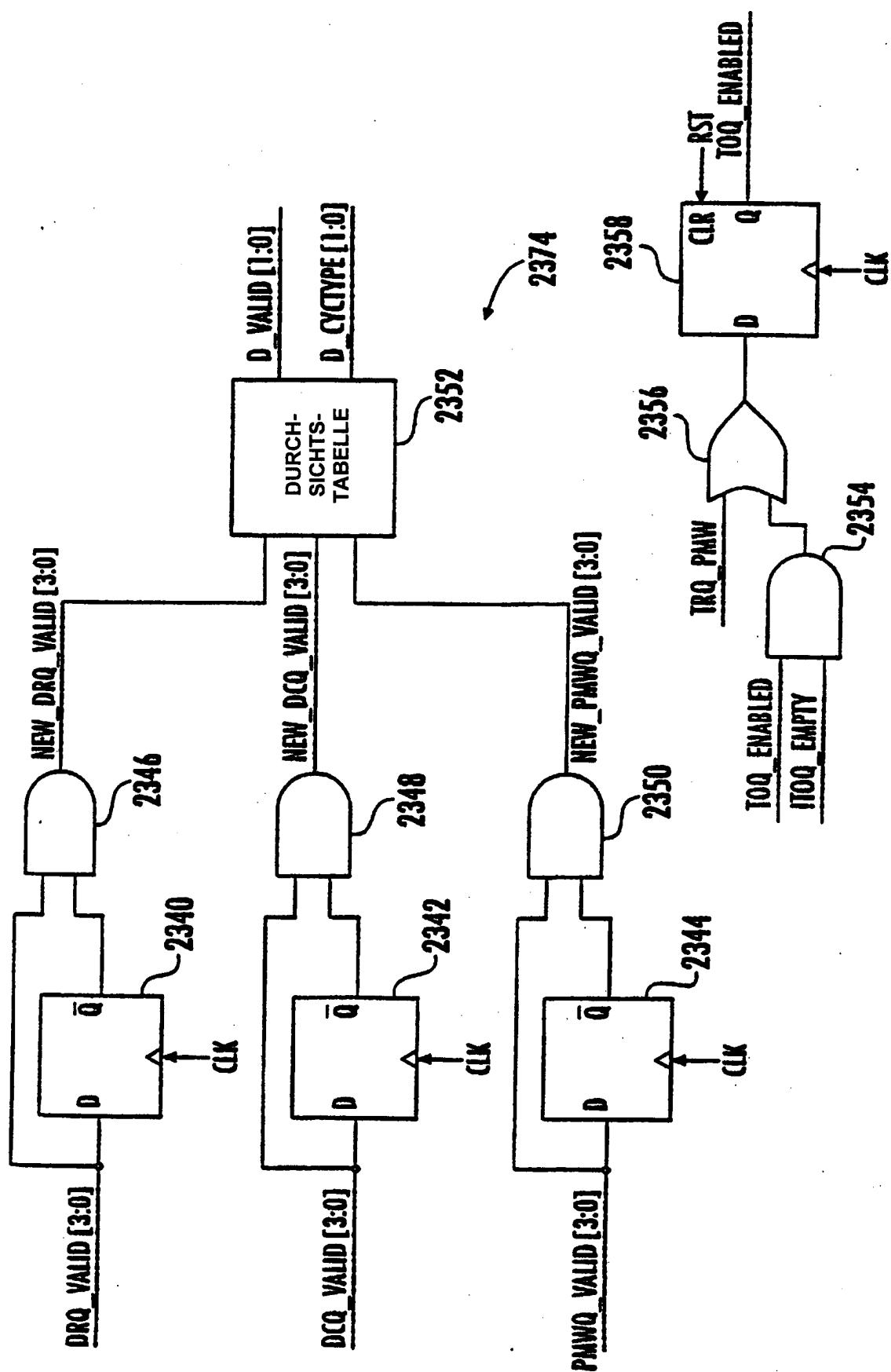

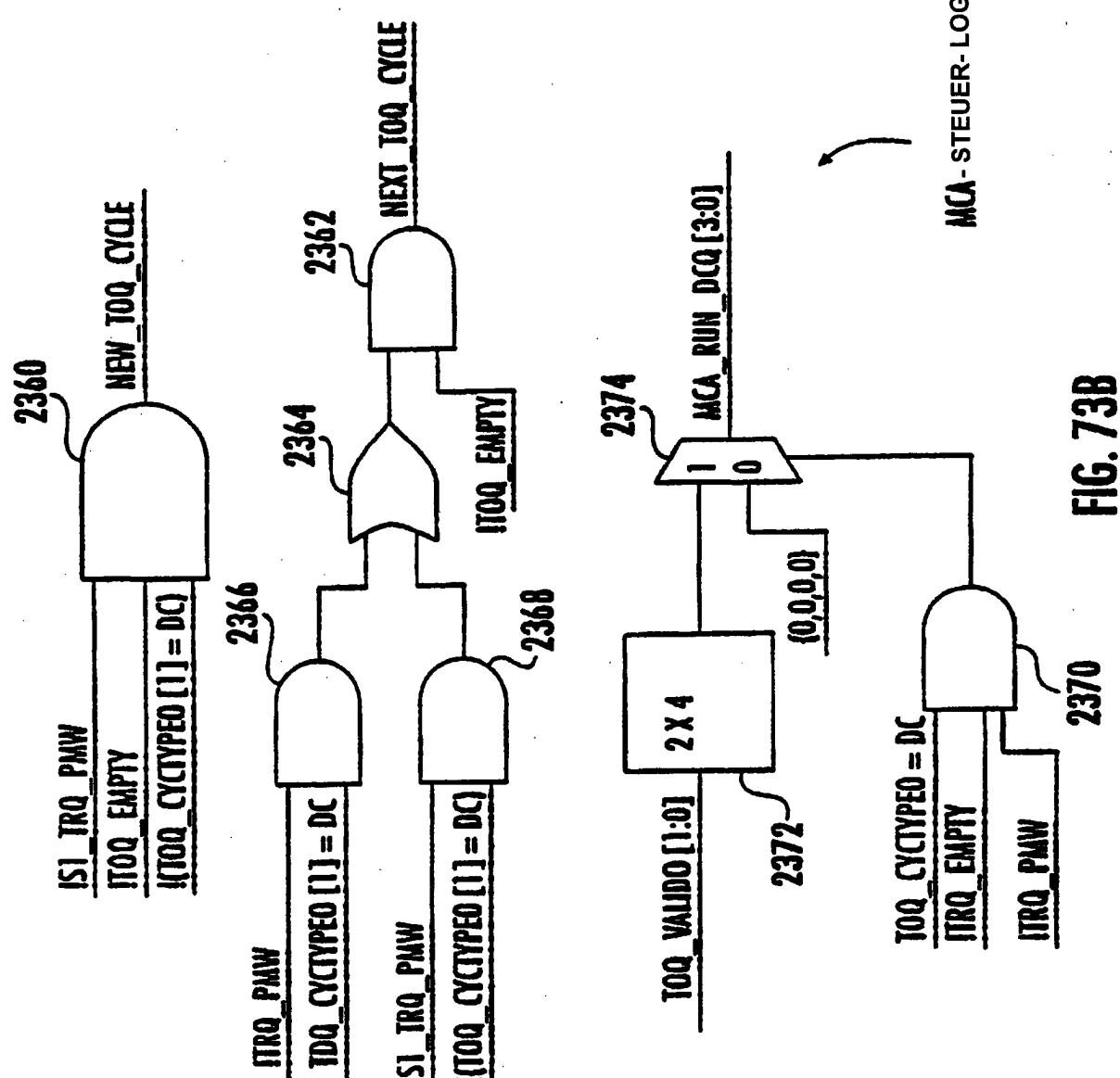

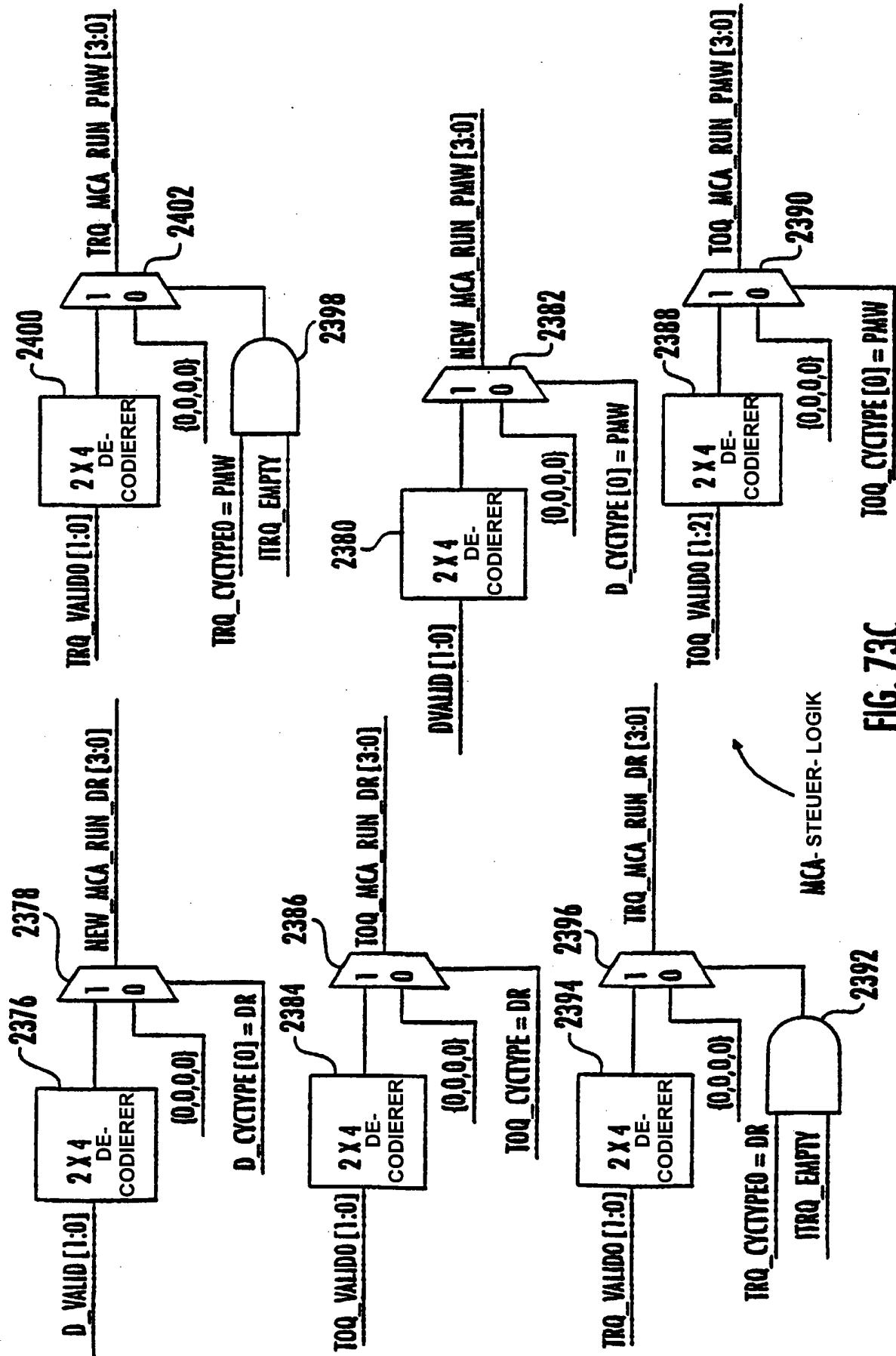

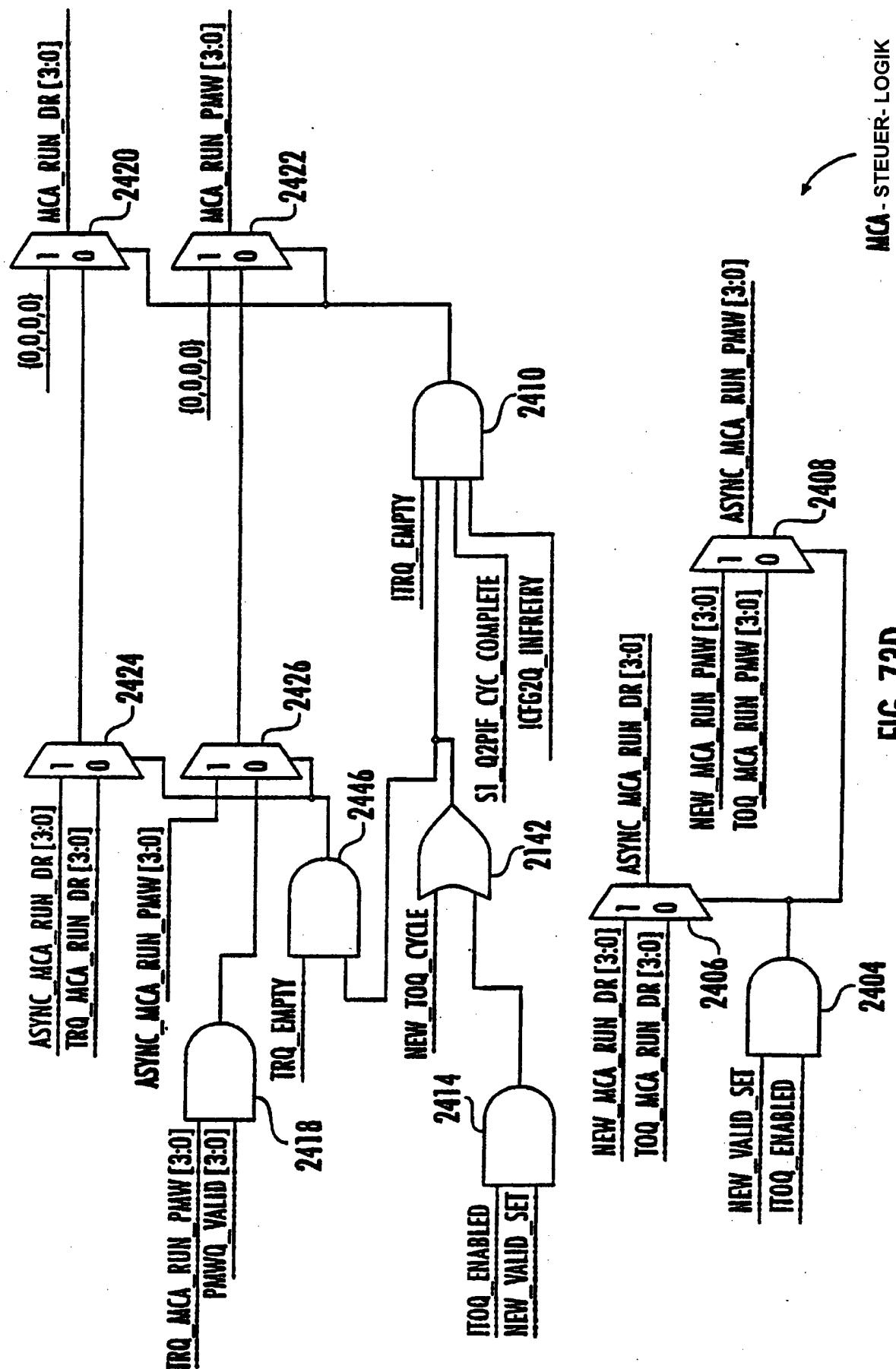

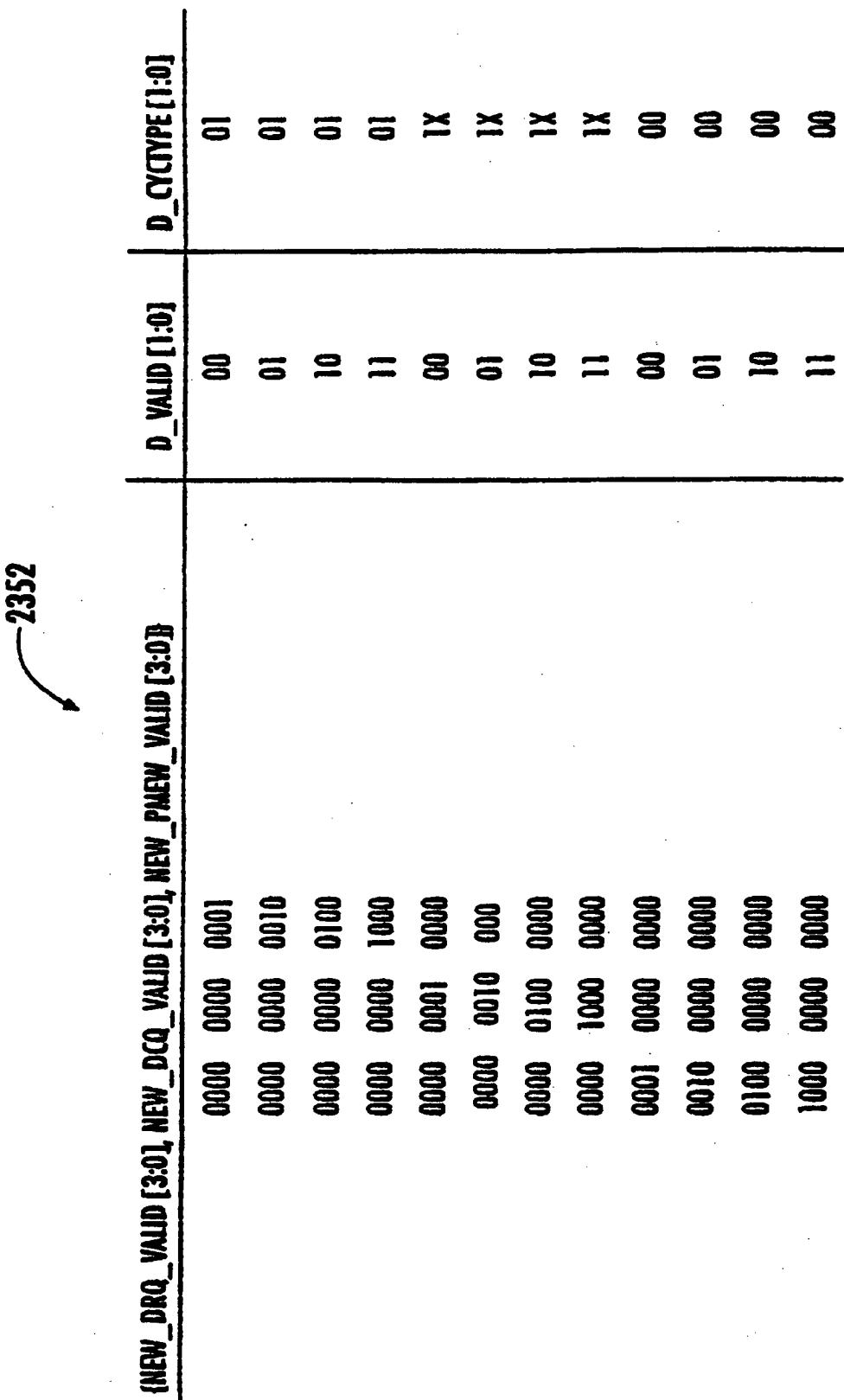

- [0091] **Fig.** 70–74 zeigen schematische Diagramme und eine Tabelle einer Master-Zyklus-Entscheidungseinrichtung.

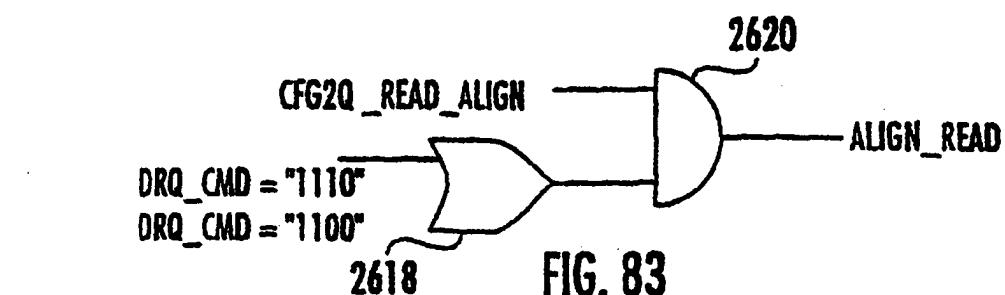

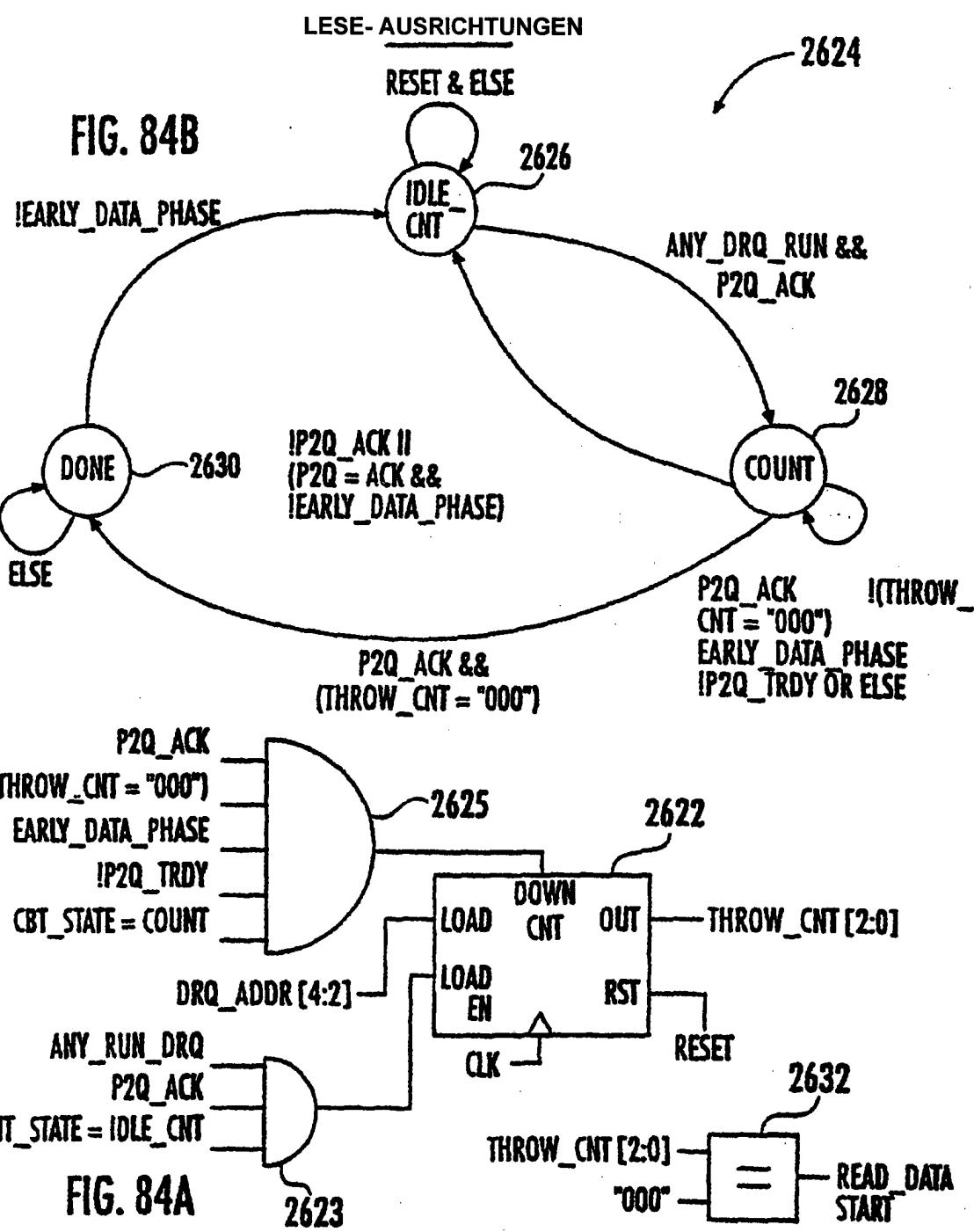

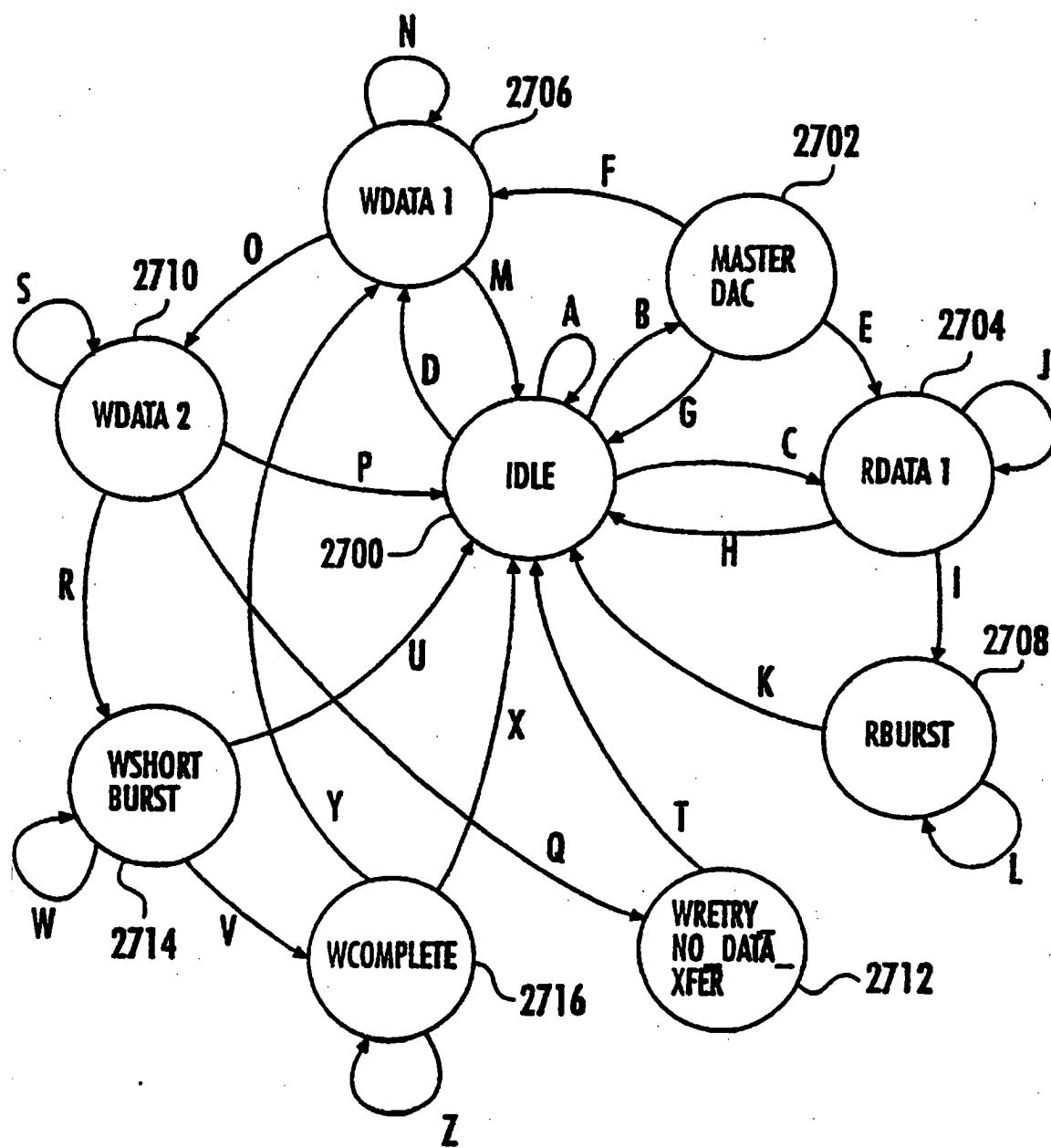

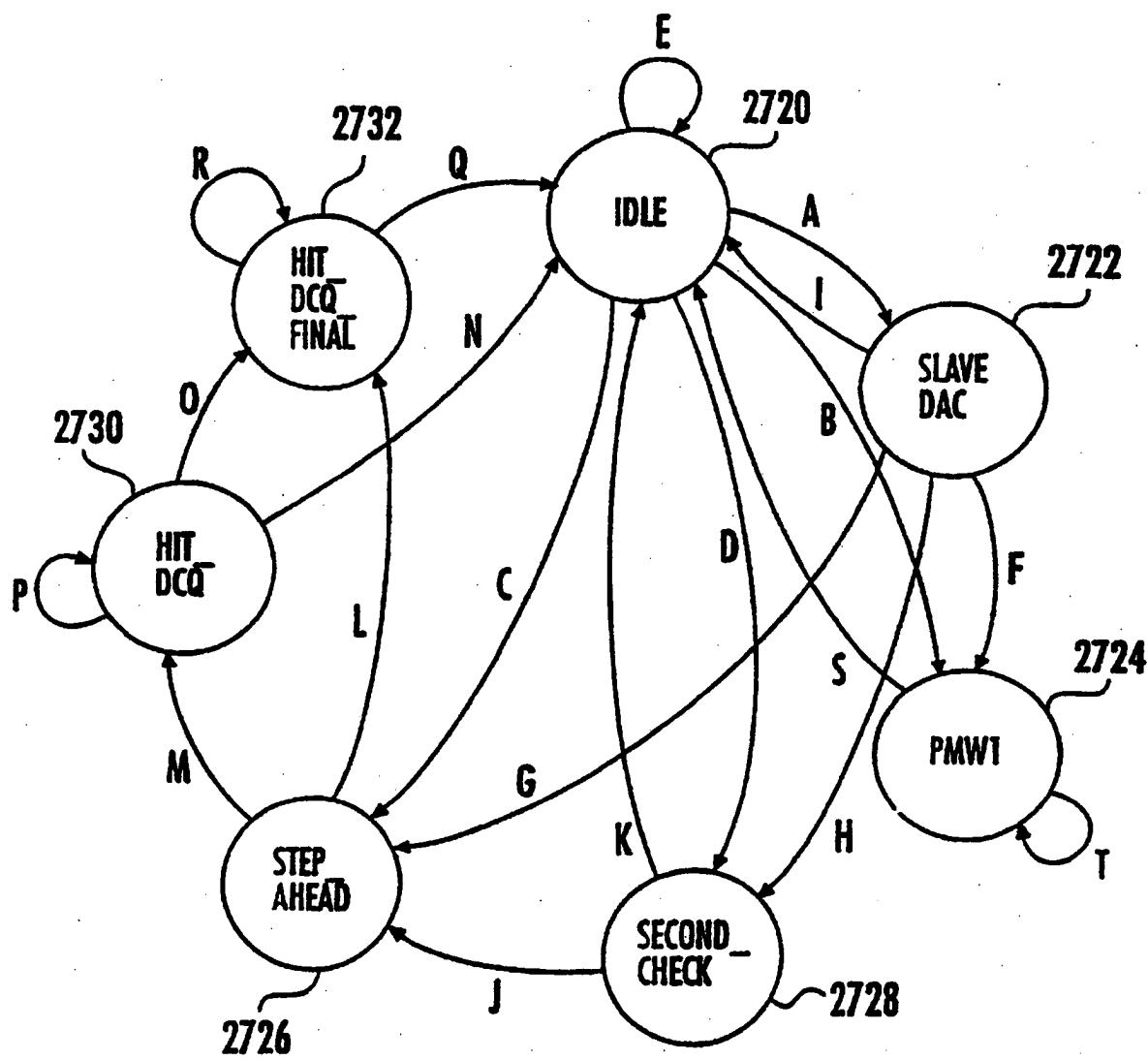

- [0092] **Fig.** 75–87 zeigen schematische und Zustand-Übergangs-Diagramme einer Warteschlange-Block-zu-PCI-Bus-Schnittstelle.

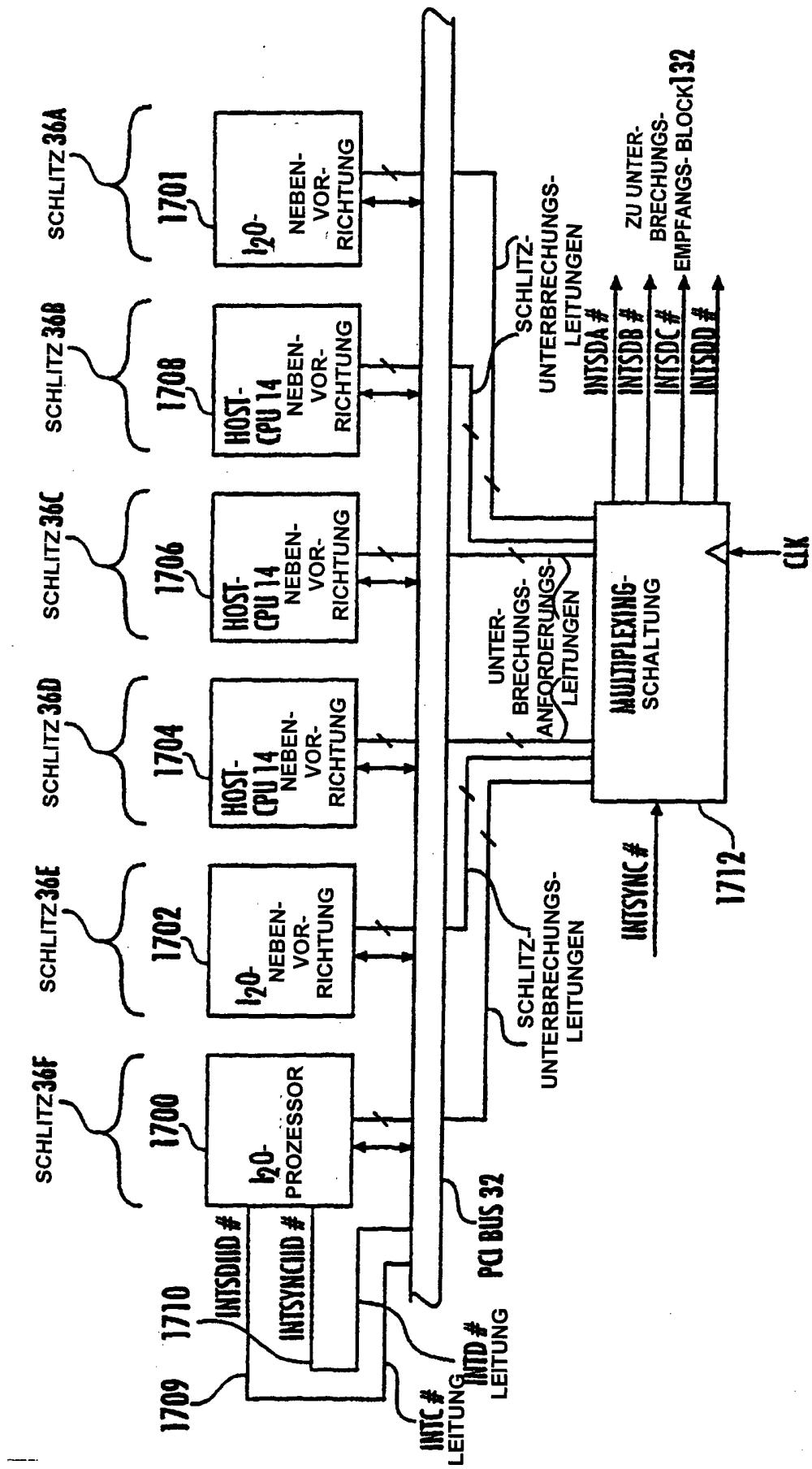

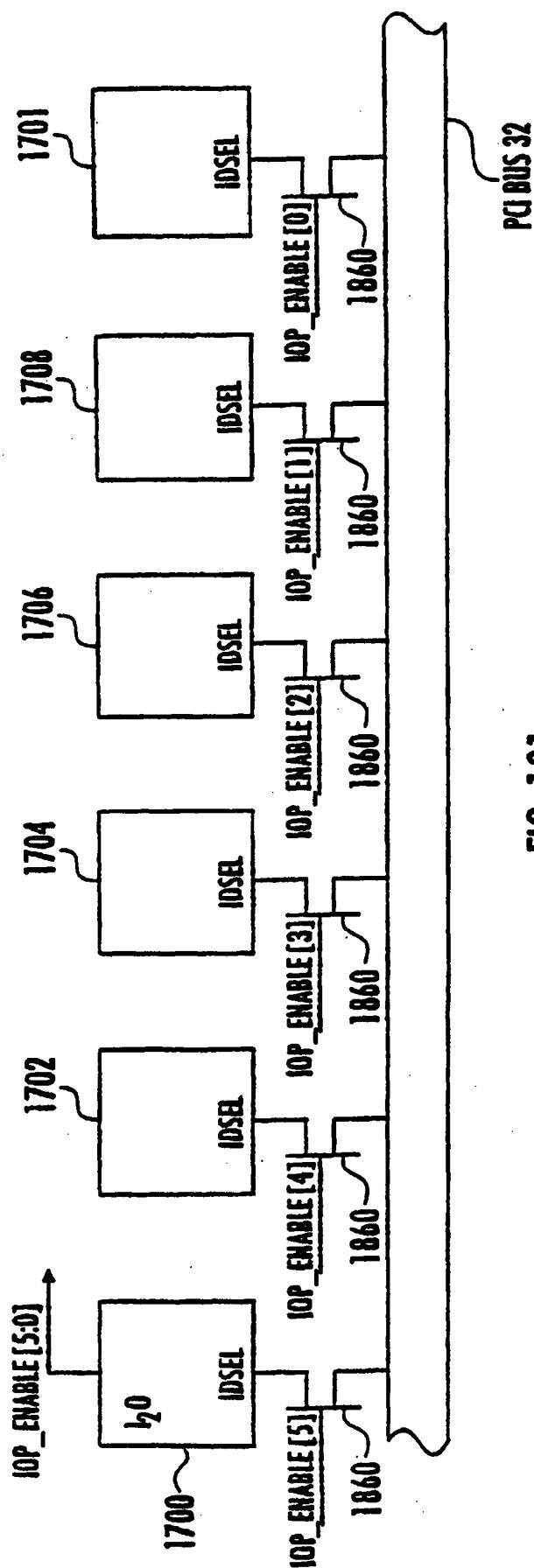

- [0093] **Fig.** 88 zeigt ein schematisches Blockdiagramm, das Bus-Vorrichtungen darstellt, verbunden mit einem Expansions-Bus.

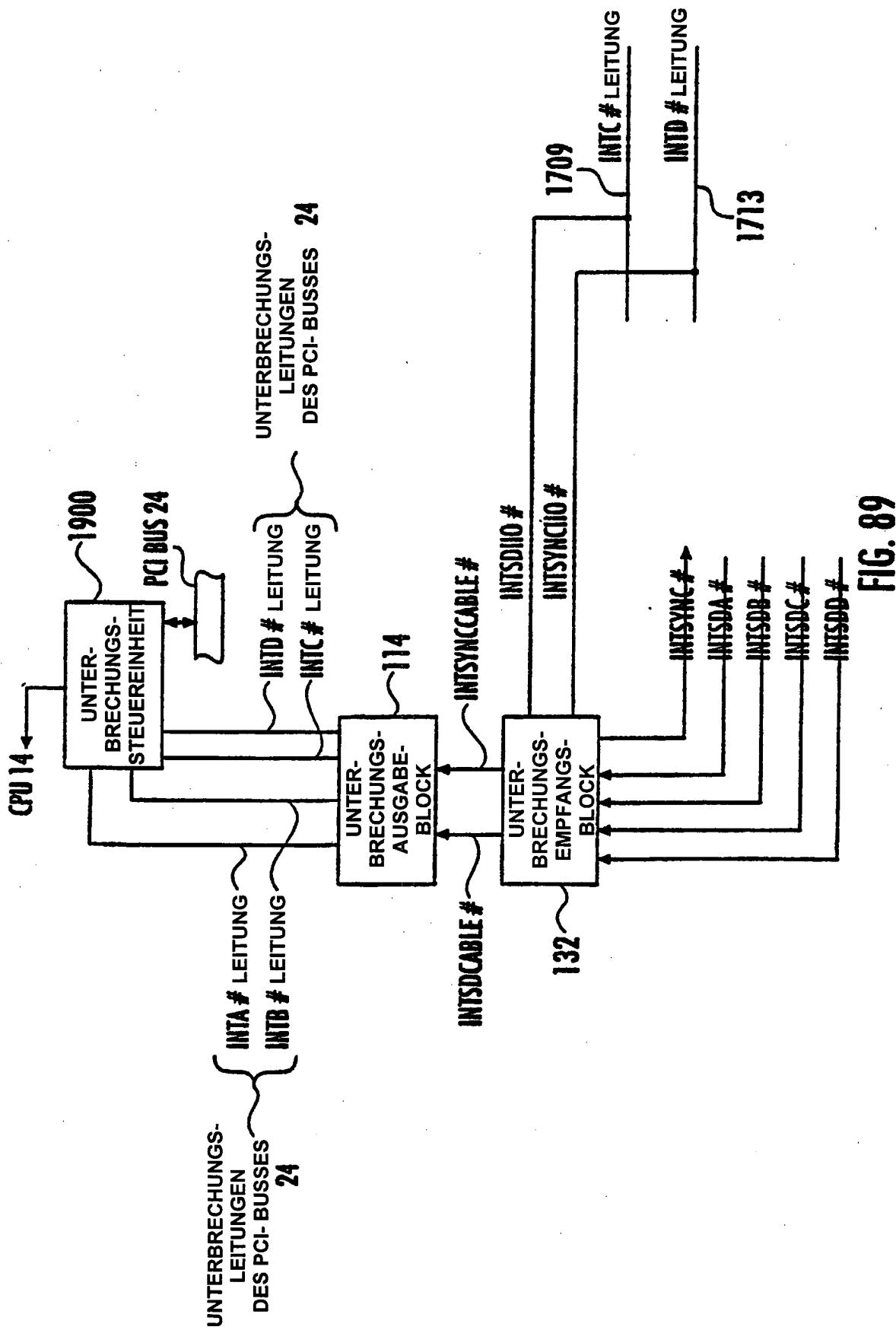

- [0094] **Fig.** 89 zeigt ein schematisches Blockdiagramm, dass eine Schaltung darstellt, um Unterbrechungs-Anforderungen weiterzuführen.

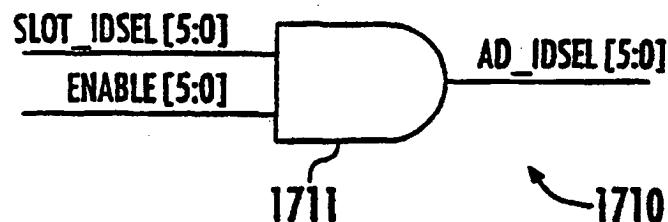

- [0095] **Fig.** 90 zeigt ein schematisches Diagramm einer Vorrichtungs-Auswahl-Logik.

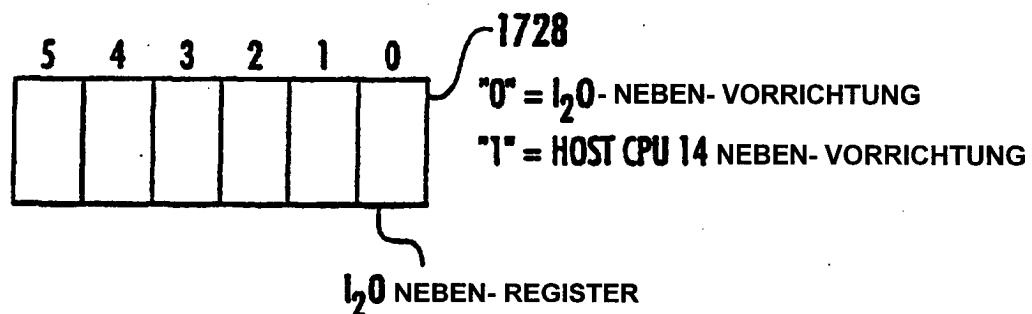

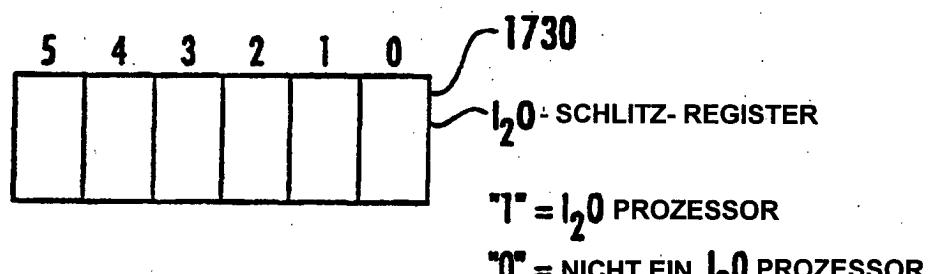

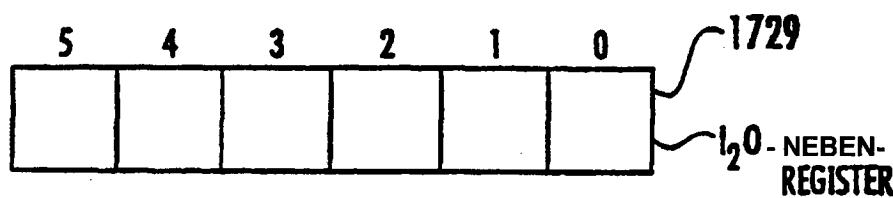

- [0096] **Fig.** 91–94 zeigen schematische Blockdiagramme von Registern.

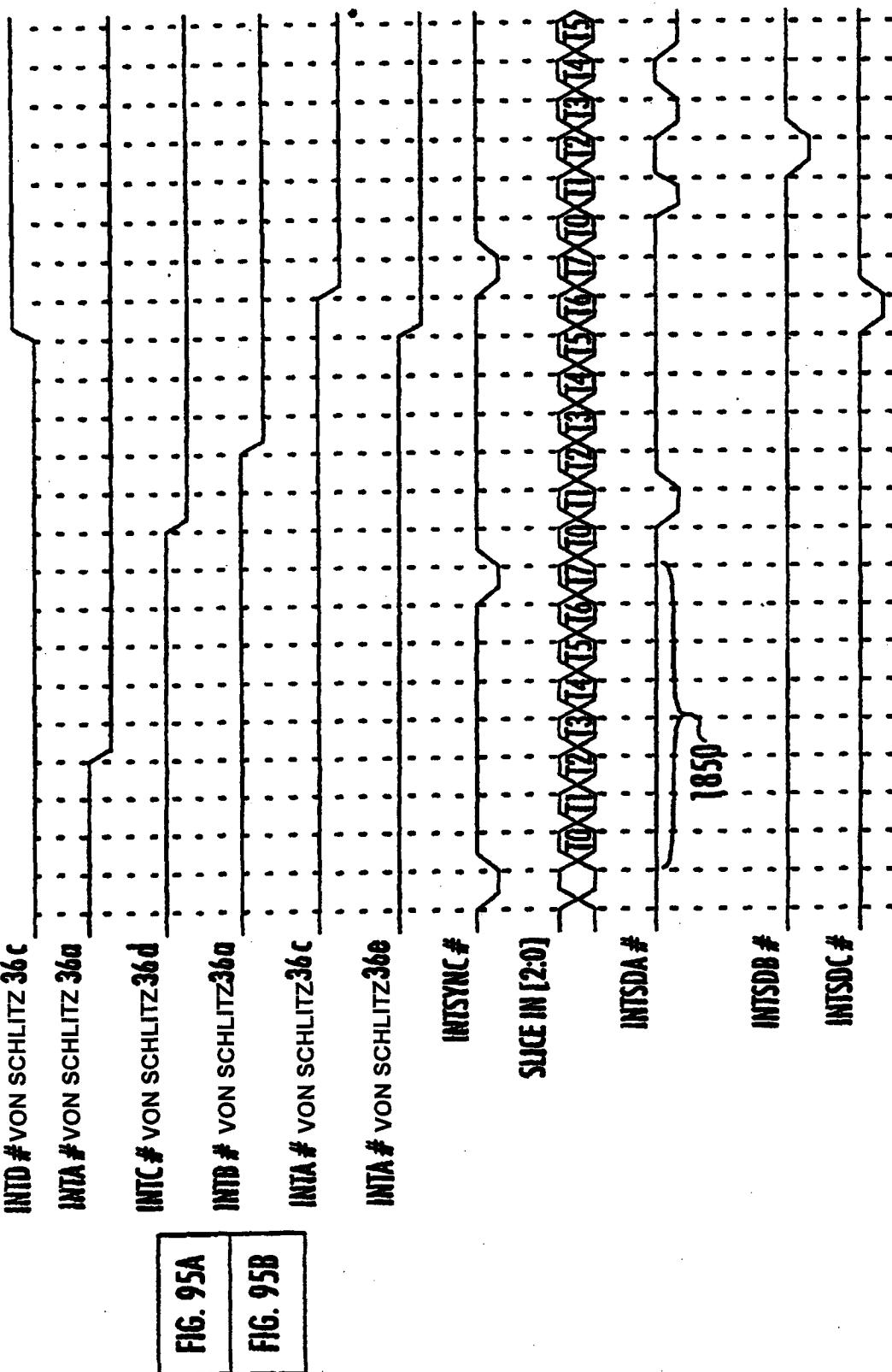

- [0097] **Fig.** 95 zeigt eine grafische Darstellung, die Wellenformen für das Computersystem darstellt.

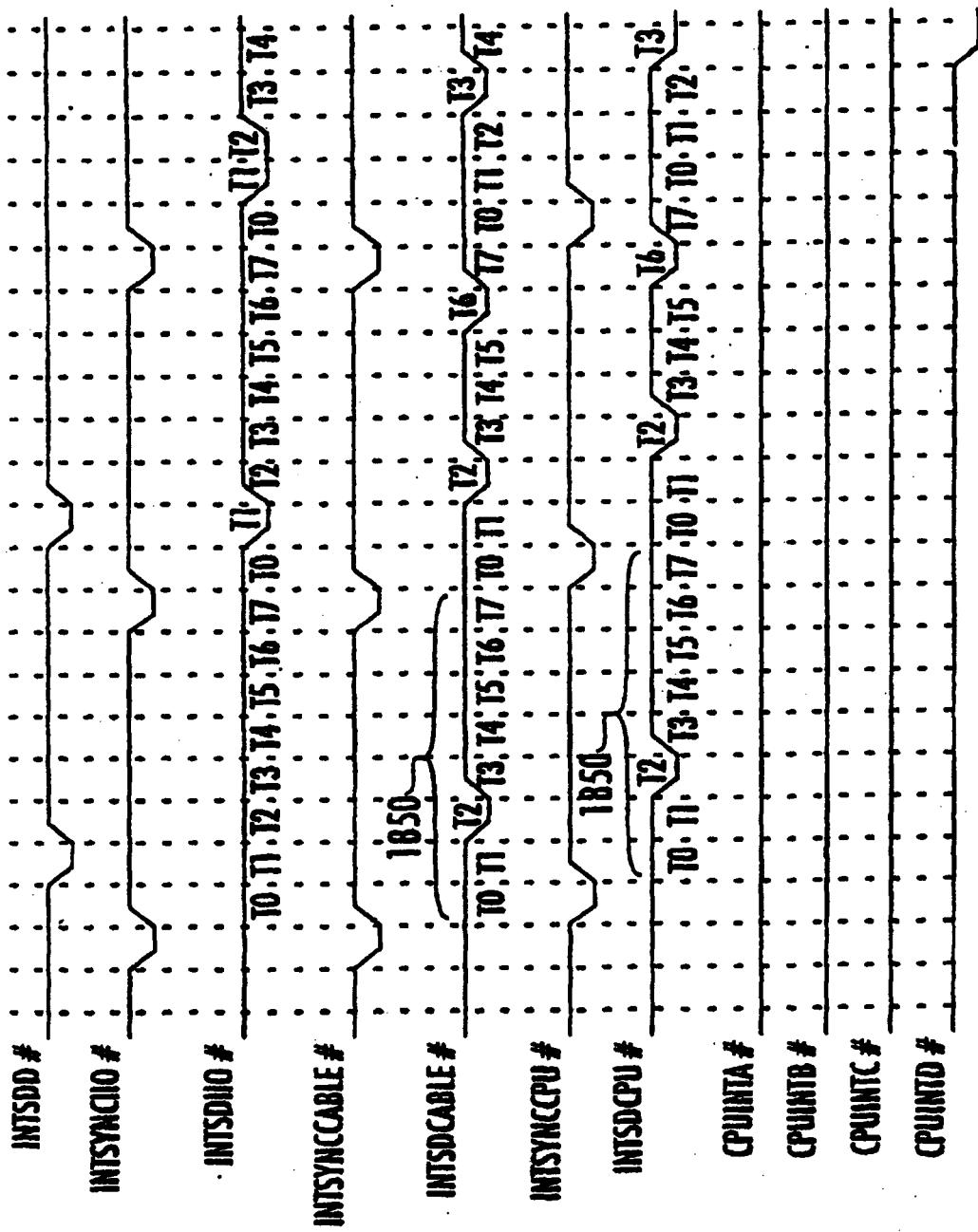

- [0098] **Fig.** 96 zeigt ein schematisches Diagramm der im Multiplex-Betrieb arbeitenden Schaltung.

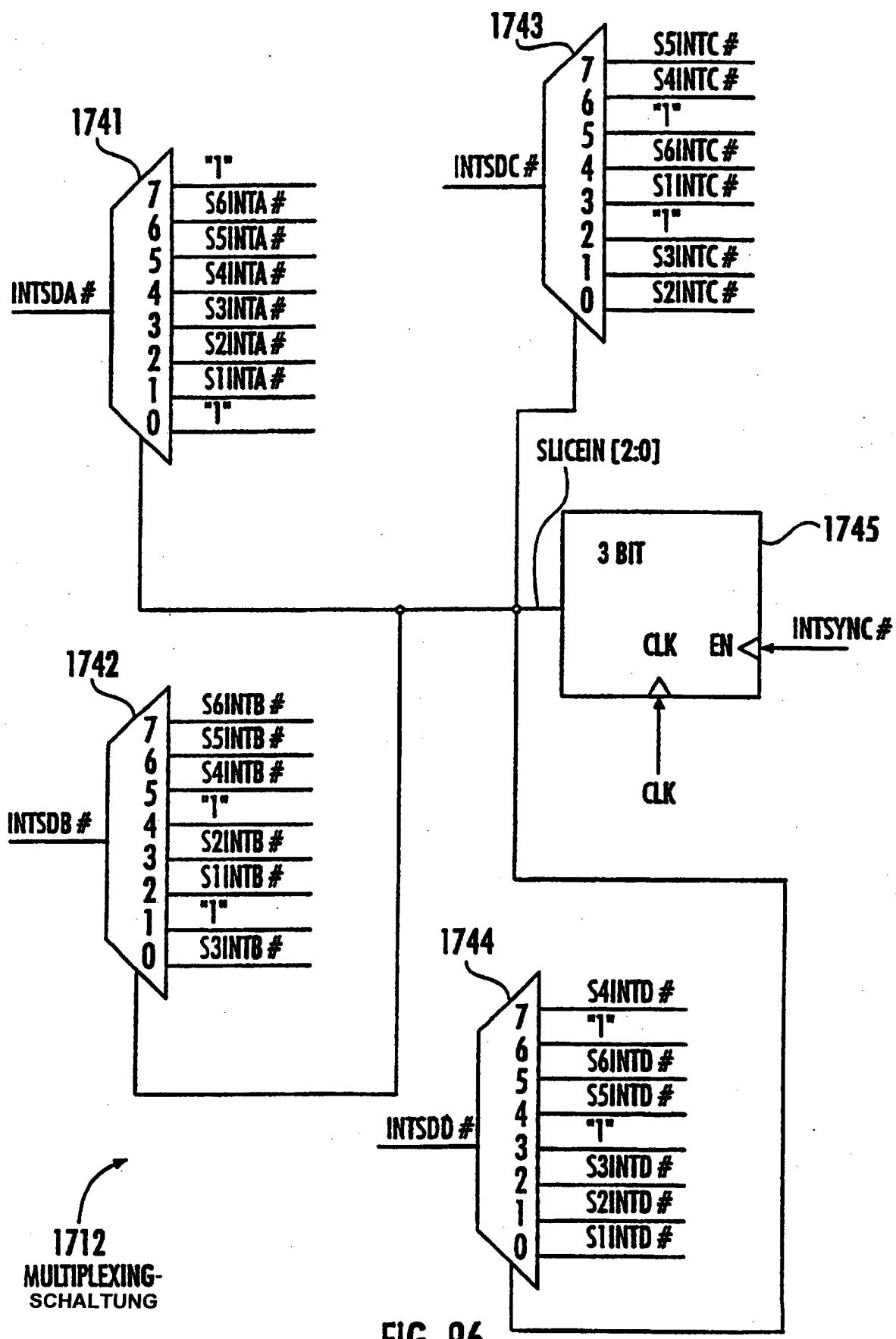

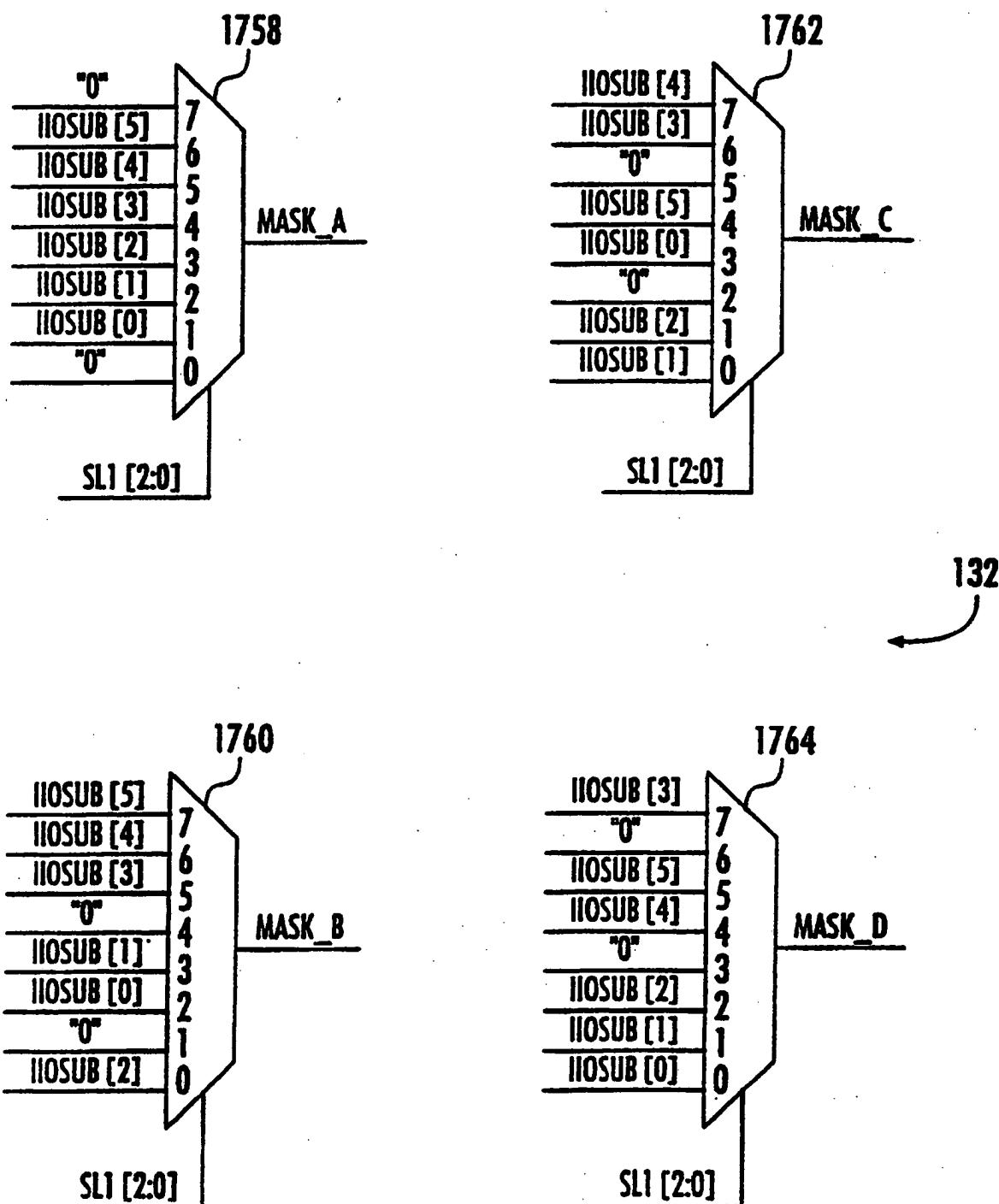

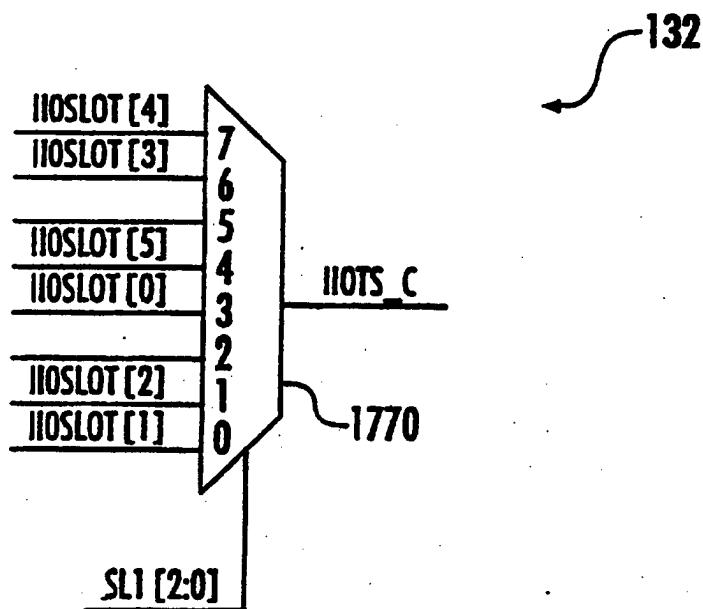

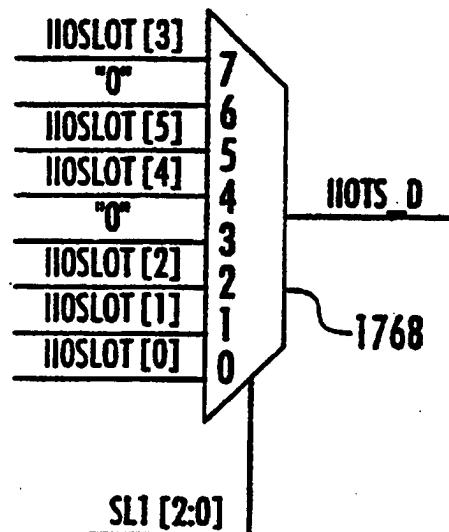

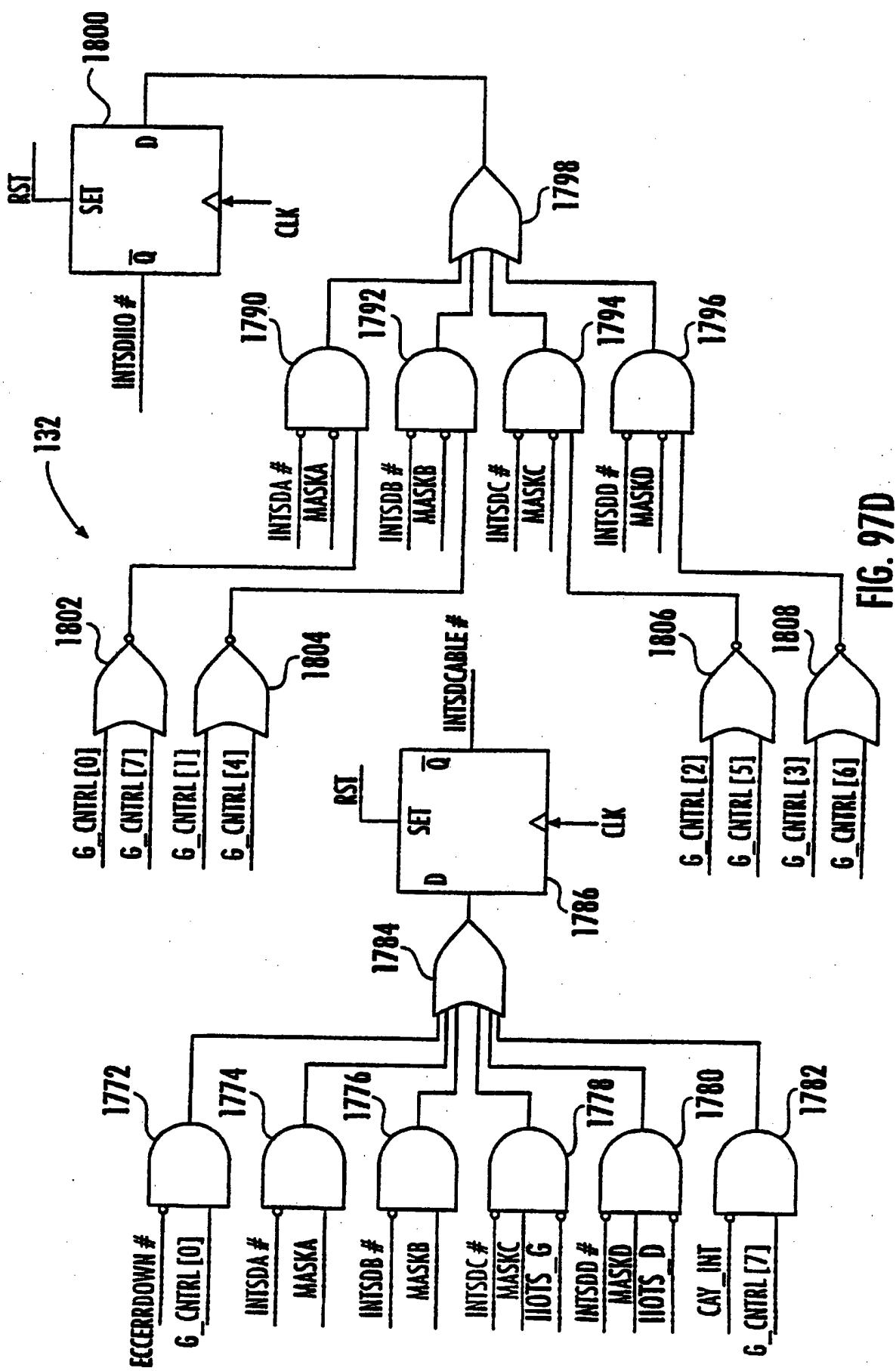

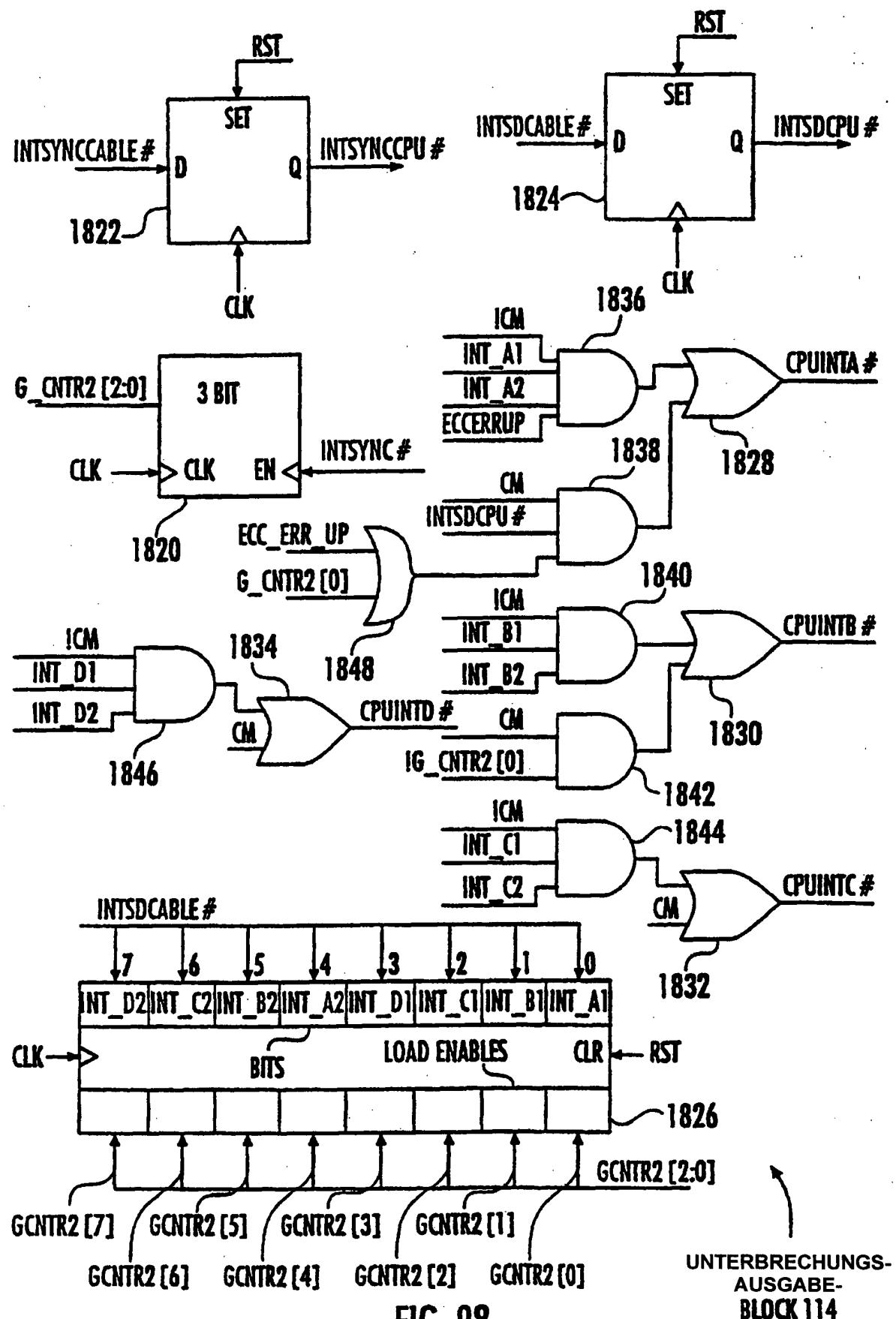

- [0099] **Fig.** 97A–D zeigen schematische Diagramme des Unterbrechungs-Aufnahme-Blocks.

- [0100] **Fig.** 98 zeigt ein schematisches Diagramm des Unterbrechungs-Ausgabe-Blocks.

- [0101] **Fig.** 99 zeigt ein Diagramm, das die Zeitmultiplexverarbeitung von Unterbrechungs-Anforderungs-Signalen darstellt.

- [0102] **Fig.** 100 zeigt ein Diagramm, das eine Unterbrechungs-Anforderungs-Auflistung darstellt.

- [0103] Figur 101 zeigt ein schematisches Blockdiagramm, dass Bus-Vorrichtungen darstellt, verbunden mit einem Erweiterungsbust.

## ÜBERSICHT

- [0104] In der folgenden Beschreibung geben alle Signal-Mnemoniken, gefolgt durch ein „#“, „\_“ oder „!“, oder diesen vorausgehend, invertierte, logische Zustände an.

- [0105] Wie in **Fig.** 1 dargestellt ist, umfasst ein Computersystem **10** einen primären PCI-Bus **24**, der mit einem Brücken-Chip **26a** und einem Brücken-Chip **26b** verbunden ist, wobei beide davon von einem gemeinsamen Design **26** sind. Der Brücken-Chip **26a** ist mit einem Brücken-Chip **48a** über ein Kabel **31** verbunden und der Brücken-Chip **26b** ist mit dem Brücken-Chip **48b** über ein Kabel **28** verbunden. Die Brücken-Chips **48a** und **48b** sind von einem gemeinsamen Design **48**, was gemeinsam zu dem Design **26** ist, mit der Ausnahme, dass das Design **26** ein eingangsseitiger Mode ist und das Design **48** ein ausgangsseitiger Mode ist.

- [0106] Der PCI-Bus **24** ist mit einem lokalen Bus **22** über eine System-Steuereinheit/Host-Brücken-Schaltung **28** schnittstellenmäßig verbunden. Die Systemsteuereinheit/Host-Brücken-Schaltung **18** steuert auch einen Zugriff zu einem Systemspeicher **20**, der auch mit dem lokalen Bus **22** zusammen mit der CPU **14** und einem Level-2-(L2)-Cachespeicher **16** verbunden ist.

- [0107] Eine PCI Extended Industry Standard Architecture (EISA) Brücke **15** verbindet schnittstellenmäßig den PCI-Bus **24** mit einem ISA-Bus **17**. Sowohl eine Tastenfeld-Steuereinheit **21** als auch ein Read Only Memory (ROM) **23** sind mit dem ISA-Bus **17** verbunden. Ein nicht-flüchtiger Random Access Speicher (NVRAM) **70**, verbunden mit dem ISA-Bus **17**, speichert Informationen, die das Computersystem übernehmen sollte, wenn es abgeschaltet wird. Ein automatischer Server-Zurückgewinnungs-Zeitgeber **72** überwacht das Computersystem hinsichtlich einer Inaktivität. Falls sich das System verriegelt, wird der ASR-Zeitgeber **72** nach ungefähr 10 Minuten ablaufen. Ein Tastenfeld **19** wird durch die Tastenfeld-Steuereinheit **21** hinsichtlich einer Erfassung von niedergedrückten Tasten überwacht.

- [0108] Wie **Fig.** 2 zeigt, bildet der Brücken-Chip **48a** eine Schnittstelle zu einem PCI-Bus **32a** und der Brücken-Chip **48b** bildet eine Schnittstelle zu einem PCI-Bus **32b**. Die PCI-Busse **32a** und **32b** sind an zwei Expansionskästen **30a** und **30b**, mit einem gemeinsamen Design **30**, angeordnet, und jeder Expansionskasten **30** besitzt sechs Hot-Plug-Schlüsse bzw. Steckplätze **36** (**36a–f**), die dazu geeignet sind, herkömmliche Erweiterungskarten **807** aufzunehmen (**Fig.** 27A). Ein Schlitz **34** an dem Expansionskasten nimmt eine Karte **46** auf, die den Brücken-Chip **26** besitzt. Jeder Hot-Plug-Schlitz **36** besitzt zugeordnet eine Umschalt-Schaltung **41** zum Verbinden und Trennen des Schlitzes **36** mit und von dem PCI-Bus **32**. Sechs mechanische Hebel **802** werden dazu verwendet, selektiv die Karten **807** an entsprechenden Schlitten zu sichern (wenn sie geschlossen oder verriegelt sind), wie weiterhin in der US-Patentanmeldung Serial-Nr. 08/658385, mit dem Titel „Secu-

ring a Card in an Electronic Device", angemeldet an demselben Datum wie diese Anmeldung und hier unter Bezugnahme darauf eingeschlossen, beschrieben ist. Jeder Erweiterungskasten **30** umfasst Register **52** und **82** zum Überwachen der Hebel **802** und von Status-Signalen des Erweiterungskastens **30** und ein Register **80** zum Kontrollieren einer Verbindung und einer Trennung von Schlitzen **36** und von dem PCI-Bus **32**.

[0109] Wie **Fig. 3** zeigt, ist der Brücken-Chip so ausgelegt, um in Paaren **26** und **48** verwendet zu werden, um eine PCI-PCI-Brücke zwischen dem primären PCI-Bus **24** und dem sekundären PCI-Bus **32** zu bilden. Das Programmiermodell ist dasjenige von zwei hierarchischen Brücken. Zu der Systemsoftware hin erscheint das Kabel **28** als ein PCI-Bus, der exakt eine Vorrichtung enthält, und zwar den ausgangsseitigen Brücken-Chip **48**. Dies vereinfacht stark die Konfiguration der 2-Chip-PCI-PCI-Brücke, die den primären und sekundären Bus miteinander verbindet. Der Brücken-Chip **26**, der näher zu der CPU **14** hin liegt, verbindet den primären PCI-Bus **24** mit dem Kabel **28**. Die zweite PCI-PCI-Brücke **48** ist in dem Erweiterungskasten **30** vorhanden und verbindet das Kabel **28** mit dem sekundären Bus **32**. Ein Mode-Stift-Upstream-Chip bestimmt, ob der Brücken-Chip in dem ausgangsseitigen Mode oder dem eingangsseitigen Mode arbeitet. Einige Nicht-Brücken-Funktionen, wie beispielsweise ein Bus-Monitor **106** und eine Hot-Plug-Logik in einem SIO **50**, werden nur in dem Erweiterungskasten **30** verwendet und sind nicht in dem einlaufseitigen Mode-Chip **26** funktional.

[0110] Ein Taktgenerator **102** in dem Brücken-Chip **26** erzeugt Takte basierend auf dem Takt PCI CLK1 auf dem primären PCI-Bus **24**, wobei einer der erzeugten Takte über das Kabel **28** zu einem Taktgenerator **122** in dem ausgangsseitigen Brücken-Chip **48** vorgesehen wird. Der Taktgenerator **122** erzeugt die PCI-Takte in dem Erweiterungskasten **30** bei derselben Frequenz des primären PCI-Busses **24** und steuert ihn an, was dazu führt, dass beide Brücken-Chips **26** und **48** unter derselben Frequenz laufen. Der ausgangsseitige Brücken-Chip **48** läuft dem eingangsseitigen Brücken-Chip **24** in der Phase mit der Verzögerung des Kabels **28** hinterher. Eine asymmetrische Grenze in dem eingangsseitigen Brücken-Chip **26** an dem Punkt, wo Daten von dem Kabel **28** abgegriffen werden, ermöglicht, dass sich die Phasenverzögerung bei irgendeinem Wert befindet (und deshalb soll das Kabel von irgendeiner Länge sein), wobei das einzige Erfordernis dasjenige ist, dass die Frequenz der zwei Brücken-Chips dieselbe ist.

[0111] Die Kern-Logik jedes Brücken-Chips ist der Brücken-Logik-Block (**100** oder **120**), der einen PCI-Master (**101** oder **123**) zum Arbeiten als ein Master auf dem jeweiligen PCI-Bus, ein PCI-Target oder eine -Slave (**103** oder **121**) zum Arbeiten als eine Slave-Vorrichtung auf dem jeweiligen PCI-Bus, Konfigurations-Register (**105** oder **125**), die die Konfigurations-Informationen des entsprechenden Brücken-Chips enthalten, und einen Warteschlangen-Block (**107** oder **127**), der verschiedene Warteschlangen enthält, in denen Daten, zugeordnet zu Transaktionen zwischen dem primären PCI-Bus und dem sekundären PCI-Bus **32**, in die Warteschlange gestellt und gemanagt werden, aufweist. Die Daten, übertragen zwischen dem eingangsseitigen Brücken-Chip **26** und dem ausgangsseitigen Brücken-Chip **48**, werden durch Kabelschnittstellen **104** und **130** in den Brücken-Chips **26** und **48** jeweils gepuffert.

[0112] Eine Unterbrechungs-Programm-Logik ist auch in jedem Brücken-Chip enthalten. Dabei sind 8 Unterbrechungen, 6 von den Sekundär-Bus-Schlitten, 1 von einer SIO-Schaltung **50** und 1 von dem ausgangsseitigen Brücken-Chip **48**, vorhanden. In dem ausgangsseitigen Chip **48** werden die Unterbrechungen durch einen Unterbrechungs-Aufnahme-Block **132** aufgenommen und entlang des Kabels **28** als eine serielle Datenfolge in sequenziellen Zeit-Stücken geschickt. In dem ausgangsseitigen Brücken-Chip **26** werden die Unterbrechungen durch einen Unterbrechungs-Ausgangs-Block **114** empfangen, der die Unterbrechungen zu einer Unterbrechungs-Steuereinheit weiterleitet.

[0113] Die SIO-Schaltung **50** liefert Steuersignale zum Beleuchten von LED's, zum Steuern eines Reset und für ein selektives Verbinden der Schlitze **36** mit dem Bus **32**. Sie umfasst auch eine Logik zum Lesen des Eingriffs-Status der Hebel **802** und des Status-Zustands der Karten **807** in jedem Schlitz **36**.

[0114] Die Brücken-Schaltung **26** umfasst einen Support für Unterbrechungen in dem Erweiterungskasten **30**, und, wenn sie in dem Host-System mit der anwendereigenen Schnittstelle zu einer Mehrfachkanal-Unterbrechungs-Steuereinheit installiert ist, schickt sie die Status-Zustände jeder Unterbrechung in einer seriellen Datenfolge. Die Brückenschaltung **26** kann auch so konfiguriert sein, um standardmäßige PCI-INTA, INTB, INTC und INTD Signale anzusteuern, falls sie in einem Standard-Schlitz in dem Host-System installiert ist.

[0115] Jeder Brücken-Chip umfasst auch einen PCI-Arbitrierer (**116** oder **124**) zum Steuern eines Zugriffs auf bis zu sieben Bus-Master. Da die eingangsseitige Brücke **26** in einem Schlitz installiert ist, wird der PCI-Arbitrierer **116** in dem eingangsseitigen Brücken-Chip **26** gesperrt. Jeder Brücken-Chip umfasst auch eine I<sup>2</sup>C-Steuereinheit (**108** oder **126**) für eine Kommunikation mit Vorrichtungen, wie beispielsweise EEPROMs, Temperatursensoren, usw., einen JTAG-Master (**110** oder **128**) zum Durchführen von Test-Zyklen, einen Bus-Monitor (**106** oder **127**) zum Messen einer Bus-Benutzung und einer Effektivität und der Effektivität des Vorabruf-Algorithmus des Brücken-Chips, und einen Bus-Beobachter (Bus-Watcher) (**119** oder **129**) zum Speichern einer Bus-Historie und von Status-Vektor-Informationen und zum Informieren der CPU **14** über einen Bus-Hängend-Zustand. Bestimmte Blöcke werden in jedem Brücken-Chip gesperrt, wenn sie nicht verwendet werden. In dem eingangsseitigen Brücken-Chip **26** werden Bus-Watcher **119**, der SIO **118**, der PCI-Arbitrierer **116** und der Bus-Monitor **106** gesperrt. Zusätzlich werden der die Unterbrechung aufnehmende Block **112** in dem ein-

gangsseitigen Chip **126** und der Unterbrechungs-Ausgangs-Block **134** in dem ausgangsseitigen Chip **48** gesperrt.

## ÜBERSICHT DES WARTESCHLANGEN-BLOCKS

[0116] Wie **Fig. 4** zeigt, managen die Warteschlangen-Blöcke **107** und **127** Transaktionen, die zwischen dem primären PCI-Bus **24** (in dem eingangsseitigen Chip) oder dem sekundären PCI-Bus **32** (in dem ausgangsseitigen Chip) und der Kabel-Schnittstelle **130** fließen.

[0117] (Von hier an wird auf den ausgangsseitigen Brücken-Chip unter der Annahme Bezug genommen, dass der eingangsseitige Chip identisch arbeitet, ohne dass dies ansonsten angegeben ist). Der Warteschlangen-Block **127** umfasst einen Kabel-Decodierer **146**, der von der Kabel-Schnittstelle **130** Transaktionen aufnimmt, die auf dem sekundären PCI-Bus **32** abgeschlossen werden. Nach einem Decodieren einer Transaktion platziert der Decodierer **146** die Transaktionen, zusammen mit allen Informationen, umfasst in der Transaktion, in eine von drei Warteschlangen **140**, **142** und **144**. Jede Warteschlange enthält verschiedene Transaktions-Puffer, wobei jeder davon eine einzelne Transaktion speichert, und ist deshalb in der Lage, verschiedene Transaktionen simultan zu handhaben.

[0118] Die erste Warteschlange, eine gepostete Speicher-Schreib-Warteschlange (PMBQ) **140**, speichert gepostete Speicher-Schreib-Zyklen, ausgegeben durch die CPU, auf dem primären Bus zusammen mit allen Informationen, die erforderlich sind, um jeden Zyklus auf dem sekundären Bus **32** auszuführen. Die PMWQ **140** besitzt vier Transaktions-Puffer, wobei jeder davon eine gepostete Speicher-Schreib-Transaktion hält, die bis zu 8 Cache-Linien (256 Bytes) an Daten enthält. Unter bestimmten Umständen kann eine gepostete Speicher-Schreib-Transaktion, die mehr als acht Cache-Linien bzw. -Zeilen an Daten besitzt, in einen oder mehrere darauffolgende Puffer überlaufen, wie dies nachfolgend beschrieben ist.

[0119] Die zweite Warteschlange, eine verzögerte Anforderungs-Warteschlange (Delayed Request Queue – **142**), speichert verzögerte Anforderungs-Transaktionen (d. h. verzögerte Lese-Anforderungen (Delayed Read Requests – DRR), wie beispielsweise ein Speicher-Lesen (Memory Read – MR), eine Speicher-Lese-Linie (Memory Read Line – MRL), und Speicher-Lese-Mehrzahl-(Memory Read Multiple – MRM)-Anforderungen; und in dem ausgangsseitigen Chip, Eingangs/Ausgangs-(I/O)-Lese-Schreib-Vorgänge und Konfigurationen (config – Lese/Schreib-Vorgänge), ausgegeben durch die CPU auf dem primären Bus, zusammen mit allen Informationen, erforderlich dazu, jede Transaktion auf dem sekundären Bus **32** auszuführen. Die DRQ **142** besitzt drei Transaktions-Puffer, wobei jeder davon in der Lage ist, ein Doppelwort, oder „dword“, an Daten für verzögerte Schreibvorgänge zu halten.

[0120] Die dritte Warteschlange, eine verzögerte Abschluss-Warteschlange (Delayed Completion Queue (DCQ)) **144**, speichert verzögerte Abschluss-Informationen, geliefert durch den eingangsseitigen Chip, in Abhängigkeit von verzögerten Anforderungs-Transaktionen, erzeugt auf dem sekundären Bus **32**. Für eine verzögerte Lese-Anforderung enthalten die entsprechenden Abschluss-Informationen die Lese-Daten, angefordert durch die initierende Vorrichtung, und den Lese-Status (d. h. eine Indikation darüber, ob ein Paritäts-Fehler auf dem Target-Abort aufgetreten ist). Die verzögerten Abschluss-Informationen, zurückgeführt für eine verzögerte Schreib-Transaktion, sind dieselben wie diejenigen, zurückgeführt für eine verzögerte Lese-Anforderung, mit der Ausnahme, dass keine Daten für verzögerte Schreibvorgänge zurückgeführt sind. Da I/O- und config-Lese-Schreibvorgänge nur auf dem ausgangsseitigen Bus auftreten, wird nur die eingangsseitige DCQ verzögerte Abschluss-Informationen entsprechend zu einer von diesen Transaktionen enthalten. Die DCQ **144** besitzt acht Abschluss-Puffer, wobei jeder davon bis zu acht Cache-Linien bzw. Zeilen an Abschluss-Informationen für eine einzelne, verzögerte Anforderung halten kann. Zusätzlich zu den Abschluss-Informationen enthält jeder Abschluss-Puffer auch eine Kopie der verzögerten Anforderung, die die Informationen erzeugte. Für verzögerte Lese-Transaktionen kann eine Daten-„Folge“ zwischen dem primären Bus **24** und dem sekundären Bus **32** eingerichtet werden, wenn die anfordernde Vorrichtung damit beginnt, die angeforderten Daten aufzusuchen, bevor die Target-Vorrichtung damit stoppt, sie zu der DCQ **144** zu liefern. Unter bestimmten Umständen wird die DCQ **144** automatisch zusätzliche Daten erneut aufsuchen, oder „vorababrufen“ („prefetch“), wenn eine anfordernde Vorrichtung alle die angeforderten Daten von dem entsprechenden Puffer in der DCQ **144** aufsucht. Sowohl ein Streaming als auch ein automatisches Vorababrufen (prefetching) werden in weiterem Detail nachfolgend diskutiert.

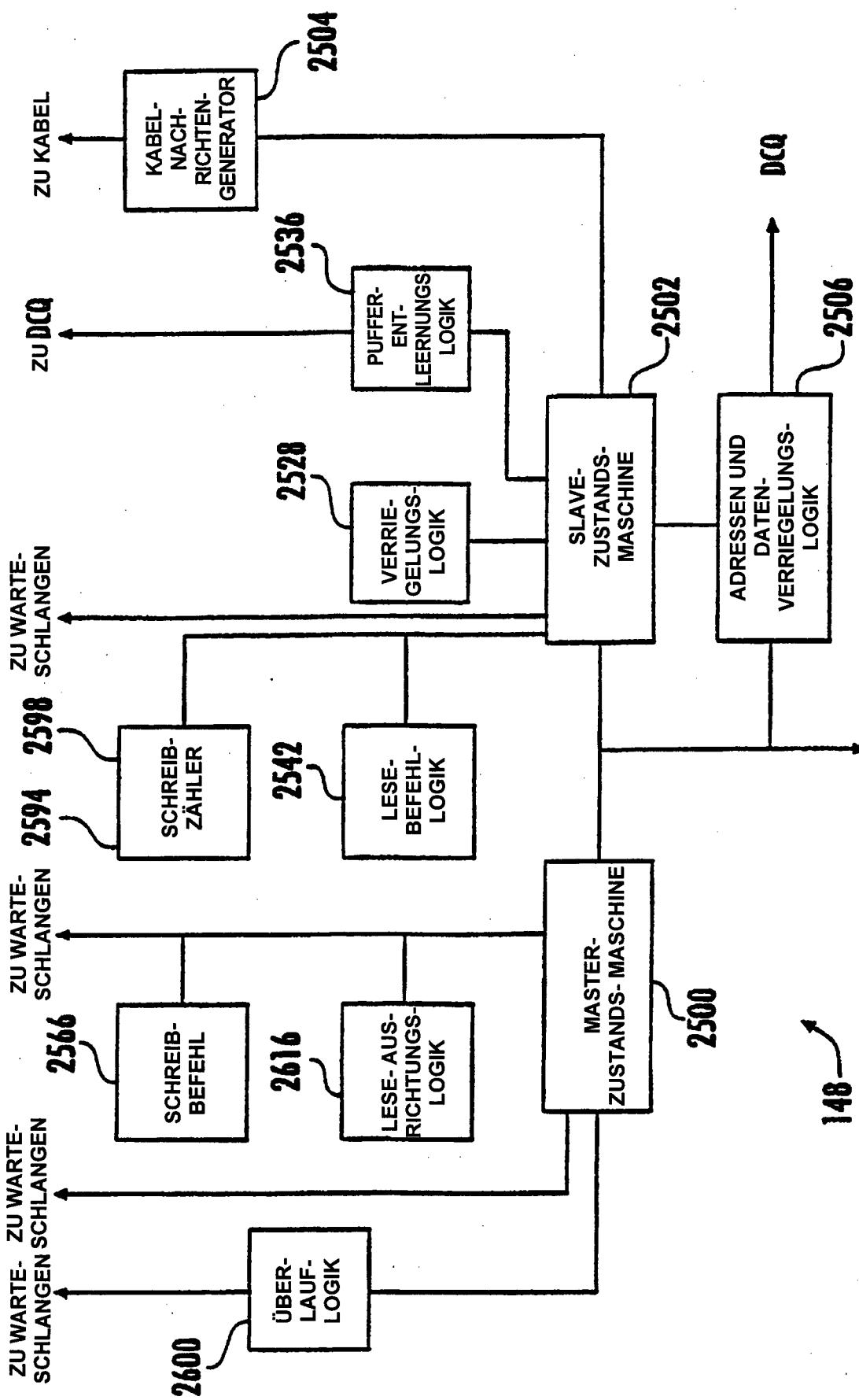

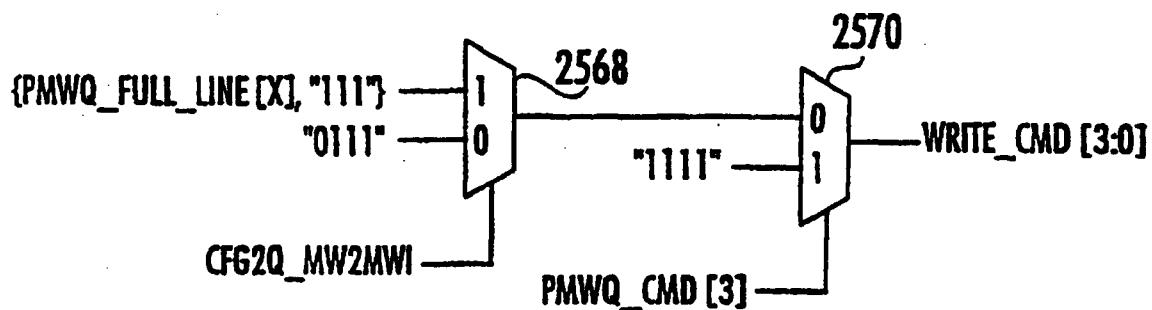

[0121] Eine Warteschlangen-zu-PCI-Schnittstelle (Queue-to-PCI Interface – QPIF) **148** verwaltet Transaktionen, die von den Warteschlangen **140**, **142** und **144** zu dem PCI-Bus **32** und von dem PCI-Bus **32** zu der DCQ **144** und zu dem eingangsseitigen Chip über die Kabel-Schnittstelle **130** fließen. Die QPIF **148** tritt in einen „Master“ Mode ein, um gepostete Speicher-Schreib- und verzögerte Anforderungs-Transaktionen von der PMWQ **140** und der DRQ **142** auf dem sekundären Bus laufen zu lassen. Für sowohl gepostete Speicher-Schreib- als auch verzögerte Lese-Transaktionen kann die QPIF **148** eine Transaktion „unterstützen“, die weniger als eine Cache-Zeile an Daten einsetzt (d. h. eine Speicher-Schreib-(Memory Write – MW) oder eine Speicher-Lese-(Memory Read – MR) Transaktion), gegenüber einer solchen, die eine oder mehrere Cache-Zei-

len (d. h. eine Speicher-Schreib- und Ungültigkeits-(MWI)-Transaktion oder eine Speicher-Lese-Zeile (MRL) oder eine Speicher-Lese-Mehrzahl-(MRM) Transaktion erfordert, falls bestimmte Zustände erfüllt werden. Die QPIF **148** kann auch eine Lese-Transaktion, die eine Einzel-Cache-Zeile von Daten einsetzt (d. h. eine MRL Transaktion), in eine von mehreren Cache-Zeilen an Daten (d. h. eine MRM-Transaktion) umwandeln. Die QPIF **148** kann auch eine MRL- oder MRM-Transaktion „korrigieren“, die in der Mitte einer Cache-Zeile beginnt, und zwar durch Lesen der gesamten Cache-Zeile und dann aussondern des nicht angeforderten Teils der Daten. Eine Transaktion-Unterstützung und eine Lese-Korrektur, wobei beide davon in weiterem Detail nachfolgend beschrieben sind, verbessern eine Systemeffektivität durch Verringern der Zeit, die dazu erforderlich ist, Daten von einer Speichervorrichtung aufzusuchen.

[0122] Die QPIF **148** gibt einen „Slave“ Code ein, um Daten von der DCQ **144** zu einer anfordernden PCI-Vorrichtung zu liefern oder Transaktionen von dem PCI-Bus **32** zu der DCQ **144** und zu dem eingangsseitigen Chip über das Kabel zu schicken. Wenn die QPIF **148** eine gepostete Schreib-Transaktion von dem Bus **32** empfängt, führt sie die Transaktion weiter zu dem eingangsseitigen Chip, falls eine entsprechende Eine einer Gruppe von Transaktionszählern **159** anzeigt, dass die PMWQ in dem anderen Brücken-Chip nicht voll ist, wie dies nachfolgend diskutiert ist. Wenn die QPIF **148** eine verzögerte Anforderung aufnimmt, führt sie zuerst die Anforderung zu der DCQ **144** weiter, um zu bestimmen, ob die Transaktion bereits in der DCQ platziert worden ist, und, falls dies der Fall ist, ob die entsprechenden, verzögerten Abschluss-Informationen zu der DCQ **144** zurückgeführt worden sind. Falls die verzögerten Abschluss-Informationen in der DCQ vorhanden sind, werden die Informationen zu der anfordernden Vorrichtung geführt und die Transaktion wird beendet. Falls die Anforderung bereits in eine Warteschlange gestellt ist, allerdings die Verzögerungs-Abschirmungs-Informationen nicht zurückgeführt worden sind, wird die anfordernde Vorrichtung erneut versucht und die Transaktion wird auf dem PCI-Bus **32** beendet. Falls die Transaktion noch nicht in die Warteschlange gestellt ist, reserviert die DCQ **144** einen Abschluss-Puffer für die Transaktion und die QPIF **148** führt die Transaktion zu dem eingangsseitigen Chip über die Kabel-Schnittstelle **130** weiter, solange wie der entsprechende Transaktionszähler **149** anzeigt, dass der andere Brückenchip nicht voll ist.

[0123] Falls die DCQ **144** bestimmt, dass einer deren Pufferdaten enthält, vorgesehen für eine anfordernde Vorrichtung, allerdings unterschiedlich als die Daten, die in der momentanen Transaktion angefordert sind, kann der Puffer geleert werden, um zu verhindern, dass der anfordernde Master überholte Daten empfängt. Der Puffer wird dann geleert, wenn er Prefetch-Daten enthält, (d. h. Daten, die in dem Puffer verbleiben, nachdem die anfordernde Vorrichtung einige der Daten aufgesucht hat, oder Daten, die nicht spezifisch durch die Vorrichtung angefordert wurden), allerdings wird er nicht gelöscht, wenn er Abschluss-Daten enthält (d.h. spezifisch angefordert durch eine Vorrichtung, die bis jetzt noch nicht zurückgekehrt ist, um sie zu empfangen). Falls der Puffer-Abschluss-Daten enthält und die anfordernde Vorrichtung eine Anforderung ausgegeben hat, die nicht den Puffer „trifft“ („hit“), versieht die DCQ **144** die Vorrichtung mit einem Zeichen als eine „Multi-Threaded“ Vorrichtung (d. h. eine solche, die in der Lage ist, mehr als eine Transaktion zu einem Zeitpunkt beizubehalten), und ordnet einen anderen Abschluss-Puffer der neuen Anforderung zu. Die Puffer-Löschen- und Mehrfach-Puffer-Zuordnungs-Schemen werden in weiterem Detail nachfolgend beschrieben.

[0124] Ein Master-Zyklus-Arbitrierer (MCA) **150** in dem Warteschlangen-Block **127** hält Standard-Reihenfolgen-Einschränkungen zwischen geposteten Speicher-Schreib-, verzögerten Anforderungs- und verzögerten Abschluss-Transaktionen bei, wie dies in der PCI Bridge Architecture Specification, Version **2.1**, angegeben ist. Diese Einschränkungen erfordern, dass Bus-Zyklen eine starke Schreib-Reihenfolge beibehalten und dass Entblockungen (Deadlocks) nicht auftreten. Deshalb bestimmt der MCA **150** die Reihenfolge, in der gepostete Speicher-Schreib-Transaktionen in der PMWQ **140** und verzögerte Anforderungs-Transaktionen in der DRQ **142** auf dem PCI-Bus **32** laufen. Der MCA **150** steuert auch die Verfügbarkeit von verzögerten Abschluss-Informationen, gespeichert in der DCQ **144**. Um eine Übereinstimmung mit diesen Regeln sicherzustellen, gibt der ausgangsseitige MCA **150** jedem geposteten Speicher-Schreib-Zyklus eine Gelegenheit, früher ausgegebene, verzögerte Anforderungs-Zyklen im Bypass zu passieren, während sowohl der eingangsseitige als auch der ausgangsseitige MCA **150** nicht zulassen, dass verzögerte Anforderungs- und verzögerte Abschluss-Zyklen früher ausgegebene, gepostete Speicher-Schreib-Zyklen im Bypass passieren. Eine Transaktions-Reihenfolge durch den MCA **150** wird in weiterem Detail nachfolgend beschrieben.

[0125] Die Transaktions-Zähler **159** in dem ausgangsseitigem Warteschlangen-Block **127** behalten eine Zählung der Zahl von Transaktionen, in dem eingangsseitigen Brücken-Chip in die Warteschlange gestellt, bei. Ein Zähler **160** für ein gepostetes Speicher-Schreiben (Posted Memory Write – PMW) zeigt die Zahl von PMW-Transaktionen, gehalten in der eingangsseitigen, geposteten Speicher-Schreib-Warteschlange, an. Der PMW-Zähler **160** wird zu jedem Zeitpunkt erhöht, zu dem eine PMW-Transaktion zu der Kabel-Schnittstelle **130** geschickt wird. Der Zähler **160** wird zu jedem Zeitpunkt erniedrigt, zu dem die QPIF **148** ein Signal von dem Kabel-Decodieren **146** aufnimmt, anzeigen, dass ein PMW-Zyklus auf dem eingangsseitigen PCI-Bus **24** abgeschlossen worden ist. Wenn die eingangsseitige PMWQ die maximale Zahl (vier) der PMW Transaktionen in die Warteschlange gestellt hat, gibt der PMW-Zähler **160** ein PMW-Voll-Signal (tc\_pmw\_full) aus, und teilt der QPIF **148** mit, zusätzliche PMW-Zyklen von dem PCI-Bus **32** erneut zu versuchen. In ähnlicher Weise

zählt ein Zähler **161** für eine verzögerte Anforderung (Delayed Request – DR) die Zahl von DR-Transaktionen, gehalten in der eingangsseitigen, verzögerten Anforderungs-Warteschlange. Wenn die DRQ die maximale Zahl (drei) von DR-Transaktionen hält, stellt der DR-Zähler **161** ein DR-Voll-Signal (tc\_dr\_full) auf, das anzeigt, dass die QPIF **148** alle darauffolgenden DR-Transaktionen von dem PCI-Bus **32** erneut versuchen muss. Ein Zähler **162** für einen verzögerten Abschluss (Delayed Completion – DC), zählt die Zahl von verzögerten Abschlüssen, die indem eingangsseitigen Master-Zyklus-Arbitrierer in die Warteschlange gestellt sind. Wenn der MCA die maximale Zahl (vier) von verzögerten Abschlüssen hält, stellt der DC-Zähler **162** ein DC-Voll-Signal (tc\_dc\_full) auf, das verhindert, dass die ausgangsseitige QPIF **148** verzögerte Anforderungs-Transaktionen auf dem sekundären PCI-Bus **32** laufen lässt. Sobald der Voll-Zustand verschwindet, können Informationen über den verzögerten Abschluss zu der ausgangsseitigen DCQ geschickt werden.

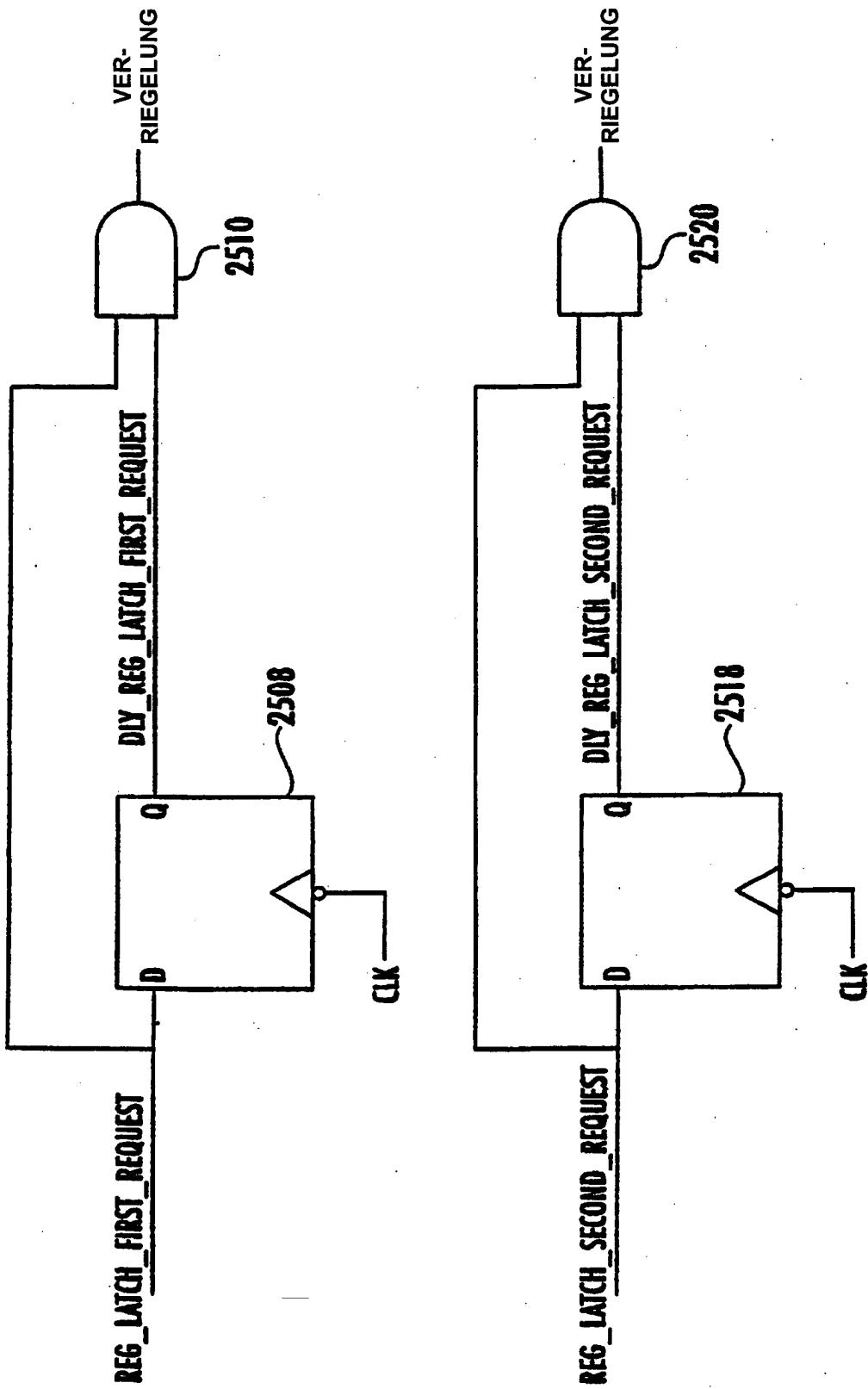

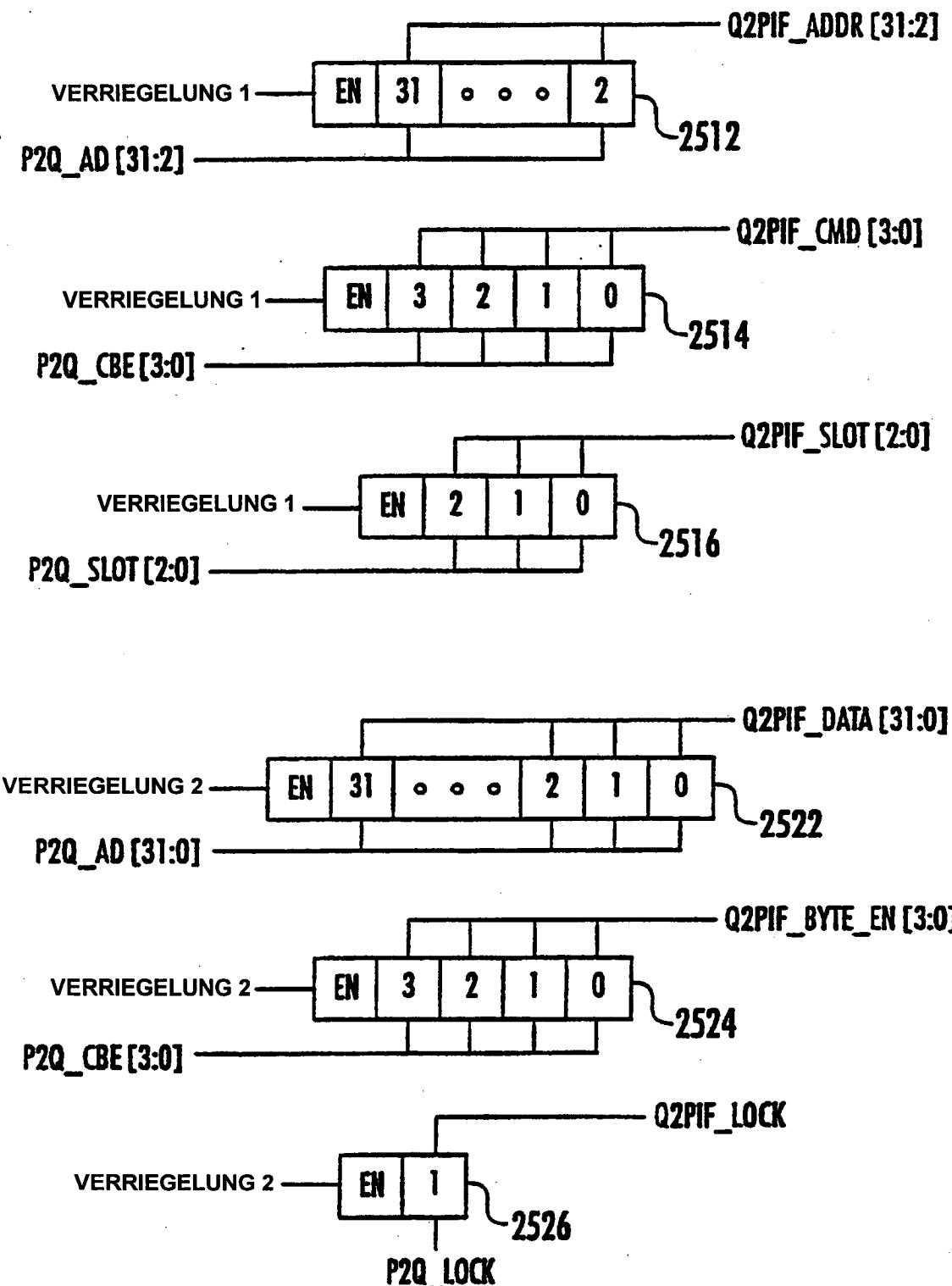

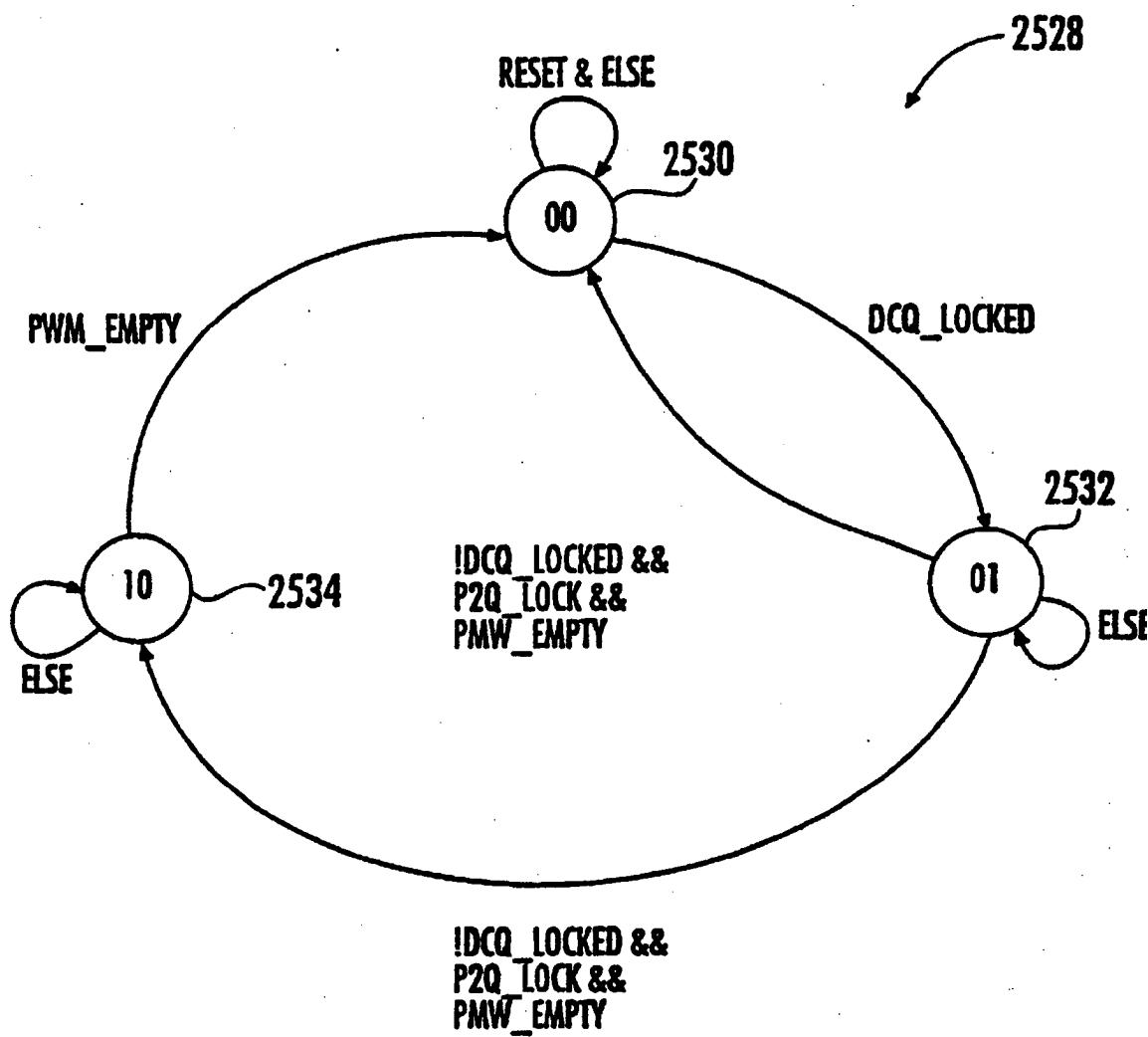

[0126] Ein PCI-Schnittstellen-Block **152** ist zwischen dem PCI-Bus **32** und dem Warteschlangen-Block **127** vorhanden. Die PCI-Schnittstelle **152** umfasst einen Master-Block **123** und einen Slave-(Target)-Block **121**. Der Slave-Block **121** ermöglicht PCI-Vorrichtungen auf dem Bus **32**, auf interne Register von Brücken-Chips (z. B. Target-Speicher-Bereichs-Register **155** und Konfigurations-Register) zuzugreifen, um Abschluss-Informationen zu beanspruchen, die in der DCQ **144** gespeichert sind, und um auch Transaktionen zu initiieren, die durch die QPIF **148** und die Kabel-Schnittstelle **130** zu dem primären Bus geführt werden. Der Slave-Block **121** steuert die Verfügbarkeit des PCI-Busses **32** zu den PCI-Vorrichtungen auf dem Bus **32** durch Erkennen, wann jede Vorrichtung auf deren REQ#-Zeile zugreift und die REQ#-Signale zu den PCI-Arbitrierer **124** weiterführt. Wenn der PCI-Arbitrierer **124** eine anfordernde Vorrichtung auswählt, um eine Steuerung des Busses zu empfangen, erteilt der Slave-Block **121** den Bus zu der Vorrichtung durch Aufstellen der GNT# Leitung der Vorrichtung. Sobald der Bus **32** zu der anfordernden Vorrichtung erteilt ist und die Vorrichtung deren FRAME# Signal aufstellt, das den Beginn einer Transaktion anzeigt, verriegelt der Slave-Block **121** die Transaktions-Informationen (z. B. Adresse, Befehl, Daten, Byte-Freigaben, Parität, usw.) in ein Slave-Verriegelungsregister **156**. Der Warteschlangen-Block **127** ist dann in der Lage, die Transaktions-Informationen von dem verriegelnden Register **156** aufzusuchen und sie zu der DCQ **144** und/oder der Kabel-Schnittstelle **130** zu liefern.

[0127] Transaktionen, unterstützt durch den PCI-Slave-Block **121**, sind in der folgenden Tabelle dargestellt.

| Transaktions-Typ                    | Primäre Schnittstelle | Sekundäre Schnittstelle |

|-------------------------------------|-----------------------|-------------------------|

| Unterbrechungs-Bestätigung          | nicht unterstützt     | nicht unterstützt       |

| spezieller Zyklus                   | verzögert             | verzögert               |

| I/O-Lesen                           | verzögert             | verzögert               |

| I/O-Schreiben                       | verzögert             | verzögert               |

| Speicher-Lesen                      | verzögert             | verzögert               |

| Speicher-Schreiben                  | gepostet              | gepostet                |

| Konfigurations-Lesen (Typ 0)        | sofort                | nicht unterstützt       |

| Konfigurations-Schreiben (Typ 0)    | sofort                | nicht unterstützt       |

| Konfigurations-Lesen (Typ 1)        | verzögert             | nicht unterstützt       |

| Konfigurations-Schreiben (Typ 1)    | verzögert             | nicht unterstützt       |

| Speicher-Lese-Multiple              | verzögert (streaming) | verzögert (streaming)   |

| Dual-Adressen-Zyklus                | nicht unterstützt     | sofort                  |

| Speicher-Lese-Zeile                 | verzögert             | verzögert               |

| Speicher-Schreiben und Ungültigkeit | gepostet              | gepostet                |

#### PCI-Schnittstellen-Slave-Transaktionen

[0128] Der Master-Block **123** der PCI-Schnittstelle **152** lässt nur einen Zyklus laufen, initiiert durch den War-

teschlangen-Block **127** (d. h. Transaktionen, gehalten in der PMWQ **140** und der DRQ **142**). Der Warteschlangen-Block **127** fordert von dem PCI-Bus durch Senden eines Anforderungs-Signals (q2p\_req) zu dem PCI-Master **123** an, der dann bestimmt, ob ein entsprechendes Anforderungs-Signal (b1req\_) zu dem PCI-Arbitrierer **124** aufgestellt ist. Der Master-Block **123** stellt b1req\_ auf, falls der Warteschlangen-Block **127** nicht einen verriegelten Zyklus läuft und der PCI-Bus **32** nicht durch eine PCI-Vorrichtung verriegelt ist. Wenn der PCI-Arbitrierer **124** den Warteschlangen-Block **127** auswählt, schickt der Master-Block **123** ein Bestätigungs-Signal (p2q\_ack), um den Warteschlangen-Block **127** wissen zu lassen, das er eine Kontrolle des Busse **32** inne hat. Falls der PCI-Arbitrierer **124** keine offenen Anforderungen von anderen Vorrichtungen auf dem Bus **32** vorliegen hat, schickt der Master-Block **123** automatisch das p2q\_ack Erteilungs-Signal zu dem Warteschlangen-Block **127**, sogar dann, wenn der Warteschlangen-Block **127** nicht das q2p\_req Signal aufgestellt hat. Sobald wie der Warteschlangen-Block **127** eine Arbitrierung erhält (d. h. der Arbitrierer **124** stellt das b1gnt\_ Signal auf) und sein q2p\_frame Signal aufstellt, um den Beginn einer Transaktion anzugeben, verriegelt der PCI-Master **123** Informationen über abgehende Transaktionen (d. h. Adresse, Befehl, Daten, Byte-Freigaben, Parität, usw.) in ein Master-Verriegelungs-Register **158** in der PCI-Schnittstelle **152**. Die Transaktions-Informationen werden dann verwendet, um die Transaktion auf dem PCI-Bus **32** abzuschließen. [0129] Transaktionen, unterstützt durch den Master-Block **123**, sind in der folgenden Tabelle dargestellt.

| Transaktions-Typ                    | Primäre Schnittstelle | Sekundäre Schnittstelle |

|-------------------------------------|-----------------------|-------------------------|

| Unterbrechungs-Bestätigung          | nicht unterstützt     | nicht unterstützt       |

| spezieller Zyklus                   | unterstützt           | unterstützt             |

| I/O-Lesen                           | unterstützt           | unterstützt             |

| I/O-Schreiben                       | unterstützt           | unterstützt             |

| Speicher-Lesen                      | unterstützt           | unterstützt             |

| Speicher-Schreiben                  | unterstützt           | unterstützt             |

| Konfigurations-Lesen                | nicht unterstützt     | unterstützt             |

| Konfigurations-Schreiben            | nicht unterstützt     | unterstützt             |

| Speicher-Lese-Multiple              | unterstützt           | unterstützt             |

| Dual-Adressen-Zyklus                | unterstützt           | nicht unterstützt       |

| Speicher-Lese-Zeile                 | unterstützt           | unterstützt             |

| Speicher-Schreiben und Ungültigkeit | gepostet              | gepostet                |

#### PCI-Schnittstellen-Master-Transaktionen

[0130] Allgemein arbeitet der Master-Block **123** als ein Standard-PCI-Master. Allerdings wird, im Gegensatz zu Standard-PCI-Brücken, der Master-Block nicht eine MRL, MRM oder MWI Transaktion beenden, bis eine Cache-Zeilen-Grenze erreicht ist, gerade nachdem der Master-Latenz-Zeitgeber (Master Latency Timer – MLT) abläuft. Auch stellt der Master-Block **123** nicht „Initiator Ready“ (IRDY) Warte-Zustände auf. Der Master-Block **123** läuft einen verriegelten Zyklus auf dem PCI-Bus **32**, falls der Warteschlangen-Block **127** sein „Verriegelungs“ Signal (q2p\_lock) aufstellt und seine Verriegelung auf dem Bus **32** freigibt, wenn der Warteschlangen-Block **127** sein „Entriegelungs“ Signal (q2p\_unlock) aufstellt.

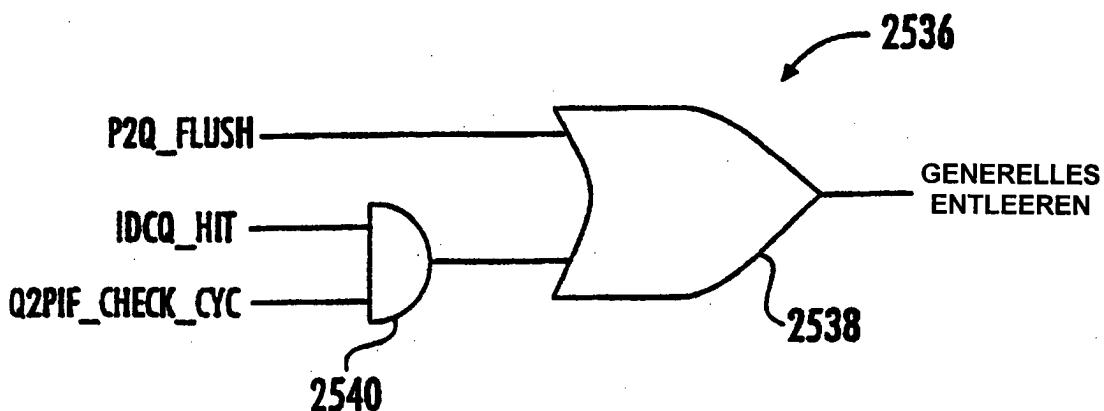

[0131] Wie auch **Fig. 57** zeigt, enthält die PCI-Schnittstelle **152** eine Puffer-Entleerungs-Logik **154**, die bestimmt, wann einer oder alle der DCQ Abschluss-Puffer durch den Warteschlangen-Block **127** geleert werden sollten. Die PCI-Slave **121** erzeugt zwei Signale, die durch den Warteschlangen-Block **127** verwendet werden, um die Abschluss-Puffer zu leeren: ein Flush-Signal (p2q\_flush), das angebt, wann ein Puffer geleert werden sollte, und ein Schlitz- bzw. Steckplatzauswahl-Signal (p2q\_slot[2:0]), das angebt, welche PCI-Vorrichtung (d. h. welcher Einstechplatz an dem PCI-Bus) hinsichtlich seiner Daten geleert werden sollte. Die folgende Tabelle stellt die Beziehung zwischen p2q\_slot[2:0], und der PCI-Schlitz-Zahl dar.

| p2q_slot[2:0] | Einsteckplatz-Zahl |

|---------------|--------------------|

| 000           | alle               |

| 001           | 1                  |

| 010           | 2                  |

| 011           | 3                  |

| 100           | 4                  |

| 101           | 5                  |

| 110           | 6                  |

| 111           | 7                  |

Erzeugung von p2q\_slot[2:0]

[0132] Wenn p2q\_flush aufgestellt ist, wird der Warteschlangen-Block **127** entweder alle Abschluss-Puffer in der DCQ **144** entleeren, falls p2q\_slot[2:0] gleich zu „000“ ist, oder den entsprechenden Einen der acht Abschluss-Puffer, falls p2q\_slot[2:0] irgendeinen anderen Wert hat. Der Warteschlangen-Block 127 behält ein Protokoll davon bei, welche Abschluss-Puffer, falls welche vorhanden sind, jedem PCI-Steckplatz zu irgendeinem gegebenen Zeitpunkt entsprechen.

[0133] Das p2q\_flush Signal wird an der ansteigenden Flanke des ersten PCI-Takt-(CLK)-Zyklus aufgestellt, nachdem ein config Schreib-(WR-CFG)-Zyklus auftritt, oder nachdem ein I/O-Schreib-(iowr)-Zyklus auftritt, oder ein Speicher-Schreib-(memwr)-Zyklus ein ausgangsseitiges Target (hit\_tmem) während eines Befehl-Prüf-Zustands (cmd\_chk\_st) trifft. Gates **2014**, **2016**, **2018** und **2020** und ein Flip-Flop **2022** sind so angeordnet, um p2q\_flush auf diese Art und Weise zu erzeugen.

[0134] In dem eingangsseitigen Brücken-Chip (d.h. wenn das Upstream\_chip\_i Signal aufgestellt ist) besitzt p2q\_slot[2:0] immer einen Wert von „001“, da die CPU der einzige Master auf dem primären PCI-Bus ist. In dem ausgangsseitigen Chip hängt der Wert von p2q\_slot davon ab, ob der Zyklus, der zu einem Flush-Zustand (Flush Condition) führt, ein Zyklus von dem sekundären Bus **32** zu dem Warteschlangen-Block **127** ist (d. h. falls p2q\_qcyc aufgestellt ist). Falls das p2q\_qcyc Signal aufgestellt ist, nimmt p2q\_slot[2:0] den Wert des reg\_slot[2:0] Signals an, erzeugt durch die PCI-Slave **121**. Das reg\_slot[2:0] Signal zeigt an, welcher der sieben Vorrichtungen auf dem sekundären PCI-Bus **32** eine Kontrolle des Busses **32** erteilt worden ist. Die PCI-Slave **121** erzeugt das reg\_slot[2:0] Signal durch Verriegeln des Werts der GNT# Leitung für jeden der sieben Schlitze bzw. Steckplätze auf dem Bus **32**, um ein verriegeltes Erteilungs-Signal mit sieben Bits (latched\_gnt[7:1]; die achte Erteilungs-Leitung, die zu dem Warteschlangen-Block gehört, wird ignoriert) zu bilden, und durch Codieren von latched\_gnt[7:1] entsprechend einer Durchsichtstabelle **2006**, die nachfolgend angegeben ist.

[0135]

| latched_gnt[7:1] | reg_slot[2:0] |

|------------------|---------------|

| 1111111          | 000           |

| 1111110          | 001           |

| 1111101          | 010           |

| 1111011          | 011           |

| 1110111          | 100           |

| 1101111          | 101           |

| 1011111          | 110           |

| 0111111          | 111           |

Erzeugung von req\_slot[2:0]

[0136] Falls der Zyklus, der zu dem Entleeren führt, nicht ein Sekundär-PCI-zu-Warteschlangen-Block-Zyklus ist, muss er eine I/O-Lesung oder eine config-Lesung zu dem Sollspeicherbereich von einem der Steckschlüsse an dem sekundären Bus **32** sein. Wenn der Zyklus eine I/O-Lesung oder eine config-Lesung ist (d. h. !iowr AND !wr\_cfg), nimmt p2q\_slot[2:0] den Wert des PCI-Schlitzes an, dessen Speicherbereich getroffen worden ist (mrange\_slot[2:0]). Ansonsten ist der Zyklus ein I/O-Schreiben oder ein config-Schreiben und p2q\_slot[2:0]

wird gleich zu „000“, so dass alle Abschluss-Puffer geleert werden. Gates **2008** und **2010** und Multiplexer **2002** und **2004** sind so angeordnet, um p2q flush[2:0] auf diese Art und Weise zu erzeugen.

#### KABEL-DECODIERER

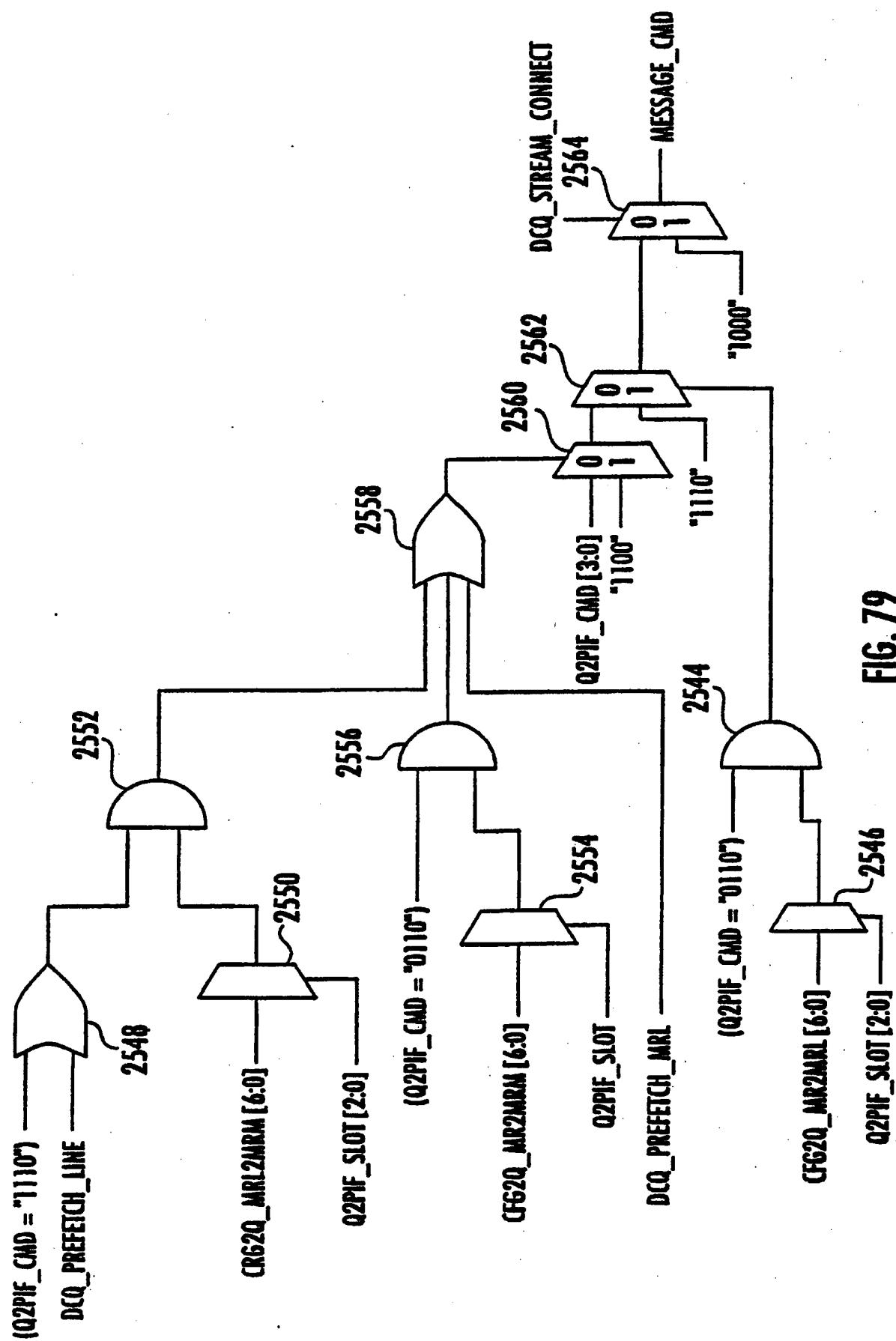

[0137] Wie **Fig. 58** zeigt, empfängt der Kabel-Decodierer **146** Transaktionen von der Kabel-Schnittstelle und wählt die geeignete Warteschlange so aus, um jede Transaktion zu empfangen. Wenn sich der Kabeldecodierer in der Daten-Phase befindet (d.h. wenn data\_phase oder next\_data\_phase vorliegt, wird ein asynchrones Signal, das den Wert von data\_phase einstellt, an dem nächsten CLK-Zyklus aufgestellt ist), sieht der Kabel-Decodierer **146** an dem Befehl-Code (cd\_cmd[3:0]), geschickt über das Kabel, nach, um zu bestimmen, welche Warteschlange die Transaktion empfangen sollte. Wie in der Tabelle nachfolgend dargestellt ist, ist, wenn cd\_cmd[3:0] einen Wert von „1001“ hat, die Transaktion ein verzögerter Abschluss, so dass der Kabel-Decodierer ein cd\_dcq\_select Signal aufstellt, das der dcq mitteilt, die Transaktion zu beanspruchen. Wenn die drei LSB des Befehl-Code-Signals (cd\_cmd[2:0]) „111“ sind, ist die Transaktion ein gepostetes Speicher-Schreiben, so dass der Kabel-Decodierer ein cd\_pmwq\_select Signal erzeugt, um die pmwq über die ankommende Transaktion zu warnen. Wenn die Transaktion weder ein gepostetes Speicher-Schreiben noch ein verzögerter Abschluss ist und der Befehl-Code nicht ein Streaming-Signal darstellt, stellt der Kabel-Decodierer ein cd\_drg\_select Signal auf, das der DRQ mitteilt, die Transaktion zu beanspruchen. Gates **2024**, **2026**, **2028** und **2030** sind so konfiguriert, um die cd\_dcq\_select, cd\_pmwq\_select, und cd\_drg\_select Signale auf diese Art und Weise zu erzeugen.

[0138] Die nachfolgende Tabelle stellt die Befehl-Code mit vier Bits, zugeordnet zu jedem Typ einer Transaktion, dar.

[0139]

| Transaktions-Typ         | Befehl-Code |

|--------------------------|-------------|

| I/O-Lesen                | 0010        |

| I/O-Schreiben            | 0011        |

| Config-Lesen             | 1010        |

| Config-Schreiben         | 1011        |

| Speicher-Lesen           | 0110        |

| MRL                      | 1110        |

| MRM                      | 1100        |

| Speicher-Schreiben       | 0111        |

| MWI                      | 1111        |

| verzögerter Abschluss    | 1001        |

| Datenfolge eingereichtet | 1000        |

#### Transaktions-Befehl-Code

[0140] Wenn der ausgangsseitige Brücken-Chip eine Datenfolge zwischen dem primären Bus und einem sekundären Bus-Master eingerichtet hat, empfängt der eingangsseitige Kabel-Decodierer einen Befehl-Code von „1000“. Dieser Code stellt ein Streaming-Signal dar, erzeugt durch den ausgangsseitigen Chip, um den eingangsseitigen Chip zu informieren, dass eine Datenfolge eingerichtet worden ist. Wenn der Kabeldecodierer diesen Befehl-Code empfängt, stellt er ein cd\_stream Signal auf, das der QPIF in der eingangsseitigen Vorrichtung mitteilt, die Transaktion fortzuführen. Der Kabel-Decodierer erzeugt auch ein cd\_stream\_next\_data Signal, das den eingangsseitigen Chip instruiert, einen anderen Teil von Daten zu dem sekundären Bus zu liefern. Das cd\_stream-next\_data Signal wird dann aufgestellt, wenn ein cd\_stream Signal aufgestellt ist, wobei sich die Transaktion in der Daten-Phase befindet (d. h. data\_phase ist aufgestellt), und ein next\_data Signal ist von dem eingangsseitigen Chip über die Kabel-Schnittstelle empfangen worden (das next\_data Signal erscheint auf einer der Leitungen des c2q\_buff[3:0] Signals, das, wenn keine Datenfolge auftritt, dem Warteschlangen-Block mitteilt, welcher ausgangsseitige DCQ-Puffer der momentanen Transaktion zugeordnet ist). Das cd\_stream\_next\_data Signal wird zurückgenommen, wenn entweder das cd\_stream Signal zurückgenommen ist oder wenn eine neue Anforderung von der Kabel-Schnittstelle empfangen ist (d. h. c2q\_new\_req ist aufgestellt). Gates **2032** und **2034** sind so konfiguriert, um die cd\_stream und die cd\_stream\_next\_data Signale auf diese Art und Weise zu erzeugen.

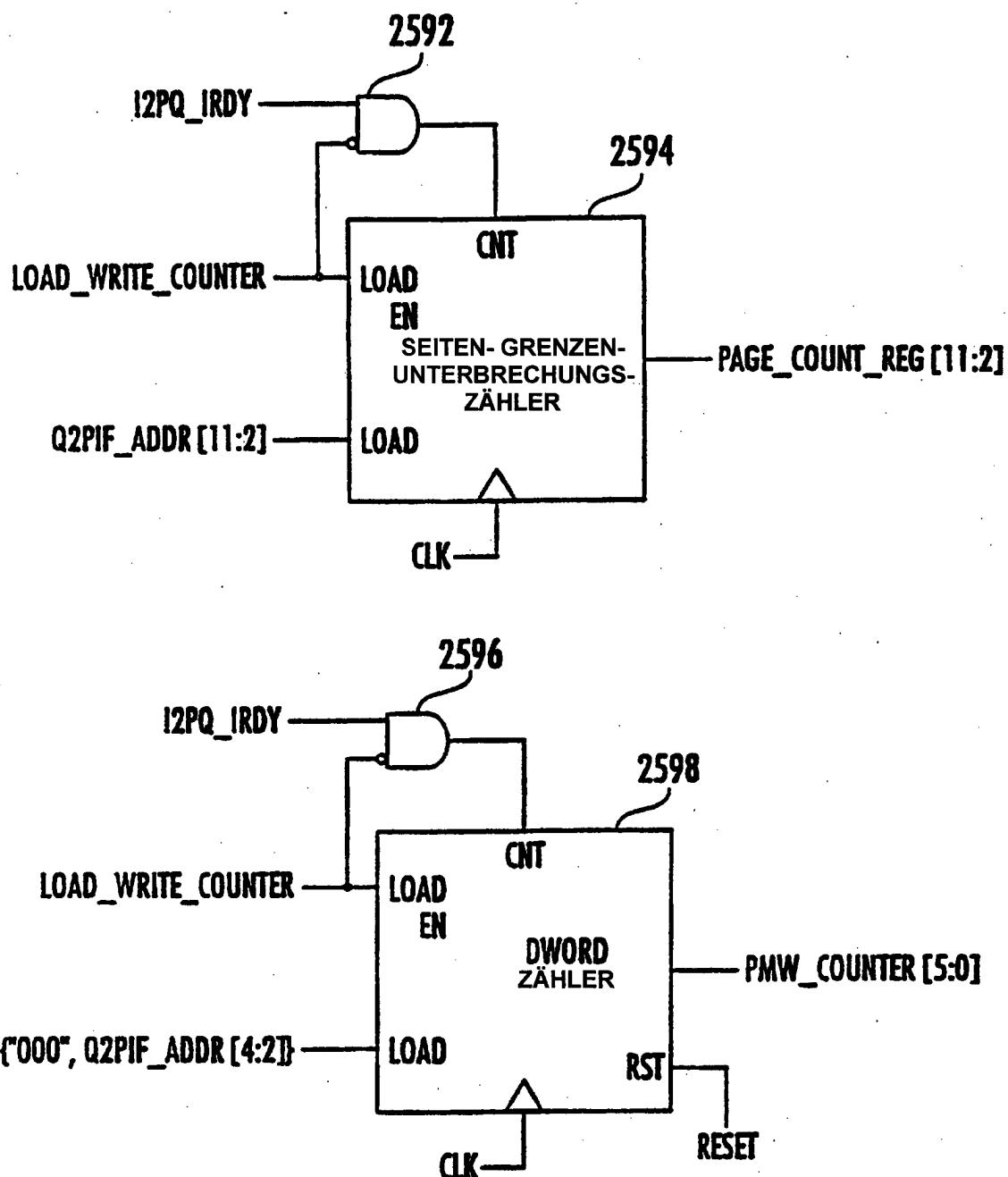

#### GESPEICHERTE-SCHREIB-WARTESCHLANGE

[0141] Wie **Fig. 59** zeigt, ist die gepostete Speicher-Schreib-Warteschlange (PMWQ) **140** ein Speicherelement, das alle die Befehl-Informationen enthält, die benötigt werden, um gepostete Schreib-Transaktionen auf

dem Target-Bus auszuführen. Die PMWQ umfasst einen Zeichen- bzw. Tag-Speicher-Bereich **2036**, der Informationen hält, die jede Transaktion identifizieren, einen Daten-RAM **2038**, der die Schreib-Daten hält, die jeder Transaktion in der PMWQ zugeordnet sind, und verschiedene Steuerblöcke, um den Fluß von Transaktionen in die PMWQ hinein und von dieser heraus zu verwalten. Für jede Transaktion in der PMWQ behält der Zeichen-Speicher **2036** Informationen bei, wie beispielsweise über die Adresse, zu der geschrieben werden soll, den PCI-Befehl-Code (MW oder MWI), ein Adressen-Paritäts-Bit, und „einen verriegelten Zyklus“ und einen „Dual-Adressen-Zyklus“ Indikations-Bits, wie in der folgenden Tabelle dargestellt ist. Der Zeichenspeicher **2036** speichert auch einen Hinweiszeiger zu der Daten-RAM-Stelle der Daten entsprechend zu jeder der Transaktionen in der PMWQ.

| Feld           | Bits           | Anmerkungen                                                                                                                                                            |

|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Adresse        | 64             | eingangsseitige Transaktionen unterstützende Dual-Adressen-Zyklen                                                                                                      |

| PCI Befehl     | 1              | Speicher-Schreiben 0111<br>Speicher-Schreiben und Ungültigkeit 1111<br>(nur notwendig, um cbe[3] zu speichern)                                                         |

| Byte-Freigaben | 0              | Speichere BEs an jedem gültigen Übertragungs-Takt in dem Daten-RAM                                                                                                     |

| Parität        | 1/Adresse<br>0 | muss PAR mit jeder Übertragung zusammen mit 32-Bit addr/Daten speichern.<br>muss Daten-Paritäts-Bits bei jeder gültigen Daten-Übertragung in einem Daten-RAM speichern |

| Daten          | 0              | gespeichert in Daten-RAM bis zu 8 Cache-Zeilen                                                                                                                         |

| Verriegelung   | 1              |                                                                                                                                                                        |

| DAC-Indikation | 1              | zeigt an, ob Adresse 32 oder 64 Bits ist                                                                                                                               |

#### Inhalte von PMWQ

[0142] Da die PCI Spec. **2.1** fordert, dass gepostete Speicher-Schreib-Transaktionen in der Reihenfolge ausgeführt werden, in der sie empfangen werden, ist der Zeichen- bzw. Tag-Speicher **2036** eine zirkuläre FIFO-Vorrichtung. Die PMWQ, und deshalb der Zeichen-Speicher **2036**, können bis zu vier gepostete Speicher-Schreib-Transaktionen simultan handhaben.

[0143] Der Daten-RAM **2038**, umfasst vier Daten-Puffer **2042**, **2044**, **2046** und **2048**, einen für jede Transaktion in der PMWQ. Jeder Puffer kann bis zu acht Cache-Zeilen, oder 256 Bytes, an Daten (acht Worte pro Cache-Zeile) speichern. Für jede Cache-Zeile in einem Puffer speichert der Puffer acht Daten-Paritäts-Bits **2040** (eins pro dword) und zweieinunddreißig Freigabe-Bits **2050** (eines pro Byte).

[0144] Ein Kabel-Schnittstellen-Block **2060** empfängt jede Transaktion und die entsprechenden Daten von dem Kabel-Codierer und platziert die Transaktion in dem Zeichen-Speicher **2036**. Ein Warteschlangen-Schnittstellen-Block **2053** empfängt die Daten von dem Kabel-Schnittstellen-Block **2060** und platziert sie in der geeigneten Stelle in dem Daten-RAM **2038**. Die Warteschlangen-Schnittstelle **2053** empfängt auch Daten von dem Daten-RAM **2038** und liefert sie zu der QPIF, wenn die QPIF die entsprechende Transaktion auf dem PCI-Bus laufen lässt. Ein Eingangs-Hinweis-Zeiger Logik-Block **2054** erzeugt vier Eingangs-Hinweis-Zeiger, einen für jeden Puffer, die der Warteschlangen-Schnittstelle **2053** mitteilen, wo das nächste Wort von Daten zu platzieren ist. Ein Gültigkeits(Ausgangs)-Hinweiszeiger-Block **2056** erzeugt vier Ausgangs-Hinweiszeiger, einen für jeden Puffer, die die Position des nächsten Worts, das herangezogen werden soll, anzeigen.

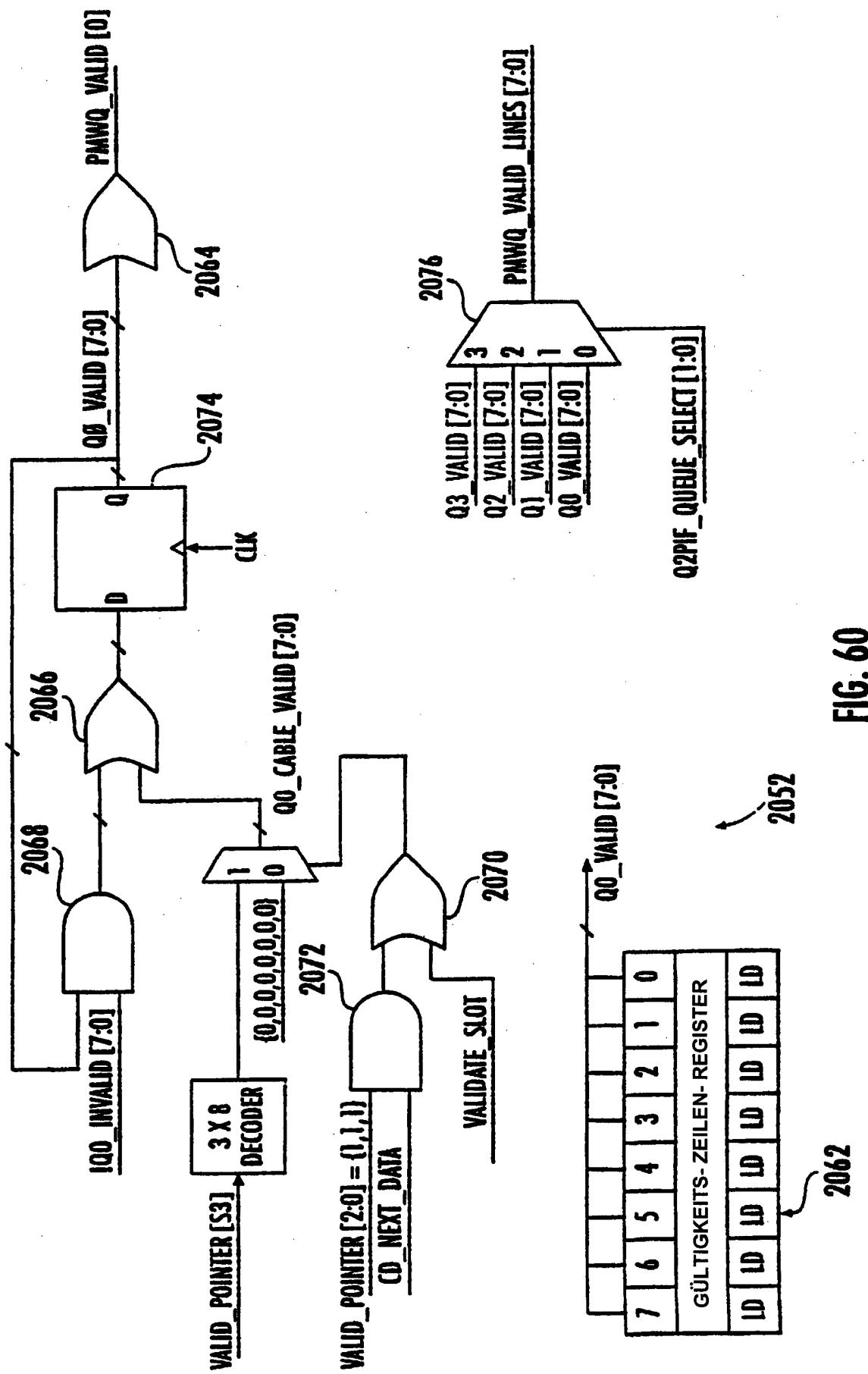

[0145] Wie **Fig. 60** zeigt, hält ein Gültigkeits-Flag-Logik-Block **2052** ein Acht-Bit-Gültigkeits-Zeilen-Register **2062** für jeden der vier Puffer in dem Daten-RAM **2038** aufrecht. Das Gültigkeits-Zeilen-Register **2062** zeigt an, welche der acht Cache-Zeilen in jedem Puffer gültige Daten enthält. Wenn das letzte Wort in einer Cache-Zeile mit Daten gefüllt worden ist (d.h. valid\_pointer[2:0] entspricht „111“ und cd\_next-data wird aufgestellt, was anzeigt, dass das Wort gefüllt worden ist), wird das entsprechende Bit in einem Acht-Bit-Kabel-Gültigkeits-Signal (d. h. q0\_cable\_valid[7:0], q1\_cable\_valid[7:0], usw.) eingestellt. Das Bit, das eingestellt werden soll, wird durch die drei signifikantesten Bits des Gültigkeits-Hinweiszeigers (valid\_pointer[5:3]) bestimmt, die anzeigen, dass die Cache-Zeile gefüllt ist. Das entsprechende Bit in dem Kabel-Gültigkeits-Signal wird auch eingestellt, wenn ein Einstechplatz-Gültigkeitssignal (validate\_slot) von dem Kabel-Decodierer an dem Ende einer Transaktion empfangen ist. Das Kabel-Gültigkeits-Signal wird in das Gültigkeits-Zeilen-Register **2062** entsprechend dem ausgewählten Daten-Puffer an der ansteigenden Flanke des ersten PCI-Takt-Zyklus (CLK)

verriegelt, nachdem das letzte Wort gefüllt ist, oder das valid\_slot Signal empfangen ist. Ansonsten hält das Gültigkeits-Zeilen-Register seinen momentanen Wert bei. Die Bits in dem Gültigkeits-Zeilen-Register **2062** werden dann gelöscht, wenn die entsprechenden Bits eines Acht-Bit-Ungültigkeits-Signals (d.h. q0\_invalid[7:0], q1\_invalid[7:0], usw.) aufgestellt sind.

[0146] Der Gültigkeits-Flag-Logik-Block **2052** erzeugt ein pmwq\_valid[3:0] Signal, das anzeigt, welcher, falls irgendeiner vorhanden ist, der vier Daten-Puffer mindestens eine gültige Zeile an Daten enthält. Der Gültigkeits-Block **2052** erzeugt auch ein pmwq\_valid\_lines[7:0] Signal, das anzeigt, welche der acht Cache-Zeilen eines ausgewählten Daten-Puffers gültig sind. Ein Warteschlangen-Auswahl-Signal von dem QPIF (p2pif\_queue\_select[1:0]) wird dazu verwendet, auszuwählen, welches gültige Zeilen-Register **2062** eines Daten-Puffers verwendet wird, um das pmwq\_valid\_lines[7:0] Signal zu erzeugen. Wenn der Warteschlangen-Block eine Steuerung des Busses erhält, um einen geposteten Speicher-Schreib-Zyklus laufen zu lassen, und zwar von einem ausgewählten Daten-Puffer, überträgt der Warteschlangen-Block alle Daten in jeder Zeile, deren entsprechendes Bit in dem pewg\_valid\_lines[7:0] Signal eingestellt ist. Gates **2064**, **2066**, **2068**, **2070** und **2072** und ein Flip-Flop **2074** sind so angeordnet, um die Werte in dem Gültigkeits-Zeilen-Register **2062** für den ersten Daten-Puffer (q0\_valid[7:0]) einzustellen. Eine ähnliche Schaltung bestimmt die Inhalte der Gültigkeits-Register für die anderen drei Daten-Puffer. Ein Multiplexer **2076** wählt den Wert des pmwg\_valid\_lines[7:0] Signals aus.

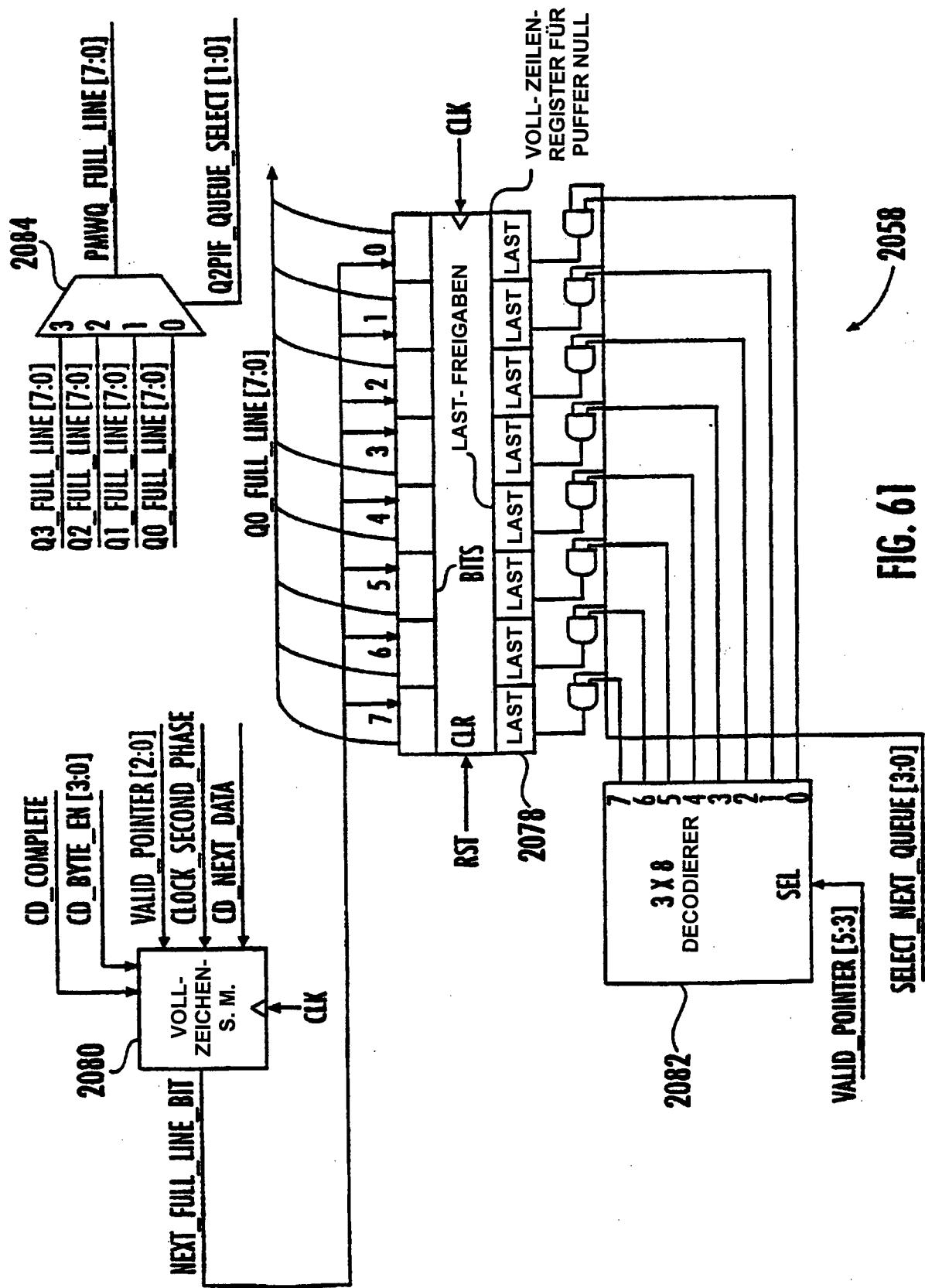

[0147] Wie nun **Fig. 61** zeigt, hält ein Voll-Zeilen-Logik-Block **2058** ein Acht-Bit-Voll-Zeilen-Register **2078** für jeden der vier Daten-Puffer aufrecht. Die Inhalte jedes Voll-Zeilen-Registers **2078** zeigen an, welche der acht Cache-Zeilen in dem entsprechenden Daten-Puffer voll sind. Die Bits in jedem Voll-Zeilen-Register **2078** werden durch ein asynchrones next\_full\_line\_bit Signal, erzeugt durch die Voll-Zeilen-Zustand-Maschine **2080**, was nachfolgend beschrieben ist, eingestellt. Wenn ein Warteschlangen-Auswahl-Signal von der QPIF (select\_nex\_queue[3:1]) einen der Daten-Puffer auswählt und das next\_full\_line\_bit Signal aufgestellt ist, wird das Bit in dem Voll-Zeilen-Register **2078** entsprechend zu der Cache-Zeile, angezeigt durch die drei signifikantesten Bits, des Gültigkeits-Hinweiszeigers (valid\_pointer[5:3]) eingestellt. Ein **3x8** Decodierer **2082** wandelt den Drei-Bit-Gültigkeits-Hinweiszeiger in ein Acht-Bit-Signal um, das bestimmt, welches Bit einzustellen ist. Ein Acht-Bit-Voll-Zeilen-Signal (q0\_full\_line) wird für jeden Daten-Puffer von den Inhalten des entsprechenden Voll-Zeilen-Registers **2078** erzeugt. Das Voll-Zeilen-Signal zeigt an, welche Zeilen in dem entsprechenden Daten-Puffer voll sind. Der Voll-Zeilen-Logik-Block **2058** erzeugt auch ein pmwg\_full\_line[7:0] Signal, das anzeigt, welche Cache-Zeilen eines ausgewählten Daten-Puffers voll sind. Der Multiplexer **2084** und das q2pif\_queue\_select[1:0] Signal werden dazu verwendet, das pmwg\_full\_line[7:0] Signal zu erzeugen.

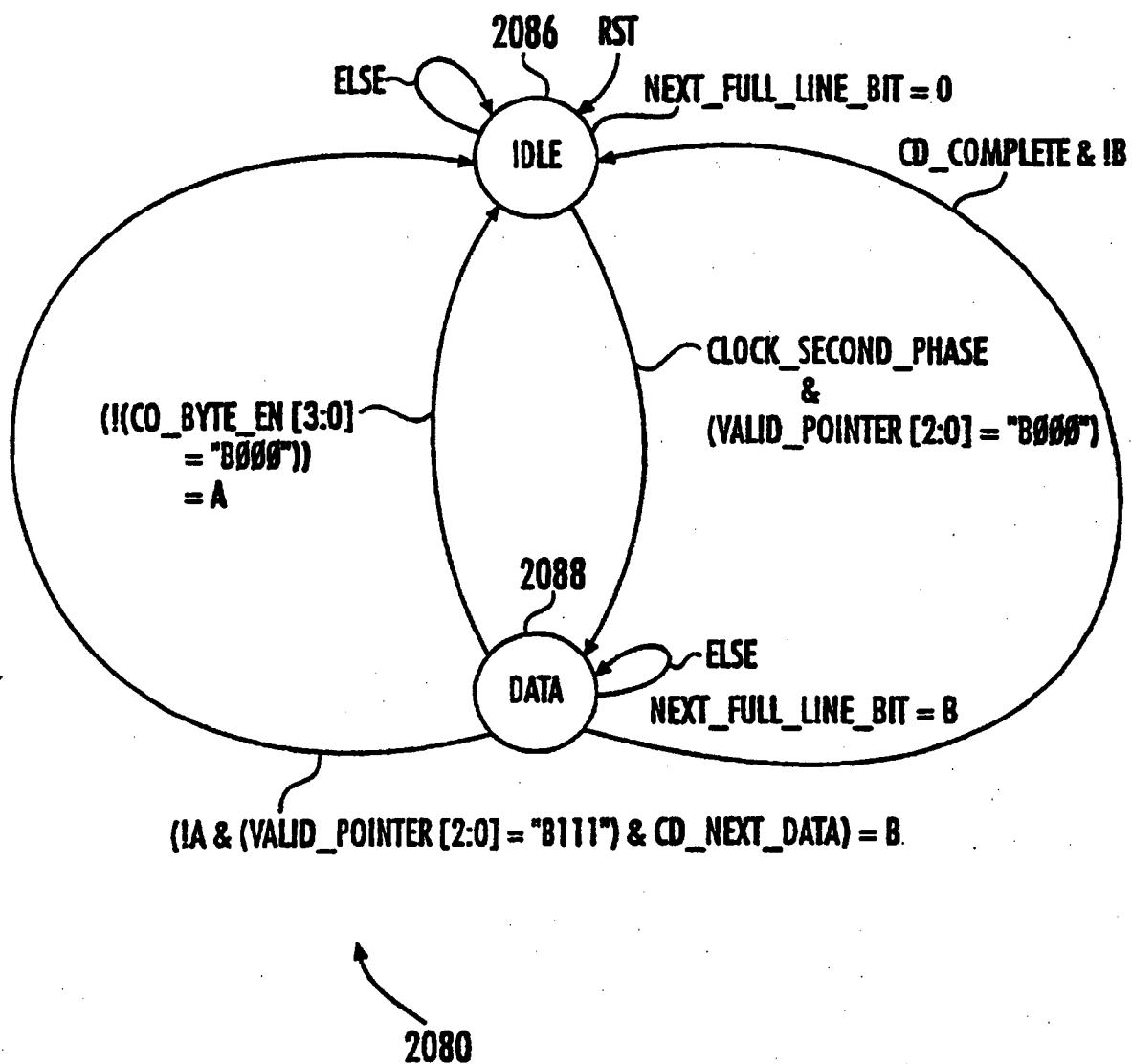

[0148] Wie auch **Fig. 62** zeigt, wird die Voll-Zeilen-Zustand-Maschine **2080** in einen IDLE Zustand **2086** bei einem Reset platziert. In dem IDLE Zustand **2086** wird das next\_full\_line\_bit auf Null gesetzt. Wenn eine Transaktion in die PMWQ platziert wird, tritt die Transaktion in zwei Phasen auf, eine Adressen-Phase und eine Daten-Phase. Wenn die Daten-Phase beginnt (d. h. ein clock\_second\_phase Signal wird aufgestellt) und der Gültigkeits-Hinweiszeiger zu dem ersten Wort in der Cache-Zeile hinweist (valid\_pointer[2:0] = „000“), geht die Zustand-Maschine **2080** zu einem DATA Zustand **2088** über. In dem Datenzustand wird das next\_full\_line\_bit Signal nur dann aufgestellt, wenn der Gültigkeits-Hinweiszeiger auf das letzte Wort in der Cache-Zeile hinweist (valid\_pointer[2:0] = „111“), wird das cd\_next\_data Signal durch den Kabel-Decodierer aufgestellt (anzeigend, dass das letzte Wort mit Daten gefüllt wurde), und das Byte-Freigabe-Signal von dem Kabel-Decodierer (cd\_byte\_en[3:0]) gleicht „0000“. Die Zustand-Maschine geht auch zurück zu dem IDLE Zustand **2086**, wenn diese Zustände auftreten. Falls diese Zustände nicht auftreten, bevor die Transaktion endet (d.h. cd\_complete wird aufgestellt), bleibt das next\_full\_line\_bit Signal nicht aufgestellt und die Zustand-Maschine **2080** geht zurück zu dem IDLE Zustand **2086**. Die Zustand-Maschine **2080** geht auch zu dem IDLE Zustand **2086** ohne Aufstellen des next\_full\_line\_bit Signals über, wenn das cd\_byte\_en[3:0] Signal einen Wert, einen anderen als „0000“, annimmt.

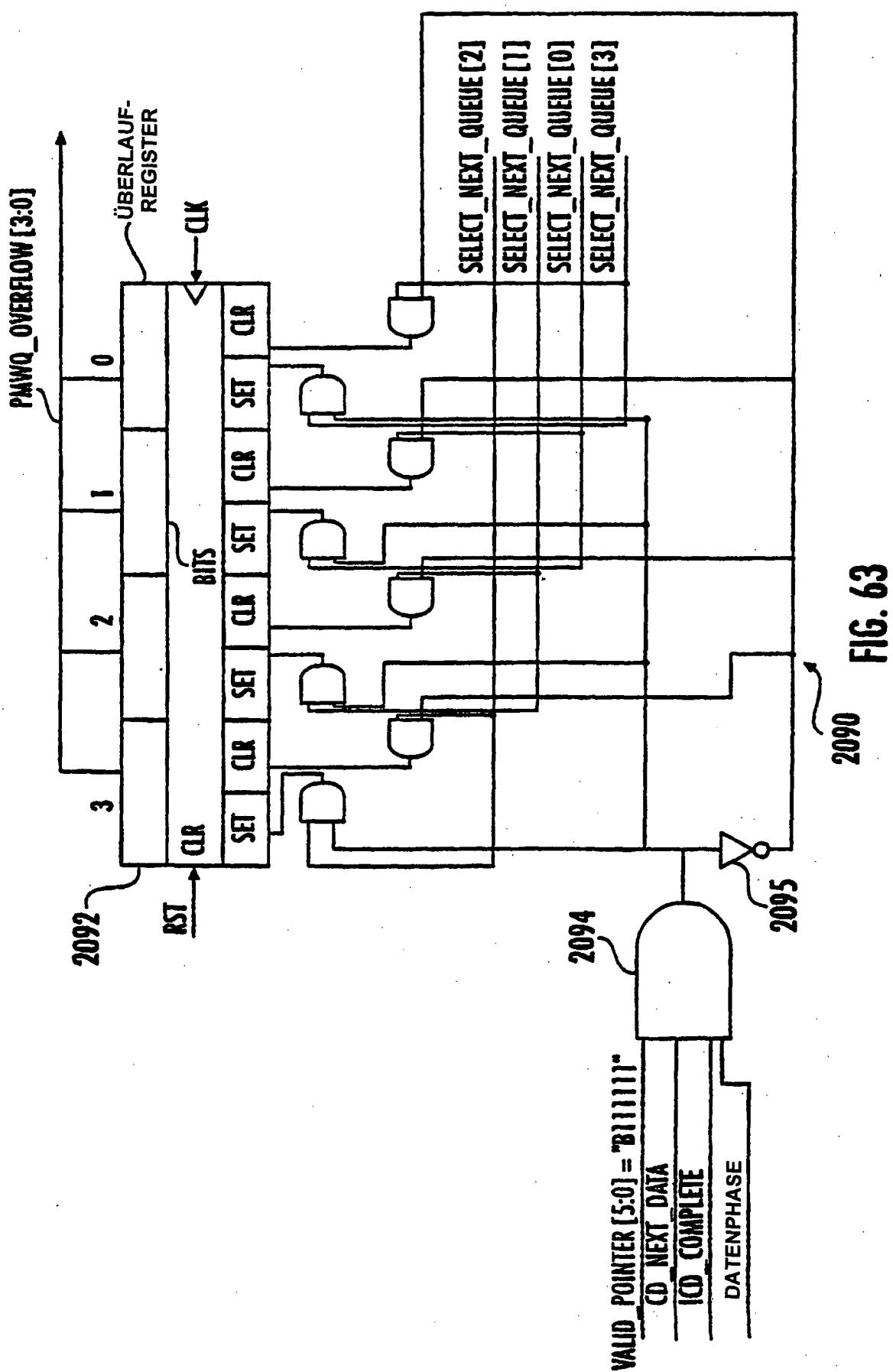

[0149] Wie wiederum **Fig. 59** und auch **Fig. 63** zeigen, muss die PMWQ normalerweise eine Transaktion von dem Kabel-Decodierer beenden, wenn der Daten-Puffer, der die entsprechenden Daten aufnimmt, voll ist. Allerdings lässt, wenn der Kabel-Decodierer fortfährt, Daten zu verschicken, nachdem der Puffer voll ist, ein Überlauf-Logik-Block **2090** zu, dass die Daten in den nächsten, leeren Puffer überlaufen. Der Überlauf-Logik-Block **2090** führt ein Überlauf-Register **2092**, das anzeigt, welche, falls irgendwelche vorhanden sind, der vier Daten-Puffer als Überlauf-Puffer verwendet werden. Die Inhalte des Überlauf-Registers **2092** werden dazu verwendet, ein Vier-Bit-Überlauf-Signal (pmwq\_overflow[3:0]) zu erzeugen. Wenn sich die Transaktion in der Daten-Phase befindet (d.h. data\_phase ist aufgestellt), erreicht der Gültigkeits-Hinweiszeiger das letzte Wort eines Daten-Puffers (d. h. valid\_pointer[5:0] = „111111“), der Kabel-Decodierer zeigt an, dass mehr Daten ankommen (d. h. cd\_next\_data wird aufgestellt), und der Kabel-Decodierer hat nicht angezeigt, dass die Transaktion abgeschlossen ist (d. h. cd\_complete ist nicht aufgestellt), das select\_next\_queue[3:0] Signal, das auf den am kürzesten vorher gefüllten Daten-Puffer hinweist, wird dazu verwendet, das Überlauf-Register-Bit entsprechend dem nächsten Daten-Puffer einzustellen. Falls die Bedingungen nicht erfüllt sind, wird das Überlauf-Bit gelöscht. Gates **2094** und **2095** werden in Verbindung mit dem select\_next\_queue[3:0] Signal verwen-

det, um die geeigneten Überlauf-Register-Bits einzustellen und zu löschen, wenn diese Zustände erfüllt sind. [0150] Eine einzelne Transaktion kann fortführen, um in zusätzliche Puffer überzulaufen, bis der letzte, nicht benutzte Puffer voll ist. Falls mehr als ein Puffer als ein Überlauf-Puffer verwendet wird, werden Mehrfach-Überlauf-Register-Bits eingestellt. Aufeinanderfolgende, eingestellte Bits in dem Überlauf-Register zeigen an, dass eine einzelne Transaktion in mehr als einen Puffer übergelaufen ist. Die Überlauf-Bits werden entweder eingestellt oder gelöscht, wenn die gepostete Schreib-Transaktion in die PMWQ hinein platziert ist. Auch kann, falls die QPIF beginnt, die PMW-Transaktion auf dem Target-Bus laufen zu lassen und den originalen Puffer zu entleeren, während sich die Daten noch dabei befinden, in die PMWQ einzutreten, wobei der Original-Puffer wieder verwendet werden, um die Überlauf-Transaktion fortzuführen. Der Überlauf kann fortführen, bis alle verfügbaren Puffer voll sind.

#### WARTESCHLANGE FÜR VERZÖGERTE ANFORDERUNG

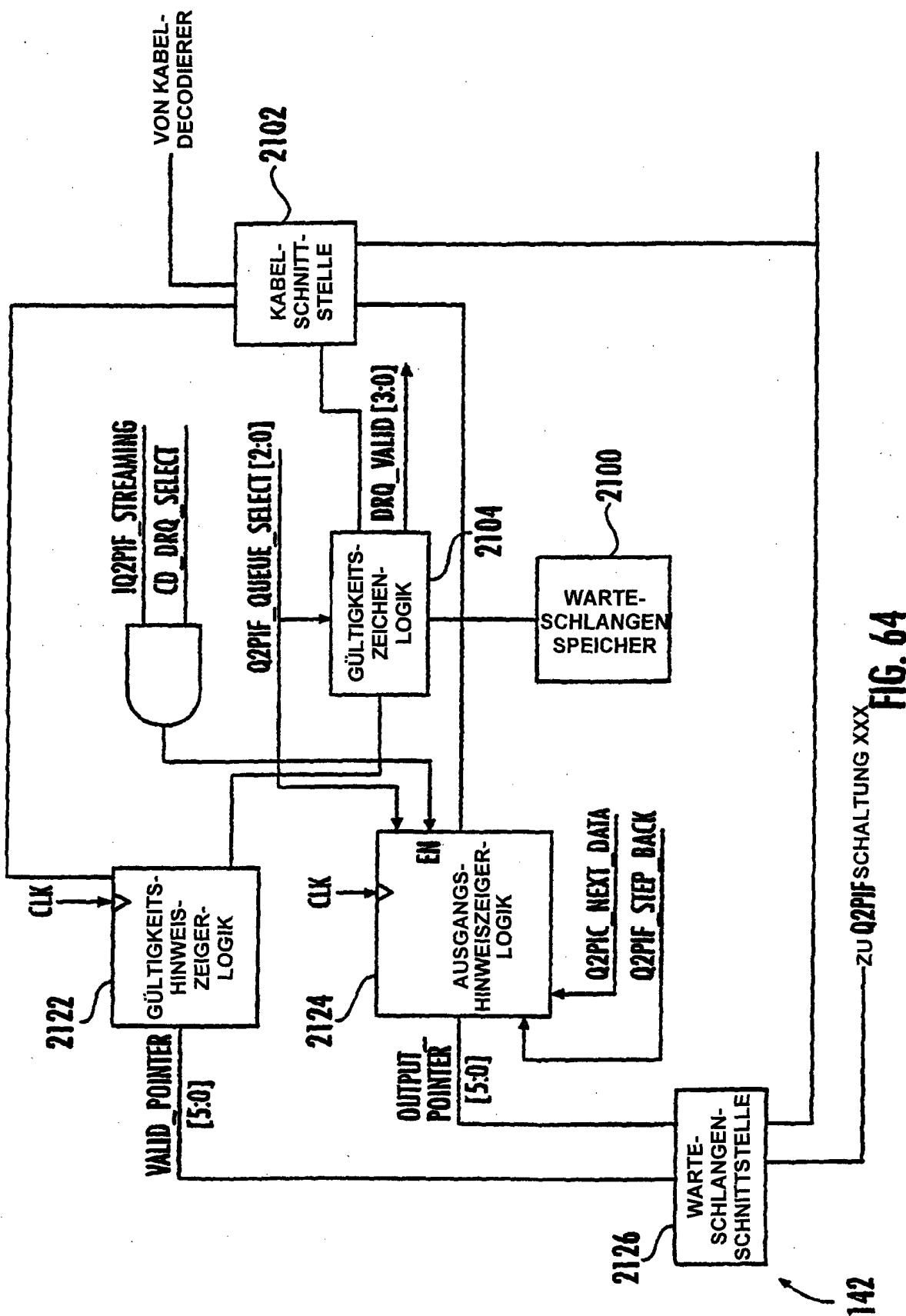

[0151] Wie **Fig. 64** zeigt, speichert die DRQ **142** alle die Informationen, die dazu benötigt werden, eine verzögerte Lese-Anforderung- (Delayed Read Request – DRR) und eine verzögerte Schreib-Anforderung- (Delayed Write Request – DRW) Transaktionen auf dem Target-Bus abzuschließen. Die DRQ umfasst einen Warteschlangenspeicher **2100**, der Informationen hält, wie beispielsweise die Adresse, die davon gelesen oder dazu geschrieben werden soll, den PCI-Befehl-Code, Byte-Freigaben, Adressen- und Daten-Paritäts-Bits, Indikations-Bits über einen „verriegelten Zyklus“ und einen „Dual-Adressen-Zyklus“, und die Puffer-Zahl des Puffers für den verzögerten Abschluss, reserviert in dem initierenden Brücken-Chip für die Abschluss-Informationen. Der Warteschlangen-Speicher **2100** hält auch bis zu zweieinhalbzig Bits (ein Wort) an Daten, die zu dem Target-Bus in einem verzögerten Schreib-Zyklus geschrieben werden sollen. Da verzögerte Schreib-Zyklen niemals mehr als ein Wort an Daten einsetzen, wird kein Daten-RAM in der DRQ benötigt. Die DRQ, und deshalb der Warteschlangen-Speicher **2100**, ist in der Lage, bis zu drei verzögerte Anforderungs-Transaktionen auf einmal zu halten. Ein Kabel-Schnittstellen-Block **2102** beansprucht verzögerte Anforderungs-Transaktionen von dem Kabel-Decodierer und platziert sie in den Warteschlangen-Speicher **2100**. Die folgende Tabelle zeigt die Informationen, die in dem DRQ-Warteschlangen-Speicher beibehalten werden.

| Feld           | Bits                             | Anmerkungen                                                                                                                       |

|----------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Adresse        | 64                               | eingangsseitige Transaktionen unterstützen Dual-Adressen-Zyklen                                                                   |

| PCI-Befehl     | 4                                | I/O-Lesen<br>I/O-Schreiben<br>Config-Lesen<br>Config-Schreiben<br>Speicher-Lesen<br>Speicher-Lese-Zeile<br>Speicher-Lese-Multiple |

| Byte-Freigaben | 4                                | Byte-Freigaben, nicht notwendig an MRL, MRM                                                                                       |

| Parität        | 1/Adresse<br>1/Daten-Übertragung | schicke Daten PAR mit verzögerten Schreib-Transaktionen                                                                           |

| Daten          | 32                               | Daten, in die Warteschlange gestellt, bei verzögerten Schreib-Transaktionen                                                       |

| Verriegelung   | 1                                |                                                                                                                                   |

| DAC-Indikation | 1                                | zeigt an, ob Adresse 32 oder 64 Bits ist                                                                                          |

| Buff Num       | 3                                | zeigt DCQ-Puffer, zugeordnet für Abschluss-Daten, an                                                                              |

#### Inhalte von DRQ

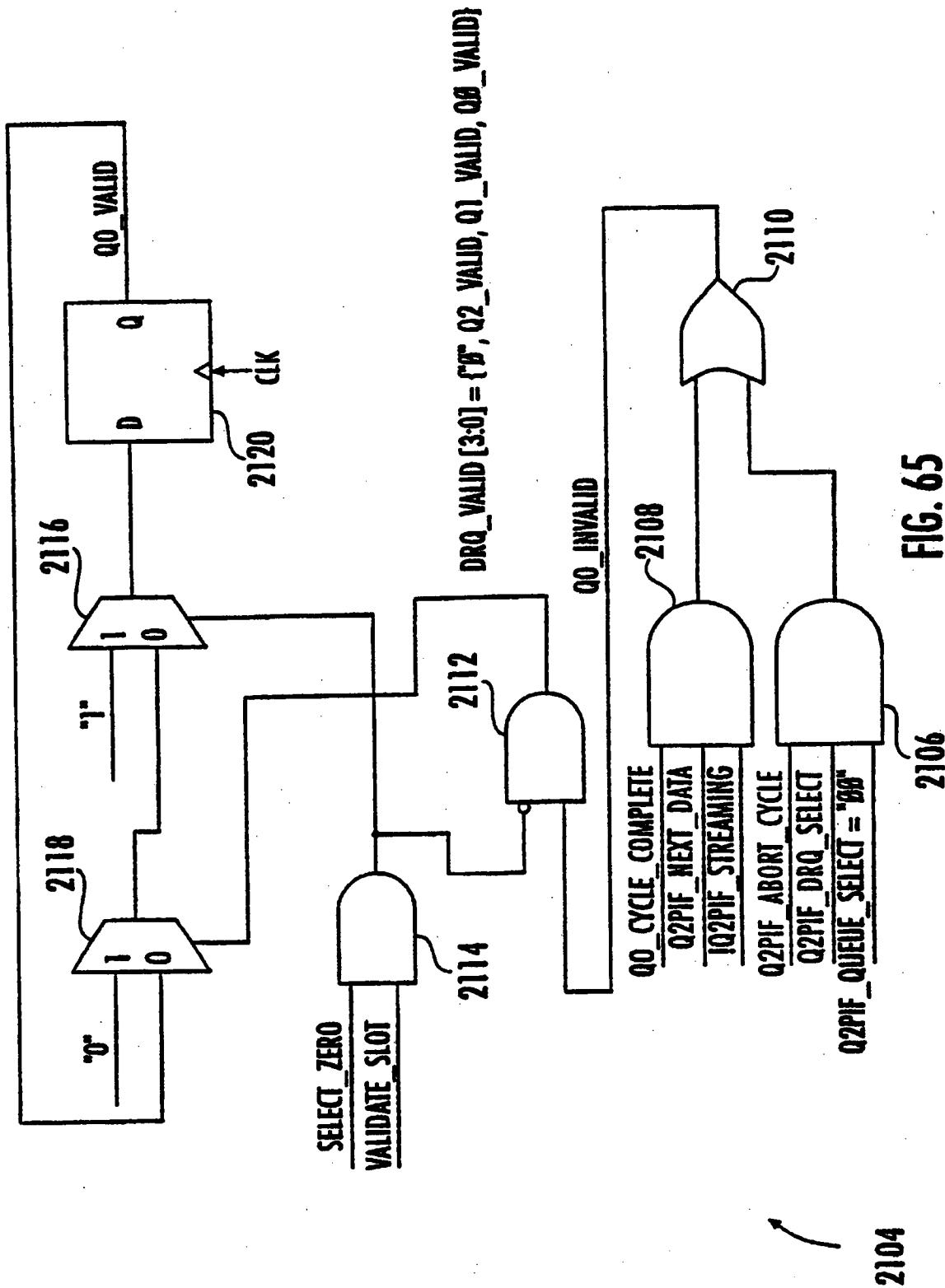

[0152] Wie auch **Fig. 65** zeigt, bestimmt ein Gültigkeits-Flag-Logik-Block **2104**, wann die DRQ alle die Informationen empfangen hat, die dazu notwendig sind, die Transaktionen in dem Warteschlangen-Speicher **2100** laufen zu lassen. Wenn einer der DRQ-Schlüsse durch ein entsprechendes Schlitz-Auswahl-Signal ausgewählt ist (d.h. select\_zero für den ersten Schlitz, select\_one für den zweiten Schlitz und select\_two für den dritten Schlitz) und der Schlitz durch ein validate\_slot Signal für gültig erklärt ist, anzeigen, dass der Kabel-Decodierer ein Zuführen der Transaktion zu der DRQ abgeschlossen hat, wird ein Gültigkeits-Signal entsprechend zu

dem Schlitz (d.h. q0\_valid, q1\_valid oder q2\_valid) an der ansteigenden Flanke des nächsten PCI-Takt-(CLK)-Zyklus aufgestellt. Falls ein Schlitz nicht ausgewählt ist und durch ein valid\_slot Signal für gültig erklärt ist, wird das Gültigkeits-Signal für den Schlitz bzw. den Einstekplatz wieder zurückgenommen, falls die QPIF den Schlitz ausgewählt hat, durch Aufstellen eines DRQ-Auswahl-Signals (q2pif\_drq\_select) und durch Identifizieren des Schlitzes bzw. des Einstekplatzes (q2pif\_queue\_select = Schlitz-Zahl), allerdings die Transaktion durch Aufstellen eines Zyklus-Aussonderungs-Signals (q2pif\_abort\_cycle) ausgesondert hat. Das Gültigkeits-Signal wird auch zurückgenommen, falls die DRQ die Transaktion durch Aufstellen eines Zyklus-Abschluss-Signals (z. B. q0\_cycle\_complete) beendet, während die QPIF auf mehr Daten wartet (d. h. q2pif\_next\_data ist aufgestellt). Allerdings wird das Zyklus-Abschluss-Signal ignoriert, falls die QPIF momentan Daten zu dem anderen Brücken-Chip (d.h.

[0153] q2pif\_streaming ist aufgestellt) als Datenfolge überträgt. Ansonsten hält, falls das Gültigkeits-Signal des Schlitzes nicht spezifisch aufgestellt oder an einem Takt-Zyklus zurückgenommen ist, er seinen momentanen Wert bei. Der Gültigkeits-Flag-Logik-Block **2104** erzeugt auch ein DRQ Gültigkeits-Signal (drq\_valid[3:0]), das anzeigt, welcher, falls irgendeiner vorhanden ist, der drei DRQ-Schlitz eine gültige Transaktion enthält, und zwar durch Kombinieren der Gültigkeits-Signale für jeden individuellen Schlitz (d.h. drq\_valid = {0, q2\_valid, q1\_valid, q0\_valid}). Gates **2106**, **2108**, **2110**, **2112** und **2114**, Multiplexer **2116** und **2118** und ein Flip-Flop **2120** sind so angeordnet, um die Schlitz-Gültigkeits-Signale und die DRQ-Gültigkeits-Signale auf diese Art und Weise zu erzeugen.

[0154] Die DRQ umfasst auch Hinweiszeiger-Logik-Blöcke, die Hinweiszeiger zu den Speicher-Stellen beibehalten, von denen Daten während verzögter Lese-Anforderungs-Transaktionen gelesen werden sollen. Wenn die Adresse, an der die verzögerten Lese-Transaktionen beginnen wird, in den Warteschlangen-Speicher **2100** eingeladen ist, erzeugt ein Gültigkeits-Hinweiszeiger-Logik-Block **2122** einen Sechs-Bit-Gültigkeits-Hinweiszeiger, der anzeigt, wo die Transaktion enden wird. Falls die Transaktion ein einzelnes Wort umfasst (z. B. ein Speicher-Lesen), stellt die Gültigkeits-Hinweiszeiger-Logik **2122** den gültigen Hinweiszeiger gleich zu der Adresse, eingeladen in den Warteschlangen-Speicher **2100** hinein, auf. Für eine Speicher-Lese-Zeilen-Transaktion gibt die Gültigkeits-Hinweiszeiger-Logik **2122** dem gültigen Hinweiszeiger einen Wert von „000111“, was anzeigt, dass der letzte, gültige Teil der Daten ein acht dwords (d. h. eine Cache-Zeile) über den Startpunkt hinaus ist. Für eine Speicher-Lese-Mehrzahl-Transaktion wird der gültige Hinweiszeiger auf „111111“ gesetzt, was anzeigt, dass der letzte, gültige Teil an Daten vierundsechzig dwords (d. h. acht Cache-Zeilen) über den Startpunkt ist. Die Gültigkeits-Hinweiszeiger-Logik **2122** behält einen gültigen Hinweiszeiger für jeden Schlitz in der DRQ (valid\_pointer\_0[5:0], valid\_pointer\_1[5:0] und valid\_pointer\_2[5:0]) bei. Die Stelle des gültigen Hinweiszeigers wird durch die DRQ dann ignoriert, wenn sie ein Streaming-Signal von der QPIF (q2pif\_streaming) empfängt, wie dies in weiterem Detail nachfolgend beschrieben ist.