(19) 日本国特許庁(JP)

(12) 特許公報(B2)

(11) 特許番号

特許第5526529号

(P5526529)

(45) 発行日 平成26年6月18日(2014.6.18)

(24) 登録日 平成26年4月25日(2014.4.25)

|               |              |

|---------------|--------------|

| (51) Int.Cl.  | F 1          |

| HO 1 L 29/786 | (2006.01)    |

| HO 1 L 21/336 | (2006.01)    |

| HO 1 L 27/08  | (2006.01)    |

| HO 1 L 27/00  | (2006.01)    |

|               | HO 1 L 29/78 |

|               | HO 1 L 29/78 |

|               | HO 1 L 29/78 |

|               | HO 1 L 27/08 |

|               | HO 1 L 27/00 |

|               | HO 1 L 331 E |

|               | HO 1 L 301 C |

請求項の数 21 (全 27 頁)

(21) 出願番号 特願2008-294913 (P2008-294913)

(22) 出願日 平成20年11月18日 (2008.11.18)

(65) 公開番号 特開2010-123696 (P2010-123696A)

(43) 公開日 平成22年6月3日 (2010.6.3)

審査請求日 平成23年11月17日 (2011.11.17)

(73) 特許権者 000004112

株式会社ニコン

東京都千代田区有楽町1丁目12番1号

(74) 代理人 100104156

弁理士 龍華 明裕

(74) 代理人 100118005

弁理士 飯山 和俊

(74) 代理人 100143502

弁理士 明石 英也

(74) 代理人 100112520

弁理士 林 茂則

(72) 発明者 松岡 新吾

東京都千代田区丸の内3丁目2番3号 株式会社ニコン内

最終頁に続く

(54) 【発明の名称】積層半導体装置及び積層半導体装置の製造方法

(57) 【特許請求の範囲】

【請求項1】

電子素子が形成された素子領域を有する第1半導体装置が設けられた第1基板と、

前記第1基板に積層され、前記電子素子の動作の閾値電圧を動的に制御する制御回路が

形成された第2半導体装置が設けられた第2基板と、

前記第1基板及び前記第2基板の少なくとも一方を貫通するように前記第1半導体装置

及び前記第2半導体装置の少なくとも一方に形成され、前記素子領域と前記制御回路とを

互いに電気的に結合する貫通結合部と、

を備える積層半導体装置。

【請求項2】

前記貫通結合部は、前記素子領域から前記第1半導体装置の内部を前記第2半導体装置

に向けて伸び、前記第2半導体装置は、前記貫通結合部に接続される外部接続部を有し、

前記外部接続部および前記貫通結合部を介して前記第1半導体装置の前記電子素子の動作

の閾値電圧を動的に制御する請求項1に記載の積層半導体装置。

10

【請求項3】

前記第1半導体装置は、

単結晶シリコンのベース部と、

前記ベース部の上の絶縁層と、

前記絶縁層の上の単結晶シリコン層と、

前記単結晶シリコン層に形成され前記絶縁層に達する分離溝構造とを有し、

20

前記素子領域は、前記分離溝構造で囲まれた前記単結晶シリコン層の領域であり、前記貫通結合部は、少なくとも前記ベース部および前記絶縁層を貫通し、前記素子領域に電気的に結合する請求項2に記載の積層半導体装置。

【請求項4】

前記貫通結合部と前記素子領域とは、直接および中間層の少なくとも一方を介して接触する請求項1から3のいずれか一項に記載の積層半導体装置。

【請求項5】

前記第1半導体装置は、前記電子素子を構成する部材および前記電子素子より後に形成される部材の少なくとも一方と同一の工程で形成される配線を有し、

前記貫通結合部と前記素子領域とは、前記配線を介して接触する請求項1から4のいずれか一項に記載の積層半導体装置。 10

【請求項6】

前記貫通結合部は、前記電子素子の形成前に形成され、高濃度に不純物がドープされた半導体を含む請求項1から5の何れか一項に記載の積層半導体装置。

【請求項7】

前記貫通結合部は、前記電子素子の形成後に形成され、金属を含む請求項1から5の何れか一項に記載の積層半導体装置。 20

【請求項8】

前記素子領域に形成された前記電子素子は、トランジスタである請求項1から7のいずれか一項に記載の積層半導体装置。 20

【請求項9】

電子素子が形成された素子領域を有する第1半導体装置が設けられた第1基板を準備する段階と、

前記電子素子の動作の閾値電圧を動的に制御する制御回路が形成された第2半導体装置が設けられた第2基板を準備する段階と、

前記第1基板と前記第2基板とを互いに積層する段階と、

前記第1半導体装置及び前記第2半導体装置の少なくとも一方に、前記素子領域と前記制御回路とを互いに電気的に結合する貫通結合部を前記第1基板及び前記第2基板の少なくとも一方を貫通するように形成する段階とを有する積層半導体装置の製造方法。 30

【請求項10】

前記第1基板を準備する段階は、

前記素子領域から前記第1半導体装置の内部を前記第2半導体装置に向けて伸びるように前記貫通結合部を形成する段階を有し、

前記第2基板を準備する段階は、前記貫通結合部に接続される外部接続部を前記第2半導体装置に形成する段階を有し、

前記積層する段階では、前記第2半導体装置の前記外部接続部と前記貫通結合部とが接触するよう、前記第1基板と前記第2基板とを積層する請求項9に記載の積層半導体装置の製造方法。

【請求項11】

前記第1基板を準備する段階は、

単結晶シリコンのベース部、前記ベース部の上の絶縁層、および、前記絶縁層の上の単結晶シリコン層を有するSOI基板を準備する段階と、

前記単結晶シリコン層に前記絶縁層に達する分離溝構造を形成して、前記単結晶シリコン層の前記素子領域を画定する段階とを有する請求項9または10に記載の積層半導体装置の製造方法。

【請求項12】

前記第1基板を準備する段階は、

少なくとも前記ベース部および前記絶縁層を貫通し、前記素子領域に電気的に結合するよう、前記貫通結合部を形成する段階を有する請求項11に記載の積層半導体装置の製造方法。 50

## 【請求項 1 3】

前記第1基板を準備する段階は、少なくとも前記ベース部および前記絶縁層を貫通することとなる孔を形成する段階と、前記孔に金属を埋め込む段階と、前記電子素子が形成されていない側の前記ベース部を薄化して前記金属を露出させ、前記貫通結合部を形成する段階とを有する請求項12に記載の積層半導体装置の製造方法。

## 【請求項 1 4】

前記素子領域を画定する段階は、前記孔に形成した金属が直接および中間層の少なくとも一方を介して前記素子領域に接触するよう、前記素子領域を画定する請求項13に記載の積層半導体装置の製造方法。

10

## 【請求項 1 5】

前記素子領域と前記孔に形成した金属とを電気的に結合する配線を形成する工程を更に有する請求項13に記載の積層半導体装置の製造方法。

## 【請求項 1 6】

前記電子素子を構成する部材の形成工程において、前記素子領域と前記孔に形成した金属とを電気的に結合する配線を同時に形成する請求項13に記載の積層半導体装置の製造方法。

## 【請求項 1 7】

前記第1基板を準備する段階は、少なくとも前記ベース部および前記絶縁層を貫通し、前記素子領域に電気的に結合する、不純物が高濃度にドープされた半導体の前記貫通結合部を形成する段階を有する請求項11に記載の積層半導体装置の製造方法。

20

## 【請求項 1 8】

前記貫通結合部を形成する段階において、前記貫通結合部が直接および中間層の少なくとも一方を介して前記素子領域に接触するよう、前記貫通結合部を形成する請求項16に記載の積層半導体装置の製造方法。

## 【請求項 1 9】

前記素子領域と前記貫通結合部とを電気的に結合する配線を形成する工程を更に有する請求項17に記載の積層半導体装置の製造方法。

## 【請求項 2 0】

30

前記電子素子を構成する部材の形成工程において配線を同時に形成する請求項17に記載の積層半導体装置の製造方法。

## 【請求項 2 1】

前記第1基板を準備する段階は、

前記素子領域に前記電子素子としてトランジスタを形成する段階を有する請求項9から20のいずれか一項に記載の積層半導体装置の製造方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、積層半導体装置及び積層半導体装置の製造方法に関する。

40

## 【背景技術】

## 【0002】

半導体装置の動作速度を向上でき、消費電力の少ないデバイスとして、SOI (silicon-on-insulator) 層を有するSOI基板に、トランジスタ等の半導体素子を形成したSOIデバイスが注目されている。例えば、特許文献1には、SOI層の上部に形成される部分トレンチ分離(以下、PTIと称する場合がある。)を有するデバイスが開示されている。特許文献1に記載されたPTIを有するSOIデバイスは、PTIの下に残存するSOI層を通して、トランジスタが形成されたウエルの電位を制御できる。これにより、上記ウエルの電位を一定に固定して、トランジスタの動作を安定化できること、および、トランジスタの用途によっては上記ウエルの電位を動的に制御できる

50

ことが開示されている。

【特許文献 1】特開 2007-5575 号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、上記 PTI を有する SOI デバイスと、当該 SOI デバイスのウエルの電位を制御するデバイスとを、一枚の SOI 基板の中に形成する場合には、プロセスが複雑になる。

【課題を解決するための手段】

【0004】

上記課題を解決するために、本発明の第 1 の態様においては、単結晶シリコンのベース部と、ベース部の上の絶縁層と、絶縁層の上の単結晶シリコン層と、単結晶シリコン層に形成され絶縁層に達する分離溝構造と、分離溝構造で囲まれた単結晶シリコン層のボディ領域と、ボディ領域に形成されるトランジスタと、少なくともベース部および絶縁層を貫通し、ボディ領域に電気的に結合する貫通結合部とを有する第 1 半導体装置と、貫通結合部に接する外部接続部を有する第 2 半導体装置と、を備え、第 2 半導体装置は、貫通結合部を介して第 1 半導体装置のボディ領域の電位を制御する積層半導体装置が提供される。

【0005】

本発明の第 2 の態様においては、単結晶シリコンのベース部と、ベース部の上の絶縁層と、絶縁層の上の単結晶シリコン層と、単結晶シリコン層に形成され絶縁層に達する分離溝構造と、分離溝構造で囲まれた単結晶シリコン層のボディ領域と、ボディ領域に形成されるトランジスタと、少なくともベース部および絶縁層を貫通し、ボディ領域に電気的に結合する貫通結合部と、を有する第 1 半導体装置を準備する段階と、第 2 半導体装置の外部接続部と貫通結合部とが接触するよう、第 1 半導体装置と第 2 半導体装置とを積層する段階とを備え、第 1 半導体装置を準備する段階は、ベース部、絶縁層および単結晶シリコン層を有する SOI 基板を準備する段階と、少なくともベース部および絶縁層を貫通することとなる孔を形成する段階と、孔に金属を埋め込む段階と、単結晶シリコン層に絶縁層に達する分離溝構造を形成して、単結晶シリコン層のボディ領域を画定する段階と、ボディ領域にトランジスタを形成する段階と、トランジスタが形成されていない側のベース部を薄化して金属を露出させ、貫通結合部を形成する段階と、を有する、積層半導体装置の製造方法が提供される。

【0006】

本発明の第 3 の態様においては、単結晶シリコンのベース部と、ベース部の上の絶縁層と、絶縁層の上の単結晶シリコン層と、単結晶シリコン層に形成され絶縁層に達する分離溝構造と、分離溝構造で囲まれた単結晶シリコン層のボディ領域と、ボディ領域に形成されるトランジスタと、少なくともベース部および絶縁層を貫通し、ボディ領域に電気的に結合する貫通結合部と、を有する第 1 半導体装置を準備する段階と、第 2 半導体装置の外部接続部と貫通結合部とが接触するよう、第 1 半導体装置と第 2 半導体装置とを積層する段階とを備え、第 1 半導体装置を準備する段階は、ベース部、絶縁層および単結晶シリコン層を有する SOI 基板を準備する段階と、単結晶シリコン層に絶縁層に達する分離溝構造を形成して、単結晶シリコン層のボディ領域を画定する段階と、ボディ領域にトランジスタを形成する段階と、少なくともベース部および絶縁層を貫通し、ボディ領域に電気的に結合する、不純物が高濃度にドープされた半導体の貫通結合部を形成する段階とを有する、積層半導体装置の製造方法が提供される。

【0007】

なお、上記の発明の概要は、本発明の必要な特徴の全てを列挙したものではない。また、これらの特徴群のサブコンビネーションもまた、発明となりうる。

【発明を実施するための最良の形態】

【0008】

以下、発明の実施の形態を通じて本発明を説明するが、以下の実施形態は特許請求の範

10

20

30

40

50

囲にかかる発明を限定するものではない。また、実施形態の中で説明されている特徴の組み合わせの全てが発明の解決手段に必須であるとは限らない。

【0009】

以下、図面を参照して、実施形態について説明するが、図面の記載において、同一または類似の部分には同一の参照番号を付して重複する説明を省く場合がある。なお、図面は模式的なものであり、厚みと平面寸法との関係、比率等は現実のものとは異なる場合がある。また、説明の都合上、図面相互間においても互いの寸法の関係又は比率が異なる部分が含まれる場合がある。

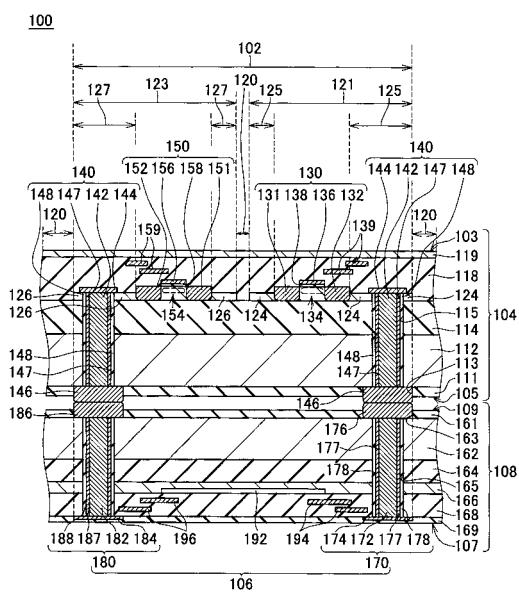

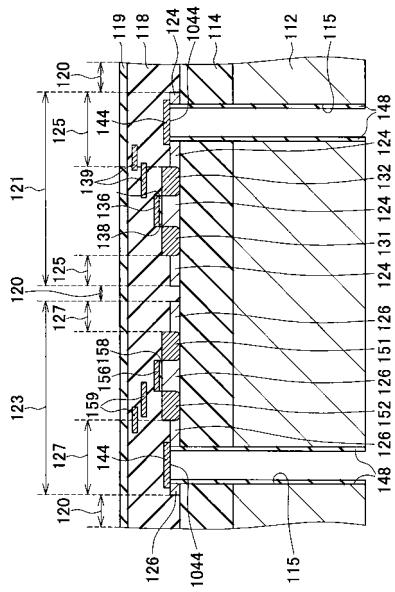

【0010】

図1は、積層半導体装置100の断面図の一例を概略的に示す。積層半導体装置100は、半導体装置102と、半導体装置106とを備える。半導体装置102は、第1半導体装置の一例であってよい。半導体装置106は、第2半導体装置の一例であってよい。半導体装置102および半導体装置106は、トランジスタ、または、トランジスタを含む集積回路であってよい。積層半導体装置100は、例えば、複数の半導体装置102が形成された基板104と、複数の半導体装置106が形成された基板108とを積層して得られる。

【0011】

まず、基板104に形成される半導体装置102について説明する。図1に示すとおり、半導体装置102は、Si基板112と、絶縁層114と、絶縁層114の上に形成された素子分離領域120、半導体素子121および半導体素子123とを有してよい。半導体装置102は、基板104の表面103側に表面保護層119を有してよく、基板104の裏面105側に裏面保護層111を有してよい。また、半導体装置102は、絶縁層114と表面保護層119との間に、層間配線層118を有してよい。

【0012】

Si基板112および絶縁層114には、Si基板112および絶縁層114を貫通する開口115が形成されてよい。裏面保護層111には、裏面保護層111を貫通する開口113が形成されてよい。開口113および開口115は、例えば、エッチング、レーザー加工により形成できる。

【0013】

Si基板112は、単結晶シリコンを含んでよい。Si基板112は、ベース部の一例であってよい。Si基板112は、Si基板であってもよく、SOI基板の一部であってもよい。絶縁層114は、Si基板112の上に形成される。絶縁層114は、Si基板112の一方の面に接してよい。絶縁層114として、SiO<sub>2</sub>等の酸化膜を用いてよい。絶縁層114は、SOI基板の一部であってよい。

【0014】

層間配線層118は、内部に、電子素子間を電気的に結合する配線が配される。半導体装置102、半導体装置106、半導体素子121および半導体素子123は、電子素子の一例であってよい。層間配線層118として、SiO<sub>2</sub>を用いてよく、SiCOH等の低誘電率材料(LOW-k材料)を用いてよい。層間配線層118は、例えば、CVD法、塗布法により形成できる。裏面保護層111および表面保護層119は、半導体装置102を保護する。裏面保護層111および表面保護層119として、ポリイミド等の絶縁性の材料を用いてよい。裏面保護層111および表面保護層119は、例えば、塗布法により形成できる。

【0015】

素子分離領域120は、電子素子間を素子分離してよい。素子分離領域120は、半導体素子121と、半導体素子123とを素子分離してよい。基板104に複数の半導体装置102が形成されている場合には、素子分離領域120は、一の半導体装置102と、他の半導体装置102とを素子分離してよい。

【0016】

素子分離領域120は、絶縁層114のSi基板112に接する面と反対側の面に接す

10

20

30

40

50

る単結晶シリコン層に形成され、絶縁層 114 に達する分離溝構造の一例であってよい。上記単結晶シリコン層は、SOI 基板の SOI 層であってよい。素子分離領域 120 は、例えば、上記単結晶シリコン層に形成され絶縁層 114 に達する溝であってよい。素子分離領域 120 は、例えば、エッチングにより上記単結晶シリコン層の一部を溝状に除去することで形成できる。上記単結晶シリコン層の素子分離領域 120 で囲まれた領域に、電子素子を形成することで、当該電子素子と他の電子素子とを電気的に分離できる。

#### 【0017】

なお、本実施形態において、絶縁層 114 の上に形成された上記単結晶シリコン層の一部をエッチングにより除去して、絶縁層 114 に達する溝を形成することで、分離溝構造を形成する場合について説明した。しかし、分離溝構造の形成方法は、これに限定されない。例えば、絶縁層 114 の上の単結晶シリコン層の一部を酸化、窒化、または酸窒化して、絶縁層 114 に達する酸化シリコン、窒化シリコン、酸窒化シリコンを形成することで、分離溝構造を形成してよい。

#### 【0018】

半導体素子 121 は、絶縁層 114 および素子分離領域 120 により、素子分離されてよい。半導体素子 121 は、第 1 半導体装置の一例であってよい。半導体素子 121 は、素子領域 124 と、リセス部 125 と、PMOS 型トランジスタ 130 と、層間配線 139 と、リセス部 125 と電気的に結合される貫通電極 140 とを含んでよい。PMOS 型トランジスタ 130 は、不純物領域 131 および不純物領域 132 と、チャネル領域 134 と、ゲート電極 136 と、ゲート絶縁膜 138 とを有してよい。貫通電極 140 は、導電性部材 142 と、電極パッド 144 と、バンプ電極 146 と、金属層 147 と、絶縁層 148 とを有してよい。

#### 【0019】

半導体素子 121 は、貫通電極 140 を介して電気的に結合された半導体装置 106 により、素子領域 124 の電位を制御される。これにより、素子領域 124 に形成された PMOS 型トランジスタ 130 の閾値電圧を動的に制御できる。例えば、PMOS 型トランジスタ 130 の待機時には閾値電圧を高くすることで、オフ電流を抑制できる。一方、PMOS 型トランジスタ 130 の動作時には閾値電圧を低くすることで、オン電流を増加させることができる。また、半導体素子 121 と、素子領域 124 の電位を制御する半導体装置 106 とが異なる基板に形成されているので、半導体素子 121 と半導体装置 106 とを、それぞれに最適なプロセスで製造することができる。

#### 【0020】

素子領域 124 には、リセス部 125、PMOS 型トランジスタ 130 および貫通電極 140 が形成される。素子領域 124 は、ボディ領域の一例であってよい。素子領域 124 は、単結晶シリコンを含んでよい。素子領域 124 は、絶縁層 114 の Si 基板 112 に接する面と反対側の面に接する単結晶シリコン層に形成されてよい。上記単結晶シリコン層は、SOI 基板の SOI 層であってよい。素子領域 124 は、上記単結晶シリコン層において、周囲を素子分離領域 120 に囲まれてよい。本実施形態において、素子領域 124 には PMOS 型トランジスタ 130 が形成されるので、素子領域 124 には、P、As、Sb 等の N 型の不純物がドープされてよい。

#### 【0021】

リセス部 125 は素子領域 124 の一部に形成され、リセス部 125 における素子領域 124 の厚さは、不純物領域 131、不純物領域 132 およびチャネル領域 134 が形成される領域における素子領域 124 の厚さより薄い。リセス部 125 は、例えば、エッチングにより形成できる。

#### 【0022】

本実施形態において、基板 104 には複数の開口 115 が形成され、開口 115 の一つは、Si 基板 112 および絶縁層 114 だけでなく、リセス部 125 の一部をも貫通する。図 1 に示すとおり、上記の開口 115 は、リセス部 125 の貫通電極 140 が形成される領域を、裏面 105 側から表面 103 側に向かって貫通する。

10

20

30

40

50

## 【0023】

P MOS型トランジスタ130は、素子領域124に形成される。P MOS型トランジスタ130は、ボディ領域に形成されるトランジスタの一例であってよい。不純物領域131および不純物領域132は、それぞれ、MOS型トランジスタのドレイン領域およびソース領域であってよい。不純物領域131および不純物領域132の厚さは、素子領域124の厚さと同等であってよい。不純物領域131および不純物領域132は、例えば、A1、B等のP型の不純物をドープすることで形成できる。

## 【0024】

ゲート電極136は、素子領域124の上に形成される。ゲート電極136は、少なくとも、不純物領域131および不純物領域132に挟まれたチャネル領域134の上に形成され、チャネル領域134に電位または電流の作用を及ぼす。例えば、ゲート電極136は電圧を印加され、チャネル領域134の電流を制御する。図中の点線は、ゲート電極136に所定の電圧が印加された場合におけるチャネル領域134の一例を示す。ゲート電極136は、ポリシリコンを含んでよく、W等の金属を含んでもよい。ゲート電極136は、例えば、真空蒸着法、CVD法により形成できる。

## 【0025】

ゲート絶縁膜138は、素子領域124とゲート電極136とを絶縁する。ゲート絶縁膜138として、 $\text{SiO}_2$ を用いてもよく、 $\text{ZrO}_2$ 、 $\text{HfO}_2$ 、 $\text{Al}_2\text{O}_3$ 等の高誘電率材料(High-k材料)を用いてもよい。ゲート絶縁膜138は、例えば、真空蒸着法、CVD法により形成できる。

## 【0026】

層間配線139は、P MOS型トランジスタ130と、N MOS型トランジスタ150等の他の電子素子とを電気的に結合する。層間配線139は、層間配線層118の内部で、多層に配されてよい。層間配線139は、A1等の金属を含んでよい。層間配線139は、例えば、真空蒸着法、CVD法により形成できる。

## 【0027】

貫通電極140は、半導体素子121の素子領域124と、基板104の裏面105に形成されるバンプ電極146とを電気的に結合する。貫通電極140は、素子領域124のリセス部125と接触してよい。貫通電極140は、貫通結合部の一例であってよい。

## 【0028】

導電性部材142は、少なくともSi基板112および絶縁層114を貫通して、素子領域124に電気的に結合する。導電性部材142は、電極パッド144を介して素子領域124と接触してよい。導電性部材142は、貫通結合部の一例であってよい。導電性部材142は、開口115の内部に形成されてよい。

## 【0029】

導電性部材142は、ポリシリコンを含んでよく、Cu等の金属を含んでもよい。導電性部材142がP MOS型トランジスタ130の形成前に形成される場合には、導電性部材142は、高濃度に不純物がドープされた半導体を含んでよい。上記半導体は、ポリシリコンであってよい。導電性部材142がP MOS型トランジスタ130の形成後に形成される場合には、導電性部材142は、金属を含んでよい。上記金属は、Cuであってよい。導電性部材142は、例えば、めっき法、CVD法により形成できる。

## 【0030】

電極パッド144は、導電性部材142と素子領域124とを電気的に結合する。電極パッド144は、リセス部125の一部において、素子領域124の上に形成されてよい。電極パッド144は、P MOS型トランジスタ130を構成する部材が形成されるより前に形成されてよい。電極パッド144は、ポリシリコンを含んでよく、W、A1等の金属を含んでもよい。電極パッド144は、例えば、真空蒸着法、CVD法により形成できる。

## 【0031】

バンプ電極146は、半導体装置102と半導体装置106との接点であってよい。バ

10

20

30

40

50

ンプ電極 146 は、裏面保護層 111 に形成された開口 113 の内部に形成されてよい。バンプ電極 146 は、Au、Ni、Cu 等の金属を含んでよく、Sn-Ag 合金等の合金を含んでよい。バンプ電極 146 は、例えば、めっき法、塗布法、リフローにより形成できる。

【0032】

金属層 147 は、開口 115 の内部に形成される。金属層 147 は、導電性部材 142 と絶縁層 148 との間に配されてよい。金属層 147 は、TiN 等のバリアメタルを含んでよい。これにより、導電性部材 142 に含まれる Cu 等の金属が Si 基板 112、素子領域 124 等に拡散することを抑制できる。金属層 147 は、めっき法により導電性部材 142 を形成する場合に反応を促進するシードメタルを含んでよい。

10

【0033】

絶縁層 148 は、開口 115 の内部に形成され、導電性部材 142 および金属層 147 と、Si 基板 112、絶縁層 114 および素子領域 124 とを絶縁する。絶縁層 148 として、SiO<sub>2</sub> を用いてよい。絶縁層 148 は、例えば、CVD 法により形成できる。

【0034】

なお、本実施形態において、導電性部材 142 と素子領域 124 とが、素子領域 124 の上に形成された電極パッド 144 を介して接触する場合について説明したが、導電性部材 142 と素子領域 124 との接触方法は、これに限定されない。例えば、導電性部材 142 は、素子領域 124 と直接接触してよい。また、本実施形態において、導電性部材 142 が、リセス部 125 において素子領域 124 と接触する場合について説明したが、導電性部材 142 と素子領域 124 との接触方法は、これに限定されない。例えば、導電性部材 142 は、チャネル領域 134 が形成される領域において、裏面 105 側から素子領域 124 に接触してよい。

20

【0035】

また、本実施形態において、導電性部材 142 と素子領域 124 とを電気的に結合する電極パッド 144 が PMOS 型トランジスタ 130 を構成する部材が形成されるより前に形成される場合について説明したが、導電性部材 142 と素子領域 124 とを電気的に結合する部材は、これに限定されない。例えば、層間配線層 118 に形成された層間配線の一部を介して電気的に結合されてよい。この場合、上記層間配線は、PMOS 型トランジスタ 130 を構成する部材または PMOS 型トランジスタ 130 より後に形成される部材と同一の工程で形成されてよい。

30

【0036】

半導体素子 123 は、絶縁層 114 および素子分離領域 120 により、素子分離されてよい。半導体素子 123 は、第 1 半導体装置の一例であってよい。半導体素子 123 は、素子領域 126 と、リセス部 127 と、NMOS 型トランジスタ 150 と、層間配線 159 と、リセス部 127 と電気的に結合する貫通電極 140 とを含んでよい。NMOS 型トランジスタ 150 は、不純物領域 151 および不純物領域 152 と、チャネル領域 154 と、ゲート電極 156 と、ゲート絶縁膜 158 とを有してよい。

【0037】

半導体素子 123 は、貫通電極 140 を介して電気的に結合された半導体装置 106 により、素子領域 126 の電位を制御される。これにより、素子領域 126 に形成された NMOS 型トランジスタ 150 の閾値電圧を動的に制御できる。例えば、NMOS 型トランジスタ 150 の待機時には閾値電圧を高くすることで、オフ電流を抑制できる。一方、NMOS 型トランジスタ 150 の動作時には閾値電圧を低くすることで、オン電流を増加させることができる。また、半導体素子 123 と、素子領域 126 の電位を制御する半導体装置 106 とが異なる基板に形成されているので、半導体素子 123 と半導体装置 106 とを、それぞれに最適なプロセスで製造することができる。

40

【0038】

素子領域 126 は、半導体素子 121 の素子領域 124 に対応する。素子領域 126 には、リセス部 127、NMOS 型トランジスタ 150 および貫通電極 140 が形成される

50

。素子領域 126 は、ボディ領域の一例であってよい。素子領域 126 は、単結晶シリコンを含んでよい。素子領域 126 は、絶縁層 114 の Si 基板 112 に接する面と反対側の面に接する単結晶シリコン層に形成されてよい。上記単結晶シリコン層は、SOI 基板の SOI 層であってよい。素子領域 126 は、上記単結晶シリコン層において、周囲を素子分離領域 120 に囲まれてよい。本実施形態において、素子領域 126 には NMOS 型トランジスタ 150 が形成されるので、素子領域 126 には、A1、B 等の P 型の不純物がドープされてよい。

#### 【0039】

リセス部 127 は、半導体素子 121 のリセス部 125 に対応する。リセス部 127 は素子領域 126 の一部に形成され、リセス部 127 における素子領域 126 の厚さは、不純物領域 151、不純物領域 152 およびチャネル領域 154 が形成される領域における素子領域 126 の厚さより薄い。リセス部 127 は、例えば、エッティングにより形成できる。

10

#### 【0040】

本実施形態において、基板 104 には複数の開口 115 が形成され、開口 115 の一つは、Si 基板 112 および絶縁層 114 だけでなく、リセス部 127 の一部をも貫通する。図 1 に示すとおり、上記の開口 115 は、リセス部 127 の貫通電極 140 が形成される領域を、裏面 105 側から表面 103 側に向かって貫通する。

#### 【0041】

NMOS 型トランジスタ 150 は、半導体素子 121 の PMOS 型トランジスタ 130 に対応する。NMOS 型トランジスタ 150 は、素子領域 126 に形成される。NMOS 型トランジスタ 150 は、ボディ領域に形成されるトランジスタの一例であってよい。不純物領域 151 および不純物領域 152 は、それぞれ、MOS 型トランジスタのドレイン領域およびソース領域であってよい。不純物領域 151 および不純物領域 152 の厚さは、素子領域 126 の厚さと同等であってよい。不純物領域 151 および不純物領域 152 は、例えば、P、As、Sb 等の N 型の不純物をドープすることで形成できる。

20

#### 【0042】

ゲート電極 156 は、素子領域 126 の上に形成される。ゲート電極 156 は、少なくとも、不純物領域 151 および不純物領域 152 に挟まれたチャネル領域 154 の上に形成され、チャネル領域 154 に電位または電流の作用を及ぼす。例えば、ゲート電極 156 は電圧を印加され、チャネル領域 154 の電流を制御する。図中の点線は、ゲート電極 156 に所定の電圧が印加された場合におけるチャネル領域 154 の一例を示す。ゲート電極 156 は、ポリシリコンを含んでよく、W 等の金属を含んでもよい。ゲート電極 156 は、例えば、真空蒸着法、CVD 法により形成できる。

30

#### 【0043】

ゲート絶縁膜 158 は、素子領域 126 とゲート電極 156 とを絶縁する。ゲート絶縁膜 158 として、SiO<sub>2</sub> を用いてもよく、ZrO<sub>2</sub>、HfO<sub>2</sub>、Al<sub>2</sub>O<sub>3</sub> 等の高誘電率材料 (High-k 材料) を用いてもよい。ゲート絶縁膜 158 は、例えば、真空蒸着法、CVD 法により形成できる。

#### 【0044】

40

層間配線 159 は、半導体素子 121 の層間配線 139 に対応する。層間配線 159 は、PMOS 型トランジスタ 130 と、NMOS 型トランジスタ 150 等の他の電子素子とを電気的に結合する。層間配線 159 は、層間配線層 118 の内部で、多層に配されてよい。層間配線 159 は、A1 等の金属を含んでよい。層間配線 159 は、例えば、真空蒸着法、CVD 法により形成できる。層間配線 139、層間配線 159 等により、例えば、不純物領域 131 と不純物領域 151 とを電気的に結合して、不純物領域 132 を電源と電気的に結合して、不純物領域 152 を接地することで、PMOS 型トランジスタ 130 および NMOS 型トランジスタ 150 を含む CMOS を形成できる。

#### 【0045】

半導体素子 123 は、半導体素子 121 と同様の貫通電極 140 を有する。半導体素子

50

123の貫通電極140は、半導体素子121の貫通電極140と同様に、半導体素子123の素子領域126と、基板104の裏面105に形成されるバンプ電極146とを電気的に結合する。半導体素子121の場合と同様に、リセス部127の一部において、素子領域126の上に電極パッド144が形成されてよい。電極パッド144は、導電性部材142と素子領域126とを電気的に結合する。

#### 【0046】

なお、半導体素子121の場合と同様に、導電性部材142は、素子領域126と直接接觸してよい。導電性部材142は、チャネル領域154が形成される領域において、裏面105側から素子領域126に接觸してよい。また、導電性部材142と素子領域126とが、層間配線層118に形成された層間配線の一部を介して電気的に結合されてよい。

10

#### 【0047】

以上、基板104に形成される半導体装置102について説明した。以上の説明によれば、単結晶シリコンのベース部と、ベース部の上の絶縁層と、絶縁層の上の単結晶シリコン層と、単結晶シリコン層に形成されるボディ領域と、ボディ領域に形成されるトランジスタと、少なくともベース部および絶縁層を貫通して、ボディ領域に電気的に結合する貫通結合部とを有する半導体装置が開示される。

#### 【0048】

次に、基板108に形成される半導体装置106について説明する。半導体装置106は、貫通電極140または導電性部材142を介して、素子領域124および素子領域126の少なくとも一方の電位を制御してよい。これにより、素子領域124に形成されたPMOS型トランジスタ130および素子領域126に形成されたNMOS型トランジスタ150の少なくとも一方の閾値電圧を動的に制御できる。また、半導体装置102と、半導体装置106とが異なる基板に形成されているので、半導体装置102と半導体装置106とを、それぞれに最適なプロセスで製造することができる。

20

#### 【0049】

図1に示すとおり、半導体装置106は、Si基板162と、絶縁層164と、SOI層166と、層間配線層168とを有してよい。半導体装置106は、貫通電極170および貫通電極180と、半導体素子192と、層間配線194および層間配線196とを有してよい。半導体装置106は、基板108の表面107側に表面保護層169を有してよく、基板108の裏面109側に裏面保護層161を有してよい。

30

#### 【0050】

Si基板162、絶縁層164、SOI層166および層間配線層168には、これらを貫通する開口165が形成されてよい。裏面保護層161には、裏面保護層161を貫通する開口163が形成されてよい。開口163および開口165は、例えば、エッチング、レーザー加工により形成できる。

#### 【0051】

Si基板162は、単結晶シリコンを含んでよい。Si基板162は、Si基板であってもよく、SOI基板の一部であってもよい。絶縁層164は、Si基板162の上に形成される。絶縁層164は、Si基板162の一方の面に接してよい。絶縁層164は、 $SiO_2$ 等の酸化膜であってよい。絶縁層164は、SOI基板の一部であってよい。SOI層166は、絶縁層164の上に形成される。SOI層166は、絶縁層164のSi基板162に接する面と反対側の面に接してよい。SOI層166は、単結晶シリコンを含んでよい。SOI層166は、SOI基板のSOI層であってよい。

40

#### 【0052】

層間配線層168は、内部に、電子素子間を電気的に結合する配線が配される。層間配線194、層間配線196は、上記配線の一例であってよい。層間配線層168として、 $SiO_2$ を用いてもよく、 $SiCOH$ 等の低誘電率材料(Low-k材料)を用いてもよい。層間配線層168は、例えば、CVD法、塗布法により形成できる。裏面保護層161および表面保護層169は、半導体装置106を保護する。裏面保護層161および表

50

面保護層 169 として、ポリイミド等の絶縁性の材料を用いてよい。裏面保護層 161 および表面保護層 169 は、例えば、塗布法により形成できる。

【0053】

貫通電極 170 は、半導体素子 121 のバンプ電極 146 と接する。貫通電極 170 は、半導体素子 192 と半導体素子 121 とを電気的に結合する。貫通電極 170 は、外部接続部の一例であってよい。貫通電極 170 は、導電性部材 172 と、電極パッド 174 と、バンプ電極 176 と、金属層 177 と、絶縁層 178 とを有してよい。貫通電極 170 は、電極パッド 174 が層間配線層 168 の表面 107 側の面に形成される点で貫通電極 140 と相違する。貫通電極 170 は、導電性部材 172、金属層 177 および絶縁層 178 が Si 基板 162、絶縁層 164、SOI 層 166 および層間配線層 168 を貫通する開口 165 の内部に形成される点で貫通電極 140 と相違する。

10

【0054】

貫通電極 170 は、上記相違点以外の構成については、貫通電極 140 と同様の構成を有してよい。即ち、導電性部材 172、電極パッド 174、バンプ電極 176、金属層 177 および絶縁層 178 は、それぞれ、導電性部材 142、電極パッド 144、バンプ電極 146、金属層 147 および絶縁層 148 と同様の構成を有してよい。なお、本実施形態において、電極パッド 174 は、層間配線層 168 に形成された層間配線 194 を介して、半導体素子 192 と電気的に結合されてよい。

【0055】

貫通電極 180 は、半導体素子 123 のバンプ電極 146 と接する。貫通電極 180 は、半導体素子 192 と半導体素子 123 とを電気的に結合する。貫通電極 180 は、外部接続部の一例であってよい。貫通電極 180 は、導電性部材 182 と、電極パッド 184 と、バンプ電極 186 と、金属層 187 と、絶縁層 188 とを有してよい。貫通電極 180 は、電極パッド 184 が層間配線層 168 の表面 107 側の面に形成される点で貫通電極 140 と相違する。貫通電極 180 は、導電性部材 182、金属層 187 および絶縁層 188 が Si 基板 162、絶縁層 164、SOI 層 166 および層間配線層 168 を貫通する開口 165 の内部に形成される点で貫通電極 140 と相違する。

20

【0056】

貫通電極 180 は、上記相違点以外の構成については、貫通電極 140 と同様の構成を有してよい。即ち、導電性部材 182、電極パッド 184、バンプ電極 186、金属層 187 および絶縁層 188 は、それぞれ、導電性部材 142、電極パッド 144、バンプ電極 146、金属層 147 および絶縁層 148 と同様の構成を有してよい。なお、本実施形態において、電極パッド 184 は、層間配線層 168 に形成された層間配線 196 を介して、半導体素子 192 と電気的に結合されてよい。

30

【0057】

半導体素子 192 は、貫通電極 140 または導電性部材 142 を介して、素子領域 124 および素子領域 126 の少なくとも一方の電位を制御してよい。半導体素子 192 は、第 2 半導体装置の一例であってよい。半導体素子 192 は、トランジスタ、または、トランジスタを含む集積回路であってよい。

【0058】

40

層間配線 194 および層間配線 196 は、半導体素子 192 と、他の電子素子とを電気的に結合する。層間配線 194 および層間配線 196 は、層間配線層 168 の内部で、多層に配されてよい。層間配線 194 および層間配線 196 は、A1 等の金属を含んでよい。層間配線 194 および層間配線 196 は、例えば、真空蒸着法、CVD 法により形成できる。

【0059】

なお、本実施形態において、半導体素子 192 が Si 基板 162、絶縁層 164 および SOI 層 166 を有する SOI 基板の SOI 層 166 に形成される場合について説明したが、半導体素子 192 はこれに限定されない。例えば、半導体素子 192 は、Si 基板に形成されてよい。

50

## 【0060】

本実施形態において、半導体素子192が、Si基板162、絶縁層164等を貫通する貫通電極170または貫通電極180を介して、半導体素子121または半導体素子123と電気的に結合される場合について説明したが、半導体素子192はこれに限定されない。例えば、基板104の裏面105と、基板108の表面107とが対向するように積層され、半導体素子192が基板108の表面107に形成されたバンプ電極を介して、半導体素子121または半導体素子123と電気的に結合されてもよい。

## 【0061】

また、本実施形態において、半導体装置102が半導体素子121および半導体素子123を含むCMOSを有する場合について説明したが、半導体装置102はこれに限定されない。例えば、半導体装置102は、半導体素子121、半導体素子123の何れか一方を有してもよく、半導体装置102は、より多くの電子素子を有してもよい。

10

## 【0062】

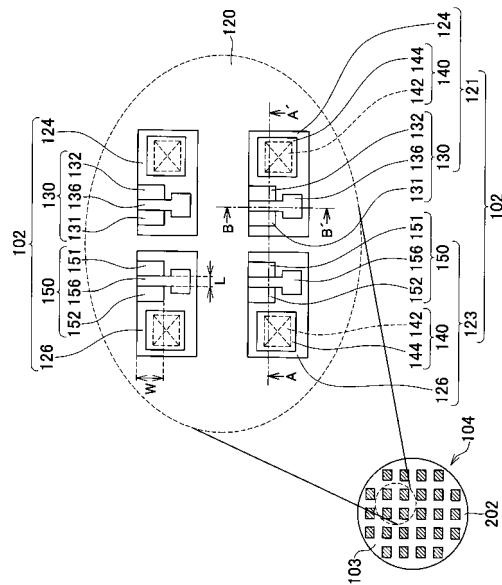

図2は、積層半導体装置100の製造に用いられる、基板104の平面図の一例を概略的に示す。図2は、基板104を表面103側から見た図を示す。説明を簡略化する目的で、図2では、層間配線層118、表面保護層119、層間配線139および層間配線159を省略している。また、図2は、基板104の点線部分を拡大した図面を合わせて示す。

## 【0063】

図2に示すとおり、基板104には、複数の半導体装置102が形成される。基板104は、ノッチ202を有する。ノッチ202は、例えば、基板104と基板108とを積層する場合に、位置合わせ用の指標として用いられる。なお、図1は、図2のA-A'断面を示す。

20

## 【0064】

図2の拡大図に示すとおり、素子領域124および素子領域126は、素子分離領域120に囲まれて、絶縁層114の上に長方形の島状に形成される。素子領域124および素子領域126には、それぞれ、チャネル幅L、チャネル長WのPMOS型トランジスタ130およびNMOS型トランジスタ150が形成される。素子領域124および素子領域126の、PMOS型トランジスタ130またはNMOS型トランジスタ150が形成されていない領域の一部には、貫通電極140が形成される。

30

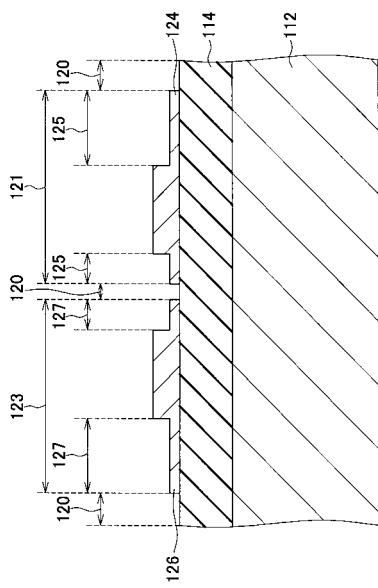

## 【0065】

図3は、積層半導体装置100の製造に用いられる、基板104の平面図の一例を概略的に示す。図3は、図2のB-B'断面を示す。図3に示すとおり、素子領域124は、素子分離領域120に囲まれて、絶縁層114の上に島状に形成される。素子領域124には、PMOS型トランジスタ130が形成される領域と、リセス部125とが形成される。リセス部125における素子領域124の厚さは、チャネル領域134が形成される領域における素子領域124の厚さより薄い。ゲート電極136のチャネル幅Wに対応する領域は、ゲート絶縁膜138を介してPMOS型トランジスタ130が形成される領域の上に形成され、ゲート電極136のチャネル幅Wに対応しない領域は、層間配線層118を介してリセス部125の上に形成される。

40

## 【0066】

図4から図13は、積層半導体装置100の製造過程における基板104の断面図の一例を示す。積層半導体装置100は、半導体装置102と、半導体装置106とを積層して形成される。積層半導体装置100は、例えば、以下の手順で製造できる。

## 【0067】

複数の半導体装置102が形成された基板104と、複数の半導体装置106が形成された基板108とを準備して、基板104と基板108とを積層する。基板104と基板108とは、半導体装置102の貫通電極140と、半導体装置106の貫通電極170または貫通電極180とが電気的に結合できるように位置合わせした後、押圧および加熱することで積層できる。貫通電極140と、貫通電極170または貫通電極180とは、

50

直接接触してもよく、導電性フィルムなどを介して電気的に結合してもよい。これにより、貫通電極 140 と、貫通電極 170 または貫通電極 180 とが接触するよう、半導体装置 102 と半導体装置 106 とを積層できる。

【0068】

積層された基板は、ダイシング等により個々の積層半導体装置 100 に分割される。これにより、半導体装置 102 および半導体装置 106 が積層された積層半導体装置 100 を製造できる。以下、図 4 から図 13 を用いて、基板 104 に半導体装置 102 を形成して半導体装置 102 を準備する方法の一例を説明する。

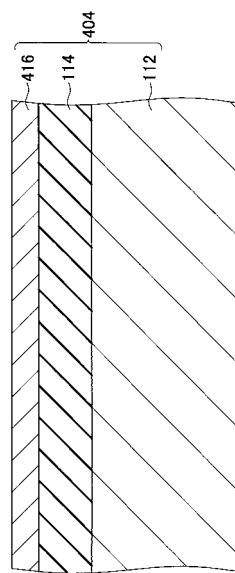

【0069】

図 4 は、積層半導体装置 100 の製造過程における基板 104 の断面図の一例を示す。図 4 に示すとおり、基板 104 となる SOI 基板 404 が準備される。SOI 基板 404 は、Si 基板 112、絶縁層 114、SOI 層 416 をこの順に備える。SOI 基板 404 は、市販の SOI 基板であってよい。SOI 層 416 は、絶縁層 114 の Si 基板 112 に接する面と反対側の面に接する単結晶シリコン層であってよい。

【0070】

図 5 は、積層半導体装置 100 の製造過程における基板 104 の断面図の一例を示す。図 5 に示すとおり、絶縁層 114 に達する素子分離領域 120 が SOI 層 416 に形成され、素子領域 124 および素子領域 126 が画定される。これにより、SOI 層 416 に形成され絶縁層 114 に達する素子分離領域 120 と、素子分離領域 120 で囲まれ单結晶シリコン層を含む素子領域 124 および素子領域 126 とが形成される。

【0071】

素子分離領域 120 は、例えば、エッチング等により SOI 層 416 をパターニングして、絶縁層 114 を露出させることで形成できる。これにより、絶縁層 114 の上に、素子分離領域 120 に囲まれた島状の素子領域 124 および素子領域 126 を形成できる。

【0072】

素子領域 124 は、P、As、Sb 等の N 型の不純物をドープされてよい。素子領域 126 は、Al、B 等の P 型の不純物をドープされてよい。不純物のドープは、例えば、イオン注入法により素子領域 124 および素子領域 126 に不純物を導入した後、熱処理することで実施できる。なお、熱処理は、不純物領域 131、不純物領域 132、不純物領域 151 または不純物領域 152 を熱処理する工程で実施されてよい。

【0073】

また、素子領域 124 の一部に、リセス部 125 が形成される。素子領域 126 の一部に、リセス部 127 が形成される。リセス部 125 およびリセス部 127 は、例えば、エッチング等により素子領域 124 および素子領域 126 をパターニングして、当該部分における素子領域 124 および素子領域 126 の厚さを薄くすることで形成できる。

【0074】

なお、本実施形態において、SOI 層 416 の一部をエッチングにより除去して、絶縁層 114 に達する溝を形成することで、素子分離領域 120 を形成する場合について説明した。しかし、素子分離領域 120 の形成方法は、これに限定されない。例えば、SOI 層 416 層の一部を酸化、窒化、または酸窒化して、絶縁層 114 に達する酸化シリコン、窒化シリコン、酸窒化シリコンを形成することで、素子分離領域 120 を形成してよい。

【0075】

図 6 は、積層半導体装置 100 の製造過程における基板 104 の断面図の一例を示す。図 6 に示すとおり、素子領域 124 のリセス部 125 の一部に電極パッド 144 が形成される。素子領域 126 のリセス部 127 の一部に別の電極パッド 144 が形成される。また、素子分離領域 120、リセス部 125 およびリセス部 127 の上に、絶縁層 618 が形成される。絶縁層 618 は、素子分離領域 120、リセス部 125 およびリセス部 127 の形成過程で除去された部分を充填するように形成されてよい。

【0076】

10

20

30

40

50

電極パッド 144 は、真空蒸着法等により W 等の金属薄膜を形成した後、エッチング等により当該金属薄膜をパターニングすることで形成できる。絶縁層 618 は、PMOS 型トランジスタ 130 および NMOS 型トランジスタ 150 を形成する領域をマスクで保護した後、CVD 法等により SiO<sub>2</sub> を形成して、CMP 法等により余計な SiO<sub>2</sub> を除去することで形成できる。PMOS 型トランジスタ 130 および NMOS 型トランジスタ 150 を形成する領域を保護するマスクは、除去してよい。

#### 【0077】

図 7 は、積層半導体装置 100 の製造過程における基板 104 の断面図の一例を示す。図 7 に示すとおり、素子領域 124 に、PMOS 型トランジスタ 130 を構成するゲート電極 136 およびゲート絶縁膜 138 が形成される。素子領域 126 に、NMOS 型トランジスタ 150 を構成するゲート電極 156 およびゲート絶縁膜 158 が形成される。ゲート電極 136、ゲート絶縁膜 138、ゲート電極 156 およびゲート絶縁膜 158 は、例えば、以下の手順で形成できる。

#### 【0078】

CVD 法等により、ゲート電極 136 およびゲート電極 156 となる SiO<sub>2</sub> 層を形成する。真空蒸着法等により、上記 SiO<sub>2</sub> 層の上に、ゲート絶縁膜 138 およびゲート絶縁膜 158 となる W 等の金属薄膜を形成する。エッチング等により、上記 SiO<sub>2</sub> 層および上記金属薄膜をパターニングすることで、ゲート電極 136、ゲート絶縁膜 138、ゲート電極 156 およびゲート絶縁膜 158 を形成できる。

#### 【0079】

図 8 は、積層半導体装置 100 の製造過程における基板 104 の断面図の一例を示す。図 7 に示すとおり、素子領域 124 に、PMOS 型トランジスタ 130 を構成する不純物領域 131 および不純物領域 132 が形成される。素子領域 126 に、NMOS 型トランジスタ 150 を構成する不純物領域 151 および不純物領域 152 が形成される。不純物領域 131 および不純物領域 132 は、例えば、A1、B 等の P 型の不純物をドープすることで形成できる。不純物領域 151 および不純物領域 152 は、例えば、P、As、Sb 等の N 型の不純物をドープすることで形成できる。

#### 【0080】

不純物のドープは、例えば、イオン注入法により素子領域 124 または素子領域 126 に不純物を導入した後、熱処理することで実施できる。このとき、不純物領域 131 および不純物領域 132 に挟まれた領域の上には、ゲート電極 136 およびゲート絶縁膜 138 が形成されているので、当該領域への不純物のドープが抑制される。また、リセス部 125 の上には、絶縁層 618 が形成されているので、リセス部 125 への不純物のドープが抑制される。同様に、不純物領域 151 および不純物領域 152 に挟まれた領域、および、リセス部 127 への不純物のドープが抑制される。以上により、素子領域 124 に PMOS 型トランジスタ 130 を形成できる。また、素子領域 126 に NMOS 型トランジスタ 150 を形成できる。

#### 【0081】

図 9 は、積層半導体装置 100 の製造過程における基板 104 の断面図の一例を示す。図 9 に示すとおり、PMOS 型トランジスタ 130、NMOS 型トランジスタ 150 および絶縁層 618 の上に、層間配線層 118、層間配線 139 および層間配線 159 が形成される。また、層間配線層 118 の上に、表面保護層 119 が形成される。

#### 【0082】

例えば、SiO<sub>2</sub> 層の形成と、A1 等の金属薄膜の形成および当該金属薄膜のパターニングとを繰り返すことで、層間配線 139 および層間配線 159 の形成された層間配線層 118 を形成できる。SiO<sub>2</sub> 層は、CVD 法等により形成できる。A1 等の金属薄膜は、真空蒸着法等により形成できる。表面保護層 119 は、塗布法等によりポリイミド膜等を形成することで、形成できる。

#### 【0083】

図 10 は、積層半導体装置 100 の製造過程における基板 104 の断面図の一例を示す

10

20

30

40

50

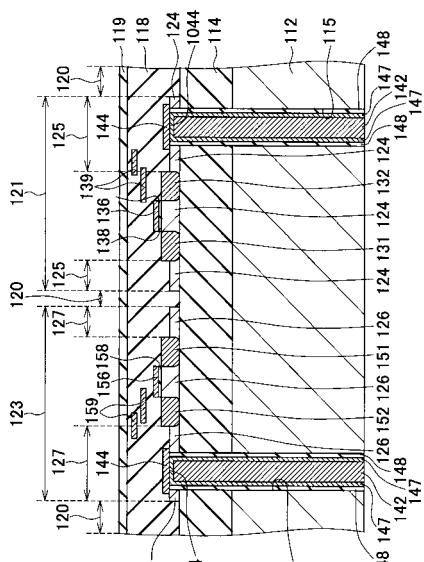

。図10に示すとおり、基板104に、2つの開口115が形成される。開口115は、少なくともSi基板112および絶縁層114を貫通する。一方の開口115は、素子領域124のリセス部125の一部を貫通して、電極パッド144の裏面1044を露出させる。他方の開口115は、素子領域126のリセス部125の一部を貫通して、電極パッド144の裏面1044を露出させる。また、開口115の内部に露出するSi基板112、絶縁層114および素子領域124を覆う絶縁層148が形成される。

【0084】

開口115は、例えば、反応性イオンエッティング等により、裏面105側から基板104をエッティングすることで形成できる。このとき、エッティングに用いるガスを切り替えながら、開口115を形成してよい。絶縁層148は、例えば、CVD法等により、開口115の内面にSiO<sub>2</sub>を形成して、エッティング等により開口115の底面のSiO<sub>2</sub>を除去することで形成できる。これにより、電極パッド144の裏面1044を露出できる。これにより、導電性部材142と、Si基板112、絶縁層114、素子領域124および素子領域126とを絶縁できる。

【0085】

図11は、積層半導体装置100の製造過程における基板104の断面図の一例を示す。図11に示すとおり、開口115の内部に、金属層147および導電性部材142が形成される。金属層147は、スパッタリング等によりTiN等のバリアメタルを形成して、その上に、めっき電極用のシード層として、無電解めっき法等によりCu薄膜を形成することで、形成できる。導電性部材142は、めっき法等により、開口115の内部にCuを充填することで形成できる。これにより、貫通電極140または導電性部材142が、直接または中間層を介して、素子領域124または素子領域126に接触するよう、貫通電極140または導電性部材142を形成できる。

【0086】

図12は、積層半導体装置100の製造過程における基板104の断面図の一例を示す。図12に示すとおり、基板104の裏面105側から、Si基板112を研削、研磨して、Si基板112を薄化してよい。即ち、PMOS型トランジスタ130およびNMOS型トランジスタ150が形成されていない側のSi基板112を薄化して、開口115の内部に充填した金属を露出させ、導電性部材142を形成してよい。これにより、Si基板112の厚みが、h<sub>0</sub>からh<sub>1</sub>になる。研削、研磨は、CMP法等により実施できる。なお、本実施形態において、導電性部材142を形成した後、Si基板112を薄化する場合について説明したが、薄化の順番はこれに限定されない。例えば、導電性部材142を形成する前に、Si基板112を薄化してよい。

【0087】

図13は、積層半導体装置100の製造過程における基板104の断面図の一例を示す。図13に示すとおり、薄化したSi基板112の裏面105側に、裏面保護層111が形成される。裏面保護層111は、塗布法等によりポリイミド膜を形成することで、形成できる。さらに、エッティング等により、裏面保護層111に開口113を形成した後、めっき法等によりバンプ電極146を形成することで、半導体装置102が形成された基板104を準備できる。このように準備された半導体装置102と、別途準備された基板108とを積層することで、積層半導体装置100を製造できる。

【0088】

なお、本実施形態において、PMOS型トランジスタ130およびNMOS型トランジスタ150を形成した後、開口115および導電性部材142を形成する場合について説明したが、開口115および導電性部材142の形成方法は、これに限定されない。例えば、PMOS型トランジスタ130およびNMOS型トランジスタ150を形成する前に、開口115および導電性部材142を形成してよい。このとき、導電性部材142として、ポリシリコン等の半導体を用いてよい。上記半導体には、不純物が高濃度にドープされてよい。

【0089】

10

20

30

40

50

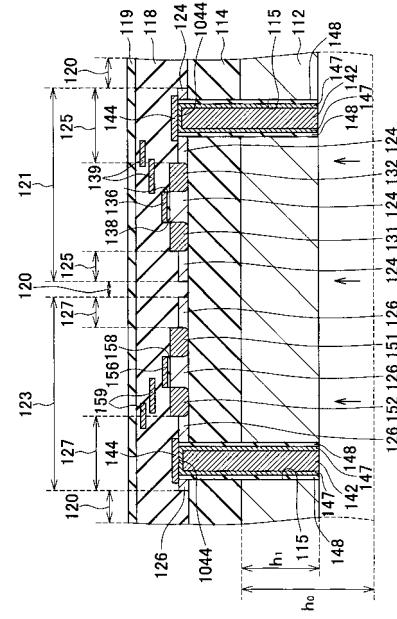

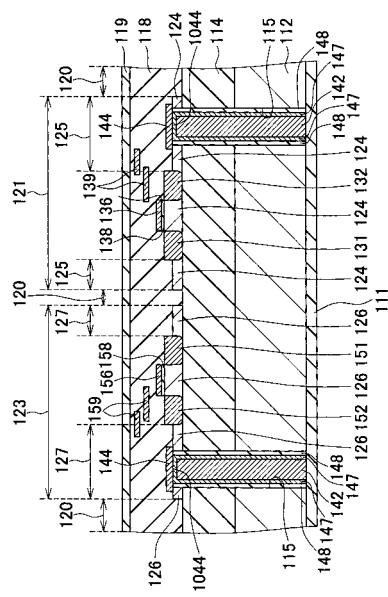

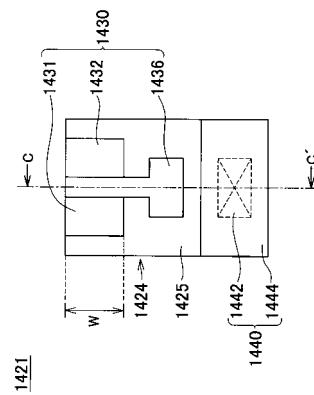

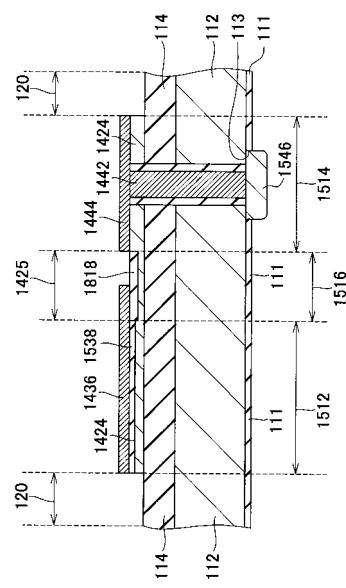

図14は、他の半導体素子1421の平面図の一例を概略的に示す。半導体素子1421は、第1半導体装置の一例であってよい。半導体素子1421は、半導体素子121の別の例であってよい。即ち、半導体素子121の代わりに素子領域1424を有する半導体装置102と、半導体装置106とを積層して、積層半導体装置100を形成してよい。以下、半導体素子1421を用いて、半導体素子121の別の構造、および、半導体素子121の別の製造方法について説明する。

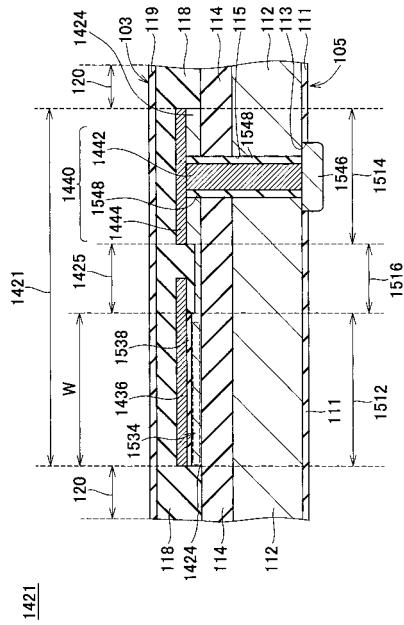

#### 【0090】

図15は、他の半導体素子1421の断面図の一例を概略的に示す。図15は、図14のC-C'断面を示す。図14および図15に示すとおり、半導体素子1421は、素子分離領域120に囲まれた素子領域1424と、素子領域1424に形成されるPMOS型トランジスタ1430および貫通電極1440とを備える。素子領域1424は、ボディ領域の一例であってよい。PMOS型トランジスタ1430は、ボディ領域に形成されるトランジスタの一例であってよい。貫通電極1440は、貫通結合部の一例であってよい。

10

#### 【0091】

素子領域1424には、部分分離溝1425が形成される。部分分離溝1425は、エッチング等により、素子領域1424の厚さを薄くすることで形成できる。PMOS型トランジスタ1430は、不純物領域1431および不純物領域1432と、チャネル領域1534と、ゲート電極1436と、ゲート絶縁膜1538とを有する。貫通電極1440は、導電性部材1442と、電極パッド1444と、バンプ電極1546と、絶縁層1548とを有する。

20

#### 【0092】

素子領域1424、部分分離溝1425、PMOS型トランジスタ1430および貫通電極1440は、素子領域124、リセス部125、PMOS型トランジスタ130および貫通電極140に対応して、同様の構成を有してよい。即ち、不純物領域1431、不純物領域1432、チャネル領域1534、ゲート電極1436およびゲート絶縁膜1538は、不純物領域131、不純物領域132、チャネル領域134、ゲート電極136およびゲート絶縁膜138に対応して、同様の構成を有してよい。導電性部材1442、電極パッド1444、バンプ電極1546、および絶縁層1548は、導電性部材142、電極パッド144、バンプ電極146および絶縁層148に対応して、同様の構成を有してよい。以下、半導体素子1421を構成する部材と、半導体素子121を構成する部材との相違点について説明する。なお、対応する部材と同様の構成については、説明を省略する場合がある。

30

#### 【0093】

素子領域1424は、部分分離溝1425により隔離される素子形成領域1512および電極形成領域1514と、素子形成領域1512および電極形成領域1514を電気的に結合する結合領域1516とを有する。素子形成領域1512には、PMOS型トランジスタ1430が形成される。電極形成領域1514には、貫通電極1440が形成される。

40

#### 【0094】

本実施形態において、ゲート電極1436および電極パッド1444は、同一の工程により形成されてよい。なお、電極パッド1444は、PMOS型トランジスタ1430より後に形成される部材と同一の工程で形成されてもよい。電極パッド1444は、PMOS型トランジスタ130を構成する部材またはPMOS型トランジスタ130より後に形成される部材と同一の工程で形成される配線の一例であってよい。

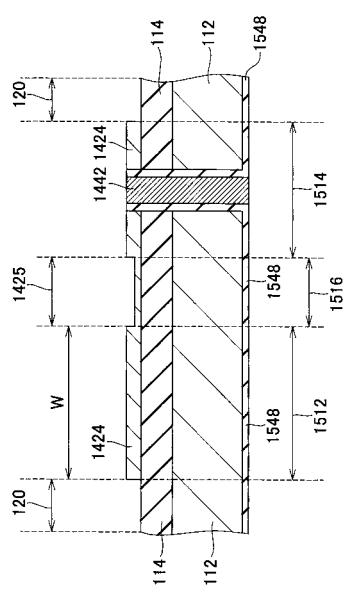

#### 【0095】

図16は、他の半導体素子1421の製造過程における断面図の一例を示す。図16に示すとおり、Si基板112、絶縁層114、SOI層1616をこの順に備えるSOI基板1604が準備される。SOI基板1604は、市販のSOI基板であってよい。SOI層1616は、絶縁層114のSi基板112に接する面と反対側の面に接する単結

50

晶シリコン層であってよい。

【0096】

SOI基板1604には、SOI基板1604を表面1603から裏面1605まで貫通する開口115が形成され、開口115の内部には、絶縁層1548および導電性部材1442が形成される。本実施形態において、PMOS型トランジスタ1430が形成される前に、SOI基板1604に、開口115および導電性部材1442が形成される点で、半導体素子121と相違する。また、開口115および導電性部材1442が形成される前に、Si基板112が薄化される点で、半導体素子121と相違する。開口115、導電性部材1442および絶縁層1548は、例えば、以下の手順により、形成できる。

10

【0097】

まず、CMP法等により、裏面1605側からSi基板112を研削、研磨して、Si基板112を薄化する。次に、反応性イオンエッティング等により、表面1603から裏面1605まで貫通する開口115を形成する。次に、CVD法等により、Si基板112の裏面1605側および開口115の内面にSiO<sub>2</sub>膜を形成して、絶縁層1548を形成する。その後、CVD法等により、開口115の内部にポリシリコン等の半導体を充填して、導電性部材1442を形成する。このとき、導電性部材1442には、不純物が高濃度にドープされてよい。

【0098】

なお、開口115は、表面1603側から形成されてもよく、裏面1605側から形成されてもよい。さらに、表面1603側と裏面1605側の両方から形成されてもよい。即ち、開口115は、少なくともベース部および絶縁層を貫通することとなる孔の一例であってよい。

20

【0099】

図17は、他の半導体素子1421の製造過程における断面図の一例を示す。図17に示すとおり、絶縁層114に達する素子分離領域120がSOI層1616に形成され、素子領域1424が画定される。これにより、SOI層1616に形成され絶縁層114に達する素子分離領域120と、素子分離領域120で囲まれ、単結晶シリコン層を含む素子領域1424が形成される。このとき、開口115に形成した導電性部材1442が直接または中間層を介して素子領域1424に接触するよう、素子領域1424を画定してよい。

30

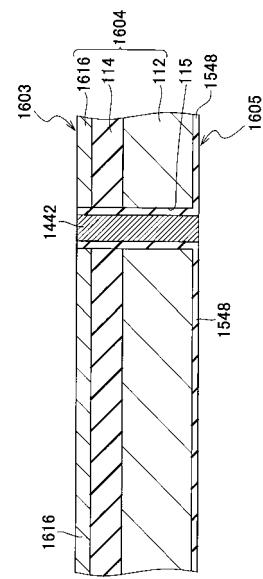

【0100】

また、PMOS型トランジスタ1430が形成される領域と、電極パッド1444が形成される領域とを隔離するように、部分分離溝1425が形成される。部分分離溝1425は、エッティング等により素子領域1424をパターニングして、当該部分における素子領域1424の厚さを薄くすることで形成できる。これにより、素子領域1424には、PMOS型トランジスタ1430が形成される素子形成領域1512と、電極パッド1444が形成される電極形成領域1514と、素子形成領域1512および電極形成領域1514を電気的に結合する結合領域1516が形成される。

40

【0101】

図18は、他の半導体素子1421の製造過程における断面図の一例を示す。図18に示すとおり、部分分離溝1425の上に、絶縁層1818が形成される。例えば、CVD法等によりSiO<sub>2</sub>を形成することで、絶縁層1818を形成できる。このとき、素子形成領域1512の上にもSiO<sub>2</sub>を形成してよい。素子形成領域1512の上に形成されたSiO<sub>2</sub>を、エッティング等によりパターニングすることで、ゲート絶縁膜1538を形成できる。上記パターニングは、ゲート電極1436を形成する工程で実施されてもよい。

【0102】

図18に示すとおり、素子形成領域1512の上にゲート電極1436が形成され、電極形成領域1514の上に電極パッド1444が形成される。ゲート電極1436および

50

電極パッド 1444 は、例えば、以下の手順で形成できる。まず、真空蒸着法等により、素子形成領域 1512 および電極形成領域 1514 の上に、ゲート電極 1436 および電極パッド 1444 となる W 等の金属薄膜を形成する。次に、エッチング等により、上記金属薄膜をパターニングする。以上の工程により、ゲート電極 1436 および電極パッド 1444 を形成できる。本実施形態においては、PMOS 型トランジスタ 1430 を構成する部材の形成工程において、電極パッド 1444 を同時に形成する。

#### 【0103】

図 18 に示すとおり、Si 基板 112 の裏面 1605 側に、裏面保護層 111 およびバンプ電極 1546 が形成される。Si 基板 112 の裏面 1605 側の面に形成された絶縁層 1548 を除去した後、例えば、塗布法によりポリイミド膜を形成することで、裏面保護層 111 を形成できる。また、エッチング等により裏面保護層 111 に開口 113 を形成した後、リフロー等により、開口 113 に Sn - Ag 合金、半田等を充填して、バンプ電極 1546 を形成できる。

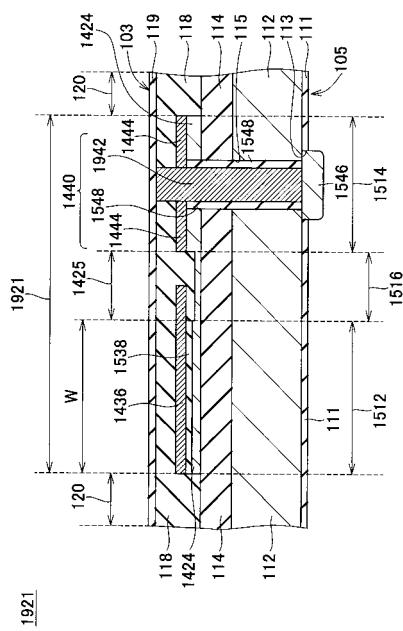

#### 【0104】

図 19 は、他の半導体素子 1921 の断面図の一例を概略的に示す。半導体素子 1921 は、半導体素子 121 および半導体素子 1421 の他の例であってよい。半導体素子 1921 は、第 1 半導体装置の一例であってよい。半導体素子 1921 は、導電性部材 1442 の代わりに、導電性部材 1942 を有する点で、半導体素子 1421 と相違する。図 19 に示すとおり、導電性部材 1942 は、電極パッド 1444 を貫通してよい。これにより、導電性部材 1942 と電極パッド 1444 とが、確実に接触できる。なお、その他の点については、半導体素子 1421 と同様の構成を有してよく、説明を省略する。

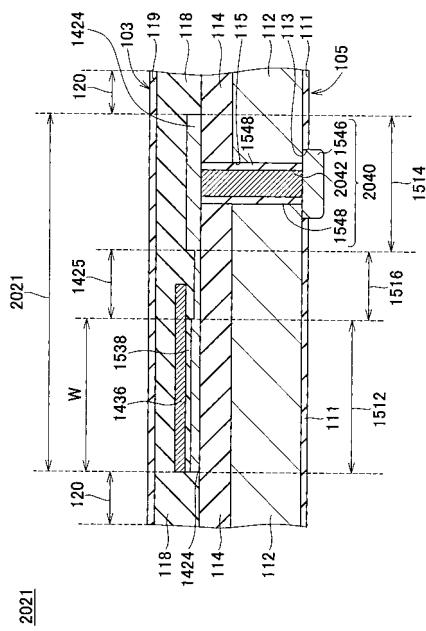

#### 【0105】

図 20 は、他の半導体素子 2021 の断面図の一例を概略的に示す。半導体素子 2021 は、半導体素子 121、半導体素子 1421 の他の例であってよい。半導体素子 2021 は、第 1 半導体装置の一例であってよい。半導体素子 2021 は、貫通電極 1440 の代わりに、貫通電極 2040 を有する点、および、貫通電極 2040 が電極パッド 1444 を有しない点で、半導体素子 1421 と相違する。図 20 に示すとおり、貫通電極 2040 は、導電性部材 2042 と、バンプ電極 1546 と、絶縁層 1548 とを有する。半導体素子 2021 において、導電性部材 2042 は、素子領域 1424 と直接接触する。なお、その他の点については、半導体素子 1421 と同様の構成を有してよく、説明を省略する。

#### 【0106】

以上、本発明を実施の形態を用いて説明したが、本発明の技術的範囲は上記実施の形態に記載の範囲には限定されない。上記実施の形態に、多様な変更または改良を加えることが可能であることが当業者に明らかである。その様な変更または改良を加えた形態も本発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。

#### 【0107】

特許請求の範囲、明細書、および図面中において示した装置、システム、プログラム、および方法における動作、手順、ステップ、および段階等の各処理の実行順序は、特段「より前に」、「先立って」等と明示しておらず、また、前の処理の出力を後の処理で用いるのでない限り、任意の順序で実現しうることに留意すべきである。特許請求の範囲、明細書、および図面中の動作フローに関して、便宜上「まず、」、「次に、」等を用いて説明したとしても、この順で実施することが必須であることを意味するものではない。

#### 【図面の簡単な説明】

#### 【0108】

【図 1】積層半導体装置 100 の断面図の一例を概略的に示す。

【図 2】積層半導体装置 100 の製造に用いられる基板 104 の平面図の一例を概略的に示す。

【図 3】積層半導体装置 100 の製造に用いられる基板 104 の平面図の一例を概略的に示す。

10

20

30

40

50

- 【図4】積層半導体装置100の製造過程における基板104の断面図の一例を示す。

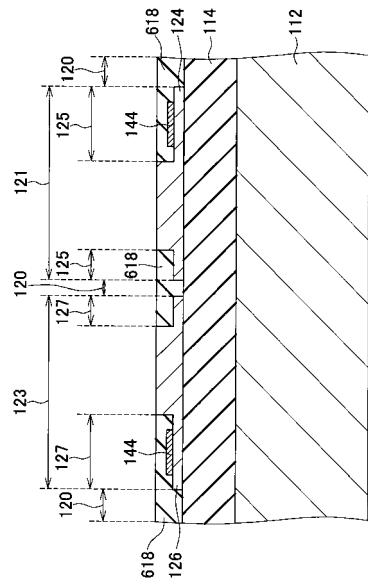

【図5】積層半導体装置100の製造過程における基板104の断面図の一例を示す。

【図6】積層半導体装置100の製造過程における基板104の断面図の一例を示す。

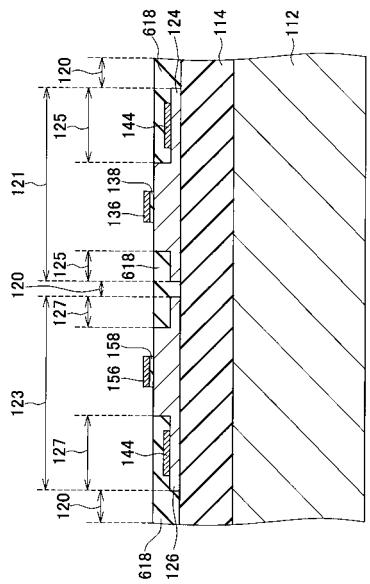

【図7】積層半導体装置100の製造過程における基板104の断面図の一例を示す。

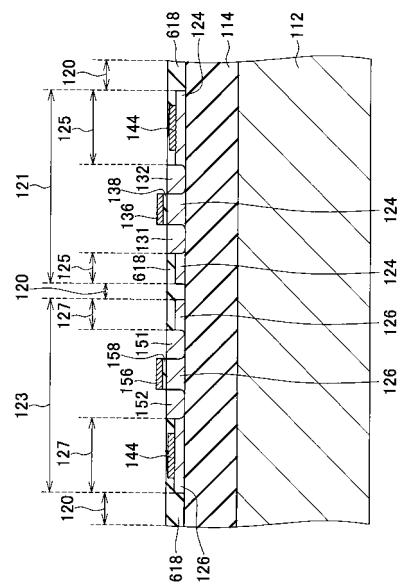

【図8】積層半導体装置100の製造過程における基板104の断面図の一例を示す。

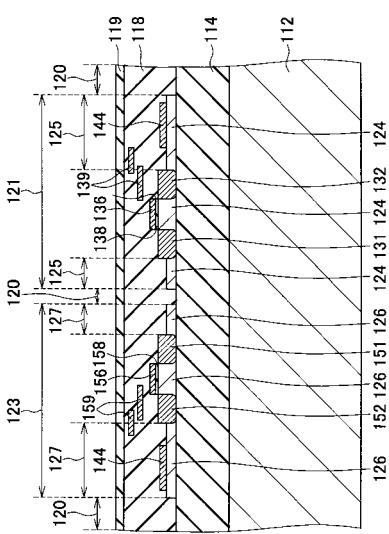

【図9】積層半導体装置100の製造過程における基板104断面図の一例を示す。

【図10】積層半導体装置100の製造過程における基板104断面図の一例を示す。

【図11】積層半導体装置100の製造過程における基板104断面図の一例を示す。

【図12】積層半導体装置100の製造過程における基板104断面図の一例を示す。

【図13】積層半導体装置100の製造過程における基板104断面図の一例を示す。

【図14】他の半導体素子1421の平面図の一例を概略的に示す。

【図15】他の半導体素子1421の断面図の一例を概略的に示す。

【図16】他の半導体素子1421の製造過程における断面図の一例を示す。

【図17】他の半導体素子1421の製造過程における断面図の一例を示す。

【図18】他の半導体素子1421の製造過程における断面図の一例を示す。

【図19】他の半導体素子1921の断面図の一例を概略的に示す。

【図20】他の半導体素子2021の断面図の一例を概略的に示す。

## 【符号の説明】

## 【0109】

|     |             |    |

|-----|-------------|----|

| 100 | 積層半導体装置     | 20 |

| 102 | 半導体装置       |    |

| 103 | 表面          |    |

| 104 | 基板          |    |

| 105 | 裏面          |    |

| 106 | 半導体装置       |    |

| 107 | 表面          |    |

| 108 | 基板          |    |

| 109 | 裏面          |    |

| 111 | 裏面保護層       |    |

| 112 | Si基板        | 30 |

| 113 | 開口          |    |

| 114 | 絶縁層         |    |

| 115 | 開口          |    |

| 118 | 層間配線層       |    |

| 119 | 表面保護層       |    |

| 120 | 素子分離領域      |    |

| 121 | 半導体素子       |    |

| 123 | 半導体素子       |    |

| 124 | 素子領域        |    |

| 125 | リセス部        | 40 |

| 126 | 素子領域        |    |

| 127 | リセス部        |    |

| 130 | PMOS型トランジスタ |    |

| 131 | 不純物領域       |    |

| 132 | 不純物領域       |    |

| 134 | チャネル領域      |    |

| 136 | ゲート電極       |    |

| 138 | ゲート絶縁膜      |    |

| 139 | 層間配線        |    |

| 140 | 貫通電極        | 50 |

|         |                 |    |

|---------|-----------------|----|

| 1 4 2   | 導電性部材           |    |

| 1 4 4   | 電極パッド           |    |

| 1 4 6   | バンプ電極           |    |

| 1 4 7   | 金属層             |    |

| 1 4 8   | 絶縁層             |    |

| 1 5 0   | N M O S 型トランジスタ |    |

| 1 5 1   | 不純物領域           |    |

| 1 5 2   | 不純物領域           |    |

| 1 5 4   | チャネル領域          |    |

| 1 5 6   | ゲート電極           | 10 |

| 1 5 8   | ゲート絶縁膜          |    |

| 1 5 9   | 層間配線            |    |

| 1 6 1   | 裏面保護層           |    |

| 1 6 2   | S i 基板          |    |

| 1 6 3   | 開口              |    |

| 1 6 4   | 絶縁層             |    |

| 1 6 5   | 開口              |    |

| 1 6 6   | S O I 層         |    |

| 1 6 8   | 層間配線層           |    |

| 1 6 9   | 表面保護層           | 20 |

| 1 7 0   | 貫通電極            |    |

| 1 7 2   | 導電性部材           |    |

| 1 7 4   | 電極パッド           |    |

| 1 7 6   | バンプ電極           |    |

| 1 7 7   | 金属層             |    |

| 1 7 8   | 絶縁層             |    |

| 1 8 0   | 貫通電極            |    |

| 1 8 2   | 導電性部材           |    |

| 1 8 4   | 電極パッド           |    |

| 1 8 6   | バンプ電極           | 30 |

| 1 8 7   | 金属層             |    |

| 1 8 8   | 絶縁層             |    |

| 1 9 2   | 半導体素子           |    |

| 1 9 4   | 層間配線            |    |

| 1 9 6   | 層間配線            |    |

| 2 0 2   | ノッチ             |    |

| 4 0 4   | S O I 基板        |    |

| 4 1 6   | S O I 層         |    |

| 6 1 8   | 絶縁層             |    |

| 1 0 4 4 | 裏面              | 40 |

| 1 4 2 1 | 半導体素子           |    |

| 1 4 2 4 | 素子領域            |    |

| 1 4 2 5 | 部分分離溝           |    |

| 1 4 3 0 | P M O S 型トランジスタ |    |

| 1 4 3 1 | 不純物領域           |    |

| 1 4 3 2 | 不純物領域           |    |

| 1 4 3 6 | ゲート電極           |    |

| 1 4 4 0 | 貫通電極            |    |

| 1 4 4 2 | 導電性部材           |    |

| 1 4 4 4 | 電極パッド           | 50 |

|         |          |

|---------|----------|

| 1 5 1 2 | 素子形成領域   |

| 1 5 1 4 | 電極形成領域   |

| 1 5 1 6 | 結合領域     |

| 1 5 3 4 | チャネル領域   |

| 1 5 3 8 | ゲート絶縁膜   |

| 1 5 4 6 | バンプ電極    |

| 1 5 4 8 | 絶縁層      |

| 1 6 0 3 | 表面       |

| 1 6 0 4 | S O I 基板 |

| 1 6 0 5 | 裏面       |

| 1 6 1 6 | S O I 層  |

| 1 8 1 8 | 絶縁層      |

| 1 9 2 1 | 半導体素子    |

| 1 9 4 2 | 導電性部材    |

| 2 0 2 1 | 半導体素子    |

| 2 0 4 0 | 貫通電極     |

| 2 0 4 2 | 導電性部材    |

【 义 1 】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 义 8 】

【図9】

【図10】

### 【図11】

【図12】

### 【図13】

【図14】

### 【図15】

### 【図17】

【図16】

【図18】

### 【図19】

【図20】

---

フロントページの続き

審査官 鈴木 聰一郎

(56)参考文献 国際公開第2006/019156 (WO, A1)

特開昭60-098654 (JP, A)

特開平08-125120 (JP, A)

特開2003-017708 (JP, A)

特開2002-026283 (JP, A)

特開2005-086157 (JP, A)

特開2001-230423 (JP, A)

特開2004-349537 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 21/822

H01L 21/8234 - 21/8238

H01L 21/8249

H01L 27/00

H01L 27/04

H01L 27/06

H01L 27/08

H01L 27/088 - 27/092

H01L 29/76

H01L 29/772

H01L 29/78 - 29/786