(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4702392号 (P4702392)

(45) 発行日 平成23年6月15日(2011.6.15)

(24) 登録日 平成23年3月18日 (2011.3.18)

(51) Int.Cl. F 1

**G 1 O H** 1/00 (2006.01) G 1 O H 1/00 C **G 1 O K** 15/12 (2006.01) G 1 O K 15/00 B

請求項の数 5 (全 17 頁)

(21) 出願番号

特願2008-116875 (P2008-116875)

(22) 出願日 (65) 公開番号 平成20年4月28日 (2008.4.28) 特開2009-265470 (P2009-265470A)

(43) 公開日 審査請求日 平成21年11月12日 (2009.11.12) 平成21年9月4日 (2009.9.4) ||(73)特許権者 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

|(74)代理人 100099715

弁理士 吉田 聡

|(72)発明者 仲江 哲一

東京都羽村市栄町3丁目2番1号 カシオ 計算機株式会社 羽村技術センター内

審査官 鈴木 聡一郎

最終頁に続く

(54) 【発明の名称】共鳴音発生装置および電子楽器

## (57)【特許請求の範囲】

### 【請求項1】

楽音信号データに付加するための共鳴音データを発生する共鳴音発生装置であって、 インパルス応答特性を表す時間軸上の値であるインパルス応答係数を含むインパルス応 答データを記憶するインパルス応答データ記憶手段と、

時間軸上の一連の楽音信号データと、前記インパルス応答データ記憶手段から読み出されたインパルス応答係数との積和演算をする積和演算手段であって、前記楽音信号データを、第1段から第(n-1)段までそれぞれ遅延させる遅延手段、インパルス応答係数と前記楽音信号データ或いは前記遅延手段から出力される遅延された楽音信号データとを乗算する乗算手段、および、前記乗算手段の出力を加算する加算手段を有する積和演算手段と、

10

前記積和演算手段の遅延手段における第1の所定の遅延出力を、前記積和演算手段に帰還させる帰還手段であって、前記遅延手段の第(n - 1)段の遅延出力を受け入れて、<u>所定の</u>乗算係数と乗算する乗算手段、および、前記積和演算手段における前記遅延手段の第 p 段(p < n - 1)の遅延出力と、前記帰還手段の乗算手段の乗算出力とを加算して、前記積和演算手段の第 p 段の乗算入力および第(p + 1)段への遅延入力とする加算手段を有する帰還手段と、を備え、

前記帰還手段が、当該帰還手段の加算手段に出力すべき、前記帰還手段の乗算手段の出力レベルを調整する第1のレベル調整手段と、前記帰還手段の加算手段に出力すべき、前記遅延回路からの遅延出力の出力レベルを調整する第2のレベル調整手段と、を有し、

前記積和演算手段が、前記第 p 段以降の乗算手段のインパルス応答係数を、前記第 1 のレベル調整手段および第 2 のレベル調整手段の前記レベル調整にしたがって調整する係数調整手段を有することを特徴とする共鳴音発生装置。

#### 【請求項2】

電子楽器に設けられたダンパペダルの踏み込み状態にしたがって、ダンパペダルの踏み込みが大きくなるのにしたがって、前記帰還手段の乗算手段の乗算係数が大きくなるように、前記乗算係数を制御する乗算係数制御手段を備えたことを特徴とする請求項1に記載の共鳴音発生装置。

## 【請求項3】

電子楽器に設けられた鍵盤の押鍵数に応じて、前記押鍵数が大きくなるのにしたがって、前記帰還手段の乗算手段の乗算係数が大きくなるように、前記乗算係数を制御する乗算係数制御手段を備えたことを特徴とする請求項1に記載の共鳴音発生装置。

### 【請求項4】

電子楽器に設けられたダンパペダルの踏み込み状態にしたがって、ダンパペダルの踏み込みが大きくなるのにしたがって、前記帰還手段の乗算手段の乗算係数が大きくなるように、前記乗算係数を制御するとともに、前記ダンパペダルが踏み込まれていないときに、前記電子楽器に設けられた鍵盤の押鍵数に応じて、前記押鍵数が大きくなるのにしたがって、前記帰還手段の乗算手段の乗算係数が大きくなるように、前記乗算係数を制御する乗算係数制御手段を備えたことを特徴とする請求項1に記載の共鳴音発生装置。

### 【請求項5】

請求項1に記載の共鳴音発生装置と、

鍵盤と

踏み込み状態を示す信号を出力するダンパペダルと、

前記鍵盤を構成する鍵のうち、押鍵された鍵の音高の楽音信号データを生成する発音手段と、

前記楽音信号データと前記共鳴音発生装置により発生された共鳴音データとを合成する合成手段と、を備えたことを特徴とする電子楽器。

【発明の詳細な説明】

# 【技術分野】

[0001]

本発明は、楽音信号の共鳴音を発生する共鳴音発生装置および共鳴音発生装置を備えた電子楽器に関する。

## 【背景技術】

[0002]

電子楽器にダンパペダルを接続し、ダンパペダルを踏み込むことにより、楽音を変更させるような技術が従前から知られている。特に、ダンパペダルの踏み込みに応答して、楽音信号データに基づく共鳴音データを発生し、発生した共鳴音データを楽音信号データに付加する共鳴音付加装置が提案されている。

### [0003]

上述した共鳴音付加装置は、ディジタルの楽音信号データを受け入れて、楽音信号データにディジタルフィルタによるフィルタ処理を施して共鳴音データを生成するのが一般的である。フィルタ処理においては、FIR(有限インパルス応答:Finite Impulse Response)フィルタ或いはIIR(無限インパルス応答:Infinite Impulse Response)フィルタが利用される。

## [0004]

FIRフィルタを利用する場合には、入力された楽音信号のデータ×(n-k)(k=0,1,2,・・・,n-1)と、音楽ホールの残響特性などから得たインパルス応答 a(k)を畳み込み演算することで、共鳴音のデータy(n)= ×(n-k)×a(k)を得ることができる。

## [0005]

10

20

30

40

特許文献 1 には、ペダルの踏み込み量にしたがって、楽音信号データのエンベロープを変更することで、特にハーフペダルのときの楽音を発生させることができる電子楽器が開示されている。

#### [0006]

特許文献 2 には、楽音波形に対応する波形データ S W D に基づいて共鳴音データ R W D を生成する共鳴音発生装置を備え、ダンパペダルの踏み込みに伴って、ダンパペダル踏み込み量の検知出力が最小値 0 から最大値 1 に向けていく過程において波形データ S W D が乗算器により振幅レベルが減少するように制御されるとともに、共鳴音発生装置からの共鳴音データ R W D が、乗算器により振幅レベルが増加するように制御されることが開示されている。

[0007]

特に、ピアノの共鳴音は複雑であり、ピアノの弦の共鳴音を生成するための技術が提案 されている。

[0008]

特許文献3には、音名ごとの倍音に相当する共振周波数を有するディジタルフィルタである複数の弦共鳴回路をグルーピングした弦共鳴回路群を有し、各弦共鳴回路の出力を畳み込み演算することでピアノの弦の共鳴音に類似する共鳴音を生成する技術が提案されている。

【特許文献1】特開平7-84574号公報

【特許文献2】特許第2692672号公報

【特許文献3】特開2007-193129号公報

【発明の開示】

【発明が解決しようとする課題】

[0009]

特許文献1のように、楽音信号データのエンベロープを変更するだけでは、ピアノのダンパペダルを踏み込んだときの残響音を含む共鳴音を、電子楽器で再現することができない。

[0010]

また、特許文献 2 に提案された技術においては、いわゆるクロスフェードにより共鳴音との混合比を変更しているが、共鳴音自体は変わらないため、ペダルの踏み込みに伴う共鳴音の変化に乏しいという問題点があった。

[0011]

また、特許文献 3 に提案された技術においては、鍵域ごとに複数の弦共鳴回路を備えるため、大規模な回路を要するという問題点があった。また、ピアノの構造を考慮した共鳴音の生成をしているわけではないため、回路規模が大きいにもかかわらず、十分に共鳴音を再現することができないという問題点があった。

[0012]

本発明は、適切な時間長の自然な共鳴音を発生させることができる共鳴音発生装置および当該共鳴音発生装置を備えた電子楽器を提供することを目的とする。

【課題を解決するための手段】

[0013]

本発明の目的は、楽音信号データに付加するための共鳴音データを発生する共鳴音発生装置であって、

インパルス応答特性を表す時間軸上の値であるインパルス応答係数を含むインパルス応答データを記憶するインパルス応答データ記憶手段と、

時間軸上の一連の楽音信号データと、前記インパルス応答データ記憶手段から読み出されたインパルス応答係数との積和演算をする積和演算手段であって、前記楽音信号データを、第1段から第(n-1)段までそれぞれ遅延させる遅延手段、インパルス応答係数と前記楽音信号データ或いは前記遅延手段から出力される遅延された楽音信号データとを乗算する乗算手段、および、前記乗算手段の出力を加算する加算手段を有する積和演算手段

10

20

30

40

(4)

٤,

前記積和演算手段の遅延手段における第1の所定の遅延出力を、前記積和演算手段に帰還させる帰還手段であって、前記遅延手段の第(n - 1)段の遅延出力を受け入れて、<u>所定の</u>乗算係数と乗算する乗算手段、および、前記積和演算手段における前記遅延手段の第p段(p < n - 1)の遅延出力と、前記帰還手段の乗算手段の乗算出力とを加算して、前記積和演算手段の第p段の乗算入力および第(p + 1)段への遅延入力とする加算手段を有する帰還手段と、を備え、

前記帰還手段が、当該帰還手段の加算手段に出力すべき、前記帰還手段の乗算手段の出力レベルを調整する第1のレベル調整手段と、前記帰還手段の加算手段に出力すべき、前記遅延回路からの遅延出力の出力レベルを調整する第2のレベル調整手段と、を有し、

前記積和演算手段が、前記第 p 段以降の乗算手段のインパルス応答係数を、前記第 1 のレベル調整手段および第 2 のレベル調整手段の前記レベル調整にしたがって調整する係数調整手段を有することを特徴とする共鳴音発生装置により達成される。

## [0019]

別の好ましい実施態様においては、電子楽器に設けられたダンパペダルの踏み込み状態にしたがって、ダンパペダルの踏み込みが大きくなるのにしたがって、前記帰還手段の乗算手段の乗算係数が大きくなるように、前記乗算係数を制御する乗算係数制御手段を備える。

### [0020]

さらに別の好ましい実施態様においては、電子楽器に設けられた鍵盤の押鍵数に応じて、前記押鍵数が大きくなるのにしたがって、前記帰還手段の乗算手段の乗算係数が大きくなるように、前記乗算係数を制御する乗算係数制御手段を備える。

### [0021]

また、好ましい実施態様においては、電子楽器に設けられたダンパペダルの踏み込み状態にしたがって、ダンパペダルの踏み込みが大きくなるのにしたがって、前記帰還手段の乗算手段の乗算係数が大きくなるように、前記乗算係数を制御するとともに、前記ダンパペダルが踏み込まれていないときに、前記電子楽器に設けられた鍵盤の押鍵数に応じて、前記押鍵数が大きくなるのにしたがって、前記帰還手段の乗算手段の乗算係数が大きくなるように、前記乗算係数を制御する乗算係数制御手段を備える。

## [0022]

また、本発明の目的は、上記共鳴音発生装置と、

#### 鍵般と

踏み込み状態を示す信号を出力するダンパペダルと、

前記鍵盤を構成する鍵のうち、押鍵された鍵の音高の楽音信号データを生成する発音手段と、

前記楽音信号データと前記共鳴音発生装置により発生された共鳴音データとを合成する合成手段と、を備えたことを特徴とする電子楽器により達成される。

### 【発明の効果】

### [0023]

本発明によれば、適切な時間長の自然な共鳴音を発生させることができる共鳴音発生装置および当該共鳴音発生装置を備えた電子楽器を提供することが可能となる。

#### 【発明を実施するための最良の形態】

### [0024]

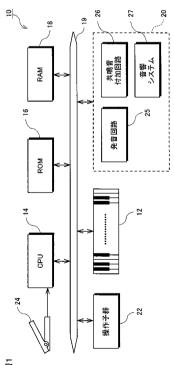

以下、添付図面を参照して、本発明の第1の実施の形態について説明する。図1は、本 発明の第1の実施の形態にかかる電子楽器の構成を示すブロックダイヤグラムである。

## [0025]

図1に示すように、本実施の形態にかかる電子楽器10は、鍵盤12、CPU14、ROM16、RAM18、楽音生成部20、操作子群22、ダンパペダル24を有する。鍵盤12、CPU14、ROM16、RAM18、楽音生成部20および操作子群22は、バス19を介して接続される。楽音生成部20は、発音回路25、共鳴音付加回路26お

10

20

30

30

40

よび音響システム 2 7 を有する。本実施の形態にかかる電子楽器 1 0 は、ピアノ音色、ヴァイオリン音色、ギター音色など種々の楽音を生成することができる。

#### [0026]

鍵盤12は、演奏者の押鍵操作に応じて、押鍵された鍵を特定する情報および押鍵された鍵のベロシティを示す情報をCPU14に伝達することができる。

### [0027]

CPU14は、電子楽器全体の制御、押鍵された鍵に応じた音高の楽音を生成するための楽音生成部20に与える種々の制御信号の生成などを実行する。ROM16は、プログラムや、プログラムの実行の際に使用される定数、楽音生成部20により生成される楽音信号データの基となる波形データ、共鳴音付加回路26にて用いられるインパルス応答データ記憶部31はROM16に設けられる。RAM18は、プログラムの実行の過程で生じるデータ、変数、パラメータなどを一時的に記憶する。

## [0028]

ダンパペダル24は、オン・オフのみではなくその中間の段階を示す信号を出力することができる。たとえば、本実施の形態においては、ダンパペダル24には縦方向(ペダルの回動軸と垂直方向)に2つのスイッチ(図示せず)が配置され、第1スイッチおよび第2スイッチの双方がオフの状態(ダンパペダル24が踏み込まれていない状態)、第1スイッチのみがオンされている状態(ダンパペダル24が途中まで踏み込まれている状態)、および、第1スイッチおよび第2スイッチの双方がオンされている状態(ダンパペダル24がフルに踏み込まれている状態)を作ることができる。このような構成により、2つのスイッチ双方がオンであるとフルペダル、第1スイッチのみがオンであるとハーフペダル、双方のスイッチがオフであると、ペダルのオフという3つの状態を作ることが可能となる。

### [0029]

或いは、ダンパペダル24の踏み込み量に応じて抵抗値が変更できる可変抵抗値を備え、抵抗値に応じた信号を出力するように構成しても良い。

#### [0030]

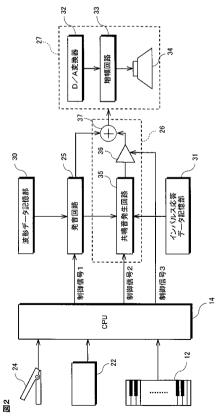

図2は、本実施の形態にかかる発音回路、共鳴音付加回路およびこれらに関連する構成部材の例を示すブロックダイヤグラムである。図1および図2に示すように、発音回路25は、CPU14から与えられた、発音すべき楽音の音色を示す音色情報、発音すべき音高を示す音高情報およびベロシティ情報を含む制御信号1に基づいて、波形データ記憶部30に記憶された波形データを読み出し、所定の音色で、かつ、所定音高の楽音信号データを出力する。

### [0031]

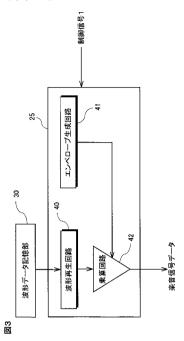

図3は、発音回路25および発音回路25に関連する構成部材をより詳細に示すブロックダイヤグラムである。図3に示すように、本実施の形態にかかる発音回路25は、波形再生回路40、エンベロープ生成回路41および乗算回路42を有する。波形データ記憶部30には、たとえば、ピアノ系、ヴァイオリン系、ギター系など種々の音色の波形データが記憶されている。

## [ 0 0 3 2 ]

波形再生回路40は、波形データ記憶部30に記憶された波形データから、制御信号1に含まれる音色情報にしたがって所定の種別の波形データを、制御信号1に含まれる音高情報にしたがって読み出す。また、エンベロープ生成回路41は、制御信号1に含まれるベロシティ情報にしたがったエンベロープデータを出力する。波形データとエンベロープデータとは、乗算回路42において乗算され、楽音信号データが出力される。なお、発音回路25から出力される楽音信号データは、単一の鍵を押鍵されたときの単一のデータだけではなく、複数の鍵が押鍵されているときには、押鍵された複数の鍵のそれぞれについて、楽音信号データが生成され、その合成データが出力される。

## [0033]

50

10

20

30

10

20

30

40

50

制御信号1に含まれる音高情報およびベロシティ情報は、鍵盤12からの信号に基づいて、CPU14により生成される。また、制御信号1に含まれる音色情報は、演奏者による操作子群22に含まれる操作子を操作した情報に基づいて、CPU14により生成される。

## [0034]

図2に示すように、共鳴音付加回路26は、共鳴音発生回路35、乗算回路36および加算回路37を有する。共鳴音発生回路35は、後述するように、帰還手段付きのFIRフィルタである。共鳴音発生回路35は、楽音信号データおよびインパルス応答データ記憶部31から読み出された、複数のインパルス応答係数を含むインパルス応答データに基づいて、畳み込み演算を実行して共鳴音データを生成する。生成された共鳴音データは、乗算回路36において制御信号3にしたがってレベル調整され、レベル調整された共鳴音データおよび楽音信号データは、加算回路37において加算される。

### [0035]

音響システム27は、D/A変換器32、増幅回路33およびスピーカ34を有し、加算回路37から出力された合成データをアナログ信号に変換して、アナログ信号を増幅し、スピーカから放音する。

### [0036]

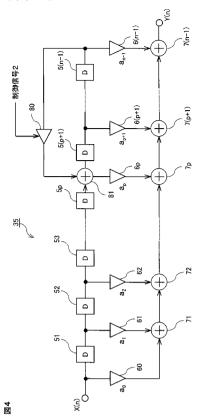

図4は、本実施の形態にかかる共鳴音発生回路の概略を示すプロックダイヤグラムである。図4に示すように、本実施の形態にかかる共鳴音発生回路35は、楽音信号データを遅延させる複数の遅延回路51~5(n-1)、楽音信号データ或いは遅延された楽音信号データと、インパルス応答係数 $a_0 \sim a_{n-1}$ とを、それぞれ乗算する乗算回路60~6(n-1)、乗算回路において乗算された結果を順次加算する加算回路71~7(n-1)、および、最終段(第(n-1)段)の遅延回路5(n-1)からの出力を受け入れて、制御信号2にしたがった乗算係数を用いて乗算する乗算回路80と、第p段および第(p+1)段の遅延回路5p、5(p+1)の間に配置され、遅延回路5pから出力された、遅延された楽音信号データと、乗算回路80の出力とを加算する加算回路81と、を有している。

### [0037]

本実施の形態にかかる共鳴音発生回路 35 では、入力された楽音信号データが、順次、遅延回路 51、52、・・・、5(n-1)によって遅延される。乗算回路 60、61、62、・・・、6p、6(p+1)、・・・、6(n-1)には、それぞれ、インパルス応答データを構成するインパルス応答係数  $a_0$ 、 $a_1$ 、 $a_2$ 、・・・、 $a_p$ 、 $a_{p+1}$ 、・・・、 $a_{n-1}$  が与えられる。乗算回路 60、61、・・・、6(n-1) においては、楽音信号データ或いは遅延された楽音信号データと、対応するインパルス応答係数とが乗算される。

### [0038]

乗算回路 6.0、6.1、・・・、6.00、6.10、・・・、6.00、6.10、・・・、6.00、6.00、毎算結果が、共鳴音データ 9.00、9.00 として出力される。すなわち、遅延回路 9.00、9.00 を 9.00 を 9

## [0039]

さらに、本実施の形態においては、乗算回路 8 0 が、最終段の(n-1)段だけ遅延された楽音信号データと、制御信号 2 にしたがった乗算係数とを乗算して、適切にレベル調整されたフィードバック波形データを生成する。フィードバック波形データは、第 p 段および第 (p+1) 段の遅延回路 5 p、 5 (p+1) の間に配置された加算回路 8 1 に出力される。したがって、加算回路 8 1 においては、遅延された楽音信号データと、フィードバック波形データとが加算され、第 (p+1) 段の遅延回路 5 (p+1) に出力される。したがって、第 (p+1) 段以降の乗算回路 6 (p+1)、6 (p+2)、・・・、6 (p+1) においては、フィードバック波形データが加算された、遅延された楽音信号データと、インパルス応答係数とが乗算される。

#### [0040]

図4に示すように、本実施の形態にかかる共鳴音発生回路35は、帰還回路(乗算回路80および加算回路81)を備えたnタップのFIRフィルタである。共鳴音発生回路35の遅延回路51~5(n・1)、乗算回路60~6(n・1)および加算回路71~7(n・1)が畳み込み演算回路を構成し、乗算回路80および加算回路81が帰還回路を構成する。たとえば、帰還回路を考慮しないタップ数nのFIRフィルタによって、1.8秒分の共鳴音を生成することができる。本実施の形態においては、1.8秒分のピアノ波形の波形データが、最長時間の波形データとして波形データ記憶部30に記憶されている。したがって、上記波形データの共鳴音が生成できるようにnタップ(1.8秒分)のインパルス応答係数を、インパルス応答データとしてインパルス応答データ記憶部31に格納している。したがって、帰還回路によるフィードバック波形の帰還を考慮しない場合には、発音開始から1.8秒の間、楽音信号データ、および、共鳴音データが合成されて出力されることになる。

## [0041]

楽音信号データおよび共鳴音データの合成データには、もとの波形データに含まれる弦鳴り音、箱鳴り音および弦共鳴音、および、共鳴音データにおいて再現された箱鳴り音や弦共鳴音が含まれる。しかしながら、実際のピアノ音では、微小ではあるが弦共鳴音が10秒以上、場合によっては数十秒にわたって響き続ける。したがって、1.8秒程度の共鳴音の再現では物足りない場合がある。

### [0042]

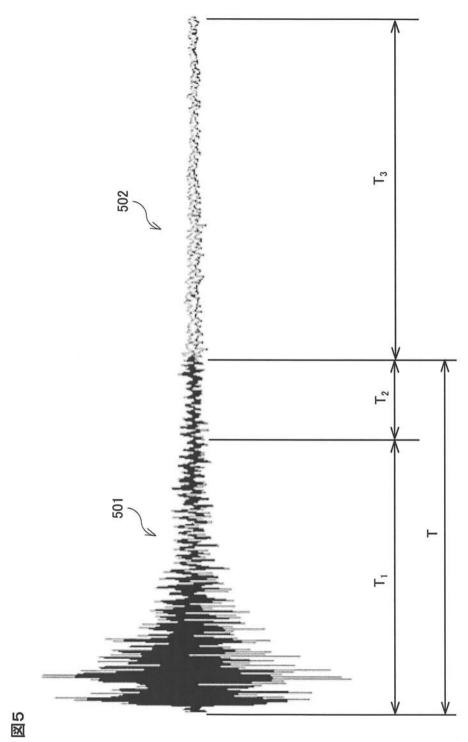

図 5 は、本実施の形態において生成される楽音信号データおよび共鳴音データの例を示す図である。図 5 において、時間Tが、ピアノ波形の楽音信号データの時間1.8 秒に相当する。上記ピアノ波形においては、最初の時間T $_1$ (=約1.6秒)においては、楽音が、主として箱鳴り音および弦共鳴音から構成され、残りの時間T $_2$ (=約0.2秒)においては、溪音が、主として弦共鳴音から構成されている。そこで、本実施の形態においては、図 5 に示す時間T $_2$ に相当する 0.2 秒分だけ、楽音信号データを帰還させている。つまり、第(p+1)段から第(n-1)段までのタップ数が、0.2 秒に相当する。これにより、帰還された波形データ(フィードバック波形データ)が楽音信号データと足し合わされ、第p+1段以降の乗算回路によって、インパルス応答係数と畳み込み演算され、畳み込み演算が繰り返される。

## [0043]

図 5 において、最初の時間 T に生成される波形 (符号 5 0 1 参照) に、時間 T  $_3$  だけ、フィードバック波形および楽音信号データを用いた畳み込み演算による波形 (符号 5 0 2 ) が付加される。この時間 T  $_3$  および波形 5 0 2 のレベルは、乗算回路 8 0 に与えられる制御信号 2 に基づいて制御される。

#### [0044]

本実施の形態にかかる電子楽器では、鍵盤12の押鍵に応答して、CPU14が、押鍵された鍵に応じた音高の楽音を生成するために制御信号1を生成し、発音回路25に出力して発音を指示する。発音回路25においては、波形再生回路40が、波形データ記憶部30に記憶された波形データから、制御信号1に含まれる音色情報にしたがって所定の種別の波形データを、制御信号1に含まれる音高情報にしたがって読み出す。また、エンベロープ生成回路41は、制御信号1に含まれるベロシティ情報にしたがったエンベロープデータを出力する。波形データとエンベロープデータとは、乗算回路42において乗算され、楽音信号データが出力される。

#### [0045]

また、CPU14は、ダンパペダル24の状態を検出し、ダンパペダルが、フルペダルの状態、ハーフペダルの状態、オフの状態のそれぞれに応じた制御信号1を生成することができる。さらに、本実施の形態においては、上記ダンパペダル24の状態に基づいて、共鳴音発生回路35の乗算回路40に与える制御信号2に含まれる乗算係数を算出している。

10

20

30

#### [0046]

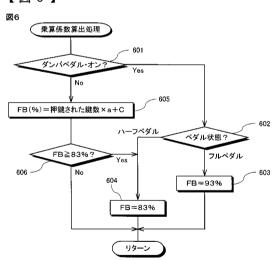

図6は、制御信号2に含まれる乗算係数算出処理の例を示すフローチャートである。図6の乗算係数算出処理は、CPU14により押鍵が検出され、CPU14が、発音回路25に対する制御信号1を生成する際に実行される。図6に示すように、CPU14は、ダンパペダル24がオンであるか否かを判断する(ステップ601)。ダンパペダル24がフルペダルの状態或いはハーフペダルの状態であれば、ダンパペダル24はオンであると判断される。ステップ601で4は、ペダル状態が、フルペダルであるかハーフペダルであるかを判断する(ステップ602)。ステップ602でフルペダルと判断された場合には、CPU14は、乗算係数FB=93%に設定する(ステップ603)。乗算係数FBは、制御信号2として乗算回路40に与えられ、また、RAM18の所定の領域に記憶される。ステップ602でハーフペダルと判断された場合には、CPU14は、乗算係数FB=83%に設定する(ステップ604)。上記乗算係数は、フルペダル、ハーフペダル何れの状態においても、発振を防止するために100%より小さい値としている。

### [0047]

その一方、ステップ601でNo、つまり、ダンパペダル24がオフ状態であるときには、CPU14は、FB(%)=押鍵された鍵数×a(係数)+C(定数)を算出する(ステップ605)。たとえば、係数a=8、定数C=30である。次いで、CPU14は、算出されたFBが、83%以上であるか否かを判断する(ステップ606)。ステップ606でYesと判断された場合には、CPU14は、乗算係数FB=83%に設定する(ステップ604)。ダンパペダルがオフ状態であるときは、基本的には、押鍵された鍵のみの弦共鳴音だけが発生する。したがって、最大でも、ハーフペダルのときの共鳴音と同程度のレベルおよび残響時間の残響音を再現するようにしている。

#### [0048]

本実施の形態においては、ダンパペダル24がオフ状態である場合には、押鍵数に応じて、フィードバック波形データのレベル、つまり、フィードバック量を規定する乗算係数を変化させ、一定レベルに達するまでは、押鍵数が大きくなるのにしたがって、乗算係数も増大させている。これにより、押鍵が多い方が、残響音のレベルおよび残響時間が大きくなることを再現することができる。

## [0049]

また、ダンパペダル 2 4 がオンされているときには、ペダル状態に応じて、それぞれ一定値の乗算係数を得ている。ダンパペダル 2 4 がオンされるときには、押鍵された鍵だけではなく、他の鍵の弦共鳴音も存在するからである。また、フルペダルの状態の乗算係数が、ハーフペダルの状態の乗算係数よりも大きくすることで、ペダル状態に応じたレベルおよび残響時間の残響音を再現することが可能である。

#### [0050]

上述したように算出された乗算係数は、共鳴音発生回路 3 5 の乗算回路 4 0 に与えられる。これにより、n タップの F I R フィルタの最終段(第(n-1)段)の遅延回路 5 (n-1)から出力された波形データと乗算係数とが乗算され、1以下の帰還量となったフィードバック波形データが帰還され、第(p+1)段以降の遅延回路 5 (p+1)、・・・により順次遅延されるとともに、第 p 段以降の乗算回路 6 p、6 (p+1)、・・・において、インパルス応答係数との畳み込み乗算が行われ、加算回路 7 1、7 2、・・・7 p、・・・において累算され、共鳴音データ Y (n)として出力される。

## [0051]

さらに、共鳴音発生回路35から出力された共鳴音データは、乗算回路35において、制御信号3に基づいてレベル調整され、加算回路37に出力される。加算回路37は、発音回路25から出力された楽音信号データと、共鳴音データとを加算して、音響システム27に出力する。

### [0052]

フィードバック波形のレベルは漸次減少するため、共鳴音データY(n)のレベルも漸

10

20

30

40

次減少して最終的にはほぼ「0」となる。レベルが「0」になるまでの時間は、上記乗算係数FBにしたがって変化する。本実施の形態においては、インパルス応答係数のうち、最後の時間 T2(図5参照)に相当する部分が、乗算係数だけ小さくなりながら、繰り返し、波形データと乗算されることになる。

### [0053]

本実施の形態によれば、積和演算回路からの第1の所定の遅延出力(最終段の遅延出力)を所定の乗算係数と乗算して、積和演算回路の第2の所定の遅延出力(第p段の遅延出力)と乗算出力とを加算して出力する。これにより、所定のレベルの楽音信号データを帰還させて、帰還された波形データ(フィードバック波形データ)と遅延された楽音信号データとが加算された波形データについて積和演算が実行される。これにより、楽音信号データの再生時間よりも長時間にわたって、自然な共鳴音を再生することが可能となる。

### [0054]

より詳細には、本実施の形態においては、積和演算回路の遅延遅延が、前記楽音信号データを、第1段から第(n-1)段までそれぞれ遅延させ、帰還回路の乗算回路80が、積和演算回路における第(n-1)段の遅延出力を受け入れて、乗算係数と乗算し、帰還回路の加算回路81が、積和演算回路における第p段(p<n-1)の遅延出力と、乗算回路80の乗算出力とを加算して、積和演算回路の第p段の乗算入力および第(p+1)段への遅延入力としている。このpを所望のように設定することで、帰還させる楽音信号データの時間長を調整することが可能となる。

## [0055]

また、本実施の形態においては、ダンパペダル24が踏み込まれているとき(オンされているとき)に、フルペダルの状態およびハーフペダルの状態が検出される。ダンパペダル24がフルペダルの状態のときが、ハーフペダルの状態のときよりも、帰還回路の乗算回路80に与える乗算係数が大きくなるように乗算係数が制御される。すなわち、フルペダルの状態の場合は、ハーフペダルの状態のときよりも共鳴音のレベルが大きく、かつ、残響時間も長くなる。これにより、実際の鍵盤楽器の演奏形態に沿った共鳴音を再現することが可能となる。

#### [0056]

また、本実施の形態においては、ダンパペダルが踏み込まれていないとき(オフであるとき)に、鍵盤12の押鍵数に応じて、押鍵数が大きくなるのにしたがって、帰還回路の乗算回路80の乗算係数が大きくなるように、乗算係数が制御される。これにより、押鍵数が多くなるのにしたがって、共鳴音のレベルが大きく、かつ、残響時間も長くなる。これにより、実際の鍵盤楽器の演奏形態に沿った共鳴音を再現することが可能となる。

### [0057]

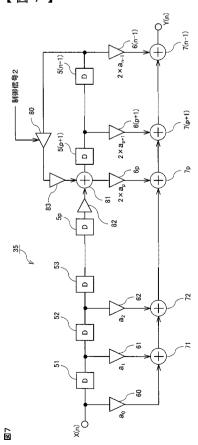

次に、本発明の第2の実施の形態について説明する。第2の実施の形態にかかる共鳴音発生回路35においては、遅延された楽音信号データとフィードバック波形データの加算によるオーバーフローを防止するように、それぞれのデータのレベルを調整する乗算回路が付加される。第2の実施の形態にかかる電子楽器の構成は、図1に示す第1の実施の形態と同様である。図7は、第2の実施の形態にかかる共鳴音発生回路の構成を示すブロックダイヤグラムである。図7において、図4に示す第1の実施の形態にかかる共鳴音発生回路と同様の構成部分には同様の符号を付している。

#### [0058]

図 7 に示すように、第 2 の実施の形態にかかる共鳴音発生回路は、第 (n-1) 段の遅延回路 5 (n-1) からの楽音信号データを制御信号 2 に基づく乗算係数で乗算する乗算回路 8 0 の出力を、1 / 2 とする乗算回路 8 3 と、第 p 段の遅延回路 5 p からの楽音信号データを、1 / 2 にする乗算回路 8 2 とを備えている。また、第 p 段から第 (n-1) 段の畳み込み演算を行う乗算回路 6 p 、6 (p+1) 、・・・、6 (n-1) は、それぞれ、遅延された楽音信号データと、対応するインパルス応答係数を 2 倍した係数  $(2 \times a_p \times 2 \times a_{(p+1)}$  、・・・、2  $\times a_{(p+1)}$  )とを乗算するように構成されている。

## [0059]

10

20

40

30

第2の実施の形態においては、乗算回路80から出力されたフィードバック波形データのレベルを1/2にするとともに、遅延回路5pから出力される楽音信号データのレベルも1/2とすることで、レベルが1/2となったフィードバック波形データおよび楽音信号データを加算して、オーバーフローが生じることを防止する。その一方、第p段以降の乗算回路では、インパルス応答係数の2倍の係数で乗算することで、上記加算された楽音信号データのレベルが1/2となったことを補償している。

### [0060]

なお、第2の実施の形態において、帰還回路の乗算回路82、83の乗算係数、および、積和演算回路の乗算回路6p、6(p+1)、・・・、6(n-1)の乗算係数は、CPU14によって制御され得る。上記第2の実施の形態では、乗算回路82、83の乗算係数は「1/2」、乗算回路6p、6(p+1)、・・・、6(n-1)の乗算係数は、それぞれのインパルス応答係数の2倍であるが、これに限られず、前者を、a(a<1)、後者をインパルス応答係数の「1/a」倍としても良い。

### [0061]

第2の実施の形態によれば、帰還回路の加算回路81に出力すべき乗算回路80の出力レベルが調整され、かつ、加算回路81に出力すべき第p段の遅延回路5pの出力レベルが調整される。また、このレベル調整にともなって、第p段以降の乗算回路のインパルス応答係数が、上記レベル調整にしたがって調整される。これにより、加算回路81におけるオーバーフローが防止されるとともに、第p段以降の畳み込み演算の出力レベルも適切に調整される。したがって、レベルが適切で自然な共鳴音の再現が可能となる。

### [0062]

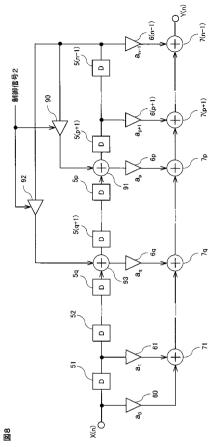

次に、本発明の第3の実施の形態について説明する。第3の実施の形態においては、フィードバック波形データを、第p段の遅延回路5pと第(p+1)段の遅延回路5(p+1)との間に帰還させるほか、フィードバック波形データを、第p段(a<p)の遅延回路5 q と第(a+1)段の遅延回路5(a+1)との間に帰還させることが可能となっている。なお、第3の実施の形態にかかる電子楽器の構成は、図1に示す第1の実施の形態と同様である。図8は、第3の実施の形態にかかる共鳴音発生回路の構成を示すブロックダイヤグラムである。図8において、図4に示す第1の実施の形態にかかる共鳴音発生回路と同様の構成部分には同様の符号を付している。

## [0063]

図8に示すように、第3の実施の形態にかかる共鳴音発生回路は、第(n-1)段の遅延回路5(n-1)からの楽音信号データを制御信号2に基づく第1の乗算係数で乗算する乗算回路90と、第p段の遅延回路5pの出力と、乗算回路90の出力とを加算する加算回路91と、第(n-1)段の遅延回路5(n-1)からの楽音信号データを制御信号2に基づく第2の乗算係数で乗算する乗算回路92と、第q段の遅延回路5qと第(q+1)段の遅延回路5(q+1)との間に配置され、第q段の遅延回路5qの出力と、乗算回路92の出力とを加算する加算回路93と、を有している。

## [0064]

第1の乗算係数および第2の乗算係数は、たとえば、一方の乗算係数が、図5の処理で算出されたFBであれば、他方の乗算係数が「0」となるように、CPU14により制御される。また、第3の実施の形態においては、たとえば、nタップのFIRフィルタによって1.8秒の共鳴音が生成され、かつ、第(p+1)段~第(n・1)段までのタップで0.2秒、第(a+1)段から第(n・1)段までのタップで0.4秒の共鳴音が生成されるように、p、gが設定される。

## [0065]

たとえば、第1の乗算係数をFB、第2の乗算係数を「0」とすることで、第1の実施の形態と同様のFIRフィルタとすることができる。その一方、第1の乗算係数を「0」、第2の乗算係数をFBとすることで、より長い0.4秒分の楽音信号データを帰還させることもできる。

20

10

30

40

#### [0066]

さらに、第3の実施の形態においては、CPU14が、第1の乗算係数を、 $t\times FB$ ( $t:0\sim1$ の間の所定の数)、第2の乗算係数を、 $(1-t)\times FB$ と算出して、乗算回路90、92にそれぞれ与えても良い。これにより、0.2秒分の楽音信号データの帰還および0.4秒分の楽音信号データの帰還の双方を、所望の割合にて実現することができる。

## [0067]

第3の実施の形態によれば、帰還回路において、2つのフィードバック波形の経路を設け、それぞれにおいて乗算回路において乗算係数を調整できる。したがって、フィードバック波形を帰還させる位置を切り換えることもできる。或いは、乗算係数を調整することで、それぞれの帰還経路を経た2つのフィードバック波形を帰還させることも可能である

[0068]

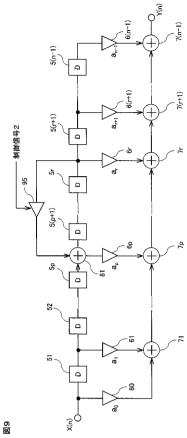

次に、本発明の第4の実施の形態について説明する。第1~第3の実施の形態においては、第(n-1)段の遅延回路5(n-1)の出力を帰還させて、乗算回路において乗算係数と乗算し、フィードバック波形データを生成した。第4の実施の形態では、第r段(r<n-1)の遅延回路5rの出力を帰還させている。つまり、タップ数nのFIRフィルタにおいて、最終段(第(n-1)段)の出力を帰還させずに、途中の出力を帰還させている。なお、第4の実施の形態にかかる電子楽器の構成は、図1に示す第1の実施の形態と同様である。図9は、第4の実施の形態にかかる共鳴音発生回路の構成を示すブロックダイヤグラムである。図9において、図4に示す第1の実施の形態にかかる共鳴音発生回路と同様の構成部分には同様の符号を付している。

[0069]

図9に示すように、第4の実施の形態にかかる共鳴音発生回路は、第r段(r < n - 1)の遅延回路5rの出力を受け入れて、制御信号2に含まれる乗算係数と乗算する乗算回路95と、第p段(p < r)の遅延回路5pと第(p + 1)段の遅延回路5(p + 1)との間に配置され、第p段(p < r)の遅延回路5pから出力された楽音信号データと、乗算回路95から出力されたフィードバック波形データとを加算する加算回路81とを有する。

[0070]

第4の実施の形態においては、(r - p)タップに相当する楽音信号データが帰還される。楽音信号データの長さ(時間)が、n タップに相当する時間より小さい場合には、第(n - 1)段の遅延回路の出力を帰還させることによりフィードバック波形データを生成すると、遅延された波形データが既に存在せず、畳み込み演算の出力は「0」となるのにもかかわらず、フィードバック波形データにより、畳み込み演算の出力が「0」以外の値となってしまう可能性があり、不自然な残響音が生成されるおそれがある。そこで、第4の実施の形態においては、楽音信号データの長さ(時間)と、r タップに相当する時間をほぼ一致させ、或いは、楽音信号データの長さが、r タップに相当する時間をように、楽音信号データを帰還させる第r 段を設定し、第r 段の遅延回路 5 r の出力を帰還させることで、不自然な残響音の発生を防止することができる。

[0071]

本発明は、以上の実施の形態に限定されることなく、特許請求の範囲に記載された発明 の範囲内で、種々の変更が可能であり、それらも本発明の範囲内に包含されるものである ことは言うまでもない。

[0072]

上記実施の形態において、共鳴音発生回路により構成されるFIRフィルタは、(n-1)個の遅延回路(たとえば、図4の遅延回路51~5(n-1))、n個の乗算回路(図4の乗算回路60~6(n-1))、および、(n-1)個の加算回路(図5の加算回路71~7(n-1))を含むように記載されている。しかしながら、実際には、上述した個数の遅延回路、乗算回路、加算回路は必要ではない。たとえば、パイプライン演算に

10

20

30

40

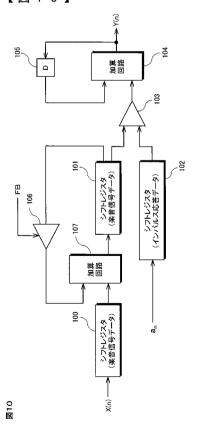

より、第1の実施の形態にかかる共鳴音発音回路は、図10に示すようなハードウェア構成をとることができる。

### [0073]

図10の例において、共鳴音発音回路は、楽音信号データをシフトさせるシフトレジスタ100、101、インパルス応答データをシフトさせるシフトレジスタ102、楽音信号データとインパルス応答データ中のインパルス応答係数をと乗算する乗算回路103と、加算回路104、遅延回路105を有する。シフトレジスタ100は、(p+1)段のシフトレジスタであり、(n-p+1)段のシフトレジスタである。上記シフトレジスタ100、101が、楽音信号データとでが積和演算回路を構成する。また、シフトレジスタ100、101が、楽音信号データを遅延させる遅延回路に相当し、また、乗算回路103が、楽音信号データ或いは遅延された楽音信号データと、対応するインパルス応答係数とを乗算する乗算回路に相当し、加算回路104および遅延回路105が、乗算結果を加算する加算回路に相当する。

## [0074]

また、図10の例において、共鳴音発生回路は、シフトレジスタ101の出力と乗算係数FBとを乗算する乗算回路106、および、楽音信号データと乗算回路106の乗算出力とを加算する加算回路107を備えている。これらが帰還回路を構成する。図10に示すような構成を採用することで、積和演算回路を少ないハードウェアで実現することができる。

## [0075]

また、前記第4の実施の形態において、第2の実施の形態のように、乗算回路95の出力レベルを調整する乗算回路を設けるとともに、遅延回路5pの出力レベルを調整する乗算回路を設け、かつ、第p段以降の乗算回路6p~6(n-1)の出力レベルも、上記レベル調整に伴って調整するように構成しても良い。第3の実施の形態においても同様である。

## [0076]

さらに、前記実施の形態においては、ダンパペダル24のオン状態として、フルペダルおよびハーフペダルという2つの状態を設け、ダンパペダル24がフルペダルの状態のときが、ハーフペダルの状態のときよりも、帰還回路の乗算回路80に与える乗算係数が大きくなるように乗算係数が制御される。しかしながら、このような構成に限定されるものではなく、たとえば、ダンパペダル24の踏み込み量に応じて抵抗値が変更できる可変抵抗値を備え、抵抗値に応じた信号を出力するように構成され、信号にしたがって、ダンパペダルの踏み込み量が大きくなるのにしたがって、帰還回路の乗算回路80に与える乗算係数が大きくなるように乗算係数が制御されても良い。

【図面の簡単な説明】

#### [0077]

【図1】図1は、本発明の第1の実施の形態にかかる電子楽器の構成を示すブロックダイ ヤグラムである。

【図2】図2は、本実施の形態にかかる発音回路、共鳴音付加回路およびこれらに関連する構成部材の例を示すブロックダイヤグラムである。

【図3】図3は、発音回路25および発音回路25に関連する構成部材をより詳細に示す ブロックダイヤグラムである。

【図4】図4は、本実施の形態にかかる共鳴音発生回路の概略を示すブロックダイヤグラムである。

【図5】図5は、本実施の形態において生成される楽音信号データおよび共鳴音データの 例を示す図である。

【図 6 】図 6 は、制御信号 2 に含まれる乗算係数算出処理の例を示すフローチャートである。

【図7】図7は、第2の実施の形態にかかる共鳴音発生回路の構成を示すブロックダイヤグラムである。

10

20

30

40

【図8】図8は、第3の実施の形態にかかる共鳴音発生回路の構成を示すブロックダイヤ グラムである。

【図9】図9は、第4の実施の形態にかかる共鳴音発生回路の構成を示すブロックダイヤ グラムである。

【図10】図10は、第1の実施の形態にかかる共鳴音発生回路のハードウェア構成例を 示す図である。

## 【符号の説明】

# [0078]

| _ |     | _           |      |   |

|---|-----|-------------|------|---|

|   | 1 ( | 0 電子楽器      |      |   |

|   | 1 2 | 2 鍵盤        | 10   | ) |

|   | 1 4 | 4 C P U     |      |   |

|   | 1 6 | 5 ROM       |      |   |

|   | 1 8 | R A M       |      |   |

|   | 2 ( | ) 楽音生成部     |      |   |

|   | 2 2 | 2 操作子群      |      |   |

|   | 2 4 | 4 ダンパペダル    |      |   |

|   | 2 5 | 5 発音回路      |      |   |

|   | 2 6 | 5 共鳴音付加回路   |      |   |

|   | 2 7 | 7 音響システム    |      |   |

|   | 3 ( | ひ 波形データ記憶部  | 20   | ) |

|   | 3 1 | 1 インパルス応答デー | 夕記憶部 |   |

|   | 3 5 | 5 共鳴音発生回路   |      |   |

|   | 3 6 | 5 乗算回路      |      |   |

|   | 3 7 | 7 加算回路      |      |   |

|   |     |             |      |   |

# 【図1】

# 【図2】

【図3】

【図4】

【図6】

【図7】

【図8】

【図9】

【図10】

【図5】

## フロントページの続き

## (56)参考文献 特開平09-090967(JP,A)

特表2005-534992(JP,A)

特開平09-026788(JP,A)

特開2005-338471(JP,A)

特開平05-188950(JP,A)

特開2005-308946(JP,A)

特開2008-065232(JP,A)

特開2001-128299(JP,A)

特開平06-250650(JP,A)

特開平06-242781 (JP,A)

# (58)調査した分野(Int.CI., DB名)

G10H 1/00- 7/12

G10K 15/00- 15/12