(10) **DE 10 2017 212 818 B4 2022.06.23**

(12)

## Patentschrift

(21) Aktenzeichen: **10 2017 212 818.6**

(51) Int Cl.: **H01L 29/861 (2006.01)**

(22) Anmelddatag: **26.07.2017**

**H01L 29/739 (2006.01)**

(43) Offenlegungstag: **29.03.2018**

(45) Veröffentlichungstag

der Patenterteilung: **23.06.2022**

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

**2016-186769 26.09.2016 JP**

(72) Erfinder:

**Fujii, Hidenori, Tokyo, JP**

(73) Patentinhaber:

**Mitsubishi Electric Corporation, Tokyo, JP**

(56) Ermittelter Stand der Technik:

|           |                         |           |

|-----------|-------------------------|-----------|

| <b>US</b> | <b>2015 / 0 132 895</b> | <b>A1</b> |

| <b>US</b> | <b>2016 / 0 211 258</b> | <b>A1</b> |

| <b>WO</b> | <b>2016/ 129 041</b>    | <b>A1</b> |

| <b>JP</b> | <b>2013- 110 373</b>    | <b>A</b>  |

| <b>JP</b> | <b>2010- 114 248</b>    | <b>A</b>  |

(74) Vertreter:

**Hoefer & Partner Patentanwälte mbB, 81543 München, DE**

(54) Bezeichnung: **Halbleiteranordnung**

(57) Hauptanspruch: Halbleiteranordnung, mit einer Mehrschichtstruktur aufweisend:

- eine erste Halbleiterschicht (3) eines ersten Leitfähigkeitsstyps;

- eine zweite Halbleiterschicht (4) eines zweiten Leitfähigkeitsstyps, die an einer Vorderseite der ersten Halbleiterschicht (3) ausgebildet ist;

- eine dritte Halbleiterschicht (7) des ersten Leitfähigkeitsstyps, die an einer Rückseite der ersten Halbleiterschicht (3) ausgebildet ist;

- eine vierte Halbleiterschicht (5) des ersten Leitfähigkeitsstyps und eine fünfte Halbleiterschicht (6) des zweiten Leitfähigkeitsstyps, die an einer Rückseite der dritten Halbleiterschicht (7) oder sowohl an der Rückseite der ersten Halbleiterschicht (3) als auch der dritten Halbleiterschicht (7) auf solche Art und Weise ausgebildet sind, dass die vierte Halbleiterschicht (5) und die fünfte Halbleiterschicht (6) in einer Draufsicht benachbart zueinander sind oder benachbarte Abschnitte der vierten Halbleiterschicht (5) und der fünften Halbleiterschicht (6) sich in einer Draufsicht gegenseitig überlagern;

- eine erste Elektrode (8), die eine Vorderseite der zweiten Halbleiterschicht (4) abdeckt; und

- eine zweite Elektrode (16), die eine Rückseite der vierten Halbleiterschicht (5) und der fünften Halbleiterschicht (6) abdeckt, und wobei:

- eine vertikale Position der vierten Halbleiterschicht (5) in der Mehrschichtstruktur und eine vertikale Position der fünften Halbleiterschicht (6) in der Mehrschichtstruktur sich voneinander unterscheiden,

- eine Dicke der ersten Halbleiterschicht (3) in der Mehr-

schichtstruktur, die die vierte Halbleiterschicht (5) aufweist, und eine Dicke der ersten Halbleiterschicht (3) in der Mehrschichtstruktur, die die fünfte Halbleiterschicht (6) aufweist, sich voneinander unterscheiden,

- die Mehrschichtstruktur des Weiteren eine dritte Elektrode (15) aufweist, die zwischen der vierten Halbleiterschicht (5) und der zweiten Elektrode (16) ausgebildet ist, und

- eine Differenz zwischen der Dicke der ersten Halbleiterschicht (3) in der Mehrschichtstruktur, die die vierte Halbleiterschicht (5) aufweist, und der Dicke der ersten Halbleiterschicht (3) in der Mehrschichtstruktur, die die fünfte Halbleiterschicht (6) aufweist, identisch ist mit einer Dicke, die erhalten wird durch Addieren eines Höhenunterschieds zwischen der vierten Halbleiterschicht (5) und der fünften Halbleiterschicht (6) zu einer Dicke der dritten Elektrode (15).

**Beschreibung**

Hintergrund der Erfindung

Gebiet der Erfindung

**[0001]** Die vorliegende Erfindung betrifft eine Halbleiteranordnung und insbesondere einen Rückseitenaufbau einer Leistungshalbleiteranordnung.

Stand der Technik

**[0002]** In letzter Zeit werden RFC (Relaxed Field of Cathode)-Dioden und rückwärtsleitende Bipolartransistoren mit isoliertem Gate (RC-IGBT) und dergleichen als Leistungshalbleiteranordnungen hergestellt. Aufgrund einer pn-Struktur an der Rückseite davon ermöglichen eine solche RFC-Diode und ein RC-IGBT die Steuerung und/oder Regelung von elektrischen Eigenschaften. Die hierin verwendete „pn-Struktur“ bezieht sich auf eine Beschaffenheit, bei der ein Bereich, in dem p-leitende Fremdstoffe ausgebildet sind, und ein Bereich, in dem n-leitende Fremdstoffe ausgebildet sind, in einer Draufsicht benachbart zueinander an einer Rückseite eines Halbleitersubstrats, das eine Leistungshalbleiteranordnung bildet, ausgebildet sind.

**[0003]** Wenn ein p-leitender Fremdstoffbereich und ein n-leitender Fremdstoffbereich durch Hochenergie-Implantieren oder hochdosiertem Implantieren ausgebildet werden, um eine pn-Struktur an der Rückseite einer Leistungshalbleiteranordnung zu bilden, verstärkt eine solche Implantierung eine Beschädigung an einem Halbleitersubstrat. Um dieses Problem zu lösen, kann ein stufenweises Fremdstoffkonzentrationsprofil bei Leistungshalbleiteranordnungen eingesetzt werden, bei dem die Rückseite eines Halbleitersubstrats, das Si aufweist, geschmolzen wird, um eine einheitliche Konzentration von Fremdstoffen in einem mit Fremdstoffen versehenen Bereich zu haben (vergleiche beispielsweise die Druckschrift JP 5 309 360 B2). Techniken zur Ausbildung einer Elektrode mit ohmschen Eigenschaften, die für eine p-Leitung und eine n-Leitung geeignet ist, an der gesamten Rückseite eines Halbleitersubstrats einer Leistungshalbleiteranordnung sind beispielsweise in den japanischen Patentanmeldungsoffenlegungen JP 2007- 184 486 A und JP 2015- 211 149 A offenbart.

**[0004]** Wenn die in der Druckschrift JP 5 309 360 B2 offenbare Technik auf eine Leistungshalbleiteranordnung angewendet wird, sind ein p-leitender Fremdstoffbereich und ein n-leitender Fremdstoffbereich allein in einem Bereich verbunden, der eine Tiefe aufweist, die gleich oder kleiner als 1 µm von der Rückseite des Halbleitersubstrats beträgt, um die Rückseite zu schmelzen. Dementsprechend ist es schwierig, die elektrischen Eigenschaften eines

pnp-Bereichs, der in dem p-leitenden Fremdstoffbereich ausgebildet ist, und die elektrischen Eigenschaften eines pn-Bereichs, der in dem n-leitenden Fremdstoffbereich ausgebildet ist, individuell zu steuern und/oder zu regeln. Mit anderen Worten ist es schwierig, einen Betrieb des pnp-Bereichs und einen Betrieb des pn-Bereichs individuell zu steuern und/oder zu regeln.

**[0005]** Gemäß den in den japanischen Patentanmeldungsoffenlegungen JP 2007- 184 486 A und JP 2015- 211 149 A offenbarten Techniken werden der p-leitende Fremdstoffbereich und der n-leitende Fremdstoffbereich bei einer flachen Tiefe miteinander verbunden, und die Tiefen davon sind im Wesentlichen dieselben. Dementsprechend ist es schwierig, Elektroden mit ohmschen Eigenschaften bereitzustellen, die für die p-Leitung und die n-Leitung jeweils an dem p-leitenden Fremdstoffbereich und dem n-leitenden Fremdstoffbereich geeignet sind.

**[0006]** Die US 2015 / 0 132 895 A1 beschreibt ein Verfahren zum Herstellen einer Halbleitervorrichtung. Die Halbleitervorrichtung weist einen Kathodenbereich der Diode, einen ersten Pufferbereich angrenzend an den Kathodenbereich an einer hinteren Oberflächenseite eines Halbleitersubstrats, einen Kollektorbereich des IGBT und einen zweiten Pufferbereich angrenzend an den Kollektorbereich an der Rückseite Oberflächenseite auf. Das Verfahren weist das Bilden des Stufenabschnitts auf der Vorderfläche, so dass der dünne Abschnitt und der dicke Abschnitt in dem Halbleitersubstrat gebildet werden, und das Injizieren von n-Störstellen in einen Bereich auf der Vorderfläche auf, der sich über die dünnen und dicken Abschnitte erstreckt, so dass die erste Pufferregion und die zweite Pufferregion gebildet werden.

**[0007]** Die US 2016 / 0 211 258 A1 betrifft rückwärtsleitende IGBTs, bei denen die Kollektorseite Diodenanschlussgebiete aufweist und das Halbleitermaterial durch die Diodenanschlussgebiete viel dicker ausgebildet ist als durch die Kollektorgebiete. Dies nutzt den Flächenanteil aus, der von den Diodenanschlussbereichen eingenommen wird, um dem Wafer eine erhöhte Steifigkeit zu verleihen und somit ein Verziehen zu vermeiden.

**[0008]** Die WO 2016/ 129 041 A1 schlägt eine Halbleitervorrichtung vor, bei welcher eine p-Anodenschicht auf einer vorderen Fläche einer n-Driftschicht in einem aktiven Bereich ausgebildet ist. Eine n-Pufferschicht ist auf einer hinteren Fläche der n-Driftschicht ausgebildet. Eine n-Kathodenschicht und eine p-Kathodenschicht sind nebeneinander auf einer hinteren Fläche der n-Pufferschicht ausgebildet. Eine n-Schicht ist auf der hinteren Fläche der n-Pufferschicht in einem Übergangsbereich zwis-

schen dem aktiven Bereich und der Seite des Anschlussbereichs neben der n-Kathodenschicht und der p-Kathodenschicht angeordnet. Eine Erstreckungslänge der n-Schicht zur Seite des aktiven Bereichs, mit einem Endabschnitt des aktiven Bereichs als ein Ausgangspunkt, beträgt mindestens 10 µm und höchstens 500 µm.

**[0009]** Die JP 2010- 114 248 A offenbart eine Halbleitervorrichtung, die eingerichtet ist, eine Durchlassspannung einer Diode zu reduzieren, während eine Stehspannung eines IGBT in einer Halbleitervorrichtung sichergestellt wird, die sowohl den IGBT als auch eine Diode innerhalb eines Halbleitersubstrats aufweist. Der IGBT und die Diode sind in der Halbleitervorrichtung ausgebildet. Ein erster Basisbereich eines ersten Leitfähigkeitsstyps erstreckt sich sowohl zu einem IGBT-Bereich als auch zu einem Diodenbereich. Ein zweiter Basisbereich vom zweiten Leitfähigkeitsstyp ist auf der Oberfläche des ersten Basisbereichs ausgebildet. Der zweite Basisbereich ist sowohl im IGBT-Bereich als auch im Diodenbereich vorgesehen. Der erste Basisbereich ist im IGBT-Bereich dick und im Diodenbereich dünn ausgebildet.

**[0010]** Die JP 2013- 110 373 A nennt eine Halbleitervorrichtung, welche mit einem Halbleiterchip, der mit einem SiC-IGBT ausgebildet ist, aufweisend, mit einer SiC-Halbleiterschicht, die eine erste Oberfläche und eine zweite Oberfläche aufweist, mit einem Kollektorgebiet von einem ersten Leitfähigkeitsstyp, das so ausgebildet ist, dass das Kollektorgebiet auf der zweiten Oberfläche der SiC-Halbleiterschicht freiliegt, mit einem Basisgebiet von einem zweiten Leitfähigkeitsstyp, das bezüglich des Kollektorgebiets näher an der ersten Oberfläche der SiC-Halbleiterschicht ausgebildet ist, derart, dass das Basisgebiet mit dem Kollektorgebiet in Kontakt ist, mit einem Kanalgebiet vom ersten Leitfähigkeitsstyp, das bezüglich des Basisgebiets näher an der ersten Oberfläche der SiC-Halbleiterschicht ausgebildet ist, derart, dass das Kanalgebiet mit dem Basisgebiet in Kontakt ist, mit einem Emittergebiet vom zweiten Leitfähigkeitsstyp, das bezüglich des Kanalgebiets näher an der ersten Oberfläche der SiC-Halbleiterschicht ausgebildet ist, derart, dass das Emittergebiet mit dem Kanalgebiet in Kontakt ist, wobei das Emittergebiet einen Teil der ersten Oberfläche der SiC-Halbleiterschicht definiert, mit einer Kollektorelektrode, die so ausgebildet ist, dass die Kollektorelektrode mit der zweiten Oberfläche der SiC-Halbleiterschicht in Kontakt ist, wobei die Kollektorelektrode mit dem Kollektorgebiet verbunden ist, und mit einer Emittorelektrode, die so eingerichtet ist, dass die Emittorelektrode mit der ersten Oberfläche der SiC-Halbleiterschicht in Kontakt ist, wobei die Emittorelektrode mit dem Emittergebiet verbunden ist, und mit einem MOSFET ausgebildet ist, der mit dem SiC-IGBT parallelgeschaltet ist, wobei der MOSFET

ein Source-Gebiet vom zweiten Leitfähigkeitsstyp, das mit der Emittorelektrode elektrisch verbunden ist, und ein Drain-Gebiet vom zweiten Leitfähigkeitsstyp aufweist, das mit der Kollektorelektrode elektrisch verbunden ist, wobei der MOSFET einen in dem Halbleiterchip vorgesehenen SiC-MOSFET aufweist, das Source-Gebiet unter Verwendung des Emittergebiets des SiC-IGBTs ausgebildet ist, das Drain-Gebiet neben dem Kollektorgebiet des SiC-IGBTs ausgebildet ist, derart, dass das Drain-Gebiet selektiv auf der zweiten Oberfläche der SiC-Halbleiterschicht freiliegt, und die Kollektorelektrode gemeinsam mit dem Drain-Gebiet und dem Kollektorgebiet verbunden ist, und wobei die SiC-Halbleiterschicht ein SiC-Substrat vom zweiten Leitfähigkeitsstyp, das die zweite Oberfläche der SiC-Halbleiterschicht definiert und selektiv mit einem Graben von der zweiten Oberfläche zu der ersten Oberfläche ausgebildet ist, und eine SiC-Basissschicht vom zweiten Leitfähigkeitsstyp aufweist, die auf dem SiC-Substrat ausgebildet ist, um als das die erste Oberfläche der SiC-Halbleiterschicht definierende Basisgebiet zu dienen, und wobei das Drain-Gebiet unter Verwendung des SiC-Substrats ausgebildet ist, und das Kollektorgebiet an der unteren Fläche des Grabens ausgebildet ist.

#### Zusammenfassung der Erfindung

**[0011]** Eine Aufgabe der vorliegenden Erfindung ist es, eine Halbleiteranordnung bereitzustellen, die zum individuellen Steuern und/oder Regeln eines Betriebs des pnp-Bereichs und eines Betriebs des pn-Bereichs eingerichtet ist.

**[0012]** Die Lösung dieser Aufgabe erfolgt durch die Merkmale des Anspruches 1. Die Unteransprüche offenbaren bevorzugte Weiterbildungen der Erfindung.

**[0013]** Gemäß einem Aspekt der vorliegenden Erfindung wird eine Halbleiteranordnung bereitgestellt, die eine Mehrschichtstruktur aufweist, die eine erste Halbleiterschicht eines ersten Leitfähigkeitsstyps, eine zweite Halbleiterschicht eines zweiten Leitfähigkeitsstyps, die an einer Vorderseite der ersten Halbleiterschicht ausgebildet ist, eine dritte Halbleiterschicht des ersten Leitfähigkeitsstyps, die an einer Rückseite der ersten Halbleiterschicht ausgebildet ist, eine vierte Halbleiterschicht des ersten Leitfähigkeitsstyps und eine fünfte Halbleiterschicht des zweiten Leitfähigkeitsstyps, die an einer Rückseite der dritten Halbleiterschicht oder sowohl an der Rückseite der ersten Halbleiterschicht als auch der dritten Halbleiterschicht auf solche Art und Weise ausgebildet sind, dass die vierte Halbleiterschicht und die fünfte Halbleiterschicht in einer Draufsicht benachbart zueinander angeordnet sind oder sich benachbarte Abschnitte der vierten Halbleiterschicht und der fünften Halbleiterschicht in einer Draufsicht gegenseitig überlagern, eine erste Elektrode, die eine Vorder-

seite der zweiten Halbleiterschicht abdeckt, und eine zweite Elektrode, die eine Rückseite der vierten Halbleiterschicht und der fünften Halbleiterschicht abdeckt, aufweist. Bei der Halbleiteranordnung unterscheiden sich eine vertikale Position der vierten Halbleiterschicht in der Mehrschichtstruktur und eine vertikale Position der fünften Halbleiterschicht in der Mehrschichtstruktur voneinander. Ferner unterscheiden sich eine Dicke der ersten Halbleiterschicht in der Mehrschichtstruktur, die die vierte Halbleiterschicht aufweist, und eine Dicke der ersten Halbleiterschicht in der Mehrschichtstruktur, die die fünfte Halbleiterschicht aufweist voneinander. Die Mehrschichtstruktur weist des Weiteren eine dritte Elektrode auf, die zwischen der vierten Halbleiterschicht und der zweiten Elektrode ausgebildet ist. Schließlich ist eine Differenz zwischen der Dicke der ersten Halbleiterschicht in der Mehrschichtstruktur, die die vierte Halbleiterschicht aufweist, und der Dicke der ersten Halbleiterschicht in der Mehrschichtstruktur, die die fünfte Halbleiterschicht aufweist, identisch mit einer Dicke, die erhalten wird durch Addieren eines Höhenunterschieds zwischen der vierten Halbleiterschicht und der fünften Halbleiterschicht zu einer Dicke der dritten Elektrode.

**[0014]** Gemäß diesem Aspekt der vorliegenden Erfindung umfasst eine Halbleiteranordnung eine Mehrschichtstruktur, die eine erste Halbleiterschicht eines ersten Leitfähigkeitstyps, eine zweite Halbleiterschicht eines zweiten Leitfähigkeitstyps, die an einer Vorderseite der ersten Halbleiterschicht ausgebildet ist, eine dritte Halbleiterschicht des ersten Leitfähigkeitstyps, die an einer Rückseite der ersten Halbleiterschicht ausgebildet ist, eine vierte Halbleiterschicht des ersten Leitfähigkeitstyps und eine fünfte Halbleiterschicht des zweiten Leitfähigkeits-typs, die an einer Rückseite der dritten Halbleiterschicht oder sowohl an der Rückseite der ersten Halbleiterschicht als auch der dritten Halbleiterschicht auf solche Art und Weise ausgebildet sind, dass die vierte Halbleiterschicht und die fünfte Halbleiterschicht in einer Draufsicht benachbart zueinander angeordnet sind oder sich benachbarte Abschnitte der vierten Halbleiterschicht und der fünften Halbleiterschicht in einer Draufsicht gegenseitig überlagern, eine erste Elektrode, die eine Vorderseite der zweiten Halbleiterschicht abdeckt, und eine zweite Elektrode, die eine Rückseite der vierten Halbleiterschicht und der fünften Halbleiterschicht abdeckt, aufweist, wobei sich eine vertikale Position der vierten Halbleiterschicht in der Mehrschichtstruktur und eine vertikale Position der fünften Halbleiterschicht in der Mehrschichtstruktur voneinander unterscheiden. Mit diesem Aufbau können der Betrieb des pnp-Bereichs und der Betrieb des pn-Bereichs individuell gesteuert und/oder geregelt werden.

**[0015]** Diese und weitere Aufgaben, Merkmale, Aspekte und Vorteile der vorliegenden Erfindung werden deutlicher aus der folgenden detaillierten Beschreibung der vorliegenden Erfindung im Zusammenhang mit den anliegenden Zeichnungen.

### Figurenliste

**Fig. 1** ist eine Schnittdarstellung, die ein Beispiel eines Aufbaus einer Halbleiteranordnung zur Erläuterung des technischen Hintergrunds der vorliegenden Erfindung zeigt;

**Fig. 2** ist eine Schnittdarstellung, die ein anderes Beispiel eines Aufbaus einer Halbleiteranordnung zur Erläuterung des technischen Hintergrunds der vorliegenden Erfindung zeigt;

**Fig. 3** ist eine Schnittdarstellung, die ein weiteres Beispiel eines Aufbaus einer Halbleiteranordnung zur Erläuterung des technischen Hintergrunds der vorliegenden Erfindung zeigt;

**Fig. 4** ist eine Schnittdarstellung, die ein Beispiel eines Aufbaus einer Halbleiterschicht gemäß einem Ausführungsbeispiel der vorliegenden Erfindung zeigt;

**Fig. 5-6** sind Schnittdarstellungen, die weitere Beispiele zur Erläuterung des technischen Hintergrunds der vorliegenden Erfindung zeigen; und

**Fig. 7** ist eine Schnittdarstellung eines Beispiels eines Aufbaus einer Halbleiteranordnung gemäß einem Stand der Technik.

### Beschreibung der bevorzugten Ausführungsbeispiele

**[0016]** Bevorzugte Ausführungsbeispiele der vorliegenden Erfindung werden unten mit Bezug auf die Zeichnungen beschrieben.

#### <Stand der Technik>

**[0017]** Zunächst wird ein Stand der Technik bezüglich der vorliegenden Erfindung beschrieben.

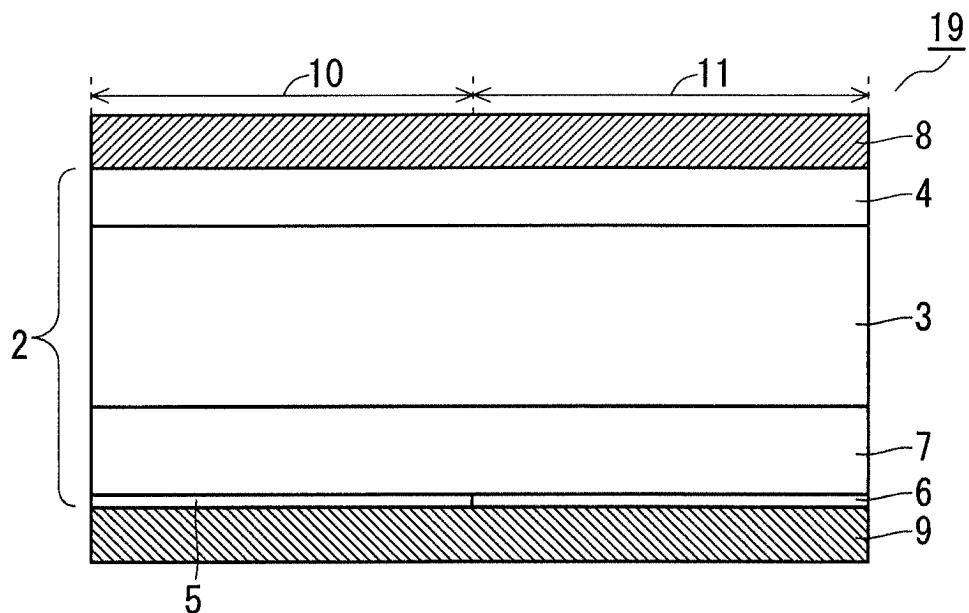

**[0018]** **Fig. 7** ist eine Schnittdarstellung eines Beispiels eines Aufbaus einer Halbleiteranordnung 19 gemäß dem Stand der Technik.

**[0019]** Die Halbleiteranordnung 19 umfasst ein Halbleitersubstrat 2, das aus Silizium (Si) hergestellt ist, eine Vorderseitenelektrode 8, die eine erste Elektrode ist, die an der Vorderseite des Halbleitersubstrats 2 ausgebildet ist, und eine Rückseitenelektrode 9, die eine zweite Elektrode ist, die an der Rückseite des Halbleitersubstrats 2 ausgebildet ist. Das Halbleitersubstrat 2 umfasst eine n-i-Schicht 3, eine p-Anodenschicht 4, eine n<sup>+</sup>-Kathodenschicht 5, eine p-Kollektorschicht 6 und ein n-Pufferschicht 7.

Ein pin-Bereich 10 hat eine Mehrschichtstruktur, aufweisend die p-Anodenschicht, die n-i-Schicht 3, die n-Pufferschicht 7 und die n<sup>+</sup>-Kathodenschicht 5. Ein pnp-Bereich 11 hat eine Mehrschichtstruktur, aufweisend die p-Anodenschicht 4, n-i-Schicht 3, n-Pufferschicht 7 und die p-Kollektorschicht 6.

**[0020]** Sowohl „n“ als auch „p“ beziehen sich auf einen Leitfähigkeitstyp, und die n-Leitung bezieht sich auf einen ersten Leitfähigkeitstyp und die p-Leitung bezieht sich auf einen zweiten Leitfähigkeitstyp. Das hierin verwendete „n“ deutet an, dass die n-leitende Fremdstoffdichte im Vergleich zu den weiteren n-leitenden Fremdstoffdichten relativ gering ist. Das hierin verwendete „n<sup>+</sup>“ deutet an, dass die n-leitende Fremdstoffdichte im Vergleich zu den weiteren n-leitenden Fremdstoffkonzentrationen relativ hoch ist. Es sei angemerkt, dass sich in der folgenden Beschreibung die n-Leitung auf den ersten Leitfähigkeitstyp und die p-Leitung auf den zweiten Leitfähigkeitstyp bezieht, jedoch kann sich die p-Leitung auf den ersten Leitfähigkeitstyp und die n-Leitung auf den zweiten Leitfähigkeitstyp beziehen.

**[0021]** Die n-i-Schicht 3, die eine erste Halbleiterschicht des ersten Leitfähigkeitstyps ist, ist als eine n-leitende intrinsische Halbleiterschicht ausgebildet. Die p-Anodenschicht 4, die eine zweite Halbleiterschicht des zweiten Leitfähigkeitstyps ist, ist näher an der Vorderseite des Halbleitersubstrats 2 angeordnet als die n-i-Schicht 3. Die n-Pufferschicht 7, die eine dritte Halbleiterschicht des ersten Leitfähigkeitstyps ist, ist näher an der Rückseite des Halbleitersubstrats 2 angeordnet als die n-i-Schicht 3. Die n<sup>+</sup>-Kathodenschicht 5, die eine vierte Halbleiterschicht des ersten Leitfähigkeitstyps ist, und die p-Kollektorschicht 6, die eine fünfte Halbleiterschicht des zweiten Leitfähigkeitstyps ist, sind näher an der Rückseite des Halbleitersubstrats 2 angeordnet als die n-i-Schicht 3. Die n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 sind in einer Draufsicht benachbart zueinander. Mit anderen Worten bilden die n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 eine pn-Struktur.

**[0022]** Mit Bezug auf **Fig. 7** sind die n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 im Wesentlichen bei derselben Tiefe von der Rückseite des Halbleitersubstrats 2 ausgebildet. Mit anderen Worten sind die vertikale Position der n<sup>+</sup>-Kathodenschicht 5 in der Mehrschichtstruktur in dem pin-Bereich 10 und die vertikale Position der p-Kollektorschicht 6 in der Mehrschichtstruktur in dem pnp-Bereich 11 im Wesentlichen dieselben. Wie oben beschrieben, macht es dieser Aufbau schwierig, den Betrieb des pin-Bereichs 10 und den Betrieb des pnp-Bereichs 11 individuell zu steuern und/oder zu regeln.

**[0023]** Die vorliegende Erfindung wurde gemacht, um ein solches Problem zu lösen, und ist unten im Detail beschrieben.

<Beispiel zur Erläuterung des technischen Hintergrunds der Erfindung>

<Aufbau>

**[0024]** Der Aufbau der Halbleiteranordnungen gemäß den bevorzugten Ausführungsbeispielen der vorliegenden Erfindung wird unten beschrieben.

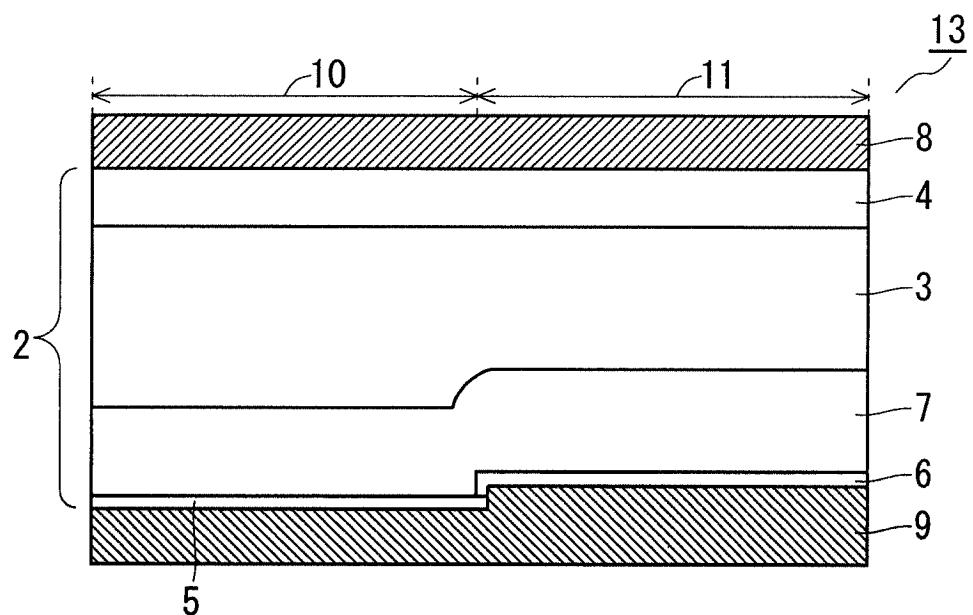

**Fig. 1** ist eine Schnittdarstellung eines Beispiels eines Aufbaus einer Halbleiteranordnung 1 zur Erläuterung des technischen Hintergrunds der Erfindung.

**[0025]** Gemäß der Halbleiteranordnung 1 des ersten bevorzugten Ausführungsbeispiels unterscheidet sich die Dicke der n<sup>+</sup>-i-Schicht 3 in dem pin-Bereich 10 von der Dicke der n-i-Schicht 3 in dem pnp-Bereich 11. Insbesondere ist die Dicke der n-i-Schicht 3 in dem pnp-Bereich 11 geringer als diejenige der n-i-Schicht 3 in dem pin-Bereich 10. Die vertikale Position der n<sup>+</sup>-Kathodenschicht 5 in der Mehrschichtstruktur in dem pin-Bereich 10 und die vertikale Position der p-Kollektorschicht 6 in der Mehrschichtstruktur in dem pnp-Bereich 11 unterscheiden sich voneinander. Der übrige Aufbau ist derselbe wie derjenige der Halbleiteranordnung 19 gemäß dem in **Fig. 7** gezeigten Stand der Technik, und die detaillierte Beschreibung davon wird daher weggelassen.

**[0026]** Gemäß der Halbleiteranordnung 1 ist eine Differenz zwischen der Dicke der n-i-Schicht 3 in dem pin-Bereich 10 und der Dicke der n-i-Schicht 3 in dem pnp-Bereich 11 gleich dem Höhenunterschied zwischen der n<sup>+</sup>-Kathodenschicht 5 und der p-Kollektorschicht 6. Der Höhenunterschied zwischen der n<sup>+</sup>-Kathodenschicht 6 und der p-Kollektorschicht 6 bezieht sich auf einen Höhenunterschied zwischen der Grenzfläche zwischen der n<sup>+</sup>-Kathodenschicht 5 und der Rückseitenelektrode 9 und der Grenzfläche zwischen der p-Kollektorschicht 6 und der Rückseitenelektrode 9.

**[0027]** Mit Bezug auf **Fig. 1** sind die n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 an der Rückseite der n-Pufferschicht 7 ausgebildet. Die n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 sind in einer Draufsicht benachbart zueinander, und die benachbarten Abschnitte der n<sup>+</sup>-Kathodenschicht 5 und der p-Kollektorschicht 6 überlagern sich in einer Draufsicht nicht gegenseitig.

<Herstellungsverfahren>

**[0028]** Ein Verfahren zum Herstellen der Halbleiteranordnung 1 wird unten beschrieben.

**[0029]** Zuerst wird das Halbleitersubstrat 2, das die n-i-Schicht 3 aufweist, fertiggestellt. Dann werden Bor(B)-Ionen in das Halbleitersubstrat 2 von der Vorderseite davon aus implantiert, und es wird ein Eintrebschritt zur Ausbildung der p-Anodenschicht 4 durchgeführt. Die Implantierdosis der B-Ionen beträgt 1E13 bis 1E16 (1/cm<sup>2</sup>). Der Eintrebschritt wird unter 900°C bis 1200°C für 30 bis 120 Minuten durchgeführt.

**[0030]** Dann wird die Vorderseitenelektrode 8 ausgebildet, um die p-Anodenschicht 4 abzudecken. Die Rückseite des Halbleitersubstrats 2 wird nachfolgend geschliffen, bis das Halbleitersubstrat 2 eine gewünschte Dicke aufweist. Nach dem Schleifen werden Phosphor(P)-Ionen, die in die n<sup>+</sup>-Kathodenschicht 5 einzufügen sind, in die gesamte Rückseite des Halbleitersubstrats 2 implantiert. Die Implantierdosis der P-Ionen beträgt 1E14 bis 1E16 (1/cm<sup>2</sup>).

**[0031]** Als nächstes wird eine pn-Struktur, in der ein Bereich für die n<sup>+</sup>-Kathodenschicht 5 abgedeckt wird und ein Bereich für die p-Kollektorschicht 6 geöffnet wird, an der Rückseite des Halbleitersubstrats 2 ausgebildet, und dann wird das Halbleitersubstrat 2 in dem Bereich für die p-Kollektorschicht 6 geätzt, bis das Halbleitersubstrat 2 eine gewünschte Dicke aufweist. Nach dem Ätzen werden B-Ionen, die in die p-Kollektorschicht 6 einzufügen sind, in den Bereich für die p-Kollektorschicht 6 implantiert. Die Implantierdosis der B-Ionen beträgt 1E13 bis 1E16 (1/cm<sup>2</sup>). Mit diesen Schritten werden die n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 ausgebildet.

**[0032]** Die pn-Struktur wird danach entfernt, und dann werden P-Ionen in das Halbleitersubstrat 2 von der Rückseite davon aus durch die n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 implantiert, um die n-Pufferschicht 7 auszubilden. Die Implantierdosis der P-Ionen beträgt 1E13 bis 1E15 (1/cm<sup>2</sup>). Mit diesen Schritten wird die n-Pufferschicht 7 ausgebildet, deren n-leitende Fremdstoffdichte höher ist als diejenige der n-i-Schicht 3.

**[0033]** Dann wird das Halbleitersubstrat 2 einer Wärmebehandlung unterworfen, um die n<sup>+</sup>-Kathodenschicht 5, die p-Kollektorschicht 6 und die n-Pufferschicht 7 zu aktivieren. Als Wärmebehandlung wird Laserglühen und dergleichen verwendet.

**[0034]** Als letzter Schritt wird die Rückseitenelektrode 9, die eine Dicke von mehreren Mikrometern (µm) aufweist, durch Plattieren, Sputtern oder Gasphasenabscheidung ausgebildet, um die n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 abzudecken. Mit diesen Schritten wird die Halbleiteranordnung 1, die den pin-Bereich 10 und den pnp-Bereich 11 aufweist, fertiggestellt.

**[0035]** Gemäß dem ersten bevorzugten Ausführungsbeispiel unterscheiden sich die Dicke der n-i-Schicht 3 in dem pin-Bereich 10 und die Dicke der n-i-Schicht 3 in dem pnp-Bereich 11 voneinander, und somit können der Betrieb des pin-Bereichs 10 und der Betrieb des pnp-Bereichs 11 individuell gesteuert und/oder geregelt werden.

**[0036]** Die Dicke der n-i-Schicht 3 in dem pnp-Bereich 11 ist geringer als diejenige der n-i-Schicht 3 in dem pin-Bereich 10. Dementsprechend können ein geringer Ein-Widerstand und geringe Schaltverluste in IGBTs erhalten werden, und bei Dioden kann die Durchschlagstärke im Erholungsbetrieb verbessert werden.

**[0037]** Es sei angemerkt, dass **Fig. 1** einen Fall zeigt, bei dem das Halbleitersubstrat 2 die n-i-Schicht 3 umfasst, jedoch ist der Fall nicht hierauf eingeschränkt. Statt n-i-Schicht 3 kann das Halbleitersubstrat 2 eine Halbleiterschicht aufweisen, die eine größere Menge von n-leitenden Fremdstoffen enthält. In einem solchen Fall wird der pin-Bereich 10 aus **Fig. 1** ein pn-Bereich.

<Zweites Beispiel zur Erläuterung des technischen Hintergrunds der Erfindung>

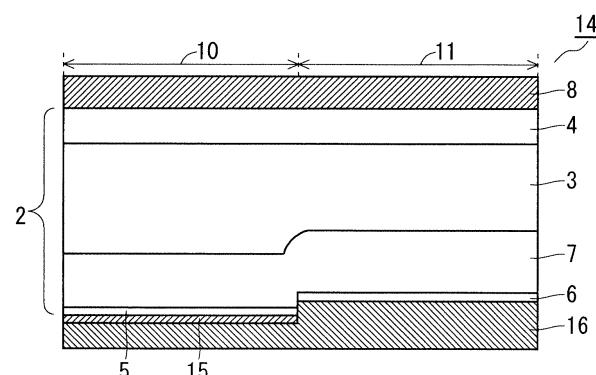

**[0038]** **Fig. 2** ist eine Schnittdarstellung eines Beispiels eines Aufbaus einer Halbleiteranordnung 12 zur Erläuterung des technischen Hintergrunds der vorliegenden Erfindung.

**[0039]** Bei der Halbleiteranordnung 12 gemäß dem zweiten bevorzugten Ausführungsbeispiel entspricht eine Differenz zwischen der Dicke der n-i-Schicht 3 in dem pin-Bereich 10 und der Dicke der n-i-Schicht 3 in dem pnp-Bereich 11 einer Dicke, die erhalten wird durch Addieren eines Höhenunterschieds zwischen der n<sup>+</sup>-Kathodenschicht 5 und der p-Kollektorschicht 6 zu der Dicke der n-Pufferschicht in dem pnp-Bereich 11. Der übrige Aufbau ist derselbe wie derjenige der in **Fig. 1** gezeigten Halbleiteranordnung 1 gemäß dem ersten bevorzugten Ausführungsbeispiel, und daher wird die detaillierte Beschreibung davon weggelassen.

**[0040]** Mit Bezug auf **Fig. 2** ist die n-Pufferschicht 7 nicht in dem pin-Bereich 10 ausgebildet und ist in dem pnp-Bereich 11 ausgebildet. Die n<sup>+</sup>-Kathodenschicht 5 ist an der Rückseite der n-i-Schicht 3 ausgebildet und die p-Kollektorschicht 6 ist an der Rückseite der n-Pufferschicht 7 ausgebildet. Die n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 sind in einer Draufsicht benachbart zueinander und die benachbarten Abschnitte der n<sup>+</sup>-Kathodenschicht 5 und der p-Kollektorschicht 6 überlagern sich in einer Draufsicht nicht gegenseitig.

**[0041]** Ein Verfahren zum Herstellen der Halbleiteranordnung 12 wird unten beschrieben. Die folgende Beschreibung richtet sich auf Unterschiede zu dem Verfahren zum Herstellen der Halbleiteranordnung 1 gemäß dem ersten bevorzugten Ausführungsbeispiel. Das Verfahren ist bis auf die folgenden Unterschiede dasselbe wie dasjenige des ersten bevorzugten Ausführungsbeispiels.

**[0042]** Eine pn-Struktur, in der ein Bereich für die n<sup>+</sup>-Kathodenschicht 5 abgedeckt wird und ein Bereich für die p-Kollektorschicht 6 geöffnet wird, wird an der Rückseite des Halbleitersubstrats 2 ausgebildet, und dann wird das Halbleitersubstrat 2 in dem Bereich für die p-Kollektorschicht 6 geätzt, bis das Halbleitersubstrat 2 eine gewünschte Dicke aufweist. Dann werden B-Ionen, die in die p-Kollektorschicht 6 einzufügen sind, in den Bereich für die p-Kollektorschicht 6 implantiert. Mit diesen Schritten werden die n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 ausgebildet.

**[0043]** Als nächstes werden in einem Zustand, in dem die pn-Struktur ausgebildet wird, P-Ionen in das Halbleitersubstrat 2 von der Rückseite davon aus durch die p-Kollektorschicht 6 implantiert, um die n-Pufferschicht 7 auszubilden. Die Implantierdosis der B-Ionen beträgt 1E13 bis 1E15 (1/cm<sup>2</sup>). Dann wird die pn-Struktur entfernt, um die Rückseitenelektrode 9 auszubilden.

**[0044]** Aufgrund des Obigen bietet das zweite bevorzugte Ausführungsbeispiel dieselben Effekte wie das erste bevorzugte Ausführungsbeispiel. Zusätzlich kann der Druckwiderstand des pin-Bereichs 10 verbessert werden, da die n-Pufferschicht 7 nicht in dem pin-Bereich 10 ausgebildet wird und die Dichte der n-leitenden Fremdstoffe im Vergleich zu dem in **Fig. 1** gezeigten pin-Bereich 10 reduziert wird.

<Drittes Beispiel zur Erläuterung des technischen Hintergrunds der Erfindung>

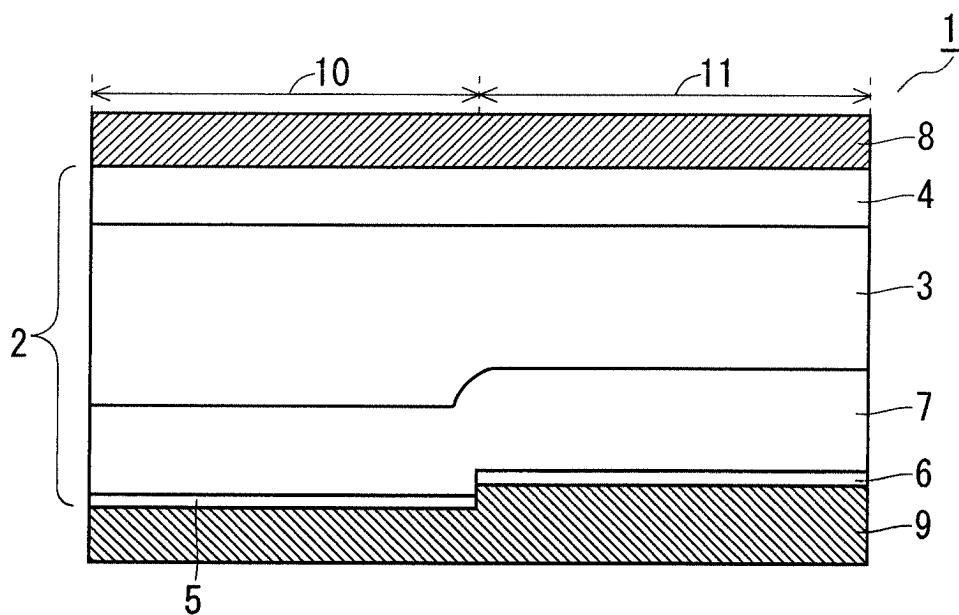

**[0045]** **Fig. 3** ist eine Schnittdarstellung eines Beispiels eines Aufbaus einer Halbleiteranordnung 13 zur Erläuterung des technischen Hintergrunds der vorliegenden Erfindung.

**[0046]** Bei der Halbleiteranordnung 13 gemäß dem dritten bevorzugten Ausführungsbeispiel ist die vertikale Position der p-Kollektorschicht 6 in der Mehrschichtstruktur in dem pnp-Bereich 11 näher an der n-i-Schicht 3 als die vertikale Position der n<sup>+</sup>-Kathodenschicht 5 in der Mehrschichtstruktur in dem pin-Bereich 10, und benachbarte Abschnitte der n<sup>+</sup>-Kathodenschicht 5 und der p-Kollektorschicht 6 überlagern sich in einer Draufsicht gegenseitig. Die p-Kollektorschicht 6 ist zwischen der n<sup>+</sup>-Kathodenschicht 5 und der p-Kollektorschicht 6 an einer Posi-

tion vorhanden, wo sich die benachbarten Abschnitte in einer Draufsicht gegenseitig überlagern. Der übrige Aufbau ist derselbe wie derjenige der in **Fig. 1** gezeigten Halbleiteranordnung 1 des ersten bevorzugten Ausführungsbeispiels, weshalb die detaillierte Beschreibung davon weggelassen wird.

**[0047]** Mit Bezug auf **Fig. 3** werden n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 an der Rückseite der n-Pufferschicht 7 ausgebildet. Die n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 sind in einer Draufsicht benachbart zueinander und die benachbarten Abschnitte der n<sup>+</sup>-Kathodenschicht 5 und der p-Kollektorschicht 6 überlagern sich in einer Draufsicht gegenseitig.

**[0048]** Ein Verfahren zur Herstellung der Halbleiteranordnung 13 wird unten beschrieben. Die folgende Beschreibung richtet sich auf Unterschiede zu dem Verfahren zum Herstellen der Halbleiteranordnung 1 gemäß dem ersten bevorzugten Ausführungsbeispiel. Das Verfahren außer den folgenden Unterschieden ist dasselbe wie dasjenige des ersten bevorzugten Ausführungsbeispiels.

**[0049]** Eine pn-Struktur, in der ein Bereich für die n<sup>+</sup>-Kathodenschicht 5 abgedeckt wird und ein Bereich für die p-Kollektorschicht 6 geöffnet wird, wird an der Rückseite des Halbleitersubstrats 2 ausgebildet, und dann wird das Halbleitersubstrat 2 in dem Bereich für die p-Kollektorschicht 6 geätzt, bis das Halbleitersubstrat 2 eine gewünschte Dicke aufweist. Dann werden B-Ionen, die in die p-Kollektorschicht 6 einzufügen sind, in den Bereich für die p-Kollektorschicht 6 durch Drehionenimplantation implantiert. Die hierin verwendete „Drehionenimplantation“ bezieht sich auf eine Technik zum Implantieren von Ionen, während das Halbleitersubstrat 2 gedreht wird.

**[0050]** Aufgrund des Obigen bietet das dritte bevorzugte Ausführungsbeispiel dieselben Effekte wie das erste bevorzugte Ausführungsbeispiel. Zusätzlich kann ein Leckstrom reduziert werden, da die n-Pufferschicht 7 mit einer geringen Fremdstoffdichte und die Rückseitenelektrode 9 nicht in Kontakt miteinander sind.

<Ausführungsbeispiel>

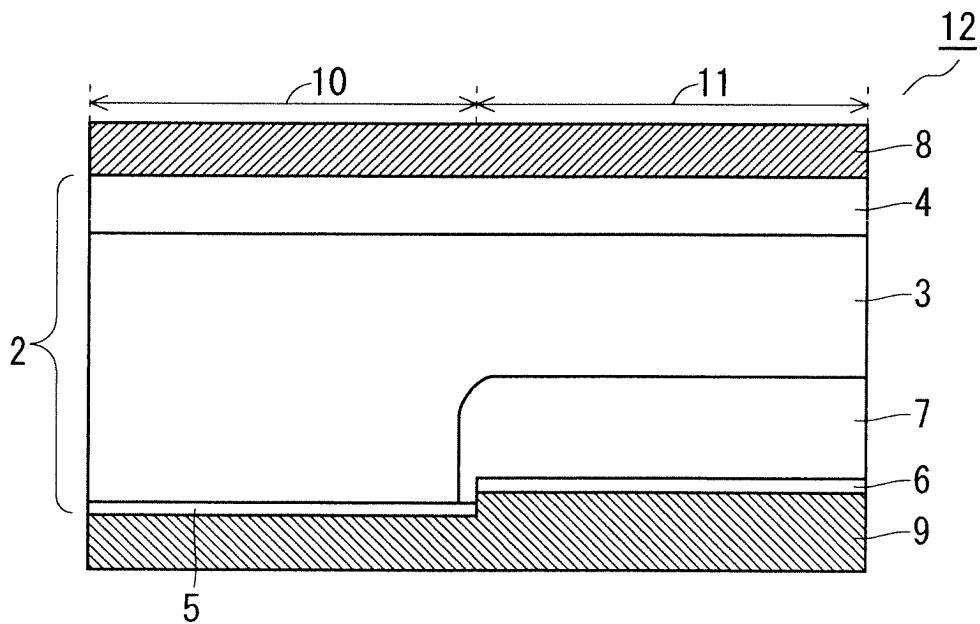

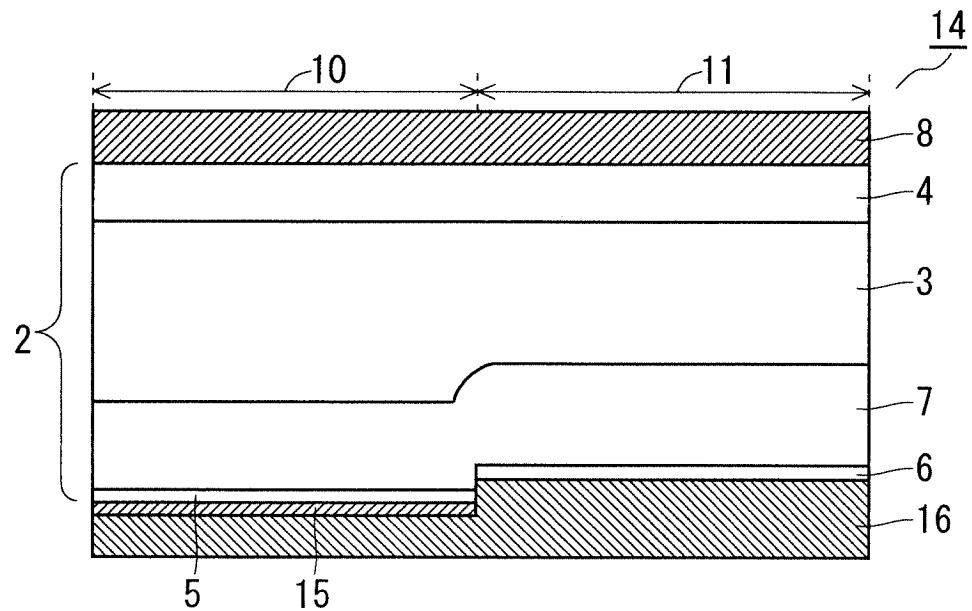

**[0051]** **Fig. 4** ist eine Schnittdarstellung eines Beispiels eines Aufbaus einer Halbleiteranordnung 14 gemäß einem Ausführungsbeispiel der vorliegenden Erfindung.

**[0052]** Die Halbleiteranordnung 14 gemäß dem Ausführungsbeispiel umfasst eine Elektrode 15 zur n-Leitung und eine Elektrode 16 zur p-Leitung. Die Elektrode 15 zur n-Leitung ist eine Elektrode mit zur n-Leitung geeigneten ohmschen Eigenschaften. Die

Elektrode 16 zur p-Leitung ist eine Elektrode mit zur p-Leitung geeigneten ohmschen Eigenschaften.

**[0053]** Die Elektrode 15 zur n-Leitung, die eine dritte Elektrode ist, deckt die n<sup>+</sup>-Kathodenschicht 5 ab. Die Elektrode 16 zur p-Leitung deckt die Elektrode 15 zur n-Leitung und die p-Kollektorschicht 6 ab. Eine Differenz zwischen der Dicke der n-i-Schicht 3 in dem pin-Bereich 10 und der Dicke der n-i-Schicht 3 in dem pnp-Bereich 11 entspricht einer Dicke, die erhalten wird durch Addieren eines Höhenunterschieds zwischen der n<sup>+</sup>-Kathodenschicht 5 und der p-Kollektorschicht 6 zu der Dicke der Elektrode 15 zur n-Leitung. Der übrige Aufbau ist derselbe wie derjenige der in **Fig. 1** gezeigten Halbleiteranordnung 1 des ersten bevorzugten Ausführungsbeispiels, weshalb die detaillierte Beschreibung davon weggelassen wird.

**[0054]** Mit Bezug auf **Fig. 4** werden n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 an der Rückseite der n-Pufferschicht 7 ausgebildet. Die n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 sind in einer Draufsicht benachbart zueinander und die benachbarten Abschnitte der n<sup>+</sup>-Kathodenschicht 5 und der p-Kollektorschicht 6 überlagern sich in einer Draufsicht nicht gegenseitig.

**[0055]** Ein Verfahren zum Herstellen der Halbleiteranordnung 14 wird unten beschrieben. Die folgende Beschreibung richtet sich auf Unterschiede zu dem Verfahren zum Herstellen der Halbleiteranordnung 1 gemäß dem ersten bevorzugten Ausführungsbeispiel. Das Verfahren ist außer den folgenden Unterschieden dasselbe wie dasjenige des ersten bevorzugten Ausführungsbeispiels.

**[0056]** Nachdem die n-Pufferschicht 7 ausgebildet worden ist, wird die Elektrode 15 zur n-Leitung an der n<sup>+</sup>-Kathodenschicht 5 ausgebildet. Dann wird die Elektrode 16 zur p-Leitung ausgebildet, um die Elektrode 15 zur n-Leitung und die p-Kollektorschicht 6 abzudecken.

**[0057]** Aufgrund des Obigen bietet das vierte bevorzugte Ausführungsbeispiel dieselben Effekte wie das erste bevorzugte Ausführungsbeispiel. Zusätzlich werden die ohmschen Eigenschaften verbessert, da die Elektrode 15 zur n-Leitung für die n<sup>+</sup>-Kathodenschicht 5 ausgebildet wird und die Elektrode 16 zur p-Leitung für die p-Kollektorschicht 6 ausgebildet wird.

<Beispiel zur Erläuterung des technischen Hintergrunds der Erfindung >

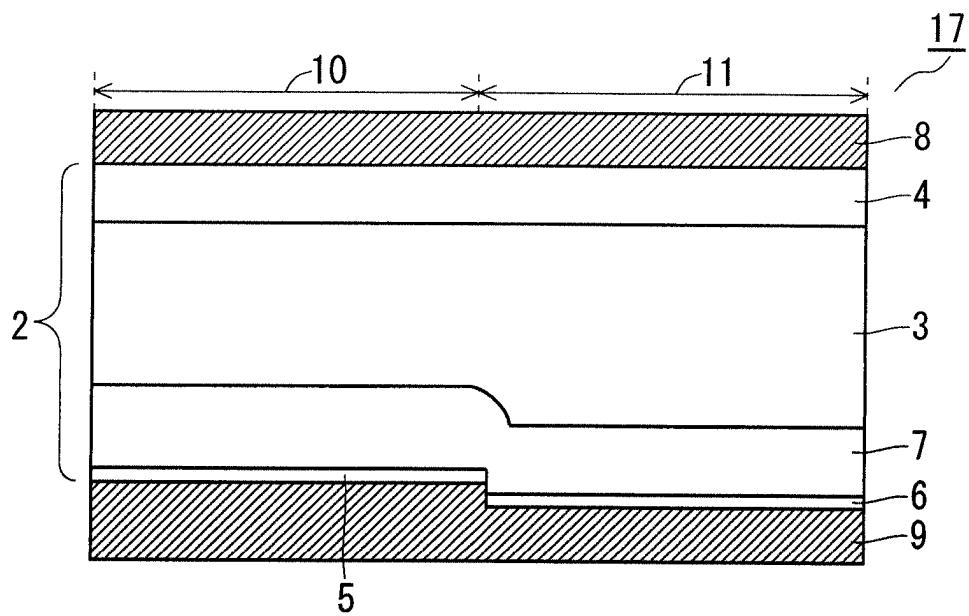

**[0058]** **Fig. 5** ist eine Schnittdarstellung eines weiteren Beispiels eines Aufbaus einer Halbleiteranordnung 17 zur Erläuterung des technischen Hintergrunds der vorliegenden Erfindung.

**[0059]** Bei der Halbleiteranordnung 17 ist eine Dicke n-i-Schicht 3 in dem pin-Bereich 10 kleiner als diejenige der n-i-Schicht 3 in dem pnp-Bereich 11. Der übrige Aufbau ist derselbe wie derjenige der in **Fig. 1** gezeigten Halbleiteranordnung 1 des ersten bevorzugten Ausführungsbeispiels, weshalb die detaillierte Beschreibung davon weggelassen wird.

**[0060]** Mit Bezug auf **Fig. 5** werden die n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 an der Rückseite der n-Pufferschicht 7 ausgebildet. Die n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 sind in einer Draufsicht benachbart zueinander und die benachbarten Abschnitte der n<sup>+</sup>-Kathodenschicht 5 und der p-Kollektorschicht 6 überlagern sich in einer Draufsicht nicht gegenseitig.

**[0061]** Ein Verfahren zum Herstellen der Halbleiteranordnung 17 wird unten beschrieben. Die folgende Beschreibung richtet sich auf Unterschiede zu dem Verfahren zum Herstellen der Halbleiteranordnung 1 gemäß dem ersten bevorzugten Ausführungsbeispiel. Das Verfahren ist bis auf die folgenden Unterschiede dasselbe wie dasjenige des ersten bevorzugten Ausführungsbeispiels.

**[0062]** Nachdem die Vorderseitenelektrode 8 ausgebildet worden ist und das Halbleitersubstrat 2 geschliffen worden ist, werden B-Ionen, die in die p-Kollektorschicht 6 einzufügen sind, in die gesamte Rückseite des Halbleitersubstrats 2 implantiert.

**[0063]** Als nächstes wird eine pn-Struktur, in der ein Bereich für die p-Kollektorschicht 6 abgedeckt wird und ein Bereich für n<sup>+</sup>-Kathodenschicht 5 geöffnet wird, an der Rückseite des Halbleitersubstrats 2 ausgebildet, und dann wird das Halbleitersubstrat 2 in dem Bereich für die n<sup>+</sup>-Kathodenschicht 5 geätzt, bis das Halbleitersubstrat 2 eine gewünschte Dicke aufweist. Dann werden P-Ionen, die in die n<sup>+</sup>-Kathodenschicht 5 einzufügen sind, in den Bereich für die n<sup>+</sup>-Kathodenschicht 5 implantiert.

**[0064]** Nach dem Entfernen der pn-Struktur werden P-Ionen in das Halbleitersubstrat 2 von der Rückseite davon aus durch die n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 implantiert, um die n-Pufferschicht 7 auszubilden.

**[0065]** Aufgrund des Obigen können gemäß dem fünften bevorzugten Ausführungsbeispiel der Betrieb des pin-Bereichs 10 und der Betrieb des pnp-Bereichs 11 individuell gesteuert und/oder geregelt werden. Zusätzlich ist die Dicke der n-i-Schicht 3 in dem pin-Bereich 10 kleiner als diejenige der n-i-Schicht 3 in dem pnp-Bereich 11. Dieser Aufbau ermöglicht es einer Diode, einen geringen Ein-Widerstand und einen geringen Erholungsverlust aufzuweisen.

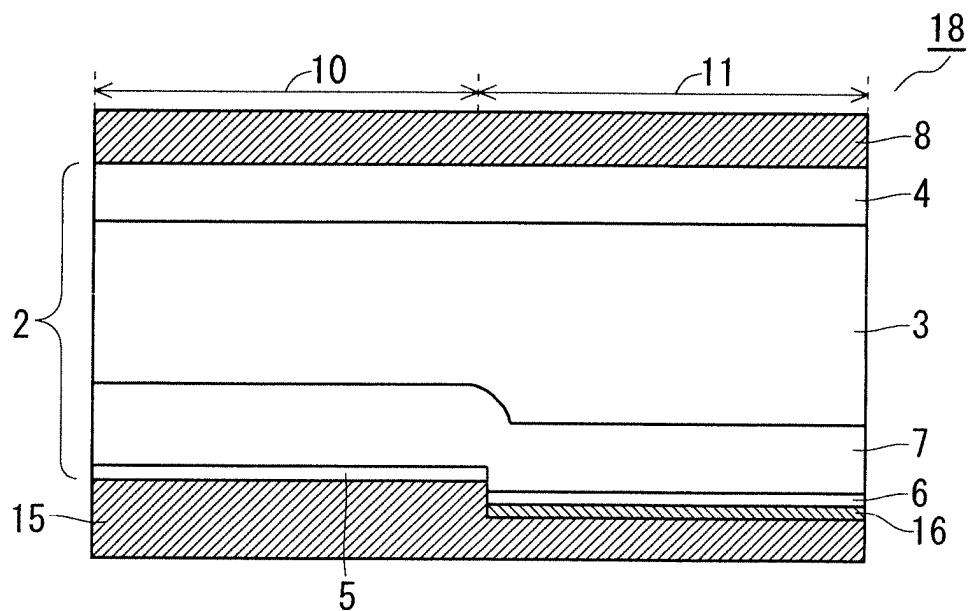

**[0066]** Mit Bezug auf **Fig. 6** kann die Halbleiteranordnung 18 die Elektrode 15 zur n-Leitung und die Elektrode 16 zur p-Leitung aufweisen. Die Elektrode 16 zur p-Leitung deckt die p-Kollektorschicht 6 ab. Die Elektrode 15 zur n-Leitung deckt die n<sup>+</sup>-Kathodenschicht 5 und die Elektrode 16 zur p-Leitung ab. In diesem Fall wird die Elektrode 15 zur n-Leitung für die n<sup>+</sup>-Kathodenschicht 5 ausgebildet und die Elektrode 16 zur p-Leitung wird für die p-Kollektorschicht 6 ausgebildet, wie bei dem vierten bevorzugten Ausführungsbeispiel. Dementsprechend sind die ohmschen Eigenschaften verbessert.

**[0067]** Bei den in den **Fig. 5** und **Fig. 6** gezeigten Halbleiteranordnungen 17, 18 ist die vertikale Position der n<sup>+</sup>-Kathodenschicht 5 in der Mehrschichtstruktur in dem pin-Bereich 10 näher an der n-i-Schicht 3 als die vertikale Position der p-Kollektorschicht 6 in der Mehrschichtstruktur in dem pnp-Bereich 11, und die benachbarten Abschnitte der n<sup>+</sup>-Kathodenschicht 5 und der p-Kollektorschicht 6 können sich in einer Draufsicht gegenseitig überlagern. Die n<sup>+</sup>-Kathodenschicht 5 kann zwischen der n<sup>+</sup>-Kathodenschicht 5 und die p-Kollektorschicht 6 an einer Position vorhanden sein, wo sich die benachbarten Abschnitte in einer Draufsicht gegenseitig überlagern. In diesem Fall kann ein Leckstrom reduziert werden, da die n-Pufferschicht 7 mit einer geringen Fremdstoffdichte und die Rückseitenelektrode 9 nicht in Kontakt miteinander sind, wie bei dem dritten bevorzugten Ausführungsbeispiel.

#### Bezugszeichenliste

- |    |                          |

|----|--------------------------|

| 1  | Halbleiteranordnung      |

| 2  | Halbleitersubstrat       |

| 3  | erste Halbleiterschicht  |

| 4  | zweite Halbleiterschicht |

| 5  | vierte Halbleiterschicht |

| 6  | fünfte Halbleiterschicht |

| 7  | dritte Halbleiterschicht |

| 8  | erste Elektrode          |

| 9  | zweite Elektrode         |

| 10 | pin-Bereich              |

| 11 | pnp-Bereich              |

| 12 | Halbleiteranordnung      |

| 13 | Halbleiteranordnung      |

| 14 | Halbleiteranordnung      |

| 15 | dritte Elektrode         |

| 16 | Elektrode                |

| 17 | Halbleiteranordnung      |

| 18 | Halbleiteranordnung      |

19 Halbleiteranordnung

#### Patentansprüche

1. Halbleiteranordnung, mit einer Mehrschichtstruktur aufweisend:

- eine erste Halbleiterschicht (3) eines ersten Leitfähigkeitsstyps;

- eine zweite Halbleiterschicht (4) eines zweiten Leitfähigkeitsstyps, die an einer Vorderseite der ersten Halbleiterschicht (3) ausgebildet ist;

- eine dritte Halbleiterschicht (7) des ersten Leitfähigkeitsstyps, die an einer Rückseite der ersten Halbleiterschicht (3) ausgebildet ist;

- eine vierte Halbleiterschicht (5) des ersten Leitfähigkeitsstyps und eine fünfte Halbleiterschicht (6) des zweiten Leitfähigkeitsstyps, die an einer Rückseite der dritten Halbleiterschicht (7) oder sowohl an der Rückseite der ersten Halbleiterschicht (3) als auch der dritten Halbleiterschicht (7) auf solche Art und Weise ausgebildet sind, dass die vierte Halbleiterschicht (5) und die fünfte Halbleiterschicht (6) in einer Draufsicht benachbart zueinander sind oder benachbarte Abschnitte der vierten Halbleiterschicht (5) und der fünften Halbleiterschicht (6) sich in einer Draufsicht gegenseitig überlagern;

- eine erste Elektrode (8), die eine Vorderseite der zweiten Halbleiterschicht (4) abdeckt; und

- eine zweite Elektrode (16), die eine Rückseite der vierten Halbleiterschicht (5) und der fünften Halbleiterschicht (6) abdeckt, und wobei:

- eine vertikale Position der vierten Halbleiterschicht (5) in der Mehrschichtstruktur und eine vertikale Position der fünften Halbleiterschicht (6) in der Mehrschichtstruktur sich voneinander unterscheiden,

- eine Dicke der ersten Halbleiterschicht (3) in der Mehrschichtstruktur, die die vierte Halbleiterschicht (5) aufweist, und eine Dicke der ersten Halbleiterschicht (3) in der Mehrschichtstruktur, die die fünfte Halbleiterschicht (6) aufweist, sich voneinander unterscheiden,

- die Mehrschichtstruktur des Weiteren eine dritte Elektrode (15) aufweist, die zwischen der vierten Halbleiterschicht (5) und der zweiten Elektrode (16) ausgebildet ist, und

- eine Differenz zwischen der Dicke der ersten Halbleiterschicht (3) in der Mehrschichtstruktur, die die vierte Halbleiterschicht (5) aufweist, und der Dicke der ersten Halbleiterschicht (3) in der Mehrschichtstruktur, die die fünfte Halbleiterschicht (6) aufweist, identisch ist mit einer Dicke, die erhalten wird durch Addieren eines Höhenunterschieds zwischen der vierten Halbleiterschicht (5) und der fünften Halbleiterschicht (6) zu einer Dicke der dritten Elektrode (15).

2. Halbleiteranordnung nach Anspruch 1, wobei eine Differenz zwischen der Dicke der ersten Halbleiterschicht (3) in der Mehrschichtstruktur, die die

vierte Halbleiterschicht (5) aufweist, und der Dicke der ersten Halbleiterschicht (3) in der Mehrschichtstruktur, die die fünfte Halbleiterschicht (6) aufweist, identisch ist mit einem Höhenunterschied zwischen der vierten Halbleiterschicht (5) und der fünften Halbleiterschicht (6).

3. Halbleiteranordnung nach Anspruch 1, wobei eine Differenz zwischen der Dicke der ersten Halbleiterschicht (3) in der Mehrschichtstruktur, die die vierte Halbleiterschicht (5) aufweist, und der Dicke der ersten Halbleiterschicht (3) in der Mehrschichtstruktur, die die fünfte Halbleiterschicht (6) aufweist, identisch ist mit einer Dicke, die erhalten wird durch Addieren eines Höhenunterschieds zwischen der vierten Halbleiterschicht (5) und der fünften Halbleiterschicht (6) zu einer Dicke der dritten Halbleiterschicht (7) in der Mehrschichtstruktur, die die fünfte Halbleiterschicht (6) aufweist.

4. Halbleiteranordnung nach einem der vorangehenden Ansprüche, wobei:

- die vertikale Position der fünften Halbleiterschicht (6) in der Mehrschichtstruktur näher an der Vorderseite der ersten Halbleiterschicht (3) ist als die vertikale Position der vierten Halbleiterschicht (5) in der Mehrschichtstruktur,

- die vierte Halbleiterschicht (5) und die fünfte Halbleiterschicht (6) auf solche Art und Weise ausgebildet sind, dass sich benachbarte Abschnitte gegenseitig überlagern, und

- die fünfte Halbleiterschicht (6) zwischen der fünften Halbleiterschicht (6) und der vierten Halbleiterschicht (5) an einer Position vorhanden ist, wo sich die benachbarten Abschnitte gegenseitig überlagern.

Es folgen 4 Seiten Zeichnungen

## Anhängende Zeichnungen

F I G . 1

F I G . 2

F I G . 3

F I G . 4

F I G . 5

F I G . 6

F I G . 7 Stand der Technik