(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5730484号

(P5730484)

(45) 発行日 平成27年6月10日(2015.6.10)

(24) 登録日 平成27年4月17日(2015.4.17)

|               |                            |

|---------------|----------------------------|

| (51) Int.Cl.  | F 1                        |

| H 01 L 21/20  | (2006.01) H 01 L 21/20     |

| H 01 L 21/205 | (2006.01) H 01 L 21/205    |

| H 01 L 33/32  | (2010.01) H 01 L 33/00 186 |

| C 23 C 16/34  | (2006.01) C 23 C 16/34     |

請求項の数 30 (全 16 頁)

|               |                               |           |                                                                           |

|---------------|-------------------------------|-----------|---------------------------------------------------------------------------|

| (21) 出願番号     | 特願2009-547307 (P2009-547307)  | (73) 特許権者 | 508159031<br>クリスタル アイエス インコーポレイテッド                                        |

| (86) (22) 出願日 | 平成20年1月25日 (2008.1.25)        |           | アメリカ合衆国ニューヨーク州12183<br>, グリーン・アイランド, コーホーズ・アベニュー・70                       |

| (65) 公表番号     | 特表2010-517298 (P2010-517298A) | (74) 代理人  | 100087642<br>弁理士 古谷 聰                                                     |

| (43) 公表日      | 平成22年5月20日 (2010.5.20)        | (74) 代理人  | 100076680<br>弁理士 溝部 孝彦                                                    |

| (86) 國際出願番号   | PCT/US2008/001003             | (74) 代理人  | 100121061<br>弁理士 西山 清春                                                    |

| (87) 國際公開番号   | W02008/094464                 | (72) 発明者  | ショーウォルター, レオ, ジェイ<br>アメリカ合衆国ニューヨーク州12110<br>, レイサム, コード・ドライヴ・25<br>最終頁に続く |

| (87) 國際公開日    | 平成20年8月7日 (2008.8.7)          |           |                                                                           |

| 審査請求日         | 平成23年1月24日 (2011.1.24)        |           |                                                                           |

| (31) 優先権主張番号  | 60/897,572                    |           |                                                                           |

| (32) 優先日      | 平成19年1月26日 (2007.1.26)        |           |                                                                           |

| (33) 優先権主張国   | 米国(US)                        |           |                                                                           |

(54) 【発明の名称】厚みのある擬似格子整合型の窒化物エピタキシャル層

## (57) 【特許請求の範囲】

## 【請求項 1】

窒化アルミニウム単結晶基板、及び

前記窒化アルミニウム単結晶基板上にエピタキシャル成長させた少なくとも1つの擬似格子整合型の膜であって、AlN、GaN、InN又はそれらの任意の二元若しくは三元の合金の組合せの少なくとも1つを含む少なくとも1つの擬似格子整合型の膜を備え、

(i) 前記少なくとも1つの擬似格子整合型の膜の厚みが、当該少なくとも1つの擬似格子整合型の膜に関する、Matthews-Blakeslee理論により計算される予測臨界厚みを少なくとも5倍で上回り、(ii) 前記少なくとも1つの擬似格子整合型の膜が、10,000 cm<sup>-2</sup>未満の平均の貫通転位密度を有し、及び(iii) 前記少なくとも1つの擬似格子整合型の膜の前記平均の貫通転移密度が、前記窒化アルミニウム単結晶基板の平均の貫通転移密度の10倍以下の大きさである、半導体ヘテロ構造。

## 【請求項 2】

前記窒化アルミニウム単結晶基板と前記少なくとも1つの擬似格子整合型の膜との間にバッファ層をさらに備えている、請求項1に記載の半導体ヘテロ構造。

## 【請求項 3】

前記バッファ層と前記少なくとも1つの擬似格子整合型の膜との間に傾斜層をさらに備えている、請求項2に記載の半導体ヘテロ構造。

## 【請求項 4】

前記少なくとも 1 つの擬似格子整合型の膜の厚みが、前記予測臨界厚みを少なくとも 10 倍で上回る、請求項 1 から 3 のいずれか一項に記載の半導体ヘテロ構造。

【請求項 5】

前記少なくとも 1 つの擬似格子整合型の膜が実質的に In 不含である、請求項 1 から 4 のいずれか一項に記載の半導体ヘテロ構造。

【請求項 6】

前記少なくとも 1 つの擬似格子整合型の膜に対して平行な歪みが、該少なくとも 1 つの擬似格子整合型の膜と同じ組成を有する歪みのない合金の平行格子パラメータと前記少なくとも 1 つの擬似格子整合型の膜の下に設けられた緩和プラットフォームの平行格子パラメータとの差の 80 % より大きい、請求項 1 から 5 のいずれか一項に記載の半導体ヘテロ構造。 10

【請求項 7】

前記少なくとも 1 つの擬似格子整合型の膜が、Al<sub>x</sub>Ga<sub>1-x</sub>N を含み、該少なくとも 1 つの擬似格子整合型の膜の厚みが 200 nm より大きく、x が 0.65 未満である、請求項 1 から 6 のいずれか一項に記載の半導体ヘテロ構造。

【請求項 8】

前記少なくとも 1 つの擬似格子整合型の膜の厚みが 1 μm より大きい、請求項 1 から 7 のいずれか一項に記載の半導体ヘテロ構造。

【請求項 9】

前記少なくとも 1 つの擬似格子整合型の膜上に設けられた緩和されたキャップ層をさらに含む、請求項 1 から 8 のいずれか一項に記載の半導体ヘテロ構造。 20

【請求項 10】

半導体ヘテロ構造を形成する方法であって、

窒化アルミニウム単結晶基板を設け、

前記窒化アルミニウム単結晶基板上に、AlN、GaN、InN 又はそれらの任意の二元若しくは三元の合金の組合せの少なくとも 1 つを含む擬似格子整合型の膜をエピタキシャル堆積させることを含み、

(i) 前記擬似格子整合型の膜の厚みが、当該擬似格子整合型の膜に関する、Matthews-Blakeslee 理論によって計算される予測臨界厚みを少なくとも 5 倍で上回り、(ii) 前記擬似格子整合型の膜が、10,000 cm<sup>-2</sup> 未満の平均の貫通転位密度を有し、及び (iii) 前記擬似格子整合型の膜の前記平均の貫通転移密度が、前記窒化アルミニウム単結晶基板の平均の貫通転移密度の 10 倍以下の大きさである、方法。 30

【請求項 11】

前記擬似格子整合型の膜を堆積させる前に、前記窒化アルミニウム単結晶基板上にバッファ層を形成することをさらに含む、請求項 10 に記載の方法。

【請求項 12】

前記バッファ層と前記擬似格子整合型の膜との間に傾斜層を形成することをさらに含む、請求項 11 に記載の方法。

【請求項 13】

前記擬似格子整合型の膜の厚みが、前記予測臨界厚みを少なくとも 10 倍で上回る、請求項 10 から 12 のいずれか一項に記載の方法。 40

【請求項 14】

前記擬似格子整合型の膜が実質的 In 不含である、請求項 10 から 13 のいずれか一項に記載の方法。

【請求項 15】

前記擬似格子整合型の膜が Al<sub>x</sub>Ga<sub>1-x</sub>N を含み、前記擬似格子整合型の膜をエピタキシャル堆積させることができ、トリメチルアルミニウム及びトリメチルガリウムを反応器内に導入することを含む、請求項 10 から 14 のいずれか一項に記載の方法。

【請求項 16】

前記擬似格子整合型の膜の堆積の際のトリメチルガリウムの初期流量が、トリメチルガ 50

リウムの最終流量より大きい、請求項1 5に記載の方法。

**【請求項 1 7】**

前記窒化アルミニウム単結晶基板が、 $10 \mu\text{m} \times 10 \mu\text{m}$ の面積に対して約 $0.5 \text{ nm}$ 、未満の RMS 表面粗さ、約 $0.3^\circ \sim 4^\circ$ の表面の配向ずれ、及び約 $10^4 \text{ cm}^{-2}$ 未満の貫通転位密度を有する、請求項1 0から1 6のいずれか一項に記載の方法。

**【請求項 1 8】**

前記擬似格子整合型の膜の貫通転位密度が、前記窒化アルミニウム単結晶基板の貫通転位密度にほぼ等しい、請求項1 0から1 7のいずれか一項に記載の方法。

**【請求項 1 9】**

前記擬似格子整合型の膜上に、緩和されたキャップ層を形成することをさらに含み、前記擬似格子整合型の膜が、前記緩和されたキャップ層を形成した後、歪みを維持している、請求項1 0から1 8のいずれか一項に記載の方法。10

**【請求項 2 0】**

前記擬似格子整合型の膜は、 $1100$  より高い温度から $1300$  までの範囲の成長温度で堆積される、請求項1 0から1 9のいずれか一項に記載の方法。

**【請求項 2 1】**

電界効果トランジスタ、発光ダイオード及び半導体レーザからなる群から選択されたデバイスであって、

前記デバイスが、歪みヘテロ構造の少なくとも一部を含み、該歪みヘテロ構造の少なくとも一部が、20

窒化アルミニウム単結晶基板、及び

前記窒化アルミニウム単結晶基板上にエピタキシャル成長させた少なくとも 1 つの擬似格子整合型の膜であって、AlN、GaN、InN 又はそれらの任意の二元若しくは三元の合金の組合せの少なくとも 1 つを含む少なくとも 1 つの擬似格子整合型の膜を含み、

( i ) 前記少なくとも 1 つの擬似格子整合型の膜の厚みが、当該少なくとも 1 つの擬似格子整合型の膜に関する、Matthews-Blakeslee 理論により計算される予測臨界厚みを少なくとも 10 倍で上回り、( i i ) 前記少なくとも 1 つの擬似格子整合型の膜が、 $10,000 \text{ cm}^{-2}$  未満の平均の貫通転位密度を有し、及び( i i i ) 前記少なくとも 1 つの擬似格子整合型の膜の前記平均の貫通転位密度が、前記窒化アルミニウム単結晶基板の平均の貫通転位密度の 10 倍以下の大きさである、デバイス。30

**【請求項 2 2】**

前記窒化アルミニウム単結晶基板と前記少なくとも 1 つの擬似格子整合型の膜との間にバッファ層をさらに備えている、請求項2 1に記載のデバイス。

**【請求項 2 3】**

前記バッファ層と前記少なくとも 1 つの擬似格子整合型の膜との間に傾斜層をさらに備えている、請求項2 2に記載のデバイス。

**【請求項 2 4】**

前記デバイスが、少なくとも 1 つの互いに入り込むコンタクトを含む発光ダイオードである、請求項2 1から2 3のいずれか一項に記載のデバイス。40

**【請求項 2 5】**

前記少なくとも 1 つの擬似格子整合型の膜上に設けられた緩和されたキャップ層をさらに含む、請求項2 1から2 4のいずれか一項に記載のデバイス。

**【請求項 2 6】**

電界効果トランジスタ、発光ダイオード及び半導体レーザからなる群から選択されるデバイスであって、

前記デバイスが、歪みヘテロ構造の少なくとも一部を含み、該歪みヘテロ構造の少なくとも一部が、

窒化アルミニウム単結晶基板、及び

前記窒化アルミニウム単結晶基板上にエピタキシャル成長させた複数の擬似格子整合型50

の膜であって、前記複数の擬似格子整合型の膜の各々が、AlN、GaN、InN又はそれらの任意の二元若しくは三元の合金の組合せの少なくとも1つを含む、複数の擬似格子整合型の膜

を含み、

(i) 前記複数の擬似格子整合型の膜の全厚みが、当該複数の擬似格子整合型の膜に関する、Matthews-Blakeslee理論により計算される予測臨界厚みを少なくとも10倍で上回り、(ii) 前記複数の擬似格子整合型の膜が、 $10,000 \text{ cm}^{-2}$ 未満の平均の貫通転位密度を有し、及び(iii) 前記複数の擬似格子整合型の膜の前記平均の貫通転移密度が、前記窒化アルミニウム単結晶基板の平均の貫通転移密度の10倍以下の大きさである、デバイス。

10

#### 【請求項27】

前記窒化アルミニウム単結晶基板と前記複数の擬似格子整合型の膜との間にバッファ層をさらに備えている、請求項28に記載のデバイス。

#### 【請求項28】

前記バッファ層と前記複数の擬似格子整合型の膜との間に傾斜層をさらに備えている、請求項27に記載のデバイス。

#### 【請求項29】

前記複数の擬似格子整合型の膜の各々の、前記窒化アルミニウム単結晶基板の表面に対して平行な格子パラメータが、前記窒化アルミニウム単結晶基板の格子パラメータから0.2%未満だけ異なる、請求項26から28のいずれか一項に記載のデバイス。

20

#### 【請求項30】

前記複数の擬似格子整合型の膜上に設けられた緩和されたキャップ層をさらに含む、請求項26からう29のいずれか一項に記載のデバイス。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

#### 関連出願

本出願は、2007年1月26日付け出願の米国特許仮出願第60/897,572号明細書の利益及び優先権を主張するものであり、その開示全体が参照によりここに援用される。

30

#### 【0002】

#### 発明の分野

ここに開示の技術は、概略的に、格子不整合の半導体ヘテロ構造、より詳細には、擬似格子整合型(pseudomorphic)層であって、それに関する予測臨界厚みより大きな厚みを有するものに関する。

#### 【背景技術】

#### 【0003】

半導体活性デバイス層全体にわたり低欠陥密度を得ることは、実際に販売される窒化物ベースの半導体デバイスを製造する上で重要である。大きな直径を有し且つ欠陥密度の低いAlN基板を形成することは、参考によりここに援用される米国特許出願第11/503,660号明細書(「'660出願」)に記載されているように、可能である。しかし、多くの所望のデバイス用途では、AlN、GaN及びInNの合金をベースとするデバイス層をAlN基板上に成長させるのが好ましく、その場合、GaN及びInNの濃度が増大すると、AlN基板に対する格子不整合も増大する。例えば、GaNのc面における格子パラメータは、AlNの格子パラメータよりも約2.4%大きい。基板上で格子不整合層をエピタキシャル成長させる場合、典型的には、初期の層は擬似格子整合的に成長する、つまり、基板の固有の格子パラメータがエピタキシャル層の固有の格子パラメータよりも小さい場合には、エピタキシャル層が基板表面の平面で圧縮される(圧縮歪みを受ける)。一方、エピタキシャル層の固有の格子パラメータが基板の格子パラメータよりも小さい場合には、エピタキシャル層が伸ばされる若しくは引張り歪み下に置かれる。しかし

40

50

、エピタキシャル層の厚みが大きくなるにつれ、エピタキシャル層中の歪みエネルギーも大きくなり、典型的には、層は、歪みエネルギーを減らすためのいくつかの手段をとることになる。それは、転位の運動 (motion of dislocation) による塑性流れ (plastic flow) 、歪みを緩和するような表面形態構造 (surface morphological features) の形成、又は特に歪みが引張り歪みである場合に膜のクラッキングによるものであってよい。

#### 【0004】

擬似格子整合型層は、少なくとも2つの理由から有用である。第1の理由は、エピタキシャル層を低転位基板上で成長させた場合、擬似格子整合型エピタキシャル層も極めて低い転位密度で、多くの場合には基板と同じ転位密度で成長することができる。第2の利点は、得られる大きな二軸歪みによってバンド構造を調整可能であるということに基づく。例えば、歪みを使用して、重キャリアバンドと軽キャリアバンドとの間の縮退を解くことができ、その結果、より高いキャリア移動度が得られる。10

#### 【発明の概要】

#### 【0005】

A<sub>1</sub>N、GaN及びInNの合金の極めて厚い擬似格子整合型の膜を、高品質のA<sub>1</sub>N基板上に成長させる技術を提供する。擬似格子整合型の膜は、界面に平行な歪みが、その膜中の格子を変形させて基板の格子に整合させるのに必要な歪みにおおよそ等しくなっている膜である。よって、擬似格子整合型膜内の前記平行歪みは、界面に対して平行な歪みのない基板と界面に対して平行な歪みのないエピタキシャル層との間での格子パラメータの差にほぼ又はおおよそ等しくなる。ここで用いる限り、「極めて厚い」とは、エピタキシャル膜についての予測臨界厚みを実質的に（実質的にIn不含の層について少なくとも5倍で又はInを含む層については少なくとも10倍で）上回るエピタキシャル層の厚みを指し、前記予測臨界厚みは、核生成及び／又は貫通転位の運動によって歪み緩和が開始する厚みの標準的な計算（又はエネルギー平衡計算）に基づく。この予測臨界厚みは、例えば、参照によりここに援用される、Matthews and Blakeslee, J. Crystal Growth 27, 118 (1974)及び／又は米国特許第4,088,515号明細書に記載のように計算することができる。20

#### 【0006】

1つの局面で、本発明の態様は、窒化アルミニウム単結晶基板及びその上にエピタキシャル成長させた少なくとも1つの歪み層を含む半導体ヘテロ構造に関する。歪み層は、A<sub>1</sub>N、GaN、InN又はそれらの二元若しくは三元の合金の任意の組合せの少なくとも1つを含む。歪み層の厚みは、それと関連する予測臨界厚みを、少なくとも5倍又はさらには少なくとも10倍で上回る。歪み層は、実質的にIn不含であり且つ／又は約1mm<sup>-2</sup>未満の巨視的な欠陥の密度を有する。一態様では、巨視的な欠陥の密度は約0mm<sup>-2</sup>である。30

#### 【0007】

本発明の態様は、以下の1つ以上の特徴を含み得る。歪み層に対して平行な歪みは、歪み層と同じ組成の歪みのない合金と歪み層の下に設けられた緩和プラットフォームとの平行な格子パラメータの差の80%より大きい。この歪み層に対して平行な歪みは、上記差の約95%～100%にもなり得る。緩和プラットフォームは、基板そのもの又は基板と歪み層との間に形成された緩和半導体層であってよい。歪み層は、A<sub>1</sub><sub>x</sub>Ga<sub>1-x</sub>Nを含み得、約200nmより大きな厚みを有し、約0.65より小さいA<sub>1</sub>含量xを有する。歪み層の厚みは、約1μmより大きくてよく、歪み層の平均の貫通転位密度は、約10,000cm<sup>-2</sup>未満であってよい。予測臨界厚みは、Matthews-Blakeslee理論によつて計算することができる。40

#### 【0008】

別の局面で、本発明の態様は、半導体構造を形成する方法であって、窒化アルミニウム単結晶基板を供し、その上に歪み層をエピタキシャル堆積させることを含む方法に関する。歪み層は、A<sub>1</sub>N、GaN、InN又はそれらの任意の二元若しくは三元合金の組合せの少なくとも1つを含む。歪み層の厚みは、それに関連する予測臨界厚みを、少なくとも50

5倍で又はさらには少なくとも10倍で上回る。歪み層は、実質的にIn不含であり且つ/又は約 $1\text{ mm}^{-2}$ より小さい巨視的な欠陥密度を有していてよい。一態様では、その巨視的な欠陥密度は、約 $0\text{ mm}^{-2}$ である。

#### 【0009】

本発明の態様は、以下の1つ以上の特徴を含み得る。歪み層を堆積させる前に、バッファ層を基板上に形成することができ、またバッファ層と歪み層との間に傾斜層を形成することができる。歪み層はAlGaNを含むことができ、歪み層を堆積させることは、トリメチルアルミニウム及びトリメチルガリウムを反応器内に導入することを含み得る。歪み層の堆積中のトリメチルガリウムの初期流量は、トリメチルガリウムの最終流量よりも小さくてよい。予測臨界厚みは、Matthews-Blakeslee理論によって計算することができる。

窒化アルミニウム単結晶基板は、 $10\text{ }\mu\text{m} \times 10\text{ }\mu\text{m}$ の面積に対して約 $0.5\text{ nm}$ より小さいRMS表面粗さを有し、約 $0.3^\circ \sim 4^\circ$ の表面配向のずれ(misorientation)、及び約 $10^4\text{ cm}^{-2}$ より小さい貫通転位密度を有していてよい。歪み層の貫通転位密度は、窒化アルミニウム単結晶基板の貫通転位密度にはほぼ等しくなっていてよい。

10

#### 【0010】

さらに別の局面では、本発明の態様は、上述の歪みヘテロ構造の少なくとも一部を含む、電界効果トランジスタ、発光ダイオード及び半導体レーザ(レーザダイオード)からなる群から選択されるデバイスに関する。このデバイスは、少なくとも1つの互いに入り込む(嵌合する)コンタクトを有する発光ダイオードであってよい。

20

#### 【0011】

別の局面では、本発明の態様は、電界効果トランジスタ、発光ダイオード及び半導体レーザからなる群から選択される、歪みヘテロ構造の少なくとも一部を含むデバイスであって、歪みヘテロ構造が、窒化アルミニウム単結晶基板及びその上にエピタキシャル成長させた複数の歪み層を含むものに関する。複数の歪み層の各層は、AlN、GaN、InN又は任意のそれらの任意の二元若しくは三元の合金の組合せの少なくとも1つを含む。複数の歪み層の全厚みは、それに関連(対応)する予測臨界厚みを、少なくとも5倍で又はさらには少なくとも10倍で上回る。複数の歪み層の各層の、窒化アルミニウム単結晶基板の表面に対して平行な格子パラメータは、窒化アルミニウム単結晶基板の格子パラメータとは $0.2\%$ 未満で異なる。複数の歪み層(全ての層を含む)の1つ以上は、In不含であってよい。

30

#### 【図面の簡単な説明】

#### 【0012】

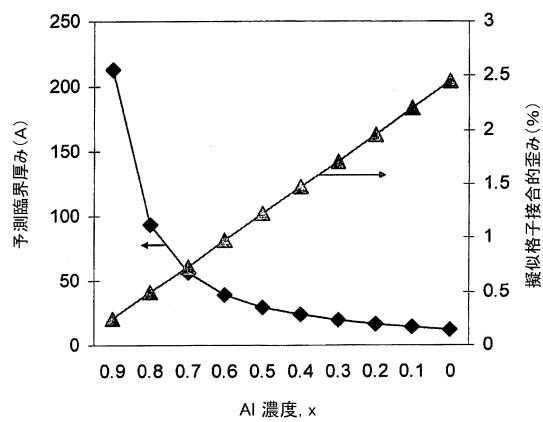

【図1】AlN基板上に形成された様々なAl含量×の $\text{Al}_x\text{Ga}_{1-x}\text{N}$ 層についての、予測臨界厚み及び擬似格子整合型歪みのグラフである。

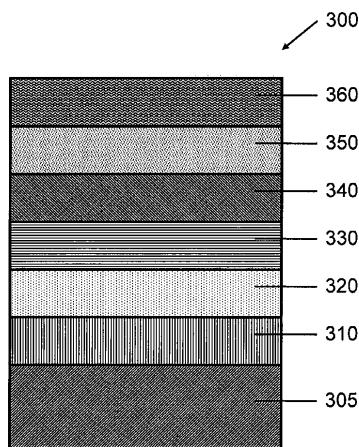

【図2】基板上に形成された擬似格子整合型歪み層を示す概略図である。

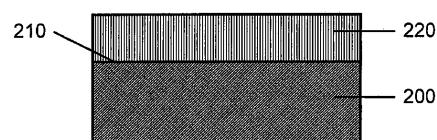

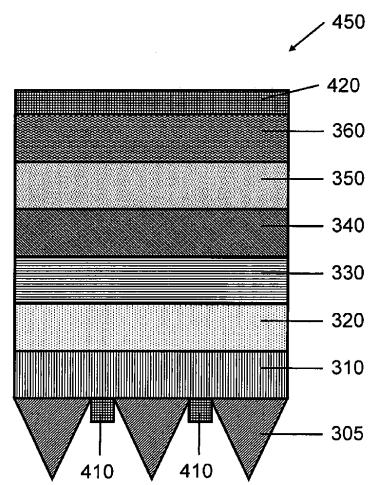

【図3】擬似格子整合型歪み層ベースのデバイス構造の概略図である。

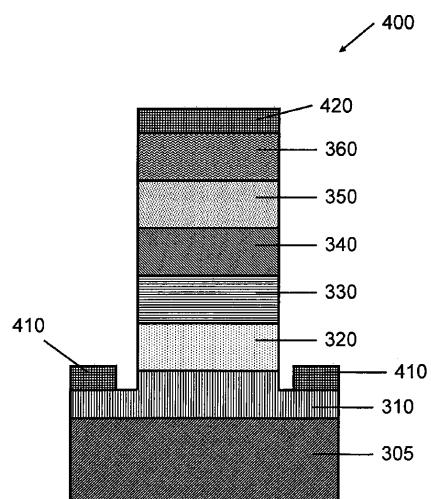

【図4A】図3の層構造を利用した、プロセス工程後のデバイスの概略図である。

【図4B】図3の層構造を利用した、プロセス工程後の別のデバイスの概略図である。

#### 【発明を実施するための形態】

#### 【0013】

40

図面において、類似の番号は概して、異なる図面においても同じ部分を指す。また、図面は必ずしも正しい縮尺で描かれておらず、概して本発明の原則を示すように示されている。以下の説明では、本発明の様々な態様を図面を参照して記述する。

#### 【0014】

#### 製造技術

Matthews-Blakeslee理論に基づいて計算された予測臨界厚みを、c面AlN基板上に成長させた $\text{Al}_x\text{Ga}_{1-x}\text{N}$ 層中のAl濃度の関数として、図1に示す。図1には、緩和なしで得られた $\text{Al}_x\text{Ga}_{1-x}\text{N}$ 層の擬似格子整合型の歪みも示す。予想に反して、予測臨界厚みよりずっと大きな厚みを有する擬似格子整合型層を成長させることができることが見出された。例えば、図1に示すように、 $x = 0.6$ での $\text{Al}_x\text{Ga}_{1-x}\text{N}$ 層の臨

50

界厚みは、約 40 ナノメートル (nm) である。さらに、本発明者は、この Al 濃度の層を 1 マイクロメートル ( $\mu\text{m}$ ) を上回る厚みにまで成長させ、しかも極めて高品質で鏡面のように滑らかな擬似格子整合型の歪み層を得ることができた。ここで用いる限り、「高品質」という用語は、約  $10^{-6} \text{ cm}^{-2}$  以下の貫通転位密度を有するエピタキシャル層を指す。特定の態様では、高品質層は、約  $10^{-4} \text{ cm}^{-2}$  以下又はさらには約  $10^{-2} \text{ cm}^{-2}$  以下の貫通転位密度を有する。また、「擬似格子整合型」という用語は、ここでは、下層の基板の格子パラメータの少なくとも約 80% にまで歪ませた（つまり、その固有の格子パラメータに対し約 20% 未満で緩和されている）エピタキシャル層を指すものとして用いられる。いくつかの態様では、擬似格子整合型層は、下層の基板の格子パラメータに対しほぼ完全に歪ませていてよい。「鏡面のように滑らかな」という用語は、 $5 \mu\text{m} \times 5 \mu\text{m}$  の面積における約 5 nm 未満の層二乗平均平方根での（「RMS」）表面粗さ（原子間力顯微鏡によって測定）を指す。好ましい態様では、RMS 表面粗さは、 $5 \mu\text{m} \times 5 \mu\text{m}$  の面積において約 1 nm 未満である。10

#### 【0015】

図 2 に、本発明によって製造された厚い擬似格子整合型半導体層を示す。半導体基板 200 が設けられている。一態様では、半導体基板 200 は、AlN を含むか又は本質的に AlN からなっている。半導体基板 200 の上面 210 が、その上に 1 つ以上のエピタキシャル層を堆積させる前に、（例えば化学機械研磨による）平坦化又は洗浄の少なくとも 1 つによってエピタキシャル成長のために準備（処理）される。次に、半導体基板 200 上に、歪みエピタキシャル層 220 を、例えば有機金属気相エピタキシーによって、その予測臨界厚みを超える厚みにまで堆積させる。図 1 より分かるように、AlN からなる半導体基板 200 上に成長させた、 $\text{Al}_{x}\text{Ga}_{1-x}\text{N}$  からなる例示的なエピタキシャル層 220 の予測臨界厚みは、Al 含量  $x$  に依存する。一態様では、エピタキシャル層 220 の厚みは、その予測臨界厚みを少なくとも 5 倍で又はさらに少なくとも 10 倍で上回るが、エピタキシャル層 220 は擬似格子整合型を維持する。エピタキシャル層 220 の厚みは、その予測臨界厚みを 20 倍以上で上回りえるすることもある。20

#### 【0016】

特定の態様では、エピタキシャル層 220 は、実際、複数の個別層からなっており、各層は、半導体基板 200 の格子パラメータに対して（に近づくように）擬似格子整合的に歪ませていてよい。この複数の層は、例えば AlN、InN 及び / 又は GaN を含み、III 族原子の 1 つ以上の濃度が厚みと共に変化する傾斜する組成を有する複数の層を含んでいてよい。このような層では、個々の段階で又は線形的に組成が傾斜していてよい。30

#### 【0017】

歪みエピタキシャル層 220 は、半導体基板 200 上に形成された任意の緩和半導体層（図示せず）上に設けることができる。この場合、エピタキシャル層 220 中の歪み及びその予測臨界厚みは、半導体基板 200 の格子パラメータの関数ではなく、緩和半導体層の格子パラメータの関数であってよい。この場合も、エピタキシャル層 220 は擬似格子整合を維持し、エピタキシャル層 220 の厚みは、前記予測臨界厚みを少なくとも 5 倍で上回る。特定の態様では、エピタキシャル層 220 の厚みは、前記予測臨界厚みを、少なくとも 10 倍で又はさらには少なくとも 20 倍で上回る。よって、半導体基板 200 又は任意の緩和半導体層は、緩和「プラットホーム」として機能することができ、エピタキシャル層 220 が、そのプラットホームに適合するように歪ませられる。40

#### 【0018】

基板、例えば特定の AlN 基板上に、低い貫通転位密度（「TDD」）で、III 族窒化物の極めて大きな歪みを有する合金を成長させることができることのできる能力は、（i）基板結晶品質、（ii）表面処理、（iii）基板表面の結晶配向、（iv）合金濃度、（v）成長中の基板温度及び V - III 比を含む成長条件、並びに / 又は（vi）合金濃度の傾斜率に依存することが分かった。エピタキシャル層 220 の緩和は、エピタキシャル成長の際に低い表面粗さを維持することによって最小限化又は排除することができる。層表面の粗面化又はアイランド（island）の形成は、層の不都合な緩和を招き得る。表面に伝搬し50

た基板中の欠陥又は不適切な表面洗浄によって生じ得る半導体基板 200 の表面での欠陥も、エピタキシャル層 220 の粗面化を引き起こし得る。粗面化が生じると、歪みの緩和が、エピタキシャル表面上のテラス及びアイランドの側壁で生じる。このテラスやアイランドが融合すると、融合境界で、不都合な高い貫通転位密度が形成されてしまう。

#### 【0019】

エピタキシャル堆積中にステップフロー成長 (step flow growth) を維持することによつて、緩和の防止を助成され、ステップフロー成長のための適切な条件は、半導体基板 200 の基板配向に依存する。基板が極めて軸上近くで配向している（つまり、基板の表面法線が、主たる結晶軸に極めて近似に整列している）場合、基板の表面にわたってのステップの密度は低い。よつて、成長するエピタキシャル層にステップのエッジに組み込まれる、つまり、ステップフロー成長が維持されるためには、到来する Al、Ga 又は In 原子が、比較的大きな距離で拡散し易くなつていなければならぬ。よつて、ステップフロー成長は、（i）成長種の到来原子の長距離拡散を増大させること及び / 又は（ii）ステップのエッジに到達するのに必要とされる拡散距離を減少させること（つまり、表面におけるステップの密度を増大させること）によつて維持することができる。上記長距離拡散は、より高温（つまり、約 1100 まで）で又は In 不含の場合には高い Al 含量（例えば、約 50% より大きな Al 含量）で、成長温度を約 1100 より高い温度から約 1300 までの範囲に増大させてエピタキシャル成長を行うことによつて増大させることができる。いくつかの態様では、例えば、50% より大きな Al 濃度に対し、長距離拡散は、エピタキシャル反応器内で、窒素種（つまり V 族種）の III 族種と比較した比率を減少させることによつて、増大させることもできる。一態様では、成長種の長距離拡散を増大させるために有利な V - III 比率は、約 1,000 未満であり、約 10 未満であつてもよい。半導体基板 200 上でのステップのエッジの密度も、主たる結晶軸と基板の表面法線との間での配向のずれを大きくすることによつて、増大させることができる（それにより、ステップに到達するのに必要な所要拡散距離が低減する）。一態様では、半導体基板 200 の配向のずれは約 1° である。

#### 【0020】

歪み緩和に対するキネティックバリア（動力学的バリア、kinetic barriers）も、厚い擬似格子整合型のエピタキシャル層を生成するために、有利に利用することができる。AlN、GaN 及び InN の任意の合金（GaN 又は InN の含量がゼロではない）は、下層の AlN 基板よりも大きな緩和格子パラメータを有するので、これらのエピタキシャル膜は、典型的には、クラッキングによって緩和することはない。緩和は、AlN 基板とエピタキシャル合金層との間の界面に平行に走るミスフィット転位の形成によつて起こり得る。このようなミスフィット転位は、半導体基板 200 からエピタキシャル層 220 へ伝搬する既存の貫通転位の運動によつて、又は表面から若しくは基板 200 の表面上のいくつかの巨視的な欠陥から形成される新しい転位ループによつて起こり得る。よつて、半導体基板 200 中の欠陥源の排除によつて、緩和に対するキネティックバリアが生成し、厚い擬似格子整合型のエピタキシャル層 220 の製造が簡単になる。一態様で、半導体基板 200 は、約  $10^6 \text{ cm}^{-2}$  未満の貫通転位密度を有する。別の態様で、半導体基板 200 は、約  $10 \text{ cm}^{-2}$  未満又はさらに約  $10^2 \text{ cm}^{-2}$  未満の貫通転位密度を有する。半導体基板 200 は、約  $100 \text{ cm}^{-2}$  未満の粒子表面欠陥密度を有してもよい。このような最適化された半導体基板の利用によつて、緩和機構としての既存の転位の滑り及び表面欠陥での転核生成が最小限化又は排除される。残りの緩和機構は、転位ループの表面核生成であるが、これは、厚い擬似格子整合型エピタキシャル層の製造を容易にするには十分に高い歪みエネルギーでしか起こらない。したがつて、その予測臨界厚みより少なくとも約 5 倍大きい厚みを有する厚い歪みエピタキシャル層 220 の製造は、容易である。さらに、In には、転位の運動及びそれと同時に起る緩和を妨げる追加的な効果があるので、In を含む歪みエピタキシャル層 220 は、その予測臨界厚みより大きな擬似格子整合型厚みを少なくとも約 10 倍で達成することができる。

#### 【0021】

10

20

30

40

50

加えて、極めて大きな歪み合金の厚いエピタキシャル層の製造では、半導体基板200の特定の結晶配向が、特に好ましい。特に、Liuらは、GaN及びその合金のウルツ鉱型結晶構造の主たる滑りシステムが<11.2>{00.2}であることを指摘している。(参照によりその開示全体がここに援用される、R. Liu, J. Mei, S. Srinivasan, H. Omiya, F.A. Ponce, D. Cherns, Y. Narukawa and T. Mukai, 「Misfit Dislocation Generation in InGaN Epilayers on Free-Standing GaN」、Jap. J. Appl. Physics 45, L549 (2006)を参照。)この滑りシステムは、良好に配向されたc面基板(つまり、表面法線が結晶のc軸と整合している基板)において活性ではなく、それというのは、格子不整合歪みは、この面に沿って転位が移動するいかなる歪み緩和も起こさないからである。この現象は、c面基板に対する許容可能なミスカット(mis cut)を限定し、その上の極めて大きな歪み及び/又は厚い擬似格子整合型エピタキシャル層を可能にする。しかし、上述のように、有限の表面の配向のずれによってステップフロー成長が簡単になる。よって、一様では、半導体基板200の配向のずれは、0°より大きく、約4°未満である。

#### 【0022】

1つの工程で、低転位密度(ほぼ $5 \times 10^3 \text{ cm}^{-2}$ )の大きなc面AlN基板を、'660号出願明細書に記載のように、準備した。この基板のミスカットは、約1°であった。c面AlN基板のAl極性表面、つまり(0001)面を、参照によりその開示全体がここに援用される米国特許第7,037,838号明細書(「'838号特許明細書」)に記載のように、準備した。基板をAixtron model 200/4 RF-S有機金属気相エピタキシー(「OMVPE」)反応器内に導入した後、水素及びアンモニアガス混合物の流れ下で、基板を1100まで加熱した。続いて、トリメチルアルミニウム('TMA')を導入し、厚み $0.3 \mu\text{m}$  AlNバッファ層を、基板上に、 $0.6 \mu\text{m}/\text{時}$ のおおよその成長速度で成長させた。続いて、傾斜層 $\text{Al}_x\text{Ga}_{1-x}\text{N}$ を、TMGガス流の量を上昇させ、TMAガス流の量を低下させてトリメチルガリウム('TMG')を切り換えることによって成長させ、それにより、15分の間隔にわたり目標のAl%に達し、線形的に傾斜(勾配)する合金が約 $0.1 \mu\text{m}$ が成長した。この遷移層の後、TMA及びTMG流を一定に維持し、63%Al濃度及び約 $0.6 \mu\text{m}$ 厚みの最終層を、 $1.0 \mu\text{m}/\text{時}$ のおおよその成長速度で成長させた。成長の間、チャンバ圧力は、上限 $25 \sim 100 \text{ mbar}$ までに維持した。V-III比率は、成長連続工程中では $500 \sim 2,000$ に維持した。層が予測臨界厚みを1桁より大きな度合いで上回っていても、平行な歪み(つまり、基板の平面での歪み)は、0.8%よりわずかに大きく、擬似格子整合型成長を示すと測定された。 $\text{Al}_x\text{Ga}_{1-x}\text{N}$ 層に対する、(00.2)及び(10.2)反射についての複結晶ロッキング曲線幅(Philip X'Pertシステムにより測定)は、それぞれ50秒角及び60秒角であった。界面に対して平行な歪みは、ほぼ1%であることが測定され、エピタキシャル層は、下層のAlN基板に対して擬似格子整合型であった。 $\text{Al}_x\text{Ga}_{1-x}\text{N}$ エピタキシャル層における貫通転位密度を決定するために、エッチピット密度が溶融KOHのエッチングを利用して測定される。測定された密度は、 $0.8 \sim 3 \times 10^5 \text{ cm}^{-2}$ の範囲であった。

#### 【0023】

同様の工程が利用されて、Al濃度50%の $\text{Al}_x\text{Ga}_{1-x}\text{N}$ 合金の厚み $0.6 \mu\text{m}$ のエピタキシャル層を成長させた。この場合、界面に平行な歪みは、~1%にとどまり、これは完全な擬似格子整合型の歪みの約80%であった。

#### 【0024】

別の工程では、約 $5 \times 10^3 \text{ cm}^{-2}$ の転位密度を有する大きなc面AlN基板を、第'660号出願明細書に記載のように準備した。c面AlN基板のAl極性表面(約1.5°で不整合)を、第'838号特許明細書に記載のように処理した。基板をVeeco D180 OMVPE反応器内に導入した後、基板を、水素及びアンモニアガス混合物の流れ下で、約1100に加熱した。さらに、TMAを導入し、厚み $0.4 \mu\text{m}$ のAlNバッファ層を $0.4 \mu\text{m}/\text{時}$ のおおよその成長速度で基板が成長した。次に、傾斜層 $\text{Al}_x\text{Ga}_{1-x}\text{N}$ を、TMGガス流を維持しながらTMG流の量を上昇させながらTMGを切り換え導

10

20

30

40

50

入することによって成長させ、それにより、6分の間隔にわたり目標のA 1 %に達し、線形的に傾斜した合金約0.05 μmを成長させた。この遷移層の後、TMA及びTMG流を一定に維持し、~58%のA 1濃度及び約0.5 μmの厚みを有する最終層を、0.8 μm / 時のおおよその成長速度で成長させた。成長の間、チャンバ圧力を、約20 Torrに維持した。V - I II比率は、成長連続工程の間、900~3,200に維持した。層が予測臨界厚みを1桁を超える大きさで上回っていても、平行な歪みは、1.0%よりわずかに大きく、擬似格子整合型成長であったことが測定された。

#### 【0025】

不完全な表面処理は転位密度を増大させるが、これは、表面処理を改善することによって修正することができる。低欠陥AlN基板について、適切な表面処理技術が、第'83 10 8号特許明細書及び米国特許出願第2006/0288929号明細書に記載されており、その開示内容全体が参照によりここに援用される。

#### 【0026】

擬似格子整合型エピタキシャル層220は、格子緩和をほとんど受けていないか全く受けていないので、その層における貫通転位密度は、半導体基板200の貫通転位密度にはほぼ等しくなり得る。例えば、第'660号出願明細書に記載の技術によって成長させたAlNプールから得た基板は、極めて低い転位密度、つまり $10,000 \text{ cm}^{-2}$ 未満、典型的には約 $1,000 \text{ cm}^{-2}$ 未満、特定の態様では、 $500 \text{ cm}^{-2}$ 未満、さらには $100 \text{ cm}^{-2}$ 未満の転位密度を有していてよく、これは、その上に成長させた擬似格子整合型エピタキシャル層によって「受け継がれる」。別の態様では、エピタキシャル層220の貫通転位密度は、半導体基板200の貫通転位密度の約10倍以下の大きさである場合がある。このような低い貫通転位密度によって、高い効率の紫外発光ダイオード（「UV LED」）及び半導体レーザ（「LD」）、並びに電子デバイス、例えば高周波数（例えば、 $> 2 \text{ GHz}$ ）、高出力動作用のトランジスタの製造が可能となる。

#### 【0027】

一態様で、歪みエピタキシャル層220は、例えばアイランド及びピンホールのような巨視的な欠陥の形成によって引き起こされた局所的な弾性歪み緩和を実質的に含まない（後述する）。さらに、エピタキシャル層220中の歪みは、ほぼ完全に、基板200に対する格子不整合の結果となり得る。例えば、エピタキシャル層220には、基板200に対する熱膨張の不整合のために、歪みがほぼない。

#### 【0028】

デバイスで利用される場合には、エピタキシャル層220における極性作用（polarization effects）は、デバイス性能に影響を与える。非極性の上表面210（例えば、AlNを含む基板200のa面又はm面）上に製造されたエピタキシャル層220では、極性の作用は層内で最小限化される。このことにより、その後に形成される極性作用に対して元来無反応のデバイスが表面と関連付けられ、極性表面、例えばc面上に形成された従来のデバイスで観察されるdc-RFの分散が排除されるか又は最小限化される。一方、[0001]方向に沿ってc面上で成長させた擬似格子整合型構造は、大きな極性作用を有し得、これは、デバイス内での電荷の分布に影響を与える。チャネル／バリア境界での極性電荷は、AlNバッファ構造から遷移するAlN/GaNヘテロ境界に関連する背面欠乏作用（backside depletion effects）に対抗するように、慎重に増大させるのが好ましい。

#### 【0029】

##### デバイスでの利用

遠紫外LED（ディープUV LED）の性能を制限する重要な問題は、活性デバイス領域における高い転位密度であり、これは、電気効率、内部量子効率（「IQE」）及びデバイスの寿命を低下させる。簡単に、参照によりその開示内容全体がここに援用される、Solid State Lighting Report (Dept. of Energy, 2007)で述べられているように、電気的効率（電力効率）、つまり $v$ （加えられる電圧及び電荷の積で除した光子エネルギー、つまり $h/eV$ として定義される）は、光子エネルギーに変換される電気エネルギーの量

10

20

30

40

50

を表す。加えられる順方向電圧は、ダイオードの性質によって決められ、所与の入力電力に対して最高の電流を得るためにできるだけ低くする（そして光子に変換可能な電子の数を最大にする）ことが望ましい。IQEは、半導体チップの活性領域で生成された光子の、LEDに注入された電子に対する比である。

#### 【0030】

図3を参照すると、擬似格子整合型のUV発光ダイオード（「PUVLED」）構造300が形成されている。1つ以上の半導体材料を含むか又はその材料から本質的になる半導体基板305が設けられている。一態様では、半導体基板305は、III族窒化物半導体材料、例えば、AlNを含むか又はその材料から本質的になる。半導体基板305は、そのc軸とその表面法線とがなす角度が0.3°～4°であるようにミスカットされていてよい。好ましい態様では、半導体基板305の表面の配向のずれは約1°である。半導体基板305の表面は、Al極性又はN極性を有していてよく、例えば化学機械研磨によって平坦化されていてよい。一態様では、半導体基板305の表面を、第'838号特許明細書に記載のように準備した。半導体基板のRMS表面粗さは、好ましくは、10μm×10μmの面積に対して約0.5nm未満である。いくつかの態様では、原子間顕微鏡によって精査した場合に、表面上で原子レベルのステップが検出可能である。半導体基板305の貫通転位密度は、例えば5分間の450でのKOH-NaOH共晶エッティング後のエッチピット密度測定を利用して測定することができる。好ましくは、貫通転位密度は、約 $2 \times 10^3 \text{ cm}^{-2}$ 未満である。いくつかの態様では、基板305は、半導体基板200を参照して上述したような、さらに低い貫通転位密度を有している。半導体基板305は、例えばAlNのような半導体基板300中に存在する同じ半導体材料を含むか又はその材料から本質的になるホモエピタキシャル層（図示せず）で上部を覆われていてよい。10

#### 【0031】

一態様では、傾斜バッファ層310が半導体基板305上に形成されている。傾斜バッファ層310は、例えば $\text{Al}_x\text{Ga}_{1-x}\text{N}$ のような1つ以上の半導体材料を含むか又はその材料から本質的になっていてよい。好ましい態様では、傾斜バッファ層310は、基板305との界面で、半導体基板305の組成にほぼ等しい組成を有しており、それにより、二次元の成長が促進され、不都合なアイランド形成（そのようなアイランド形成により、傾斜バッファ層310及び後続の成長層での不都合な弾性の歪み緩和が起こる）が回避される。後続の成長層（後述する）との界面での傾斜バッファ層310の組成は、一般に、デバイスの所望の活性領域の組成に近くなるように選択される（例えば、PUVLEDからの所望の波長での発光が得られる $\text{Al}_x\text{Ga}_{1-x}\text{N}$ 濃度で）。一態様では、傾斜バッファ層310は、約100%のAl濃度xから約60%のAl濃度xへと傾斜する $\text{Al}_x\text{Ga}_{1-x}\text{N}$ 傾斜を含む。20

#### 【0032】

続いて、底部コンタクト層320が傾斜層310上に形成され、この底部コンタクト層320は、本質的に少なくとも1つの不純物、例えばSiでドープされた $\text{Al}_x\text{Ga}_{1-x}\text{N}$ を含むか又はそれから本質的になっていてよい。一態様では、底部コンタクト層320中のAl濃度xは、傾斜層310中の最終のAl濃度xにほぼ等しい。底部コンタクト層320は、デバイス製造（後述の通り）後に電力集中を防ぐのに且つ/又はコンタクトを製造するためのエッティング中に停止するのに十分な厚みを有していてよい。例えば、底部コンタクト層320の厚みは、約200nm未満であってよい。そのような厚みの底部コンタクト層320を利用する場合、図4Bを参照して以下に記載するように、背面コンタクトを有するものとして最終のPUVLEDを製造することができる。多くの態様で、層が擬似格子整合型である場合には、低い欠陥密度が維持されるので、底部コンタクト層320は、厚みが小さくても高い導電性を有する。30

#### 【0033】

多重量子井戸（「MQW」）層330が、底部コンタクト層320上に製造される。MQW層330は、PUVLED構造300の「活性領域」に相当し、複数の量子井戸を含4050

み、その量子井戸のそれぞれは、AlGaNを含む又はこれから本質的になっていてよい。一態様では、MQW層330の各周期は、 $Al_xGa_{1-x}N$ 量子井戸及び $Al_yGa_{1-y}N$ 量子井戸を含み、ここで、xはyと異なる。好ましい態様で、xとyの差は、活性領域での電子及び正孔の良好な閉じ込めが得られるように十分に大きくなっている。これにより、放射性の再結合の、非放射性の再結合に対する比を高くすることができる。一態様では、xとyとの差は約0.05であり、例えばxは約0.35で、yは約0.4である。しかし、xとyの差が過度に大きい、例えば、約0.3より大きいと、MQW層330の形成中に不都合なアイランド形成が起こってしまう。MQW層330は、複数の周期を含んでいてよく、約50nm未満の全厚みを有していてよい。MQW層330上には、任意の薄い電子ブロック（又はn型コンタクトがデバイスの上部に置かれている場合には正孔ブロック）層340を形成することができ、この層340は、例えば、Mgのような1つ以上の不純物でドーピングされていてよい $Al_xGa_{1-x}N$ を含むか又はそれから本質的になっている。電子ブロック層340は、例えば約20nmの厚みを有している。電子ブロック層340の上には上部コンタクト層350が形成され、この上部コンタクト層350は、本質的に1つ以上の半導体材料、例えば、Mgのような少なくとも1つの不純物でドープされた $Al_xGa_{1-x}N$ を含むか又はそれから本質的になっている。上部コンタクト層350は、n型又はp型にドープされているが、底部コンタクト層310の導電性とは反対の導電性を有している。上部コンタクト層350の厚みは、例えば約50nm～約100nmである。上部コンタクト層350は、キャップ層360でキャップされており、そのキャップ層360は、上部コンタクト層350と同じ導電性でドープされた1つ以上の半導体材料を含むか又はその材料から本質的になる。一態様では、キャップ層360は、MgでドープされたGaNを含み、約10nm～約200nm、好ましくは約50nmの厚みを有する。いくつかの態様では、高品質のオーミックコンタクトを上部コンタクト層350に直接形成することができ、キャップ層360は省かれる。層310～350が全て擬似格子整合型であることが好ましいが、キャップ層360は、PUELED構造300の性能に不都合な影響を与える不都合な欠陥がその下の活性層内に導入されることなしに緩和させることもできる。図4A及び4Bを参照して以下に詳細に説明するように、エッチング及び最終のコンタクト形成によって、PUELED構造300の形成が終了する。層310～350のそれぞれは擬似格子整合型であり、上述のように、各層はそれぞれ、その予測臨界厚みより大きな厚みを有していてよい。さらに、層310～350を含む集合層構造は、集合体として考えた複数層についての予測臨界厚みより大きな全厚みを有していてよい（つまり、各層の厚みが、個別に考えた場合の各予測臨界厚みよりそれぞれ小さかったとしても、その構造全体が、複数層の構造について1つの予測臨界厚みを有する）。

#### 【0034】

好ましい態様では、PUELED構造300（及び/又は上述の歪みエピタキシャル層220）は、ピンホール、マウンド（mounds）若しくは「Vピット（V pits）」のような巨視的な欠陥を実質的に含まずに（つまり、約1mm<sup>2</sup>未満又はさらには約0mm<sup>-2</sup>まで）形成されている。そのような欠陥は、例えば、GaN基板上の、高い転位密度を有する歪みInGaN層の成長で観察されることが多い。（参照によりここにその開示全体が援用される、T. L. Song, J. Appl. Phys. 98, 084906 (2005)を参照）。巨視的な欠陥は、擬似格子整合型層内の歪みの局所的な緩和を引き起こすか、量子井戸構造の中止及び/又はp型及びn型コンタクトの短絡によって、エピタキシャル層から製造されたデバイスに不利な影響を与えるか、或いは層の表面粗さを増大させる。巨視的な欠陥のないPUELED構造300は、有利には、約0.1mm×約0.1mmより大きなサイズのPUELEDの製造において使用することができる。

#### 【0035】

PUELED構造300は、約210nm～約320nmの範囲の、例えば約280nmの発光波長を有する。PUELED構造300における層の少なくともほとんどが擬似格子整合型であるので、層中の貫通転位密度は約10<sup>5</sup>cm<sup>-2</sup>であり、基板305内の

貫通転位密度とほぼ等しくなつていてよい。一態様では、P U V L E D 構造 3 0 0 は、約 10 % より大きな（又はいくつかの態様ではさらに約 20 % より大きな）壁コンセント効率（wall-plug efficiency）（つまり、全光学出力を全電力入力で除したもの）及び／又は約 10,000 時間を超える寿命を有している。

#### 【 0 0 3 6 】

半導体レーザ（L D）構造も、擬似格子整合型構造から利益を得ることができる。好ましいL D構造は、P U V L E D 構造 3 0 0 の構造と類似しているが、光子を適切に閉じ込め共振空洞を作り出す層を備えている。端面発光型L Dでは、共振空洞は、成長方向に対して垂直に方向付けされ、ミラーは、半導体層構造を劈開又はエッティングすることによって形成される。この場合、M Q W層 3 3 0 下の層 3 2 0 並びにM Q W上の層 3 4 0 及び 3 5 0 は、有効クラッド層として働くように変更する必要があり、それにより、放出された光子が、顕著な吸収なく、層成長方向に対して垂直方向に効果的に伝搬することが保証される。例えば、図 3 で概略的に参照番号 3 2 0 、 3 4 0 及び 3 5 0 で示された層の数を増大させることができる。別態様では、垂直面発光型レーザ（「V C S E L」）で、層 3 2 0 、 3 4 0 及び 3 5 0 は、ミラーとして働く複数層構造（例えばBragg反射体）に置き換えることができ、半導体層の成長方向に沿って光子を方向付ける光子空洞（photon cavity）が作られる。このように、窒化物半導体で製造された半導体L Dは、約 3 0 0 n m より短い、いくつかの態様では約 2 8 0 n m より短い発光波長を有してよい。

#### 【 0 0 3 7 】

図 4 A 及び 4 B を参照すると、P U V L E D 構造 3 0 0 と関連する異なるコンタクト様式を使用することができる。P U V L E D 4 0 0 は、エッティングによって、例えば、P U V L E D 構造 3 0 0 中で層連続体を通しての、底部コンタクト層 3 1 0 で若しくは底部コンタクト 3 1 0 内で停止させるプラズマエッティングによって形成される。コンタクト 4 1 0 、 4 2 0 は、底部コンタクト層 3 1 0 及びキャップ層 3 6 0 上にそれぞれ形成される。コンタクト 4 1 0 、 4 2 0 は、導電性の材料、例えば金属、例えばN i / A u 合金（典型的には、p 型コンタクトに対して使用される）又はT i / A l / T i / A u スタック（典型的には、n 型コンタクトに対して使用される）から形成されており、例えばスパッタリング又は蒸着によって形成されている。コンタクト 4 1 0 、 4 2 0 は、同じ又は異なる導電性の材料を含むか又はその材料から本質的になる（この場合、最適なコンタクトが、反対符号にドープされた底部コンタクト層 3 1 0 及びキャップ層 3 6 0 に形成される）。コンタクト 4 2 0 は、紫外線（「U V」）反射器も含んでいてよい。U V 反射器は、コンタクト 4 2 0 に向かって発光する光子を再度方向付けする（光子が半導体層構造から逃げることができないように）こと並びにP U V L E D 4 0 0 、 4 5 0 の所望の発光面、例えば底部表面に向けて光子を再度方向付けることによって、デバイスの活性領域において生成される光子の抽出効率を改善するように設計される。

#### 【 0 0 3 8 】

P U V L E D 4 5 0 では、キャップ層 3 6 0 上にコンタクト 4 2 0 を形成することもできる。しかし、コンタクト 4 1 0 （複数の別個のコンタクトであってよい）は、P U V L E D 活性層構造の背面に形成される。この場合には、基板 3 0 5 は、場合によっては、例えば機械摩碎又は研磨によって、約 1 5 0 μ m に薄板化される。例えばN i から形成されたマスク層（図示せず）が、基板 3 0 5 の背面に形成され、標準的なフォトリソグラフィによってパターン形成される。基板 3 0 5 の露出した領域は、例えばプラズマ又は湿式エッティングによってエッティングされ、そのエッティングは、底部コンタクト層 3 1 0 上で又は底部コンタクト層 3 1 0 内で停止する。多くの態様で、基板 3 0 5 が純粋なA l N であるので、底部コンタクト層 3 1 0 上でのエッティング停止は、プラズマエッチャーハウジング中のG a の検出によって容易に行われる。そして、コンタクト 4 1 0 が、底部コンタクト層 3 1 0 の露出した部分上に形成される。コンタクト 4 1 0 は、P U V L E D 4 5 0 からの光出力を最大限にするように互いに入り込むものであってよい。重要なことには、基板 3 0 5 の背面で形成されるテープを有する構造が、層 3 4 0 中のM Q W構造からの遙かに大きな発光角度からの光子を集合させ、図 4 B に示すように基板 3 0 5 のエッティングされた背面に示

10

20

30

40

50

されたテーパー構造の先端近くの発光表面から光子を外方へ向けることを助成する。これにより、P U V L E D の光子抽出効率が実質的に向上し、それというのは、これらの半導体材料の屈折率が大きいために、テーパー構造なしでは、平坦な発光表面（例えば図 4 A に示すもの）に向けられた小さな割合の光子しか発光のための臨界許容円錐（critical acceptance cone）内に收まらないからである。A 1 N において、許容円錐は約 25° でしかも、これは、平坦な発光表面（平坦な表面に向けて方向付けされた半球体内への放射の等方性発光と仮定）に向けて方向付けされた光子の約 90% は全内部反射を受けてデバイスから逃げることができず、有用な発光として実現することができないことを意味する。

## 【 0 0 3 9 】

10

ここで用いられる言葉及び専門用語は、制限のためではなく説明のための語として用いられており、このような語及び表現の使用において、開示し記述した特徴と同等のものを何ら排除する意図はなく、本発明の範囲内で様々な変更が可能であることが理解されるであろう。

【 図 1 】

【 図 3 】

【 図 2 】

FIG. 3

FIG. 2

【図 4 A】

FIG. 4A

【図 4 B】

FIG. 4B

---

フロントページの続き

(72)発明者 スマート , ジョセフ , エイ

アメリカ合衆国ノースカロライナ州 28177 , ムーアスヴィル , ブルーム・ロード・358

(72)発明者 グランダスキー , ジェイムス , アール

アメリカ合衆国ニューヨーク州 12208 , アルバニー , マートル・アヴェニュー・758 , セカンド・フロア

(72)発明者 リウ , シウェン

アメリカ合衆国マサチューセッツ州 01720 , アクトン , キャッスル・ドライブ・1

審査官 河合 俊英

(56)参考文献 特開平 09 - 083016 (JP, A)

特開 2005 - 167275 (JP, A)

特表 2005 - 536873 (JP, A)

特開 2005 - 210084 (JP, A)

特開 2006 - 319107 (JP, A)

特開 2002 - 274996 (JP, A)

Sandra B. Schujman , Very low dislocation density AlN substrates for device application

s , Proc. of SPIE , 2006年 , Vol. 6121 , 61210K-1~61210K-7

Toshio Nishida , AlGaN-based ultraviolet light-emitting diodes grown on bulk AlN substrates , Applied Physics Letters , 2004年 , VOLUME 84, NUMBER 6 , 1002-1003

(58)調査した分野(Int.Cl. , DB名)

H 01 L 21 / 20

C 23 C 16 / 34

H 01 L 21 / 205

H 01 L 33 / 32