(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5200408号 (P5200408)

(45) 発行日 平成25年6月5日(2013.6.5)

(24) 登録日 平成25年2月22日(2013.2.22)

| (51) Int.Cl. |               |           | F I  |       |      |

|--------------|---------------|-----------|------|-------|------|

| HO1L         | 21/336        | (2006.01) | HO1L | 29/78 | 627C |

| HO1L         | <i>29/786</i> | (2006.01) | HO1L | 29/78 | 616K |

|              |               |           | HO1L | 29/78 | 617T |

|              |               |           | HO1L | 29/78 | 618A |

|              |               |           | HO1L | 29/78 | 619A |

請求項の数 10 (全 19 頁)

(21) 出願番号 特願2007-108012 (P2007-108012) (22) 出願日 平成19年4月17日 (2007.4.17) (65) 公開番号 特開2008-270335 (P2008-270335A) (43) 公開日 平成20年11月6日 (2008.11.6) 審査請求日 平成22年3月24日 (2010.3.24)

||(73)特許権者 000001270

コニカミノルタホールディングス株式会社 東京都千代田区丸の内二丁目7番2号

||(74)代理人 100085501

弁理士 佐野 静夫

(74)代理人 100128842

弁理士 井上 温

|(72)発明者 平尾 雄也

東京都日野市さくら町1番地コニカミノル タテクノロジーセンター株式会社内

(72) 発明者 山田 潤

東京都日野市さくら町1番地コニカミノル タテクノロジーセンター株式会社内

審査官 鈴木 聡一郎

最終頁に続く

(54) 【発明の名称】薄膜トランジスタの製造方法

## (57)【特許請求の範囲】

### 【請求項1】

フォトリソグラフィ法を用いた薄膜トランジスタの製造方法であって、

<u>ゲート電極層</u>が形成された基板の上に成膜された感光性樹脂膜をフォトリソグラフィ法により所定のパターン形状に加工するパターンニング工程と、

前記所定のパターン形状に形成された感光性樹脂膜の所定の領域部分を除去せず残留させ、後工程で用いるリフトオフレジストとするリフトオフレジスト形成工程と、

前記リフトオフレジストの形成後に、前記基板上にソース電極およびドレイン電極を形成する工程と、

前記ソース電極および<u>前記</u>ドレイン電極に接合するように半導体膜を成膜し、該半導体膜および前記リフトオフレジストが形成された前記基板を覆うように半導体保護膜を成膜する保護膜成膜工程と、

前記リフトオフレジストの上に成膜されている半導体保護膜を除去する保護膜除去工程と、を有しており、

前記薄膜トランジスタは、前記基板の上に形成された画素電極層を有し、

前記リフトオフレジスト形成工程では、前記画素電極層の上に前記リフトオフレジスト を形成し、

前記パターンニング工程では、前記感光性樹脂膜を、多諧調露光および1回の現像により、前記画素電極層上のリフトオフレジスト領域を含む所定のパターン形状に加工することを特徴とする薄膜トランジスタの製造方法。

### 【請求項2】

フォトリソグラフィ法を用いた薄膜トランジスタの製造方法であって、

<u>ソース電極およびドレイン電極が形成された基板の上に成膜された感光性樹脂膜をフォ</u>トリソグラフィ法により所定のパターン形状に加工するパターンニング工程と、

前記所定のパターン形状に形成された感光性樹脂膜の所定の領域部分を除去せず残留させ、後工程で用いるリフトオフレジストとするリフトオフレジスト形成工程と、

前記リフトオフレジストの形成後に、前記ソース電極および前記ドレイン電極に接合するように半導体膜を成膜し、該半導体膜および前記リフトオフレジストが形成された前記基板を覆うように半導体保護膜を成膜する保護膜成膜工程と、

<u>前記リフトオフレジストの上に成膜されている半導体保護膜を除去する保護膜除去工程</u>と、を有しており、

前記薄膜トランジスタは、前記基板の上に形成された画素電極層を有し、

前記リフトオフレジスト形成工程では、前記画素電極層の上に前記リフトオフレジストを形成し、

前記パターンニング工程では、前記感光性樹脂膜を、多諧調露光および1回の現像により、前記画素電極層上のリフトオフレジスト領域を含む所定のパターン形状に加工することを特徴とする薄膜トランジスタの製造方法。

### 【請求項3】

前記パターンニング工程<u>では</u>、前記感光性樹脂膜を<u>多諧調露光した後、</u>第1の現像により前記所定のパターン形状に加工し、

前記リフトオフレジスト形成工程<u>では、</u>第2の現像により前記画素電極層の上の領域に 形成された感光性樹脂膜を除く領域の感光性樹脂膜を除去する<u>ことを特徴とする請求項1</u> または2に記載の薄膜トランジスタの製造方法。

#### 【請求項4】

前記パターニング工程にて、前記感光性樹脂膜が成膜される前記基板には、ゲート電極が形成されていることを特徴とする請求項2または3に記載の薄膜トランジスタの製造方法。

### 【請求項5】

<u>前記半導体保護膜の成膜後にゲート電極を形成する工程をさらに有していることを特徴</u>とする請求項2または3に記載の薄膜トランジスタの製造方法。

#### 【請求項6】

前記感光性樹脂膜は、フォトレジスト膜であることを特徴とする請求項 1 から 5 のいずれか 1 項に記載の薄膜トランジスタの製造方法。

### 【請求項7】

前記感光性樹脂膜は、ゲート絶縁膜であることを特徴とする請求項 1 または 2 に記載の 薄膜トランジスタの製造方法。

## 【請求項8】

<u>前記パターニング工程では、前記感光性樹脂膜をパターニングすることによってバンク</u>を形成し、

前記リフトオフレジストの形成後に前記基板上に形成されるソース電極、ドレイン電極 または半導体膜の液滴材料を、前記バンクを利用して所定の領域に塗布することにより、 前記ソース電極、前記ドレイン電極または前記半導体膜を形成することを特徴とする請求 項1または2に記載の薄膜トランジスタの製造方法。

## 【請求項9】

フォトリソグラフィ法を用いた薄膜トランジスタの製造方法であって、

ゲート電極、ゲート絶縁膜、ソース電極、ドレイン電極、および半導体膜が形成された 態様の薄膜トランジスタが形成された基板の上に成膜された感光性樹脂膜をフォトリソグ ラフィ法により所定のパターン形状に加工するパターンニング工程と、

前記所定のパターン形状に形成された感光性樹脂膜の所定の領域部分を除去せず残留させ、後工程で用いるリフトオフレジストとするリフトオフレジスト形成工程と、

10

20

30

40

<u>前記態様の薄膜トランジスタおよび前記リフトオフレジストが形成された前記基板を覆</u> うように半導体保護膜を成膜する保護膜成膜工程と、

<u>前記リフトオフレジストの上に成膜されている半導体保護膜を除去する保護膜除去工程</u>と、を有しており、

前記薄膜トランジスタは、前記基板の上に形成された画素電極を有し、

前記リフトオフレジスト形成工程では、前記画素電極の上に前記リフトオフレジストを 形成し、

前記パターンニング工程では、前記感光性樹脂膜を、多諧調露光および1回の現像により、前記画素電極上のリフトオフレジスト領域を含む所定のパターン形状に加工することを特徴とする薄膜トランジスタの製造方法。

【請求項10】

前記感光性樹脂膜は、PVA膜であることを特徴とする請求項9に記載の薄膜トランジスタの製造方法。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、薄膜トランジスタの製造方法に関し、特にフォトリソグラフィ法を用いた薄膜トランジスタの製造方法に関する。

【背景技術】

[0002]

通常、平板型のディスプレイ装置においては、液晶、有機 EL、電気泳動などを利用した素子を用いて表示媒体を形成している。また、このような表示媒体では画面輝度の均一性や画面書き換え速度などを確保するために、画像駆動素子として薄膜トランジスタ(以下、TFTとも記す)により構成されたアクティブ駆動素子を用いる技術が主流になっている。

[0003]

TFTは、通常、ガラス基板上に、主にa-Si(アモルファスシリコン)、p-Si(ポリシリコン)などの半導体薄膜や、ソース電極、ドレイン電極、ゲート電極などの金属薄膜を順次形成していくことで製造される。このTFTを用いるフラットパネルディスプレイの製造には、通常、CVD法、スパッタリング法などの真空系設備や高温処理工程を要する薄膜形成工程に加え、精度の高いフォトリソグラフィ法工程が必要とされ、設備コスト、ランニングコストの負荷が非常に大きい。さらに、近年のディスプレイの大画面化のニーズに伴い、それらのコストは非常に膨大なものとなっている。

[0004]

そこで、近年、従来のTFTのデメリットを補う技術として、有機半導体材料を用いた有機TFTの開発が盛んに進められている。有機TFTは、低温プロセスで製造可能であるため、軽く、割れ難い樹脂基板を用いることができ、さらに、樹脂フィルムを基板として用いたフレキシブルなディスプレイが実現できると言われている。また、大気圧下で、印刷や塗布などのウェットプロセスで製造できる有機半導体材料を用いることで、生産性に優れ、非常に低コストのディスプレイが実現できる。

[0005]

しかしながら、有機半導体材料は、シリコンなどの無機半導体と比べて、化学的に不安定な材料であり、可視光、紫外線の照射や、有機溶剤、酸素、水分などとの接触によって特性の変化や、性能の劣化が起こる。そこで、有機 TFTをこのような性能に影響を及ぼす要因から保護するために、遮光性とガスバリア性を備えた保護膜(以下、パッシベーション膜とも記す)が半導体を覆うように形成されている。

[0006]

パッシベーション膜は、材料として有機材料、無機材料が用いられるが、酸素遮断性能、水蒸気遮断性能を考慮すると、少なくとも一層は無機材料を用いることが好ましい。無機材料の成膜には、無機材料を分散させた分散液や前駆体を溶解させた溶液などを用いる

10

20

30

40

ことができるが、薄膜性能は、真空プロセスを用いて成膜されたものよりも劣るため、通常、スパッタ法やCVD法を用いてSiOoやパレリンなどを成膜している。

### [0007]

ところで、パッシベーション膜は、通常、半導体以外の部分には不要である。例えば、画素電極がゲート電極、ソース電極、ドレイン電極と同じ面に形成されている場合は、画素電極の上のパッシベーション膜は不要であり除去する必要がある。また、開口率を上げるため、画素電極が基板の最上層の表面に形成され、下層に平坦膜が成膜されたTFTが配置された構造の場合、TFTのドレイン電極と画素電極を接続するためのスルーホールの開口部にはパッシベーション膜は不要であり除去する必要がある。

#### [0008]

このように、パッシベーション膜は、通常、半導体以外の部分には不要であり、所定の 形状にパターニングする必要がある。

#### [0009]

パッシベーション膜のパターンニング方法としては、フォトリソグラフィ法や真空蒸着法などのドライプロセスを用いた方法(例えば、特許文献 1 参照)や、パッシベーション膜の成膜前にリフトオフ用のレジスト膜を形成しておき、成膜後にリフトオフ用のレジスト層をリフトオフし除去する方法などが知られている。

【特許文献1】特開2004-221562号公報

【発明の開示】

【発明が解決しようとする課題】

[0010]

しかしながら、特許文献 1 に開示されている方法では、パッシベーション膜の成膜に加えて、パッシベーション膜のパターンニングに際し、レジストパターンを形成するためのフォトリソグラフィ法工程が必要とされ、製造工程の複雑化と製造装置の高価格化を招くといった問題がある。また、フォトリソグラフィ法により、レジストパターンを形成する際に、前工程で完成しているTFTの位置に対して、高い精度の位置合わせが必要とされ、製造装置のさらなる高価格化に繋がるといった問題がある。また、リフトオフによりパッシベーション膜をパターンニングする場合においても、リフトオフ用のレジスト膜をパターンニングする際に、特許文献 1 の場合と同様に、フォトリソグラフィ法工程や高い精度の位置合わせが必要とされ、製造工程の複雑化と製造装置の高価格化を招くといった問題がある。

## [0011]

本発明は、上記課題を鑑みてなされたもので、簡単な工程で、安定した性能が得られる薄膜トランジスタの製造方法を提供することを目的とする。

【課題を解決するための手段】

[0012]

上記目的は、下記の1乃至9いずれか1項に記載の発明によって達成される。

[0013]

1.フォトリソグラフィ法を用いた薄膜トランジスタの製造方法であって、

ゲート電極層およびソース・ドレイン電極層の少なくともいずれか一方が形成された基板の上に成膜された感光性樹脂膜をフォトリソグラフィ法により所定のパターン形状に加工するパターンニング工程と、

前記所定のパターン形状に形成された感光性樹脂膜の所定の領域部分を除去せず残留させ、後工程で用いるリフトオフレジストとするリフトオフレジスト形成工程と、

前記リフトオフレジスト形成工程の後に、ソース電極およびドレイン電極に接合するように半導体膜を成膜し、該半導体膜および前記リフトオフレジストが形成された前記基板を 覆うように半導体保護膜を成膜する保護膜成膜工程と、

前記リフトオフレジストの上に成膜されている半導体保護膜を除去する保護膜除去工程と 、を有することを特徴とする薄膜トランジスタの製造方法。

[0014]

10

20

30

40

2.前記薄膜トランジスタは、前記基板の上に形成された画素電極層を有し、前記リフトオフレジスト形成工程は、前記画素電極層の上に前記リフトオフレジストを形成することを特徴とする前記1に記載の薄膜トランジスタの製造方法。

### [0015]

3.前記パターンニング工程は、前記感光性樹脂膜を多諧調露光および第1の現像により所定のパターン形状に加工し、

前記リフトオフレジスト形成工程は、第2の現像により前記画素電極層の上の領域に形成された感光性樹脂膜を除く領域の感光性樹脂膜を除去することを特徴とする前記2に記載の薄膜トランジスタの製造方法。

### [0016]

4.前記感光性樹脂膜は、フォトレジスト膜であることを特徴とする前記1乃至3のいずれか1項に記載の薄膜トランジスタの製造方法。

#### 【 0 0 1 7 】

5.前記感光性樹脂膜は、ゲート絶縁膜であることを特徴とする前記1または2に記載の薄膜トランジスタの製造方法。

### [0018]

6.前記感光性樹脂膜は、液滴材料を所定の領域に塗布する際に用いるバンク材料からなることを特徴とする前記1または2に記載の薄膜トランジスタの製造方法。

#### [0019]

7.フォトリソグラフィ法を用いた薄膜トランジスタの製造方法であって、

ゲート電極、ゲート絶縁膜、ソース電極、ドレイン電極、および半導体膜が形成された態様の薄膜トランジスタが形成された基板の上に成膜された感光性樹脂膜をフォトリソグラフィ法により所定のパターン形状に加工するパターンニング工程と、

前記所定のパターン形状に形成された感光性樹脂膜の所定の領域部分を除去せず残留させ、後工程で用いるリフトオフレジストとするリフトオフレジスト形成工程と、

前記態様の薄膜トランジスタおよび前記リフトオフレジストが形成された前記基板を覆うように半導体保護膜を成膜する保護膜成膜工程と、

前記リフトオフレジストの上に成膜されている半導体保護膜を除去する保護膜除去工程と 、を有することを特徴とする薄膜トランジスタの製造方法。

## [0020]

8.前記薄膜トランジスタは、前記基板の上に形成された画素電極を有し、前記リフトオフレジスト形成工程は、前記画素電極の上に前記リフトオフレジストを形成することを特徴とする前記7に記載の薄膜トランジスタの製造方法。

### [0021]

9.前記感光性樹脂膜は、PVA膜であることを特徴とする前記7または8に記載の薄膜トランジスタの製造方法。

### 【発明の効果】

### [0022]

本発明によれば、薄膜トランジスタの製造過程で用いた感光性樹脂膜の所定の領域部分を除去せず残留させ、該残留部分を後工程で成膜された半導体保護膜をパターンニングする際のリフトオフレジストとして用いるようにした。これにより、半導体保護膜をパターンニングするために新たにリフトオフレジストを形成するフォトリソグラフィ法工程が不要となり、製造工程を簡略化することができる。

## [0023]

また、フォトリソグラフィ法により所定のパターン形状に加工された感光性樹脂膜の所定の領域部分をリフトオフレジストとすることにより、所定の領域部分の下地部材とリフトオフレジストとの相対位置は一意的に決まる。例えば、画素電極をパターンニングする際のエッチング用のレジストをリフトオフレジストとして用いると、画素電極の位置と半導体保護膜の開口部の位置を高精度で合致させることができる。すなわち、リフトオフ用レジストと下地部材の半導体保護膜を開口させたい領域との高い精度の位置合わせが不要

10

20

30

40

(6)

となり、製造装置を低価格化することができる。

【発明を実施するための最良の形態】

### [0024]

以下図面に基づいて、本発明に係る薄膜トランジスタ(以下、TFTとも記する)の製造方法の実施の形態を説明する。尚、本発明を図示の実施の形態に基づいて説明するが、本発明は該実施の形態に限られない。

#### [0025]

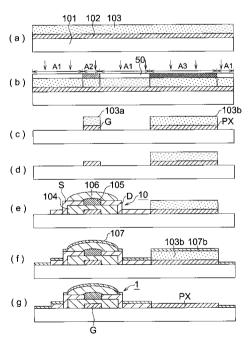

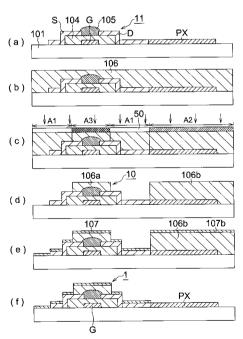

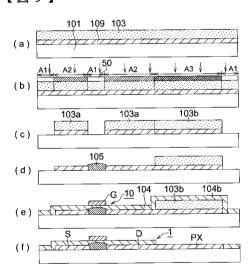

### 〔実施形態1〕

図1に実施形態1によるTFTの製造工程を示す。図1(a)~図1(g)は、工程断面図である。実施形態1によるTFT1は、図1(g)に示すように、ボトムゲートボトムコンタクト型であり、画素電極PXとゲート電極Gが同じ工程で形成されている。実施形態1は、ゲート電極Gと画素電極PXをパターニングするためのフォトレジスト膜103を利用したパッシベーション膜107(半導体保護膜)のパターニング方法である。

## [0026]

以下、図1に基づいて、実施形態1によるTFT1のパッシベーション膜107のパターニング方法を説明する。

### [0027]

最初に、基板101の上に形成されている電極層102からゲート電極G、画素電極P Xをパターニングする為に、電極層102が形成された基板101の上にフォトレジスト 膜(感光性樹脂膜;以下、レジスト膜と略称す)103を成膜する(図1(a))。

### [0028]

次に、レジスト膜103の上からマスク露光を行う。露光時にハーフトーンマスク50を用いてハーフトーン露光(多諧調露光)をすることで、露光量が100%、中間値(例えば50%)、0%の領域が形成され、その領域は、それぞれ第1現像領域A1、第2現像領域A2、リフトオフレジスト領域A3となる(図1(b))。

### [0029]

第1現像工程において第1現像領域 A 1 が現像処理されることでレジスト膜103がパターンニングされ、その後のエッチング処理でゲート電極 G 、画素電極 P X がパターニングされる(図1(c);パターンニング工程)。

## [0030]

第2現像工程において第2現像領域A2が現像処理され、ゲート電極Gの上のレジスト膜103aが除去され、画素電極PXの上にのみレジスト膜103bが残留する。このレジスト膜103bがリフトオフレジストとなる(図1(d);リフトオフレジスト形成工程)。

## [0031]

次に、公知の手法を用いてゲート絶縁膜104、ソース電極S、ドレイン電極D、半導体膜105、PVA膜106を形成することで、ボトムゲートボトムコンタクト型のTFT10を作製する(図1(e))。

### [0032]

次に、TFT10、レジスト膜103bなどが形成された基板101を覆うように、パッシベーション膜107を成膜する(図1(f);保護膜成膜工程)。成膜方法としては、通常用いられている方法で実施されればよく、手段は限定されない。また、パッシベーション膜107の材料としては、SiO $_2$ やSiNxなどがあるが、TFTを保護する性能が充分であれば材料の種類も限定されない。

### [0033]

最後に、ハーフトーン露光でリフトオフレジスト領域A3となった画素電極PXの上に残留したレジスト膜103bをリフトオフする。リフトオフによりレジスト膜103bとレジスト膜103bの上に成膜されたパッシベーション膜107bが除去されて、パッシベーション膜107がパターニングされ、画素電極PXが露出したTFT1が完成する(図1(g);保護膜除去工程)。

10

20

30

40

### [0034]

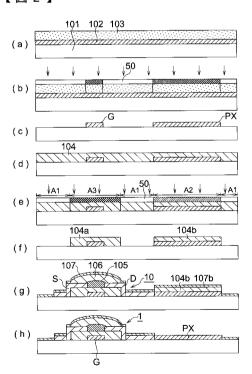

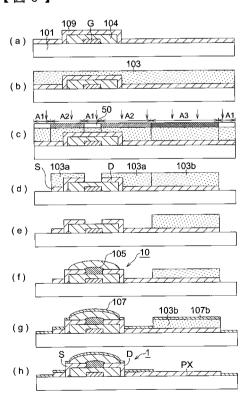

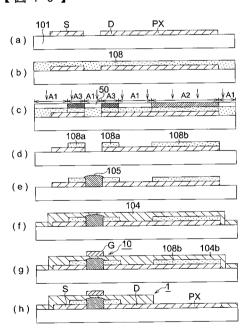

〔実施形態2〕

図2に実施形態2によるTFTの製造工程を示す。図2(a)~図2(h)は、工程断面図である。実施形態2によるTFT1は、図2(h)に示すように、実施形態1の場合と同様に、ボトムゲートボトムコンタクト型であり、画素電極PXとゲート電極Gが同じ工程で形成されている。実施形態2は、ゲート絶縁膜104を利用したパッシベーション膜107のパターニング方法である。

### [0035]

以下、図2に基づいて、実施形態2によるTFT1のパッシベーション膜107のパターニング方法を説明する。

[0036]

最初に、基板 1 0 1 の上に形成されている電極層 1 0 2 からゲート電極 G 、画素電極 P X をパターニングする為に、電極層 1 0 2 が形成された基板 1 0 1 の上にレジスト膜 1 0 3 を成膜する(図 2 ( a ) )。

[0037]

次に、レジスト膜103の上からマスク露光を行う(図2(b))。その後、現像処理、エッチング処理を行うことで、レジスト膜103が除去された領域の電極層102がエッチングされる。エッチング後に電極層102の上に残留したレジスト膜103を剥離することで、ゲート電極G、画素電極PXがパターニングされる(図2(c))。

[0038]

次に、ゲート電極 G、 画素電極 P X がパターニングされた基板 1 0 1 の上に感光性を有するゲート絶縁膜 1 0 4 (感光性樹脂膜)を成膜する(図 2 ( d ) )。

[0039]

次に、ゲート絶縁膜104の上からマスク露光を行う。露光時にハーフトーンマスク5 0を用いてハーフトーン露光をすることで、露光量が100%、中間値(例えば50%) 、0%の領域が形成され、その領域は、それぞれ第1現像領域A1、リフトオフレジスト 領域A2、ゲート絶縁膜領域A3となる(図2(e))。

[0040]

第1現像工程において第1現像領域 A 1 が現像処理されることでゲート絶縁膜104がパターンニングされ、ゲート絶縁膜104aと後工程でリフトオフされるリフトオフレジストとなる画素電極 P X の上のゲート絶縁膜104bが基板101の上に残留する(図2(f))。

[0041]

次に、公知の手法を用いてソース電極 S、ドレイン電極 D、半導膜 1 0 5、 P V A 膜 1 0 6を形成することで、ボトムゲートボトムコンタクト型の T F T 1 0を作製する。

[0042]

次に、TFT10、ゲート絶縁膜104bなどが形成された基板101を覆うように、 パッシベーション膜107を成膜する(図2(g))。

[0043]

最後に、ハーフトーン露光でリフトオフレジスト領域A2となった画素電極PXの上に 残留したゲート絶縁膜104bをリフトオフする。リフトオフによりゲート絶縁膜104 bとゲート絶縁膜104bの上に成膜されたパッシベーション膜107bが除去されて、 パッシベーション膜107がパターニングされ、画素電極PXが露出したTFT1が完成 する(図2(h))。

[0044]

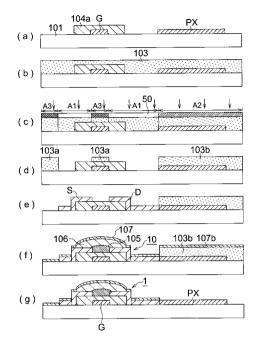

〔実施形態3〕

図3に実施形態3によるTFTの製造工程を示す。図3(a)~図3(g)は、工程断面図である。実施形態3によるTFT1は、図3(g)に示すように、実施形態1の場合と同様に、ボトムゲートボトムコンタクト型であり、画素電極PXとゲート電極Gが同じ工程で形成されている。実施形態3は、ソース電極S、ドレイン電極Dを形成するための

10

20

30

40

バンクとなるレジスト膜103を利用したパッシベーション膜107のパターニング方法である。

### [0045]

以下、図3に基づいて、実施形態3によるTFT1のパッシベーション膜107のパターニング方法を説明する。

### [0046]

最初に、図3(a)に示す工程の前工程として、実施形態2で前述した図2(a)~図2(c)の工程を経てゲート電極G、画素電極PXをパターニングする。次に、ゲート電極G、画素電極PXがパターニングされた基板101の上に感光性を有するゲート絶縁膜104を成膜する。その後、ゲート絶縁膜104の上からマスク露光、現像処理を行うことで、ゲート電極Gの部分のみにゲート絶縁膜104aをパターニングする。

### [0047]

次に、ゲート電極 G、画素電極 P X、ゲート絶縁膜 1 0 4 a がパターンニングされた基板 1 0 1 の上にソース電極 S、ドレイン電極 D を形成するためのバンクとなるレジスト膜 1 0 3 を成膜する(図 3 ( b ) )。

#### [0048]

次に、レジスト膜103の上からマスク露光を行う。露光時にハーフトーンマスク50を用いてハーフトーン露光をすることで、露光量が100%、中間値(例えば50%)、0%の領域が形成され、その領域は、それぞれ第1現像領域A1、リフトオフレジスト領域A2、ソース・ドレイン電極形成用バンク領域A3となる(図3(c))。

### [0049]

第1現像工程において第1現像領域 A 1が現像処理されることでレジスト膜103がパターンニングされ、ソース・ドレイン電極形成用バンクなるレジスト膜103aと後工程でリフトオフされるリフトオフレジストとなる画素電極 P X の上のレジスト膜103bが基板101の上に残留する(図3(d))。

### [0050]

次に、インクジェット法などの溶液プロセスやスパッタ法、蒸着などの方法を用い、ソース・ドレイン電極形成用バンク(レジスト膜 1 0 3 a )を利用してソース電極 S 、ドレイン電極 D を形成し、その後、ソース・ドレイン電極形成用バンク(レジスト膜 1 0 3 a )を剥離する(図 3 ( e ) )。

### [0051]

次に、公知の手法を用いて半導膜105、PVA膜106を形成することで、ボトムゲートボトムコンタクト型のTFT10を作製する。

## [0052]

次に、TFT10、レジスト膜103bなどが形成された基板101を覆うように、パッシベーション膜107を成膜する(図3(f))。

## [0053]

最後に、ハーフトーン露光でリフトオフレジスト領域A2となった画素電極PXの上に残留したレジスト膜103bをリフトオフする。リフトオフによりレジスト膜103bとレジスト膜103bの上に成膜されたパッシベーション膜107bが除去されて、パッシベーション膜107がパターニングされ、画素電極PXが露出したTFT1が完成する(図3(g))。

### [0054]

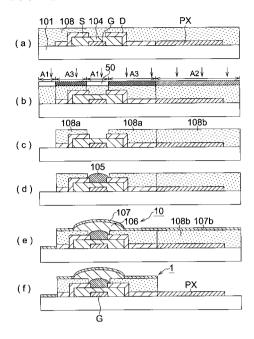

## 〔実施形態4〕

図4に実施形態4によるTFTの製造工程を示す。図4(a)~図4(f)は、工程断面図である。実施形態4によるTFT1は、図4(f)に示すように、実施形態1の場合と同様に、ボトムゲートボトムコンタクト型であり、画素電極PXとゲート電極Gが同じ工程で形成されている。実施形態4は、半導体膜105を形成するためのバンク108を利用したパッシベーション膜のパターニング方法である。

## [0055]

10

20

30

以下、図4に基づいて、実施形態4によるTFT1のパッシベーション膜107のパターニング方法を説明する。

### [0056]

最初に、図4(a)に示す工程の前工程として、実施形態1~実施形態3で前述した方法に準拠して、基板101の上にゲート電極G、ゲート絶縁膜104、ソース電極S、ドレイン電極D、画素電極PXを形成する。

#### [0057]

次に、ソース電極 S、ドレイン電極 D、画素電極 P X などが形成された基板 1 0 1 の上に半導体膜 1 0 5 を形成するためのバンク 1 0 8 a となる感光性を有するバンク材料 1 0 8 (感光性樹脂膜)を成膜する(図 4 ( a ) )。

## [0058]

次に、バンク108の上からマスク露光を行う。露光時にハーフトーンマスク50を用いてハーフトーン露光をすることで、露光量が100%、中間値(例えば50%)、0%の領域が形成され、その領域は、それぞれ第1現像領域A1、リフトオフレジスト領域A2、半導体膜形成用バンク領域A3となる(図4(b))。

#### [0059]

第1現像工程において第1現像領域 A 1が現像処理されることでバンク108がパターンニングされ、半導体膜形成用バンクとなるバンク108aと後工程でリフトオフされるリフトオフレジストとなる画素電極 P X の上のバンク108bが基板101の上に残留する(図4(c))。

### [0060]

次に、インクジェット法やディスペンサ法などの溶液プロセスを用い、半導体膜形成用 バンク(バンク108a)を利用して半導体膜105を形成する(図4(d))。

#### [0061]

次に、公知の手法を用いてPVA膜106を形成することで、ボトムゲートボトムコンタクト型のTFT10を作製する。

### [0062]

次に、TFT10、バンク108bなどが形成された基板101を覆うように、パッシベーション膜107を成膜する(図4(e))。

## [0063]

最後に、ハーフトーン露光でリフトオフレジスト領域 A 2 となった画素電極 P X の上に 残留したバンク 1 0 8 bをリフトオフする。リフトオフによりバンク 1 0 8 b とバンク 1 0 8 b の上に成膜されたパッシベーション膜 1 0 7 b が除去されて、パッシベーション膜 1 0 7 がパターニングされ、画素電極 P X が露出した T F T 1 が完成する(図 4 ( f ) )

### [0064]

## 〔実施形態5〕

図5に実施形態5によるTFTの製造工程を示す。図5(a)~図5(f)は、工程断面図である。実施形態5によるTFT1は、図5(f)に示すように、実施形態1の場合と同様に、ボトムゲートボトムコンタクト型であり、画素電極PXとゲート電極Gが同じ工程で形成されている。実施形態5は、PVA膜106を利用したパッシベーション膜107のパターニング方法である。

### [0065]

以下、図 5 に基づいて、実施形態 5 によるTFT1のパッシベーション膜107のパターニング方法を説明する。

## [0066]

最初に、図5(a)に示す工程の前工程として、実施形態1~実施形態4で前述した方法に準拠して、基板101の上にゲート電極G、ゲート絶縁膜104、ソース電極S、ドレイン電極D、半導体膜105、画素電極PXが形成された態様のTFT11を形成する

10

20

30

#### [0067]

次に、TFT11が形成された基板101の上に感光性を有するPVA膜106(感光性樹脂膜)を成膜する(図5(b))。

### [0068]

次に、PVA膜106の上からマスク露光を行う。露光時にハーフトーンマスク50を用いてハーフトーン露光をすることで、露光量が100%、中間値(例えば50%)、0%の領域が形成され、その領域は、それぞれ第1現像領域A1、リフトオフレジスト領域A2、半導体膜保護用PVA領域A3となる(図5(c))。

## [0069]

第1現像工程において第1現像領域 A 1 が現像処理されることで P V A 膜 1 0 6 がパターンニングされ、半導体膜 1 0 5 の保護用となる P V A 膜 1 0 6 a と後工程でリフトオフされるリフトオフレジストとなる画素電極 P X の上の P V A 膜 1 0 6 b が基板 1 0 1 の上に残留する(図 5 ( d ); パターンニング工程、リフトオフレジスト形成工程)。

## [0070]

次に、TFT10、PVA膜106bなどが形成された基板101を覆うように、パッシベーション膜107を成膜する(図5(e);保護膜成膜工程)。

### [0071]

最後に、ハーフトーン露光でリフトオフレジスト領域A2となった画素電極PXの上に残留したPVA膜106bをリフトオフする。リフトオフによりPVA膜106bとPVA膜106bの上に成膜されたパッシベーション膜107bが除去されて、パッシベーション膜107がパターニングされ、画素電極PXが露出したTFT1が完成する(図5(f);保護膜除去工程)。

### [0072]

#### [実施形態6]

図6に実施形態6によるTFTの製造工程を示す。図6(a)~図6(h)は、工程断面図である。実施形態6によるTFT1は、図6(h)に示すように、ボトムゲートボトムコンタクト型であり、画素電極PXとソース電極S、ドレイン電極Dが同じ工程で形成されている。実施形態6は、画素電極PXとソース電極S、ドレイン電極Dをパターニングするためのレジスト膜103を利用したパッシベーション膜107のパターニング方法である。

## [0073]

以下、図6に基づいて、実施形態1によるTFT1のパッシベーション膜107のパターニング方法を説明する。

## [0074]

最初に、図6(a)に示す工程の前工程として、実施形態1~実施形態5で前述した方法に準拠して、基板101の上にゲート電極G、ゲート絶縁膜104を形成する。その後、ゲート絶縁膜104などが形成された基板101の上に後工程でソース電極S、ドレイン電極D、画素電極PXとなる電極層109を成膜する。

## [0075]

次に、基板101の上に形成されている電極層109からソース電極S、ドレイン電極 D、画素電極PXをパターニングする為に、電極層109が形成された基板101の上に レジスト膜103を成膜する(図6(b))。

### [0076]

次に、レジスト膜103の上からマスク露光を行う。露光時にハーフトーンマスク50を用いてハーフトーン露光をすることで、露光量が100%、中間値(例えば50%)、0%の領域が形成され、その領域は、それぞれ第1現像領域A1、第2現像領域A2、リフトオフレジスト領域A3となる(図6(c))。

### [0077]

第1現像工程において第1現像領域 A 1 が現像処理されることでレジスト膜103がパターンニングされ、その後のエッチング処理でソース電極 S 、ドレイン電極 D 、画素電極

10

20

30

40

PXがパターニングされる(図6(d))。

## [0078]

第2現像工程において第2現像領域A2が現像処理されソース電極Sとドレイン電極Dの上のレジスト膜103aが除去され、画素電極PXの上にのみレジスト膜103bが残留する。このレジスト膜103bがリフトオフレジストとなる(図6(e))。

### [0079]

次に、公知の手法を用いて半導膜105、PVA106膜を形成することで、ボトムゲートボトムコンタクト型のTFT10を作製する(図6(f))。

### [0800]

次に、TFT10、レジスト膜103bなどが形成された基板101を覆うように、パッシベーション膜107を成膜する(図6(g))。

#### [0081]

最後に、ハーフトーン露光でリフトオフレジスト領域A3となった画素電極PXの上に残留したレジスト膜103bをリフトオフする。リフトオフによりレジスト膜103bとレジスト膜103bの上に成膜されたパッシベーション膜107bが除去されて、パッシベーション膜107がパターニングされ、画素電極PXが露出したTFT1が完成する(図6(h))。

## [0082]

#### 〔実施形態7〕

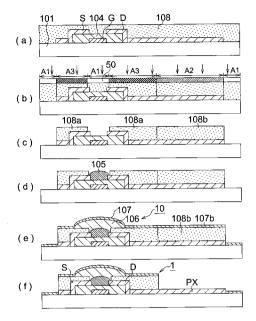

図7に実施形態7によるTFTの製造工程を示す。図7(a)~図7(f)は、工程断面図である。実施形態7によるTFT1は、図7(f)に示すように、ボトムゲートボトムコンタクト型であり、画素電極PXとソース電極S、ドレイン電極Dが同じ工程で形成されている。実施形態7は、半導体膜105を形成するためのバンク108を利用したパッシベーション膜のパターニング方法である。

## [0083]

尚、実施形態7によるTFT1の製造工程は、画素電極PXとソース電極S、ドレイン電極Dが同じ工程で形成されていることを除いては、実施形態4の場合と概ね同様であることから、説明は省略する。

### [0084]

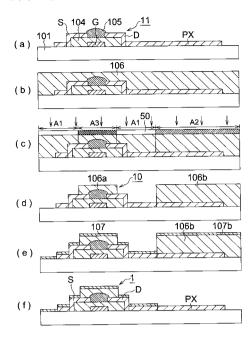

## 〔実施形態8〕

図8に実施形態8によるTFTの製造工程を示す。図8(a)~図8(f)は、工程断面図である。実施形態8によるTFT1は、図8(f)に示すように、ボトムゲートボトムコンタクト型であり、画素電極PXとソース電極S、ドレイン電極Dが同じ工程で形成されている。実施形態8は、PVA膜106を利用したパッシベーション膜107のパターニング方法である。

### [0085]

尚、実施形態 8 によるTFT1の製造工程は、画素電極 P X とソース電極 S 、ドレイン電極 D が同じ工程で形成されていることを除いては、実施形態 5 の場合と概ね同様であることから、説明は省略する。

### [0086]

## 〔実施形態9〕

図9に実施形態9によるTFTの製造工程を示す。図9(a)~図9(f)は、工程断面図である。実施形態9によるTFT1は、図9(f)に示すように、トップゲートボトムコンタクト型であり、画素電極PXとソース電極S、ドレイン電極Dが同じ工程で形成されている。実施形態9は、画素電極PXとソース電極S、ドレイン電極Dをパターニングするためのレジスト膜103を利用したパッシベーション膜107のパターニング方法である。

### [0087]

以下、図9に基づいて、実施形態9によるTFT1のパッシベーション膜107のパターニング方法を説明する。

20

10

30

40

#### [0088]

最初に、基板101の上に形成されている電極層109からソース電極S、ドレイン電極D、画素電極PXをパターニングする為に、電極層109が形成された基板101の上にレジスト膜103を成膜する(図9(a))。

### [0089]

次に、レジスト膜103の上からマスク露光を行う。露光時にハーフトーンマスク50を用いてハーフトーン露光をすることで、露光量が100%、中間値(例えば50%)、0%の領域が形成され、その領域は、それぞれ第1現像領域A1、第2現像領域A2、リフトオフレジスト領域A3となる(図9(b))。

### [0090]

第1現像工程において第1現像領域 A 1 が現像処理されることでレジスト膜103がパターンニングされ、その後のエッチング処理でソース電極 S 、ドレイン電極 D 、画素電極 P X がパターニングされる(図 9 ( c ))。

### [0091]

第2現像工程において第2現像領域A2が現像処理され、ソース電極Sとドレイン電極Dの上のレジスト膜103aが除去され、画素電極PXの上にのみレジスト膜103bが残留する。このレジスト膜103bがリフトオフレジストとなる。その後、公知の手法を用いて、ソース電極Sとドレイン電極Dとの間のチャネル部に半導体膜105を形成する(図9(d))。

## [0092]

次に、スピンコート法などを用いて、半導体膜105、レジスト膜103bなどが形成された基板101を覆うように、ゲート絶縁膜104を成膜する。その後、ゲート絶縁膜104の上にゲート電極Gを形成することで、トップゲートボトムコンタクト型のTFT10を作製する(図9(e))。この場合、ゲート絶縁膜104は、半導体膜105の上を覆うことになりパッシベーション膜としても機能する。

### [0093]

最後に、ハーフトーン露光でリフトオフレジスト領域A3となった画素電極PXの上に残留したレジスト膜103bをリフトオフする。リフトオフによりレジスト膜103bとレジスト膜103bの上に成膜されたゲート絶縁膜104bが除去されて、パッシベーション膜として機能するゲート絶縁膜104がパターニングされ、画素電極PXが露出したTFT1が完成する(図9(f))。

## [0094]

#### 〔実施形態10〕

図10に実施形態10によるTFTの製造工程を示す。図10(a)~図10(h)は、工程断面図である。実施形態10によるTFT1は、図10(h)に示すように、実施形態9の場合と同様に、トップゲートボトムコンタクト型であり、画素電極PXとソース電極S、ドレイン電極Dが同じ工程で形成されている。実施形態10は、半導体膜105を形成するためのバンク108を利用したパッシベーション膜のパターニング方法である

### [0095]

以下、図10に基づいて、実施形態10によるTFT1のパッシベーション膜107のパターニング方法を説明する。

### [0096]

最初に、図10(a)に示す工程の前工程として、実施形態1~実施形態9で前述した方法に準拠して、基板101の上にソース電極S、ドレイン電極D、画素電極PXを形成する。

### [0097]

次に、ソース電極 S 、ドレイン電極 D 、画素電極 P X が形成された基板 1 0 1 の上に半導体膜 1 0 5 を形成するためのバンク 1 0 8 a となる感光性を有するバンク 1 0 8 材料を成膜する(図 1 0 ( b ) )。

10

20

30

40

#### [0098]

次に、バンク108の上からマスク露光を行う。露光時にハーフトーンマスク50を用いてハーフトーン露光をすることで、露光量が100%、中間値(例えば50%)、0%の領域が形成され、その領域は、それぞれ第1現像領域A1、リフトオフレジスト領域A2、半導体膜形成用バンク領域A3となる(図10(c))。

### [0099]

第1現像工程において第1現像領域 A 1が現像処理されることでバンク108がパターンニングされ、半導体膜形成用バンクとなるバンク108aと後工程でリフトオフされるリフトオフレジストとなる画素電極 P X の上のバンク108bが基板101の上に残留する(図10(d))。

## [0100]

次に、インクジェット法やディスペンサ法などの溶液プロセスを用い、半導体膜形成用 バンク(バンク108a)を利用して半導体膜105を形成する(図10(e))。

## [0101]

次に、スピンコート法などを用いて、半導体膜105、バンク108bなどが形成された基板101を覆うように、ゲート絶縁膜104を成膜する(図10(f))。その後、ゲート絶縁膜104の上にゲート電極Gを形成することで、トップゲートボトムコンタクト型のTFT10を作製する(図10(g))。この場合、ゲート絶縁膜104は、半導体膜105の上を覆うことになりパッシベーション膜としても機能する。

### [0102]

最後に、ハーフトーン露光でリフトオフレジスト領域A2となった画素電極PXの上に残留したバンク108bをリフトオフする。リフトオフによりバンク108bとバンク108bの上に成膜されたゲート絶縁膜104bが除去されて、パッシベーション膜として機能するゲート絶縁膜104がパターニングされ、画素電極PXが露出したTFT1が完成する(図10(h))。

## [0103]

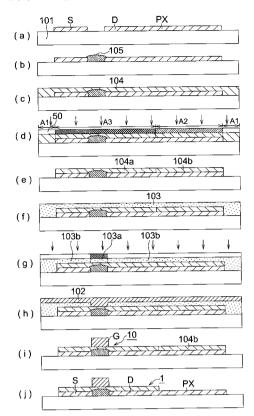

## 〔実施形態11〕

図11に実施形態11によるTFTの製造工程を示す。図11(a)~図11(j)は、工程断面図である。実施形態11によるTFT1は、図11(h)に示すように、実施形態9の場合と同様に、トップゲートボトムコンタクト型であり、画素電極PXとソース電極S、ドレイン電極Dが同じ工程で形成されている。実施形態11は、ゲート絶縁膜104を利用したパッシベーション膜107のパターニング方法である。

#### [0104]

以下、図11に基づいて、実施形態11によるTFT1のパッシベーション膜107のパターニング方法を説明する。

### [0105]

最初に、図11(a)に示す工程の前工程として、実施形態1~実施形態10で前述した方法に準拠して、基板101の上にソース電極S、ドレイン電極D、画素電極PXを形成する。

### [0106]

次に、公知の手法を用いて、ソース電極 S とドレイン電極 D との間のチャネル部に半導体膜 1 0 5 を形成する(図 1 1 ( b ) )。

### [0107]

次に、ソース電極 S、ドレイン電極 D、画素電極 P X、半導体膜 1 0 が形成された基板 1 0 1 を覆うように、感光性を有するゲート絶縁膜 1 0 4 を成膜する(図 1 1 ( c ) )。この場合、ゲート絶縁膜 1 0 4 は、半導体膜 1 0 5 の上を覆うことになりパッシベーション膜としても機能する。

### [0108]

次に、ゲート絶縁膜104の上からマスク露光を行う。露光時にハーフトーンマスク50を用いてハーフトーン露光をすることで、露光量が100%、中間値(例えば50%)

10

20

30

30

40

、0%の領域が形成され、その領域は、それぞれ第1現像領域A1、リフトオフレジスト 領域A2、ゲート絶縁膜領域A3となる(図11(d))。

### [0109]

第1現像工程において第1現像領域 A 1が現像処理されることでゲート絶縁膜104がパターンニングされ、ゲート絶縁膜104 a と後工程でリフトオフされるリフトオフレジストとなる画素電極 P X の上のゲート絶縁膜104 b が基板101の上に残留する(図11(e))。

### [0110]

次に、ゲート電極 G をパターンニングするために、ゲート絶縁膜 1 0 4 a 、ゲート絶縁膜 1 0 4 b などが形成された基板 1 0 1 の上にレジスト膜 1 0 3 を成膜する(図 1 1 (f))。

### [0111]

次に、レジスト膜 1 0 3 の上からマスク露光、現像処理を行いゲート電極 G が形成される部分のレジスト膜 1 0 3 a を除去する。

### [0112]

次に、ゲート電極 G を形成するためのレジスト膜 1 0 3 b がパターニングされた基板 1 0 1 の上に、蒸着法やスパッタ法などを用いて電極層 1 0 2 を成膜する(図 1 1 ( h ) )。その後、レジスト膜 1 0 3 b を基板 1 0 1 から剥離することで所望の部分にゲート電極 G が形成され、トップゲートボトムコンタクト型のTFT 1 0 を作製する(図 1 1 ( i ) )。

### [0113]

最後に、ハーフトーン露光でリフトオフレジスト領域 A 2 となった画素電極 P X の上に 残留したゲート絶縁膜 1 0 4 b をリフトオフする。リフトオフによりゲート絶縁膜 1 0 4 b が除去されて、パッシベーション膜として機能するゲート絶縁膜 1 0 4 がパターニング され、画素電極 P X が露出した T F T 1 が完成する(図 1 0 ( h ) )。

### [0114]

このように、本発明に係る本発明に係るTFT1の製造方法においては、TFT1の製造過程で用いた感光性樹脂膜(フォトレジスト膜103、ゲート絶縁膜104、バンク材料108、PVA膜106)の所定の領域部分を除去せず残留させ、該残留部分を後工程で成膜されたパッシベーション膜107やパッシベーション膜として機能するゲート絶縁膜104をパターンニングする際のリフトオフレジストとして用いるようにした。これにより、パッシベーション膜107やパッシベーション膜として機能するゲート絶縁膜104をパターンニングするために新たにリフトオフレジストを形成するフォトリソグラフィ法工程が不要となり、製造工程を簡略化することができる。

### [0115]

また、フォトリソグラフィ法により所定のパターン形状に加工された感光性樹脂膜の所定の領域部分をリフトオフレジストとすることにより、所定の領域部分の下地部材とリフトオフレジストとの相対位置は一意的に決まる。例えば、画素電極 P X をパターンニングする際のエッチング用のレジスト膜 1 0 3 をリフトオフレジストとして用いると、画素電極 P X の位置とパッシベーション膜 1 0 7 の開口部の位置を高精度で合致させることができる。すなわち、リフトオフ用レジストと下地部材のパッシベーション膜 1 0 7 を開口させたい領域との高い精度の位置合わせが不要となり、製造装置を低価格化することができる。

## 【図面の簡単な説明】

### [0116]

- 【図1】本発明の実施形態1によるTFTの製造工程を示す図である。

- 【図2】本発明の実施形態2によるTFTの製造工程を示す図である。

- 【図3】本発明の実施形態3によるTFTの製造工程を示す図である。

- 【図4】本発明の実施形態4によるTFTの製造工程を示す図である。

- 【図5】本発明の実施形態5によるTFTの製造工程を示す図である。

20

10

30

40

- 【図6】本発明の実施形態6によるTFTの製造工程を示す図である。

- 【図7】本発明の実施形態7によるTFTの製造工程を示す図である。

- 【図8】本発明の実施形態8によるTFTの製造工程を示す図である。

- 【図9】本発明の実施形態9によるTFTの製造工程を示す図である。

- 【図10】本発明の実施形態10によるTFTの製造工程を示す図である。

- 【図11】本発明の実施形態11によるTFTの製造工程を示す図である。

### 【符号の説明】

## [0117]

1, 10 TFT

- 101 基板

- 102、109 電極層

- 103 レジスト膜

- 104 ゲート絶縁膜

- 1 0 5 半導体膜

- 106 PVA膜

- 107 パッシベーション膜

- 108 バンク

- D ドレイン電極

- G ゲート電極

- PX 画素電極

- S ソース電極

- 50 ハーフトーンマスク

## 【図1】

## 【図2】

10

## 【図3】

# 【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

# 【図11】

# フロントページの続き

(56)参考文献 特開2007-115808(JP,A) 特開2006-093656(JP,A)

(58)調査した分野(Int.CI., DB名)

H 0 1 L 2 1 / 3 3 6 H 0 1 L 2 9 / 7 8 6