(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2007-538474

(P2007-538474A)

(43) 公表日 平成19年12月27日(2007.12.27)

| (51) Int.C1.                 | F 1         | テーマコード (参考) |

|------------------------------|-------------|-------------|

| <b>HO3K 19/173</b> (2006.01) | HO3K 19/173 | 101 5B046   |

| <b>GO6F 17/50</b> (2006.01)  | GO6F 17/50  | 656A 5F038  |

| <b>HO1L 21/82</b> (2006.01)  | HO1L 21/82  | A 5F064     |

| <b>HO1L 21/822</b> (2006.01) | HO1L 21/82  | C 5J042     |

| <b>HO1L 27/04</b> (2006.01)  | HO1L 27/04  | M 5J056     |

審査請求 未請求 予備審査請求 未請求 (全 46 頁) 最終頁に続く

|               |                              |          |                     |

|---------------|------------------------------|----------|---------------------|

| (21) 出願番号     | 特願2007-527379 (P2007-527379) | (71) 出願人 | 597154922           |

| (86) (22) 出願日 | 平成17年5月18日 (2005.5.18)       |          | アルテラ コーポレイション       |

| (85) 翻訳文提出日   | 平成19年1月5日 (2007.1.5)         |          | Altera Corporation  |

| (86) 國際出願番号   | PCT/US2005/017265            |          | アメリカ合衆国 95134 カリフォル |

| (87) 國際公開番号   | WO2005/116878                |          | ニア州 サン ホセ イノベーション ド |

| (87) 國際公開日    | 平成17年12月8日 (2005.12.8)       |          | ライヴ 101             |

| (31) 優先権主張番号  | 10/848,953                   | (74) 代理人 | 100078282           |

| (32) 優先日      | 平成16年5月19日 (2004.5.19)       |          | 弁理士 山本 秀策           |

| (33) 優先権主張国   | 米国(US)                       | (74) 代理人 | 100062409           |

| (31) 優先権主張番号  | 10/865,402                   |          | 弁理士 安村 高明           |

| (32) 優先日      | 平成16年6月10日 (2004.6.10)       | (74) 代理人 | 100113413           |

| (33) 優先権主張国   | 米国(US)                       |          | 弁理士 森下 夏樹           |

最終頁に続く

(54) 【発明の名称】集積回路の性能を調整するための装置および方法

## (57) 【要約】

プログラマブルロジックデバイス (PLD) は、遅延回路およびボディバイアスジェネレータを含む。遅延回路は、PLDにおけるユーザー回路のインプリメントの遅延を表すように構成された遅延回路を有する。ボディバイアスジェネレータは、ユーザー回路内のトランジスタのボディバイアスを調整するように構成される。ボディバイアスジェネレータは、遅延回路の信号伝播遅延から引き出されたレベルに応答し、トランジスタのボディバイアスを調整する。

**【特許請求の範囲】****【請求項 1】**

プログラマブルロジックデバイス(PLD)であって、

遅延回路であって、該プログラマブルロジックデバイス(PLD)においてインプリメントされるユーザー回路の遅延を表すように構成された遅延を有する遅延回路と、

ボディバイアスジェネレータであって、該遅延回路の伝播遅延から引き出されたレベルに応答する該ユーザー回路内のトランジスタのボディバイアスを調整するように構成されたボディバイアスジェネレータと

を備える、プログラマブルロジックデバイス(PLD)。

**【請求項 2】**

前記遅延回路は、組み合わせロジックを備える、請求項1に記載のプログラマブルロジックデバイス(PLD)。

**【請求項 3】**

前記遅延回路は、少なくとも一つのロジック遅延要素および少なくとも一つのルーティング遅延要素を備える、請求項1に記載のプログラマブルロジックデバイス(PLD)。

**【請求項 4】**

前記少なくとも一つのロジック遅延要素および前記少なくとも一つの遅延要素は、前記プログラマブルロジックデバイス(PLD)内のプログラマブル回路網を使用してインプリメントされる、請求項3に記載のプログラマブルロジックデバイス(PLD)。

**【請求項 5】**

位相比較器であって、前記遅延回路の入力に印加される基準信号に応答する該遅延回路の出力信号の位相と該基準信号の位相を比較するように構成された位相比較器をさらに備える、請求項1に記載のプログラマブルロジックデバイス(PLD)。

**【請求項 6】**

前記比較器は第1の出力信号および第2の出力信号を供給するようにさらに構成された、請求項5に記載のプログラマブルロジックデバイス(PLD)。

**【請求項 7】**

前記第1の出力信号に応答して、前記ボディバイアスジェネレータは、前記トランジスタの動作をスピードアップするように該トランジスタの該ボディバイアスを調整する、請求項6に記載のプログラマブルロジックデバイス(PLD)。

**【請求項 8】**

前記第2の出力信号に応答して、前記ボディバイアスジェネレータは、前記トランジスタの動作をスローダウンするように該トランジスタの該ボディバイアスを調整する、請求項6に記載のプログラマブルロジックデバイス(PLD)。

**【請求項 9】**

前記遅延回路は、構成可能遅延回路を備える、請求項5に記載のプログラマブルロジックデバイス(PLD)。

**【請求項 10】**

前記構成可能遅延回路の前記伝播遅延は、構成可能である、請求項9に記載のプログラマブルロジックデバイス(PLD)。

**【請求項 11】**

前記ユーザー回路は、少なくとも一つのプログラマブルロジック要素および少なくとも一つのプログラマブル相互接続要素を備える、請求項1に記載のプログラマブルロジックデバイス(PLD)。

**【請求項 12】**

プログラマブルロジックデバイス(PLD)であって、

該プログラマブルロジックデバイス(PLD)においてインプリメントされるユーザー回路の伝播遅延を表す遅延を生成するための手段と、

該生成された遅延に従って少なくとも一つの信号を引き出すための手段と、

該少なくとも一つの信号に応答して該ユーザー回路にあるトランジスタのボディバイア

10

20

30

40

50

スをプログラムするための手段と

を備える、プログラマブルロジックデバイス(PLD)。

【請求項13】

前記ユーザー回路の前記トランジスタは、プログラマブルロジック要素内にある、請求項12に記載のプログラマブルロジックデバイス(PLD)。

【請求項14】

前記ユーザー回路の前記トランジスタは、プログラマブル相互接続要素内にある、請求項12に記載のプログラマブルロジックデバイス(PLD)。

【請求項15】

前記遅延を生成するための手段によって生成される該遅延は調整可能である、請求項12に記載のプログラマブルロジックデバイス(PLD)。

【請求項16】

前記遅延の調整は、前記少なくとも一つの信号における変化を引き起こす、請求項15に記載のプログラマブルロジックデバイス(PLD)。

【請求項17】

少なくとも一つの信号を引き出すための前記手段は、前記トランジスタの前記ボディバイアスをプログラムするための該手段が該トランジスタをスピードアップさせるようにして、該少なくとも一つの信号を引き出す、請求項16に記載のプログラマブルロジックデバイス(PLD)。

【請求項18】

少なくとも一つの信号を引き出すための前記手段は、前記トランジスタの前記ボディバイアスをプログラムするための該手段が該トランジスタをスローダウンさせるようにして、該少なくとも一つの信号を引き出す、請求項16に記載のプログラマブルロジックデバイス(PLD)。

【請求項19】

プログラマブルロジックデバイス(PLD)であって、

基準トランジスタであって、該プログラマブルロジックデバイス(PLD)における回路に関係した電流を供給するように構成された該基準トランジスタと、

電流測定回路であって、該基準トランジスタによって供給された該電流を測定し、測定された電流信号を供給するように構成された該測定回路と、

ボディバイアスジェネレータであって、該測定された電流信号からの少なくとも一つのボディバイアス信号を引き出すように構成され、該ボディバイアスジェネレータは、該少なくとも一つのボディバイアス信号を該プログラマブルロジックデバイス(PLD)における回路に供給するようにさらに構成される該ボディバイアスジェネレータと

を備える、プログラマブルロジックデバイス(PLD)。

【請求項20】

前記電流測定回路および前記ボディバイアスジェネレータに結合された比較器であって、該比較器は、前記測定された電流信号を基準信号と比較することによって、信号を引き出すように構成され、該比較器は、該信号を該ボディバイアスジェネレータへ供給するようにさらに構成された比較器

をさらに備える、請求項19に記載のプログラマブルロジックデバイス(PLD)。

【請求項21】

前記比較器と前記ボディバイアスジェネレータとの間ににおいて結合されたフィルタをさらに備える、請求項20に記載のプログラマブルロジックデバイス(PLD)。

【請求項22】

前記フィルタは、積分器を備える、請求項21に記載のプログラマブルロジックデバイス(PLD)。

【請求項23】

前記電流測定回路は、電流ミラーを備え、該電流ミラーは、前記基準トランジスタによって供給された前記電流を增幅し、增幅された電流を供給するように構成された、請求項

10

20

30

40

40

50

20に記載のプログラマブルロジックデバイス(PLD)。

【請求項24】

前記測定回路は、電流計数回路をさらに備え、該電流計数回路は、前記増幅された電流を測定するように構成される、請求項23に記載のプログラマブルロジックデバイス(PLD)。

【請求項25】

前記比較器は、構成可能な比較器を備える、請求項20に記載のプログラマブルロジックデバイス(PLD)。

【請求項26】

前記電流測定回路および前記ボディバイアスジェネレータに結合された第1および第2の比較器であって、該第1および該第2の比較器は、前記測定された電流信号を該第1および該第2の基準信号と比較することによって一対の信号を引き出すように構成され、該第1および該第2の比較器は、該一対の信号を該ボディバイアスジェネレータへ供給するようにさらに構成された第1および第2の比較器

をさらに備える、請求項19に記載のプログラマブルロジックデバイス(PLD)。

【請求項27】

前記第1および前記第2の電流基準信号は、それぞれ、より低いリーク値およびより高いリーク値に対応する、請求項20に記載のプログラマブルロジックデバイス(PLD)。

【請求項28】

前記第1および第2の比較器に結合されたカウンタであって、該カウンタは、該第1および該第2の比較器によって供給される一対の信号に応答しカウントするように構成され、該カウンタは、カウント値を前記ボディバイアスジェネレータへ供給するようにさらに構成されたカウンタ

をさらに備える、請求項27に記載のプログラマブルロジックデバイス(PLD)。

【請求項29】

前記第1の比較器は、構成可能な比較器を備え、前記第2の比較器は、構成可能な比較器を備える、請求項28に記載のプログラマブルロジックデバイス(PLD)。

【請求項30】

前記プログラマブルロジックデバイス(PLD)内の前記回路は、プログラマブルロジックを備える、請求項19に記載のプログラマブルロジックデバイス(PLD)。

【請求項31】

前記プログラマブルロジックデバイス(PLD)内の前記回路は、プログラマブルロジック相互接続を備える、請求項30に記載のプログラマブルロジックデバイス(PLD)。

【請求項32】

前記測定された電流信号は、リーク電流信号を備える、請求項19に記載のプログラマブルロジックデバイス(PLD)。

【請求項33】

前記測定された電流信号は、トランジスタの閾値電圧( $V_T$ )から引き出された電流を備える、請求項19に記載のプログラマブルロジックデバイス(PLD)。

【請求項34】

前記測定された電流信号は、トランジスタの飽和電流( $I_{d,sat}$ )を備える、請求項19に記載のプログラマブルロジックデバイス(PLD)。

【請求項35】

プログラマブルロジックデバイス(PLD)であって、

回路におけるリーク電流を得る手段と、

該リーク電流を測定することによって、測定されたリーク電流を生成する手段と、

該測定されたリーク電流に応答して該回路におけるトランジスタのボディバイアスをプログラムするための手段と

10

20

30

40

50

を備える、プログラマブルロジックデバイス（PLD）。

【請求項 3 6】

リーク電流を得るための前記手段は、前記回路にある、請求項 3 5 に記載のプログラマブルロジックデバイス（PLD）。

【請求項 3 7】

前記測定されたリーク電流を少なくとも一つのリーク基準信号と比較するための手段をさらに備える、請求項 3 5 に記載のプログラマブルロジックデバイス（PLD）。

【請求項 3 8】

比較するための前記手段は、少なくとも一つの出力信号を前記ボディバイアスジェネレータへ供給する、請求項 3 7 に記載のプログラマブルロジックデバイス（PLD）。 10

【請求項 3 9】

比較のための前記手段の前記少なくとも一つの出力信号を処理することによって、少なくとも一つの処理された信号を生成するため、および、該少なくとも一つの処理された信号を前記ボディバイアスジェネレータへ供給するための手段をさらに備える、請求項 3 8 に記載のプログラマブルロジックデバイス（PLD）。

【請求項 4 0】

前記測定されたリーク電流を比較するための前記手段は、該測定されたリーク電流を第 1 および第 2 のリーク基準信号と比較し、該第 1 および第 2 のリーク基準信号は、前記回路におけるリーク電流の所望の範囲に対応する、請求項 3 7 に記載のプログラマブルロジックデバイス（PLD）。 20

【請求項 4 1】

複数のユーザー回路であって、該ユーザー回路の各々は、プログラマブルロジックデバイス（PLD）においてインプリメントされるユーザー回路と、

複数のボディバイアスジェネレータであって、該複数のボディバイアスジェネレータにおける少なくとも一つのボディバイアスジェネレータは、該複数のユーザー回路における少なくとも一つのユーザー回路内のトランジスタのボディバイアスを選択的に調整するように構成されている複数のボディバイアスジェネレータと

を備える、プログラマブルロジックデバイス（PLD）。

【請求項 4 2】

前記複数のボディバイアスジェネレータにおける前記少なくとも一つのボディバイアスジェネレータは、前記複数のユーザー回路における該少なくとも二つのユーザー回路の各々内のトランジスタのボディバイアスを選択的に調整するようにさらに構成される、請求項 4 1 に記載のプログラマブルロジックデバイス（PLD）。 30

【請求項 4 3】

前記複数のボディバイアスジェネレータにおける各ボディバイアスジェネレータは、前記複数のユーザー回路における対応するユーザー回路内のトランジスタのボディバイアスを選択的に調整するように構成される、請求項 4 2 に記載のプログラマブルロジックデバイス（PLD）。

【請求項 4 4】

前記複数のユーザー回路の各々における前記トランジスタの前記ボディバイアスは、個々のレベルに調整される、請求項 4 3 に記載のプログラマブルロジックデバイス（PLD）。 40

【請求項 4 5】

前記トランジスタの前記ボディバイアスは、動作速度とワット損をトレードオフするよう調整される、請求項 4 1 に記載のプログラマブルロジックデバイス（PLD）。

【請求項 4 6】

前記トランジスタの前記ボディバイアスは、動作速度とリーク電流をトレードオフするよう調整される、請求項 4 1 に記載のプログラマブルロジックデバイス（PLD）。

【請求項 4 7】

電子回路をインプリメントするためのプログラマブルロジックデバイス（PLD）を使 50

用する方法であって、

設計を生成するために、該電子回路を該プログラマブルロジックデバイス（P L D）内の機能リソースにマッピングするステップと、

該生成された設計の少なくとも一つの部分内の信号伝播遅延を表す遅延からボディバイアス値を引き出すステップと、

該生成された設計の該少なくとも一つの部分内の少なくとも一つのトランジスタのボディバイアスレベルを該ボディバイアス値へプログラムするステップと

を包含する、方法。

#### 【請求項 4 8】

前記電子回路を前記プログラマブルロジックデバイス（P L D）内の機能リソースへのマッピングすることは、該電子回路の少なくとも一部分を該プログラマブルロジックデバイス（P L D）内のプログラマブルロジックリソースにマッピングすることをさらに包含する、請求項 4 7 に記載の方法。 10

#### 【請求項 4 9】

前記電子回路を前記プログラマブルロジックデバイス（P L D）内の機能リソースへのマッピングすることは、該電子回路の少なくとも一部分を該プログラマブルロジックデバイス（P L D）内のプログラマブルロジックリソースにマッピングすることをさらに包含する、請求項 4 7 に記載の方法。

#### 【請求項 5 0】

前記生成された設計の少なくとも一部分内の信号伝播遅延を表す遅延からボディバイアス値を引き出すステップは、該遅延を既知の期間と比較することをさらに包含する、請求項 4 7 に記載の方法。 20

#### 【請求項 5 1】

前記遅延は、調整可能である、請求項 5 0 に記載の方法。

#### 【請求項 5 2】

前記遅延は、前記プログラマブルロジックデバイス（P L D）内においてインプリメントされるロジック回路によって生成される、請求項 4 7 に記載の方法。

#### 【請求項 5 3】

プログラマブルロジック回路（P L D）内において実施される回路におけるトランジスタのリークレベルを調整する方法であって、 30

該トランジスタのリーク電流を表す電流を得るステップと、

該得られた電流からボディバイアスレベルを引き出すステップと、

該トランジスタの該ボディバイアスレベルを該引き出されたボディバイアスレベルへ調整するステップと

を包含する、方法。

#### 【請求項 5 4】

前記トランジスタのリーク電流を表す電流を得るステップは、前記回路におけるリーク電流の測定するステップをさらに包含する、請求項 5 3 に記載の方法。

#### 【請求項 5 5】

前記得られた電流からボディバイアスレベルを引き出すステップは、該得られた電流を少なくとも一つのリーク基準値と比較し、少なくとも一つのエラー信号を生成するステップをさらに包含する、請求項 5 3 に記載の方法。 40

#### 【請求項 5 6】

前記得られた電流からボディバイアスレベルを引き出すステップは、前記少なくとも一つのエラー信号から該ボディバイアスレベルを引き出すステップをさらに包含する、請求項 5 5 に記載の方法。

#### 【請求項 5 7】

前記得られた電流からボディバイアスレベルを引き出す方法であって、

前記少なくとも一つのエラー信号を濾過し、濾過された信号を生成するステップと、

該濾過した信号からボディバイアスレベルを引き出すステップと

50

をさらに包含する、請求項 5 6 に記載の方法。

【請求項 5 8】

前記得られた電流と少なくとも一つのリーク基準値と比較するステップは、該得られた電流を第 1 および第 2 のリーク基準値との比較するステップをさらに包含し、該第 1 および第 2 の基準値は前記トランジスタのリーク電流の範囲を規定する、請求項 5 5 に記載の方法。

【請求項 5 9】

プログラマブルロジック回路 (P L D) における少なくとも一つの回路領域におけるユーザーの回路を実現する方法であって、

該回路領域における少なくとも一つのトランジスタ用のボディバイアスレベルを選択するステップと、

プログラマブルロジックデバイス (P L D) 内の該回路領域の初期配置を生成するステップと、

既存のボディバイアスレベルおよび配置が所定の性能基準を満たさない場合、該回路領域における該少なくとも一つのトランジスタに印加されるべき該ボディバイアスレベルを少なくとも 1 回別のレベルに変更するステップと

を包含する、方法。

【請求項 6 0】

前記既存のバイアスレベルおよび配置が所定の性能基準を満たさない場合、該ボディバイアスの新しいレベルから引き出された遅延推定を使用することによって、前記回路領域のタイミングを少なくとも 1 回分析するステップをさらに包含する、請求項 5 9 に記載の方法。

【請求項 6 1】

前記既存のバイアスレベルおよび配置が所定の性能基準を満たさない場合、前記プログラマブルロジックデバイス (P L D) 内の前記回路領域の該配置を少なくとも 1 回改善するステップをさらに包含する、請求項 6 0 に記載の方法。

【請求項 6 2】

前記既存のバイアスレベルおよび配置が所定の性能基準を満たす場合、前記回路領域の該現在の配置およびバイアスレベルを記録するステップをさらに包含する、請求項 6 1 に記載の方法。

【請求項 6 3】

前記所定の性能基準は、タイミング基準を備える、請求項 5 9 に記載の方法。

【請求項 6 4】

前記所定の性能基準は、電力基準を備える、請求項 5 9 に記載の方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

(関連出願の相互参照)

本出願は、2004年5月19日出願の米国特許出願第10/848,953号、代理人整理番号第A L T R : 026号の発明の名称「Apparatus and Methods for Adjusting the Performance of Programmable Logic Devices」の一部継続出願であり、それを参考として援用する。

【0 0 0 2】

発明コンセプトは、一般に、プログラマブルロジックデバイス (P L D) を含む集積回路 (I C) の性能の調整に関する。

【背景技術】

【0 0 0 3】

P L D は、設計者のみならずエンドユーザーにも柔軟性を提供するユビキタスな電子デバイスである。電子回路またはシステムの設計サイクル時、設計者は、設計ごとに P L D

10

20

30

40

50

を単純に再プログラムすることによって、比較的多くの回数の設計反復を実行し得る。従って、設計サイクルの長さと費用は、他の代案と比較して減少する。同様に、エンドユーザーは、PLDを含む設計の機能性に対するコントロールの所望のレベルを有し得る。PLDを実地にまたはリアルタイムベースでさえプログラムすることによって、ユーザーは、回路またはシステムが動作する方法を変更し得る。

#### 【0004】

ますます複雑化する設計を収容するため、現代のPLDは比較的多数のトランジスタを含む。さらにユーザーは、ますます高い性能を要求し、結果的に、より大きな動作周波数となる。その結果、PLDの消費電力、ワット損、ダイ温度、および従って、電力密度（種々の回路またはロックのワット損）は、増加する傾向である。しかし、出力密度を上げていくと、PLDの設計とインプリメンテーションを非現実的または故障しやすくする。調整可能な消費電力および性能を特徴とするPLDに対する必要性が存在する。さらに、汎用IC内のトランジスタの性能（リーク、速度、およびワット損）を直接コントロールする必要性が存在する。

#### 【発明の開示】

#### 【課題を解決するための手段】

#### 【0005】

##### （要約）

開示された新しいコンセプトは、たとえば、速度と消費電力をトレードオフすることによって、PLDの性能を調整するための装置および方法に関する。発明のコンセプトの局面は、PLDの性能を調整するための装置に関する。一実施形態において、ユーザーの回路をインプリメントするように構成されたPLDは、遅延回路およびボディバイアスジエネレータを含む。遅延回路は、PLDにおいてインプリメントされるユーザーの回路の遅延を表す遅延を有する。ユーザーの回路は、少なくとも一つのトランジスタを含む。ボディバイアスジエネレータは、遅延回路の伝播遅延から引き出された量に応答し、ユーザーの回路におけるトランジスタのボディバイアスを調整する。

#### 【0006】

別の実施形態において、PLDは、基準トランジスタ、電流測定回路、およびボディバイアスジエネレータを含む。基準トランジスタは、PLD内の回路に関係する電流を供給する。電流測定回路は、基準トランジスタによって供給される電流を測定し、測定された電流信号をボディバイアスジエネレータに供給する。ボディバイアスジエネレータは、測定された電流信号から少なくとも一つのボディバイアス信号を引き出し、ボディバイアス信号をPLDの回路に供給する。

#### 【0007】

さらに別の実施形態において、PLDは、複数のユーザー回路および複数のボディバイアスジエネレータを含む。ユーザー回路の各々は、PLDにおいてインプリメントされる。複数のボディバイアスジエネレータの少なくとも一つは、ユーザー回路の少なくとも一つ内のトランジスタのボディバイアスを選択的に調整するように構成される。

#### 【0008】

発明コンセプトの別の局面は、PLDの性能を調整し、ユーザーの回路をインプリメントするためにPLDを使用することの方法に関する。一実施形態において、電子回路をインプリメントするためにPLDを使用する方法は、設計を生成するために電子回路をPLD内の機能リソースにマッピングすること、および生成された設計の少なくとも一つの部分内の信号伝播遅延を表す遅延からボディバイアス値を引き出すことを含む。方法はさらに、生成された設計の部分内の少なくとも一つのトランジスタのボディバイアスレベルをボディバイアス値にプログラムすることを含む。

#### 【0009】

別の実施形態において、PLD内で実施される回路におけるトランジスタのリークレベルを調整する方法は、トランジスタのリーク電流を表す電流を得ること、および得られた電流からボディバイアスレベルを引き出すことを含む。方法はさらに、トランジスタのバ

イアスレベルを引き出されたボディバイアスレベルに調整することを含む。

#### 【0010】

さらに別の実施形態において、PLDにおける少なくとも一つの回路領域においてユーザー回路を実現する方法は、回路領域において少なくとも一つのトランジスタのボディバイアスレベルを選択し、PLD内における回路領域の初期配置を生成することを含む。方法はさらに、既存のボディバイアスレベルおよび配置が所定の性能基準を満たさない場合、回路領域においてトランジスタに印加されるべきボディバイアスレベルを少なくとも1回別のレベルに変更することを含む。

#### 【0011】

添付の図面は、発明の例示的実施形態を示すに過ぎなく、従って、発明の範囲を制限するものと考えられるべきではない。本発明の記述からメリットを享受する当業者は、開示された発明のコンセプトがその他の等しく有効な実施形態に役立つことを理解する。図面において、二つ以上の図面において使用される同じ数字符号は、同じ、同様な、または同等な機能性、コンポーネント、またはブロックを示す。

#### 【発明を実施するための最良の形態】

#### 【0012】

##### (詳細な説明)

本発明コンセプトは、調整可能な出力および性能を特徴とするPLDのための装置および関連方法を意図する。発明コンセプトは、従来のPLDが被っている過度の出力密度レベルを克服するのを助ける。さらに、本発明に従い、PLDの所望の部分またはすべての性能レベルを調整し得る(すなわち、個別のトランジスタからPLD全体に至るまでの範囲にわたる粒状ベースで)。

#### 【0013】

より具体的には、以下に詳細に記述されているように、発明コンセプトは、PLD内の個別のトランジスタまたはトランジスタのグループのボディバイアスまたはウェルバイアスの設定、プログラム、または調整を意図する。ボディバイアスを調整することは、トランジスタの消費電力および性能を変動させる。

#### 【0014】

この発明コンセプトは、従来のインプリメンテーションに対して以下の利点を提供する。第1に、発明コンセプトは、性能と消費電力とのトレードオフ、または性能 消費電力のトレードオフの最適化を可能にする。第2に、PLDのクリティカル回路バスまたは部品において、必要に応じ、それらの性能を向上させるために、ボディバイアスレベルを選択的に設定し、プログラムし、または、調整し得る。逆に、非クリティカル回路バスまたはPLDのパートにおいて、ボディバイアスレベルを選択的に設定し、プログラムし、または、調整し得、従って、それらの消費電力を減少させ、それらの出力密度を低下させ得る。

#### 【0015】

さらに、PLD内で使用しない部品または回路を遮断または不能にし得、それによって、それらの消費電力を減少させ、それらの出力密度を低下させ得る。また、熱暴走を防ぐ(またはその可能性を減少させる)ために、発明コンセプトを採用し得る。より具体的には、従来のPLDにおいて、比較的高速で動作する回路は、より多くの電力を消費する傾向があり、その結果、PLDの温度上昇を招く。消費電力の増加は、これらの回路がさらに多くの電力を消費させる原因になり得る。このプラスのフィードバックメカニズムは、出力密度を不安全なまたは破壊的なレベルまで増加させ得る。

#### 【0016】

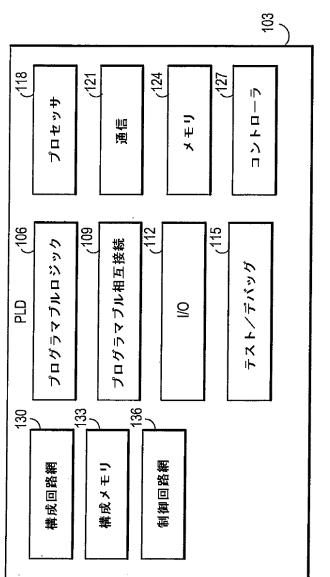

図1は、発明の例示的実施形態に従う、PLD103の汎用ブロック図を示す。PLD103は、構成回路網130、構成メモリ133、制御回路網136、プログラマブルロジック106、プログラマブル相互接続109、およびI/O回路網112を含む。さらに、PLD103は、必要に応じ、テスト/デバッグ回路網115、一つ以上のプロセッサ118、一つ以上の通信回路網121、一つ以上のメモリ124、一つ以上のコントロ

10

20

30

40

50

ーラ 127 を含み得る。

【0017】

図1は、PLD103の簡略なブロック図を示すことに注意されたい。このように、PLD103は、当業者が理解するように、その他のブロックおよび回路網を含み得る。そのような回路網の例は、クロック発振および分配回路、冗長回路などを含む。さらに、PLD103は、必要に応じ、アナログ回路網、その他のデジタル回路網、および/または混合モード回路網を、含み得る。

【0018】

プログラマブルロジック106は、ルックアップテーブル(LUT)、プロダクトタームロジック、マルチプレクサ、ロジックゲート、レジスタ、メモリなどの構成可能なロジック回路網またはプログラマブルロジック回路網のブロックを含む。プログラマブル相互接続109は、プログラマブルロジック106に結合し、プログラマブルロジック106内の種々のブロックとPLD103内または外部のその他の回路網との間の構成可能な相互接続(結合メカニズム)を提供する。

【0019】

制御回路網136は、PLD103内の種々の動作を制御する。制御回路網136の監視の下に、PLD構成回路網130は、PLD103の機能性をプログラム、または、構成するために、構成データを使用する(PLD構成回路網は、そのデータをストレージデバイス、ホストなどの外部ソースから得る)。本発明の記述の助けをもって当業者が理解するように、構成データは、プログラマブルロジック106およびプログラマブル相互接続109をプログラムすることによって、PLD103の機能性を決定する。

【0020】

本発明の記述のたすけを有する当業者が理解するように、I/O回路網は、幅広い種々のI/Oデバイスまたは回路を構成する。I/O回路網112は、PLD103の種々の部品、たとえば、プログラマブルロジック106およびプログラマブル相互接続109など、に接続する。I/O回路112は、外部回路またはデバイスと通信するために、PLD103内の種々のブロック用の機構および回路網を提供する。

【0021】

テスト/デバッグ回路網115は、PLD103内の種々のブロックおよび回路のテストおよびトラブルシューティングを容易にする。テスト/デバッグ回路網115は、本発明の記述のたすけを有する当業者に知られている種々のブロックまたは回路を含み得る。たとえば、テスト/デバッグ回路網115は、必要に応じ、PLD103のパワーアップまたはリセット後のテストを実行する回路を含み得る。テスト/デバッグ回路網115はまた、必要に応じ、コーディングおよびパリティ回路も含む。

【0022】

上記されるように、PLD103は、一つ以上のプロセッサ118を含み得る。プロセッサ118は、PLD103内のその他のブロックおよび回路に結合し得る。本発明の記述のたすけをもって当業者が理解するように、プロセッサ118は、PLD103内または外部の回路からデータおよび情報を受け取り得、幅広い種々の方法で情報を処理し得る。一つ以上のプロセッサ118は、デジタル信号プロセッサ(DSP)を構成し得る。DSPは、必要に応じ、圧縮、圧縮解除、音声処理、映像処理、フィルタリングなどの幅広い種々の信号処理タスクの実行を可能にする。

【0023】

PLD103はまた、一つ以上の通信回路網121も含み得る。本発明の記述からメリットを享受する当業者は理解するように、通信回路網121は、PLD103内の種々の回路とPLD103の外部の回路との間のデータおよび情報の交換を容易にし得る。一例として、通信回路網121は、必要に応じ、種々のプロトコル機能性(たとえば、伝送制御プロトコル/インターネットプロトコル(TCP/IP)、ユーザデータグラムプロトコル(UDPなど)を提供し得る。別の例として、通信回路網121は、必要に応じ、ネットワーク(たとえば、イーサネット(登録商標)、トーカンリングなど)またはバスイ

10

20

30

40

50

ンターフェース回路網を含み得る。

【0024】

P L D 1 0 3 はさらに、一つ以上のメモリ 1 2 4 および一つ以上のコントローラ 1 2 7 を含み得る。メモリ 1 2 4 は、P L D 1 0 3 内の種々のデータおよび情報（ユーザーデータ、中間結果、計算結果など）の格納を可能にする。メモリ 1 2 4 は、必要に応じ、粒状形またはブロック形を有し得る。コントローラ 1 2 7 は、P L D の外部の回路網の動作および種々の機能にインタフェースし、制御することを可能にする。たとえば、コントローラ 1 2 7 は、必要に応じ、外部の同期ダイナミックランダムアクセスメモリ（S D R A M）にインタフェースし、制御するメモリコントローラを構成し得る。

【0025】

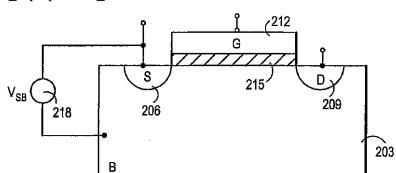

P L D 1 0 3 内の回路網のブロックは、多数のトランジスタを含む。より具体的には、トランジスタは、必要に応じ、n 型M O S（N M O S）、p 型M O S（P M O S）、相補型M O S（C M O S）、または、部分空乏シリコンオンインシュレータ（S O I）M O S トランジスタ（またはこれらの種類のトランジスタの組み合せ）などの金属酸化物半導体（M O S）トランジスタを構成する。

57 図 2 は、本発明に従う、例示的な実施形態において使用されるM O S トランジスタを示す。M O S トランジスタは、本体（または基板）領域 2 0 3、ソース領域 2 0 6、ドレイン領域 2 0 9、ゲートインシュレータ 2 1 5、およびゲート 2 1 2 を含む。動作の飽和領域におけるM O S トランジスタのドレイン電流は、トランジスタの閾値電圧およびゲートからソースへの電圧に依存し、

$$i_D = K (V_{GS} - V_T)^2 \quad (1)$$

である。ここで、

$i_D$  = 全ドレイン電流（すなわち、A C およびD C 成分を含む）

K = 定数

$V_{GS}$  = ゲートからソースへの全電圧（すなわち、A C およびD C 成分を含む）、および

$V_T$  = 閾値電圧

である。

【0026】

閾値電圧  $V_T$  は、トランジスタのソース領域 2 0 6 と本体領域 2 0 3 との間の電圧などの多数の要因に依存する。下記の等式は、本体からソースへの電圧の関数としての閾値電圧を提供する：

【0027】

【数 1】

$$V_T = V_{T(0)} + \gamma \sqrt{2\phi_F - v_{BS}} - \sqrt{2\phi_F} \quad (2A)$$

代わりに、ソースから本体への電圧の点から、等式 2 A は：

【0028】

【数 2】

$$V_T = V_{T(0)} + \gamma \sqrt{2\phi_F + v_{SB}} - \sqrt{2\phi_F} \quad (2B)$$

と書き得る。ここで、

$V_T(0)$  = ソースから本体（または本体からソース）への電圧が 0 にセットされた閾値電圧

= 本体係数で、本体のドーピングレベルに依存する定数

$\gamma$  = 定数

$v_{BS}$  = 本体からソースへの全電圧（すなわち、A C およびD C 成分を含む）、および

10

20

20

30

40

50

$S_B$  = ソースから本体への全電圧（すなわち、ACおよびDC成分を含む）である。本体からソースへの電圧、 $B_S$ （または、ソースから本体への電圧、 $S_B$ ）が0に等しいとき、閾値電圧 $V_T$ は、 $V_T(0)$ に等しいことに注意されたい。

#### 【0029】

等式2Bが示すように、有限本体係数に関して、ソースから本体への電圧、 $S_B$ 、が増加すると、トランジスタの閾値電圧は増加する。しかし、等式(1)は、特定のゲートからソースへの電圧に関して、閾値電圧における増加は、トランジスタのドレイン電流 $i_D$ を減少させることを示す。換言すると、等式1および2Bに従って、定数のゲートからソースへの電圧 $G_S$ に関して、ソースから本体への電圧 $S_B$ における増加は、閾値電圧、 $V_T$ における増加の原因になる。

10

#### 【0030】

増加した閾値電圧 $V_T$ は、今度は、量( $G_S V_T$ )における減少の原因となり、その結果、トランジスタのドレイン電流 $i_D$ における減少となる。このように、ゲートからソースへの一定の電圧 $G_S$ に関して、ソースから本体への電圧 $S_B$ における増加は、トランジスタの電流駆動能力（性能の一つの基準）における減少の原因となる。トランジスタの減少した電流駆動能力は、今度は、回路動作を遅くすることになり、最終的には、トランジスタを含むPLDの動作を遅くする。

20

#### 【0031】

トランジスタのワット損もまた、その閾値電圧における変化に従って、変動する。より具体的には、閾値電圧が小さくなると、トランジスタのOFF状態のリーク電流( $I_{f_f}$ )が増加する。逆もまた同様である。トランジスタの $I_{f_f}$ は、そのスタティック（非スイッチング）のワット損に影響する。さらに、より小さい閾値電圧は、トランジスタのダイナミックまたはスイッチングワット損を増加させる。このように、ボディバイアスを調整することによって閾値電圧を変化させると、MOSトランジスタのワット損に影響する。

20

#### 【0032】

さらに、所定の供給電圧、 $V_{DD}$ 、に関して、閾値電圧、 $V_T$ 、における増加は、トランジスタがパストランジスタとして動作するときに、トランジスタが伝導し得る最大電圧を制限する。換言すると、閾値電圧、 $V_T$ 、が、ゲートからソースへの電圧 $G_S$ に等しいかまたは超える点まで増加する場合、ドレイン電流は0に減少する。このように、トランジスタのドレインに印加される電圧、たとえば、ロジック1レベルに対応する電圧は、トランジスタのソースに適切に伝導しない。その結果、トランジスタは、パストランジスタとして信頼性をもって動作しない。

30

#### 【0033】

上記に示すように、MOSトランジスタのボディバイアス、従ってトランジスタのソースから本体への電圧を調整することによって、MOSトランジスタの性能に影響を及ぼし得る（最終的には、閾値電圧における変化の結果を招く）。ボディバイアスを調整すると、電流駆動能力、動作速度、ワット損、などの性能基準に影響する。

30

#### 【0034】

上記のように、発明に従う実施形態において、必要に応じ、PLD内の個々のトランジスタ、個々の回路またはブロック、トランジスタまたはブロックのグループ、またはPLD全体までのボディバイアスを調整し得る。さらに、必要に応じ、個々のNMOSおよびPMOSトランジスタのボディバイアス、または、NMOSおよびPMOSトランジスタのグループのボディバイアスを調整し得る。以下の説明は、詳細を提供する。

40

#### 【0035】

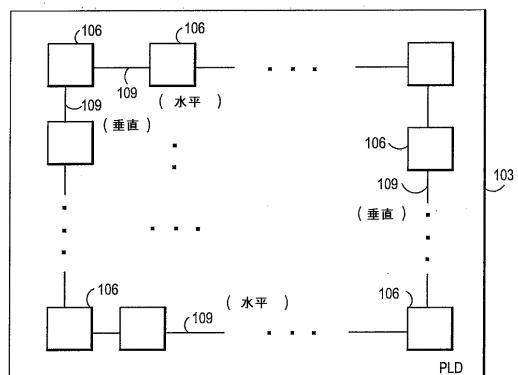

図3は、発明の例示的実施形態に従うPLD103の平面図を示す。PLD103は、二次元アレイとして配置されているプログラマブルロジック106を含む。水平相互接続および垂直相互接続として配置されたプログラマブル相互接続109は、プログラマブルロジック106のブロックを互いに結合する。必要に応じ、プログラマブルロジック106の各ブロック、プログラマブル相互接続109の各セグメント、またはその両方のボデ

50

ィバイアスを調整し得る。さらに、必要に応じ、プログラマブルロジック 106 の一つ以上のブロックの部分、プログラマブル相互接続 109 の部分、またはその両方のボディバイアスを調整し得る。

【0036】

例示的実施形態において、発明に従うPLDは、階層アーキテクチャを有する。換言すると、図3のプログラマブルロジック106の各ブロックは、今度は、より小さいかまたはより多い粒状のプログラマブルロジクブロックまたは回路を含み得る。必要に応じ、PLDの階層アーキテクチャの各レベルにおけるトランジスタのボディバイアスを調整し得る。

【0037】

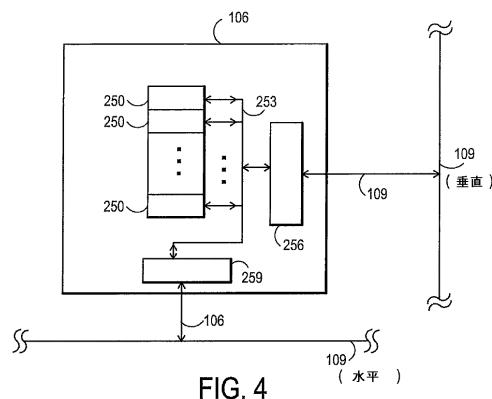

図4は、発明の例示的な実施形態に従うPLDにおけるプログラマブルロジック106のブロック図を示す。プログラマブルロジック106は、論理要素またはプログラマブルロジック回路250、ローカル相互接続253、インターフェース回路256およびインターフェース回路259を含む。本発明の記述からメリットを享受する当業者は理解するよう、論理要素250は、構成可能なロジック機能またはプログラマブルロジック機能、たとえば、LUT、レジスタ、プロダクトタームロジックなどを提供する。ローカル相互接続253は、必要に応じ、論理要素250が互いにまたはプログラマブル相互接続109（「グローバル相互接続」と呼ばれることがある）に結合するように構成可能なメカニズムまたはプログラマブルメカニズムを提供する。

【0038】

インターフェース回路256およびインターフェース回路259は、回路網のプログラマブルロジック106がプログラマブル相互接続109（および従って、図3に示すように、他のプログラマブルロジック106）に結合するように、構成可能な方法またはプログラマブルな方法を提供する。本発明の記述からメリットを享受する当業者は理解するよう、インターフェース回路256およびインターフェース回路259は、マルチプレクサ（MUX）、レジスタ、バッファ、ドライバなどを含み得る。

【0039】

必要に応じ、PLD103（図1、図3、および図4を参照）内の回路網の各部分またはブロックのボディバイアスを調整し得る。さらに、必要に応じ、個々または集合的ベースで、回路網の各部分またはブロックのボディバイアスを他に無関係に調整し得る。回路網の各部分またはブロック内で、必要に応じ、個々または集合的ベースで、各サブブロックまたはトランジスタのボディバイアス、またはサブブロックまたはトランジスタのグループのボディバイアスを調整し得る。

【0040】

たとえば、発明の例示的な実施形態に従い、PLD内の下記の回路網のすべてまたは部分のボディバイアスを調整し得る：図1の一つ以上のブロック（たとえば、プログラマブルロジック106、プログラマブル相互接続109など）；一つ以上のプログラマブルロジックブロック106内の一つ以上の論理要素250；一つ以上のプログラマブルロジックブロック106内の一つ以上のインターフェース回路256および/または259；一つ以上のプログラマブルロジック106内の一つ以上のローカル相互接続；および一つ以上のインターフェース回路256および/または259内の一つ以上のMUX、ドライバ、バッファなど。

【0041】

上記のとおり、ボディバイアス調整を、粒状度の任意の所望レベルで、行い得る。換言すると、必要また適用可能に応じ、個々のトランジスタ、トランジスタのグループ、サブブロック、ブロックまたはPLD全体に適用可能な調整を行い得る。たとえば、必要に応じ、一つ以上のNMOSトランジスタのボディバイアス調整を、一つ以上のPMOSトランジスタに無関係に、行い得る。

【0042】

さらに、必要に応じ、PLD103内の一つの要素のボディバイアスを、その他のすべ

10

20

30

40

50

ての要素に無関係に、調整し得る。本発明の記述からメリットを享受する当業者は理解するよう、必要に応じ、PLDのいくつかの部品のボディバイアス調整を行い得、さらにPLDのその他の部品の固定またはデフォルトのボディバイアスを提供し得る。

#### 【0043】

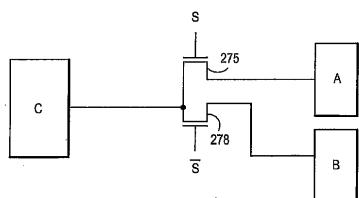

ボディバイアス調整の粒状度の例として、2入力、1出力のMUXを考慮されたい。図5は、ボディバイアス調整を含む発明の例示的実施形態に従うPLDにおいて使用されるMUXを示す。MUXは、トランジスタ275およびトランジスタ278を含む。MUXは、回路Aから信号を受信し、別の信号を回路Bから受信する。選択信号、S、およびそのコンプリメントS'に応答し、MUXは、回路Aまたは回路Bのいずれかからの信号を回路C(MUXの出力に結合された)に伝送する。

10

#### 【0044】

トランジスタ275およびトランジスタ278のボディバイアスは多数の方法で調整し得る。第1に、ボディバイスを調整しないことを選択し得る(たとえば、PLD内のデフォルトボディバイアスを使用する)。第2に、トランジスタ275のボディバイアスをトランジスタ278のボディバイアスと同レベルに調整し得る。代案として、トランジスタ275およびトランジスタ278のみのボディバイアスを調整し得る。別の選択として、トランジスタ275およびトランジスタ278の各々のボディバイアスを個々に調整し得る。

#### 【0045】

従って、MUXの性能特性を柔軟性ある方法で構成し得る。他の方法では、MUXの動作速度、電流駆動能力、およびワット損のバランスまたはトレードオフを、互いに対しても、行い得る。さらなる例として、ボディバイアス調整コンセプトを、MUXのトランジスタの一セット、特定の信号ルート(たとえば、特定の入力に対応した信号伝送ルーティング)、パストランジスタの一セット(たとえば、プログラマブルルーティングにおけるパストランジスターセットで、それが、構成メモリビット数を節約するために他のパストランジスタのセットによって共有されたMUXに入力する)、などに広げ得ることに注意されたい。

20

#### 【0046】

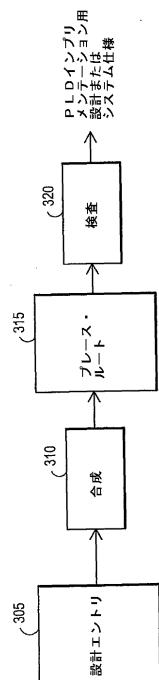

上記のとおり、ユーザーは、本発明に従い、PLDの種々の部分のボディバイアスを調整し得る。ユーザーは、PLDの設計をマッピングするために使用されるソフトウェアを使用することによって、そのように行い得る。図6Aは、発明の例示的実施形態に従うPLDコンピュータ支援設計(CAD)ソフトウェアが使用する種々のソフトウェアモジュールを示す。モジュールは、設計入力モジュール305、合成モジュール310、プレース・ルートモジュール315、および検査モジュール320を含む。

30

#### 【0047】

設計入力(design-entry)モジュール305は、多様な設計ファイルの統合を可能にする。ユーザーは、必要に応じ、設計入力モジュール305を使用することによってまたは種々の電子設計オートメーション(EDA)またはCADツール(業界標準のEDAツールなど)を使用することによって、設計ファイルを生成し得る。ユーザーは、必要に応じ、グラフ形式、波形ベース形式、スケマティック形式で、テキストまたはバイナリ形式で、またはこれらの形式の組み合わせで、設計を入力し得る。

40

#### 【0048】

合成モジュール310は、設計入力モジュール305の出力を受け取る。ユーザー提供の設計に基づき、合成モジュール310は、ユーザー提供の設計を実現する適切なロジック回路網を生成する。一つ以上のPLD(明白には示されてない)は、合成された全体設計またはシステムを実行する。合成モジュール310はまた、ユーザーの設計における種々のモジュールの統合および適切な動作およびインタフェースを可能にする任意のグループ(g1ue)ロジックも生成し得る。たとえば、合成モジュール310は、一つのブロックの出力が別のブロックの入力と適切にインタフェースするように、適切なハードウェアを提供する。合成モジュール310は、全体設計またはシステムにおいてモジュールの各

50

々の仕様に合致するように、適切なハードウェアを提供する。

【0049】

さらに、合成モジュール310は、合成された設計を最適化するためのアルゴリズムおよびルーチンを含み得る。最適化によって、合成モジュール310は、全体設計またはシステムを実行する一つ以上のPLDのリソースをより効率的に使用するよう努める。合成モジュール310は、プレース・ルートモジュール315への出力を提供する。

【0050】

プレース・ルートモジュール315は、最適なロジックマッピングおよび配置を行うため、設計者のタイミング仕様を使用する。ロジックマッピングおよび配置は、PLD内のルーティングリソースの使用を決定する。換言すると、設計の所定の部品のためにPLDとの特定のプログラマブル相互接続を使用することによって、プレース・ルートモジュール315は、全体設計またはシステムの性能の最適化を支援する。PLDルーティングリソースを適切に使用することによって、プレース・ルートモジュール315は、全体設計またはシステムのクリティカルタイミングパスを満たすように支援する。プレース・ルートモジュール315は、本発明の記述からメリットを享受する当業者に知られている方法より速く、クリティカルタイミングパスを最適化し、タイミング閉止の提供を支援する。その結果、全体設計またはシステムは、より速い性能（すなわち、より高いクロックレイトまたはより高いスループットでの動作）を達成し得る。

【0051】

さらに、プレース・ルートモジュール315は、設計およびシステムを実行するPLDの部分またはすべてのボディバイアスを調整する。プレース・ルートモジュール315は、それを自動的に行うか、ユーザー指定の基準に従って行うか、またはその二つの組み合わせに従って、行い得る。プレース・ルートモジュール315は、ユーザー指定の基準（たとえば、ワット損、速度、および/または電流駆動能力などの性能仕様）を使用し得る。さらに、または、その代わりに、プレース・ルートモジュール315は、必要に応じ、設計またはシステムのパートまたはすべてのボディバイアスを調整するために、設計またはシステム内のクリティカルパスに関する情報を使用し得る。

【0052】

たとえば、プレース・ルートモジュール315は、より高い性能を達成するために、設計またはシステムのクリティカルパートのボディバイアスを調整し得る。プレース・ルートモジュール315は、必要に応じ、パワーおよび性能のトレードオフを行うために、ワット損基準（たとえば、最大出力密度）を考慮に入れ得る。プレース・ルートモジュール315は、検査モジュール320に対する最適な設計を提供する。

【0053】

検査モジュール320は、設計のシミュレーションおよび検査を実行する。シミュレーションおよび検査は、設計がユーザーの規定した仕様に従うことを検査することをその一部において努める。シミュレーションおよび検査はまた、設計を試作する前に、すべての設計問題を検出し、修正することを意図する。このように、検査モジュール320は、ユーザーが全体設計またはシステムの総コストを削減し、市場へ出すまでの時間を短縮するよう支援する。

【0054】

検査モジュール320は、必要に応じ、種々の検査およびシミュレーションオプションを支持し、実行し得る。オプションは、必要に応じ、設計規則チェック、機能上の検査、テストベンチ（test-bench）生成、スタティックタイミング解析、タイミングシミュレーション、ハードウェア/ソフトウェアシミュレーション、システム内検査、ボードレベル（board-level）タイミング解析、信号の完全性分析および電磁環境適合性（EMC）、形式的なネットリスト検査、および消費電力推定を含み得る。必要に応じ、また本発明の記述からメリットを享受する当業者は理解するように、他のまたは追加の検査技術が実行し得ることに注意されたい。上記のとおり、発明に従うPLDアーキテクチャおよび回路網は、ユーザーが、PLDまたはPLDの領域において、速度を犠

10

20

30

40

50

牲にしてリーク（および従って、ワット損）に対処できる能力を提供する。ユーザーがこの機能性を使用することをできるだけ便利にするために、発明の例示的実施形態に従うPLD CADは、ユーザーの仕様と基準を自動的に満たすように、回路網を自動的に構成し得る。さらに、ユーザーの回路への速度への影響を最小にしながらリーク減少を最大にするため、発明の種々な実施形態に従うPLD CADは、ユーザー回路のインプリメンテーション時にバイアス領域の存在を考慮し、バイアス領域の有効性を最大にするように回路を最適化する。以下の説明は、PLD CADの機能性の詳細を提供する。

#### 【0055】

基板バイアスを最高に活用するタイミング駆動のPLD CADシステムに関して、設計インプリメンテーション時に、そのシステムが、PLDまたはPLDの各領域（一つ以上のトランジスタを含み得る）に対して基板バイアスを推定すべきである。PLD CADは、設計のタイミング分析時にボディバイアスを考慮に入れる。このように、ボディバイアスレベルは、タイミングの観点から設計のどの部分がクリティカルになるかについて影響する。

#### 【0056】

最初、CADシステムは、ユーザーが一つ以上のトランジスタのボディバイアスレベルの設定またはプログラムを望むPLDの各領域に対して、あるボディバイアスレベル（および従って、リーク／速度設定）を想定する。一つの可能性ある選択として、PLD CADは、すべての影響を受けた領域が比較的低速度設定（すなわち、比較的低リークレベルの結果となるボディバイアス）を使用すると想定し得る。PLD CADシステムは、PLD回路網の初期配置を提供する。配置は、その初期配置の反復の改善によって、進行する。

#### 【0057】

この反復の改善手順の種々の時点において、PLD CADは、回路の速度を推定し、関係するすべての接続に対してタイミングスラック値を計算する。タイミングスラック値の計算は、遅延を推定するときに、各領域に対して選ばれた現在のボディバイアスレベルを考慮に入れる。PLD CADは、ボディバイアス選択を配置の反復の改善にインタリープすることに注意されたい。PLD CADは、より高速な（および対応するより高いリークの）ボディバイアス設定への変換のため、より小さい平均および最悪ケースの接続スラック値を有する回路の部分を含む領域を評価する。CADソフトウェアは、一つ以上の領域について新候補バイアス設定を選択し、回路タイミングの点から新設定の総原価、ならびにリーク電流および／または漏れ電力における全増加を推定することによって、バイアス設定を評価する。新バイアス設定が、領域におけるすべての接続についてプラスのスラック値に導く場合（または、領域におけるより少ないマイナススラックレベル）、PLD CADは、一般に、新バイアス設定を採用する。

#### 【0058】

同様に、CADソフトウェアは、より低速度のボディバイアス設定への変換のために、現在比較的高いバイアス設定を有する領域で、すべての接続がプラスのスラック値を有する領域を評価する。新ボディバイアス採用することが、どの回路タイミング基準に対しても違反を引き起こすことにならない場合、CADソフトウェアは、新ボディバイアス設定を採用する。

#### 【0059】

一つ以上のバイアス設定を変更次第、反復配置改善は、変更されたバイアス設定によって発生するすべての起こりうるタイミングの懸念または違反を解決する試みを継続し、または、よりタイムクリティカルな回路網をより高速度を有する新しく作成されたバイアス領域に移動するよう試みる。配置とルーティングがユーザーのタイミングおよびパワー目標を満たすときか、または、所望または所定の反復限界に達した（それ以上の改善がなされ得ないように見える）のいずれかのとき、アルゴリズムは終了する。

#### 【0060】

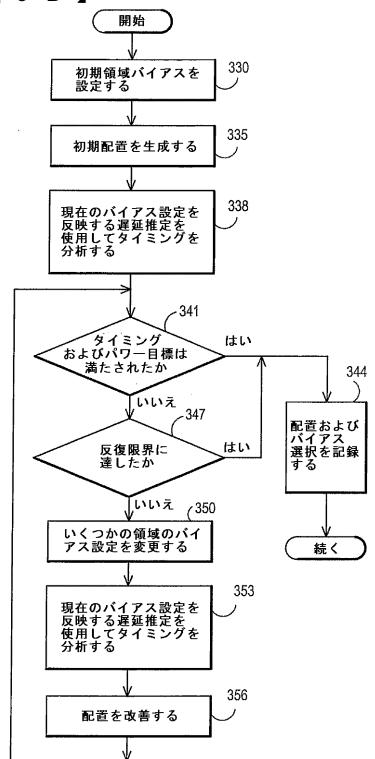

図6Bは、発明の例示的実施形態に従うPLD CADソフトウェアの流れ図を示す。

10

20

30

40

50

図 6 B に示される P L D C A D は、 P L D の各領域に対するボディバイアスの選択をタイミング駆動のプレース・ルート C A D システムに組み入れる。

【 0 0 6 1 】

より具体的には、 3 3 0 において、 P L D C A D は、初期領域ボディバイアス設定をセットする。 3 3 5 において、ソフトウェアは初期配置を生成する。次に、 3 3 8 において、ソフトウェアは、現在のボディバイアス設定を反映する遅延推定を使用して、回路網のタイミングを分析する。 3 4 1 において、ソフトウェアは、ユーザーのタイミングおよびパワー目標を満たしたかどうかについて判断する。満たしたと判断する場合、 3 4 4 において、ソフトウェアは、配置およびボディバイアス選択を記録する。満たさなかったと判断する場合、ソフトウェアは、 3 4 7 において、反復限界に達したかどうかをチェックし判断する。達したと判断する場合、ソフトウェアは、 3 4 4 に進み、現在の配置およびボディバイアス選択を記録する。ソフトウェアが反復限界に達していない場合、ソフトウェアは、反復カウント（明白には示されていない）をインクリメントし、 3 5 0 において、少なくともいくつかの領域のバイアス設定を変更する。 3 5 3 において、ソフトウェアは、変更されたボディバイアス設定を反映する遅延推定を使用して回路網のタイミングを分析する。 3 5 6 において、ソフトウェアは、回路の配置を改善し、 3 4 1 に飛び、ユーザーのタイミングおよびパワー目標を満たしたかどうかを判断する。

【 0 0 6 2 】

本発明の記述からメリットを享受する当業者は理解するように、本明細書に記述されたアルゴリズムの多くの変種を使用し得る。たとえば、すべての領域を低速または高速に設定するなど、種々の初期ボディバイアスの設定を使用し得る。ソフトウェアが、配置におけるすべてのタイミング仕様を満たすと推定する場合、より大きなプラススラック値を有する接続を含む領域を優先して、高速バイアス領域を低速領域への変換を評価する。いくつかの領域を低速領域に変換後に、ソフトウェアは配置改善を再開する。ソフトウェアは、これらの二つのステップをユーザーのパワーおよびタイミングの目標を満たすまで、反復し得る。

【 0 0 6 3 】

第 2 の例として、ソフトウェアは、ユーザーのチップ平面図からバイアス領域の初期設定を生成し得る。ソフトウェアは、高速動作用の平面図におけるタイムクリティカル領域のためのバイアスを初期設定し、比較的低速動作用のその他の領域のためのバイアスを設定する。ソフトウェアは、次に、バイアス選択のさらなる改善のために、図 6 B に示される技術を使用し得る。

【 0 0 6 4 】

第 3 の例として、ソフトウェアは、回路の迅速な配置からボディバイアスの初期設定を生成し、その後続いて、タイミング分析を行い、速度クリティカル領域をその他の領域から識別し得る。配置は、正規の配置を構成し得るか、または、どのボディバイアス領域においてユーザーの回路の各パートを見つけるかを判断する「粗配置」を構成し得る。ソフトウェアは、次に、これらの初期バイアス設定をさらに改善するために、図 6 B のアルゴリズムを使用し得る。

【 0 0 6 5 】

第 4 の例として、配置を開始する前に、ソフトウェアは、回路をボディバイアス領域を構成する比較的大きな回路要素にクラスタ化し得る。クラスタの各々は、タイムクリティカルかまたは非タイムクリティカルである回路網から成り立ち得る。ソフトウェアは、クラスタを P L D のボディバイアス領域を表す粗いグリッド上に配置し得る。ソフトウェアは、次に、ソフトウェア内に置かれた回路網の種類に従い、各領域のバイアスレベルを設定し得る。このように、タイムクリティカルな回路は、比較的高速のボディバイアス設定を受け取り、一方非タイムクリティカル回路は、比較的低速を受け取る。ソフトウェアは、次に、配置を改善するこれらの初期バイアス設定を有する図 6 B にあるアルゴリズムを使用し得る。

【 0 0 6 6 】

10

20

30

40

50

第5の例として、ルーティングアルゴリズムなどの配置アルゴリズム以外のその他のアルゴリズムは、それらのアルゴリズムの遅延推定における所定の領域のボディバイアスを考慮し得る。領域ボディバイアス選択および正規のアルゴリズム最適化をインタリープすることによって、そのようなアルゴリズムをボディ領域バイアス微同調にインタリープし得る。

#### 【0067】

一旦、PLD CADが、設計をインプリメントすると（たとえば、設計を合成し、配置し、ルーティングする）、CADソフトウェアは、ボディバイアス回路網（たとえば、ボディバイアス生成回路網、ボディバイアス制御回路網）を正しい状態およびボディバイアスレベルに自動的にセットする。ソフトウェアは、ボディバイアス回路網の動作の詳細およびユーザーの目標によるいくつかの方法によって、その動作を行い得る。

#### 【0068】

一つの代案として、ユーザーが漏れ電力目標を有し、バイアス回路網は、リークロックループ（leakage-locked loop）（詳細は下記）を組み入れている場合、PLD CADは、漏れ電力がユーザーのワット損目標より少ないか同等になるようにバイアス回路網を設定する。CADソフトウェアは、次に、比較的高温で回路のタイミングを、および、リーク電流の「オン」トランジスタ駆動電流に対する最高比率を有する処理コーナーを、回路がその処理および動作条件においてすべてのタイミング仕様を満たすようにして、解析し得る。代わりに、ユーザーが、すべてのタイミング仕様を満たす条件で、漏れ電力を最小にする目標を有する場合、トランジスタが、最悪の予想される処理および動作コーナーにおいてすべてのタイミングの制限を満たす状況において動作するように、ソフトウェアは、各領域におけるリークロックループを設定し得る。一般に、コーナーは、比較的高温で、および、リーク電流の「オン」トランジスタ駆動電流に対する最高比率を有する処理コーナーにおいて発生する。

#### 【0069】

別の代案として、ユーザーがいくつかのタイミング仕様を満たす条件で電力を最小にする目標を有し、バイアス回路網が遅延ロックループを含む場合、CADソフトウェアは、回路がこれらのタイミング仕様を満たすように、遅延ループを設定またはプログラムし得る。ソフトウェアはそのような動作を、タイミング解析によって各ボディバイアス領域における回路網から最もクリティカルなパスを抽出することによって、行い得る。遅延ロックループがプログラマブル遅延連鎖を使用する場合、ソフトウェアは、それが各ボディバイアス領域における基準連鎖の遅延を、対応するボディバイアス領域のクリティカルパスの名目遅延より大きい名目遅延値に設定するように回路網を設定する。ソフトウェアは、クリティカルパス用ランチ（launch）およびキャプチャエッジを定義する適切なクロック信号を遅延ロック回路網へ伝送する。通例、同じクロック信号は、ランチと捕獲エッジの両方を定義するが、複数の位相および周波数関係クロック信号を有する設計において、別のクロックドメインが、ランチおよび捕獲エッジを定義し得る。遅延ロックループが「ソフト」で、あるPLD回路網にロックする場合、CADシステムは、遅延ロックループの基準遅延として使用されるよう、各バイアス領域に対する各クリティカルパスのできるだけ正確なコピーを行う。

#### 【0070】

さらに代案として、PLD CADは、ボディバイアス回路網をプログラムすることによって、ユーザーに種々の電力と遅延との間のトレードオフの選択を行う能力を与える。その場合、CADソフトウェアは、ユーザーが選んだバイアス設定に従う適切な電力および遅延モデルを調べ、それらのモデルを電力およびタイミング解析において使用する。ソフトウェアは、電力および遅延モデルをより旧式でないようとする（最悪ケース）。これは、ユーザーへの出荷前にデバイスをテストすることによって、またPLD（たとえば、PLD内にある不揮発性メモリ）においてトランジスタ速度およびリークを示すデータを（一般に閾値電圧の形式で）格納することによって、行われる。CADソフトウェアは、プログラム時に、ユーザーの所望の電力遅延トレードオフをデバイスに、なおもプログラ

10

20

30

40

50

ムするが、オンチップハードウェアは、この「所望された」トレードオフを格納されたデバイス特性と比較し、トランジスタが所望の電力遅延トレードオフを有するように、適切なボディバイアスレベルを計算し、適用する。

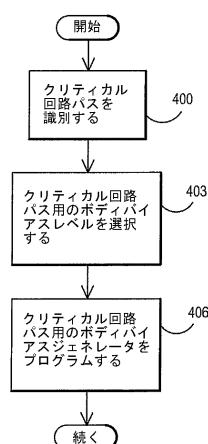

#### 【0071】

図7は、発明の例示的実施形態に従うボディバイアス調整の処理の流れ図を示す。図6Aに関連して記述されたソフトウェアなどのプログラムは、図7における処理を実行する。

#### 【0072】

403において一旦処理が開始すると、処理は、上記、および本発明の記述からメリットを享受する当業者は理解するように、設計またはシステムをインプリメントするPLD内のクリティカル回路パスを識別する。403において、処理は、識別されたクリティカル回路パス内のトランジスタのボディバイアスを調整する。換言すると、処理は、一つ以上のトランジスタまたはトランジスタのセット用の一つ以上のボディバイアスレベルを選択する。次に、406において処理は、クリティカル回路パス用に一つ以上のボディバイアスジェネレータをプログラムまたは構成する。ボディバイアスジェネレータは、403で選択された一つ以上のボディバイアスレベルを生成する。

#### 【0073】

処理は、識別されたクリティカル回路パスまたはブロックだけに限定する必要がないことに注意されたい。その代わり、またはさらに、ユーザーが特定の性能基準を満たすことを希望した回路パスまたはブロックをユーザーは、識別し指定し得る。たとえば、ユーザーは、PLD内でインプリメントされた高速加算器を有することを希望し得る。ユーザーは、加算器をインプリメントするために使用される回路網またはブロックを識別し得、特定のタイミング仕様を満たすために回路網またはブロックのボディバイアスレベルを調整するソフトウェアを指定し得る。ユーザーは、ワット損などのその他の性能仕様または基準を提供し得る。ソフトウェアは、回路パスまたはブロックのボディバイアスレベルを選択するために、種々性能仕様をトレードオフし得る。

#### 【0074】

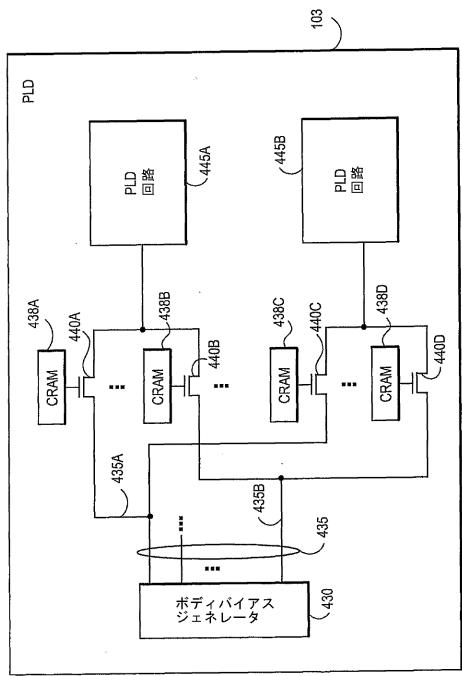

図8は、所望のPLD回路網またはブロックの調整、プログラムまたは設定するために、発明の例示的実施形態に従うPLD内の回路のブロック図を示す。回路網は、ボディバイアスジェネレータ430、複数の構成メモリ（構成ランダムアクセスメモリ、すなわち、CRAM、またはその他のメモリのインプリメンテーション）セル438A～438D、複数のトランジスタ440A～440D、およびPLD回路445A～445Bを含む。

#### 【0075】

ボディバイアスジェネレータ430は、一つ以上のボディバイアス信号435を生成し、それらの信号をトランジスタ440A～440Dに提供する。CRAMセル438A～438Dにあるデータの各々の一つに応答し、トランジスタ440A～440Dは、ボディバイアス信号435をPLD回路445A～445Bに提供する。PLD回路445A～445Bは、上記の、個別トランジスタ、トランジスタのグループ、回路ブロック回路などの回路でその回路のボディバイアスレベルを設定、プログラム、または調整することが所望される回路網を構成し得る。

#### 【0076】

たとえば、CRAMセル438Aおよび438Cはバイナリ1を格納するが一方、CRAMセル438Bおよび438Dはバイナリ0を格納すると想定されたい。その結果、トランジスタ440Aおよび440Cはオンとなり、ボディバイアス信号435AをPLD回路445A～445Bに供給する。トランジスタ440Bおよび440Dはオフとなり、従ってどの信号もPLD回路445A～445Bに供給しない。

#### 【0077】

別の例として、前の例の逆の状況が存在する（すなわち、CRAMセル438A～438Dがバイナリデータ0,1,0,1をそれぞれ保持する）と想定されたい。この場合、

トランジスタ 440A および 440C はオフとなり（従って、信号を P L D 回路 445A ~ 445B に供給しない）、トランジスタ 440B および 440D はオンとなる。その結果、トランジスタ 440B および 440D はボディバイアス信号 435B を P L D 回路 445A ~ 445D に供給する。

#### 【 0078 】

例示的な実施形態において、C R A M セル 438A ~ 438D は、必要に応じ、複数の目的を扱う。より具体的には、C R A M セル 438A ~ 438D は P L D 内の種々の回路網（たとえば、P L D 回路 445A または 445B）のボディバイアスを制御し得る。さらに、C R A M セル 438A ~ 438D はルーティング C R A M セルとして働き得る。換言すると、ボディバイアスレベルの制御に加えて、C R A M セル 438A ~ 438D の一つ以上は、必要に応じ、M U X 内の一つの回路バスを別のバスに優先して選択し得る（すなわち、M U X 内の代替のルーティングと反対に、M U X 内の一つのルーティングを選択し得る。 10

#### 【 0079 】

本発明の記述からメリットを享受する当業者は理解するように、種々の方法でボディバイアスジェネレータ 430 をインプリメントし得ることに注意されたい。たとえば、バイアスソース（たとえば、種々の公知のバイアスソースの一つ）を使用し得、次に、チャージポンプを使用してボディバイアス信号 435 を生成し得、その信号は適切または所望のレベルに注入される。別の例として、ボディバイアスレベルに対応して格納されたデジタルデータを使用し得、所望のボディバイアス信号 435 を生成するために、一つ以上のデジタル - アナログ変換器（D A C）と共に一つ以上のスケーラ回路を使用し得る。 20

#### 【 0080 】

ボディバイアスレベルの調整、プログラムまたは設定に加えて、ワット損、および従って、P L D の出力密度を制御するために他の手段を使用し得る。より具体的には、P L D 内の回路網の部分を選択的に遮断または電源を切り得る。その結果、P L D 内のワット損をさらに減少し得る。 30

#### 【 0081 】

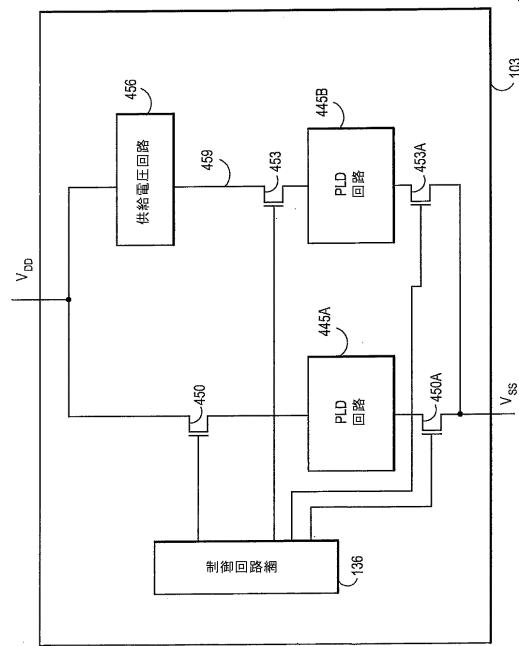

図 9 は、発明の例示的な実施形態に従い、回路網の電源を選択的にオフにするか、あるいは、P L D 内の回路網の消費電力を削減または全体的制御するための回路のブロック図を示す。回路は、制御回路網 136、トランジスタ 450、および P L D 回路 445A を含む。さらに、回路は、トランジスタ 450A、トランジスタ 453、供給電圧回路 456、トランジスタ 453A および P L D 回路 445B を含み得る。 30

#### 【 0082 】

P L D 回路 445A の遮断を希望すると想定されたい。トランジスタ 450 は P L D 回路 445A を供給電圧  $V_{DD}$  に結合する。換言すると、トランジスタ 450 がオンの場合、P L D 回路 445A は供給電圧  $V_{DD}$  を受け取る。逆もまた同様である。トランジスタ 450 は、制御回路網 136 からの制御信号に応答し、電源をオンおよびオフする。このように、P L D 回路 445A の電源をオフするために、制御回路網 136 をトランジスタ 450 のゲート信号をデアサート（d e - a s s e r t）にし、P L D 回路 445A への電源供給を中断させる。その後、制御回路網 136 の監視の下にトランジスタ 450 のゲート信号をアサート（a s s e r t）することによって、P L D 回路 445A の電源をオンにし得る。 40

#### 【 0083 】

トランジスタ 450 の電源をオンまたはオフにするよりはむしろ、トランジスタ 450 を可変インピーダンスデバイスとして使用するためにトランジスタ 450 のゲート電圧を制御し得ることに注意されたい。このように、トランジスタ 450 は、極限において、比較的高いインピーダンス（オフ状態）、比較的低いインピーダンス（オン状態）、または、それらの二状態間のインピーダンスレベルを有し得る。その結果、P L D 回路 445A の電源をオフおよびオンするだけでなく、トランジスタ 450 のインピーダンスを制御することによって、それらの回路内のワット損をも制御する。 50

## 【0084】

供給電圧  $V_{DD}$  を PLD 回路 445A への供給を制御する（上記のとおり、電源をオン、オフまたはこれらの極限間のどれにでも）トランジスタ 450 を使用することに加えて、またはその代わりに、供給電圧  $V_{SS}$ （代表的には、回路アース）の供給を制御するトランジスタ 450A を使用し得る。本発明の記述からメリットを享受する当業者は理解するように、動作の詳細は、トランジスタ 450 および供給電圧  $V_{DD}$  に関する上記の詳細と同様である。

## 【0085】

PLD103 は、必要に応じ、一つ以上得の供給電圧を使用し得る。換言すると、一次供給電圧  $V_{DD}$  から二次供給電圧を生成するために、供給電圧回路 456 を任意に使用し得る。二次供給電圧 459 は、必要に応じ、一次供給電圧より小さいまたは大きい絶対値を有し得る。さらに、必要に応じ、二つ以上の供給電圧を使用し得る。二次供給電圧 445B は、PLD 回路 445B に電力を供給する。制御回路網 136 の監視の下に、トランジスタ 453 のゲート信号をそれぞれ非表明および表明することによって、PLD 回路 445B を遮断またはパワーアップし得る。

## 【0086】

トランジスタ 453 の電源をオフまたはオンにするよりはむしろ、トランジスタ 453 を可変インピーダンスデバイスとして使用するためにトランジスタ 453 のゲート電圧を制御し得ることに注意されたい。このように、トランジスタ 453 は、極限において、比較的高いインピーダンス（オフ状態）、比較的低いインピーダンス（オン状態）、または、それらの二状態間のインピーダンスレベルを有し得る。その結果、PLD 回路 445B の電源をオフおよびオンするだけでなく、トランジスタ 453 のインピーダンスを制御することによって、それらの回路内のワット損も制御する。

## 【0087】

二次供給電圧 459 を PLD 回路 445B への供給を制御する（上記のとおり、電源をオン、オフまたはそれらの極限間のどれにでも）トランジスタ 453 を使用することに加えて、またはその代わりに、供給電圧  $V_{SS}$ （代表的には、回路アース）の供給を制御するトランジスタ 453A を使用し得る。本発明の記述からメリットを享受する当業者は理解するように、動作の詳細は、トランジスタ 453 および二次供給電圧 459 に関する上記の詳細と同様である。

## 【0088】

各 PLD 回路 445A および / または PLD 回路 445B は、必要に応じ、PLD プロック（たとえば、図 1、図 3、および図 4 を参照されたい）、PLD ブロックの部分、または PLD ブロックの一セットを構成し得ることに注意されたい。換言すると、必要に応じ、電力制御技術を、PLD 内の一つ以上のブロック、サブブロック、またはブロックの部分に選択的に適用し得る。

## 【0089】

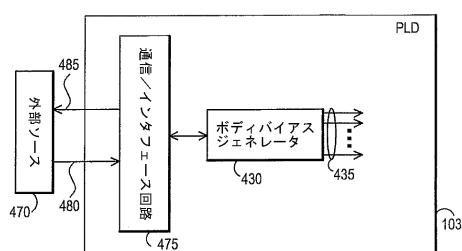

PLD の外部ソースに応答し、ボディバイアスレベルを調整、プログラム、または設定し得ることに注意されたい。たとえば、PLD の性能を調整し、修正するために、ボディバイアスレベルを PLD に伝達し得る。図 10 は、外部ソース 470 に応答し、PLD 内のボディバイアスレベルを調整するための、発明の例示的実施形態に従う回路配置を示す。回路配置は、外部ソース 470、通信 / インタフェース回路 475、およびボディバイアスジェネレータ 430 を含む。

## 【0090】

通信 / インタフェース回路 475 は、情報を通信し交換するため、外部ソース 470 のメカニズムおよびボディバイアスジェネレータ 430 を提供する。外部ソース 470 は、一つ以上の制御信号 480 を PLD103 内の通信 / インタフェース回路 475 に提供し得る。通信 / インタフェース回路 475 は、外部ソース 470 から受け取った情報をボディバイアスジェネレータ 430 に提供する。それに応答して、ボディバイアスジェネレータ 430 は、制御信号 480 に対応するレベルを有する一つ以上のボディバイアス信号 4

10

20

30

40

50

35を生成する。通信／インターフェース回路475は、ボディバイアスジェネレータ430（または一般的にはPLD103）からのステータス信号などの情報を外部ソース470に供給する。

#### 【0091】

本発明の記述からメリットを享受する当業者は理解するように、外部ソース470は、種々のデバイス、構造、または配置を構成し得る。本発明の記述からメリットを享受する当業者は理解するように、たとえば、外部ソース470は、必要に応じ、インターネット、コンピュータネットワーク、バスなどを構成し得る。

#### 【0092】

変化する条件（たとえば、性能仕様における変化）を考慮に入れ、それに応答するため、必要に応じ、ダイナミックまたは時間変動ベースで、PLDにおけるボディバイアスレベルを調整、プログラムまたは設定し得ることに注意されたい。一例として、図10を参照すると、外部ソース470は、それがPLD103に供給する制御信号480を更新、または、修正し得る。応答して、ボディバイアスジェネレータ430は、更新されたまたは修正された制御信号480に対応するボディバイアス信号435を供給する。

#### 【0093】

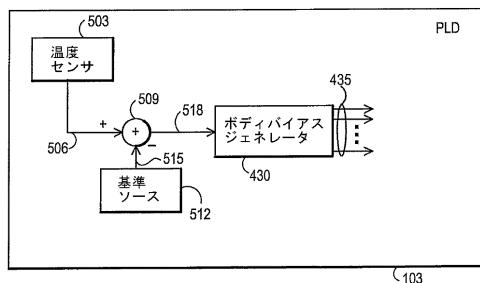

別の例として、PLD103自体内における変化、たとえば、PLD103の一つ以上の回路または領域における温度の変化、に応答して、ボディバイアスレベルを変更または調整し得る。図11は、発明の例示的実施形態に従うPLD内のボディバイアスレベルを修正するための回路配置を示す。

#### 【0094】

回路配置は、一つ以上の温度センサ503、一つ以上の基準ソース512、減算器509、およびボディバイアスジェネレータ430を含む。温度センサ503は、PLD103内の一つ以上の領域、回路またはブロックにおける温度を感知し、温度信号506を減算器509に供給する。基準ソース512は、基準信号515を減算器509に供給する。基準信号515は、種々の温度レベルに対応する数値を有し得る。

#### 【0095】

減算器509は、基準信号515を温度信号506から減じ、差信号518をボディバイアスジェネレータ430に供給する。差信号518は、PLD103の一つ以上のパートにおける実際の温度と所望温度との間の差を構成し得る。

#### 【0096】

差信号518に応答して、ボディバイアスジェネレータ430は、ボディバイアス信号435を生成する。ボディバイアスジェネレータ430は、PLD103の性能の種々の局面に影響するボディバイアス信号435を生成するために差信号518を使用し得る。たとえば、差信号518が、スレショルド温度または最大温度より低い温度を示す場合、ボディバイアスジェネレータ430は、PLD103内の一つ以上のトランジスタの閾値電圧を減少させる（および従って、性能の向上の原因となる）ボディバイアス信号を生成し得る。対照的に、差信号518が、安全レベルまたは最大レベルより高い温度レベルを示す場合、ボディバイアスジェネレータ430は、PLD103内の一つ以上のトランジスタの閾値電圧を増加させる（従って、性能の劣化にもかかわらず温度レベルの減少の原因となる）ボディバイアス信号を生成し得る。

#### 【0097】

より一般的には、特定の性能基準を目標にして、ボディバイアスレベルを生成するフィードバックループをインプリメントし得る。別の言い方をすると、PLDの実際の性能手段と所望または特定の手段または基準と比較し、それに従い、ボディバイアスレベルを調整、プログラムまたは設定し得る。

#### 【0098】

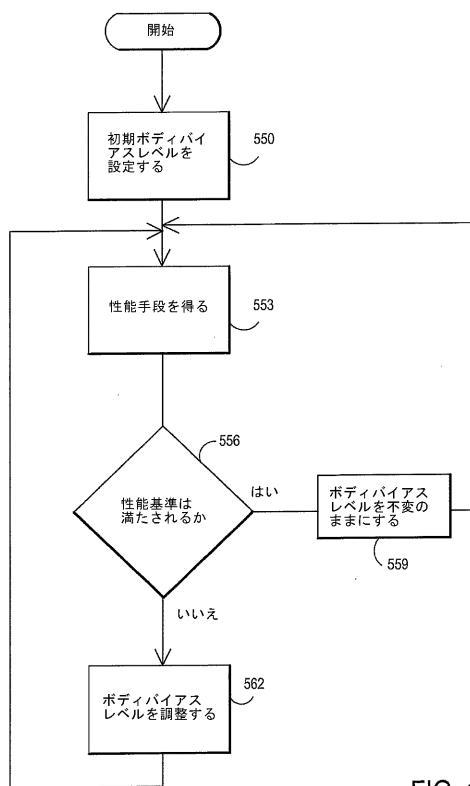

図12は、発明の例示的実施形態において使用されるPLDにおけるボディバイアスレベルを調整、プログラムまたは設定する処理または技術の流れ図を示す。制御回路網136などの適切な回路網（または、回路網およびソフトウェアまたはファームウェアとの組

10

20

30

40

50

み合わせ)を使用することによって、処理または技術をインプリメントし得る。

#### 【0099】

処理は以下のとおり動作する。550において、PLDの所望の部分用の初期ボディバイアスレベルを設定またはプログラムする。その後、553で、PLDの性能手段を得る。本発明の記述からメリットを享受する当業者は理解するように、性能手段は、所定の動作に要する時間、消費電力、出力密度、スループット、オンチップセルフテスト結果などの幅広い様々の基準を含み得る。

#### 【0100】

次に、556において、実際の性能手段が所望または指定の基準を満たすかどうかの判断のためチェックする。満たす場合、559において、処理は、ボディバイアスレベルをそのままにする。他方、実際の性能手段が所望または指定の基準を満たさない場合、562において、処理は、実際の性能手段と所望の性能手段との間の差を減少させるように新しいまたは更新されたボディバイアスレベルを調整、プログラム、または設定する。次に、処理は、553に戻り、実際の性能手段に対する新しいボディバイアスレベルの影響をチェックする。処理は、必要に応じ、無期限か所定の回数を継続し得る。

10

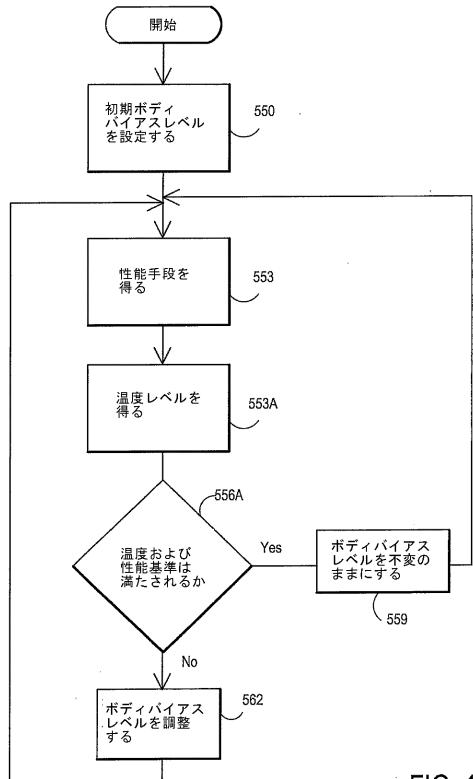

#### 【0101】

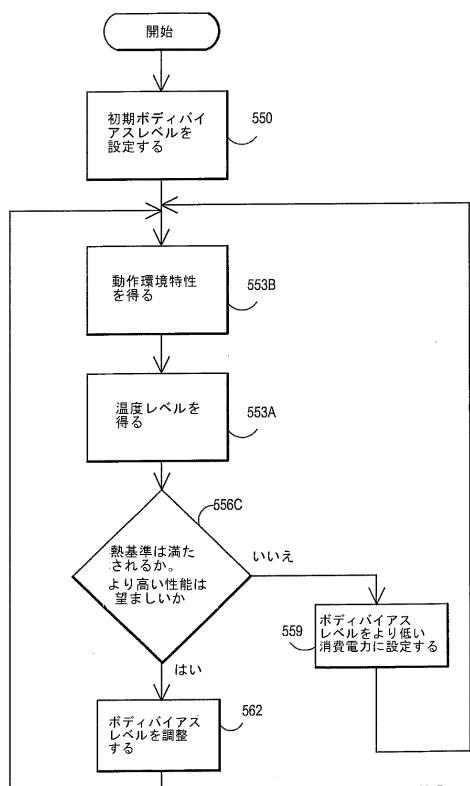

性能手段(たとえば、動作速度、スループット、消費電力など)をチェックすることに加え、PLD内の一つ以上のパートまたは回路の温度レベルをチェックし得る。図13は、温度レベルを考慮に入れ、ボディバイアスレベルを調整、プログラム、または設定する処理または技術の流れ図を示す。上記の通り、制御回路136などの適切な回路網(または、回路網およびソフトウェアまたはファームウェアとの組み合わせ)を使用することによって、処理または技術をインプリメントし得る。

20

#### 【0102】

550において、処理は、PLD内の所望のトランジスタ、回路、ブロックなどの初期ボディバイアスレベルを設定、プログラム、または、調整する。553において、処理は、性能手段を得る。上記のとおり、性能手段は、幅広いパラメータまたは変数を含み得る。当業者が理解するように、性能手段の選択は、PLDがインプリメントする回路またはシステムのための設計および性能仕様などの要因に依存する。

#### 【0103】

その後、553Aにおいて、処理は、温度レベルを得る。上記のとおり、PLDの種々のパートから一つ以上の温度レベルを得、チェックし得る。例示的実施形態において、任意の識別されたクリティカルパス、または、一般に、比較的に高消費電力および従って比較的に高温度レベルを有し得る任意の回路網から温度レベルを得られ得る。

30

#### 【0104】

556Aにおいて、処理は、実際の性能手段が所望または指定の基準を満たすかどうかの判断のためチェックする。さらに、処理は、実際の温度レベルが所望または指定の基準を満たすかどうか(たとえば、実際の温度が所定の範囲内にあるかまたはスレショルドレベル以下に落ちるかどうか)の判断のためチェックする。

#### 【0105】

559において、両方との条件が当てはまる場合、処理はボディバイアスレベルを不变のままにする。しかし、両方との条件が当てはまらない場合、562において、処理は、実際の性能手段と所望の性能手段との間の差および実際の温度レベルと所望または所定の温度レベルとの差を減らすように、新しいまたは更新されたボディバイアスレベルを調整、プログラム、または設定する。次に、処理は、553に戻り、実際の性能手段、および温度レベルに対する新しいボディバイアスレベルの影響をチェックする。処理は、必要に応じ、無期限か所定の回数を継続し得る。

40

#### 【0106】

その他の実施形態において、PLDがインプリメントする回路またはシステムの動作環境に応答または依存して、ボディバイアスレベルを調整、プログラムまたは設定し得る。たとえば、通信ネットワークのコントローラまたはルータを実現するために、発明に従う

50

P L D を使用すると仮定されたい。動作時、P L D は、コントローラまたはルータが動作する環境の条件または特性についての情報を得られ得る。

#### 【 0 1 0 7 】

たとえば、P L D は、環境内のトラフィックレベルに関する手段を得られ得る。P L D の動作環境における条件またはその特性に依存し、P L D は、P L D の性能が動作環境の必要性にマッチするように、P L D の一つ以上のトランジスタにおけるボディバイアスレベルを調整、プログラムまたは設定し得る。もちろん、上の例は、そのようなP L D を使用し得る方法の一例示を構成するに過ぎない。本発明の記述からメリットを享受する当業者は理解するように、発明コンセプトを、回路、システムおよび動作環境で、各々それ自身の特性および条件を有する幅広い回路、システムおよび動作環境に適用し得る。

10

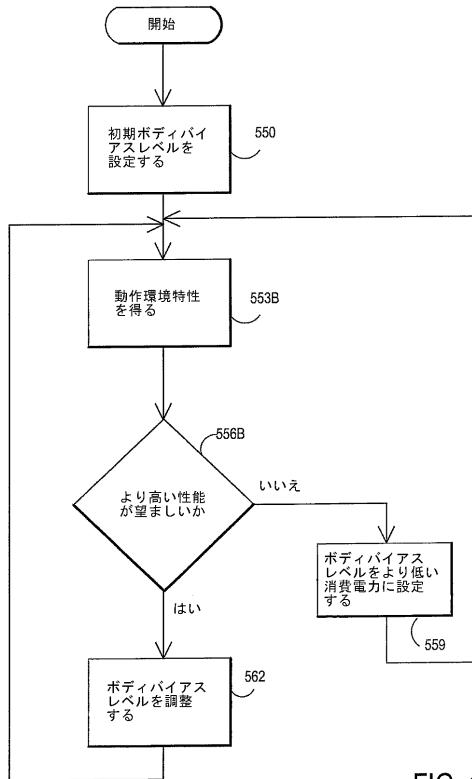

#### 【 0 1 0 8 】

図14は、P L D が動作する環境の特性または条件を考慮に入れ、ボディバイアスレベルを調整、プログラム、または設定する処理または技術のための流れ図を示す。上記のとおり、制御回路網136などの適切な回路網（または、回路網およびソフトウェアまたはファームウェアとの組み合わせ）を使用することによって、処理または技術をインプリメントし得る。

#### 【 0 1 0 9 】

処理は以下のとおり動作する。550において、P L D の所望の部分のための初期ボディバイアスレベルをプログラムまたは設定する。その後、553Bにおいて、P L D が動作する環境、回路またはシステムの一つ以上の条件または特性を得る。上記のとおり、条件または特性は、幅広い様々なアイテムを含み得る。

20

#### 【 0 1 1 0 】

次に、556Bにおいて、処理は、動作環境の条件または特性がP L D のより高い性能レベルを望ましくするかどうかについて判断するためにチェックする。（上の例を使用するため、たとえば、ネットワークトラフィックレベルは比較的高く、従って、より高いP L D 性能またはスループットをより望ましくするかどうか）そうでない場合は、559において、処理は、ボディバイアスレベルをそのままにする。他方、より高いP L D 性能またはスループットが望ましい場合、562において、処理は、実際の性能手段と所望の性能手段との差を減らすように、新しいまたは更新されたボディバイアスレベルを調整、プログラム、または設定する。次に、処理は、553Bに戻り、実際の性能手段に対する新しいボディバイアスレベルの影響をチェックする。処理は、必要に応じ、無期限か所定の回数を継続し得る。

30

#### 【 0 1 1 1 】

所定のアプリケーションまたはインプリメンテーション用の設計および性能仕様などの要因によって、発明コンセプトに従う種々の実施形態を使用し得る。たとえば、図14を参照すると、図13に関連し記述された実施形態と同様に、必要に応じ、P L D の種々のバーツの温度レベルを考慮に入れ得ることに注意されたい。

#### 【 0 1 1 2 】

別の言い方をすると、より高いP L D 性能またはスループットの望ましさを検査するのみならず、P L D 内の温度レベルまたは出力密度が向上したP L D 性能を安全または適切にするかどうかについても検査する。図15は、そのような実施形態を実現する処理を示す。その手順をアプリケーションによって、所望の回数を繰り返し得る。上記のとおり、制御回路網136などの適切な回路網（もしくは、回路網およびソフトウェアまたはファームウェアとの組み合わせ）を使用することによって、処理または技術をインプリメントし得る。

40

#### 【 0 1 1 3 】

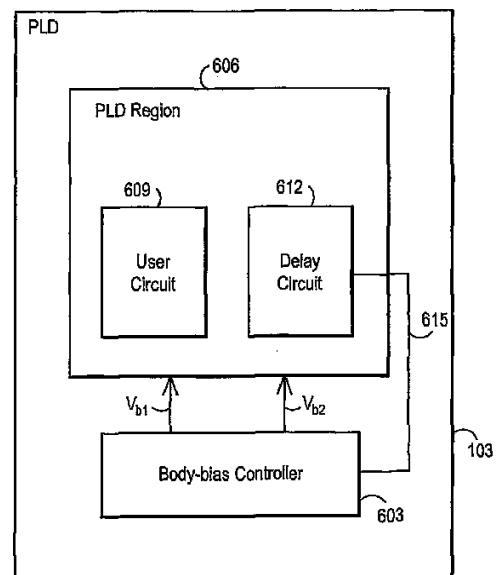

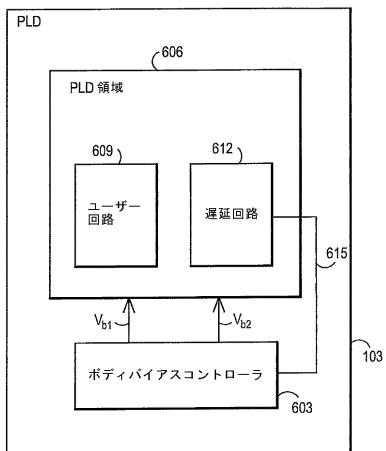

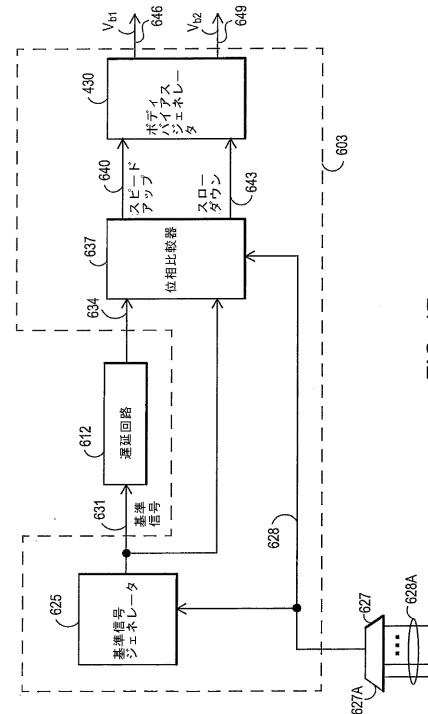

本開示の別の局面は、P L D 内の選択された回路または領域の遅延を測定することによって、P L D 内の回路網のボディバイアスの設定または調整に関する。図16は、ユーザー回路のトランジスタのボディバイアスを、ユーザー回路の動作遅延を表す遅延に基づき調整する回路配置を示す。より具体的には、回路配置は、P L D 103、P L D 領域60

50

6、ユーザー回路 609、遅延回路 612、およびボディバイアスコントローラ 603 を含む。

【0114】

P L D 領域 606 は、ユーザー回路 609 および遅延回路 612 を含む。ユーザー回路 609 は、ユーザーインプリメントまたは指定の回路、または回路の部分（たとえば、クリティカルパス）などの任意の所望の回路網を含み得る。遅延回路 612 は、ユーザー回路 609 の実際の遅延を表すか、またはそのモデルとなる。一般に、遅延は、ユーザー回路 609 の遅延を表し、遅延は、ユーザー回路 609 と同じ遅延を有する必要はない。たとえば、遅延回路 612 は、必要に応じ、ユーザー回路 609 と同じ遅延、2 倍の遅延、半分の遅延などを有し得る。

10

【0115】

遅延回路 612 は、信号リンク 615（導体などの一つ以上の結合メカニズム）を介して、ボディバイアスコントローラ 603 と結合する。遅延回路 612 の実際の遅延に応答して、ボディバイアスコントローラ 603 は、一つ以上のボディバイアス信号を P L D 領域 606 の少なくともいくつかのトランジスタを提供する（詳細は以下に記述される）。

【0116】

図 16 は、二つのボディバイアス信号  $V_{b_1}$  および  $V_{b_2}$  を示すことに注意されたい。ボディバイアス信号は、P L D 領域 606 における少なくとも一つのトランジスタのボディバイアスを調整または設定する。たとえば、一方のボディバイアス信号（たとえば、 $V_{b_1}$ ）は、P M O S トランジスタのボディバイアスを設定し得るが、他方のボディバイアス信号（たとえば、 $V_{b_2}$ ）は、N M O S トランジスタであるボディバイアスを設定し得る、などである。ユーザー回路 609 におけるトランジスタのボディバイアスを調整することによって、上記のとおり、ユーザー回路の速度とリードとを制御または調整し得る。

20

【0117】

図 17 は、発明の例示的実施形態に従うボディバイアスコントローラ 603 のブロック図を示す。ボディバイアスコントローラ 603 は、基準信号ジェネレータ 625、遅延回路 612、位相比較器 637、およびボディバイアスジェネレータ 430 を含む。任意に、ボディバイアスコントローラ 603 は、詳細は以下に記述のとおり、M U X 627 を含み得る。

30

【0118】

基準信号ジェネレータ 625 は、クロック信号 628 から基準信号 631 を生成する。回路の実際の設計およびインプリメンテーションに依存する要因（たとえば、遅延回路 612 における遅延とユーザー回路 609 における遅延との関係など）により、基準信号 631 は、必要に応じ、クロック信号 628 と特定の関係を有し得る。たとえば、基準信号 631 は、クロック信号 628 の半分の周波数を有し得る。基準信号 631 は、遅延回路 612 に入力（feed）する。応答して遅延回路 612 は、基準信号 631 の遅延バージョンである出力信号 634 を生成する。

【0119】

必要に応じ、多数のクロック信号 628 A の一つを選択する能力を提供する M U X 627 を任意に使用し得ることに注意されたい。以下に詳細に記述されているように、ボディバイアスコントローラ 603 は、クロック信号 628 の周期を使用し基準回路の遅延を測定し、その測定の結果を使用して、ボディバイアス信号を生成し P L D 103 内の種々の回路へ供給する。M U X 627 の選択信号 627 A によって、選ばれたクロック信号が所望または特定の周期を有するようにクロック信号 628 A の一つを選択し得る。その方法によって、ボディバイアスコントローラ 603 の柔軟性を増加し得る。

40

【0120】

位相比較器 637 は、基準信号 631 と遅延回路 612 の出力信号 634 を比較する。二つの信号の相対位相によって、比較器 637 は、出力信号 640（スピードアップ）および出力信号 643（スローダウン）を生成する。出力信号 640 および 643 は、ボディバイアスジェネレータ 430 を駆動する。ボディバイアスジェネレータ 430 は、出力

50

信号 640 および 643 に応答して、ボディバイアス信号を生成する。図 17 に示す特定の例において、ボディバイアスジェネレータは、ボディバイアス信号 646 ( $b_1$ ) およびボディバイアス信号 649 ( $b_2$ ) を生成する。

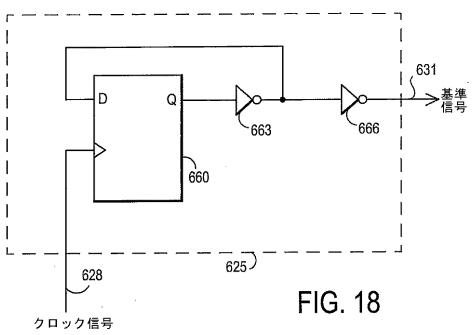

【0121】

図 18 は、本発明の例示的実施形態に従う基準信号ジェネレータ 625 の回路配置を示す。基準信号ジェネレータ 625 は、フリップフロップ 660 ならびにインバータ 663 および 666 を含む。この特定の例において、基準信号ジェネレータ 625 は、2 で割る回路を構成する。このように、フリップフロップ 660 およびインバータ 663 は、クロック信号 628 の周波数の半分を有する信号を生成する。インバータ 666 は、その信号をバッファリングし、基準信号 631 を供給する。本発明の記述からメリットを享受する当業者は理解するように、回路構成およびアプリケーションによって、必要に応じ、インバータ 666 を使用する必要がなく、それを省き得る。

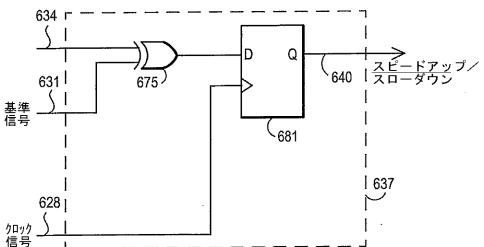

【0122】

図 19 は、発明の例示的実施形態に従う位相比較器 637 の回路配置を示す。比較器 637 は、排他的 OR (XOR) ゲート 675、およびフリップフロップ 681 を含む。遅延回路 612 の出力は、XOR ゲート 675 の 1 入力に入力 (feed) する。基準信号 631 は、XOR ゲート 675 の第 2 の入力に入力する。

【0123】

XOR ゲート 675 の出力は、フリップフロップ 681 のデータ (D) 入力に入力する。クロック信号 628 はフリップフロップ 681 および 684 を駆動する。フリップフロップ 681 の出力 Q は出力信号 640

【0124】

【数 3】

SPEEDUP/SLOWDOWN

を供給する。出力信号が高いことは、回路があまりに遅く流れていることを示し (より順のボディバイアスを有すべき)、を示し、逆もまた同様である (低信号は、回路がより逆のボディバイアスを有すべきことを示す)。

【0125】

遅延回路 612 による遅延がクロック信号 628 の周期より短い場合、ユーザー回路は、あまりに速く動作する。この場合、ゲート 675 の出力は、クロック信号 628 の立ち上がり遷移時にロジックゼロとなる。逆に、遅延回路 612 による遅延がクロック信号 628 の周期より長い場合、ユーザー回路は、あまりに遅く動作する。それらの状況の下に、XOR ゲート 675 は、クロック信号 628 の立ち上がり遷移時の出力時にロジックハイ信号を供給する。その結果、フリップフロップ 681 はスピードアップ出力信号を提供する。

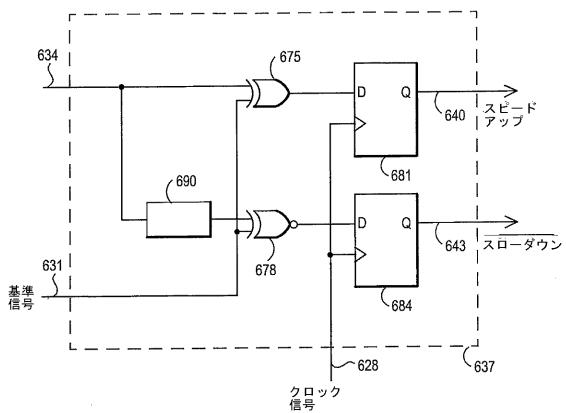

【0126】

図 20 は、発明の例示的実施形態に従う位相比較器 637 の別の回路配置を示す。図 19 と同様に、図 20 の比較器 637 は、排他的 OR (XOR) ゲート 675、排他的 NOR (XNOR) ゲート 678、およびフリップフロップ 681 および 684 を含む。さらに、図 20 の比較器 637 は不感帯遅延回路 690 を含む。不感帯遅延回路 690 は、PLD 103 内のトランジスタをより安定に電力効率的なボディバイアス調整を行う。

【0127】

より具体的には、不感帯遅延回路 690 は、XNOR ゲート 678 が基準信号 634 自体よりはむしろ、基準信号 634 の遅延バージョンを受信する原因となる。不感帯遅延回路 690 がない場合、比較器 637 は、ユーザー回路 609 用の平衡速度、リーク、消費電力を見つけるよう求めるので、比較器のスピードアップおよびスローダウン出力信号を繰り返しおよび交互にアサートし得る。ボディ調整を繰り返す (トランジスタボディの充電と放電) と、電力消費の増加、および従って、効率の低下の原因となる。

【0128】

不感帯遅延回路 690 は、比較器 637 が、その出力時に、「チャタ (chatter)」がより少なくなるように助ける。別の言い方をすると、遅延回路 612 および不感帯遅延回路 690 を含む比較器 637 の場合 (すなわち、図 20)、一つの遅延回路は最小遅延を形成し、両方の合計は最大の遅延を形成する。クロック信号 628 の周期が両方の遅延の合計を超えた場合、ユーザー回路 609 はあまりに速く動作する。その結果、比較器 637 はスローダウン出力信号をアサートする。

#### 【0129】

逆に、クロック周期が遅延回路 612 の遅延より短い場合、ユーザー回路 609 は、あまりに遅く動作する。その結果、比較器 637 はスピードアップ出力信号をアサートする。ユーザー回路 609 が、速度の許容可能または所定の範囲内で (対応するリークおよび消費電力レベルを伴って) 動作する場合、比較器 637 は、その出力信号のいずれもアサートしない。その結果、比較器 637 は、ユーザー回路 609 の許容可能な動作速度を達成するために、比較器の出力信号の繰り返しの変更を避ける。

#### 【0130】

遅延回路 612 は、固定または調整可能な構成可能な遅延のいずれかを提供し得ることに注意されたい。固定遅延の場合、遅延回路 612 は、所望または所定の遅延を有するロジック回路を含む。たとえば、遅延回路 612 は、ゲートなどの組み合わせの論理要素の配置を含み得る。プログラマブルロジック 106 およびプログラマブルルーティングまたは相互接続 109 などの、PLD 103 のプログラマブルリソースを使用して遅延回路 612 をインプリメントし得る (図 1 を参照されたい)。

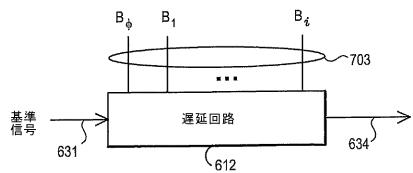

#### 【0131】

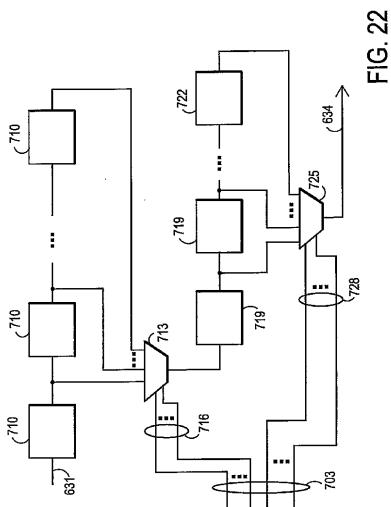

代わりに、遅延回路 612 は、構成可能な遅延を有し得る。図 21 は、発明に従う例示的実施形態における使用のための構成可能な遅延回路 612 を示す。図 21 の遅延回路 612 は、構成または調整信号 703 の 1 セットを受け入れる。信号 703 は、 $B_0 \sim B_i$  で示されるビットの 1 セットを含む。構成信号 703 は、遅延回路 612 の遅延を調整または構成する。換言すると、構成信号 703 においてビットの値を設定することによって、時間量を調整し得、その時間量によって遅延回路 612 は、その出力信号を生成するためにその入力信号を遅延させる。

#### 【0132】

図 22 は、発明の例示的実施形態に従う構成可能な遅延回路の回路配置を示す。構成可能な遅延回路は、相互接続またはルーティング遅延要素 710 の 1 セットのカスケード結合、ロジック遅延要素 719 の 1 セットのカスケード結合、MUX 713 および MUX 725 を含む。

#### 【0133】

ルーティング遅延要素 710 の出力信号は、MUX 713 の入力信号を構成する。MUX 713 はまた、一つ以上の選択信号 716 を受信する。本発明の記述からメリットを享受する当業者は理解するように、選択信号 716 の数は、ルーティング遅延要素 710 の数に依存する。選択信号 716 によって、ルーティング遅延要素 710 の一つの出力を MUX 713 の出力に選択的に結合し得る。このように、第 1 のルーティング遅延要素の入力信号 (基準信号 631) から MUX 713 の出力までの遅延の量を構成し得る。

#### 【0134】

同様に、ロジック遅延要素 719 の出力信号は、MUX 725 の入力信号を供給。MUX 725 もまた、一つ以上の選択信号 728 を受信する。本発明の記述からメリットを享受する当業者は理解するように、選択信号 728 の数は、ロジック遅延要素 719 に依存する。選択信号 728 を使用することによって、ロジック遅延要素 719 の一つの出力を MUX 728 の出力へ選択的に結合し得る。従って、第 1 のロジック遅延要素の入力信号 (すなわち、MUX 713 の出力信号) から MUX 725 の出力までの遅延の量を構成し得る。

#### 【0135】

MUX 713 および MUX 725 を使用することによって、所望数のルーティング遅延

10

20

30

40

50

要素 710 とロジック遅延要素 719 とのそれぞれの遅延組み合わせを構成するために構成可能な遅延回路の遅延を構成し得る。このように、遅延回路の遅延がユーザーの回路の遅延を表すように、遅延回路を構成し得る（たとえば、詳細上記の PLD 構成ソフトウェアによって）。さらに、必要に応じ、ダイナミックな方法で（変化する動作環境、外部制御、ユーザー制御に応答して）遅延を構成し得る。

#### 【0136】

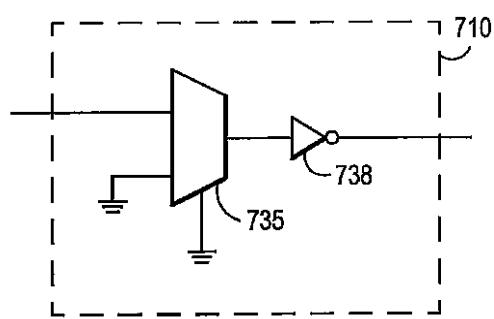

図 23 は、本発明の例示的実施形態に従うルーティング遅延要素 710 用の回路配置を示す。ルーティング遅延要素 710 は、MUX 735 およびインバータ 738 を含む。MUX 735 およびインバータ 738 は、一緒になって、PLD 103 内の代表的なルーティングメカニズム（その対応する遅延を含む）を表すよう捜す。MUX 735 は、その入力の一つおよびその選択入力が接地され、その結果、MUX 735 はその入力信号をインバータ 738 に結合する。インバータ 738 の出力信号は、ルーティング遅延要素 738 の出力信号を構成する。このように、ルーティング遅延ロジック 710 は、その出力信号としてその入力信号の反転したバージョンを供給する。

#### 【0137】

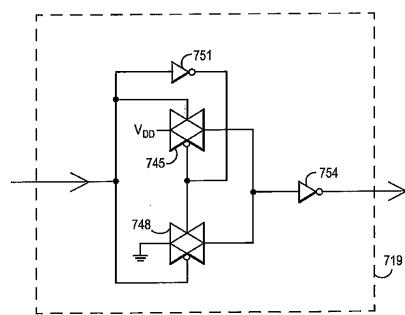

図 24 は、発明の例示的実施形態に従うロジック遅延要素 719 の回路配置を示す。ロジック遅延要素 719 は、送信ゲート 745、送信ゲート 748、インバータ 751、およびインバータ 754 を含む。ロジック遅延要素 719 内の回路要素は、一緒になって、PLD 103 内のプログラマブルロジック回路（およびその回路の対応する遅延）を表すように求める。送信ゲート 745 および 748 およびインバータ 751 は、入力信号（そのロジック値に関わらず）をインバータ 754 の入力に結合するためのメカニズムを提供する。インバータ 754 の出力信号は、ロジック遅延要素 719 の出力信号を構成する。このように、ロジック遅延ロジック 719 は、その出力信号としてその入力信号の反転したバージョンを供給する。

#### 【0138】

図（たとえば、図 18 ~ 20 および 22 ~ 24）は、図が表すそれぞれの回路の例示的な実施形態を提供するに過ぎないことに注意されたい。本発明の記述からメリットを享受する当業者は理解するように、設計および性能仕様などの要因によって、必要に応じ、その他の回路および実施形態を使用し得る。

#### 【0139】

単なる一例として、離散的時間出力値を有する比較器を使用するよりはむしろ、連続的時間出力値を有する比較器を使用し得る。さらに、調整可能またはプログラマブルなボディバイアス信号を PLD 103 の種々のパーツに供給するために、必要に応じ、二つ以上のボディバイアスコントローラ 603（および比較器）を使用し得る。

#### 【0140】

別の例として、必要に応じ、たとえば、制御回路網 136（図 1 を参照されたい）のパーツとしての専用の回路網を使用して、図にある種々の回路（たとえば、ボディバイアスコントローラ 603）を実現し得る。代案として、必要に応じ、PLD 103 のプログラマブルリソースにおけるそれらの回路（たとえば、図 1、図 3、および図 4 を参照されたい）すなわち、プログラマブルロジック 106 およびプログラマブル相互接続 109、をインプリメントし得る。本発明の記述からメリットを享受する当業者は、これらの二つの手法の組み合わせを使用し得ること理解する。換言すると、必要に応じ、一部では PLD 103 のプログラマブルリソースを使用することによって、および、一部では専用の回路網を使用して、回路網を実現し得る。インプリメンテーションが PLD プログラマブルリソースを使用する場合、PLD CAD ソフトウェアは（たとえば、図 6A および附属の説明を参照されたい）、PLD 103 のプログラマブル構造（プログラマブルロジック 106 およびプログラマブル相互接続 109）内の種々の回路要素を配置し、伝送する。

#### 【0141】

さらに、PLD CAD ソフトウェアは、遅延回路 112 をインプリメントする回路要素（組み合わせのロジック要素またはルーティング遅延要素 710 およびロジック遅延要

10

20

30

40

50

素 719) を選択、配置、および伝送する。PLD CAD ソフトウェアは、遅延回路 612 がユーザー回路 609 の遅延を表すように回路要素を選択する。PLD CAD ソフトウェアは、構成メモリ 133 のビット値をプログラムし(図 1 を参照されたい)、構成メモリ 133 は、その後、MUX 選択信号 627A(図 17 を参照されたい)および構成信号 703(図 21 を参照されたい)などの種々の構成またはプログラム信号用の値を供給する。代わりの実施形態において、ユーザーは、ユーザー回路 609 をモデルにするため、遅延回路 612 のパラメータを定義し得る。代わりの実施形態は、ユーザーに対し PLD 回路網の性能をユーザーの仕様または要件に適合させる能力を提供する。

#### 【0142】

一つの遅延回路 612 および比較器 637 を使用するよりはむしろ、その代わりに必要に応じ、複数の遅延回路 612 および/または比較器 637 を使用し得ることに注意されたい。そうすることによって、遅延連鎖によって提供される遅延のより多くの解決、および従って、ボディバイアスコントローラの収束の改善を提供し得る。

#### 【0143】

開示の別の局面は、一般に、IC 内のトランジスタの性能(リーク、速度、およびワット損)を直接に調整またはプログラムする(それらのトランジスタを含む回路の性能をモデルにする遅延回路を使用するよりはむしろ)ことに関する。より具体的には、IC 内の一つ以上のトランジスタのリークレベルをトランジスタのボディバイアスをプログラムまたは調整することによって設定するために、リーコロックループ(LLL)を使用し得る。

#### 【0144】

リーコロックループ技術は、リーク電流の尺度としての代表遅延を使用することによる間接制御よりはむしろ、その技術が回路のリークを直接に制御する能力を提供するというメリット有する。その技術は、ユーザーが許容または所望リークレベルを指定し、性能とリーク電流およびワット損との間の所望のトレードオフを選択し指定することを可能にする。リーコロックループのコンセプトを、一般に、PLD を含む IC に適用し得ることに注意されたい。

#### 【0145】

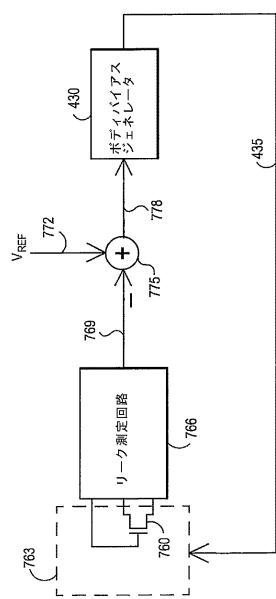

図 25 は、発明の例示的実施形態に従った、リーコロックループのブロック図を示す。リーコロックループは、基準トランジスタ 760、リーク測定回路 766、加算器 775、およびボディバイアスジェネレータ 430 を含む。一般的に言って、リーコロックループは負フィードバック回路を含む。リーコロックループは、IC 回路 763 内のトランジスタのリーク電流を測定するために、基準トランジスタ 760 を使用し、それらのトランジスタ用のボディバイアス信号を生成するために、測定されたリーク電流を使用する。

#### 【0146】

必要に応じ、また、本発明の記述からメリットを享受する当業者は理解するように、他の量を測定するリーコロックループの他の実施形態を設計し得、一つ以上のユーザー指定の基準を満たすように一つ以上のトランジスタのボディバイアスを調整し得ることに注意されたい。そのような量の例は、基準トランジスタの閾値電圧( $V_T$ )または基準トランジスタの飽和電流( $I_{dsat}$ )を含む。

#### 【0147】

基準トランジスタ 760 は、IC 回路 763 にある。必要に応じ、二つ以上の基準トランジスタ 760 を使用し得ること(たとえば、IC 回路 763 の二箇所以上の場所におけるリーク電流を測定すること)に注意されたい。IC 回路 763 は、IC の性能がボディバイアスレベルによって調整またはプログラムされるように求められるその IC 内の回路網を構成する。たとえば、IC は PLD であるという状況において、IC 回路 763 は、ユーザー回路 609 を構成し得る(たとえば、図 16 を参照されたい)。

#### 【0148】

一般に、IC 回路 763 のトランジスタ(基準トランジスタ 760 を含む)が同様な電気的特性を有するようにし、条件の変動(たとえば、処理、電圧、および温度、または P

10

20

30

40

50

V T ) が I C 回路 7 6 3 全体のボディバイアスのプログラムを実質的に劣化しないように、I C 内の回路網の十分に小さな部分を含めて、I C 回路 7 6 3 を選択する。

【 0 1 4 9 】

リーク測定回路 7 6 6 は、基準トランジスタ 7 6 0 のリークを測定し、リーク信号 7 6 9 を加算器 7 7 5 へ供給する。加算器 7 7 5 は、リーク信号 7 6 9 を基準リーク信号 (ref) 7 7 2 に比較し、エラー信号 7 7 8 を生成する。ボディバイアスジェネレータ 4 3 0 は、エラー信号を使用し、一つ以上のボディバイアス信号 4 3 5 を生成する。ボディバイアスジェネレータ 4 3 0 は、ボディバイアス信号 4 3 5 を I C 回路 7 6 0 内の所望のトランジスタに供給する。

【 0 1 5 0 】

図 2 5 のリークロックループにおいて、必要に応じ、構成可能コンポーネントを使用し得ることに注意されたい。たとえば、必要に応じ、リーク測定回路 7 6 6 (構成可能利得)、構成可能加算器 7 7 5 (構成可能利得) または加算器 7 7 5 に続く個別の利得ブロック、構成可能基準リーク信号 7 7 2 (構成可能レベル)、および / またはボディバイアスジェネレータ 4 3 0 における構成可能利得を使用し得る。PLD 構成 RAM ビット、PLD 上のユーザー回路からの信号、またはこの二つの組み合わせを、それらの構成可能コンポーネントの各々を構成するために、必要に応じ、使用し得ることに注意されたい。

【 0 1 5 1 】

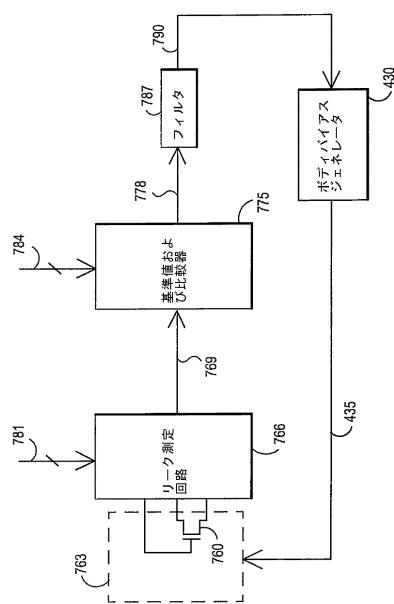

図 2 6 は、発明の別の例示的実施形態に従ったリークロックループのブロック図を示す。図 2 6 におけるリークロックループは、基準トランジスタ 7 6 0 (I C 回路 7 6 3 にある)、リーク測定回路 7 6 6 、基準値および比較器回路 7 7 5 、フィルタ 7 8 7 、およびボディバイアスジェネレータ 4 3 0 を含む。

【 0 1 5 2 】

基準トランジスタ 7 6 0 および I C 回路 7 6 3 は、図 2 5 に関連する上記のそれらのものと同じかまたは同様の構成を有する。リーク測定回路 7 6 6 は、制御信号 7 8 1 によって、プログラマブル利得を供給する。より具体的には、リーク測定回路 7 6 6 がリーク信号 7 6 9 を供給するために、測定されたリーク電流に印加する利得は、制御信号 7 8 1 によって、調整し得る。

【 0 1 5 3 】

基準値および比較器回路 7 7 5 は、リーク信号を処理する。基準値および比較器回路 7 7 5 は、必要に応じて、プログラマブル基準値、プログラマブル利得、またはその両方を、制御信号 7 8 4 によって供給する。換言すると、制御信号 7 8 4 によって、基準リーク信号 (図 2 5 の基準リーク信号 7 7 2 に類似した)、リーク信号 7 6 9 を基準リーク信号と比較しリークエラー信号 7 7 8 を生成する比較器 (明白には示されていない)、またはその両方を、必要に応じ、調整し得る。基準値および比較器回路 7 7 5 は、必要に応じて、比較器の出力信号を量子化する量子化器を任意に含み得る。

【 0 1 5 4 】

フィルタ 7 8 7 は、リークエラー信号 7 7 8 を濾波および処理し、濾波された信号 7 9 0 を生成する。ボディバイアスジェネレータ 4 3 0 は、図 2 5 に関連する上記の方法で動作し、一つ以上のボディバイアス信号を I C 回路 2 6 3 に供給する。

【 0 1 5 5 】

必要に応じ、フィルタ 7 8 7 をリークロックループから省略し得ることに注意されたい。フィルタ 7 8 7 は、利得ブロックまたは回路、ローパス転送機能または積分器トランジスタ機能などの所望の転送機能を有し得る。本発明の記述からメリットを享受する当業者は理解するように、フィルタ 7 8 7 およびその特定の転送機能を含めるかどうかの選択は、設計および性能仕様ならびに考慮に依存する。

【 0 1 5 6 】

必要に応じ、リーク測定回路 7 6 6 、および、基準値および比較器回路 7 7 5 を種々の方法によって実行し得る。本発明の記述からメリットを享受する当業者は理解するように、回路の選択およびインプリメンテーションは、種々の要因 (たとえば、使用される I C

技術、所望の性能特性など)に依存する。図27~図29は、いくつかの例を提供する。

【0157】

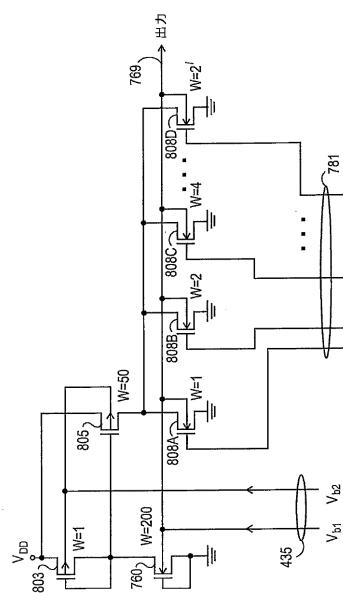

図27は、発明の例示的実施形態に従ったリーク測定回路766を示す。リーク測定回路766は、PMOSトランジスタ803および805、基準トランジスタ760、および複数のNMOSトランジスタ808A~808Dを含む。

【0158】

基準トランジスタ760のゲートはそのソースに結合し、そのことは、基準トランジスタ760をオフ状態にする。このように、基準トランジスタ760を通じて伝導される電流は、基準トランジスタのリーク電流を表す。トランジスタ803は、基準トランジスタ760とシリアルに結合する。トランジスタ803のゲートは、そのトランジスタのドレンに結合する(いわゆる「ダイオード接続構成」)。

【0159】

トランジスタ803およびトランジスタ805は、電流ミラーを形成する。電流ミラーは、リーク電流(基準トランジスタ760を通った電流)を増幅する。本発明の記述からメリットを享受する当業者は理解するように、増幅のレベルは、トランジスタ803および805の相対サイズに依存する。

【0160】

電流ミラーによって増幅される電流は、オン状態の任意のトランジスタ808A~808Dを通して流れる。トランジスタ808A~808Dは、構成可能な出力電流(リーク電流769)を供給する。適切なレベルの制御信号781を印加することによってトランジスタ808A~808Dを選択的にオンにすることによって、出力電流を構成し得る。一般に、<sup>i</sup>ビットを有する制御信号781に関して、基準電流の2<sup>i</sup>レベルを供給する。トランジスタ808A~808Dは、制御信号781に応答し所望の基準電流プロファイルを供給するように選択された相対サイズを有し得る。

【0161】

本発明の記述からメリットを享受する当業者は理解するように、トランジスタの数とサイズの種々の組み合わせを使用し得る。一例として、トランジスタ808B~808Dの各々がその前のトランジスタの2倍の幅を有するよう(2進重み付け構成)、トランジスタ808A~808Dのサイズを決め得る。一つの例示的実施形態において、所定のチャネル長に関して、トランジスタ760は200の幅を有し、トランジスタ803は1の幅、トランジスタ805は50の幅、トランジスタ808Aは1の幅、およびトランジスタ808B~808Dは2進重み付け幅を有する(すなわち、トランジスタ808Bは2の幅、トランジスタ808Cは4の幅、など)。

【0162】

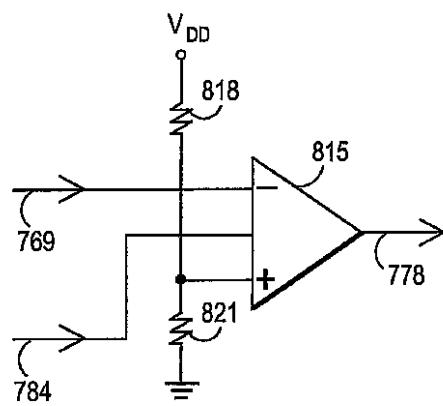

図28は、発明の例示的実施形態に従った基準値および比較器回路775を示す。回路は、抵抗818、抵抗821および比較器815を含む。抵抗818および821は、リーク基準信号772を比較器815に供給する分圧器を形成する。所望の基準レベルを供給するように、抵抗818および821の値を選択し得る。比較器815は、リーク信号769をリーク基準信号772と比較し、リークエラー信号778を供給する。比較器815は、必要に応じ、構成可能な利得を有し得る(制御信号784に応答して)。図28は簡略な比較器815を示し、その比較器815は、必要に応じ、比較的正確な基準電圧を供給するために安定した基準回路を含め得ることに注意されたい。

【0163】

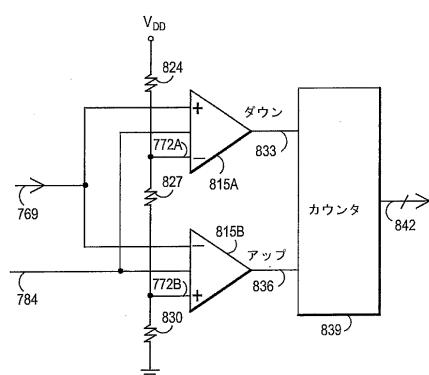

図29は、発明の別の例示的実施形態に従った基準値および比較器回路775を示す。回路は、抵抗824、抵抗827、抵抗830、比較器815A、比較器815B、およびカウンタ839を含む。比較器815Aおよび/または815Bは、必要に応じ、構成可能な利得を有し得る(制御信号784に応答して)。

【0164】

図29における基準値および比較器回路775は図28の回路と同様であるが、この回路は、リーク電流用に下限と上限を供給するように二つの基準信号を使用する。より具体

10

20

30

40

50

的には、抵抗 824、827、および 830 は、リーク基準信号 772A を比較器 815A に供給し、リーク基準信号 772B を比較器 815B に供給する分圧器を形成する。リーク基準信号 772A および 772B は、リーク電流用の上下限を構成する。別の言い方をすると、リーク基準信号 772A および 772B は、リーク電流用の値の「ウィンドウ」を供給する。リーク基準信号 772A および 772B の所望のレベルを供給するように、抵抗 824、827、および 830 の値を選択し得る。

#### 【0165】

比較器 815A は、リーク信号 769 をリーク基準信号 772A と比較し、ダウン信号 833 を供給する。ダウン信号 833 は、カウンタ 839 をカウントダウンさせる（すなわち、I C 回路の動作速度を下げる）。逆に、比較器 815B は、リーク信号 769 をリーク基準信号 772B と比較し、アップ信号 836 を供給する。アップ信号 836 は、カウンタ 839 をカウントアップさせる（すなわち、I C 回路の動作速度を上げる）。別の言い方をすると、カウンタ 839 は、図 26 のフィルタ 787 としての積分器を使用することに類似している。カウント信号 842 は、カウンタ 839 の電流カウント値を提供する。ボディバイアスジェネレータ 430（図 29 に示されない）カウント信号 842 を使用し、ボディバイアス信号 435（図 29 に示されない）を生成し、その信号を I C 回路 763 に供給する。

#### 【0166】

ボディバイアスレベルの制御またはプログラムをさらに供給するために、必要に応じ、I C 内に二つ以上のボディバイアスジェネレータ回路 430 を含め得る。そのような構成において、各ボディバイアスジェネレータ 430 は一つ以上のボディバイアス信号 435 を回路（I C 回路 763 など）または I C 内の領域に供給する。

#### 【0167】

このように、ボディバイアスジェネレータ 430 をプログラムし、I C の各回路または領域用の特定のまたは個々に区別されたボディバイアス信号を供給し得る。代案として、ユーザーは、I C の所定の回路または領域用にボディバイアス信号 435 の所望の数およびレベルを生成するようにボディバイアスジェネレータ 430 用のプログラムを特定し、または供給し得る。特に適合されまたはプログラムされたボディバイアスレベルは、I C の各回路または領域用に性能とリークおよびワット損とのトレードオフを可能にする。その結果、ユーザーは、より細かい粒状度で、I C 内の種々の部品および回路について性能と電力とのトレードオフに対する制御を増加させる。

#### 【0168】

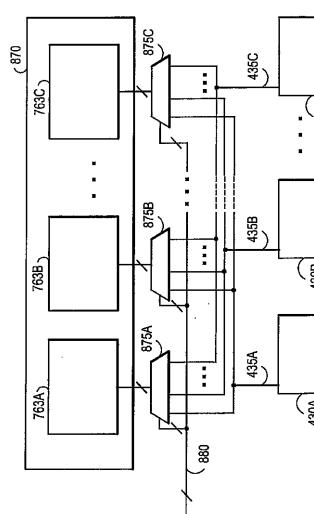

図 30 は、発明の例示的実施形態に従った、I C における複数のボディバイアス回路を供給するための回路配置を示す。回路配置は、I C 領域 870、I C 回路 763A～763C のセット、対応する数の MUX 875A～875C、およびボディバイアスジェネレータ 435A～435C を含む。

#### 【0169】

ボディバイアスジェネレータ 430A～430C の各々は、ボディバイアス信号 435A～435C として示される一つ以上のボディバイアス信号を生成し、信号を MUX 875A～875C の各々に供給する。選択信号 880 に応答し、MUX 875A～875C の各々は、ボディバイアスジェネレータ 435A～435C の一つからのボディバイアス信号を選択し、選択されたボディバイアス信号を I C 回路 763A～763C の対応する一つに供給する。

#### 【0170】

MUX 875A～875C を使用するよりはむしろ、プログラマブル不揮発性結合メカニズム（ヒューズなど）を使用し得る。そのような状況において、個々の I C の特性（たとえば、リークのレベル）を判定するために、製作後個々の I C をテストし得、所望または適切なボディバイアス信号を I C の種々の領域または回路に供給するように不揮発性結合メカニズムをプログラムし得る。多数のボディバイアスジェネレータを含むことによって、ユーザーは、それらの領域または回路のボディバイアスレベルを独立してプログラム

10

20

30

40

50

する能力が与えられる。

【0171】

別の実施形態において、不揮発性メモリに記憶された値（I Cの特性（たとえば、リーケベル）またはI C内の特定の領域または回路に関係する値など）とユーザー構成またはユーザー特定の値との組み合わせを使用し、ボディバイアスレベルを生成し得る。この案は、性能とワット損およびリーケベルとをトレードオフするために、I Cの特性およびユーザー特定のパラメータの両方を考慮に入れることを可能にする。

【0172】

P L Dの場合、P L D領域870は、P L D領域606を構成し得（たとえば、図25を参照されたい）、各I C回路763はユーザー回路609に対応し得る。一つ以上の適合またはプログラムされたボディバイアス信号435をP L D103内の各ユーザー回路609（たとえば、図25を参照されたい）に供給し得る。別の実施形態において、I C回路763は、P L D回路（プログラマブルロジック106およびプログラマブル相互接続109）の物理的に近いセット、またはプログラマブルロジック106およびプログラマブル相互接続109の選択されたグループ（たとえば、図3の長方形のアレイに配列されたプログラマブルロジック回路106のグループ）に対応し得る。

【0173】

図30は、ボディバイアス信号435A～435Cを供給する回路網としてのボディバイアスジェネレータ430A～430Cを示す。P L Dの場合、一般に、ボディバイアスジェネレータ430A～430Cよりはむしろ、ボディバイアスコントローラ603A～603C（たとえば、図25を参照されたい）を使用し得る。

【0174】

図30は、I C回路763A～763Cを含むとしてのI C領域870を示すことに注意されたい。しかし、本発明の記述からメリットを享受する当業者は理解するように、逆の状況が存在し得る（すなわち、各I C回路は一つ以上のI C領域870含み得る）。

【0175】

上記の性能同調コンセプトをその他の技術と組み合わせ、出力密度を減少し、または出力密度を安全な範囲内に維持し得ることにさらに注意されたい。たとえば、P L D内の種々の回路をオンまたはオフにし得（図9および添付の説明を参照されたい）、所望の性能レベルと安全または所定の消費電力レベルまたは出力密度とのトレードオフを達成し得る。その他の変種および実施形態は、本発明の記述からメリットを享受する当業者にとって、明らかであろう。

【0176】

一般に、必要に応じ、また、本発明の記述からメリットを享受する当業者は理解するように、発明コンセプトを、当業界で他の名前で公知の種々のプログラマブルロジック回路網またはI Cへ効果的に適用し得ることに注意されたい。そのような回路網は、複合プログラマブルロジックデバイス（C P L D）、プログラマブルゲートアレイ（P G A）、およびフィールドプログラマブルゲートアレイ（F P G A）として公知のデバイスを含む。

【0177】

図を参照すると、当業者は、示された種々のブロックは主としてコンセプトの機能および信号流れを示し得ることに気づく。実際の回路インプリメンテーションは、種々の機能ブロック用の別々に識別可能なハードウェアを含み得または含まれ得なく、また、示された特定の回路網を使用し得または使用し得ない。

【0178】

たとえば、必要に応じ、種々のブロックの機能性を一つの回路ブロックに結合し得る。さらに、必要に応じ、いくつかの回路ブロックにおいて一つのブロックの機能性を実現し得る。本発明の記述からメリットを享受する当業者は理解するように、回路インプリメンテーションの選択は、所定のインプリメンテーション用の特定の設計および性能仕様などの種々の要因に依存する。

【0179】

10

20

30

40

50

この明細書に記述された発明の実施形態に加えて、その他の修正および代わりの実施形態は、本発明の記述からメリットを享受する当業者にとって、明らかであろう。従って、この記述は、当業者に発明の実施方法を教え、例示的としてのみと解釈すべきである。

【0180】

示され記述された発明の形式は、現在好適なまたは例示的な実施形態として解すべきである。当業者は、本明細書に記述された発明の範囲から逸脱することなく、形状、サイズ、および部品の配置における種々の変更を行い得る。たとえば、当業者は、本明細書に例示および記述されたエレメントの代わりに同等のエレメントを用い得る。さらに、本発明の記述からメリットを享受する当業者は、発明の範囲から逸脱することなく、発明の特定の特徴を他の特徴の使用とは無関係に使用し得る。

10

【図面の簡単な説明】

【0181】

【図1】図1は、本発明の実施形態に従う、PLDの全体ブロック図を示す。

【図2】図2は、本発明に従う、例示的実施形態において使用されるMOSトランジスタを例示する。

【図3】図3は、本発明の例示的実施形態に従う、PLDの平面図を示す。

【図4】図4は、本発明の例示的実施形態に従う、PLDにおけるプログラマブルロジックのブロック図を示す。

【図5】図5は、ボディバイアス調整を組み込んだ本発明の例示的実施形態に従う、PLDにおいて使用されるマルチプレクサを例示する。

20

【図6A】図6Aは、本発明の例示的実施形態に従う、PLDのコンピュータ支援設計(CAD)ソフトウェアにおいて使用される種々のソフトウェアモジュールを示す。

【図6B】図6Bは、本発明の例示的実施形態に従う、PLD CADソフトウェアの流れ図を例示する。

【図7】図7は、本発明の例示的実施形態に従う、ボディバイアスを調整する処理の流れ図を示す。

【図8】図8は、本発明の例示的実施形態に従う、所望のPLD回路網またはブロックのボディバイアスレベルを調整、プログラムまたは設定するためのPLD内の回路網のブロック図を例示する。

30

【図9】図9は、本発明の例示的実施形態に従う、回路網の電源を選択的にオフにするか、あるいは、PLD内の回路網の消費電力を削減または全体的制御する回路のブロック図を示す。

【図10】図10は、本発明の例示的実施形態に従う、外部ソースに応答し、PLD内のボディバイアスレベルを調整するための回路配置を示す。

【図11】図11は、本発明の例示的実施形態に従う、PLD内のボディバイアスレベルを修正するための回路配置を例示する。

【図12】図12は、本発明の例示的実施形態において使用されるPLDにおけるボディバイアスレベルを調整、プログラムまたは設定する処理または技術の流れ図を示す。

40

【図13】図13は、温度レベルを考慮に入れ、ボディバイアスレベルを調整、プログラム、または設定する処理または技術の流れ図を示す。

【図14】図14は、PLDが動作する環境の特性を考慮に入れ、ボディバイアスレベルを調整、プログラム、または設定する処理または技術の流れ図を例示する。

【図15】図15は、PLDが動作する環境の温度レベルおよび特性を考慮に入れ、ボディバイアスレベルを調整、プログラム、または設定する処理または技術の流れ図を示す。

【図16】図16は、ユーザー回路におけるトランジスタのボディバイアスをユーザー回路の動作遅延を表す遅延に基づき調整するための回路配置を示す。

【図17】図17は、本発明の例示的実施形態に従う、ボディバイアスコントローラのブロック図を例示する。

【図18】図18は、本発明の例示的実施形態に従う、基準信号ジェネレータの回路配置を示す。

50

【図19】図19は、本発明の例示的実施形態に従う、位相比較器の回路配置を示す。

【図20】図20は、本発明の例示的実施形態に従う、位相比較器の別の回路配置を例示する。

【図21】図21は、本発明の例示的実施形態において使用する構成可能な遅延回路を示す。

【図22】図22は、本発明の例示的実施形態に従う、構成可能な遅延回路の回路配置を示す。

【図23】図23は、本発明の例示的実施形態に従う、ルーティング遅延要素の回路配置を例示する。

【図24】図24は、本発明の例示的実施形態に従う、ロジック遅延要素の回路配置を示す。 10

【図25】図25は、本発明の例示的実施形態に従う、リーコロックループのブロック図を示す。

【図26】図26は、本発明の別の例示的実施形態に従う、リーコロックループのブロック図を例示する。

【図27】図27は、本発明の別の例示的実施形態に従う、リーク測定回路を示す。

【図28】図28は、本発明の例示的実施形態に従う、基準値および比較器回路を示す。

【図29】図29は、本発明の別の例示的実施形態に従う、基準値および比較器回路を例示する。

【図30】図30は、本発明の例示的実施形態に従う、ICにおける複数のボディバイアス回路を提供するための回路配置を示す。 20

【図1】

FIG.1

【図3】

FIG.3

【図2】

FIG.2

【図4】

【図5】

FIG. 5

【図6A】

FIG. 6A

【図6B】

FIG. 6B

【図7】

FIG. 7

【図8】

FIG.8

【図9】

FIG.9

【図10】

FIG.10

【図12】

【図11】

FIG.11

FIG.12

【図13】

FIG. 13

【図14】

FIG. 14

【図15】

FIG. 15

【図16】

FIG. 16

【 図 17 】

FIG. 17

【 図 1 8 】

FIG. 18

【 図 1 9 】

FIG. 19

【 図 20 】

FIG. 20

【 図 2 2 】

FIG. 22

### 【 図 2 1 】

FIG. 21

【図23】

FIG. 23

【図24】

FIG. 24

【図25】

FIG. 25

【図26】

FIG. 26

【図27】

FIG. 27

【図28】

FIG. 28

【図29】

FIG. 29

【図30】

FIG. 30

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                | Intern<br>al Application No<br>PCT/US2005/017265                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>H03K19/00 G06F17/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                |                                                                                |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>H03K G06F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                |                                                                                |

| Electronic data base consulted during the International search (name of data base and, where practical, search terms used)<br>EPO-Internal, INSPEC, WPI Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                |                                                                                |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                |                                                                                |

| Category °                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Citation of document, with indication, where appropriate, of the relevant passages             | Relevant to claim No.                                                          |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 2004/025135 A1 (HART MICHAEL J ET AL)<br>5 February 2004 (2004-02-05)<br>the whole document | 1-18,<br>41-52,<br>59-64                                                       |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 2001/047506 A1 (HOUSTON THEODORE W)<br>29 November 2001 (2001-11-29)<br>the whole document  | 1-18,<br>41-52,<br>59-64                                                       |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 6 147 508 A (BECK ET AL)<br>14 November 2000 (2000-11-14)<br>the whole document             | 1-18,<br>41-52,<br>59-64                                                       |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 2003/001658 A1 (MATSUMOTO KOICHI)<br>2 January 2003 (2003-01-02)<br>the whole document      | 1-18,<br>41-52,<br>59-64                                                       |

| <input type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| ° Special categories of cited documents :<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier document but published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the International filing date but later than the priority date claimed                                                                               |                                                                                                |                                                                                |

| "T" later document published after the International filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention<br>"X" document of particular relevance; the claimed Invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone<br>"Y" document of particular relevance; the claimed Invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art<br>"E" document member of the same patent family |                                                                                                |                                                                                |

| Date of the actual completion of the International search<br>11 October 2005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Date of mailing of the International search report<br>20.01.2006                               |                                                                                |

| Name and mailing address of the ISA<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL-2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 851 epo nl<br>Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Authorized officer<br>Meulemans, B                                                             |                                                                                |

## INTERNATIONAL SEARCH REPORT

national application No.

PCT/US2005/017265

## Box II Observations where certain claims were found unsearchable (Continuation of item 2 of first sheet)

This International Search Report has not been established in respect of certain claims under Article 17(2)(a) for the following reasons:

1.  Claims Nos.: because they relate to subject matter not required to be searched by this Authority, namely:

2.  Claims Nos.: because they relate to parts of the International Application that do not comply with the prescribed requirements to such an extent that no meaningful International Search can be carried out, specifically:

3.  Claims Nos.: because they are dependent claims and are not drafted in accordance with the second and third sentences of Rule 6.4(a).

## Box III Observations where unity of invention is lacking (Continuation of item 3 of first sheet)

This International Searching Authority found multiple inventions in this International application, as follows:

see additional sheet

1.  As all required additional search fees were timely paid by the applicant, this International Search Report covers all searchable claims.

2.  As all searchable claims could be searched without effort justifying an additional fee, this Authority did not invite payment of any additional fee.

3.  As only some of the required additional search fees were timely paid by the applicant, this International Search Report covers only those claims for which fees were paid, specifically claims Nos.: