(19) (KR)

(12) (B1)

(51) . Int. Cl.<sup>6</sup> (45) 2004 03 24

H03L 7/089 (11) 10-0414864

(24) 2003 12 29

|      |                 |      |                 |

|------|-----------------|------|-----------------|

| (21) | 10-1996-0038662 | (65) | 10-1997-0019097 |

| (22) | 1996 09 06      | (43) | 1997 04 30      |

(30) 1995-242044 1995 09 20 (JP)

(74)

1

(54) PLL

PLL

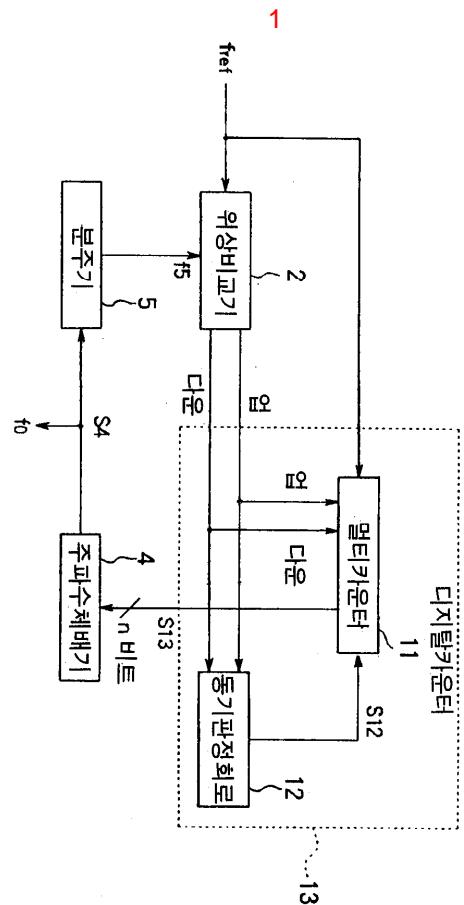

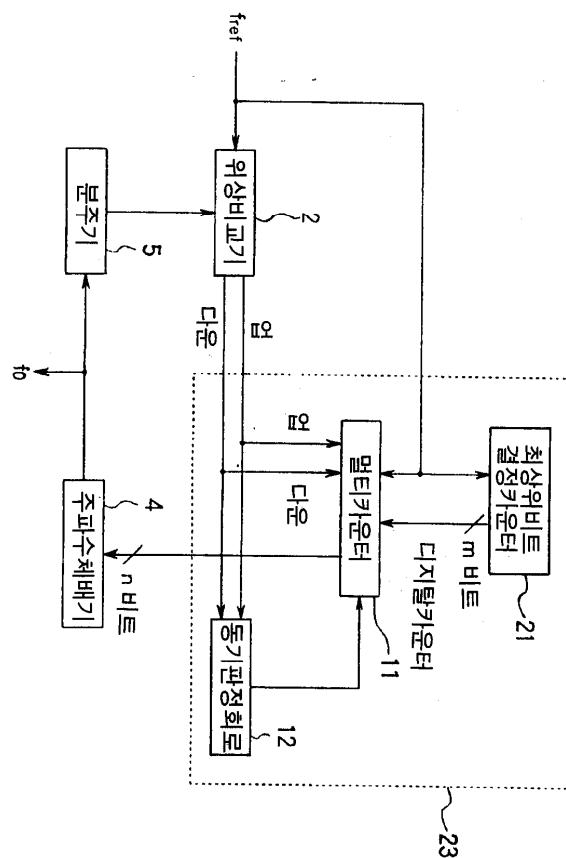

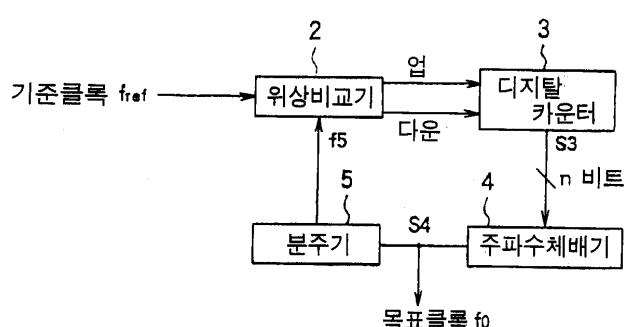

(2) ,  $f_{ref}$  (11) (分周器)(5) (同期) (12) S5

가 (11),

(遞倍器)(4) (12), (2)

가 S12 (11)

1

|   |   |     |     |

|---|---|-----|-----|

| 1 |   | 1   | PLL |

| 2 | 3 | 1   |     |

| 4 | 1 |     |     |

| 5 |   | 2   | PLL |

| 6 | 5 |     |     |

| 7 |   | 3   | PLL |

| 8 |   | PLL | .   |

| 9 | 8 |     | PLL |

10 8 PLL .

< >

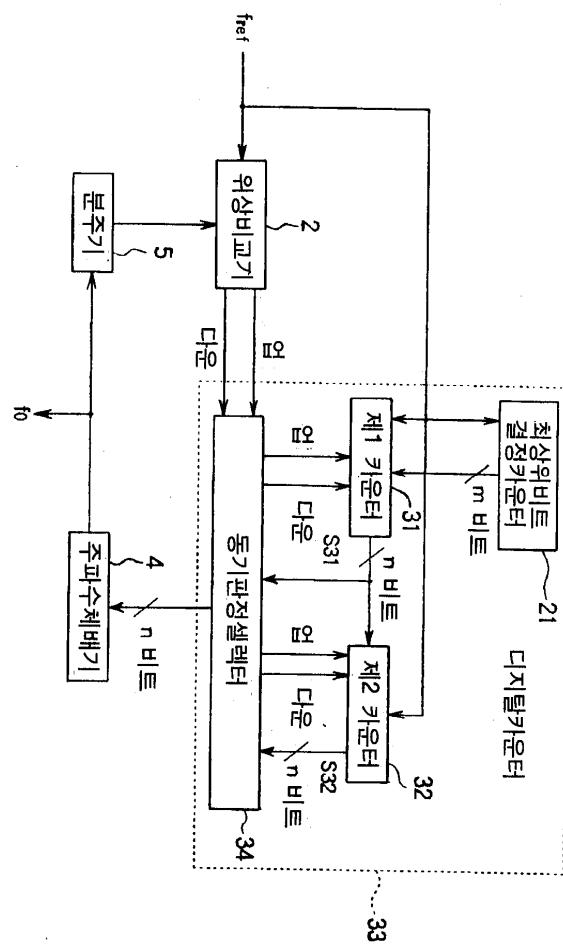

2 : , 3,13,23,33 : , 4 : (遞倍器), 5 : (分周器), 11 : , 12 :

(同期) , 21 : , 31 : 1 , 32 : 2 , 34 : .

PLL(Phase Locked Loop)

```

graph TD

fref[fref] --> PFD[S3]

PFD --> VCO[VCO]

VCO --> f0[f0]

f0 --> S4[S4]

S4 --> PFD

```

The diagram illustrates a Phase Locked Loop (PLL) system. It consists of a Phase Frequency Detector (S3), a Voltage Controlled Oscillator (VCO), and a Frequency Divider (S4). The VCO generates a local oscillator signal  $f_0$ , which is then divided by the Frequency Divider (S4) to produce a feedback signal. This feedback signal is compared with the reference signal  $f_{ref}$  at the Phase Frequency Detector (S3) to maintain lock.

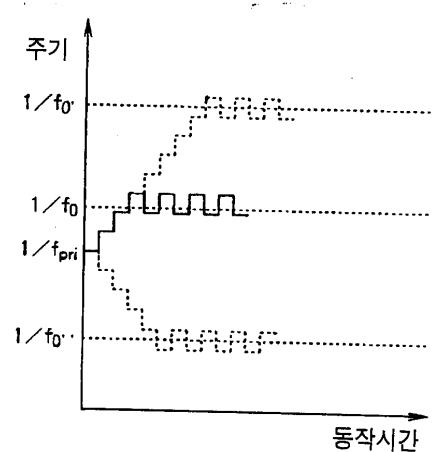

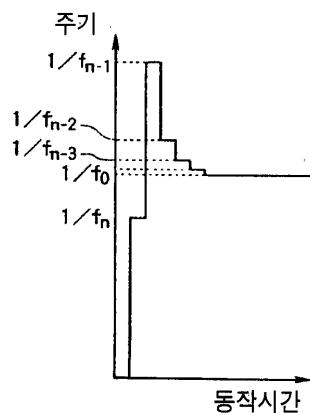

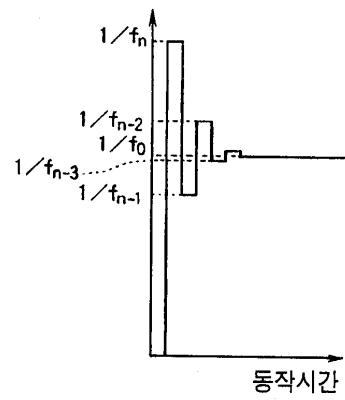

1, 2 C4, (4) (2), 3 f<sub>ref</sub> 1/f<sub>n-1</sub> f<sub>n-1</sub> 가

, C5 (11), C4 가, (11), n-1 3 1/f<sub>n-2</sub> 가

2) n-2 1, 2 C6, (2), f<sub>ref</sub> f<sub>n-2</sub> 가

, C7 (11), C6 가, (11), n-2 3 1/f<sub>n-3</sub> 가

2) n-3 1, 2 가, (12) S12가

PLL, f<sub>0</sub>, (11) f<sub>ref</sub> S13

, 2<sup>n</sup>, (13) (13) 2n (5

2(n+1))

n=10 2<sup>10</sup>=1024

2(10+1)=22 (13) 1/50

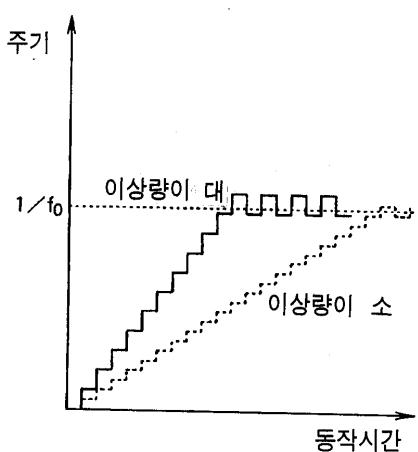

, 2 가, (13) 가, PLL

PLL S12가, (11) f<sub>ref</sub>

, S13

, 1, 1 (13), (13) 가 가, 1, 2, 4

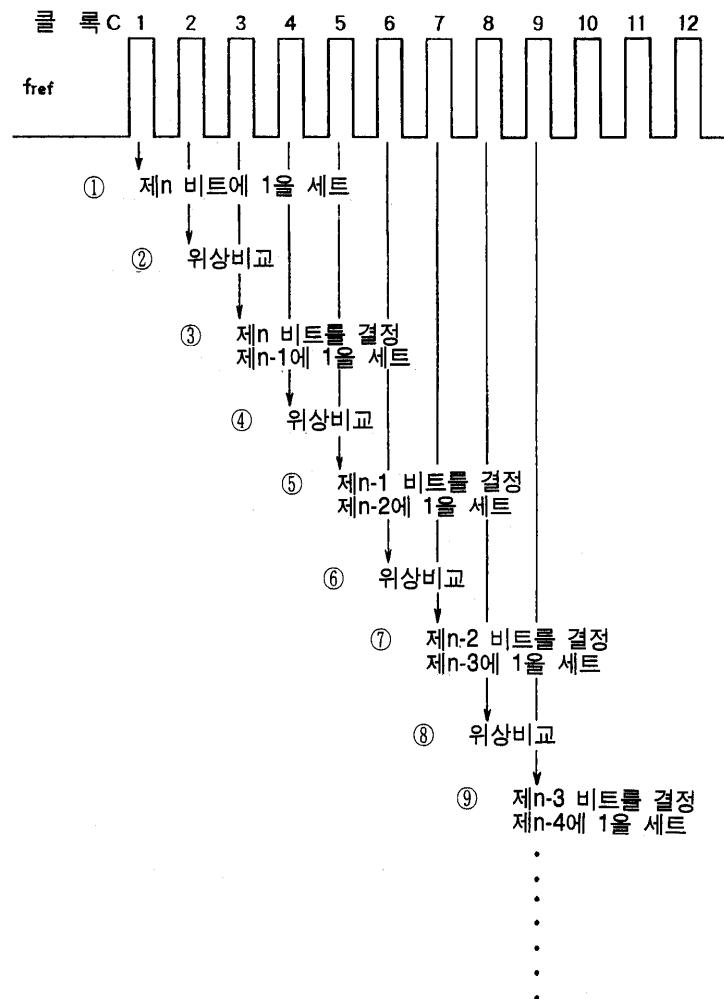

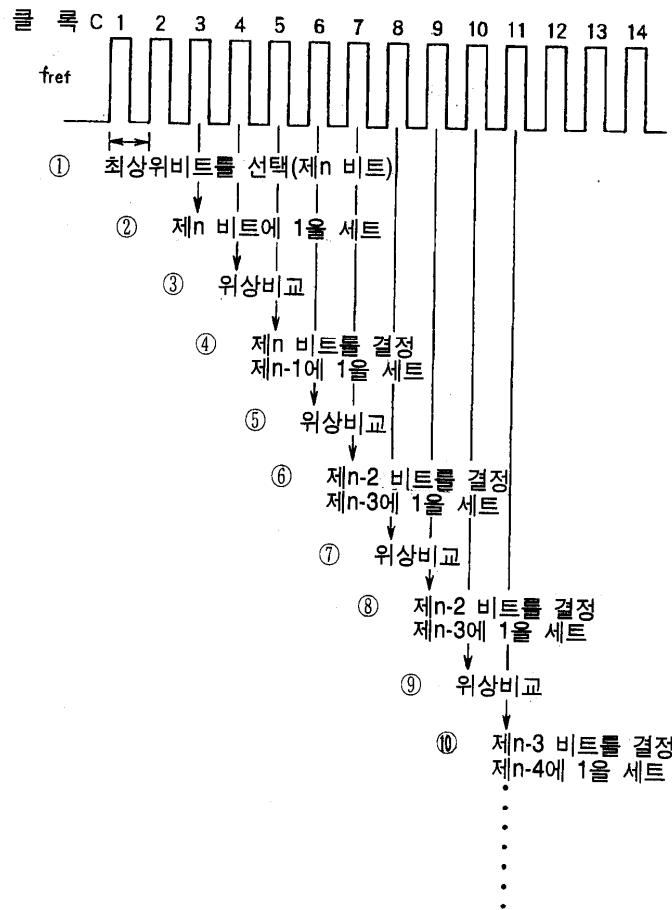

, 2 (4) f<sub>ref</sub> n 가, 2, 4 C1, n 1

, 2 C2, (2), (11), n 4 1/f<sub>n</sub> f<sub>ref</sub> f<sub>n</sub> 가

2) -1 C3 (11), C2 가, (4) (11), n 4 1/f<sub>n-1</sub> 1

, 2 C4, (2), f<sub>ref</sub> f<sub>n-1</sub> 가

, C5 (11), C4 가, (11), n-1 4 1/f<sub>n-2</sub> 1

, 2 C6, (2), f<sub>ref</sub> f<sub>n-2</sub> 가

2) n-3 C7 (11), C6 가, (4) (11), n-2 4 1/f<sub>n-3</sub> 1

, 2 가, (12) S12 가

, S13

2

5, PLL

(57)

1.

(frequency multiplying circuit)

(同期)

3.

2 ,

1 , 2 ,

1 ,

2 ,

1

2 , 1 ,

4.

, ,

,

PLL .

5.

4 ,

PLL .

6.

5 ,

1 , 2 ,

1 ,

2 ,

1

2 , 1 ,

PLL .

2

3

4

5

7

8

9

10