(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 603 17 771 T2 2008.12.04

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 477 902 B1

(21) Deutsches Aktenzeichen: 603 17 771.9

(86) PCT-Aktenzeichen: PCT/JP03/01800

(96) Europäisches Aktenzeichen: 03 706 966.3

(87) PCT-Veröffentlichungs-Nr.: WO 2003/071437

(86) PCT-Anmeldetag: 19.02.2003

(87) Veröffentlichungstag

der PCT-Anmeldung: 28.08.2003

(97) Erstveröffentlichung durch das EPA: 17.11.2004

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 28.11.2007

(47) Veröffentlichungstag im Patentblatt: 04.12.2008

(51) Int Cl.<sup>8</sup>: G06F 13/12 (2006.01)

G06F 3/06 (2006.01)

G06F 3/08 (2006.01)

G06K 19/00 (2006.01)

(30) Unionspriorität:

2002045252 21.02.2002 JP

(84) Benannte Vertragsstaaten:

DE, FR, GB

(73) Patentinhaber:

Sony Corp., Tokio/Tokyo, JP

(72) Erfinder:

BANDO, Hideaki, Tokyo 141-0001, JP

(74) Vertreter:

Mitscherlich & Partner, Patent- und

Rechtsanwälte, 80331 München

(54) Bezeichnung: EXTERNE VERBINDUNGSEINRICHTUNG, HOST-EINRICHTUNG UND DATENKOMMUNIKATIONSSYSTEM

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

### Technisches Gebiet

**[0001]** Diese Erfindung betrifft eine externe Verbindungseinrichtung wie beispielsweise eine mit einer Informationsverarbeitungseinrichtung wie beispielsweise einem Computer verbundene IC-Speichereinrichtung, eine Hosteinrichtung, mit der diese externe Verbindungseinrichtung verbunden ist, und ein mit dieser externen Verbindungseinrichtung und Hosteinrichtung verbundenes

Datenkommunikationssystem.

Hintergrundtechnik

**[0002]** Herkömmlicherweise ist als ein externes Speichermedium eine Hosteinrichtung wie beispielsweise ein PDA (= personal digital assistant (persönlicher digitaler Assistent)), ein Tischmodell- bzw. -gerätcomputer, ein Notizbuchmodell- bzw. -gerätcomputer, ein tragbares Telefon, eine Audioeinrichtung oder ein elektrisches Heimgerät, eine entfernbare kartenartige kleine IC-Speichereinrichtung, die einen Halbleiterspeicher aufweist, der in diese Einrichtungen eingesetzt/aus diesen Einrichtungen entfernt werden kann, benutzt worden.

**[0003]** Die Speichereinrichtung dieses Typs weist generell einen nichtflüchtigen Halbleiterspeicher (IC-Speicher) wie beispielsweise einen Flash-Speicher (Blitzspeicher) auf und speichert unterschiedliche digitale Daten wie beispielsweise Statischbilddaten, Dynamischbilddaten, Audiodaten und Musikdaten. Diese IC-Speichereinrichtung fungiert als ein externes Speichermedium einer Hosteinrichtung wie beispielsweise eines PDA, eines Tischgerätcomputers, eines Notizbuchgerätcomputers, eines tragbaren Telefons, einer Audioeinrichtung oder eines elektrischen Heimgeräts.

**[0004]** Die Operation einer solchen IC-Speichereinrichtung wird durch die Hosteinrichtung über eine vorbestimmte Schnittstelle gesteuert. Typischerweise wird von der Hosteinrichtung ein Verarbeitungsbefehl zur IC-Speichereinrichtung übertragen und infolgedessen die Operation gesteuert.

**[0005]** Die Zugriffsgeschwindigkeit des in der IC-Speichereinrichtung benutzten Flash-Speichers ist niedrig. Deshalb ist es zur Reduzierung einer Datenübertragungssequenz zwischen der Hosteinrichtung und der IC-Speichereinrichtung effektiv, eine Unterbrechungsanforderung (interrupt request) vorzuschreiben, die von der IC-Speichereinrichtungsseite über das Ende einer Verarbeitung informiert.

**[0006]** Aus EP-A-1050 821 geht eine Speichereinheit und eine Speicherplatte hervor, die über einen Bus kommuniziert und die eine Maßnahme für eine Übertragung eines Unterbrechungssignals (interrupt signal) aufweist.

### Offenbarung der Erfindung

**[0007]** Es ist eine Aufgabe der vorliegenden Erfindung, eine externe Verbindungseinrichtung, die eine Lösung der Probleme der herkömmlichen IC-Speichereinrichtung ermöglicht, eine Hosteinrichtung, mit der die externe Verbindungseinrichtung verbunden ist, und ein diese externe Verbindungseinrichtung und Hosteinrichtung benutzendes Datenkommunikationssystem bereitzustellen.

**[0008]** Es ist eine andere Aufgabe der vorliegenden Erfindung, eine externe Verbindungseinrichtung und eine Hosteinrichtung, die eine Reduktion bei der Datenübertragungsverarbeitungszeit zwischen der Hosteinrichtung und der externen Verbindungseinrichtung durch effiziente Bereitstellung eines Unterbrechungssignals von der externen Verbindungseinrichtung zur Hosteinrichtung ermöglichen, und ein diese externe Verbindungseinrichtung und diese Hosteinrichtung benutzendes Datenkommunikationssystem bereitzustellen.

**[0009]** Zur Lösung der oben beschriebenen Aufgaben ist eine externe Verbindungseinrichtung gemäß der vorliegenden Erfindung eine mit einer Hosteinrichtung zu verbindende externe Verbindungseinrichtung, wobei die externe Verbindungseinrichtung aufweist: eine Datenkommunikationseinrichtung zur Ausführung bidirektionaler Kommunikation von Übertragungsdaten zu und von der Hosteinrichtung über einen Datenbus, eine Buszustandssignal-Empfangseinrichtung zum Empfang eines den Zustand des Datenbusses von der Hosteinrichtung anzeigenenden Buszustandssignals, und einen Kontroller zur Steuerung der Operation dieser Einrichtung entsprechend einem Operationssteuerungsbefehl, der in den Übertragungsdaten inkludiert ist, wobei die Datenkommunikationseinrichtung über den Datenbus zur Hosteinrichtung Information, die den Inhalt eines auf

der Basis des von der Hosteinrichtung dem Kontroller (= Steuerungseinrichtung) bereitgestellten Operationssteuerungsbefehls erzeugten Elements einer Unterbrechung anzeigt, sendet, wenn der Zustand des Buszustandssignals ein Zustand zum Akzeptieren einer Unterbrechung von dieser Einrichtung zur Hosteinrichtung ist.

**[0010]** Bei der externen Verbindungseinrichtung gemäß der vorliegenden Erfindung wird, wenn der Zustand des Buszustandssignals ein Zustand zum Akzeptieren einer Unterbrechung von dieser Einrichtung zur Hosteinrichtung ist, Information, die den Inhalt eines auf der Basis des von der Hosteinrichtung dem Kontroller bereitgestellten Operationssteuerungsbefehls erzeugten Elements einer Unterbrechung anzeigt, als ein Unterbrechungssignal über den Datenbus zur Hosteinrichtung gesendet.

**[0011]** Eine Hosteinrichtung gemäß der vorliegenden Erfindung ist eine Hosteinrichtung, mit der eine externe Verbindungseinrichtung verbunden ist, wobei die Hosteinrichtung aufweist: eine Datenkommunikationseinrichtung zur Ausführung bidirektionaler Kommunikation von Übertragungsdaten zu und von der externen Verbindungseinrichtung über einen Datenbus, eine Buszustandssignal-Sendeeinrichtung zum Senden eines den Zustand des Datenbusses anzeigenenden Buszustandssignals zur externen Verbindungseinrichtung, und einen Kontroller zur Ausgabe eines Steuerungsbefehls zur Steuerung einer Operation der externen Verbindungseinrichtung, wobei der Steuerungsbefehl in den Übertragungsdaten inkludiert ist, wobei die Datenkommunikationseinrichtung von der externen Verbindungseinrichtung über den Datenbus Information, die den Inhalt eines auf der Basis des von dieser Einrichtung der externen Verbindungseinrichtung bereitgestellten Operationssteuerungsbefehls erzeugten Elements einer Unterbrechung anzeigt, empfängt, wenn der Zustand des Buszustandssignals ein Zustand zum Akzeptieren einer Unterbrechung von der externen Verbindungseinrichtung zu dieser Einrichtung ist.

**[0012]** Bei der Hosteinrichtung gemäß der vorliegenden Erfindung wird, wenn der Zustand des Buszustandssignals ein Zustand zum Akzeptieren einer Unterbrechung von der externen Verbindungseinrichtung zu dieser Einrichtung ist, Information, die den Inhalt eines auf der Basis des von dieser Einrichtung der externen Verbindungseinrichtung bereitgestellten Operationssteuerungsbefehls erzeugten Elements einer Unterbrechung anzeigt, von der externen Verbindungseinrichtung über den Datenbus empfangen.

**[0013]** Die anderen Aufgaben der vorliegenden Erfindung und von der vorliegenden Erfindung bereitgestellte spezifische Vorteile werden durch die sich auf die Zeichnungen beziehende folgende Beschreibung einer Ausführungsform weiter erläutert.

#### Kurze Beschreibung der Zeichnungen

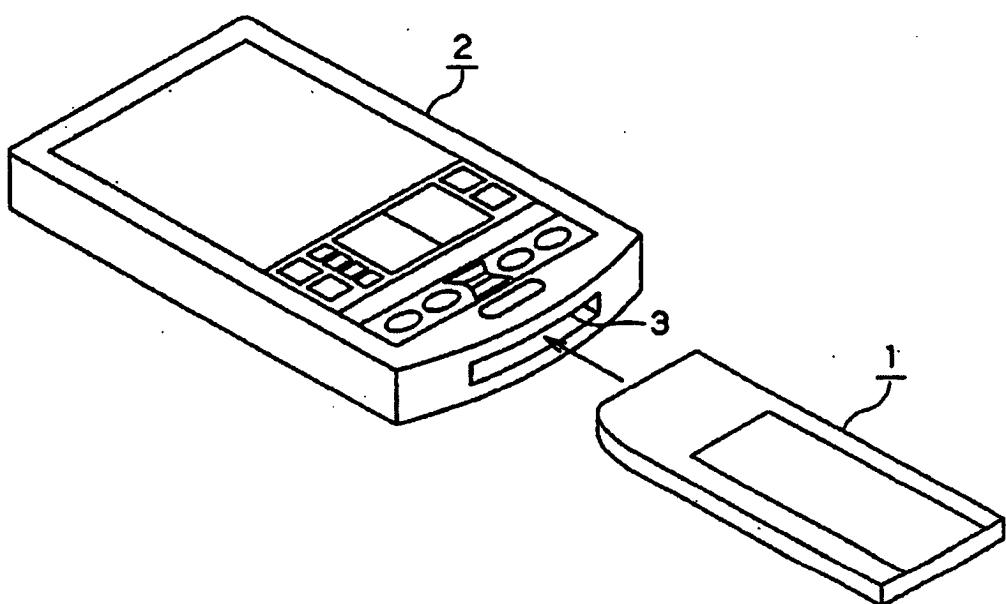

**[0014]** [Fig. 1](#) ist eine perspektivische Darstellung, die eine Speicherplatine, bei der die vorliegende Erfindung angewendet ist, und eine diese Speicherplatine benutzende Hosteinrichtung zeigt.

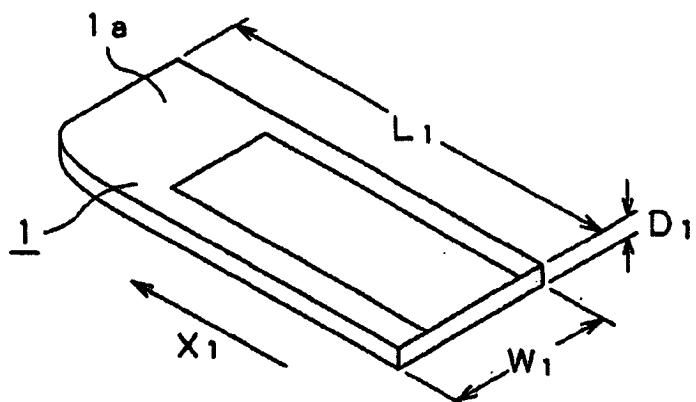

**[0015]** [Fig. 2](#) ist eine perspektivische Darstellung, die eine Speicherplatine von ihrer Vorderseite zeigt.

**[0016]** [Fig. 3](#) ist eine perspektivische Darstellung, welche die Speicherplatine von ihrer Rückseite zeigt.

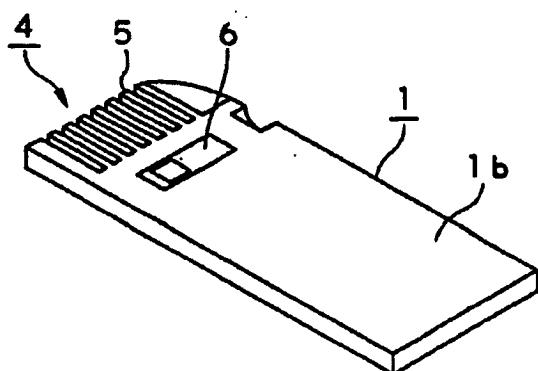

**[0017]** [Fig. 4](#) ist ein Blockdiagramm, das einen internen Blockaufbau der Speicherplatine zeigt.

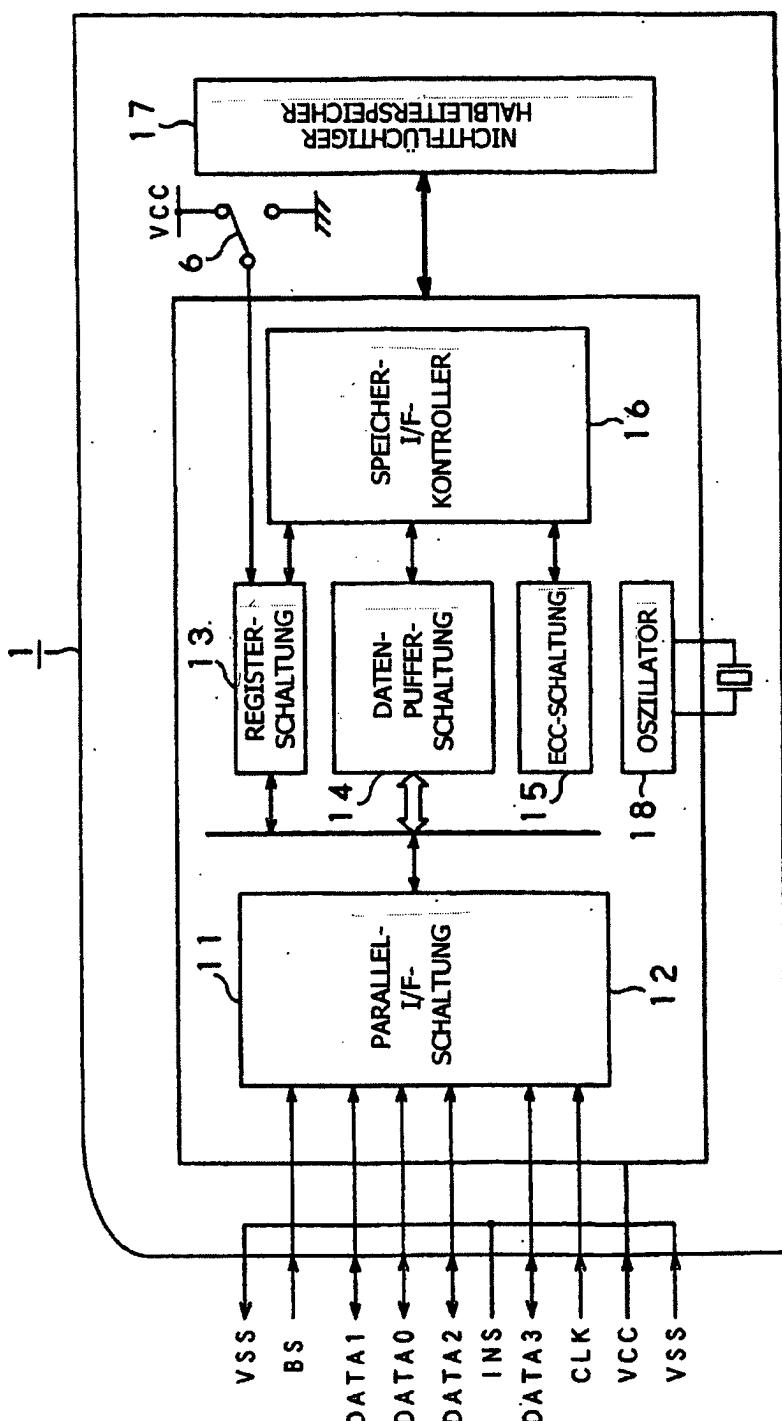

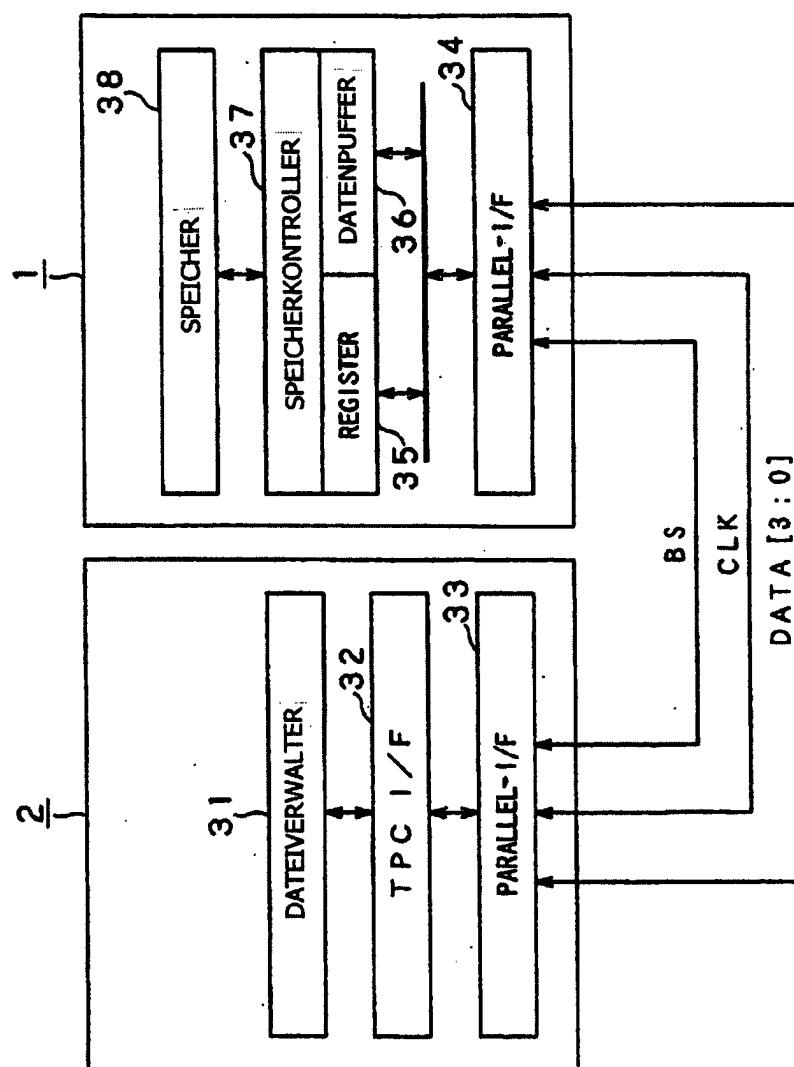

**[0018]** [Fig. 5](#) ist eine strukturelle Darstellung einer Schnittstellenfunktion zur Übertragung von Daten zwischen der Speicherplatine und der Hosteinrichtung.

**[0019]** [Fig. 6](#) ist eine Darstellung zur Erläuterung eines Signals, das zwischen der Speicherplatine und der Hosteinrichtung übertragen wird.

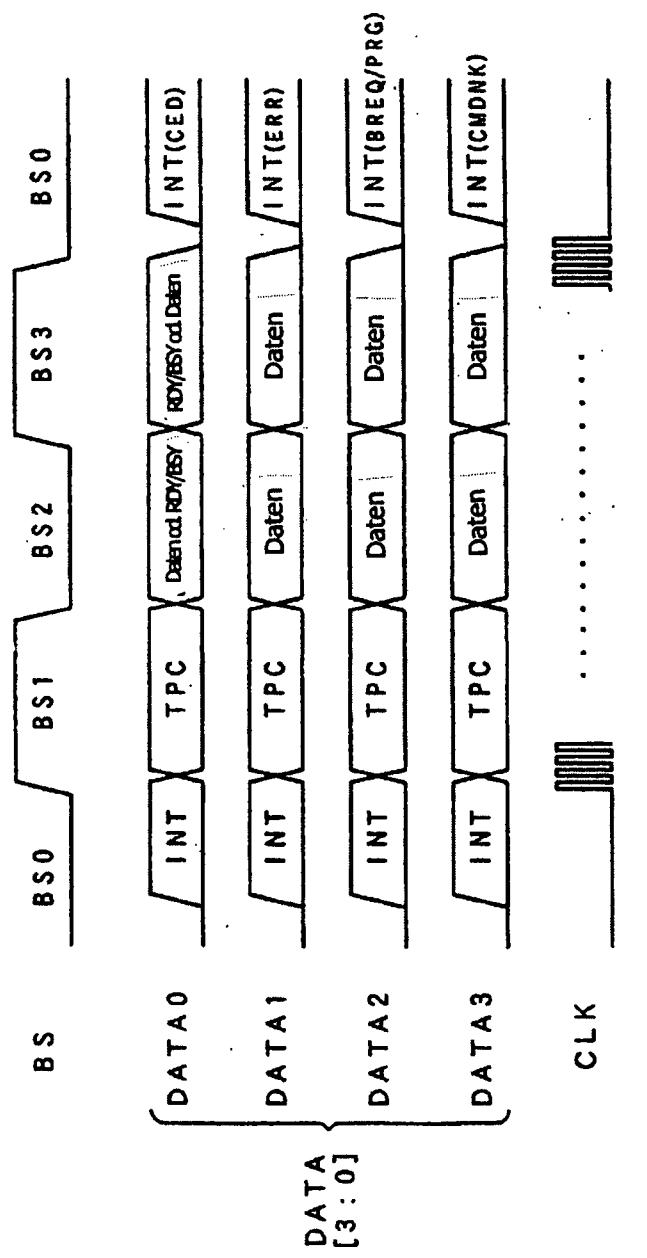

**[0020]** [Fig. 7](#) ist eine Darstellung zur Erläuterung des Inhalts einer Kommunikation in jedem Zustand.

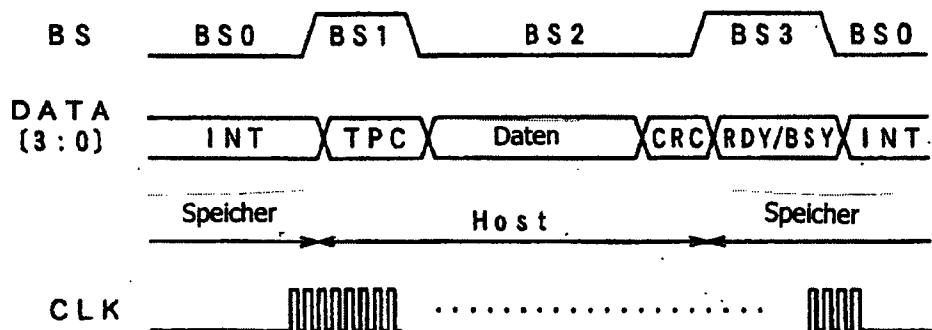

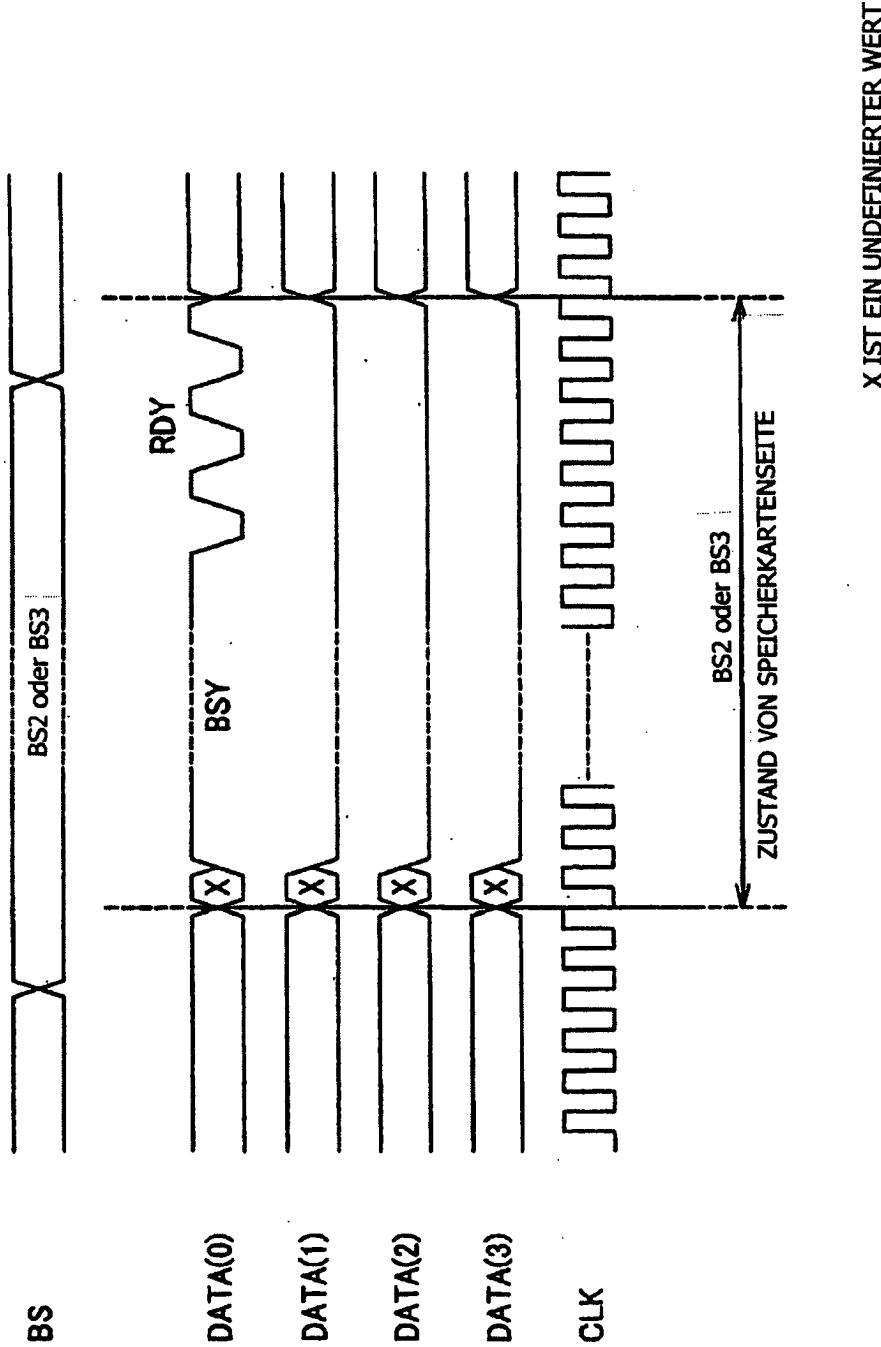

**[0021]** [Fig. 8](#) ist ein Zeitsteuerungs- bzw. Timingdiagramm von Paralleldaten, eines Buszustands (bus state) und eines Taks zur Zeit einer Übertragung eines Schreibpaketes.

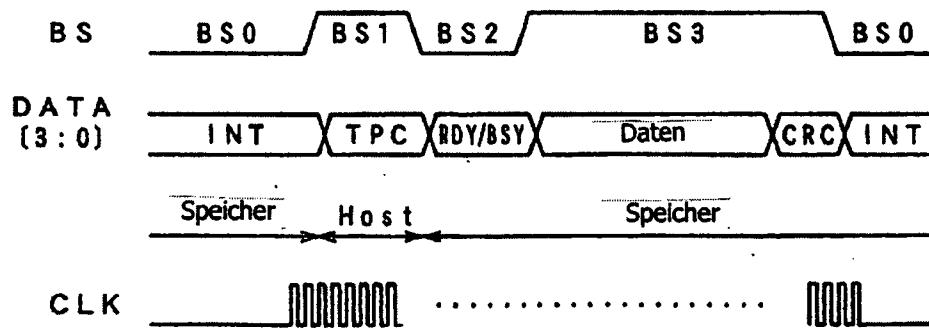

**[0022]** [Fig. 9](#) ist ein Timingdiagramm von Paralleldaten, eines Buszustands und eines Taks zur Zeit einer Übertragung eines Lesepaketes.

**[0023]** [Fig. 10](#) ist ein Timingdiagramm eines Besetzungssignals (busy signal) und einer Bereitsignale (ready sig-

nal) eines Schreibpaket und eines Lesepakets.

[0024] [Fig. 11](#) ist eine Darstellung, die interne Register zeigen, welche eine Statusregistergruppe bilden.

[0025] [Fig. 12](#) ist eine Darstellung, die den Inhalt von Bits in einem INT-Register zeigt.

[0026] [Fig. 13](#) ist eine Darstellung, die einen mit jedem Bitwert im INT-Register korrespondierenden Operatonszustand der Speicherplatte zeigt.

[0027] [Fig. 14](#) ist eine Darstellung, die interne Register zeigt, welche eine Parameterregistergruppe bilden.

[0028] [Fig. 15](#) ist eine Darstellung, die Übertragungsdaten im Fall von SET\_CMD\_TPC zeigt.

[0029] [Fig. 16](#) ist eine Darstellung, die Übertragungsdaten im Fall von EX\_SET\_CMD\_TPC zeigt.

[0030] [Fig. 17](#) ist eine Darstellung, die exemplarische Steuerungsbefehle zeigt.

#### Beste Art und Weise zur Ausführung der Erfindung

[0031] Nachfolgend wird eine Ausführungsform beschrieben, bei der die vorliegende Erfindung bei einer entfernbaren kleinen IC-Speichereinrichtung und einer Datenverarbeitungseinrichtung, die diese kleine IC-Speichereinrichtung als eine externes Speichermedium benutzt, angewendet ist.

[0032] In der folgenden Beschreibung wird die kleine IC-Speichereinrichtung als Speicherplatte bezeichnet, und die Datenverarbeitungseinrichtung, mit der diese Speicherplatte verbunden wird, wird als Hosteinrichtung bezeichnet.

[0033] Zuerst wird der Überblick über die Hosteinrichtung, bei der die vorliegende Erfindung angewendet ist, und die Speicherplatte, die mit dieser Hosteinrichtung zu verbinden ist, anhand der [Fig. 1](#) beschrieben.

[0034] Eine Speicherplatte **1** gemäß der vorliegenden Erfindung weist in ihr einen nichtflüchtigen Halbleiter-speicher (IC-Speicher) auf und kann unterschiedliche Daten wie beispielsweise Statischbilddaten, Dynamischbilddaten, Audiodaten und Musikdaten speichern. Diese Speicherplatte **1** fungiert als ein externes Speichermedium einer Hosteinrichtung **2** wie beispielsweise eines PDA, eines Tischgerätcomputers, eines Notizbuchgerätcomputers, eines tragbaren Telefons, einer Audioeinrichtung oder eines elektrischen Heimgeräts.

[0035] Die Speicherplatte **1** wird benutzt, wenn sie in einen Einsetz/Ausgabe-Anschluss bzw. -Port **3** eingesetzt ist, der, wie in [Fig. 1](#) gezeigt, in der Hosteinrichtung **2** bereitgestellt ist. Ein Benutzer kann die Speicherplatte **1** frei in den Einsetz/Ausgabe-Port **3** einsetzen und frei aus diesem Port **3** entnehmen. Deshalb kann die in eine gewisse Hosteinrichtung eingesetzte Speicherplatte **1** dieser Einrichtung entnommen und in eine andere Hosteinrichtung eingesetzt werden. Das heißt, diese Speicherplatte **1** kann zur Übertragung von Daten zwischen unterschiedlichen Hosteinrichtungen benutzt werden.

[0036] Die Speicherplatte **1** und die Hosteinrichtung **2** übertragen Daten über eine Parallelschnittstelle unter Benutzung eines Sechsdrähtsystem-Halbduplex-Parallelprotokolls zur Übertragung von sechs Signalen, das heißt von Vierbit-Paralleldaten, einem Taktsignal und einem Buszustandssignal.

[0037] Die Speicherplatte ist, wie in [Fig. 2](#) gezeigt, in einer im Wesentlichen rechteckigen dünnen plattenartigen Form ausgebildet. Sie weist in der Längsrichtung eine Länge  $L_1$  von 50 mm, eine Breite  $W_1$  von 21,45 mm und eine Dicke  $D_1$  von 2,8 mm auf. Eine Seite in der Speicherplatte **1** ist eine Vorderseite **1a**, und die andere Seite ist eine Rückseite **1b**. Wie in [Fig. 3](#) gezeigt ist auf der Rückseite **1b** an einer Endseite in der Längsrichtung der Speicherplatte **1** eine durch zehn flache Elektroden gebildete Verbindungsanschlussgruppe **4** bereitgestellt. Die Elektroden, welche die Verbindungsanschlussgruppe **4** bilden, sind in der Richtung der Breite in der Speicherplatte **1** parallel bereitgestellt. Zwischen den Elektroden sind Trennungsteile **5**, die sich von der Rückseite **1b** vertikal erheben, bereitgestellt. Jedes Trennungsteil **5** dient zur Verhinderung, dass ein mit einer jeweiligen Elektrode verbundener Verbindungsanschluss die anderen Elektroden kontaktiert. Wie in [Fig. 3](#) gezeigt ist an einem zentralen Teil an einer Endseite der Rückseite **1b** der Speicherplatte **1** ein Schiebeschalter **6** zur Verhinderung eines irrtümlichen Löschens bereitgestellt.

[0038] In der Hosteinrichtung **2**, in welche die oben beschriebene Speicherplatte **1** geladen wird, ist der Ein-

setz/Ausgabe-Port **3** zum Einsetzen und Ausgeben der Speicherplatine **1** bereitgestellt. Wie in [Fig. 1](#) gezeigt ist der Einsetz/Ausgabe-Port **3** als eine mit der Breite  $W_1$  und der Dicke  $D_1$  der Speicherplatine **1** korrespondierende Öffnung auf der Vorderseite der Hosteinrichtung **2** ausgebildet. Die durch den Einsetz/Ausgabe-Port **3** in die Hosteinrichtung **2** eingesetzte Speicherplatine **1** wird in der Hosteinrichtung **2** gehalten und an einem Abgleiten gehindert, wenn die Verbindungsanschlüsse der Hosteinrichtung **2** mit den die Verbindungsanschlussgruppe **4** bildenden Elektroden verbunden sind. Der Verbindungsanschluss der Hosteinrichtung **2** weist zehn Kontakte auf, die mit den auf der zu ladenden Speicherplatine **1** bereitgestellten, die Verbindungsanschlussgruppe **4** bildenden Elektroden korrespondieren.

**[0039]** Bei der Speicherplatine **1** gemäß der vorliegenden Erfindung ist eine Seite, bei der die Verbindungsanschlussgruppe **4** bereitgestellt ist, ein Einsetzende, und die Richtung eines Pfeiles X1 in [Fig. 2](#) ist die Richtung zum Einsetzen. Die Speicherplatine **1** wird auf diese Weise durch den Einsetz/Ausgabe-Port **3** in die Hosteinrichtung **2** geladen. Die in die Hosteinrichtung **2** geladene Speicherplatine kann Signale übertragen und empfangen, wenn die Elektroden, welche die Anschlussgruppe **4** bilden, und die Kontakte des Verbindungsanschlusses der Hosteinrichtung **2** miteinander verbunden sind.

**[0040]** Der interne Aufbau der Speicherplatine **1** gemäß der vorliegenden Erfindung wird nun anhand der [Fig. 4](#) beschrieben.

**[0041]** Wie in [Fig. 4](#) gezeigt weist die Speicherplatine **1** gemäß der vorliegenden Erfindung eine Parallelschnittstellenschaltung bzw. Parallel-I/F-Schaltung **12**, eine Registerschaltung **13**, eine Datenpufferschaltung **14**, eine ECC-Schaltung **15**, einen Speicherschnittstellenkontroller bzw. Speicher-I/F-Kontroller **16**, einen nichtflüchtigen Halbleiterspeicher **17** und eine Oszillationssteuerungsschaltung **18** auf.

**[0042]** Die Parallel-I/F-Schaltung **12** ist eine Schaltung zur Übertragung von Daten zu und von der Hosteinrichtung **2** unter Benutzung eines Sechsdrahtsystems-Halbduplex-Datenübertragungsprotokolls.

**[0043]** Die Registerschaltung **13** ist eine Schaltung beispielsweise zum Speichern eines von der Hosteinrichtung übertragenen Operationssteuerungsbefehls zum Speicher-I/F-Kontroller **16** (nachfolgend wird dieser Operationssteuerungsbefehl als Steuerungsbefehl bezeichnet), des internen Zustands der Speicherplatine **1**, unterschiedlicher Parameter, die zur Ausführung des Steuerungsbefehls notwendig sind, von Dateiverwaltungsinformation im nichtflüchtigen Halbleiterspeicher **17** usw. Auf diese Registerschaltung **13** wird sowohl von der Hosteinrichtung **2** als auch dem Speicher-I/F-Kontroller zugegriffen. Die Hosteinrichtung **2** greift auf die Registerschaltung **13** unter Benutzung eines TPC (= transfer protocol command (Übertragungsprotokollbefehl) zu, der auf dem Datenübertragungsprotokoll dieser Speicherplatine vorgeschrieben ist. Das heißt, wenn die Hosteinrichtung **2** den Steuerungsbefehl und unterschiedliche Parameter, die in der Registerschaltung **13** gespeichert sind, schreibt oder liest, benutzt die Hosteinrichtung **2** einen TPC.

**[0044]** Die Datenpufferschaltung **14** ist eine Speicherschaltung zum temporären Speichern bzw. Sichern von Daten, die in den nichtflüchtigen Halbleiterspeicher **17** zu schreiben sind, und Daten, die aus dem nichtflüchtigen Halbleiterspeicher **17** zu lesen sind. Das heißt, wenn Daten von der Hosteinrichtung **2** in den nichtflüchtigen Halbleiterspeicher **17** zu schreiben sind, werden Schreibzieldaten entsprechend dem Datenübertragungsprotokoll von der Hosteinrichtung **2** in die Datenpufferschaltung **14** übertragen, und dann schreibt der Speicher-I/F-Kontroller **16** die in der Datenpufferschaltung **14** gespeicherten Schreibzieldaten in den nichtflüchtigen Halbleiterspeicher **17**. Wenn Daten vom nichtflüchtigen Halbleiterspeicher **17** zur Hosteinrichtung **2** ausgelesen werden, liest der Speicher-I/F-Kontroller **16** Lesezieldaten aus dem nichtflüchtigen Halbleiterspeicher **17** aus und speichert die gelesenen Lesezieldaten temporär in der Datenpufferschaltung **14**, und dann werden die Lesezieldaten von der Datenpufferschaltung **14** entsprechend dem Datenübertragungsprotokoll zur Hosteinrichtung **2** übertragen.

**[0045]** Die Datenpufferschaltung **14** weist eine Datenkapazität für eine vorbestimmten Datenschreibeinheit auf (beispielsweise 512 Bytes, die gleich der Seitengröße des Flash-Speichers sind). Die Hosteinrichtung **2** greift auf die Datenpufferschaltung **14** unter Benutzung eines TPC zu. Das heißt, wenn die Hosteinrichtung **2** Daten, die in der Datenpufferschaltung **14** gespeichert sind, schreibt oder ausliest, benutzt die Hosteinrichtung **2** einen TPC.

**[0046]** Die ECC-Schaltung **15** hängt an Daten, die in den nichtflüchtigen Halbleiterspeicher **17** zu schreiben sind, einen Fehlerkorrekturcode (ECC) an. Die ECC-Schaltung **15** führt auch eine Fehlerkorrekturverarbeitung von Daten aus, die aus dem nichtflüchtigen Halbleiterspeicher **17** auf der Basis eines Fehlerkorrekturcodes ausgelesen werden, der an diese ausgelesenen Daten angehängt ist. Beispielsweise ist an eine Dateneinheit

von 512 Bytes ein Fehlerkorrekturcode von drei Bytes angehängt.

**[0047]** Der Speicher-I/F-Kontroller **16** führt eine Steuerung einer Datenübertragung zwischen der Datenpufferschaltung **14** und dem nichtflüchtigen Halbleiterspeicher **17**, eine Steuerung einer Datensicherheitsverwaltung des nichtflüchtigen Halbleiterspeichers **17**, eine Steuerung der anderen Funktionen der Speicherplatine **1**, eine Aktualisierungsverarbeitung der in der Registerschaltung **13** gespeicherten Daten usw. entsprechend Steuerungsbefehlen, die in der Registerschaltung **13** gespeichert sind, aus.

**[0048]** Der nichtflüchtige Halbleiterspeicher **17** ist ein nichtflüchtiger Halbleiterspeicher wie beispielsweise ein NAND-Typ-Flash-Speicher. Die Kapazität des nichtflüchtigen Halbleiterspeichers **17** ist beispielsweise 16 Megabytes, 32 Megabytes, 64 Megabytes und 120 Megabytes. Im nichtflüchtigen Halbleiterspeicher **17** besteht eine Löschblockeinheit aus beispielsweise 16 Kilobytes. Eine Lese/Schreib-Einheit wird als eine Seite bezeichnet und besteht wie in der Datenpufferschaltung **14** aus 512 Bytes. Die Oszillationssteuerungsschaltung **18** erzeugt einen Operationstakt in dieser Speicherplatine **1**.

**[0049]** Als die Verbindungsanschlüsse der Speicherplatine **1** sind VSS-Anschlüsse, ein VCC-Anschluss, ein DATA0-Anschluss, ein DATA1-Anschluss, ein DATA2-Anschluss, ein DATA3-Anschluss, ein BS-Anschluss, ein CLK-Anschluss und ein INS-Anschluss bereitgestellt. Da zwei VSS-Anschlüsse bereitgestellt sind, sind in der Speicherplatine **1** insgesamt zehn Verbindungsanschlüsse bereitgestellt. Ähnliche Verbindungsanschlüsse sind auch auf der Hosteinrichtung bereitgestellt.

**[0050]** Die VSS-Anschlüsse sind mit VSS (0-Volt-Referenzspannung) verbunden. Die VSS-Anschlüsse verbinden die Erde auf der Hosteinrichtungsseite und die Erde auf der Speicherplattenseite und bewirken 0-Volt-Referenzpotentiale der Hosteinrichtung und der Speicherplatine, um miteinander zu koinzidieren. Dem VCC-Anschluss wird von der Hosteinrichtung eine Energieversorgungsspannung (VCC) zugeführt.

**[0051]** Am DATA0-Anschluss wird ein Datensignal (DATA0) des niedrigstwertigen Bits der zwischen der Speicherplatine **1** und der Hosteinrichtung **2** übertragenen Vierbit-Paralleldaten eingegeben/ausgegeben. Beim DATA1-Anschluss wird ein Datensignal (DATA1) des zweitniedrigstwertigen Bits von zwischen der Speicherplatine **1** und der Hosteinrichtung **2** übertragenen Vierbit-Paralleldaten eingegeben/ausgegeben. Beim DATA2-Anschluss wird ein Datensignal (DATA2) des dritttniedrigstwertigen Bits von zwischen der Speicherplatine **1** und der Hosteinrichtung **2** übertragenen Vierbit-Paralleldaten eingegeben/ausgegeben. Beim DATA3-Anschluss wird ein Datensignal (DATA3) des viertniedrigstwertigen Bits von zwischen der Speicherplatine **1** und der Hosteinrichtung **2** übertragenen Vierbit-Paralleldaten eingegeben/ausgegeben.

**[0052]** Beim BS-Anschluss wird ein Buszustandssignal von der Hosteinrichtung in die Speicherplatine eingegeben. Beim CLK-Anschluss wird ein Taktsignal von der Hosteinrichtung **2** eingegeben. Der INS-Anschluss wird für eine Einsetz/Ausgabe-Detektion benutzt, so dass die Hosteinrichtung **2** entscheiden kann, ob die Speicherplatine in den Schlitz eingesetzt ist oder nicht. Der INS-Anschluss der Speicherplatine **1** ist mit der Erde verbunden, und der INS-Anschluss der Hosteinrichtung ist über einen Widerstand hochgezogen.

**[0053]** Als Nächstes wird anhand der [Fig. 5](#) der funktionelle Aufbau der Schnittstelle zur Übertragung von Daten zwischen der Speicherplatine **1** und der Hosteinrichtung **2** beschrieben.

**[0054]** Wie in [Fig. 5](#) gezeigt weisen die Schnittstellenfunktionen der Hosteinrichtung **2** einen Dateiverwalter **31**, eine TPC-Schnittstelle **32** und eine Parallelschnittstelle **33** auf. Die Schnittstellenfunktionen der Speicherplatine **1** weisen eine Parallelschnittstelle **34**, ein Register **35**, einen Datenpuffer **36**, einen Speicherkontroller **37** und einen Speicher **38** auf.

**[0055]** Der Dateiverwalter **31** verwaltet auf dem Betriebssystem der Hosteinrichtung Dateien, die in der Speicherplatine gespeichert sind, und Dateien, die in anderen Medien der Hosteinrichtung gespeichert sind. Der Dateiverwalter **31** ist eine durch den Kontroller oder dgl. in der Hosteinrichtung **2** realisierte Funktion.

**[0056]** Die TPC-Schnittstelle **32** ist eine niedrigere Schicht, die unter dem Dateiverwalter **31** ist. Die TPC-Schnittstelle **32** greift auf das Register **35** und den Datenpuffer **31** in der Speicherplatine **1** entsprechend einem Datenübertragungsprotokoll zu, das einen für diese Schnittstelle richtigen Befehl vorschreibt (TPC oder Übertragungsprotokollbefehl). Diese TPC-Schnittstelle **32** ist eine vom Kontroller oder dgl. in der Hosteinrichtung **32** realisierte Funktion.

**[0057]** Die Parallelschnittstellen **33**, **34** sind niedrigere Schichten, die unter der TPC-Schnittstelle **32** sind.

Diese sind physikalische hierarchische Schichten dieses Schnittstellensystems. Die Parallelschnittstellen **33**, **34** übertragen Daten entsprechend einem Sechsdrahtsystem-Halbduplex-Parallelprotokoll, das ein Datenübertragungsprotokoll zur Übertragung von sechs Signalen ist, die Vierbit-Paralleldaten, einen Takt und ein Buszustandssignal umfassen. Die Parallelschnittstellen **33**, **34** sind Funktionen, die von der Parallelschnittstellschaltung **12** realisiert werden.

**[0058]** Das Register **35** speichert Steuerungsbefehle, die vom Host übertragen werden, den internen Zustand der Speicherplatine, die Adresse von Daten, auf die im Speicher **38** zuzugreifen ist, unterschiedliche Parameter, die zur Ausführung der Steuerungsbefehle notwendig sind, Dateiverwaltungsinformation im Speicher usw. Das Register **35** ist eine auf der Registerschaltung **13** der Speicherplatine **1** realisierte Funktion.

**[0059]** Der Datenpuffer **36** ist ein Pufferbereich zum temporären Sichern von Daten, die in den Speicher **38** zu schreiben sind, und Daten, die aus dem Speicher **38** gelesen werden. Der Datenpuffer **36** ist eine auf der Datenpufferschaltung **14** der Speicherplatine **1** realisierte Funktion.

**[0060]** Der Speicherkontroller **37** steuert Lesen, Schreiben und Löschen von Daten zwischen dem Datenpuffer **36** und dem Speicher **38** und aktualisiert unterschiedliche Information im Register **35** entsprechend Befehlen und unterschiedliche Information, die im Register **35** gespeichert ist. Der Speicherkontroller **37** ist eine vom Speicher-I/F-Kontroller **16** der Speicherplatine **1** realisierte Funktion.

**[0061]** Der Speicher **38** ist ein Speicherbereich für Daten. Der Speicher **38** ist durch den Speicherkontroller **37** als ein eindeutiges Modell virtuell gemacht. Der Speicher **38** ist eine vom nichtflüchtigen Halbleiterspeicher **17** der Speicherplatine **1** realisierte Funktion.

**[0062]** Mit der Hosteinrichtung und der Speicherplatine der oben beschriebenen Aufbauten können Daten, die in vom Dateiverwalter **131** verwalteten anderen Medien gespeichert sind, über die Parallelschnittstellen **33**, **34** zum Speicher **38** übertragen werden. Auch können im Speicher **38** gespeicherte Daten über die Parallelschnittstellen **33**, **34** zu vom Dateiverwalter verwalteten anderen Medien übertragen werden.

**[0063]** Es wird nun das Datenübertragungsprotokoll zwischen der Speicherplatine **1** und der Hosteinrichtung **2** gemäß der vorliegenden Erfindung beschrieben.

**[0064]** Die Merkmale des Datenübertragungsprotokolls zwischen der Speicherplatine **1** und der Hosteinrichtung **2** umfassen Definieren von vier Buszuständen und Identifizieren der Übertragungsrichtung und Attribute von Übertragungsdaten, Zugreifen auf die Registerschaltung **13** und die Datenpufferschaltung **14** der Speicherplatine **1** von der Hosteinrichtung **2** unter Benutzung eines TPC, Steuerung der Operation der Speicherplatine **1** durch die Hosteinrichtung **2** unter Benutzung von Steuerungsbefehlen, Detektieren eines Fehlers von Übertragungsdaten zwischen der Speicherplatine **1** und der Hosteinrichtung **2** unter Benutzung von CRC (= cyclic redundancy check codes (zyklische Redundanzprüfungscode)), Vorschreiben eines Unterbrechungssignals (INT-Signal) von der Speicherplatine **1** zur Hosteinrichtung **2** usw.

**[0065]** Wie in [Fig. 6](#) gezeigt sind die Speicherplatine **1** und die Hosteinrichtung durch sechs Signale miteinander verbunden, die ein Buszustandssignal (BS), vier Paralleldatensignale und ein Taktsignal (SCLK) umfassen.

**[0066]** Die Paralleldatensignale sind Datensignale, die zwischen der Speicherplatine **1** und der Hosteinrichtung **2** übertragen werden. Die Paralleldatensignale übertragen Paralleldaten (DATA[3:0]) mit einer Vierbitbreite, und die Übertragungsrichtung und Attribute der Paralleldaten (DATA[3:0]) ändern sich entsprechend dem vom Buszustandssignal vorgeschriebenen Zustand.

**[0067]** Das Buszustandssignal ist ein den Zustand der Paralleldatensignale und das Übertragungsstarttiming für die Paralleldatensignale in jedem Zustand vorschreibendes Signal. Dieses Buszustandssignal wird von der Hosteinrichtung **2** zur Speicherplatine **1** übertragen. Der Zustand ist in insgesamt vier Zustände unterteilt, das heißt einen Zustand (BS0), bei dem eine Paketkommunikation nicht ausgeführt wird, und drei Zustände (BS1 bis BS3), bei denen eine Paketkommunikation ausgeführt wird. Das Buszustandssignal schaltet den Zustand von BS0 bis BS3 mit einem Schaltzeitpunkt von „hoch“ und „niedrig“

**[0068]** Das Taktsignal ist ein Takt für die Paralleldatensignale und das Buszustandssignal. Das Taktsignal wird von der Hosteinrichtung zur Speicherplatine übertragen. Das Taktsignal wird notwendigerweise in den drei Zuständen (BS1 bis BS3) ausgegeben, bei denen eine Paketkommunikation ausgeführt wird.

[0069] Die Inhalte einer Kommunikation in jedem Zustand sind in [Fig. 7](#) gezeigt.

[0070] BS0 ist der Zustand, bei dem ein Unterbrechungssignal (INT-Signal) von der Speicherplatine **1** zur Hosteinrichtung zu den Leitungen der Paralleldatensignale übertragen werden kann. Das INT-Signal wird mit dem Takt asynchron übertragen. Im Zustand BS0 wird keine Paketkommunikation ausgeführt. Der Signalpegel des BS0 anzeigen Buszustandssignals ist als „niedrig“ ausgedrückt. Der Operationszustand der Speicherplatine **1** wird auf das INT-Signal reflektiert und es wird später beschrieben.

[0071] BS1 ist der Zustand, bei dem TPCs zu den Leitungen der Paralleldatensignale übertragen werden. Der Signalpegel des BS1 anzeigen Buszustandssignals ist als „hoch“ ausgedrückt. TPCs werden von der Hosteinrichtung **2** zur Speicherplatine **1** übertragen. Die TPCs sind Befehle für die Hosteinrichtung **2** zum Zugriff auf die Registerschaltung **13** und die Datenpufferschaltung **14** der Speicherplatine **1**. Die TPCs umfassen einen Befehl zum Schreiben oder Lesen von Daten zu oder von der Datenpufferschaltung **14**, einen Befehl zum Schreiben oder Lesen von Daten zu oder von der Registerschaltung **13**, einen Befehl zum Schreiben eines dem Speicher-I/F-Kontroller **16** zu gebenden Steuerungsbefehls in die Registerschaltung **13** usw. Spezifische Inhalte der TPCs und des Steuerungsbefehls werden später beschrieben.

[0072] In den Zuständen BS2 und BS3 sind die Übertragungsrichtung und Attribute von zu den Paralleldatensignalen übertragenen Paralleldaten (DATA[3:0]) zwischen einem Schreibpaket zur Übertragung von Daten von der Hosteinrichtung **2** zur Speicherplatine **1** und einem Lesepaket zur Übertragung von Daten von der Speicherplatine **1** zur Hosteinrichtung **2** unterschiedlich. Der Typ eines Pakets, das heißt, ob ein Paket ein Schreibpaket oder ein Lesepaket ist, wird entsprechend den Inhalten von im Zustand BS1 übertragenen TPCs entschieden.

[0073] Die Inhalte von BS2 und BS3 im Fall eines Schreibpakets werden nun anhand der [Fig. 8](#), die ein Timingdiagramm für ein Schreibpaket zeigt, beschrieben.

[0074] Im Zustand BS2 sind im Fall eines Schreibpakets Übertragungsdaten auf Paralleldatensignalen Schreibzieldaten zur Registerschaltung **13** und Datenpufferschaltung **14** und ein CRC dieser Schreibzieldaten. Im Zustand BS2 werden die Übertragungsdaten auf den Paralleldatensignalen von der Hosteinrichtung **2** zur Speicherplatine **1** übertragen.

[0075] Im Zustand BS3 sind im Fall des Schreibpakets Übertragungsdaten auf Paralleldatensignalen ein Besetzsiegel (BSY-Signal) und ein Bereitsignal (RDY-Signal), die von der Speicherplatine **1** erzeugt werden. Im Zustand BS3 werden im Fall des Schreibpakets das Besetzsiegel und das Bereitsignal auf den Paralleldatensignalen von der Speicherplatine **1** zur Hosteinrichtung **2** übertragen. Im Zustand BS3 wird im Fall des Schreibpakets eine Verarbeitung eines TPC und von Übertragungsdaten, die von der Hosteinrichtung **2** in den Zuständen BS1 und BS2 zur Speicherplatine **1** übertragen werden, ausgeführt. Während die Speicherplatine **1** die Verarbeitung des TPC und der Übertragungsdaten ausführt (das heißt, wenn die Verarbeitung nicht vollendet ist), sendet die Speicherplatine **1** das Besetzsiegel zur Hosteinrichtung **2**. Bei Vollendung der Verarbeitung sendet die Speicherplatine das Bereitsignal zur Hosteinrichtung **2**. Das Besetzsiegel und das Bereitsignal werden nur zur Signalleitung des niedrigstwertigen Bits (DATA0) der vier Paralleldatensignale übertragen. Das Besetzsiegel ist ein Signal zur Einstellung der Signalleitung des niedrigstwertigen Bits (DATA0) auf einen hohen Pegel. Das Bereitsignal ist ein Signal zum Schalten des Pegels der Signalleitung des niedrigstwertigen Bits (DATA0) abwechselnd und wiederholt zwischen einem hohen Pegel und einem niedrigen Pegel durch den Takt. Das Besetzsiegel und das Bereitsignal werden auf diese Weise übertragen, und zwischen der Speicherplatine **1** und der Hosteinrichtung **2** kann im Fall des Schreibpakets mit dem Timing von BS3 ein Quittungsaustausch- bzw. Signalaustauschzustand (handshaking state) hergestellt werden, wenn Daten nicht übertragen werden.

[0076] Die Inhalte von BS2 und BS3 im Fall eines Lesepakets werden nun anhand der [Fig. 9](#), die ein Timingdiagramm für ein Lesepaket zeigt, beschrieben.

[0077] Im Zustand BS2 sind im Fall eines Lesepakets Übertragungsdaten auf Paralleldatensignalen ein Besetzsiegel und ein Bereitsignal, die von der Speicherplatine erzeugt werden. Im Zustand BS2 bereitet die Speicherplatine **1** im Fall des Lesepakets eine Datenübertragung entsprechend einem von der Hosteinrichtung **2** zur Speicherplatine **1** im Zustand BS1 übertragenen TPC vor. Während die Speicherplatine **1** eine Datenübertragung in Bezug auf den TPC vorbereitet (das heißt, wenn die Vorbereitung zur Übertragung nicht vollendet ist), sendet die Speicherplatine **1** das Besetzsiegel zur Hosteinrichtung **2**. Bei Vollendung der Vorbereitung zur Übertragung sendet die Speicherplatine **1** das Bereitsignal zur Hosteinrichtung **2**. Wenn das Besetzsiegel und das Bereitsignal auf diese Weise übertragen werden, kann im Fall des Lesepakets im Zustand BS2 ein Quittungsaus-

tausch- bzw. Signalaustauschzustand zwischen der Speicherplatine **1** und der Hosteinrichtung **2** hergestellt werden, wenn Daten nicht übertragen werden.

**[0078]** Im Zustand BS3 sind im Fall des Lesepakets Übertragungsdaten auf Paralleldatensignalen Leseziel-daten von der Registerschaltung **13** und der Datenpufferschaltung **14** und ein CRC dieser Leseziel-daten. Im Zustand BS3 werden Übertragungsdaten auf den Paralleldatensignalen von der Speicherplatine **1** zur Hosteinrichtung **2** übertragen.

**[0079]** [Fig. 10](#) zeigt ein detailliertes Timingdiagramm des Besetzungssignals und des Bereitsignals, die in den Zuständen BS2 und BS3 erzeugt werden. Wie in [Fig. 10](#) gezeigt werden das Besetzungssignal und das Bereitsignal nur auf der Signalleitung des niedrigstwertigen Bits (DATA0) von den vier Paralleldatensignalen übertragen. Die anderen Bits (DATA1 bis DATA3) werden auf einen niedrigen Pegel eingestellt. Die Hosteinrichtung **2** empfängt nur das zur Signalleitung von DATA0 übertragene Signal und ignoriert die Signale der anderen Bits. Das niedrigstwertige Bit (DATA0) korrespondiert mit der Übertragungsleitung für serielle Daten in der Speicherplatine unter Benutzung des herkömmlichen Dreidrahtsystem-Halbduplex-Protokolls. Deshalb ist die Speicherplatine **1** mit einer herkömmlichen Speicherplatine kompatibel.

**[0080]** Als Nächstes wird ein INT-Signal, das von der Speicherplatine **1** zur Hosteinrichtung **2** übertragen wird, wenn der Buszustand BS0 ist, beschrieben.

**[0081]** In der Speicherplatine **1** wird ein Flash-Speicher als der nichtflüchtige Halbleiterspeicher **17** benutzt. Die Zugriffszeit zum Flash-Speicher ist viel langer als die Datenübertragungszeit zwischen der Speicherplatine **1** und der Hosteinrichtung **2**. Deshalb ist es zum Reduzieren der Datenverarbeitungssequenz auf der Seite der Hosteinrichtung **2** effektiv, eine Unterbrechungsanforderung vorzuschreiben, die von der Seite der Speicherplatine **1** im Hinblick auf das Datenübertragungsprotokoll über das Ende der Verarbeitung und dgl. informiert. Das heißt, wenn eine Unterbrechungsanforderung von der Speicherplatine **1** vorgeschrieben ist, kann die Verarbeitung durch die CPU auf der Seite der Hosteinrichtung **2** für eine andere Verarbeitung offengemacht werden, während auf den Flash-Speicher zugegriffen wird.

**[0082]** Im Zustand BS0 überträgt die Speicherplatine **1**, wenn in der Speicherplatine **1** eine gewisse Unterbrechungsanforderung erzeugt wird, ein Unterbrechungssignal (INT-Signal) zur Hosteinrichtung **2**. Das INT-Signal wird von der Speicherplatine **1** asynchron mit einem Taktsignal ausgegeben. Wenn im Zustand BS0 das Bit einer der Signalleitungen der Paralleldaten (DATA[3:0]) auf einen hohen Pegel geschaltet wird, zeigt es an, dass das Unterbrechungssignal von der Seite der Speicherplatine **1** erzeugt wird. Wenn alle Bits der Paralleldaten (DATA[3:0]) auf einem niedrigen Pegel sind, wird angezeigt, dass die Speicherplatine **1** eine Verarbeitung ausführt und dass keine Unterbrechungsanforderung existiert.

**[0083]** Die von der Speicherplatine **1** erzeugte Unterbrechung umfasst mehrere Elemente. Beispielsweise weist sie eine Unterbrechung zum Informieren der Hosteinrichtung **2** über die Vollendung einer Operationssteuerung in Reaktion auf einen zur Speicherplatine **1** gegebenen Steuerungsbefehl, eine Unterbrechung zum Informieren der Hosteinrichtung **2** über das Auftreten eines Fehlers, wenn in Reaktion auf einen zur Speicherplatine **1** gegebenen Steuerungsbefehl eine Operationssteuerung ausgeführt wird, eine Unterbrechung für einen Anforderungszugriff auf die Hosteinrichtung, eine Unterbrechung zum Informieren der Hosteinrichtung **2** über eine Information zum Bewirken, dass ein zur Speicherplatine **1** gegebener Steuerungsbefehl nicht ausführbar ist usw. auf.

**[0084]** In der Speicherplatine **1** werden die oben beschriebenen Elemente einer Unterbrechung den jeweiligen Bits der Paralleldaten (DATA[3:0]) und Änderungen der Leitung, die entsprechend erzeugten Elementen einer Unterbrechung auf einem hohen Pegel sein sollten, zugeteilt. Das heißt, ein INT-Signal derart, dass die Bitposition, die im Zustand BS0 auf einem hohen Pegel sein soll, entsprechend den in der Speicherplatine **1** erzeugten Inhalten einer Unterbrechung variiert, von der Speicherplatine **1** erzeugt wird.

**[0085]** Im Zustand BS0 überwacht die Hosteinrichtung **2** die Pegel der jeweiligen Bits der Paralleldaten (DATA[3:0]) und detektiert infolgedessen zur gleichen Zeit die Erzeugung einer Unterbrechungsanforderung von der Speicherplatine **1**, die Bitposition, die auf einem hohen Pegel ist, und das Element einer Unterbrechung von der Speicherplatine **1**.

**[0086]** Im Gegensatz dazu informiert bei einem herkömmlichen Speicherplatten-System die Speicherplatine einfach die Hostseite über die Anwesenheit/Abwesenheit einer Unterbrechungsanforderung. Deshalb kann, selbst wenn es eine Unterbrechungsanforderung von der Speicherplatine gibt, die Hostseite das Element einer

Unterbrechung zusammen mit der Anforderung nicht bestätigen, und die Hostseite muss eine Paketkommunikation herstellen, um das Element einer Unterbrechung von der Speicherkartenseite auszulesen. Jedoch werden bei der Speicherplatine **1** und der Hosteinrichtung **2** der Ausführungsform der vorliegenden Erfindung die Elemente einer Unterbrechung jeweils den Bits der vier Bitdatenleitungen zugeteilt. Deshalb kann die Hosteinrichtung **2** die Unterbrechungsanforderung und das Element einer Unterbrechung zur gleichen Zeit bestätigen.

**[0087]** Deshalb braucht bei der vorliegenden Erfindung, wenn eine Unterbrechungsanforderung von der Speicherplatine **1** erzeugt wird, die Hosteinrichtung **2** keine Paketkommunikation zur Bestätigung der Inhalte der Anforderung auszuführen. Kurz ausgedrückt kann die Ausführungszeit der Datenübertragungssequenz zwischen der Speicherplatine **1** und der Hosteinrichtung **2** reduziert werden.

**[0088]** Bei dieser Ausführungsform weist das INT-Signal der Speicherplatine **1** jeden Bitwert auf, der in einem INT-Register gespeichert ist und durch den Operationszustand auf der Basis eines Steuerungsbefehls reflektiert wird. Das INT-Register ist in einer Statusregistergruppe in der Registerschaltung **13** bereitgestellt. Wenn das Buszustandssignal BS0 anzeigt, bezieht sich die Parallelschnittstellenschaltung **12** der Speicherplatine **1** auf jeden Bitwert des INT-Registers. Wenn der Bitwert valid (gültig) (1) ist, wird die mit diesem Bit korrespondierende Datenleitung auf einen hohen Pegel gesteuert. Wenn der Bitwert invalid (ungültig) (0) ist, wird die mit diesem Bitwert korrespondierende Datenleitung auf einen niedrigen Pegel gesteuert. Die spezifischen Inhalte des INT-Registers und die Relation zwischen jedem Wert des INT-Registers und den Paralleldaten (DATA[3:0]) wird in der folgenden Beschreibung der Registerschaltung beschrieben.

**[0089]** Es wird nun die Registerschaltung **13** beschrieben.

**[0090]** Die Registerschaltung **13** weist mehrere interne Register auf. Die internen Register der Registerschaltung **13** werden entsprechend den Anwendungen in die folgenden Gruppen **1** bis **5** klassifiziert:

1. eine Statusregistergruppe, in welcher der Status der Speicherplatine **1** und dgl. gespeichert wird;

2. eine Parameterregistergruppe, in der Parameter, die zur Ausführung und dgl. von Befehlen benutzt werden, gespeichert werden;

3. eine Extradatenregistergruppe, die für jede Seite des Flash-Speichers bereitgestellt wird und in der Verwaltungsdaten und dgl. jeder Seite gespeichert werden;

4. ein Registeradressenregister, in welchem Adressen zum Spezifizieren von Zugriffspositionen zu den Registern der oben beschriebenen Gruppen **1**, **2** und **3** gespeichert werden; und

5. ein Befehlsregister, in welchem Steuerungsbefehle, die von der Hosteinrichtung **2** bereitgestellt werden, gespeichert werden.

**[0091]** Wie in [Fig. 11](#) gezeigt weist die Statusregistergruppe **5** interne Register auf, das heißt ein INT-Register, ein Statusregister, ein Typregister, ein Kategorieregister und ein Clusterregister auf. Die in den internen Register der Statusregistergruppe gespeicherten Werte werden vom Speicher-I/F-Kontroller **16** aktualisiert. Auf die internen Register der Statusregistergruppe kann von der Hosteinrichtung **2** unter Benutzung eines READ\_REG\_TPC (der einer der TPCs ist und später im Detail beschrieben wird) zugegriffen werden. Der Zugriff von der Hosteinrichtung **2** ist ein Nurlesezugriff. Jedes der internen Register der Statusregistergruppe kann Bitwerte von acht Bits speichern, und für jedes wird eine Adresse gesetzt.

\*INT-Register

**[0092]** Das INT-Register ist ein Register, in welchem der Operationszustand der Speicherplatine **1** eingestellt wird. Der Wert in diesem INT-Register wird vom Speicher-I/F-Kontroller **16** entsprechend dem Resultat einer mit einem von der Hosteinrichtung **2** der Speicherplatine **1** bereitgestellten Steuerungsbefehl aktualisiert. Wie in [Fig. 12](#) gezeigt ist das TNT-Register ein Achtbitregister. Im INT-Register wird der Operationszustand beim niedrigstwertigen Bit (D0) und bei drei Bits (D5 bis D7) hoher Ordnung von acht Bits eingestellt. Die verbleibenden Bits werden reserviert.

**[0093]** Das Bit D7 des TNT-Registers ist ein CED-Bit (CED = command end (Befehlsende)). Das CED-Bit ist ein Bit, welches das Ende einer Ausführung eines durch EX\_SET\_CMD\_TPC oder SET\_CMD\_TPC (der einer der TPCs ist und später im Detail beschrieben wird) gesetzten Steuerungsbefehls anzeigen. Das Ende einer Ausführung bedeutet in diesem Fall das Ende einer Ausführung ungeachtet dessen, ob die Ausführung normal endete oder durch eine Fehler endete. Der Bitwert des CED-Bits wird vom Speicher-I/F-Kontroller **16** invalid (0) gemacht, wenn der auf EX\_SET\_CMD\_TPC oder SET\_CMD\_TPC basierende Steuerungsbefehl gesetzt oder in einem Anfangszustand ist. Der Bitwert des CED-Bits wird vom Speicher-I/F-Kontroller **16** valid (1) gemacht, wenn eine Ausführung des auf EX\_SET\_CMD\_TPC oder SET\_CMD\_TPC basierenden Steuerungs-

befehls endet.

**[0094]** Das Bit D6 des INT-Registers ist ein ERR-Bit (ERR = Error (Fehler)). Das ERR-Bit ist ein Bit, das anzeigen, dass als ein Resultat einer Ausführung eines Speicherzugriffsbefehls (Steuerungsbefehl) und eines Sicherheitsbefehls (Steuerungsbefehl), die vom EX\_SET\_CMD\_TPC oder SET\_CMD\_TPC gesetzt werden, ein Fehler auftrat. Der Bitwert des ERR-Bits wird vom Speicher-I/F-Kontroller **16** valid (1) gemacht, wenn ein Fehler auftritt. Der Bitwert des ERR-Bits wird vom Speicher-I/F-Kontroller **16** invalid (0) gemacht, wenn ein Steuerungsbefehl durch einen neuen EX\_SET\_CMD\_TPC oder SET\_CMD\_TPC gesetzt wird oder wenn der Fehlerzustand beseitigt wird.

**[0095]** Das Bit D5 des INT-Registers ist ein BREQ\_PRG\_BIT (BREQ\_PRG = buffer request/progress (Puffer-Anforderung(Fortschritt)). Das BREQ\_PRG-Bit ist ein Bit, das im Fall einer Zugriffsanforderung zum Zugriff auf die Datenpufferschaltung **14** zur Hosteinrichtung **2**, die als ein Resultat einer Ausführung eines vom EX\_SET\_CMD\_TPC oder SET\_CMD\_TPC gesetzten Speicherzugriffsbefehls (Steuerungsbefehl) und Sicherheitsbefehls (Steuerungsbefehl) erzeugt wird, den Status eines Fortschritts anzeigt, und es werden eine interne Löschverarbeitung und Formatierung des nichtflüchtigen Halbleiterspeichers **17** ausgeführt. Beispielsweise ist es ein Bit, das die Existenz einer Datenschreibanforderung zum Schreiben von Daten in die Datenpufferschaltung **14**, wenn ein Schreibbefehl an den nichtflüchtigen Halbleiterspeicher **17** ausgegeben wird, einer Datenleseanforderung zum Lesen von Daten von der Datenpufferschaltung **14**, wenn ein Lesebefehl zum Lesen von Daten vom nichtflüchtigen Halbleiterspeicher **17** ausgegeben wird, oder einer Empfangsanforderung zum Empfang von Sicherheitsdaten anzeigt. Der Bitwert des BREQ/PRG-Bits wird vom Speicher-I/F-Kontroller **16** valid (1) gemacht, wenn jede betreffende Anforderung erzeugt wird. Der Bitwert des BREQ/PRG-Bits wird vom Speicher-I/F-Kontroller **16** invalid (0) gemacht, wenn durch die Hosteinrichtung **2** in Reaktion auf die Anforderung ein auf einem TPC basierender Zugriff auftritt. Der Bitwert des BREQ/PRG-Bits wird vom Speicher-I/F-Kontroller **16** entsprechend dem Status eines Fortschritts einer Formatierung oder Löschung aktualisiert.

**[0096]** Das Bit D0 des INT-Registers ist ein CMDNK-Bit (CMDNK = command nack (Befehlsnegativrückmeldung). Das CMDNK-Bit ist ein Bit, das anzeigen, dass ein vom EX\_SET\_CMD\_TPC oder SET\_CMD\_TPC gesetzter Befehl nicht ausgeführt werden kann. Der Bitwert wird vom Speicher-I/F-Kontroller **16** valid (1) gemacht, wenn der vom EX\_SET\_CMD\_TPC oder SET\_CMD\_TPC gesetzte Steuerungsbefehl nicht ausgeführt werden kann. Der Bitwert wird invalid (0) gemacht, wenn der vom EX\_SET\_CMD\_TPC oder SET\_CMD\_TPC gesetzte Steuerungsbefehl ausgeführt werden kann.

**[0097]** Die wie oben beschriebenen Bits werden in das INT-Register gesetzt. Infolgedessen können, wenn die Bitwerte des INT-Registers richtig kombiniert sind, Betriebszustände, wie sie in [Fig. 13](#) gezeigt sind, in Reaktion auf den letzten Steuerungsbefehl als der Betriebszustand der Speicherplatine **1** ausgedrückt werden.

**[0098]** Insbesondere wenn CED = 1, ERR = 0, BREQ/PRG = 0 und CMDNK = 0 gilt, zeigen diese Werte einen Betriebszustand an, dass eine Ausführung eines gegebenen Steuerungsbefehls normal endete. Wenn CED = 1, ERR = 1, BREQ/PRG = 0 und CMDNK = 0 gilt, zeigen diese Werte einen Betriebszustand an, dass eine Ausführung eines gegebenen Steuerungsbefehls mit einem Fehler endete. Wenn CED = 0, ERR = 0, BREQ/PRG = 1 und CMDNK = 0 gilt, zeigen diese Werte einen Betriebszustand an, dass die Ausführung eines gegebenen Steuerungsbefehls normal ausgeführt wird und dass eine Zugriffsanforderung zur Hosteinrichtung **2** gemacht wird. Wenn CED = 0, ERR = 1, BREQ/PRG = 1 und CMDNK = 0 gilt, zeigen diese Werte einen Betriebszustand (operating state) an, dass bei der Ausführung eines gegebenen Steuerungsbefehls ein Fehler erzeugt wird und dass eine Zugriffsanforderung an die Hosteinrichtung **2** gemacht wird. Wenn CED = 0, ERR = 0, BREQ/PRG = 0 und CMDNK = 0 gilt, zeigen diese Werte einen Betriebszustand an, dass ein gegebener Steuerungsbefehl ausgeführt wird. Wenn CED = 0, ERR = 1, BREQ/PRG = 0 und CMDNK = 0 gilt, zeigen diese Werte einen Betriebszustand an, dass ein Löschen des nichtflüchtigen Halbleiterspeichers **17** ausgeführt wird oder eine Formatierung ausgeführt wird. Wenn CED = 1, ERR = 0, BREQ/PRG = 0 und CMDNK = 1 gilt, zeigen diese Werte einen Betriebszustand an, dass ein gegebener Steuerungsbefehl nicht ausführbar ist.

**[0099]** Wenn vom EX\_SET\_CMD\_TPC oder SET\_CMD\_TPC ein neuer Steuerungsbefehl gesetzt wird, werden im INT-Register die Anfangswerte der Bits vom Speicher-I/F-Kontroller **16** wiederhergestellt (das heißt alle Bitwerte sind 0).

\*Relation zwischen INT-Register und INT-Signal

**[0100]** Wie oben beschrieben werden die Werte der jeweiligen Bits (CED, ERR, BREQ/PRG, CMDNK) im

INT-Register auf das INT-Signal reflektiert. Im Zustand BS0 steuert die Parallelschnittstellenschaltung **12** der Speicherplatte **1** die jeweiligen Datenleitungen der Paralleldaten (DATA[3:0]) entsprechend den Bitwerten (CED, ERR, BREQ/PRG, CMDNK) des INT-Registers auf einen hohen Pegel oder einen niedrigen Pegel. Das Folgende ist die Relation zwischen den jeweiligen Bits des INT-Registers und den jeweiligen Leitungen der Paralleldaten.

DATA0:CED

DATA1:ERR

DATA2:BREQ/PRG

DATA3:CMDNK

**[0101]** Die Parallelschnittstellenschaltung **12** bezieht sich während der Periode, wenn der Zustand BS0 ist, konstant auf die Werte im INT-Register. Wenn irgendeiner der Bitwerte im INT-Register valid (1) ist, steuert die Parallelschnittstellenschaltung **12** die korrespondierende Datenleitung auf einen hohen Pegel (1). Wenn irgendeiner der Bitwerte invalid (0) ist, steuert die Parallelschnittstellenschaltung **1** die korrespondierende Datenleitung auf einen niedrigen Pegel (0). Während der Periode, wenn der Zustand BS0 ist, überwacht die Hosteinrichtung **2** die Pegel der jeweiligen Datenleitungen der Paralleldaten (DATA[3:0]) und entscheidet, ob von der Speicherplatte **1** eine Unterbrechungsanforderung ausgegeben wird oder nicht. Wenn von der Speicherplatte **1** eine Unterbrechungsanforderung ausgegeben wird, dass heißt, wenn entschieden wird, dass eine der Datenleitungen von einem niedrigen Pegel auf einen hohen Pegel geschaltet wird, detektiert die Hosteinrichtung **2** die Leitung, die auf einem hohen Pegel ist und detektiert infolgedessen einen der in [Fig. 13](#) gezeigten Betriebszustände. Dann führt die Hosteinrichtung **2** eine mit dem detektierten Betriebszustand korrespondierende Verarbeitung aus.

**[0102]** In der Parameterregistergruppe sind, wie in [Fig. 14](#) gezeigt, interne Register bereitgestellt, das heißt ein Systemparameterregister, ein Datenzählungs/Sicherheitsparameter-Register, ein Datenadressen/Revisionszahl-Register, ein TPC-Parameter-Register und ein Befehlsparameter-Register. Die in den internen Registern in der Parameterregistergruppe gespeicherten Werte werden von der Hosteinrichtung **2** aktualisiert, und auf diese Werte wird Bezug genommen, wenn der Speicher-I/F-Kontroller **16** einen Steuerungsbefehl ausführt. Auf die internen Register in der Parameterregistergruppe kann von der Hosteinrichtung **2** unter Benutzung eines WRITE-REG-TPC und EX\_SET\_CMD\_TPC (der jeweils einer der TPCs ist und später im Detail beschrieben wird) zugegriffen werden. In den internen Registern in der Parameterregistergruppe ist alle acht Bits eine Adresse gesetzt.

\*Datenzählungs/Sicherheitsparameter-Register

**[0103]** Im Datenzählungs/Sicherheitsparameter-Register ist die Anzahl von Daten gespeichert, die notwendig ist, wenn ein von der Hosteinrichtung **2** der Speicherplatte **1** bereitgestellter Speicherzugriffsbefehl (Steuerungsbefehl) ausgeführt wird. Beispielsweise wird die Datengröße der beim Auslesen von Daten aus dem nichtflüchtigen Halbleiterspeicher **17** gelesenen Daten und die Datengröße der beim Schreiben von Daten in den nichtflüchtigen Halbleiterspeicher **17** geschriebenen Daten eingestellt. Außerdem sind im Datenzählungs/Sicherheitsparameter-Register unterschiedlich eingestellte Werte, die bei Ausführung eines Sicherheitsbefehls (Steuerungsbefehl) notwendig sind, gespeichert. Die Größe des Datenzählungs/Sicherheitsparameter-Registers ist 16 Bits, und für AchtbitEinheiten werden jeweils zwei Adressen gesetzt.

\*Datenadressen/Revisionszahl-Register

**[0104]** Im Datenadressen/Revisionszahl-Register wird auf dem nichtflüchtigen Halbleiterspeicher **17** eine Adresse, die bei Ausführung eines von der Hosteinrichtung **2** der Speicherplatte **1** bereitgestellten Speicherzugriffsbefehls (Steuerungsbefehls) notwendig ist, gespeichert. Beispielsweise wird eine Führungs- bzw. Anfangsadresse (leading address) einer Leseposition beim Auslesen von Daten aus dem nichtflüchtigen Halbleiterspeicher **17** oder eine Führungs- bzw. Anfangsadresse einer Schreibposition beim Schreiben von Daten in den nichtflüchtigen Halbleiterspeicher **17** gespeichert. Außerdem wird im Datenadressen/Revisionszahl-Register eine Revisionszahl, die bei Ausführung eines Sicherheitsbefehls (Steuerungsbefehl) notwendig ist, gespeichert. Die Größe des Datenadressen/Revisionszahl-Registers ist 32 Bits, und für AchtbitEinheiten werden jeweils vier Adressen gesetzt.

**[0105]** Auf das Datenzählungs/Sicherheitsparameter-Register und das Datenadressen/Revisionszahl-Register wird bei Ausführung von READ\_DATA, READ\_INFO, WRITE\_DATA, WRITE\_INFO und dgl. von Speicherzugriffsbefehlen (Steuerungsbefehlen) Bezug genommen. Entsprechend einem WRITE\_REG\_TPC und EX\_SET\_CMD\_TPC werden Daten in das Datenzählungs/Sicherheitsparameter-Register und das Datena-

dressen/Revisionszahl-Register geschrieben. Die Inhalte dieser Steuerungsbefehle werden später im Detail beschrieben.

**[0106]** Das Registeradressenregister ist ein Register, das eine Führungs- bzw. Anfangsadresse und eine Datenlänge eines Registers, auf das zuzugreifen ist, wenn die Hosteinrichtung **2** auf die oben beschriebene Statusregistergruppe und Parameterregistergruppe durch Benutzung eines TPC zugreift, voreinstellt.

**[0107]** Daten können in die oben beschriebene Statusregistergruppe und Parameterregistergruppe unter Benutzung eines WRITE\_REG\_TPC (der einer der einer der TPCs ist und später im Detail beschrieben wird) geschrieben werden. Daten können aus der Statusregistergruppe und Parameterregistergruppe unter Benutzung eines READ\_REG\_TPC (der einer der TPCs ist und später im Detail beschrieben wird) gelesen werden. Jedoch weisen dieser READ\_REG\_TPC und READ\_REG\_TPC keine Information, die eine Registerposition als einen Faktor spezifiziert, auf. Deshalb werden, wenn die Hosteinrichtung **2** unter Benutzung eines WRITE\_REG\_TPC oder READ\_REG\_TPC auf ein Register zugreift, eine Adresse und eine Datenlänge für die Statusregistergruppe und Parameterregistergruppe eingestellt. Wenn ein WRITE\_REG\_TPC oder READ\_REG\_TPC gegeben ist, bezieht sich der Speicher-I/F-Kontroller **16** auf die im Registeradressenregister gespeicherte Information und führt die mit jedem Befehl korrespondierende Verarbeitung aus. Ein TPC zum Speichern der Registeradresse und der Datenlänge im Registeradressenregister ist ein SET\_R\_W\_REG\_ADRS\_TPC, der später im Detail beschrieben wird.

**[0108]** Das Befehlsregister ist ein Register zum Speichern von Steuerungsbefehlen, die von der Hosteinrichtung **2** bereitgestellt werden. In Reaktion auf die im Befehlsregister gespeicherten Steuerungsbefehle führt der Speicher-I/F-Kontroller **16** unterschiedliche Operationssteuerung aus. Ein TPC zum Speichern von Steuerungsbefehlen im Befehlsregister ist SET\_CMD\_TPC und EX\_SET\_CMD\_TPC, die später im Detail beschrieben werden. Es werden nun TPCs (TPC = transfer protocol commands (Übertragungsprotokollbefehle) beschrieben.

**[0109]** TPCs sind Befehle, die auf dem Datenübertragungsprotokoll der vorliegenden Speicherplatine **1** und Hosteinrichtung **2** vorgeschrieben sind. TPCs werden in der Hosteinrichtung **2** benutzt, wenn sie auf die Registerschaltung **13** und die Datenpufferschaltung **14** in der Speicherplatine **1** zugreift. TPCs werden von der Hosteinrichtung **2** zur Speicherplatine **1** mit dem Timing übertragen, wenn der Buszustand BS1 ist. Die Codeinhalte dieser TPCs und ihre spezifischen Operationen werden beschrieben.

**[0110]** Das Folgende sind exemplarische TPCs.

```

READ_LONG_DATA_TPC

READ_SHORT_DATA_TPC

READ_REG_TPC

GET_INT_TPC

WRITE_LONG_DATA_TPC

WRITE_SHORT_DATA_TPC

WRITE_REG_TPC

SET_R_W_REG_ADRS_TPC

EX_SET_CMD_TPC

SET_CMD_TPC

```

**[0111]** READ\_LONG\_DATA\_TPC ist ein Befehl zum Auslesen von Daten aus 512 Bytes aus der Datenpufferschaltung **14**. Das heißt er ist ein Befehl zur Übertragung aller der in der Datenpufferschaltung **14** gespeicherten Daten zur Hosteinrichtung **2**. READ\_LONG\_DATA\_TPC ist ein Lesesystembefehl. Insbesondere werden bei Ausgabe des READ\_LONG\_DATA\_TPC aus der Hosteinrichtung **2** zur Speicherplatine **1** im Zustand BS1 Daten aus 512 Bytes in der Datenpufferschaltung **14** im Zustand BS3 von der Speicherplatine **1** zur Hosteinrichtung **2** übertragen.

**[0112]** READ\_SHORT\_DATA\_TPC ist ein Befehl zum Auslesen von Daten mit einer durch das TPC-Parameter-Register eingestellten Datenlänge aus der Datenpufferschaltung **14**. Das heißt, er ist ein Befehl zur Übertragung einer vorbestimmten Menge von in der Datenpufferschaltung **14** gespeicherten Daten zur Hosteinrichtung **2**. READ\_SHORT\_DATA\_TPC ist ein Lesesystembefehl. Insbesondere werden bei Ausgabe des READ\_SHORT\_DATA\_TPC aus der Hosteinrichtung **2** zur Speicherplatine **1** im Zustand BS1 Daten einer vor-

bestimmten Anzahl von Bytes in der Datenpufferschaltung **14** im Zustand BS3 von der Speicherkarte **1** zur Hosteinrichtung **2** übertragen.

**[0113]** READ\_REG\_TPC ist ein Befehl zum Auslesen des Werts eines Registers, das eine dafür gesetzte Adresse aufweist. Das Register, das eine dafür gesetzte Adresse aufweist, ist jedes interne Register der Statusregistergruppe, der Parameterregistergruppe und der Extraregistergruppe. Die Adressenposition (Führungsadresse und Datenlänge) des Registers, von dem Lesen auszuführen ist, ist der im Registeradressenregister gespeicherte Wert. Kurz ausgedrückt ist es, wenn auf einen Wert in einem Register Bezug genommen wird, notwendig, die Zieladressenposition im Voraus in das Registeradressenregister zu schreiben. Ein TPC zum Schreiben der Adressenposition in das Registeradressenregister ist SET\_R\_W\_REG\_ADRS\_TPC. READ\_REG\_TPC ist ein Lesesystembefehl. Insbesondere werden bei Ausgabe von READ\_REG\_TPC von der Hosteinrichtung **2** zur Speicherkarte **1** im Zustand BS1 Daten einer vorbestimmten Anzahl von Bits im Zielregister im Zustand BS3 von der Speicherkarte **1** zur Hosteinrichtung **2** übertragen.

**[0114]** GET\_INT\_TPC ist ein Befehl zum Auslesen des Werts (von acht Bits) des INT-Registers, das ein internes Register der Statusregistergruppe ist. Anders als der oben beschriebene READ\_REG\_TPC dient dieser GET\_INT\_TPC zum Auslesen des Werts des INT-Registers ohne Speicherung der Adressenposition im Registeradressenregister. GET\_INT\_TPC ist ein Lesesystembefehl. Insbesondere werden bei Ausgabe von GET\_INT\_TPC aus der Hosteinrichtung **2** zur Speicherkarte **1** im Zustand BS1 Daten von acht Bits im INT-Register im Zustand BS3 von der Speicherkarte **1** zur Hosteinrichtung **2** übertragen.

**[0115]** WRITE\_LONG\_DATA\_TPC ist ein Befehl zum Schreiben von Daten aus 512 Bytes in die Datenpufferschaltung **14**. Das heißt, er ist ein Befehl zur Übertragung all der Daten für die Datenpufferschaltung **14** von der Hosteinrichtung **2** zur Speicherkarte **1**. WRITE\_LONG\_DATA\_TPC ist ein Schreibsystembefehl. Insbesondere werden bei Ausgabe von WRITE\_LONG\_DATA\_TPC von der Hosteinrichtung **2** zur Speicherkarte **1** im Zustand BS1 Daten aus 512 Bytes, die in die Datenpufferschaltung **14** zu schreiben sind, im Zustand BS2 von der Hosteinrichtung **2** zur Speicherkarte **1** übertragen.

**[0116]** WRITE\_SHORT\_DATA\_TPC ist ein Befehl zum Schreiben von Daten, die eine durch das TPC-Parameterregister eingestellte Datenlänge aufweisen, in die Datenpufferschaltung **14**. Das heißt, er ist ein Befehl zur Übertragung einer vorbestimmten Menge von Daten von der Hosteinrichtung **2** in die Datenpufferschaltung **14**. WRITE\_SHORT\_DATA\_TPC ist ein Schreibsystembefehl. Insbesondere werden bei Ausgabe von WRITE\_SHORT\_DATA\_TPC von der Hosteinrichtung **2** zur Speicherkarte **1** im Zustand BS1 Daten einer vorbestimmten Anzahl von Bytes, die in die Datenpufferschaltung **14** zu schreiben sind, im Zustand BS2 von der Hosteinrichtung **2** zur Speicherkarte **1** übertragen.

**[0117]** WRITE\_REG\_TPC ist ein Befehl zum Schreiben des Werts eines Registers, das eine dafür gesetzte Adresse aufweist. Das Register, das eine dafür gesetzte Adresse aufweist, ist jedes interne Register der Statusregistergruppe, der Parameterregistergruppe und der Extraregistergruppe. Jedoch ist das Register, in das von der Hosteinrichtung **2** ein Wert geschrieben werden kann, in der Parameterregistergruppe und der Extraregistergruppe inkludiert. Die Adressenposition (Führungs- bzw. Anfangsadresse und Datenlänge) des Registers, bei dem ein Schreiben auszuführen ist, ist der im Registeradressenregister gespeicherte Wert. Kurz ausgedrückt ist es beim Schreiben eines Werts in ein Register notwendig, die Zieladressenposition im Voraus in das Registeradressenregister zu schreiben. Ein TPC zum Schreiben der Adressenposition in das Registeradressenregister ist SET\_R\_W\_REG\_ADRS\_TPC. WRITE\_REG\_TPC ist ein Schreibsystembefehl. Insbesondere werden bei Ausgabe von WRITE\_REG\_TPC aus der Hosteinrichtung **2** zur Speicherkarte **1** im Zustand BS1 Daten, die in das Zielregister zu schreiben sind, im Zustand BS2 von der Hosteinrichtung **2** zur Speicherkarte **1** übertragen.

**[0118]** SET\_R\_W\_REG\_ADRS\_TPC ist ein Befehl zum Speichern der Adressenposition eines Registers, auf das entsprechend READ\_REG\_TPC oder WRITE\_REG\_TPC zuzugreifen ist, im Registeradressenregister. SET\_R\_W\_REG\_ADRS\_TPC ist ein Schreibsystembefehl. Insbesondere werden bei Ausgabe von SET\_R\_W\_REG\_ADRS\_TPC aus der Hosteinrichtung **2** zur Speicherkarte **1** im Zustand BS1 Daten, die in das Registeradressenregister zu schreiben sind, im Zustand BS2 von der Hosteinrichtung **2** zur Speicherkarte **1** übertragen.

**[0119]** SET\_CMD\_TPC ist ein Befehl zum Speichern eines Steuerungsbefehls zum Speicher-I/F-Kontroller **16** im Befehlsregister als einen Operationsbefehl. Wenn im Befehlsregister ein Steuerungsbefehl entsprechend SET\_CMD\_TPC gespeichert wird, führt der Speicher-I/F-Kontroller **16** eine mit dem Steuerungsbefehl korrespondierende Operationssteuerung aus. Die Inhalte der Operation umfassen beispielweise eine Opera-

tionssteuerung für den Speicher, eine Operation zu unterschiedlichen Funktionen mit Ausnahme für den Speicher, eine sich auf die Sicherheit von Daten beziehende Operation usw. Auf Basis des Steuerungsbefehls wird die Operation abhängig von den Inhalten der Operation in Bezug auf den im Parameterregister gespeicherten Wert ausgeführt. In diesem Fall ist es notwendig, den Wert vor Ausgabe von SET\_CMD\_TPC unter Benutzung des oben beschriebenen WRITE\_REG\_TPC im

**[0120]** Voraus in einem Paket in ein vorbestimmtes internes Register der Parameterregistergruppe zu schreiben. SET\_CMD\_TPC ist ein Schreibsystembefehl. Insbesondere wird bei Ausgabe von SET\_CMD\_TPC von der Hosteinrichtung **2** zur Speicherplatte **1** im Zustand BS1 ein Code eines in das Befehlsregister zu schreibenden Steuerungsbefehls im Zustand BS2 von der Hosteinrichtung **2** zur Speicherplatte **1** übertragen.

**[0121]** EX\_SET\_CMD\_TPC ist ein Befehl zum Speichern von Daten im Datenzählungs/Sicherheitsparameter-Register und Datenadressen/Revisionszahl-Register und zum Speichern eines Steuerungsbefehls im Befehlsregister. Wenn ein Speicherzugriffsbefehl als ein Steuerungsbefehl entsprechend EX\_SET\_CMD\_TPC übertragen wird, wird die Datenmenge von Daten, auf die im nichtflüchtigen Halbleiterspeicher **17** zuzugreifen ist, im Datenzählungs/Sicherheitsparameter-Register gespeichert, und die Datenadresse im nichtflüchtigen Halbleiterspeicher **17** wird im Datenadressen/Revisionszahl-Register gespeichert. Wenn ein Sicherheitsbefehl als ein Steuerungsbefehl entsprechend EX\_SET\_CMD\_TPC übertragen wird, wird ein Parameter zur Sicherheitsverwaltung im Datenzählungs/Sicherheitsparameter-Register gespeichert, und eine Revisionszahl zur Sicherheitsverwaltung wird im Datenadressen/Revisionszahl-Register gespeichert. Wenn ein Steuerungsbefehl entsprechend EX\_SET\_CMD\_TPC übertragen wird, werden Übertragungsdaten im Datenzählungs/Sicherheitsparameter-Register und Datenadressen/Revisionszahl-Register gespeichert, bevor der Speicher-I/F-Kontroller **16** den Steuerungsbefehl ausführt.

**[0122]** EX\_SET\_CMD\_TPC ist ein Schreibsystembefehl. Insbesondere wird bei Ausgabe von EX\_SET\_CMD\_TPC aus der Hosteinrichtung **2** zur Speicherplatte **1** im Zustand BS1 ein Code eines Steuerungsbefehls oder dgl. im Zustand BS2 von der Hosteinrichtung **2** zur Speicherplatte **1** übertragen.

**[0123]** Die gleiche Datenübertragungsoperation wie die von EX\_SET\_CMD\_TPC kann auch mit EX\_SET\_CMD\_TPC realisiert werden. Jedoch beispielsweise im Fall einer Übertragung eines Steuerungsbefehls für eine sich auf einen in einem internen Register der Parameterregistergruppe gespeicherten Wert beziehenden Operationssteuerung müssen im Fall einer Übertragung eines Steuerungsbefehls wie beispielsweise READ\_DATA, READ\_INFO, WRITE\_DATA oder WRITE\_INFO die Daten, auf die Bezug zu nehmen ist, im Voraus zum Parameterregister übertragen werden. Das heißt, SET\_R\_W\_REG\_ADRS\_TPC und WRITE\_REG\_TPC müssen vor der Ausführung von SET\_CMD\_TPC übertragen werden.

**[0124]** Wenn andererseits EX\_SET\_CMD\_TPC benutzt wird, ist es nicht notwendig, Daten im Voraus unter Benutzung von WRITE\_REG\_TPC im Datenzählungs/Sicherheitsparameter-Register und Datenadressen/Revisionszahl-Register zu speichern. Kurz ausgedrückt kann EX\_SET\_CMD\_TPC die Datenübertragungsoperation, die im Fall einer Benutzung von SET\_CMD\_TPC drei Pakete erfordern würde, mit nur einem einzelnen Paket realisieren.

**[0125]** Deshalb muss bei Übertragung eines Steuerungsbefehls unter Benutzung von EX\_SET\_CMD\_TPC keine Paketsequenz zur Übertragung von SET\_R\_W\_REG\_ADRS\_TPC und WRITE\_REG\_TPC ausgeführt werden, und es kann eine Hochgeschwindigkeitsverarbeitung realisiert werden.

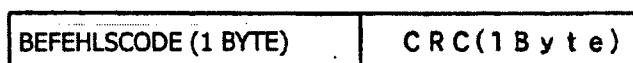

**[0126]** [Fig. 15](#) zeigt ein spezielles Beispiel einer Übertragung von Daten, die von der Hosteinrichtung **2** zur Speicherplatte **1** übertragen werden, wenn SET\_CMD\_TPC ausgeführt wird. [Fig. 16](#) zeigt ein spezielles Beispiel einer Übertragung von Daten, die von der Hosteinrichtung **2** zur Speicherplatte **1** übertragen werden, wenn EX\_SET\_CMD\_TPC ausgeführt wird. Die in den [Fig. 15](#) und [Fig. 16](#) gezeigten Übertragungsdaten werden im Zustand BS2 übertragen.

**[0127]** Übertragungsdaten im Fall, dass SET\_CMD\_TPC ausgeführt wird, weisen einen Befehlscode aus einem einzelnen Byte und einem CRC aus zwei Bytes auf. Der Einbyte-Befehlscode ist ein Code, der einen Steuerungsbefehl spezifiziert, der im Speicher-I/F-Kontroller **16** auszuführen wird. Der Befehlscode wird im Befehlsregister gespeichert.

**[0128]** Übertragungsdaten im Fall, dass EX\_SET\_CMD\_TPC ausgeführt wird, weisen einen Befehlscode aus einem einzelnen Byte, Zählungs/Sicherheitsparameter-Daten aus zwei Bytes, Adressen/Revisionszahl-Daten aus zwei Bytes und einen CRC aus zwei Bytes auf. Die Zählungs/Sicherheitsparameter-Daten sind Daten, die

im Datenzählungs/Sicherheitsparameter-Register zu speichern sind. Die Adressen/Revisionszahl-Daten sind Daten, die im Datenadressen/Revisionszahl-Register zu speichern sind.

**[0129]** Wie in den [Fig. 15](#) und [Fig. 16](#) gezeigt weisen die Übertragungsdaten im Fall von EX\_SET\_CMD\_TPC eine längere Datenlänge als die Übertragungsdaten im Fall von SET\_CMD\_TPC auf. Deshalb benutzt, wenn ein Befehlscode übertragen wird, der ohne Neuzugnahme auf das Datenzählungs/Sicherheitsparameter-Register und das Datenadressen/Revisionszahl-Register ausgeführt werden kann, die Hosteinrichtung **2** durch Benutzung von SET\_CMD\_TPC anstelle von EX\_SET\_CMD\_TPC ein kurzes Paket. Deshalb kann, wenn SET\_CMD\_TPC und EX\_SET\_CMD\_TPC als ein TPC-Befehllssatz gesetzt und entsprechend einem zu übertragenden Steuerungsbefehl adaptiv ausgewählt werden, eine Verarbeitung mit einer höheren Geschwindigkeit ausgeführt werden.

**[0130]** Es werden mm Steuerungsbefehle beschrieben.

**[0131]** Steuerungsbefehle sind Operationssteuerungsbefehle, die von der Hosteinrichtung **2** dem Speicher-I/F-Kontroller **16** der Speicherplatine **1** bereitgestellt werden. Ein Steuerungsbefehl wird von der Hosteinrichtung **2** entsprechend SET\_CMD\_TPC oder EX\_SET\_CMD\_TPC im Befehlsregister in der Speicherplatine **1** gespeichert. Wenn der Steuerungsbefehl im Befehlsregister gespeichert wird, führt der Speicher-I/F-Kontroller **16** eine mit diesem Steuerungsbefehl korrespondierende Operationssteuerung aus. Dann aktualisiert der Speicher-I/F-Kontroller **16** jeden Wert im INT-Register zusammen mit der Ausführung der Operationssteuerung richtig.

**[0132]** Steuerungsbefehle sind als drei Typen klassifiziert, das heißt Speicherzugriffsbefehle, Funktionsbefehle und Sicherheitsbefehle. Speicherzugriffsbefehle sind Befehle zum Zugriff auf den nichtflüchtigen Halbleiterspeicher **17** in der Speicherplatine **1**. Funktionsbefehle sind Befehle zum Zugriff auf unterschiedliche Funktionen auf der Speicherplatine **1**. Sicherheitsbefehle sind Befehle zum Realisieren notwendiger Sicherheitsfunktionen zum Urheberrechts- bzw. Copyrightschutz.

**[0133]** Die Speicherzugriffsbefehle weisen beispielsweise einen Befehl zum Auslesen von Daten aus dem nichtflüchtigen Halbleiterspeicher **17** in die Datenpufferschaltung **14**, einen Befehl zum Schreiben von Daten von der Datenpufferschaltung **14** in den nichtflüchtigen Halbleiterspeicher **17**, einen Befehl zum Löschen von Daten im nichtflüchtigen Halbleiterspeicher **17** usw. auf.

**[0134]** Die Funktionsbefehle umfassen beispielsweise einen Formatierungsbefehl zur Wiederherstellung des Zustands dieser Speicherplatine **1** zur Zeit eines Versands von der Fabrik, einen Schlaf- bzw. Ruhebefehl zum Stoppen der Operation des Oszillators **18** der Speicherplatine **1** usw.

**[0135]** Die Sicherheitsbefehle umfassen beispielsweise einen Befehl zum Auslesen einer für diese Speicherplatine **1** richtigen ID, einen Befehl zur Ausführung einer Operation in Bezug auf das Sperren eines Inhaltschlüssels, einen Befehl zum Erzeugen einer Zufallszahl usw.

**[0136]** [Fig. 17](#) zeigt Beispiele der Speicherzugriffsbefehle.

**[0137]** Wie in [Fig. 17](#) gezeigt umfassen die Speicherzugriffsbefehle READ\_DATA, WRITE\_DATA\_READ\_INFO, WRITR\_INFO, READ\_ATRB, STOP, ERASE usw.

**[0138]** READ\_DATA ist ein Befehl zum kontinuierlichen Auslesen von Daten von einer bezeichneten Adresse in einem Benutzerbereich des nichtflüchtigen Halbleiterspeichers **17**. Wenn dieser READ\_DATA dem Speicher-I/F-Kontroller **16** bereitgestellt wird, bezieht sich der Speicher-I/F-Kontroller **16** auf eine im Daten-Adressen/Revisionszahl-Register gespeicherte Adresse und greift auf diese Adresse im nichtflüchtigen Halbleiterspeicher **17** zu und liest infolgedessen von dieser Adresse Daten aus. Die Auslesedaten werden temporär zur Datenpufferschaltung **14** übertragen. Wenn die Datenpufferschaltung **14** gefüllt ist, das heißt wenn Daten von 512 Bytes ausgelesen sind, validiert (1) der Speicher-I/F-Kontroller **16** das BREQ/PRG-Bit im INT-Register und gibt an die Hosteinrichtung **2** eine Unterbrechung für eine Übertragungsanforderung aus. Wenn dann die Daten in der Datenpufferschaltung **14** von der Hosteinrichtung **2** ausgelesen werden, überträgt der Speicher-I/F-Kontroller **16** die nachfolgenden Daten vom nichtflüchtigen Halbleiterspeicher **17** in die Datenpufferschaltung **14**. Der Speicher-I/F-Kontroller **16** wiederholt die oben beschriebene Verarbeitung, bis er Daten, die mit der im Datenzählungs/Sicherheitsparameter-Register gespeicherten Menge von Daten korrespondieren, ausliest. Wenn die Daten bis zum Ende ohne Fehler ausgelesen werden, validiert (1) der Speicher-I/F-Kontroller **16** das CMD-Bit im INT-Register und beendet die Verarbeitung. Wenn während der Verarbeitung ein Fehler auftritt,

validiert (1) der Speicher-I/F-Kontroller **16** das CMD-Bit im INT-Register und validiert (1) auch das ERR-Bit bis zum Ende der Verarbeitung.

**[0139]** WRITE\_DATA ist ein Befehl zum kontinuierlichen Schreiben der in der Datenpufferschaltung **14** gespeicherten Daten, startend bei einer bezeichneten Adresse im Benutzerbereich des nichtflüchtigen Halbleiterspeichers **17**. Wenn dem Speicher-I/F-Kontroller **16** WRITE\_DATA bereitgestellt wird, bezieht sich der Speicher-I/F-Kontroller **16** auf eine im Datenadressen/Revisionszahl-Register gespeicherte Adresse und greift auf diese Adresse im nichtflüchtigen Halbleiterspeicher **17** zu. Startend bei dieser Adresse schreibt der Speicher-I/F-Kontroller **16** sequentiell Daten. Die zu schreibenden Daten sind Daten, die in der Datenpufferschaltung **14** gespeichert sind.

**[0140]** Wenn die Datenpufferschaltung **14** leer wird, das heißt Daten von 512 Bytes geschrieben sind, validiert (1) der Speicher-I/F-Kontroller **16** das BREQ/PRG-Bit im INT-Register und gibt an die Hosteinrichtung **2** eine Unterbrechung für eine Übertragungsanforderung aus. Wenn die nachfolgenden Daten von der Hosteinrichtung **2** in die Datenpufferschaltung **14** geschrieben werden, schreibt der Speicher-I/F-Kontroller **16** die Daten sequentiell von der Datenpufferschaltung **14** in den nichtflüchtigen Halbleiterspeicher **17**.

**[0141]** Der Speicher-I/F-Kontroller **16** wiederholt die oben beschriebene Verarbeitung, bis er Daten schreibt, die mit der im Datenzählungs/Sicherheitsparameter-Register gespeicherten Menge von Daten korrespondiert. Wenn die Daten bis zum Ende ohne Fehler geschrieben werden, validiert (1) der Speicher-I/F-Kontroller **16** das CMD-Bit im INT-Register und beendet die Verarbeitung. Wenn während der Verarbeitung ein Fehler auftritt, validiert (1) der Speicher-I/F-Kontroller **16** das CMD-Bit im INT-Register und validiert (1) auch das ERR-Bit, um die Verarbeitung zu beenden.

**[0142]** READ\_INFO ist ein Befehl zum kontinuierlichen Auslesen von Daten von einer bezeichneten Adresse im Informationsbuchbereich eines Systembereichs im nichtflüchtigen Halbleiterspeicher **17**. Die vom Speicher-I/F-Kontroller **16** durchzuführende Verarbeitungsprozedur ist die gleiche wie im Fall READ\_DATA.

**[0143]** WIRTE\_INFO ist ein Befehl zum kontinuierlichen Schreiben von Daten in eine bezeichnete Adresse im Informationsbuchbereich (information book area) des Systembereichs im nichtflüchtigen Halbleiterspeicher **17**. Die vom Speicher-I/F-Kontroller **16** durchzuführende Verarbeitungsprozedur ist die gleiche wie im Fall READ\_DATA.

**[0144]** READ\_ATRB ist ein Befehl zum Auslesen von Attributinformation aus dem nichtflüchtigen Halbleiter-speicher **17**. Wenn dieser READ\_ATRB dem Speicher-I/F-Kontroller **16** bereitgestellt wird, liest der Speicher-I/F-Kontroller **16** Attributinformation im nichtflüchtigen Halbleiterspeicher **17** aus und überträgt die Attribu-tinformation zur Datenpufferschaltung **14**.

**[0145]** STOP ist ein Befehl zu Beendigung der Ausführung der Verarbeitung von READ\_DATA, WRITE\_DATA, READ\_INFO, WRITE\_INFO oder READ\_ATRB auf halben Weg. Wenn dem Speicher-I/F-Kontroller **16** STOP bereitgestellt wird, stoppt der Speicher-I/F-Kontroller **16** die Ausführung von READ\_DATA, WRITE\_DATA, READ\_INFO, WRITE\_INFO oder READ\_ATRB.

**[0146]** ERASE ist ein Befehl zum Löschen von Daten von einer bezeichneten Adresse im Benutzerbereich. Wenn ERASE dem Speicher-I/F-Kontroller **16** bereitgestellt wird, bezieht sich der Speicher-I/F-Kontroller **16** auf eine im Daten-Adressen/Revisionszahl-Register gespeicherte Adresse und löscht Daten, die mit der im Datenzählungs/Sicherheitsparameter-Register gespeicherte Menge von Daten korrespondieren, vom nichtflüchtigen Halbleiterspeicher **17**, startend bei der durch die Adresse angezeigten Position.