(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-279682

(P2010-279682A)

(43) 公開日 平成22年12月16日(2010.12.16)

(51) Int.Cl.

**A63F 7/02** (2006.01)

F 1

A 6 3 F 7/02 3 2 6 Z

A 6 3 F 7/02 3 3 4

テーマコード (参考)

2 C 0 8 8

審査請求 未請求 請求項の数 10 O L (全 23 頁)

(21) 出願番号 特願2010-69232 (P2010-69232)

(22) 出願日 平成22年3月25日 (2010.3.25)

(62) 分割の表示 特願2009-132953 (P2009-132953)

の分割

原出願日 平成21年6月2日 (2009.6.2)

(71) 出願人 391010943

株式会社藤商事

大阪府大阪市中央区内本町一丁目1番4号

(74) 代理人 100100376

弁理士 野中 誠一

(72) 発明者 野尻 貴史

大阪府大阪市中央区内本町一丁目1番4号

株式会社藤商事内

(72) 発明者 大川 貴史

大阪府大阪市中央区内本町一丁目1番4号

株式会社藤商事内

F ターム (参考) 2C088 BC56 BC58

## (54) 【発明の名称】遊技機

## (57) 【要約】

【課題】適切なノイズ対策を採用して安定してCPUを動作させること。

【解決手段】遊技動作を中心統括的に制御する主制御部21と、遊技媒体を扱う払出制御部24と、演出動作を実行する演出制御部22, 23と、交流電圧を受けて各制御部で使用される複数種類の直流電圧を生成する電源部20と、を有して構成される。主制御部及び/又は払出制御部には、電源部から受けた複数種類の直流電圧の何れかが異常レベルまで降下すると第一リセット信号RS1を出力してCPU以外の回路素子をリセットする第一回路と、第一リセット信号に基づいて第二リセット信号RS2を出力してCPUをリセットする第二回路と、に区分されたリセット回路RSTが設けられている。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

所定の遊技動作の発生を示す検出信号に起因して抽選処理を実行し、遊技者に有利な遊技状態を発生させるか否かを決定する遊技機であって、

遊技動作を中心統括的に制御する主制御部と、前記主制御部から出力される払出動作用の制御コマンドに基づいて遊技媒体を払出す払出制御部と、前記主制御部から出力される演出動作用の制御コマンドに基づいて演出動作を実行する演出制御部と、交流電圧を受けて前記各制御部で使用される複数種類の直流電圧を生成する電源部と、を有して構成され、

前記主制御部及び／又は前記払出制御部には、

10

前記電源部から受けた複数種類の直流電圧の何れかが異常レベルまで降下すると第一リセット信号を出力してCPU以外の回路素子をリセットする第一回路と、

前記第一リセット信号に基づいて第二リセット信号を出力してCPUをリセットする第二回路と、に区分されたリセット回路が設けられていることを特徴とする遊技機。

**【請求項 2】**

前記電源部から受けた複数種類の直流電圧には、前記主制御部及び／又は前記払出制御部のCPUに供給される電源電圧が含まれている請求項1に記載の遊技機。

**【請求項 3】**

前記第一回路は、前記直流電圧の何れかが異常レベルまで降下しても、所定時間以内に正常レベルに回復した場合には、第一リセット信号を出力しないよう構成されている請求項1又は2に記載の遊技機。

20

**【請求項 4】**

前記第二回路は、前記電源部から受けた自らの電源電圧が、異常レベルまで降下すると、第一リセット信号を受けるか否かに拘らず、第二リセット信号を出力するよう構成されている請求項1～3の何れかに記載の遊技機。

**【請求項 5】**

前記第二回路は、自らの電源電圧が異常レベルまで降下しても、所定時間以内に正常レベルに回復した場合には、第二リセット信号を出力しないよう構成されている請求項4に記載の遊技機。

**【請求項 6】**

第二リセット回路は、ウォッチドッグタイマ機能を有しており、所定時間以上、クリアパルスが途絶えると、第二リセット信号だけが出力されるよう構成されている請求項1～5の何れかに記載の遊技機。

30

**【請求項 7】**

第二リセット回路には、第一リセット信号のレベルに対応してON/OFF動作するスイッチ回路が設けられている請求項1～6の何れかに記載の遊技機。

**【請求項 8】**

前記スイッチ回路がON動作すると、それまで充電状態であったキャパシタンス素子の放電動作が開始されるよう構成されている請求項7に記載の遊技機。

**【請求項 9】**

前記第一リセット信号によりリセットされる回路素子は、データ保持機能を有している請求項1～8の何れかに記載の遊技機。

40

**【請求項 10】**

前記主制御部及び前記払出制御部に供給される直流電圧と、前記演出制御部に供給される直流電圧とは、前記電源部に配置された別々の整流回路の出力電圧に基づいて生成されている請求項1～6の何れかに記載の遊技機。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、弾球遊技機やスロットマシンなど、遊技動作に起因する抽選処理によって大

50

当たり状態を発生させる遊技機に関し、特に、誤動作によるCPUリセットの可能性を抑制した遊技機に関する。

【背景技術】

【0002】

パチンコ機などの弾球遊技機は、電動チューリップや図柄始動口などの遊技部品を配置した遊技盤と、中央開口を有する本体枠とに区分されて構成されている。そして、中央開口に遊技盤を嵌合させることで遊技機が完成状態となる。

【0003】

遊技盤には、複数の表示図柄による一連の図柄変動様を表示する図柄表示部や、開閉板が開閉される大入賞口などが設けられている。そして、図柄始動口に設けられた検出入イッチが遊技球の通過を検出すると入賞状態となり、遊技球が賞球として払出された後、図柄表示部では表示図柄が所定時間変動される。その後、7-7-7などの所定の様で図柄が停止すると大当たり状態となり、大入賞口が繰返し開放されて、遊技者に有利な利益状態を発生させている。

10

【0004】

この種のパチンコ機では、一般に、遊技動作を中心統括的に制御する主制御基板と、主制御基板から出力される払出動作用の制御コマンドに基づいて遊技媒体を払出す払出制御基板と、主制御基板から出力される演出動作用の制御コマンドに基づいて演出動作を実行する演出制御基板と、交流電圧を受けて各制御基板で使用される複数種類の直流電圧を生成する電源基板と、を有して構成されている。

20

【0005】

そして、各制御基板の電源電圧Vccを正確な電圧レベル(5V)に維持するため、電源基板で生成された高レベルの直流電圧(例えば12V)を、各制御基板に配電し、これを受けた制御基板において、電圧レベルを降下させることで、CPUや他のIC素子に供給すべき電源電圧Vcc(=5V)を生成していた(例えば、特許文献1)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009-000434号公報

30

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上記のような構成を採ると、下流側の制御基板と、上流側の制御基板とが、DC12Vの給電ラインを通して接続されることになり、最も重要な主制御基板に対して、下流側制御基板から高周波ノイズが伝送されるおそれがある。また、主制御基板を通して、演出制御基板と払出制御基板の給電ラインも接続状態となるので、下流側制御基板から払出制御基板に対して高周波ノイズが伝送されるおそれもある。そして、伝送された高周波ノイズによって、万一、主制御基板や払出制御基板のCPUが暴走すると、遊技動作や払出動作に異常が生じることになる。

40

【0008】

なお、かかる問題に対処するため、所定レベル(5V)に生成した電源電圧Vccを、電源基板から各制御基板に個々的に給電することも考えられる。しかし、このような構成を採ると、DC5Vの給電ラインを別に設ける分だけ、給電ラインの本数が増加傾向となり、個々の給電ラインの異常に対応できる構成が必要となる。すなわち、特定の給電ラインだけに異常が生じた場合にも、適切に対応できる構成が必要となる。

【0009】

また、各IC素子の電源端子は、比較的長いDC5Vの給電ラインを通して、電源基板に接続されるので、スパイクノイズなどによって直流電圧の供給が一瞬だけ途絶える可能性も否定できず、このような瞬間的な異常時にも適切に対応できる過敏に過ぎない構成が必要となる。

50

**【0010】**

本発明は、上記の問題点に鑑みてなされたものであって、適切なノイズ対策を採用して安定してCPUを動作させることができる遊技機を提供することを目的とする。

**【課題を解決するための手段】****【0011】**

上記の目的を達成するため、本発明は、所定の遊技動作の発生を示す検出信号に起因して抽選処理を実行し、遊技者に有利な遊技状態を発生させるか否かを決定する遊技機であって、遊技動作を中心統括的に制御する主制御部と、前記主制御部から出力される払出動作の制御コマンドに基づいて遊技媒体を払出す払出制御部と、前記主制御部から出力される演出動作の制御コマンドに基づいて演出動作を実行する演出制御部と、交流電圧を受けて前記各制御部で使用される複数種類の直流電圧を生成する電源部と、を有して構成され、前記主制御部及び／又は前記払出制御部には、前記電源部から受けた複数種類の直流電圧の何れかが異常レベルまで降下すると第一リセット信号を出力してCPU以外の回路素子をリセットする第一回路と、前記第一リセット信号に基づいて第二リセット信号を出力してCPUをリセットする第二回路と、に区分されたリセット回路が設けられていることを特徴とする。10

**【0012】**

本発明では、複数種類の直流電圧の何れかが異常レベルまで降下すると、これに対応してCPUなどの回路素子がリセットされるので、給電ラインの本数を増加させても、個々の給電ラインの異常に適切に対応できる。また、本発明では、CPUへのリセット信号と、その他の回路素子へのリセット信号を別々に生成するので、CPUの特性に対応した最適なリセット時間その他を確保することができる。20

**【0013】**

前記電源部から受ける複数種類の直流電圧には、好ましくは、前記主制御部及び／又は前記払出制御部のCPUに供給される電源電圧が含まれている。

**【0014】**

前記第一回路は、前記直流電圧の何れかが異常レベルまで降下しても、所定時間以内に正常レベルに回復した場合には、第一リセット信号を出力しないよう構成されているのが好ましく、この場合には過敏な反応を抑制できる。

**【0015】**

前記第二回路は、好ましくは、前記電源部から受けた自らの電源電圧が、異常レベルまで降下すると、第一リセット信号を受けるか否かに拘らず、第二リセット信号を出力するよう構成されている。ここで、第二回路は、自らの電源電圧が異常レベルまで降下しても、所定時間以内に正常レベルに回復した場合には、第二リセット信号を出力しないよう構成するのが過敏な反応を抑制する上で好適である。30

**【0016】**

第二リセット回路は、ウォッチドッグタイマ機能を有しており、所定時間以上、クリアパルスが途絶えると、第二リセット信号だけが出力されるよう構成されているのが好ましい。また、第二リセット回路には、第一リセット信号のレベルに対応してON/OFF動作するスイッチ回路が設けられているのが好適である。この場合、前記スイッチ回路がON動作すると、それまで充電状態であったキャパシタンス素子の放電動作が開始されるよう構成されるのが効果的である。40

**【0017】**

前記第一リセット信号によりリセットされる回路素子は、好ましくは、データ保持機能を有している。また、前記主制御部及び前記払出制御部に供給される直流電圧と、前記演出制御部に供給される直流電圧とは、前記電源部に配置された別々の整流回路の出力電圧に基づいて生成されるのが効果的である。

**【発明の効果】****【0018】**

上記した本発明によれば、適切なノイズ対策を採用して安定してCPUを動作させるこ50

とができる遊技機を実現することができる。

**【図面の簡単な説明】**

**【0019】**

【図1】実施例に示すパチンコ機の斜視図である。

【図2】図1のパチンコ機の遊技盤を詳細に図示した正面図である。

【図3】図1のパチンコ機の全体構成を示すブロック図である。

【図4】電源基板の回路構成を示す回路図である。

【図5】主制御部と払出制御部のリセット回路の回路図である。

【図6】電源監視部とリセット回路の動作を示すタイムチャートである。

10

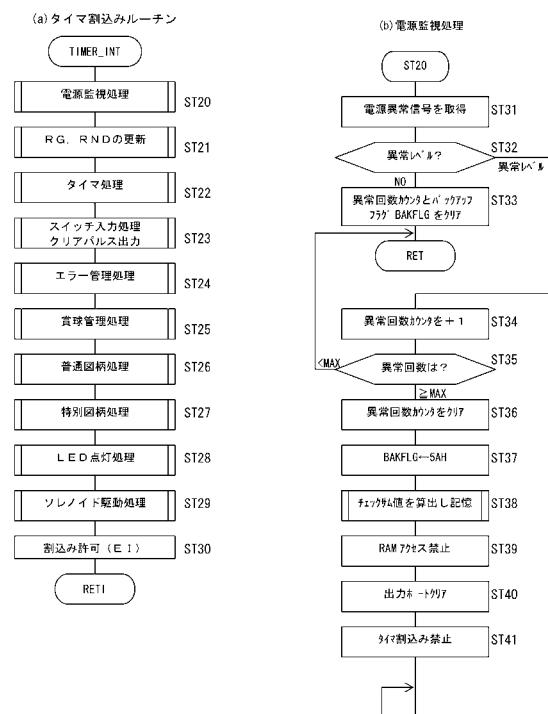

【図7】主制御部のシステムリセット処理を説明するフローチャートである。

【図8】主制御部のタイマ割込み処理を説明するフローチャートである。

**【発明を実施するための形態】**

**【0020】**

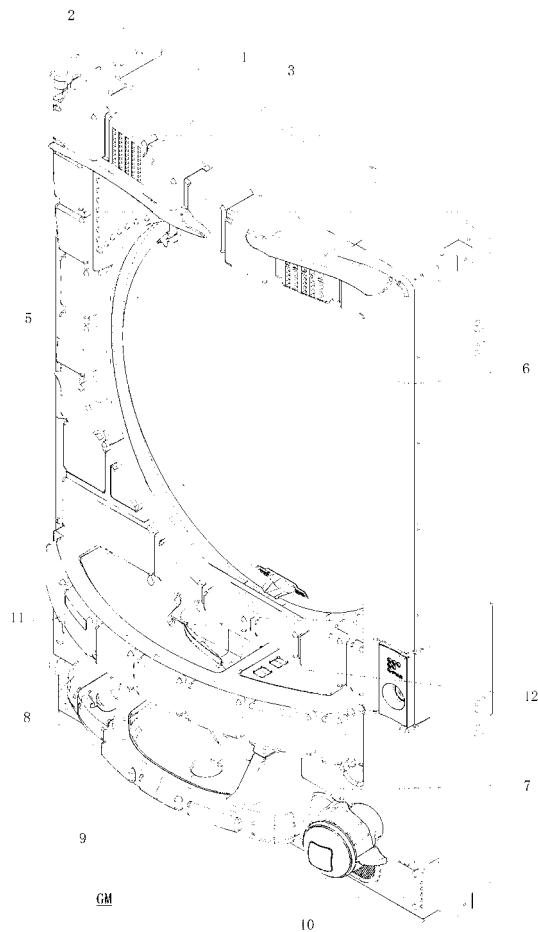

以下、本発明の実施例について詳細に説明する。図1は、本実施例のパチンコ機GMを示す斜視図である。このパチンコ機GMは、島構造体に着脱可能に装着される矩形枠状の木製外枠1と、外枠1に固着されたヒンジ2を介して開閉可能に枢着される前枠3とで構成されている。この前枠3には、遊技盤5が、裏側からではなく表側から着脱自在に装着され、その前側には、ガラス扉6と前面板7とが夫々開閉自在に枢着されている。

**【0021】**

ガラス扉6の外周には、LEDランプなどによる電飾ランプが、略C字状に配置されている。前面板7には発射用の遊技球を貯留する上皿8が装着され、前枠3の下部には、上皿8から溢れ出し又は抜き取った遊技球を貯留する下皿9と、発射ハンドル10とが設けられている。発射ハンドル10は発射モータと連動しており、発射ハンドル10の回動角度に応じて動作する打撃槌によって遊技球が発射される。

20

**【0022】**

上皿8の外周面には、チャンスボタン11が設けられている。このチャンスボタン11は、遊技者の左手で操作できる位置に設けられており、遊技者は、発射ハンドル10から右手を離すことなくチャンスボタン11を操作できる。このチャンスボタン11は、通常時には機能していないが、ゲーム状態がボタンチャンス状態となると内蔵ランプが点灯されて操作可能となる。なお、ボタンチャンス状態は、必要に応じて設けられるゲーム状態である。

30

**【0023】**

上皿8の右部には、カード式球貸し機に対する球貸し操作用の操作パネル12が設けられ、カード残額を3桁の数字で表示する度数表示部と、所定金額分の遊技球の球貸しを指示する球貸しスイッチと、ゲーム終了時にカードの返却を指令する返却スイッチとが設けられている。

30

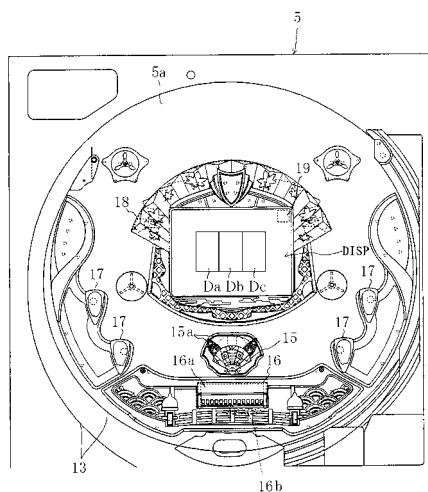

**【0024】**

図2に示すように、遊技盤5には、金属製の外レールと内レールとからなるガイドレール13が環状に設けられ、その内側の遊技領域5aの略中央には、液晶カラーディスプレイである表示装置DISPが配置されている。また、遊技領域5aの適所には、図柄始動口15、大入賞口16、複数個の普通入賞口17（大入賞口16の左右に4つ）、通過口であるゲート18が配設されている。これらの入賞口15～18は、それぞれ内部に検出スイッチを有しており、遊技球の通過を検出できるようになっている。

40

**【0025】**

表示装置DISPは、大当たり状態に係わる特定図柄を変動表示すると共に背景画像や各種のキャラクタなどをアニメーション的に表示する。この表示装置DISPは、中央部に特別図柄表示部Da～Dcと右上部に普通図柄表示部19を有している。そして、特別図柄表示部Da～Dcでは、大当たり状態の招来を期待させるリーチ演出が実行されたり、特別図柄表示部Da～Dc及びその周りでは、当否結果を不確定に報知する予告演出などが実行される。

50

## 【0026】

普通図柄表示部19は普通図柄を表示するものであり、ゲート18を通過した遊技球が検出されると、普通図柄が所定時間だけ変動し、遊技球のゲート18の通過時点において抽出された抽選用乱数値により決定される停止図柄を表示して停止するようになっている。

## 【0027】

図柄始動口15は、左右1対の開閉爪15aを備えた電動式チューリップで開閉されるよう例えれば構成され、普通図柄表示部19の変動後の停止図柄が当り図柄を表示した場合には、開閉爪15aが所定時間だけ、若しくは、所定個数の遊技球を検出するまで開放されるようになっている。

10

## 【0028】

図柄始動口15に遊技球が入賞すると、特別図柄表示部D<sub>a</sub>～D<sub>c</sub>の表示図柄が所定時間だけ変動し、図柄始動口15への遊技球の入賞タイミングに応じた抽選結果に基づいて決定される停止図柄で停止する。なお、特別図柄表示部D<sub>a</sub>～D<sub>c</sub>及びその周りでは、一連の図柄演出の間に、予告演出が実行される場合がある。

## 【0029】

大入賞口16は、例えは前方に開放可能な開閉板16aで開閉制御されるが、特別図柄表示部D<sub>a</sub>～D<sub>c</sub>の図柄変動後の停止図柄が「777」などの大当たり図柄のとき、「大当たりゲーム」と称する特別遊技が開始され、開閉板16aが開放されるようになっている。

20

## 【0030】

大入賞口16の開閉板16aが開放された後、所定時間が経過し、又は所定数（例えは10個）の遊技球が入賞すると開閉板16aが閉じる。このような動作は、最大で例えは15回まで特別遊技が継続され、遊技者に有利な状態に制御される。なお、特別図柄表示部D<sub>a</sub>～D<sub>c</sub>の変動後の停止図柄が特別図柄のうちの特定図柄であった場合には、特別遊技の終了後のゲームが高確率状態となるという特典が付与される。

## 【0031】

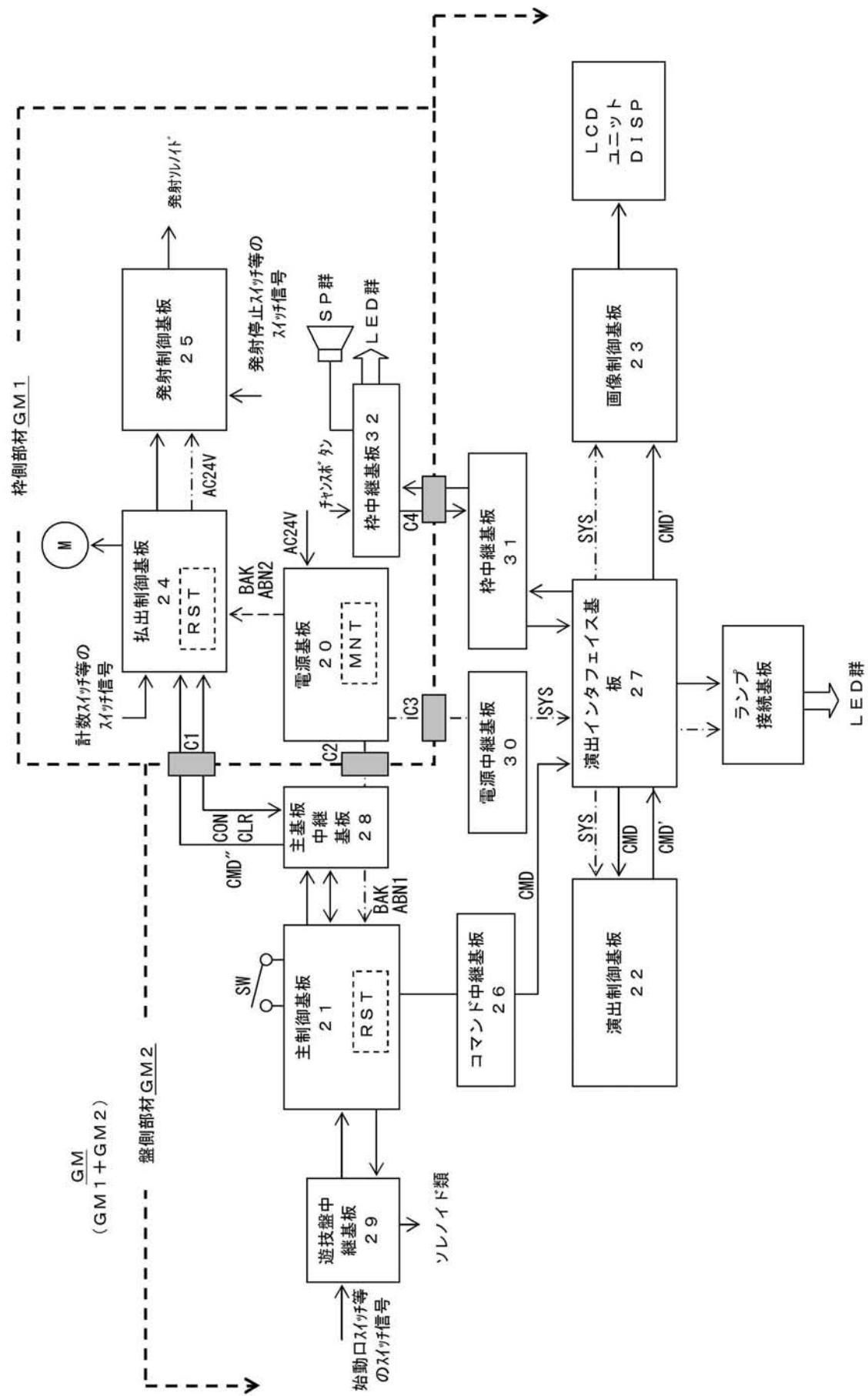

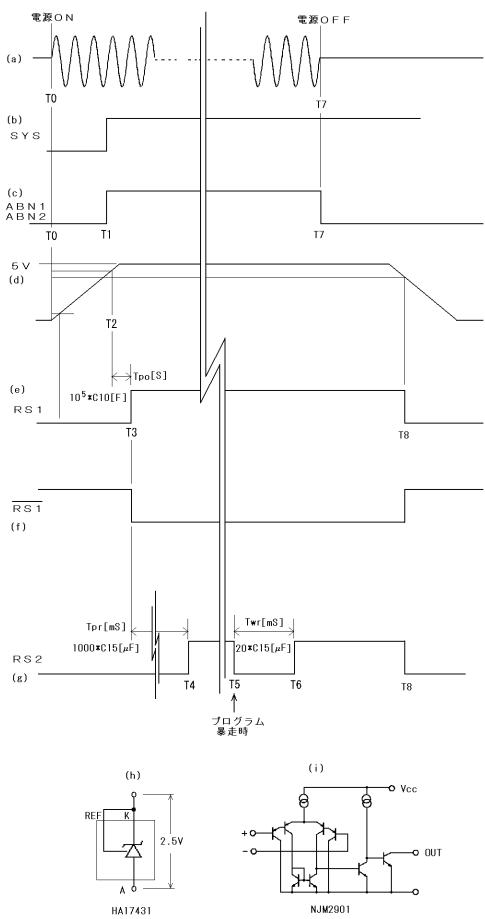

図3は、上記した各動作を実現するパチンコ機GMの全体回路構成を示すブロック図である。図中の一点破線は、主に、直流電圧ラインを示している。

## 【0032】

図示の通り、このパチンコ機GMは、AC24Vを受けて各種の直流電圧や、電源異常信号ABN1、ABN2やシステムリセット信号（電源リセット信号）SYSなどを出力する電源基板20と、遊技制御動作を中心統括的に担う主制御基板21と、主制御基板21から受けた制御コマンドCMDに基づいてランプ演出及び音声演出を実行する演出制御基板22と、演出制御基板22から受けた制御コマンドCMD'に基づいて表示装置DISPを駆動する画像制御基板23と、主制御基板21から受けた制御コマンドCMD"に基づいて払出モータMを制御して遊技球を払い出す払出制御基板24と、遊技者の操作に応答して遊技球を発射させる発射制御基板25と、を中心に構成されている。

30

## 【0033】

但し、この実施例では、主制御基板21が出力する制御コマンドCMDは、コマンド中継基板26と演出インターフェイス基板27を経由して、演出制御基板22に伝送される。また、演出制御基板22が出力する制御コマンドCMD'は、演出インターフェイス基板27を経由して、画像制御基板23に伝送され、主制御基板21が出力する制御コマンドCMD"は、主基板中継基板28を経由して、払出制御基板24に伝送される。

40

## 【0034】

これら主制御基板21、演出制御基板22、画像制御基板23、及び払出制御基板24には、ワンチップマイコンを備えるコンピュータ回路がそれぞれ搭載されている。そこで、これらの制御基板21～24に搭載された回路、及びその回路によって実現される動作を機能的に総称して、本明細書では、主制御部21、演出制御部22、画像制御部23、及び払出制御部24と言うことがある。なお、演出制御部22、画像制御部23、及び払出制御部24の全部又は一部がサブ制御部である。

50

## 【0035】

ところで、このパチンコ機GMは、図3の破線で囲む枠側部材GM1と、遊技盤5の背面に固定された盤側部材GM2とに大別されている。枠側部材GM1には、ガラス扉6や前面板7が枢着された前枠3と、その外側の木製外枠1とが含まれており、機種の変更に拘わらず、長期間にわたって遊技ホールに固定的に設置される。一方、盤側部材GM2は、機種変更に対応して交換され、新たな盤側部材GM2が、元の盤側部材の代わりに枠側部材GM1に取り付けられる。なお、枠側部材1を除く全てが、盤側部材GM2である。

## 【0036】

図3の破線枠に示す通り、枠側部材GM1には、電源基板20と、払出制御基板24と、発射制御基板25と、枠中継基板32とが含まれており、これらの回路基板が、前枠3の適所に各々固定されている。一方、遊技盤5の背面には、主制御基板21、演出制御基板22、画像制御基板23が、表示装置DISPやその他の回路基板と共に固定されている。そして、枠側部材GM1と盤側部材GM2とは、一箇所に集中配置された接続コネクタC1～C4によって電気的に接続されている。

10

## 【0037】

電源基板20は、接続コネクタC2を通して、主基板中継基板28に接続され、接続コネクタC3を通して、電源中継基板30に接続されている。そして、主基板中継基板28は、電源基板20から受けた電源異常信号ABN1、バックアップ電源BAK、及びDC5V, DC12V, DC32Vを、そのまま主制御部21に出力している。一方、電源中継基板30は、電源基板20から受けたシステムリセット信号SYSや、交流及び直流の電源電圧を、そのまま演出インターフェイス基板27に出力している。なお、演出インターフェイス基板27は、受けたシステムリセット信号SYSを、そのまま演出制御部22と画像制御部23に出力している。

20

## 【0038】

一方、払出制御基板24は、中継基板を介することなく、電源基板20に直結されており、主制御部21が受けると同様の電源異常信号ABN2や、バックアップ電源BAKを、他の電源電圧と共に直接的に受けている。

## 【0039】

電源基板20が出力するシステムリセット信号SYSは、電源基板20に交流電源24Vが投入されたことを示す電源リセット信号であり、この電源リセット信号によって演出制御部22と画像制御部23のワンチップマイコンは、他のIC素子と共に電源リセットされるようになっている。

30

## 【0040】

但し、このシステムリセット信号SYSは、主制御部21と払出制御部24には、供給されておらず、各々の回路基板21, 24のリセット回路\_RSTにおいて電源リセット信号(CPUリセット信号)が生成されている。そのため、例えば、接続コネクタC2がガタついたり、或いは、配線ケーブルにノイズが重畠しても、主制御部21や払出制御部24のCPUが異常リセットされるおそれはない。なお、演出制御部22と画像制御部23は、主制御部21からの制御コマンドに基づいて、従属的に演出動作を実行することから、回路構成の複雑化を回避するために、電源基板20から出力されるシステムリセット信号SYSを利用している。

40

## 【0041】

また、この実施例では、RAMクリア信号CLRは、主制御部21で生成されて主制御部21と払出制御部24のワンチップマイコンに伝送されている。ここで、RAMクリア信号CLRは、各制御部21, 24のワンチップマイコンの内蔵RAMの全領域を初期設定するか否かを決定する信号であって、係員が操作する初期化スイッチSWのON/OFF状態に対応した値を有している。

## 【0042】

主制御部21及び払出制御部24が、電源基板20から受ける電源異常信号ABN1, ABN2は、交流入力電源AC24Vが降下し始めたことを示す信号であり、この電源異

50

常信号 A B N 1 , A B N 2 を受けることによって、各制御部 2 1 、 2 4 では、停電や営業終了に先立って、必要な終了処理を開始するようになっている。また、バックアップ電源 B A K は、営業終了や停電により交流電源 2 4 V が遮断された後も、主制御部 2 1 と払出制御部 2 4 のワンチップマイコンの内蔵 R A M のデータを保持する D C 5 V の直流電源である。したがって、主制御部 2 1 と払出制御部 2 5 は、電源遮断前の遊技動作を電源投入後に再開できることになる（電源バックアップ機能）。このパチンコ機では少なくとも数日は、各ワンチップマイコンの R A M の記憶内容が保持されるよう設計されている。

#### 【 0 0 4 3 】

図 3 に示す通り、主制御部 2 1 は、主基板中継基板 2 8 を経由して、払出制御部 2 5 に制御コマンド C M D ”を送信する一方、払出制御部 2 5 からは、遊技球の払出動作を示す賞球計数信号や、払出動作の異常に係わるステータス信号 C O N を受信している。ステータス信号 C O N には、例えば、補給切れ信号、払出不足エラー信号、下皿満杯信号が含まれる。

10

#### 【 0 0 4 4 】

また、主制御部 2 1 は、遊技盤中継基板 2 9 を経由して、遊技盤 5 の各遊技部品に接続されている。そして、遊技盤上の各入賞口 1 6 ~ 1 8 に内蔵された検出スイッチのスイッチ信号を受ける一方、電動チューリップなどのソレノイド類を駆動している。ソレノイド類や検出スイッチは、主制御部 2 1 から給電された電源電圧 V B ( 1 2 V ) で動作するよう構成されている。そして、図柄始動口 1 5 への入賞状態などを示す各スイッチ信号は、電源電圧 V B ( 1 2 V ) と電源電圧 V c c ( 5 V ) とで動作するインタフェース I C で、T T L レベルのスイッチ信号に変換された上で、主制御部 2 1 に伝送される。

20

#### 【 0 0 4 5 】

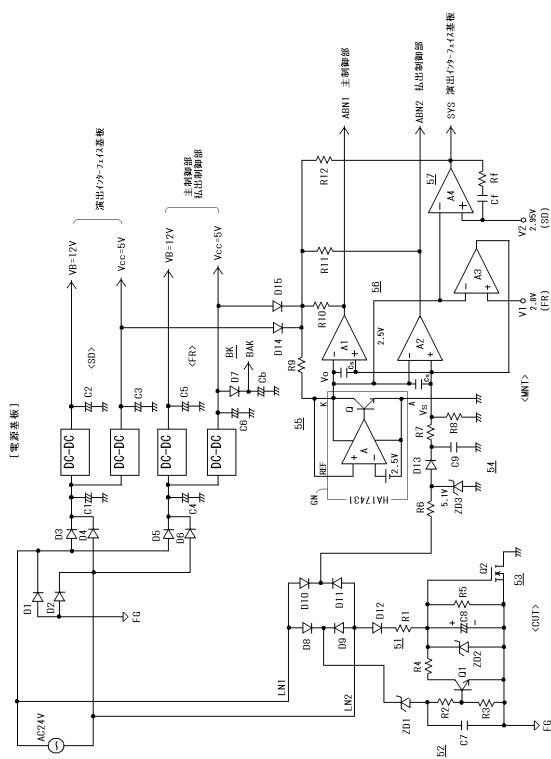

図 4 は、電源基板 2 0 の電源回路を示す回路図である。この電源回路は、演出インターフェイス基板 2 7 に供給される直流電圧を生成する第二電源部 S D と、主制御部 2 1 と払出制御部 2 4 に供給される直流電圧を生成する第一電源部 F R と、電源投入と電源遮断とを監視する電源監視部 M N T と、過大な交流電圧を受けるとグランドラインを遮断する電源遮断部 C U T と、を有して構成されている。なお、払出制御部 2 4 に供給される他の直流電圧 ( D C 3 2 V ) や、演出インターフェイス基板 2 7 に供給される他の直流電圧 ( D C 3 2 V , D C 1 5 V ) については、図示を省略している。

30

#### 【 0 0 4 6 】

##### < 第二電源部 S D >

第二電源部 S D は、ダイオード D 1 ~ D 4 による全波整流回路と、平滑コンデンサ C 1 と、直流電圧 V B ( 1 2 V ) を生成する D C - D C コンバータと、直流電圧 V c c ( 5 V ) を生成する D C - D C コンバータと、平滑コンデンサ C 2 , C 3 とを有して構成されている。2つの D C - D C コンバータは、何れもチョッパ型であり、平滑コンデンサ C 1 を共通的に受けて動作している。第二電源部 S D で生成された直流電圧は、演出インターフェイス基板 2 7 に伝送された後、適宜に降圧されて、演出インターフェイス基板 2 7 と、演出制御基板 2 2 と、画像制御基板 2 3 とで使用される。

#### 【 0 0 4 7 】

##### < 第一電源部 F R >

第一電源部 F R は、ダイオード D 1 , D 2 , D 5 , D 6 による全波整流回路と、平滑コンデンサ C 4 と、直流電圧 V B ( 1 2 V ) を生成する D C - D C コンバータと、直流電圧 V c c ( 5 V ) を生成する D C - D C コンバータと、平滑コンデンサ C 5 , C 6 と、ダイオード D 7 及びコンデンサ C b とで構成された蓄電部 B K とを有して構成されている。この2つの D C - D C コンバータも、チョッパ型であり、平滑コンデンサ C 4 を共通的に受けて動作している。また、蓄電部 B K で生成された直流電圧は、主制御部 2 1 と払出制御部 2 4 のワンチップマイコンの内蔵 R A M のデータを保持するバックアップ電源 B A K となる。

40

#### 【 0 0 4 8 】

第一電源部 F R で生成された直流電圧 V B と直流電圧 V c c は、主制御部 2 1 と払出制

50

御部24だけに供給されており、演出インターフェイス基板27に伝送される直流電圧とは配線上で区別されている。そのため、主制御部21や派出制御部24が、他のサブ制御部22, 23と電源ラインを経由して接続されることはなく、高周波ノイズなどの伝送が阻止される。

#### 【0049】

なお、主制御部21や派出制御部24での総電流は、最大でも、電源電圧VBラインで600mAを超えることがなく、また、電源電圧Vccラインでも300mAを超えることがないので、各電源電圧VB, Vccの給電ラインの電圧降下は、全く問題にならない。

#### 【0050】

<電源遮断部CUT>

電源遮断部CUTは、交流電圧AC24Vから所定レベルの直流電圧を生成する整流部51と、交流電源ラインLN1, LN2の過電圧時にON動作する交流監視部52と、交流監視部52のON動作に対応してOFF動作するスイッチ回路53と、を有して構成されている。

#### 【0051】

整流部51は、交流電源ラインLN2から交流電圧を受けるダイオードD12と、電流制限抵抗R1と、コンデンサC8及びツエナーダイオードZD2の並列回路と、が直列に接続されて構成されている。そして、正常時には、コンデンサC8の両端電圧は、ツエナーダイオードZD2の降伏電圧に一定化されている。

#### 【0052】

スイッチ回路53は、大電流容量のMOSトランジスタQ2と、コンデンサC8に並列接続されたバイアス抵抗R5と、を有して構成されている。ここで、トランジスタQ2は、コンデンサC8の両端電圧が所定レベルである限り、ON状態であって、遊技機の全回路のグランドラインとフレームグランドFGとを接続状態にしている。

#### 【0053】

交流監視部52は、交流電源ラインLN1, LN2に接続された2つのダイオードD8, D9と、ダイオードD8, D9の接続点に接続されたツエナーダイオードZD1と、バイアス抵抗R2, R3及びコンデンサC7の並列回路と、バイアス抵抗R3の両端電圧が上昇するとON動作するトランジスタQ1と、トランジスタQ1の電流制限抵抗R4とを有して構成されている。

#### 【0054】

ツエナーダイオードZD1は、通常は、OFF状態であるが、交流電源ラインLN1, LN2に過大な交流電圧（例えばAC100V）が加わると、降伏状態となる。この降伏状態では、バイアス抵抗R3の両端電圧が上昇してトランジスタQ1がON動作することでコンデンサC8の両端電圧が降下する。

#### 【0055】

すると、それまでON状態であったトランジスタQ2がOFF遷移することで、回路グランドとフレームグランドFGとが非接続となって、全ての遊技機の全ての電源電圧が遮断状態となる。電源遮断部CUTの動作内容は、以上の通りであり、交流電源ラインLN1, LN2の両端電圧が限界値を超えると、全ての遊技機の全ての電源電圧を一気に遮断する機能を果たしている。

#### 【0056】

<電源監視部MNT>

次に、電源監視部MNTについて説明する。電源監視部MNTは、交流電源ラインLN1, LN2の電圧レベルを監視する給電監視部54と、電源電圧Vccを受けて比較基準電圧Voを出力する比較電圧部55と、給電監視部54と比較電圧部55の出力電圧を対比して電源異常を検出する異常検出部56と、システムリセット信号SYSを生成する電源リセット部57と、を有して構成されている。

#### 【0057】

10

20

30

40

50

[ 給電監視部 5 4 ]

給電監視部 5 4 は、交流電源ライン L N 1 , L N 2 に接続された 2 つのダイオード D 1 0 , D 1 1 と、ダイオード D 1 0 , D 1 1 の接続点に接続された抵抗 R 6 及びツェナーダイオード Z D 3 の直列回路と、ツェナーダイオード Z D 3 に並列接続されたダイオード D 1 3 及び平滑コンデンサ C 9 の直列回路と、平滑コンデンサ C 9 に並列接続された抵抗 R 7 , R 8 の直列回路と、抵抗 R 8 を短絡させるコンパレータ A 3 と、を有して構成されている。

【 0 0 5 8 】

この実施例では、ツェナーダイオード Z D 3 の降伏電圧が 5 . 1 V 程度であり、ツェナーダイオード Z D 3 は、電流制限抵抗 R 6 を通して、交流電圧 A C 2 4 V を受けている。そのため、交流入力電源の給電状態であれば、平滑コンデンサ C 9 の両端電圧は、4 . 5 V 程度の一定値となる。また、2 つの抵抗 R 7 , R 8 は、その抵抗値が  $R_8 >> R_7$  に設定されているので、抵抗 R 8 の両端電圧  $V_s$  は、正常レベルの交流電圧 A C 2 4 V に対応して約 4 . 5 V となる。但し、コンパレータ A 3 の出力が L レベルであると、これに対応して、抵抗 R 8 の両端電圧  $V_s$  は、ほぼ 0 V となる。なお、抵抗 R 7 は、L レベル出力時のコンパレータ A 3 に対する電流制限抵抗として機能する。

【 0 0 5 9 】

コンパレータ A 3 は、他のコンパレータ A 1 ~ A 4 と共に、Q U A D コンパレータ ( N J M 2 9 0 1 ) で構成されている。この Q U A D コンパレータには、4 つのコンパレータ A 1 ~ A 4 が内蔵されているが、何れのコンパレータ A 1 ~ A 4 も、オープンコレクタタイプとなっている ( 図 6 ( i ) 参照 ) 。

【 0 0 6 0 】

そして、コンパレータ A 3 のマイナス端子には、比較電圧部 5 5 の出力電圧  $V_o$  が供給され、プラス端子には、定常状態では 2 . 8 V 程度の比較電圧  $V_1$  が供給されている。この比較電圧  $V_1$  は、第一電源部 F R が生成した二種類の電源電圧  $V_{c c}$  ,  $V_B$  を抵抗で分圧して生成されている。

【 0 0 6 1 】

後述するように、電源投入時には、比較電圧部 5 5 の出力電圧  $V_o$  は、レベル上昇中の電源電圧  $V_{c c}$  に対応したレベルとなる ( $V_o = V_{c c} - V_f$  ) 。なお、 $V_f$  とは、ダイオード D 1 4 , D 1 5 と、抵抗 R 9 における電圧降下である。

【 0 0 6 2 】

一方、比較電圧  $V_1$  は、電源電圧  $V_{c c}$  ,  $V_B$  を分圧して生成されるので、電源投入直後は、比較電圧部 5 5 の出力電圧  $V_o$  より低い。そのため、電源投入直後の過渡状態では、コンパレータ A 3 の出力が L レベルとなって抵抗 R 8 を短絡させ、その結果、給電監視部 5 4 の出力電圧  $V_s$  がほぼ 0 V となる。

【 0 0 6 3 】

一方、電源電圧  $V_{c c}$  ,  $V_B$  が所定レベルに達した定常状態では、比較電圧  $V_1$  が、2 . 8 V 程度となる一方、比較電圧部 5 5 の出力電圧  $V_o$  は 2 . 5 V 程度に一定化される。つまり、コンパレータ A 3 は、[ プラス入力への入力電圧 ] > [ マイナス端子への入力電圧 ] の大小関係となるが、コンパレータ A 3 の出力部がオープンコレクタであり ( 図 6 ( i ) 参照 ) 、図 4 に示す通り、その出力端子がプルアップされていないので、コンパレータ A 3 の出力部は開放状態となって他の回路に影響を与えない。

【 0 0 6 4 】

以上説明した給電監視部 5 4 の動作を整理すると以下の通りである。

( 1 ) 交流電圧 A C 2 4 V が投入された電源投入直後は、抵抗 R 8 がコンパレータ A 3 の出力部によって短絡されるので、抵抗 R 8 の両端電圧  $V_s$  がほぼ 0 V となる。

( 2 ) その後、電源電圧  $V_{c c}$  が正常レベル近くまで増加すると、コンパレータ A 3 の出力部が開放状態となるので、抵抗 R 8 の両端電圧  $V_s$  は、ツェナーダイオード Z D 3 の両端電圧に対応してほぼ 4 . 5 V となる。

( 3 ) 交流電圧 A C 2 4 V が遮断状態となると、抵抗 R 8 の両端電圧  $V_s$  は、素早く 0 V

10

20

30

40

50

まで降下する。しかし、交流電圧 A C 2 4 V が遮断されても、しばらくは、電源電圧 V c c , V B が所定レベルを維持するので、コンパレータ A 3 の出力部は、そのまま開放状態を維持する。

#### 【 0 0 6 5 】

##### [ 比較電圧部 5 5 ]

比較電圧部 5 5 は、第一電源部 F R と第二電源部 S D とで別々に生成された 2 つの電源電圧 V c c , V c c を各アノード端子に受けるダイオード D 1 4 , D 1 5 と、ダイオード D 1 4 , D 1 5 の各カソード端子に接続される電流制限抵抗 R 9 と、電圧生成部 G N と、が直列に接続されて構成されている。この実施例では、電圧生成部 G N として、シャントレギュレータ ( H A 1 7 4 3 1 : R E N E S A S ) を使用している。

10

#### 【 0 0 6 6 】

このシャントレギュレータは、アノード端子 A とカソード端子 K と比較端子 R E F とを有するが、アノード端子 A とカソード端子 K とを接続した図示の状態では、ツェナーダイオードと同等に機能して、降伏動作時には、アノード・カソード端子間に一定の基準電圧 V o ( 2 . 5 V ) を出力する ( 図 6 ( h ) 参照 ) 。一方、非降伏動作時には、内部回路が O F F 動作して、アノード・カソード端子間が開放状態となる。

#### 【 0 0 6 7 】

したがって、電源投入時、電源電圧 V c c が所定レベルに達するまでは、比較電圧部 5 5 ( 電圧生成部 G N ) の出力電圧 V o は、レベル上昇中の電源電圧 V c c に対応して、 V o = V c c - V f - となる。一方、電源電圧 V c c が所定レベルに達すると、比較電圧部 5 5 の出力電圧 V o は、一定の比較基準電圧 ( 2 . 5 V ) となる。

20

#### 【 0 0 6 8 】

##### [ 異常検出部 5 6 ]

異常検出部 5 6 は、主制御部 2 1 への電源異常信号 A B N 1 を生成するコンパレータ A 1 と、派出制御部 2 4 への電源異常信号 A B N 2 を生成するコンパレータ A 2 と、各コンパレータ A 1 , A 2 のプルアップ抵抗 R 1 0 , R 1 1 と、各コンパレータ A 1 , A 2 の入力端子間に接続されたコンデンサ C s とを有して構成されている。各コンパレータ A 1 , A 2 のマイナス端子には、比較電圧部 5 5 の出力電圧 V o が供給され、プラス端子には、抵抗 R 8 の両端電圧 V s が供給されている。なお、コンパレータ A 1 , A 2 は、先に説明した Q U A D コンパレータ ( N J M 2 9 0 1 ) に内蔵されている。

30

#### 【 0 0 6 9 】

図示を省略しているが、コンパレータ A 1 , A 2 から出力される電源異常信号 A B N 1 、 A B N 2 は、主制御部 2 1 と派出制御部 2 4 の入力ポートに供給されている。そして、各入力ポートの入力端子とグランド間には、適宜なコンデンサを接続されており、各入力ポートが、適宜な抵抗を経由して電源異常信号を受けることで耐ノイズ性を確保している。また、適宜なソフトウェア処理 ( 図 8 の S T 3 4 ~ S T 3 5 ) によって、スパイクノイズの影響を排除している。

#### 【 0 0 7 0 】

給電監視部 5 4 が前記した ( 1 ) ~ ( 3 ) の通りに動作するので、これに対応して異常検出部 5 6 は、以下の通りに動作する。

40

#### 【 0 0 7 1 】

( 1 ) 交流電圧 A C 2 4 V が投入された電源投入直後は、抵抗 R 8 の両端電圧 V s がほぼ 0 V であり、一方、比較電圧部 5 5 の出力電圧 V o は、レベル上昇中の電源電圧 V c c に対応して、 V c c - V f - となる。そのため、コンパレータ A 1 , A 2 が出力する電源異常信号 A B N 1 , A B N 2 は、レベル変動することなく、 L レベルを安定的に維持する。図 6 ( c ) のタイミング T 0 ~ T 1 は、この電源投入時の安定した L レベル状態を示している。

#### 【 0 0 7 2 】

( 2 ) その後、レベル上昇中の電源電圧 V c c が所定レベルを超えた後は、比較電圧部 5 5 の出力電圧 V o は、 2 . 5 V を維持する。また、電源電圧 V c c が正常レベル近くま

50

で増加すると、コンパレータ A 3 の出力部が開放状態となるので、抵抗 R 8 の両端電圧 V<sub>s</sub> は、ツエナーダイオード Z D 3 の両端電圧に対応してほぼ 4 . 5 V となる。

#### 【 0 0 7 3 】

そのため、コンパレータ A 1 , A 2 が出力する電源異常信号 A B N 1 , A B N 2 が H レベルに遷移して、その後は、正常状態を示す H レベルを定的に維持する。図 6 ( c ) のタイミング T 1 以降は、正常レベルの電源異常信号 A B N 1 , A B N 2 を示している。

#### 【 0 0 7 4 】

( 3 ) その後、何らかの理由で交流電圧 A C 2 4 V が遮断状態となると、抵抗 R 8 の両端電圧 V<sub>s</sub> は、素早く 0 V まで降下する。しかし、電源電圧 V<sub>c c</sub> , V<sub>B</sub> は、しばらく所定レベルを維持するので、コンパレータ A 3 や比較電圧部 5 5 は、それまでの動作を維持する。

10

#### 【 0 0 7 5 】

したがって、図 6 ( a ) のタイミング T 7 において、交流電圧 A C 2 4 V が遮断状態になると、コンパレータ A 1 , A 2 が出力する電源異常信号 A B N 1 , A B N 2 は、直ちに、H レベルから L レベルに遷移して異常事態の発生を示す。なお、主制御部 2 1 と派出制御部 2 4 では、この電源異常信号 A B N 1 , A B N 2 を定期的にチェックしており、電源異常信号 A B N 1 , A B N 2 が L レベルに遷移したことを確認すると、直ちにバックアップ処理を開始するようになっている。

#### 【 0 0 7 6 】

##### [ 電源リセット部 5 7 ]

次に、コンパレータ A 4 で構成された電源リセット部 5 7 について説明する。図示の通り、コンパレータ A 4 の出力端子には、プルアップ抵抗 R 1 2 が接続され、出力端子とプラス端子との間には、抵抗 R<sub>f</sub> とコンデンサ C<sub>f</sub> の直列回路が接続されている。また、コンパレータ A 4 のマイナス端子には、比較電圧部 5 5 の出力電圧 V<sub>o</sub> が供給され、プラス端子には、定常状態では 2 . 9 5 V 程度の比較電圧 V<sub>2</sub> が供給されている。この比較電圧 V<sub>2</sub> は、第二電源部 S D が生成した二種類の電源電圧 V<sub>c c</sub> , V<sub>B</sub> を抵抗で分圧して生成されている。

20

#### 【 0 0 7 7 】

電源リセット部 5 7 は、上記の通りに構成されているので、以下の通りに動作する。

#### 【 0 0 7 8 】

( 1 ) 交流電圧 A C 2 4 V が投入された電源投入直後は、比較電圧部 5 5 の出力電圧 V<sub>o</sub> は、レベル上昇中の電源電圧 V<sub>c c</sub> に対応して、V<sub>c c</sub> - V<sub>f</sub> - となる。一方、比較電圧 V<sub>2</sub> は、第二電源部 S D の電源電圧 V<sub>c c</sub> , V<sub>B</sub> を分圧して生成されるので、レベル上昇中の出力電圧 V<sub>o</sub> より低い。そのため、このような過渡状態では、コンパレータ A 4 から出力されるシステムリセット信号 S Y S が L レベルとなる( 図 6 ( a ) 参照 )。

30

#### 【 0 0 7 9 】

( 2 ) その後、レベル上昇中の電源電圧 V<sub>c c</sub> が所定レベルに達した後は、比較電圧部 5 5 の出力電圧 V<sub>o</sub> は、2 . 5 V を維持する。また、電源電圧 V<sub>c c</sub> , V<sub>B</sub> が正常レベル近くまで増加すると、比較電圧 V<sub>2</sub> が定常値 2 . 9 5 V に近づく。そのため、コンパレータ A 4 から出力されるシステムリセット信号 S Y S は、適宜なタイミングで、L レベルから H レベルに遷移する。

40

#### 【 0 0 8 0 】

このようにして生成されたシステムリセット信号 S Y S は、演出インタフェイス基板 2 7 を経由して、演出制御部 2 2 と画像制御部 2 3 に伝送されるが、各制御部 2 2 , 制御部 2 3 に設けられた遅延回路を経由して C P U やその他の I C を電源リセットしている。なお、抵抗 R<sub>f</sub> とコンデンサ C<sub>f</sub> の直列回路も、遷移動作を遅延させる機能を発揮する。

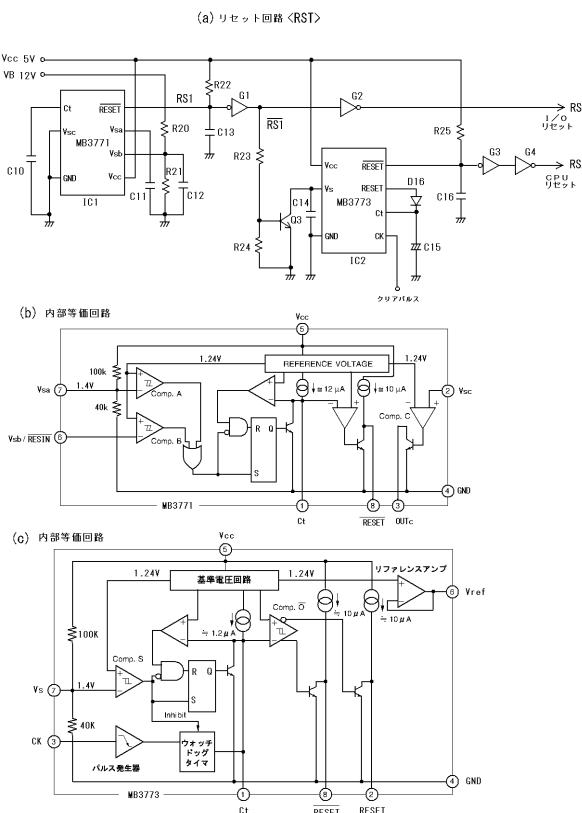

#### 【 0 0 8 1 】

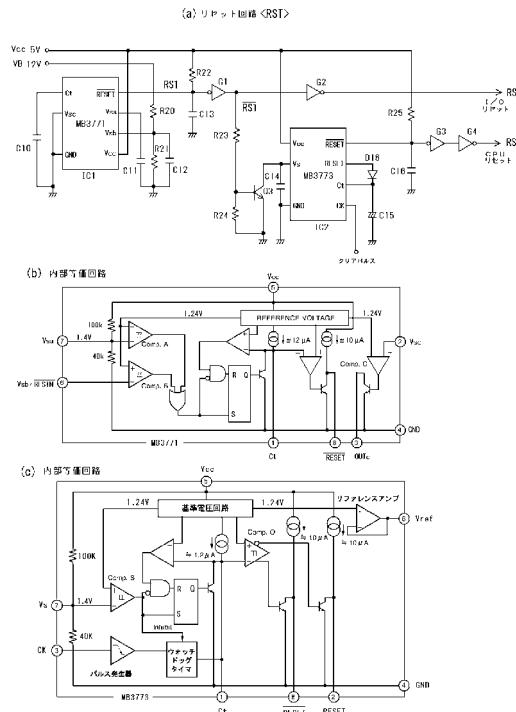

図 5 ( a ) は、主制御部 2 1 と派出制御部 2 4 に配置されたリセット回路 R S T を示す回路図である。この実施例では、電源電圧監視用 I C 1 ( M B 3 7 7 1 富士通マイクロエレクトロニクス ) と、ウォッチドッグタイマ機能付き電源電圧監視用 I C 2 ( M B 3 7 7

50

3 富士通マイクロエレクトロニクス)とを活用してリセット回路 R S T を構成している。

【0082】

図 5 ( b ) の等価回路を示す通り、電源電圧監視用 I C 1 は、2つのコンパレータ C o m p A , C o m p B を内蔵して構成されている。そして、2つのコンパレータ C o m p A , C o m p B のプラス端子は、内蔵回路によって 1 . 2 4 V 程度に設定される。

【0083】

また、実施例の回路構成では、V s a 端子がコンデンサ C 1 1 を経由してグランドに接続されているので、コンパレータ C o m p A のマイナス端子の電位は、内蔵された抵抗で分圧されて 1 . 4 V 程度となる。一方、V s b 端子には、外付けの分圧抵抗 R 2 0 、R 2 1 によって電源電圧 V B が分圧して供給されているので、V s b 端子の電位は、 $V B * R 2 1 / ( R 2 0 + R 2 1 )$  である。なお、抵抗 R 2 1 には、電圧安定用のコンデンサ C 1 2 が並列接続されている。また、C t 端子には遅延コンデンサ C 1 0 が接続されている。

10

【0084】

電源電圧監視用 I C 1 は、図 5 ( b ) の内部回路を有しているので、電源投入後、電源電圧 V c c が所定レベルまで上昇すると(図 6 ( d ) のタイミング T 2 参照)、内蔵された定電流源によって、遅延コンデンサ C 1 0 の充電が開始される。そして、遅延コンデンサ C 1 0 が所定レベルまで充電されるまでの間は(図 6 ( e ) の T 3 参照)、リセット端子から出力される基礎リセット信号 R S 1 が L レベルに維持される。なお、このリセットホールド時間 T p o [ S ] は、外付けコンデンサ C 1 0 の容量に対応して T p o [ S ] =  $10^5 * C 1 0 [ F ]$  となっている。

20

【0085】

このようにして、タイミング T 3 で H レベルとなった基礎リセット信号 R S 1 は、電源電圧 V c c , V B が降下しない限り、そのレベルを維持する。しかし、V s b 端子の電位は、 $V B * R 2 1 / ( R 2 0 + R 2 1 )$  であって、このV s b 端子において電源電圧 V B のレベルを監視している。同様に、V s a 端子の電位は、内蔵抵抗 4 0 k 、1 0 0 k に対応して、 $V c c * 4 0 / ( 4 0 + 1 0 0 )$  であって、このV s a 端子において電源電圧 V c c のレベルを監視している。

【0086】

そのため、交流入力 A C 2 4 V の遮断や、電源部 F R , S D の故障などによって、電源電圧 V c c , V B の双方又は一方の電圧レベルが降下すると(図 6 ( d ) のタイミング T 8 参照)、内蔵コンパレータ C o m p A , C o m p B のいずれかの出力端子が H レベルに遷移する。すると、内蔵されたフリップフロップがセットされて、リセット端子から出力される基礎リセット信号 R S 1 が、直ちに L レベルに降下する(図 6 ( e ) のタイミング T 8 参照)。

30

【0087】

ところで、本実施例では、V s a 端子とグランド間には、コンデンサ C 1 1 が接続され、V s b 端子とグランド間には、コンデンサ C 1 2 が接続されている。図 5 ( b ) の等価回路から明らかな通り、これらのコンデンサ C 1 1 , C 1 2 は、内部回路の動作を遅延させる機能を果しており、電源電圧 V c c , V B が短時間だけ、例えば 4 V 以下に低下して回復する瞬低状態や瞬断状態では、基礎リセット信号 R S 1 が出力されることはない。

40

【0088】

本実施例では、C 1 1 = C 1 2 = 1 0 0 0 p F 程度に設定されており、これに対応して、直流電圧(5 V , 1 2 V)のレベル降下が、4 0 μ S 以内に回復する瞬断状態や瞬低状態では、電源電圧監視用 I C 1 が反応しないよう構成されている。したがって、電源基板 2 0 から供給される電源電圧 V c c , V B の給電ラインの何れかに、パルス幅 4 0 μ S 以内のスパイクノイズが重畠しても、基礎リセット信号 R S 1 が異常に出力されることはない。

【0089】

上記の通りに動作する電源電圧監視用 I C 1 に対応して、基礎リセット信号 R S 1 は、2つのNOTゲート G 1 , G 2 を経由して、I/Oリセット信号として主制御部 2 1 や拡

50

出制御部 24 に搭載されたデータ入出力用 I C のリセット端子に供給される。好ましくは、ラッチ機能を有するデータ入出力用 I C に基礎リセット信号( I / O リセット信号 ) R S 1 が供給される。そのため、電源投入時にランダムにラッチされたデータ入出力用 I C ( 例えは、 S N 7 4 2 7 3 、 S N 7 4 L V 8 1 5 5 など ) のデータが、基礎リセット信号 R S 1 によって確実にクリアされる。

#### 【 0 0 9 0 】

また N O T ゲート G 1 を経由した基礎リセット信号 R S 1 バーは、ウォッチドッグタイマ機能付き電源電圧監視用 I C 2 に供給されている。図示の通り、電源電圧監視用 I C 2 は、 C P U リセット信号 R S 1 を出力するが、電源電圧監視用 I C 2 の C t 端子には、遅延コンデンサ C 1 5 が接続され、 C K 端子には、ワンチップマイコンからクリアパルスが供給されるよう構成されている。10

#### 【 0 0 9 1 】

また、電源電圧監視用 I C 2 の V s 端子は、コンデンサ C 1 4 を経由してグランドに接続され、コンデンサ C 1 4 には、トランジスタ Q 3 のコレクタ端子とエミッタ端子とが並列接続されている。そして、トランジスタ Q 3 のベース端子には、バイアス抵抗 R 2 3 , R 2 4 によって分圧された基礎リセット信号 R S 1 バーが供給されている。

#### 【 0 0 9 2 】

コンデンサ C 1 4 は、内部回路の動作を遅延させる遅延素子である。電源電圧監視用 I C 1 の場合と同様、コンデンサ C 1 4 の静電容量を適宜に設定することで、電源電圧 V c c の瞬断状態や瞬低状態では、電源電圧監視用 I C 2 が反応しないよう構成することができる。20

#### 【 0 0 9 3 】

電源電圧監視用 I C 2 は、図 5 ( c ) の内部回路を有しており、 V s 端子が開放状態であれば、 V s 端子の電位は、内蔵抵抗によって 1 . 4 V 程度に設定されている。また、この V s 端子は、内蔵されたコンパレータ C o m p S のマイナス端子に接続され、コンパレータ C o m p S のプラス端子には、内蔵回路によって 1 . 2 4 V 程度の電圧が供給されている。

#### 【 0 0 9 4 】

以下、電源電圧監視用 I C 2 の動作を説明すると、電源投入後、タイミング T 3 ( 図 6 ( f ) 参照 ) に至るまでの期間は、基礎リセット信号 R S 1 バーが H レベルであるので、トランジスタ Q 3 が O N 状態である。そのため、電源電圧監視用 I C 2 の V s 端子の電位が 0 V であって、コンパレータ C o m p S の出力が H レベルとなる。30

#### 【 0 0 9 5 】

ところが、タイミング T 3 において、基礎リセット信号 R S 1 バーが L レベルに遷移してトランジスタ Q 3 が O F F 状態となると、コンパレータ C o m p S の出力が L レベルに遷移することで、内蔵されたフリップフロップがリセット状態となり、遅延コンデンサ C 1 5 への充電動作が開始される。そして、遅延コンデンサ C 1 5 が所定レベルまで充電された後 ( 図 6 ( g ) のタイミング T 4 参照 ) 、 C P U リセット信号 R S 2 が L レベルから H レベルに遷移する。

#### 【 0 0 9 6 】

C P U リセット信号 R S 2 が L レベルの間は、ワンチップマイコンのリセット端子が L レベルに維持されるので、 C P U コアその他は確実にリセット状態となる。なお、リセットホールド時間 T p r [ m S ] は、外付けコンデンサ C 1 5 の容量に対応して、 T p r [ m S ] = 1 0 0 0 \* C 1 5 [ μ F ] となっている。40

#### 【 0 0 9 7 】

この電源電圧監視用 I C 2 では、 C P U リセット信号 R S 2 が H レベルに遷移して、ワンチップマイコンが動作開始するタイミングに合わせ、電源電圧監視用 I C 2 に内蔵されたウォッチドッグタイマ回路が動作を開始するよう構成されている。

#### 【 0 0 9 8 】

そのため、その後は、ウォッチドッグタイマ機能が発揮される。具体的に確認すると、50

ワンチップマイコンの動作開始に合わせて、電源電圧監視用 I C 2 では、遅延コンデンサ C 1 5 の放電動作が開始され、ワンチップマイコンがクリアパルスを供給する毎に、遅延コンデンサ C 1 5 の放電動作が充電動作に切り替わる。

#### 【 0 0 9 9 】

しかし、プログラム暴走などのトラブルが発生すると（図 6 ( g ) のタイミング T 5 参照）、遅延コンデンサ C 1 5 の放電動作が継続されることになり、C t 端子の電位が 0 . 4 V 程度まで降下すると、C P U リセット信号 R S 2 が強制的に L レベルに遷移される。その後、C P U リセット信号 R S 2 は、L レベルに維持されるが、所定の維持時間 T w r の経過後、C P U リセット信号 R S 2 が H レベルに復帰すると、C P U は、電源投入状態と同様の初期処理プログラムの実行を開始する。なお、継続時間 T w r [ m S ] は、遅延コンデンサ C 1 5 の容量に対応して、T w r [ m S ] = 2 0 \* C 1 5 [ μ F ] となっている。

10

#### 【 0 1 0 0 】

次に、電源遮断時における電源電圧監視用 I C 2 の動作を説明する。電源電圧 V c c が所定レベル ( 4 . 2 V ) まで降下すると、C P U リセット信号 R S 2 が L レベルに遷移する（図 6 ( g ) のタイミング T 8 ）。そして、その後は、ウォッチドッグタイマ回路の動作が禁止される。

20

#### 【 0 1 0 1 】

ところで、本実施例では、ワンチップマイコンに内蔵されたウォッチドッグタイマ回路を活用せず、あえて、外付けの専用 I C 2 を使用している。それは、C P U が暴走するような異常時には、ワンチップマイコンの内蔵回路にも、何らかの異常が発生している可能性を否定できないため、万全の安全対策を探ったことによる。

20

#### 【 0 1 0 2 】

また、本実施例では、電源電圧監視用 I C 1 と電源電圧監視用 I C 2 とを重複して配置し、電源電圧監視用 I C 2 から出力される電源リセット信号（C P U リセット信号）R S 2 を、ワンチップマイコンだけに供給し、電源電圧監視用 I C 1 から出力される電源リセット信号（基礎リセット信号）R S 1 を、ワンチップマイコン以外のデータ入出力用 I C だけに供給している。また、電源電圧監視用 I C 2 のウォッチドッグタイマ機能によって生成された C P U リセット信号 R S 2 は、ワンチップマイコンだけに供給されているが、このような構成を探る理由は以下の通りである。

30

#### 【 0 1 0 3 】

先ず、本実施例の弾球遊技機は、電源バックアップ機能を有しているので、電源投入時に、電源遮断前（前日や停電前）の遊技を再開することもある。そのため、電源投入時には、特に、ラッチ機能を有するデータ入出力用 I C を確実にリセット状態にする必要がある。但し、リセットホールド時間は、短くて足りるので、電源電圧監視用 I C 1 を利用して電源リセット信号（基礎リセット信号）R S 1 を生成している。

#### 【 0 1 0 4 】

一方、ワンチップマイコンについては、電源電圧 V c c , V B が安定した後、十分なりセットホールド時間が必要である。また、前記した理由から、ウォッチドッグタイマ回路を外付けするのが好ましく、このウォッチドッグタイマによる C P U リセット信号 R S 2 についても、所望のリセットホールド時間が必要となる。そこで、本実施例では、電源電圧監視用 I C 1 と電源電圧監視用 I C 2 とを直列的に接続して、最適なリセットホールド時間 (= T p o + T p r ) を有する電源リセット信号（C P U リセット信号）R S 2 を生成すると共に、電源電圧監視用 I C 2 を利用して、異常発生時の C P U リセット信号 R S 2 を生成している。リセットホールド時間は、C P U リセット後の初期処理時間なども考慮して、主制御部 2 0 と払出制御部 2 4 とで各々最適値に設定される。したがって、例えば、払出制御部 2 4 の初期処理動作中に、制御コマンドが送信されることはない。もっとも、初期処理時間において、主制御部 2 0 の方が、払出制御部より明らかに長い場合には、リセットホールド時間を同一に設定したので足りる。

40

#### 【 0 1 0 5 】

50

なお、プログラム暴走などによる異常発生時には、基礎リセット信号 R S 1 が発生されることはないので、データ入出力用 I C はリセットされない。しかし、電源投入時とは異なり、異常リセット時に、データ入出力用 I C にランダムなデータがラッチされることはなく、また、異常リセット時には、R A Mクリア処理が実行され、遊技動作が再開されることはないので、データ入出力用 I C をリセットしないことに何の問題も生じない。

#### 【 0 1 0 6 】

一方、電源電圧 ( V B , V c c c ) の瞬断状態が短時間とはいうものの、コンデンサ C 1 1 , C 1 2 で吸収できない程度に継続した場合には、電源電圧監視用 I C 1 から、短いパルス幅の基礎リセット信号 R S 1 が出力される。そして、この基礎リセット信号 R S 1 は、トランジスタ Q 3 を短時間だけ O N 動作させる。しかし、トランジスタ Q 3 の O N 抵抗を適宜な値に設定すると共に、トランジスタ Q 3 に並列接続されるコンデンサ C 1 4 を適度な静電容量に設定することで、C P Uリセット信号 R S 2 の出力を回避することもできる。

10

#### 【 0 1 0 7 】

このような場合、データ入出力用 I C だけがリセットされることになるが、このリセット動作は、特に、図柄始動口などのスイッチ信号を生成するために使用される電源電圧 V B ( 1 2 V ) が、瞬低状態に陥った場合に、データ入出力用 I C だけがクリアされる点で効果的である。

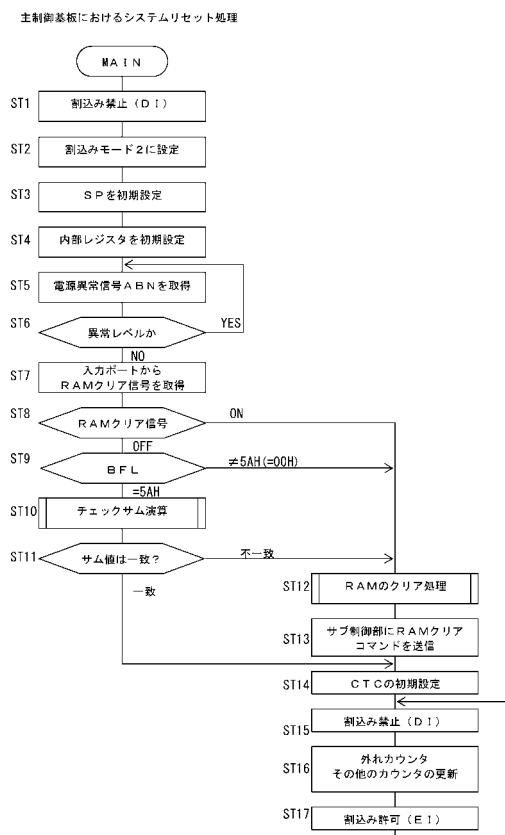

#### 【 0 1 0 8 】

続いて、遊技動作を統括的に制御する主制御部 2 1 のプログラムの概要を説明する。図 7 ~ 図 8 は、主制御部 2 1 の制御プログラムを示すフローチャートである。主制御部 2 1 の制御プログラムは、電源電圧の復旧や投入に基づいて起動されるシステムリセット処理 ( 図 7 ) と、所定時間毎 ( 2 m S ) に起動されるマスク可能なタイマ割込み処理 ( 図 8 ( a ) ) とで構成されている。なお、払出制御部 2 4 の動作内容も、システムリセット処理とタイマ割込み処理の基本構成において共通している。

20

#### 【 0 1 0 9 】

以下、図 7 を参照しつつ、システムリセット処理プログラム ( メイン処理 ) について説明する。メイン処理が開始されるのは、停電状態からの復旧時のように初期化スイッチ S W が O F F 状態で電源が O N 状態になる場合と、遊技ホールの開店時のように、初期化スイッチ S W が O N 操作されて電源が O N 状態になる場合とがある。なお、制御プログラムが暴走したことにより、電源電圧監視用 I C 2 のウォッチドッグタイマ機能が発揮されて C P U が強制的にリセットされる場合もある。

30

#### 【 0 1 1 0 】

何れの場合でも、Z 8 0 C P U は、最初に自らを割込み禁止状態に設定すると共に ( S T 1 ) 、割込みモード 2 に設定する ( S T 2 ) 。また、C P U 内部のスタックポインタ S P の値を、スタック領域の最終アドレスに初期設定すると共に ( S T 3 ) 、ワンチップマイコンの各部を含めて内部レジスタの値を初期設定する ( S T 4 ) 。

#### 【 0 1 1 1 】

続いて、入力ポートから電源異常信号 A B N 1 を取得し、これが正常レベルに変化するまで、同一の処理を繰返す ( S T 5 ~ S T 6 ) 。これは、電源遮断時に、図 8 ( b ) の S T 4 1 の処理を終えた後でも、電源電圧 V c c が降下し切らない場合もあることを考慮したものである。すなわち、図 8 ( b ) の電源監視処理を終えて、無限ループ処理を繰返しているタイミングで、ウォッチドッグタイマ機能が発揮されて C P U がリセットされることはあっても、その後の処理は、ステップ S T 7 以降に進むことはない。

40

#### 【 0 1 1 2 】

このような待機処理 ( S T 5 ~ S T 6 ) を設けていないと、ステップ S T 5 から進行した定常処理によって R A M のデータ ( チェックサム演算の基礎データや、S T 3 3 で更新されるバックアップフラグ B F L ) が書き換えられ、しかも、そのデータが電源遮断後も保存されることになる。このような場合、翌日の判定において、バックアップフラグ B F L = 0 となるか、或いは、前日にバックアップされたチェックサム値 ( S T 3 8 ) と、翌

50

日の電源投入後に算出するチェックサム値に不一致となるので、せっかくのバックアップ処理（S T 3 7 ~ S T 3 8）が無駄になる。

#### 【0 1 1 3】

また、ステップS T 5 ~ S T 6 の処理は、電源電圧監視用I C 2によるウォッチドッグタイマ機能と協働することで、交流入力電圧の給電が一瞬だけ停止される瞬停状態でも有効に機能する。すなわち、図5に関して説明した通り、たとえ瞬停状態であっても、電源異常信号A B N 1 , A B N 2 が主制御部2 1と派出制御部2 4に供給されるので、図8(b)の電源監視処理が開始されることがある。そして、電源異常信号A B N 1 , A B N 2 のパルス幅によっては、ステップS T 3 6 ~ S T 4 0 の処理を終えて無限ループ処理に移行する可能性もある。しかし、このような場合であっても、その後ウォッチドッグタイマ機能によってC P Uがリセットされ、その後、ステップS T 5 ~ S T 6 の処理を通過することで、それまでの遊技動作を再開することができる。

10

#### 【0 1 1 4】

このような場合も含め、ステップS T 6 の処理において、電源異常信号A B N 1 が正常レベルであることが確認されたら、続いて、入力ポートからR A Mクリア信号C L R を取得する（S T 7）。先に説明した通り、R A Mクリア信号C L Rとは、ワンチップマイコンの内蔵R A Mの全領域を初期設定するか否かを決定する信号であって、係員が操作する初期化スイッチS WのO N / O F F 状態に対応した値を有している。

#### 【0 1 1 5】

次にR A Mクリア信号のレベルが判定されるが（S T 8）、R A Mクリア信号がO N 状態であったと仮定すると、内蔵R A Mの全領域がゼロクリアされる（S T 1 2）。したがって、図8(b)のステップS T 3 7 の処理でセットされたバックアップフラグB F L の値は、他のチェックサム値などと共にゼロとなる。

20

#### 【0 1 1 6】

次に、R A M領域がゼロクリアされたことを報知するための電源投入コマンドが出力され（S T 1 3）、タイマ割込み動作（図8(a)）を起動する割込み信号I N T を出力するC T Cを初期設定する（S T 1 4）。そして、C P Uを割込み禁止状態にセットした状態で（S T 1 5）、各種のカウンタについて更新処理を実行し（S T 1 6）、その後、C P Uを割込み許可状態に戻してステップS T 1 5 に戻る。なお、ステップS T 1 6 で更新されるカウンタには、外れ図柄用カウンタが含まれているが、この外れ図柄用カウンタは、図8(a)の特別図柄処理（S T 2 7）における大当たり抽選処理の結果が外れ状態となつた場合に、どのような様の外れゲームを演出するかを決定するためのカウンタである。

30

#### 【0 1 1 7】

さて、ステップS T 8 の判定処理に戻って説明すると、C P Uがウォッチドッグタイマによって強制的にリセットされた場合や、停電状態からの復旧時には、R A Mクリア信号はO F F 状態である。そして、このような場合には、ステップS T 8 の判定に続いて、バックアップフラグB F L の内容が判定される（S T 9）。バックアップフラグB F Lとは、図8(b)の電源監視処理の動作が実行されたことを示すデータであり、この実施例では、電源遮断時のステップS T 3 7 の処理でバックアップフラグB F L が5 A H とされ、電源復帰後のステップS T 3 3 の処理でゼロクリアされる。

40

#### 【0 1 1 8】

電源投入時や、停電状態からの復旧時である場合には、バックアップフラグB F L の内容が5 A H の筈である。但し、何らかの理由でプログラムが暴走状態となり、ウォッチドッグタイマによるC P Uリセット動作が生じたような場合には、バックアップフラグB F L = 0 0 H である。したがって、B F L = 5 A H (通常はB F L = 0 0 H )となる場合には、ステップS T 9 からステップS T 1 2 の処理に移行させて遊技機の動作を初期状態に戻す。

#### 【0 1 1 9】

一方、バックアップフラグB F L = 5 A H であれば、チェックサム値を算出するためのチェックサム演算を実行する（S T 1 0）。ここで、チェックサム演算とは、内蔵R A M

50

のワーク領域を対象とする8ビット加算演算である。そして、チェックサム値が算出されたら、この演算結果を、RAMのSUM番地の記憶値と比較をする(ST11)。

#### 【0120】

SUM番地には、電圧降下時に実行される電源監視処理(図8(b))において、同じチェックサム演算によるチェックサム値が記憶されている(ST38)。そして、記憶された演算結果は、内蔵RAMの他のデータと共に、バックアップ電源によって維持されている。したがって、本来は、ステップST11の判定によって両者が一致する筈である。

#### 【0121】

しかし、電圧降下時にチェックサム演算(ST38)の実行できなかった場合や、実行できても、その後、メイン処理のチェックサム演算(ST10)の実行時までの間に、ワーク領域のデータが破損している場合もあり、このような場合にはステップST11の判定結果は不一致となる。判定結果の不一致によりデータ破損が検出された場合には、ステップST12の処理に移行させてRAMクリア処理を実行し、遊技機の動作を初期状態に戻す。一方、ステップST9の判定において、チェックサム演算(ST10)によるチェックサム値と、SUM番地の記憶値とが一致する場合には、ステップST14の処理に移行する。

#### 【0122】

続いて、上記したメイン処理を中断させて、2mS毎に開始されるタイマ割込み処理プログラム(図8(a))を説明する。タイマ割込みが生じると、CPUのレジスタを保存することなく、直ちに電源監視処理が実行される(ST20)。これは、タイマ割込み処理が起動されるタイミングが、ステップST15の直後に固定されているためである。

#### 【0123】

電源監視処理(ST20)では、電源基板20から供給されている電源異常信号のレベルを判定するが、具体的な処理内容については後述する。電源監視処理(ST20)が終わると、普通図柄処理(ST26)における抽選動作で使用される当り用カウンタRGと、特別図柄処理(ST27)における抽選動作で使用される大当たり判定用の乱数値RNDとが更新される(ST21)。

#### 【0124】

2つのカウンタRG, RNDの更新処理(ST21)が終わると、各遊技動作の時間を管理しているタイマについて、タイマ減算処理が行なわれる(ST22)。ここで減算されるタイマは、主として、電動チューリップや大入賞口の開放時間やその他の遊技演出時間を管理するために使用される。

#### 【0125】

続いて、電源電圧監視用IC2のCK端子にクリアパルスを出力すると共に、図柄始動口15や大入賞口16の入賞検出スイッチを含む各種スイッチ類のON/OFF信号が入力され、ワーク領域にON/OFF信号レベルや、その立上り状態が記憶される(ST23)。次に、エラー管理処理が行われる(ST24)。エラー管理処理は、遊技球の補給が停止したり、遊技球が詰まっていないなど、機器内部に異常が生じていないかの判定を含んでいる。

#### 【0126】

次に、図柄始動口や大入賞口などからの検出信号に基づく管理処理を実行した後(ST25)、普通図柄処理を行う(ST26)。普通図柄処理とは、電動チューリップなど、普通電動役物を作動させるか否かの判定を意味する。具体的には、ステップST23のスイッチ入力処理で、遊技球がゲートを通過していると判定された場合に、乱数更新処理(ST21)で更新された当り用カウンタRGを、当り当選値と対比して行われる。そして、対比結果が当選状態であれば当り中の動作モードに変更する。また、当り中となれば、電動チューリップなど、普通電動役物の作動に向けた処理を行う。

#### 【0127】

続いて、特別図柄処理を行う(ST27)。特別図柄処理とは、大入賞口16など特別電動役物を作動させるか否かの判定であり、ステップST23のスイッチ入力処理で、図

10

20

30

40

50

柄始動口に遊技球が入賞したと判定された場合には、乱数更新処理( S T 2 1 )で更新された乱数値 R N D に使用して大当たり抽選処理を実行する( S T 6 6 )。そして、図示省略しているが、抽選結果が当選状態であれば大当たり中の動作モードに変更する。また、大当たり中となれば、大入賞口など種特別電動役物の作動に向けた処理を行う。

#### 【 0 1 2 8 】

このような特別図柄処理( S T 2 7 )の後、主制御部 2 1 で管理する L E D について点灯動作を進行させると共に( S T 2 8 )、電動チューリップや大入賞口などの開閉動作を実現するソレノイド駆動処理を実行した後( S T 2 9 )、C P U を割込み許可状態 E I に戻してタイマ割込みを終える( S T 3 0 )。その結果、割込み処理ルーチンからメイン処理の無限ループ処理( 図 7 )に戻り、ステップ S T 1 7 の処理が実行される。

10

#### 【 0 1 2 9 】

続いて、図 8 ( b )に示す電源監視処理( S T 2 0 )について説明する。電源監視処理( S T 2 0 )では、先ず、電源基板 2 0 から供給される電源異常信号 A B N 1 を、入力ポート( 不図示 )を通して取得し( S T 3 1 )、それが異常レベルでないか判定する( S T 3 2 )。そして、異常レベルでない場合には、異常回数カウンタとバックアップフラグ B F L をゼロクリアして処理を終える( S T 3 3 )。

#### 【 0 1 3 0 】

一方、電源異常信号 A B N 1 が異常レベルである場合には、異常回数カウンタをインクリメント( + 1 )して( S T 3 4 )、計数結果が上限値 M A X を超えていないかを判定する( S T 3 5 )。これは、入力ポートからの取得データが、ノイズなどの影響でビット化けしている可能性があることを考慮したものであり、所定回数( 例えば、上限値 M A X = 2 )連続して異常レベルを維持する場合には、交流電源が現に遮断されたと判定する。

20

#### 【 0 1 3 1 】

このように、本実施例では、電源遮断時にも、直ぐには以降のバックアップ処理を開始せず、動作開始のタイミングが、 M A X × 2 m S だけ遅れる。しかし、( 1 )電源降下信号は、直流電源電圧の降下ではなく、交流直流電圧の降下を検出すること、( 2 )直流電源電圧は、大容量のコンデンサによって交流電源の遮断後もしばらくは維持されること、( 3 )電源監視処理が高速度( 2 m S 毎 )で繰り返されること、( 4 )バックアップ処理が極めてシンプルであり、迅速に終わることから、実質的には何の弊害もない。

30

#### 【 0 1 3 2 】

ところで、ステップ S T 3 5 の判定の結果、異常回数カウンタの計数値が上限値 M A X に一致した場合には、異常回数カウンタをゼロクリアした後( S T 3 6 )、バックアップフラグ B F L に 5 A H を設定する( S T 3 7 )。次に、メインルーチンのステップ S T 7 の場合と、全く同じ演算を、全く同じ作業領域( ワークエリア )に対して実行し、その演算結果を記憶する( S T 3 8 )。なお、実行される演算は、典型的には 8 ピット加算演算である。

#### 【 0 1 3 3 】

そして、その後はワンチップマイコンを R A M アクセス禁止状態に設定すると共に( S T 3 9 )、全ての出力ポートの出力データをクリアする( S T 4 0 )。以上のバックアップ処理が終われば、 C T C に対する設定処理によって割込み信号 I N T の生成を禁止すると共に、無限ループ処理を繰り返しつつ直流電源電圧が降下するのを待つ( S T 4 1 )。なお、このタイミングでは、 C P U は、もともと割込み禁止状態であるが( S T 3 0 参照 )、電源電圧の降下による誤動作の可能性を、可能な限り排除する趣旨から、本実施例では、 C T C からの割込み信号 I N T の出力も禁止している。

40

#### 【 0 1 3 4 】

ところで、先に説明した通り、ステップ S T 2 0 の処理は、交流電源の遮断後( 図 6 のタイミング T 7 参照 )、 2 m S 以内に迅速に開始され、速やかに終了される。一方、電源電圧 V c c が所定レベルまで降下するのは、電源回路などに配置された平滑コンデンサの影響でかなり遅れる( 図 6 のタイミング T 8 参照 )。

#### 【 0 1 3 5 】

50

そして、電源電圧  $V_{CC}$  が所定レベルまで降下しない限り、電源電圧監視用 I C 2 のウォッチドッグタイマは機能し続ける。そのため、ステップ S T 2 0 の処理が開始され、全ての処理が終わった後、無限ループ処理中に、ウォッチドッグタイマによって C P U が異常リセットされる可能性もある。しかし、前記した通り、本実施例では、ステップ S T 5 ~ S T 6 の待機処理を設けているので、バックアップ処理が無駄になることはない。なお、S T 3 1 S T 3 2 S T 3 4 S T 3 5 S T 3 6 . . . S T 4 1 までの電源監視処理の全処理時間は、クリアパルスの出力周期 ( 2 m S ) より短く設定されており、電源監視処理を終えるまでにウォッチドッグタイマが起動することはない。

【 0 1 3 6 】

以上、本発明の実施例を具体的に説明したが、具体的な記載内容はこれら本発明を限定するものではなく、各種の改変が可能である。例えば、実施例では、主制御部21と派出制御部24にバックアップ機能を持たせたが、主制御部21だけに限定しても良いのは勿論である。

## 【 符号の説明 】

【 0 1 3 7 】

|           |          |

|-----------|----------|

| G M       | 遊技機      |

| 2 1       | 主制御部     |

| 2 4       | 払出制御部    |

| 2 2 , 2 3 | 演出制御部    |

| 2 0       | 電源部      |

| R S 1     | 第一リセット信号 |

| R S 2     | 第二リセット信号 |

| R S T     | リセット回路   |

【図1】

【 図 2 】

【 四 4 】

【図5】

【図6】

【図7】

【図8】

【 図 3 】