(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

28 June 2007 (28.06.2007)

PCT

(10) International Publication Number

WO 2007/073354 A1(51) International Patent Classification:

*H01L 33/00* (2006.01)      *H01L 27/00* (2006.01)

*H01L 21/00* (2006.01)

(74) Agent: CALLINAN, Keith, William; Lloyd Wise, Tan-jong Pagar, P.O. Box 636, Singapore 910816 (SG).

(21) International Application Number:

PCT/SG2006/000395

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(22) International Filing Date:

19 December 2006 (19.12.2006)

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

200508210-2      20 December 2005 (20.12.2005) SG**Published:**

— with international search report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(71) Applicant (for all designated States except US): TINGGI TECHNOLOGIES PRIVATE LIMITED [SG/SG]; 83 Science Park Drive, #03-01/02, The Curie, Science Park 1, Singapore 118258 (SG).

(72) Inventors; and

(75) Inventors/Applicants (for US only): YUAN, Shu [AU/SG]; 8 Jalan Pakis, Singapore 678598 (SG). LIN, Jing [CN/SG]; Blk 609 Clementi West St. 1, #02-97, Singapore 120609 (SG).

(54) Title: LOCALIZED ANNEALING DURING SEMICONDUCTOR DEVICE FABRICATION

(57) Abstract: A process for the fabrication of semiconductor devices on a substrate, the semiconductor devices including at least one metal layer. The process includes, removing the substrate and applying a second substrate; and annealing the at least one metal layer by application of a beam of electromagnetic radiation on the at least one metal layer.

WO 2007/073354 A1

## Localized Annealing During Semiconductor Device Fabrication

### Field of the Invention

5 This invention relates to optical annealing during semiconductor device fabrication and refers particularly, though not exclusively, to annealing during semiconductor device fabrication by use of lasers or lamps after the substrate is removed.

### Background of the Invention

10 Many semiconductor devices are fabricated in large numbers on a substrate. During fabrication they incorporate at least one layer of a metal. Most metal layers applied to semiconductors devices during the fabrication of the semiconductor devices are annealed following their application. Annealing is normally in an oven or the like for a period of time and a predetermined temperature. Often the temperature is relatively high, for example, the annealing temperature for the Ohmic contact metal to n-type GaN is done at 900 C [Z. Fan et al, Applied Physics Letters, Volume 68, page 1672, 1996]. The use of relatively high temperatures has many problems that degrade device performance. For example, unwanted atomic 15 diffusions can take place at high annealing temperatures, degrading the device performance. It is desirable to have the annealing done at low temperatures, preferably at room temperature. Due to the difference between the thermal 20 expansion coefficients of different materials on a wafer (such as, for example, the substrate, epitaxial layers, metals, dielectrics, and so forth), conventional annealing often causes thermal stress in the wafer as the heating is applied to the whole 25 wafer. If the stress is not buffered properly, it often causes cracking in the wafer or the peeling of thin films from the wafer, or creating defects in the wafer. This is especially true in certain wafer fabrication technologies where the substrate is removed and the epitaxial layers are bonded to another mechanical support that acts like a new substrate.

### Summary of the Invention

35 In accordance with a first preferred aspect, in a process for the fabrication of semiconductor devices being fabricated on a substrate and including at least one metal layer, after removal of the substrate and applying a second substrate, there

is provided the step of annealing the at least one metal layer by application of a beam of electromagnetic radiation on the least one metal layer.

According to a second preferred aspect there is provided a process for the 5 fabrication of semiconductor devices being fabricated on a substrate and including at least one metal layer, the process comprising removing the substrate from the semiconductor devices, forming a second substrate on the at least one metal layer, and annealing the at least one metal layer by application of a beam of electromagnetic radiation at a number of locations on the at least one metal layer.

10 For both aspects the second substrate may be applied to the semiconductor devices before or after the substrate is removed. The beam of electromagnetic radiation may be a laser beam, light from at least one lamp, or light from a bank of lamps.

15 The second substrate may be applied to the semiconductor devices on a second surface of the semiconductor devices, the substrate having been removed from a first surface of the semiconductor devices, the first and second surfaces being different. The first surface may be opposite the second surface.

20 The duration of the application of the laser beam may also be determined by the metal of the at least one metal layer, and the thickness of the at least one metal layer. The laser beam may be of a frequency and intensity determined by the metal of the at least one metal layer, the thickness of the at least one metal layer, 25 and the material of the semiconductor devices.

There may be a plurality of metal layers. The plurality of metal layers may be annealed sequentially or simultaneously. The laser beam may be sequentially applied to the number of locations.

30 The laser beam may be applied directly to the at least one layer, or may be applied through the semiconductor device to the at least one metal layer. It may be to an interface of the at least one metal layer and the semiconductor device.

35 The beam of electromagnetic radiation may be applied at a number of locations on the at least one metal layer.

For both aspect the number and spacing of the locations may be determined by the metal of the at least one metal layer, and a thickness of the at least one metal layer.

5 A mask may be placed between a source of the beam of electromagnetic radiation and the semiconductor devices; the screen having at least one aperture therethrough for the passage through the at least one aperture of the beam of electromagnetic radiation. The at least one aperture may be sized and shaped to be substantially the same as the at least one metal layer.

10

#### **Brief Description of the Drawings**

15 In order that the present invention may be fully understood and readily put into practical effect, there shall now be described by way of non-limitative example only preferred embodiments of the present invention, the description being with reference to the accompanying illustrative drawings.

20 In the drawings:

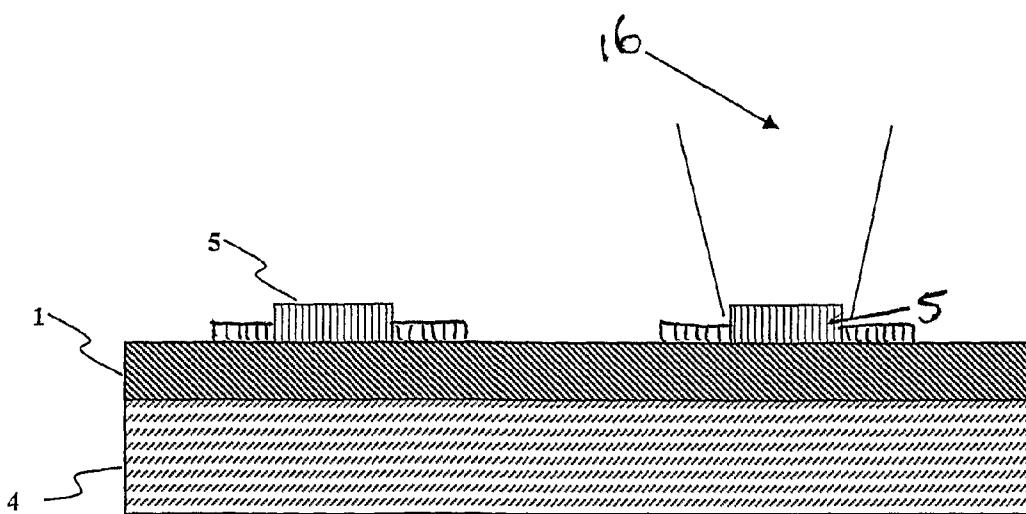

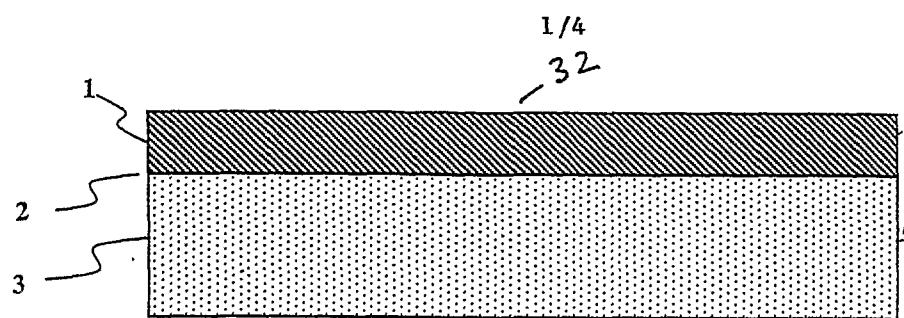

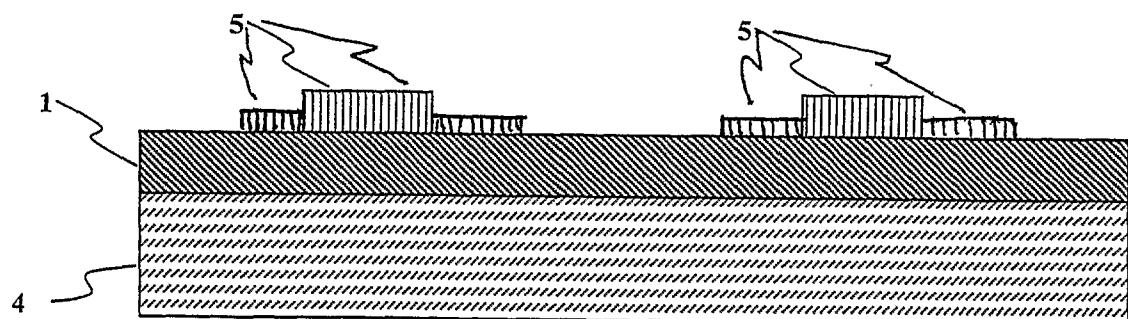

Figure 1 is a schematic vertical cross-sectional view of a preferred form of semiconductor device on which will be performed a preferred method; and

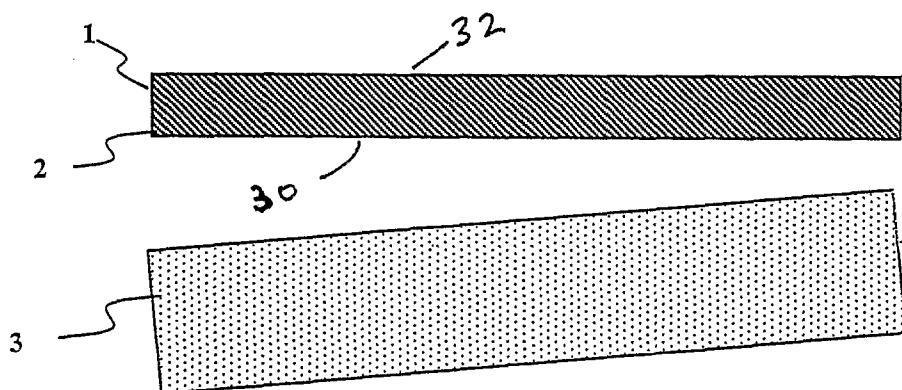

Figure 2 is a view corresponding to Figure 1 after removal of the first substrate;

Figure 3 is a view corresponding to Figures 1 and 2 after formation of the second substrate;

25

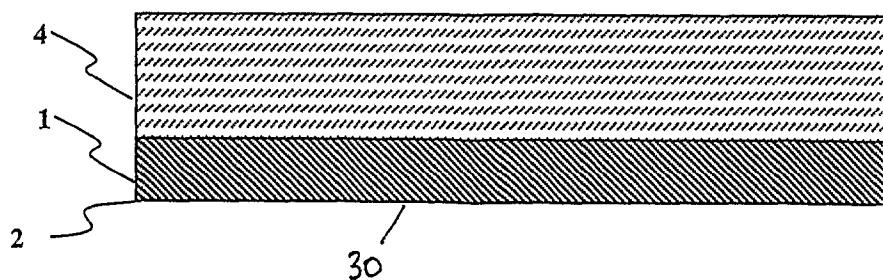

Figure 4 is a side view corresponding to Figures 1 to 3 after formation of an ohmic contact layer;

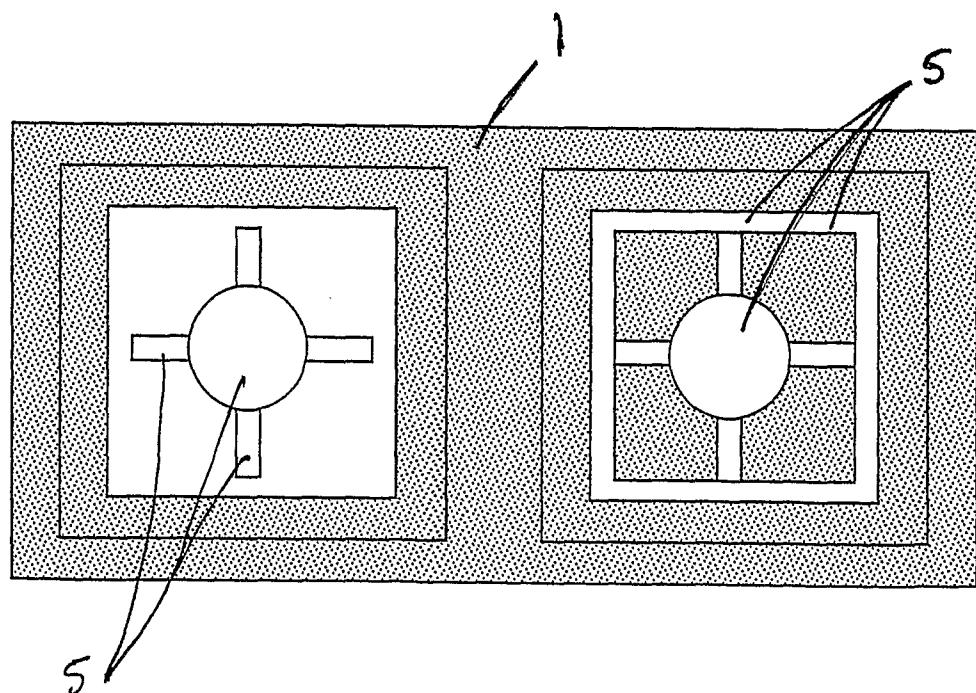

Figure 5 is a top view corresponding to Figure 4;

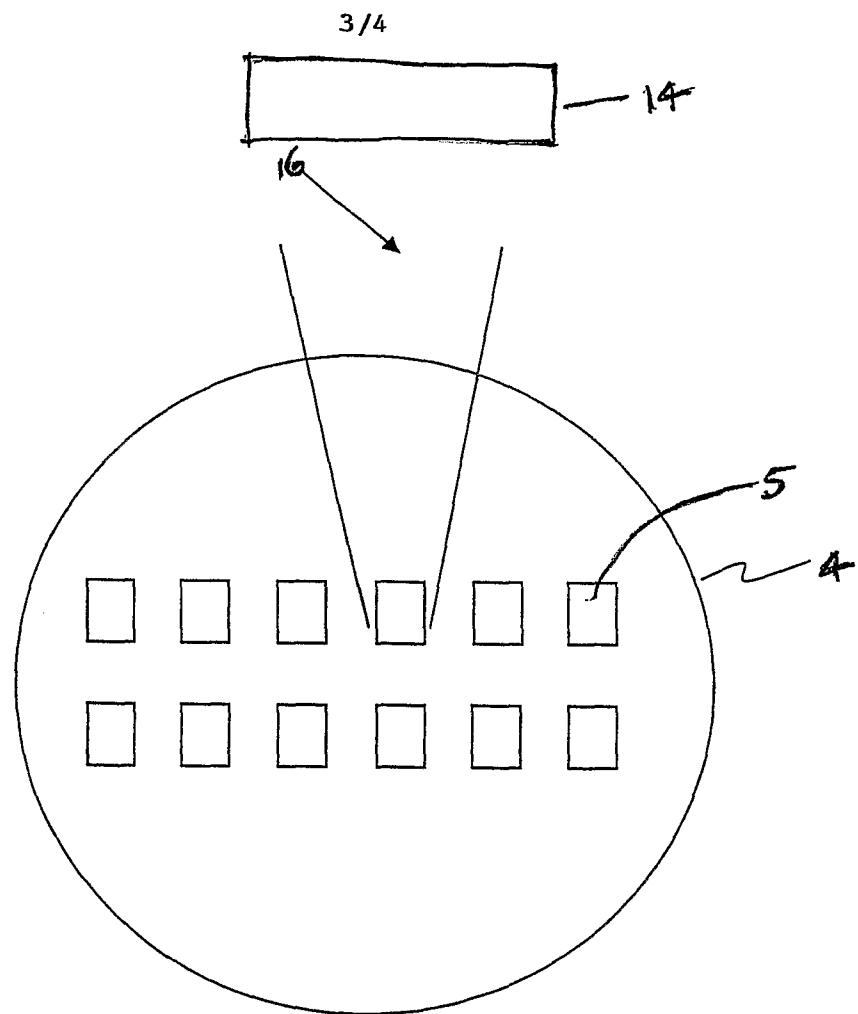

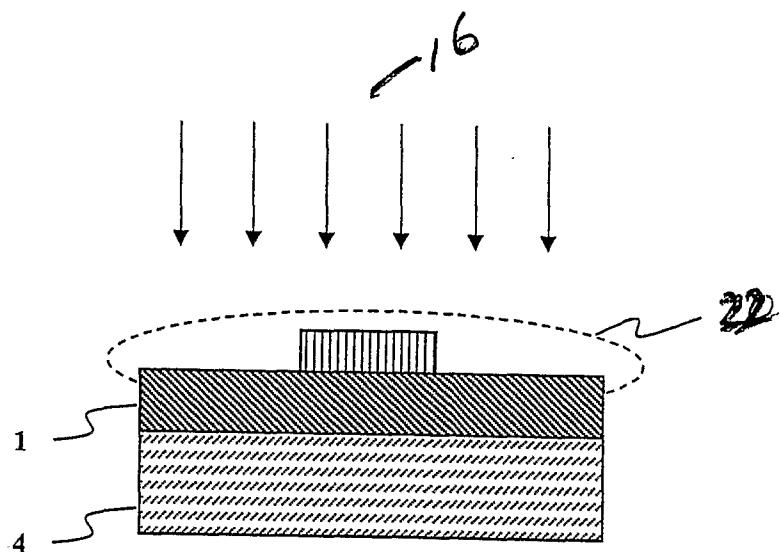

Figure 6 is a schematic top view of the semiconductor devices of Figures 4 and 5 30 during annealing;

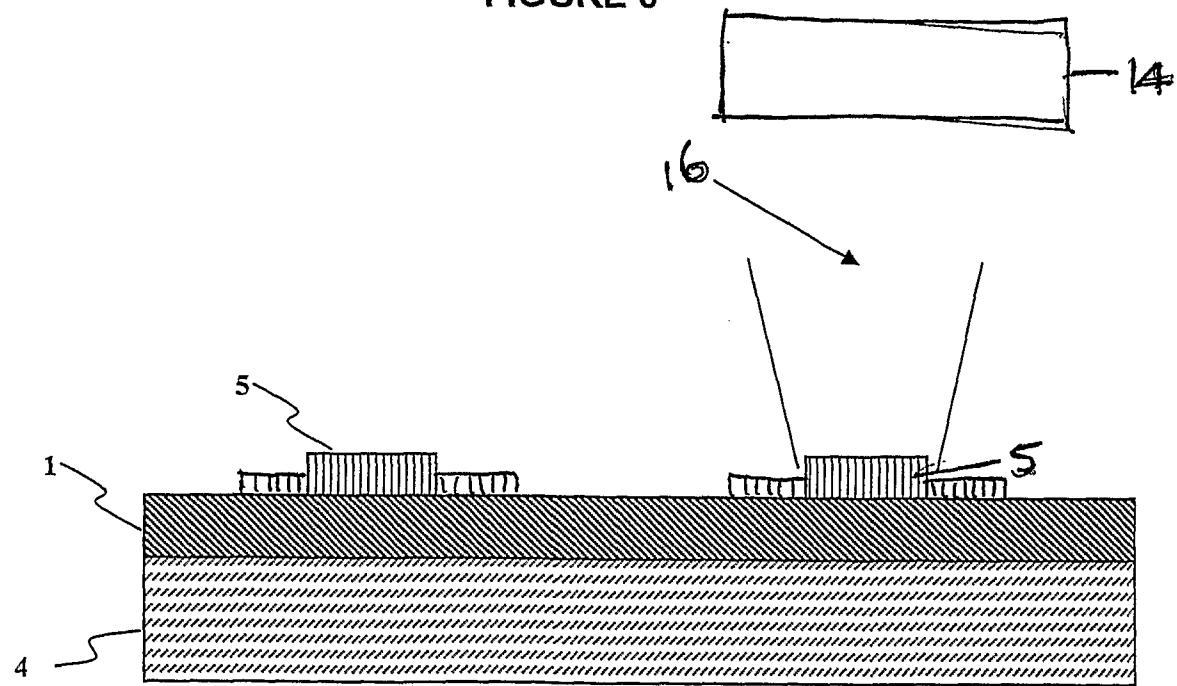

Figure 7 is a side view corresponding to the Figure 6;

Figure 8 is a localized side view corresponding to Figure 7; and

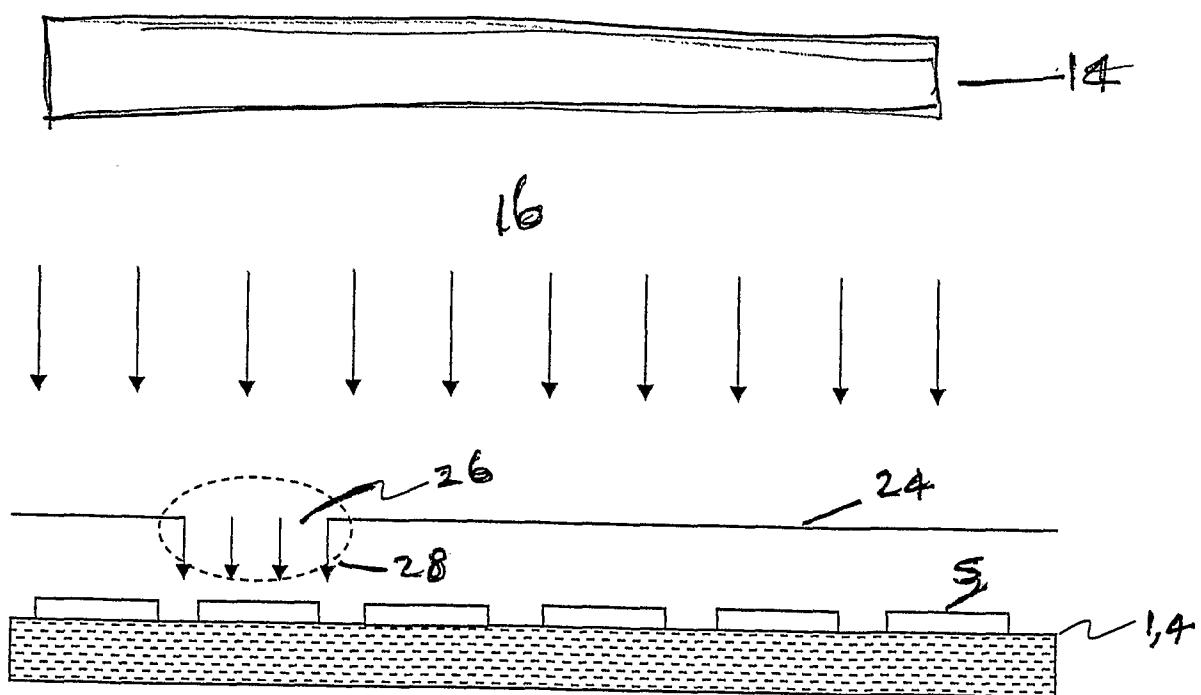

Figure 9 is a schematic side view corresponding to Figure 6 of a second embodiment;

35

#### **Detailed Description of the Preferred Embodiments**

To refer to the drawings there is shown a substrate 3 on which are epitaxial layers 1 and quantum well layer that together from the beginning of a semiconductor device. As shown in Figure 2 the substrate is removed from the quantum well layer 2 and epitaxial layers 1 by any known technique. A second substrate 4 (such as for example, copper) is added above the epitaxial layer 1 (Figure 3). Figures 4 and 5 show that ohmic contact layers 5 are then formed on the epitaxial layers 1. All of this may be in accordance with one or more of our earlier application PCT/SG2003/00022, PCT/SG2003/000223, PCT/SG2005/00061, PCT/SG2005/000062, SG200506301-1 and SG200506897-8; the contents of which are incorporated herein by reference as if disclosed herein in their entirety.

The second substrate 4 is preferably formed on a second surface 32 of the semiconductor device 20, the substrate 3 having been removed from a first surface 30 of the semiconductor devices 20, the first and second surfaces 30, 32 being different. Preferably, the first and second surfaces 30, 32 are opposite surfaces. The second substrate 4 may be formed on or applied to the second surface either before or after the substrate 3 is removed.

In Figure 6 there is shown an apparatus 14 for producing a beam 16 of electromagnetic radiation. The apparatus 14 may be a laser, at least one lamp, or a bank of lamps. The substrate 4 has a number of semiconductor devices 20 being fabricated on the substrate 4. Although twelve semiconductor devices 20 and shown, there may be any suitable number. After the ohmic contacts 5 are formed (after removal of the substrate 3), the ohmic contacts 5 are annealed to enable them to be more strongly adhered to the epitaxial layers 1. This is by a form of fusion of the ohmic contacts 5 and the epitaxial layers 1 at their interface.

The apparatus 14 produces the beam 16. The beam 16 will be a laser beam if apparatus 14 is a laser, or will be light of desired frequency if apparatus 14 is at least one lamp, or a bank of lamps. The beam 16 is focused on the exposed surface of the ohmic contact 5. As such the ohmic contact 5 is heated by the beam 16. Due to the inherent heat conductivity of the ohmic contact 5, the beam 16 does not need to be applied to the entirety of the surface of the ohmic contact 5

The beam 16 is shown being applied to one semiconductor device 20. It may be applied to two or more simultaneously, up to being simultaneously applied to all semiconductor devices 20.

5 As shown in Figure 8, the heat conductivity of the ohmic contact 5 means that heating is limited to the immediate area 30 of the ohmic contact 5 and thus not all of the epitaxial layers 1 are heated. In this way the heat in the epitaxial layers 1 is dispersed through the epitaxial layers 1 and does not affect the interface of epitaxial layers 1 and the second substrate 4. Therefore the temperature at the

10 interface of the epitaxial layer 1 and the second substrate 4 will be less than the temperature at the interface of the ohmic contact 5 and the epitaxial layer 1.

15 The duration, wavelength, radiation power, and radiation power density of the application of the electromagnetic beam 16 may be determined by the metal of the at least one metal layer 5, and the thickness of the at least one metal layer 5, and the materials of the semiconductor devices 20.

20 Figure 9 shows a second embodiment. This may be used when the beam 16 is laser beam, but should be used when the beam 16 is of light. A mask 24 is placed between source 14 and the semiconductor devices 20. The mask 24 has at least one aperture 26 that is preferably sized and shaped to be substantially the same as that of the area to be annealed – in this case the ohmic contact 5. In that way the light 28 passing through the aperture 26 only contacts the ohmic contact 5 and not the epitaxial layers 1. There may be the same number of apertures 26 in

25 screen 24, and their location and spacing may be the same, as the ohmic contact 5.

30 This has the advantage of reducing fabrication time, reducing risk of cross-contamination of wafers, and increasing productivity. It also enables device repair, and localized annealing.

35 By use of this invention, localized optical annealing is used in semiconductor device fabrication, where the original wafer substrate is removed and the semiconductor layers are transferred to a new substrate either before or after the optical annealing. Both laser annealing and lamp annealing may be used. Laser annealing can be applied to where annealing is required by directing the laser beam to that area. A broad light beam that is generated by a lamp, a bank of

lamps, or a broadened laser beam can also be applied to the whole surface of the wafer, or to an interface in the wafer if the light is so chosen that it can pass certain layers (or substrate) of the wafer without being significantly absorbed before reaching the interface.

5

The above-described process may also be used to anneal a more substantial metal layer such as, for example, the second substrate 4. In this case, and as the second substrate 4 is a layer of a metal (copper) that has high conductivity, the beam 16 does not need to be applied to the entirety of the metal layer 4, but is 10 applied sequentially to locations on the surface of the metal layer 4 for annealing of the metal layer 4 to take place. The number and spacing of the locations, the duration of the application of the beam 16 at each location, the intensity of the laser beam 16 and the frequency of the laser beam 16 will be determined by the metal of the metal layer 4, and the thickness of the metal layer 4. Alternatively, the beam 15 16 may be applied simultaneously to the number of locations. Preferably, the order of application of the beam 16 matches heat flow in the metal layer 4 to maximize the annealing. If the beam 16 is from a lamp or bank of lamps, the aperture(s) 26 will be sized, shaped, spaced and located to substantially match the size, shape, spacing and location of the metal layers 4.

20

The beam 16 may be applied directly to the at least one metal layer 22, or may be applied to the at least one metal layer 22 through the semiconductor device 20. In the latter case, the beam 16 is preferably applied to the interface between the at least one metal layer 22 and the semiconductor devices 20.

25

If there is more than one layer in the least one metal layer 22, each layer may be annealed sequentially, or simultaneously.

30

The nature of the beam 16 will depend significantly on the materials of the ohmic or metal layer 5, and the epitaxial layers 1. This will include the thickness of the ohmic or metal layer 5. For a laser beam 16, the nature of the laser, especially the laser wavelength and the laser conditions, will be determined in this way. Laser conditions include pulse width of the laser, number of pulses, the frequency of the pulses, and the power and density of the laser beam.

35

Whilst there has been described in the foregoing description preferred embodiments of the present invention, it will be understood by those skilled in the

technology concerned that many variations or modifications in details of design or construction may be made without departing from the present invention.

## THE CLAIMS

1. In the process for the fabrication of semiconductor devices being fabricated on a substrate and including at least one metal layer and a plurality of semiconductor layers on the 5 substrate, the improvement comprising:

removing the substrate and applying a second substrate to the semiconductor devices, and

annealing the at least one metal layer by application of a beam of electromagnetic radiation on the least one metal layer.

10 2. The improvement of claim 1, wherein the second substrate is applied to the semiconductor devices before the substrate is removed.

3. The improvement of claim 1, wherein the second substrate is applied to the semiconductor devices after the substrate is removed.

15 4. The improvement of claim 1, wherein the second substrate is applied to the semiconductor devices on a second surface of the semiconductor devices, the substrate having been removed from a first surface of the semiconductor devices, the first and second surfaces being different.

5. The improvement of claim 4, wherein the first surface is opposite the second surface.

6. The improvement of claim 1, wherein the beam of electromagnetic radiation is applied 20 at a number of locations on the at least one metal layer.

7. The improvement of claim 6, wherein the number and spacing of the locations is determined by the metal of the at least one metal layer, and a thickness of the at least one metal layer.

8. The improvement of claim 6, wherein the laser beam is applied sequentially to the 25 number of locations.

9. The improvement as claimed in claim 1, wherein a mask is placed between a source of the beam of electromagnetic radiation and the semiconductor devices; the mask having at least

one aperture therethrough for the passage through the at least one aperture of the beam of electromagnetic radiation.

10. The improvement as claimed in claim 9, wherein the at least one aperture is sized and shaped to be substantially the same as the at least one metal layer.

5 11. The improvement of any one of claims 1 to 10, wherein the duration, wavelength, radiation power, and radiation power density of the application of the electromagnetic beam are determined by the metal of the at least one metal layer, and the thickness of the at least one metal layer, and the materials of the semiconductor devices.

10 12. The improvement of any one of claims 1 to 10, wherein the laser beam is of a frequency and intensity determined by the metal of the at least one metal layer, the thickness of the at least one metal layer, and the material of the semiconductor devices.

13. The improvement of any one of claims 1 to 10, wherein there are a plurality of metal layers, the plurality of metal layers being annealed in a manner selected from the group consisting of: sequentially, and simultaneously.

15 14. The improvement of any one of claims 1 to 10, wherein the beam of electromagnetic radiation is applied in a manner selected from the group consisting of: directly on the at least one metal layer, and through the semiconductor device to the at least one metal layer.

15. The improvement as claimed in any one of claims 1 to 10, wherein the beam of electromagnetic radiation is applied to an interface between the at least one metal layer and the 20 semiconductor device.

16. The improvement as claimed in any one of claims 1 to 10, wherein the at least one metal layer is an ohmic contact layer.

17. The improvement of any one of claims 1 to 10, wherein the beam of electromagnetic radiation is selected from the group consisting of: a laser beam, light from at least one lamp, and 25 light from a bank of lamps.

18. A process for the fabrication of semiconductor devices being fabricated on a substrate and including at least one metal layer, the process comprising:

removing the substrate and applying a second substrate to the second semiconductor devices; and

annealing the at least one metal layer by application of a beam of electromagnetic radiation on the at least one metal layer.

5 19. The process of claim 18, wherein the second substrate is applied to the semiconductor devices before the substrate is removed.

20. The process of claim 18, wherein the second substrate is applied to the semiconductor devices after the substrate is removed.

10 21. The process of claim 18, wherein the second substrate is applied to the semiconductor devices on a second surface of the semiconductor devices, the substrate been removed from a first surface of the semiconductor devices, the first and second surfaces being different.

22. The process of claim 21, wherein the first surface is opposite the second surface.

23. The process of claim 18, wherein the beam of electromagnetic radiation is applied at a number of locations on the at least one metal layer.

15 24. The process of claim 23, wherein the number and spacing of the locations is determined by the metal of the at least one metal layer, and a thickness of the at least one metal layer.

25. The process of claim 23, wherein the laser beam is applied sequentially to the number of locations.

20 26. The process as claimed in claim 18, wherein a mask is placed between a source of the beam of electromagnetic radiation and the semiconductor devices; the screen having at least one aperture therethrough for the passage through the at least one aperture of the beam of electromagnetic radiation.

27. The process as claimed in claim 26, wherein the at least one aperture is sized and shaped to be substantially the same as the at least one metal layer.

25 28. The process of any one of claims 18 to 27, wherein the duration, wavelength, radiation power, and radiation power density of the application of the electromagnetic beam are

determined by the metal of the at least one metal layer, and the thickness of the at least one metal layer, and the materials of the semiconductor devices.

29. The process of any one of claims 18 to 27, wherein the laser beam is of a frequency and intensity determined by the metal of the at least one metal layer, and the thickness of the at least 5 one metal layer, and the semiconductor devices material.

30. The process of any one of claims 18 to 27, wherein there are a plurality of metal layers, the plurality of metal layers being annealed in a manner selected from the group consisting of: sequentially, and simultaneously.

31. The process of any one of claims 18 to 27, wherein the beam of electromagnetic 10 radiation is applied in a manner selected from the group consisting of: directly on the at least one metal layer, and through the semiconductor device to the at least one metal layer.

32. The process as claimed in any one of claims 18 to 27, wherein the beam of electromagnetic radiation is applied to an interface between the at least one metal layer and the semiconductor device.

15 33. The process as claimed in any one of claims 18 to 27, wherein the at least one metal layer is an ohmic contact layer.

34. The process of any one of claims 18 to 27, wherein the beam of electromagnetic radiation is selected from the group consisting of: a laser beam, light from at least one lamp, and light from a bank of lamps.

**FIGURE 1****FIGURE 2****FIGURE 3**

2/4

**FIGURE 4****FIGURE 5**

FIGURE 6

FIGURE 7

4/4

**FIGURE 8****FIGURE 9**

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/SG2006/000395

## A. CLASSIFICATION OF SUBJECT MATTER

Int. Cl.

**H01L 33/00** (2006.01)      **H01L 21/00** (2006.01)      **H01L 27/00** (2006.01)

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

DWPI: semiconductor? AND (metal+ (w) +layer?) AND (anneal+ or heat+) AND fabricat+ [and similar terms corresponding to these]

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                              | Relevant to claim No. |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 2004/0104395 A (HAGIMOTO <i>et. al.</i> ) 3 June 2004<br>Whole document and in particular abstract, Figures, paragraphs [0025]-[0028], [0276]-[0280], [0313] | 1-34                  |

| X, Y      | US 6365429 B (KNEISSL <i>et. al.</i> ) 2 April 2002<br>Whole document and in particular Figures, col. 10, line 11+                                              | 1, 18                 |

| Y         | US 5405804 A (YABE) 11 April 1995<br>Whole document and in particular Fig. 5, col. 5, line 6-8                                                                  | 1, 17, 18, 34         |

Further documents are listed in the continuation of Box C See patent family annex

|                                                                                                                                                                         |     |                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| * Special categories of cited documents:                                                                                                                                |     |                                                                                                                                                                                                                                              |

| "A" document defining the general state of the art which is not considered to be of particular relevance                                                                | "T" | later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                              |

| "E" earlier application or patent but published on or after the international filing date                                                                               | "X" | document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone                                                                     |

| "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) | "Y" | document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art |

| "O" document referring to an oral disclosure, use, exhibition or other means                                                                                            | "&" | document member of the same patent family                                                                                                                                                                                                    |

| "P" document published prior to the international filing date but later than the priority date claimed                                                                  |     |                                                                                                                                                                                                                                              |

Date of the actual completion of the international search

16 February 2007

Date of mailing of the international search report

26 FEB 2007

Name and mailing address of the ISA/AU

AUSTRALIAN PATENT OFFICE

PO BOX 200, WODEN ACT 2606, AUSTRALIA

E-mail address: pct@ipaaustralia.gov.au

Facsimile No. (02) 6285 3929

Authorized officer

LYNN BLOOMFIELD

Telephone No : (02) 6283 2851

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/SG2006/000395

| C (Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT   |                                                                                                                               |                       |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category*                                               | Citation of document, with indication, where appropriate, of the relevant passages                                            | Relevant to claim No. |

| Y                                                       | US 6420242 B (CHEUNG <i>et. al.</i> ) 16 July 2002<br>Whole document and in particular Fig. 2-5 and col. 4                    | 1, 17, 18, 34         |

| Y                                                       | EP 1139409 A (AGERE SYSTEMS GUARDIAN CORPORATION) 4 October 2001<br>Whole document and in particular paragraphs [0043]-[0045] | 1, 17, 18, 34         |

| A                                                       | US 2002/0179910 A (SLATER, JR) 5 December 2002<br>Whole document                                                              | 1-34                  |

| A                                                       | US 6573537 B (STEIGERWALD <i>et. al.</i> ) 3 June 2003<br>Whole document                                                      | 1-34                  |

| A                                                       | WO 2005/088743 A (TINGGI TECHNOLOGIES PRIVATE LIMITED)<br>22 September 2005<br>Whole document                                 | 1-34                  |

| Any of the Y documents can be combined with US 6365429. |                                                                                                                               |                       |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No.

PCT/SG2006/000395

This Annex lists the known "A" publication level patent family members relating to the patent documents cited in the above-mentioned international search report. The Australian Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

| Patent Document Cited in Search Report |            |    | Patent Family Member |    |            |    |

|----------------------------------------|------------|----|----------------------|----|------------|----|

| US                                     | 2004104395 | JP | 2004207508           | JP | 2004228540 | JP |

|                                        |            | JP | 2004235506           | JP | 2004235581 | JP |

| US                                     | 6365429    | JP | 2000196197           | US | 6448102    | US |

|                                        |            | US | 6757314              | US | 2004105471 |    |

| US                                     | 5405804    | JP | 6310500              |    |            |    |

| US                                     | 6420242    | US | 6071795              |    |            |    |

| EP                                     | 1139409    | JP | 2001313390           | KR | 2001008572 | US |

| US                                     | 2002179910 | AU | 63916/99             | CA | 2343416    | CA |

|                                        |            | CN | 1323446              | CN | 1579008    | EP |

|                                        |            | EP | 1440460              | KR | 2005003517 | MX |

|                                        |            | US | 6803243              | US | 6884644    | US |

|                                        |            | US | 2004171204           | WO | 0016382    | WO |

| US                                     | 6573537    | AU | 27389/01             | DE | 10213701   | EP |

|                                        |            | JP | 2001237458           | JP | 2002335014 | US |

|                                        |            | WO | 0147039              |    |            |    |

| WO                                     | 2005088743 | EP | 1730790              |    |            |    |

Due to data integration issues this family listing may not include 10 digit Australian applications filed since May 2001.

END OF ANNEX