(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5478855号

(P5478855)

(45) 発行日 平成26年4月23日(2014.4.23)

(24) 登録日 平成26年2月21日(2014.2.21)

(51) Int.Cl.

G06F 12/16 (2006.01)

G11C 16/02 (2006.01)

F 1

G06F 12/16 310A

G11C 17/00 601B

G11C 17/00 601E

G11C 17/00 614

請求項の数 4 (全 24 頁)

(21) 出願番号 特願2008-205414 (P2008-205414)

(22) 出願日 平成20年8月8日 (2008.8.8)

(65) 公開番号 特開2010-39983 (P2010-39983A)

(43) 公開日 平成22年2月18日 (2010.2.18)

審査請求日 平成23年8月3日 (2011.8.3)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部 1753 番地

(74) 代理人 100089071

弁理士 玉村 静世

(72) 発明者 望月 義則

神奈川県川崎市麻生区王禅寺 1099 番地

株式会社日立製作所 システム開発研究所内

(72) 発明者 受田 賢知

神奈川県川崎市麻生区王禅寺 1099 番地

株式会社日立製作所 システム開発研究所内

最終頁に続く

(54) 【発明の名称】不揮発性メモリ制御方法及び半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のページを含んで構成され、上記ページ単位でアクセス可能な不揮発性メモリと、乱数を生成可能な乱数発生器と、

上記乱数発生器に結合され、且つ、上記不揮発性メモリにアクセス可能なコントローラと、を有するシステムでの不揮発性メモリ制御方法であって、

上記不揮発性メモリへのアクセスが行われる毎に、上記アクセス対象のページとは無関係に、上記乱数発生器で発生された乱数に基づいて、リフレッシュ対象のページを決定し、当該ページに対して再書き込みを行うリフレッシュ制御を上記コントローラに実行させ、

上記不揮発性メモリは、それぞれがN個のページで構成される1または複数のブロックを含んで構成され、

上記乱数発生器によって生成される乱数の最大値は、上記Nより大きく、

上記不揮発性メモリへのアクセスが行われる毎に、上記乱数発生器で発生された乱数に対応するページがある場合は、当該ページに対して再書き込みを行うリフレッシュ制御を上記コントローラに実行させ、上記乱数発生器で発生された乱数に対応するページがない場合には、リフレッシュ制御を省略することを特徴とする不揮発性メモリ制御方法。

## 【請求項 2】

上記乱数は真正乱数である、請求項1記載の不揮発性メモリ制御方法。

## 【請求項 3】

複数のページを含んで構成され、上記ページ単位でアクセス可能な不揮発性メモリを含む半導体装置であって、

乱数を生成可能な乱数発生器と、

上記不揮発性メモリへのアクセスが行われる毎に、上記アクセス対象のページとは無関係に、上記乱数発生器で発生された乱数に基づいて、リフレッシュ対象ページを決定し、当該ページに対して再書き込みを行うリフレッシュ制御を実行するコントローラと、を含み、

上記不揮発性メモリは、それぞれがN個のページで構成される1または複数のブロックを含んで構成され、

上記乱数発生器によって生成される乱数の最大値は、上記Nより大きく、

10

上記不揮発性メモリへのアクセスが行われる毎に、上記乱数発生器で発生された乱数に対応するページがある場合は、当該ページに対して再書き込みを行うリフレッシュ制御を上記コントローラに実行させ、上記乱数発生器で発生された乱数に対応するページがない場合には、リフレッシュ制御を省略することを特徴とする半導体装置。

**【請求項4】**

上記乱数は真正乱数である、請求項3記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、不揮発性メモリにおけるリフレッシュ制御技術に関し、例えば不揮発性メモリを備えたマイクロコンピュータに適用して有効な技術に関する。 20

**【背景技術】**

**【0002】**

大容量のメモリに対する要望が高まっており、不揮発性メモリが広く使用されるようになってきている。不揮発性メモリの大容量化を阻害する大きな要因としては、チップ面積の増大によるチップコストの増大がある。不揮発性メモリにおけるチップ面積の縮小化のために1ビット/1トランジスタで構成されたSingle·MONOS (Metal Oxide Nitride Oxide Semiconductor) メモリが提案されている(例えば特許文献1参照)。

**【0003】**

**【特許文献1】特開2006-185530号公報**

30

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0004】**

1ビット/1トランジスタで構成されたSingle·MONOSメモリにおいては、特許文献1の図1A-図1Dに示されるような所定電圧をメモリゲートMG、ウェル、ソース(S)及びドレイン(D)に印加することにより、選択したビットに対して消去、書き込み及び読み出しを行うことができる。また、この場合、選択していないビット(非選択ビット)の誤動作を防ぐため、非選択ビットに阻止電圧を印加する必要がある。しかし、それについて本願発明者が検討したところ、上記阻止電圧の印加によって、消去、書き込み及び読み出し時に非選択ビットが弱い消去状態もしくは書き込み状態になり、それによってメモリセルの閾値(Vth)が変動する現象(これを「ディスターク」)という)が生じてしまう。ディスターク対策として、書き込み毎に、あるいは読み出し毎に、若しくは消去毎に、再書き込みによるリフレッシュを行うことが考えられる。しかし、書き込み毎に、あるいは読み出し毎に、若しくは消去毎にリフレッシュを行うようにすると、このリフレッシュ動作によって各ページの書き込み回数が不所望に増大する虞がある。 40

**【0005】**

本発明の目的は、不揮発性メモリにおいて、書き込み回数を不所望に増大させることなく、閾値を変動前の状態に戻すための技術を提供することにある。

**【0006】**

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明ら

50

かになるであろう。

【課題を解決するための手段】

【0007】

本願において開示される発明のうち代表的なものについて簡単に説明すれば下記のとおりである。

【0008】

すなわち、不揮発性メモリと、乱数発生器と、上記不揮発性メモリにアクセス可能なコントローラとを含むシステムで、上記不揮発性メモリへのアクセスが行われる毎に、上記乱数発生器で発生された乱数に基づいて、リフレッシュ対象領域を上記コントローラで決定する。そして、上記リフレッシュ対象領域に対して再書き込みを行うリフレッシュ制御を上記コントローラに実行させる。このようなリフレッシュ制御によって、書き込み回数を不所望に増大させることなく、閾値を変動前の状態に戻すことができる。

10

【0009】

また、上記不揮発性メモリにおける全てのアクセス対象領域についてのアクセス回数の合計値と、リフレッシュ対象領域とを管理し、上記不揮発性メモリに対するアクセスが発生される毎に、上記不揮発性メモリに対するアクセス回数の合計値を更新し、その更新結果に基づいて、上記リフレッシュ対象領域に対して再書き込みを行うリフレッシュ制御を上記コントローラに実行させる。これにより、不揮発性メモリにおけるアクセス対象領域について偏りなくリフレッシュすることができる。そしてこのリフレッシュによって、メモリセルの閾値を変動前の状態に戻すことができる。

20

【発明の効果】

【0010】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記の通りである。

【0011】

すなわち、不揮発性メモリにおいて、書き込み回数を不所望に増大させることなく、閾値を変動前の状態に戻すことができる。

【発明を実施するための最良の形態】

【0012】

1. 代表的な実施の形態

30

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面の参照符号はそれが付された構成要素の概念に含まれるものを見示すに過ぎない。

【0013】

[1] 本発明の代表的な実施の形態に係る不揮発性メモリ制御方法は、不揮発性メモリ(14)と、乱数を生成可能な乱数発生器(12)と、上記乱数発生器に結合され、且つ、上記不揮発性メモリにアクセス可能なコントローラ(15)とを含むシステムで実施する。すなわち、上記不揮発性メモリへのアクセスが行われる毎に、上記乱数発生器で発生された乱数に基づいて、リフレッシュ対象領域を決定し、当該領域に対して再書き込みを行うリフレッシュ制御を上記コントローラに実行させる。

40

【0014】

このような制御方法によれば、上記乱数発生器で発生された乱数に基づいて、リフレッシュ対象領域が決定され、当該領域に対して再書き込みが不揮発性メモリにおける各アクセス対象領域(Page 1 ~ Page N)について偏りなくリフレッシュすることができる。そしてこのリフレッシュによって、メモリセルの閾値を変動前の状態に戻すことができる。また、上記不揮発性メモリへのアクセスが行われる毎に乱数が発生され、その乱数に対応するアクセス対象領域について再書き込みが行われるので、リフレッシュに起因して書き込み回数が不所望に増大するのを回避することができる。

【0015】

[2] 上記不揮発性メモリにおける全てのアクセス対象領域についてのアクセス回数の

50

合計値と、リフレッシュ対象領域とを管理し、上記不揮発性メモリに対するアクセスが発生される毎に、上記不揮発性メモリに対するアクセス回数の合計値を更新し、その更新結果に基づいて、上記リフレッシュ対象領域に対して再書き込みを行うリフレッシュ制御を上記コントローラに実行させる。これにより、不揮発性メモリにおけるアクセス対象領域（Page 1 ~ Page N）について偏りなくリフレッシュすることができる。そしてこのリフレッシュによって、メモリセルの閾値を変動前の状態に戻すことができる。

【0016】

[3] 上記〔2〕において、上記コントローラでのリフレッシュ制御は、上記不揮発性メモリに対するアクセスが発生される毎に、上記不揮発性メモリにおける全てのアクセス対象領域についてのアクセス回数の合計値を取得する第1処理（602, 1001）と、上記第1処理で取得された合計値と、所定の閾値とを比較する第2処理（603, 1004）と、上記第2処理での比較結果に応じて、上記リフレッシュ対象領域に対する再書き込みを実行する第3処理（605, 1006）と、上記第3処理の後に、必要に応じて上記閾値を更新する第4処理（607, 1009）とを含めることができる。10

【0017】

[4] 上記〔2〕において、上記コントローラでのリフレッシュ制御は、上記不揮発性メモリに対するアクセスが発生される毎に、上記不揮発性メモリにおける全てのアクセス対象領域についてのアクセス回数の合計値と、アクセス対象領域毎のアクセス回数との差分を得る第5処理（1202, 1404）と、

上記第5処理で得られた差分と所定の閾値とを比較する第6処理（1203, 1405）と、20

上記第6処理で求められた差分に応じてリフレッシュ対象領域を決定し、そのリフレッシュ対象領域に対してリフレッシュのための再書き込みを実行する第7処理（1204, 1406）とを含めることができる。

【0018】

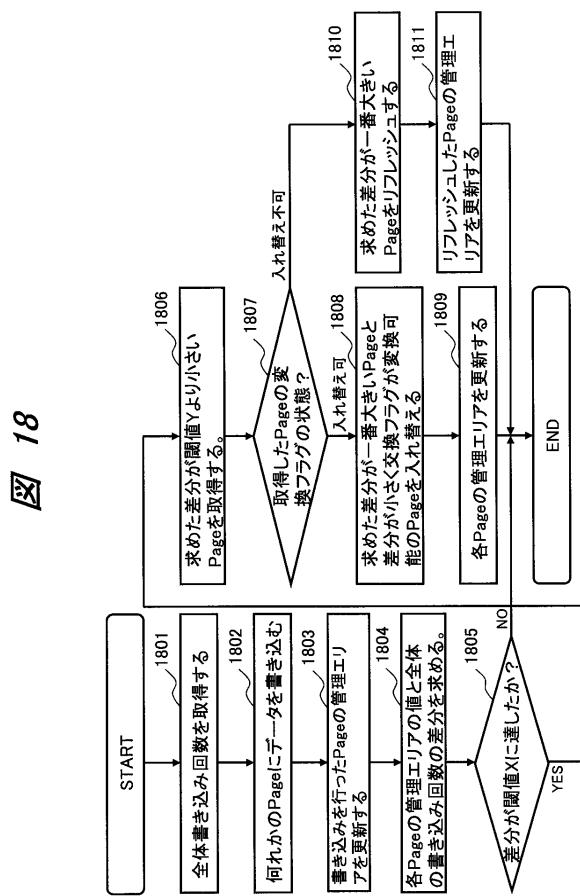

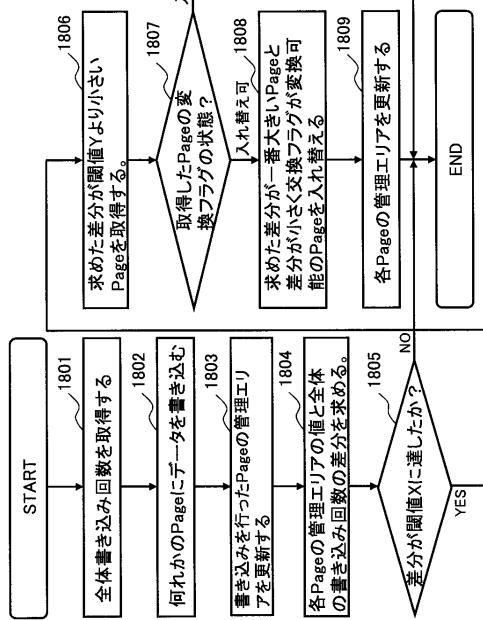

[5] 上記〔2〕において、上記コントローラでのリフレッシュ制御には、上記不揮発性メモリに対するアクセスが発生される毎に、上記不揮発性メモリにおける全てのアクセス対象領域についてのアクセス回数の合計値と、上記不揮発性メモリにおけるアクセス対象領域毎のアクセス回数との差分を得る第8処理（1804）と、上記第8処理で得られた差分のうち、所定の閾値より小さな差分に対応する第1アクセス対象領域を取得する第9処理（1806）とを含めることができる。そして、上記第9処理で取得された第1アクセス対象領域がそれとは異なる第2アクセス対象領域との間で、論理アドレスに対する物理アドレスの入れ替えが可能か否かの判別を行う第10処理（1807）と、上記第10処理での判別において、論理アドレスに対する物理アドレスの入れ替えが可能であると判断された場合には、上記第1アクセス対象領域と上記第2アクセス対象領域との間で論理アドレスに対する物理アドレスの入れ替えを行う第11処理（1808）とを含めることができる。さらに、上記第10処理での判別において、論理アドレスに対する物理アドレスの入れ替えが不可能であると判断された場合には、上記第8処理で求められた差分に応じてリフレッシュ対象領域を決定し、そのリフレッシュ対象領域に対してリフレッシュのための再書き込みを実行する第12処理（1810）とを含めることができる。30

【0019】

[6] 上記〔5〕において、上記第2アクセス対象領域は、上記第8処理で得られた差分に基づいて決定することができる。

【0020】

[7] 本発明の代表的な実施の形態に係る半導体装置（10）は、不揮発性メモリ（14）を含む。そして、乱数を生成可能な乱数発生器（12）と、上記不揮発性メモリへのアクセスが行われる毎に、上記乱数発生器で発生された乱数に基づいて、リフレッシュ対象領域を決定し、当該領域に対して再書き込みを行うリフレッシュ制御を実行するコントローラ（15）とが設けられる。

【0021】

50

〔8〕本発明の代表的な実施の形態に係る半導体装置(10)は不揮発性メモリ(14)を含む。そして、上記不揮発性メモリにおける全てのアクセス対象領域についてのアクセス回数の合計値とリフレッシュ対象領域とを管理可能な管理エリア(51)と、上記不揮発性メモリに対するアクセスが発生される毎に、上記不揮発性メモリに対するアクセス回数の合計値を更新し、その更新結果に基づいて、上記リフレッシュ対象領域に対して再書き込みを行うリフレッシュ制御を実行するコントローラ(15)とが設けられる。

【0022】

〔9〕上記〔8〕において、上記管理エリアは、上記不揮発性メモリにおける記憶領域の一部を使って形成することができる。

【0023】

〔10〕上記〔8〕において、上記不揮発性メモリとは別に設けられた半導体メモリに形成することができる。

【0024】

〔11〕上記〔8〕において、上記コントローラに、上記不揮発性メモリに対するアクセスが発生される毎に、上記不揮発性メモリにおける全てのアクセス対象領域についてのアクセス回数の合計値を取得する第1処理(602,1001)と、

上記第1処理で取得された合計値と、所定の閾値とを比較する第2処理(603,1004)と、

上記第2処理での比較結果に応じて、上記リフレッシュ対象領域に対する再書き込みを実行する第3処理(605,1006)と、

上記第3処理の後に、必要に応じて上記閾値を更新する第4処理(607,1009)とを実行させることができる。

【0025】

〔12〕上記〔8〕において、上記コントローラに、上記不揮発性メモリに対するアクセスが発生される毎に、上記不揮発性メモリにおける全てのアクセス対象領域についてのアクセス回数の合計値と、アクセス対象領域毎のアクセス回数との差分を得る第5処理(1202,1404)と、

上記第5処理で得られた差分と所定の閾値とを比較する第6処理(1203,1405)と、

上記第6処理で求められた差分に応じてリフレッシュ対象領域を決定し、そのリフレッシュ対象領域に対してリフレッシュのための再書き込みを実行する第7処理(1204,1406)とを実行させることができる。

【0026】

〔13〕上記〔8〕において、上記半導体装置は、外部から与えられた論理アドレスを上記不揮発性メモリにおける物理アドレスに変換するための論理/物理アドレス変換テーブル(17)を更に含む。そして、上記コントローラには、上記不揮発性メモリに対するアクセスが発生される毎に、上記不揮発性メモリにおける全てのアクセス対象領域についてのアクセス回数の合計値と、不揮発性メモリにおけるアクセス対象領域毎のアクセス回数との差分を得る第8処理(1804)と、上記第8処理で得られた差分のうち、所定の閾値より小さな上記差分に対応する第1アクセス対象領域を取得する第9処理(1806)とを実行させることができる。さらに上記コントローラには、上記第9処理で取得された第1アクセス対象領域がそれとは異なる第2アクセス対象領域との間で、論理アドレスに対する物理アドレスの入れ替えが可能か否かの判別を行う第10処理(1807)と、上記第10処理での判別において、論理アドレスに対する物理アドレスの入れ替えが可能であると判断された場合には、上記第1アクセス対象領域と上記第2アクセス対象領域との間で論理アドレスに対する物理アドレスの入れ替えを行う第11処理(1808)とを実行させることができる。そして、上記コントローラには、上記第10処理での判別において、論理アドレスに対する物理アドレスの入れ替えが不可能であると判断された場合には、上記第8処理で求められた差分に応じてリフレッシュ対象領域を決定し、そのリフレッシュ対象領域に対してリフレッシュのための再書き込みを実行する第12処理(181

10

20

30

40

50

0)とを実行させることができる。

【0027】

[14]上記アクセス対象領域は、上記不揮発性メモリがセクタ単位でアクセスされる場合には「セクタ」とされ、上記不揮発性メモリがページ単位でアクセスされる場合には「ページ」とされ、上記不揮発性メモリがブロック単位でアクセスされる場合には「ブロック」とされる。また、上記アクセスには、上記不揮発性メモリへの書き込みのためのアクセス、上記不揮発性メモリの消去のためのアクセス、上記不揮発性メモリからの読み出しのためのアクセスが含まれる。

【0028】

2. 実施の形態の説明

10

次に、実施の形態について更に詳述する。

【0029】

<実施の形態1>

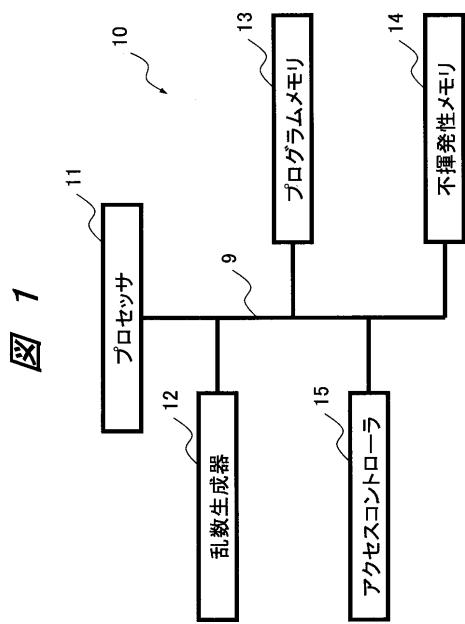

図1には、本発明にかかる半導体装置の一例とされるマイクロコンピュータの構成例が示される。図1に示されるマイクロコンピュータ10は、特に制限されないが、プロセッサ11、乱数発生器12、プログラムメモリ13、不揮発性メモリ14、及びアクセスコントローラ15を含み、公知の半導体集積回路製造技術により、単結晶シリコン基板などの一つの半導体基板に形成される。プロセッサ11、乱数発生器12、プログラムメモリ13、及び不揮発性メモリ14は、バス9を介して互いに各種信号のやり取りが可能に結合される。不揮発性メモリ14は、例えば1ビット/1トランジスタで構成されたSingle MONOS(Metal Oxide Nitride Oxide Semiconductor)メモリとされる。

20

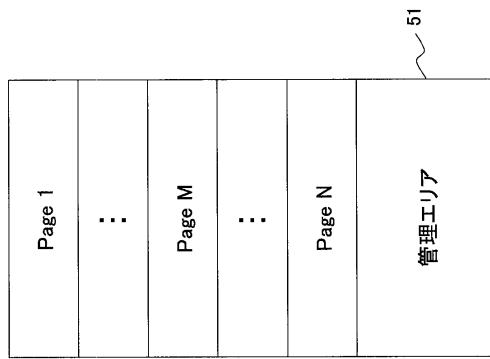

【0030】

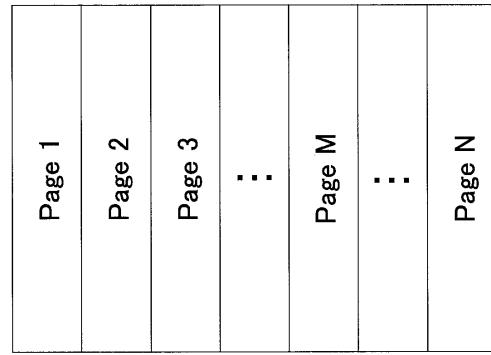

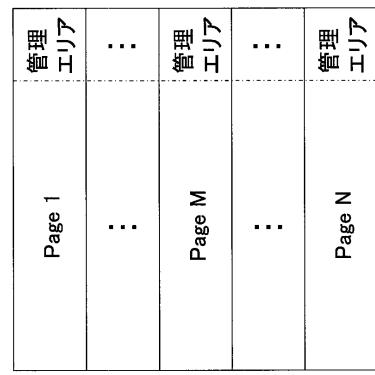

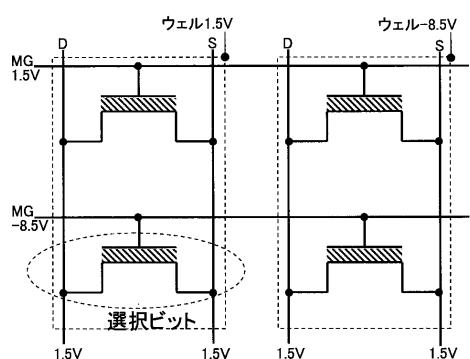

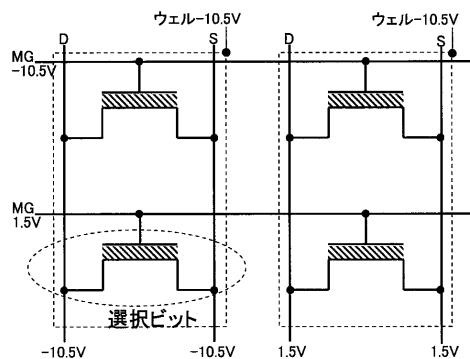

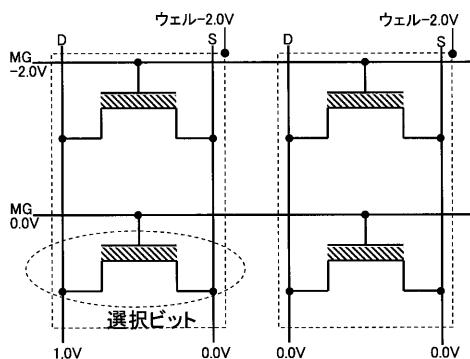

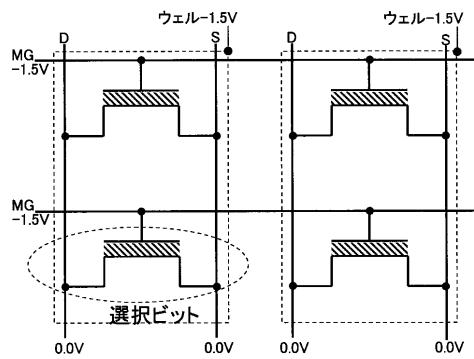

上記不揮発性メモリ14は、複数の不揮発性メモリセルがアレイ状に配列されて成り、上記プロセッサ11には、処理に用いられる各種データが格納される。不揮発性メモリ14は、複数のブロックによって構成され、各ブロックはさらに図2に示されるように、複数のページPage1~PageNによって構成される。書き込みや消去や読み出しへは、このページ単位で行われる。消去や、書き込み、読み出しなどの各モードにおいて所定の動作バイアスが印加されるようになっている。例えば図20Aに示されるように、消去時には、メモリゲート(MG)に-8.5V、ウェル、ソース(S)及びドレイン(D)に電源電圧である1.5Vを印加し、トンネル効果でNitride膜中の電子をウェル側に抜くことにより、メモリセルの閾値(Vth)をマイナス側にしている。図20Bに示されるように、書き込み時には、メモリゲートMGに1.5V、ウェル、ソース(S)及びドレイン(D)に-10.5Vを印加し、トンネル効果でNitride膜中に電子を注入することにより、メモリセルの閾値(Vth)をプラス側にしている。図20Cに示されるように、読み出し時には、選択するMGに0V、ソース(S)を0V、ドレイン(D)に1.0Vを設定することで、もしメモリセルが消去状態であれば、Vthがマイナスのため、ドレイン(D)-ソース(S)間に電流が流れ、ドレイン電位が下がるのを検出し、メモリセルが書き込み状態であれば、Vthがプラスのため、ドレイン(D)-ソース(S)間には電流が流れずドレイン電位は1Vのままキープされることを検出することになる。また、図20Dに示されるように、スタンバイ時には、MG、ウェルをメモリセル消去Vth以下である-1.5Vを印加することにしている。

30

【0031】

図20A-図20Dに示されるような所定電圧をメモリゲートMG、ウェル、ソース(S)及びドレイン(D)に印加することにより、選択したビットに対して消去、書き込み及び読み出しを行うことができる。また、この場合、選択していないビット(非選択ビット)の誤動作を防ぐため、非選択ビットに阻止電圧を印加する必要がある。しかし、上記阻止電圧の印加によって、消去、書き込み及び読み出し時に非選択ビットが弱い消去状態もしくは書き込み状態になり、それによってメモリセルの閾値(Vth)が変動、すなわちディスターべを生ずる。ディスターべ対策として、書き込み毎に、あるいは読み出し毎に

40

50

、若しくは消去毎に、再書き込みによるリフレッシュを行うことが考えられるが、書き込み毎に、あるいは読み出し毎に、若しくは消去毎にリフレッシュを行うようになると、このリフレッシュ動作によって各ページの書き込み回数が不所望に増大する虞がある。そこで本例では以下のようにリフレッシュを行うようにしている。

【0032】

上記乱数発生器12は、真性乱数、すなわち、出現する数に偏りが無い乱数を発生する。上記プロセッサ11は、所定のプログラムに従って所定の演算処理を実行する。また、上記プロセッサ11は、マイクロコンピュータ10全体の動作制御を司る。本例において上記不揮発性メモリ14のリフレッシュ制御は、上記プロセッサ11や上記アクセスコントローラ15等によって行われるが、本説明では、アクセスコントローラ15が行うものとする。上記アクセスコントローラ15によるリフレッシュ制御では、上記不揮発性メモリ14への書き込みが行われる毎に、上記乱数発生器12で発生された乱数に基づいてリフレッシュ対象ページが決定され、当該ページに対して再書き込みが行われるようになっている。

10

【0033】

ここで、上記乱数発生器12で生成される乱数の最大値は、上記不揮発性メモリ14における総ページ数Nよりも十分に大きな値とされる。このようにするのは、本例のリフレッシュ制御では、発生された乱数の値が1～Nに含まれるか否かを判定し、乱数の値が1～Nに含まれる場合にリフレッシュのための再書き込みが実行されるためである。仮に、上記乱数発生器12で生成される乱数の最大値を上記不揮発性メモリ14における総ページ数Nよりも小さな値とした場合には、乱数が発生される毎にリフレッシュのための再書き込みが実行されてしまい、その結果、必要以上にリフレッシュが行われることになる。

20

【0034】

上記プログラムメモリ13には、上記プロセッサ11で実行されるプログラムが格納されている。

【0035】

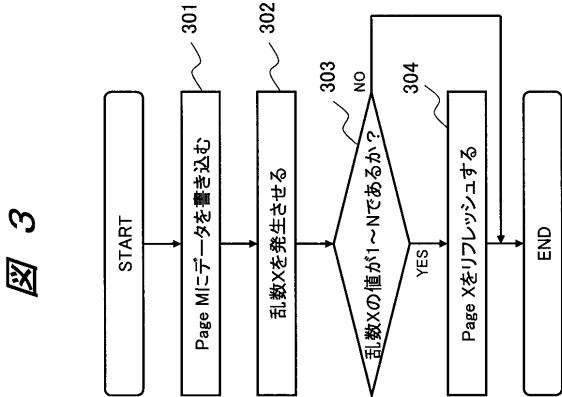

図3には、リフレッシュ制御の流れが示される。

【0036】

プロセッサ11がアクセスコントローラ15に、何れかのページ、例えばPageMへのデータ書き込みを要求し、アクセスコントローラ15がPageMにデータを書き込むと(301)、アクセスコントローラ15は、さらに、乱数生成器12に対して乱数Xを発生させ(302)、発生された乱数Xの値が1～Nに含まれるか否かの判別を行う(303)。この判別において、発生された乱数の値が1～Nに含まれる(YES)と判断した場合、アクセスコントローラ15は、その乱数に対応するページ(PageX)についての再書き込みを行うことでリフレッシュを実行する。例えば発生された乱数の値が「3」の場合、Page3についてのリフレッシュが行われる。このように本例によれば、不揮発性メモリ14における何れかのページにデータが書き込まれる毎に、乱数生成器12により真性乱数が発生され、その真性乱数に対応するページについて再書き込みが行われる。ここで真性乱数は、出現する数に偏りがないので、不揮発性メモリ14における各ページ(Page1～PageN)について偏りなくリフレッシュすることができる。このリフレッシュによって、メモリセルの閾値が変動前の状態に戻される。尚、不揮発性メモリ14が複数のブロックによって構成され、各ブロックがさらに複数のページ(Page1～PageN)によって構成される場合には、当該他のブロックにおいても、上記と同様にプロセッサ11によるリフレッシュ制御が行われる。

30

40

【0037】

上記例によれば、以下の作用効果を得ることができる。

【0038】

(1) 不揮発性メモリ14における何れかのページにデータが書き込まれる毎に、乱数生成器12により真性乱数が発生され、その真性乱数に対応するページについて再書き込みが行われるので、不揮発性メモリ14における各ページ(Page1～PageN)に

50

ついて偏りなくリフレッシュすることができる。そしてこのリフレッシュによって、メモリセルの閾値が変動前の状態に戻される。

【0039】

(2) 上記(1)の作用効果により、マイクロコンピュータ10の信頼性の向上を図ることができる。

【0040】

(3) 不揮発性メモリ14において、書き込み毎に、あるいは読み出し毎に、若しくは消去毎にリフレッシュを行うようにすると、このリフレッシュ動作によって各ページの書き込み回数が不所望に増大する虞があるが、上記のように不揮発性メモリ14における何れかのページにデータが書き込まれる毎に、乱数生成器12により真性乱数が発生され、その真性乱数に対応するページについて再書き込みが行われるため、リフレッシュに起因して書き込み回数が不所望に増大されることが回避される。

【0041】

<実施の形態2>

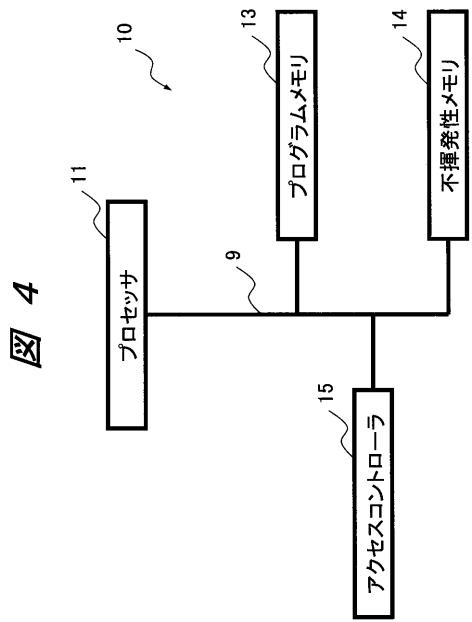

図4には、本発明にかかる半導体装置の一例とされるマイクロコンピュータの別の構成例が示される。図4に示されるマイクロコンピュータ10が図1に示されるのと大きく相違するのは、乱数発生器12が省略され、それに代えて、不揮発性メモリ14内に、リフレッシュについての管理エリアが確保されている点である。本例においてアクセスコントローラ15は、上記管理エリアでの管理情報に基づいてリフレッシュ制御を行う。上記不揮発性メモリ14は、例えば図5に示されるように、Page1～PageNとは別に、管理エリア51が設けられる。この管理エリア51には、不揮発性メモリ14における全てのページについての書き込み回数の合計値(「全体書き込み回数」という)と、リフレッシュ対象とされるページ(リフレッシュPage)を特定するための情報が設定される。この管理エリア51内の各情報は、アクセスコントローラ15によって更新される。

【0042】

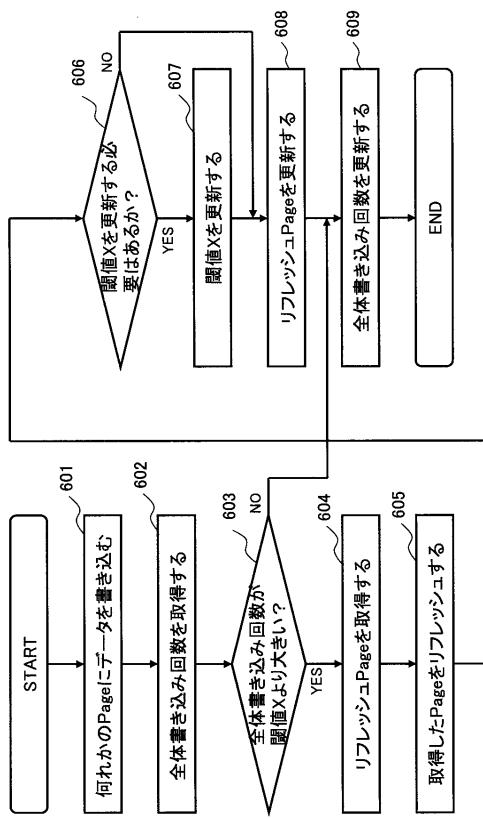

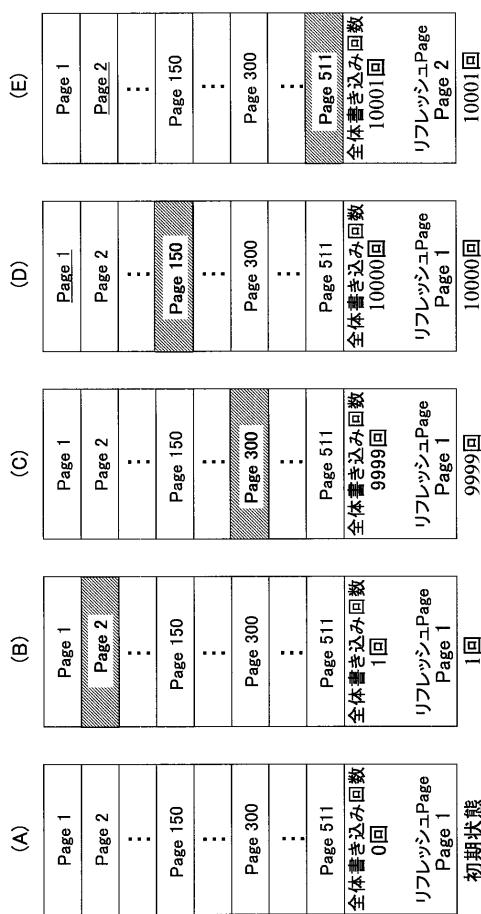

図6には、図4に示されるマイクロコンピュータ10におけるリフレッシュ制御の全体的な流れが示される。尚、このリフレッシュ制御はプロセッサ11やアクセスコントローラ15等によって行われるが、本説明では、アクセスコントローラ15が行うものとする。また、図7には上記リフレッシュ制御における不揮発性メモリ14の状態変化が示される。尚、図7において、ハッチングが付されているのは書き込みが行われるページであり、下線が付されているのはリフレッシュが行われるページである。

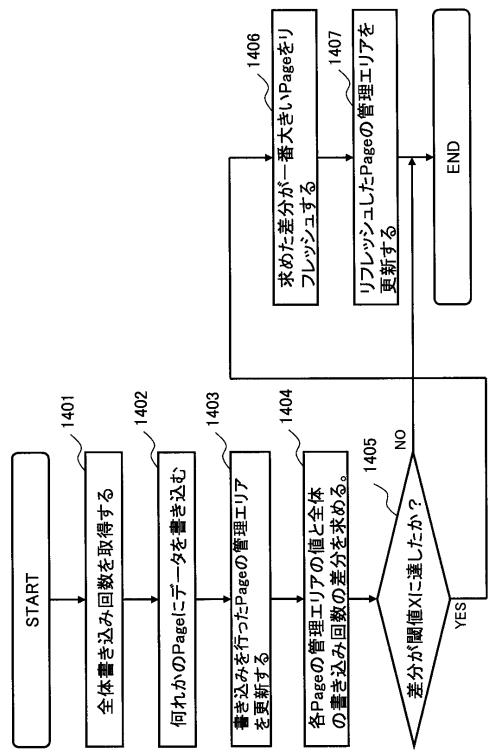

【0043】

図7(A)の状態を初期状態とする。この初期状態において、全体書き込み回数は「0」、リフレッシュPageは「Page1」とされる。また、閾値Xは、「10000」に設定される。この状態でアクセスコントローラ15の制御により上記不揮発性メモリ14へのデータ書き込みが行われる場合を考える。アクセスコントローラ15の制御により、例えば上記不揮発性メモリ14におけるPage2にデータの書き込みが行われるものとする(601)。この書き込みが終了すると、プロセッサ11により、管理エリア51が参照されることで、不揮発性メモリ14の全体書き込み回数が取得される(602)。そして、プロセッサ11において、全体書き込み回数が閾値Xより大きいか否かの判別が行われる(603)。閾値Xはプロセッサ11内の適宜のレジスタ等に設定されている。ステップ603の判別において、全体書き込み回数が閾値Xより大きいか否かの判断された場合には、アクセスコントローラ15の制御により、全体書き込み回数が更新される(609)。例えば、図7(A)の初期状態で、全体書き込み回数は「0」であり、それは閾値Xより大きくないため、ステップ603の判別において「NO」と判断され、全体書き込み回数が更新される(609)。図7(B)に示される例では、全体書き込み回数が「0」から「1」に更新されている。同様に、図7(C)に示される状態では、Page300へのデータ書き込みが行われる。このとき全体書き込み回数は「9999」となっている。図7(D)に示される状態では、Page150へのデータ書き込みが行われる。このとき全体書き込み回数は「10000」となっている。図7(E)に示され

10

20

30

40

50

る状態では、Page 511へのデータ書き込みが行われる。このとき全体書き込み回数は「10001」となり、そのときの閾値  $X = 10000$  を越えている。この状態では、ステップ 603 での判別で「YES」と判断される。そして、上記ステップ 603 の判別において、「YES」と判断された場合には、管理エリア 51 からリフレッシュ Page の情報が取得される。リフレッシュが必要か否かの判別が行われる(604)。例えば、上記ステップ 604 で取得されたリフレッシュ Page への書き込みが上記ステップ 601 で行われた場合には、このリフレッシュ Page へのリフレッシュのための再書き込みは不要である。そこで、上記ステップ 604 で取得されたリフレッシュ Page と、上記ステップ 601 で書き込みを行った Page とを比較し、同一 Page の場合には、当該ページに対するリフレッシュは不要と判断し、異なる Page の場合には、当該ページに対するリフレッシュは必要と判断する。上記ステップ 604 の判別において、リフレッシュが必要と判断された場合には、対応するページ(ここでは、Page 1)のリフレッシュ、すなわち再書き込みが実行される(605)。そして、全体書き込み回数との関係で閾値  $X$  を更新する必要があるか否かの判別が行われる(606)。また、上記ステップ 604 の判別において、リフレッシュが不要と判断された場合には、上記ステップ 605 でのリフレッシュを行うことなく、上記ステップ 607 の判別が行われる。

#### 【0044】

全体書き込み回数が閾値  $X$  を越えた場合には、ステップ 606 の判別で「YES」と判断され、それにより閾値  $X$  が、それまでの値より大きな値に更新される(607)。ここでもし閾値  $X$  の値をそれまでの値より大きな値に変更しなければ、いずれかのページへの書き込みが行われる毎に、ステップ 604 の判別で必ず「リフレッシュが必要」と判断されてリフレッシュが実行されることから、不必要的再書き込みが頻繁に行われてしまう。これを避けるため、全体書き込み回数が閾値  $X$  を越えた場合には、ステップ 606 の判別で「YES」と判断され、それにより閾値  $X$  が、それまでの値より大きな値に更新されるようになっている(607)。そして閾値  $X$  が更新された後に、リフレッシュ Page が更新され(608)、その後、全体書き込み回数が更新される(609)。全体書き込み回数との関係で閾値  $X$  を更新する必要が無い場合には、上記ステップ 606 の判別で「NO」と判断され、閾値  $X$  が更新されることなく、リフレッシュ Page が更新され(608)、その後、全体書き込み回数が更新される(609)。図 7(E) に示される例では、全体書き込み回数が「10001」とされ、リフレッシュ Page が「Page 2」に更新されているため、Page 511へのデータ書き込みが行われた場合に、ステップ 603 の判別で「YES」と判断され、ステップ 605 で Page 2 のリフレッシュが行われることになる。

#### 【0045】

上記例によれば、以下の作用効果を得ることができる。

#### 【0046】

(1) 不揮発性メモリ 14 における何れかのページにデータが書き込まれる毎に、全体書き込み回数が閾値より大きいか否かの判別が行われ(603)、全体書き込み回数が閾値より大きい場合に、リフレッシュ Page として取得されたページがリフレッシュされる。そして、全体書き込み回数との関係で閾値  $X$  が更新される(609)。このようなりフレッシュ制御により、不揮発性メモリ 14 における各ページ(Page 1 ~ Page N)について偏りなくリフレッシュすることができる。そしてこのリフレッシュによって、メモリセルの閾値が変動前の状態に戻される。

#### 【0047】

(2) 上記(1)の作用効果により、マイクロコンピュータ 10 の信頼性の向上を図ることができる。

#### 【0048】

(3) 不揮発性メモリ 14 において、書き込み毎に、あるいは読み出し毎に、若しくは消去毎にリフレッシュを行うようにすると、このリフレッシュ動作によって各ページの書き込み回数が不所望に増大する虞があるが、上記のように不揮発性メモリ 14 における何

10

20

30

40

50

れかのページにデータが書き込まれる毎に、全体書き込み回数が閾値より大きいか否かの判別が行われ（603）、全体書き込み回数が閾値より大きい場合に、リフレッシュPageとして取得されたページがリフレッシュされるため、リフレッシュに起因して書き込み回数が不所望に増大されることが回避される。

#### 【0049】

＜実施の形態3＞

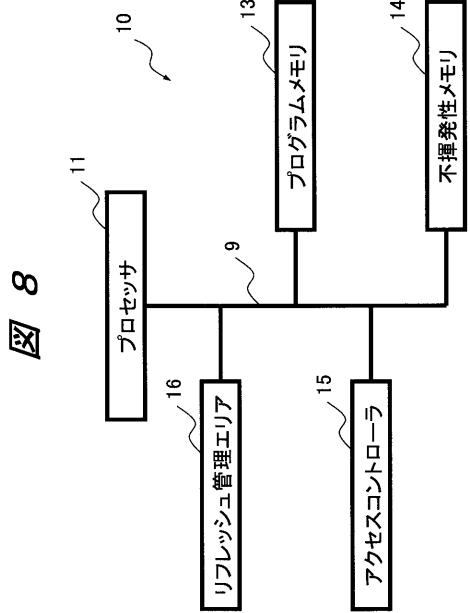

図8には、本発明にかかる半導体装置の一例とされるマイクロコンピュータの別の構成例が示される。図8に示されるマイクロコンピュータ10が図4に示されるのと大きく相違するのは、不揮発性メモリ14内の各Pageに、リフレッシュについての管理エリアが確保されている点と外部にリフレッシュ管理エリア16が形成されている点である。上記リフレッシュ管理エリア16は、バス9に結合されたRAM（ランダム・アクセス・メモリ）などに形成される。上記不揮発性メモリ14は、例えば図9（A）に示すように、Page毎に管理エリアが設けられる。この管理エリアは、図9（B）に示されるように、リフレッシュフラグと、全体書き込み回数との記憶エリアを含む。ここでリフレッシュフラグは、リフレッシュが行われたか否かを示すもので、例えばリフレッシュフラグが論理値「0」の場合には、未だリフレッシュが行われていないことを示し、リフレッシュフラグが論理値「1」の場合には、リフレッシュ済であることを示している。リフレッシュ管理エリア16は、電源投入時に管理エリアを検索することによって入手する全体書き込み回数ならびにリフレッシュPageを保存するエリアである。このリフレッシュ管理エリア16により、全体書き込み回数ならびにリフレッシュPageをメモリアクセス毎に検索する手間を省くことが可能となる。

#### 【0050】

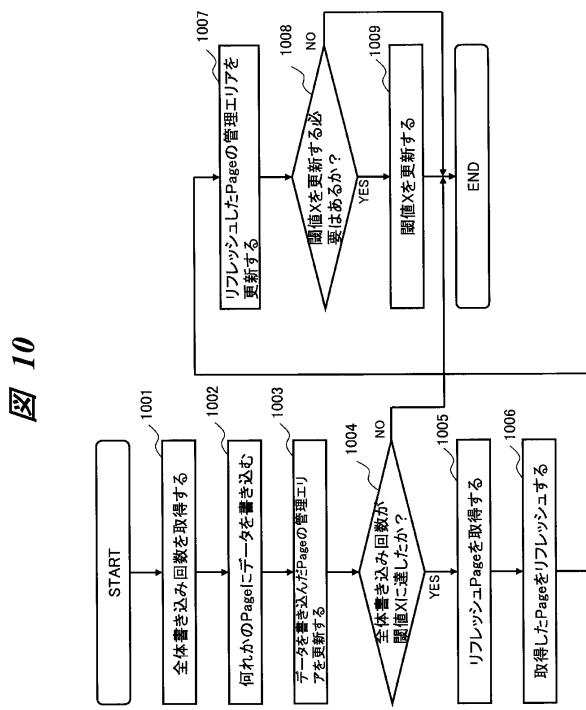

図10には、図8に示されるマイクロコンピュータ10におけるリフレッシュ制御の全体的な流れが示される。尚、このリフレッシュ制御はプロセッサ11やアクセスコントローラ15等によって行われるが、本説明では、アクセスコントローラ15が行うものとする。また、図11には上記リフレッシュ制御における不揮発性メモリ14の状態変化が示される。尚、図11において、ハッチングが付されているのは書き込みが行われるページであり、下線が付されているのはリフレッシュが行われるページである。

#### 【0051】

図11（A）の状態を初期状態とする。この初期状態においては、全てのページ（例えばPage1～Page511）において、リフレッシュフラグは論理値「0」、全体書き込み回数は「0」にそれぞれ設定されている。また、閾値Xは、「10000」に設定されているものとする。

#### 【0052】

先ず、アクセスコントローラ15により、リフレッシュ管理エリア16が参照され、不揮発性メモリ14における全体書き込み回数が取得される（1001）。そして、アクセスコントローラ15の制御により、不揮発性メモリ14における何れかのページにデータの書き込みが行われると（1002）、当該ページの管理エリアも更新される（1003）。そして、全体書き込み回数が閾値Xに達したか否かの判別が行われる（1004）。この判別において、全体書き込み回数が閾値Xに達していない（NO）と判断された場合には、処理が終了される。例えば、図11（B）に示されるように、Page2にデータが書き込まれた場合には、このPage2の管理エリアも更新される。図11（B）に示される例では、Page2以外の書き込みは行われていないので、不揮発性メモリ14における全体書き込み回数は、それまでの「0」から「1」に更新されている。また、図11（C）に示される例では、Page300にデータ書き込みが行われているが、このとき、既に他のページへのデータ書き込みが行われており、不揮発性メモリ14における全体書き込み回数は、「9999」に更新されている。さらに、図11（D）に示される例では、Page150にデータ書き込みが行われ、このPage150へのデータ書き込みによって、不揮発性メモリ14における全体書き込み回数は、「10000」となり、そのときの閾値X = 10000に達したことから、ステップ1004の判別において、「

10

20

30

40

50

Y E S」と判断され、リフレッシュ Page が取得される。リフレッシュが必要か否かの判別が行われる(1005)。例えば、上記ステップ1005で取得されたリフレッシュ Page への書き込みが上記ステップ1002で行われた場合には、このリフレッシュ Page へのリフレッシュのための再書き込みは不要である。そこで、上記ステップ1005で取得されたリフレッシュ Page と、上記ステップ1002で書き込みを行った Page とを比較し、同一 Page の場合には、当該ページに対するリフレッシュは不要と判断し、異なる Page の場合には、当該ページに対するリフレッシュは必要と判断する。この判別において、リフレッシュが必要と判断された場合には、対応するページ(ここでは、Page 1)のリフレッシュ、すなわち再書き込みが実行される(1006)。尚、電源投入時に管理エリア内のリフレッシュフラグを参照し、このリフレッシュフラグが論理値「0」のページがリフレッシュ Page としてリフレッシュ管理エリア16に保存されている。リフレッシュ Page が複数ある場合、その中でページ番号が最も小さいものが選択される。そして、リフレッシュ管理エリア16の更新やリフレッシュされたページの管理エリアが更新される(1007)。例えば図11(D)に示される例では、Page 1のリフレッシュが行われ、それに対応するリフレッシュフラグが、それまでの論理値「0」から論理値「1」に更新されている。また、図11(E)に示される例では、Page 511へのデータ書き込みによって、不揮発性メモリ14における全体書き込み回数は、「10001」となり、そのときの閾値  $X = 10000$  に達していることから、ステップ1004の判別において、「Y E S」と判断され、リフレッシュ Page の取得が行われる(1005)。この例では、Page 1についてのリフレッシュフラグは論理値「1」とされ、既にリフレッシュが完了しているから、Page 2についてのリフレッシュが行われ(1006)、このPage 2に対応するリフレッシュフラグが、それまでの論理値「0」から論理値「1」に更新される(1007)。このように、何れかのページへのデータ書き込みが行われる毎に、全体書き込み回数が閾値 X に達したか否かの判別が行われ(1004)、その判別結果に基づいてリフレッシュが行われる(1006)。そして、閾値 X を更新する必要があるか否かの判別が行われる(1008)。Page 1～Page 511に対応する全てのリフレッシュフラグが論理値「1」になった場合には、閾値 X を更新する必要がある(Y E S)と判断され、閾値 X が、それまでの「10000」から例えば「30000」などに更新され(1009)、管理エリアが初期状態に戻される。そして、図10に示されるリフレッシュ制御が再び開始される。

#### 【0053】

上記の例によれば、以下の作用効果を得ることができる。

#### 【0054】

(1) 何れかのページへのデータ書き込みが行われる毎に、全体書き込み回数が閾値 X に達したか否かの判別が行われ(1004)、その判別結果に基づいてリフレッシュが行われる(1006)。そして、閾値 X を更新する必要があるか否かの判別が行われる(1008)。Page 1～Page 511に対応する全てのリフレッシュフラグが論理値「1」になった場合には、閾値 X が更新される。このようなリフレッシュ制御により、不揮発性メモリ14における各ページ(Page 1～Page N)について偏りなくリフレッシュすることができる。そしてこのリフレッシュによって、メモリセルの閾値が変動前の状態に戻される。

#### 【0055】

(2) 上記(1)の作用効果により、マイクロコンピュータ10の信頼性の向上を図ることができる。

#### 【0056】

(3) 不揮発性メモリ14において、書き込み毎に、あるいは読み出し毎に、若しくは消去毎にリフレッシュを行うようにすると、このリフレッシュ動作によって各ページの書き込み回数が不所望に増大する虞があるが、上記のように全体書き込み回数が閾値 X に達したか否かの判別が行われ(1004)、その判別結果に基づいてリフレッシュが行われるため(1006)、リフレッシュに起因して書き込み回数が不所望に増大されることが

10

20

30

40

50

回避される。

【0057】

<実施の形態4>

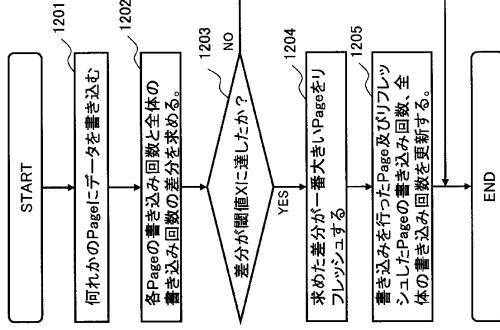

図12には、図4及び図5に示される構成における別のリフレッシュ制御の全体的な流れが示される。

【0058】

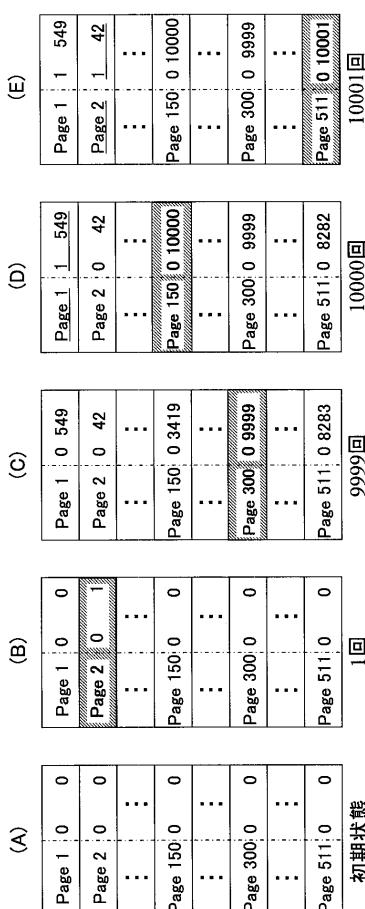

図5に示される管理エリア51には、不揮発性メモリ14における全体書き込み回数と、各ページの書き込みが行われた際の全体書き込み回数とが格納され、それに基づいてプロセッサ11やアクセスコントローラ15等によりリフレッシュ制御が行われる。尚、本説明では、アクセスコントローラ15が行うものとする。また、図13には上記リフレッシュ制御における不揮発性メモリ14の状態変化が示される。尚、図13において、ハッチングが付されているのは書き込みが行われるページであり、下線が付されているのはリフレッシュが行われるページである。10

【0059】

図13(A)の状態を初期状態とする。この初期状態において、全体書き込み回数は「0」、各ページの書き込み回数は「0」とされる。また、閾値Xは、「4000」に設定される。この状態でアクセスコントローラ15の制御により上記不揮発性メモリ14へのデータ書き込みが行われる場合を考える。

【0060】

先ず、何れかのページにデータの書き込みが行われると(1201)、アクセスコントローラ15は、図5に示される管理エリア51を参照して、各ページの書き込みを行った際の全体書き込み回数と全体的の書き込み回数との差分が求められる(1202)。例えば図13(B)に示されるようにPage150にデータの書き込みが行われた場合(1201)、このPage150についてのデータ書き込み回数は「1」、他のページについてのデータ書き込み回数は「0」であるから、この時点で、不揮発性メモリ14の全体書き込み回数は「1」とされる。20

【0061】

そして、各ページの書き込みを行った際の全体書き込み回数と全体的の書き込み回数との差分が閾値Xに達したか否かの判別が行われる(1203)。この判別において、差分が閾値Xに達していない(NO)と判断された場合、書き込みを行ったページの全体書き込み回数、全体書き込み回数が更新される(1206)。また、ステップ1203の判別において、差分が閾値Xに達した(YES)と判断された場合、求められた差分の中で、差分値が最も大きなページがリフレッシュされる(1204)。図13(C)に示される例では、Page1の全体書き込み回数は「5000」、Page2の全体書き込み回数は「1000」、Page150の全体書き込み回数は「3340」、Page300の全体書き込み回数は「2300」、Page511の全体書き込み回数は「4300」、不揮発性メモリ14の全体書き込み回数は「5000」とされる。Page2の全体書き込み回数は「1000」で、これと不揮発性メモリ14の全体書き込み回数は「5000」との差分が「4000」となり、この差分が閾値X=4000に達したことから、ステップ1203の判別においてYESと判断され、差分の一番大きなページ(ここではPage2)がリフレッシュされる(1204)。このようにするのは、差分の一番大きなページは書き込み回数が最も少なく、他のページに優先してディスクトップ対策する必要があるからである。そして、図13(D)に示されるように、書き込みを行ったページ及びリフレッシュしたページの書き込み回数、全体の書き込み回数が更新される(1205)。30

【0062】

上記例によれば、以下の作用効果を得ることができる。

【0063】

(1) 不揮発性メモリ14における何れかのページにデータが書き込まれる毎に、各ページの書き込み回数と全体的の書き込み回数との差分が求められ(1202)、各ページの書き込み回数と全体的の書き込み回数との差分が閾値Xに達したか否かの判別が行われ40

(1203)、ステップ1203の判別において、差分が閾値Xに達した(YES)と判断された場合、求められた差分の中で、差分値が最も大きなページがリフレッシュされることにより(1204)、不揮発性メモリ14における各ページ(Page 1 ~ Page 511)について偏りなくリフレッシュすることができる。そしてこのリフレッシュによって、メモリセルの閾値が変動前の状態に戻される。

【0064】

(2)上記(1)の作用効果により、マイクロコンピュータ10の信頼性の向上を図ることができる。

【0065】

(3)不揮発性メモリ14において、書き込み毎に、あるいは読み出し毎に、若しくは消去毎にリフレッシュを行うようにすると、このリフレッシュ動作によって各ページの書き込み回数が不所望に増大する虞があるが、各ページの書き込み回数と全体的の書き込み回数との差分が求められ、この差分が閾値Xに達した(YES)と判断された場合、求められた差分の中で、差分値が最も大きなページがリフレッシュされることにより、リフレッシュに起因して書き込み回数が不所望に増大されることが回避される。10

【0066】

<実施の形態5>

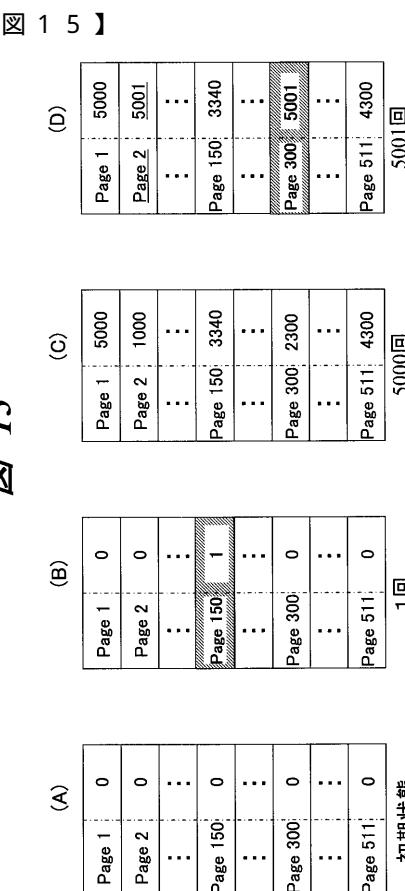

図14には、図8及び図9に示される構成における別のリフレッシュ制御の全体的な流れが示される。各Pageの管理エリアには、各ページの書き込みが行われた際の全体書き込み回数が格納される。また、図8に示されるリフレッシュ管理エリア16は、電源投入時に管理エリアを検索することによって入手する全体書き込み回数が格納され、それに基づいてプロセッサ11やアクセスコントローラ15によりリフレッシュ制御が行われる。尚、本説明では、アクセスコントローラ15が行うものとする。また、図15には、上記リフレッシュ制御における管理エリアの状態変化が示される。尚、図15において、ハッシュングが付されているのは書き込みが行われるページであり、下線が付されているのはリフレッシュが行われるページである。20

【0067】

図15(A)の状態を初期状態とする。この初期状態において、全体書き込み回数は「0」、各ページの書き込み回数は「0」とされる。また、閾値Xは「4000」に設定される。この状態でプロセッサ11の制御により上記不揮発性メモリ14へのデータ書き込みが行われる場合を考える。30

【0068】

先ず、アクセスコントローラ15によってリフレッシュ管理エリア16が参照され、不揮発性メモリ14の全体書き込み回数が取得される(1401)。そして、何れかのページにデータ書き込みが行われた場合(1402)、当該ページの管理エリアも更新される(1403)。つまり、各ページの管理エリアには、当該ページにデータ書き込みが行われた時点での全体書き込み回数が格納されるようになっている。また、リフレッシュ管理エリア16に格納してある全体書き込み回数も更新する。

そして、アクセスコントローラ15によって、各ページの管理エリアの保持値と、現時点での全体の書き込み回数との差分が求められる(1404)。その後、上記ステップ1404で求められた差分が閾値Xに達したか否かの判別が行われる(1405)。ステップ1405の判別において、上記ステップ1404で求められた差分が閾値Xに達していない(NO)と判断された場合には、処理が終了される。ステップ1405の判別において、上記ステップ1404で求められた差分が閾値Xに達している(YES)と判断された場合には、上記ステップ1404で求められた差分が最も大きなページがリフレッシュされ(1406)、リフレッシュしたページの管理エリアが更新される(1407)。また、リフレッシュ管理エリア16に格納してある全体書き込み回数も更新する。例えば、図15(B)では、Page 150へのデータ書き込みが行われることで、管理エリアにおける全体書き込み回数が「1」に更新される。図15(C)に示される例では、Page 1に対応する管理エリアが「5000」となっており、この値が最も大きいことから、不40

揮発性メモリ14の現在の全体書き込み回数が「5000」であることが示される。次に、Page300にデータ書き込みが行われた場合、このPage300に対応する管理エリアは、図15(D)に示されるように、 $5000 + 1 = 5001$ に更新される(1403)。また、図15(C)の状態で、各ページの管理エリアの保持値と、現時点での全体の書き込み回数との差分が求められ(1404)、Page2の管理エリアの保持値(1000)と、現時点での全体の書き込み回数(5000)との差分は「4000」であり、それが、閾値 $X = 4000$ に達したため、求められた差分が最も大きなページ(ここではPage2)がリフレッシュされ(1406)、そのページの管理エリアが「5001」に更新される。

## 【0069】

10

上記例によれば、以下の作用効果を得ることができる。

## 【0070】

(1) 何れかのページにデータ書き込みが行われた場合(1402)、その書き込みが行われたページの管理エリアにおいて全体書き込み回数が更新される(1403)。そして、アクセスコントローラ15によって、各ページの管理エリアの保持値と、現時点での全体の書き込み回数との差分が求められ(1404)、その後、上記ステップ1404で求められた差分が閾値Xに達したか否かの判別が行われる(1405)。ステップ1405の判別において、YESと判断された場合には、上記ステップ1404で求められた差分が最も大きなページがリフレッシュされ(1406)、リフレッシュしたページの管理エリアが更新される(1407)。これにより、不揮発性メモリ14における各ページ(Page1~Page511)について偏りなくリフレッシュすることができる。そしてこのリフレッシュによって、メモリセルの閾値が変動前の状態に戻される。

20

## 【0071】

(2) 上記(1)の作用効果により、マイクロコンピュータ10の信頼性の向上を図ることができる。

## 【0072】

30

(3) 不揮発性メモリ14において、書き込み毎に、あるいは読み出し毎に、若しくは消去毎にリフレッシュを行うようにすると、このリフレッシュ動作によって各ページの書き込み回数が不所望に増大する虞があるが、各ページの管理エリアの保持値と、現時点での全体の書き込み回数との差分が求められ(1404)、この差分が閾値Xに達した(YES)と判断された場合、求められた差分の中で、差分値が最も大きなページがリフレッシュされることにより、リフレッシュに起因して書き込み回数が不所望に増大されることが回避される。

## 【0073】

40

## &lt;実施の形態6&gt;

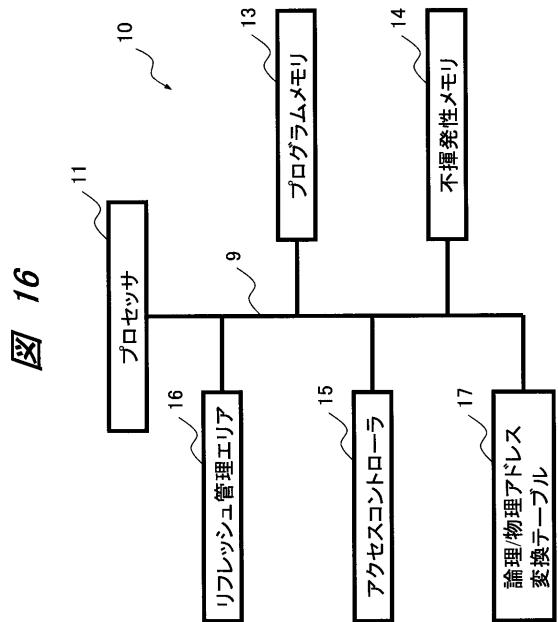

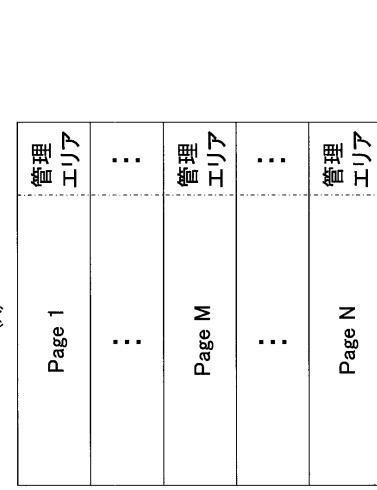

図16には、本発明にかかる半導体装置の一例とされるマイクロコンピュータの別の構成例が示される。図16に示されるマイクロコンピュータ10が、図8に示されるのと大きく相違するのは、プロセッサ11から与えられた論理アドレスを、不揮発性メモリ14における物理アドレスに変換するための論理/物理アドレス変換テーブル17が設けられている点である。アクセスコントローラ15によって不揮発性メモリ14がアクセスされる際に、論理/物理アドレス変換テーブル17によって論理アドレスが不揮発性メモリ14の物理アドレスに変換され、その物理アドレスによって不揮発性メモリ14の書き込みや読み出し等が行われる。上記不揮発性メモリ14は、例えば図17(A)に示すように、Page毎に管理エリアが設けられる。この管理エリアは、図17(B)に示されるように、変換フラグと、全体書き込み回数との記憶エリアを含む。ここで、変換フラグとは、論理アドレスに対応する物理アドレスの入れ替えが可能か否かを示すのもので、例えば変換フラグが論理値「0」の場合には、入れ替えが可能であることを示し、変換フラグが論理値「1」の場合には、入れ替えが不可能であることを示している。リフレッシュ管理エリア16は、電源投入時に管理エリアを検索することによって入手する全体書き込み回数を格納するエリアである。このリフレッシュ管理エリア16により、全体書き込み回数

50

をメモリアクセス毎に検索する手間を省くことが可能となる。

#### 【0074】

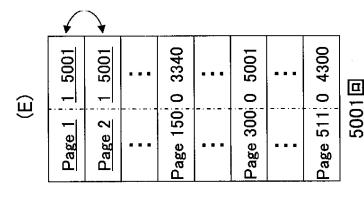

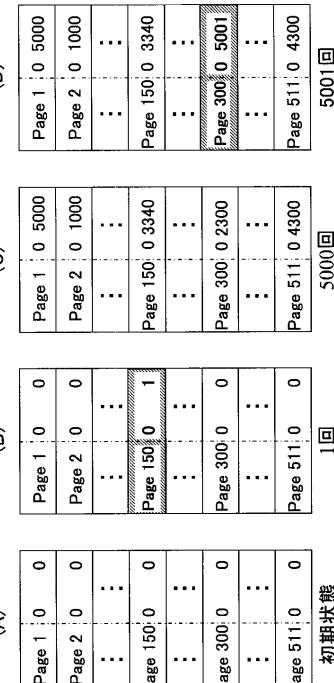

図18には、図16に示されるマイクロコンピュータ10におけるリフレッシュ制御の全体的な流れが示される。このリフレッシュ制御はプロセッサ11やアクセスコントローラ15によって行われるが、本説明では、アクセスコントローラ15が行うものとする。また、図19には上記リフレッシュ制御における管理エリアの状態変化が示される。尚、図19において、ハッチングが付されているのは書き込みが行われるページであり、下線が付されているのはリフレッシュが行われるページである。

#### 【0075】

図19(A)の状態を初期状態とする。この初期状態においては、全てのページ(例えばPage1～Page511)において、変換フラグは論理値「0」、全体書き込み回数は「0」にそれぞれ設定されている。また、閾値Xは、「4000」に設定されているものとする。この状態でアクセスコントローラ15により、全体書き込み回数が取得される(1801)。そして、何れかのページにデータの書き込みが行われると(1802)、当該ページの管理エリアが更新される(1803)。また、リフレッシュ管理エリア16の全体書き込み回数も更新される。例えば図19(B)に示されるように、アクセスコントローラ15によってPage150にデータの書き込みが行われた場合には、アクセスコントローラ15によってPage150の管理エリアにおける全体書き込み回数が、それまでの「0」から「1」に更新される。そして、各ページの管理エリアの値と全体の書き込み回数の差分を求め(1804)、差分が閾値Xに達したか否かの判別が行われる(1805)。例えば図19(C)に示される例では、Page2の管理エリアの値が「1000」とされ、それと、そのときの全体書き込み回数「5000」との差分「4000」が閾値X(ここでは4000設定)に達している。これにより、ステップ1805の判別において、YESと判断され、こんどは、上記ステップ1804で求められた差分が、閾値Yより小さいページが取得される(1806)。ここで閾値Yは、閾値Xよりも小さな値とされ、例えば「100」などとされ、プロセッサ11内の適宜のレジスタ等に設定されているものとする。そして、取得したページの変換フラグの状態がチェックされる(1807)。変換フラグの状態が論理値「0」の場合には、入れ替えが可能であることを示しているため、求めた差分が最も大きいページと、差分が閾値Yより小さいページとの間で、ページの入れ替えが行われ(1808)、各ページの管理エリアも更新される(1809)。例えば図19(D)に示される例では、全体の書き込み回数(5001)との差分が最も大きいページは、Page2であり、差分が閾値Yより小さいページは、Page1である。そしてそれらの変換フラグの状態が論理値「0」であるため、ここでは、Page1とPage2との入れ替えが行われる(1808)。このページの入れ替えは、Page1の物理アドレスと、Page2の物理アドレスとを入れ替えることで実現される。Page1とPage2との入れ替えが行われた後、各ページの管理エリアが更新される(1809)。また、上記ステップ1807の判別において、入れ替え不可能(NO)と判断された場合には、差分の最も大きなページがリフレッシュされ(1810)、リフレッシュしたページの管理エリアが更新される(1811)。例えば図19(E)に示される例では、差分の最も大きなPage2のリフレッシュが行われ、その管理エリアの最大書き込み回数が「5001」に更新されている。

#### 【0076】

上記の例によれば、以下の作用効果を得ることができる。

#### 【0077】

(1) アクセスコントローラ15によってデータの書き込みが行われた場合には、各ページの管理エリアの値と全体の書き込み回数の差分が求められ(1804)、差分が閾値Xに達したか否かの判別が行われ(1805)、差分の最も大きなページがリフレッシュされ(1810)、リフレッシュしたページの管理エリアも更新される(1811)。これにより、不揮発性メモリ14における各ページ(Page1～Page511)について偏りなくリフレッシュすることができる。そしてこのリフレッシュによって、メモリセ

10

20

30

40

50

ルの閾値が変動前の状態に戻される。

【0078】

(2) 求めた差分が最も大きいページと、差分が閾値Yより小さいページとの間で、ページの入換が行われ(1808)、各ページの管理エリアも更新される(1809)。このページの入れ替えは、Page1の物理アドレスと、Page2の物理アドレスとを入れ替えることで実現される。これにより、不揮発性メモリ14における各ページ(Page1～Page511)における書き込み回数の偏りが更に低減される。

【0079】

(3) 上記(1)、(2)の作用効果により、マイクロコンピュータ10の信頼性の向上を図ることができる。

10

【0080】

(4) 不揮発性メモリ14において、書き込み毎に、あるいは読み出し毎に、若しくは消去毎にリフレッシュを行うようにすると、このリフレッシュ動作によって各ページの書き込み回数が不所望に増大する虞があるが、各ページの管理エリアの保持値と、現時点での全体の書き込み回数との差分が求められ(1804)、この差分が閾値Xに達したと判断された場合、求められた差分の中で、差分値が最も大きなページがリフレッシュされることにより、リフレッシュに起因して書き込み回数が不所望に増大されることが回避される。

【0081】

以上本発明者によってなされた発明を具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

20

【0082】

例えば、上記の例ではアクセスコントローラ15によってリフレッシュ制御を行うようにしたが、このリフレッシュ制御専用のコントローラを上記プロセッサ11やアクセスコントローラ15とは別に設けることができる。

【0083】

上記の例では、上記不揮発性メモリへの書き込みが行われる毎に乱数発生器で発生された乱数に基づいてリフレッシュ対象ページを決定したり、書き込み回数の合計値(全体書き込み回数)を更新したりしたが、上記不揮発性メモリの消去又は読み出しが行われる毎に乱数発生器で発生された乱数に基づいてリフレッシュ対象ページを決定したり、消去回数又は読み出し回数の合計値を更新するようにしても良い。

30

【0084】

上記の例では、不揮発性メモリの書き込み回数を用いてリフレッシュ制御するようにしたが、不揮発性メモリにおける全てのページについての書き込み回数に代えて、不揮発性メモリにおける全てのページについての消去回数又は読み出し回数を用いてリフレッシュ制御することができる。

【0085】

上記の例では、アクセス対象領域をページ(Page)としたが、これに限定されない。例えばアクセス対象領域をセクタやブロックとすることができます。

40

【0086】

また、マイクロコンピュータ10内のRAM(ランダム・アクセス・メモリ)に、全体書き込み回数を記録するようにしても良い。バッテリなどによって上記RAMがバックアップされていない場合には、システムの電源遮断の直前に上記RAM内の全体書き込み回数を適宜の不揮発性メモリに待避し、システムのパワーオンリセットにおいて、上記不揮発性メモリ内の全体書き込み回数を上記RAMにロードすれば良い。

【0087】

以上の説明では主として本発明者によってなされた発明をその背景となった利用分野であるマイクロコンピュータに適用した場合について説明したが、本発明はそれに限定されるものではなく、半導体装置に広く適用することができる。

【図面の簡単な説明】

50

## 【0088】

【図1】本発明にかかる半導体装置の一例とされるマイクロコンピュータの構成例プロック図である。

【図2】図1に示されるマイクロコンピュータに含まれる不揮発性メモリの構成例説明図である。

【図3】図1に示されるマイクロコンピュータに含まれる不揮発性メモリのリフレッシュ制御のフローチャートである。

【図4】本発明にかかる半導体装置の一例とされるマイクロコンピュータの別の構成例プロック図である。

【図5】図4に示されるマイクロコンピュータに含まれる不揮発性メモリの構成例説明図である。 10

【図6】図4に示されるマイクロコンピュータに含まれる不揮発性メモリのリフレッシュ制御のフローチャートである。

【図7】図4に示されるマイクロコンピュータに含まれる不揮発性メモリの上記リフレッシュ制御における状態変化の説明図である。

【図8】本発明にかかる半導体装置の一例とされるマイクロコンピュータの別の構成例プロック図である。

【図9】図8に示されるマイクロコンピュータに含まれるリフレッシュ管理エリアの構成例説明図である。 20

【図10】図8に示されるマイクロコンピュータに含まれる不揮発性メモリのリフレッシュ制御のフローチャートである。

【図11】図8に示されるマイクロコンピュータに含まれる不揮発性メモリのリフレッシュ制御における状態変化の説明図である。

【図12】図4及び図5に示される構成における別のリフレッシュ制御のフローチャートである。

【図13】図4及び図5に示される構成における別のリフレッシュ制御における状態変化の説明図である。

【図14】図8及び図9に示される構成における別のリフレッシュ制御のフローチャートである。

【図15】図8及び図9に示される構成における別のリフレッシュ制御における状態変化の説明図である。 30

【図16】本発明にかかる半導体装置の一例とされるマイクロコンピュータの別の構成例プロック図である。

【図17】図16に示されるマイクロコンピュータに含まれるリフレッシュ管理エリアの構成例説明図である。

【図18】図16に示されるマイクロコンピュータに含まれる不揮発性メモリのリフレッシュ制御のフローチャートである。

【図19】図16に示されるマイクロコンピュータに含まれる不揮発性メモリの上記リフレッシュ制御における状態変化の説明図である。

【図20A】上記不揮発性メモリにおける主要部の構成と電圧印加の説明図である。 40

【図20B】上記不揮発性メモリにおける主要部の構成と電圧印加の説明図である。

【図20C】上記不揮発性メモリにおける主要部の構成と電圧印加の説明図である。

【図20D】上記不揮発性メモリにおける主要部の構成と電圧印加の説明図である。

## 【符号の説明】

## 【0089】

10 マイクロコンピュータ

11 プロセッサ

12 乱数生成器

13 プログラムメモリ

14 不揮発性メモリ

- 15 アクセスコントローラ

16 リフレッシュ管理エリア

【図1】

【図2】

【図3】

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図 8】

図 8

【図 9】

(B)

リフレッシュフラグ 全体書き込み回数

【図 10】

図 10

【図 11】

(A)

|          |   |   |

|----------|---|---|

| Page 1   | 0 | 0 |

| Page 2   | 0 | 1 |

| ⋮        | ⋮ | ⋮ |

| Page 150 | 0 | 0 |

| ⋮        | ⋮ | ⋮ |

| Page 300 | 0 | 0 |

| ⋮        | ⋮ | ⋮ |

| Page 511 | 0 | 0 |

初期状態

(E)

|          |   |       |

|----------|---|-------|

| Page 1   | 1 | 549   |

| Page 2   | 0 | 42    |

| ⋮        | ⋮ | ⋮     |

| Page 150 | 0 | 10000 |

| ⋮        | ⋮ | ⋮     |

| Page 300 | 0 | 9999  |

| ⋮        | ⋮ | ⋮     |

| Page 511 | 0 | 8282  |

10000回

(D)

|          |   |      |

|----------|---|------|

| Page 1   | 1 | 549  |

| Page 2   | 0 | 42   |

| ⋮        | ⋮ | ⋮    |

| Page 150 | 0 | 3419 |

| ⋮        | ⋮ | ⋮    |

| Page 300 | 0 | 9999 |

| ⋮        | ⋮ | ⋮    |

| Page 511 | 0 | 8282 |

9999回

(C)

|          |   |       |

|----------|---|-------|

| Page 1   | 0 | 549   |

| Page 2   | 0 | 42    |

| ⋮        | ⋮ | ⋮     |

| Page 150 | 0 | 10000 |

| ⋮        | ⋮ | ⋮     |

| Page 300 | 0 | 9999  |

| ⋮        | ⋮ | ⋮     |

| Page 511 | 0 | 8282  |

10000回

(B)

|          |   |   |

|----------|---|---|

| Page 1   | 0 | 0 |

| Page 2   | 0 | 1 |

| ⋮        | ⋮ | ⋮ |

| Page 150 | 0 | 0 |

| ⋮        | ⋮ | ⋮ |

| Page 300 | 0 | 0 |

| ⋮        | ⋮ | ⋮ |

| Page 511 | 0 | 0 |

1回

図 14

図 12

図 14

図 13

図 13

JP 5478855 B2 2014.4.23

(21)

(22)

JP 5478855 B2 2014.4.23

### 【図16】

【 図 17 】

(B)

【図18】

【 図 1 9 】

18

19

初期状態

4

【図 20 A】

図 20A

【図 20 B】

図 20B

【図 20 C】

図 20C

【図 20 D】

図 20D

---

フロントページの続き

(72)発明者 塩田 茂雅

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

審査官 桜井 茂行

(56)参考文献 特表2007-507804 (JP, A)

特開2008-090778 (JP, A)

特開2008-181380 (JP, A)

特開2004-240572 (JP, A)

特開2004-259144 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 16

G 11 C 16 / 02