(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6218904号

(P6218904)

(45) 発行日 平成29年10月25日(2017.10.25)

(24) 登録日 平成29年10月6日(2017.10.6)

(51) Int.Cl.

F 1

|                |           |        |        |         |

|----------------|-----------|--------|--------|---------|

| HO 1 L 29/786  | (2006.01) | HO 1 L | 29/78  | 6 1 7 N |

| HO 1 L 21/8242 | (2006.01) | HO 1 L | 29/78  | 6 1 3 B |

| HO 1 L 27/108  | (2006.01) | HO 1 L | 29/78  | 6 1 8 B |

| HO 1 L 27/10   | (2006.01) | HO 1 L | 27/108 | 3 2 1   |

| C23C 14/08     | (2006.01) | HO 1 L | 27/10  | 4 6 1   |

請求項の数 2 (全 19 頁) 最終頁に続く

(21) 出願番号 特願2016-178580 (P2016-178580)

(22) 出願日 平成28年9月13日 (2016.9.13)

(62) 分割の表示 特願2012-89256 (P2012-89256)

の分割

原出願日 平成24年4月10日 (2012.4.10)

(65) 公開番号 特開2017-22399 (P2017-22399A)

(43) 公開日 平成29年1月26日 (2017.1.26)

審査請求日 平成28年9月26日 (2016.9.26)

(31) 優先権主張番号 特願2011-90843 (P2011-90843)

(32) 優先日 平成23年4月15日 (2011.4.15)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2011-112792 (P2011-112792)

(32) 優先日 平成23年5月19日 (2011.5.19)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 坂田 淳一郎

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 竹口 泰裕

最終頁に続く

(54) 【発明の名称】半導体素子

## (57) 【特許請求の範囲】

## 【請求項 1】

酸化物半導体層と、

前記酸化物半導体層の第1の面に接する第1の絶縁層と、

前記第1の面の裏面である前記酸化物半導体層の第2の面に接する第2の絶縁層と、

前記第1の絶縁層を介して前記酸化物半導体層と重畳する第1の導電層と、

前記第2の絶縁層を介して前記酸化物半導体層と重畳する第2の導電層と、

前記第1の面の一端において前記酸化物半導体層と接する第3の導電層と、

前記第1の面の他端において前記酸化物半導体層と接する第4の導電層と、

前記第2の面の一端において前記酸化物半導体層と接する第5の導電層と、

前記第2の面の他端において前記酸化物半導体層と接する第6の導電層と、を有し、

前記第1の導電層の一端が前記第1の絶縁層を介して前記第3の導電層の一端と重畳し、且つ前記第1の導電層の他端が前記第1の絶縁層を介して前記第4の導電層の一端と重畳し、

前記第2の導電層の一端が前記第2の絶縁層を介して前記第5の導電層の一端と重畳し、且つ前記第2の導電層の他端が前記第2の絶縁層を介して前記第6の導電層の一端と重畳し、

前記第3の導電層は、前記酸化物半導体層を介して、前記第5の導電層及び前記第6の導電層と重なっておらず、

前記第4の導電層は、前記酸化物半導体層を介して、前記第5の導電層及び前記第6の

10

20

導電層と重なっていない半導体素子。

【請求項 2】

酸化物半導体層と、

前記酸化物半導体層の第1の面に接する第1の絶縁層と、

前記第1の面の裏面である前記酸化物半導体層の第2の面に接する第2の絶縁層と、

前記第1の絶縁層を介して前記酸化物半導体層と重畳する第1の導電層と、

前記第2の絶縁層を介して前記酸化物半導体層と重畳する第2の導電層と、

前記第1の面の一端において前記酸化物半導体層と接する第3の導電層と、

前記第1の面の他端において前記酸化物半導体層と接する第4の導電層と、

前記第2の面の一端において前記酸化物半導体層と接する第5の導電層と、

前記第2の面の他端において前記酸化物半導体層と接する第6の導電層と、を有し、

前記酸化物半導体層が、前記第1の面を含む第1の酸化物半導体領域と、前記第2の面を含む第2の酸化物半導体領域と、前記第1の酸化物半導体領域及び前記第2の酸化物半導体領域に挟まれた酸化物絶縁体領域と、を有する半導体素子。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関する。特に、本発明は、電気的スイッチとしての機能を有する半導体素子に関する。また、当該半導体素子を有する記憶回路、及び当該記憶回路を有する集積回路に関する。また、当該集積回路の駆動方法に関する。

【背景技術】

【0002】

近年、トランジスタの構成材料として、高移動度と、均一な素子特性とを兼ね備えた酸化物半導体と呼ばれる、半導体特性を示す金属酸化物に注目が集まっている。金属酸化物は様々な用途に用いられている。例えば、酸化インジウムは、液晶表示装置において画素電極の材料として用いられている。半導体特性を示す金属酸化物としては、例えば、酸化タンゲステン、酸化錫、酸化インジウム、酸化亜鉛などがあり、このような半導体特性を示す金属酸化物によってチャネルが形成されるトランジスタが、既に知られている（特許文献1及び特許文献2）。

【先行技術文献】

30

【特許文献】

【0003】

【特許文献1】特開2007-123861号公報

【特許文献2】特開2007-96055号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

上述のトランジスタは、回路を構成する素子の一である。例えば、中央演算素子（CPU（Central Processing Unit）及びDSP（Digital Signal Processor）等）は、数千万個以上という多数のトランジスタをスイッチとして用いた集積回路である。今後は、より多数のトランジスタによって集積回路を構成することが期待されている。ただし、単純に回路規模を拡大する場合には、回路面積の拡大が伴う。そのため、回路規模が拡大された集積回路を所望の回路面積において作製するため、各種素子の微細化に関する研究開発が活発に行われている。しかし、当該研究開発は既に数十年に渡って行われており、素子単体の微細化によってさらなる回路規模の拡大に対応することは困難となってきた。

【0005】

そこで、本発明の一態様は、回路規模の拡大に資する新規の半導体素子を提供することを目的の一とする。

【課題を解決するための手段】

40

50

## 【0006】

本発明の一態様の半導体素子においては、独立した2つの電気的スイッチが単体の酸化物半導体層を用いて構成されることを要旨とする。例えば、当該半導体素子は、当該酸化物半導体層の下面（第1の面）近傍におけるチャネル（電流経路）の形成と、上面（第2の面）近傍におけるチャネルの形成とを独立して制御することが可能な半導体素子である。

## 【0007】

ここで、酸化物半導体は、バンドギャップが広く、且つ真性キャリア密度が低いという特徴を有する。よって、チャネルが形成されない領域の酸化物半導体層に生じる電流を極めて低くすることが可能である。これにより、単体の酸化物半導体層の下面近傍及び上面近傍に別個にチャネルが形成される場合であっても、両者間に生じる電流を極めて低くすることが可能となる。

## 【0008】

具体的には、本発明の一態様は、酸化物半導体層と、酸化物半導体層の第1の面に接する第1の絶縁層と、第1の面の裏面である酸化物半導体層の第2の面に接する第2の絶縁層と、第1の絶縁層を介して酸化物半導体層と重畳する第1の導電層と、第2の絶縁層を介して酸化物半導体層と重畳する第2の導電層と、第1の面の一端において酸化物半導体層と接する第3の導電層と、第1の面の他端において酸化物半導体層と接する第4の導電層と、第2の面の一端において酸化物半導体層と接する第5の導電層と、第2の面の他端において酸化物半導体層と接する第6の導電層と、を有する半導体素子である。

## 【0009】

また、本発明の一態様の半導体素子は、酸化物半導体層と、第1のゲート絶縁層及び第2のゲート絶縁層と、第1のゲート及び第2のゲートと、第1のソース及び第2のソースと、第1のドレイン及び第2のドレインと、を有し、第1のゲート絶縁層を介して酸化物半導体層の第1の面近傍に生じる電界を第1のゲート及び第1のソース間の電圧に応じて制御することで酸化物半導体層に第1のソース及び第1のドレイン間のチャネルが形成され、第2のゲート絶縁層を介して第1の面の裏面である酸化物半導体層の第2の面近傍に生じる電界を第2のゲート及び第2のソース間の電圧に応じて制御することで、酸化物半導体層に第2のソース及び第2のドレイン間のチャネルが形成される半導体素子であると換言することもできる。

## 【発明の効果】

## 【0010】

本発明の一態様の半導体素子においては、独立した2つの電気的スイッチを単体の酸化物半導体層を用いて構成される。よって、2つの電気的スイッチを別個に設ける場合（例えば、2つのトランジスタを別個に設ける場合）と比較して、回路面積を縮小することが可能となる。すなわち、当該半導体素子を用いて回路を構成することで、回路規模の拡大に伴う回路面積の拡大を抑制することが可能になる。

## 【図面の簡単な説明】

## 【0011】

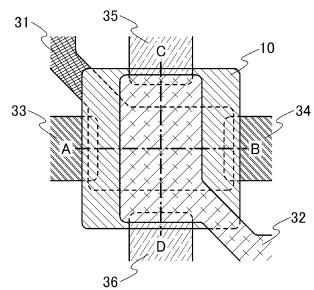

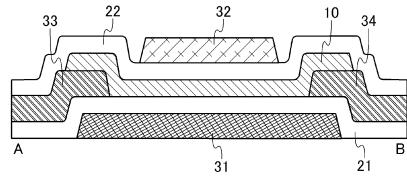

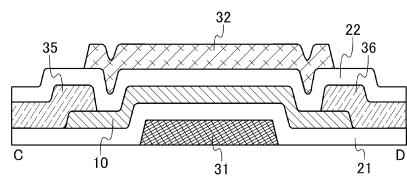

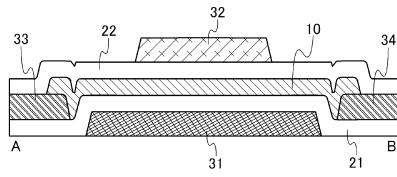

【図1】半導体素子の構成例を示す（A）上面図、（B）、（C）断面図。

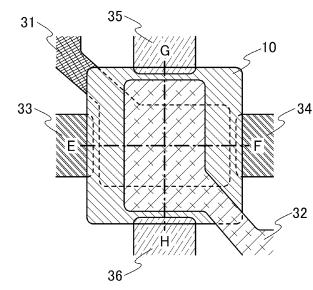

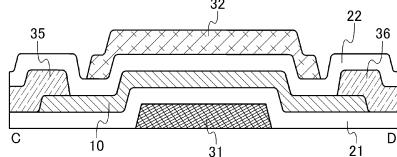

【図2】半導体素子の構成例を示す（A）上面図、（B）、（C）断面図。

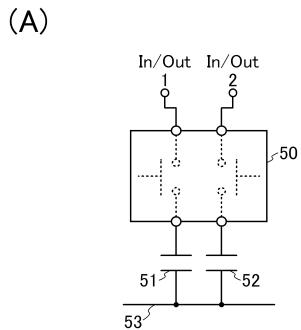

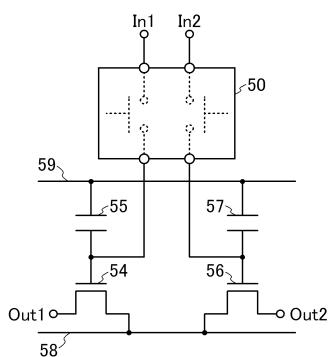

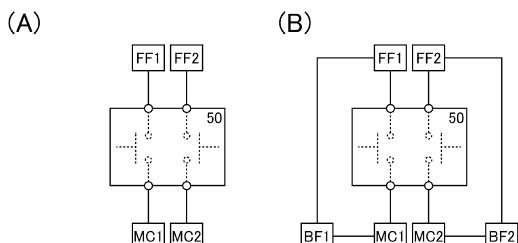

【図3】（A）、（B）記憶回路の構成例を示す図。

【図4】集積回路の（A）、（B）構成例を示すブロック図、（C）動作例を示すフローチャート。

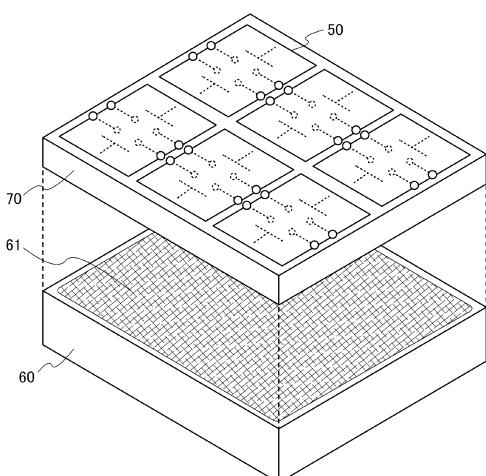

【図5】集積回路の構造例を示す図。

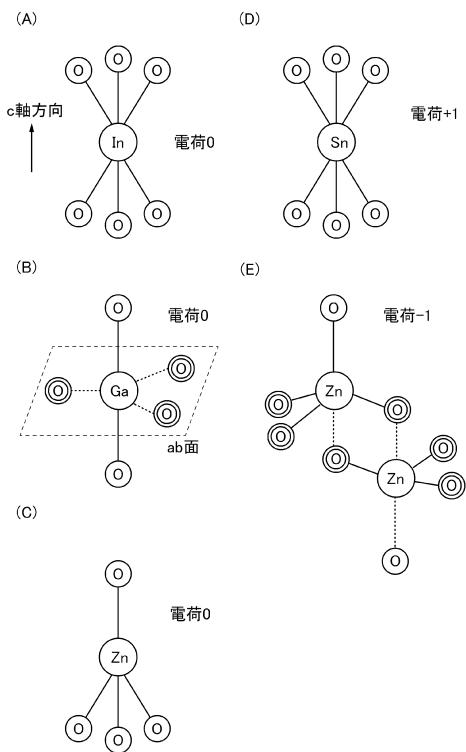

【図6】本発明の一態様に係る酸化物材料の構造を説明する図。

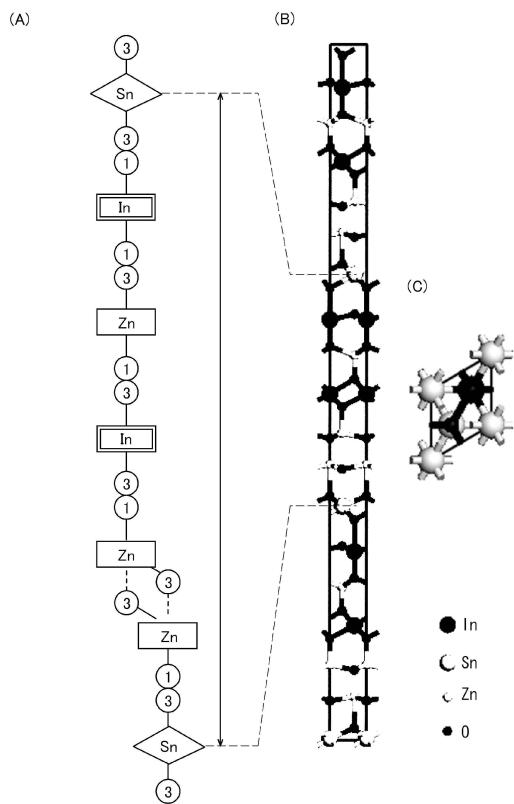

【図7】本発明の一態様に係る酸化物材料の構造を説明する図。

【図8】本発明の一態様に係る酸化物材料の構造を説明する図。

## 【発明を実施するための形態】

## 【0012】

10

20

30

40

50

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0013】

まず、本発明の一態様に係る半導体素子について図1、2を参照して説明する。

【0014】

<半導体素子の構成例>

図1(A)～(C)は、本発明の一態様に係る半導体素子の構成例を示す図である。なお、図1(A)は当該半導体素子の上面図であり、図1(B)は図1(A)に示す線分A-Bにおける当該半導体素子の断面図であり、図1(C)は図1(A)に示す線分C-Dにおける当該半導体素子の断面図である。

10

【0015】

図1(A)～(C)に示す半導体素子は、酸化物半導体層10と、酸化物半導体層10の下面に接する絶縁層21と、酸化物半導体層10の上面に接する絶縁層22と、絶縁層21を介して酸化物半導体層10と重畳する導電層31と、絶縁層22を介して酸化物半導体層10と重畳する導電層32と、酸化物半導体層10の下面の一端において酸化物半導体層10と接する導電層33と、酸化物半導体層10の下面の他端において酸化物半導体層10と接する導電層34と、酸化物半導体層10の上面の一端において酸化物半導体層10と接する導電層35と、酸化物半導体層10の上面の他端において酸化物半導体層10と接する導電層36と、を有する。

20

【0016】

なお、図1(A)～(C)に示す半導体素子は、酸化物半導体層10を共有する2つのトランジスタを有すると表現することもできる。具体的には、当該半導体素子は、ゲートとして機能する導電層31と、ゲート絶縁層として機能する絶縁層21と、ソースとして機能する導電層33と、ドレインとして機能する導電層34と、酸化物半導体層10とを有する第1のトランジスタと、ゲートとして機能する導電層32と、ゲート絶縁層として機能する絶縁層22と、ソースとして機能する導電層35と、ドレインとして機能する導電層36と、酸化物半導体層10とを有する第2のトランジスタとを有すると表現することもできる。

30

【0017】

図1(A)～(C)に示す半導体素子においては、導電層31(ゲート)及び導電層33(ソース)間電圧に応じて、絶縁層21を介して酸化物半導体層10の下面近傍に生じる電界を制御することが可能である。これにより、酸化物半導体層10の下面近傍に導電層33(ソース)及び導電層34(ドレイン)間のチャネルを形成することが可能である。同様に、当該半導体素子においては、導電層32(ゲート)及び導電層35(ソース)間電圧に応じて、絶縁層22を介して酸化物半導体層10の上面近傍に生じる電界を制御することが可能である。これにより、酸化物半導体層10の上面近傍に導電層35(ソース)及び導電層36(ドレイン)間のチャネルを形成することが可能である。なお、図1(A)～(C)に示す半導体素子においては、絶縁層21のみを介して導電層31と重畳する領域の酸化物半導体層10の下面近傍が、主として導電層33及び導電層34間のチャネルとなる領域であり、絶縁層22のみを介して導電層32と重畳する領域の酸化物半導体層10の上面近傍が、主として導電層35及び導電層36間のチャネルとなる領域である。

40

【0018】

上記の通り、図1(A)～(C)に示す半導体素子においては、電圧制御によって導電層33及び導電層34間の導通状態と、導電層35及び導電層36間の導通状態とを制御することが可能である。さらに、前者及び後者のチャネルは酸化物半導体層10中の異なる領域に設けられる。ここで、酸化物半導体は、バンドギャップが広く、且つ真性キャリア密度が低いという特徴を有する。よって、チャネルが形成されない領域の酸化物半導体

50

層 10 に生じる電流を極めて低くすることが可能である。これにより、前者及び後者のチャネルが同時に形成される場合であっても、目的としない導電層間に生じる電流を極めて低くすることが可能となる。また、トランジスタの意図した駆動によっては、二つのチャネルは必ずしも分離する必要はない、すなわち、二つのチャネルは酸化物半導体層における同じ領域を共有してもよい。

【 0 0 1 9 】

なお、酸化物半導体層 10 は、積層構造とすることもできる。その場合、酸化物半導体領域に挟まれた酸化物絶縁体領域を有する構成とすることが好ましい。具体的には、酸化物半導体層 10 が、下面を含む第 1 の酸化物半導体領域と、上面を含む第 2 の酸化物半導体領域と、第 1 の酸化物半導体領域及び第 2 の酸化物半導体領域に挟まれた酸化物絶縁体領域と、を有する構成とすることが好ましい。これにより、上述の両者のチャネルが同時に形成される場合であっても、目的としない導電層間に生じる電流をさらに低減することが可能となるからである。なお、当該酸化物絶縁体領域は、酸化アルミニウム、酸化シリコンなどを用いることができ、さらには、それらの積層（例えば、第 1 の酸化シリコン領域と、第 1 の酸化シリコン領域上の酸化アルミニウム領域と、酸化アルミニウム領域上の第 2 の酸化シリコン領域との積層）を用いることも可能である。

10

【 0 0 2 0 】

また、図 1 ( A ) ~ ( C ) に示す半導体素子のように、導電層 33 及び導電層 34 間のチャネルと、導電層 35 及び導電層 36 間のチャネルとが重畳する領域を有することは好ましい構成である。これにより、回路面積の低減を図ることが可能であるからである。ただし、本明細書で開示される半導体素子においては、酸化物半導体層にチャネルが形成される領域は特定の領域に限定されない。

20

【 0 0 2 1 】

また、図 1 ( A ) ~ ( C ) に示す半導体素子のように、導電層 31 が導電層 32 よりも導電層 33 及び導電層 34 に近接し、且つ導電層 32 が導電層 31 よりも導電層 35 及び導電層 36 に近接する構成は好ましい。以下、この点について具体的に述べる。当該半導体素子においては、導電層 31 ~ 導電層 36 のそれぞれに与えられる電位に応じて、酸化物半導体層 10 に生じる電界が変化する。そして、酸化物半導体層 10 では、この電界に依存したチャネルが形成されることになる。よって、当該半導体素子においては、意図しない 2 種の導電層（導電層 33 及び導電層 34 の少なくとも一と、導電層 35 及び導電層 36 の少なくとも一と）が電気的に接続する可能性がある。これに対して、当該半導体素子を図 1 ( A ) ~ ( C ) に示す構成とすることで、意図しない 2 種の導電層が電気的に接続する蓋然性を低減することが可能である。

30

【 0 0 2 2 】

< 半導体素子の変形例 >

図 1 ( A ) ~ ( C ) に示す半導体素子は本発明の半導体素子の一態様であり、図 1 ( A ) ~ ( C ) に示した半導体素子とは異なる構成を有する半導体素子も本発明の一態様には含まれる。例えば、図 2 ( A ) ~ ( C ) に示す半導体素子も本発明の一態様である。

【 0 0 2 3 】

図 2 ( A ) は半導体素子の上面図であり、図 2 ( B ) は図 2 ( A ) に示す線分 E F における当該半導体素子の断面図であり、図 2 ( C ) は図 2 ( A ) に示す線分 G H における当該半導体素子の断面図である。

40

【 0 0 2 4 】

図 2 ( A ) ~ ( C ) に示す半導体素子は、図 1 ( A ) ~ ( C ) に示す半導体素子と同様に、酸化物半導体層 10 と、絶縁層 21、22 と、導電層 31 ~ 36 と、を有する。ただし、図 2 ( A ) ~ ( C ) に示す半導体素子は、導電層 31 の一端が絶縁層 21 を介して導電層 33 の一端と重畳せず、且つ導電層 31 の他端が絶縁層 21 を介して導電層 34 の一端と重畳しない点が図 1 ( A ) ~ ( C ) に示す半導体素子と異なる。同様に、図 2 ( A ) ~ ( C ) に示す半導体素子は、導電層 32 の一端が絶縁層 22 を介して導電層 35 の一端と重畳せず、且つ導電層 32 の他端が絶縁層 22 を介して導電層 36 の一端と重畳しない

50

点が図 1 ( A ) ~ ( C ) に示す半導体素子と異なる。

【 0 0 2 5 】

これにより、図 2 ( A ) ~ ( C ) に示す半導体素子においては、図 1 ( A ) ~ ( C ) に示す半導体素子と比較して、導電層 3 3 及び導電層 3 4 間にチャネルが形成されない状態において生じる電流を低減させること、並びに導電層 3 5 及び導電層 3 6 間にチャネルが形成されない状態において生じる電流を低減させることが可能である。他方、図 1 ( A ) ~ ( C ) に示す半導体素子においては、図 2 ( A ) ~ ( C ) に示す半導体素子と比較して、導電層 3 3 及び導電層 3 4 間にチャネルが形成される状態において生じる電流を増加させること、並びに導電層 3 5 及び導電層 3 6 間にチャネルが形成される状態において生じる電流を増加させることが可能である。

10

【 0 0 2 6 】

< 酸化物半導体層 1 0 >

図 1、2 に示す半導体素子が有する酸化物半導体層 1 0 は、少なくともインジウム ( I n ) あるいは亜鉛 ( Z n ) を含むことが好ましい。特に I n 及び Z n を含むことが好ましい。また、酸化物半導体層 1 0 を有する半導体素子の電気特性のばらつきを低減するためのスタビライザーとして、I n 及び Z n に加えて、ガリウム ( G a ) を含むことが好ましい。また、スタビライザーとしてスズ ( S n ) を含むことが好ましい。また、スタビライザーとしてハフニウム ( H f ) を含むことが好ましい。また、スタビライザーとしてアルミニウム ( A l ) を含むことが好ましい。

【 0 0 2 7 】

20

また、他のスタビライザーとして、ランタノイドである、ランタン ( L a ) 、セリウム ( C e ) 、プラセオジム ( P r ) 、ネオジム ( N d ) 、サマリウム ( S m ) 、ユウロピウム ( E u ) 、ガドリニウム ( G d ) 、テルビウム ( T b ) 、ジスプロシウム ( D y ) 、ホルミウム ( H o ) 、エルビウム ( E r ) 、ツリウム ( T m ) 、イッテルビウム ( Y b ) 、ルテチウム ( L u ) のいずれか一種あるいは複数種を含んでいてもよい。

【 0 0 2 8 】

例えば、酸化物半導体層 1 0 を構成する酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物である I n - Z n 系酸化物、 S n - Z n 系酸化物、 A l - Z n 系酸化物、 Z n - M g 系酸化物、 S n - M g 系酸化物、 I n - M g 系酸化物、 I n - G a 系酸化物、三元系金属の酸化物である I n - G a - Z n 系酸化物 ( I G Z O とも表記する ) 、 I n - A l - Z n 系酸化物、 I n - S n - Z n 系酸化物、 S n - G a - Z n 系酸化物、 A l - G a - Z n 系酸化物、 S n - A l - Z n 系酸化物、 I n - H f - Z n 系酸化物、 I n - L a - Z n 系酸化物、 I n - C e - Z n 系酸化物、 I n - P r - Z n 系酸化物、 I n - N d - Z n 系酸化物、 I n - S m - Z n 系酸化物、 I n - E u - Z n 系酸化物、 I n - G d - Z n 系酸化物、 I n - T b - Z n 系酸化物、 I n - D y - Z n 系酸化物、 I n - H o - Z n 系酸化物、 I n - E r - Z n 系酸化物、 I n - T m - Z n 系酸化物、 I n - Y b - Z n 系酸化物、 I n - L u - Z n 系酸化物、四元系金属の酸化物である I n - S n - G a - Z n 系酸化物、 I n - H f - G a - Z n 系酸化物、 I n - A l - G a - Z n 系酸化物、 I n - S n - A l - Z n 系酸化物、 I n - S n - H f - Z n 系酸化物、 I n - H f - A l - Z n 系酸化物を用いることができる。また、上記酸化物半導体に S i を含ませてもよい。

30

【 0 0 2 9 】

なお、 I n - G a - Z n 系酸化物半導体とは、インジウム ( I n ) 、ガリウム ( G a ) 、及び亜鉛 ( Z n ) を含む酸化物半導体、という意味であり、その組成比は問わない。また、 I n と G a と Z n 以外の金属元素が含まれていてもよい。

【 0 0 3 0 】

また、酸化物半導体層は、化学式 I n M O <sub>3</sub> ( Z n O ) <sub>m</sub> ( m > 0 ) で表記される薄膜を用いることもできる。ここで、 M は、 Z n 、 G a 、 A l 、 M n 、 F e 及び C o から選ばれた一または複数の金属元素を示す。例えば M として、 G a 、 G a 及び A l 、 G a 及び M n 、または G a 及び C o などがある。また、酸化物半導体層として、 I n <sub>3</sub> S n O <sub>5</sub> ( Z

40

50

$nO_n$  ( $n > 0$ 、且つ、 $n$  は整数) で表記される材料を用いてもよい。

【0031】

より具体的には、 $In : Ga : Zn = 1 : 1 : 1$  ( $= 1/3 : 1/3 : 1/3$ ) あるいは  $In : Ga : Zn = 2 : 2 : 1$  ( $= 2/5 : 2/5 : 1/5$ ) の原子数比の  $In - Ga - Zn$  系酸化物やその組成の近傍の酸化物を用いることができる。また、 $In : Sn : Zn = 1 : 1 : 1$  ( $= 1/3 : 1/3 : 1/3$ )、 $In : Sn : Zn = 2 : 1 : 3$  ( $= 1/3 : 1/6 : 1/2$ )、あるいは  $In : Sn : Zn = 2 : 1 : 5$  ( $= 1/4 : 1/8 : 5/8$ ) の原子数比の  $In - Sn - Zn$  系酸化物やその組成の近傍の酸化物を用いることができる。

【0032】

また、酸化物半導体として  $In - Zn$  系の材料を用いる場合、原子数比で、 $In/Zn = 0.5 \sim 5.0$ 、好ましくは  $In/Zn = 1 \sim 2.0$ 、さらに好ましくは  $In/Zn = 1.5 \sim 1.5$  とする。 $Zn$  の原子数比を好ましい前記範囲とすることで、上述の半導体素子における電界効果移動度を向上させることができる。ここで、化合物の原子数比が  $In : Zn : O = X : Y : Z$  のとき、 $Z > 1.5X + Y$  とする。

【0033】

しかし、これらに限らず、必要とする半導体特性（例えば、電界効果移動度等）に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

【0034】

例えば、 $In - Sn - Zn$  系酸化物では比較的容易に高い電界効果移動度が得られる。しかしながら、 $In - Ga - Zn$  系酸化物でも、バルク内欠陥密度を低減することにより電界効果移動度を向上させることができる。

【0035】

なお、例えば、 $In, Ga, Zn$  の原子数比が  $In : Ga : Zn = a : b : c$  ( $a + b + c = 1$ ) である酸化物の組成が、原子数比が  $In : Ga : Zn = A : B : C$  ( $A + B + C = 1$ ) の酸化物の組成の近傍であるとは、 $a, b, c$  が、 $(a - A)^2 + (b - B)^2 + (c - C)^2 = r^2$  を満たすことをいい、 $r$  は、例えば、 $0.05$  とすればよい。他の酸化物でも同様である。

【0036】

なお、上述したように酸化物半導体層 10 が第 1 及び第 2 の酸化物半導体領域並びに酸化物絶縁体領域を含む場合には、酸化物半導体領域を少なくとも  $In, Ga, Sn$  及び  $Zn$  から選ばれた一種以上の元素を用いて構成し、酸化物絶縁体領域を酸化アルミニウム、酸化シリコンなどを用いて構成することが可能である。

【0037】

また、酸化物半導体層 10 としては、電子供与体（ドナー）となる水分又は水素などの不純物が低減されて高純度化される（ $i$  型化又は  $i$  型に限りなく近い状態にされる）ことが好ましい。これにより、酸化物半導体層 10 にチャネルが形成されない状態において生じる電流を低減することが可能となるからである。具体的には、高純度化された酸化物半導体層 10 は、二次イオン質量分析法（S I M S : Secondary Ion Mass Spectrometry）による水素濃度の測定値が、 $5 \times 10^{-9} / \text{cm}^3$  以下、好ましくは  $5 \times 10^{-8} / \text{cm}^3$  以下、より好ましくは  $5 \times 10^{-7} / \text{cm}^3$  以下、更に好ましくは  $1 \times 10^{-6} / \text{cm}^3$  以下である。また、ホール効果測定により測定できる酸化物半導体層のキャリア密度は、 $1 \times 10^{-4} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{-2} / \text{cm}^3$  未満、更に好ましくは  $1 \times 10^{-1} / \text{cm}^3$  未満である。

【0038】

ここで、酸化物半導体層中の、水素濃度の分析について触れておく。半導体層中の水素濃度測定は、二次イオン質量分析法で行う。S I M S 分析は、その原理上、試料表面近傍や、材質が異なる層との積層界面近傍のデータを正確に得ることが困難であることが知ら

10

20

30

40

50

れている。そこで、層中における水素濃度の厚さ方向の分布をS I M Sで分析する場合、対象となる層が存在する範囲において、値に極端な変動がなく、ほぼ一定の値が得られる領域における平均値を、水素濃度として採用する。また、測定の対象となる層の厚さが小さい場合、隣接する層内の水素濃度の影響を受けて、ほぼ一定の値が得られる領域を見いだせない場合がある。この場合、当該層が存在する領域における、水素濃度の極大値又は極小値を、当該層中の水素濃度として採用する。更に、当該層が存在する領域において、極大値を有する山型のピーク、極小値を有する谷型のピークが存在しない場合、変曲点の値を水素濃度として採用する。

## 【0039】

スパッタリング法を用いて酸化物半導体層10を作製する場合には、ターゲット中の水素濃度のみならず、チャンバー内に存在する水、水素を極力低減しておくことが重要である。具体的には、当該形成以前にチャンバー内をベークする、チャンバー内に導入されるガス中の水、水素濃度を低減する、及びチャンバーからガスを排気する排気系における逆流を防止するなどを行うことが効果的である。

## 【0040】

また、酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでもよいし、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でもよいし、非アモルファスでもよい。

## 【0041】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるために、これを用いて半導体素子を作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

## 【0042】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の電界効果移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ( $R_a$ )が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

## 【0043】

なお、 $R_a$ は、J I S B 0 6 0 1で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、以下の式にて定義される。

## 【0044】

## 【数1】

$$R_a = \frac{1}{S_0} \int_{y_1}^{y_2} \int_{x_1}^{x_2} |f(x, y) - Z_0| dx dy$$

## 【0045】

上記において、 $S_0$ は、測定面(座標( $x_1, y_1$ ) ( $x_1, y_2$ ) ( $x_2, y_1$ ) ( $x_2, y_2$ )で表される4点によって囲まれる長方形の領域)の面積を指し、 $Z_0$ は測定面の平均高さを指す。 $R_a$ は原子間力顕微鏡(A F M : A t o m i c F o r c e M i c r o s c o p e)にて評価可能である。

## 【0046】

また、非単結晶である酸化物半導体層10の一例として、c軸配向を有した結晶(C Axis Aligned Crystal: C A A Cとも呼ぶ)を含む酸化物半導体(C A A C - O S)膜を用いることも可能である。

## 【0047】

具体的には、C A A C - O S膜は、C A A C - O S膜が成膜される膜表面に平行なa-b面において六角形の格子を有する結合を有し、なおかつ、a-b面に概略垂直なc軸配向を有する、六方晶構造の亜鉛を含む結晶を有する。

## 【0048】

10

20

30

40

50

C AAC - OS 膜は単結晶ではないが、非晶質のみから形成されているものでもない。また、C AAC - OS 膜は結晶化した部分（結晶部分）を含むが、1つの結晶部分と他の結晶部分の境界を明確に判別できることもある。

【0049】

C AAC - OS 膜を構成する酸素の一部は窒素で置換されてもよい。また、C AAC - OS 膜を構成する個々の結晶部分の c 軸は一定の方向（例えば、C AAC - OS 膜を支持する基板面、C AAC - OS 膜の表面などに垂直な方向）に揃っていてもよい。または、C AAC - OS 膜を構成する個々の結晶部分の a b 面の法線は一定の方向（例えば、C AAC - OS 膜を支持する基板面、C AAC - OS 膜の表面などに垂直な方向）を向いていてもよい。

10

【0050】

C AAC - OS 膜は、その組成などに応じて、導体であったり、半導体であったり、絶縁体であったりする。また、その組成などに応じて、可視光に対して透明であったり不透明であったりする。

【0051】

このようなC AAC - OS 膜の例として、膜状に形成され、膜表面または支持する基板面に垂直な方向から観察すると三角形または六角形の原子配列が認められ、かつその膜断面を観察すると金属原子または金属原子及び酸素原子（または窒素原子）の層状配列が認められる結晶を挙げることもできる。

【0052】

C AAC - OS 膜は、非晶質の酸化物半導体と比較して、金属と酸素の結合が秩序化している。すなわち、酸化物半導体が非晶質の場合は、個々の金属原子によって配位数が異なることも有り得るが、C AAC - OS 膜では金属原子の配位数はほぼ一定となる。そのため、微視的な酸素の欠損が減少し、水素原子（水素イオンを含む）又はアルカリ金属原子の脱着による電荷の移動や不安定性を減少させる効果がある。

20

【0053】

したがって、酸化物半導体層 10 を C AAC - OS 膜で構成することによって、上述の半導体素子の信頼性を向上させることが可能である。

【0054】

なお、スパッタリング法を用いて C AAC - OS 膜を成膜する場合には、雰囲気中の酸素ガス比が高い方が好ましい。例えば、アルゴン及び酸素の混合ガス雰囲気中でスパッタリング法を行う場合には、酸素ガス比を 30 % 以上とすることが好ましく、40 % 以上とすることがより好ましい。雰囲気中からの酸素の補充によって、C AAC - OS 膜の結晶化が促進されるからである。

30

【0055】

また、スパッタリング法を用いて C AAC - OS 膜を成膜する場合には、C AAC - OS 膜が成膜される基板を 150 以上に加熱しておくことが好ましく、170 以上に加熱しておくことがより好ましい。基板温度の上昇に伴って、C AAC - OS 膜の結晶化が促進されるからである。

【0056】

また、C AAC - OS 膜に対して、窒素雰囲気中又は真空中において熱処理を行った後には、酸素雰囲気中又は酸素と他のガスとの混合雰囲気中において熱処理を行うことが好ましい。先の熱処理で生じる酸素欠損を後の熱処理における雰囲気中からの酸素供給によって復元することができるからである。

40

【0057】

また、C AAC - OS 膜が成膜される膜表面（被成膜面）は平坦であることが好ましい。C AAC - OS 膜は、当該被成膜面に概略垂直となる c 軸を有するため、当該被成膜面に存在する凹凸は、C AAC - OS 膜における結晶粒界の発生を誘発することになるからである。よって、C AAC - OS 膜が成膜される前に当該被成膜表面に対して化学機械研磨（Chemical Mechanical Polishing : CMP）などの平

50

坦化処理を行うことが好ましい。また、当該被成膜面の平均ラフネスは、0.5 nm以下であることが好ましく、0.3 nm以下であることがより好ましい。

【0058】

<絶縁層21、22>

図1、2に示す半導体素子が有する絶縁層21、22として、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化タンタルなどの絶縁体を適用することができる。また、これらの材料の積層構造を適用することもできる。なお、酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものであり、濃度範囲として酸素が55～65原子%、窒素が1～20原子%、シリコンが25～35原子%、水素が0.1～10原子%の範囲において、合計100原子%となるように各元素を任意の濃度で含むものをいう。また、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多いものであり、濃度範囲として酸素が15～30原子%、窒素が20～35原子%、Siが25～35原子%、水素が15～25原子%の範囲において、合計100原子%となるように各元素を任意の濃度で含むものをいう。

10

【0059】

<導電層31～36>

図1、2に示す半導体素子が有する導電層31～36として、アルミニウム(A1)、銅(Cu)、チタン(Ti)、タンタル(Ta)、タンゲステン(W)、モリブデン(Mo)、クロム(Cr)、ネオジム(Nd)、スカンジウム(Sc)から選ばれた元素、上述した元素を成分とする合金、または上述した元素を成分とする窒化物を適用することができる。また、これらの材料の積層構造を適用することもできる。

20

【0060】

<CACACの一例>

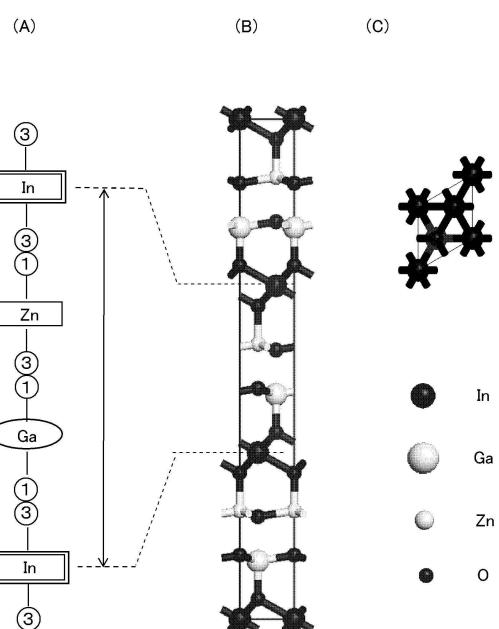

次いで、上述したCACACの一例について、図6乃至図8を用いて詳細に説明する。なお、特に断りがない限り、図6乃至図8は上方向をc軸方向とし、c軸方向と直交する面をab面とする。なお、単に上半分、下半分という場合、ab面を境にした場合の上半分、下半分をいう。また、図6において、丸で囲まれたOは4配位のOを示し、二重丸で囲まれたOは3配位のOを示す。

【0061】

図6(A)に、1個の6配位のInと、Inに近接の6個の4配位の酸素原子(以下4配位のO)と、を有する構造を示す。ここでは、金属原子が1個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。図6(A)の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図6(A)の上半分及び下半分にはそれぞれ3個ずつ4配位のOがある。図6(A)に示す小グループは電荷が0である。

30

【0062】

図6(B)に、1個の5配位のGaと、Gaに近接の3個の3配位の酸素原子(以下3配位のO)と、Gaに近接の2個の4配位のOと、を有する構造を示す。3配位のOは、いずれもab面に存在する。図6(B)の上半分及び下半分にはそれぞれ1個ずつ4配位のOがある。また、Inも5配位をとるため、図6(B)に示す構造をとりうる。図6(B)に示す小グループは電荷が0である。

40

【0063】

図6(C)に、1個の4配位のZnと、Znに近接の4個の4配位のOと、を有する構造を示す。図6(C)の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。また、図6(C)の上半分に3個の4配位のOがあり、下半分に1個の4配位のOがあつてもよい。図6(C)に示す小グループは電荷が0である。

【0064】

図6(D)に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造を示す。図6(D)の上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。図6(D)に示す小グループは電荷が+1となる。

【0065】

50

図6(E)に、2個のZnを含む小グループを示す。図6(E)の上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。図6(E)に示す小グループは電荷が-1となる。

#### 【0066】

ここでは、複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を大グループ(ユニットセルともいう。)と呼ぶ。

#### 【0067】

ここで、これらの小グループ同士が結合する規則について説明する。図6(A)に示す6配位のInの上半分の3個のOは、下方向にそれぞれ3個の近接Inを有し、下半分の3個のOは、上方向にそれぞれ3個の近接Inを有する。図6(B)に示す5配位のGaの上半分の1個のOは、下方向に1個の近接Gaを有し、下半分の1個のOは、上方向に1個の近接Gaを有する。図6(C)に示す4配位のZnの上半分の1個のOは、下方向に1個の近接Znを有し、下半分の3個のOは、上方向にそれぞれ3個の近接Znを有する。この様に、金属原子の上方向の4配位のOの数と、そのOの下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のOの数と、そのOの上方向にある近接金属原子の数は等しい。Oは4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。従って、金属原子の上方向にある4配位のOの数と、別の金属原子の下方向にある4配位のOの数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。例えば、6配位の金属原子(InまたはSn)が下半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子(GaまたはIn)または4配位の金属原子(Zn)のいずれかと結合することになる。

10

20

30

#### 【0068】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。また、このほかにも、層構造の合計の電荷が0となるように複数の小グループが結合して中グループを構成する。

#### 【0069】

図7(A)に、In-Sn-Zn-O系の層構造を構成する中グループのモデル図を示す。図7(B)に、3つの中グループで構成される大グループを示す。なお、図7(C)は、図7(B)の層構造をc軸方向から観察した場合の原子配列を示す。

30

#### 【0070】

図7(A)においては、簡単のため、3配位のOは省略し、4配位のOは個数のみ示し、例えば、Snの上半分及び下半分にはそれぞれ3個ずつ4配位のOがあることを丸枠の3として示している。同様に、図7(A)において、Inの上半分及び下半分にはそれぞれ1個ずつ4配位のOがあり、丸枠の1として示している。また、同様に、図7(A)において、下半分には1個の4配位のOがあり、上半分には3個の4配位のOがあるZnと、上半分には1個の4配位のOがあり、下半分には3個の4配位のOがあるZnとを示している。

#### 【0071】

図7(A)において、In-Sn-Zn-O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分及び下半分にあるSnが、4配位のOが1個ずつ上半分及び下半分にあるInと結合し、そのInが、上半分に3個の4配位のOがあるZnと結合し、そのZnの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分及び下半分にあるInと結合し、そのInが、上半分に1個の4配位のOがあるZn2個からなる小グループと結合し、この小グループの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分及び下半分にあるSnと結合している構成である。この中グループが複数結合して大グループを構成する。

40

#### 【0072】

ここで、3配位のO及び4配位のOの場合、結合1本当たりの電荷はそれぞれ-0.667、-0.5と考えることができる。例えば、In(6配位または5配位)、Zn(4

50

配位)、 $S_n$ (5配位または6配位)の電荷は、それぞれ+3、+2、+4である。従つて、 $S_n$ を含む小グループは電荷が+1となる。そのため、 $S_n$ を含む層構造を形成するためには、電荷+1を打ち消す電荷-1が必要となる。電荷-1をとる構造として、図6(E)に示すように、2個の $Z_n$ を含む小グループが挙げられる。例えば、 $S_n$ を含む小グループが1個に対し、2個の $Z_n$ を含む小グループが1個あれば、電荷が打ち消されるため、層構造の合計の電荷を0とすることができます。

#### 【0073】

具体的には、図7(B)に示した大グループが繰り返されることで、 $In-Sn-Zn-O$ 系の結晶( $In_2SnZn_3O_8$ )を得ることができる。なお、得られる $In-Sn-Zn-O$ 系の層構造は、 $In_2SnZn_2O_7 (ZnO)_m$ ( $m$ は0または自然数。)とする組成式で表すことができる。

10

#### 【0074】

また、このほかにも、四元系金属の酸化物である $In-Sn-Ga-Zn$ 系酸化物や、三元系金属の酸化物である $In-Ga-Zn$ 系酸化物( $IGZO$ とも表記する。)、 $In-Al-Zn$ 系酸化物、 $Sn-Ga-Zn$ 系酸化物、 $Al-Ga-Zn$ 系酸化物、 $Sn-Al-Zn$ 系酸化物や、 $In-Hf-Zn$ 系酸化物、 $In-La-Zn$ 系酸化物、 $In-Ce-Zn$ 系酸化物、 $In-Pr-Zn$ 系酸化物、 $In-Nd-Zn$ 系酸化物、 $In-Sm-Zn$ 系酸化物、 $In-Eu-Zn$ 系酸化物、 $In-Gd-Zn$ 系酸化物、 $In-Tb-Zn$ 系酸化物、 $In-Dy-Zn$ 系酸化物、 $In-Ho-Zn$ 系酸化物、 $In-Er-Zn$ 系酸化物、 $In-Tm-Zn$ 系酸化物、 $In-Yb-Zn$ 系酸化物、 $In-Lu-Zn$ 系酸化物や、二元系金属の酸化物である $In-Zn$ 系酸化物、 $Sn-Zn$ 系酸化物、 $Al-Zn$ 系酸化物、 $Zn-Mg$ 系酸化物、 $Sn-Mg$ 系酸化物、 $In-Mg$ 系酸化物や、 $In-Ga$ 系酸化物などを用いた場合も同様である。

20

#### 【0075】

例えば、図8(A)に、 $In-Ga-Zn-O$ 系の層構造を構成する中グループのモデル図を示す。

#### 【0076】

図8(A)において、 $In-Ga-Zn-O$ 系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分及び下半分にある $In$ が、4配位のOが1個上半分にある $Zn$ と結合し、その $Zn$ の下半分の3個の4配位のOを介して、4配位のOが1個ずつ上半分及び下半分にある $Ga$ と結合し、その $Ga$ の下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分及び下半分にある $In$ と結合している構成である。この中グループが複数結合して大グループを構成する。

30

#### 【0077】

図8(B)に3つの中グループで構成される大グループを示す。なお、図8(C)は、図8(B)の層構造をc軸方向から観察した場合の原子配列を示している。

#### 【0078】

ここで、 $In$ (6配位または5配位)、 $Zn$ (4配位)、 $Ga$ (5配位)の電荷は、それぞれ+3、+2、+3であるため、 $In$ 、 $Zn$ 及び $Ga$ のいずれかを含む小グループは、電荷が0となる。そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に0となる。

40

#### 【0079】

また、 $In-Ga-Zn-O$ 系の層構造を構成する中グループは、図8(A)に示した中グループに限定されず、 $In$ 、 $Ga$ 、 $Zn$ の配列が異なる中グループを組み合わせた大グループも取りうる。

#### 【0080】

<半導体素子を有する記憶回路>

次いで、上述した半導体素子を有する記憶回路について図3を参照して説明する。図3(A)、(B)は、記憶回路の構成例を示す図である。具体的には、図3(A)、(B)は、上述した半導体素子と、2つの記憶素子と、を有する記憶回路の構成例を示す図であ

50

る。なお、当該半導体素子は、酸化物半導体層 10 に電気的に接続された 4 つの端子（図 1、2 における導電層 33～36 に対応）を有すると表現できる。さらに、当該 4 つの端子に含まれる、いずれか 2 つの端子間の電気的な接続及び残りの 2 つの端子間の電気的な接続を制御する機能を有すると表現できる。この点に鑑み、本明細書においては、図 3 (A)、(B) に示す 50 が付された記号を上述の半導体素子を表す記号として使用することとする。

#### 【0081】

図 3 (A) に示す記憶回路は、第 1 の端子が第 1 の入出力端子 (In / Out 1) として機能し、第 2 の端子が第 2 の入出力端子 (In / Out 2) として機能する半導体素子 50 と、一方の電極が半導体素子 50 の第 3 の端子に電気的に接続され、他方の電極が一定電位を供給する配線 53 に電気的に接続された容量素子 51 と、一方の電極が半導体素子 50 の第 4 の端子に電気的に接続され、他方の電極が一定電位を供給する配線 53 に電気的に接続された容量素子 52 と、を有する。

#### 【0082】

なお、図 3 (A) に示す記憶回路は、半導体素子 50 の第 3 の端子及び容量素子 51 の一方の電極が電気的に接続する第 1 のノードにおいてデータの保持を行う記憶素子と、半導体素子 50 の第 4 の端子及び容量素子 52 の一方の電極が電気的に接続する第 2 のノードにおいてデータの保持を行う記憶素子とを有すると表現できる。また、当該一定電位としては、接地電位 (GND) 又は 0V などを適用することが可能である。

#### 【0083】

図 3 (A) に示す記憶回路では、第 1 のノード及び第 2 のノードのそれぞれの電位（容量素子 51 及び容量素子 52 のそれぞれに保持される電荷）を 2 値又は多値のデータに対応させることができ。具体的には、読み出し時に第 1 の入出力端子又は第 2 の入出力端子に電気的に接続された配線の電位が、第 1 のノード及び第 2 のノードのそれぞれの電位（容量素子 51 及び容量素子 52 のそれぞれに保持される電荷）に応じて変動する。この時の当該配線の電位の値によって保持されたデータを判別することが可能である。

#### 【0084】

図 3 (B) に示す記憶回路は、第 1 の端子が第 1 の入力端子 (In 1) として機能し、第 2 の端子が第 2 の入力端子 (In 2) として機能する半導体素子 50 と、ゲートが半導体素子 50 の第 3 の端子に電気的に接続され、ソース及びドレインの一方が一定電位を供給する配線 58 に電気的に接続され、ソース及びドレインの一方が第 1 の出力端子 (Out 1) として機能するトランジスタ 54 と、一方の電極が半導体素子 50 の第 3 の端子及びトランジスタ 54 のゲートに電気的に接続され、他方の電極が読み出しワード線 59 に電気的に接続された容量素子 55 と、ゲートが半導体素子 50 の第 4 の端子に電気的に接続され、ソース及びドレインの一方が一定電位を供給する配線 58 に電気的に接続され、ソース及びドレインの一方が第 2 の出力端子 (Out 2) として機能するトランジスタ 56 と、一方の電極が半導体素子 50 の第 4 の端子及びトランジスタ 56 のゲートに電気的に接続され、他方の電極が読み出しワード線 59 に電気的に接続された容量素子 57 と、を有する。

#### 【0085】

なお、図 3 (B) に示す記憶回路は、半導体素子 50 の第 3 の端子、トランジスタ 54 のゲート、及び容量素子 55 の一方の電極が電気的に接続する第 1 のノードにおいてデータの保持を行う記憶素子と、半導体素子 50 の第 4 の端子、トランジスタ 56 のゲート、及び容量素子 57 の一方の電極が電気的に接続する第 2 のノードにおいてデータの保持を行う記憶素子とを有すると表現できる。また、当該一定電位としては、接地電位 (GND) 又は 0V などを適用することが可能である。また、トランジスタ 54、56 が有する半導体材料は特に限定されない。

#### 【0086】

図 3 (B) に示す記憶回路では、第 1 のノード又は第 2 のノードの電位に応じて、トランジスタ 54、56 のスイッチングを制御することが可能である。加えて、第 1 のノード

10

20

30

40

50

及び第2のノードの電位は、読み出しワード線59との容量結合によって制御することが可能である。そのため、図3(B)に示す記憶回路では、多値の情報を記憶することが可能である。すなわち、読み出しワード線59の電位が異なる複数の条件においてトランジスタ54、56の導通状態(オン状態又はオフ状態)を判別することで、第1のノード又は第2のノードの電位が多値化されても読み出しを行うことが可能である。なお、当該読み出しが、トランジスタ54又はトランジスタ56を用いて構成された分圧回路の出力信号を判別することなどによって行うことができる。また、図3(B)に示す記憶回路は、2値のデータを保持するメモリセルとして使用することもできる。

#### 【0087】

図3(A)、(B)に示す記憶回路においては、2つの記憶素子に対するデータの入力を単体の半導体素子50によって制御することが可能である。よって、別個にスイッチを設ける場合と比較して回路面積を縮小することが可能となる。 10

#### 【0088】

<記憶回路を有する集積回路>

次いで、上述した記憶回路を有する集積回路について図4を参照して説明する。図4(A)、(B)は、集積回路の構成例を示すブロック図であり、図4(C)は、当該集積回路の動作例を示すフローチャートである。

#### 【0089】

図4(A)は、半導体素子50を介して2つのフリップフロップ(FF1、2)と、2つの記憶素子(MC1、2)とのデータの直接的な授受が可能な集積回路を示すブロック図であり、図4(B)は、半導体素子50を介した2つのフリップフロップ(FF1、2)から2つの記憶素子(MC1、2)へのデータの転送と、バッファ(BF1、2)を介した2つの記憶素子から2つのフリップフロップ(FF1、2)へのデータの転送とを行うことが可能な集積回路を示すブロック図である。例えば、図3(A)に示す記憶回路を有する集積回路として図4(A)に示す構成を適用することが可能であり、図3(B)に示す記憶回路を有する集積回路として図4(B)に示す構成を適用することが可能である。 20

#### 【0090】

なお、図4(A)、(B)に示すフリップフロップ(FF1、2)としては、1ビットのデータの保持が可能な揮発性メモリであればどのような回路を適用してもよい。また、図4(B)に示すバッファ(BF1、2)としては、記憶素子(MC1、2)に保持されたデータをフリップフロップ(FF1、2)に対して転送することができる構成であればどのような回路を適用してもよい。 30

#### 【0091】

図4(C)は、フリップフロップ(FF1、2)に対する電源電圧の供給を停止する場合の動作例を示すフローチャートである。ここで、半導体素子50は、酸化物半導体層10におけるチャネルの形成を制御することでスイッチとして機能する素子である。上述したように、酸化物半導体層10においては、チャネルが形成されない領域に生じる電流を極めて低くすることが可能である。よって、記憶素子(MC1、MC2)では、長期間に渡ってデータの保持を行うことが可能である。 40

#### 【0092】

図4(C)に示すように、当該集積回路においては、電源電圧の供給を停止する前にフリップフロップ(FF1、2)が保持するデータを記憶素子(MC1、2)へと転送する。電源電圧の供給停止に伴ってフリップフロップ(FF1、2)から消失するデータを退避させるためである。なお、半導体素子50においては、フリップフロップ(FF1)から記憶素子(MC1)へのデータの転送と、フリップフロップ(FF2)から記憶素子(MC2)へのデータの転送とを同時にすることが可能である。

#### 【0093】

次いで、フリップフロップ(FF1、2)に対する電源電圧の供給を停止する。これにより、当該集積回路における消費電力を低減することが可能となる。 50

## 【0094】

次いで、フリップフロップ（FF1、2）に対する電源電圧の供給を再開する。

## 【0095】

次いで、記憶素子（MC1、2）が保持するデータをフリップフロップ（FF1、2）へと転送する。フリップフロップ（FF1、2）のデータを復元するためである。なお、図4（A）に示す半導体素子50においては、記憶素子（MC1）からフリップフロップ（FF1）へのデータの転送と、記憶素子（MC2）からフリップフロップ（FF2）へのデータの転送とを同時に行うことが可能である。

## 【0096】

図4（A）、（B）に示す集積回路は、半導体素子50を有する。よって、回路面積を縮小することが可能である。また、図4（C）に示す動作を行うことによって、当該集積回路における消費電力を低減することが可能である。さらに、当該集積回路においては、2つのフリップフロップ（FF1、2）から2つの記憶素子（MC1、2）へのデータの転送、又は2つの記憶素子（MC1、2）から2つのフリップフロップ（FF1、2）へのデータの転送を同時に行うことによって、動作速度を向上させることが可能である。10

## 【0097】

<集積回路の構造例>

次いで、上述した集積回路の構造例について図5を参照して説明する。

## 【0098】

集積回路が有するフリップフロップ（FF1、2）は、トランジスタなどを用いて構成される。ここで、当該トランジスタとしては、電界効果移動度の高いトランジスタを適用することが好ましい。よって、上述の半導体素子50は、酸化物半導体層10にチャネルが形成されるのに対して、当該トランジスタは、多結晶シリコン層又は単結晶シリコン層にチャネルが形成されるトランジスタであることが好ましい。20

## 【0099】

図5は、そのような集積回路の構造例を示す図である。図5に示す集積回路は、当該フリップフロップなどを含む機能回路部61を有する単結晶シリコン基板60と、機能回路部61と重畳する領域に設けられる半導体素子50を有する層70とを有する。そして、層70に設けられる開口部において当該フリップフロップと、半導体素子50とを電気的に接続させる。図5に示すように、集積回路が有する機能回路部61と、半導体素子50とを重畳して設ける構造は、好ましい構造である。さらなる回路面積の縮小が可能となるからである。30

## 【0100】

なお、本明細書で開示される集積回路は、図5に示す構造に限定されないことを付記する。例えば、図5では単結晶シリコン基板60を有する集積回路について例示したが、単結晶シリコン基板60を絶縁表面上に単結晶シリコン層が設けられた基板（いわゆる、SOI基板）に置換することなどが可能である。

## 【符号の説明】

## 【0101】

|     |         |

|-----|---------|

| 1 0 | 酸化物半導体層 |

| 2 1 | 絶縁層     |

| 2 2 | 絶縁層     |

| 3 1 | 導電層     |

| 3 2 | 導電層     |

| 3 3 | 導電層     |

| 3 4 | 導電層     |

| 3 5 | 導電層     |

| 3 6 | 導電層     |

| 5 0 | 半導体素子   |

| 5 1 | 容量素子    |

10

20

30

40

50

5 2 容量素子

5 3 配線

5 4 トランジスタ

5 5 容量素子

5 6 トランジスタ

5 7 容量素子

5 8 配線

5 9 配線

6 0 単結晶シリコン基板

6 1 機能回路部

7 0 層

10

【図1】

(A)

(B)

(C)

【図2】

(A)

(B)

(C)

【図3】

(B)

【図4】

(C)

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(51)Int.Cl.

| F I     |             |

|---------|-------------|

| H 0 1 L | 27/10 4 8 1 |

| H 0 1 L | 27/10 4 9 5 |

| C 2 3 C | 14/08 K     |

(56)参考文献 特開2010-157702 (JP, A)

特表2007-529119 (JP, A)

特開2010-123938 (JP, A)

特開平04-267551 (JP, A)

特開平03-132041 (JP, A)

特開2010-287735 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 1 / 3 3 6、2 9 / 7 8 6