(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6422319号

(P6422319)

(45) 発行日 平成30年11月14日(2018.11.14)

(24) 登録日 平成30年10月26日(2018.10.26)

(51) Int.Cl.

H04N 5/378 (2011.01)

F 1

H04N 5/378

請求項の数 16 (全 18 頁)

(21) 出願番号 特願2014-244334 (P2014-244334)

(22) 出願日 平成26年12月2日 (2014.12.2)

(65) 公開番号 特開2016-111402 (P2016-111402A)

(43) 公開日 平成28年6月20日 (2016.6.20)

審査請求日 平成29年12月1日 (2017.12.1)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 中村 恒一

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 板野 哲也

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

最終頁に続く

(54) 【発明の名称】撮像装置、及びそれを用いた撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

行列状に配置された複数の画素と、

それぞれが前記複数の画素の少なくとも1つの画素列に対応して設けられ、それぞれが

動作を制御するためのスイッチを含む複数の比較器と、

前記複数の比較器の前記スイッチに対して共通に設けられ、前記複数の比較器の前記ス

イッチを制御する制御信号を供給するための信号線と、

前記信号線に前記制御信号を供給する制御信号生成部と、

を有する撮像装置において、

前記撮像装置は、前記信号線の電位を固定電位に制御するための信号線制御部をさらに

有し、

前記制御信号生成部と、前記信号線制御部との間に、前記複数の比較器が配置されてい

ることを特徴とする撮像装置。

## 【請求項 2】

前記複数の比較器のそれぞれは、入力端子と、出力端子とを含む差動增幅回路を有し、

前記複数の比較器のそれぞれにおいて、前記スイッチは、前記出力端子と一端が接続され、

前記入力端子と前記出力端子との接続を制御することを特徴とする請求項1に記載の

撮像装置。

## 【請求項 3】

前記複数の比較器のそれぞれにおいて、前記スイッチの他端は前記入力端子と接続され

10

20

ていることを特徴とする請求項 2 に記載の撮像装置。

【請求項 4】

前記スイッチがオンしている期間は、前記信号線制御部は動作しないことを特徴とする請求項 2 または 3 に記載の撮像装置。

【請求項 5】

前記複数の比較器のそれぞれは、電流源を含む差動增幅回路を有し、

前記スイッチは、前記電流源のオンオフを制御することを特徴とする請求項 1 に記載の撮像装置。

【請求項 6】

前記信号線制御部は、固定電位を供給する電源と、前記固定電位と前記信号線との接続を制御する第 2 のスイッチとを有することを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の撮像装置。 10

【請求項 7】

前記信号線制御部は、入力端子と出力端子を含むバッファを有し、

前記信号線は、第 1 の信号線と第 2 の信号線とを有し、

前記第 1 の信号線は前記バッファの前記入力端子と接続し、前記第 2 の信号線は前記バッファの前記出力端子と接続することを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の撮像装置。

【請求項 8】

前記制御信号生成部は、前記信号線の一端と接続し、

前記信号線制御部は、前記信号線の他端と接続することを特徴とする請求項 1 乃至 6 のいずれか 1 項に記載の撮像装置。 20

【請求項 9】

前記制御信号生成部と前記信号線制御部との間に、前記複数の比較器のうち少なくとも 1 つの比較器が配置されていることを特徴とする請求項 1 乃至 8 のいずれか 1 項に記載の撮像装置。

【請求項 10】

前記撮像装置は、前記信号線制御部の他に、前記信号線を固定電位に接続するための第 2 の信号線制御部を有することを特徴とする請求項 1 乃至 9 のいずれか 1 項に記載の撮像装置。 30

【請求項 11】

前記信号線制御部と前記第 2 の信号線制御部との間に、前記複数の比較器のうち少なくとも 1 つの比較器が配置されていることを特徴とする請求項 10 に記載の撮像装置。

【請求項 12】

前記複数の比較器のそれぞれは、差動增幅回路と、前記差動增幅回路から信号を出力するための出力回路とを有し、

前記複数の比較器のそれぞれの前記出力回路は、第 2 の出力端子と、前記第 2 の出力端子と接続する第 2 のスイッチを有し、

前記複数の比較器の前記第 2 のスイッチを制御する第 2 の制御信号を前記制御信号生成部から供給され、前記複数の比較器の前記第 2 のスイッチに対して共通に設けられ、前記複数の比較器の前記第 2 のスイッチに前記第 2 の制御信号を供給する第 2 の信号線と、前記第 2 の信号線を固定電位に接続するための第 3 の信号線制御部と、を有することを特徴とする請求項 1 乃至 11 のいずれか 1 項に記載の撮像装置。 40

【請求項 13】

前記複数の比較器のそれぞれには、前記画素列からの信号と、参照信号とが入力され、前記画素列からの信号と前記参照信号との電位を比較することを特徴とする請求項 1 乃至 12 のいずれか 1 項に記載の撮像装置。

【請求項 14】

更に、それぞれが前記複数の比較器からの信号に基づきカウント値を保持する複数の記憶部を有し、

前記複数の比較器と前記複数の記憶部が A D 変換器を構成することを特徴とする請求項 1 乃至 1 3 のいずれか 1 項に記載の撮像装置。

【請求項 1 5】

前記 A D 変換器は、ランプ型 A D 変換器であることを特徴とする請求項 1 4 に記載の撮像装置。

【請求項 1 6】

請求項 1 乃至 1 5 のいずれか 1 項に記載の撮像装置と、

前記撮像装置からの信号を処理する処理部と、を有する撮像システム。

【発明の詳細な説明】

【技術分野】

10

【0 0 0 1】

本発明は、撮像装置、及びそれを用いた撮像システムに関する。

【背景技術】

【0 0 0 2】

画素の列に対応して設けられた A D 変換器を有する撮像装置が知られている。 A D 変換器は、画素信号と参照信号とを比較する比較器を備えている。特許文献 1 には、校正用のフィードバックスイッチを有する比較器ごとのオフセットを低減するため、フィードバックスイッチを制御する制御信号の振幅を制限する技術が開示されている。

【先行技術文献】

【特許文献】

20

【0 0 0 3】

【特許文献 1】特開 2 0 1 0 - 0 1 6 6 5 6 号公報

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 4】

特許文献 1 において、フィードバックスイッチを制御する制御信号の信号線は、他の列の比較器のフィードバックスイッチにも接続されている。このような構成では、比較器の出力が反転した際に、他の列の比較器の出力へ影響を与える場合がある。つまり、クロストークが生じてしまう。このクロストークが生じると、他の列の比較器の結果に誤差を生じさせてしまう可能性がある。比較器の結果の誤差は、A D 変換結果の誤差であり、画質を低下させてしまう。このようなクロストークは、フィードバックスイッチ用の配線のみならず、比較器の動作を制御するための信号線を、複数の比較器で共通に設けた場合において生じ得る。

30

【0 0 0 5】

本発明は、上記課題を鑑みてなされたもので、信号の比較時に生じる誤差を低減することを目的とする。

【課題を解決するための手段】

【0 0 0 6】

本発明の撮像装置は、行列状に配置された複数の画素と、それぞれが前記複数の画素の少なくとも 1 つの画素列に対応して設けられ、それぞれが動作を制御するためのスイッチを含む複数の比較器と、前記複数の比較器の前記スイッチに対して共通に設けられ、前記複数の比較器の前記スイッチを制御する制御信号を供給するための信号線と、前記信号線に前記制御信号を供給する制御信号生成部と、を有する撮像装置において、前記撮像装置は、前記信号線の電位を固定電位に制御するための信号線制御部をさらに有し、前記制御信号生成部と、前記信号線制御部との間に、前記複数の比較器が配置されていることを特徴とする撮像装置である。

40

【発明の効果】

【0 0 0 7】

本発明の撮像装置によって、信号の比較時に生じる誤差を低減することが可能となる。

【図面の簡単な説明】

50

## 【0008】

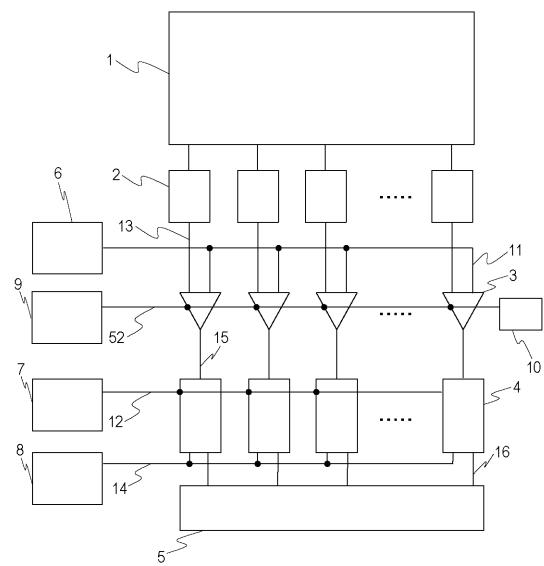

【図1】第1の実施形態の撮像装置を説明するためのブロック図である。

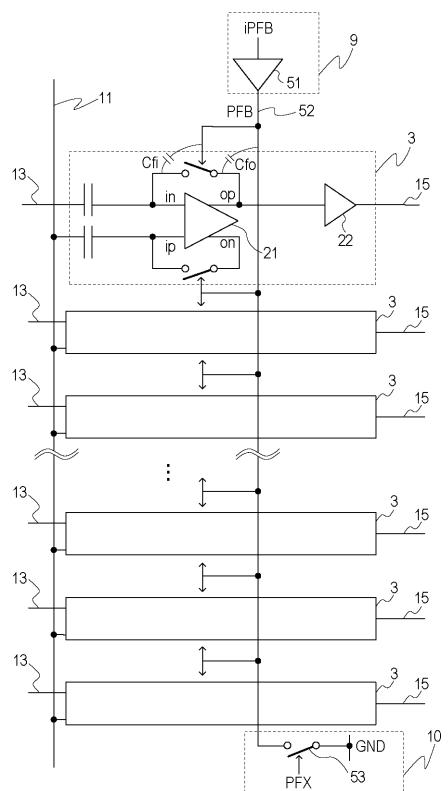

【図2】第1の実施形態の比較器を説明するための回路図である。

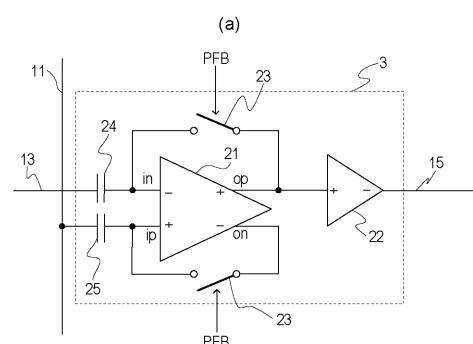

【図3】第1の実施形態の比較器を説明するための回路図である。

【図4】第1の実施形態の画素、及び読み出し部を説明するための回路図である。

【図5】第1の実施形態の撮像装置の駆動方法を説明するためのタイミング図である。

【図6】第1の実施形態の撮像装置の駆動方法を説明するためのタイミング図である。

【図7】第1の実施形態の比較例の比較器を説明するための回路図である。

【図8】第1の実施形態の比較例を説明するためのタイミング図である。

【図9】第1の実施形態の比較例を説明するためのタイミング図である。

10

【図10】第2の実施形態の比較器を説明するための回路図である。

【図11】第3の実施形態の比較器を説明するための回路図である。

【図12】第4の実施形態の比較器を説明するための回路図である。

【図13】第5の実施形態の撮像システムを説明するためのブロック図である。

## 【発明を実施するための形態】

## 【0009】

## (第1の実施形態)

本実施形態について、図1～図9を用いて説明する。図1～図9において、同一の構成に対しては同一の符号を付している。以降の説明において、スイッチは、ハイレベル（以下、Hレベル）の時にオンし、ローレベル（以下、Lレベル）の時にオフする。スイッチは、例えば、MOSトランジスタや、CMOSスイッチ等である。端子や一端や他端とは、電極に限らず、ノードを意味する場合を含む。また、以降の説明において、符号VDDは任意の電源電圧であり、符号GNDはグランド電位を示す。

20

## 【0010】

図1は、第1の実施形態の撮像装置を説明するためのブロック図である。撮像装置は、画素部1と、複数の読み出し部2と、複数の比較器3と、複数の記憶部4と、水平走査部5と、ランプ源6と、カウンタ7と、信号処理部8と、制御信号生成部9とを有する。そして、撮像装置は、制御信号生成部9が信号を出力する信号線52に接続する信号線制御部10を有する。この信号線制御部については、後に詳述する。また、撮像装置は、垂直走査部等の機能ブロック（不図示）を更に有している。

30

## 【0011】

画素部1には、複数の画素が行列状に配置されている。読み出し部2は、画素部1の画素列に対応して配置され、画素部1からの画素信号を信号線13へ出力する。ランプ源6は、ランプ信号用の信号線11を介して、ランプ信号を複数の比較器3に供給する。ランプ信号は参照信号とも称する。ランプ信号は、一般には、時間に応じて単調に増加あるいは減少する信号であるが、例えば、階段状に変化する信号であってもよい。カウンタ7は、カウントデータ用の信号線12を介して、カウント値を複数の記憶部4に供給する。

## 【0012】

比較器3は、画素部1の画素列に対応して配置される。比較器3は、画素信号とランプ信号とを比較し、比較結果に応じたHレベル、又はLレベルの信号を信号線15へ出力する。比較器3が出力する信号は、画素信号の電位とランプ信号の電位の大小関係が変わる際に、HレベルからLレベル、又はLレベルからHレベルへと遷移（反転）する。記憶部4は、比較器3が出力した信号が反転するタイミングで、カウント値をデジタルデータとして記憶する。この動作によって、画素信号がデジタルデータに変換（A/D変換）される。ここで、比較器3には、制御信号生成部9から、信号線52を介して、比較器3の動作を制御するための制御信号が供給されている。A/D変換部は、少なくとも比較器3と、記憶部4を含む。本実施形態のA/D変換器は、いわゆるランプ型A/D変換器である。

40

## 【0013】

水平走査部5は、記憶部4の信号の出力を制御する制御信号を信号線16へ出力する。

記憶部4に記憶されたデジタルデータは、水平走査部5の制御信号によって、信号線14

50

に出力され、信号処理部8へ順次転送される。信号処理部8では、デジタルデータを用いて相関二重サンプリング(以下、CDS)などの信号処理を行った後、撮像装置の外部へ信号を出力する。

#### 【0014】

本実施形態では、1つの画素列に対して、1つの読み出し部2と、1つの比較器3が設けられているが、複数の画素列に対して1つの読み出し部2や1つの比較器3が設けられてもよい。また、撮像装置は、読み出し部2を有していない構成であってもよい。

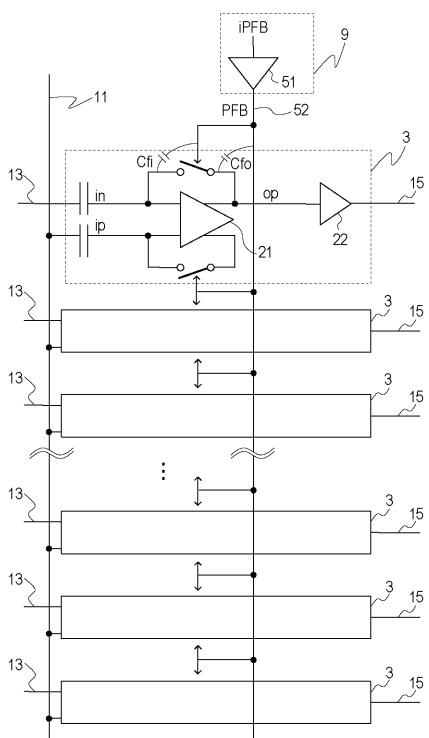

#### 【0015】

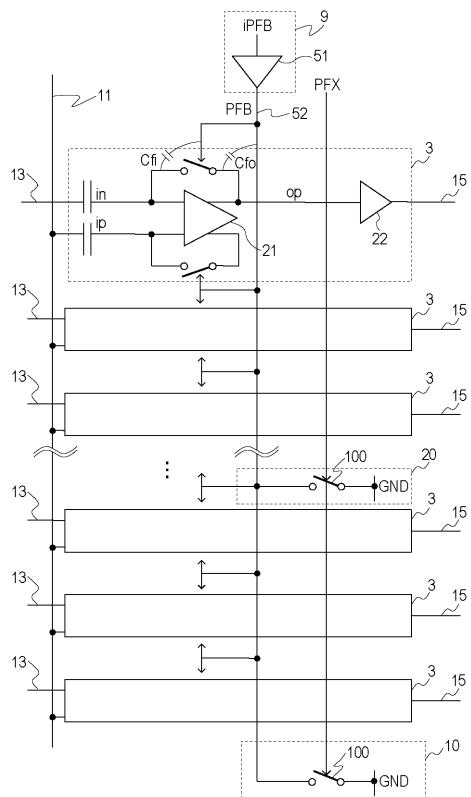

図2は、複数の比較器3の構成を示した回路図である。図2では1つの比較器3の回路構成を示しているが、他の比較器3も同一の構成を有しているものとする。図2は、図1のブロック図を左に90度回転させた図となっている。複数の比較器3のそれぞれは、差動增幅回路21と、出力回路22と、入力用の2つの容量を有する。差動增幅回路21は、帰還(フィードバック、以下FB)経路の形成を制御するFBスイッチを有する。各比較器3のFBスイッチには、共通の信号線52から、制御信号PFBが供給されている。制御信号生成部9は、バッファ51を含む。元となる信号IPFBが入力されたバッファ51は、信号線52に制御信号PFBを出力する。

10

#### 【0016】

ここで、図1にも示したように、撮像装置は、信号線52に接続する信号線制御部10を有する。信号線制御部10は、信号線52の電位を固定電位に制御するための回路を含み、信号線52の電位を固定電位にする、あるいは近づけるように動作する。本実施形態では、信号線制御部10は、固定電位としてグランド電位を供給する電源GNDと、スイッチ53を含む。スイッチ53は制御信号PFXによって、そのオンオフが制御されている。制御信号PFXによってスイッチ53がオフの場合には、信号線制御部10は動作せず、制御信号PFXによってスイッチ53がオンの場合には、信号線制御部10は動作する。このような構成によって、信号線52の電位は、制御信号生成部9と信号線制御部10によって、一定の電位になるように制御される。よって、ある比較器3の出力が反転した場合に、反転による変動が信号線52を介して別の比較器3へ伝搬することを低減することが可能となる。

20

#### 【0017】

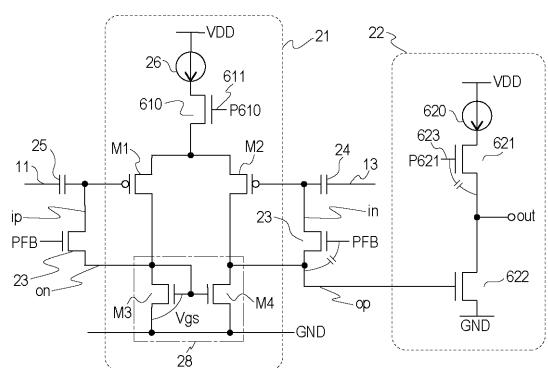

以下、本実施形態についてより詳細に説明する。図3(a)及び図3(b)は、図2に示す比較器3を詳細に示した回路図である。図3(b)は、図3(a)の差動增幅回路21をより詳細に記載した回路図である。

30

#### 【0018】

図3(a)に示すように、比較器3は、差動增幅回路21と、出力回路22と、入力用の2つの容量24、25を有する。差動增幅回路21は、非反転入力端子ipと、反転入力端子inと、非反転出力端子opと、反転出力端子onと、2つのFBスイッチ23とを有する。1つのFBスイッチ23は、一端が反転入力端子inと接続し、他端が非反転出力端子opと接続し、反転入力端子inと非反転出力端子opとの接続を制御する。もう1つのFBスイッチ23は、一端が非反転入力端子ipと接続し、他端が反転出力端子onと接続し、非反転入力端子ipと反転出力端子onとの接続を制御する。なお、差動增幅回路21の出力は、非反転出力端子opであり、この端子opが出力回路22の入力端子に接続される。反転入力端子inには容量24が接続され、非反転入力端子ipには容量25が接続される。反転入力端子inは、容量24を介して信号線13が接続され、非反転入力端子ipは、容量25を介して信号線11に接続される。信号線11は、ランプ信号が供給されている。出力回路22は、ソース接地増幅回路である。出力回路22の出力端子が信号線15に接続しており、出力回路22が出力する信号は比較器3が出力する信号となる。

40

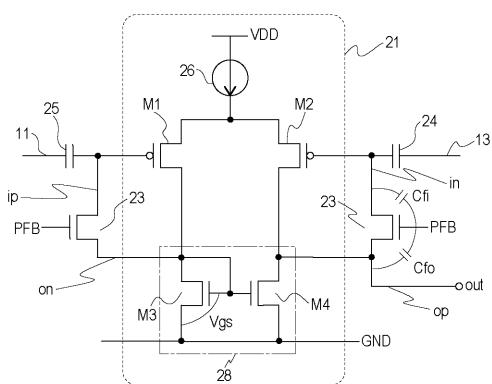

#### 【0019】

図3(b)は差動增幅回路21の詳細を示した回路図である。差動增幅回路21は、差動入力トランジスタ対と、電流源26と、カレントミラー回路28とを含む。差動入力ト

50

ランジスタ対は、P型のMOSトランジスタであるトランジスタM1、M2である。電流源26は、例えば定電流源であり、トランジスタM1、M2のソースに接続される。カレントミラー回路28は、ドレインとゲートがダイオード接続されたトランジスタM3と、ゲートがM3のゲートと接続されたトランジスタM4と、例えばグランド電位の電源GNDからなる。

#### 【0020】

2つのFBスイッチ23は、N型MOSトランジスタからなる。1つのFBスイッチ23がトランジスタM1のゲートとドレインの間を接続し、もう1つのFBスイッチ23がトランジスタM2のゲートとドレインとの間を接続する。トランジスタM1のゲートが非反転入力端子ipであり、容量25を介して信号線11に接続される。トランジスタM1のドレインが反転出力端子onであり、ダイオード接続されたトランジスタM3のドレインと接続される。また、トランジスタM2のゲートが反転入力端子inであり、容量24を介して、信号線13が接続される。またM2のドレインが非反転出力端子opであり、ダイオード接続されたトランジスタM4のドレインと接続される。ここで、図2と図3(b)に示す容量Cfiは、信号線52と反転入力端子inとの間に生じる寄生容量である。図2と図3(b)に示す容量Cfoは、信号線52と非反転出力端子opとの間に生じる寄生容量である。

10

#### 【0021】

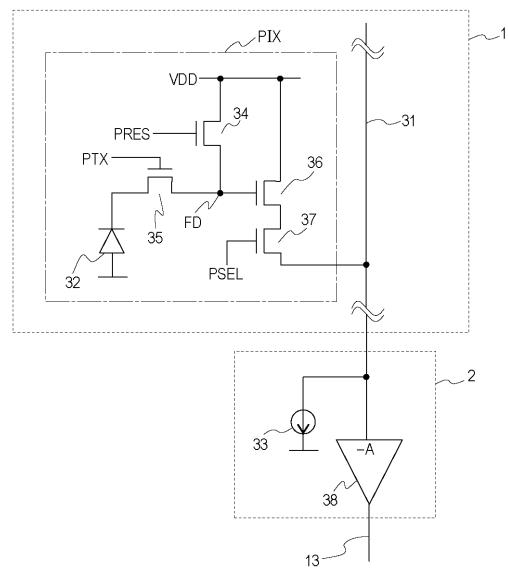

図4は、画素部1の1つの画素PIXと、1つの読み出し部2の回路を示した図である。画素PIXは、典型的なCMOSイメージセンサの回路であり、光電変換素子32と、リセットトランジスタ34と、転送トランジスタ35と、増幅トランジスタ36と、選択トランジスタ37と、を有する。リセットトランジスタ34と、転送トランジスタ35と、増幅トランジスタ36は、フローティングディフュージョン(以下、FD)のノードに接続されている。リセットトランジスタ34と、転送トランジスタ35と、選択トランジスタ37は、それぞれ制御信号PRE S、PTX、PSELによって制御される。画素信号を読み出す時には、制御信号PSELがHレベルとなり、選択トランジスタ37がオンとなる。この時、増幅トランジスタ36と読み出し回路部2に含まれる電流源33とでソースフォロワ回路が形成される。読み出し部2は、画素信号が出力される信号線31に接続され、電流源33と、-A倍のゲインを持つアンプ38とで構成される。

20

#### 【0022】

30

画素PIXから画素信号を読み出す際の動作は次のようになる。制御信号PRE SがHレベルとなりリセットトランジスタ34がオンし、リセットトランジスタ34がFDをリセットする。そして、制御信号PRE SがLレベルになりリセットトランジスタ34がオフする。ここで、選択トランジスタ37をオンの状態にしておくことで、リセットされたFDの電位に基づく信号(リセット信号)が信号線31に出力される。その後、制御信号PTXがHレベルになり、光電変換素子32に蓄えられた電荷がFDに転送される。この時、光電変換素子32において生じた電荷によってFDの電位が変化する。この変化したFDの電位に基づく信号(画像信号)が、信号線31に出力される。アンプ38では、リセット信号と画像信号をそれぞれ-A倍し、出力する。画素から出力されるリセット信号と画像信号を画素信号と称する。

40

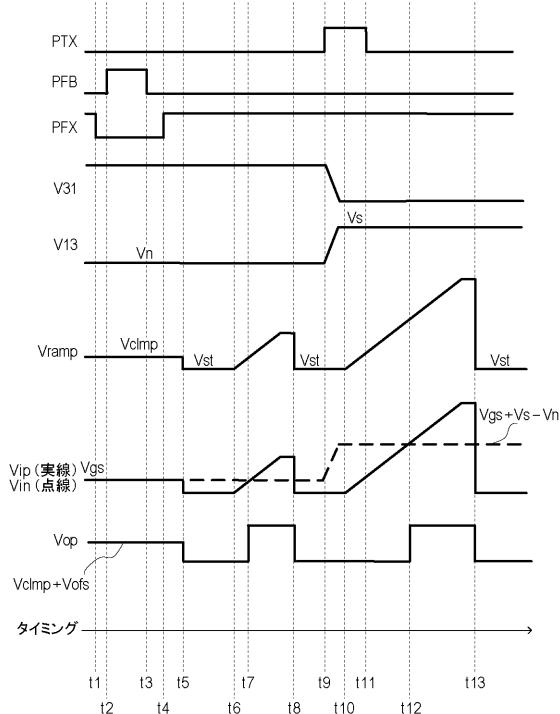

#### 【0023】

このような回路構成の本実施形態の撮像装置の動作について、図5を用いて説明する。図5は、画素PIXから比較器3までの動作を説明するためのタイミング図である。図5には、制御信号PTXと、制御信号PFBと、制御信号PFXと、信号線31の電位V31と、信号線13の電位V13と、ランプ信号の電位Vram pが示されている。更に、図5には、差動增幅回路21の非反転入力端子ipの電位Vip(実線)と、差動增幅回路21の反転入力端子inの電位Vin(点線)と、差動增幅回路21の非反転出力端子opの電位Vopが示されている。また、画素PIXの他の制御信号PSELや制御信号PRE S、及び比較器3の出力については説明を簡易にするため省略する。

#### 【0024】

50

時刻  $t_1$ において、画素  $P_{IX}$ からリセット信号が出力されており、電位  $V_{13}$ は、リセット信号を示す電位  $V_n$ となる。この時、制御信号  $P_{FX}$ がLレベルに遷移する。ランプ信号の電位  $V_{ramp}$ は、オフセットキャンセル用の電位  $V_{clmp}$ である。また、電位  $V_{op}$ は、電位  $V_{clmp} +$  電位  $V_{ofs}$ である。電位  $V_{ofs}$ とは、差動增幅回路21のオフセット電位である。

#### 【0025】

時刻  $t_2$ において、制御信号  $P_{FB}$ がHレベルに遷移する。つまり、 $FB$ スイッチ23がオンとなり、トランジスタM1のゲートの電位は、トランジスタM3のゲート電位である電位  $V_{gs}$ となる。トランジスタM3のゲートの電位は、ソースがグランド電位であるため、ゲートとソース間の電圧  $V_{gs}$ と等しい(図3(b)参照)。この時、トランジスタM4のドレインとソース間に流れる電流と、トランジスタM3のドレインとソース間に流れる電流は等しい。よって、トランジスタM4のドレインと、それと同一ノードのトランジスタM2のゲートの電位も電位  $V_{gs}$ となる。つまり、電位  $V_{in}$ と電位  $V_{op}$ が電位  $V_{gs}$ を示す。ここで、容量24の両端の電位差と容量25の両端の電位差は、電位  $V_{clmp} -$  電位  $V_{gs}$ である。

#### 【0026】

時刻  $t_3$ において、制御信号  $P_{FB}$ はLレベルに遷移する。つまり、 $FB$ スイッチ23がオフとなり、容量24と容量25のそれぞれに、電位  $V_{clmp} -$  電位  $V_{gs}$ の差が保持される。この動作により、比較器3を構成する差動增幅回路21において、オフセットキャンセルを行うことができる。

#### 【0027】

時刻  $t_4$ において、制御信号  $P_{FX}$ がHレベルに遷移し、時刻  $t_5$ において、ランプ信号の電位  $V_{ramp}$ が電位  $V_{st}$ に下がる。時刻  $t_6$ において、電位  $V_{ramp}$ が上昇し始め、AD変換が開始される。電位  $V_{ip}$ は、ランプ信号の変化に伴って、時刻  $t_5$ において電位が下がり、時刻  $t_6$ において電位が上昇する。一方、電位  $V_{op}$ は、時刻  $t_5$ から電位  $V_{gs}$ のままである。そして、時刻  $t_7$ において、電位  $V_{ip}$ が電位  $V_{gs}$ を超えると、電位  $V_{op}$ がLレベルからHレベルへ遷移する。つまり、比較器3の出力は、HレベルからLレベルになる。記憶部4は、この時のカウント値をリセット信号のデジタルデータとして記憶する。時刻  $t_8$ において、ランプ信号の電位  $V_{ramp}$ が再度、電位  $V_{st}$ に下がる。ここまででノイズ信号のAD変換が完了する。

#### 【0028】

次に、時刻  $t_9$ において、制御信号  $P_{TX}$ がLレベルからHレベルに遷移すると、画素  $P_{IX}$ から画像信号が出力される期間になる。電位  $V_{13}$ は、画像信号を示す電位  $V_s$ となる。この時、電位  $V_{in}$ は電位  $V_{gs} +$  電位  $V_s -$  電位  $V_n$ となる。時刻  $t_{10}$ において、電位  $V_{ramp}$ が上昇し始め、画像信号のAD変換が始まる。ここで、制御信号  $P_{TX}$ は、例えば、時刻  $t_{11}$ において、Lレベルに戻る。時刻  $t_{12}$ において、電位  $V_{ip}$ が電位  $V_{gs} +$  電位  $V_s -$  電位  $V_n$ を超えると、電位  $V_{op}$ はLレベルからHレベルと遷移する。つまり、比較器3の出力は、HレベルからLレベルになる。記憶部4は、この時のカウント値を画像信号のデジタルデータとして記憶する。その後、時刻  $t_{13}$ において、ランプ信号の電位の電位  $V_{ramp}$ が再度、電位  $V_{st}$ に下がる。ここまでで画像信号のAD変換が完了する。その後、信号処理部8では、記憶部4に記憶されたリセット信号及び画像信号のデジタルデータの減算を行い出力し、1画素のAD変換が終了する。

#### 【0029】

本実施形態においては、制御信号  $P_{FB}$ がLレベルからHレベルに遷移する前に、制御信号  $P_{FX}$ がHレベルからLレベルに遷移し、制御信号  $P_{FB}$ がHレベルからLレベルに遷移した後に制御信号  $P_{FX}$ がLレベルからHレベルに遷移する。つまり、制御信号  $P_{FB}$ がHレベルであるオフセットキャンセル期間には、信号線制御部10が動作しない。また、リセット信号と画素信号のAD変換期間(時刻  $t_6$  ~ 時刻  $t_8$ と時刻  $t_{10}$  ~ 時刻  $t_{13}$ )は、信号線制御部10が動作し、信号線52の電位が固定電位になるように制御している。この動作によって、他の比較器3へのクロストークを低減することができ、AD

10

20

30

40

50

変換の誤差を低減することが可能となる。

#### 【0030】

図6～図9を用いて、このクロストークの現象について説明する。まず、本実施形態の比較例について図7～図9を用いて説明する。

#### 【0031】

図7は、本実施形態の比較例の撮像装置の複数の比較器3を示す回路図である。図7は、図2と対応しており、図2で説明した個所については詳細な説明は省略する。図7が図2と異なる点は、撮像装置に信号線制御部10が設けられていない点である。

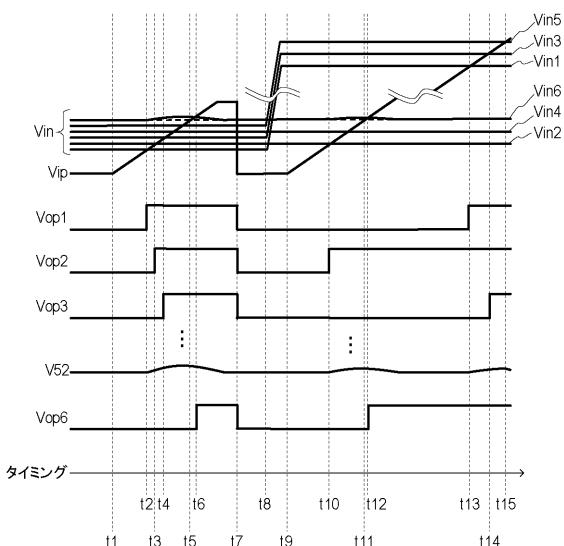

#### 【0032】

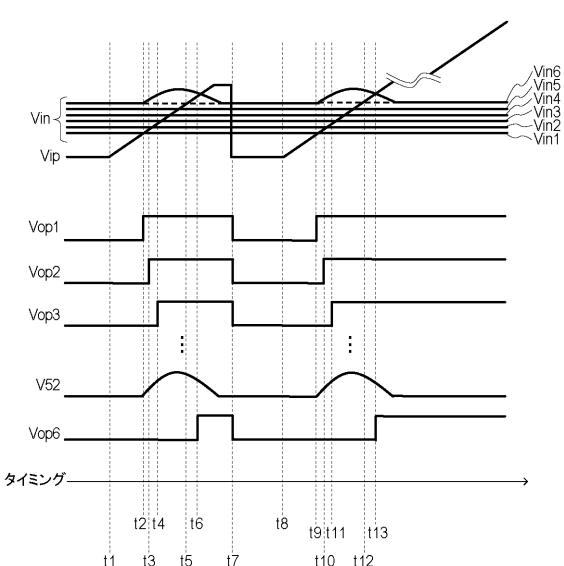

図8は、画素部1に光が入射されていない時、すなわち暗時のリセット信号と画像信号のA/D変換期間を示したタイミング図である。図8は、比較器3の差動增幅回路21の各端子の電位と、信号線52の電位V52を示している。差動增幅回路21の各端子の電位として、非反転入力端子ipの電位Vipと、反転入力端子inの電位Vinと、非反転出力端子opの電位Vopを示す。図8では、第1～第6の画素列に対応して設けられた複数の比較器3の各電位を示している。複数の比較器3を第1～第6の比較器3とする。第1～第6の比較器3の電位Vinを、電位Vin1～電位Vin6と示す。一方、第1～第6の比較器3の電位Vipは、説明を簡単にするためにはらつきがないものとし、1つの電位Vipとして示す。第1～第6の比較器3の電位Vopを、電位Vop1～電位Vop6として示す。なお、図8において電位Vop4と電位Vop5は省略されている。

10

20

#### 【0033】

時刻t1において、リセット信号のA/D変換が始まる。このA/D変換の開始時のカウント値は0である。時刻t2において、第1の画素列の電位Vin1と電位Vipの大小関係が変わり、電位Vop1がLレベルからHレベルへ遷移する。この電位Vop1のプラス(以下、+)方向への遷移は、図7に示した非反転出力端子opと信号線52との間の寄生容量Cfoを介して、信号線52の電位V52を+方向に変動させる。しかし、制御信号生成部9によって、信号線52がLレベルに制御されているため、信号線52はある時間を経ると元の電位となる。結果として、信号線52の電位V52は上凸状の波形となる。この時、信号線52の変動は、FBスイッチ23の周りにおける寄生容量Cfo、Cfiが主な要因であると考えられる。しかし、信号線52の変動は、出力端子opに接続する配線等と信号線52との間の寄生容量や入力端子inに接続する配線等と信号線52との間の寄生容量でも生じる可能性がある。

30

#### 【0034】

時刻t3において、第2の画素列の電位Vin2と電位Vipの大小関係が変わり、時刻t4において、第3の画素列の電位Vin3と電位Vipの大小関係が変わる。よって、対応する電位Vop2と電位Vop3は、それぞれの時刻において、LレベルからHレベルに遷移する。この電位Vop2と電位Vop3の+方向への遷移も、電位V52を+方向に変動させる。時刻t3に生じる電位V52の変動は電位Vop1の変動に重畠し、時刻t4に生じる変動は時刻t3に生じる電位V52の変動に重畠する。電位Vin4及び電位Vin5に対応する電位Vop4及び電位Vop5も同様に、電位V52を変動させる。つまり、電位V52が変動した後、元の電位に戻る前に、他の画素列の電位VopがLレベルからHレベルに遷移すると、電位V52の変動は大きくなってしまう。また、同時刻に電位VopがLレベルからHレベルに遷移する画素列が多いほど、電位V52の変動は大きくなってしまう。

40

#### 【0035】

ここで、電位V52の変動は、図7に示した信号線52と反転入力端子inとの間の寄生容量Cfiを介して、反転入力端子inの電位Vinを変動させる。この変動を、図8の時刻t2～時刻t7の間の電位Vin6に示している。なお、比較のために電位Vin6においてクロストークの影響がない状態を点線で示す。電位Vin6は、電位Vin0～電位Vin5の電位よりも大きいため、電位Vin6と電位Vipの電位の大小関係が

50

変わる前に、電位  $V_{op1}$  ~ 電位  $V_{op5}$  が遷移してしまう。この電位  $V_{op1}$  ~ 電位  $V_{op5}$  の遷移による変動が、電位  $V_{in6}$  の値に影響を与えててしまう。

#### 【0036】

時刻  $t_6$ において、電位  $V_{in6}$ と電位  $i_p$ との大小関係が変わり、電位  $V_{op6}$ はLレベルからHレベルへ遷移する。この時刻  $t_6$ のカウント値が記憶部4に保持される。しかし、クロストークの影響がなければ、時刻  $t_5$ において電位  $V_{op6}$ の遷移が生じたはずである。つまり、信号線5\_2の変動によって、時刻  $t_5$  - 時刻  $t_6$ 分のカウントだけデジタルデータに誤差が生じてしまう。

#### 【0037】

時刻  $t_7$ において、電位  $V_{ip}$ がA/D変換の開始前の電位に戻り、カウンタもリセットされカウント値が0になる。そして、時刻  $t_8$ から、画像信号のA/D変換が始まる。なお、暗時の画像信号であるため、電位  $V_{in1}$  ~ 電位  $V_{in6}$ は、リセット信号の電位  $V_{in1}$  ~ 電位  $V_{in6}$ とほぼ同じ値である。よって、時刻  $t_9$  ~ 時刻  $t_{11}$ は、時刻  $t_2$  ~ 時刻  $t_4$ と同様の動作が行われる。つまり、順次、電位  $V_{in1}$  ~ 電位  $V_{in3}$ と電位  $i_p$ との大小関係の変化が生じ、電位  $V_{op1}$  ~ 電位  $V_{op3}$ のLレベルからHレベルへの遷移が生じる。電位  $V_{in4}$ 及び電位  $V_{in5}$ に対応する電位  $V_{op4}$ 及び電位  $V_{op5}$ も同様に遷移する。よって、電位  $V_{5_2}$ に変動の影響が生じ、電位  $V_{in6}$ に変動が生じる。この変動によって、電位  $V_{op6}$ がLレベルからHレベルに遷移する時刻は、時刻  $t_{12}$ ではなく時刻  $t_{13}$ となる。

#### 【0038】

ここで、暗時の撮影で、電位  $V_{in1}$  ~ 電位  $V_{in6}$ のリセット信号の値と撮像信号の値で大きな違いがなければ、電位  $V_{in6}$ のリセット信号と撮像信号に生じる変動がほぼ等しくなる可能性がある。この場合には、画像信号のデジタルデータからリセット信号のデジタルデータを減算するCDS処理を行えば、誤差を無くす、あるいは低減することができる。しかし、撮像装置を用いる場合には、多くの場合において、リセット信号の値と撮像信号の値が異なるため、誤差を低減することは困難である。また、暗時であっても、欠陥画素等が存在すると、誤差が生じる可能性がある。

#### 【0039】

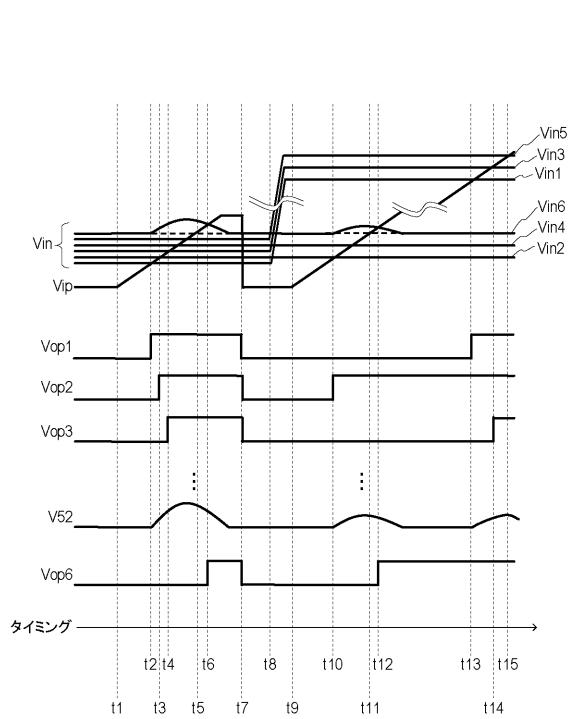

更に、図9を用いて、画素部1に光が入射されている場合について説明する。図9は、画素部1に光が入射されている場合のリセット信号と画像信号のA/D変換期間を示したタイミング図である。図9は図8と対応しており、同一の符号を付したものとの説明は省略する。時刻  $t_1$  ~ 時刻  $t_7$ は、図8の時刻  $t_1$  ~ 時刻  $t_7$ と同じ動作が行われているため説明を省略する。

#### 【0040】

時刻  $t_8$ において、画素PIXから画像信号が出力され、電位  $V_{in1}$  ~ 電位  $V_{in6}$ の電位が変化する。ここでは、第1 ~ 第6の画素列のうち、第1、3、5の画素列に光が入射されたものとする。

#### 【0041】

時刻  $t_9$ において、画像信号のA/D変換が開示される。時刻  $t_{10}$ にて、電位  $V_{in2}$ と電位  $V_{ip}$ の大小関係が変わり、電位  $V_{op2}$ がLレベルからHレベルへ遷移する。この時、電位  $V_{5_2}$ が電位  $V_{op2}$ の遷移に伴って変動する。その後、電位  $V_{in4}$ と電位  $V_{ip}$ の大小関係が変わり、電位  $V_{op4}$ がLレベルからHレベルへ遷移する(不図示)。この時、電位  $V_{5_2}$ には、電位  $V_{op2}$ の遷移に伴う変動に加え、電位  $V_{op4}$ の遷移に伴う変動が生じる。この時、信号線5\_2を介して、電位  $V_{in6}$ の電位が変動してしまう。

#### 【0042】

そして、時刻  $t_{12}$ において、電位  $V_{in6}$ と電位  $V_{ip}$ の大小関係が変わり、電位  $V_{op6}$ がLレベルからHレベルへ遷移する。図8と同様に、変動がなければ、電位  $V_{in6}$ と電位  $V_{ip}$ の大小関係の変化は時刻  $t_{11}$ にて生じたはずである。

#### 【0043】

10

20

30

40

50

その後、時刻  $t_{13}$ において、電位  $V_{in1}$ と電位  $V_{ip}$ の大小関係が変わり、電位  $V_{op1}$ がLレベルからHレベルへ遷移する。時刻  $t_{14}$ において、電位  $V_{in3}$ と電位  $V_{ip}$ の大小関係が変わり、電位  $V_{op3}$ がLレベルからHレベルへ遷移する。時刻  $t_{15}$ において、電位  $V_{in5}$ と電位  $V_{ip}$ の大小関係が変わり、電位  $V_{op5}$ がLレベルからHレベルへ遷移する(不図示)。時刻  $t_{13}$ ～時刻  $t_{15}$ においても、電位  $V_{52}$ が電位  $V_{op1}$ や電位  $V_{op3}$ の遷移に伴って変動するため、電位  $V_{in5}$ が変動し、電位  $V_{in5}$ と電位  $V_{ip}$ の大小関係が変わる時刻が変化してしまう可能性がある。

#### 【0044】

図9の動作においては、リセット信号のAD変換の期間において、電位  $V_{in6}$ は、電位  $V_{op1}$ ～電位  $V_{op5}$ が遷移する影響を受ける。一方、画像信号のAD変換の期間においては、電位  $V_{in6}$ は、電位  $V_{op2}$ と電位  $V_{op4}$ が遷移する影響を受ける。つまり、電位  $V_{in6}$ が受ける変動の影響が、リセット信号のAD変換期間中と、画像信号のAD変換期間中とで異なる。よって、例えCDS処理を行ったとしても、誤差を無くすことができない。

#### 【0045】

図8及び図9に示すように、比較器の出力が反転した際に、他の列の比較器の出力へと影響が生じてしまう場合がある。つまり、クロストークが生じてしまう。クロストークが生じると、他の列のAD変換の結果に誤差を生じさせてしまう。次に、図6を用いて、図1～図5にて示した本実施形態の撮像装置によるクロストークの低減について説明する。

#### 【0046】

図6は、画素部1に光が入射されている場合のリセット信号と画像信号のAD変換期間を示したタイミング図である。図6は、図9と対応しており、同一の構成については説明を省略する。

#### 【0047】

図6の時刻  $t_1$ ～時刻  $t_7$ は、ノイズ信号のAD変換期間であり、図9の時刻  $t_1$ ～時刻  $t_7$ と同様の動作が行われている。しかし、時刻  $t_2$ から生じる電位  $V_{52}$ の変動の量が、図9における電位  $V_{52}$ の変動の量より小さい。そして、電位  $V_{52}$ の変動に伴い生じる電位  $V_{in6}$ の変動の量も、図9における電位  $V_{in6}$ の変動の量より小さい。図1等に示すように、信号線制御部10によって、信号線52の電位  $V_{52}$ が制御されているためである。よって、誤差である時刻  $t_5$ ～時刻  $t_6$ 分のカウントが、図9の時刻  $t_5$ ～時刻  $t_6$ 分のカウントよりも小さくなる。

#### 【0048】

図6の時刻  $t_8$ ～時刻  $t_{15}$ は、画像信号の出力と、画像信号のAD変換期間であり、図9の時刻  $t_7$ ～時刻  $t_{15}$ と同様の動作が行われている。ノイズ信号のAD変換期間と同様に、時刻  $t_{10}$ から生じる電位  $V_{52}$ の変動の量が、図9における電位  $V_{52}$ の変動の量より小さい。そして、電位  $V_{52}$ の変動に伴い生じる電位  $V_{in6}$ の変動の量も、図9における電位  $V_{in6}$ の変動の量より小さい。図1等に示すように、信号線制御部10によって、信号線52の電位  $V_{52}$ が制御されているためである。よって、誤差である時刻  $t_{11}$ ～時刻  $t_{12}$ 分のカウントが、図9の時刻  $t_{11}$ ～時刻  $t_{12}$ 分のカウントよりも小さくなる。

#### 【0049】

このように、クロストークを軽減することが可能となり、誤差が小さいノイズ信号と画像信号のデジタルデータを得ることができる。更に、CDS処理をすれば誤差を無くす、あるいはより低減することができる。

#### 【0050】

本実施形態では、第6の画素列の画素信号のAD変換時に誤差が生じる場合について説明したが、他の画素列でも生じ得る。しかし、信号線制御部10を設けることで、他の画素列でのAD変換時の誤差も低減可能である。

#### 【0051】

本実施形態では、図2に示すように信号線制御部10は、信号線制御部10と制御信号

10

20

30

40

50

生成部 9 の間に複数の比較器 3 が位置するように配置されている。つまり、信号線 5 2 の一端に制御信号生成部 9 が接続し、信号線 5 2 の他端に信号線制御部 1 0 が接続している。しかし、信号線制御部 1 0 は、複数の比較器 3 の間に位置するように配置されていてもよい。また、信号線制御部 1 0 の数は 1 つに限らない。

#### 【 0 0 5 2 】

また、信号線制御部 1 0 は、図 2 に示す制御信号生成部 9 と同様の構成であってもよい。つまり、信号線 5 2 を両端から制御する構成であってもよい。しかしながら、このような構成では、信号線 5 2 に貫通電流が流れる可能性があるため、本実施形態の構成の方が好ましい。

#### 【 0 0 5 3 】

また、各比較器 3 の 2 つの F B スイッチ 2 3 は、同一の制御信号 P F B で制御されている。しかし、例えば、2 つの F B スイッチ 2 3 はそれぞれ別の制御信号によって、別に制御されていてもよい。この場合には、制御信号のための信号線のそれぞれに信号線制御部 1 0 を設けることが望ましい。

#### 【 0 0 5 4 】

更に、本実施形態の信号線制御部 1 0 のスイッチ 5 3 は電源 G N D と接続しているが、電源 G N D ではなく電源電圧である電源 V D D や、任意の電圧を供給する配線と接続してもよい。

#### 【 0 0 5 5 】

なお、本実施形態では、動作を制御するためのスイッチとして、F B スイッチについて説明したが、他の比較器の動作を制御するスイッチであってもよい。この他の比較器の動作を制御するスイッチの例については、後述する。

#### 【 0 0 5 6 】

本実施形態では、ランプ型 A D 変換器が有する比較器について説明したが、逐次比較型等の A D 変換器でも、スイッチに対して共通に設けられた信号を有する構成であれば、信号線制御部 1 0 の構成は適用可能である。また、A D 変換器だけでなく、信号を比較する場合、例えば、比較結果によって増幅器のゲインを切り替え、ダイナミックレンジを拡大させる等の機能を有する撮像装置においても、本実施形態で説明した信号線制御部 1 0 を比較器に適用することが可能である。

#### 【 0 0 5 7 】

##### ( 第 2 の実施形態 )

本実施形態について、図 1 0 を用いて説明する。図 1 0 において、第 1 の実施形態と同一の構成に対しては同一の符号を付し、説明を省略する。本実施形態では、第 1 の実施形態では 1 つであった信号線制御部 1 0 に対して、信号線制御部 1 0 に加えて別の信号線制御部 2 0 が設けられている。つまり、本実施形態では、複数の信号線制御部 1 0 、 2 0 が設けられている。

#### 【 0 0 5 8 】

信号線制御部 2 0 は、第 1 の実施形態の信号線制御部 1 0 と同様に、電源 G N D と、スイッチ 1 0 0 を有している。信号線制御部 2 0 は、制御信号生成部 9 と信号線制御部 1 0 との間に配置されている。制御信号生成部 9 と信号線制御部 2 0 との間と、信号線制御部 1 0 と信号線制御部 2 0 との間には、複数の比較器 3 が配置されている。このような構成によって、第 1 の実施形態よりも信号線 5 2 の変動を低減することが可能となり、A D 変換時に生じる誤差を更に低減することが可能となる。

#### 【 0 0 5 9 】

本実施形態では、撮像装置が 2 つの信号線制御部を有する構成を示したが、更に多くの信号線制御部を有していてもよい。複数の信号線制御部を設ける場合には、その配置は等間隔であることが望ましいが、それに限らない。

#### 【 0 0 6 0 】

##### ( 第 3 の実施形態 )

本実施形態について、図 1 1 を用いて説明する。図 1 1 において、第 1 の実施形態と同

10

20

30

40

50

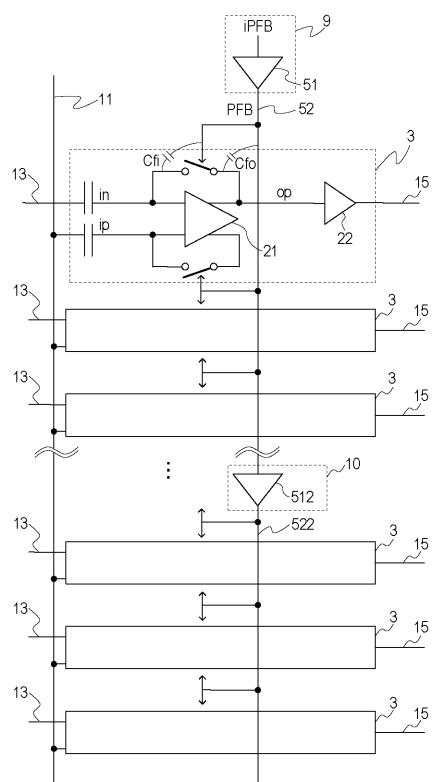

一の構成に対しては同一の符号を付し、説明を省略する。第1の実施形態の信号線制御部10は電源GNDとスイッチ53で構成されていたが、本実施形態では信号線制御部10はバッファ512で構成されている。

#### 【0061】

制御信号生成部9のバッファ51が制御信号PFBを信号線52に供給する。信号線52を介して信号線制御部10のバッファ512に制御信号PFBが入力され、バッファ512は制御信号PFBに基づく制御信号を信号線522へ出力する。つまり、1つのバッファが駆動する信号線の抵抗が小さくなるため、第1の実施形態に比べて、信号線52及び信号線522の変動を低減することが可能となる。よって、AD変換時に生じる誤差を更に低減することが可能となる。

10

#### 【0062】

なお、信号線522のバッファ512と接続する端部とは反対側の端部に、第1の実施形態の信号線制御部10を設けてもよい。これらの構成は、適宜、組み合わせができる。

#### 【0063】

##### (第4の実施形態)

本実施形態について、図12を用いて説明する。図12において、第1の実施形態と同一の構成に対しては同一の符号を付し、説明を省略する。第1の実施形態の比較器3の動作を制御するスイッチとして、FBスイッチ23の場合を説明したが、本実施形態では、電流源26のスイッチ610の場合を説明する。

20

#### 【0064】

図12は、第1の実施形態の図3(b)と対応する比較器3を詳細に示した回路図である。図12において、差動増幅回路21は、図3(b)の構成に加えて、電流源26と差動入力トランジスタ対との間の導通を制御するスイッチ610を有する。スイッチ610がオンする場合には、電流源26から電流が供給され差動増幅回路21が動作し、スイッチ610がオフする場合には、電流源26からの電流が供給されず差動増幅回路21が動作しない。よって、スイッチ610によって必要な時にだけ電流を流すことで、消費電力を低減することができる。このように、スイッチ610は比較器3の動作を制御する。

#### 【0065】

このスイッチ610の動作を制御する制御信号P610を供給する信号線611も、第1の実施形態の信号線52と同様に、複数の比較器3に共通に設けられる場合がある。このような場合においても、信号線611に信号線制御部を設けることで、他の比較器3へのクロストークを低減することが可能となる。よって、AD変換時の誤差を低減することが可能となる。

30

#### 【0066】

また、図12は、出力回路22の回路の一例を示している。出力回路22は、ソース接地増幅回路であり、電源VDDと、電流源620と、トランジスタ621と、トランジスタ622と、電源GNDとを有する。トランジスタ621とトランジスタ622は例えば、N型のMOSトランジスタである。トランジスタ622は、差動増幅回路21の出力端子opと接続するゲートと、出力端子outを有するドレインと、電源GNDと接続したソースとを有する。トランジスタ621は、電流源620と、トランジスタ622のドレインとの間の導通を制御するスイッチである。トランジスタ621はゲートに供給される制御信号P621によって動作が制御されている。ここで、制御信号P621を供給する信号線623は、他の比較器3の出力回路22と共に設けられる場合がある。このような場合においても、差動増幅回路21の出力端子opの電位の変動を他の比較器3に伝搬してしまう可能がある。よって、出力回路22の制御信号を供給する信号線623に対しても、信号線制御部を設けてもよい。

40

#### 【0067】

##### (第5の実施形態)

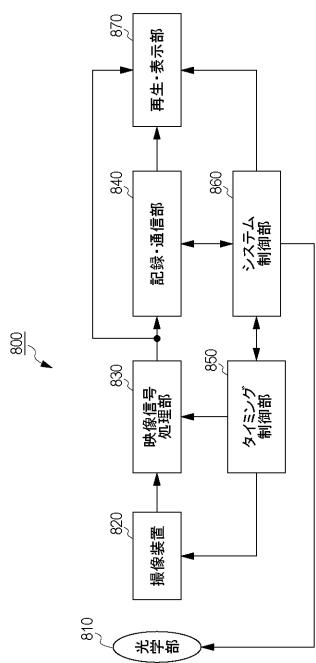

本実施形態について、図13を用いて説明する。図13は撮像システムの構成例を示す

50

ブロック図である。撮像システム 800 には、撮影を主目的とする装置（例えば、カメラ、カムコーダ）のみならず、撮影機能を補助的に備える装置（例えば、パーソナルコンピュータ、携帯端末）も含まれる。撮像システムは、上記の実施形態として例示された撮像装置と、該撮像装置から出力される信号を処理する処理部とを含む。該処理部は、例えば、撮像装置から出力されるデジタルデータを処理するプロセッサを含みうる。

#### 【0068】

図13において、撮像システム 800 は、例えば、光学部 810、撮像装置 820、映像信号処理部 830、記録・通信部 840、タイミング制御部 850、システム制御部 860、及び再生・表示部 870 を含む。

#### 【0069】

レンズ等の光学系である光学部 810 は、被写体からの光を撮像装置 820 の、複数の画素が2次元状に配列された画素部1に結像させ、被写体の像を形成する。撮像装置 820 は、タイミング制御部 850 からの信号に基づくタイミングで、画素部1に結像された光に応じた信号を出力する。撮像装置 820 から出力された信号は、処理部である映像信号処理部 830 に入力され、映像信号処理部 830 が、プログラム等によって定められた方法に従って信号処理を行う。映像信号処理部 830 での処理によって得られた信号は画像データとして記録・通信部 840 に送られる。記録・通信部 840 は、画像を形成するための信号を再生・表示部 870 に送り、再生・表示部 870 に動画や静止画像を再生・表示させる。記録・通信部 840 は、また、映像信号処理部 830 からの信号を受けて、システム制御部 860 と通信を行うほか、不図示の記録媒体に、画像を形成するための信号を記録する動作も行う。

10

#### 【0070】

システム制御部 860 は、撮像システムの動作を統括的に制御するものであり、光学部 810、タイミング制御部 850、記録・通信部 840、及び再生・表示部 870 の駆動を制御する。また、システム制御部 860 は、例えば記録媒体である不図示の記憶装置を備え、ここに撮像システムの動作を制御するのに必要なプログラム等が記録される。また、システム制御部 860 は、例えばユーザの操作に応じて駆動モードを切り替える信号を撮像システム内に供給する。具体的な例としては、読み出す行やりセットする行の変更、電子ズームに伴う画角の変更や、電子防振に伴う画角のずらし等である。タイミング制御部 850 は、システム制御部 860 による制御に基づいて撮像装置 820 及び映像信号処理部 830 の駆動タイミングを制御する。また、タイミング制御部 850 は、撮像装置 820 の撮影感度を設定する感度設定部としても機能しうる。

20

#### 【0071】

上述の実施形態の撮像装置によって、A/D変換時の誤差を低減することが可能となる。各実施形態の構成は、適宜変更することが可能である。また、各実施形態を適宜組み合わせることも可能である。

30

#### 【符号の説明】

#### 【0072】

- 1 画素部

- 2 読み出し部

- 3 比較器

- 4 記憶部

- 6 ランプ源

- 7 カウンタ

- 9 制御信号生成部

- 10 信号線制御部

- 52 信号線

40

【図1】

【図2】

【図3】

(b)

【図4】

【 図 5 】

【 四 6 】

【 図 7 】

【 义 8 】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

(72)発明者 樋山 拓己

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 亀山 弘明

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 斎藤 和宏

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 松永 隆志

(56)参考文献 特開2014-096670(JP,A)

特開2008-060791(JP,A)

特開2009-124513(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/225 - 5/378