(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6337148号

(P6337148)

(45) 発行日 平成30年6月6日(2018.6.6)

(24) 登録日 平成30年5月11日(2018.5.11)

(51) Int.Cl.

F 1

H04B 7/005 (2006.01)

H04B 7/06 (2006.01)H04B 7/005

H04B 7/06

請求項の数 15 (全 19 頁)

(21) 出願番号 特願2016-565434 (P2016-565434)

(86) (22) 出願日 平成27年3月9日 (2015.3.9)

(65) 公表番号 特表2017-520950 (P2017-520950A)

(43) 公表日 平成29年7月27日 (2017.7.27)

(86) 國際出願番号 PCT/US2015/019490

(87) 國際公開番号 WO2015/167669

(87) 國際公開日 平成27年11月5日 (2015.11.5)

審査請求日 平成30年1月10日 (2018.1.10)

(31) 優先権主張番号 14/267,846

(32) 優先日 平成26年5月1日 (2014.5.1)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 591025439

ザイリンクス インコーポレイテッド

X I L I N X I N C O R P O R A T E D

アメリカ合衆国 カリフォルニア州 95

124-3400 サンホセ ロジック

ドライブ 2100

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 ディック, クリストファー・エイチ

アメリカ合衆国、95124 カリフォル

ニア州、サン・ノゼ、ロジック・ドライブ

、2100

審査官 鴨川 学

最終頁に続く

(54) 【発明の名称】波形微分中継器

## (57) 【特許請求の範囲】

## 【請求項 1】

信号分析および分類ブロックを有する中継器を含む、装置であって、

前記信号分析および分類ブロックは、信号分析ブロックと、分類ブロックとを含み、

前記信号分析ブロックは、前記中継器によって受信された入力信号のデジタルバージョンであるデジタル信号を受信するために結合され、

前記信号分析ブロックは、前記デジタル信号に関する信号情報を前記分類ブロックに提供するために結合され、

前記分類ブロックは、一群の波形タイプのうちの1つの波形タイプであるとして提供される前記信号情報を使用して前記デジタル信号を分類するために、分類情報を提供するように構成され、

前記分類ブロックは、前記波形タイプに基づいてパラメトリック入力を選択するために前記分類情報を提供するために、波高率低減ブロックまたはデジタルプリディストーションブロックのうちの少なくとも1つに結合される、装置。

## 【請求項 2】

前記中継器は、前記信号分析ブロックに結合されたデジタルアップコンバータを有し、

前記信号分析ブロックは、前記デジタル信号の分解された信号を前記デジタルアップコンバータに提供するために結合される、請求項1に記載の装置。

## 【請求項 3】

前記中継器は、前記波高率低減ブロックと、前記デジタルプリディストーションブロック

10

20

クとを有し、

前記信号分析ブロックはスペクトル分析ブロックであり、

前記波高率低減ブロックは前記デジタルアップコンバータに結合され、前記デジタルアップコンバータから、前記分解された信号のアップコンバートされたバージョンに基づく再構築された信号を受信し、

前記デジタルプリディストーションブロックは前記波高率低減ブロックに結合され、前記波高率低減ブロックから、前記再構築された信号の波高率低減バージョンを受信する、請求項2に記載の装置。

【請求項4】

前記分類ブロックは前記波高率低減ブロックに結合され、前記波高率低減ブロックが使用するための前記波形タイプのための前記パラメトリック入力を選択するために、前記分類情報を前記波高率低減ブロックに提供する、請求項3に記載の装置。 10

【請求項5】

前記分類ブロックは前記デジタルプリディストーションブロックに結合され、前記デジタルプリディストーションブロックが使用するための前記波形タイプのための前記パラメトリック入力を選択するために、前記分類情報を前記デジタルプリディストーションブロックに提供する、請求項3に記載の装置。

【請求項6】

前記分類情報は、周期定常性ベースの情報を含む、請求項3に記載の装置。

【請求項7】

前記周期定常性ベースの情報は、周期自己相關情報、周期周波数、およびシンボルタイミング再生情報からなる群から選択される、請求項6に記載の装置。 20

【請求項8】

前記中継器は、前記周期定常性ベースの情報を受信するために前記分類ブロックに結合された、プロセッサベースのハードウェアアクセラレータを有し、

前記プロセッサベースのハードウェアアクセラレータは、前記周期定常性ベースの情報に応答して、前記波形タイプのための前記パラメトリック入力を生成するように構成される、請求項6に記載の装置。

【請求項9】

プロセッサベースのハードウェアアクセラレータは前記波高率低減ブロックに結合され、前記パラメトリック入力のための波高率低減情報を前記波高率低減ブロックに提供する、請求項6に記載の装置。 30

【請求項10】

プロセッサベースのハードウェアアクセラレータは前記デジタルプリディストーションブロックに結合され、前記パラメトリック入力のためのデジタルプリディストーション情報を前記デジタルプリディストーションブロックに提供する、請求項7に記載の装置。

【請求項11】

前記一群の波形タイプは、直交周波数分割多重化信号、スペクトル拡散信号、周波数ホッピング帯域信号、静的狭帯域信号、およびそれらの組合せからなる、請求項8に記載の装置。 40

【請求項12】

前記信号情報は、前記デジタル信号の帯域の占有情報、前記デジタル信号の中心周波数、前記デジタル信号の帯域幅、前記デジタル信号の搬送周波数、または前記デジタル信号のチャネル間隔を含む、請求項1～11のいずれかに記載の装置。

【請求項13】

方法であって、

中継器によって入力信号を受信するステップを含み、前記中継器は、信号分析および分類ブロックに結合された入力処理チェーンを含み、前記信号分析および分類ブロックは信号分析ブロックと分類ブロックとを含み、前記方法はさらに、

前記入力処理チェーンで前記入力信号をデジタル信号に変換するステップと、

10

20

30

40

50

前記信号分析ブロックによって前記デジタル信号を受信するステップと、

前記デジタル信号に関する信号情報を前記信号分析ブロックから前記分類ブロックに提供するステップと、

一群の波形タイプから選択された1つの波形タイプであるとして提供される前記信号情報を使用して前記デジタル信号を分類するために、前記分類ブロックで分類情報を生成するステップと、

波高率低減ブロックまたはデジタルプリディストーションブロックのうちの少なくとも1つのために、前記分類情報を使用して、前記波形タイプのためのパラメトリック入力を選択するステップとを含む、方法。

【請求項14】

10

前記デジタル信号の分解された信号を、前記信号分析ブロックから前記中継器のデジタルアップコンバータに提供するステップと、

再構築された信号を提供するために、前記分解された信号を前記デジタルアップコンバータで再構成するステップと、

波高率低減信号を提供するために、前記再構築された信号を前記中継器の前記波高率低減ブロックで波高率低減するステップと、

デジタルプリディストーション信号を提供するために、前記波高率低減信号を前記中継器の前記デジタルプリディストーションブロックで歪ませるステップと、

前記波形タイプのための波高率低減のための前記パラメトリック入力を選択するために、前記分類情報の第1の部分を前記分類ブロックから前記波高率低減ブロックに提供するステップと、

20

前記波形タイプのためのデジタルプリディストーションのための前記パラメトリック入力を選択するために、前記分類情報の第2の部分を前記分類ブロックから前記デジタルプリディストーションブロックに提供するステップとをさらに含む、請求項13に記載の方法。

【請求項15】

前記デジタル信号の分解された信号を、前記信号分析ブロックから前記中継器のデジタルアップコンバータに提供するステップと、

再構築された信号を提供するために、前記分解された信号を前記デジタルアップコンバータで再構成するステップと、

30

波高率低減信号を提供するために、前記再構築された信号を前記中継器の前記波高率低減ブロックで波高率低減するステップと、

デジタルプリディストーション信号を提供するために、前記波高率低減信号を前記中継器の前記デジタルプリディストーションブロックで歪ませるステップと、

前記分類情報を前記分類ブロックから前記中継器のプロセッサベースのハードウェアアクセラレータに提供するステップと、

前記分類情報に応答して、前記プロセッサベースのハードウェアアクセラレータで、前記波形タイプのための前記パラメトリック入力を生成するステップと、

前記プロセッサベースのハードウェアアクセラレータから生成された前記パラメトリック入力を、波高率低減情報として前記波高率低減ブロックに、またはデジタルプリディストーション情報として前記デジタルプリディストーションブロックに提供するステップとをさらに含む、請求項13に記載の方法。

40

【発明の詳細な説明】

【技術分野】

【0001】

以下の説明は集積回路デバイス(integrated circuit: IC)に関する。より特定的には、以下の説明はIC用の波形微分中継器に関する。

【背景技術】

【0002】

背景

50

基地局は、中継器を通して、別の基地局または1つ以上のユーザデバイスに結合され得る。従来の中継器は到来通信波形を受入れ、受信したそのような到来波形を再増幅する。このタイプの中継器は「増幅および転送」中継器と呼ばれ得る。別のタイプの中継器は受信信号をデジタル化し、そのような受信信号を増幅のために処理し、次に、そのような信号を再送信のために再増幅し得る。しかしながら、従来、そのような中継器は、受信した波形のタイプに対して遅延処理せずにすべての到来信号を処理していた。しかしながら、複数の無線インターフェイスプロトコル用の多くのタイプの無線通信波形があり得る。波形タイプの例は、さまざまなタイプの波形または無線インターフェイスプロトコルの中でも特に、OFDM(たとえば、LTEまたはWiMAX用など)、スペクトル拡散(たとえば、WCDMA(登録商標)、TD-SCDMAまたはCDMA2000用など)、周波数ホッピング帯域信号または静的狭帯域信号(たとえば、それぞれ、周波数ホッピングまたは静的GSM(登録商標)用など)、もしくはそれらの組合せを含む。このため、そのような従来の中継器では、通信波形はタイプを考慮せずに再送信されたかも知れず(「ブラインド処理」)、基地局によって元々送信されたものよりも著しく減少した波形をもたらす。信号のそのような「ブラインド処理」は、関連付けられた1つ以上の信号処理アルゴリズムが使用されないかも知れないということを意味し得る。そのような1つ以上のアルゴリズムは、たとえば電力増幅器などの電力効率を向上させ、および/または、中継器/リレーと基地局との間の通信リンクの品質または堅牢性を高める能力を有し得るため、そのような1つ以上の信号処理アルゴリズムを適用できることは実際、操作上の支出を増加させるかも知れない。

10

20

#### 【0003】

よって、再送信のための前処理のために受信された波形のタイプに対して何らかの区別を提供して、そのような再送信される波形の品質を高める中継器を提供することが望ましいであろう。

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0004】

##### 概要

装置は一般に中継器に関する。そのような装置では、中継器は信号分析および分類ブロックを有する。信号分析および分類ブロックは、信号分析ブロックと、分類ブロックとを含む。信号分析ブロックは、中継器によって受信された入力信号のデジタルバージョンであるデジタル信号を受信するために結合される。信号分析ブロックは、デジタル信号に関する信号情報を分類ブロックに提供するために結合される。分類ブロックは、一群の波形タイプのうちの1つの波形タイプであるとして提供される信号情報を使用してデジタル信号を分類するために、分類情報を提供するように構成される。

30

#### 【0005】

いくつかの例では、信号情報は、デジタル信号の帯域の占有情報を含んでいてもよい。

いくつかの例では、信号情報は、デジタル信号の中心周波数を含んでいてもよい。

#### 【0006】

いくつかの例では、信号情報は、デジタル信号の帯域幅を含んでいてもよい。

40

いくつかの例では、信号情報は、デジタル信号の搬送周波数を含んでいてもよい。

#### 【0007】

いくつかの例では、信号情報は、デジタル信号のチャネル間隔を含んでいてもよい。

いくつかの例では、中継器は、信号分析ブロックに結合されたデジタルアップコンバータを有していてもよく、信号分析ブロックは、デジタル信号の分解された信号をデジタルアップコンバータに提供するために結合されてもよい。

#### 【0008】

いくつかの例では、中継器は、波高率低減ブロックと、デジタルプリディストーションブロックとを有していてもよく、信号分析ブロックはスペクトル分析ブロックであり、波高率低減ブロックはデジタルアップコンバータに結合され、デジタルアップコンバータか

50

ら、分解された信号のアップコンバートされたバージョンに基づく再構築された信号を受信し、デジタルプリディストーションブロックは波高率低減ブロックに結合され、波高率低減ブロックから、再構築された信号の波高率低減バージョンを受信する。

【0009】

いくつかの例では、分類ブロックは波高率低減ブロックに結合され、波高率低減ブロックが使用するための波形タイプのための波高率低減パラメトリック入力を選択するために、分類情報を波高率低減ブロックに提供してもよい。

【0010】

いくつかの例では、分類ブロックはデジタルプリディストーションブロックに結合され、デジタルプリディストーションブロックが使用するための波形タイプのためのデジタルプリディストーションパラメトリック入力を選択するために、分類情報をデジタルプリディストーションブロックに提供してもよい。

10

【0011】

いくつかの例では、分類情報は、周期定常性ベースの情報を含んでいてもよい。

いくつかの例では、周期定常性ベースの情報は、周期自己相関情報、周期周波数、およびシンボルタイミング再生情報からなる群から選択されてもよい。

【0012】

いくつかの例では、中継器は、周期定常性ベースの情報を受信するために分類ブロックに結合された、プロセッサベースのハードウェアアクセラレータを有していてもよく、プロセッサベースのハードウェアアクセラレータは、周期定常性ベースの情報に応答して、波形タイプのためのパラメトリック入力を生成するように構成される。

20

【0013】

いくつかの例では、プロセッサベースのハードウェアアクセラレータは波高率低減ブロックに結合され、パラメトリック入力のための波高率低減情報を波高率低減ブロックに提供してもよい。

【0014】

いくつかの例では、プロセッサベースのハードウェアアクセラレータはデジタルプリディストーションブロックに結合され、パラメトリック入力のためのデジタルプリディストーション情報をデジタルプリディストーションブロックに提供してもよい。

【0015】

30

いくつかの例では、一群の波形タイプは、直交周波数分割多重化信号、スペクトル拡散信号、周波数ホッピング帯域信号、静的狭帯域信号、およびそれらの組合せからなっていてもよい。

【0016】

方法は一般に中継器の動作に関する。そのような方法では、入力信号が中継器によって受信される。中継器は、信号分析および分類ブロックに結合された入力処理チェーンを含む。信号分析および分類ブロックは、信号分析ブロックと、分類ブロックとを含む。入力信号は、入力処理チェーンでデジタル信号に変換される。デジタル信号は、信号分析ブロックによって受信される。デジタル信号に関する信号情報が、信号分析ブロックから分類ブロックに提供される。一群の波形タイプから選択された1つの波形タイプであるとして提供される信号情報を使用してデジタル信号を分類するために、分類ブロックで分類情報が生成される。

40

【0017】

いくつかの例では、方法はさらに、デジタル信号の分解された信号を、信号分析ブロックから中継器のデジタルアップコンバータに提供するステップと、再構築された信号を提供するために、分解された信号をデジタルアップコンバータで再構成するステップと、波高率低減信号を提供するために、再構築された信号を中継器の波高率低減ブロックで波高率低減するステップと、デジタルプリディストーション信号を提供するために、波高率低減信号を中継器のデジタルプリディストーションブロックで歪ませるステップと、波形タイプのための波高率低減パラメトリック入力を選択するために、分類情報の第1の部分を

50

分類ブロックから波高率低減ブロックに提供するステップと、波形タイプのためのデジタルプリディストーションパラメトリック入力を選択するために、分類情報の第2の部分を分類ブロックからデジタルプリディストーションブロックに提供するステップとを含んでいてもよい。

【0018】

いくつかの例では、方法はさらに、デジタル信号の分解された信号を、信号分析ブロックから中継器のデジタルアップコンバータに提供するステップと、再構築された信号を提供するために、分解された信号をデジタルアップコンバータで再構成するステップと、波高率低減信号を提供するために、再構築された信号を中継器の波高率低減ブロックで波高率低減するステップと、デジタルプリディストーション信号を提供するために、波高率低減信号を中継器のデジタルプリディストーションブロックで歪ませるステップと、分類情報を分類ブロックから中継器のプロセッサベースのハードウェアアクセラレータに提供するステップと、分類情報に応答して、プロセッサベースのハードウェアアクセラレータで、波形タイプのためのパラメトリック入力を生成するステップと、プロセッサベースのハードウェアアクセラレータから、パラメトリック入力を、波高率低減情報として波高率低減ブロックに提供するステップとを含んでいてもよい。

10

【0019】

いくつかの例では、方法はさらに、デジタル信号の分解された信号を、信号分析ブロックから中継器のデジタルアップコンバータに提供するステップと、再構築された信号を提供するために、分解された信号をデジタルアップコンバータで再構成するステップと、波高率低減信号を提供するために、再構築された信号を中継器の波高率低減ブロックで波高率低減するステップと、デジタルプリディストーション信号を提供するために、波高率低減信号を中継器のデジタルプリディストーションブロックで歪ませるステップと、分類情報を分類ブロックから中継器のプロセッサベースのハードウェアアクセラレータに提供するステップと、分類情報に応答して、プロセッサベースのハードウェアアクセラレータで、波形タイプのためのパラメトリック入力を生成するステップと、プロセッサベースのハードウェアアクセラレータから、パラメトリック入力を、デジタルプリディストーション情報としてデジタルプリディストーションブロックに提供するステップとを含んでいてもよい。

20

【0020】

30

図面の簡単な説明

添付図面は例示的な装置および／または方法を示す。しかしながら、添付図面は特許請求の範囲を限定すると解釈されるべきではなく、単に説明および理解のためのものである。

【図面の簡単な説明】

【0021】

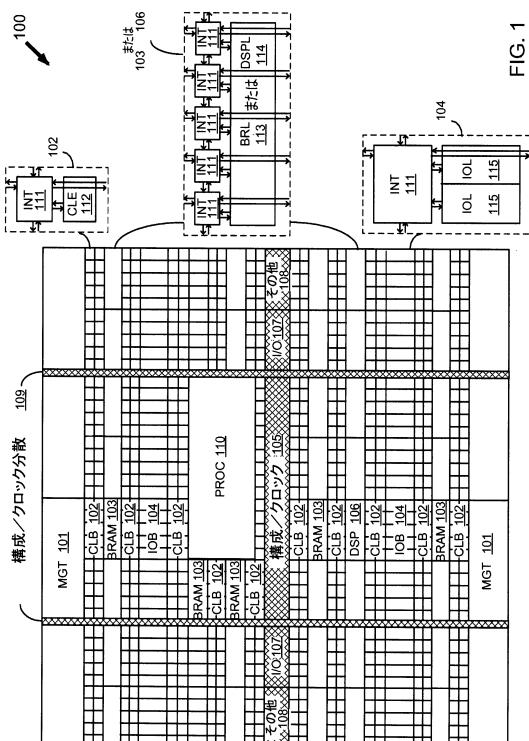

【図1】例示的な柱状フィールドプログラマブルゲートアレイ（Field Programmable Gate Array : F P G A）アーキテクチャを示す、簡略化されたブロック図である。

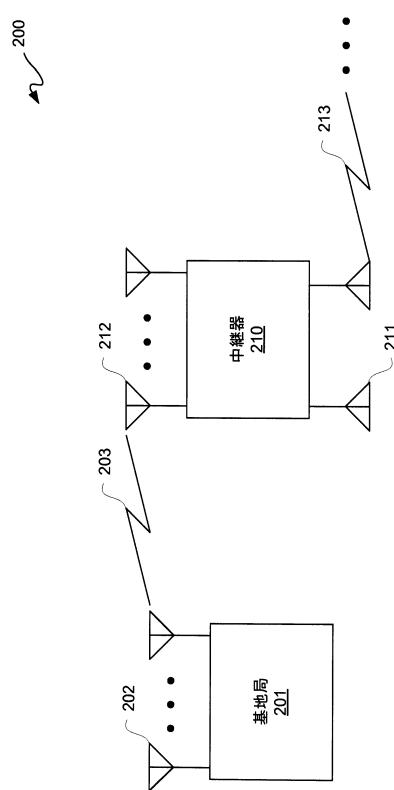

【図2】例示的なオーバー・ジ・エア（over-the-air）（無線）通信システムを示すブロック図である。

40

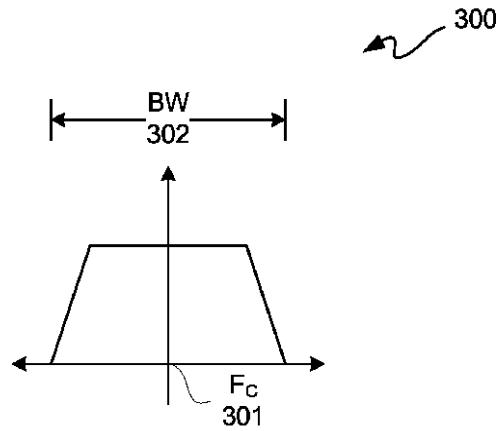

【図3】図5の中継器によって受信され得るような受信信号の例示的な一実施形態を示す信号図である。

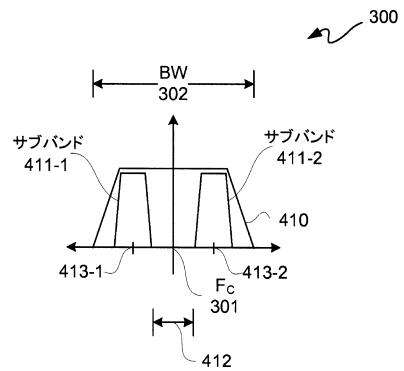

【図4】図5の中継器によって受信され得るような別の受信信号の例示的な一実施形態を示す信号図である。

【図5】例示的な中継器を示すブロック図である。

【図6】例示的な信号分析および分類ブロック505を示すブロック図である。

【図7】図5の中継器のための例示的な信号処理フローを示すフロー図である。

【図8】図5の中継器のための別の例示的な信号処理フローを示すフロー図である。

【発明を実施するための形態】

【0022】

50

### 詳細な説明

以下の説明では、ここに説明される具体例のより完全な説明を提供するために、多くの具体的な詳細が述べられる。しかしながら、1つ以上の他の例、および／またはこれらの例の変形が、以下に与えられる具体的な詳細がすべてなくても実践され得る、ということは、当業者には明らかであるはずである。他の場合では、ここでの例の説明を不明瞭にしないよう、周知の特徴は詳細には説明されていない。例示しやすくするために、異なる図において、同じ項目に言及するために、同じ番号が使用される。しかしながら、代替例では、項目は異なるかもしれない。

#### 【0023】

いくつかの図で例示的に示された例を説明する前に、概略紹介が、さらなる理解のために提供される。

10

#### 【0024】

これまで、中継器は、再送信のための前処理のために受信された波形のタイプに対して区別を提供してこなかった。しかしながら、さまざまな無線インターフェイスプロトコル用の波形のタイプには違いがあり、これらの違いは実際、そのような波形がすべて同じく処理される場合、より低品質の信号が中継器によって再送信のために再生されるかもしれない、ということを意味する。より最近では、同じ基地局が、異なる波形を有する複数の無線インターフェイスプロトコルからの信号を処理するように構成され得る。それに沿って、基地局の中には、マルチ無線アクセス技術 (radio access technology) (マルチRAT) で構成されるものもあり得る。しかしながら、そのような基地局から送信された信号を再送信するために中継器が使用される場合、そのようなさまざまな波形を処理する際にそのような基地局の効率および／または信号品質の多くが失われるかもしれない。

20

#### 【0025】

以下に説明するように、中継器は、到来波形の波形タイプに適合するように構成される。そのような適合は、受信信号に対して信号分析を行なってその信号情報を取得し、次に、取得されたそのような信号情報を使用して、受信された波形を、無線インターフェイスプロトコルに関連付けられ得るようにタイプに従って分類することを伴う。波形タイプによって通知されて、パラメトリック入力が、波形タイプに特有の波高率低減、デジタルブリディストーション、または他の信号処理などのために選択または生成され得る。これは、中継器がより高品質の信号、すなわち基地局からの元々の送信をより正確に表わす信号を再送信することを可能にする。

30

#### 【0026】

以上の一般的な理解を念頭に置いて、中継器についてのさまざまな実施形態を以下に概して説明する。

#### 【0027】

上述の例の1つ以上が、ある特定のタイプのICを使用してここに説明されるため、そのようなICの詳細な説明を以下に提供する。しかしながら、他のタイプのICが、ここに説明される手法の1つ以上から利益を得てもよい、ということが理解されるはずである。

#### 【0028】

プログラマブルロジックデバイス (programmable logic device: PLD) は、特定されたロジック機能を行なうようにプログラミングされ得る周知のタイプの集積回路である。1つのタイプのPLDであるフィールドプログラマブルゲートアレイ (FPGA) は典型的には、プログラマブルタイルのアレイを含む。これらのプログラマブルタイルは、たとえば、入力／出力ブロック (input/output block: I/O B)、構成可能ロジックブロック (configurable logic block: CLB)、専用ランダムアクセスメモリブロック (random access memory block: BRAM)、マルチプライヤ、デジタル信号処理ブロック (digital signal processing block: DSP)、プロセッサ、クロックマネージャ、遅延ロックループ (delay lock loop: DLL)などを含み得る。ここに使用されるように、「含む」と「含んで」とは、限定なしで含むことを意味する。

40

50

## 【0029】

各プログラマブルタイルは典型的には、プログラマブル相互接続およびプログラマブルロジックの双方を含む。プログラマブル相互接続は典型的には、プログラマブル相互接続点 (programmable interconnect point: PIP) によって相互接続された、さまざまな長さの多数の相互接続線を含む。プログラマブルロジックは、たとえば関数発生器、レジスタ、演算ロジックなどを含み得るプログラマブル素子を使用して、ユーザ設計のロジックを実現する。

## 【0030】

プログラマブル相互接続およびプログラマブルロジックは典型的には、プログラマブル素子がどのように構成されるかを規定する内部構成メモリセルに構成データのストリームをロードすることによってプログラミングされる。構成データは、メモリから（たとえば外部 PROM から）読出され、または、外部装置によって FPGA に書き込まれ得る。次に、個々のメモリセルの集合的な状態が、FPGA の機能を決定する。

10

## 【0031】

別のタイプの PLD は、複合プログラマブルロジックデバイス (Complex Programmable Logic Device)、すなわち CPLD である。CPLD は、ともに接続され、かつ相互接続スイッチマトリックスによって入力 / 出力 (I/O) リソースに接続された、2つ以上の「機能ブロック」を含む。CPLD の各機能ブロックは、プログラマブルロジックアレイ (Programmable Logic Array: PLA) およびプログラマブルアレイロジック (Programmable Array Logic: PAL) デバイスで使用されるものと同様の 2 レベル AND/OR 構造を含む。CPLD では、構成データは典型的には、不揮発性メモリにおいてチップ上に格納される。いくつかの CPLD では、構成データは不揮発性メモリにおいてチップ上に格納され、次に、初期構成 (プログラミング) シーケンスの一環として揮発性メモリにダウンロードされる。

20

## 【0032】

これらのプログラマブルロジックデバイス (PLD) のすべてについて、デバイスの機能性は、その目的のためにデバイスに提供されるデータビットによって制御される。データビットは、揮発性メモリ（たとえば、FPGA およびいくつかの CPLD でのようなスタティックメモリセル）、不揮発性メモリ（たとえば、いくつかの CPLD でのような FLASH メモリ）、または任意の他のタイプのメモリセルに格納可能である。

30

## 【0033】

他の PLD は、デバイス上のさまざまな素子をプログラマブルに相互接続する、金属層などの処理層を適用することによって、プログラミングされる。これらの PLD は、マスクプログラマブルデバイスとして公知である。PLD はまた、他のやり方で、たとえばヒューズまたはアンチヒューズ技術を使用して実現することもできる。「PLD」とおよび「プログラマブルロジックデバイス」という用語は、これらの例示的なデバイスを含むが、これらに限定されず、部分的にのみプログラマブルなデバイスも包含する。たとえば、1つのタイプの PLD は、ハードコード化されたトランジスタロジックと、ハードコード化されたトランジスタロジックをプログラマブルに相互接続するプログラマブルスイッチファブリックとの組合せを含む。

40

## 【0034】

上述のように、高度な FPGA は、いくつかの異なるタイプのプログラマブルロジックブロックを、アレイに含み得る。たとえば、図 1 は、マルチギガビット・トランシーバ (multi-gigabit transceiver: MGT) 101 と、構成可能ロジックブロック (CLB) 102 と、ランダムアクセスメモリブロック (RAM) 103 と、入力 / 出力ブロック (IOB) 104 と、構成およびクロッキングロジック (configuration and clocking logic: CONFIG / CLOCK) 105 と、デジタル信号処理ブロック (DSP) 106 と、特殊入力 / 出力ブロック (I/O) 107 (たとえば、構成ポートおよびクロックポート) と、デジタルクロックマネージャ、アナログ・デジタル変換器、システムモニタリングロジックなどといった他のプログラマブルロジック 108 とを含む多数の異なるブ

50

ログラマブルタイルを含む、FPGAアーキテクチャ100を示す。いくつかのFPGAは、専用プロセッサブロック(processor block: PROC)110も含む。

#### 【0035】

いくつかのFPGAでは、各プログラマブルタイルはプログラマブル相互接続素子(interconnect element: INT)111を含み、それは、隣接する各タイルにおける対応する相互接続素子への、およびそれからの標準化された接続を有する。したがって、ともにまとめられたプログラマブル相互接続素子は、図示されたFPGAのためのプログラマブル相互接続構造を実現する。プログラマブル相互接続素子111はまた、図1の上部に含まれる例によって示されるように、同じタイル内のプログラマブルロジック素子への、およびそれからの接続も含む。

10

#### 【0036】

たとえば、CLB102は、ユーザロジックを実現するようにプログラミングされ得る構成可能ロジック素子(configurable logic element: CLE)112と、単一のプログラマブル相互接続素子(INT)111とを含み得る。BRAM103は、1つ以上のプログラマブル相互接続素子に加えて、BRAMロジック素子(BRAM logic element: BRL)113を含み得る。典型的には、1つのタイルに含まれる相互接続素子の数は、タイルの高さに依存する。図示された実施形態では、BRAMタイルは5つのCLBと同じ高さを有するが、他の数(たとえば4つ)も使用可能である。DSPタイル106は、適切な数のプログラマブル相互接続素子に加えて、DSPロジック素子(DSP logic element: DSP)114を含み得る。IOB104は、たとえば、プログラマブル相互接続素子111の1つのインスタンスに加えて、入力/出力ロジック素子(input/output logic element: IOL)115の2つのインスタンスを含み得る。当業者には明らかであるように、たとえばI/Oロジック素子115に接続された実際のI/Oパッドは典型的には、入力/出力ロジック素子115のエリアに制限されない。

20

#### 【0037】

図示された実施形態では、(図1に示す)ダイの中央近くの水平エリアは、構成、クロックおよび他の制御ロジックのために使用される。この水平のエリアまたは列から延在している垂直の列109は、FPGAの幅にわたってクロックおよび構成信号を分散させるために使用される。

30

#### 【0038】

図1に示すアーキテクチャを利用するいくつかのFPGAは、FPGAの大部分を構築する通常の柱状構造を分断する追加のロジックブロックを含む。追加のロジックブロックは、プログラマブルブロックおよび/または専用ロジックであり得る。たとえば、プロセッサブロック110は、CLBおよびBRAMのいくつかの列にまたがっている。

#### 【0039】

なお、図1は、単に例示的なFPGAアーキテクチャを例示するよう意図されている。たとえば、1行におけるロジックブロックの数、行の相対的な幅、行の数および順序、行に含まれるロジックブロックのタイプ、ロジックブロックの相対的なサイズ、ならびに、図1の上部に含まれる相互接続/ロジック実現化例は、単に例示的なものである。たとえば、実際のFPGAでは、CLBが現われる場所であればどこでも、CLBの2つ以上の隣接する行が典型的には含まれて、ユーザロジックの効率的な実現を容易にするが、隣接するCLB行の数は、FPGAの全体サイズとともに変化する。

40

#### 【0040】

図2は、例示的なオーバー・ジ・エア(無線)通信システム200を示すブロック図である。通信システム200は、基地局201と、中継器210とを含む。基地局201は、1つ以上の送信アンテナ202を有する。中継器210は、無線アップリンク203を通してそのような1つ以上の送信アンテナ202に結合される1つ以上の受信アンテナ212を有する。中継器210は、基地局201からアップリンク203を介して中継器210に送信された送信を再送信するように構成される。中継器210は、そのような送信を、別の無線アップリンク213などのために、中継器210の1つ以上の受信送信アン

50

テナ 211 を介して再送信してもよい。

【0041】

図3は、中継器210によって受信され得るような受信信号300の例示的な一実施形態を示す信号図である。受信信号300のいくつかの特性は、信号帯域幅 (bandwidth: B W) 302と、中心周波数 (center frequency:  $F_c$ ) 301とを含み得る。

【0042】

図4は、中継器210によって受信され得るような別の受信信号300の例示的な一実施形態を示す信号図である。この受信信号300のいくつかの特性は、信号帯域幅 302と、中心周波数 301と、チャネル間隔またはガードバンド 412と、チャネルキャビティ 410内のサブバンド 411-1 および 411-2 といった1つ以上のサブバンドとを含み得る。さらに、サブバンド 411-1 および 411-2 は、それら各自のそれぞれの中心周波数 413-1 および 413-2、ならびに帯域幅を有し得る。

【0043】

図2～4の上述の説明に沿って、受信信号300は、送信された信号のタイプに依存して、多くの異なる特徴を有し得る。基地局201は、1つ以上の中継器210を通して、別の基地局および/または1つ以上のユーザデバイスに結合され得る。受信した波形のタイプに対して遅延処理せずにすべての到来信号を同様に処理する代わりに、中継器210は、再送信のための前処理のために受信された波形のタイプに何らかの遅延処理を提供して、そのような再送信される波形の品質を高めるように構成される。しかしながら、複数の無線インターフェイスプロトコル用の多くのタイプの無線通信波形があり得る。波形タイプの例は、さまざまなタイプの波形または無線インターフェイスプロトコルの中でも特に、OFDM (たとえば、LTEまたはWiMAX用など)、スペクトル拡散 (たとえば、WCDMA、TD-SCDMAまたはCDMA2000用など)、周波数ホッピング帯域信号または静的狭帯域信号 (たとえば、それぞれ、周波数ホッピングまたは静的GSM用など)、もしくはそれらの組合せを含む。このため、高品質の再送信、すなわち、基地局201による信号の元々送信されたバージョンの元の形により密接に適合する受信信号300の再送信を提供するために、波形タイプを考慮して受信信号300を再送信するよう、通信波形は分析され、次に、そのような基地局201の元々の送信をより正確に再生するためのパラメトリック入力を提供するために分類され得る。この信号分析はベースバンドへの変換後であってもよく、この信号分析は、分類を提供するための信号特徴ベクトルを識別するために使用されてもよい。それに沿って、1組の信号特徴ベクトルが信号分析ブロックによって通信波形から抽出されてもよく、そのような1組の信号特徴ベクトルからの各ベクトルは、そのような信号分析ブロックから提供され、分類ブロックによる分類のために提供されてもよい。

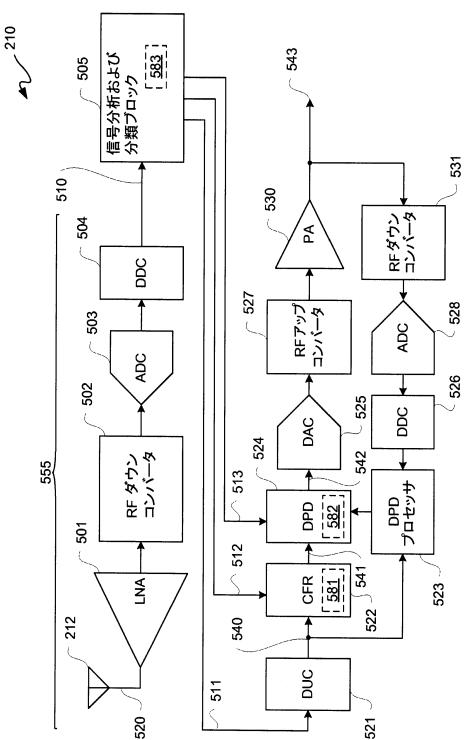

【0044】

そのような高品質の再送信を提供するために、入力された波形タイプを、それに対応するパラメトリック入力を選択および/または生成するために識別することができる中継器210が使用され得る。図5は、例示的な中継器210を示すブロック図である。中継器210の受信アンテナ212によって、オーバー・ジ・エア入力信号が受信され得る。中継器210は、図2のような1つ以上の受信アンテナ212および1つ以上の送信アンテナ211に加えて、低ノイズ増幅器 (low noise amplifier: LNA) 501と、送信周波数から中間周波数 (intermediate frequency: IF) へのダウンコンバージョンのための無線周波数 (radio frequency: RF) ダウンコンバータ502と、アナログ・デジタル変換器 (analog-to-digital converter: ADC) 503と、ベースバンド周波数 (「ベースバンド」) へのダウンコンバージョンのためのデジタルダウンコンバータ (digital down converter: DDC) 504と、信号分析および分類 (signal analysis and classification: SAAC) ブロック505と、IFへのアップコンバージョンのためのデジタルアップコンバータ (digital up converter: DUC) 521と、波高率低減 (crest factor reduction: CFR) ブロック522と、デジタルプリディストーション (digital pre-distortion: DPD) ブロック524と、DPDプロセッサ523と、デジタル・

10

20

30

40

50

アナログ変換器 (digital-to-analog converter: D A C) 5 2 5 と、送信周波数へのアップコンバージョンのための R F アップコンバータ 5 2 7 と、 D D C 5 2 6 と、 プレアンプを含む電力増幅器 (power amplifier: P A) 5 3 0 と、 A D C 5 2 8 と、 I F へのダウンコンバージョンのための R F ダウンコンバータ 5 3 1 とをさらに含んでいてもよい。1つ以上の受信アンテナ 2 1 2 と、 L N A 5 0 1 と、 R F ダウンコンバータ 5 0 2 と、 A D C 5 0 3 と、 オプションで D D C 5 0 4 とを含む入力処理チェーン 5 5 5 は、 従来のものであってもよい。したがって、 S A A C ブロック 5 0 5 への配信に先立って、 入力信号はベースバンド信号にダウンコンバートされてもよく、 S A A C ブロック 5 0 5 への入力に先立ってデジタル化されてもよい、 ということが理解されるべきである。しかしながら、 別の構成では、 たとえば対象スペクトルの一部を限定なしで含むダウンコンバージョンおよび/またはデジタル化が、 S A A C ブロック 5 0 5 によって行なわれてもよい。

10

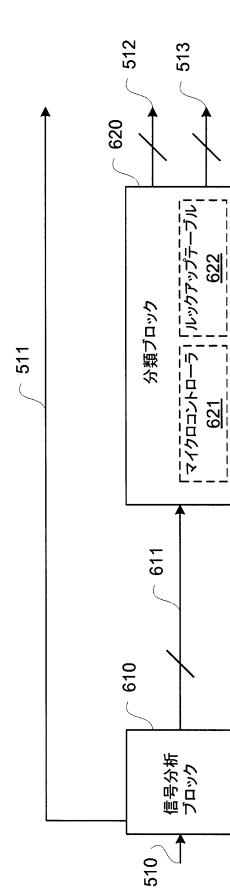

#### 【 0 0 4 5 】

図 6 は、 例示的な S A A C ブロック 5 0 5 を示すブロック図である。 S A A C ブロック 5 0 5 は、 信号分析ブロック 6 1 0 と、 分類ブロック 6 2 0 とを含む。 一例では、 信号分析ブロック 6 1 0 は、 スペクトル分析ブロックとして構成されてもよい。 図 5 および図 6 を同時に参照して、 S A A C ブロック 5 0 5 を含む中継器 2 1 0 についてさらに説明する。

#### 【 0 0 4 6 】

中継器 2 1 0 の少なくとも 1 つの受信アンテナ 2 1 2 が、 L N A 5 0 1 による増幅のために、 オーバー・ジ・エア入力信号 5 2 0 を受信する。 L N A 5 0 1 は、 増幅した信号を、 送信周波数から I F へのダウンコンバージョンのために R F ダウンコンバータ 5 0 2 に提供する。 R F ダウンコンバータ 5 0 2 は、 そのような I F の増幅信号を、 アナログ入力として、 デジタル信号への変換のために A D C 5 0 3 に提供する。 D D C 5 0 4 は、 そのようなデジタル信号をベースバンドに変換するために A D C 5 0 3 に結合されてもよい。 A D C 5 0 3 から直接、 または D D C 5 0 4 から、 受信されたオーバー・ジ・エア入力信号 5 2 0 のデジタルバージョンであるデジタル信号 5 1 0 が、 入力として S A A C ブロック 5 0 5 に提供されてもよい。

20

#### 【 0 0 4 7 】

信号分析ブロック 6 1 0 は、 デジタル信号 5 1 0 を受信するために結合されてもよい。 信号分析ブロック 6 1 0 は、 デジタル信号 5 1 0 に関する、 たとえばスペクトル情報または他の信号情報といった信号情報を提供するために結合されてもよい。 スペクトル分析ブロック 6 1 0 は、 分解された信号 5 1 1 を、 スペクトル情報出力 6 1 1 とは別個の出力として提供するように構成されてもよい。

30

#### 【 0 0 4 8 】

分解された信号 5 1 1 は、 デジタル信号 5 1 0 のチャネルごとの分解であってもよい。 分解された信号 5 1 1 を入力として D U C 5 2 1 に提供し、 そこからデジタル信号 5 1 0 を再構築または再構成して、 そのような再構築されたデジタル信号をアップコンバートしてもよく、 すなわち、 分解された信号 5 1 1 からデジタル信号 5 1 0 の I F バージョンを提供してもよく、 それは再構築された信号 5 4 0 である。 これは、 スペクトル分析ブロック 6 1 0 がデジタル信号 5 1 0 に対してある程度の破壊試験を行なうと推定する。 しかしながら、 別の構成では、 デジタル信号 5 1 0 のために平行な信号経路を使用して非破壊実現化例を提供してもよい。

40

#### 【 0 0 4 9 】

分類ブロック 6 2 0 は、 信号分析ブロック 6 1 0 から信号情報出力 6 1 1 を受信するように結合されてもよい。 分類ブロック 6 2 0 は、 信号情報出力 6 1 1 から提供された信号情報を使用してデジタル信号 5 1 0 を分類するように構成されてもよい。 そのような分類は、 デジタル信号 5 1 0 が一群の波形タイプのうちの 1 つの波形タイプであることにに関するものであってもよい。 一群の波形タイプは、 直交周波数分割多重化信号、 スペクトル拡散信号、 周波数ホッピング帯域信号、 静的狭帯域信号、 およびそれらの組合せからなっていてもよい。

50

## 【0050】

信号分析ブロック610が提供するように構成され得る信号情報の例は、分類に使用され得るスペクトルの使用に関連付けられた特定の区別的特徴の中でも特に、デジタル信号510の帯域の占有情報、デジタル信号510の中心周波数、デジタル信号510の帯域幅、デジタル信号510の搬送周波数、および／またはデジタル信号510のチャネル間隔を含んでいてもよい。占有情報はたとえば、2つ以上のサブバンドが帯域に存在するかどうかを示す、そのような帯域の占有統計を含んでいてもよい。

## 【0051】

分類ブロック620は、信号情報から波形のパターンまたは構造を検出するように構成されてもよい。たとえば、分類ブロック620は、周期定常性のまたは周期定常性ベースの分類情報を生成するように構成されてもよく、そのような周期定常性ベースの分類情報は、それに提供される信号情報を使用して生成された、周期自己相関関数 (cyclic autocorrelation function : CAF)、周期周波数、および／またはシンボルタイミング再生情報を含んでいてもよい。それに沿って、分類ブロック620は、周期定常性の動作を行なうように構成されてもよい。波形分類における追加の詳細は、LTE OFDM信号の分類についての「モバイルWiMAXおよびLTE OFDM信号の2次周期定常性、ならびにコグニティブ無線システムにおけるスペクトル認識への応用」 (Second-order cyclostationary of mobile WiMAX and LTE OFDM signals and application to spectrum awareness in cognitive radio systems)、A.アル・ハバシュナ (Al-Habashna)、O. A.ドブレ (Dobre)、R.ベンカテサン (Venkatesan) およびD. C. ポペスク (Popescu)、IEEE J. of Selected topics in signal processing、第6巻、第1号、2012年2月、第26～42頁に見出され得る。行なわれ得る他の動作は、「より低いSNRでの2次4次モーメントチップに基づいたWCDMA信号の検出方法」 (A detection method of WCDMA signal based on quadratic fourth-order moment chip at lower SNR)、P. ジュンジエ (Junjie) およびZ. ズイジン (Zhijin)、無線通信、ネットワーキングおよびモバイルコンピューティング (Wireless Communications, Networking and Mobile Computing)、2009年、WiCom '09などにおいて、CDMA信号を識別し分類するためのものであってもよい。さまざまなオーバー・ジ・エアプロトコル用の多くのタイプの波形があるため、起こり得るあらゆる波形動作の完全なリストについては、限定することなく明確にするために、ここでは不必要なまで詳細には説明しない。

## 【0052】

分類ブロック620は、判断された波形タイプに対応するパラメトリック入力の選択のための、オプションのルックアップテーブル (look-up table : LUT) 622を含んでいてもよい。それに沿って、分類ブロック620は、それに提供された信号情報に応答して分類情報を生成し、LUT 622に格納されたパラメトリック情報を選択してもよい。オプションで、LUTまたは他のストレージが使用されてもよく、CFRブロック522および／またはDPDブロック524に分散されてもよい。そのようなオプションの構成では、分類ブロック620によって生成された分類情報は、サイドバンド情報として、CFRブロック522および／またはDPDブロック524に、それらのブロックの各々におけるLUTでのそれぞれのルックアップのために提供されてもよい。しかしながら、明確にするために、LUT 622が分類ブロック620に含まれると仮定する。

## 【0053】

前述のように、CFRブロック522はDUC521に結合され、そこから、再構築された信号540を受信してもよい。再構築された信号540は加えて、入力としてDPDプロセッサ523に提供されてもよい。DPDブロック524はCFRブロック522に結合され、そこから、再構築された信号540の波高率低減バージョン、すなわち波高率低減信号541を受信してもよい。DPDブロック524は、CFR信号541をデジタルプリディストーションし、デジタルプリディストーション信号542を入力としてDAC525に提供するように構成されてもよい。DAC525はデジタルプリディストーション信号542を、RFアップコンバータ527への入力のためにアナログ信号に変換し

10

20

30

40

50

てもよく、RFアップコンバータ527はそのようなアナログ信号を、PA530への入力のためにIFから送信周波数にアップコンバートしてもよい。PA530は、中継器210による処理後のオーバー・ジ・エア入力信号520の再送信のために、図2の1つ以上のアンテナ211に結合される送信予定信号543を出力してもよい。そのような処理は、そのような再送信のためにオーバー・ジ・エア入力信号520の元々のバージョンの高品質再生を提供するために、波形タイプに対応するパラメトリック入力を提供することによって強化されてもよい。

#### 【0054】

そのような送信予定信号543は、1つ以上の送信アンテナ211を介した送信のために送信機端（明確にするために図示せず）に提供されてもよく、また、送信周波数からIF周波数へのダウンコンバージョンのために中継器210のフィードバック経路に沿ってRFダウンコンバータ531に提供されてもよい。RFダウンコンバータ531の出力は、アナログ信号からデジタル信号への変換のためにADC528に提供されてもよい。ADC528の出力はDDC526に提供され、ADC528から出力されたそのようなデジタル信号をIFからベースバンドに変換してもよい。DDC526から出力されたそのようなベースバンドデジタル信号は、入力としてDPDプロセッサ523に提供されてもよく、DPDプロセッサ523は同様に、再構成された信号540を受信するために結合されてもよい。DPDプロセッサ523の出力は、別の入力としてDPDブロック524に提供されてもよい。DPDプロセッサ523は、PA530の出力への適合のためのフィードバックループのためのものであってもよい。

10

#### 【0055】

分類ブロック620はCFRブロック522に結合され、それに、パラメトリック入力信号512を介してCFRパラメトリック入力を提供してもよい。そのようなCFRパラメトリック入力は、対応する波形タイプと関連付けてLUT622に格納されたCFRパラメータを含んでいてもよい。オプションで、別の実現化例では、LUT622は、以下により詳細に説明されるように、CFRブロック522のLUT581およびDPDブロック524のLUT582として効果的に分散されてもよい。さらに、オプションで、SACブロック505は、ブロック522および524のいずれかまたは双方のためのパラメトリック入力を生成するために分類ブロック620によって生成された分類情報を受信するために結合された、プロセッサベースのハードウェアアクセラレータ583を含んでいてもよい。しかしながら、限定することなく明確にするために、LUT622が使用されると仮定する。

20

#### 【0056】

分類ブロック620によって生成された分類情報は、識別された波形タイプのためのそのようなCFRパラメトリック入力を選択するために使用されてもよい。波形タイプに従って変わり得るCFRパラメトリック入力の例は、CFRパラメータの中でも特に、クリッピングしきい値および/または1組のフィルター係数を含んでいてもよい。

30

#### 【0057】

オプションで、または追加で、分類ブロック620はDPDブロック524に結合され、それに、パラメトリック入力信号513を介してDPDパラメトリック入力を提供してもよい。そのようなDPDパラメトリック入力は、対応する波形タイプと関連付けてLUT622に格納されたDPDパラメータを含んでいてもよい。CFRパラメトリック入力およびDPDパラメトリック入力はオプションで、同じ波形タイプのためにともに格納されてもよい。分類ブロック620によって生成された分類情報は、識別された波形タイプのためのそのようなDPDパラメトリック入力を選択するために使用されてもよい。波形タイプに従って変わり得るDPDパラメトリック入力の例は、DPDパラメータの中でも特に、1組のフィルター係数、および/またはI変更値およびQ変更値を含んでいてもよい。

40

#### 【0058】

信号分析ブロック610および分類ブロック620は、図1のFPGA100のログ

50

ラマブルリソースを使用して実現されてもよい。しかしながら、他の実現化例では、FPGA、ASIC、ASSP、または他のタイプのICのいずれの専用リソースおよび/またはプログラマブルリソースが使用されてもよい。しかしながら、限定することなく明確にするために、FPGA実現化例が使用されると仮定する。

#### 【0059】

オプションで、分類ブロック620は、より動的に適合性のあるシステムを提供するために、分類ブロック620を介して提供された構成情報に応答して、CFRパラメトリック入力であれ、および/またはDPDパラメトリック入力であれ、パラメトリック入力を生成するように構成されたマイクロコントローラ621を含んでいてもよい。それに沿って、マイクロコントローラ621は、たとえば周期定常性ベースの情報を受信するために分類ブロック620に結合され、または含まれる、プロセッサベースのハードウェアアクセラレータであってもよく、そのようなプロセッサベースのハードウェアアクセラレータは、そのような周期定常性ベースの情報を応答して、波形タイプのためのパラメトリック入力を生成するように構成されてもよい。それに沿って、そのようなプロセッサベースのハードウェアアクセラレータはCFRブロック522に結合され、それに、CFRパラメータを有するCFRパラメトリック入力信号512を提供してもよく、またはオプションで、CFRブロック522によるCFRパラメータの選択のためのCFR情報が、CFRパラメトリック入力信号512を介して提供されてもよい。同様に、そのようなプロセッサベースのハードウェアアクセラレータはDPDブロック524に結合され、それに、DPDパラメータを有するDPDパラメトリック入力信号513を提供してもよく、またはオプションで、DPDブロック524によるDPDパラメータの選択のためのDPD情報が、DPDパラメトリック入力信号513を介して提供されてもよい。

10

20

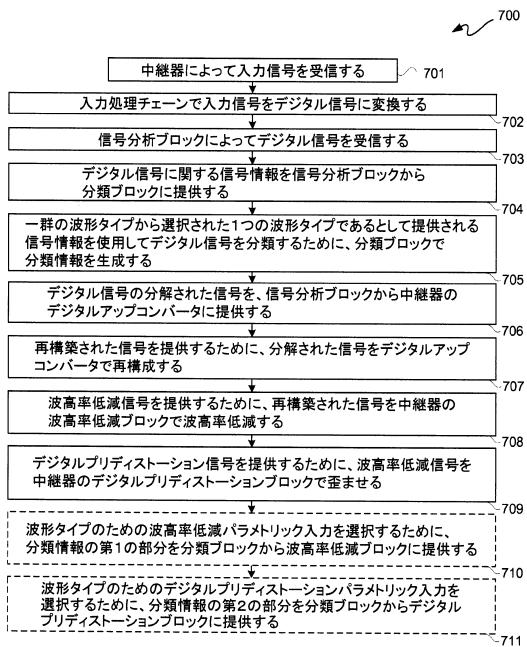

#### 【0060】

図7は、図5の中継器210のための例示的な信号処理フロー700を示すフロー図である。図5~7を同時に参照して、信号処理フロー700についてさらに説明する。

#### 【0061】

701で、入力信号が中継器210によって受信される。中継器210は、SACブロック505に結合された入力処理チェーン555を含んでいてもよく、SACブロック505は、信号分析ブロック610と、分類ブロック620とを含んでいてもよい。

30

#### 【0062】

702で、701で受信されたそのような入力信号は、入力処理チェーン555によってデジタル信号510に変換されてもよい。703で、信号分析ブロック610はそのようなデジタル信号510を受信する。704で、デジタル信号510に関する信号情報が、信号分析ブロック610から分類ブロック620に提供されてもよい。705で、一群の波形タイプから選択された1つの波形タイプであるとして提供される信号情報を使用してデジタル信号510を分類するために、分類ブロックで分類情報が生成されてもよい。

#### 【0063】

706で、デジタル信号510の分解された信号511が、信号分析ブロック610から中継器210のデジタルアップコンバータ521に提供されてもよい。707で、再構築された信号540を提供するために、分解された信号511がデジタルアップコンバータ521で再構成されてもよい。708で、再構築された信号540の波高率低減バージョン、すなわち波高率低減信号541を提供するために、再構築された信号540が中継器210のCFRブロック522で波高率低減されてもよい。709で、デジタルプリディエストーション信号542を提供するために、波高率低減信号541が中継器210のDPDブロック524で歪められてもよい。

40

#### 【0064】

オプションで、710で、701で受信され、または他の態様で取得された入力信号について識別された波形タイプのための波高率低減パラメトリック入力を選択するために、705で分類ブロック620によって生成された分類情報の第1の部分が、CFRブロック522に提供されてもよい。それに沿って、CFRブロック522はオプションで、波

50

高率低減信号 541 の品質を高めるために、そのような波形タイプのための、 C F R ブロック 522 をパラメータ化するためのパラメトリック入力が格納された L U T 581 を含んでいてもよい。そのようなパラメトリック入力は、 L U T 581 に格納されるような対応する波形タイプに関連付けられてもよい。

【 0065 】

オプションで、 711 で、識別されたそのような波形タイプのためのデジタルプリディストーションパラメトリック入力を選択するために、 705 で分類ブロック 620 によって生成された分類情報の第 2 の部分が、 D P D ブロック 524 に提供されてもよい。それに沿って、 D P D ブロック 524 はオプションで、デジタルプリディストーション信号 542 の品質を高めるために、そのような波形タイプのための、 D P D ブロック 524 をパラメータ化するためのパラメトリック入力が格納された L U T 582 を含んでいてもよい。そのようなパラメトリック入力は、 L U T 582 に格納されるような対応する波形タイプに関連付けられてもよい。

10

【 0066 】

C F R ブロック 522 および D P D ブロック 524 にそれぞれ提供される、そのようなパラメトリック入力は、そのようなブロックからそれぞれ出力される信号 540 および 541 の品質を特に高めるために、受信された入力信号の識別された波形タイプのためにそのようなブロックをパラメータ化するためのものであってもよい。より一般的には、そのようなパラメトリック入力の 1 つ以上は、そのような入力信号の元々のバージョンのより正確な複製の再送信によって、中継器 210 による再送信の品質全体を高め得る。

20

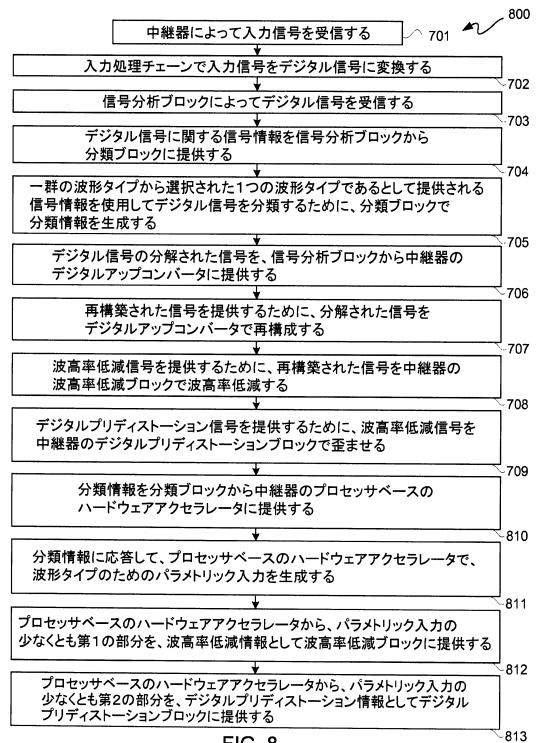

【 0067 】

図 8 は、図 5 の中継器 210 のための別の例示的な信号処理フロー 800 を示すフロー図である。図 5 、図 6 、および図 8 を同時に参照して、信号処理フロー 800 についてさらに説明する。 701 ~ 709 での動作は、図 7 を参照して前述したものと同じであるため、そのような特徴は繰り返さない。

【 0068 】

810 で、 705 で分類ブロック 620 によって生成された分類情報は、中継器 210 のオプションのプロセッサベースのハードウェアアクセラレータ 583 に提供されてもよく、オプションのプロセッサベースのハードウェアアクセラレータ 583 は S A A C 505 の一部であってもよい。 811 で、そのようなプロセッサベースのハードウェアアクセラレータ 583 に提供された分類情報に応答して、プロセッサベースのハードウェアアクセラレータ 583 で、波形タイプのためのパラメトリック入力が生成されてもよい。 812 で、そのようなパラメトリック入力の少なくとも一部が、波高率低減情報として、プロセッサベースのハードウェアアクセラレータ 583 から C F R ブロック 522 に提供されてもよい。 813 で、そのようなパラメトリック入力の別の少なくとも一部が、デジタルプリディストーション情報として、プロセッサベースのハードウェアアクセラレータ 583 から D P D ブロック 524 に提供されてもよい。

30

【 0069 】

ここでも、 C F R ブロック 522 および D P D ブロック 524 に提供される、そのようなパラメトリック入力は、そのようなブロックからそれぞれ出力される信号 540 および 541 の品質を特に高めるために、受信された入力信号の識別された波形タイプのためにそのようなブロックをパラメータ化するためのものであってもよい。しかしながら、より一般的には、そのようなパラメトリック入力の 1 つ以上は、そのような入力信号の元々のバージョンのより正しい複製の再送信によって、中継器 210 による再送信の品質全体を高め得る。 C F R ブロック 522 および D P D ブロック 524 にそれぞれ提供される、そのようなパラメトリック入力は、そのようなブロックからそれぞれ出力される信号 540 および 541 の品質を特に高めるために、受信された入力信号の識別された波形タイプのためにそのようなブロックをパラメータ化するためのものであってもよい。より一般的には、そのようなパラメトリック入力の 1 つ以上は、そのような入力信号の元々のバージョンのより正確な複製の再送信によって、中継器 210 による再送信の品質全体を高め得る

40

50

◦

【 0 0 7 0 】

前述の事項は例示的な装置および／または方法を説明しているが、ここに説明された1つ以上の局面に従った他のおよびさらなる例が、請求項およびそれらの均等物によって定められ得るその範囲から逸脱することなく考案され得る。ステップを列挙する請求項は、ステップのいかなる順序も暗示しない。商標は、それらのそれぞれの所有者の所有物である。

【 図 1 】

【 図 2 】

FIG. 2

【図3】

【図4】

FIG. 4

FIG. 3

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

---

フロントページの続き

(56)参考文献 米国特許第5544661(US, A)

国際公開第2011/149089(WO, A1)

特開平5-218914(JP, A)

特開2012-114508(JP, A)

米国特許出願公開第2005/254442(US, A1)

国際公開第2010/088110(WO, A2)

国際公開第2010/124297(WO, A1)

米国特許出願公開第2013/101066(US, A1)

(58)調査した分野(Int.Cl., DB名)

|        |           |   |           |

|--------|-----------|---|-----------|

| H 04 B | 7 / 1 4   | - | 7 / 2 2   |

| H 04 B | 1 / 7 6   | - | 3 / 4 4   |

| H 04 B | 3 / 5 0   | - | 3 / 6 0   |

| H 04 B | 7 / 0 0 5 | - | 7 / 0 1 5 |

| H 04 B | 7 / 0 0   |   |           |

| H 04 B | 7 / 0 2   | - | 7 / 1 2   |

| H 04 L | 1 / 0 2   | - | 1 / 0 6   |