(19) RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

**11 N° de publication :**

(à n'utiliser que pour les commandes de reproduction)

**2 623 675**

**(21) N° d'enregistrement national :**

87 16357

⑤1 Int Cl<sup>4</sup> : H 04 L 7/00.

12

# **DEMANDE DE BREVET D'INVENTION**

A1

(22) Date de dépôt : 25 novembre 1987.

71 Demandeur(s) : ELECTRONIQUE SERGE DASSAULT,

Société Anonyme. — FR.

③〇 Priorité :

(72) Inventeur(s) : Benoît Ponsard.

(43) Date de la mise à disposition du public de la demande : BOPI « Brevets » n° 21 du 26 mai 1989.

⑥ Références à d'autres documents nationaux appartenants :

**(73) Titulaire(s) :**

⑦4) Mandataire(s) : Cabinet Netter.

(54) Dispositif de synchronisation d'une horloge par rapport à un signal numérique incident, notamment à haut débit.

(57) Le dispositif selon l'invention comprend des moyens de prétraitement 5 qui délivrent, à une boucle à verrouillage de phase, un signal prétraité ST obtenu à partir d'une réplique R1, R3 du signal incident S décalée temporellement d'une fraction de période du signal d'horloge de la boucle à verrouillage de phase.

Ce dispositif permet alors une synchronisation rapide de l'horloge de la boucle à verrouillage de phase par rapport au signal incident S, notamment à haut débit.

E.S.D: - Aff. 380

1

Dispositif de synchronisation d'une horloge par rapport

à un signal numérique incident, notamment à haut débit.

L'invention concerne un dispositif de traitement d'un signal numérique incident pour établir un état de synchronisation entre un signal d'horloge et le signal numérique incident. Elle s'applique aux transmissions, en bande de base, 5 et convient particulièrement pour un débit élevé de transmission, supérieur à 1 mégabit par seconde, bien qu'elle puisse également servir pour des débits plus faibles.

La transmission d'un message binaire en bande de base se fait à l'aide d'un signal d'horloge de transmission. On crée à une cadence définie par cette horloge, des transitions qui sont fonction du contenu binaire du message et du code en ligne utilisé. Par exemple, le code bi-phase consiste à transmettre, pour un bit "1", un état haut suivi 10 d'un état bas à la période des impulsions d'horloge; on fait bien entendu l'inverse pour un bit "0". L'homme de l'art sait qu'il en résulte des absences de transition dans le signal transmis, lorsque le bit de message change. Plus généralement, l'invention s'applique à tout message numérique 15 codé par une succession d'états hauts et/ou bas.

Pour exploiter les messages numériques transmis il faut disposer de leur signal d'horloge à la réception. Le plus souvent on utilise à cet effet un étage de reconstitution

d'horloge agencé en boucle à verrouillage de phase.

Cette boucle comprend de façon classique, un oscillateur générant le signal d'horloge, dit ci-après principal, et 5 des moyens de synchronisation de cette horloge avec le signal numérique incident tout au long de la transmission. Après synchronisation la boucle fournit également les états successifs du signal incident, d'où l'on peut tirer le message. Pour faciliter l'acquisition du synchronisme, le début 10 de la transmission numérique comprend en principe une succession d'états alternativement hauts et bas, habituellement dénommé préambule.

Cependant la durée de cette synchronisation initiale dépend 15 de l'écart temporel entre le signal d'horloge principal et le signal numérique. Si cet écart est proche de zéro, la synchronisation de l'horloge se fait rapidement. Si cet écart est proche en valeur absolue d'une demi-période de l'horloge, la boucle à verrouillage de phase se situe dans 20 une zone instable. L'acquisition du synchronisme prend alors un temps assez long. La longueur du préambule doit être allongée en conséquence. Ceci est manifestement pénalisant pour des transmissions à haut débit. Ce phénomène d'antisynchronisme prolongé, connu sous le nom anglais de "hang-up", 25 sera appelé ci-après "suspension".

Une méthode pour s'affranchir de ce phénomène de "suspension" consiste à agir directement sur la boucle de verrouillage de phase. Cette action peut consister à en modifier rapidement 30 les caractéristiques, par exemple en inversant brutalement les valeurs hautes et basses des états successifs du signal d'horloge principal (on inverse alors la phase de l'horloge). Ce genre d'opération, acceptable pour des débits n'excédant pas 1 mégabit par seconde, ne convient pas pour 35 des débits beaucoup plus élevés de l'ordre de 32 mégabits par seconde, par exemple : se posent alors, notamment, des problèmes pour la reconnaissance de la succession des états hauts et/ou bas du signal après inversion brutale de la

phase de l'horloge.

Un autre problème existe, après synchronisation, à la réception des messages numériques, au niveau des détecteurs de phase classiques de la boucle à verrouillage de phase. En 5 effet le codage du message par succession d'états hauts et/ou bas fait, par nature, disparaître des transitions dans le signal numérique incident. Dans ces conditions, les boucles à verrouillage de phase classiques fonctionnent assez mal car elles interprètent souvent une telle absence 10 de transition comme un écart temporel très important entre le signal d'horloge et le signal numérique. Ceci se traduit par un à-coup sur la tension de commande de l'oscillateur de la boucle à verrouillage de phase et déstabilise cette dernière.

15

La présente invention pallie ces inconvénients en proposant d'effectuer un prétraitement du signal numérique avant son entrée dans l'étage de reconstitution d'horloge, ceci afin de fournir à ce dernier un signal numérique prétraité propre 20 à une synchronisation rapide du signal d'horloge principal.

Un autre but de l'invention est dans le cas de l'utilisation d'une boucle à verrouillage de phase, de délivrer à l'oscillateur générant le signal d'horloge principal, un signal 25 de commande sensiblement nul en l'absence de transition du signal prétraité, de façon à ne pas déstabiliser la boucle.

L'invention a donc pour objet un dispositif de traitement 30 d'un signal numérique incident, véhiculant, en bande de base, des messages codés par une succession d'états hauts et/ou bas sur une horloge de transmission, comportant:

- une entrée de réception du signal numérique incident,

- 35 - un étage de reconstitution d'horloge comprenant une horloge principale ajustable, de fréquence nominale reliée à celle de l'horloge de transmission, et une entrée de syn-

chronisation de cette horloge principale, susceptible d'être reliée à l'entrée de réception,

5 caractérisé en ce qu'il comporte, en outre, des moyens de prétraitement comprenant:

- un commutateur à trois états, dans chacun desquels il relie respectivement sa première, sa deuxième et sa troisième entrée à ladite entrée de synchronisation,

10

- des moyens de retard interposés entre l'entrée de réception et le commutateur, et propres à fournir respectivement aux deuxième et troisième entrées du commutateur, au moins une première paire de répliques du signal incident, différentes, les deux répliques étant décalées temporellement l'une par rapport à l'autre d'une fraction de période de l'horloge principale, de préférence sensiblement une demi-période,

20 - une horloge auxiliaire, opérant à une fréquence prédéterminée choisie pour autoriser son application à la première entrée du commutateur, aux fins de synchroniser l'horloge principale, et

25 - des moyens de commande sensibles à la présence du signal numérique incident pour:

30 - en l'absence de signal incident, mettre le commutateur dans son premier état, l'horloge principale étant alors synchronisée sur l'horloge auxiliaire,

35 - en présence du signal incident, mettre le commutateur dans son deuxième ou son troisième état en fonction de la situation temporelle de l'horloge auxiliaire relativement au signal incident.

Dans un mode préféré de réalisation, le signal numérique incident peut commencer par une succession d'états alterna-

tivement hauts et bas.

Selon une variante de l'invention, en présence du signal incident, les moyens de commande mettent le commutateur 5 dans son deuxième ou son troisième état en fonction de la situation temporelle de l'horloge auxiliaire relativement à ladite première paire de répliques.

Dans un mode préféré de réalisation, les moyens de retard 10 sont propres à fournir une deuxième paire de répliques du signal incident, différentes des répliques de la première paire, et également décalées l'une par rapport à l'autre de ladite fraction de période de l'horloge principale, l'une des répliques de cette deuxième paire étant décalée temporellement 15 par rapport à chacune des deux répliques de la première paire sensiblement de la moitié de ladite fraction de période de l'horloge principale.

En présence d'un signal incident, les moyens de commande 20 mettent avantageusement le commutateur dans son deuxième ou son troisième état en fonction de la situation temporelle de l'horloge auxiliaire relativement à cette deuxième paire de répliques du signal incident.

25 Les moyens de commande comprennent avantageusement, d'une part, des moyens échantillonneurs, pour échantillonner à la fréquence de l'horloge auxiliaire, simultanément et séparément, chacune des répliques de la paire relativement à laquelle est déterminée la situation temporelle de l'horloge auxiliaire, et, d'autre part, des moyens de comparaison 30 de ces répliques échantillonées fournissant un signal de comparaison représentatif de la valeur respective de ces répliques.

35 Les moyens de commande comprennent, de préférence, en outre, une logique de commande, commandée à la fréquence de l'horloge auxiliaire, et des moyens de mémorisation de la valeur respective des deux répliques de la paire relativement à

laquelle est déterminée la situation temporelle de l'horloge auxiliaire, la sortie de ces moyens de mémorisation et une sortie de la logique de commande faisant partie d'un signal de commande pour le commutateur.

5

Dans un mode préféré de réalisation, les moyens échantillonneurs, les moyens de mémorisation et la logique de commande comprennent des bascules-mémoires.

- 10 Avantageusement, la présence ou l'absence de signal incident, sont évaluées par des moyens de détection recevant deux répliques distinctes.

Ces moyens de détection comprennent de préférence, des moyens de comparaison supplémentaires recevant lesdites deux répliques, la sortie de ces moyens de comparaison supplémentaires étant reliée à un monostable redéclenchable dont la durée minimale est égale au moins au temps maximum séparant deux transitions successives du signal numérique incident.

20

Dans un mode de réalisation particulièrement avantageux, l'étage de reconstitution d'horloge est agencé en une boucle à verrouillage de phase.

- 25 Cet étage de reconstitution d'horloge peut comprendre alors un étage détecteur de phase, possédant une première entrée reliée à l'entrée de synchronisation, une deuxième entrée reliée à l'horloge principale, et une sortie délivrant un signal de commande d'horloge, dont la valeur moyenne est

30 sensiblement proportionnelle à l'écart temporel entre le signal d'horloge principal et le signal numérique présent à l'entrée de synchronisation, et dont l'amplitude est sensiblement nulle en l'absence de transition du signal numérique présent à l'entrée de synchronisation.

35

Avantageusement l'étage détecteur de phase comprend des moyens de retard supplémentaires, reliés à la première en-

trée et délivrant une réplique du signal numérique présent à l'entrée de synchronisation, décalée sensiblement d'une période de l'horloge principale; l'étage détecteur de phase comprend également de préférence un premier échantillonneur 5 du signal numérique présent à l'entrée de synchronisation, un second échantillonneur de la sortie du premier échantillonneur, ladite réplique étant d'une part, comparée à la sortie du premier échantillonneur et, d'autre part à la sortie du deuxième échantillonneur, la différence des valeurs 10 de ces deux comparaisons fournissant le signal de commande d'horloge.

Selon une variante de l'invention, permettant de traiter le signal numérique incident en utilisant seulement deux 15 répliques de ce signal, l'horloge auxiliaire comprend une source de fréquence multiple de la fréquence de l'horloge auxiliaire suivie d'un diviseur.

D'autres avantages et caractéristiques de l'invention apparaîtront à l'examen de la description détaillée ci-après 20 et des dessins annexés sur lesquels:

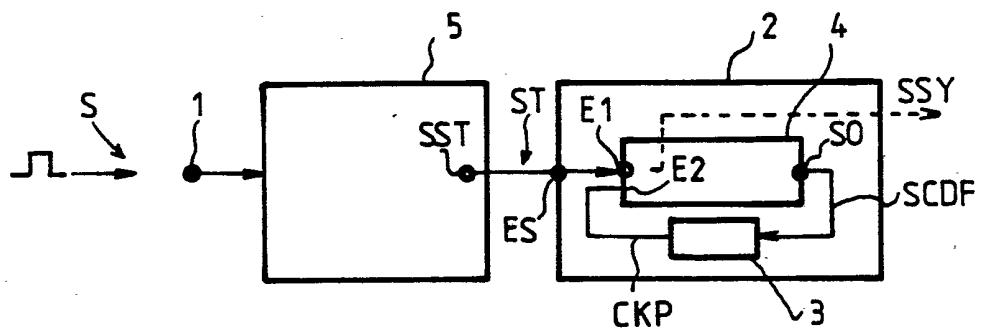

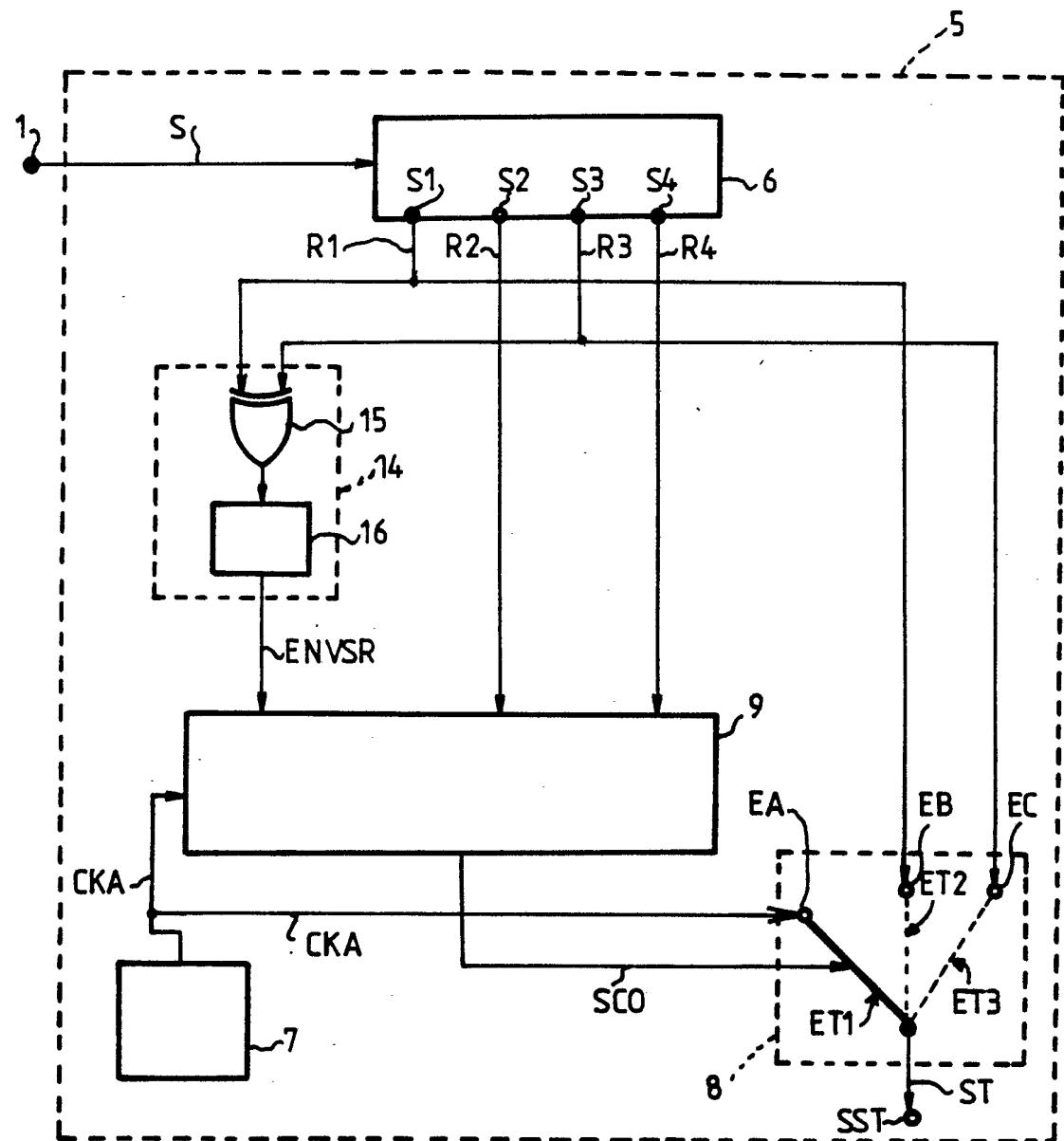

- la figure 1 est un synoptique schématique du dispositif de traitement selon l'invention,

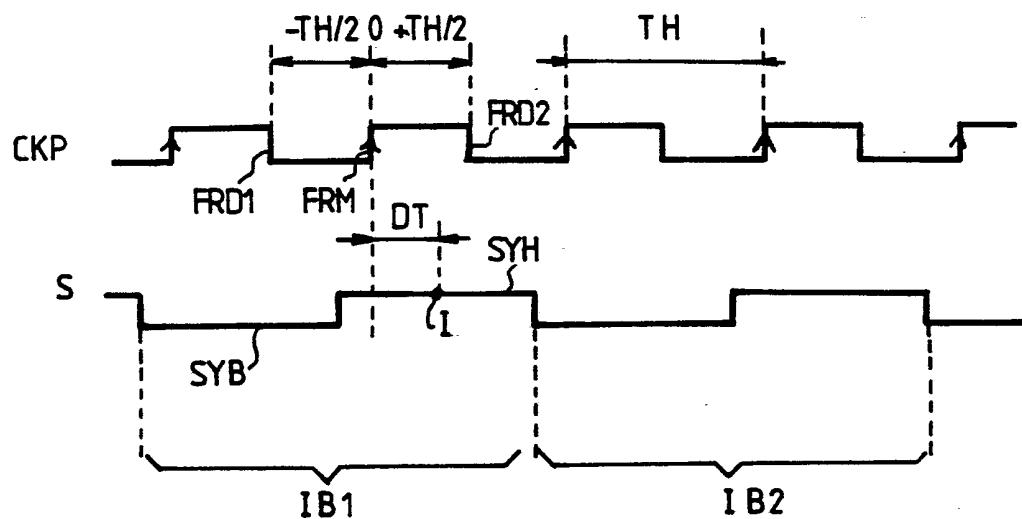

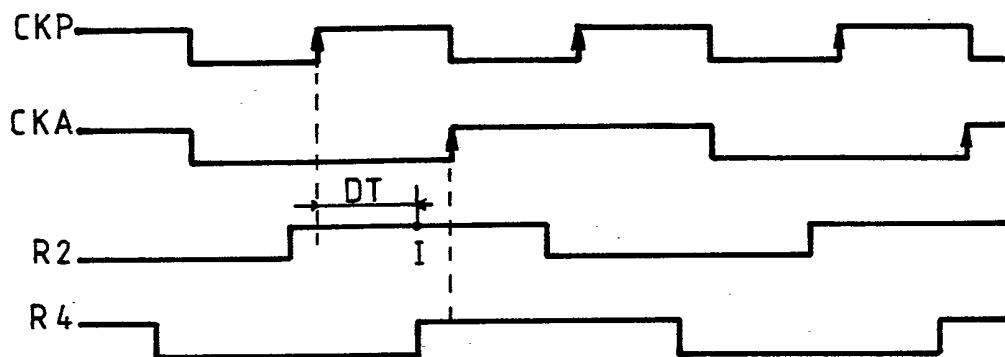

- 25 - la figure 2 est un diagramme temporel définissant un signal numérique incident et son codage par rapport à un signal d'horloge,

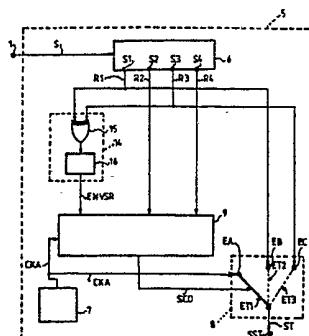

- 30 - la figure 3 est un synoptique schématique des moyens de prétraitement du dispositif de traitement de la figure 1,

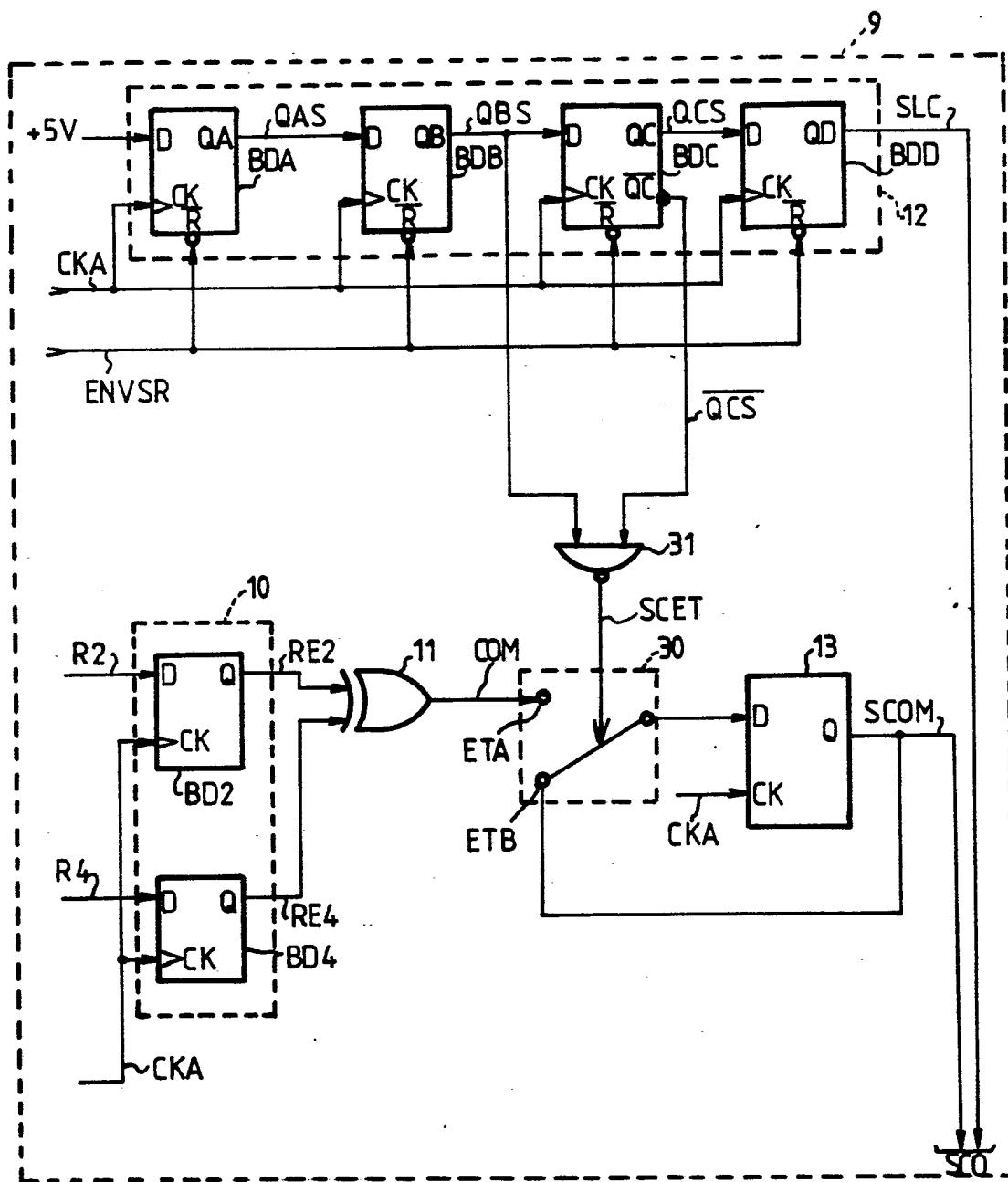

- la figure 4 est un synoptique schématique des moyens de commande des moyens de prétraitement de la figure 3,

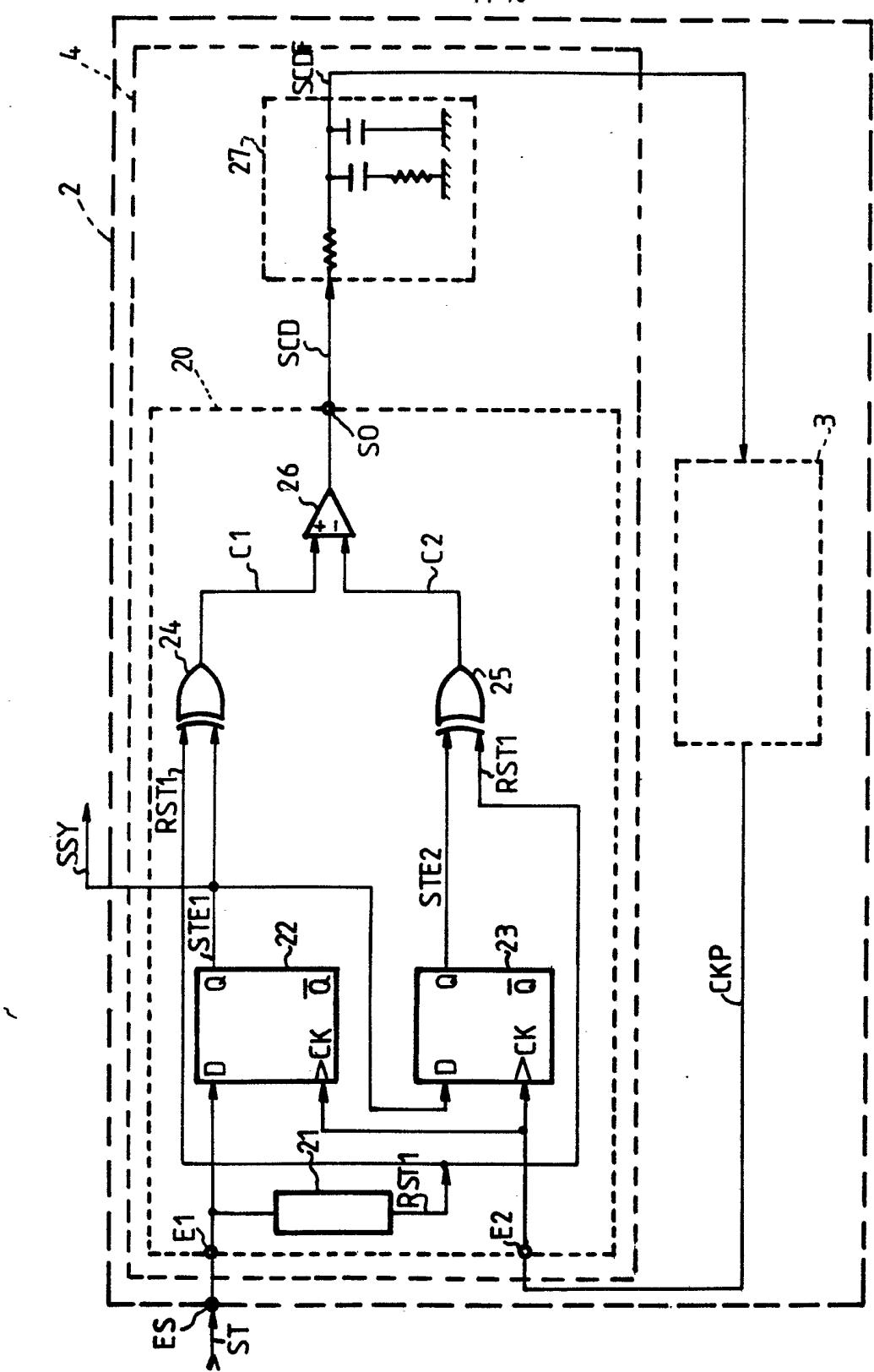

- 35 - la figure 5 est un synoptique schématique de l'étage de reconstitution d'horloge du dispositif de traitement de

la figure 1,

- la figure 6 représente des diagrammes temporels illustrant un cas de fonctionnement du dispositif de traitement

5 de la figure 1,

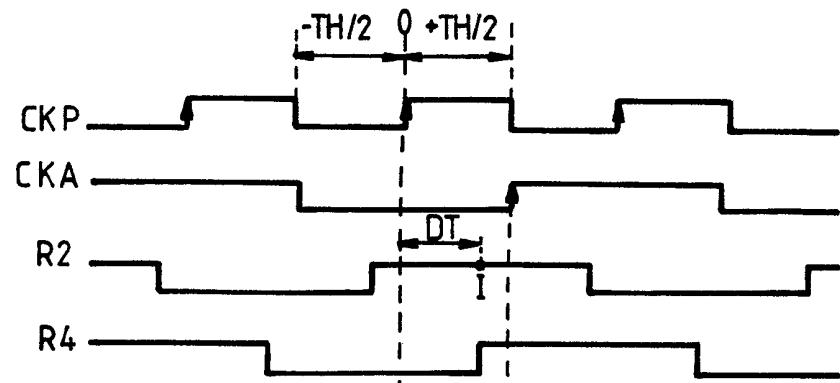

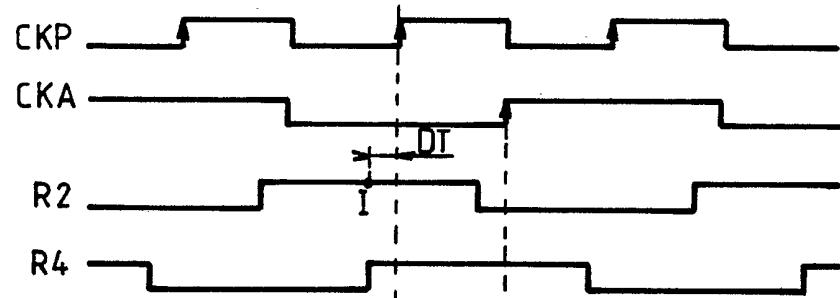

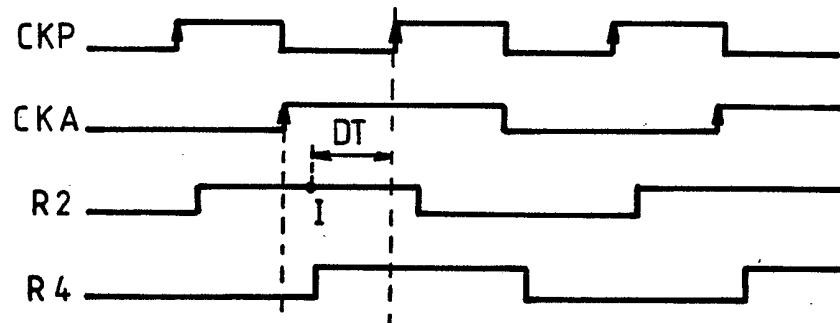

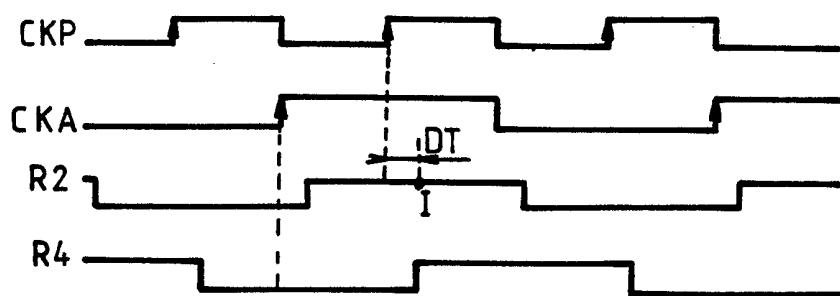

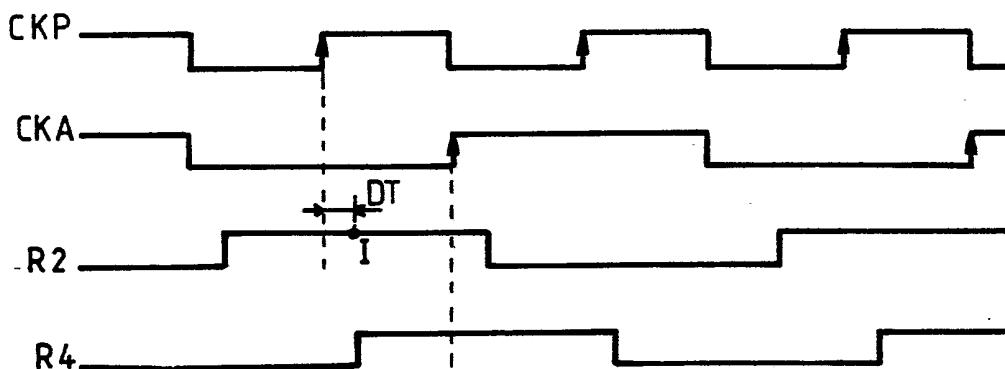

- les figures 7A à 7F sont des diagrammes temporels illustrant différents cas de fonctionnement des moyens de commande de la figure 4, et,

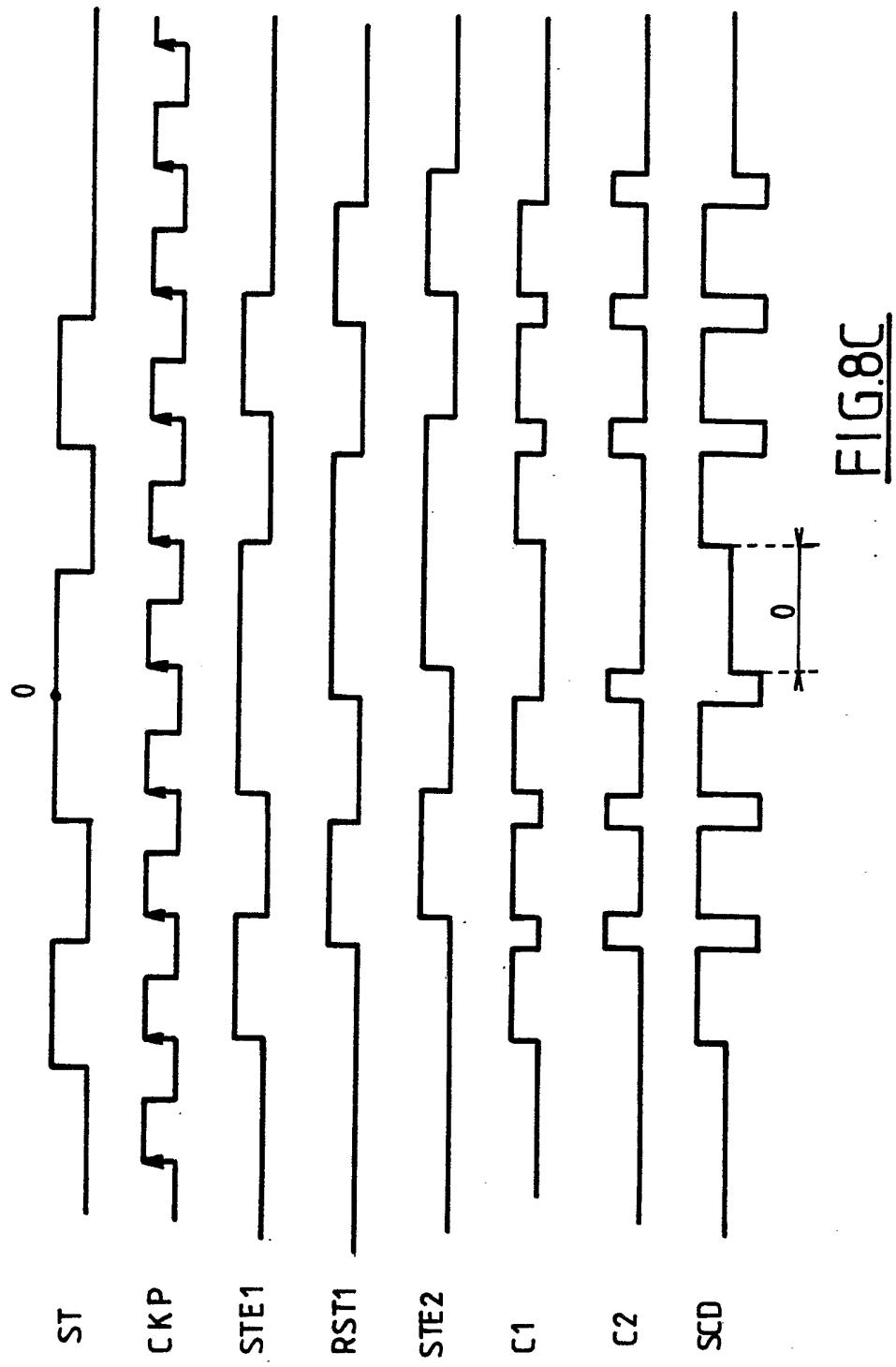

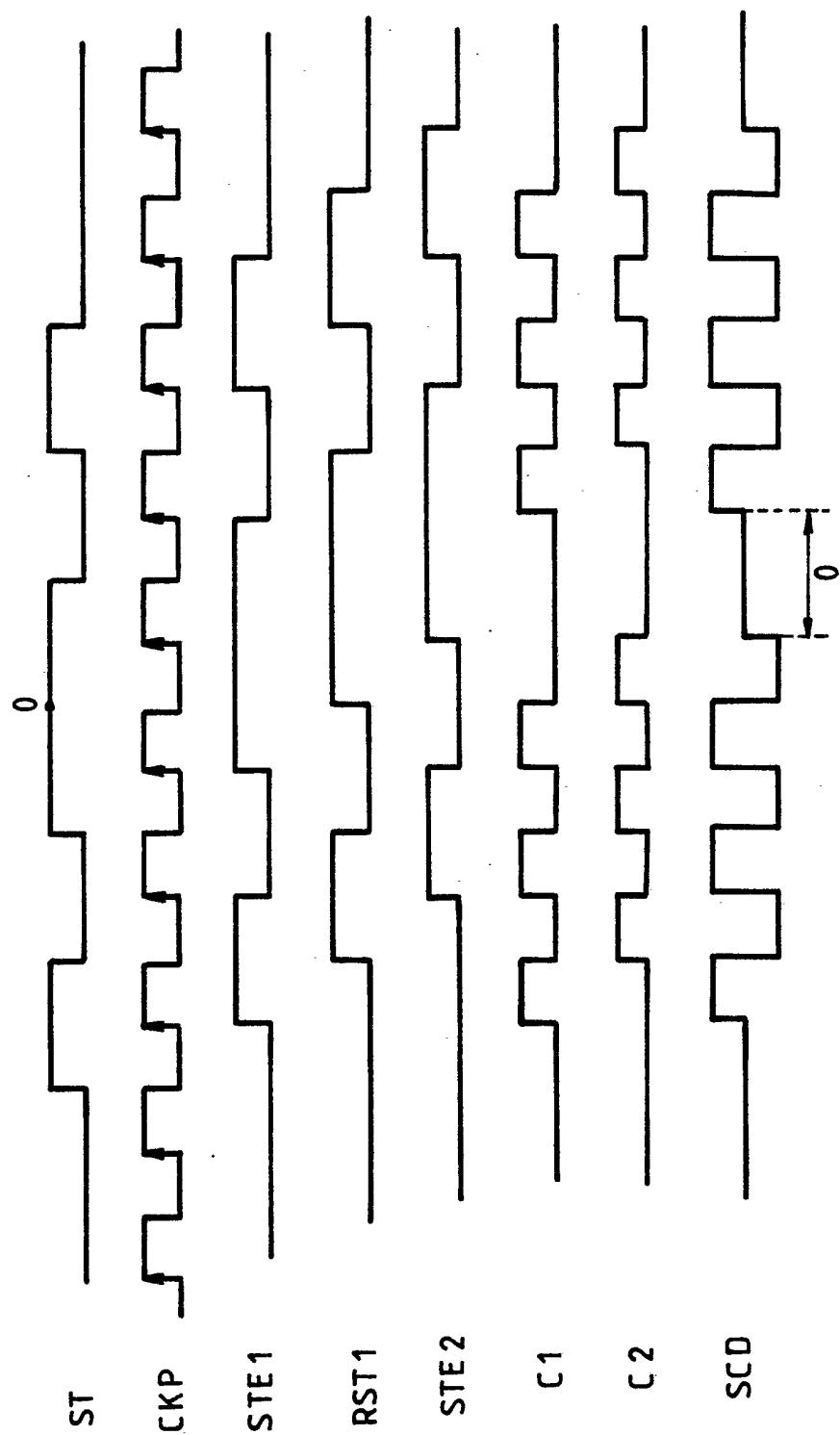

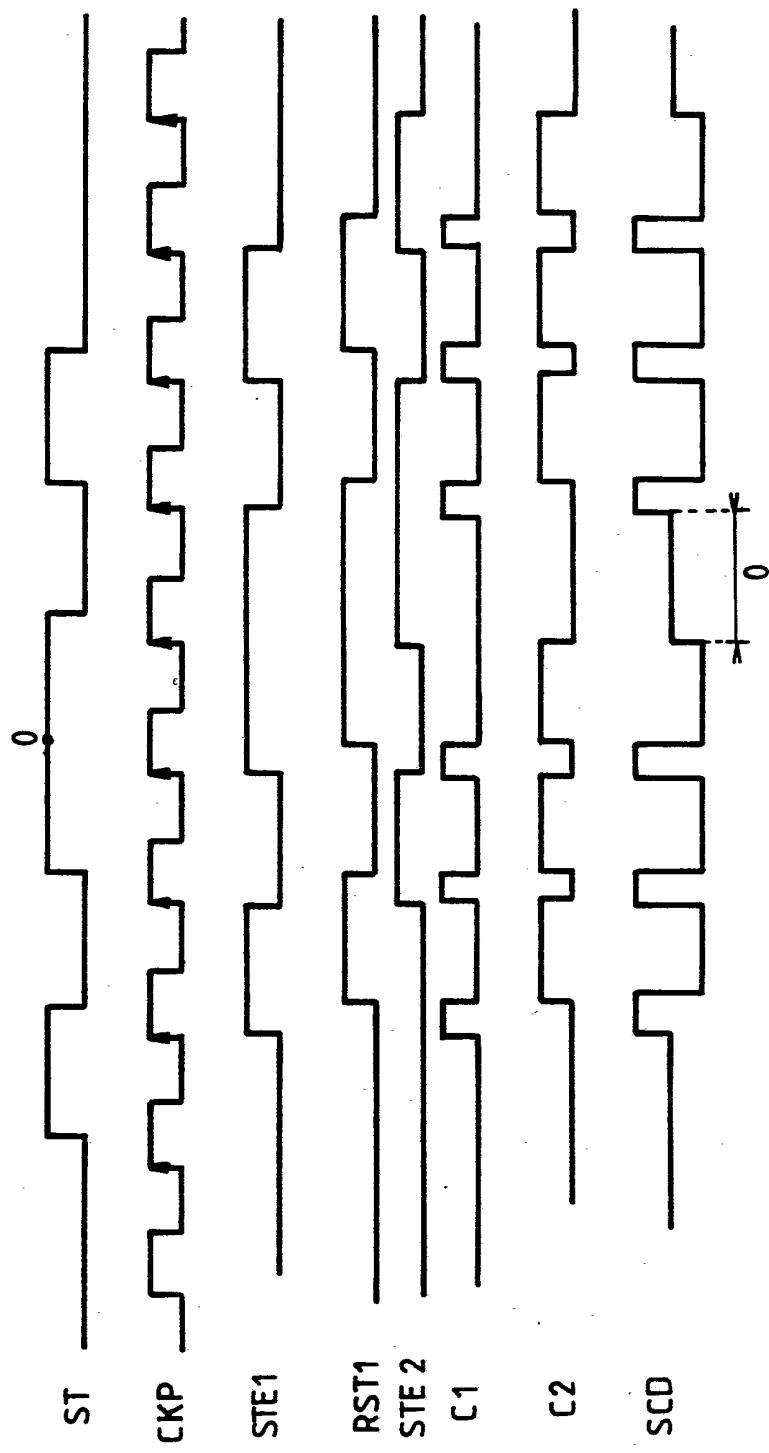

10 - les figures 8A à 8C sont des diagrammes temporels illustrant différents cas de fonctionnement de l'étage de reconstitution d'horloge de la figure 5.

- 15 Les dessins annexés comportant pour l'essentiel des éléments de caractère certain, pourront servir non seulement à mieux faire comprendre la description détaillée ci-après, mais aussi le cas échéant, à la définition de l'invention.

- 20 Le dispositif de traitement représenté sur la figure 1 comprend une entrée de réception 1 recevant un signal numérique incident S. Ce dispositif de traitement comprend également un étage de reconstitution d'horloge 2 comportant, une horloge principale 3 générant un signal d'horloge principal CKP, et, une entrée de synchronisation ES de cette horloge principale 3. Cet étage de reconstitution d'horloge 2 comprend également des moyens de synchronisation 4 de cette horloge, possèdant deux entrées, l'une étant reliée à l'entrée de synchronisation ES et l'autre recevant le signal d'horloge CKP. Ainsi qu'il sera expliqué ci-après, l'étage de reconstitution d'horloge est agencé pour former une boucle à verrouillage de phase et fournit le signal SSY synchronisé avec le signal CKP.

25

30

35 Le dispositif de traitement comprend, en outre, des moyens de prétraitement 5 du signal numérique incident S. Ceux-ci possèdent une sortie SST reliée à l'entrée de synchronisation ES et délivrant un signal prétraité ST.

Si l'on se réfère à la figure 2, on voit que le signal numérique incident est composé d'une succession d'états hauts SYH et d'états bas SYB, arrivant à la fréquence de l'horloge de transmission. On admettra dans la suite du texte,

5 que le signal numérique S est codé en code bi-phase, bien que, l'invention s'applique à tout signal numérique codé par succession d'états hauts et/ou bas. En principe le signal S commence par une succession d'états alternativement hauts et bas, constituant un préambule.

10 Ainsi qu'il a été expliqué ci-avant, dans le code bi-phase, la transmission d'une information binaire s'effectue par la transmission successive de deux états de valeur différente. Ainsi pour transmettre une information binaire

15 IBI égale à 0 (respectivement égale à 1), on transmettra successivement un état bas SYB (respectivement un état haut SYH) et un état haut SYH (respectivement un état bas SYB). On admettra également que les informations binaires IBI, IB2 représentées sur la figure 2 constituent une partie

20 du préambule du signal S servant à la synchronisation du signal d'horloge CKP. Ces informations binaires IBI et IB2 sont identiques et égales à zéro de façon à ne pas supprimer de transition dans le préambule. Le message proprement dit, véhiculé par le signal S et venant après le préambule est

25 également composé d'une suite d'informations binaires telles que celles représentées sur la figure 2.

Le signal d'horloge principal CKP a une fréquence nominale reliée à celle du signal d'horloge de transmission du signal S. Dans le cas présent, la fréquence de l'horloge principale est égale à 32 mégahertz. Sa période TH est donc égale à 31,25 nanosecondes. La fréquence de transmission des états hauts SYH et/ou bas SYB est également égale à 32 mégahertz. Le débit d'informations binaires IB transmises est donc de "16 méga-informations par seconde".

Ainsi qu'il a été expliqué ci-avant, l'écart temporel entre le signal d'horloge CKP et le signal numérique S con-

ditionne le temps de synchronisation de ce signal CKP par rapport au signal S. Cet écart temporel DT s'apprécie en évaluant l'écart entre le point milieu I d'un état haut SYH (ou d'un état bas SYB) et le front montant le plus proche FRM (impulsion) du signal d'horloge CKP. Si cet écart est nul, les deux signaux sont en phase. Si le point I est proche du front descendant FRD2 (respectivement FRD1) suivant (respectivement précédent) le front montant FRM, le signal S est en retard (respectivement en avance), sur le signal d'horloge CKP et l'écart temporel DT est proche d'une demi-période TH/2 du signal d'horloge CKP (respectivement de - TH/2).

Si l'on se réfère maintenant plus particulièrement à la figure 3, on voit que les moyens de prétraitement 5 du signal numérique incident S comprennent des moyens de retard reliés à l'entrée de réception 1 du dispositif de traitement. Ces dits moyens de retard possèdent quatre sorties S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>, S<sub>4</sub> fournissant respectivement quatre répliques R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub>, R<sub>4</sub> du signal numérique incident S, ces répliques étant différentes l'une de l'autre et étant décalées successivement l'une par rapport à l'autre sensiblement d'un quart de période de l'horloge principale. Ce décalage vaut donc environ 7,81 nanosecondes. Bien entendu une marge d'incertitude sur ce décalage est tolérée et est égale environ à  $\pm$  2 nanosecondes.

La première réplique R<sub>1</sub> peut être le signal S lui-même, ou éventuellement une réplique retardée par rapport au signal S soit par propagation dans la connexion depuis l'entrée de réception 1 soit par passage dans des éléments amplificateurs ("buffers"). Les répliques R<sub>1</sub> et R<sub>3</sub> constituant une première paire de répliques, sont alors décalées l'une par rapport à l'autre sensiblement de la moitié de la période de l'horloge principale. Il en est de même pour les deux répliques R<sub>2</sub> et R<sub>4</sub> constituant une deuxième paire de répliques.

Les moyens de retard 6 peuvent être constitués par une fibre optique ou bien un circuit de retard classique capacité-inductance, ou encore une ligne coaxiale.

- 5 Les deux répliques R1 et R3 sont utilisées pour effectuer une détection du signal d'entrée S. Les sorties correspondantes S1, S3 sont reliées en effet aux deux entrées d'une porte logique OU EXCLUSIF 15 suivie d'un monostable redéclenchable 16. Ce monostable 16 a une durée minimale égale à au moins deux fois la période de transmission des états haut ou bas soit 62,50 nanosecondes. Cette durée est de façon générale adaptée au codage en ligne utilisé afin de couvrir au moins le temps maximum séparant deux transitions successives du signal d'entrée S. La sortie de ce monostable 16 délivre un signal de détection ENVSR qui passe donc à la valeur 1 dès la réception du signal incident S. L'ensemble (porte logique 15 - monostable 16) constitue des moyens de détection 14.

- 20 Les moyens de prétraitement 5 comportent également un commutateur 8 possédant trois entrées EA, EB, EC et une sortie qui correspond à la borne de sortie SST des moyens de prétraitement 5. Les trois entrées correspondent respectivement à trois états ET1, ET2, ET3. Ces moyens de prétraitement 5 comportent également une horloge auxiliaire 7 opérant à la fréquence sensiblement moitié de celle de l'horloge principale 3. L'horloge auxiliaire 7 opère donc à 16 mégahertz environ avec une marge d'incertitude égale à environ  $\pm 1\%$ .

- 30 Cette horloge auxiliaire 7 délivre un signal d'horloge auxiliaire CKA qui alimente la première entrée EA du commutateur 8; la deuxième EB et la troisième EC entrées sont respectivement alimentées par les deux répliques R1 et R3.

- 35 Les moyens de prétraitement 5 comprennent enfin des moyens de commande 9 de ce commutateur 8. Ces moyens de commande 9 reçoivent le signal ENVSR, les deux autres répliques R2

et R4 ainsi que le signal d'horloge auxiliaire CKA. Ils délivrent un signal de commande SCO au commutateur 8 pour le mettre soit dans son état ET1 ou dans son état ET2 ou dans son état ET3 afin de délivrer à l'étage de reconstitution d'horloge 2 le signal numérique prétraité ST qui est en fait, soit le signal d'horloge auxiliaire CKA, soit une réplique du signal incident S plus ou moins décalée temporellement par rapport à ce signal S.

- 10 Si l'on se réfère maintenant plus particulièrement à la figure 4 on voit que les moyens de commande 9 comprennent des moyens échantillonneurs 10 composés de deux bascules D BD2 et BD4 recevant respectivement sur leur entrée D les deux répliques R2 et R4. Ces deux bascules BD2 et BD4 reçoivent sur l'entrée CK le signal d'horloge auxiliaire CKA. Les sorties Q de ces deux bascules BD2 et BD4 délivrent respectivement deux répliques échantillonnées RE2 et RE4 qui sont comparées dans une porte logique OU EXCLUSIF 11. Le signal de comparaison COM issu de cette porte logique 11

20 est affecté à l'état ETA d'un commutateur 30 à deux états ETA, ETB dont la sortie est reliée à l'entrée D d'une autre bascule D 13. Ainsi qu'on le verra ci-après cette bascule 13 constitue un moyen de mémorisation de la valeur du signal COM. L'entrée CK de cette bascule 13 reçoit également le

25 signal d'horloge auxiliaire CKA, la sortie Q de cette bascule 13 délivrant un signal de comparaison SCOM qui est une des composantes du signal de commande SCO. Le deuxième état ETB du commutateur 30 est relié directement à la sortie Q de la bascule 13. Cet état ETB est en fait un état de repos alors que l'état ETA est un état de travail.

Les moyens de commande 9 comprennent également une logique de commande 12 qui est constituée d'un registre à décalage composé de quatre bascules D respectivement référencées BDA, BDB, BDC, BDD. L'entrée CK de chacune de ces bascules BDA à BDD reçoit le signal d'horloge auxiliaire CKA et l'entrée de mise à zéro  $\bar{R}$  de chacune de ces bascules BDA à BDD reçoit le signal de détection ENVSR. L'entrée D de la pre-

mière bascule BDA est alimentée par le 5 volts continu. La sortie QA de cette bascule délivre un signal QAS sur l'entrée D de la bascule BDB il en est de même pour la sortie QB de la bascule BDB qui délivre un signal QBS sur l'entrée 5 D de la bascule BDC et pour la bascule BDC qui délivre un signal QCS sur l'entrée D de la bascule BDD. La sortie QD de la bascule BDD délivre un signal de logique de commande SLC qui constitue la deuxième partie du signal de commande SCO. Les signaux QBS et  $\overline{QCS}$  des bascules BDB et BDC sont 10 reliés aux deux entrées d'une porte logique NON ET 31 délivrant en sortie un signal SCET qui commute le commutateur à deux états 30, sur l'un de ces deux états ETA, ETB.

Si l'on se réfère maintenant à la figure 5, on voit que 15 les moyens de synchronisation 4 de l'étage de reconstitution d'horloge 2, comprennent un premier étage 20 ayant deux entrées E1 et E2 et une sortie SO reliées à un étage de filtrage 27 dont la sortie est reliée à un oscillateur commandé en tension 3 délivrant à la borne d'entrée E2 du 20 premier étage 20 le signal d'horloge principal CKP. On désigne abusivement par la même référence l'oscillateur commandé en tension et l'horloge principale. Seul le terme horloge principale sera employé dans la suite.

25 L'entrée E1 de ce premier étage 20, reliée à l'entrée de synchronisation ES, étage qui est en fait un étage détecteur de phase, reçoit le signal prétraité ST. Cet étage comprend des moyens de retard supplémentaires 21 reliés à l'entrée E1 et fournissant une réplique RST1 du signal numérique 30 prétraité ST, réplique décalée temporellement d'un retard sensiblement égal à une période de l'horloge principale 3 soit 31,25 nanosecondes (la marge de tolérance sur ce retard est de l'ordre de  $\pm 5$  nanosecondes). Le signal numérique prétraité ST est relié à l'entrée D d'une première bascule 35 D 22 constituant un premier échantillonneur. La sortie Q de cette bascule 22 délivre un signal échantillonné STE1 sur l'entrée D d'une deuxième bascule D 23 constituant un second échantillonneur. La sortie Q de ce second échantillon-

neur 23 délivre un signal échantillonné STE2. Les entrées CK de chacune des deux bascules 22 et 23 reçoivent le signal d'horloge principal CKP. Le signal échantillonné STE1 est comparé à la réplique décalée RST1 du signal ST dans une 5 porte logique OU EXCLUSIF 24 et le signal échantillonné STE2 est comparé à la réplique décalée RST1 dans une deuxième porte logique OU EXCLUSIF 25. Ces deux portes 24 et 25 délivrent respectivement deux signaux de comparaison C1 et C2 reliés respectivement à un amplificateur différentiel 26, 10 dont la sortie est reliée à la sortie SO du premier étage 20, et qui délivre un signal de commande de l'horloge principale SCD. L'homme de l'art remarquera que les états successifs du signal incident après synchronisation, (signal SSY) sont fournis par le signal échantillonné STE1.

15 L'étage de filtrage 27 est constitué classiquement d'un réseau résistif capacitif et le signal de commande filtré SCDF commande effectivement l'horloge principale 3.

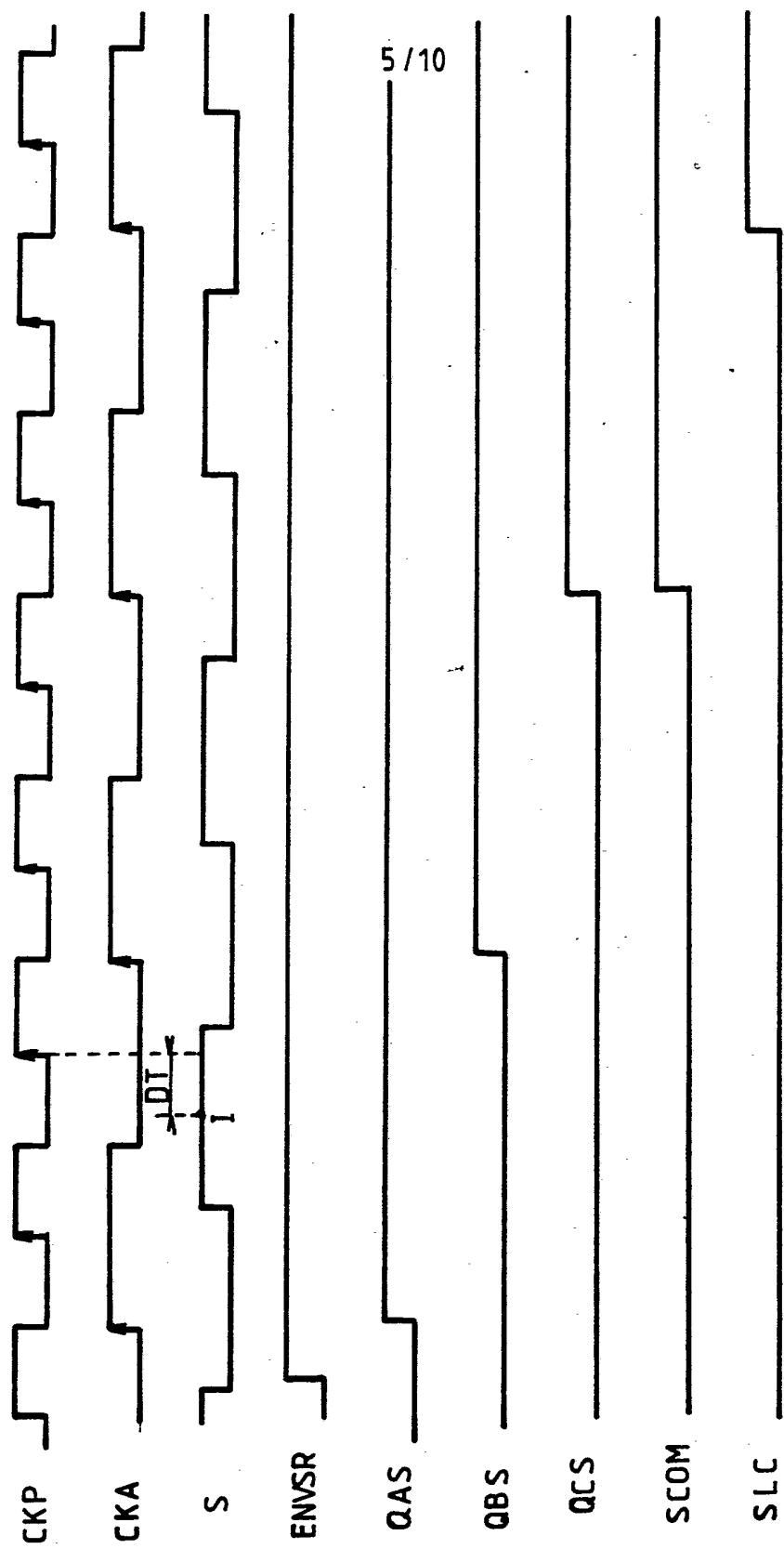

20 Afin de décrire le fonctionnement de ce dispositif de traitement on va se référer maintenant plus particulièrement à la figure 6 qui montre des diagrammes temporels permettant d'appréhender le fonctionnement des moyens de prétraitement 5. Le principe de ce fonctionnement est basé sur 25 l'utilisation du signal d'horloge auxiliaire CKA pour échantillonner le signal incident S. Comme il a été expliqué ci-avant, l'écart temporel entre le signal d'horloge principal CKP et le signal numérique S s'apprécie en examinant l'écart existant entre un point milieu I d'un état du signal S et un front montant du signal d'horloge CKP. Cependant, l'horloge auxiliaire 7 étant synchrone de l'horloge principale 3, l'écart temporel entre les deux signaux d'horloge principale et auxiliaire est connu. Ainsi en utilisant 30 le signal d'horloge auxiliaire pour échantillonner le signal numérique S on pourra évaluer l'écart temporel existant entre le signal d'horloge principal CKP et le signal numérique S. C'est pourquoi tous les constituants des moyens de prétraitement 5 sont cadencés au rythme des fronts 35

montants de l'horloge auxiliaire 7.

Il est avantageux que cette horloge auxiliaire 7 soit en phase avec l'horloge principale 3 c'est-à-dire que les fronts 5 montants du signal d'horloge principal CKP coïncident avec le point milieu I situé entre un front montant et un front descendant du signal d'horloge auxiliaire CKA. En effet, en l'absence de signal numérique S, ou avant toute décision de commutation, le commutateur 8 est mis dans son état 10 ET1. L'entrée EA de ce commutateur est donc reliée à la sortie SST des moyens de commande et donc à l'entrée de synchronisation ES. Ainsi dans cet état ET1 le signal d'horloge auxiliaire CKA joue le rôle de signal numérique d'entrée et l'écart temporel entre le signal d'horloge principal CKP et le signal d'horloge auxiliaire CKA est nul. La boucle à verrouillage de phase est donc dans un état d'équilibre stable. Un autre avantage de cet asservissement de 15 l'horloge principale sur l'horloge auxiliaire est d'empêcher une dérive en fréquence de l'horloge principale 3.

20 Dans le cas de la figure 6, l'écart temporel DT entre le signal CKP et le signal S est négatif et proche d'une demi-période du signal d'horloge CKP. Lorsque le signal numérique S arrive à l'entrée des moyens de retard 6, les deux 25 répliques R1 et R3 de ce signal vont conditionner la montée du signal ENVSR à 1. Les quatre bascules BDA à BDD qui étaient forcées à zéro lorsque le signal ENVSR était égal à zéro, ne le sont plus lorsque le signal ENVSR a la valeur 1. Au premier front montant du signal d'horloge CKA qui suit la 30 montée du signal ENVSR, le signal QAS de la bascule BDA prend la valeur 1. Le commutateur 30 est alors dans son état de repos ETB. Au front montant suivant du signal d'horloge CKA le signal QBS sortant de la bascule BDB passe à 1. Le signal QCS étant égal à 1, le signal SCET issu de 35 la porte logique NON ET 31 vaut donc 0 et fait passer le commutateur 30 dans son état de travail ETA reliant le signal de comparaison COM à l'entrée D de la bascule 13. Au front montant suivant, le signal QCS issu de la bascule BDC passe

à 1. La valeur du signal de comparaison COM est mémorisée dans la bascule 13, et est disponible en sortie de cette bascule par le signal SCOM. Le signal  $\overline{QCS}$  passe à 0 et le commutateur 30 sous l'action du signal SCET remonté à 1

5 repasse dans son état de repos ETB. Au front montant de l'horloge suivante, le signal SLC issu de la sortie QD de la bascule BDD passe à 1 et sous l'action combinée de ce signal SLC et de la valeur du signal SCOM déterminant la valeur du signal de commande SCO, le commutateur 8 passe

10 soit dans son état ET2 soit dans son état ET3. Le commutateur restera par la suite définitivement dans cet état choisi.

Le choix entre ces deux états ET2 et ET3 dépend de l'échantillonnage des répliques R2 et R4 du signal incident S dans

15 les bascules BD2 et BD4, et du résultat de cette comparaison COM à la sortie de la porte logique 11. Afin de mieux comprendre les conditions de ce choix on fait référence maintenant au diagramme temporel des figures 7A à 7D.

20 Sur la figure 7A on a représenté une réplique R2 du signal S en retard par rapport au signal de l'horloge principale CKP. L'écart temporel entre ce signal d'horloge CKP et la réplique R2 est positif et proche d'une demi-période de TH/2 du signal d'horloge CKP. La réplique R4 est en retard

25 d'une demi-période de l'horloge principale par rapport à la réplique R2. Dans cette configuration, il n'est bien entendu pas envisageable d'injecter le signal S tel quel dans l'étage de reconstitution d'horloge 2. On injectera donc la réplique R1 de ce signal numérique en avance d'un quart de période par rapport à la réplique R2 de façon à ramener cet écart temporel DT dans une plage comprise entre - TH/4 et + TH/4, ceci afin d'éviter le phénomène de "suspension". Cette configuration est déterminée par l'échantillonnage des répliques R2 et R4 par les deux bascules BD2 et

30 BD4 au front montant de l'horloge auxiliaire CKA. Ainsi,

35 dans ce cas, les valeurs de la réplique échantillonnée RE2 et de la réplique échantillonnée RE4 valent 1 et la sortie du signal COM vaut par conséquent 0.

- Sur le diagramme de la figure 7B, l'écart temporel DT est négatif et proche de 0. Ainsi qu'il sera expliqué ci-après, comme on ne peut pas déterminer si cet écart est proche de 0 ou proche de  $- TH/2$ , on injectera dans l'étage de reconstitution d'horloge 2 une réplique du signal numérique en retard d'un quart de période de l'horloge principale par rapport à cette réplique R2 de façon à amener l'écart temporel DT dans une plage comprise entre  $- TH/4$  et  $+ TH/4$ .

Dans cette configuration l'échantillonnage par le front montant de l'horloge CKA conduit à une comparaison de valeurs 0 et 1 et la sortie du signal COM est égale à 1. On injectera donc la réplique R3 dans l'étage de reconstitution d'horloge 2.

- Dans le cas représenté sur la figure 7C, où l'écart temporel DT est négatif mais proche d'une demi-période de l'horloge principale, la valeur du signal de comparaison donnera également la valeur 1 et on injectera la réplique R3 de façon à ramener l'écart temporel DT dans une plage comprise entre  $- TH/4$  et  $+ TH/4$ .

Enfin dans le cas représenté sur la figure 7D, où l'écart temporel est positif et proche de 0, la valeur du signal de comparaison sera égale à 0 et on injectera à l'entrée de synchronisation ES par l'intermédiaire de l'état ET2 du commutateur 8 la réplique R1 du signal, c'est-à-dire celle qui est en avance d'un quart de période de l'horloge principale par rapport à la réplique R2.

Ainsi que l'a compris l'homme de l'art, il peut y avoir dans certains cas une ambiguïté dans la détermination de l'écart temporel DT. Ceci est illustré par les diagrammes temporels des figures 7E et 7F. Dans le cas de la figure 7E l'écart temporel DT est positif et proche d'une demi-période de l'horloge principale. Dans ce cas, l'échantillonnage par le front montant de l'horloge CKA conduira à la comparaison des valeurs 1 et 1 dans la porte logique 11 et la valeur du signal SCOM aura la valeur 0. Dans le cas de la figure 7F l'écart temporel DT est positif et proche de 0.

Mais dans ce cas également, l'échantillonnage par le front montant de l'horloge CKA conduira à la comparaison des deux valeurs 1 et 1 dans la porte logique 11 et le signal SCOM aura la valeur 0. Bien entendu en théorie, dans le cas de 5 la figure 7F, on pouvait injecter tel quel le signal numérique incident dans l'étage de reconstitution d'horloge 2, car l'écart DT étant faible le temps de synchronisation est court. Par contre si l'on effectuait cette opération sans précaution dans le cas de la figure 7E, on aboutirait 10 à un phénomène de "suspension". Pour lever cette indétermination on choisira donc d'injecter une réplique telle que, dans tous les cas, l'écart temporel entre le signal d'horloge principal et le signal numérique incident soit compris entre  $- TH/4$  et  $+ TH/4$ , ce qui conduit à injecter la réplique R1. Dans ce mode de réalisation donc, il est absolument 15 nécessaire que les moyens de retard fournissent quatre répliques du signal incident.

On a donc bien réalisé par ces moyens de prétraitement 20 5 un dispositif permettant une synchronisation rapide de l'horloge principale par rapport au signal numérique incident et ce quel que soit l'écart temporel entre le signal d'horloge principal et le signal numérique, notamment à haut débit.

25 Le fonctionnement de la boucle à verrouillage de phase 2 va maintenant être illustré en se référant aux figures 8A à 8C. Sur la figure 8A, on a représenté un diagramme temporel du signal numérique prétraité ST arrivant sur l'entrée ES et donc sur l'entrée E1 de la boucle à verrouillage de phase. Ce signal est en phase avec le signal d'horloge principal CKP. Autrement dit l'écart temporel DT est nul. Après échantillonnage dans la bascule 22, on obtient la sortie échantillonnée STE1; après passage dans les moyens de retard supplémentaires 21, on obtient la réplique retardée du signal numérique RST1 et l'échantillonnage de la sortie STE1 donne le signal STE2. Après comparaison dans les portes logiques 30 35 24 et 25 on obtient les signaux de comparaison C1 et C2

et finalement la différence ( $C_1 - C_2$ ) représentée par le signal de commande d'horloge SCD.

On remarque d'une part, donc que la valeur moyenne du signal SCD est nulle ce qui ne produit aucun effet sur l'horloge principale 3 celle-ci restant en phase avec le signal ST. D'autre part on remarque que, dans le signal numérique ST, il n'y a pas de transition au niveau du point 0. Cette absence de transition se retrouve dans le signal SCD 10 au niveau de l'intervalle repéré 0 et sur lequel le signal SCD est nul. On n'agit donc pas sur l'horloge principale ce qui évite de déstabiliser la boucle à verrouillage de phase.

15 Sur la figure 8B, on a représenté un signal ST en avance par rapport au signal d'horloge CKP (DT est négatif). On retrouve d'une façon analogue les signaux STE1, RST1, STE2, C1, C2 et SCD. On remarque alors que la valeur moyenne du signal SCD est négative et cette valeur moyenne sera d'autant 20 plus importante en valeur absolue que l'écart temporel DT entre le signal d'horloge CKP et le signal numérique ST présent à l'entrée de synchronisation est importante. On remarque également que, comme il n'y a pas de transition au point 0, la valeur du signal SCD dans l'intervalle repéré 25 0 est nulle.

Sur la figure 8C on a représenté un signal ST en retard par rapport au signal de l'horloge CKP (DT est positif). D'une façon analogue on retrouve tous les signaux des figures 8A et 8B et l'on remarque alors que la valeur moyenne du signal SCD est positive ce qui contribuera à réduire cet écart temporaire. L'absence de transition au point 0 se traduit toujours par un signal SCD nul sur l'intervalle repéré 0. D'une façon analogue la valeur moyenne du signal 30 SCD est d'autant plus importante que l'écart temporel DT 35 est important en valeur absolue.

L'homme de l'art comprendra donc que l'on a bien réalisé

ici un dispositif permettant d'une part de corriger l'écart temporel entre le signal d'horloge CKP par rapport au signal numérique incident S, mais également, d'autre part, de ne pas perturber la boucle à verrouillage de phase lors d'une absence de transition dans le signal numérique à l'entrée de cette boucle à verrouillage de phase.

L'invention peut admettre des variantes, notamment les suivantes:

- dans le mode de réalisation préféré ci-dessus décrit, le choix des répliques à échantillonner peut bien sûr varier. La seule condition est de prendre deux répliques décalées temporellement l'une par rapport à l'autre d'une demi-période de l'horloge principale. De même le choix des deux répliques permettant de détecter l'absence ou la présence d'un signal numérique incident est quelconque.

- On a vu précédemment que quatre sorties des moyens de retard 6 étaient nécessaires pour pallier l'ambiguïté dans la détermination de l'écart temporel entre le signal d'horloge principal et le signal numérique incident. Ceci était nécessaire car l'horloge auxiliaire 7 opérait à une fréquence sensiblement moitié de celle de l'horloge principale 3. Cependant on pourrait envisager la réalisation de moyens de prétraitement avec des moyens de retard ne comprenant que deux sorties seulement, fournissant deux répliques décalées temporellement l'une par rapport à l'autre d'une demi-période de l'horloge principale, mais en utilisant dans ce cas alors une horloge auxiliaire opérant à fréquence sensiblement double de celle de l'horloge principale.

En effet la résolution d'écart temporel que l'on obtenait avec des moyens de retard ayant quatre sorties est maintenant réduite de moitié. Il faut donc compenser cette perte de résolution "spatiale" par une augmentation de résolu-

tion "temporelle" que l'on obtient en multipliant par quatre la fréquence de l'horloge auxiliaire. Ce nouvel agencement nécessiterait non seulement d'échantillonner les deux répliques du signal incident, mais également d'échantillonner à l'aide du signal d'horloge auxiliaire, le signal d'horloge principal afin de lever l'ambiguïté dans la détection de phase. Dans ce cas on pourrait envisager, (puisque, en l'absence de signal ou en l'absence de décision de commutation, le signal d'horloge auxiliaire doit asservir l'horloge principale 3), que l'horloge auxiliaire 7 comprenne une source de fréquence double de celle de l'horloge principale suivie d'un diviseur.

Bien entendu on pourrait généraliser cet agencement en utilisant une source de fréquence multiple de celle de l'horloge auxiliaire suivie d'un diviseur. Cet agencement de l'horloge auxiliaire pourrait d'ailleurs être appliqué même dans le cas de moyens de retard utilisant quatre sorties.

## Revendications.

1. Dispositif de traitement d'un signal numérique incident, véhiculant, en bande de base, des messages codés par une succession d'états hauts et/ou bas sur une horloge de transmission, comportant:

5

- une entrée de réception (1) du signal numérique incident.

- un étage de reconstitution d'horloge (2) comprenant une horloge principale ajustable (3), de fréquence nominale

10 reliée à celle de l'horloge de transmission, et une entrée de synchronisation (ES) de cette horloge principale (3), susceptible d'être reliée à l'entrée de réception (1),

- caractérisé en ce qu'il comporte, en outre, des moyens

15 de prétraitement (5) comprenant:

- un commutateur (8) à trois états (ET1, ET2, ET3), dans chacun desquels il relie respectivement sa première (EA),

20 sa deuxième (EB) et sa troisième (EC) entrée à ladite entrée de synchronisation (ES),

- des moyens de retard (6) interposés entre l'entrée de réception (1) et le commutateur (8), et propres à fournir respectivement aux deuxième (EB) et troisième (EC) entrées

25 du commutateur (8) au moins une première paire de répliques (R1, R3) du signal incident (S) différentes, ces deux répliques (R1, R3) étant décalées temporellement l'une par rapport à l'autre d'une fraction de période de l'horloge principale (3),

30

- une horloge auxiliaire (7), opérant à une fréquence pré-déterminée choisie pour autoriser son application à la première entrée du commutateur (8), aux fins de synchroniser l'horloge principale, et

35

- des moyens de commande (9) sensibles à la présence d'un

signal numérique incident pour:

- en l'absence de signal incident (S), mettre le commutateur (8) dans son premier état (ET1), l'horloge principale (3) étant alors synchronisée sur l'horloge auxiliaire (7),

- en présence d'un signal incident (S) mettre le commutateur (8) dans son deuxième état (ET2) ou son troisième état (ET3) en fonction de la situation temporelle de l'horloge auxiliaire (7) relativement au signal incident (S).

2. Dispositif selon la revendication 1, caractérisé en ce que ledit décalage temporel entre les répliques est sensiblement égal à une demi-période de l'horloge principale.

3. Dispositif selon l'une des revendications 1 et 2, caractérisé en ce que, en présence d'un signal incident (S), les moyens de commande (9) mettent le commutateur (8) dans son deuxième (ET2) ou son troisième (ET3) état en fonction de la situation temporelle de l'horloge auxiliaire (7) relativement à ladite première paire de répliques (R1, R3).

4. Dispositif selon l'une des revendications 1 et 2, caractérisé en ce que les moyens de retard (6) sont propres à fournir une deuxième paire de répliques (R2, R4) du signal incident, différentes des répliques (R1, R3) de la première paire et également décalées l'une par rapport à l'autre de ladite fraction de période de l'horloge principale (3), l'une des répliques de cette deuxième paire étant décalée temporellement par rapport à chacune des deux répliques (R1, R3) de la première paire sensiblement de la moitié de ladite fraction de période de l'horloge principale,

- en ce que, en présence d'un signal incident (S), les moyens de commande (9) mettent le commutateur dans son deuxième (ET2) ou son troisième (ET3) état en fonction de la situa-

tion temporelle de l'horloge auxiliaire (7) relativement à cette deuxième paire de répliques (R2, R4) du signal incident (S).

- 5 5. Dispositif selon l'une des revendications 3 et 4, caractérisé en ce que les moyens de commande (9) comprennent, d'une part, des moyens échantillonneurs (10), pour échantillonner à la fréquence de l'horloge auxiliaire (7), simultanément et séparément, chacune des répliques (R2, R4) de la paire relativement à laquelle est déterminée la situation temporelle de l'horloge auxiliaire (7), d'autre part, des moyens de comparaison (11) de ces répliques échantillonnées (RE2, RE4) fournissant un signal de comparaison (COM) représentatif des valeurs de ces répliques (R2, R4).

15

- 10 6. Dispositif selon l'une des revendications 3 à 5, caractérisé en ce que les moyens de commande (9) comprennent, en outre, une logique de commande (12), commandée à la fréquence de l'horloge auxiliaire (7), et des moyens de mémorisation (13) de la valeur respective des deux répliques (R2, R4) de la paire relativement à laquelle est déterminée la situation temporelle de l'horloge auxiliaire (7), la sortie (SCOM) de ces moyens de mémorisation (13) et une sortie (SLC) de la logique de commande (12) faisant partie d'un signal de commande (SCO) pour le commutateur (8).

20

- 25 7. Dispositif selon la revendication 6, caractérisé en ce que les moyens échantillonneurs (10), les moyens de mémorisation (13) et la logique de commande (12) comprennent des bascules-mémoires (BD).

30

- 35 8. Dispositif selon l'une des revendications précédentes, caractérisé en ce que la présence ou l'absence de signal (S) sont évaluées par des moyens de détection (14) recevant deux répliques distinctes (R1, R3) fournies par les moyens de retard (6).

9. Dispositif selon la revendication 8; caractérisé en ce que les moyens de détection (14) comprennent des moyens de comparaison supplémentaires (15), recevant les deux répliques (R1, R3), et dont la sortie est reliée à un monostable redéclenchable (16) dont la durée minimale est égale au moins au temps maximum séparant deux transitions successives du signal numérique (S).

10. Dispositif selon l'une des revendications précédentes, caractérisé en ce que l'étage de reconstitution d'horloge (2) est agencé en une boucle à verrouillage de phase.

11. Dispositif selon la revendication 10, caractérisé en ce que l'étage de reconstitution d'horloge (2) comprend un étage détecteur de phase (20) possèdant une première entrée (E1) reliée à l'entrée de synchronisation (ES), une deuxième entrée (E2) reliée à l'horloge principale (3), et une sortie (SO) délivrant un signal de commande d'horloge (SCD), dont la valeur moyenne est sensiblement proportionnelle à l'écart temporel entre le signal d'horloge principal (CKP) et le signal numérique (ST) présent à l'entrée de synchronisation, et dont l'amplitude est sensiblement nulle en l'absence de transition du signal numérique (ST) présent à l'entrée de synchronisation (ES).

25 12. Dispositif selon la revendication 11, caractérisé en ce que l'étage détecteur de phase (20) comprend des moyens de retard supplémentaires (21), reliés à la première entrée (E1) et délivrant une réplique (RST1) du signal numérique (ST) présent à l'entrée de synchronisation, décalée sensiblement d'une période de l'horloge principale (3), un premier échantillonneur (22) du signal (ST) présent à l'entrée de synchronisation (ES), un second échantillonneur (23) de la sortie (STE1) du premier échantillonneur (22), ladite réplique (RST1), étant, d'une part, comparée (C1) à la sortie (STE1) du premier échantillonneur (22) et, d'autre part (C2) à la sortie (STE2) du deuxième échantillonneur (23), la différence des valeurs de ces deux comparaisons (C1, C2)

fournissant le signal de commande d'horloge (SCD).

13. Dispositif selon l'une des revendications précédentes, caractérisé en ce que l'horloge auxiliaire (7) comprend une source de fréquence multiple de la fréquence de l'horloge auxiliaire suivie d'un diviseur, ce qui permet de traiter le signal numérique incident (S) avec seulement deux répliques de ce signal (S).

14. Dispositif selon l'une des revendications précédentes, caractérisé en ce que le signal numérique incident (S) commence par une succession d'états alternativement hauts et bas.

1 / 10

FIG.1FIG.2

2/10

FIG.3

3 / 10

FIG.4

4 / 10

FIG.5

2623675

FIG. 6

6 / 10

FIG.7A

FIG.7B

FIG.7C

FIG.7D

7 / 10

FIG.7E

FIG.7F

8 / 10

FIG.8A

9/10

FIG. 8B

2623 675

10/10