(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-508409

(P2006-508409A)

(43) 公表日 平成18年3月9日(2006.3.9)

(51) Int.C1.

G06F 13/362 (2006.01)

G06F 1/04 (2006.01)

F 1

G06F 13/362 510 D

G06F 1/04 301 C

テーマコード(参考)

5B061

5B079

審査請求 未請求 予備審査請求 有 (全 29 頁)

(21) 出願番号 特願2003-575244 (P2003-575244)

(86) (22) 出願日 平成15年3月5日 (2003.3.5)

(85) 翻訳文提出日 平成16年9月29日 (2004.9.29)

(86) 國際出願番号 PCT/US2003/007107

(87) 國際公開番号 WO2003/077094

(87) 國際公開日 平成15年9月18日 (2003.9.18)

(31) 優先権主張番号 10/094,053

(32) 優先日 平成14年3月8日 (2002.3.8)

(33) 優先権主張国 米国(US)

(71) 出願人 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国テキサス州78729, オ

ースティン, ウエスト・パーマー・レーン

7700

(74) 代理人 100116322

弁理士 桑垣 衛

(72) 発明者 モイヤー、ウイリアム シー.

アメリカ合衆国 78620 テキサス州

ドリッピング スプリングス ピア ブ

ランチ ロード 1005

最終頁に続く

(54) 【発明の名称】データ処理システムを低電力化するシステムおよび方法

## (57) 【要約】

低電力装置の復帰可能な状態を特定するシステムおよび方法について説明する。複数のバスマスターへのシステムバスアクセスを許可するアービタ(110、310、または410)を有する低電力装置(100、300、または400)が、低電力動作モードを起動するように設定される。低電力装置内の低電力コントローラ(150、350、または450)は、低電力モードを起動する要求をバスアービタに与える。バスアービタは、バスマスターへのバス要求の許可を停止し、システムバスが現在のバスアクセスをすべて処理する時期を特定する。システムバスがアイドル状態になると、バスアービタは、低電力コントローラにバス許可信号を返す。バスマスターに関連するクロックは、ディスエーブルされてバスアービタを一時停止するとともに、低電力装置の低電力化を可能にする。

## 【特許請求の範囲】

## 【請求項 1】

低電力モードへの移行を判定するステップと、

前記低電力モードへの移行の判定に応答して、アービタ(110、310、または410)にバス要求を与えるステップと、

前記バス要求に応答して、前記アービタに関連する第1のバスマスター(120または130)の少なくとも一部に与えられた第1のクロックをディスエーブルするステップと、

から成る方法。

## 【請求項 2】

前記バス要求に応答して、前記アービタに関連する第2のバスマスターの少なくとも一部に与えられた第2のクロックをディスエーブルするステップをさらに含む、請求項1記載の方法。 10

## 【請求項 3】

前記バス要求に関連するバス許可信号を受け取るステップをさらに含む、請求項1記載の方法。

## 【請求項 4】

前記第1のクロックをディスエーブルするステップは、前記バス許可信号を受け取るステップに応答して行なわれる、請求項3記載の方法。

## 【請求項 5】

前記バス許可信号を受け取るステップに応答して、前記第1のバスマスターに加え、システムの第1の部分への電力を低減するステップをさらに含む、請求項3記載の方法。 20

## 【請求項 6】

電力モードを示すレジスタ(152、352、または452)と、

前記レジスタに接続され、電力モードをモニタすると共に、定格電力モードとは異なる低電力モードが示された場合に、第1のバスマスターおよび第2のバスマスターの少なくとも一方に関連するバス要求の処理を防止する、アービタ(110、310、または410)と、

から成るシステム。

## 【請求項 7】

前記アービタは、前記低消費電力モードが特定された場合に低電力バス要求を処理するとともに、低電力バス要求が発生された後に、前記バスマスターのバス要求のうちの少なくとも1つの処理を防止する請求項6記載のシステム。 30

## 【請求項 8】

前記アービタは、前記第1のバスマスターおよび第2のバスマスターの少なくとも一方の少なくとも一部に与えられたクロック信号をディスエーブルする、請求項6記載のシステム。

。

## 【請求項 9】

複数の切り替えられるシステムバス(179)と、

第1のバスマスター(120または130)と、

第2のバスマスター(120または130)と、

1つが複数の切り替えられるシステムバスの各1つに関連付けられている、複数のアービタ(110、310、または410)と、

40

制御モジュール(150、350、または450)と、から成るシステムであって、制御モジュール(150、350、または450)が、

電力モードを特定し、

前記電力モードが定格電力モードよりも低い場合に、前記複数のアービタのサブセットにバス要求を提供し、

前記複数のアービタの前記サブセットから、前記バス要求に関連するバス許可を受け取り、

前記第1のバスマスターまたは第2のバスマスターの少なくとも一方に関連するクロック 50

をディスエーブルするものである、システム。

【請求項 10】

前記制御モジュールは、前記バス許可の受け取りに基づいて、低電力モードを示す信号を与えるのにさらに使用される、請求項 9 記載のシステム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般に半導体装置に関し、特に半導体装置の低電力モードを実現するシステムおよび方法に関する。

【背景技術】

【0002】

低電力の携帯機器の使用が次第に一般的になっている。例えば、セル式電話機、携帯情報端末（PDA）等の携帯端末は、ますます普及している。多くのマイクロプロセッサ装置が、電力節約に対処すべく、1つまたは2つ以上の低電力状態を備えるように設計されている。電力の節約により、バッテリ寿命を延ばすことができるので、携帯端末をさらに長時間動作させることができる。

【0003】

最新のマイクロコントローラおよびマイクロプロセッサにおける、低電力状態を実現する1つの方法は、低電力命令を与えることである。低電力命令の実行により、装置は、シャットダウンシーケンスを初期化でき、それによって、装置は、装置が低電力状態からその後復帰できるような方法によって、シャットダウンに対する準備をする。例えば、低電力マイクロプロセッサがメモリアクセスサイクル中にシャットダウンされる場合、プロセッサをメモリのような外部装置よりも前にディスエーブル（disable）して、要求されたデータを戻すことができるであろう。プロセッサが、起動後すぐにこれらの終了サイクルの発生を予期している場合、プロセッサは、発生しないメモリアクセスを事前に察しているので、それは装置を異常停止させてしまう。しかし、低電力命令を実行することによって、公知の方法で低電力モードに移行した後に動作を終了するような方法で、プロセッサに関連するマシンをシャットダウン状態にすることができる。

【0004】

多くのマイクロプロセッサコアが、既知条件の低電力状態に移行する低電力命令の使用をサポートしているが、そのような命令の使用および他の方法は、すべてのマイクロプロセッサコアで普遍的に利用可能というわけではない。そのようなマイクロプロセッサコアを低電力装置で使用することが望ましい場合、低電力動作モードに移行する代替方法が定義される必要がある。また、DMA装置および他のシステム機能ブロックのようなバスマスター装置は、低電力モード命令を直接実行しなくてもよく、同様の明白な方法によってそのような装置を低電力状態に移行させることができ、低電力システムの要件でもある。したがって、効率的な方法で低電力動作モードに移行できることが有用である。

【発明を実施するための最良の形態】

【0005】

本開示の特定の実施形態を本明細書で提示した図面に示し、説明する。本開示の種々の目的、利点、特徴、および特性のみならず、他の方法、関連する構成要素の動作および機能、ならびに製造上の部品の組み合わせおよび経済性が、そのすべてがこの明細書の一部を構成する、添付の図面に関する以下の説明および請求項を考慮することによって、明らかにされるであろう。

【0006】

本発明の少なくとも1つの実施形態は、装置を低電力動作モードに移行させる方法を提供する。低電力コントローラが、バスアービタ（bus arbiter）に、低電力モードを起動するバス要求を行う。その要求は、バスアービタによって受け取られた他の要求よりも高い優先順位で処理される。バスアービタは、インターフェース接続されたバスマスターからの新しい要求の承認を停止し、システムバスが現在のバスアクセスを処理し終え

10

20

30

40

50

るまで待つ。いったん、システムバスがアイドル状態になると、バスアービタは、低電力コントローラのバス要求を承認し、これはシステムが低電力動作モードを自由に取れることを示す。一実施形態において、バスアービタに関連するバスマスターが一時停止され、低電力消費を可能にする。本発明の特定の実施形態において、バスアービタは、低電力コントローラにバス許可信号を返し、低電力コントローラが低電力動作モードを自由に取れることを示す。この方法によって、バスマスターとしても作動する装置を復帰可能な状態に移行させることができ、そのような装置は、バスアービタのサポートによって安全な低電力モードに容易にシャットダウンされる。

#### 【0007】

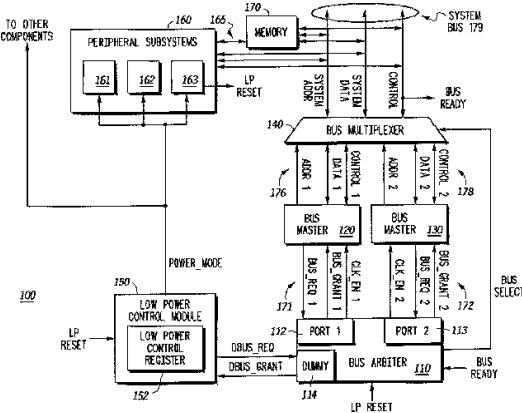

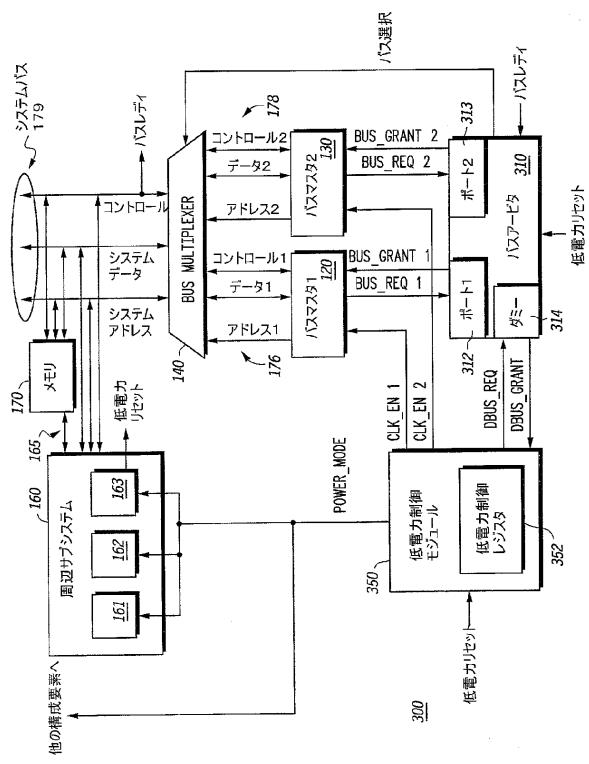

図1に低電力装置100の一部を示す。このような低電力装置の特定の例としては、携帯型PDA、電話機を始めとする携帯型通信装置、ラジオ、および他の装置を挙げることができる。低電力装置100は、バスアービタ110、バスマスター120、バスマスター130、バスマルチプレクサ140、低電力制御モジュール150、周辺サブシステム160、およびメモリ170を備えている。

#### 【0008】

バスアービタ110は、次の信号を与える：バスマスター120へのバス許可1（bus\_grant1）およびクロックイネーブル1（clk\_en1）信号、バスマスター130へのクロックイネーブル2（clk\_en2）およびバス許可2（bus\_grant2）信号、バスマルチプレクサ140へのバス選択信号、低電力制御モジュール150への低電力バス許可（dbus\_grant）信号。バスマスター120は、次の信号を与える：バスマルチプレクサ140に接続された双方向バス176へのアドレス1（addr1）、データ1（data1）、およびコントロール1信号、バスアービタ110へのバス要求1（bus\_req1）信号。バスマスター130は、次の信号を与える：バスマルチプレクサ140との間にあるバス178へのアドレス2、データ2、およびコントロール2信号、バスアービタ110へのバス要求2（bus\_req2）信号。ハンドシェイクコントロール171は、バスマスター120に関連し、バスアービタ110の第1のポート112にインタフェース接続されているが、バス要求1と、バス要求1に応答してバスアービタ110によって与えられるバス許可1（bus\_grant1）と、バスマスター120のクロックをイネーブルまたはディスエーブルするのに使用されるクロックイネーブル1（clk\_en1）とを含む。同様に、ハンドシェイクコントロール172は、バスマスター130に関連し、バスアービタ110の第2のポート113にインタフェース接続されているが、バス要求2と、バス要求2に応答してバスアービタ110によって提供されるバス許可2（bus\_grant2）と、バスマスター130のクロックをイネーブルまたはディスエーブルするのに使用されるクロックイネーブル2（clk\_en2）とを含む。バスマルチプレクサ140は、バスマスター120およびバスマスター130にそれぞれ関連する各ローカルシステムバス176および178との間で情報の送受信を行う。さらに、バスマルチプレクサ140は、システムバス179との間で情報の送受信を行う。低電力制御モジュール150は、バスアービタ110への低電力バス要求（dbus\_req）と、周辺サブシステム160、および低電力装置100の残りの部分への電力モードインジケータ（power\_mode）とを与える。周辺サブシステム160は、バスインタフェース165を介してメモリ170にインタフェース接続するとともに、低電力制御モジュール150に低電力リセット（lp\_reset）を与える。メモリ170は、システムバス179およびバスインタフェース165を介して周辺サブシステム160にインタフェース接続している。周辺サブシステム160も、システムバス179に接続している。

#### 【0009】

動作の際、低電力制御モジュール150が、低電力装置100の低電力モードを起動する。低電力制御モジュール150は、低電力制御レジスタ152を含んでいる。一実施形態において、低電力制御モジュール150は、低電力制御レジスタ152の値に基づいて、低電力装置100が低電力モードに設定されるべき時期を判定する。低電力装置100

10

20

30

40

50

が低電力モードに移行するとき、低電力制御レジスタ152は設定される。例えば、ユーザがキーパッド（図示されない）を始めとするユーザインターフェースを作動していない場合に、低電力装置100のユーザ動作をモニタするアプリケーション（図示されない）または周辺サブシステム160のサブシステムが、低電力制御レジスタ152を設定できる。代替的に、低電力装置100に電力を供給するのに使用されるパワーセル（図示しない）が低電力になり、低電力装置100が低電力モードに移行できる場合に、低電力制御レジスタ152を設定してもよい。したがって、ユーザはパワーセルを交換するのに、または所望のデータをバックアップするのに必要な手段を講じる時間を持つことができる。さらに、いくつかの実施形態において、低電力制御レジスタ152は、バス転送によって低電力制御レジスタ152へのアクセスを可能にするために、システムバス179にインターフェース接続されていてもよい。

10

#### 【0010】

いったん、低電力制御レジスタ152が設定されたことを低電力制御モジュール150が検出すると、低電力制御モジュール150は、バスアービタ110に低電力バス要求（`bus_req`）を与えることができる。低電力バス要求は、バスアービタ110に与えられるバス要求信号を表し、該低電力バス要求は、システムバス179へのアクセスに使用されるのではなく、バスアービタ110へ指示を与えるのに使用される。同様に、バスアービタ110によって与えられる低電力バス許可信号（`bus_grant`）は、低電力バス要求を承認するために使用される。一実施形態において、低電力制御モジュール150は、バスアービタ110に低電力バス要求`bus_req`をアサートした後、バスアービタ110からの低電力バス許可信号`bus_grant`信号の受け取りを待つ。

20

#### 【0011】

低電力制御モジュール150が`bus_grant`信号を受け取ると、低電力制御モジュール150は、電力モードインジケータを与えて、周辺サブシステム160、および低電力装置100の他の部分を低電力状態に移行させることができる。一実施形態において、低電力制御モジュール150は設定を適用して、周辺サブシステム160に与えられる電力を低減する。一実施形態において、低電力制御モジュール150は、低電力装置100が低電力モードから定格電力モードに移行されるべきことを指示する低電力リセット信号（`LP_RESET`）を待つ。したがって、低電力制御モジュール150は、低電力リセット信号に応答して、周辺サブシステム160を通常動作モードに復帰させることができる。定格電力モードは、低電力装置100の一般的な機能が利用可能な通常動作モードを表わしている。さらに、通常動作モード中、低電力装置100は、低電力動作モード中に消費される電力量よりも大きな、通常の電力量を消費し得る。本発明の範囲から逸脱することなく、低電力モードを特定する他の方法を利用できることが理解されるべきであろう。さらに、低電力制御モジュール150は、ここに説明した以外の手段を講じて、低電力装置100を低電力モードに移行させることができる。さらに、本発明の範囲または精神から逸脱することなく、低電力リセット（`LP_RESET`）ではなく、低電力モードを終了すべきことを示す代替の手段を使用してもよい。

30

#### 【0012】

バスアービタ110は、バスマスター120、バスマスター130、および低電力制御モジュール150のような複数のリクエスタからの要求を受け取り、リクエスタの1つ、すなわちバスマスター120や130が、システムバス179にアクセスするのを許可するために使用される。一実施形態において、バスアービタ110は、アービトレーション方式を利用して、バスマスター120に関連する第1のポート112、またはバスマスター130に関連する第2のポート113のいずれか一方からのバスアクセス要求を認識する。例えば、バスアービタ110は、バスアービタ110が第1のポート112または第2のポート113からの複数の許可要求を交互に認識するラウンドロビンアービトレーション（`round-robin arbitration`）を利用できる。いったんポートが選択されると、バスアービタ110の第1のポート112または第2のポート113は、バスマ

40

50

スタ 1 2 0 またはバスマスター 1 3 0 のような関連するバスマスターに、バス許可信号、すなわちバス許可 1 またはバス許可 2 をそれぞれ与える。一実施形態において、バスマスター 1 0 は、バスマルチプレクサ 1 4 0 へも制御信号を与え、アドレス、データ、およびコントロール信号のような情報を、選択されたポート（すなわち第 1 のポート 1 1 2 または第 2 のポート 1 1 3 ）に関連する利用可能なバスマスターの 1 つ（すなわちバスマスター 1 2 0 またはバスマスター 1 3 0 ）からそれぞれ受け取る。バスマスター 1 2 0 およびバスマスター 1 3 0 は、バスマスター装置を表わす。例えば、バスマスター 1 2 0 および 1 3 0 は、中央処理装置（C P U）のような低電力装置 1 0 0 に組み込まれたプロセッサを含むことができる。バスマスター 1 2 0 および 1 3 0 は、ダイレクトメモリーアクセス（D M A）エンジンまたは他のプロセッサを含むこともできる。

10

## 【 0 0 1 3 】

一実施形態において、バスアービタ 1 1 0 は、低電力制御モジュール 1 5 0 から低電力バス要求信号を受け取る低電力ポート 1 1 4 を含んでいる。バスアービタ 1 1 0 は、追加のリクエスターとしての低電力制御モジュール 1 5 0 からの要求を処理できる。例えば、バスアービタ 1 1 0 は、第 1 のポート 1 1 2 、第 2 のポート 1 1 3 、および低電力ポート 1 1 4 によって受け取られた複数の要求の間の仲裁を行う（arbitrate）ことができる。一実施形態において、バスアービタ 1 1 0 が低電力バス要求信号を受け取ると、バスアービタ 1 1 0 は、バスレディ信号を待つ。バスレディ信号は、システムバス 1 7 9 によって使用される信号であって、システムバス 1 7 9 上の未処理要求が処理された時期を示す信号である。いったんバスレディ信号が受け取られると、バスアービタ 1 1 0 は、低電力制御モジュール 1 5 0 に、低電力装置 1 0 0 を低電力モードに設定できることを示す低電力バス許可信号を与えることができる。

20

## 【 0 0 1 4 】

図示の実施形態において、バスアービタ 1 1 0 が低電力制御モジュール 1 5 0 に低電力バス許可信号を与えるとき、バスアービタ 1 1 0 は、クロックイネーブル信号、すなわちクロックイネーブル 1 およびクロックイネーブル 2 をも利用して、バスマスター 1 2 0 およびバスマスター 1 3 0 に関連するクロックをそれぞれディスエーブルする。一実施形態において、いったんシステムバス 1 7 9 が未処理要求を処理してしまうと、バスマスター 1 2 0 および 1 3 0 は、システムバス 1 7 9 からの応答を待っていない状態になるので、バスマスター 1 2 0 および 1 3 0 は、復帰可能な状態にあると考えられる。バスアービタ 1 1 0 は、低電力動作のために、バスマスター 1 2 0 および 1 3 0 へのクロックをディスエーブルすることによって、バスマスター 1 2 0 および 1 3 0 をこの復帰可能な状態に維持できる。さらに、バスアービタ 1 1 0 は、第 1 のポート 1 1 2 および第 2 のポート 1 1 3 からのさらなる要求が承認されない運転モードを起動することができる。バスアービタ 1 1 0 は、低電力リセット信号がアサートされて通常動作モードに戻るべき時期を決定するまで待機することができる。したがって、低電力リセット信号がアサートされると、バスアービタ 1 1 0 は、クロックイネーブル 1 およびクロックイネーブル 2 信号を使用して、バスマスター 1 2 0 および 1 3 0 へのクロックを再イネーブルでき、第 1 のポート 1 1 2 および第 2 のポート 1 1 3 から受け取った複数の要求の間の仲裁処理に戻ることができる。

30

## 【 0 0 1 5 】

代替の実施形態において、バスアービタ 1 1 0 は、低電力リセット信号 L P R E S E T に直接応答しなくてもよく、その代わりに、低電力動作モードがもはや望まれておらず通常モードへの復帰が発生すべきことを示すポート 1 1 4 を介した低電力バス要求のネガーション（negation）を待っているだけでもよい。

40

## 【 0 0 1 6 】

一実施形態において、バスアービタ 1 1 0 は、さらに、受け取った要求の優先順位を付けることができる。例えば、できるだけ早く低電力モードに入ることが望ましいとする。その場合、バスアービタ 1 1 0 は、バスマスター 1 2 0 およびバスマスター 1 3 0 からの新しい要求を無視して、順番を変えて低電力ポート 1 1 4 からの低電力バス要求を処理できる。バスマスター 1 2 0 および 1 3 0 からのバスアクセス要求よりも高い優先順位を低電力制

50

御モジュール150からの低電力バス要求に与えることによって、バスアービタ110は確実に、低電力モードを速やかに実行可能にする。優先順位は、低電力装置100の要望に応じて変更できる。例えば、それほど厳格でない低電力動作が望ましい場合、低電力ポート114を通して受け取られた低電力バス要求の優先順位は、バスマスター120からの要求よりも低いけれどもバスマスター130からの要求よりも高いというようにすることできる。代替的に、低電力ポート114に関連する優先順位を、固定優先順位に設定することもできる。

#### 【0017】

バスマルチプレクサ140は、バスマスター120および130にそれぞれ関連するローカルバス176および178を、システムバス179に接続するために使用される。一実施形態において、バスマルチプレクサ140によって選択されるバスマスターは、バスアービタ110によって与えられるバス選択信号によって特定される。例えば、バス選択信号が、バスマスター120が選択されるべきことを指示すれば、バスマルチプレクサ140は、システムバス179のシステムアドレス、システムデータ、およびコントロール線に、ローカルバス176からのアドレス1、データ1、およびコントロール1の信号線をそれぞれ接続する。代わりに、バス選択信号が、バスマスター130が選択されるべきことを指示すれば、バスマルチプレクサ140は、システムバス179のシステムアドレス、システムデータ、およびコントロール線に、ローカルバス178のアドレス2、データ2、およびコントロール2の信号線を接続できる。

#### 【0018】

システムバス179は、バスマスター120および130を、メモリ170、周辺サブシステム160、および他のシステム構成要素（図示されない）に接続するために使用できる。したがって、バスマスター120および130は、システムバス179に接続されたメモリ170および周辺装置160のような低電力装置100の構成要素に書き込み（write）、または読み出し（read）すべきデータを与えることができる。一実施形態において、システムバス179に沿って送信されたアドレス情報およびデータはインタリープされる。システムバス179のシステムアドレス線上で送信されるアドレスは、システムバス179のシステムデータ線からのデータの次の群に書き込むバスアドレスを示している。データがシステムデータ線上でアクセスされている間、新しいアドレスは、データの新しい群の新しいアドレスを示すシステムアドレス線上に置くことができる。本発明の範囲から逸脱することなく、システムバス179のようなシステムバスに沿ったアドレス情報およびデータを通す他の形態を組み込めることは十分に理解されるべきであろう。

#### 【0019】

周辺サブシステム160は、システムバス179に接続されるとともに、バスインターフェース165を介してメモリ170に接続できる。周辺サブシステム160は、低電力装置100のクロスセクションを処理するためのいくつかの構成要素を含んでいる。例えば、第1のサブシステム161は、低電力装置100の映像を処理するために使用できる。第2のサブシステム162は、低電力装置100の音声を処理するために使用できる。さらに、第3のサブシステム163は、キーパッドへのユーザ入力のようなユーザインターフェースを処理するために使用できる。サブシステム161～163は、低電力制御モジュール150によって与えられた低電力モードインジケータに応答して、パワーダウンモードに移行させることができる。パワーダウンされることをすべてのサブシステムが望んでいるとは限らないことは十分に理解されるべきであろう。例えば、サブシステム163は、低電力モードの間にユーザ入力をモニタするのに使用できる。その場合、ユーザがキーパッドを軽く叩くような方法で低電力装置100へのアクセスを試みると、第3のサブシステム163は、低電力リセット信号をアサートして、低電力装置100を低電力モードから復帰させ、通常動作モードに戻すことができる。周辺サブシステム160に関して説明したシステムに加えて、またはその代わりに、他のサブシステムが使用できることは十分に理解されるべきであろう。さらに、本発明の範囲から逸脱することなく、低電力モードから復帰する時期を検出する他の手段を使用できる。

10

20

30

40

50

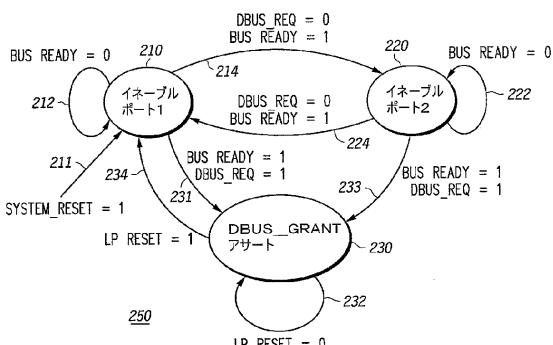

## 【0020】

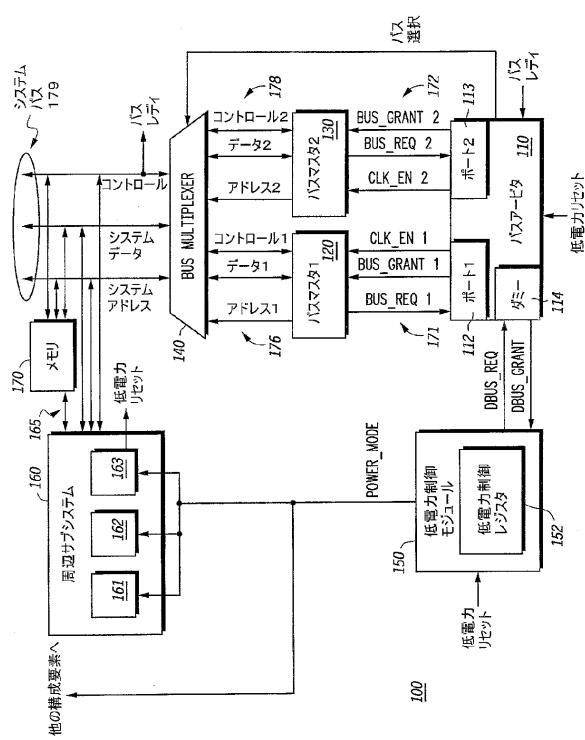

ここで図2を参照すると、本発明の一実施形態による、図1のバスアービタの一部の特定の機能を表す状態図が示され、図2全体を状態図200と称する。バスアービタ110(図1)は、バスマスター120および130(図1)のような現在のリクエスタを特定して、バスアクセスを許可する。低電力制御モジュール150(図1)のような制御装置は、追加のリクエスタとして処理される。バスアービタ110は、低電力装置のシステムバス上の未処理バスアクセスが処理されてしまったときだけ、低電力装置の低電力動作の実行を許可するのに使用できる。一実施形態において、バスアービタは、ラウンドロビンアービトレーションのようなアービトレーション方式によって、第1のバスマスターに関連する第1のポートと、第2のバスマスターに関連する第2のポートとの間で切り替わる。低電力制御装置への要求は、バスマスターからの要求よりも高い優先順位で処理される。したがって、低電力モードに移行する制御装置からの要求は、すぐに実行可能である。

## 【0021】

一実施形態において、バスアービタは、システムリセット信号(SYSTEM\_RESET)のアサーションによる起動またはリセットが発生するとすぐに、経路211を経由して状態210から開始する。状態210で、バスアービタは、第1のポートが第1のバスマスターにアクセスするのを許可する。バスアクセスの要求が状態210の第1のポート上で未処理の場合、バスアービタは、バスアクセス要求を許可する。上に説明したように、バスアービタは、この要求を第1のバスマスターへ許可するために、第1のバスマスターにバス許可信号をアサートするとともに、バスマルチプレクサにバス選択信号を与えて、ローカルバス線を第1のバスマスターに関連するシステムバスに接続する。一実施形態において、バスレディ(BUS\_READY)信号がオフまたは「0」値に設定され、システムバスが現在の要求を処理するのに使用されていることを示している間、バスアービタは、経路212を経由して状態210にとどまっている。代替的に、バスレディ信号がオン状態に設定され、かつ制御装置からの低電力バス要求(DBUS\_REQ)信号がアサートされない場合、バスアービタは、経路214を経由して状態220に移動する。状態220で、バスアービタは、第2のポートが第2のバスマスターにアクセスすることを許可する。状態210と同様に、第2のバスマスターからの要求が第2のポート上にある場合、バスアービタは、その要求を許可し、バスが要求を処理してしまうまで、経路222を経由して状態220にとどまっている。いったんバスレディ信号がアサートされるか、第2のポート上に要求が未処理になっていない場合、バスアービタは、経路224によって状態210に戻る。したがって、バスアービタは、第1のポートと第2のポート間で切り替わり、制御装置からの低電力バス要求信号がアサートされるまで、ラウンドロビン方法で利用可能な要求を処理できる。

## 【0022】

状態210および220にいる間に、制御装置からの低電力バス要求信号がアサートされ、かつバスレディ信号がアサートされると、バスアービタは、それぞれ経路216または経路226を経由して状態240に切り替わる。状態240にいる間、バスアービタは、低電力モードの実行を開始する。一実施形態において、バスアービタは、第1および第2のバスマスターのようなバスマスターに関連したクロックをディスエーブルできる。バスアービタは、制御装置に要求許可信号(DBUS\_GRANT)を与えて、バスマスターと低電力装置が復帰可能な状態にあり、かつ制御装置が低電力装置の他の構成要素を低電力モードに移行できることを示すことができる。バスアービタは、低電力リセット信号が経路242によってアサートされるまで状態240にとどまることができる。一実施形態において、低電力リセット信号は、低電力装置が低電力の実行状態から復帰されるべきことを示している。状態240にいる間に低電力リセット信号がアサートされた場合、バスアービタは、経路244を介して状態210に戻り、第1のポートおよび第2のポート間のアービトレーションを継続する。本発明の範囲から逸脱することなく、バスマスターと制御装置間の他の仲裁方法が実現できることは十分に理解されるべきであろう。

## 【0023】

10

20

30

40

50

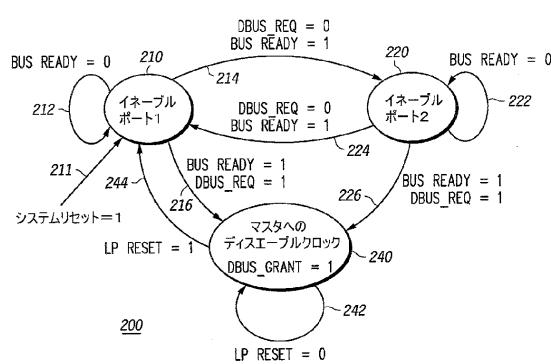

ここで図3を参照すると、本発明の一実施形態による、図1のバスアービタの一部の特定の機能を表わす他の状態図が示される。バスアービタ110のポート112(図1)のようなバスアービタに関連する異なったポートが、異なるバスマスタ間の要求を処理するのに使用される。特定のバスポートは、バス要求が関連するバスマスタから受け取られるか、または低電力モードが起動されるべきことを示す低電力バス要求が受け取られるかのいずれかまで、アイドル状態260にとどまることができる。

【0024】

一実施形態において、バスポートは、処理を開始するか、またはリセット信号(SYSTEM\_RESET)のアサーションによって、経路264を経由してアイドル状態260にリセットされる。バスポートは、アイドル状態260の間、低電力バス要求信号または関連するバスマスタからのバス要求信号(BUS\_REQ)のいずれかのアサーションを待つ。バス要求信号がアサートされない場合、バスポートは、経路263を経由して状態260にとどまっている。バス要求信号がアサートされ、低電力バス要求信号がアサートされない場合、バスポートは、経路262を通じて状態270に移行する。状態270で、バスポートは、バスアービタからの許可信号を待つ。アービタによってバス許可信号がアサートされない場合、バスポートは、経路275によって状態270にとどまっている。いったん、バス許可信号がアサートされると、バスポートは、関連するバスマスタにバス許可信号をアサートする。次に、バスポートは、経路271によって状態280に移行する。状態280で、バスポートは許可されたバス要求が終了したことを示すバスレディ信号を待つ。バスポートは、バスレディ信号がアサートされない間、経路282によって状態280にとどまっている。バスレディ信号がアサートされると、バスポートは、経路284によって状態に260に戻る。

【0025】

バスポートがアイドル状態260の間に低電力バス要求信号がアサートされると、バスポートは、低電力状態265に移行する。低電力状態265において、バスポートは、関連するバスマスタに与えられるクロックイネーブル信号をアサート停止する(deassert)。したがって、バスポートが状態265にいる間、バスマスタに関連するクロックは、ディスエーブルされるので、バスマスタが低電力モードにいることが可能になる。低電力リセット信号(LP\_RESET)が、経路266によってアサート停止され、「0」またはオフ状態にある間、バスポートは、低電力状態265にとどまっている。低電力リセット信号がアサートされると、バスポートは、経路267によってアイドル状態260に戻ることができる。したがって、いったん、バスポートがアイドル状態260に移行すると、クロックイネーブル信号は、再アサート可能になり、関連するバスマスタのクロックを再イネーブルできる。

【0026】

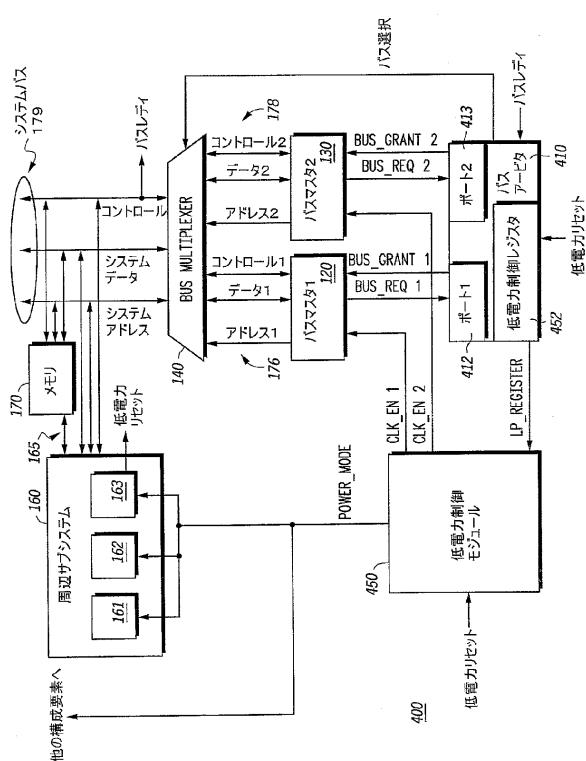

ここで図4を参照すると、本発明の一実施形態による、複数のバスマスタと1つのバスアービタを有するシステムを図示するブロック図が示され、図4全体を装置300と称する。低電力装置300は、図1の低電力装置100と類似の動作をする。バスアービタ310は、バスマスタ120またはバスマスタ130の1つを選択して、システムバス179のアクセスを許可する。低電力制御モジュール350が、低電力装置300の低電力モードを起動する。バスアービタ310は、低電力装置300が低電力動作モードに復帰可能な状態になる時期を特定するために使用される。

【0027】

注意すべき低電力装置300と低電力装置100の動作上の違いは、低電力制御モジュール150(図1)と比較した低電力制御モジュール350の動作、およびバスアービタ110(図1)と比較したバスアービタ310の動作である。特に、バスアービタ110によってクロックイネーブル信号が与えられ、低電力装置100のバスマスタ120および130に関連するクロックをイネーブルおよびディスエーブルしていたが、低電力装置300にクロックイネーブル信号を与えるのは、低電力制御モジュール350である。

【0028】

10

20

30

40

50

低電力制御モジュール350は、低電力制御レジスタ352の設定を監視する。低電力制御レジスタ352は、低電力制御レジスタ152(図1)と類似の動作をする。低電力装置300が低電力動作モードに移行されると、外部構成要素が、低電力制御レジスタ352の少なくとも一部を設定する。低電力制御レジスタ352が設定されると、低電力制御モジュール350は、低電力ポート314を通して、バスアービタ310に低電力バス要求信号を与える。低電力制御モジュール350は、バスアービタ310からの低電力バス許可信号を待つ。低電力制御モジュール350は、バスアービタ310からの低電力バス許可信号を受け取るとすぐに、次に説明するように、クロックイネーブル信号であるc1k\_en1およびc1k\_en2によって、バスマスター120およびバスマスター130のクロックをディスエーブルする。

10

#### 【0029】

一実施形態において、低電力制御モジュール350は、バスマスター120と130の両方のクロックをディスエーブルする。代替的に、低電力制御モジュール350は、バスマスター120またはバスマスター130の一方のみのクロックをディスエーブルしてもよい。例えば、バスマスター120によって行なわれる動作が重要なので、低電力モード中はディスエーブルされるべきでない場合、低電力制御モジュールは、バスマスター130に関連するクロックのみをディスエーブルできる。低電力制御モジュール350は、周辺サブシステム160、および低電力装置300の他の構成要素に電力モードインジケータを与えることもできる。したがって、周辺サブシステム160、および低電力装置300の他の構成要素は、低電力動作モードに設定できる。本発明の範囲から逸脱することなく、低電力装置300を低電力動作モードに移行させる他の対策を講じることができるのは認識されるべきであろう。さらに、本発明の範囲から逸脱することなく、バスマスター120およびバスマスター130をディスエーブルする他の方法を利用することもできる。

20

#### 【0030】

上に説明したように、バスアービタ310は、システムバス179へのアクセスを許可されるバスマスター120またはバスマスター130の1つを選択する。バスアービタ310は、アービトレーション方式に従って、バスマスター120に関連する第1のポート312、またはバスマスター130に関連する第2のポート313のいずれか一方からの要求を認識することができる。さらに、バスアービタ310は、低電力制御モジュール350からの要求を、低電力ポート314を通して処理するように選択できる。一実施形態において、バスアービタ310が低電力ポート314を通して低電力バス要求信号を認識すると、バスアービタ310は、システムバス179からバスレディ信号がアサートされるのを待つ。バスアービタ310は、未処理要求がすべてシステムバス179によって処理されてしまったことと、低電力装置300が低電力動作モードに移行するための復帰可能な状態にあることを示すバスレディ信号の出力に応答して、低電力制御モジュール350に低電力バス許可信号を与えることができる。

30

#### 【0031】

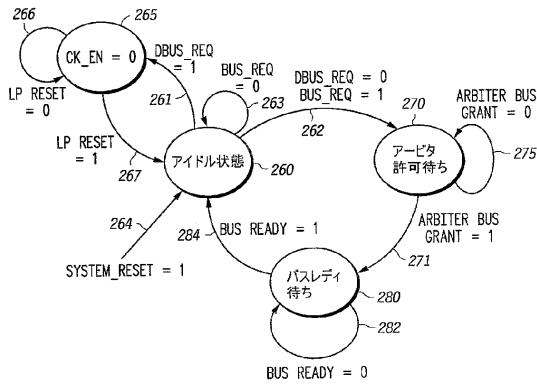

ここで図5を参照すると、本発明の一実施形態による、図4のバスアービタの特定の実施形態を実現する状態図が示され、図5全体を状態図250と称する。バスアービタは、第1のバスマスターに関連する第1のポートのイネーブルと第2のバスマスターに関連する第2のポートのイネーブルとの間で切り替わる。図示の実施形態において、バスアービタは、ラウンドロビンアービトレーションを利用して、利用可能なポートの中の1つを選択する。

40

#### 【0032】

状態図250は、図2の状態図200と類似の動作をする。低電力バス要求信号がアサートされないとき、バスアービタは、第1のポートをイネーブルするのに使用される状態210と第2のポートをイネーブルするのに使用される状態220との間で切り替わる。一実施形態において、バスレディ信号と低電力バス要求信号とが両方ともアサートされる場合、バスアービタは、状態210または状態220のいずれかから状態230に、経路231または経路233を経由してそれぞれ切り替わる。状態230で、バスアービタは

50

、低電力バス許可信号をアサートして、バスアービタに関連する低電力装置が復帰可能な状態にあり、かつ低電力動作モードに移行できることを示す。状態 230 にいる間、バスアービタは、低電力リセット信号がアサートされるのを待つ。低電力リセット信号は、バスアービタに関連する低電力装置が通常動作モードに戻るべきことを示している。低電力リセット信号がオフ状態または「0」値に設定されている間、バスアービタは、経路 232 を経由して状態 230 にとどまっている。代替的に、低電力リセット信号がアサートされた場合、バスアービタは、経路 234 を経由して状態 210 に戻り、バスアービタは、利用可能なバスマスターの 1 つから受け取った複数の要求の間の仲裁を実行する。

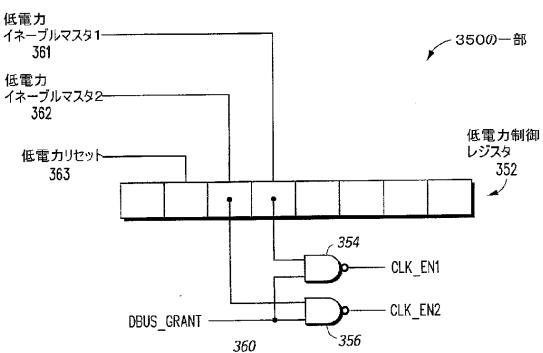

### 【0033】

ここで図 6 を参照すると、本発明の一実施形態による、図 4 の低電力制御モジュール 350 の特定の部分を図示するブロック図が示され、図 6 全体をブロック図 360 と称する。ブロック図 360 は、制御レジスタ、すなわち図 4 の低電力装置 300 のような低電力装置内の低電力動作をイネーブルする低電力制御レジスタ 352 を含んでいる。特に、ブロック図 360 は、クロックイネーブル信号、すなわち低電力制御モジュール 350 によって使用されるクロックイネーブル 1 (clk\_en1)、およびクロックイネーブル 2 (clk\_en2) をアサート (assert) およびアサート停止 (de-assert) することに使用され、NAND ゲート 354 および 356 を使用してバスマスター 120 およびバスマスター 130 (図 1) をイネーブルおよびディスエーブルできる。

### 【0034】

第 1 の NAND ゲート 354 は、バスマスター 120 へのクロックイネーブル 1 信号を与えるのに使用される。動作の際、制御レジスタの低電力イネーブルマスター 1 のビット 361 または低電力バス許可信号のいずれかがオフ状態にあるか、または「0」値に設定されていると、NAND ゲート 354 は、アサートされたクロックイネーブル 1 信号をバスマスター 120 に与え、バスマスター 120 に関連するクロックをイネーブルする。また、低電力イネーブルマスター 1 のビット 361 と低電力バス許可信号が共にアサートされるか、またはオン状態にあると、NAND ゲート 354 は、クロックイネーブル 1 をオフ状態に設定し、バスマスター 120 内のクロックをディスエーブルする。同様に、低電力制御レジスタ 352 および低電力バス許可信号の低電力イネーブルマスター 2 のビット 362 の値に基づいて、NAND ゲート 356 は、クロックイネーブル 2 信号をアサートまたはアサート停止することにより、バスマスター 130 のクロックをイネーブルまたはディスエーブルできる。低電力リセットビット 363 は、低電力リセット信号のアサーションによって設定される。低電力リセット信号は、低電力装置 300 のサブシステム 163 を始めとするサブシステムによって使用され、低電力装置 300 が通常動作モードに復帰すべき時期を示す。本発明の範囲から逸脱することなく、クロックイネーブル 1 およびクロックイネーブル 2 のようなクロックイネーブル信号を発生させる他の方法が実現できることは十分に理解されるべきであろう。

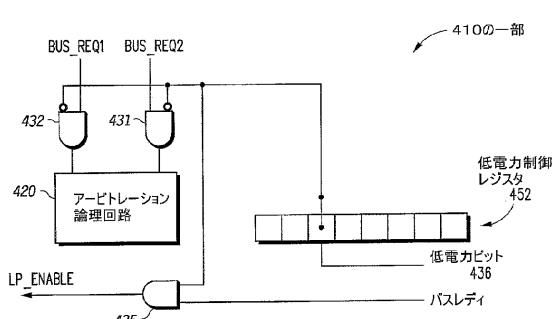

### 【0035】

ここで図 7 を参照すると、本発明の一実施形態による、バスアービタによって制御される複数のバスマスターを有するシステムを図示したブロック図が示され、図 7 全体を低電力装置 400 と称する。低電力装置 400 は、低電力装置 300 と類似の動作をする。バスアービタ 410 は、低電力装置 400 が低電力動作モードに移行できる復帰可能な状態を特定する。バスアービタ 410 は、低電力制御モジュール 450 に低電力イネーブル信号を与えて、低電力モードが起動されていることを示す。低電力イネーブル信号 (LPE\_NABLE) に応答して、低電力制御モジュール 450 は、バスマスター 120 およびバスマスター 130 へのクロックをディスエーブルできる。

### 【0036】

図 4 では、低電力モードを起動する時期を特定するために、低電力装置 300 の低電力制御モジュール 350 (図 4) が使用されたが、図 7 では、低電力装置 400 の低電力を起動する時期を特定するのはバスアービタ 410 である。バスアービタ 410 は、ポート 412 および 413 を通して、バスマスター 120 またはバスマスター 130 へのバス許可要

10

20

30

40

50

求の中からいずれかを別々に選択する。バスアービタ410は、ラウンドロビンアービトレーションのようなアービトレーション方式を使用して、ポート412またはポート413からの要求を選択して許可できる。図示の実施形態において、バスアービタ410は、低電力制御レジスタ452を備えている。バスアービタ410の外部にある、低電力装置400の構成要素またはサブシステムは、低電力装置が低電力動作モードに設定可能であることを示す特定の値に低電力制御レジスタ452を設定できる。一方、バスアービタ410は、低電力モードが起動されるべき時期を特定することができる。低電力制御レジスタ452の設定が終了すると、バスアービタ410は、低電力装置400が復帰可能な状態になるのを待つ。一実施形態において、バスアービタ410は、バスマスター120および130に関連するバス要求の許可を停止し、システムバス179からのバスレディ信号のアサーションを待つ。上に説明したように、バスレディ信号は、すべての未処理バス要求の処理をシステムバス179が終了したことを示す。したがって、低電力装置400は、システムバス179に沿ったデータの損失または不完全な転送を発生させることなく、シャットダウンまたは低電力モードに移行できる。図示の実施形態において、バスアービタ410は、低電力制御モジュール450に低電力イネーブル信号をさらに与える。

#### 【0037】

低電力制御モジュール450は、バスマスター120および130に、クロックイネーブル信号、すなわちクロックイネーブル1およびクロックイネーブル2を与える。クロックイネーブル信号は、バスマスター120および130に関連するクロックをイネーブルおよびディスエーブルするのに使用される。低電力制御モジュール450がバスアービタ410から低電力イネーブル信号(LP\_ENABLE)を受け取ると、低電力制御モジュール450は、クロックイネーブル信号をアサート停止するか、オフ状態に置くことができる。したがって、低電力イネーブル信号がアサートされると、低電力制御モジュール450は、バスマスター120および130のクロックをディスエーブルすることができる。同様に、低電力イネーブル信号がアサートされると、低電力制御モジュールは、周辺サブシステム160に電力モードインジケータをさらに与えて、サブシステム161～163をシャットダウンまたは低電力動作モードに移行できることを示すことができる。低電力制御モジュール450は、低電力モードがアクティブであることを、低電力装置400の他の部分に知らせることもできる。

#### 【0038】

低電力リセット信号は、低電力装置400を低電力モードから呼び覚ますのに使用できる。低電源リセット信号がアサートされると、低電力制御モジュール450は、クロックイネーブル、すなわちクロックイネーブル1およびクロックイネーブル2を再アサートすることによって、バスマスター120および130のクロックを再度イネーブルすることができる。さらに、低電力制御モジュール450は、電力モードインジケータの値を変更し、周辺サブシステム160および低電力装置400の他の部分に通知して、通常動作モードに復帰することができる。低電力リセット信号がアサートされると、バスアービタ410は、低電力イネーブル信号をアサート停止して、ポート412およびポート413間の仲裁を継続できる。

#### 【0039】

ここで図8を参照すると、本発明の一実施形態によるバス要求信号をゲート制御する論理回路を含んだ図7のバスアービタの一部が示される。バスアービタ410の図示された部分は、低電力モードが起動される時期を示す低電力制御レジスタ452と、要求を通過または阻止するANDゲート432と、バスマスター120のような第1のバスマスターに関連するバス要求1(bus\_req1)と、要求を通過または阻止するANDゲート431と、バスマスター130のような第2のバスマスターに関連するバス要求2(bus\_req2)とを含んでいる。一連のアービトレーション論理回路420が、ANDゲート432またはANDゲート431によって渡された要求を選択するために使用される。バスアービタ410の図示された部分は、低電力装置400のような装置が低電力動作モードに移行できることを示す低電力イネーブル信号をアサートするANDゲート435を含んで

10

20

30

40

50

いる。

#### 【0040】

動作の際、低電力制御レジスタ452の低電力ビット436がアサートされると、ANDゲート432および431は、両方の要求、すなわちバス要求1とバス要求2を阻止する。低電力ビット436がオフ状態の場合には、ANDゲート432および431は、要求、すなわちバス要求1およびバス要求2を通過させる。したがって、低電力ビット436がアサートされないと、アービトレーション論理回路420は、バス要求を単に受け取れるだけである。ANDゲート435は、バスレディ信号と低電力ビット436の両方がアサートされる場合にのみ低電力イネーブル信号をアサートする。上に説明したように、システムバス179(図7)のようなシステムバスが、未処理バス要求をすべて処理し終えた場合には、バスレディ信号のみがアサートされる。

10

#### 【0041】

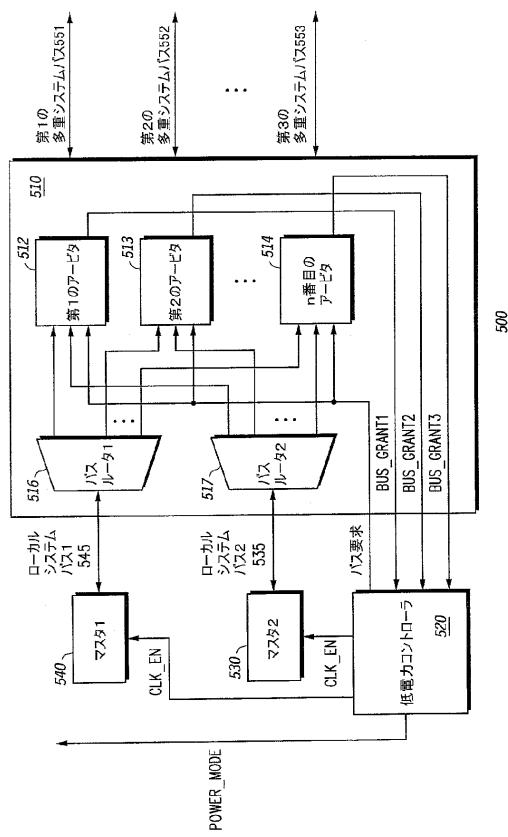

ここで図9を参照すると、本発明の一実施形態による、複数のバスマスターと複数のバスアービタを有するシステムを表すブロック図が示され、図9全体をシステム500と称する。システム500は、クロスバースイッチ510に要求を与える第1のバスマスター540および第2のバスマスター530を含んでいる。クロスバースイッチ510は、第1の多重システムバス551、第2の多重システムバス552、およびn番目の多重システム553を含む複数の多重システムバスの1つへの要求を処理する。一実施形態において、クロスバースイッチ510は、バスマスター540のローカルシステムバス545に接続された第1のバスルータ516と、第2のバスマスター530のローカルシステムバス535に接続された第2のバスルータ517とを含んでいる。バスルータ516および517は、第1のアービタ512、第2のアービタ513、およびn番目のアービタ514を含む複数のアービタの1つを通して、受け取った要求を処理する。複数のアービタの各アービタは、複数の多重システムバスの1つの多重システムバスに関連付けられている。低電力コントローラ520は、低電力モードが起動されるべき時期を特定するのに使用され、バスマスター530および540に関連するクロックをディスエーブルして、バスマスター530および540を低電力モードに移行させることができる。

20

#### 【0042】

クロスバースイッチ510は、バスマスター540および530から関連するシステムバスへの要求を処理する。第1のバスルータ516は、バスマスター540に関連するシステムバスを特定する。一実施形態において、バスルータ516は、バスマスター540からの要求に関連付けられたアドレスによって、関連するシステムバスを特定する。例えば、アドレスの第1のブロックは、第1の多重システムバス551に関連付けられ、アドレスの第2のブロックは、第2の多重システムバス552に関連付けられる。バスルータ516は、特定された多重システムバスに関連したアービタに要求を与える。例えば、要求が第1の多重システム551に関連付けられている場合、バスルータ516は、第1のアービタ512に要求を与え、要求が第2の多重システムバス552に関連付けられている場合、バスルータ516は、第2のアービタ513に要求を与える。同様に、第2のバスルータ517は、バスマスター530から受け取った要求を、複数のアービタの1つに与える。アービタ512～514は各々、バスルータ516および/またはバスルータ517から受け取った要求の中から選択する。いったん、第1のアービタ512のようなアービタが要求を選択すると、クロスバースイッチ510は、第1の多重システムバス551を始めとする関連の多重システムバスに要求を与える。一実施形態において、アービタ512～514は、低電力コントローラ520からの要求をさらに受け取ることができる。システム500は、2つのバスマスター、すなわちバスマスター540および530を有するように説明したが、本発明の精神および範囲から逸脱せずに、他のバスマスターが含まれていてもよく、サポートされるバスマスターの数が変更できることは理解されるべきであろう。

30

40

#### 【0043】

低電力コントローラ520は、システム500内の低電力動作を起動する。一実施形態において、システム500のサブシステムは、低電力コントローラ520に関連する信号

50

またはレジスタ値をアサートして、低電力モードが起動されるべき時期を示すことができる。低電力コントローラ 520 が、低電力モードが起動されるべきことを特定すると、低電力コントローラ 520 は、アービタ 512 ~ 514 の個々にバス要求を与える。低電力コントローラ 520 からのバス要求が受け取られると、バスアービタ 512 ~ 514 は、低電力コントローラ 520 に、バス許可信号、BUS\_GRANT1、BUS\_GRANT2、およびBUS\_GRANT3 を返す。バス許可要求は、アービタ 512 ~ 514 に関連するそれぞれの多重システムバス 551 ~ 553 が未処理要求をすべて処理し終えたことを示している。一実施形態において、低電力コントローラ 520 は、低電力動作を起動する前に、アービタ 512 ~ 514 のすべてからのバス許可が受け取られるまで待機する。いったん、すべてのバス許可が受け取られると、低電力コントローラ 520 は、バスマスター 530 および 540 に与えるクロックイネーブル信号をアサート停止し、システム 500 の一部に低電力状態インジケータ POWER\_MODE をアサートできる。したがって、低電力コントローラ 520 は、バスマスター 530 および 540、および多重システムバス 551 ~ 553 に関連するすべてのバスアクセスが処理されてしまったときだけバスマスター 530 および 540 をディスエーブルし、システム 500 を、低電力動作モードを起動する復帰可能な状態にとどめることができる。本発明の代替の実施形態は、バスマスター 530 または 540 が、アービタ 512 ~ 514 からのそれぞれのバス許可が受け取られると、未処理の転送がすべて終了したことを判定した後に、バスマスター 530 および 540 へのクロックをディスエーブルすることができる。

10

20

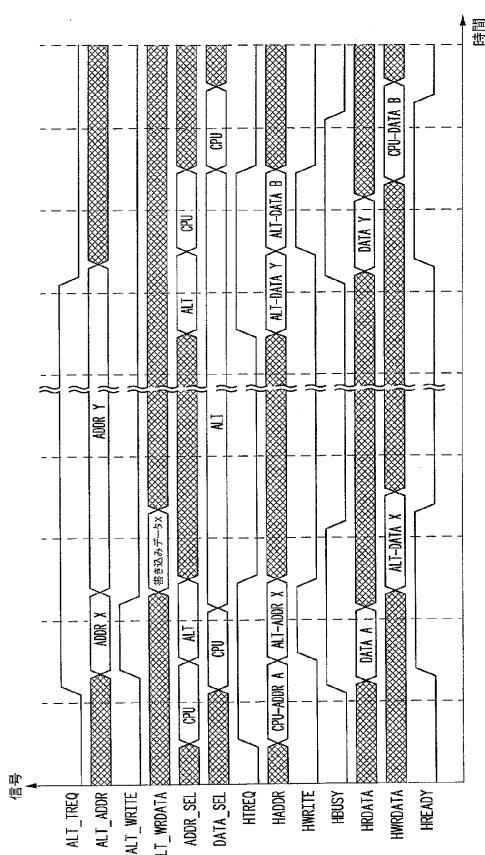

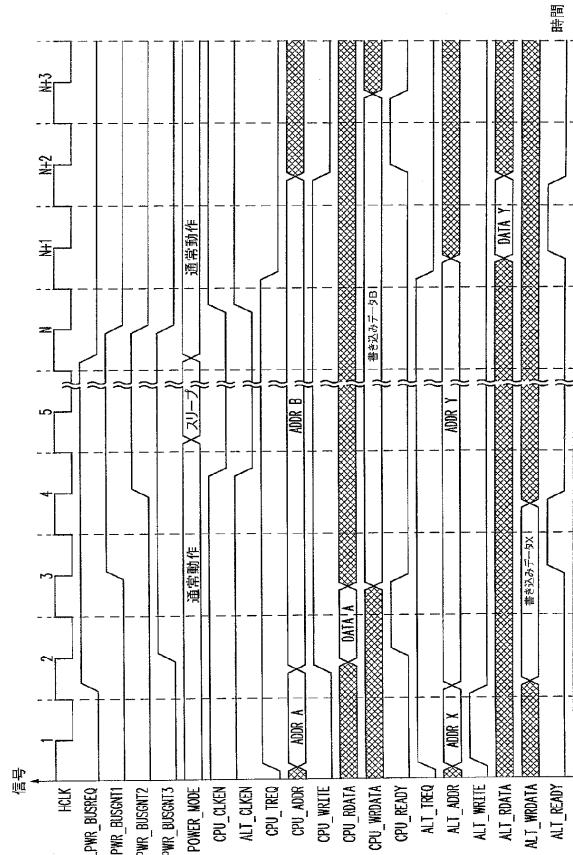

**【0044】**

ここで図 10 を参照すると、本発明の一実施形態の特定の動作を図示したタイミング図が示される。図示の実施形態では、2つのバスマスター、すなわち CPU と第2の代替のバスマスター (ALT) が、低電力装置 100 (図 1) のようなシステムに存在する。CPU が、システムバス 179 (図 1) のようなバスの所有権を取得したい場合、バス要求 (CPU\_BUSREQ) をアサートする。バスアービタ 110 (図 1) のようなバスアービタは、バス許可信号 (CPU\_BUSGRANT) をアサートして、CPU にバスの所有権を許可する。ALT バスマスターがバスの所有権を取得したい場合、ALT バスマスターがバス要求 (ALT\_BUSREQ) をアサートする。バスアービタは、バス許可信号 (ALT\_BUSGRANT) をアサートして、ALT バスマスターにバスの所有権を許可する。CPU は、先ずアドレス位置 ADDR\_A に読み出しアクセスを行ない、次にアドレス位置 ADDR\_B に書き込みアクセスを行う。ALT は、先ずアドレス位置 ADDR\_X に書き込みアクセスを行ない、次にアドレス位置 ADDR\_Y に読み出しアクセスを行う。

30

40

40

**【0045】**

バスアービタは、バスアービトレーション優先順位決定機構によって、共有のシステムバスに対する CPU のアクセスと ALT のアクセスの相対順位を判定する。複数の優先順位決定方式が利用可能であり、早入れ早出し (first-come first-served)、ラウンドロビン (round-robin)、および固定優先順位 (fixed priority) のような方式が当業界でよく知られている。本発明は、CPU バスマスターと ALT バスマスター間の優先順位については、特定の方式に依存していないので、この実施例では、ALT が CPU よりも高い優先順位を有する簡単な固定方式を示している。

**【0046】**

本発明の一実施形態によれば、追加の要求入力 (LPWR\_BUSREQ) が、低電力制御モジュール 150 (図 1) のような低電力モード制御装置 (LPMC) によってバスアービタに与えられる。バスアービタは、低電力モード制御装置に、追加の出力バス許可信号、LPWR\_BUSGNT を与える。低電力モード制御装置は、一連の出力信号 POWER\_MODE を与え、システムの現在の運転モードを示す。図には、CPU マスターおよび ALT マスターへのクロック発生を制御するクロックイネーブル信号が示されている。低電力動作は、CPU への CPU クロックイネーブル信号、CPU\_CLOCKEN、および

50

AL Tマスタへの代替クロックイネーブル信号、AL T\_C L K E Nをネゲートする（ネゲートする）ことによってサポートされている。これらの信号のネゲーションは、これらの装置に対するクロック発生を一時停止するので、消費電力を低減できる。図示の実施例において、低電力動作モードは、CPUマスタおよびAL Tマスタによって行なわれたアクセスの間に起動される。

【0047】

クロックサイクル1において、システムは、通常モードを示す電力モード信号POWER\_MODEによって示されるような通常動作モードで動作している。クロックサイクル1が始まると、CPUは、CPU\_BUSREQをアサートして、CPUがシステムバスの所有権を望んでいたことを示し、CPUが転送を開始していることを示すCPU\_TRREQ信号をアサートし、所望のアクセス位置に対応するADDR\_AでCPUアドレス線、CPU\_ADDRを駆動する。CPU\_WRITE信号はネゲートされ、アクセスが読み出しあることを示す。AL Tマスタは、サイクル1でバス所有権を要求していないので、バスアービタはCPUにバス所有権を許可し、サイクル1でCPU\_BUSGNTをアサートする。バスアービタは、制御信号ADDR\_SELを使ってシステムバス信号HADDRおよびHWRITE上にそれぞれ駆動されるCPU\_ADDRおよびCPU\_WRITEを選択する。システムバス転送要求HREQがアサートされ、転送がシステムバス上で要求されていることを示す。他のアクセスが既に処理されているので、転送が始まり、転送のアドレスフェーズは、サイクル1の終わりで終了する。位置ADDR\_Aへの転送のデータフェーズがサイクル2で始まり、HBUSY信号がアサートされ、システムのデータバスが使用中であることを示す。図示の実施例では、個別の読み出し/書き込みデータバスを示しているが、代替の実施形態では、単一の双方向データバスを使用することもできる。

【0048】

サイクル2で、システム読み出しデータバスHDATAは、アドレス位置ADDR\_Aに対応するシステム、または装置によって、ADDR\_Aに対応するデータで駆動される。バスアービタは、既にDATA\_SEL信号を駆動していて、データフェーズがCPUに属することを示している。HDATAからのデータは、CPU\_RDATA信号としてCPUに与えられる。応答装置は、システムバスレディ信号HREADYのアサーションを発生させ、要求データが既に与えられたことを示す。サイクル2の終わりで、位置ADDR\_Aへのアクセスのデータフェーズは終了し、CPUは、読み出しデータを内部にラッピングしている。サイクル2の間、CPUはCPU\_BUSREQをアサートし続け、CPUは、位置ADDR\_Bへの次のアクセスを要求していて、CPU\_ADDR信号上にADDR\_Bを駆動し、CPU\_WRITEをアサートして、要求されたアクセスが書き込みサイクルであること示している。またサイクル2の間、AL Tマスタは、AL TBUSREQをアサートして、それがシステムバスの所有権を望んでいることを示し、AL T\_TREQをアサートして値ADDR\_XでAL T\_ADDRを駆動し、AL Tマスタが、位置ADDR\_Xにアクセスが行われるべきことを要求していることを示す。AL T\_WRITE信号もアサートされ、要求されたアクセスが書き込みであること示す。バスアービタは、CPU\_BUSREQおよびAL T\_BUSREQを受け取り、AL Tマスタがシステムバスの所有権を許可されるべきことを決定する。バスアービタは、CPU\_BUSGNTをネゲートし、AL T\_BUSGNTをアサートし、ADDR\_SEL信号を変更して、システムバス信号HADDRおよびHWRITE上にそれぞれ駆動されるAL T\_ADDRおよびAL T\_WRITE信号を選択することによって、サイクル2で始まるアドレスフェーズの間バス所有権をAL Tマスタに与え、CPUからのアドレスバスの所有権を保留する。HREQ信号は、サイクル2の間アサートされ続け、他のシステムバス転送が要求されていることを示す。現在のデータフェーズが、CPUがバス所有権を許可された前のアドレスフェーズに関連付けられているので、バスマスタは、DATA\_SEL信号を駆動して、現在のデータフェーズの間CPUを選択する。

【0049】

10

20

30

40

50

サイクル3の間、位置ADD R Xに対応するデータフェーズが発生し、ALTマスタは、DATA XでALT\_WRD ATAを駆動する。バスアービタは、DATA\_SE L信号を駆動し、システム書き込みバスHWR DATAに接続されるALT\_WRD ATAを選択することで、書き込み用にアクセスされた装置にDATA Xを与えることができる。サイクル3の間、HBUS Yはアサートされ続け、システムデータバスが使用中であることを示す。アドレス位置ADD R Xに対応するアクセスされた装置は、システムバスレディ信号HREADYのアサーションを発生させ、書き込みデータが受け取り中であることを示す。サイクル3の終わりで、位置ADD R Xへのアクセスのデータフェーズは終了する。サイクル3の間、CPUは、CPU\_ADD R上にCPU\_BUSREQ、CPU\_TREQ、およびADD R Bを駆動し続け、システムバス所有権のみならず、サイクルが依然として要求されていることを示す。ALTマスタも、ALT\_BUSREQおよびALT\_TREQを駆動し続け、ALT\_ADD Rバス上にADD R Yを駆動して、システムバス所有権のみならず、サイクルが依然として要求されていることを示す。ALT\_WRITE信号がネゲートされ、ADD R YへのALTマスタアクセスが読み出しサイクルであることを示す。サイクル3で、低電力コントローラは、バスアービタにLPWR\_BUSREQをアサートして、低電力モードへの移行に備える。本発明の一実施形態によれば、この要求は、すべての可能性のある要求のなかで最高の優先順位を割り当てられる。LPWR\_BUSREQのアサーションは、アービタに、他のすべてのリクエスタへのバス許可をネゲートさせるので、サイクル3で、CPU\_BUSGNTおよびALT\_BUSGNTはネゲートされ、CPUまたはALTマスタのいずれもがバス所有権を許可されないことを示す。バスマスタの要求からバス所有権を削除したことにより、アドレスフェーズがサイクル3で起動されないので、システムバス転送要求信号HTR EQは、サイクル3でネゲートされる。転送が要求されていないので、システムアドレスバス、HADDRは、有効であると見なされないが、バスアービタは、デフォルトによって駆動されるALT\_ADD RまたはCPU\_ADD Rのいずれかを選択し得る。サイクル3で、システムデータバスが、位置ADD R Xへのアクセスのデータフェーズで使用されているので、HBUS Yがアサートされ続ける。

#### 【0050】

サイクル4で、HBUS Yはネゲートし、システムデータバスがここでアイドル状態であることを示す。この時点では、バスアービタは、低電力コントローラにLPWR\_GNT信号をアサートして、システムバス動作が休止状態になったことを示すので、ここで安全に低電力動作モードに移行することができる。次に、クロックイネーブル信号CPU\_CLKENおよびALT\_CLKENが、サイクル4でネゲートされ、CPUマスタおよびALTマスタのさらなるクロックを一時停止し、それによって、システムの電力消費を最小限に抑えることができる。サイクル5で、低電力コントローラは、POWER\_MODE信号を変更して、低電力スリープ状態に移行してしまったことを示す。低電力モード制御装置がLPWR\_BUSREQをアサートし続けている間、低電力スリープ状態は有効であり、CPU\_CLKENおよびALT\_CLKENはネゲートされ続け、システムの電力消費は最小限に抑えられる。

#### 【0051】

いったん、システムイベントが通常動作モードへの復帰を指示すると、低電力コントローラは、バスアービタへのLPWR\_BUSREQをネゲートする。図10において、このことは、クロックサイクルN中に発生する。LPWR\_BUSREQがネゲートされると、バスアービタは、LPWR\_BUSGNTをネゲートし、CPUマスタとALTマスタ間のアービトレーションが再開される。アービトレーション優先順位に基づいて、バスアービタは、サイクルNでALTマスタへのシステムバス所有権を許可し、ADD R\_SELをそれに応じて駆動することによって、システムバスHADDRは、ADD R Yで駆動され、HWRITEがネゲートされる。HTR EQがサイクルNでアサートされ、新しいシステムバス転送が要求されていることを示す。サイクルNとN+1の間、CPUは、CPU\_ADD R上にCPU\_BUSREQ、CPU\_TREQ、およびADD R B

10

20

30

40

50

を駆動し続け、システムバス所有権のみならず、サイクルが依然として要求されていることを示す。サイクルN + 1において、ALTマスタは、ALT\_BUSREQおよびALT\_TREQをネゲートして、システムバスの所有権がもはや望まれていないこと、転送が要求されていないことを示す。バスアービタは、CPUにシステムバス所有権を移譲するために、ALT\_BUSGNTをネゲートし、CPU\_BUSGNTをアサートする。バスアービタは、ADDR\_SEL信号を駆動して、CPU\_ADDRおよびCPU\_WRITE信号をHADDRおよびHWRITEのそれぞれに接続する。HADDRが値ADDRBで駆動され、HWRITEがアサートされ、CPUが要求したアクセスが書き込みサイクルであることを示す。

## 【0052】

10

サイクルN + 1の間、HBUSYがアサートされ、システムデータバスがデータフェーズに使用されていることを示す。サイクルN + 1の間、読み出しデータが、システム読み出しデータバスHREADDATAとして、アドレス位置ADDR\_Yに対応する装置によって返され、システムバスレディ信号HREADYのアサーションを発生させて、読み出しデータが与えられていることを示すとともに、バスアービタがDATA-SELを駆動して、このデータフェーズがALTマスタ用であることを示す。ALTマスタは、サイクルN + 1で、返ってきた読み出しDATA\_Yをラッチし、サイクルN + 1の終わりで、位置ADDR\_Yへのアクセスのデータフェーズは終了する。

## 【0053】

20

サイクルN + 2の間、バスアービタは、DATA\_SELを駆動して、CPU\_WRDATA信号上にアサートされた書き込みデータをシステムバス書き込みデータ信号HWRDATAと結合されるようにする。サイクルN + 2の間、HBUSYはアサートされ続け、システムデータバスが使用中であることを示す。ADDR\_Bに対応するアクセスされた装置は、システムバスレディ信号HREADYのアサーションを発生させ、書き込みデータが受け取り中であることを示す。サイクルN + 2の終わりで、位置ADDR\_Bへのアクセスのデータフェーズは終了する。CPUは、CPU\_TREQおよびCPU\_BUSREQをネゲートし、転送がそれ以上要求されていないこと、システムバス所有権がもはや望まれていないことを示す。サイクルN + 3の間、HBUSYはネゲートされ、システムデータバスがアイドル状態であること示す。

## 【0054】

30

バスアービトレーション動作およびシステムバスハンドオフの他の実施例は、当業界で公知であり、上述の実施例は、本発明の範囲をここに示した厳密なシーケンスまたはプロトコルに限定することを意図しているものではない。バスアービトレーションに関して代替のバスマスタとして作動することによって、低電力コントローラは、低電力モードへの移行を適切な境界で確実に行い、かつ低電力モードをイネーブルする前、かつCPUおよび代替のマスタ論理回路のクロックゲーティングを行なう前に、未処理のシステムバスアクセスを確実に終了させることができる。

## 【0055】

40

図10に示した低電力アービトレーション動作の実施例は、システム500(図9)のように複数のシステムバスが存在しているシステムに拡張することができる。このような環境では、低電力コントローラ520(図5)のような低電力コントローラは、すべてのシステムバスの所有権を要求する。現在のバス動作が終了すると、低電力コントローラは、すべてのシステムバスの所有権を最終的に許可される。この処理は、逐一発生してもよいし、同時にまたは任意の組み合わせで発生してもよい。いったん、すべてのシステムバスの所有権が全部取得されると、低電力コントローラは、次にシステムを低電力モードに強制的に移行することができる。代替的に、低電力コントローラは、その特定のバスの所有権が低電力コントローラに許可されるとすぐに、所与のシステムバスに関連するロック、ユニット、または構成要素を低電力モードに移行させることもできる。特定のロックまたはユニットが複数のシステムバスに関連付けられている場合、ロックがアイドル状態なのか、または未処理のバスアクセスがそのロックまたはユニットに存在しないよ

50

うなバスサイクルの境界に達したのかのいずれかを判定できるまで、そのブロックの低電力モードへの移行は、延期される。

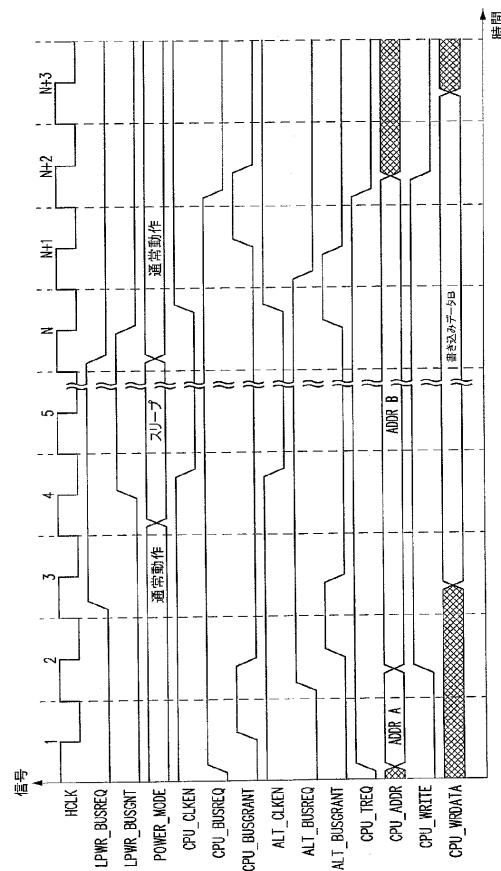

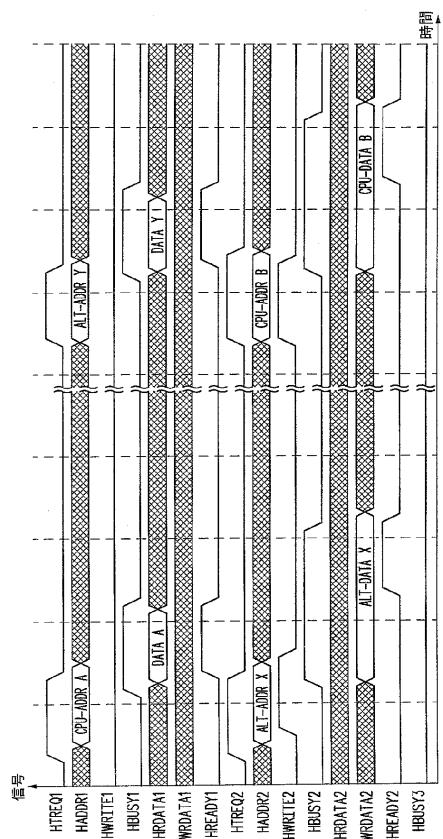

【0056】

ここで図11を参照すると、本発明の他の実施形態に関連する信号タイミングを図示したタイミング図が示される。図示の実施形態において、3つのシステムバスが存在し、2つのバスマスタであるCPUマスタおよびALTマスタに相互接続されている。この実施例において、CPUは、先ずアドレス位置ADDR\_Aに読み出しアクセスを行ない、次にアドレス位置ADDR\_Bに書き込みアクセスを行う。ALTは、先ずアドレス位置ADDR\_Xに書き込みアクセスを行ない、次にアドレス位置ADDR\_Yに読み出しアクセスを行う。各システムバスに関連するバスアービタは、バスアービトレーション優先順位機構によって、それぞれのシステムバスに対するCPUのアクセスとALTのアクセスの相対順位を判定する。複数の優先順位決定方式が利用可能で、早入れ早出し、ラウンドロビン、および固定優先順位のような方式が当業界でよく知られている。本発明は、CPUバスマスタとALTバスマスタ間の優先順位については、特定の方式に依存していないので、この実施例については、ALTがCPUよりも高い優先順位を有する簡単な固定方式を示している。代替の実施形態は、異なる優先順位方式を取り入れてもよく、各特定のシステムバスに対して異なる方式を取り入れることもできる。

【0057】

図示の実施例において、CPUマスタおよびALTマスタは、クロスバースイッチ510(図9)のような完全に相互接続されたクロスバースイッチによって、システムバス1、2、および3に相互接続される。スイッチの各システムバス出力で、制御論理回路は、CPU信号CPU\_TREQおよびCPU\_ADDRならびにALTマスタ信号ALT\_TREQおよびALT\_ADDRを受け取る。本発明の一実施形態において、各システムバスは、システムアドレス空間の特定の部分に対応している。CPU\_ADDRおよびALT\_ADDRの一部を復号することによって、各個々のシステムバス接続は、CPUまたはALTマスタによって現在要求されているアクセスが、その特定のシステムバスに目標設定されているかどうかを判定する。各転送要求は、特定のアクセスアドレスに基づいて、複数のシステムバス接続の1つに目標設定しているので、この復号機構は、CPUマスタおよびALTマスタによる「默示の」バス要求に備えている。各バスマスタからのアクセスアドレスの一部を復号することによって、特定のシステムバスに対する要求がなされているという判定は、容易に行われる。両方のバスマスタが、同一のサイクルで、同じシステムバスポートに該当するアクセス要求を示した場合、複数の要求間のアービトレーションは、各システムのバスアービタによって行なわれる。本発明の代替の実施形態は、各バスマスタから複数のシステムバスアービタの各々に、明示のバス要求を与えてよい。

【0058】

本発明の一実施形態によれば、追加の明示の要求入力(LPWR\_BUSREQ)は、低電力モード制御装置によって、複数のシステムバスアービタの各々に与えられる。各バスアービタは、低電力モード制御装置に追加のバス許可出力信号を与える。図示の実施例において、システムバス1、2、および3にそれぞれ対応するLPWR\_BUSGNT1、LPWR\_BUSGNT2、およびLPWR\_BUSGNT3の3つの信号が与えられる。低電力モード制御装置は、一連の出力信号POWER\_MODEを与え、システムの現在の運転モードを示す。2つのバスマスタ、すなわちCPUマスタおよびALTマスタへのクロック発生を制御するクロックイネーブル信号を図示している。低電力動作は、クロックイネーブル信号、すなわちCPUへのCPU\_CLKENと、ALTマスタへのALT\_CLKENをゲートすることによってサポートされる。これらの信号のネゲーションは、これらのユニットに対するクロック発生を一時停止するので、消費電力を低減できる。図示の実施例において、低電力動作モードは、CPUマスタおよびALTマスタによって行なわれるアクセスの間で起動される。

【0059】

10

20

30

40

50

クロックサイクル1において、システムは、標準モードを信号する電力モード信号POWER\_MODEによって示されるような通常動作モードで動作している。クロックサイクル1が始まると、CPUは、CPU\_TREQをアサートして、CPUが転送を要求していること示し、所望のアクセス位置に対応するADDR\_AでCPU\_ADDRを駆動する。CPU\_WRITEはネガートされ、アクセスが読み出しであることを示す。この実施例では、ADDR\_Aは、システムバス1に関連する位置に一致する。またサイクル1で、ALTマスタは、ALT\_TREQをアサートして、ALTマスタが転送を要求していることを示し、所望のアクセス位置に対応するADDR\_XでALT\_ADDRを駆動する。ALT\_WRITEがアサートされ、アクセスが書き込みであることを示す。この実施例では、ADDR\_Xは、システムバス2に関連する位置に一致する。サイクル1で、ALTマスタは、システムバス1へのバス転送を要求していないので、システムバスアービタ1は、CPUにバスの所有権を許可し、システムバス1信号HADDR1およびHWRITE1上に駆動されるCPU\_ADDRおよびCPU\_WRITEを選択する。システムバス1転送要求HTREQ1がアサートされ、転送がシステムバス1上で要求されていることを示す。他のアクセスは既に処理されているので、転送が始まり、転送のアドレスフェーズは、サイクル1の終わりで終了する。またサイクル1で、システムバスアービタ2は、ALTマスタにバス所有権を許可し、システムバス2信号HADDR2およびHWRITE2上に駆動されるALT\_ADDRおよびALT\_WRITEを選択する。システムバス2転送要求HTREQ2がアサートされ、転送がシステムバス2上で要求されていることを示す。他のアクセスは既に処理されているので、転送が始まり、転送のアドレスフェーズは、サイクル1の終わりで終了する。CPUマスタおよびALTマスタによって要求されたアクセスは、異なったシステムバスに対応するアドレス向けだったので、これらのアクセスは、同時に行なわれることに注意されたい。

#### 【0060】

システムバス1上の位置ADDR\_Aへの転送のデータフェーズがサイクル2で始まり、HBUSY1がアサートされ、システムデータバス1が使用中であることを示す。システムバス2上の位置ADDR\_Xへの転送のデータフェーズがサイクル2で始まり、HBUSY2がアサートされ、システムデータバス2が使用中であることを示す。図示の実施例では、個別の読み出し/書き込みデータバスを示しているが、代替の実施形態では、単一の双方向データバスを使用することもできる。サイクル2で、システム読み出しデータバス1であるHRDATA1は、アドレス位置ADDR\_Aに対応する装置によって、ADDR\_Aに対応するデータで駆動される。HRDATA1からのデータは、CPU\_RDATAとしてCPUに与えられる。応答装置は、システムバス1レディ信号HREADY1のアサーションを発生させ、要求データが既に与えられたことを示し、その後CPU\_READYがアサートされる。

#### 【0061】

サイクル2の終わりで、位置ADDR\_Aへのアクセスのデータフェーズは終了し、CPUは、読み出しデータを内部にラッピングしている。サイクル2の間、システム書き込みデータバス2であるHWRDATA2は、アドレス位置ADDR\_Xに対応するALTマスタのALT\_WRDATAバスから書き込みデータで駆動される。この転送では、応答装置が使用中であり、サイクル2で書き込み転送を終了できないので、応答装置は、システムバス2レディ信号HREADY2をネガートし、書き込みデータがまだ受け取られていないことを示す。サイクル2の終わりで、転送がまだ終了していないので、位置ADDR\_Xへのアクセスのデータフェーズは延長される。ALT\_READYはネガートされ、データフェーズが延長されなければならないことをALTマスタに知らせる。サイクル2の間、CPUは、CPU\_TREQをアサートし続けて位置ADDR\_Bへの次のアクセスを要求し、ADDR\_BをCPU\_ADDR信号上に駆動し、CPU\_WRITEをアサートして、要求されたアクセスが書き込みサイクルであることを示す。またサイクル2の間、ALTマスタはALT\_TREQをアサートし、値ADDR\_YでALT\_ADDRを既に駆動していて、ALTマスタが、位置ADDR\_Yに他のアクセスが行なわれる

10

20

30

40

50

ことを要求していることを示す。ALT\_WRITEはネゲートされ、要求されたアクセスが読み出しであることを示す。

【0062】

サイクル1および2の間、システムバス3に対応する位置へのアクセスが要求されていないので、ネゲートされたHBUSY3によって示されるように、システムバス3はアイドル状態のままである。この実施例では、システムバス3に対するアクセスが要求されないので、すべてのシステムバス3信号が示されているものではないことは注意されるべきであろう。サイクル2で、低電力コントローラは、システムを低電力モードに移行させることを望んでいるので、LPWR\_BUSREQをシステムバスアービタ1、2、および3にアサートする。システムバス3が現在アイドル状態にあるので、サイクル2で、システムバスアービタ3は、LPWR\_BUSREQを受け取り、LPWR\_BUSGNT3をアサートする。低電力バス要求が未処理なので、サイクル2で、システムバスの1および2の転送要求信号HREQ1およびHREQ2は、それぞれのシステムバス制御装置によってネゲートされ、新しい転送の起動が防止される。

10

【0063】

サイクル3で、システムバス1信号HBUSY1がネゲートされ、システムバス1が現在アイドル状態であり、バスサイクルの境界に来たので、システムバス1のバスアービタは、LPWR\_BUSGNT1をアサートすることを低電力コントローラに知らせる。またサイクル3で、システムバス2のHREADY2信号が位置ADDR\_Xに対応する装置によってアサートされ、これはサイクル1で起動された書き込みサイクルが現在終了していることを示す。サイクル4で、システムバス2は、アイドル状態になり、HBUSY2信号がネゲートされる。バストランザクションが進行中ではないので、システムバス2のバスアービタは、低電力コントローラにLPWR\_BUSGNT2をアサートする。この時点で、低電力コントローラは、すべてのシステムバスのバス所有権を取得しており、システムバス動作が休止状態に達したことを示すため、ここで安全に低電力動作モードに移行することができる。サイクル4で、次にクロックイネーブル信号、すなわちCPU\_CLKENおよびALT\_CLKENがネゲートされ、CPUマスタおよびALTマスタのさらなるクロックを一時停止し、それによってシステムの電力消費を最小限に抑えることができる。サイクル5で、低電力コントローラは、POWER\_MODE信号を変更して、低電力スリープ状態に移行したことを示す。低電力スリープ状態は、低電力モード制御装置がLPWR\_BUSREQおよびCPU\_CLKENをアサートし続けている間、有効状態が続き、ALT\_CLKENはネゲートされ続けて、システムの電力消費が最小限に抑えられる。

20

【0064】

いったん、システムイベントが通常動作モードへの復帰を指示すると、低電力コントローラは、すべてのシステムバスアービタへのLPWR\_BUSREQをネゲートする。図11において、このことは、クロックサイクルN中に発生する。LPWR\_BUSREQがネゲートされると、システムバスアービタ1、2、および3は、LPWR\_BUSGNT1、LPWR\_BUSGNT2、およびLPWR\_BUSGNT3をそれぞれネゲートし、CPUマスタとALTマスタ間のアービトレーションが再開される。CPUマスタおよびALTマスタはいずれも、未処理アクセス要求(CPU\_TREQおよびALT\_TREQが両方ともアサートされる)を有している。CPUは、システムバス2に対応する位置ADDR\_Bに書き込みを要求し、ALTマスタは、システムバス1に対応するADDR\_Yに読み出しあクセスを要求している。システムバス1および2へのアクセスにはコンフリクトが存在しないので、両方のアクセスがサイクルNで起動される。転送の残りは、サイクルN+1～N+3に示され、上に説明したプロトコルに従う。

30

【0065】

バスアービトレーション動作およびシステムバスハンドオフの他の実施例は、当業界で公知であり、所与の実施例は、この本発明の範囲をここに示した厳密なシーケンスまたはプロトコルに限定することを意図するものではない。バスアービトレーションに関して代

40

50

替のバスマスターとして作動することによって、低電力コントローラは、低電力モードへの移行を適切な境界で確実に行い、かつ低電力モードをイネーブルする前、かつCPUおよび代替のマスター論理回路のクロックゲーティングを行なう前に、複数のシステムバス上の未処理のシステムバスアクセスを確実に終了させることができる。図11は、すべてのシステムバスがアイドル状態であった後に発生したクロックゲーティングを示しているが、代替の実施形態は、各システムバスが休止状態になったときに、システム要素のサブセットを、クロックゲート制御されたまたは他の低電力状態に移行させてよい。

#### 【0066】

ここに説明したシステムは、情報処理システムの一部であってよい。用語「情報処理システム」は、情報を処理することができる、またはあるソースから他のソースに情報を転送することができる、任意のシステムを意味している。情報処理システムは、コンピュータのような単一の装置、携帯情報端末（PDA）のような携帯型計算器、ケーブルセットトップボックス、セルラー電話のようなインターネット対応装置等であってよい。あるいは情報処理システムは、そのような装置の集合体を指していてよい。ここに説明したシステムは、低電力装置の低電力動作モードを起動する復帰可能な状態の特定という利点を持つことは理解されるべきであろう。

#### 【0067】

上記実施形態の詳細な説明において、その実施形態の一部を構成する添付図面について説明し、本開示を実施できる特定の実施形態を図示した。これらの実施形態について、当業者が本開示を実施できる程度に十分詳細に説明したが、他の実施形態を利用できるとともに、本開示の精神または範囲から逸脱することなく、論理的、機械的、および電気的な変更がなされてもよいことは理解されるはずである。当業者を本開示を実施可能にするのに必要でない細部の説明を避けるために、ここでの説明は、当業者に周知の特定の情報を省略している場合がある。さらに、本開示の教示を取り入れた他の多くの様々な実施形態が、当業者によって容易に構成され得るであろう。したがって、本開示は、ここに述べた特定の形態に限定するように意図されているものではなく、これとは逆に、本開示は、本開示の精神および範囲の中に適切に含まれ得るこのような他の変更物、改変物、および等価物を包含するようことを意図する。したがって、上記の詳細な説明は限定的な意味で解釈されるべきでなく、本開示の範囲は、添付の請求項によってのみ定義される。

#### 【図面の簡単な説明】

#### 【0068】

【図1】本発明の一実施形態による、バスアービタによって制御される複数のバスマスターを有するシステムを示すブロック図。

【図2】本発明の一実施形態による、図1のバスアービタの一部の特定の機能を示す状態図。

【図3】本発明の一実施形態による、図1のバスアービタの一部の機能に対する特定の実施形態を実現する他の状態図。

【図4】本発明の一実施形態による、複数のバスマスターおよび1つのバスアービタを有するシステムを示すブロック図。

【図5】本発明の一実施形態による、図4のバスアービタの他の特定の実施形態を実現する状態図。

【図6】本発明の一実施形態による、レジスタを含む図4の低電力制御モジュールの特定の部分を示すブロック図。

【図7】本発明の一実施形態による、バスアービタによって制御される複数のバスマスターを有するシステムを示すブロック図。

【図8】本発明の一実施形態による、バス要求信号のゲート制御する論理回路を含んだ図7のバスアービタの一部を示すブロック図。

【図9】本発明の一実施形態による、複数のバスマスターおよび複数のバスアービタを有するシステムを示すブロック図。

#### 【図10A】本発明の特定の実施形態による、システム内の信号を示すタイミング図。

10

20

30

40

50

【図10B】本発明の特定の実施形態による、システム内の信号を示すタイミング図。

【図11A】本発明の特定の実施形態による、システム内の信号を示す他のタイミング図

【図11B】本発明の特定の実施形態による、システム内の信号を示す他のタイミング図

8

【 义 1 】

【 义 2 】

【 図 3 】

【 図 4 】

【図5】

【 図 6 】

【 図 7 】

【 図 8 】

【 図 9 】

【 义 1 0 B 】

【図10A】

【 図 1 1 A 】

【 図 1 1 B 】

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | International Application No<br>PCT/US 03/07107                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>IPC 7 G06F1/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 G06F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Relevant to claim No.                                                          |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | US 5 471 625 A (CIRCELLIO JOSEPH C ET AL)<br>28 November 1995 (1995-11-28)<br>abstract<br>column 1, line 48 -column 2, line 27<br>column 3, line 29 -column 3, line 38<br>column 3, line 50 -column 3, line 60<br>column 4, line 58 -column 5, line 8<br>column 5, line 56 -column 6, line 13<br>column 8, line 4 -column 8, line 18<br>figures 1,3,4<br>---<br>EP 0 644 475 A (ADVANCED MICRO DEVICES<br>INC) 22 March 1995 (1995-03-22)<br>column 2, line 25 -column 2, line 57<br>column 7, line 13 -column 7, line 29<br>column 9, line 48 -column 10, line 8;<br>figures 2-6<br>---<br>-/- | 1-10<br>1-7,9,10                                                               |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| * Special categories of cited documents :<br>*A* document defining the general state of the art which is not considered to be of particular relevance<br>*E* earlier document but published on or after the international filing date<br>*L* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>*O* document referring to an oral disclosure, use, exhibition or other means<br>*P* document published prior to the international filing date but later than the priority date claimed                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                |

| *T* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention<br>*X* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone<br>*Y* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.<br>*&* document member of the same patent family |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                |

| Date of the actual completion of the international search<br><br>30 March 2004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Date of mailing of the international search report<br><br>06/04/2004           |

| Name and mailing address of the ISA<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Authorized officer<br><br>Leineweber, H                                        |

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/US 03/07107

| C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                            |                       |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category                                             | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                         | Relevant to claim No. |

| X                                                    | US 6 070 215 A (DESCHEPPER TODD J ET AL)<br>30 May 2000 (2000-05-30)<br>abstract<br>column 5, line 19 -column 5, line 28<br>column 5, line 50 -column 5, line 67<br>figures 2-4,7<br>----- | 6,7                   |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International Application No

PCT/US 03/07107

| Patent document cited in search report | Publication date | Patent family member(s)   |                           | Publication date |

|----------------------------------------|------------------|---------------------------|---------------------------|------------------|

| US 5471625                             | A 28-11-1995     | NONE                      |                           |                  |

| EP 0644475                             | A 22-03-1995     | US 6163848 A 19-12-2000   | US 5600839 A 04-02-1997   |                  |

|                                        |                  | EP 0644475 A2 22-03-1995  | JP 7152449 A 16-06-1995   |                  |

|                                        |                  | JP 7152450 A 16-06-1995   | AT 231254 T 15-02-2003    |                  |

|                                        |                  | DE 69529362 D1 20-02-2003 | DE 69529362 T2 30-10-2003 |                  |

|                                        |                  | EP 0679982 A1 02-11-1995  | JP 7302132 A 14-11-1995   |                  |

|                                        |                  | US 5628019 A 06-05-1997   |                           |                  |

| US 6070215                             | A 30-05-2000     | NONE                      |                           |                  |

---

フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT, BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA, GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ, EC,EE,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,M W,MX,MZ,NO,NZ,OM,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VC,VN,YU,ZA,ZM,ZW

(72)発明者 ミラー、ブライアン エム.

アメリカ合衆国 78717 テキサス州 オースティン ガレナ ドライブ 15150

(72)発明者 フィットシモンズ、マイケル ディー.

アメリカ合衆国 78731 テキサス州 オースティン ノース キャピタル オブ テキサス

ハイウェイ 7700 ナンバー 723

F ターム(参考) 5B061 BB01 BC01 RR03 SS03

5B079 AA02 BA12 BC01