# (10) **DE 11 2010 002 334 T5** 2012.08.02

(12)

# Veröffentlichung

der internationalen Anmeldung mit der

(87) Veröffentlichungs-Nr.: WO 2011/003677

in deutscher Übersetzung (Art. III § 8 Abs. 2 IntPatÜG)

(21) Deutsches Aktenzeichen: 11 2010 002 334.4

(86) PCT-Aktenzeichen: **PCT/EP2010/057678**

(86) PCT-Anmeldetag: 02.06.2010

(87) PCT-Veröffentlichungstag: 13.01.2011

(43) Veröffentlichungstag der PCT Anmeldung in deutscher Übersetzung: **02.08.2012**

(30) Unionspriorität:

12/500,490 09.07.2009 US

(71) Anmelder:

International Business Machines Corp., Armonk, N.Y., US

(74) Vertreter:

RICHARDT PATENTANWÄLTE, 65185, Wiesbaden, DF

(51) Int Cl.: **G11B 5/584** (2012.01)

(72) Erfinder:

JELITTO, Jens, CH-8803 Rueschlikon, CH; Hutchins, Robert Allen, Tucson, Arizona 95730, US; Sandberg, Melanie Jean, Tucson, Ariz., US; CHERUBINI, Giovanni, CH-8803 Rüschlikon, CH

(54) Bezeichnung: Steuerungsverfahren und Vorrichtung für ein Dualkanal-gewichtetes LPOS-Kombinierungsschema

(57) Zusammenfassung: Verfahren zur Überwachung einer Vielzahl von Servokanälen, Bereitstellen eines endlichen Automatens (FSM) umfassend eine Einzelservokanal-Betriebsart und eine kombinierte Servokanal-Betriebsart und Bewegen eines sequenziellen Informationsspeicherungsmediums, das eine Vielzahl von Servobändern umfasst, über einen Lese-/Schreibkopf, der eine entsprechende Vielzahl von Servosensoren umfasst. Das Verfahren setzt ferner einen Erfassungsflag durch einen Servokanal, wenn dieser Servokanal einem Servomuster folgt, und ersetzt einen Bitflag durch einen Servokanal, wenn ein neuer LPOS-Bit decodiert wurde. Wenn zumindest ein Erfassungsflag gesetzt ist, bestimmt das Verfahren, ob ein Bitflag durch einen mit dem gesetzten Erfassungsflag assoziierten Servokanal gesetzt wurde, und ob ein Erfassungsflag und ein Bitflag durch einen Servokanal gesetzt wurde. Das Verfahren bestimmt eine relative Positionierung jedes Servosensors in Bezug auf ein assoziiertes Servomuster.

### **Beschreibung**

# Gebiet der Erfindung

**[0001]** Die Erfindung der Anmelderin bezieht sich im Allgemeinen auf ein Verfahren zur Überwachung mehrerer Servokanäle, wo ein Steuerungsschema zwischen einer Einzelservokanal-Betriebsart und einer kombinierten Servokanal-Betriebsart schaltet.

#### Hintergrund der Erfindung

[0002] Ein Timing-basierter Servo (TBS) ist eine Technologie, die für lineare Bandlaufwerke entwickelt wurde. In TBS-Systemen bestehen aufgenommene Servomuster aus Übergängen mit zwei verschiedenen azimutalen Steigungen. Laterale Lese-/Schreibkopfpositionen werden von dem relativen Timing detektierter Pulse oder 2-Bit-Einheiten abgeleitet, die durch eine Vielzahl von Servosensoren gemessen werden, die auf dem Lese-Schreibkopf angeordnet sind. TBS-Muster erlauben auch die Codierung zusätzlicher Informationen von longitudinalen Positionen ("LPOS"), ohne die Erzeugung der transversalen Positionsfehlersignale ("PES") zu beeinträchtigen. Dies wird dadurch erreicht, dass die Übergänge von ihren nominalen Musterpositionen unter Verwendung von Pulspositionsmodulationen ("PPM") verschoben werden. Eine Spezifikation für das Servoformat in gegenwärtigen Mittelbandlaufwerken wird durch das lineare Tape Open("LTO")-Format bereitgestellt. Das komplette Format für LTO-Laufwerke der ersten Generation (LTO-1) wurde durch die European Computer Manufacturers Association ("ECMA") 2001 als ECMA-319 standardisiert.

[0003] In Bandlaufwerken sind normalerweise zwei dedizierte Servokanäle verfügbar, von denen LPOS-Informationen und PES abgeleitet werden können. Ein Signal eines Servokanals kann schwächer werden, während das andere Signal des anderen Servokanals nicht detektiert werden kann. In solch einem Fall verliert der durch das Schwächerwerden beeinträchtigte Servokanal das Timing und muss einer Neuerfassung unterzogen werden. Als Konsequenz entstehen zusätzliche Latenzzeiten und der Verlust von Informationen.

## Zusammenfassung der Erfindung

[0004] Es Liegt ein Bedürfnis für ein Verfahren zur Steuerung von einem Servokanal vor, das Betriebsarten kombiniert, die auf dem Status der individuellen Servokanäle und einer Timing-Beziehung (Bitversatz) zwischen den Servosginalen basiert. In einer Ausführungsform wird ein Verfahren zur Überwachung einer Vielzahl von Servosignalen präsentiert, bei dem ein Steuerungsschema zwischen einer Einzelservokanal-Betriebsweise und einer kombinierten Servokanal-Betriebsweise umschaltet. Zunächst hat

ein sequenzielles Informationsspeicherungsmedium mehrere Servobänder, die an einem Lese-/Schreibkopf vorbeibewegt werden, mit entsprechenden Servosensoren. Als Nächstes detektiert das Verfahren, ob ein oder mehrere Erfassungsflags gesetzt sind, wobei jeder gesetzte Flag indiziert, dass ein assozierter Servokanal einem Servomuster folgt. Wenn zumindest ein Erfassungsflag gesetzt ist, detektiert das Verfahren, ob ein Bitflag für den Servokanal gesetzt ist, der mit dem gesetzten Erfassungsflag assoziiert ist, wobei jeder Bitflag die Verfügbarkeit eines neuen LPOS-Bits indiziert. Zuletzt wird eine relative Position für jeden Servosensor in Bezug auf ein assoziiertes Servomuster bestimmt, wenn zumindest ein Bitflag gesetzt ist.

[0005] In einer anderen Ausführungsform wird eine Vorrichtung präsentiert, die ein computerlesbares Medium hat, auf dem sich computerlesbarer Programmcode befindet, um mehrere Servosignale zu überwachen, wobei ein Steuerungsschema zwischen einer Einzelservokanal-Betriebsart und einer kombinierten Servokanal-Betriebsart schaltet. Der computerlesbare Programmcode umfasst eine Serie von computerlesbaren Programmschritten, um ein sequenzielles Informationsspeichermedium mit mehreren Servobändern an einem Lese-/Schreibkopf mit entsprechenden Servosensoren vorbeizuführen, um zu detektieren, ob ein oder mehrere Erfassungsflags gesetzt sind, wobei jeder gesetzter Erfassungsflag indiziert, dass ein assoziierter Servokanal einem Servomuster folgt, wenn zumindest ein Erfassungsflag gesetzt ist, um zu detektieren, ob ein Bitflag für den Servokanal gesetzt ist, der mit dem gesetzten Erfassungsflag assoziiert ist, wobei jeder Bitflag indiziert, dass ein neues LPOS-Bit verfügbar ist; und wenn zumindest ein Bitflag gesetzt ist, wird eine relative Position für jeden der Servosensoren in Bezug auf ein assoziiertes Servomuster bestimmt.

[0006] Bei noch einer anderen Ausführungsform wird ein Computerprogrammprodukt präsentiert, das in einem computerlesbaren Medium codiert ist und mit einem programmierbaren Computerprozessor genutzt werden kann, um eine Vielzahl von Servosignalen zu überwachen, wobei ein Steuerungsschema zwischen einer Einzelservokanal-Betriebsart und einer kombinierten Servokanal-Betriebsart schaltet. Das Computerprogrammprodukt umfasst computerlesbaren Programmcode, der den programmierbaren Prozessor zu Folgendem veranlasst: Bewegen eines seguenziellen Informationsspeichermediums mit mehreren Servobändern vorbei an einem Lese-/Schreibkopf mit mehreren entsprechenden Servosensoren, Detektieren, ob ein oder mehrere Erfassungsflags gesetzt sind, wobei jeder gesetzte Erfassungsflag indiziert, dass ein assoziierter Servokanal einem Servomuster folgt, wenn zumindest ein Erfassungsflag gesetzt ist, Detektieren, ob ein Bitflag für den Servokanal gesetzt ist, der mit dem gesetzten

# DE 11 2010 002 334 T5 2012.08.02

Erfassungsflag assoziiert ist, wobei jeder Bitflag die Verfügbarkeit eines neuen LPOS-Bits indiziert; und wenn zumindest ein Bitflag gesetzt ist, Bestimmen einer relativen Position mit Bezug auf ein assoziiertes Servomuster für jeden der Servosensoren.

**[0007]** Bei noch einer weiteren Ausführungsform wird eine Datenspeicherungsvorrichtung mit mehreren Servosensoren und entsprechenden Servosteuerungseinheiten präsentiert.

**[0008]** Jede Servosteuerungseinheit umfasst einen Erfassungsflag, der indiziert, dass der Servokanal ein Servomuster erfasst, ein Bitflag, das die Verfügbarkeit eines neuen LPOS-Bits indiziert und einen Servosensor-Positionsindikator ("SRPI"), der eine Position eines Servolesers innerhalb eines Servoframes anzeigt.

[0009] Bei noch einer anderen Ausführungsform wird eine Datenspeicherungsbibliothek präsentiert, die mehrere Datenspeicherungsvorrichtungen umfasst, wobei jede Datenspeicherungsvorrichtung mehrere Servosensoren und entsprechende Servosteuerungseinheiten hat. Jede Servosteuerungseinheit umfasst einen Erfassungsflag, der indiziert, dass der Servokanal ein Servomuster erfasst hat, ein Bitflag, der die Verfügbarkeit eines neuen LPOS-Bits indiziert, und einen Servosensor-Positionsindikator ("SRPI"), der eine Position eines Servolesers innerhalb eines Servoframes anzeigt.

# Kurze Beschreibung der Figuren

**[0010]** Die Erfindung wird durch Lesen der folgenden detaillierten Beschreibung in Verbindung mit den Figuren, bei denen gleiche Bezugszeichen für die Bezeichnung gleicher Elemente verwendet werden, besser verstanden, wobei:

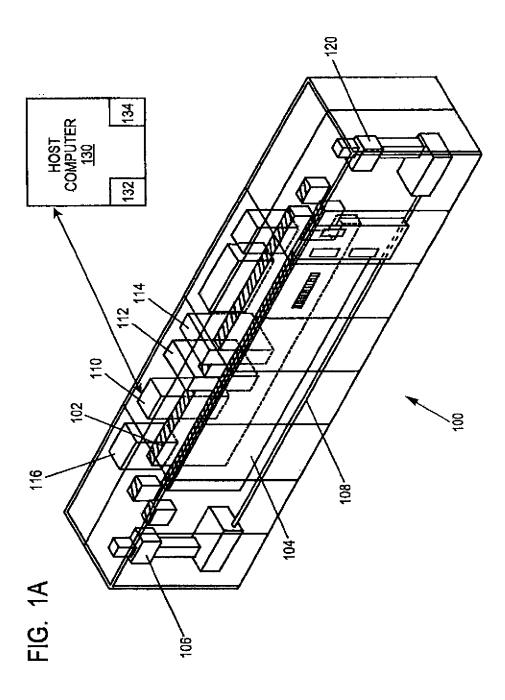

**[0011]** Fig. 1a eine Ausführungsform eines Datenspeicherungssystem der Anmelderin darstellt;

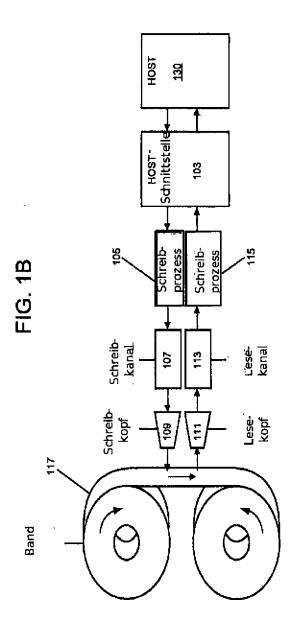

**[0012]** Fig. 1b ein Blockdiagramm einer Ausführungsform einer Datenspeicherungsvorrichtung der Anmelderin ist, in die die vorliegende Erfindung implementiert werden kann;

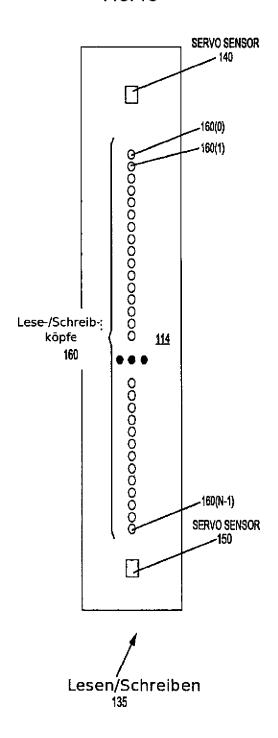

**[0013]** Fig. 1c Elemente des Lese-/Schreibkopfs der Anmelderin darstellt;

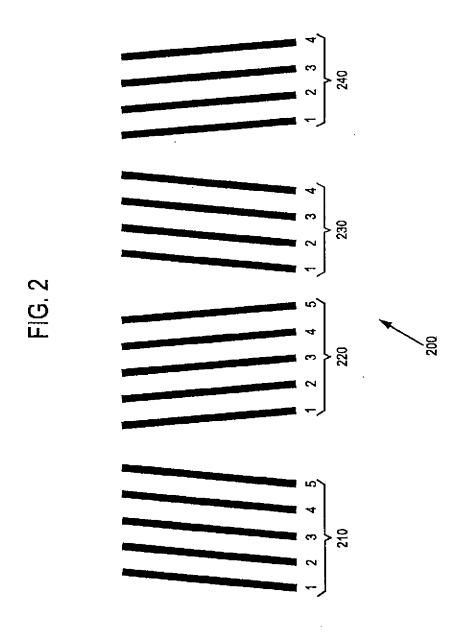

[0014] Fig. 2 eine Ausführungsform eines Servomusters der Anmelderin darstellt, wobei das Servomuster vier Bursts umfasst, wobei jeder dieser vier Bursts eine Vielzahl von Pulsen umfasst;

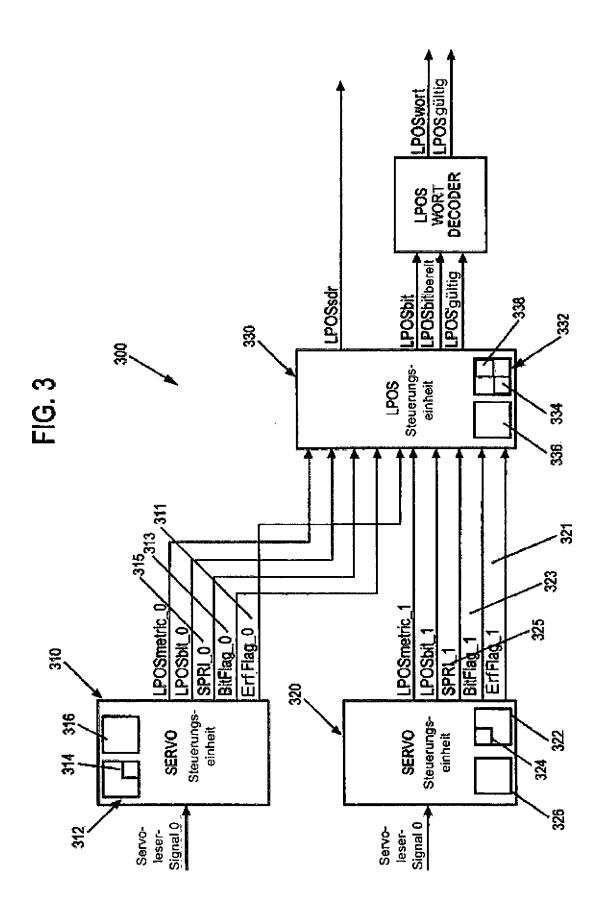

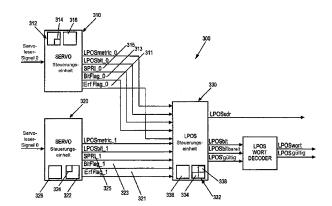

**[0015]** Fig. 3 ein Blockdiagramm ist, das bestimmte Elemente der Datenspeicherungsvorrichtung der Anmelderin darstellt;

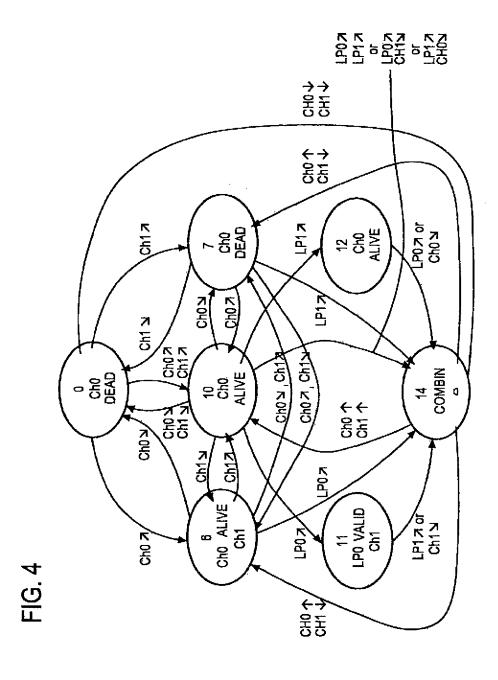

**[0016]** Fig. 4 ein Blockdiagramm einer Ausführungsform eines endlichen Automaten der Anmelderin;

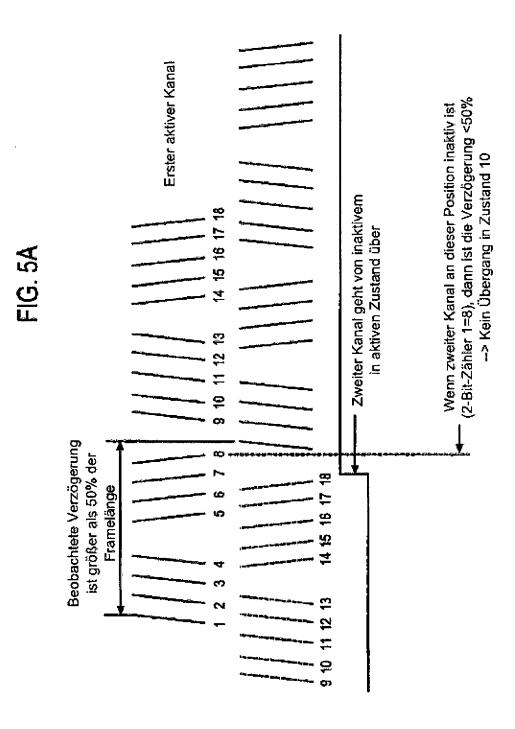

**[0017]** Fig. 5a eine Anordnung von Servoframes zeigt, wenn der zweite Servokanal bezüglich des ersten Servokanals um weniger als fünfzig (50) Prozent der Länge des Servoframes verzögert ist; und

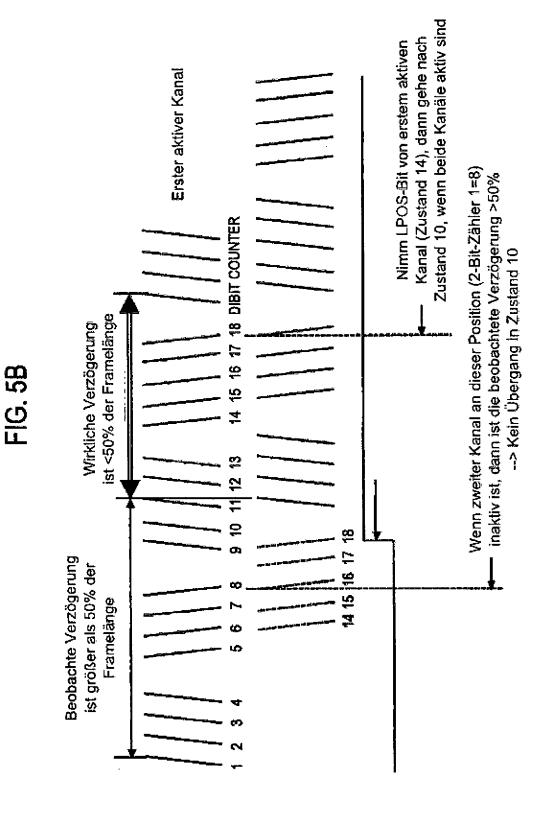

**[0018]** Fig. 5b eine Anordnung von Servoframes zeigt, wenn der zweite Servokanal gegenüber dem ersten Servokanal um mehr als fünfzig (50) Prozent der Länge des Servoframes verzögert ist.

# Detaillierte Beschreibung bevorzugter Ausführungsformen

[0019] Diese Erfindung wird in der folgenden Beschreibung anhand bevorzugter Ausführungsformen mit Bezugnahme auf die Figuren, in denen gleiche Nummern dieselben oder ähnliche Elemente repräsentieren, beschrieben. Innerhalb dieser Spezifikation bedeutet eine Bezugnahme auf "eine Ausführungsform" oder eine ähnliche Sprache, dass ein bestimmtes Merkmal, Struktur oder Charakteristik, die in Verbindung mit der Ausführungsform beschrieben werden, durch zumindest eine Ausführungsform der vorliegenden Erfindung umfasst werden. Daher können in dieser Spezifikation Ausdrücke wie "in einer Ausführungsform" und ähnliche Sprache auf dieselbe Ausführungsform Bezug nehmen, obwohl dies nicht notwendigerweise so sein muss.

[0020] Die beschriebenen Merkmale, Strukturen oder Charakteristiken der Erfindung können in irgendeiner passenden Weise in einer oder mehreren Ausführungsformen kombiniert werden. In der folgenden Beschreibung werden zahlreiche spezifische Details erwähnt, um ein ausführliches Verständnis der Ausführungsformen der Erfindung zu ermöglichen. Ein Fachmann wird trotzdem erkennen, dass die Erfindung ohne eines oder mehrere der spezifischen Details oder mit anderen Verfahren, Komponenten, Materialien usw. ausgeführt werden kann. In anderen Fällen werden wohlbekannte Strukturen, Materialien oder Betriebsarten nicht im Detail gezeigt oder beschrieben, um unklare Aspekte der Erfindung zu vermeiden.

**[0021]** Fig. 4 wird als logisches Flussdiagramm dargelegt. Als solches ist die dargestellte Rangfolge und die bezeichneten Schritte ein Hinweis auf eine Ausführungsform des präsentierten Verfahrens. Andere Schritte und Verfahren, die in Funktion, Logik oder Effekt äquivalent zu einem oder mehrerer Schritte oder ihrer Positionen des dargestellten Verfahrens, können konzipiert werden. Zusätzlich sollen das verwendete Format und die Symbole die logischen Schritte des Verfahrens erklären und sollen nicht so verstanden werden, dass sie den Umfang des Verfahrens begrenzen. Obwohl verschiedene Pfeiltypen und Li-

nientypen in den Flussdiagrammen verwendet werden können, sollen sie nicht so verstanden werden, dass sie den Umfang des entsprechenden Verfahrens begrenzen. In der Tat können einige Pfeile oder andere Verbindungselemente dazu genutzt werden, nur den logischen Fluss des Verfahrens zu bezeichnen. Zum Beispiel kann ein Pfeil eine Warte- oder Überwachungsperiode einer unbestimmten Zeitdauer zwischen den aufgezählten Schritten des dargestellten Verfahrens initiieren. Zusätzlich kann die Reihenfolge, in der ein bestimmtes Verfahren durchgeführt wird, sich streng nach der Reihenfolge der entsprechenden dargestellten Schritte richten oder auch nicht.

[0022] Fig. 1 zeigt ein Datenspeicherungssystem 100 mit einer Speichersteuerungseinheit 110, Datenspeicherungsvorrichtungen 112 und 114 und DASD 116. Das System 100 umfasst ferner eine Vielzahl von sequenziellen Datenspeicherungsmedien, die herausnehmbar in einer Vielzahl von Speicherungsslots angeordnet sind, die wiederum in einer ersten Speicherungswand 102 und/oder einer zweiten Speicherungswand 104 angeordnet sind. Das System **100** umfasst auch zumindest einen robotischen Zugriffsberechtigten 106/120 zum Transport eines spezifizierten sequenziellen Datenspeicherungsmediums zwischen einem Speicherungsslot, der in der Speicherungswand 102/104 angeordnet ist und einer Datenspeicherungsvorrichtung 112 oder 114. Die Zugriffsberechtigten sind bewegbar entlang der Schiene 108 angeordnet.

[0023] In der dargestellten Ausführungsform von Fig. 1a umfasst ein Host-Computer 130 ein Speichermanagementprogramm ("SMP") 132. In bestimmten Ausführungsformen managt dieses Speichermanagementprogramm, zum Beispiel und ohne Begrenzung das IBM Data Facility Storage Management Subsystem("DFSMS")-Speichermanagementprogramm, implementiert in dem IBM Multiple Virtual Storage("MVS")-Betriebssystem, den Datentransfer zu und von einem Datenspeicherungssystem, wie zum Beispiel System 100. in der dargestellten Ausführungsform von Fig. 1 umfasst der Host-Computer 130 ferner ein Bandmanagementsystem (Tape Management System, "TMS") 134. in bestimmten Ausführungsformen ist das TMS in das Speichermanagementprogramm integriert. In bestimmten Ausführungsformen umfasst das TMS ein IBM Removable Media Manager-Programm.

[0024] Fig. 1b ist ein Blockdiagramm, das bestimmte Elemente der Datenspeicherungsvorrichtung der Anmelderin, wie zum Beispiel die Datenspeicherungsvorrichtungen 112 und 114 aus Fig. 1a, zeigt. In der dargestellten Ausführungsform von Fig. 1a kommunizieren die Datenspeicherungsvorrichtungen 112 und 114 mit dem Host-Computer 130. In der dargestellten Ausführungsform von Fig. 1b kommunizieren ein

Schreibverarbeitungsmodul 105 und ein Leseverarbeitungsmodul 115 mit dem Host-Computer 130 über die Host-Schnittstelle 103, über die Daten und Befehle kommuniziert werden. Zu schreibende Daten werden in einem Schreibverarbeitungsmodul 105 und einem Schreibkanal 107 verarbeitet, bevor sie durch den Schreibkopf 109 auf ein sich bewegendes sequenzielles Datenspeichermedium, wie zum Beispiel das Band 117, geschrieben werden. Die Daten werden vom Band 117 durch den Lesekopf 111 gelesen und durch einen Lesekanal 113 und ein Leseverarbeitungsmodul 115 verarbeitet, bevor sie an den Host-Computer 130 über die Host-Schnittstelle 103 übermittelt werden. Das sequenzielle Datenspeicherungsmedium 117 umfasst eine Vielzahl von parallelen Datenspuren in Kombination mit einer Vielzahl von Servomustern, die in einem nicht für Daten bestimmten Teilbereich des Speichermediums codiert werden. Diese Servomuster werden dafür genutzt, Positionsfehlersignale (Position Error Signal, "PES") zu erzeugen, um einen Lese-/Schreibkopf lateral in Bezug auf die Vielzahl von Datenspuren zu positionieren, und um eine longitudinale Position ("LPOS") entlang der Länge des Mediums zu bestimmen. In Bezugnahme auf Fig. 1c umfasst der Lese-/Schreibkopf 135, der aus dem Schreibkopf 109 und dem Lesekopf 111 (Fig. 1b) besteht, mehrere Elemente, um simultan Daten von mehreren Datenspuren zu lesen. Der Lese-/Schreibkopf 135 umfasst ferner eine Vielzahl von Servoelementen, um Servosignale von den Servobändern zu detektieren. Zum Beispiel kann der Lese-/Schreibkopf zwei Servoelemente umfassen, um die Servomustern auf zwei Servobänder zu detektieren, zwischen denen parallele Datenspuren codiert sind.

[0025] Fig. 1c zeigt eine Oberfläche 114 eines Lese-/Schreibkopfs 135, wobei die Oberfläche 114 dem sequenziellen Datenspeichermedium 117 (Fig. 1b) zugewandt ist, während das Medium über den Lese-/Schreibkopf 135 bewegt wird. In der dargestellten Ausführungsform von Fig. 1c umfasst der Lese-/Schreibkopf 135 (N) Lese-/Schreibkopfelemente (160). In bestimmten Ausführungsformen wird (N) aus der Gruppe bestehend aus 8, 16, 32 und 64 gewählt. Ein Fachmann wird merken, dass der Lese-/Schreibkopf 135 zusätzliche Elemente umfassen kann, die in Fig. 1c nicht gezeigt sind.

[0026] In der dargestellten Ausführungsform von Fig. 1c umfasst der Lese-/Schreibkopf 135 einen Servosensor 140, Servosensor 150 und (N) Lese-/Schreibkopfelemente 160, die zwischen dem Servosensor 140 und Servosensor 150 angeordnet sind. Während das sequenzielle Bandmedium 117 (Fig. 1b) über den Lese-/Schreibkopf 135 bewegt wird, wird eine laterale Position des Lese-/Schreibkopfs aus den relativen Timings der Pulse hergeleitet, die durch den Servosensor 140 und/oder Servosensor 150 detektiert wurden.

[0027] In Fig. 2 umfasst das Servosensor 200 Übergänge, die eine von zwei verschiedenen azimutalen Steigungen umfassen. Die laterale Position des Lese-/Schreibkopfs wird von dem relativen Timing der Pulse abgeleitet, die durch einen oder beide Servosensoren detektiert werden. Das Servomuster 200 umfasst einen ersten Burst 210 mit fünf (5) Pulsen, wobei jeder dieser fünf (5) Pulse eine erste azimutale Steigung umfasst. Das Servomuster 200 umfasst ferner einen zweiten Burst 220 mit fünf (5) Pulsen, wobei jeder dieser fünf (5) Pulse eine zweite azimutale Steigung umfasst. Das Servomuster 200 umfasst ferner einen dritten Burst 230 mit vier (4) Pulsen, wobei jeder dieser vier (4) Pulse eine erste azimutale Steigung umfasst. Das Servomuster 200 umfasst ferner einen vierten Burst 240 mit vier (4) Pulsen, wobei jeder dieser vier (4) Pulse die zweite azimutale Steigung umfasst.

[0028] Die vorliegende Erfindung bietet ein Steuerungsschema, um die Verfügbarkeit und den Status der individuellen Servokanäle zu identifizieren, und vereinfacht ein nahtloses Schalten zwischen einer Einzelservokanal-Betriebsart und einer kombinierten Servokanal-Betriebsart, indem die individuellen Servokanäle aktiv oder inaktiv werden. In bestimmten Ausführungsformen überwacht das Steuerungsschema der Anmelderin den Status zweier Servokanäle, um den korrekten Input für das gewichtete Kombinierungsschema zu liefern Das Steuerungsschema der Anmelderin umfasst die in Fig. 3 erwähnten Komponenten, die den endlichen Automaten aus Fig. 4 implementieren.

[0029] In Fig. 3 empfängt die LPOS-Steuereinheit 330 den Output der Servosteuerungseinheit 310 und der Servosteuerungseinheit 320. In der dargestellten Ausführungsform von Fig. 3 umfasst die LPOS-Steuereinheit 330 einen Prozessor 336 und einen Speicher 332 mit Instruktionen 334 und einem Kombinierungsalgorithmus 338, der darin codiert ist.

[0030] Ferner umfasst die Servosteuerungseinheit 310 in der dargestellten Ausführungsform von Fig. 3 einen Prozessor 316 und einen Speicher 312 mit Instruktionen 314, die darin codiert sind. Ferner umfasst die Servosteuerungseinheit 320 in der dargestellten Ausführungsform von Fig. 3 einen Prozessor 326 und einen Speicher 322 mit Instruktionen 324, die darin codiert sind.

[0031] Jede Servosteuerungseinheit kann an die LPOS-Steuereinheit 330 einen Erfassungsflag 311/321, einen Bitflag 313/323 und einen Servosensor-Positionsindikator ("SRPI") 315/325 ausgeben. Der Erfassungsflag 311/321 indiziert, dass ein Servomuster erfasst wurde. Falls der Erfassungsflag gesetzt ist, folgt der Servokanal einem Servomuster und gibt regelmäßig Servokanalparameter-Updates aus (LPOS-Bit, Verlässlichkeitsinformationen, etc.).

[0032] Der Bitflag 313/323 indiziert die Verfügbarkeit eines neuen und gültigen LPOS-Bits und die assozierte Verlässlichkeitsinformation am Ende jedes Servoframes. Ein SRPI 315/325 indiziert eine gegenwärtige Position des Servolesers innerhalb eines Servoframes.

[0033] Die Erfassungsflags 311/321, die Bitflags 313/323 und die Servosensor-Positionsindikatoren ("SRPI") 315/325 werden an die LPOS-Steuereinheit 330 ausgegeben. Die LPOS-Steuereinheit 330 implementiert einen endlichen Automaten (Finite State Machine, "FSM") mit mehreren Zwischenstadien, die von einer Veränderung des Status der Servokanäle abhängen.

[0034] Fig. 4 stellt einen FSM 400 der Anmelderin dar. Der FSM 400 der Anmelderin umfasst eine endliche Anzahl an Zuständen, Übergänge zwischen diesen Zuständen und Aktionen. Nach einem Reset wird der FSM 400 in einen Anfangsruhezustand 0 gesetzt. Im Anfangsruhezustand 0 sind beide Servokanäle, Servokanal 0 und Servokanal 1, inaktiv. in bestimmten Ausführungsformen umfasst der Servokanal 0 Signale, die auf einer Servosignaldetektion durch Servosensor 140 (Fig. 1c) basieren. In bestimmten Ausführungsformen umfasst der Servokanal 1 Signale, die auf einer Servosignaldetektion durch den Servosensor 150 (Fig. 1c) basieren.

[0035] Wenn ein Erfassungsflag für einen oder beide der Servokanäle gesetzt ist, der indiziert, dass der assoziierte Servokanal (die assoziierten Servokanäle) aktiv geworden sind und ein gültiges Servomuster erfasst haben, wird ein Übergang in dem FSM in einen der drei Zwischenzustände 6, 7 oder 10 durchgeführt.

[0036] Der Zwischenzustand 6 wird angenommen, wenn nur der Erfassungsflag 311 gesetzt ist, was bedeutet, dass der Servokanal 1 aktiv geworden ist, aber der Servokanal 1 inaktiv bleibt. In ähnlicher Weise wird der Zwischenzustand 7 angenommen, wenn nur der Erfassungsflag 321 für den Servokanal 1 gesetzt ist, was bedeutet, dass der Servokanal 1 aktiv geworden ist, während der Servokanal 0 inaktiv bleibt. Zuletzt wird der Zwischenzustand 10 angenommen, wenn die Erfassungsflags 311 und 321 für beide Servokanäle gesetzt sind, was bedeutet, dass sowohl Servokanal 0 als auch Servokanal 1 aktiv ist. Ein Übergang vom Anfangsruhezustand 0 zum Zwischenzustand 10 initiiert, das Nichtvorhandensein eines Bitversatzes, das heißt, dass beide Servokanäle simultan ein gültiges Servomuster detektieren. Dies tritt wahrscheinlich dann auf, wenn die in beiden Servokanälen codierten Servomuster aufeinander abgestimmt sind.

[0037] Der FSM 400 wird in einem Zwischenzustand 6, 7 oder 10 bleiben, bis ein Bitflag gesetzt wird

und/oder der Status der Servokanäle sich verändert. Wenn zum Beispiel zunächst beide Servokanäle zum gleichen Zeitpunkt aktiv werden und den Zwischenzustand 10 annehmen, wird der FSM 400 im Zwischenzustand 10 bleiben, bis ein Bitflag empfangen wird oder bis einer der beiden Servokanäle inaktiv wird. Wenn zum Beispiel der Servokanal 1 inaktiv wird, wird der FSM 400 vom Zwischenzustand 10 in den Zwischenzustand 6 übergehen. Der FSM 400 wird wieder in dem Zwischenzustand 6 bleiben bis eine Veränderung im Servokanalstatus stattfindet oder, wie es weiter unten diskutiert wird, ein Bitflag von dem aktiven Servokanal, Servokanal 0, empfangen wird.

[0038] Wenn der FSM 400 entweder im Zwischenzustand 6 oder im Zwischenzustand 7 ist und ein zweiter Servokanal innerhalb eines vorbestimmten Zeitintervalls aktiv wird, geht der FSM 400 in den Zwischenzustand 10 über. In ähnlicher Weise wird ein Übergang in den Ursprungsruhezustand 0 durchgeführt, wenn der FSM 400 entweder im Zwischenzustand 6 oder im Zwischenzustand 7 ist und der aktive Servokanal inaktiv wird.

[0039] Wenn beide Servokanäle aktiv sind, bleibt der FSM im Zustand 10 bis einer der beiden Servokanäle ein Bitflag setzt, das die Detektion eines neuen LPOS-Bits indiziert. Wenn beide Servokanäle die Detektion eines neuen LPOS-Bits gleichzeitig indizieren, wird der Kombinierungszustand 14 angenommen und die Information von jedem Servokanal kann durch Verwendung des LPOS-Kombinierungsalgorithmus 338 (Fig. 3) verwendet werden.

[0040] Die Zwischenzustände 11 und 12 werden aus dem Zwischenzustand 10 angenommen, wenn ein Bitflag für nur einen der Servokanäle gesetzt wird und wenn beide Servokanäle aktiv sind. Wenn zum Beispiel der FSM 400 im Zustand 10 ist und das Bitflag 313 für den Servokanal 0 gesetzt ist, wird der Zwischenzustand 11 angenommen. In ähnlicher Weise wird der Zwischenzustand 12 angenommen, wenn das Bitflag 321 für den Servokanal 1 gesetzt ist. Der FSM 400 verbleibt im Zwischenzustand 11 oder 12 bis ein Bitflag für den zweiten Servokanal detektiert wird.

**[0041]** Nach der Detektion des zweiten neuen LPOS-Bits wird der Zwischenzustand 14 angenommen und die Information von jedem Servokanal kann durch den LPOS-Kombinierungsafgorithmus **338** (Fig. 3) verwendet werden.

[0042] Wenn der FSM 400 in einem Zwischenzustand 6 oder 7 ist, kann ein Bitflag nicht von dem inaktiven Kanal detektiert werden. Daher geht der FSM 400 direkt in den Kombinierungszustand 14 über, wenn ein Bitflag von dem aktiven Kanal detektiert wird. In solch einer Situation nutzt der LPOS-Kombi-

nierungsalgorithmus **338** (<u>Fig. 3</u>) nur die LPOS-Bitinformation des aktiven Servokanals.

[0043] Nachdem der LPOS-Kombinierungsalgorithmus 338 ausgeführt wurde, wird der Zustand beider Servokanäle kontrolliert und der passende Zwischenzustand wird angenommen. Falls beide Servokanäle immer noch aktiv sind, geht der FSM 400 vom Kombinierungszustand 14 in den Zwischenzustand 10 über. Wenn nur ein Servokanal aktiv ist, geht der FSM 400 vom Kombinierungszustand 14 entweder in den Zustand 6 oder 7 über. Zuletzt geht der FSM 400 vom Kombinierungszustand 14 in den Anfangsruhezustand 0 über, wenn beide Kanäle inaktiv sind.

[0044] In bestimmten Ausführungsformen können individuelle Übergänge, die in Verbindung mit Fig. 4 erwähnt wurden, kombiniert, eliminiert oder neu geordnet werden. In bestimmten Ausführungsformen sind die Instruktionen 334 (Fig. 3) in einem computerlesbaren Medium 332 (Fig. 3) codiert, wobei diese Instruktionen durch einen Prozessor 336 (Fig. 3) ausgeführt werden, um den FSM 400 (Fig. 4) zu implementieren.

[0045] In anderen Ausführungsformen umfasst die Erfindung Instruktionen, die in irgendeinem anderen Computerprogrammprodukt angeordnet sind, wobei diese durch einen Computer ausgeführt werden, der extern oder intern in Bezug auf das Datenspeicherungssystem ist, um den FSM 400 zu implementieren. in beiden Fällen können Instruktionen in einem computerlesbaren Medium codiert sein, das zum Beispiel ein magnetisches Informationsspeichermedium, ein optisches Informationsspeichermedium, ein elektronisches Informationsspeichermedium und Ähnliches sein kann. "Elektronische Speichermedien" können zum Beispiel und ohne Begrenzung eine oder mehrere Vorrichtungen meinen, wie zum Beispiel und ohne Begrenzung ein PROM, EPROM, EEPROM, Flash-PROM, Compact Flash, Smartmedia und Ähnliches.

[0046] Die zuvor in Verbindung mit dem FSM 400 beschriebenen Zustandsübergänge können wiederholt werden, während die Servokanäle gelesen werden. Daher wird das System kontinuierlich zwischen den Zuständen des FSM 400 übergehen, während die Servokanäle gelesen werden, indem Erfassungsflags und Bitflags detektiert werden.

**[0047]** Zum Beispiel, aber nicht ausschließlich, kann eine typische Zustandssequenz des FSMs, wenn beide Servokanäle aktiv sind und Servokanal 0 vor Servokanal 1 ist, sein:

$$10 \rightarrow 11 \rightarrow 14 \rightarrow 10 \rightarrow 11 \rightarrow 14 \rightarrow 10 \ ...$$

**[0048]** Eine andere typische Zustandssequenz, wenn beide Servokanäle aktiv sind und Servokanal 1 vor Servokanal 0 ist, kann sein:

$10 \rightarrow 12 \rightarrow 14 \rightarrow 10 \rightarrow 12 \rightarrow 14 \rightarrow 10 \dots$

**[0049]** Wenn Servokanal 0 aktiv ist und Servokanal 1 inaktiv ist, ist eine typische Statussequenz:  $6 \rightarrow 14 \rightarrow 6 \rightarrow 14 \rightarrow 6 \dots$

**[0050]** Ein anderes Beispiel einer typischen Statussequenz, bei der beide Servokanäle aktiv sind und neue LPQS-Bitinformationen durch Servokanal 0 indiziert wird, bevor der Servokanal 1 inaktiv wird, ist:  $10 \rightarrow 11 \rightarrow 14 \rightarrow 6 \rightarrow 14 \rightarrow 6 \rightarrow 14 \rightarrow 6 \dots$

[0051] Der FSM 400 ist so ausgebildet, dass er unter Vorhandensein eines großen zeitabhängigen Bitversatzes zwischen den beiden Servokanälen betrieben werden kann, ohne dass explizites Wissen über den Bitversatz nötig ist. Insbesondere ermöglicht das Steuerungsschema einen Bitversatz zwischen den Servokanälen von bis zu ±100 µm für standardisierte TBS-Muster oder fünfzig (50) Prozent der Servoframelänge.

[0052] Besonders wenn das Servoformat und die Anordnung des Bandpfades garantieren, dass der Bitversatz unterhalb von fünfzig (50) Prozent der Servoframelänge gehalten wird, wird eine Mehrdeutigkeit der Servokanalabgleichung ohne explizites Wissen des Bitversatzes vermieden. In Fig. 4 ist die kritische Phase für eine korrekte Servokanalabgleichung beim ersten Übergang zum Zwischenzustand 10 aus dem Zwischenzustand 6 oder Zwischenzustand 7. In dieser Phase ist nur ein Kanal schon aktiv und der zweite Kanal wird aktiv. Um die Informationen der beiden Kanäle korrekt abzugleichen, werden die jeweiligen Framegrenzen der beiden Servokanäle analysiert, wobei Informationen über die Framekanäle von einem SRPI für jeden Kanal empfangen werden.

[0053] Wie in Fig. 5a gezeigt wird, findet ein Übergang vom Zwischenzustand 6 oder Zwischenzustand 7 (Fig. 4) in den Zwischenzustand 10 (Fig. 4) statt, wenn ein zweiter Servokanal, der aktiv werden soll, hinter dem ersten Servokanal um weniger als fünfzig (50) Prozent des Servoframes verzögert ist. In diesem Falle werden beide Kanäle für die LPOS-Bitdetektion verwendet. Alternativ wird kein Übergang in den Zwischenzustand 10 (Fig. 4) für den gegenwärtigen Servoframe durchgeführt, wenn der zweite Servokanal gegenüber dem ersten Servokanal um mehr als fünfzig (50) Prozent des Servoframes verzögert ist (das heißt, dass der zweite Servokanal einen Vorsprung hat).

**[0054]** Ein Übergang vom Zwischenzustand 6 (Fig. 4) oder Zwischenzustand 7 (Fig. 4) in den Kombinierungszustand 14 wird vielmehr dann ausgeführt, sobald ein Bitflag von dem ersten aktiven Servokanal detektiert wird, das heißt, dass neue LPOS-Bitinformationen für den ersten aktiven Servokanal verfüg-

bar sind. Dieses letztere Szenario wird in Fig. 5b dargestellt.

**[0055]** Wie mit Bezugnahme auf Fig. 4 erläutert wurde, geht das System in den Zwischenzustand 10 über, wenn es den Kombinierungszustand 14 verlässt, falls beide Servokanäle immer noch aktiv sind. Alternativ wird ein Übergang vom Zwischenzustand 6 oder Zwischenzustand 7 durchgeführt, wenn nur ein Servokanal aktiv bleibt. Durch diese Vorgehensweise kann die korrekte Abgleichung der beiden Servokanäle für Bitversätze von weniger als fünfzig (50) Prozent der Servoframelänge garantiert werden.

[0056] In einer Ausführungsform wird ein Zähler für 2-Bit-Einheiten verwendet, um den Bitversatz zwischen den zwei Servokanälen zu bestimmen. Ein Servokanal kann den Zustand von inaktiv zu aktiv nur am Ende eines Servoframes wechseln, das heißt nach der Detektion von achtzehn (18) sequenziellen 2-Bit-Einheiten in Bursts von 4, 4, 5, 5 2-Bit-Einheiten. In bestimmten Ausführungsformen wird der Zustand eines inaktiven Servokanals überprüft, nachdem fünfzig (50) Prozent der Framelänge des aktiven Servokanals detektiert wurden. Diese Position stimmt mit der Detektion der achten 2-Bit-Einheit in einem Servoframe überein oder einem Wert des Zählers für 2-Bit-Einheiten von acht. Wenn an dieser Position der Status des zweiten Servokanals aktiv ist, wie in Bezugnahme auf Fig. 5 erläutert wurde, ist der zweite Servokanal gegenüber dem ersten Servokanal um weniger als fünfzig (50) Prozent der Servoframelänge verzögert und ein Übergang in den Zustand 10 (Fig. 4) wird durchgeführt.

**[0057]** Während die bevorzugten Ausführungsformen der vorliegenden Erfindung detailliert dargestellt wurden, sollte es offensichtlich sein, dass Modifikationen und Adaptionen dieser Ausführungsformen durch einen Fachmann durchgeführt werden können, ohne den Umfang der vorliegenden Erfindung, wie sie in den folgenden Ansprüchen beschrieben wird, zu verlassen.

### Patentansprüche

- 1. Verfahren zur Überwachung einer Vielzahl von Servokanälen, die in einer Datenspeicherungsvorrichtung angeordnet sind, umfassend:

- Bewegen eines sequenziellen Informationsspeicherungsmediums umfassend eine Vielzahl von Servokanälen über einen Lese-/Schreibkopf umfassend eine entsprechende Velzahl von Servosensoren, wobei der besagte Lese-/Schreibkopf in der Datenspeicherungsvorrichtung angeordnet ist, und wobei die Datenspeicherungsvorrichtung einen ersten Servokanal, einen zweiten Servokanal und einen endlichen Automaten ("FSM") umfassen, wobei der endliche Automat eine Einzelservokanal-Betriebsart und eine kombinierte Servokanal-Betriebsart umfasst:

- Setzen eines Erfassungsflags durch einen Servokanal, wenn dieser Servokanal einem Servomuster folgt:

- Setzen eines Bitflags durch einen Servokanal, wenn ein neuer LPOS-Bit decodiert wird;

- wirksam wenn zumindest ein Erfassungsflag gesetzt ist: Bestimmen, ob ein Bitflag durch einen mit dem gesetzten Erfassungsflag assoziierten Servokanal gesetzt ist; und

- wirksam wenn ein Erfassungsflag und ein Bitflag durch einen Servokanal gesetzt sind: Bestimmen einer relativen Positionierung jedes Servosensors in Bezug auf ein assoziiertes Servomuster.

- 2. Verfahren nach Anspruch 1, ferner umfassend: wenn kein durch irgendeinen Servokanal gesetzter Erfassungsflag detektiert wird, Setzen des FSM in einen Anfangszustand;

- wenn ein durch den ersten oder zweiten Servokanal gesetzter Erfassungsflag detektiert wird, während kein jeweils durch den zweiten oder ersten Servokanal gesetzter Erfassungsflag detektiert wurde, Übergang aus dem Anfangszustand in einen ersten FSM-Zwischenzustand:

- wenn ein durch den ersten oder zweiten Servokanal gesetzter Bitflag detektiert wird, Übergang von dem ersten FSM-Zwischenzustand in einen FSM-Kombinierungszustand;

- Verwendung von LPOS-Informationen, die nur durch den ersten oder zweiten Servokanal bereitgestellt wurden.

- 3. Verfahren nach Anspruch 2, ferner umfassend: wenn kein durch irgendeinen Servokanal gesetzter Erfassungsflag detektiert wird, Setzen des FSM in einen Anfangszustand;

- wenn durch sowohl den ersten Servokanal als auch den zweiten Servokanal gesetzte Erfassungsflags detektiert wurden, Übergang aus dem Anfangszustand in einen zweiten FSM-Zwischenzustand;

- wenn durch sowohl den ersten Servokanal als auch den zweiten Servokanal gesetzte Bitflags detektiert wurden, Übergang von dem zweiten FSM-Zwischenzustand in den FSM-Kombinierungszustand;

- Verwendung von LPOS-Informationen, die sowohl durch den ersten Servokanal als auch durch den zweiten Servokanal bereitgestellt wurden.

- 4. Verfahren nach Anspruch 1, ferner umfassend eine Bestimmung eines Bitversatzes zwischen dem ersten Servokanal und dem zweiten Servokanal.

- 5. Verfahren nach Anspruch 4, wobei jeder der Servokanäle eine Vielzahl von sequenziellen Servoframes umfasst, wobei jeder Servoframe eine Vielzahl von Servo-2-Bit-Einheiten umfasst, wobei das Verfahren ferner die folgenden Schritte umfasst:

- Einrichtung eines ersten 2-Bit-Einheiten-Zählers für den ersten Servokanal:

- Einrichtung eines zweiten 2-Bit-Einheiten-Zählers für den zweiten Servokanal; und

- Berechnung des Bitversatzes durch Subtraktion des ersten 2-Bit-Zählers von dem zweiten 2-Bit-Zähler

- 6. Vorrichtung umfassend ein computerlesbares Medium, computerlesbaren Programmcode, um eine Vielzahl von Servokanälen zu überwachen, die in dem besagten computerlesbaren Medium codiert sind, ein endlicher Automat ("FSM") umfassend eine Einzelservokanal-Betriebsart und eine kombinierte Servokanal-Betriebsart, die in dem computerlesbaren Medium codiert sind, wobei der computerlesbare Programmcode eine Serie von computerlesbaren Programmschritten umfasst, die Folgendes veranlassen:

- Bewegen eines sequenziellen Informationsspeicherungsmediums umfassend eine Vielzahl von Servokanälen über einen Lese-/Schreibkopf umfassend eine entsprechende Vielzahl von Servosensoren;

- Setzen eines Erfassungsflags durch einen Servokanal, wenn dieser Servokanal einem Servomuster folgt;

- Setzen eines Bitflags durch einen Servokanal, wenn ein neuer LPOS-Bit decodiert wird;

- wirksam wenn zumindest ein Erfassungsflag gesetzt ist: Bestimmen, ob ein Bitflag durch einen mit dem gesetzten Erfassungsflag assoziierten Servokanal gesetzt ist; und

- wirksam wenn ein Erfassungsflag und ein Bitflag durch einen Servokanal gesetzt sind: Bestimmen einer relativen Positionierung jedes Servosensors in Bezug auf ein assoziiertes Servomuster.

- 7. Vorrichtung nach Anspruch 6, wobei der computerlesbare Programmcode ferner eine Serie von computerlesbaren Programmschritten umfasst, die Folgendes auslösen:

- wenn kein durch irgendeinen Servokanal gesetzter Erfassungsflag detektiert wird, Setzen des FSM in einen Anfangszustand;

- wenn ein durch den ersten oder zweiten Servokanal gesetzter Erfassungsflag detektiert wird, während kein jeweils durch den zweiten oder ersten Servokanal gesetzter Erfassungsflag detektiert wurde, Übergang aus dem Anfangszustand in einen ersten FSM-Zwischenzustand;

- wenn ein durch den ersten oder zweiten Servokanal gesetzter Bitflag detektiert wird, Übergang von dem ersten FSM-Zwischenzustand in einen FSM-Kombinierungszustand;

- Verwendung von LPOS-Informationen, die nur durch den ersten oder zweiten Servokanal bereitgestellt wurden.

- 8. Vorrichtung nach Anspruch 7, wobei der computerlesbare Programmcode ferner eine Serie von computerlesbaren Programmschritten umfasst, die Folgendes auslösen:

- wenn kein durch irgendeinen Servokanal gesetzter Erfassungsflag detektiert wird, Setzen des FSM in einen Anfangszustand;

- wenn durch sowohl den ersten Servokanal als auch den zweiten Servokanal gesetzte Erfassungsflags detektiert wurden, Übergang aus dem Anfangszustand in einen zweiten FSM-Zwischenzustand;

- wenn durch sowohl den ersten Servokanal als auch den zweiten Servokanal gesetzte Bitflags detektiert wurden, Übergang von dem zweiten FSM-Zwischenzustand in den FSM-Kombinierungszustand;

- Verwendung von LPOS-Informationen, die sowohl durch den ersten Servokanal als auch durch den zweiten Servokanal bereitgestellt wurden.

- 9. Vorrichtung nach Anspruch 8, wobei der computerlesbare Programmcode ferner eine Serie von computerlesbaren Programmschritten umfasst, die eine Bestimmung eines Bitversatzes zwischen dem ersten Servokanal und dem zweiten Servokanal veranlassen.

- 10. Vorrichtung nach Anspruch 9, wobei jeder der Servokanäle eine Vielzahl von sequenziellen Servoframes umfasst, wobei jeder Servoframe eine Vielzahl von Servo-2-Bit-Einheiten umfasst, wobei der computerlesbare Programmcode ferner eine Serie von computerlesbaren Programmschritten umfasst, die Folgendes veranlassen:

- Einrichtung eines ersten 2-Bit-Einheiten-Zählers für den ersten Servokanal;

- Einrichtung eines zweiten 2-Bit-Einheiten-Zählers für den zweiten Servokanal; und

- Berechnung des Bitversatzes durch Subtraktion des ersten 2-Bit-Zählers von dem zweiten 2-Bit-Zähler.

- 11. Computerprogrammprodukt codiert in einem computerlesbaren Medium und nutzbar mit einem programmierbaren Computerprozessor, um eine Vielzahl von Servokanälen zu überwachen, wobei ein endlicher Automat ("FSM") eine Einzelservokanal-Betriebsart umd eine kombinierte Servokanal-Betriebsart umfasst, wobei das Computerprogrammprodukt Folgendes umfasst:

- computerlesbaren Programmcode, der den programmierbaren Prozessor dazu veranlasst, ein sequenzielles Informationsspeicherungsmedium, das eine Vielzahl von Servokanälen umfasst, über einen Lese-/Schreibkopf zu bewegen, der eine entsprechende Vielzahl von Servosensoren umfasst;

- computerlesbaren Programmcode, der den programmierbaren Prozessor dazu veranlasst, einen Erfassungsflag durch eine Servokanal zu setzen, wenn dieser Servokanal einem Servomuster folgt.

- computerlesbaren Programmcode, der den programmierbaren Prozessor dazu veranlasst, ein Bitflag durch den Servokanal zu setzen, wenn ein neuer LPOS-Bit decodiert wird;

- computerlesbaren Programmcode, der, wenn zumindest ein Erfassungsflag gesetzt ist, den programmierbaren Prozessor dazu veranlasst, zu bestimmen, ob ein durch einen mit dem gesetzten Erfassungsflag assoziierten Servokanal gesetzter Bitflag gesetzt ist; und

- computerlesbaren Programmcode, der, wenn ein Erfassungsflag und ein Bitflag durch einen Servokanal gesetzt sind, den programmierbaren Prozessor dazu veranlasst, eine relative Positionierung jedes Servosensors in Bezug auf ein assoziiertes Servomuster zu bestimmen.

- 12. Computerprogrammprodukt nach Anspruch 11, ferner umfassend:

- computerlesbaren Programmcode, der, wenn kein durch irgendeinen Servokanal gesetzter Erfassungsflag detektiert wurde, den programmierbaren Prozessor dazu veranlasst, den FSM in einen Anfangszustand zu setzen;

- computerlesbaren Programmcode, der, wenn ein durch den ersten oder zweiten Servokanal gesetzter Erfassungsflag detektiert wurde, während kein durch den zweiten oder ersten Servokanal gesetzter Erfassungsflag detektiert wurde, den programmierbaren Prozessor dazu veranlasst, Verfahren dem Anfangszustand in einen ersten FSM-Zwischenzustand überzugehen;

- computerlesbaren Programmcode, der, wenn ein jeweils durch den ersten oder zweiten Kanal gesetzter Bitflag detektiert wurde, den programmierbaren Prozessor dazu veranlasst, von dem ersten FSM-Zwischenzustand in einen FSM-Kombinierungszustand überzugehen;

- computerlesbaren Programmcode, der den programmierbaren Prozessor dazu veranlasst, die LPOS-Information zu verwenden, die nur durch den ersten oder zweiten Servokanal bereitgestellt wurde.

- 13. Computerprogrammprodukt nach Anspruch 12, ferner umfassend:

- computerlesbaren Programmcode, der, wenn kein durch irgendeinen Servokanal gesetzter Erfassungsflag detektiert wurde, den programmierbaren Prozessor dazu veranlasst, den FSM in einen Anfangszustand zu setzen;

- computerlesbaren Speichercode, der, wenn durch sowohl den ersten als auch den zweiten Servokanal gesetzte Erfassungsflags detektiert wurden, den programmierbaren Prozessor dazu veranlasst, von dem Anfangszustand in einen zweiten FSM-Zwischenzustand überzugehen;

- computerlesbaren Programmcode, der, wenn durch sowohl den ersten Servokanal als auch durch den zweiten Servokanal gesetzte Bitflags detektiert wurden, den programmierbaren Prozessor dazu veranlasst, von dem zweiten FSM-Zwischenzustand in einen FSM-Kombinierungszustand überzugehen;

- computerlesbaren Programmcode, der den programmierbaren Prozessor dazu veranlasst, die

LPOS-Informationen zu verwenden, die durch sowohl den ersten Servokanal als auch den zweiten Servokanal bereitgestellt wurde.

- 14. Computerprogrammprodukt nach Anspruch 13, ferner umfassend:

- computerlesbaren Programmcode, der den programmierbaren Prozessor dazu veranlasst, einen Bitversatz zwischen dem ersten Servokanal und dem zweiten Servokanal zu bestimmen.

- 15. Computerprogrammprodukt nach Anspruch 14, wobei jeder der Servokanäle eine Vielzahl von sequenziellen Servoframes umfasst, wobei jeder Servoframe eine Vielzahl von Servo-2-Bit-Einheiten umfasst, wobei das Computerprogrammprodukt ferner umfasst:

- computerlesbaren Programmcode, der den programmierbaren Prozessor dazu veranlasst, einen 2-Bit-Einheiten-Zähler für den ersten Servokanal einzurichten:

- computerlesbarer Programmcode, der den programmierbaren Prozessor dazu veranlasst, einen zweiten 2-Bit-Einheiten-Zähler für den zweiten Servokanal einzurichten; und

- computerlesbaren Programmcode, der den programmierbaren Prozessor dazu veranlasst, den Bitversatz durch Subtraktion des ersten 2-Bit-Einheiten-Zählers von dem zweiten 2-Bit-Einheiten-Zähler zu berechnen.

- 16. Datenspeicherungsvorrichtung umfassend einen ersten Servosensor, einen zweiten Servosensor, einer ersten Servosteuerungseinheit, die mit dem ersten Servosensor kommuniziert, und einer zweiten Servosteuerungseinheit, die mit dem zweiten Servosensor kommuniziert, wobei:

- die erste Servosteuerungseinheit einen ersten Erfassungsflag, der indiziert, dass ein erster Servokanal ein Servomuster erfasst hat, einen ersten Bitflag, der die Verfügbarkeit eines neuen LPOS-Bits indiziert, und einen ersten Servosensor-Positionsindikator ("SRPI"), der eine Position des ersten Servosensors in Bezug auf einen in den ersten Servokanal codierten Servoframe angibt, umfasst;

- die zweite Servosteuerungseinheit einen zweiten Erfassungsflag, der indiziert, dass ein zweiter Servokanal ein Servomuster erfasst hat, einen zweiten Bitflag, der die Verfügbarkeit eines neuen LPOS-Bits indiziert, und einen zweiten Servosensor-Positionsindikator ("SRPI"), der eine Position des zweiten Servosensors in Bezug auf einen in den zweiten Servokanal codierten Servoframe angibt, umfasst.

- 17. Datenspeicherurigsvorrichtung nach Anspruch 16, ferner umfassend eine LPOS-Steuereinheit, die einen LPOS-Kombinierungsalgorithmus umfasst, wobei die LPOS-Steuereinheit mit der ersten Servosteuerungseinheit und der zweiten Servosteuerungseinheit kommuniziert.

- 18. Datenspeicherungsvorrichtung nach Anspruch 17, wobei der LPOS-Kombinierungsalgorithmus eine Anwesenheit oder Abwesenheit des ersten Erfassungsflags, eine Anwesenheit oder Abwesenheit des zweiten Erfassungsflags, eine Anwesenheit oder Abwesenheit des zweiten Bitflags, eine Anwesenheit oder Abwesenheit des zweiten Bitflags, eine Anwesenheit oder Abwesenheit des ersten SRPIs und eine Anwesenheit oder Abwesenheit des zweiten SRPIs nutzt, um zwischen einer Einzelservokanal-Betriebsart und einer kombinierten Servokanal-Betriebsart zu wechseln.

- 19. Datenspeicherungsvorrichtung nach Anspruch 18, wobei die LPOS-Steuereinheit einen endlichen Automaten mit einem Anfangszustand, einer Vielzahl von Zwischenzuständen und einem Kombinierungszustand implementiert.

- 20. Datenspeicherungsvorrichtung nach Anspruch 19, wobei:

- der erste Servokanal einen ersten Servosensor umfasst:

- der zweite Servokanal einen zweiten Servosensor umfasst;

- der erste Servokanal eine Vielzahl von ersten sequenziellen Servoframes detektiert, wobei jeder Servoframe eine Vielzahl von ersten Servo-2-Bit-Einheiten umfasst;

- der zweite Servosensor eine Vielzahl von zweiten sequenziellen Servoframes detektiert, wobei jeder zweite Servoframe eine Vielzahl von zweiten Servo-2-Bit-Einheiten umfasst;

- der erste SRPI eine 2-Bit-Einheiten-Zähler für die Vielzahl von ersten Servo-2-Bit-Einheiten ist; und

- der zweite SRPI ein 2-Bit-Einheiten-Zähler für die Vielzahl von zweiten Servo-2-Bit-Einheiten ist.

- 21. Eine Datenspeicherungsbibliothek umfassend eine Vielzahl von Datenspeicherungsvorrichtungen, wobei jede Datenspeicherungsvorrichtung einen ersten Servosensor, einen zweiten Servosensor, eine erste Servosensorsteuerungseinheit, die mit dem ersten Servosensor kommuniziert, und eine zweite Servosteuerungseinheit, die mit dem zweiten Servosensor kommuniziert, umfasst, wobei:

- die erste Servosteuerungseinheit einen ersten Erfassungsflag, der indiziert, dass ein erster Servokanal ein Servomuster erfasst hat, einen ersten Bitflag, der die Verfügbarkeit eines neuen LPOS-Bits indiziert, und einen ersten Servosensor-Positionsindikator ("SRPI"), der eine Position des ersten Servosensors in Bezug auf einen in den ersten Servokanal codierten Servoframe angibt, umfasst;

- die zweite Servosteuerungseinheit einen zweiten Erfassungsflag, der indiziert, dass ein zweiter Servokanal ein Servomuster erfasst hat, einen zweiten Bitflag, der die Verfügbarkeit eines neuen LPOS-Bits indiziert, und einen zweiten Servosensor-Positionsindikator ("SRPI"), der eine Position des zweiten Servo-

sensors in Bezug auf einen in den zweiten Servokanal codierten Servoframe angibt, umfasst.

- 22. Datenspeicherungsbibliothek ferner nach Anspruch 21 umfassend eine LPOS-Steuereinheit, die einen LPOS-Kombinierungsalgorithmus umfasst, wobei die LPOS-Steuereinheit mit der ersten Servosteuerungseinheit und der zweiten Servosteuerungseinheit kommuniziert.

- 23. Datenspeicherungsbibliothekn nach Anspruch 22, wobei der LPOS-Kombinierungsalgorithmus eine Anwesenheit oder Abwesenheit des ersten Erfassungsflags, eine Anwesenheit oder Abwesenheit des zweiten Erfassungsflags, eine Anwesenheit oder Abwesenheit des ersten Bitflags, eine Anwesenheit oder Abwesenheit des zweiten Bitflags, eine Anwesenheit oder Abwesenheit des ersten SRPIs und eine Anwesenheit oder Abwesenheit des ersten SRPIs und eine Anwesenheit oder Abwesenheit des zweiten SRPIs dazu nutzt, um zwischen einer Einzelservokanal-Betriebsart und einer kombinierten Servokanal-Betriebsart zu wechseln.

- 24. Datenspeicherungsbibliothek nach Anspruch 23, wobei die LPOS-Steuereinheit einen endlichen Automaten implementiert, der einen Anfangszustand, eine Vielzahl von Zwischenzuständen und einen Kombinierungszustand umfasst.

- 25. Datenspeicherungsbibliothek nach Anspruch 24, wobei:

- der erste Servokanal einen ersten Servosensor umfasst;

- der zweite Servokanal einen zweiten Servosensor umfasst;

- der erste Servokanal eine Vielzahl von ersten sequenziellen Servoframes detektiert, wobei jeder erste Servoframe eine Vielzahl von zweiten Servo-2-Bit-Einheiten umfasst;

- der zweite Servosensor eine Vielzahl von zweiten sequenziellen Servoframes detektiert, wobei jeder zweite Servoframe eine Vielzahl von zweiten Servo-2-Bit-Einheiten umfasst;

- der erste SRPI ein 2-Bit-Einheiten-Zähler für die Vielzahl von ersten Servo-2-Bit-Einheiten ist; und

- der zweite SRPI ein 2-Bit-Einheiten-Zähler für die Vielzahl von zweiten Servo-2-Bit-Einheiten ist.

Es folgen 8 Blatt Zeichnungen

# Anhängende Zeichnungen

FIG. 1C