RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 478 391**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21)

**N° 80 05520**

(54) Onduleur modulaire.

(51) Classification internationale (Int. Cl. <sup>3</sup>). H 02 J 3/42; H 02 P 13/16; H 03 L 7/06; H 05 K 10/00.

(22) Date de dépôt..... 12 mars 1980.

(33) (32) (31) Priorité revendiquée :

(41) Date de la mise à la disposition du

public de la demande ..... B.O.P.I. — « Listes » n° 38 du 18-9-1981.

(71) Déposant : SOCIETE GENERALE DE TRAVAUX ELECTRIQUES et COMPAGNIE DE SIGNAUX

ET D'ENTREPRISES ELECTRIQUES, résidant en France.

(72) Invention de : Bernard Candelier, José Estruch et Michel Noé.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Bugnion Associés,

116, bd Haussmann, 75008 Paris.

## ONDULEUR MODULAIRE.

L'invention se rapporte à un onduleur modulaire notamment à découpage haute fréquence, notamment à sinusoïde de sortie reconstituée par modulation de longueur d'impulsions et notamment à étage de puissance constitué de quatre transistors montés en pont.

On connaît déjà des onduleurs de ce type qui présentent l'inconvénient majeur de ne pouvoir être montés en parallèle pour constituer une source d'énergie électrique alternative redondante, sans que l'un d'entre eux, nommément désigné n'ait une fonction essentielle et spécifique de pilotage des autres onduleurs. En conséquence, ces onduleurs connus ne permettent pas la réalisation d'une source véritablement redondante. En outre, lorsque l'onduleur pilote est défectueux, toute la source devient inutilisable. Un automatisme de mise hors service de l'onduleur pilote serait inopérant puisqu'il aurait comme conséquence le non fonctionnement de l'ensemble de la source. L'invention vise à remédier à ces inconvénients et à cet effet, elle propose un onduleur du type mentionné qui peut être associé en parallèle avec au moins un autre onduleur similaire pour constituer une source alternative redondante, chacun des onduleurs ayant la même fonction et le même fonctionnement, du fait qu'il comporte un système d'équilibrage du débit et un système de synchronisation ainsi qu'une synchronisation prioritaire sur son secteur d'alimentation. En outre, l'onduleur comporte un système assurant son exclusion automatique de la source notamment lorsqu'il est défaillant. Ce système assure en même temps la protection de l'onduleur.

Un tel onduleur est effectivement modulaire car tous les onduleurs montés en parallèle et constituant la source sont identiques quant à leur fonctionnement aucun d'entre eux n'ayant une fonction de pilotage permanent pour les autres. La possibilité d'exclure un onduleur défectueux per-

met d'éviter que la source ne soit affectée dans son ensemble si l'un seulement des onduleurs est défectueux. La protection individuelle constitue également un avantage appréciable.

L'invention sera bien comprise d'après la description qui suivra d'une forme d'exécution préférentielle mais non limitative en référence aux dessins annexés dans lesquels :

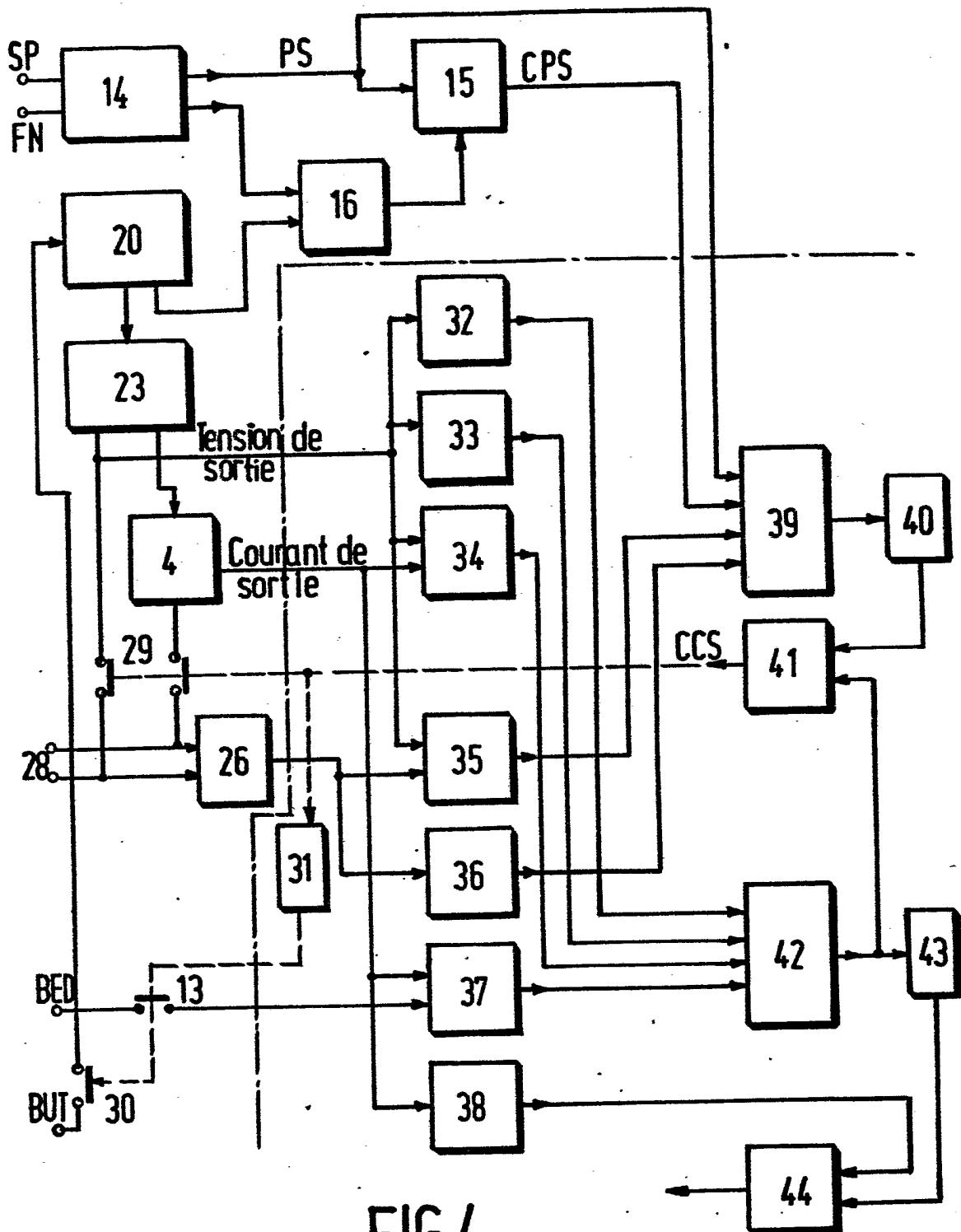

- la figure 1 est une représentation sous forme de bloc diagramme du système d'équilibrage du débit de l'onduleur selon l'invention.

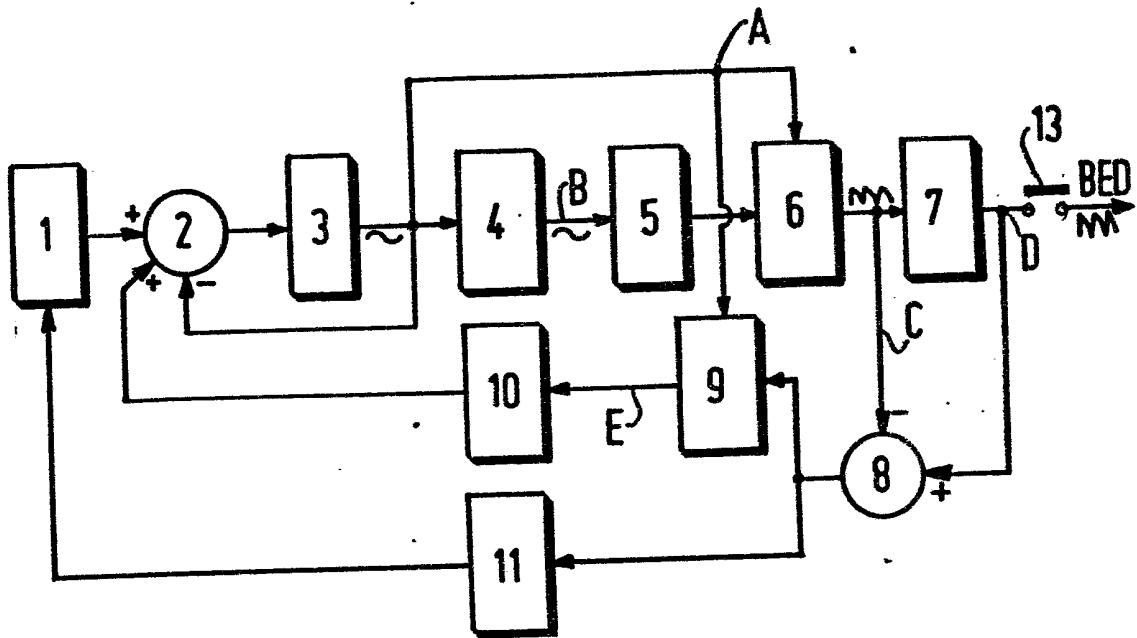

- la figure 2 est une représentation graphique des signaux dans les éléments composants du système de la figure 1.

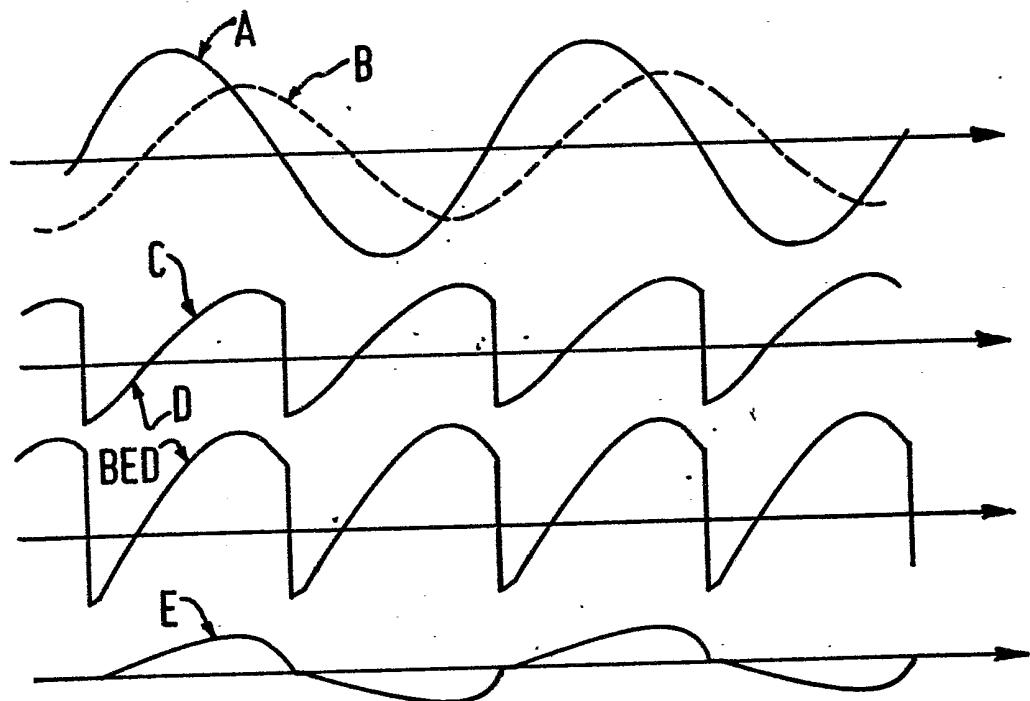

- la figure 3 est une représentation sous forme de bloc diagramme du système de synchronisation de l'onduleur suivant l'invention.

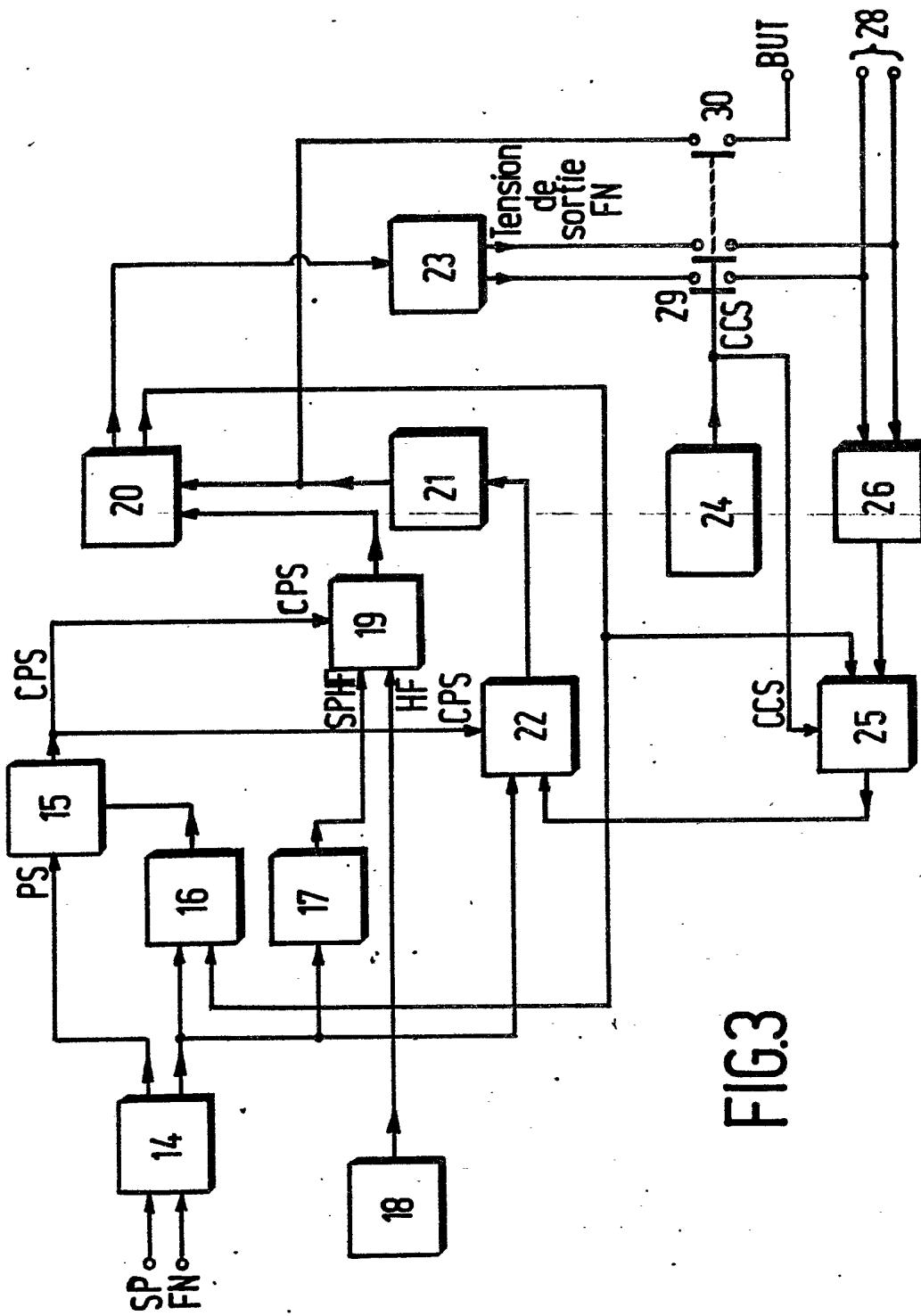

- la figure 4 est une représentation sous forme de bloc diagramme du système assurant l'exclusion automatique d'un onduleur défectueux de la source constituée par plusieurs onduleurs montés en parallèle.

L'onduleur moduleur notamment de puissance 1kVA selon l'invention est notamment du type à découpage haute fréquence, notamment 20 KHZ, dont la sinusoïde de sortie est à la fréquence FN, notamment 50 HZ, reconstruite notamment grâce à la technique de modulation de longueur d'impulsion et dont l'étage de puissance comprend notamment quatre transistors de puissance montés en pont.

Selon l'invention, plusieurs onduleurs de ce type peuvent être montés en parallèle, de manière modulaire, pour constituer une source alternative redondante, dans laquelle chacun des onduleurs a la même fonction et le même fonctionnement, aucun d'eux n'étant privilégié, en particulier constituant un pilote permanent pour les autres. En outre, et afin d'assurer un fonctionnement optimal de la source, chacun des onduleurs qui devient défectueux est automatiquement exclu de la source et mis hors d'utilisation.

5 A cet effet, l'onduleur proposé comporte un système d'équilibrage du débit et un système de synchronisation permettant la mise en parallèle des différents onduleurs et également un système assurant l'exclusion automatique d'un onduleur défectueux.

10 L'onduleur est destiné à être associé à une charge d'utilisation via deux conducteurs de puissance 28. L'onduleur est relié aux autres onduleurs de la source ainsi constituée par deux circuits bus de contrôle soit un premier circuit bus BED pour l'équilibrage des débits des onduleurs quelle que soit la charge et un second circuit bus BUT ou bus des tops pour la synchronisation des onduleurs.

15 L'onduleur comporte également un contacteur bipolaire 29 de puissance, un contacteur 13 associé au circuit bus BED et un contacteur 30 associé au circuit bus BUT permettant d'exclure l'onduleur défectueux du restant de la source. Un seul contacteur bipolaire peut assurer les fonctions des contacteurs 13 et 30.

20 Pour des raisons de simplification et afin de mieux faire comprendre l'invention, la technologie de l'onduleur proprement dite ne sera pas décrite dans le détail, la description s'intéressant exclusivement aux trois systèmes susmentionnés.

25 Le système d'équilibrage des débits selon l'invention et la figure 1 à laquelle on se réfère expressément comporte des moyens de formation d'un signal de référence 1, notamment une tension de référence, et un ensemble formant une boucle de régulation de tension comprenant un comparateur 2 et associé en sortie un étage de puissance 3. Il comporte également, montés en série, un transducteur 4, notamment un shunt ou un organe de mesure de courant de type approprié ; un amplificateur 5 ayant un gain approprié au système et au transducteur 4 ; et un découpeur 6, notamment un commutateur analogique qui découpe le courant suivant les arches positives ou négatives de la tension, ainsi qu'il est montré sur la 30 figure 2 où la courbe A figure la tension, la courbe B le 35

courant ; la courbe C le courant actif, la courbe D le courant réactif du courant découpé, la courbe BED la courbe sur le circuit bus BED et la courbe E, la courbe résultant de la différence entre les courbes précédentes après remise en forme.

5 Le système d'équilibrage comporte ensuite, en sortie du découpeur 6 une diode sans seuil 7 ; un second comparateur 8 associé à la diode 7 en amont et en aval ; des moyens de remise en forme 9 en sortie du comparateur 8 , notamment un commutateur analogique, destiné à réaliser l'opération inverse de celle réalisée par le découpeur 6 ; un premier amplificateur correcteur 10 en sortie des moyens 8, ajusté pour avoir une boucle stable et équilibrer instantanément les débits, donc associé au comparateur 2 ; et enfin un second amplificateur correcteur 11 pour équilibrer les débits en valeur efficace, monté en sortie du comparateur 8 en parallèle avec les moyens 9 et l'amplificateur 10 , agissant sur l'amplitude du signal de référence au moyen notamment d'un amplificateur à gain programmable ou d'une photorésistance.

20 Le système d'équilibrage est associé au circuit bus BED commun à tous les onduleurs associés en parallèle.

Le fonctionnement du système d'équilibrage est le suivant : les moyens de formation du signal de référence 1 envoient une tension de référence au comparateur 2 qui envoie une tension d'erreur à l'étage de puissance 3 dont la tension de sortie est envoyée au transducteur 4, au découpeur 6 et en retour au comparateur 2. Un courant de sortie B du transducteur 4 est envoyé via l'amplificateur 5 au découpeur 6 puis d'une part au circuit bus BED via la diode 7 et le contacteur 13 et d'autre part au second comparateur 8 en sortie duquel se trouvent les deux boucles constituées la première par les moyens 9 et l'amplificateur 10 vers le comparateur 2 et la seconde par l'amplificateur 11 vers les moyens 1. Ces deux boucles d'équilibrage par l'un ou l'autre des amplificateurs 10, 11 ne sont pas toujours nécessaires. L'une au moins peut suffire parfois à équilibrer le débit.

Le processus d'équilibrage est donc le suivant : le débit de chaque onduleur est ajusté sur le débit maximum délivré par l'un quelconque des onduleurs. Ce débit est représenté par le signal analogique du circuit bus BED. Pour 5 obtenir ce signal, on découpe d'abord le courant B suivant les arches positives ou négatives de sa tension A. Le courant découpé est donc l'image du courant B avec le courant actif C positif et le courant réactif D négatif. On compare ensuite ce signal à celui sur le circuit bus BED à travers la diode 10 7. Le signal du circuit bus BED est donc le courant découpé maximum en valeur relative de l'un quelconque des onduleurs. Ce signal représente en valeur absolue le courant actif maximum et le courant réactif minimum, donc le courant découpé de l'onduleur dont la tension est la plus élevée. Pour 15 équilibrer les débits, le courant découpé d'un onduleur est comparé au signal du circuit bus BED. On traite la différence entre les deux signaux de deux manières selon la boucle employée : par la seconde boucle, on amplifie cette différence, on la corrige par l'amplificateur 11 pour agir directement 20 sur le gain intervenant dans la formation du signal de référence. Cette action est généralement proportionnelle à la valeur efficace de la différence, c'est à dire lente. Le gain de l'amplificateur 11 est le plus souvent important. Par la première boucle, on remet cette différence en forme puis on 25 l'amplifie et on la corrige par l'amplificateur 10 pour agir ensuite directement sur l'amplificateur d'erreur dans le comparateur 2. Cette première boucle est rapide mais le gain de l'amplificateur 10 est généralement faible pour éviter que le système ne soit instable.

30 La seconde boucle réalise donc un équilibrage instantané des débits et la première boucle un équilibrage en valeur efficace.

35 Le système de synchronisation selon la figure 3 à laquelle on se réfère expressément permet autant la synchronisation de l'onduleur avec les autres onduleurs auquel il

est associé qu'une synchronisation prioritaire sur un signal de même fréquence (à 10% près) que le signal de sortie de l'onduleur. Ce système comporte les éléments suivants : une interface 14 de l'entrée synchro prioritaire SP, par exemple le secteur ; 5 un commutateur 15 tel qu'une porte logique, ou commutateur analogique, en sortie de l'interface 14 ; un détecteur de synchronisme 16 comportant notamment des portes logiques, également en sortie de l'interface 14 et associé au commutateur 15 ; un multiplicateur de fréquence 17 en sortie de 10 l'interface 14 et en parallèle avec le détecteur 16, comportant notamment une boucle à verrouillage de phase et un diviseur de fréquence ; un oscillateur haute fréquence 18 multiple de  $F_N$ , Notamment  $2^9 \times 50 \text{ HZ} = 25,6 \text{ KHZ}$ , notamment à quartz. Le système de synchronisation comporte également 15 des premiers moyens de sélection 19 associés en sortie du commutateur 15, du multiplicateur de fréquence 17 et de l'oscillateur 18 ; un générateur de référence 20, en sortie des moyens 19 ; un générateur de tops 21 associé au générateur 20 ; des seconds moyens de sélection 22 associés en 20 sortie du commutateur 15 et de l'interface 14 et en sortie duquel est associé le générateur 21 ; l'onduleur proprement dit 23 en sortie du générateur 20, ce générateur 20 étant en fait constitué par le générateur 1 (figure 1) et l'onduleur 23 par l'ensemble du comparateur 2 et de l'étage de puissance 3 (figure 1) ; 25 une logique de commande 24 des contacteurs de sortie 29, 30 ; des troisièmes moyens de sélection 25 associés aux moyens 22, au détecteur 16 et au générateur 20 ; et une interface de charge 26 associée aux moyens de sélection 25. Les conducteurs 28 sont associés à l'interface de charge 26 et à l'onduleur 23 30 via le contacteur 29. Les générateurs 20 et 21 sont associés au circuit bus BUT via le contacteur 30.

En fonctionnement, l'interface 14 délivre à partir d'un signal de fréquence  $F_N$  deux informations notamment un signal de présence PS envoyé au commutateur 15 et un 35 signal carré de fréquence  $F_N$  SP directement utilisable

par la logique, envoyé au détecteur de synchronisme 16, au multiplicateur de fréquence 17 et aux moyens de sélection 22. Le signal carré FN SP ne tient pas compte des éventuelles microcoupures du signal d'entrée synchro prioritaire 5 SP; En cas de disparition plus longue du signal SP, l'interface 14 continue de fournir un signal carré de fréquence FN non altéré et ce pendant plusieurs périodes, ce qui permet de détecter la disparition effective du signal SP. En cas de disparition du signal SP, le signal de sortie de 10 l'onduleur n'est altéré ni en fréquence ni en amplitude.

Le détecteur de synchronisme 16 reçoit également à partir du générateur de référence 20 un signal de référence carré de fréquence FN . A partir de ces deux signaux carrés, le détecteur de synchronisme 16 délivre un signal 15 indiquant si ces deux signaux d'entrée sont ou ne sont pas en phase. Ce signal de sortie est envoyé au commutateur 15 qui délivre à son tour un signal de passage sur synchro prioritaire CPS dont la fonction est d'ordonner au système de se synchroniser sur une entrée prioritaire, lorsqu'il est 20 avéré qu'elle est présente, grâce au signal PS, et lorsqu'elle est en phase avec la tension de référence. Le signal CPS est envoyé aux moyens de sélection 19 et 22.

Le multiplicateur de fréquence 17 délivre, à partir du signal carré qu'il a reçu SP, un signal carré dont la 25 fréquence est un multiple de celle du signal d'entrée. Ce multiplicateur est notamment le même que celui de l'oscillateur haute fréquence 18 notamment  $2^9$ .

Les moyens 19 sélectionnent à partir des trois signaux d'entrée reçus du commutateur 15, du multiplicateur 30 de fréquence 17 et de l'oscillateur 18, celui avec lequel l'onduleur va synthétiser dans le générateur 20 sa tension de référence. Normalement, le signal utilisé est le signal interne haute fréquence de l'oscillateur 18. Toutefois, dès qu'une commande de passage sur mode synchro prioritaire est 35 détectée par le commutateur 15, le signal utilisé est le signal SPHF en sortie du multiplicateur de fréquence 17.

Le générateur de référence 20 produit un signal de référence de fréquence FN sinusoïdal à partir du signal reçu des moyens 19 et sélectionné par ceux-ci et de tops de synchronisation espacés de  $1/FN$  sec., provenant du générateur de tops 21 dont la fonction est de remettre instantanément le signal de référence à zéro. Le signal de référence sinusoïdal en sortie du générateur 20 est envoyé à l'onduleur 23 qui fournit en sortie un signal de fréquence FN envoyé par le commutateur 29 vers la charge d'utilisation via le conducteur 28.

Le générateur de tops 21 produit des tops à partir d'un signal carré en sortie des moyens 22. La largeur des tops doit être très inférieure à la demi période du signal haute fréquence qui a été sélectionné par les moyens 22 entre le signal carré FN SP de l'interface 14 et le signal carré sélectionné par les moyens 25. Ce signal sélectionné est le signal carré de référence en sortie du générateur 20 ou le signal carré de charge en sortie de l'interface de charge 26. Cette sélection est réalisée selon le signal de commande du contacteur de sortie CCS fourni par la logique de commande 24, ce signal commandant également le contacteur 29 associant la sortie de l'onduleur 23 à la charge et le contacteur 30 associant le générateur de tops 21 au circuit bus BUT.

Comme on peut le remarquer, les deux moyens 22, 25 peuvent être constitués par trois entrées et deux commandes respectivement CPS et CCS ; le générateur de tops 21 peut être supprimé si à la place des signaux FN carrés on utilise des tops espacés de  $1/FN$  sec. ; le système peut fonctionner avec une fréquence FN quelconque de 25 HZ à 400 HZ ; la fréquence de l'entrée synchro prioritaire SP peut varier entre FN - 10% et FN + 10%, l'onduleur fournissant une tension en phase de même fréquence.

Le processus de fonctionnement est donc le suivant en l'absence de passage sur mode synchro prioritaire : lorsqu'un onduleur fonctionne seul, le signal haute fréquence utilisé

pour synthétiser la tension de référence est celui de l'oscillateur haute fréquence interne 18. Tant que le contacteur 30 n'est pas actionné, il n'y a aucun top de synchronisation et de remise en phase de la tension de référence. La fréquence FN du signal de référence n'est obtenue que par division de la haute fréquence interne de l'oscillateur 18. Aussitôt que les contacteurs 29, 30 ont été actionnés, le signal de référence carré interne est sélectionné ce qui permet grâce au générateur de tops 21 de former des tops envoyés d'une part au circuit bus BUT et d'autre part au générateur de référence 20 qui est ainsi autoverrouillé.

Lorsqu'un onduleur est mis en fonctionnement en parallèle avec au moins un onduleur déjà en fonctionnement, cet onduleur ne reçoit aucun signal du circuit bus BUT, le contacteur 30 étant ouvert. Le contacteur 29 n'étant pas actionné, les moyens 25 autorisent le passage du signal carré de charge qui est ensuite sélectionné par les moyens 25 pour la constitution des tops de remise en phase du signal de référence. Celui-ci est donc en phase avec le signal de charge, au retard de l'onduleur proprement dit 23 près. Le contacteur 29, peut être actionné. Les tops sélectionnés sont alors fournis à partir du signal carré 50 HZ provenant du générateur 20. Avec un retard de 50 msec., le contacteur 30 du circuit bus BUT 27 est actionné à son tour. L'onduleur adresse donc les tops de sa propre base de temps sur le circuit bus BUT et il en est de même pour les autres onduleurs. Seul le top le plus rapide est pris en compte c'est à dire que de tous les onduleurs en parallèle, celui dont la base de temps est la plus rapide impose son top aux autres toutes les  $1/FN$  sec. Les autres onduleurs remettent leurs propres références à zéro puis délivrent aussitôt après et simultanément un top sur le circuit bus BUT qui n'a aucun effet sur l'onduleur le plus rapide, tant que sa largeur reste très inférieure à la demi période de la haute fréquence.

Dans le cas d'un mode de fonctionnement synchro prioritaire, quel que soit le mode

de fonctionnement de l'onduleur au démarrage, soit seul, soit en charge, en parallèle avec d'autres onduleurs, le principe de fonctionnement reste le même : on attend que le signal de référence soit en phase avec le signal synchro prioritaire, 5 avec une certaine marge d'erreur réglable. Dès que l'on a détecté un signal à l'entrée synchro prioritaire SP en phase avec le signal de référence, on autorise le passage des signaux synchro prioritaires SP pour synthétiser la référence. Ces signaux sont le signal SP haute fréquence provenant du 10 multiplicateur de fréquence 17 et le signal carré FN SP. La fréquence du signal de référence est donc égale à la fréquence du signal SP, grâce au signal SP haute fréquence et le signal de référence est en phase avec le signal SP puisque les tops de remise à zéro sont créés à partir du signal 15 carré FN SP. On observe en outre que la synchronisation sur le signal prioritaire est réalisée sans altérer la tension de sortie ; quand l'onduleur démarre seul le contacteur de sortie peut n'être actionné que lorsque le signal de référence est en phase avec le signal SP ; un voyant lumineux peut 20 être utilisé pour indiquer ce moment.

Le système assurant l'exclusion automatique de l'onduleur modulaire défectueux assure simultanément les protections de l'onduleur. Ce système commande le contacteur 13 du circuit bus BED (figure 2) le contacteur 30 du circuit 25 bus BUT et le contacteur 29 de la charge (figure 3).

La logique de commande de ces contacteurs de sortie et des protections assurées par ce système fait intervenir certains des éléments décrits précédemment. Elle est décrite en relation avec la figure 4 à laquelle on se réfère expressément, sur laquelle les éléments déjà mentionnés portent les 30 mêmes références que sur les figures 1 et 3.

Ce système comprend un retard 31 notamment mécanique ou électronique ; un détecteur de sous-tension 32 tel qu'un comparateur ; un détecteur de surtension 33 ; un détecteur 35 d'absorption de puissance 34 ; un détecteur de synchronisme 35

un détecteur de présence 36 notamment un comparateur à seuil ; un détecteur de l'onduleur pilote 37 tel qu'un comparateur ; un détecteur de surintensité 38 . Les détecteurs 32, 33, 34, 35 sont associés en parallèle en sortie de l'onduleur 23. Les détecteurs 34, 37, 38 sont associés en parallèle en sortie du transducteur 4. Les détecteurs 35, 36 sont associés à l'interface 26. Le système comprend en outre une logique de commande 39 associé au commutateur 15 et au détecteur 35, 36 ; un second retard 40 associé en sortie de la logique 39 ; une mémoire 41 en sortie du retard 40 réalisée par exemple par un flip-flop , une bascule R/S ou tout autre moyen similaire, à laquelle est associée une logique d'exclusion 42 elle-même associée en sortie des détecteurs 32, 33, 34 et 37 ; une seconde mémoire 43 associée à la logique 42 ; et une porte OU logique 44 associée à la mémoire 43 et au détecteur 38.

Le détecteur 32 délivre un signal temporisé ou non indiquant si la tension de sortie est inférieure à un certain seuil préréglable. Le détecteur de surtension 38 indique si la tension de sortie est supérieure à un certain seuil préréglable. Le détecteur d'absorption de puissance 34 détecte si un onduleur absorbe de la puissance en mesurant le déphasage entre la tension de sortie et le courant de sortie et en le comparant à un seuil préréglable. Le détecteur de synchronisme 35 est identique au détecteur de synchronisme 16. Le détecteur de présence 36 indique en sortie si une tension est présente du côté de la charge d'utilisation. Le détecteur de l'onduleur pilote 37 reconnaît si l'onduleur impose son courant découpé sur le circuit bus BED ainsi qu'il a été décrit précédemment pour le système d'équilibrage. A cet effet, ce détecteur compare le signal du circuit bus BED au courant découpé de l'onduleur. Si la différence entre les deux signaux est inférieure à un certain seuil, l'onduleur impose son courant découpé , c'est donc lui qui est pilote. Le détecteur de surintensité 38 délivre un signal indi-

quant si le courant de sortie est supérieur à un certain seuil préréglable.

En fonctionnement, les détecteurs 32, 33, 34, 35 reçoivent un signal de la tension de sortie provenant de l'onduleur 23. Les détecteurs 34, 37, 38 reçoivent un signal de courant de sortie du transducteur 4. Les détecteurs 35 et 36 reçoivent un signal de l'interface 26. La logique de commande 39 reçoit d'une part le signal de présence PS de la sortie de l'interface 14 et le signal de passage sur synchro prioritaire CPS en sortie du commutateur 15 et d'autre part, le signal de sortie de phase du détecteur de synchronisme 35 et le signal de présence de charge du détecteur de présence 36. La logique de commande 39 effectue un traitement logique des informations nécessaires à la commande des contacteurs 13, 29, 30, comme on le verra ultérieurement. A cet effet, elle émet un signal de commande retardé par le second retard 40 puis envoyé à la mémoire 41.

La logique d'exclusion 42 reçoit de la part du détecteur de sous-tension 32 un signal de sous-tension, du détecteur de surtension 33 un signal de surtension (selon le cas), du détecteur d'absorption de puissance 34 un signal de puissance absorbée et du détecteur de l'onduleur pilote 37 son signal de sortie. Elle effectue à partir de ces signaux un traitement logique pour exclure de la source redondante un onduleur en défaut, ainsi que cela sera décrit ultérieurement. A cet effet, la logique d'exclusion 42 émet en sortie un signal de défaut qui est également envoyé dans la mémoire 41 et également dans la seconde mémoire 43.

La mémoire 41 délivre un signal de commande CCS des contacteurs de sortie 13, 29, 30. Ce signal de commande CCS est délivré en fonction des signaux délivrés respectivement par la logique de commande 39 et la logique d'exclusion 42. Ce signal commande le contacteur de charge 29 et via le retard 31 les contacteurs 13, 30 associés aux circuits bus BED et BUT.

La seconde mémoire 43 enregistre et mémorise le signal de défaut à la sortie de la logique d'exclusion 42

pour l'envoyer à la porte OU logique 44 délivrant un signal d'inhibition de déclenchement des semiconducteurs de puissance du système. A cet effet, la porte 44 reçoit également le signal de limitation d'intensité du détecteur de 5 surintensité 38.

Le processus de fonctionnement de ce système est le suivant :

la logique de commande 39 active à sa sortie le signal de commande quand: la charge est présente et en phase avec la 10 tension de sortie ; la charge et le signal synchro prioritaire sont absents ; la charge est absente, le signal SP est présent et le signal de commande de passage sur synchro prioritaire CPS est activé (condition facultative).

La logique d'exclusion 42 active à sa sortie le 15 signal de défaut quand: l'onduleur est en sous-tension, sa tension de sortie étant inférieure à un certain seuil, éventuellement avec une temporisation de l'ordre de une seconde permettant une commutation sur secteur ; l'onduleur est en surtension et l'onduleur est pilote, ce qui signifie qu'il 20 impose son courant découpé sur le circuit bus BED de la source, comme on l'a vu précédemment. En cas de surtension de l'ensemble de la source, le défaut provient le plus souvent de cet onduleur qui est instantanément disjoncté ; l'onduleur est en surtension, et il n'impose pas son courant découpé 25 sur le circuit bus BED. L'exclusion est alors temporisée notamment de 50 msec. pour permettre à cet onduleur d'être déconnecté si la surtension persiste ; l'onduleur absorbe de la puissance, notamment de la puissance active. Au-delà d'un certain déphasage tension-courant en sortie, l'onduleur 30 est défaillant et instantanément disjoncté.

La commande des contacteurs de sortie 13, 29, 30 résulte du signal de commande CCS en sortie de la mémoire 41 à partir du signal de commande retardé provenant de la logique de commande 39 via le retard 40 et du signal de défaut en provenance de la logique d'exclusion 42. Le retard 35

à la sortie du retard 40 est supérieur à toutes les temporisations de la logique d'exclusion 42. Si le signal de commande retardé apparaît à l'entrée de la mémoire 41 et que le signal de défaut n'est pas activé, l'onduleur fonctionne correctement et le signal de commande du contacteur de sortie CCS est activé et mémorisé. Le signal de commande retardé n'a plus d'influence sur le signal CCS. L'ouverture des contacteurs 13, 29, 30 résulte de la coupure de l'alimentation de l'onduleur ou d'une situation d'exclusion. Dès que le signal de défaut est actif à l'entrée de la mémoire 41, les contacteurs 13, 29, 30 s'ouvrent et restent ouverts quel que soit le signal de commande retardé ou le signal de défaut. Pour réarmer c'est à dire fermer les contacteurs 13, 29, 30, il convient d'abord de supprimer la cause du défaut, de couper puis de remettre en fonctionnement l'alimentation de l'onduleur.

Suivant l'invention, le signal de défaut en sortie de la logique d'exclusion 42 a également comme fonction d'inhiber le déclenchement des semiconducteurs de puissance de l'onduleur et ainsi de les protéger. A cet effet, le signal de défaut est mémorisé dans la seconde mémoire 43 pour activer un signal de défaut permanent ne tenant pas compte de la logique d'exclusion, appliquée à la porte 44. Le déclenchement des semiconducteurs de puissance est également inhibé lorsque le courant excède un courant de seuil maximum, comme détecté par le détecteur 38. Pour limiter l'intensité, un signal de limitation d'intensité est activé. La porte OU logique 44 a comme fonction de permettre l'inhibition du déclenchement des semiconducteurs de puissance, selon que cela résulte d'un défaut permanent (en provenance de la mémoire 43) ou d'une surintensité (en provenance du détecteur 38). Cette porte 44 n'est pas toujours nécessaire. Cela dépend des semiconducteurs utilisés et de la méthode employée pour les bloquer.

Les contacteurs 13, 30 associés aux circuits bus BED et BUT sont activés par le signal de commande du contacteur

de sortie CCS avec un retard réglable, notamment 10 msec. grâce au retard 31. En effet, il convient d'attendre que le contacteur de puissance 29 soit effectivement fermé pour que la masse électronique de l'onduleur soit au même potentiel que la masse de la source. Ce retard 31 n'est nécessaire que lorsque l'électronique de l'onduleur est référencé par rapport à la tension de sortie, la masse électronique est en prise sur l'un des deux conducteurs de puissance 28, avant ou après le transducteur 4. Au contraire, si l'électronique de l'onduleur est référencée par rapport à l'alimentation continue de l'onduleur, le retard 31 n'est plus nécessaire.

Il est de toute évidence que l'invention admet de nombreuses variantes.

REVENDICATIONS

1. Onduleur modulaire, caractérisé par le fait qu'il peut être associé en parallèle avec au moins un autre onduleur similaire afin de constituer une source alternative redondante dans laquelle chacun des onduleurs a la même fonction et le même fonctionnement, du fait qu'il comporte un système d'équilibrage du débit et un système de synchronisation.

2. Onduleur selon la revendication 1, caractérisé par le fait qu'il comporte en outre un système de synchronisation prioritaire sur un signal de même fréquence (à 10% près) que la tension de sortie de l'onduleur.

3. Onduleur selon la revendication 2, caractérisé par le fait qu'il comporte en outre un système assurant son exclusion automatique de la source notamment lorsqu'il est défectueux.

4. Onduleur modulaire selon la revendication 3, caractérisé par le fait que le système assurant son exclusion automatique a aussi comme fonction d'assurer sa protection.

5. Onduleur selon la revendication 1, caractérisé par le fait qu'il comporte indépendamment des deux conducteurs de puissance 28 deux circuits bus de contrôle soit un circuit bus BED pour l'équilibrage des débits et un circuit bus BUT ou circuit bus des tops pour la synchronisation de la source.

6. Onduleur suivant l'une quelconque des revendications 1 à 5, caractérisé par le fait qu'il comporte un contacteur bipolaire 29 de puissance, associé à l'onduleur et au conducteur 28, un contacteur 13 associé au circuit bus BED et un contacteur 30 associé au circuit bus BUT.

7. Onduleur comprenant des moyens de formation d'un signal de référence et un ensemble formant une boucle de régulation de tension constitué d'un comparateur et d'un éta-ge de puissance, selon la revendication 1, caractérisé par le fait que le système d'équilibrage comporte également un

transducteur 4, un amplificateur 5, un découpeur 6, une diode sans seuil 7, un second comparateur 8, des moyens de mise en forme 9, un premier et un second amplificateurs correcteurs 10, 11 et le circuit bus BED.

5 8. Onduleur selon la revendication 1, caractérisé par le fait que le système de synchronisation comporte une interface 14, un commutateur 15, un détecteur de synchronisme 16, un multiplicateur de fréquence 17, un oscillateur haute fréquence 18, des premiers moyens de sélection 19, un générateur de référence 20, un générateur de tops 21, des seconds moyens de sélection 22, une logique 24, des troisièmes moyens de sélection 25 et une interface de charge 26 ainsi que le circuit bus BUT.

9. Onduleur selon l'une quelconque des revendications 3 et 6, caractérisé par le fait que le système assurant l'exclusion automatique comprend un détecteur de sous-tension 32, un détecteur de surtension 33, un détecteur d'absorption de puissance 34, un détecteur de présence 36, un détecteur de l'onduleur pilote 37, une logique de commande 39, un second retard 40, un mémoire 41, une logique d'exclusion 42 et un retard 31 ainsi que les contacteurs 13, 29, 30.

10. Onduleur selon la revendication 4, caractérisé par le fait que le système assurant son exclusion automatique comprend également une seconde mémoire 43, un détecteur de surintensité 38 ou une porte OU logique 44.

11. Onduleur selon la revendication 1, caractérisé par le fait que le synchronisation se fait sur l'onduleur de la source qui est le plus rapide et qui impose son top à tous les autres onduleurs ainsi que l'onduleur dont la tension est la plus élevée qui impose son courant découpé sur le circuit bus BED.

1/3

FIG.1

FIG.2

2/3

3/3