(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7065566号

(P7065566)

(45)発行日 令和4年5月12日(2022.5.12)

(24)登録日 令和4年4月28日(2022.4.28)

(51)国際特許分類

H 0 2 J 1/00 (2006.01)

F I

H 0 2 J

1/00

3 0 7 F

請求項の数 9 (全18頁)

|                   |                                  |          |                                                                                                                                                                                                                                     |

|-------------------|----------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21)出願番号          | 特願2016-546045(P2016-546045)      | (73)特許権者 | 516043960<br>シグニファイ ホールディング ビー ヴィ<br>S I G N I F Y H O L D I N G B . V .<br>オランダ国 5 6 5 6 アーエー アイン<br>トホーフェン ハイ テク キャンパス 4 8<br>H i g h T e c h C a m p u s 4 8<br>, 5 6 5 6 A E E i n d h o v e n ,<br>T h e N e t h e r l a n d s |

| (86)(22)出願日       | 平成27年1月7日(2015.1.7)              |          |                                                                                                                                                                                                                                     |

| (65)公表番号          | 特表2017-502643(P2017-502643<br>A) |          |                                                                                                                                                                                                                                     |

| (43)公表日           | 平成29年1月19日(2017.1.19)            |          |                                                                                                                                                                                                                                     |

| (86)国際出願番号        | PCT/EP2015/050123                | (74)代理人  | 100163821<br>弁理士 柴田 沙希子                                                                                                                                                                                                             |

| (87)国際公開番号        | WO2015/106992                    | (72)発明者  | イセブート レナート<br>オランダ国 5 6 5 6 アーエー アイン<br>トホーフェン ハイ テク キャンパス 5                                                                                                                                                                        |

| (87)国際公開日         | 平成27年7月23日(2015.7.23)            | (72)発明者  | ウェント マティアス<br>オランダ国 5 6 5 6 アーエー アイン<br>最終頁に続く                                                                                                                                                                                      |

| 審査請求日             | 平成30年1月5日(2018.1.5)              |          |                                                                                                                                                                                                                                     |

| 審判番号              | 不服2021-1576(P2021-1576/J1)       |          |                                                                                                                                                                                                                                     |

| 審判請求日             | 令和3年2月4日(2021.2.4)               |          |                                                                                                                                                                                                                                     |

| (31)優先権主張番号       | 14151164.2                       |          |                                                                                                                                                                                                                                     |

| (32)優先日           | 平成26年1月14日(2014.1.14)            |          |                                                                                                                                                                                                                                     |

| (33)優先権主張国・地域又は機関 | 歐州特許庁(EP)                        |          |                                                                                                                                                                                                                                     |

(54)【発明の名称】 配電システムにおける受電装置のための低電力スタンバイ

## (57)【特許請求の範囲】

## 【請求項 1】

配電システムであって、

- 電力を供給する給電装置と、

- 負荷を含む受電装置であって、前記給電装置と着脱可能に電気的に結合され、且つ更に前記給電装置によって給電される、受電装置と、

- 前記給電装置を前記受電装置に着脱可能に電気的に結合し、且つ更に前記給電装置から前記受電装置へ前記電力を伝達する導電体と

を含み、前記給電装置が、更に、前記給電装置から前記受電装置への電流の流れを感知し、且つ、最小電流以上の電流が少なくとも周期的に感知される場合に電力を供給し、

前記受電装置が、更に、少なくとも一部の時間において前記負荷が前記最小電流よりも小さい電流を引き出すスタンバイモードで、及び少なくとも一部の時間において前記負荷が前記最小電流以上の電流を引き出す動作モードで動作し、

前記受電装置が、前記給電装置から、バルクコンデンサを含む前記受電装置の少なくとも一部を電気的に切り離す制御可能スイッチを更に含み、

前記受電装置は、少なくとも前記制御可能スイッチを制御することを通じて、前記受電装置が前記スタンバイモードで動作しているときに、前記給電装置から前記最小電流以上のパルス電流を、所定の期間にわたり且つ所定の周波数で引き出すパルス生成回路を更に含み、

前記制御可能スイッチは、更に、パルスが生成されるときに前記バルクコンデンサを切り

離して、当該バルクコンデンサが前記パルスを除去することを防ぎ、前記受電装置がパワーオーバーイーサネット（登録商標）規格において指定される受電装置であり、前記受電装置が前記導電体を介して電力を受け取るための物理インターフェースチップ又はチップセットを含み、前記パルス生成回路が前記物理インターフェースチップ又はチップセットの一部である、配電システム。

【請求項 2】

請求項 1 に記載の配電システムであって、前記受電装置の前記パルス生成回路が、

- 前記パルス電流を消費する抵抗と、

- 前記抵抗と直列に配置されるパルス生成スイッチと、

- 前記パルス生成スイッチ及び前記制御可能スイッチを制御するコントローラと

を含み、前記コントローラが、更に、前記パルス電流を消費するために前記パルス生成スイッチがオンにされ、且つ前記制御可能スイッチがオフにされるパルス生成モードと、前記パルス生成スイッチがオフにされ、且つ前記制御可能スイッチがオンにされる非パルス生成モードとの間を循環する、配電システム。

【請求項 3】

請求項 1 に記載の配電システムであって、前記受電装置の前記パルス生成回路が、

- 前記給電装置から引き出された前記パルス電流の電気エネルギーを貯蔵する、バッファコンデンサと、

- 前記バッファコンデンサと直列に配置されるパルス生成スイッチと、

- 前記パルス生成スイッチ及び前記制御可能スイッチを制御するコントローラと

を含み、前記コントローラが、更に、前記パルス電流の電気エネルギーを前記バッファコンデンサに貯蔵するよう前記パルス電流を引き出すために前記パルス生成スイッチがオンにされ、且つ前記制御可能スイッチがオフにされるパルス生成モードと、前記パルス生成スイッチがオフにされ、前記バッファコンデンサに貯蔵された前記電気エネルギーが消費され、且つ前記制御可能スイッチがオンにされる非パルス生成モードとの間を循環する、配電システム。

【請求項 4】

請求項 1 乃至 3 の何れか一項に記載の配電システムであって、前記受電装置が分離スイッチを含み、前記制御可能スイッチが前記分離スイッチである、配電システム。

【請求項 5】

請求項 1 乃至 4 の何れか一項に記載の配電システムであって、前記導電体がイーサネット（登録商標）ケーブルである、配電システム。

【請求項 6】

請求項 1 乃至 5 の何れか一項に記載のシステムにおいて使用される給電装置。

【請求項 7】

請求項 1 乃至 5 の何れか一項に記載のシステムにおいて使用される受電装置。

【請求項 8】

受電装置のスタンバイモード中に、給電装置に電気的に結合された前記受電装置において電流パルスを生成するための方法であって、

- 前記受電装置に含まれるパルス生成回路によって前記給電装置から電流を引き出して、前記電流パルスを生成するステップと、

- 前記電流パルスが生成されるときに、前記受電装置に含まれる制御可能スイッチを前記パルス生成回路によって制御することを通じて、前記給電装置から、バルクコンデンサを含む前記受電装置の少なくとも一部を電気的に切り離して、当該バルクコンデンサが前記電流パルスを除去することを防ぐステップと

を含み、

前記受電装置がパワーオーバーイーサネット（登録商標）規格において指定される受電装置であり、前記受電装置が前記給電装置から導電体を介して電力を受け取るための物理インターフェースチップ又はチップセットを含み、前記パルス生成回路が前記物理インターフェースチップ又はチップセットの一部である、方法。

10

20

30

40

50

## 【請求項 9】

コンピュータ上で実行されると、請求項8に記載のステップを実行するコンピュータプログラム。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、電力を供給するための給電装置と、給電装置によって電力を供給されることになる照明器具などの受電装置とを備えた配電システムに関する。本発明は更に、給電装置、受電装置、並びに配電システム内に電力を分配するための配電方法及びコンピュータプログラム製品に関する。

10

## 【背景技術】

## 【0002】

パワーオーバーイーサネット（登録商標）（PoE：Power over Ethernet）に関する米国電気電子学会（IEEE：Institute of Electrical and Electronics Engineers）規格802.3af/altによると、受電装置（PD：powered device）はイーサネット（登録商標）ケーブルを介して給電機器（PSE：power sourcing equipment）によって給電される。PSEは例えはスイッチであり、PDは例えはインターネットプロトコル（IP：internet protocol）カメラ、IP電話、無線アクセスポイント、照明器具、センサ、送風機等である。規格に従って、PSEは、ケーブルが切断されたか、非PoE装置に接続されたか、又はPoE準拠のPDに接続されたかどうかを判断することができる。これは、3つの段階（それらはアイドル状態の後に続く）：検出段階、分類段階、及び2イベント分類で達成され、その後、（動作状態で）PDが給電される。

20

## 【0003】

検出段階において、PSEは、PDが接続されているかどうかを検出する。検出段階の間、PoE準拠のPDは、コンデンサ（50nF～120nF）及び抵抗（25k、検出段階の間に存在する）を使用して、有効な検出シグネチャを提供するであろう。例として、PSEは2.8V～10Vの範囲内の2つの電圧を印加し、対応する電流を測定して、シグネチャ抵抗の存在を判断することができる。電流供給など、他の方法も可能となっている。分類段階では、PSE及びPDは、IEEE802.3af電力レベル（12.95W）に準拠したタイプ1、又はIEEE802.3at電力レベル（25.5W）に準拠したタイプ2として識別される。加えて、802.3at規格は、電力分類を決定する別の方法を提供する。タイプ2のPSEは、2イベント分類を実施することにより（レイヤ1）、又はPDと通信することにより（レイヤ2）、PD電力分類を取得するオプションを有している。同時に、タイプ2のPDは、タイプ2のPSEを識別し、レイヤ1及びレイヤ2を介して通信できなければならない。2イベント分類の一環として、PSEは15.5V～20.5Vの一定の電圧をPDに供給する。

30

## 【0004】

PDが接続されていると決定した（及び任意選択の電力分類の）後、PSEは、PDがもはや電力を使用しなくなるまで、PDに電力を供給する。規格では、スタンバイモード時など、PDが殆ど又は全く電力を必要としない場合、PDは電力維持シグネチャ（MPS：Maintain Power Signature）を生成しなければならないと指定している。IEEE802.3atによると、MPSは、AC MPS成分及びDC MPS成分の2つの成分から構成される。PSEは、DC MPS成分、AC MPS成分、又はその両方を監視することになっている。AC MPS成分は、ACインピーダンスが27k以下の電力インターフェースにおいて検出される場合に存在する。DC MPSは、PDが60msの最小期間にわたり少なくとも10mAを引き出すことを必要とする。最小のドロップアウト期間は300msであり（ドロップアウトしてはならない）、最大のドロップアウト期間は400msである（ドロップアウトしなければはならない）。

40

## 【0005】

PSEによってMPSが検出されない場合、PSEはPDへの電力を切断してもよい。

50

のことは、PSEが切断されたポートへ電力を供給することを防ぎ、次いでこれにより、そのようなポート（又はそのポートに接続されているケーブル）に触れている人が感電することを防ぎ得る。別の例として、これにより、電力が印加されるPSEのポートに接続されている非PoE装置への損傷を防ぐことができる。

#### 【0006】

現在、照明器具（センサー、スイッチ、光源など）、又はアクティブスピーカー、インターネットラジオ、DVDプレーヤー、セットトップボックス、及び更にはTVセットなどの娯楽機器など、全ての種類の負荷に対してPoE規格を使用するための議論が進められている。そこで、Cat5/6接続毎に最大60W以上のレベルなどのより高い電力レベルをサポートする将来の規格が必要とされている。そのような議論は、PoEに関連して進行しているだけでなく、EMerge Alliance Occupied Space Standard、又はUSB Power Delivery規格などの他の（類似の）規格に関連しても進行している。そのような配電システムを通じて給電される高電力の装置のこのような発展と共に、これらのシステムを通じて給電される装置の数が増加しているという発展も存在する。従って、向上された電気効率を有する配電システムを開発する必要性がある。

10

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0007】

向上された電気効率を有する配電システムを提供することが、本発明の目的である。特にスタンバイモードにおいて、多くの配電システムでは、キープアライブ型の信号を生成するためエネルギーが「浪費」されている。PoEについて、IEEE802.3af/at規格は、例えば、MPSの生成以外では（殆ど）電気エネルギーが消費されないモード（例えば、スタンバイモード）でPDが動作している場合、MPSを生成するために、PDによる電気エネルギーの消費を必要とする。MPSは、周期的に生成されることのみを必要とするが、およそ最低100mWの電力消費につながる。本発明の第1の態様では配電システムが提供され、この配電システムは、給電装置、受電装置、及び導電体を含む。給電装置は、電力を供給するように構成される。受電装置は、給電装置と着脱可能に電気的に結合されるように構成される。受電装置は照明装置などの負荷を含み、給電装置によって給電されるように更に構成される。導電体は、給電装置を受電装置に着脱可能に電気的に結合するように構成される。導電体は、給電装置から受電装置へ電力を伝達するように更に構成される。

20

#### 【0008】

配電システムにおいて、給電装置は、給電装置から受電装置への電流の流れを感知し、且つ、最小電流以上の電流が少なくとも周期的に感知される場合に電力を供給するように更に構成される。給電装置から受電装置へのこの電流の流れは、例えば、MPS又は別の種類のパルス若しくはキープアライブ信号であり得る。

30

#### 【0009】

配電システムにおいて、受電装置は、少なくとも一部の時間において負荷が最小電流よりも小さい電流を引き出すスタンバイモードで、及び少なくとも一部の時間において負荷が最小電流以上の電流を引き出す動作モードで動作するように更に構成される。スタンバイモード中である場合、受電装置は、給電装置が受電装置に給電したままになるような十分な電力を引き出さない。

40

#### 【0010】

配電システムにおいて、受電装置は、制御可能スイッチ及びパルス生成回路を更に含む。制御可能スイッチは、給電装置から受電装置の少なくとも一部を電気的に切り離すように構成される。パルス生成回路は、少なくとも制御可能スイッチを制御することを通じて、受電装置がスタンバイモードで動作しているときに、給電装置から最小電流以上のパルス電流を、所定の期間にわたり且つ所定の周波数で引き出すように構成される。パルス生成回路を介して受電装置が周期的に最小電流以上の電流を引き出すとき、給電装置は給電したままになるであろう。しかしながら、少量の電力が引き出されるとき、受電装置の一部

50

である電気部品がパルスを除去する、パルスの形状を変更するなどを行うことができ、これによって給電装置が電流を感知するのを防ぎ、これによって給電装置が受電装置に電力を供給したままになることを防ぐ。制御可能スイッチを制御することにより、受電装置がよりエネルギー効率的に動作することを可能にするような方法で、パルスが生成され得る。第1の例として、P o E 準拠の P D において、パルスが生成されるとき、制御可能スイッチはバルクコンデンサを切り離すことができ、この部品がパルスを除去することを防ぐ。これにより、例えば、パルスが短くなることが可能になる。別の例として、制御可能スイッチを介して、給電装置からの負荷の分離を通じて、パルス生成において消費されるエネルギーがより効果的に使用されるようになる（例えば、負荷中のアクティブな部品にエネルギーが貯蔵されない。スタンバイモードでは、これは「浪費」である）。

10

#### 【 0 0 1 1 】

本発明に従った配電システムの一実施形態において、受電装置のパルス生成回路は、抵抗、パルス生成スイッチ、及びコントローラを含む。抵抗は、パルス電流を消費するように構成される。パルス生成スイッチは、抵抗と直列に配置される。コントローラは、パルス生成スイッチ及び制御可能スイッチを制御するように構成され、パルス電流を消費するためにパルス生成スイッチがオンにされ、且つ制御可能スイッチがオフにされるパルス生成モードと、パルス生成スイッチがオフにされ、且つ制御可能スイッチがオンにされる非パルス生成モードとの間を循環するように更に構成される。この実施形態では、M P S などのパルス電流が抵抗によって消費され、制御可能スイッチがバルクコンデンサなどの受電装置の少なくとも一部を切り離す。

20

#### 【 0 0 1 2 】

本発明に従った配電システムの別の実施形態において、受電装置のパルス生成回路は、バッファコンデンサ及びコントローラを含む。バッファコンデンサは、制御可能スイッチがオンにされると、給電装置から受け取られた電気エネルギーを貯蔵するように構成される。コントローラは、制御可能スイッチを制御するように構成され、制御可能スイッチがオンにされ、且つバッファコンデンサが充電されるパルス生成モードと、制御可能スイッチがオフにされ、且つバッファコンデンサに貯蔵された電気エネルギーが消費される非パルス生成モードとの間を循環するように更に構成される。

#### 【 0 0 1 3 】

本発明に従った配電システムの更に別の実施形態において、受電装置は電力変換装置を含み、受電装置のパルス生成回路はコントローラを含む。コントローラは、電力変換装置及び制御可能スイッチを制御するように構成され、及びコントローラは、制御可能スイッチがオンにされ、且つ電力変換装置の貯蔵部品が充電される非パルス生成モードと、制御可能スイッチがオフにされ、且つ電力変換装置の貯蔵部品に貯蔵された電気エネルギーが消費されるパルス生成モードとの間を循環するように更に構成される。任意選択的に、電力変換装置は、入力電流制御モードで制御され得る。

30

#### 【 0 0 1 4 】

本発明に従った配電システムの更なる実施形態において、受電装置はパルストラ ns を含み、受電装置のパルス生成回路はコントローラを含む。コントローラはパルストラ ns 及び制御可能スイッチを制御するように構成され、コントローラは、一次電流がパルストラ ns の一次巻線で生成されるパルス生成モードと非パルス生成モードとの間を循環するように更に構成される。この実施形態において、パルス生成モードにおいてパルストラ ns の一次巻線で生成された一次電流は、パルストラ ns の二次巻線で二次電流に変換され、この二次電流は最小電流以上であり、パルストラ ns の二次巻線は給電装置を伴う閉電流ループに電気的に結合されており、制御可能スイッチは、非パルス生成モードにおいてパルストラ ns の一次巻線を短絡するように構成される。任意選択的に、受電装置は、給電装置から受電装置への電流の流れを感知するように構成された電流センサを更に含み、コントローラは、感知された電流の流れに基づいてパルストラ ns による注入電流の振幅を調節するように更に構成される。

40

#### 【 0 0 1 5 】

50

本発明に従った配電システムの特に有利な実施形態では、所定の期間は 5 ms 以下であり、所定の周波数は少なくとも 400 ms 毎に 1 パルスであり、最小電流は 20 mA 以下であり、好ましくは 10 mA である。PoE 配電システムに適用されるこの実施形態は、低減されることになる MPS の一部として電気エネルギーが消費されることを可能にする。

【0016】

本発明に従った配電システムの様々な実施形態において、給電装置はパワーオーバイーサネット（登録商標）規格において指定される給電機器であり、導電体はイーサネット（登録商標）ケーブルであり、及び / 又は受電装置はパワーオーバイーサネット（登録商標）規格において指定される受電装置であり、任意選択的に、パルス生成回路は受電装置に含まれる物理インターフェースチップ又はチップセットの一部である。

10

【0017】

本発明に従った配電システムの一実施形態では、パワーオーバイーサネット（登録商標）規格において指定される受電装置は分離スイッチを含み、制御可能スイッチがこの分離スイッチである。PoE 規格に従った PD は分離スイッチが存在することを要求するため、このスイッチは制御可能スイッチとして使用することができ、それによって追加部品を追加する必要性を省いている。

【0018】

本発明の第 2 の態様において、給電装置が提供され、この給電装置は本発明に従ったシステムにおいて使用されるように構成される。

20

【0019】

本発明の第 3 の態様において、受電装置が提供され、この受電装置は本発明に従ったシステムにおいて使用されるように構成される。

【0020】

本発明の第 4 の態様において、給電装置に電気的に結合された受電装置において電流パルスを生成するための方法が提供される。本発明に従った第 1 の方法において、方法は以下のステップ：給電装置から受電装置の少なくとも一部を電気的に切り離すステップと、給電装置から受け取られた電気エネルギーを消費するステップとを含む。本発明に従った第 2 の方法において、方法は以下のステップ：給電装置から受け取られた電気エネルギーを貯蔵部品に貯蔵するステップと、給電装置から受電装置の少なくとも一部を電気的に切り離すステップと、貯蔵部品に貯蔵された電気エネルギーを消費するステップとを含む。

30

【0021】

本発明の第 5 の態様において、コンピュータプログラム製品が提供され、このコンピュータプログラム製品は本発明に従った任意の方法のステップを実行するように構成される。

【0022】

請求項 1 に記載の配電システム、請求項 1 1 に記載の給電装置、請求項 1 2 に記載の受電装置、並びに請求項 1 3 及び 1 4 に記載の方法は、特に従属請求項で定義されるように、類似の及び / 又は同一の好ましい実施形態を有することが、理解されるべきである。

【0023】

本発明の好ましい実施形態はまた、従属請求項とそれぞれの独立請求項との任意の組み合わせであり得ることが理解されるべきである。

40

【0024】

本発明のこれらの及び他の態様は、以降に記載される実施形態から明らかになり、以降に記載される実施形態を参照して説明される。

【図面の簡単な説明】

【0025】

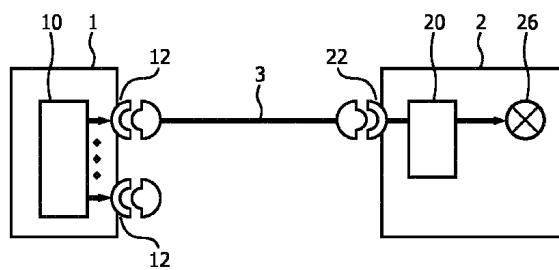

【図 1】配電システムの実施形態を概略的且つ例示的に示す。

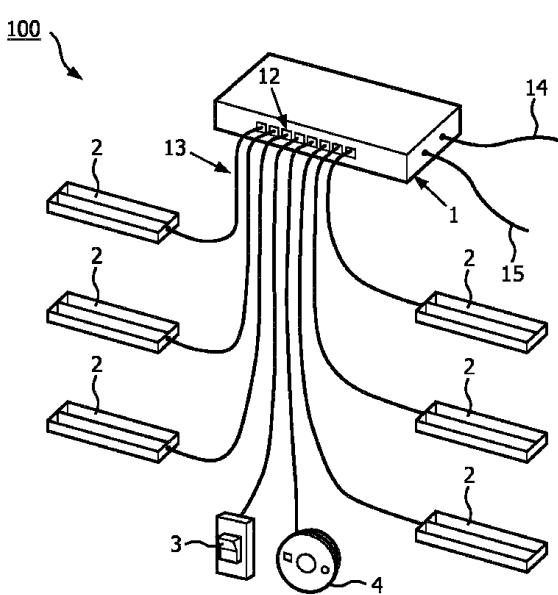

【図 2】照明用途のための配電システムの実施形態を概略的且つ例示的に示す。

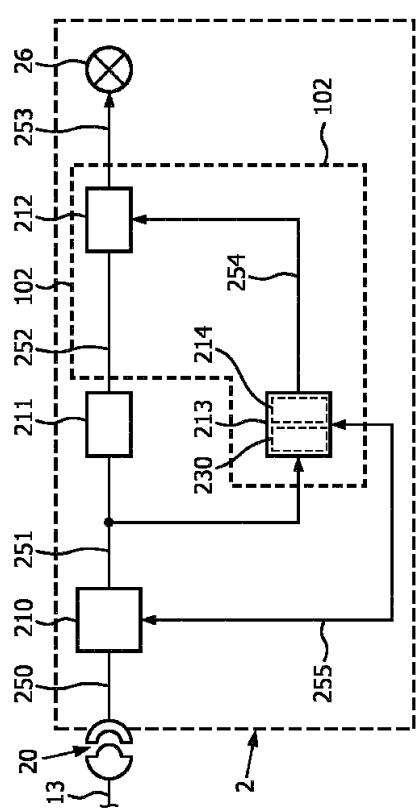

【図 3】照明用途のための受電装置の実施形態を概略的且つ例示的に示す。

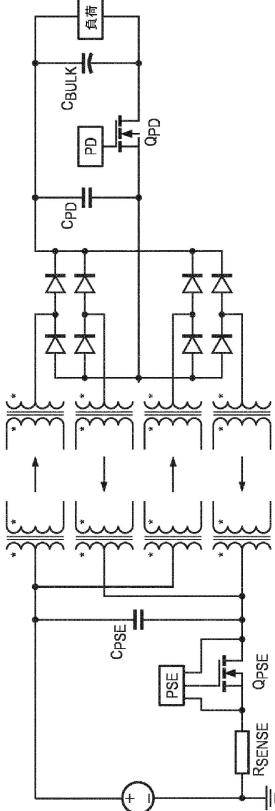

【図 4】フィルタ素子（C BULK、CPD、CPSE）及びケーブルインピーダンス（抵抗及び誘導性の値）を有する簡略化された PSE / PD 概略図を概略的且つ例示的に示す。

50

す。

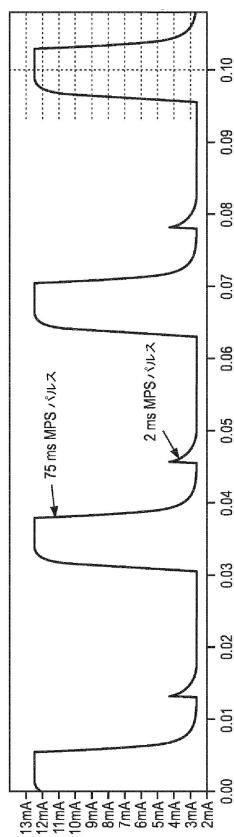

【図5】P Dインターフェース後に生成された10mAの75msパルス及び2msパルスを伴ってR S E N S Eを流れた電流の流れを示している、L T - s p i c eシミュレーションを概略的且つ例示的に示す。

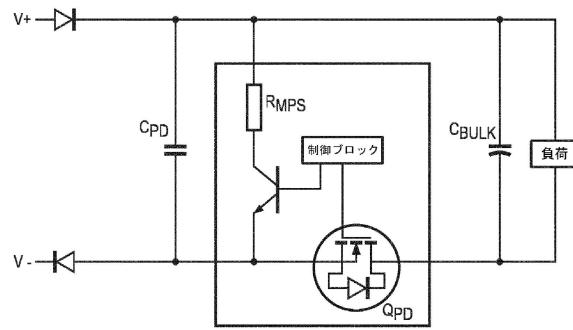

【図6】抵抗及びスイッチを含む本発明に従った受電装置の実施形態を概略的且つ例示的に示す。

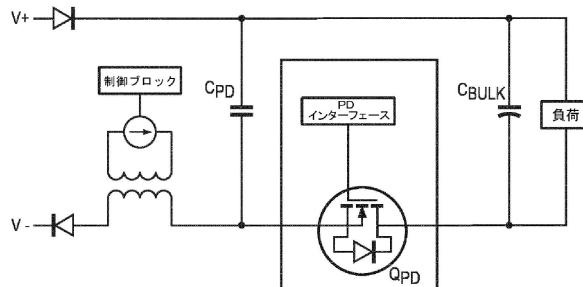

【図7】磁界貯蔵部品を含む本発明に従った受電装置の実施形態を概略的且つ例示的に示す。

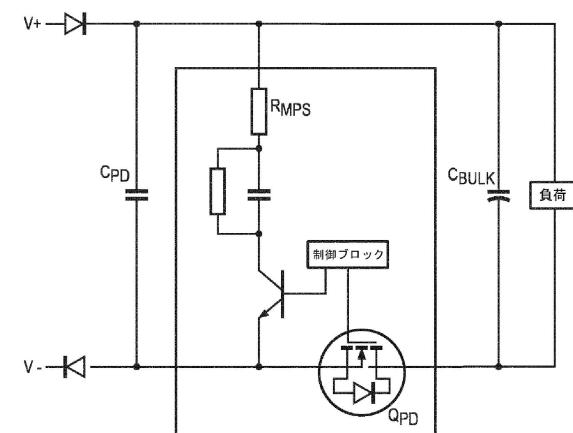

【図8】抵抗／コンデンサの一続きを含む本発明に従った受電装置の実施形態を概略的且つ例示的に示す。

10

【図9A】本発明に従った方法の実施形態を概略的且つ例示的に示す。

【図9B】本発明に従った方法の実施形態を概略的且つ例示的に示す。

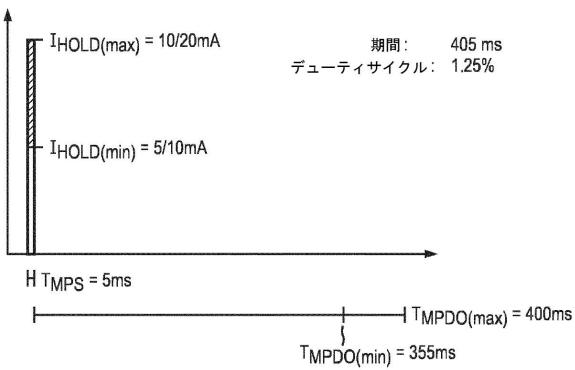

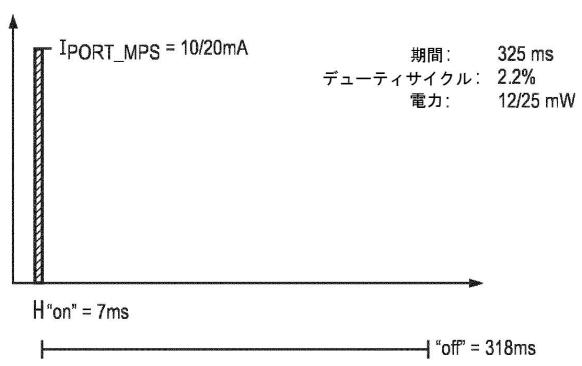

【図10】P S E側からのI E E E 8 0 2 . 3 a f / a tに従ったM P Sタイミングの概要を概略的且つ例示的に示す。

【図11】P D側からのI E E E 8 0 2 . 3 a f / a tに従ったM P Sタイミングの概要を概略的且つ例示的に示す。

【図12】P S E側からの本発明の実施形態に従ったM P Sタイミングの概要を概略的且つ例示的に示す。

【図13】P D側からの本発明の実施形態に従ったM P Sタイミングの概要を概略的且つ例示的に示す。

20

#### 【発明を実施するための形態】

##### 【0026】

I E E E 8 0 2 . 3 a f / a t規格は電力及びデータの分配システムを定義しており、このシステムは、ツイストペアイーサネット（登録商標）ケーブルを介して電力及びデータを分配することを可能にする。この規格に従うと、電気消費機器はスイッチから電力を受け取るために且つデータを交換するためにスイッチに接続され得、スイッチは複数のポートを含み、各ポートには単一の電気消費機器が接続され得る。イーサネット（登録商標）は、ローカルエリアネットワーク（L A N : local area network）のためのコンピュータネットワーク技術のファミリーである。イーサネット（登録商標）は、1980年に商業的に導入され、I E E EによってI E E E 8 0 2 . 3として1985年に標準化された。イーサネット（登録商標）は、競合する有線のL A N技術を大規模に置き換えた。イーサネット（登録商標）規格は、イーサネット（登録商標）で使用中の開放型システム間相互接続（O S I : Open Systems Interconnection）物理層の複数の配線及び信号通信の変形を含む。オリジナルの10B A S E 5イーサネット（登録商標）は共有媒体として同軸ケーブルを使用した。その後、同軸ケーブルは、ハブ又はスイッチと共にツイストペア及び光ファイバーリングによって置き換えられた。

30

##### 【0027】

10B A S E - Tイーサネット（登録商標）規格は2地点間リンクのみに対して設計され、全ての終端はイーサネット（登録商標）装置の内部に組み込まれた。より高速の接続は、速度、半二重及び全二重、並びにマスター／スレーブについて交渉するために最初のオートネゴシエーションを使用する。このオートネゴシエーションは、別の装置への接続の存在を検出するために10B A S E - T装置によって使用されるパルスと同様のパルスに基づいている。オートネゴシエーションが完了すると、送信されるデータが無い場合、リンクアップを維持するために、装置はアイドルバイトのみを送信する。

40

##### 【0028】

P o Eは、P o E電源がルーター、スイッチ、プリンタスプーラ等のような分離したネットワーク上の電気消費機器に、それらの標準イーサネット（登録商標）ケーブル接続を介して電気エネルギーを供給することを可能にする、アクティブな規格（I E E E 8 0 2 . 3 a f及びI E E E 8 0 2 . 3 a t）である。ここで、実際の標準化は、1つのC a t 5接続あたり50W超の電力レベルをサポートする予定である。現在、照明器具（センサ

50

一、スイッチ、光源)、又はアクティプスピーカー、インターネットラジオ、デジタル多用途ディスク(DVD: Digital Versatile Disk)プレーヤー、セットトップボックス、及び更にはテレビジョン(TV: television)セットなどの娛樂機器など、全ての種類の低電力消費機器について同規格を使用するための議論が進められている。PoE電話及びPoE受電制御装置は、既にオフィスで一般的なものになりつつある。

#### 【0029】

図1は、複数のPoE対応出力ポート12を備えた中央電源装置(例えば、給電機器(PSU))1を有するPoEベースの照明システムの従来のアーキテクチャを示す。各負荷装置2に対して、出力ポート12のうちの1つがコネクタ付きのCat5/6ケーブル3によって配線される。図1の例において、負荷装置2は、光源26及びPDコントローラ/ドライバ20を組み込んだPoEランプである。他の負荷装置も、送風機、センサ、又はディスプレイ若しくはスイッチパネルのようなユーザインターフェース装置を含むことができる。電源装置1は、個々の出力ポート12の各々について印加される電圧を制御し、且つ、各負荷装置内のPDコントローラ20によって伝達された電力要求に対する過電流を監視する、PSUコントローラ10を含む。

10

#### 【0030】

図2は、受電装置2、3、及び4に電力を供給するための電力供給装置1を含む、照明用途のための配電システム100の実施形態を概略的且つ例示的に示す。電力供給装置1は、受電装置2、3、及び4がイーサネット(登録商標)ケーブル13を介して接続される複数のポート12を含み、このイーサネット(登録商標)ケーブル13はデータと共に供給電力を伝達するように適合されている。電力供給装置1は、電源コンセント(図示せず)に直接接続され得る電気接続15を介して入力電力を受け取り、データは、別のイーサネット(登録商標)ケーブル14を介して、例えばスイッチなどの別の装置(図示せず)から受信され得る。受け取られた電力から、電源部11は、パワーデバイスマネージャ18を介して、受電装置2、3、及び5に供給されることになる電力を生成する。データは、パワーデバイスマネージャ18を介してそれぞれの受電装置2、3、又は4に送信される前に、ネットワークデータ処理装置19によって処理されてもよい。

20

#### 【0031】

ここで、受電装置2、3、及び4は照明器具2、スイッチング素子3、及び存在センサ4を含む。これらは、スイッチング素子3が人によって作動された後で、及び/又は存在センサ4によって人の存在が検知された後で、スイッチング素子3及び/又は存在センサ4がスイッチ1を介して照明器具2に調光コマンドを送信するように適合され得る。

30

#### 【0032】

照明器具2は、概略的且つ例示的に図3により詳細に示される。照明器具2は、この実施形態では、発光ダイオード(LED: light-emitting diode)である、電気負荷26を含む。照明器具2は、電力供給部1によって供給された電力から電気負荷電力を生成するために、且つ、この電気負荷電力を電気負荷26に提供するために、電気負荷電力提供部102を含む。イーサネット(登録商標)ケーブル13は、照明器具2のジャック20に接続されている。データと共に搬送された電力は、電力-データ経路250を介して電力-データスプリッタ210に供給される。電力-データスプリッタ210は、イーサネット(登録商標)ケーブル13によって搬送された電力とデータとを分割する。次いで、分割されたデータはデータ経路255を介して更に搬送され、分割された電力は電力経路251を介して更に搬送される。電力-データスプリッタ210は、例えば、電力信号とデータ信号とを分割するための磁気回路を含む。

40

#### 【0033】

照明器具2は、PoEシステムにおいて照明器具2を識別するために(及び任意選択的にスイッチ1と電力クラスを交渉するために)、受電装置コントローラ211を更に含む。電気負荷電力提供部102は、電力供給装置1によって供給され、受電装置コントローラ211を介して電気負荷ドライバ212によって受け取られた電力から電気負荷電力を生成するために、且つ、LED26にこの電気負荷電力を供給するために、電気負荷ドライ

50

バ212（及び電力供給装置1から受電装置2によって引き出される入力電流が、例えば、電力クラス4に対してPoE規格802.3atによって規定される0.6Aなどの所定の高い方の入力電流の閾値未満で最大化されるように電気負荷電力の電力レベルを決定するために、且つ、決定された電力レベルを示す電力制御信号を制御信号経路254を介して電気負荷ドライバ212へ送信するために、任意選択的に電気負荷電力コントローラ213）を含む。電気負荷ドライバ212は、電気負荷電力コントローラ213から受信された電力制御信号に従って、供給された電力から電気負荷電力を生成するように適合される。電気負荷電力は、電気負荷電力経路253を介して、電気負荷ドライバ212からLED26へ提供される。電気負荷ドライバ212は、LED26を駆動するために対応する電気負荷駆動電流を生成することにより、電気負荷電力を生成するように適合される。電気負荷電力提供部102、特に、電気負荷電力コントローラ213、又は電気負荷ドライバ212は、制御信号を低域通過フィルタするように適合されてもよい。

#### 【0034】

PoE規格IEEE802.3atは、多数の安全規定を有する非常に保守的な規格である。PoE規格IEEE802.3atは、CAT3（カテゴリ3）、CAT5（カテゴリ5）、及びCAT6（カテゴリ6）ケーブル並びにイーサネット（登録商標）がグローバルに使用されているほぼ全ての考えられる方法で動作するように設計されている。このことは、この規格に多くの歴史及び後方互換性を持ち込み、且つ、極めて「少数向けの」使用シナリオのサポートも可能にする。これらは、例えば、CAT3ケーブル（実用的には、少なくとも10年間はもはや使用されていない）との互換性、旧ACベースの切断検出方式との後方互換性、及びクロスオーバーケーブル（実用的には、少なくとも5年間はエンドノード接続において無関係である）との互換性を含む。

#### 【0035】

PoEを照明に使用すると、他の殆どのPD（アクセスポイント及びポイントチルトズームカメラなど）よりもはるかに計算上単純な装置が導入される。照明装置は、要求される電力が非常に低い「オフ」時間の長い期間も有する。装置は、イーサネット（登録商標）リンクを維持し、場合により低電力センサに給電することのみが可能でなければならない。IEEE802.3az及び最新の物理インターフェース（例えば、単一のマイクロコントローラに統合された）の最近の導入により、100mW未満のイーサネット（登録商標）リンクを維持することが可能になる。例えば、355ms毎に5msにMPSパルスの幅を低減することにより、エネルギー効率が向上され得る。しかしながら、そのような短いパルスがPD側におけるコンデンサから引き出されるとき、それらはPSE側における電流感知機構には見えない。問題は、ケーブル（及び他の部品の幾つか）のインピーダンスとPDインターフェース（図1を参照）とが結合された後で配置されるより大きいCBULKコンデンサにある。

#### 【0036】

図4では、フィルタ素子（CBULK、CPD、CPSE）及びケーブルインピーダンス（抵抗及び誘導性の値）を有する簡略化されたPSE/PD概略図が示されている。PSEは、PSEからPDへの（PSEのポートのうちの1つを介した）電流の流れをセンス抵抗（SENSE）上で感知する。PSEは、コンデンサ（CPSE）を有する。PSEは、PDが接続されているポートを制御するスイッチ（QPS）を有する。PDは2つのワイヤ対を含むイーサネット（登録商標）ケーブルを介してPSEに接続される。PDの側では、負荷（例えば、照明器具）に正しい極性が提供されることを確実にするために、2つのダイオードブリッジが存在する。PDは、コンデンサ（CPD）及びバルクコンデンサ（CBULK）を含む。分離スイッチなどの制御可能スイッチ（QPD）は、PSEから負荷（及びCBULK）を切り離すことができる。

#### 【0037】

220μFのコンデンサなどの典型的なPDバルクコンデンサを使用すると、MPSパルスはPSEセンス抵抗において殆ど見えないことが、シミュレーションで確認される（図5を参照）。本発明の1つの実施形態では、これは、パルス化されたMPS動作の間、バ

ルクコンデンサの効果を無効にすることを通じて克服される。それは、P D インターフェースの前にM P S パルス電流を引き出すことによって、且つ、M P S 電流が引き出される短い間隔の間にP D 内部スイッチQ P D をオフにすることによって達成され得る。これは、P D 装置に対する影響を最小限に抑えながら、R S E N S E を流れる正しい電流波形に帰着するであろう。P D スイッチ及びM P S 電流抵抗の共同管理を有するコントローラは、この解決策の第1の実施形態の一部である。例として、機能はP D インターフェースチップに統合され得るが、機能はチップの外部で実装されることもできる。

#### 【 0 0 3 8 】

図6は、抵抗及びスイッチを含む本発明に従ったP D の実施形態を示す。V + / V - は入力であり、イーサネット（登録商標）ケーブルインターフェースに（例えば、正しい極性を提供するフルダイオードブリッジを介して、）電気的に結合されている。パルス生成回路は、制御ブロック（C O N T R O L）、スイッチ、及び抵抗（R M P S ）を含む。制御ブロックは、V + / V - 入力にわたる抵抗と直列に配置されたスイッチを制御するように構成される。スイッチを開くことにより、電流がR M P S を通して流れM P S を生成する。制御ブロックは、更にQ P D を制御するように構成される。M P S 電流が引き出されている間に同時にQ P D をオフにすることにより、C B U L K はパルス生成回路及びP S E から電気的に切り離される。

10

#### 【 0 0 3 9 】

P D インターフェースの前にM P S パルス電流を引き出すことにより、典型的にP D インターフェースの後に配置されるバルクコンデンサのフィルタリング効果を無効にするために同時にP D スイッチをオフにする一方で、これは、C B U L K によってM P S が取り除かれて、M P S がP S E によって検出されなくなること、及びP D が接続されているポートへの電力をP S E がオフにすることを防ぐ。

20

#### 【 0 0 4 0 】

制御可能スイッチ（Q P D ）は、P o E 準拠のP D における分離スイッチ、又は例えばバルクコンデンサなどの1つ若しくは複数のコンデンサのみを切断するスイッチである個別スイッチであり得る。分離スイッチは、全てのP o E 準拠のP D の一部であり、検出フェーズ及び分類フェーズの間、又は電力損失の間、物理インターフェースからP D の戻り側を切断する。規格によると、P D は、4 2 V 以上のP I 電圧レベルにおいて分離スイッチをオンにし、3 0 V 以下の物理インターフェース電圧レベルにおいて分離スイッチをオフにすることを更に要求される。P D 回路の出力が1 8 0  $\mu$  F 以上のバルクコンデンサに接続されている場合、P D は自発的に始動時の電流を3 5 0 m A 以下に制限しなければならない。

30

#### 【 0 0 4 1 】

図7では、本発明の実施形態に従って、磁界貯蔵部品を含むP D が示されている。この例では、主電流ループと直列のパルストラnsが使用されて、所望のM P S パルス波形を有する余分な電流を注入する。ここで、M P S が生成されているとき、分離スイッチは導通している。パルス生成器が、パルストラnsの一次巻線において一次電流を生成する。これは、（少なくとも）最小電流である二次電流に変換されて、P S E からP D への電流の流れがP S E の側において見られることを可能にする。電流パルスをP S E に伝導するために、パルストラnsは二次巻線上でP S E への閉電流ループに接続される。V - からの電流は、分離スイッチを通り、C B U L K (Q P D が開いているため) を通ってV + に向けて流れ、二次巻線はこのループ内の何れかの箇所に直列に配置される。

40

#### 【 0 0 4 2 】

パルストラnsがM P S 電流ループからパルス生成器を分離するため、それは様々な異なる回路で実装され得る。例として、トランスの一次巻線に放電するコンデンサが使用され得る。この実施形態では、制御ブロックは制御可能スイッチを制御することができ、この制御可能スイッチは、トランスの一次巻線においてM P S が生成されていないとき、トランスの二次巻線上の電圧降下を低く維持するために一次巻線を短絡させる。なぜなら、これによりP D における電圧が低減されるからである。

50

## 【0043】

図8は、抵抗 / コンデンサ直列が使用されているPDの実施形態を示す。パルスを生成するため、単純に抵抗が使用されて所望の電流を引き出すことができるが、V+とV-との間の抵抗 / コンデンサの直列接続も使用され得る。

## 【0044】

本発明の任意の実施形態において、MPSの特性に加えられる変更は、MPSの持続期間（及び任意選択的にサイクル）に限定され得る。例として、例えばPSEなどの給電装置が、給電装置から受電装置への電流の流れ（例えば、MPS）を感知することなく電力を供給したままである最大時間は、現行のIEEE802.3規格と同じである（表1を参照）。これは、安全性の観点から有益であり得る。

## 【0045】

## 【表1】

| パラメータ                  | 現行の IEEE 802.3af/at 規格 |          | 本発明に従った実施形態における値 |           |

|------------------------|------------------------|----------|------------------|-----------|

|                        | 給電装置/ PSE              | 受電装置/ PD | 給電装置/ PSE        | 受電装置/ PD  |

| I <sub>HOLD(MAX)</sub> | 10mA                   |          | 10mA/20mA        |           |

| I <sub>PORT_MPS</sub>  |                        | 10mA     |                  | 10mA/20mA |

| T <sub>MPS</sub>       | 60ms                   | (75ms)   | 5ms              | (7ms)     |

| T <sub>MPDO(min)</sub> | 300ms                  | (250ms)  | 355ms            | (318ms)   |

| T <sub>MPDO(max)</sub> | 400ms                  |          | 400ms            |           |

表1. 現行のPoE規格と本発明に従った実施形態との比較

## 【0046】

表1では、現行のIEEE802.3af/at規格のMPSタイミング及び電流値と、本発明に従ったシステムにおいて使用され得るMPS値との比較がなされている。I<sub>HOLD(max)</sub>はPSE側におけるMPSの最大電流であり、一方、I<sub>PORT\_MPS</sub>はPDによって生成された電流の流れであり、T<sub>MPS</sub>はMPSの持続期間であり、T<sub>MPDO(min)</sub>はMPSパルス間の最小時間であり、T<sub>MPDO(max)</sub>はMPSパルス間で許容される最大時間である。これらの値の全ては、例示目的のみのために示される。

## 【0047】

表2に示すように、本発明を実装するPSE及びPDと本発明を実装しないPSE及びPDとの間で、後方互換性を確実にすることが可能である。

## 【0048】

10

20

30

40

50

【表 2】

|                                                    | IEEE 802.3af/at<br>(タイプ 1 又はタイプ 2)に従った PD  | 本発明の実施形態に従った PD                                                                                              |

|----------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| IEEE 802.3af/at<br>(タイプ 1 又は<br>タイプ 2)に<br>従った PSE | -                                          | PD は、PSE をより短い MPS をサポート<br>していない IEEE 802.3af/at に従った<br>PSE として識別し、PD は IEEE<br>802.3af/at 規格により MPS を使用する |

| 本発明の<br>実施形態に<br>従った PSE                           | PSE は、IEEE 802.3af/at により<br>MPS を検出するであろう | PD は、PSE をより短い MPS をサポート<br>している PSE として識別し、PD は<br>より短い MPS を使用する                                           |

表 2. IEEE 802.3af/at に従った MPS か、又は本発明の実施形態に従ったより短い MPS の

いずれかをサポートしている PD 及び PSE 間の互換性

## 【0049】

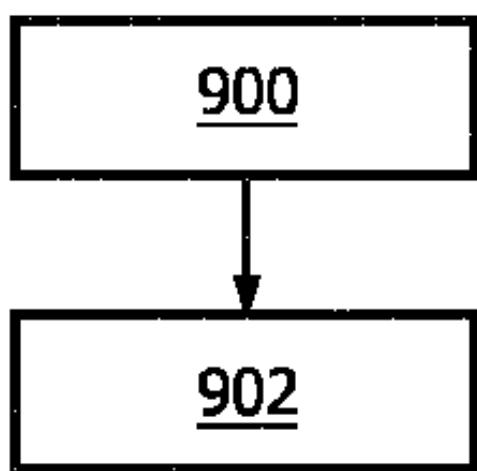

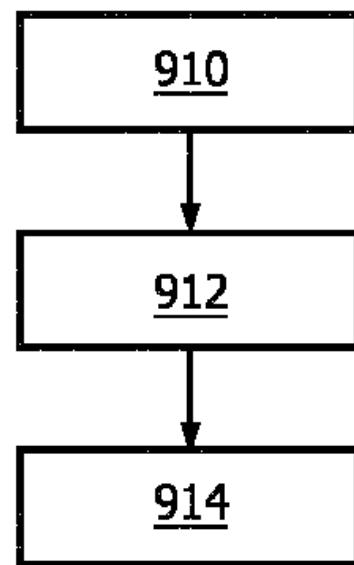

図 9 A 及び図 9 B は、本発明に従った方法の実施形態を概略的且つ例示的に示している。図 9 A は給電装置に電気的に結合された受電装置において電流パルスを生成するための方法を示し、この方法は、給電装置から受電装置の少なくとも一部を電気的に切り離す第 1 のステップ (900) と、給電装置から受け取られた電気エネルギーを消費する第 2 のステップ (902) とを含む。

## 【0050】

図 9 B は給電装置に電気的に結合された受電装置において電流パルスを生成するための方法を示し、この方法は、給電装置から受け取られた電気エネルギーを貯蔵部品に貯蔵する第 1 のステップ (910) と、給電装置から受電装置の少なくとも一部を電気的に切り離す第 2 のステップ (912) と、貯蔵部品に貯蔵された電気エネルギーを消費する第 3 のステップ (914) とを含む。

## 【0051】

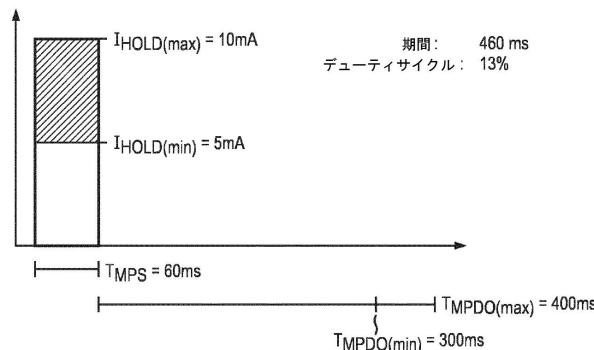

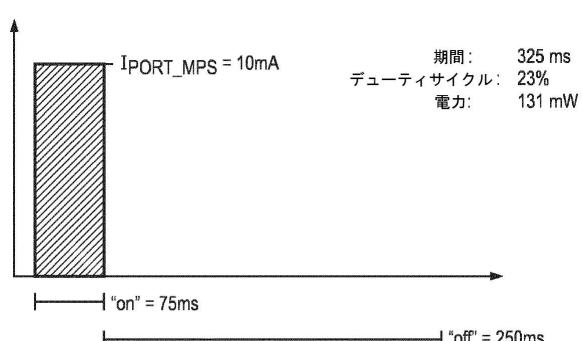

図 10、図 11、図 12、及び図 13 の各々は、IEEE 802.3af/at 規格に従った PSE 及び PD の観点からと、本発明の実施形態によるシステムにおいて実装され得るような PSE 及び PD の観点からとの、MPS タイミングの例をそれぞれ示す。PSE 側では、ポート I HOLD (min) で電力を維持するために感知されなければならない最小電流は 5 mA であり、最大 I HOLD (max) は 10 mA である。この MPS は 60 ms にわたり感知されなければならない、各パルス間が 300 ms ~ 400 ms を超えることはできない。PD 側では、MPS が、例えば、75 ms 持続し、その後に電流が全く使われない（又は 10 mA 未満が使われる）期間が 250 ms 続く、10 mA のパルスを通して、MPS が生成される。POE システムにおいて提供される典型的な電圧を用いると、この MPS は 131 mW の電気エネルギーを必要とし得る。

## 【0052】

本発明が PSE に適用される場合、PSE は、5 ms の長さであるパルスが検出されるときにポート上で電力を維持するように変更され得る。MPS の最小電流は 5 mA ~ 10 mA に、及び最大は 10 mA ~ 20 mA に設定され得る。各 MPS の後、355 ms ~ 400 ms の間、いかなる電流の流れも存在する必要がない。PD 側では、7 ms 以内に 10 ~ 20 mA を消費することにより MPS が生成され、（実質的に）エネルギーが全く消費されない 318 ms の期間が後に続く。

## 【0053】

10

20

30

40

50

M P S タイミング、最小及び最大電流等に関連して提供された例は、例示目的のみのために使用され、決して本発明の範囲を限定しない。

【 0 0 5 4 】

上述した実施形態においては、照明器具に含まれる電気負荷は発光ダイオード ( L E D ) であるが、別の実施形態では、電気負荷は、有機発光ダイオード ( O L E D : organic light-emitting diode ) 、レーザ、ハロゲンランプ等であってもよい。

【 0 0 5 5 】

特許請求される本発明を実施する際に、開示された実施形態に対する他の変形形態が、図面、開示、及び添付の特許請求の範囲の調査から当業者によって理解され、且つ実施され得る。

10

【 0 0 5 6 】

特許請求の範囲において、単語「含む ( comprising ) 」は他の要素又はステップを排除するものではなく、また、不定冠詞「 1 つの ( a ) 」又は「 1 つの ( an ) 」は、複数を排除するものではない。

【 0 0 5 7 】

単一のユニット又は装置が、特許請求の範囲に記載される複数の項目の機能を満たしてもよい。特定の措置が互いに異なる従属請求項において記載されているという単なる事実は、これらの措置の組み合わせが有利に使用され得ないことを示すものではない。

【 0 0 5 8 】

1つ若しくは複数のユニット又は装置によって実行される、電気負荷電力の電力レベルの決定などの決定、交渉手順等は、他の任意の数のユニット又は装置によって実行され得る。配電システム内部の受電装置の電気負荷に電気負荷電力を供給するための方法に従った受電装置の手順及び / 又は制御は、コンピュータプログラムのプログラムコード手段として、及び / 又は専用のハードウェアとして実装され得る。

20

【 0 0 5 9 】

コンピュータプログラムは、他のハードウェアと共に又はその一部として供給される、光記憶媒体又は固体媒体などの適切な媒体上に格納 / 配布され得るが、インターネット又は他の有線若しくは無線の通信システムを介してなど、他の形態で配布されてもよい。

【 0 0 6 0 】

特許請求の範囲におけるいかなる参照符号も、範囲を限定するものとして解釈されるべきではない。

30

40

50

【図面】

【図 1】

FIG. 1

【図 2】

FIG. 2

10

20

【図 3】

FIG. 3

【図 4】

図 4

30

40

50

【図 5】

図 5

【図 6】

図 6

10

20

【図 7】

図 7

【図 8】

図 8

30

40

50

【図 9 A】

【図 9 B】

10

20

FIG. 9A

FIG. 9B

【図 10】

図 10

【図 11】

図 11

30

40

50

【図 1 2】

図 1 2

【図 1 3】

図 1 3

10

20

30

40

50

---

フロントページの続き

トホーフェン ハイ テク キャンパス 5

合議体

審判長 酒井 朋広

審判官 清水 稔

審判官 山本 章裕

(56)参考文献

米国特許出願公開第 2013 / 0154603 (US, A1)

特表 2013 - 535731 (JP, A)

国際公開第 2014 / 002073 (WO, A1)

米国特許出願公開第 2011 / 0279096 (US, A1)

米国特許出願公開第 2013 / 0127523 (US, A1)

米国特許第 08565040 (US, B1)

(58)調査した分野 (Int.Cl. , DB名)

H02J 1/00-1/16,