## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2005-18082 (P2005-18082A)

(43) 公開日 平成17年1月20日(2005.1.20)

(51) Int.C1.7

FI

テーマコード (参考)

G02F 1/1368 HO1L 21/336 HO1L 29/786

GO2F 1/1368 HO1L 29/78

2H092 5 F 1 1 O

HO1L 29/78 612D

> 審査請求 未請求 請求項の数 9 〇L (全 29 頁)

(21) 出願番号 (22) 出願日

特願2004-190036 (P2004-190036) 平成16年6月28日 (2004.6.28)

(31) 優先権主張番号 2003-041990

(32) 優先日

平成15年6月26日 (2003.6.26)

(33) 優先権主張国 韓国(KR)

(74) 代理人 100094145

弁理士 小野 由己男

(74) 代理人 100106367

(71) 出願人 390019839

619A

弁理士 稲積 朋子

三星電子株式会社

(72) 発明者 金東奎

大韓民国京畿道龍仁市水枝邑豊徳川里11

大韓民国京畿道水原市靈通区梅灘洞416

67番地523棟1305号

Fターム(参考) 2H092 GA11 JA24 JA34 JA37 JA41

JB22 JB31 KB01 KB04 MA10 MA16 MA17 NA25 PA01 PA08

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ表示板の製造方法

## (57)【要約】

【課題】 本発明の目的は、層間の整列の誤差を最少化 することができる薄膜トランジスタ表示板の製造方法を を提供することにある。

【解決手段】 絶縁基板の上部にゲート電極を含むゲー ト線を形成する。次に、ゲート絶縁膜、半導体層、及び 抵抗性接触層を順に形成した後、導電膜を積層しパター ニングして、ソース電極を有するデータ線、ドレーン電 極、及び色フィルター用整列キーを形成する。次に、基 板の上部に顔料を含む色フィルター用感光膜を塗布し、 色フィルター用整列キーを基準として色フィルター用マ スクを整列した後、色フィルター用感光膜を露光及び現 像して赤、緑、青の色フィルターを順に形成する。次に 、保護膜を積層しパターニングして、ドレーン電極を露 出する接触孔を形成した後、保護膜の上部にIZOまた はITOを積層してからパターニングしてドレーン電極 と連結される画素電極を形成する。

【選択図】 図8

20

30

40

50

#### 【特許請求の範囲】

## 【請求項1】

基板上にゲート電極を有するゲート線を形成する段階、

前記基板上にゲート絶縁膜を積層する段階、

前記ゲート絶縁膜上部に半導体層を形成する段階、

前記半導体層上部に抵抗性接触層を形成する段階、

前記抵抗性接触層と接するソース電極を有するデータ線及びドレーン電極を形成する段階、

前 記 デ ー タ 線 と 同 一 の 層 で 色 フ ィ ル タ ー 用 整 列 キ ー を 形 成 す る 段 階 、

前記基板上部に色フィルター用感光膜を形成する段階、

前記整列キーを基準として色フィルター用マスクまたは前記基板を整列し、前記色フィルター用感光膜を露光及び現像して色フィルターを形成する段階、

前記ゲート線と前記データ線とで定義される画素領域に前記ドレーン電極と連結される画素電極を形成する段階を含む、薄膜トランジスタ表示板。

## 【請求項2】

前記画素電極下部に保護膜を形成する段階をさらに含む、請求項1に記載の薄膜トランジスタ表示板の製造方法。

#### 【請求項3】

前記保護膜は露出された前記半導体層を覆う第1保護膜または前記色フィルターを覆う第2保護膜のうち少なくとも一つで形成される、請求項2に記載の薄膜トランジスタ表示板の製造方法。

### 【請求項4】

前記第1保護膜は窒化ケイ素または酸化ケイ素で形成される、請求項3に記載の薄膜トランジスタ表示板の製造方法。

#### 【請求項5】

前記第2保護膜は有機絶縁物質で形成される、請求項3に記載の薄膜トランジスタ表示板の製造方法。

#### 【請求項6】

前記色フィルターの形成段階は、赤、緑、青の色フィルターを前記画素領域に順に形成する段階を含む、請求項 1 に記載の薄膜トランジスタ表示板の製造方法。

### 【請求項7】

互いに隣接する前記画素領域の前記赤、緑、青の色フィルターの周縁は互いに重畳して 形成される、請求項 6 に記載の薄膜トランジスタ表示板の製造方法。

## 【請求項8】

前記半導体層、前記抵抗性接触層、及び前記データ線と前記ドレーン電極は、一つの感光膜パターンを利用した写真エッチング工程で形成される、請求項1に記載の薄膜トランジスタ表示板の製造方法。

### 【請求項9】

ゲート電極を有するゲート線、半導体層、ソース電極を有するデータ線及びドレーン電極、データ線と同一の層からなる整列キー、ドレーン電極と連結される画素電極を含む薄膜トランジスタ表示板を形成する段階、

前記薄膜トランジスタ表示板と対向する対向表示板を形成する段階、

前記整列キーを利用して前記薄膜トランジスタ表示板と前記対向表示板を整列する段階

前記薄膜トランジスタ表示板と前記対向表示板を結合する段階、を含む液晶表示装置の製造方法。

#### 【発明の詳細な説明】

## 【技術分野】

## [0001]

本発明は、薄膜トランジスタ表示板の製造方法及び液晶表示装置の製造方法に関し、さ

らに詳細には、赤、緑、青の色フィルターを含む薄膜トランジスタ表示板の製造方法及び液晶表示装置の製造方法に関する。

### 【背景技術】

[0002]

液晶表示装置は、一般に、電場を生成する電極を有している二つの基板の間に液晶物質を注入し、二つの電極に互いに異なる電位を印加することによって電界を形成して液晶分子の配列を変更させ、これによって光の透過率を調節して画像を表現する装置である。

[0003]

このような液晶表示装置は、画素電極と赤色(R)、緑色(G)、青色(B)の色フィルターが形成されている複数の画素を有しており、配線を通じて印加される信号によって各画素が駆動されて表示動作が行われる。配線には走査信号を伝達するゲート線(または走査信号線)、画像信号を伝達するデータ線(または画像信号線)があり、各画素は一つのゲート線及び一つのデータ線と連結されている薄膜トランジスタが形成されており、これを通じて画素に形成されている画素電極に伝達される画像信号が制御される。

[0004]

一般に、薄膜トランジスタが形成されている表示板には、ゲート信号またはスキャニング信号を伝達するゲート線、画像信号またはデータ信号を伝達するデータ線、画像信号が送られる画素電極及びゲート信号を通じて各画素の画素電極に伝達される画像信号を制御する薄膜トランジスタなどが形成されており、薄膜トランジスタ表示板と対向する対向表示板には、様々な色の画像を実現するためにそれぞれの画素に配置されている赤、緑、青の色フィルターが形成されている。

[0005]

このような液晶表示装置において開口率を確保することは重要な課題となっており、二つの表示板の整列誤差を最少化するために赤、緑、青の色フィルターを薄膜トランジスタ表示板に形成する技術が開発されている。

[0006]

この時、薄膜トランジスタ表示板を製造するためには、薄膜を形成する成膜工程、所望の形状の薄膜をパターニングするためのマスクを用いた写真エッチング工程などが繰返し実施されるのが一般的なことであるが、写真エッチング工程において多層の薄膜を形成するときに層間に整列の誤差(misalign)が生じたときに表示特性が低下する問題点が発生する。

【発明の開示】

【発明が解決しようとする課題】

[0007]

本発明が目的とする技術的課題は層間の整列の誤差を最少化することができる薄膜トランジスタ表示板の製造方法を提供することにある。

【課題を解決するための手段】

[0008]

本発明の実施例による薄膜トランジスタ表示板の製造方法では、データ線と同一の層に色フィルター用整列(align ley)キーを形成し、これを利用してマスクを整列して赤、緑、青の色フィルターを形成する。

[0009]

さらに詳細には、本発明の実施例による薄膜トランジスタ表示板の製造方法では、基板上にゲート電極を有するゲート線を形成し、ゲート線を覆うゲート絶縁膜を形成する。次に、ゲート絶縁膜上部に半導体層を形成し、半導体層上部に抵抗性接触層を形成し、抵抗性接触層と接するソース電極を有するデータ線及びドレーン電極を形成する。この時、データ線と同一の層で色フィルター用整列キーを形成する。次に、基板上部に色フィルター用感光膜を形成し、整列キーを基準として色フィルター用マスクを整列し、色フィルター用感光膜を露光及び現像して色フィルターを形成する。次に、ゲート線とデータ線とで定義される画素領域にドレーン電極と連結される画素電極を形成する。

20

30

40

20

30

40

50

## [0010]

画素電極下部に保護膜を形成する段階をさらに含むことができるが、保護膜は露出された半導体層を覆う第1保護膜または色フィルターを覆う第2保護膜のうち少なくとも一つで形成することができ、第1保護膜は窒化ケイ素または酸化ケイ素で形成されるのが好ましく、第2保護膜は有機絶縁物質で形成されるのが好ましい。

#### $[0 \ 0 \ 1 \ 1]$

色フィルターの形成段階は、赤、緑、青の色フィルターを画素領域に順に形成するが、 互いに隣接する画素領域の赤、緑、青の色フィルターの周縁は互いに重畳させて形成する のが好ましい。

#### [0012]

この時、半導体層、抵抗性接触層、及びデータ線とドレーン電極は、一つの感光膜パターンを利用した写真エッチング工程で形成することができる。

#### 【発明の効果】

## [ 0 0 1 3 ]

本発明による製造方法では、データ線と同一の層で色フィルター用整列キーを形成し、 これを基準として赤、緑、青の色フィルターを形成することによって整列誤差を最少化す ることができ、これによりデータ線の幅を最適に形成することができる。

## 【発明を実施するための最良の形態】

## [ 0 0 1 4 ]

添付した図面を参照して本発明の実施例に対して本発明の属する技術分野における通常の知識を有する者が容易に実施できるように詳細に説明する。しかし、本発明は種々な形態に変形して実現することができ、ここで説明する実施例に限定されない。

## [0015]

図面は、各種の層及び領域を明確に表現するために、厚さを拡大して示している。明細書全体を通じて類似した部分については同一な図面符号を付けている。層、膜、領域、板などの部分が他の部分の"上に"あるとする時、これは他の部分の"すぐ上に"ある場合に限らず、その中間に更に他の部分がある場合も含む。逆に、ある部分が他の部分の"すぐ上に"あるとする時、これは中間に他の部分がない場合を意味する。

## [0016]

以下、本発明の実施例による薄膜トランジスタ表示板の製造方法について図面を参照して詳細に説明する。

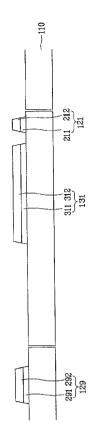

## [0017]

まず、図1乃至図3を参照して、本発明の第1実施例による液晶表示装置用薄膜トランジスタ表示板の構造について詳細に説明する。

## [0018]

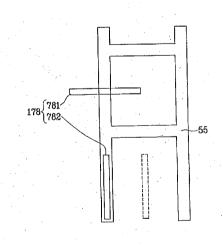

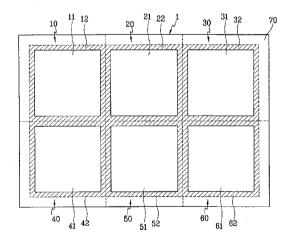

図 1 は本発明の実施例による液晶表示装置用薄膜トランジスタ表示板を製造するための基板を領域を区分して示した平面図である。

### [0019]

図1に示したように、一つの絶縁基板に同時にいくつかの液晶表示装置用表示板領域が形成される。例えば、図1のように、ガラス基板1一つに6個の液晶表示装置用パネル領域10、20、30、40、50、60は複数の画素からなる画面表示部11、21、31、41、51、61には主に薄膜トランジスタ、62を含む。画面表示部11、21、31、41、51、61には主に薄膜トランジスタ、信号線、画素電極、及び赤、緑、青の色フィルターなどが行列状に繰返し配置されており、周辺部12、22、32、42、52、62には駆動素子等と連結されている要素、つまり、信号線の端部とその他の画素電極と対向する共通電極に伝達される共通信号を外部から受けるための共通信号線などが配置されている。

## [0020]

ところが、このような液晶表示装置用薄膜トランジスタ表示板の製造方法において、多

30

40

50

層の薄膜パターンを形成するためにマスクを用いた数回の写真エッチング工程で形成される。この時、多層の薄膜は層間に正確に整列され形成されることが要求されており、層間整列を正確にするためには不透明膜からなる整列キー(align key)が必要であり、このような整列キーは基板1の郊外周辺部70に配置される。

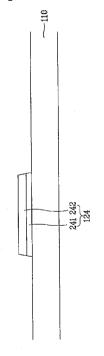

[0021]

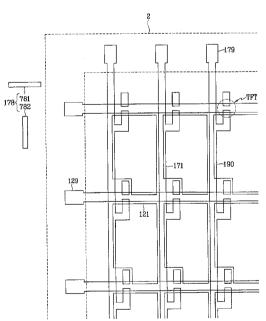

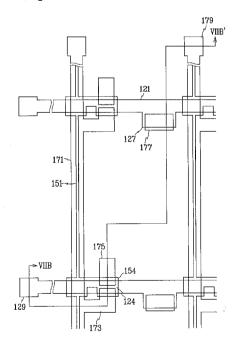

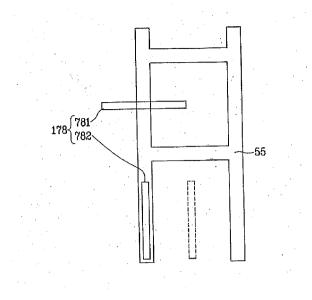

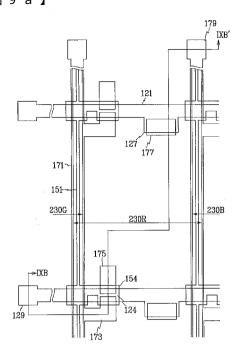

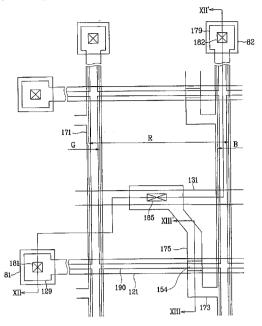

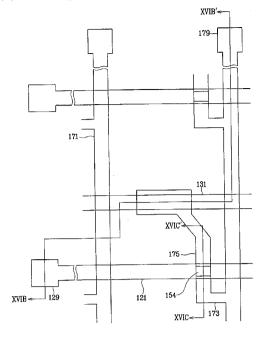

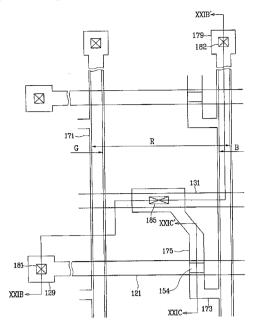

図 2 は図 1 において一つのパネル領域に形成された液晶表示装置用薄膜トランジスタ表示板の配置を概略的に示した配置図である。

[0022]

図2のように、線1で囲まれた画面表示部には複数の薄膜トランジスタ(TFT)と、それぞれの薄膜トランジスタ(TFT)に電気的に連結されている画素電極190と、ゲート線121及びデータ線171を含む信号線などが形成されている。表示部の外側の周辺部には、ゲート線121の端部129とデータ線171の端部179が配置されている。また、線2で囲まれた周辺部の外側の外郭部には、データ線171と同一の層からなり、横部781と縦部782とからなる整列キー178が形成されている。

[0023]

ここで、整列キー178は製造工程時に薄膜トランジスタ表示板に形成されている赤、緑、青の色フィルターを整列するために使用される。

[0024]

整列キー178は、液晶表示装置用薄膜トランジスタ表示板が完成され、パネル領域10、20、30、40、50、60を単位として分離された時には残らないこともあるが、その時までは残っている。

[0025]

本発明の実施例において、整列キー178は完成した表示板には残らないため、製造方法についてのみ説明する。

[0026]

まず、本発明の製造方法を適用して完成した本発明の一実施例による薄膜トランジスタ表示板の構造について具体的に説明する。

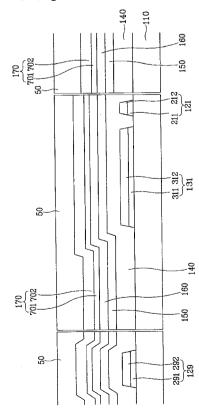

[0027]

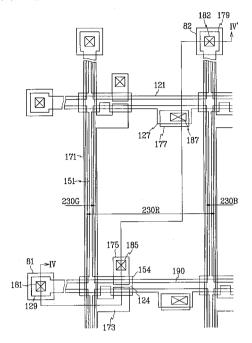

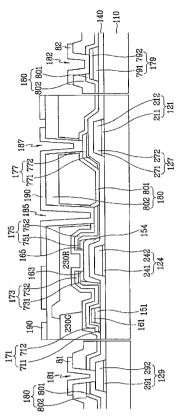

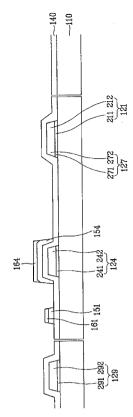

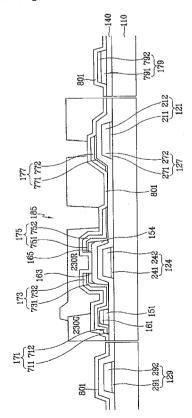

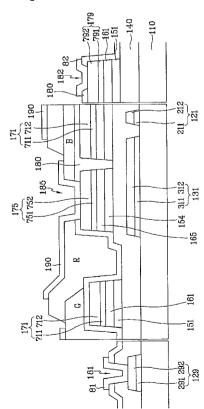

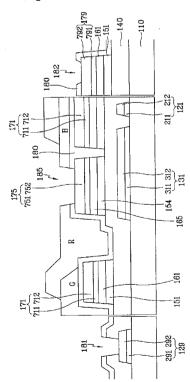

図3は本発明の一実施例による液晶表示装置用薄膜トランジスタ表示板の構造を示した配置図である。図4は図3に示す薄膜トランジスタ表示板のIV-IV´線による断面図である。

[0028]

絶縁基板 1 1 0 上にゲート信号を伝達する複数のゲート線 1 2 1 が形成されている。ゲート線 1 2 1 は図 3 中主に横方向にのびており、各ゲート線 1 2 1 の一部は複数のゲート電極 1 2 4 を形成する。また、各ゲート線の他の一部は下方向に突出して複数の拡張部(expansion) 1 2 7 を形成する。

[0029]

ゲート線121は物理的な性質が異なる二つの膜、つまり、下部膜211とその上の上部膜212を含む。上部膜212はゲート信号の遅延や電圧降下を減らすことができるように低い比抵抗(resistivity)の金属、例えば、アルミニウム(AI)やアルミニウム合金などアルミニウム系列の金属からなる。これとは異なり、下部膜211は他の物質、特に、IZO(indium zinc oxide)またはITO(indium tin oxide)との物理的、化学的、電気的な接触特性の優れた物質、例えば、モリブデン(Mo)、モリブデン合金(例:モリブデン-タングステン(MoW)合金)、クロム(Cr)などからなる。下部膜211と上部膜212との組み合わせの例としては、クロム/アルミニウム-ネオジム(Nd)合金を挙げられる。図4に、ゲート電極124の下部膜及び上部膜は各々図面符号271、272で、ゲート線121の端部129の下部膜及び上部膜は各々図面符号291、292で表示されている。

[0030]

下部膜211、241、271、291及び上部膜212、242、272、292の

30

40

50

側面は各々傾斜しており、その傾斜角は基板110の表面に対し約30°から80°である。

[0031]

ゲート線 1 2 1 上には、窒化ケイ素 ( S i Nx ) などからなるゲート絶縁膜 1 4 0 が形成されている。

[0032]

ゲート絶縁膜140上部には、水素化非晶質シリコン(非晶質シリコンはa-Siと略称する)などからなる複数の線状半導体151が形成されている。線状半導体151は主に縦方向にのびておりここから複数の突出部(extension)154がゲート電極124に向かってのびている。また、線状半導体151はゲート線121と交差する地点の付近で幅が広くなり、ゲート線121の広い面積を覆っている。

[ 0 0 3 3 ]

半導体 1 5 1 の上部には、シリサイド(silicide)またはn型不純物が高濃度にドーピングされているn+水素化非晶質シリコンなどの物質からなる複数の線状及び島型抵抗性接触部材(ohmic contact) 1 6 1 、 1 6 5 が形成されている。線状接触部材 1 6 1 は複数の突出部 1 6 3 を有しており、この突出部 1 6 3 と島状接触部材 1 6 5 は対となって半導体 1 5 1 の突出部 1 5 4 上に位置する。

[0034]

半導体 1 5 1 及び抵抗性接触部材 1 6 1 、 1 6 3 、 1 6 5 の側面もまた傾斜しており、傾斜角は 3 0 ° から 8 0 ° である。

[ 0 0 3 5 ]

抵抗接触部材161、165及びゲート絶縁膜140上には、各々複数のデータ線171と複数のドレーン電極175及び複数の維持蓄電器用導電体177が形成されている。

[0036]

データ線171は主に縦方向にのびてゲート線121と交差し、データ電圧を伝達する。各データ線171からドレーン電極175に向かってのびた複数の枝がソース電極173をなす。一対のソース電極173とドレーン電極175は互いに分離されており、ゲート電極124に対して互いに反対側に位置する。ゲート電極124、ソース電極173、及びドレーン電極175は、半導体151の突出部154と共に薄膜トランジスタ(TFT)をなしており、薄膜トランジスタのチャンネルはソース電極173とドレーン電極175との間の突出部154に形成されている。維持蓄電器用導電体177は、ゲート線121の拡張部127と重なっている。

[0037]

データ線 1 7 1、ドレーン電極 1 7 5、及び維持蓄電器用導電体 1 7 7 もまたモリブデン (Mo)、モリブデン合金、クロム (Cr) などの下部膜 7 1 1、7 3 1、7 5 1、7 7 1、7 9 1 と、その上に位置したアルミニウム系列金属である上部膜 7 1 2、 7 3 2、 7 5 2、 7 7 2、 7 9 2 とからなる。

[0038]

データ線 1 7 1、ドレーン電極 1 7 5、及び維持蓄電器用導電体 1 7 7 もゲート線 1 2 1 と同様に、その側面が約 3 0 °から 8 0 °それぞれ傾斜している。

[ 0 0 3 9 ]

抵抗性接触部材161、163、165は、その下部の半導体151とその上部のデータ線171及びドレーン電極175の間にだけ存在し接触抵抗を低くする役割をする。線状半導体151は、ソース電極173とドレーン電極175との間をはじめとして、データ線171及びドレーン電極175によって覆われず露出された部分を有しており、ほとんどの部分では線状半導体151の幅がデータ線171の幅より小さいが、既に説明したように、ゲート線121とぶつかる部分で幅が広くなり、ゲート線121とデータ線171との間の絶縁を強化する。

[0040]

データ線171、ドレーン電極175、及び維持蓄電器用導電体177と、露出された

20

30

40

50

半導体151部分の上には、窒化ケイ素または酸化ケイ素からなる第1保護膜801が形成されている。

### [0041]

第1保護膜801の上部には、ストライプ形状を有し、ドレーン電極175及び維持蓄電器用導電体177上部に開口部を有する赤、緑、青の色フィルター230R、230G、230G、230Bが順に配列されている。色フィルター230R、230G、230Bのそれぞれの周縁はデータ線171の上部で互いに重なっているが、周縁部は後続膜のステップカバレッジ(step coverage)特性を良好なものに誘導したり、表示板の平坦化を図ることによって、液晶の整列の誤差を防止できるように他の部分より薄い厚さやテーパ構造であることができ、互いに重畳する幅がデータ線171を完全に覆うようにデータ線171の幅より広く形成されることもできる。

#### [0042]

ここで、隣接する色フィルターの二つの周縁部が重畳している部分には、2種類の色が互いに重畳するためにブラック状態となりこの部分から光が漏れることを適切に遮断することができており、光遮断膜としての機能をするといった長所がある。その結果、白黒対比比を向上させることができる。本発明の実施例による薄膜トランジスタ表示板では、ゲート線121及びデータ線171と色フィルター230R、230G、230Bの重畳部分が画素間から漏れる光を遮断してブラックマトリックスの機能を代替する。

#### [ 0 0 4 3 ]

色フィルター230R、230G、230Bが形成されている第1保護膜801の上部には、平坦化特性が優れて感光性を有する有機物質、プラズマ化学気相蒸着(PECVD)で形成されるa-Si:C:O、a-Si:O:Fなどの低誘電率絶縁物質などからなる第2保護膜802が形成されている。有機絶縁膜の透過率は、窒化シリコン膜よりも透過率が高く、例えば、有機絶縁膜の厚さが10倍以上になる場合においても薄い厚さの窒化シリコン膜と同一の程度の高い透過率を現す。

#### [0044]

第1保護膜及び第2保護膜180には、ドレーン電極175、維持蓄電器用導電体177、及びデータ線171の端部179を各々露出する複数の接触孔185、187、182が形成されており、ゲート絶縁膜140と共にゲート線121の端部129を露出する複数の接触孔181が形成されている。一方、色フィルター(R、G、B)もドレーン電極175及び維持蓄電器用導電体177を露出する開口部を有しているが、図示されているように、色フィルター230R、230G、230Bの開口部も保護膜180の接触孔185、187より大きいが、そうでないこともあり、そのときには階段状の側壁で形成される。

## [0045]

図示されているように、接触孔181、185、187、182は、ゲート線121の端部129、ドレーン電極175、維持蓄電器用導電体177、及びデータ線171の端部179の上部膜292、752、772、792を露出するが、上部膜292、752、772、791を露出することもできる。さらに、これに加えて接触孔181、185、187、182が下部膜291、751、771、791の周縁の境界線の一部を露出した状態にすることもできる。特に、後に形成されるITOまたはIZOの導電膜との接触特性を確保するためには、接触孔181、185、187、183からアルミニウム系列の導電膜を除去することが好ましい。

### [0046]

保護膜180上には、IZOまたはITOからなる複数の画素電極190及び複数の接触補助部材81、82が形成されている。

#### [0047]

画素電極 1 9 0 は接触孔 1 8 5 、 1 8 7 を通じてドレーン電極 1 7 5 及び維持蓄電器用導電体 1 7 7 と各々物理的・電気的に連結されてドレーン電極 1 7 5 からデータ電圧の印

加を受けて導電体177にデータ電圧を伝達する。

### [0048]

図2のように、データ電圧が印加された画素電極190は、共通電圧の印加を受けた対向表示板200の共通電極270と共に電場を生成することによって二つの表示板100 、200間の液晶層300の液晶分子を再配列する。

#### [0049]

また、前述したように、画素電極190及び共通電極270は、蓄電器(以下、"液晶蓄電器"という)を形成して薄膜トランジスタがターンオフされた後でも印加された電圧を維持するが、電圧維持能力を強化するために液晶蓄電器と並列に連結された他の蓄電器を設ける。これを維持蓄電器という。維持蓄電器は画素電極190及びこれと隣接するゲート線121(これを前段ゲート線という)の重畳などから作られ、維持蓄電器の静電容量、すなわち、保持容量を増やすためにゲート線121を拡張した拡張部127を設けて重畳面積を拡大する一方、画素電極190と連結され拡張部127と重なっている維持蓄電器用導電体177を保護膜180下に設けて二つ間の距離を短くする。

## [0050]

画素電極190はまた隣接するゲート線121及びデータ線171と重なって開口率を向上させているが、重ならないこともある。

### [0051]

接触補助部材81、82は、接触孔181、182を通じてゲート線の端部129及びデータ線の端部179と各々連結されている。接触補助部材81、82は、ゲート線121及びデータ線171の各端部129、179と外部装置との接着性を補完し、これらを保護する役割をするものであり、これらの適用は必須ではなく選択的である。

## [0052]

本発明の他の実施例によれば、画素電極190の材料として透明な導電性ポリマー(polymer)などを使用しており、反射型(reflective)液晶表示装置の場合には不透明な反射性金属を使用しても構わない。この時、接触補助部材81、82は画素電極190と異なる物質、特にIZOまたはITOで作られることもできる。

#### [0053]

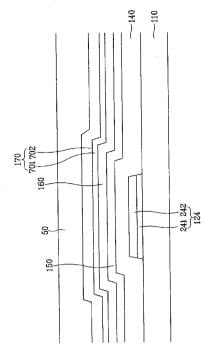

以下、図3及び図4に示した液晶表示装置用薄膜トランジスタ表示板を本発明の実施例によって製造する方法について、図5a乃至図8b及び図3、図4を参照して詳細に説明する。

## [0054]

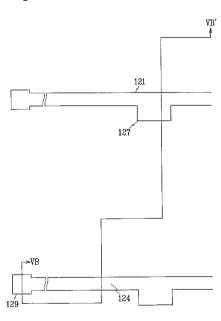

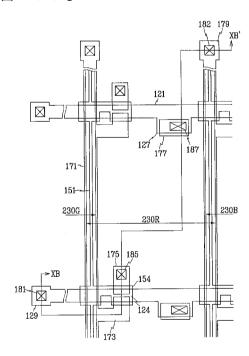

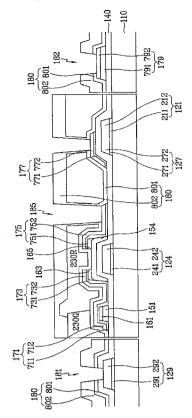

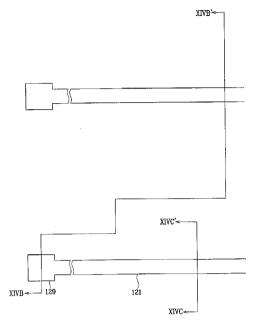

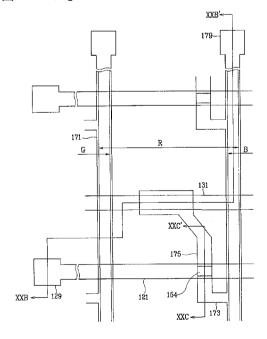

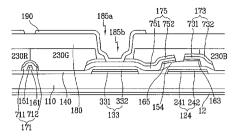

図5a、図6a、図7a、図9a、及び図10aは、図3及び図4に示した薄膜トランジスタ表示板を本発明の一実施例によって製造する方法の中間段階における薄膜トランジスタ表示板の配置図であり、その順序を示したものである。図5b、図6b、図7b、図9b、及び図10aは、各々図5a、図6a、図7a、図9a、及び図10aに示した薄膜トランジスタ表示板のVB-VB´線、VIB-VIB´線、VIIB-VIIB´線、IXB-IXB´線及びXB-XB´線による断面図である。図8は本発明の実施例による薄膜トランジスタ表示板の製造方法において、色フィルター形成時に基板の色フィルター用整列キーと色フィルター用マスクの整列キーの整列配置を示した配置図である。

## [ 0 0 5 5 ]

まず、透明なガラスなどで作られた絶縁基板110上に二つの層の金属膜、つまり、下部金属膜及び上部金属膜をスパッタリングなどの方法で順に積層する。下部金属膜はIzOまたはITOとの接触特性の優れた金属、例えば、モリブデン、モリブデン合金、またはクロムなどからなり、500 程度の厚さを有するのが好ましい。上部金属膜はアルミニウム系列金属からなり、2,500 程度の厚さを有するのが好ましい。

#### [0056]

次に、図 5 a及び図 5 bに示したように、感光膜パターンを利用した写真エッチング工程で上部金属膜及び下部金属膜を順にパターニングして、複数のゲート電極 1 2 4 と複数の拡張部 1 2 7 を含むゲート線 1 2 1 を形成する。

10

20

30

20

30

40

50

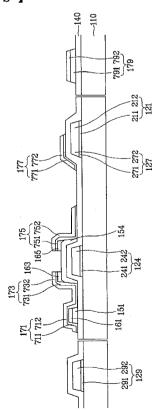

#### [0057]

写真エッチング工程において上部膜 2 1 2 、 2 7 2 、 2 4 2 及び下部膜 2 1 1 、 2 4 1 、 2 7 1 のパターニングは、互いに異なるエッチング条件で行われることもできる。例えば、これらがアルミニウム系列及びモリブデン系列の場合には、これらに対し全て側面傾斜を与えながらエッチングすることができるようなアルミニウムエッチング液として、CH  $_3$  COOH(8-15%)/HNO $_3$ (5-8%)/H $_3$  PO $_4$ (50-60%)/H $_2$  O(その他)を使用した湿式エッチングで進める。

## [ 0 0 5 8 ]

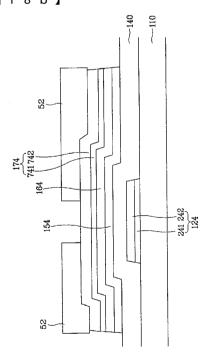

図 6 a及び図 6 bに示したように、ゲート絶縁膜 1 4 0、 真性非晶質シリコン層(intrinsic amorphous silicon)、不純物非晶質シリコン層(extrinsic amorphous silicon)の3 層膜を連続積層し、不純物非晶質シリコン層及び真性非晶質シリコン層を写真エッチングして、複数の線状不純物半導体 1 6 1、 1 6 4 と複数の突出部 1 5 4 を各々含む線状真性半導体 1 5 1、 1 5 4 を形成する。ゲート絶縁膜 1 4 0 の材料としては窒化ケイ素が好ましく、積層温度は 2 5 0 ~ 5 0 0 、厚さは 2 ,0 0 0 ~ 5 ,0 0 0 程度であるのが好ましい。

#### [0059]

次に、図7a及び図7bに示したように、二つの層の金属膜、つまり、下部金属膜及び上部金属膜をスパッタリングなどで順に積層する。下部金属膜は、IZOまたはITOとの接触特性が優れた金属、例えば、モリブデン、モリブデン合金、またはクロムなどからなり、500 程度の厚さを有するのが好ましい。 上部金属膜はアルミニウム系列金属からなっており、2,500 程度の厚さを有するのが好ましい。 感光膜パターンを利用した写真エッチング工程で上部金属膜及び下部金属膜を順にパターニングして、複数のソース電極173を有する複数のデータ線171、複数のドレーン電極175、及び複数の維持蓄電器用導電体177を形成する。この時、後に色フィルターを形成する時に使用するための色フィルター用整列キー178(図2参照)を共に形成する。

## [0060]

次に、データ線171及びドレーン電極175上部の感光膜を除去したりあるいはそのままにした状態で、データ線171、ドレーン電極175、及び維持蓄電器用導電体177によって覆われず露出された不純物半導体164部分を除去することによって、複数の突出部163を各々含む複数の線状抵抗性接触部材161及び複数の島状抵抗性接触部材165を完成する一方、その下の真性半導体151部分を露出させる。次に、真性半導体151部分の表面を安定化するために酸素プラズマを引続き実施するのが好ましい。

#### [0061]

次に、図9a及び図9bに示したように、絶縁基板110の上部に窒化ケイ素を積層して第1保護膜801を形成した後、その上部に陰性の赤色、緑色、青色の顔料のうち一つを含む色フィルター用感光膜を塗布する。この時、感光膜は光重合開始剤、単量体(monomer)、結着剤(binder)などを含む光重合型感光性組成物と、赤色、緑色、青色の顔料のうち一つを含む非水系分散液を塗布して形成する。

## [0062]

次に、図8のように、基板110の色フィルター用整列キー178及びマスクの整列キー55を利用してマスクを整列した後、マスクを利用して色フィルター用感光膜を露光後現像し、次いで、その他の二つの顔料を含む色フィルター用感光膜に対しても順に塗布し露光後現像して、図9a及び図9bのように、赤、緑、青の色フィルター230R、230G、230Bは、ドレーン電極175及び維持蓄電器用導電体177を露出する開口部を有しているが、そうでないときには後の工程でパターニングすることもできる。

#### [0063]

図 8 には整列キー 1 7 8 、 5 5 の一つの例のみを示しているが、このような整列キー 1 7 8 、 5 5 は、赤、緑、青の色フィルター 2 3 0 R、 2 3 0 G、 2 3 0 Bに対し各々配置することも、種々な形態を有することもできる。ここで、赤、緑、青の色フィルター 2 3 0

30

40

50

R、230G、230Bの周縁部はデータ線171の上部で互いに重なるように形成する。この時、本発明による実施例のように、赤、緑、青の色フィルター230R、230G、230Bのすぐ下の薄膜のデータ線171と同一層で色フィルター用整列キー178を形成する。そして、これを基準として色フィルター用マスクを整列して赤、緑、青の色フィルター230R、230G、230Bを形成することによって整列誤差を最少に抑えることができ、これによってデータ線171の幅を最少化することができる。

[0064]

次に、図10a及び図10bのように、第2保護膜802を積層し、写真エッチング工程で第1保護膜801及びゲート絶縁膜140と共に乾式エッチング工程でパターニングして複数の接触孔181、185、187、182を形成する。接触孔182、185、187、181は、ゲート線121の端部129、ドレーン電極175、維持蓄電器用導電体177及びデータ線171の端部179を露出する。この時、接触孔181、182、185、187を通じて露出された上部膜292、752、772、792を除去する工程を追加することもできる。

[0065]

次に、図3及び図4に示したように、IZOまたはITO膜をスパッタリングで積層し写真エッチングして複数の画素電極190及び複数の接触補助部材81、82を形成する。この時、IZOまたはITOのスパッタリング温度は250 以下であることが接触抵抗を最少化するために好ましい。

[0066]

この後、絶縁基板110の上部に黒色顔料を含む有機物質を積層しパターニングして、薄膜トランジスタの上部に基板間隔材(spacer)を形成する工程を追加することができ、薄膜トランジスタ表示板を完成した後に色フィルター用整列キー178は除去することができる。

[0067]

一方、このような色フィルター用整列キー178は、薄膜トランジスタ表示板とこれと対向する対向表示板を整列するときに使用することができる。つまり、液晶表示装置を完成するためには、薄膜トランジスタ表示板と対向表示板を整列して結合した後これらの間に液晶層を形成するが、薄膜トランジスタ表示板と対向表示板を整列するためには、それぞれの表示板に形成されている整列キーを利用しなければならない。この時、色フィルター用整列キー178と対向表示板に形成されている整列キーとを整列して二つの表示板を整列することができる。

[0068]

また、前記では、半導体層とデータ線を互いに異なるマスクを用いた写真エッチング工程で形成する製造方法に本発明の実施例を適用して説明したが、本発明による他の製造方法は、製造コストを最少化するために、半導体層とデータ線を一つの感光膜パターンを利用した写真エッチング工程で形成する液晶表示装置用薄膜トランジスタ表示板の製造方法にも同様に適用することができる。これについて図面を参照して詳細に説明する。

[ 0 0 6 9 ]

まず、図11乃至図13を参照して、本発明の他の実施例による液晶表示装置用薄膜トランジスタ表示板の単位画素構造について詳細に説明する。

[0070]

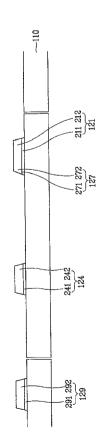

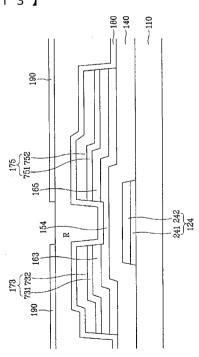

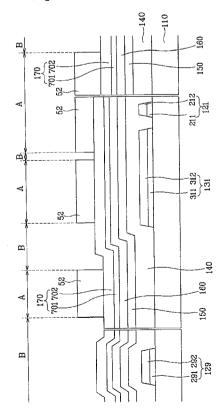

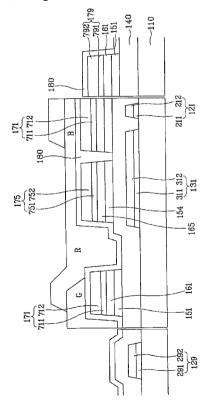

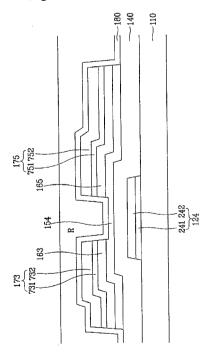

図11は本発明の他の実施例による液晶表示装置用薄膜トランジスタ表示板の配置図である。図12及び図13は各々図11に示した薄膜トランジスタ表示板のXII-XII ´線及びXIII-XIII ´線による断面図である。

[0071]

図11乃至図13のように、本実施例による液晶表示装置用薄膜トランジスタ表示板の層状構造は、図3及び図4に示した液晶表示装置用薄膜トランジスタ表示板の層状構造とほとんど同じである。つまり、基板110上に、複数のゲート電極124を含む複数のゲート線121が形成されており、その上にゲート絶縁膜140、複数の突出部154を含

む複数の線状半導体151、複数の突出部163を各々含む複数の線状抵抗性接触部材161、及び複数の島状抵抗性接触部材165が順に形成されている。抵抗性接触部材161、165及びゲート絶縁膜140の上には、複数のソース電極173を含む複数のデータ線171、複数のドレーン電極175、複数の維持蓄電器用導電体177が形成されており、その上に保護膜180が形成されている。保護膜180及び/またはゲート絶縁膜140には複数の接触孔182、185、187、181が形成されており、保護膜180上には複数の画素電極190及び複数の接触補助部材81、82が形成されている。

## [0072]

しかし、図3及び図4に示した薄膜トランジスタ表示板とは異なり、本実施例による薄膜トランジスタ表示板は、ゲート線121に拡張部を設ける代わりにゲート線121と同一の層にゲート線121と電気的に分離された複数の維持電極線131を設けてドレーン電極175と重畳させて維持蓄電器を形成する。維持電極線131は共通電圧などの予め決められた電圧の印加を外部から受け、画素電極190とゲート線121との重畳で発生する保持容量が十分な場合には、維持電極線131は省略することも、画素の開口率を極大化するために画素領域の周縁に配置することもできる。

#### [0073]

半導体 1 5 1 は、薄膜トランジスタが位置する突出部 1 5 4 を除けば、データ線 1 7 1 、ドレーン電極 1 7 5 、及びその下部の抵抗性接触部材 1 6 1 、 1 6 5 と実質的に同一の平面形状を有している。具体的には、線状半導体 1 5 1 はデータ線 1 7 1 及びドレーン電極 1 7 5 とその下部の抵抗性接触部材 1 6 1 、 1 6 5 の下に存在する部分のほかにも、ソース電極 1 7 3 とドレーン電極 1 7 5 との間にこれらによって覆われず露出された部分を有している。

## [0074]

また、データ線171及びドレーン電極175は、クロム(Cr)、モリブデン(Mo)、モリブデン合金(例:モリブデン-タングステン(MoW)合金)からなる下部膜711、751、アルミニウムまたはアルミニウム合金(例:アルミニウム-ネオジム(Nd))からなる上部膜712、752を含む。図12及び図13で、ソース電極173及びデータ線の端部179の下部膜と上部膜は、各々図面符号731、732、791、792で表示されている。

### [0075]

以下、図11乃至図13の構造を有する液晶表示装置用薄膜トランジスタ表示板を本発明の一実施例に基づいて製造する方法について、図14a乃至図20c、及び図11乃至図13を参照して詳細に説明する。

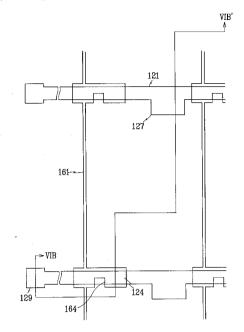

## [0076]

図14aは図11乃至図13に示す薄膜トランジスタ表示板を本発明の一実施例に基づいて製造する方法の第1段階における薄膜トランジスタ表示板の配置図である。図14b及び14cは各々図14aの薄膜トランジスタ表示板のXIVB・XIVB 、線及びXIVC・XIVC 、線による断面図である。図15a及び15bは各々図14aの薄膜トランジスタ表示板のXIVB・XIVB が線及びXIVC・XIVC 、線による断面図であり、図14b及び図14cに続く工程を示す。図16aは図15a及び15bに続く工程における薄膜トランジスタ表示板の配置図である。図16b及び16cは各々図16aに示す薄膜トランジスタ表示板のXVIB・XVIB 、線及びXVIC・XVIC 、線による断面図である。図17a、18a、19a及び図17b、18b、19bは各々図16aに示す薄膜トランジスタ表示板の配置図である。図20aは図19a及び図19bに続く工程における薄膜トランジスタ表示板の配置図である。図20aは図19a及び図19bに続く工程における薄膜トランジスタ表示板の配置図である。図20aは図19a及び図19bに続く工程における薄膜トランジスタ表示板の配置図である。図21aは図20a乃至図20cに続く工程における薄膜トランジスタ表示板の配置図である。図21b及び図21cは各々図21aに示す薄膜トランジスタ表示板の配置図である。図21b及び図21cは各々図21aに示す薄膜トランジスタ表示板の配置図である。

## [ 0 0 7 7 ]

40

20

20

30

40

50

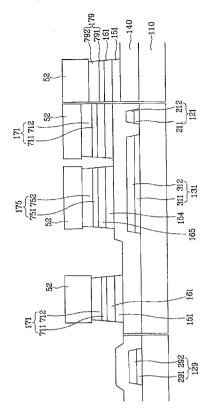

まず、図14a乃至図14cに示したように、絶縁基板110上に写真エッチング工程で複数のゲート電極124を各々含む複数のゲート線121及び複数の維持電極線131を形成する。ゲート線121及び維持電極線131は、第1実施例のように、各々下部膜211、241、291、311と上部膜212、242、292、312を有しているが、単一膜で形成することもできる。

#### [0078]

図15a及び図15bに示したように、ゲート絶縁膜140、真性非晶質シリコン層150、不純物非晶質シリコン層160を化学気相蒸着法を利用して各々約1,500 乃至約5,000 、約500 乃至約2,000 、約300 乃至約600 の厚さで連続蒸着する。次に、下部膜701及び上部膜702をスパッタリングなどの方法で連続積層して導電体層170を形成した後、その上に感光膜50を1μm乃至2μmの厚さで塗布する。

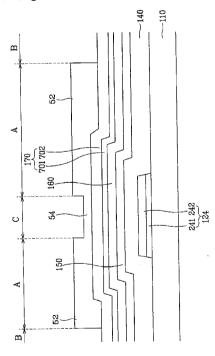

## [0079]

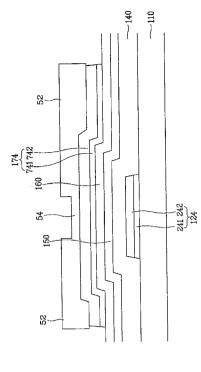

その後、光マスク(図示せず)を通じて感光膜 5 0 に光を照射した後現像する。現象された感光膜の厚さは位置によって異なるが、図 1 6 b及び図 1 6 cのように、感光膜は厚さが次第に薄くなる第 1 部分乃至第 3 部分からなっている。領域(A)(以下、配線領域という)に位置した第 1 部分及び領域(C)(以下、チャンネル領域という)に位置した第 2 部分は、各々図面符号 5 2、5 4 を付し、領域(B)(以下、その他の領域という)に位置した第 3 部分に対する図面符号は付していないが、これは第 3 部分が 0 の厚さであり下の導電体層 1 7 0 が露出されているためである。第 1 部分 5 2 と第 2 部分 5 4 の厚さとの比は後続工程における工程条件によって異ならせるが、第 2 部分 5 4 の厚さを第 1 部分 5 2 の厚さの 1 / 2 以下とするのが好ましい。例えば、 4 , 0 0 0 以下であるのが良い

## [0800]

このように、位置によって感光膜の厚さを異ならせるには種々な方法があり、露光マスクに透明領域(transparent area)と遮光領域(light blocking area)のみだけでなく、半透明領域(translucent area)を設けるのがその例である。半透明領域にはスリット(slit)パターン、格子パターン(lattice pattern)、または透過率が中間であるかあるいは厚さが中間である薄膜が備えられる。スリットパターンを使用する時には、スリットの幅やスリット間の間隔が写真工程に使用される露光器の分解能(resolution)より小さいのが好ましい。他の例としては、リフローの可能な感光膜を用いる方法である。つまり、透明領域と遮光領域だけをもつ通常のマスクにてリフロー可能な感光膜パターンを形成した後リフローさせて、感光膜が残留しない領域に流すことによって薄い部分を形成する。

# [0081]

適切な工程条件を与えれば、感光膜 5 2 、 5 4 厚さの差のために、下部層を選択的にエッチングすることができる。したがって、一連のエッチング段階を経て図 1 6 aに示したような複数のソース電極 1 7 3 を各々含む複数のデータ線 1 7 1 、複数のドレーン電極 1 7 5 を形成し、複数の突出部 1 6 3 を各々含む複数の線状抵抗性接触部材 1 6 1 及び複数の島状型抵抗性接触部材 1 6 5 、そして複数の突出部 1 5 4 を含む複数の線状半導体 1 5 1 を形成する。

#### [0082]

説明の便宜上、配線領域(A)に位置した導電体層170、不純物非晶質シリコン層160、真性非晶質シリコン層150の部分を第1部分とし、チャンネル領域(C)に位置した導電体層170、不純物非晶質シリコン層160、真性非晶質シリコン層150の部分を第2部分とし、その他の領域(B)に位置した導電体層170、不純物非晶質シリコン層160、真性非晶質シリコン層150の部分を第3部分とする。

#### [0083]

以下にはこのような構造を形成する順序の第1の例の一例を示している。(1)、(2)、(3)、(4)の順序で行われる。

20

30

40

50

- (1) その他の領域(B) に位置した導電体層 1 7 0、不純物非晶質シリコン層 1 6 0、及び非晶質シリコン層 1 5 0 の第 3 部分を除去

- (2) チャンネル領域に位置した感光膜の第2部分54を除去

- ( 3 ) チャンネル領域 ( C ) に位置した導電体層 1 7 0 及び不純物非晶質シリコン層 1 6 0 の第 2 部分を除去、そして

- (4)配線領域(A)に位置した感光膜の第1部分52を除去

別の第2の例の順序例は次の通りであり、(1)、(2)、(3)、(4)、(5)、

- (6)の順序で行われる。

- (1) その他の領域(B) に位置した導電体層170の第3部分を除去

- ( 2 ) チャンネル領域(C)に位置した感光膜の第2部分54を除去

- (3) その他の領域(B) に位置した不純物非晶質シリコン層 1 6 0 及び非晶質シリコン層 1 5 0 の第 3 部分を除去、

- ( 4 ) チャンネル領域 ( C ) に位置した導電体層 1 7 0 の第 2 部分を除去

- ( 5 ) 配 線 領 域 ( A ) に 位 置 し た 感 光 膜 の 第 1 部 分 5 2 を 除 去 、 そ し て

- (6) チャンネル領域(C) に位置した不純物非晶質シリコン層 1 6 0 の第 2 部分を除去 ここでは第 1 の例について説明する。

- [0084]

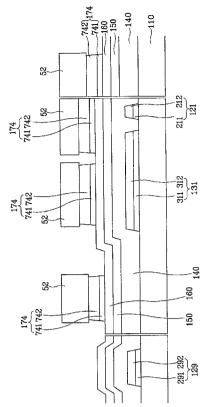

まず、図17a及び図17bに示したように、その他の領域(B)に露出されている導電体層170の上部膜702及び下部膜701を湿式または乾式エッチングで除去して下部の不純物非晶質シリコン層160の第3部分を露出させる。アルミニウム系列の導電膜は主に湿式エッチングで進め、モリブデン系列の導電膜は湿式及び乾式エッチングを選択的に進めることができる。なお、上部膜702及び下部膜701の3層膜を一つの湿式エッチング条件でパターニングすることもできる。

[0085]

図面符号 1 7 4 はデータ線 1 7 1 とドレーン電極 1 7 5 がまだ連結されている状態の導電体である。乾式エッチングを使用する場合には感光膜 5 2 、 5 4 の上部がある程度の厚さが削られる事もある。

[0086]

この時、第1実施例と同様に、色フィルター用整列キー178(図2及び図8参照)を基板110の外郭部に形成する。

[0087]

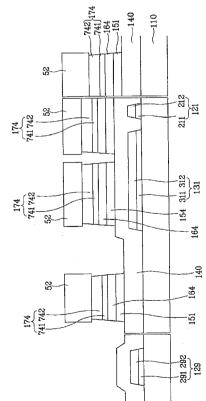

図18a及び図18bに示したように、その他の領域(B)に位置した不純物非晶質シリコン層160及びその下部の真性非晶質シリコン層150の第3部分を除去するとともに、チャンネル領域(C)の感光膜の第2部分54を除去して、下部の導電体174第2部分を露出させる。感光膜の第2部分54の除去は、不純物非晶質シリコン層160及び真性非晶質シリコン層150の第3部分の除去と同時に行うかあるいは別々に行う。チャンネル領域(C)に残っている第2部分54の残留物はアッシング(ashing)で除去する。

[0088]

この段階で線状真性半導体151が完成する。そして図面符号164は、線状抵抗性接触部材161と島状抵抗性接触部材165がまだ連結されている状態の線状の不純物非晶質シリコン層160を指すもので、以下には(線状の)不純物半導体という。

[0089]

ここで、導電体層 1 7 0 の下部膜 7 0 1 を乾式エッチングでパターニングする場合に、その下部の不純物非晶質シリコン層 1 6 0 と真性非晶質シリコン層 1 5 0 を連続して乾式エッチングすることによって製造工程を単純化することができる。この場合には、同一のエッチングチャンバーで三つの層 7 0 1、160、150に対する乾式エッチングを連続実行するインシチュー (in-situ)方法で行うことができるが、そうでないこともある。

[0090]

次に、図 1 9 a及び図 1 9 bに示したように、チャンネル領域(C)に位置した導電体 1 7 4 及び線状の不純物半導体 1 6 4 の第 2 部分をエッチングして除去する。なお、残って

20

30

40

50

いる感光膜の第1部分52も除去する。この時、図19bに示したように、チャンネル領域(C)に位置した線状真性半導体151の突出部154の上部が除去され厚さが薄くなることもあり、感光膜の第1部分52もこの時ある程度の厚さがエッチングされる。

[0091]

このようにして、導電体 1 7 4 各々が一つのデータ線 1 7 1 と複数のドレーン電極 1 7 5 に分離されながら完成し、不純物半導体 1 6 4 各々が一つの線状抵抗性接触部材 1 6 1 と複数の島状抵抗性接触部材 1 6 5 に分離されて完成する。

[0092]

次に、図8のように、第1実施例と同様に、色フィルター用感光膜を形成し、基板110の色フィルター用整列キー178及びマスクの整列キー55を利用してマスクを整列した後、マスクを用いて色フィルター用感光膜を露光し現像し、引続き、他の二つの顔料を含む色フィルター用感光膜に対しても順に塗布して露光、現像して、図20a及び図20bのように、赤、緑、青の色フィルター230R、230G、230Bを順に形成する。

[0093]

図 2 1 a乃至図 2 1 cに示したように、保護膜 1 8 0 をゲート絶縁膜 1 4 0 及び赤、緑、青の色フィルター 2 3 0 R、 2 3 0 G、 2 3 0 Bとともに写真エッチングして複数の接触孔 1 8 1、 1 8 5、 1 8 2 を形成する。もちろん、本実施例でも第 1 実施例と同様に、赤、緑、青の色フィルター 2 3 0 R、 2 3 0 G、 2 3 0 Bの上部に保護膜を形成した後で接触孔 1 8 1、 1 8 5、 1 8 2 を形成することもできる。

[0094]

最後に、図11乃至図13に示したように、500 乃至1,500 厚さのIZOまたはITO層をスパッタリング方法で蒸着し写真エッチングして複数の画素電極190及び複数の接触補助部材81、82を形成する。IZO層を使用する場合のエッチングは、(HNO3/(NH4)2Ce(NO3)6/H20)などのクロム用エッチング液を使用する湿式エッチングであるのが好ましいが、このエッチング液はアルミニウムを腐蝕させないため、データ線171、ドレーン電極175、ゲート線121におけるアルミニウム導電膜の腐食を防止することができる。

[0095]

本実施例では、データ線171及びドレーン電極175とその下部の抵抗性接触部材161、165及び半導体151を一つの写真工程で形成しており製造工程を単純化することができる。

[0096]

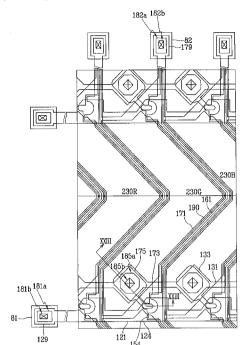

図22は本発明の他の実施例による液晶表示装置用薄膜トランジスタ表示板の配置図である。図23は図22の薄膜トランジスタ表示板のXXIII-XXIII´線による断面図である

[0097]

絶縁基板110上に横方向にゲート線121が形成されており、ゲート線121に突起状でゲート電極124が連結されている。ゲート線121の一端部129は外部回路との連結のために幅が拡張されている。

[0098]

また、絶縁基板110上には、維持電極線131と維持電極133が形成されている。維持電極線131は横方向にのびており、維持電極133は菱形もしくは長方形を維持電極線131に連結されている。

[0099]

ゲート線 1 2 1 、 1 2 4 、 1 2 9 及び維持電極配線 1 3 1 、 1 3 3 は、物理、化学的な特性の優れたCrまたはMo合金などからなる第 1 層 2 1 1 、 2 4 1 、 2 9 1 、 3 1 1 、 3 3 1 と、低抵抗のAIまたはAg合金などからなる第 2 層 2 1 2 、 2 4 2 、 2 9 2 、 3 1 2 、 3 3 2 の二重層で形成されている。これらのゲート配線 1 2 1 、 1 2 9 、 1 2 4 及び維持電極配線 1 3 1 、 1 3 3 は、必要によっては単一層あるいは 3 重層以上で形成することもできる。

20

30

40

50

ゲート配線 1 2 1 、 1 2 4 、 1 2 9 及び維持電極配線 1 3 1 、 1 3 3 の上にはゲート絶縁膜 1 4 0 が形成されている。

[0101]

[0100]

ゲート絶縁膜 1 4 0 上には、非晶質シリコンなどの半導体からなる半導体層 1 5 1 、 1 5 4 が形成されている。

[0102]

半導体層151、154の上には、シリサイドまたはn型不純物が高濃度にドーピングされているn+水素化非晶質シリコンなどの物質からなる抵抗性接触層161、163、165が形成されている。

[0103]

抵抗性接触層161、163、165及びゲート絶縁膜140上にはデータ線171及びドレーン電極175が形成されている。データ線171は長くのびておりゲート線121と交差して画素を定義し、データ線171の分枝であり抵抗性接触層163の上部まで延在しているソース電極173を有する。データ線171の一端部179は外部回路との連結のために幅が拡張されている。

[0104]

ここで、データ線171は画素の長さを周期として繰返し屈折された部分と縦に延在した部分が現れるように形成されている。この時、データ線171の屈折した部分は二つの直線部からなっており、二つの直線部分のうち一つはゲート線121に対して45度をなし、もう一つはゲート線121に対して・45度をなしている。データ線171の縦に延在した部分には、ソース電極173が連結されており、この部分がゲート線121及び維持電極線131と交差する。

[0105]

この時、データ線171の屈折した部分と縦に延在した部分との長さの比は1:1乃至9:1の間、つまり、データ線171のうち屈折した部分が占める比率が50%から90%の間である。以上のように、ゲート線121とデータ線171の交差でなされる画素は折り曲がった帯状で形成される。このように、データ線を屈折させて画素を折れた帯状で形成すれば、隣接した画素間の側方向電界がドメインの形成を助ける方向に作用してドメインが安定して形成され、共通電圧が印加される維持電極線を画素電極の切開部に重なるように配置してフリンジフィールドを強化することにより、画素の開口率を極大化することができる。

[0106]

また、ドレーン電極175は画素電極190と連結される部分が長方形に広く拡張されて維持電極133と重畳している。このように、ドレーン電極175は、維持電極133とゲート絶縁膜140のみを介在して重畳されることで保持容量を形成する。

[0107]

データ配線171及びドレーン電極175上には、赤、緑、青の色フィルター230R、230G、230Bが順に形成されており、その上部には有機絶縁膜からなる保護膜180が形成されている。ここで保護膜180は、感光性有機物質を露光及び現像して形成する。必要によっては保護膜180を感光性のない有機物質を塗布して写真エッチング工程で形成することもできるが、感光性有機物質で保護膜180を形成することに比べて形成工程が複雑になる。

[0108]

保護膜180には、ドレーン電極を露出する接触孔185bとデータ線の幅が拡張されている端部179を露出する接触孔182bとが形成されている。また、ゲート線の幅が拡張されている端部129を露出する接触孔181bは保護膜180と共にゲート絶縁膜140を貫通して形成されている。

[0109]

この時、これら接触孔 1 8 1 b、 1 8 2 b、 1 8 5 bの側壁 1 8 1 a、 1 8 2 a、 1 8 5 aは

、基板面に対し30度から85度間の緩慢な傾斜を有したりあるいは階段状のプロファイルを有する。

[0110]

また、これら接触孔 1 8 1 b、 1 8 2 b、 1 8 5 bは角のある模様であったり、円形模様など種々な形態で形成されることができ、形状寸法は 2 mm  $\times$  6 0  $\mu$  mを超えず、 0 . 5 mm  $\times$  1 5  $\mu$  m以上であるのが好ましい。

[0111]

一方、保護膜180は窒化ケイ素または酸化ケイ素などの無機絶縁物質で形成すること もできる。

[0112]

保護膜180上には接触孔185bを通じてドレーン電極175と連結されており、画素形状に沿って折り曲がった帯状に画素電極190が形成されている。この時、画素電極190は周縁がデータ線と重畳するくらいに広く形成されており最大限の開口率を確保している。

[0113]

また、保護膜180上には、接触孔181b、182bを通じてゲート線の端部129とデータ線の端部179と各々連結されている接触補助部材81、82が形成されている。ここで、画素電極190及び接触補助部材81、82はITOまたはIZOからなっている。

[0114]

このような実施例による薄膜トランジスタ表示板の製造方法は第1実施例と同一であり、データ線171と同一の層で色フィルター用整列キー178(図8参照)を形成した後、これを基準として赤、緑、青の色フィルター230R、230G、230Bを形成して整列誤差を最少化することができ、データ線171の幅を最適に形成することができる。

[ 0 1 1 5 ]

以上のように本発明の好ましい実施例について詳細に説明しましたが、本発明の権利範囲はこれに限定されるものではなく、請求の範囲で定義している本発明の基本概念を利用した当業者の様々な変形及び改良形態もまた本発明の権利範囲に属するものである。

【図面の簡単な説明】

[0116]

【図1】本発明の実施例による液晶表示装置用薄膜トランジスタ表示板を製造するための基板における領域を区分して示した平面図である。

【図2】図1の一つのパネル領域に形成された液晶表示装置用薄膜トランジスタ表示板の配置の概略的な配置図である。

【 図 3 】 本 発 明 の 一 実 施 例 に よ る 液 晶 表 示 装 置 用 薄 膜 ト ラ ン ジ ス タ 表 示 板 の 構 造 を 示 し た 配 置 図 で あ る 。

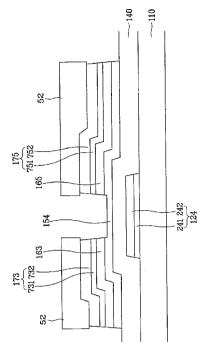

【 図 4 】 図 3 の 薄 膜 ト ラ ン ジ ス タ 表 示 板 の I V - I V ´ 線 に よ る 断 面 図 で あ る 。

【図 5 a 】図 3 及び図 4 に示す薄膜トランジスタ表示板を本発明の実施例によって製造する中間過程における薄膜トランジスタ表示板の配置図である。

【 図 5 b 】図 5 aの薄膜トランジスタ表示板のV B - V B ´ 線による断面図である。

【図 6 a 】図 3 及び図 4 に示す薄膜トランジスタ表示板を本発明の実施例によって製造する中間過程における薄膜トランジスタ表示板の配置図である。

【図 6 b 】図 6 aの薄膜トランジスタ表示板の VIB - VIB ´線による断面図であり、図 5 bに続く工程を示す。

【図 7 a 】図 3 及び図 4 に示す薄膜トランジスタ表示板を本発明の実施例によって製造する中間過程における薄膜トランジスタ表示板の配置図である。

【図7b】図7aのVIIB-VIIB ´線による断面図であり、図6bに続く工程を示す。

【図8】本発明の実施例による薄膜トランジスタ表示板の製造方法において色フィルター 形成時の基板の色フィルター用整列キー及び色フィルター用マスクの整列キーの整列配置 を示した配置図である。 10

20

30

40

- 【 図 9 a 】 図 3 及び図 4 に示す薄膜トランジスタ表示板を本発明の実施例によって製造する中間過程における薄膜トランジスタ表示板の配置図である。

- 【図9 b 】図 9 aの I X B I X B ´線による断面図であり、図 7 bに続く工程を示す。

- 【 図 1 0 a 】図 3 及び図 4 に示す薄膜トランジスタ表示板を本発明の実施例によって製造する中間過程における薄膜トランジスタ表示板の配置図である。

- 【図 1 0 b 】図 1 0 aの X B X B ´線による断面図であり、図 9 bに続く工程を示す。

- 【図 1 1 】本発明の他の実施例による液晶表示装置用薄膜トランジスタ表示板の配置図である。

- 【図12】図11の薄膜トランジスタ表示板のXII-XII ´線による断面図である。

- 【 図 1 3 】 図 1 1 の 薄 膜 ト ラ ン ジ ス タ 表 示 板 の X I I I X I I I ´ 線 に よ る 断 面 図 で あ る 。

- 【図14a】図11乃至図13の薄膜トランジスタ表示板を本発明の実施例によって製造する薄膜トランジスタ表示板の配置図である。

- 【図 1 4 b 】図 1 4 aの XIV B XIV B ´線による断面図である。

- 【図 1 4 c 】図 1 4 aの X I V C X I V C ´線による断面図である。

- 【 図 1 5 a 】 図 1 4 aの X I V B X I V B ´線による断面図であり、図 1 4 b及び図 1 4 cに続く 工程を示す。

- 【図15b】図14aのXIVC-XIVC ´線による断面図であり、図14b及び図14cに続く 工程を示す。

- 【 図 1 6 a 】 図 1 5 a 及 び 図 1 5 b に 続 く 工 程 に お け る 薄 膜 ト ラ ン ジ ス タ 表 示 板 の 配 置 図 で あ る 。

- 【図 1 6 b 】図 1 6 aの XVIB XVIB ´線による断面図である。

- 【図 1 6 c 】図 1 6 aの XVI C XVI C ´線による断面図である。

- 【図17a】図16aのXVIB-XVIB ´線による断面図であり、図16bに続く工程を工程順で示したものである。

- 【 図 1 7 b 】図 1 6 aの XVI C XVI C ´線による断面図であり、図 1 6 cに続く工程を工程順で示したものである。

- 【図18a】図16aのXVIB-XVIB ´線による断面図であり、図16bに続く工程を工程順で示したものである。

- 【 図 1 8 b 】 図 1 6 aの X V I C X V I C . 線による断面図であり、 図 1 6 c に続く工程を工程順で示したものである。

- 【図19a】図16aのXVIB-XVIB ´ 線による断面図であり、図16bに続く工程を工程順で示したものである。

- 【図19b】図16aのXVI C XVI C ´線による断面図であり、図16cに続く工程を工程順で示したものである。

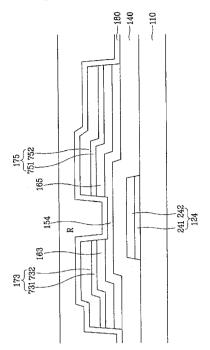

- 【図 2 0 a 】図 1 9 a及び図 1 9 bに続く工程における薄膜トランジスタ表示板の配置図である。

- 【 図 2 0 b 】 各 々 図 2 0 a の X X B X X B ´ 線 に よ る 断 面 図 で あ る 。

- 【図20c】各々図20aのXXC-XXC ´線による断面図である。

- 【 図 2 1 a 】 図 2 0 a 乃 至 図 2 0 c に 続 く 工 程 に お け る 薄 膜 ト ラ ン ジ ス タ 表 示 板 の 配 置 図 で あ る 。

- 【図21b】図21aの薄膜トランジスタ表示板のXXIB-XXIB ´線による断面図である。

- 【 図 2 1 c 】図 2 1 aの薄膜トランジスタ表示板のXXIC XXIC ´線による断面図である。

- 【図22】本発明の他の実施例による液晶表示装置用薄膜トランジスタ表示板の配置図である。

- 【 図 2 3 】 図 2 2 の 薄 膜 ト ラ ン ジ ス タ 表 示 板 の XX I I I XX I I I ´ 線 に よ る 断 面 図 で あ る 。

【符号の説明】

- [0117]

- 5 2 、 5 4 感光膜

- 100、200 表示板

- 1 1 0 絶縁基板

10

20

30

30

- 121 ゲート線

- 1 2 4 ゲート電極

- 1 4 0 ゲート絶縁膜

- 171 データ線

- 173 ソース電極

- 1 7 5 ドレーン電極

- 178 整列キー

- 1 6 1 、 1 6 5 抵抗性接触部材

- 190 画素電極

- 2 7 0 共通電極

- 3 0 0 液晶層

- 8 0 1 第 1 保 護 膜

- 8 0 2 第 2 保 護 膜

- 230R、230G、230B 色フィルター

【図1】

【図2】

【図3】

【図4】

【図5a】

【図5b】

【図 6 a】

【図 6 b】

【図7a】

【図7b】

【図8】

【図 9 a】

【図9b】

【図10a】

【図10b】

【図11】

【図12】

【図13】

【図14a】

【図14b】

【図14c】

【図15a】

【図15b】

【図16a】

【図16b】

【図16c】

【図17a】

【図17b】

【図18a】

【図18b】

【図19a】

【図19b】

【図20a】

【図20b】

【図20c】

【図21a】

【図21b】

【図21c】

【図22】

【図23】

## フロントページの続き

F ターム(参考) 5F110 AA30 BB01 CC07 DD02 EE03 EE04 EE06 EE14 EE23 EE44 FF03 FF29 GG02 GG15 GG22 GG25 GG35 GG44 GG58 HK03 HK04 HK05 HK06 HK09 HK16 HK22 HK33 HK34 HL01 HL02 HL07 HM03 HM19 NN03 NN22 NN23 NN24 NN27 NN35 NN72 NN73 QQ01 QQ04 QQ09