(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-33200

(P2014-33200A)

(43) 公開日 平成26年2月20日(2014.2.20)

| (51) Int.Cl.                 | F 1        | テーマコード (参考) |

|------------------------------|------------|-------------|

| <b>H01L 29/78</b> (2006.01)  | H01L 29/78 | 652M 4M1O4  |

| <b>H01L 29/12</b> (2006.01)  | H01L 29/78 | 652T        |

| <b>H01L 21/336</b> (2006.01) | H01L 29/78 | 658L        |

| <b>H01L 29/739</b> (2006.01) | H01L 29/78 | 655Z        |

| <b>H01L 21/28</b> (2006.01)  | H01L 21/28 | 301B        |

審査請求 未請求 請求項の数 20 O L 外国語出願 (全 17 頁) 最終頁に続く

|              |                              |          |                                                                          |

|--------------|------------------------------|----------|--------------------------------------------------------------------------|

| (21) 出願番号    | 特願2013-158388 (P2013-158388) | (71) 出願人 | 390041542<br>ゼネラル・エレクトリック・カンパニイ<br>アメリカ合衆国、ニューヨーク州、スケネ<br>クタディ、リバーロード、1番 |

| (22) 出願日     | 平成25年7月31日 (2013.7.31)       | (74) 代理人 | 100137545<br>弁理士 荒川 智志                                                   |

| (31) 優先権主張番号 | 13/567,791                   | (74) 代理人 | 100105588<br>弁理士 小倉 博                                                    |

| (32) 優先日     | 平成24年8月6日 (2012.8.6)         | (74) 代理人 | 100129779<br>弁理士 黒川 俊久                                                   |

| (33) 優先権主張国  | 米国(US)                       | (74) 代理人 | 100113974<br>弁理士 田中 拓人                                                   |

最終頁に続く

(54) 【発明の名称】バイアス温度不安定性 (BTI) を低減したデバイス

(57) 【要約】 (修正有)

【課題】バイアス温度不安定性 (BTI) を低減したデバイスを提供する。

【解決手段】絶縁層上に配置されたゲート電極と、しきい値電圧のシフトを防止する金属から構成されるソース電極と、ゲート電極とソース電極との間に配置された層間誘電体 (ILD) と、ソース電極およびウェル領域の両方と接触し、n型またはp型のいずれかであるソースコンタクト領域と、n型またはp型のいずれかである炭化ケイ素基板と、n型またはp型のいずれかであるウェル領域と、ゲート電極とは炭化ケイ素基板の反対側に配置されたドレイン電極とを備える。

【選択図】図1

FIG. 1

## 【特許請求の範囲】

## 【請求項 1】

半導体デバイスを製造するための方法であって、

半導体製造に適した炭化ケイ素ウェハを用意するステップと、

各炭化ケイ素ウェハ上に1つまたは複数の半導体デバイスを製造するステップと、

動作中の前記半導体デバイスのしきい値電圧のシフトを制限する金属を堆積することによって各半導体デバイスのソース電極を形成するステップと

を備えた方法。

## 【請求項 2】

前記金属が、水素に対する拡散バリアである、請求項1記載の方法。 10

## 【請求項 3】

前記金属が、シリカ中に水分子から分解した原子状の水素を作らない、請求項1記載の方法。

## 【請求項 4】

前記半導体デバイスが、金属-酸化膜-半導体電界効果型トランジスタ(MOSFET)を含む、請求項1記載の方法。

## 【請求項 5】

前記半導体デバイスが、絶縁ゲートバイポーラトランジスタ(IGBT)、MOS制御サイリスタ、またはゲート制御サイリスタを含む、請求項1記載の方法。 20

## 【請求項 6】

前記半導体デバイスの前記しきい値電圧の前記シフトが、前記半導体デバイスを高温で、高いバイアスで、または両方で動作させたときに、前記半導体デバイスにおけるバイアス温度不安定性(BTI)からもたらされる、請求項1記載の方法。

## 【請求項 7】

動作中の前記半導体デバイスの前記しきい値電圧の前記シフトが、1V未満である、請求項1記載の方法。

## 【請求項 8】

前記ソース電極が、金属層の組み合わせから構成される、請求項1記載の方法。

## 【請求項 9】

ゲート電極と、 30

炭化ケイ素からなり、前記ゲート電極を支持しつつ表面法線方向を規定する表面を有する基板であって、

第1の導電型を有するように第1のドーパント型を含むドリフト領域と、

前記ドリフト領域に隣接し、前記表面に対して近位にあるウェル領域であり、第2の導電型を有するように第2のドーパント型および前記ゲート電極に対して近位に配置されたチャネル領域を含むウェル領域と、

前記ウェル領域に隣接し、前記第1の導電型を有するソースコンタクト領域とを含む基板と、

前記ゲート電極の周りに、前記基板の前記表面の一部の上に配置された層間誘電体と、 40

前記ソースコンタクト領域の一部を覆って前記基板の前記表面の一部の上に配置されたコンタクト層と、

前記層間誘電体を覆って配置され、前記ソースコンタクト領域と電気的に接触するソース電極であって、動作中の金属-酸化膜半導体電界効果型トランジスタ(MOSFET)デバイスのしきい値電圧のシフトを防止する金属を含むソース電極とを備えた、金属-酸化膜電界効果型トランジスタ(MOSFET)デバイス。

## 【請求項 10】

前記ソース電極金属が、水素に対する拡散バリアである、請求項9記載のMOSFETデバイス。

## 【請求項 11】

前記ソース電極金属が、シリカ中に水分子から分解した原子状の水素を作らない、請求項 50

9 記載の M O S F E T デバイス。

【請求項 1 2】

前記 M O S F E T デバイスの前記しきい値電圧の前記シフトが、前記 M O S F E T デバイスを高温で、高いバイアスで、または両方で動作させたときに、前記 M O S F E T デバイスにおけるバイアス温度不安定性 ( B T I ) からもたらされる、請求項 9 記載の M O S F E T デバイス。

【請求項 1 3】

動作中の前記 M O S F E T デバイスのしきい値電圧の前記シフトが、1 V 未満である、請求項 9 記載の M O S F E T デバイス。

【請求項 1 4】

前記ソース電極が、金属層の組み合わせから構成される、請求項 9 記載の M O S F E T デバイス。

【請求項 1 5】

絶縁層上に配置されたゲート電極と、

動作中の半導体デバイスのしきい値電圧のシフトを防止する金属から構成されるソース電極と、

前記ゲート電極および前記絶縁層と前記ソース電極との間に配置された層間誘電体 ( I L D ) と、

前記ソース電極およびウェル領域の両方と接触し、n 型または p 型のいずれかであるソースコンタクト領域と、

前記絶縁層、前記ソースコンタクト領域、および前記層間誘電体が上に配置され、n 型または p 型のいずれかである炭化ケイ素基板と、

前記炭化ケイ素基板中へと延び、n 型または p 型のいずれかである前記ウェル領域と、

前記ゲート電極とは前記炭化ケイ素基板の反対側に配置されたドレイン電極とを備えた、半導体デバイス。

【請求項 1 6】

前記ソース電極金属が、水素に対する拡散バリアである、請求項 1 5 記載の半導体デバイス。

【請求項 1 7】

前記ソース電極金属が、シリカ中に水分子から分解した原子状の水素を作らない、請求項 1 5 記載の半導体デバイス。

【請求項 1 8】

前記半導体デバイスの前記しきい値電圧の前記シフトが、前記半導体デバイスを高温で、高いバイアスで、または両方で動作させたときに、前記半導体デバイスにおけるバイアス温度不安定性 ( B T I ) からもたらされる、請求項 1 5 記載の半導体デバイス。

【請求項 1 9】

動作中の前記半導体デバイスのしきい値電圧の前記シフトが、1 V 未満である、請求項 1 5 記載の半導体デバイス。

【請求項 2 0】

前記ソース電極が、金属層の組み合わせから構成される、請求項 1 5 記載の半導体デバイス。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本明細書において開示する主題は、半導体デバイスに関し、より詳細には、半導体デバイスの安定性を向上させることに関する。

【背景技術】

【0 0 0 2】

炭化ケイ素 ( S i C ) トランジスタなどの半導体デバイスに関して、バイアス温度不安定性 ( B T I ) が、デバイス性能における相当な変動を引き起こすことがある。例えば、

10

20

30

40

50

負バイアス温度不安定性（NBTI）は、特に、長時間にわたり負バイアスおよび／または高温などの特定の条件下で動作させたときに、SiCデバイスのしきい値電圧の著しい変化またはドリフトを引き起こすことがある。SiCデバイスにおけるNBTIは、界面電荷トラッピング（例えば、酸化膜電荷）の結果であると考えられ、界面電荷トラッピングは、例えば、長時間にわたって、高温で、および特定のバイアス条件下でデバイスを動作させることによって誘起されることがある。例えば、SiC金属-酸化膜-半導体電界効果型トランジスタ（MOSFET）は、NBTIに起因して、複合電圧温度ストレス印加を受けたときにしきい値電圧シフトを受けることがある。

#### 【0003】

場合によっては、前述のNBTIは、ゲート-ソース電圧を印加しないときでさえデバイスが導電性になることがある点まで、SiCデバイスのしきい値電圧をシフトさせる（例えば、減少させる）ことがある、ノーマリーオフデバイスをノーマリーオンデバイスに変換する。したがって、NBTIは、SiCデバイスの信頼性および性能に著しく強い影響を与える。SiCデバイスにおけるNBTIに対する産業的に受け入れられる解決策は、まだ定まっていない。したがって、SiCデバイスにおけるNBTI問題を軽減させることは、SiCがある種のシステムおよび用途に提供することができる独特な動作特性（例えば、より高い動作温度、向上された機械的特性、向上された電気的特性、等）をうまく利用するために特に望ましい。

#### 【先行技術文献】

#### 【特許文献】

#### 【0004】

【特許文献1】米国特許出願公開第2011/0215399号明細書

#### 【発明の概要】

#### 【0005】

一実施形態では、半導体デバイスを製造するための方法が提供される。本方法によれば、半導体製造に適した炭化ケイ素ウェハが用意される。1つまたは複数の半導体デバイスは、各炭化ケイ素ウェハ上に製造される。各半導体デバイスのソース電極は、動作中の半導体デバイスのしきい値電圧のシフトを制限する金属を堆積することによって形成される。

#### 【0006】

別の一実施形態では、金属-酸化膜半導体電界効果型トランジスタ（MOSFET）デバイスが提供される。MOSFETデバイスは、ゲート電極と、炭化ケイ素からなり、ゲート電極を支持しつつ表面法線方向を規定する表面を有する基板とを含む。基板は、第1の導電型を有するように第1のドーパント型を含むドリフト領域と、ドリフト領域に隣接し、表面に対して近位にあるウェル領域であって、第2の導電型を有するように第2のドーパント型およびゲート電極に対して近位に配置されたチャネル領域を含むウェル領域と、ウェル領域に隣接し、第1の導電型を有するソースコンタクト領域とを含む。また、MOSFETデバイスは、ゲート電極の周りに、基板の表面の一部の上に配置された層間誘電体と、ソースコンタクト領域の一部を覆って基板の表面の一部の上に配置されたコンタクト層と、層間誘電体を覆って配置され、ソースコンタクト領域と電気的に接触するソース電極とを含む。ソース電極は、動作中のMOSFETデバイスのしきい値電圧のシフトを防止する金属を含む。

#### 【0007】

別の一実施形態では、半導体デバイスが提供される。半導体デバイスは、絶縁層上に配置されたゲート電極と、動作中の半導体デバイスのしきい値電圧のシフトを防止する金属から構成されるソース電極と、ゲート電極および絶縁層とソース電極との間に配置された層間誘電体（ILD）と、ソース電極およびウェル領域の両方と接触し、n型またはp型のいずれかであるソースコンタクト領域と、絶縁層、ソースコンタクト領域、および層間誘電体が上に配置され、n型またはp型のいずれかである炭化ケイ素基板と、炭化ケイ素基板中へと延び、n型またはp型のいずれかであるウェル領域と、ゲート電極とは炭化ケ

10

20

30

40

50

イ素基板の反対側に配置されたドレイン電極とを備える。

【0008】

本発明のこれらのおよびその他の特徴、態様および利点は、添付の図面を参照して下記の詳細な説明を読めば、より良く理解されるようになるであろう。図面では、類似の参照符号は、図面全体を通して類似の構成要素を表す。

【図面の簡単な説明】

【0009】

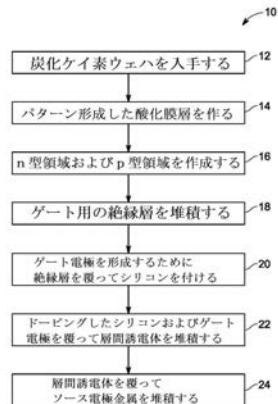

【図1】本技術のある種の実施形態による、トランジスタ製造プロセスのプロセス流れ図である。

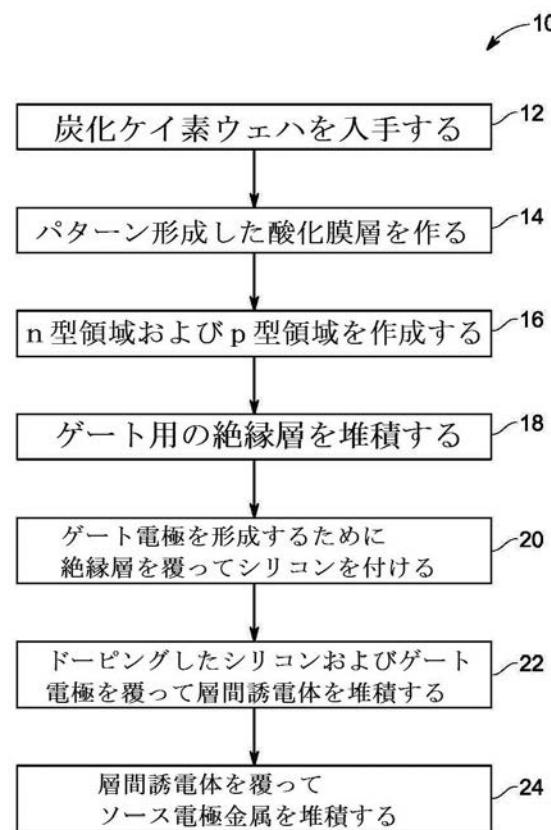

【図2】本手法の一実施形態による、SiC MOSFETの概略断面図である。 10

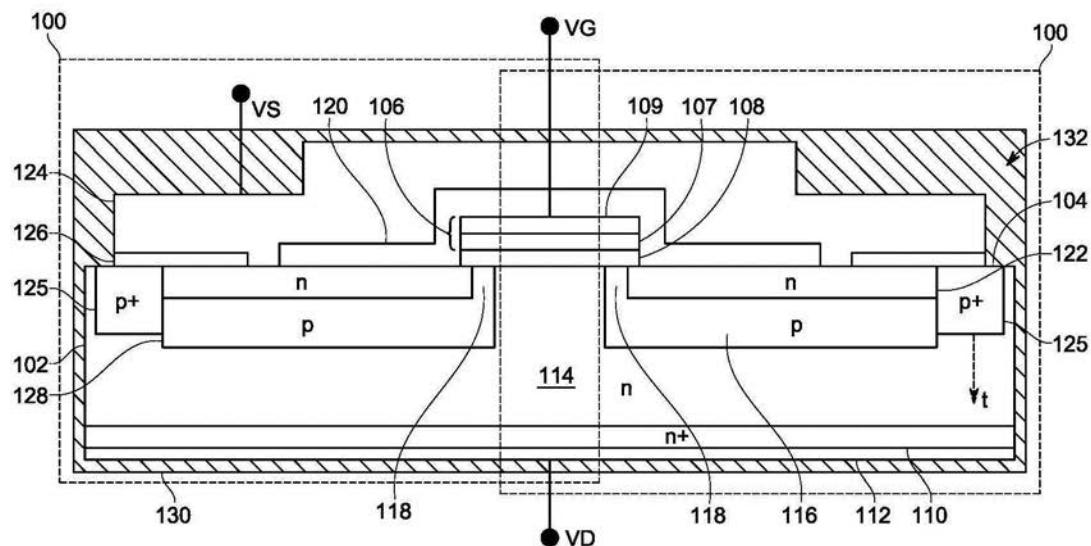

【図3】電圧および温度ストレス印加前後の従来型のMOSFETに関するゲート電圧の関数としてのドレイン電流のプロットである。

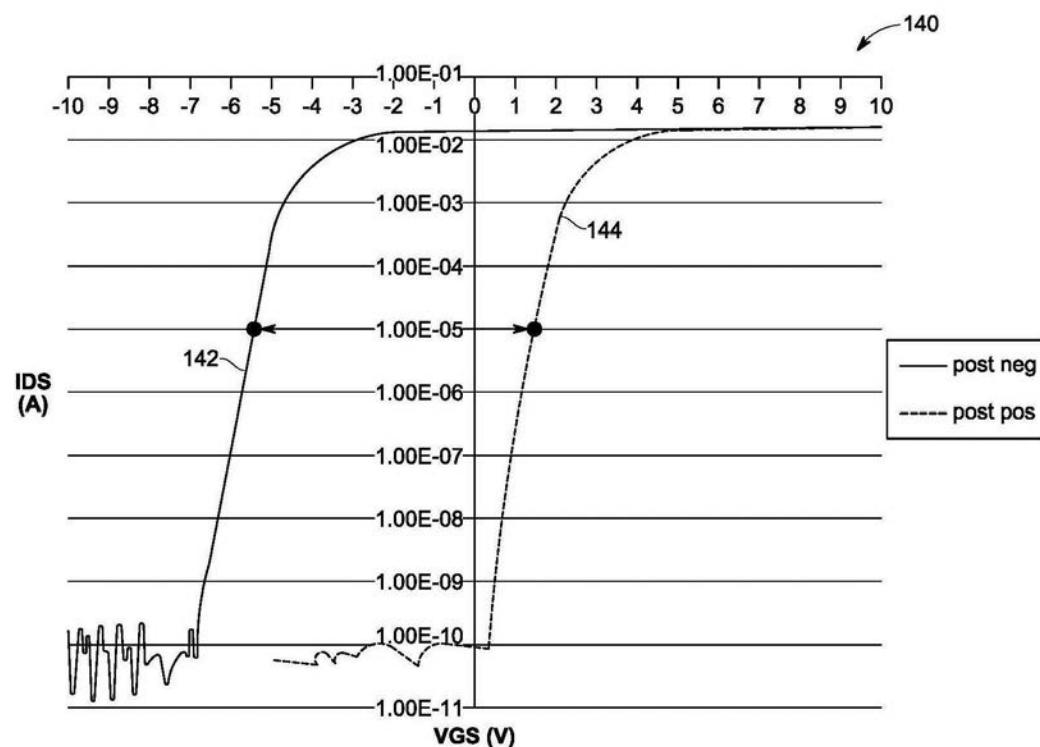

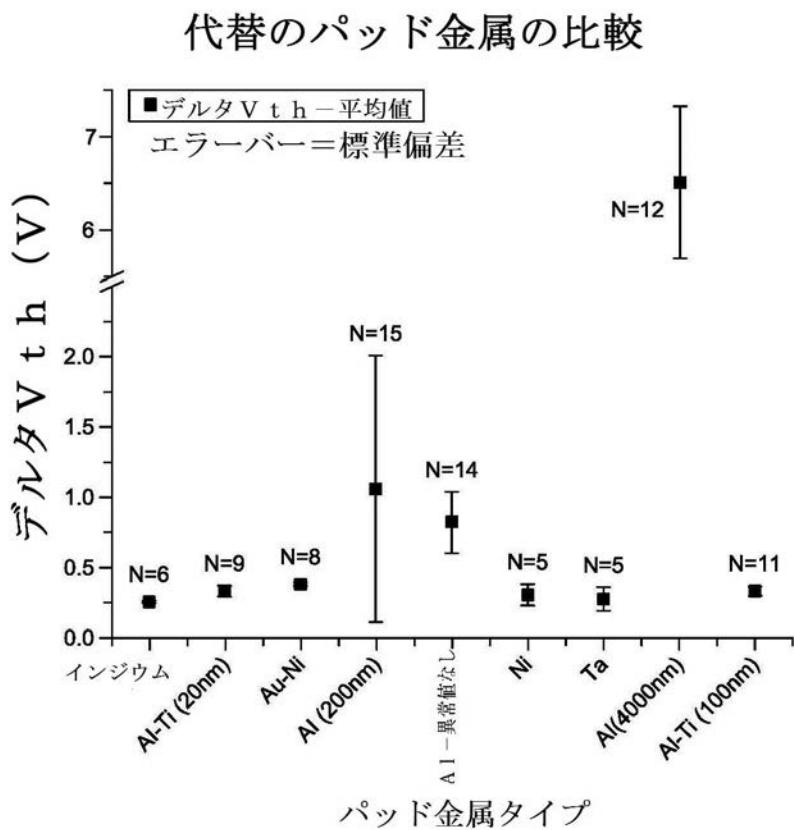

【図4】本手法の実施形態においてさまざまな金属で生じるさまざまなしきい値電圧シフトのグラフ比較図である。

【発明を実施するための形態】

【0010】

1つまたは複数の具体的な実施形態を以下に説明する。これらの実施形態の簡潔な説明を与えることを目指して、実際の実装形態のすべての特徴を明細書中では記述しない場合がある。いずれかのこの実装形態の開発において、いずれかのエンジニアリングプロジェクトまたは設計プロジェクトにおけるように、システムに関係する制約およびビジネスに関する制約にともなうコンプライアンスなどの、実装形態ごとに変わることがある開発者に特有なゴールを達成するために、数多くの実装形態に特有な判断を行わなければならないことを理解されたい。その上、このような開発の試みは、複雑でありかつ長時間を必要とするはずであるが、それにもかかわらず、この開示の恩恵を受ける当業者にとっては設計、製造、および製作の日常的な業務であるはずであることを理解されたい。 20

【0011】

本発明のさまざまな実施形態の要素を導入するときに、「a」、「an」、「the」、および「said」という冠詞は、要素の1つまたは複数があることを意味するものとする。「comprising(備える、含む)」、「including(含む)」および「having(有する)」という用語は、包括的であり、列挙した要素の他にさらなる要素があり得ることを意味するものとする。 30

【0012】

上述のように、NBTIなどのBTIは、半導体デバイス信頼性に対する挑戦課題を提示する。BTI現象に付随する物理的性質および化学的性質が複雑であることを理解されたい。したがって、BTIの正確なメカニズムが、すべての文中において完全には理解されていないことがあるが、本実施形態は、半導体デバイス(例えば、SiC MOSFET)の動作中に、NBTIなどのBTIを防止する(例えば、低減する、制限する、軽減する、または他の形で減少させる)ためのシステムおよび方法を提供する。特に、本手法は、BTIを許容できるレベル(例えば、数ボルト程度ではなく10分の数ボルト程度)に抑えるSiC半導体デバイスのソース電極としての金属を含むことを包含する。ある種の実施形態では、方法は、金属をソース電極として堆積する半導体デバイス製造プロセスにおけるステップを含む。他の実施形態では、ソース電極として金属を含むSiC半導体デバイスまたはMOSFETデバイスを提供する。 40

【0013】

下記の開示は、一般的にSiC MOSFETにおけるNBTIに焦点を当てているが、BTIを緩和するために本明細書において詳細に述べる解決策および技術は、絶縁ゲートバイポーラトランジスタ(IGBT)、MOS制御サイリスタ、およびゲート制御サイリスタなどの他の半導体デバイスへの適用可能性を有する場合があることを理解されたい。説明のための目的で、MOS制御サイリスタ(MCT)は、構造内に組み込まれている 50

2個のMOSFETを含むことができ、BTI効果の結果としてのしきい値電圧(VTH)のシフトに対して敏感であり得る。本明細書において詳細に述べる技術はまた、正バイアス下で生じるVTH効果を呼ぶ正バイアス温度不安定性(PBTI)に関係する効果も緩和するであろうこともまた企図されている。

#### 【0014】

上記を念頭に置いて、図1は、本手法のある種の実施形態による、トランジスタ製造プロセス10の一例のステップのプロセス流れ図を図示する。ブロック12によって表されているように、炭化ケイ素ウェハを入手することができる。一実施形態では、ウェハを、酸化膜層とも呼ばれる二酸化ケイ素の層を形成するために炉内で加熱することができる。炭化ケイ素ウェハを入手し、酸化膜層を形成した後で、ブロック14によって表わされているように、パターンをウェハの酸化膜層中に作成することができる。

10

#### 【0015】

一実装形態では、パターン形成済酸化膜層を作成するために、フォトレジストの層を、酸化膜層の表面を覆って塗布し、ベーク乾燥させることができる。トランジスタの回路フィーチャを画定するマスクを、フォトレジストに適用することができ、フォトレジストを紫外光で露光することができる。紫外光で露光されたフォトレジストの部分を、アルカリ溶液によって、軟化させ洗い流すことができる。強酸を、ウェハに適用することができ、フォトレジストによって保護されていない酸化膜層の部分を、溶解することができる。溶剤を次に使用することができ、残っているフォトレジストを除去することができる。これによって、パターン形成済酸化膜層を、炭化ケイ素ウェハ上に残すことができる。理解されるように、上記が適切な酸化膜パターン層を形成するための一手法に関するとはいえ、いずれかの他の適切なリソグラフィ手法を、製造しようとするデバイスの酸化膜層上に(または他の層上に)所望の図形および/またはパターン形成するために採用することができる。

20

#### 【0016】

所望の酸化膜パターンを炭化ケイ素ウェハ上に設けられた後で、ブロック16によって表したように、n型領域およびp型領域を、炭化ケイ素中に形成することができる。例えば、一実装形態では、炭化ケイ素表面中へとドナー原子またはアクセプタ原子を注入するために、イオンビームにウェハを曝すことによって、n型領域およびp型領域(すなわち、ウェル)を作成することができる。異なる種類の原子が、n型ウェルおよびp型ウェルを作成する。例えば、ホウ素イオンビームは、p型ウェルを作成することができ、一方で、リンイオンビームは、n型ウェルを作成することができる。パターン形成済酸化膜層を、ウェルの正確な配置を可能にするように設計することができる。トランジスタを製造するときに、ボックス14および16を、数回繰り返して、炭化ケイ素中に複雑なウェルパターンを作成することができる。

30

#### 【0017】

製造しようとするデバイスに応じて、ウェルを所定の場所に作った後で、もう1つの酸化膜層を上述の方式で形成することができる。ボックス18によって表したように、薄い絶縁層を、ドリフト領域を覆って堆積することができる。ある種の実施形態では、絶縁層を、炭化ケイ素ウェハの一部の上に堆積するまたは熱成長させることができる。絶縁層を、二酸化ケイ素またはもう1つの適切な絶縁体から作ることができる。絶縁層を堆積した18後で、ボックス20によって表したように、ポリシリコンを、ゲート電極を形成するために絶縁層を覆って堆積することができる。ある種の実施形態では、追加の低抵抗層を、ポリシリコン層を覆って堆積することができる。

40

#### 【0018】

ポリシリコン層を堆積した後で、ボックス22によって表したように、層間誘電体(ILD)を、ポリシリコン層を覆って堆積することができる。ILDを、ゲート電極のポリシリコンまたは金属材料をソース電極から絶縁するために使用することができる。ボックス24によって表したように、ソース電極を、ILDを覆って次に堆積することができる。本明細書において論じるように、ソース電極を、動作中のトランジスタのしきい値電圧

50

のシフトを防止するまたは制限する金属から作ることができる。

【0019】

前述の製造操作の一例を念頭に置いて、図2は、本手法の一実施形態による、金属-酸化膜半導体電界効果型トランジスタ(MOSFET)100を図示する。ある種の実施形態では、図示したMOSFET100を、(例えば、ほぼ125より高い、ほぼ175

より高い、および/またはほぼ300より高い)高温動作作用に設計されたSiC系MOSFETとすることができる。加えて、図示したMOSFET100を、上述のプロセスなどの標準マイクロエレクトロニク製造プロセスを使用して製造することができる。これらのプロセスは、例えば、リソグラフィ、膜堆積/成長法(例えば、物理気相堆積および化学気相堆積、メッキ、酸化、等)、結晶成長法、ならびにウェットエッチングおよびドライエッチング法を含むことができる。図示したMOSFET100は、炭化ケイ素(SiC)などの半導体材料から作ることができる基板102を含む。基板102を、半導体ダイまたはウェハとすることができる、基板は主表面104および表面法線方向または「厚さ方向」tを規定し、表面法線方向は表面から面直方向で基板102中へと延びる。図2が、一例のMOSFET100中のさまざまな構成要素の相対的な位置を図示することを目的とし、これらの構成要素の相対的な尺度または寸法を示唆するようには解釈すべきではないことを理解されたい。

【0020】

示された実施形態では、図示した表面104は、ゲート電極106を支持する。加えて、図示したゲート電極106は、絶縁層108(これはまた、ゲート酸化膜またはゲート誘電体層とも呼ばれることがある)上に配置され、絶縁層108は基板102の表面104と直接接触する。絶縁層108を、一般に、二酸化ケイ素(SiO<sub>2</sub>)などの電気的絶縁性材料から作ることができる。さらにその上、図示した絶縁層108は、表面104に沿って広がり、コンタクト層126までの任意の点まで広がることができる。ゲート電極106は、多結晶シリコン層107を含むことができ、やはり、例えば、電気的導電性材料(例えば、金属および/またはシリサイド)から形成される低抵抗層109を含むことができる。ゲート電極106を、ゲート電圧、VG、を受けるように構成することができる。

【0021】

図示した基板102はまた、ドレイン電極112と接触する第2の表面110を規定し、ドレイン電極112は、一般にドレイン電圧、VD、を受けるように構成される。図2は1個のMOSFETセルの概略断面図であり、全体のMOSFETデバイスは、典型的には、互いに隣り合って位置した多数のセルからなり、多数のセルは共通のゲート電極106およびドレイン電極112を共有することに留意されたい。

【0022】

図示した基板102は、ウェル領域116に加えてドリフト領域114を含み、ウェル領域116は、ドリフト領域114に隣接して配置され、表面104の近位にある。ドリフト領域114を、第1のドーパント型でドープすることができ、第1の多数電荷キャリアをともなう第1の導電型を有する、一方で、ウェル領域116を、第2のドーパント型でドープすることができ、第2の多数電荷キャリアをともなう第2の導電型を有する。例えば、SiC基板102では、第1のドーパント型を、窒素およびリン(「n型ドーパント」)のうちの1つまたは複数とすることができます、一方で、第2のドーパント型を、アルミニウム、ホウ素、ガリウム、およびベリリウム(「p型ドーパント」)のうちの1つまたは複数とすることができます、それぞれ、nドープ領域およびpドープ領域をもたらす。そのような実施形態に関して、第1および第2の多数電荷キャリアは、それぞれ電子および正孔であるはずである。

【0023】

図示した基板102は、さらに、第1の導電型(例えば、図2ではn型)を有するソースコンタクト領域122を含む。ウェル領域116を、コンタクト領域122の近位に配置することができ、その結果、ウェル領域116は、ゲート電極106の近位に配置され

るチャネル領域 118 をその中に含むことができる。例えば、チャネル領域 118 は、ゲート電極 106 の下で表面 104 に沿って広がることができる（ここでは、「下に」は、さらに厚さ方向  $t$  に沿うことを意味する）。加えて、誘電体層 120、時には層間誘電体（ILD）と呼ばれる、を、ゲート電極 106 および絶縁層 108 を覆って配置することができる。一例では、誘電体層は、リンケイ酸ガラス（PSG）を含む材料である。

#### 【0024】

一実施形態では、ソースコンタクト領域 122 を、表面 104 に隣接して配置することができ、ウェル領域 116 は、ソースコンタクト領域 122 を取り囲むことができる。基板 102 はまた、ある種の実施形態では、第 2 の導電型（例えば、図 2 では p 型）を有するボディコンタクト領域 125 を含む。図示した実施形態のボディコンタクト領域 125 は、ウェル領域 116 および表面 104 に隣接して配置される。

10

#### 【0025】

ソース電極 124（例えば、ニッケルなどの金属から形成される）を、ソースコンタクト領域 122 およびボディコンタクト領域 125 を覆って配置することができ、ソース電圧、VS、を受けるように構成することができる。さらに、ソース電極 124 を、ソースコンタクト領域 122 およびボディコンタクト領域 125 の両方と電気的に接触させることができる。例えば、図示した実施形態では、ソース電極 124 とソースコンタクト領域 122 およびボディコンタクト領域 125 との電気的な接触は、コンタクト層 126（例えば、ニッケルまたは別の適切な金属から形成される）を介して行われる。ソース電極 124 の形成および構成を、下記に非常に詳細に論じる。

20

#### 【0026】

動作中には、MOSFET 100 は、一般にスイッチとして働く。電圧差  $VDS = VD - VS$  がドレイン電極 112 とソース電極 124 との間に印加されると、これらの同じ電極間の出力電流（IDS）を、ゲート電極 106 に印加される入力電圧  $VGS$  によって変調することができる、または他の形で制御することができ、ここでは、 $VGS = VG - VS$  である。MOSFET 100 の「しきい値電圧」（ $VTH$ ）よりも低いゲート電圧  $VG$  に対して、電流  $IDS$  は、名目上約ゼロのままであるとはいえ、ゲート電圧がしきい値電圧よりも低いとしても、比較的小さな漏れ電流が存在することがある。しきい値電圧  $VTH$  は、とりわけ、MOSFET 100 の寸法、材料、およびドーピングレベルの関数であり、MOSFET は、典型的には、所定のしきい値電圧  $VTH$  を示すように設計される。MOSFET 100 を組み込んでいる回路を、次に、期待する（所定の）しきい値電圧  $VTH$  に設計することができる。

30

#### 【0027】

MOSFET についてのしきい値電圧（ $VTH$ ）が一義的には定められないことを理解されたい。 $VTH$  を測定するための少なくとも 5 つの異なる技術があり、特定の例に関しては、これらが必ずしも正確に同じ結果を生じる必要がない。本明細書において採用する方法は、「しきい値ドレイン電流法」と呼ばれ、そこでは、指定されたドレイン電流におけるゲート電圧を、しきい値電圧とする。

#### 【0028】

SiC MOSFET を含む従来型のMOSFET は、ゲート電極 106 とソース電極 124 との間に電位差を受けると、特に、高温でかつ長時間にわたってこの電位を受けると、NBTI に起因するしきい値電圧のシフトを受けることが見出されている。具体的には、述べたように、負バイアス温度不安定性（NBTI）は、SiC デバイスにとっての関心事である。このようなしきい値電圧シフトの例を図示すると、図 3 は、電圧および温度ストレス印加の前後の従来型のMOSFET についてのゲート電圧の関数としてのドレイン電流のプロット 140 である。すなわち、図 3 は、本明細書において論じるように、動作中の NBTI 効果を制限するソース電極 124 を欠いたストレス印加した SiC MOSFET デバイスにおける NBTI 効果を図示する。

40

#### 【0029】

図 3 に関連して、「サブしきい値技術」の変形であるしきい値ドレイン電流法を、Si

50

C MOSFETデバイスにおけるNBTI現象を特徴付けるときに使用することができる。図3のプロット140に図示したデータを生成するために使用した例のテスト条件を、下記に記述する。ある種の実施形態では、テスト条件を、増幅特性曲線測定値が一定のストレス温度においてMOSFETについて取られるように設定することができる。例えば、最初に、ゲート電圧を、一定の-20ボルト(V)で15分間保持することができ、VDSを0Vのところに保持することができる。次に、小さな一定電圧を、ソース端子とドレイン端子との間に(例えば、ほぼ100mV)印加することができ、ゲート電圧を、-10Vから+10Vまで掃引することができ、範囲はMOSFETの低電流範囲(例えば、この特定のケースでは0.1ナノアンペア未満)から飽和電流(例えば、ほぼ16ミリアンペア)までを取り込むために十分に大きく、図3に示された「post neg」増幅特性曲線142を画定する。+20Vの定電圧ゲート正ストレスバイアスを、次に、VDS=0Vで、さらに15分間にわたりゲートに印加することができる。最後に、ゲート電圧の同様の逆掃引を、+10Vから-10Vまで行うことができ、VDS=0.1Vで「post pos」増幅特性曲線144を取り込むことができる。

10

#### 【0030】

VTH決定のためのしきい値ドレン電流の選択として10マイクロアンペアを使用することは、実際的な理由で行われる。例えば、しきい値ドレン電流は、片対数増幅特性曲線の線形サブしきい値部分上に存在するように十分に小さく、かつ正確に測定しデータから容易に抽出するために十分に大きい。MOSFETパラメータおよびデータ収集用のテスト条件は、下記の通りであった、VDS=0.1V、温度=175、ゲート酸化膜厚(Tox)=500オングストローム、デバイス能動領域面積=0.067cm<sup>2</sup>、1個のMOSセルの面積=1.6E-4cm<sup>2</sup>、1個のMOSセルのチャネル幅対長さ比(W/L)=6900。より大きなデバイスまたはより小さなデバイスへのしきい値ドレン電流のスケーリングは、デバイス能動領域面積、1個のMOSセルの面積およびW/Lについての線形依存性を有する。しかしながら、しきい値曲線は、ゲート酸化膜厚(Tox)で逆にスケーリングされることに留意されたい。

20

#### 【0031】

したがって、図3は、正および負のゲートバイアスストレス印加に続くしきい値電圧のドリフトまたはシフト(例えば、IDSが著しく増加する電圧のシフト)を実証する。縦軸は、ドレン電流(アンペア)であり、横軸は、ゲートからソースへの電圧(ボルト)である。しきい値電圧シフトは、したがって、バイアス温度不安定性(BTI)の効果の一例を表す。VTHドリフトは、10マイクロアンペアのソースからドレンへの電流におけるVTH正電圧ストレス値とVTH負電圧ストレス値との間の電圧差として取られる。図3に図示した例では、VTHドリフトは、ほぼ6.9Vである。

30

#### 【0032】

ある種の実施形態に関する実験では、ソース電極金属としてのアルミニウムが、水素およびOHラジカルとのアルミニウムの化学的反応性に起因したNBTIに寄与する要因になり得ることを仮定した。一組の実験では、堆積した最終的なソース金属を持たないデバイス上にインジウムリボンの小片を使用した。これらの実験では、インジウムリボンを、SiC半導体のソースパッド領域上に押し付け、125で加熱した。加熱手法は、SiC半導体へのインジウムの接着を向上させた。アルミニウムをインジウムで置き換えることの効果を調査するために、2種類のテストを実行した。第1の系統のテストを、低真空まで真空引きすることができ、さらにSiC半導体におけるNBTIを生じさせるために十分な温度である125まで昇温することができるチャンバ内で行った。第2のテストを、150および175に加熱したヒータにおいて大気条件下で行った。そこでデータを、真空近くでの125、大気条件での125、大気条件での150、および大気条件での175について取得した。インジウムの使用が、SiC半導体におけるNBTIによって生じる結果を軽減したことを、各テストは示した。

40

#### 【0033】

上述のインジウムを用いた実験研究の拡張は、インジウムと同じ機能を可能性として実

50

証するはずの他の金属を含む。一組の実験では、水素に対する優れた拡散バリアである金属は、ソース電極 124 を形成する際の使用が考えられる。加えて、ソース電極 124 を形成する際に使用される金属を評価する際に考慮するもう 1 つの要因は、金属が、シリカ中に水から分解した原子状の水素を生成しないはずであることであった。さらに、金属が分解した原子状の水素を実際に生成する場合には、金属は水素種のゲッタとして機能するはずである。例えば、チタンおよびアルミニウムは、両者とも水から水素を生成するが、チタンは、水素をゲッタできる。これを念頭に置いて、図 4 は、ソース電極のアルミニウム層の下にチタンの層を追加することの利点を示す。上述の特性に基づいて、さまざまな金属および金属の組み合わせをテストするために選択した、金 + 10 ナノメートルニッケル、ニッケル、タンタル、およびアルミニウム。一実験では、ニッケルの 10 ナノメートル層を、半導体表面への金の接着を助けるために接着層として選択した。アルミニウムを、他の金属と NBTI 測定値比較するための基準線として採用した。

#### 【0034】

代替金属実験用の半導体を準備するために、炭化ケイ素ウェハは、ロットがパッド金属堆積ステップに達した後に取り出された。金属堆積の前に、炭化ケイ素ウェハには、標準パッド金属パターンでパターン形成したが、ネガリフトオフレジストを使用した。パターン形成したウェハを、次に、各々おおよそ 20 個のダイの 12 個の長方形片へとレーザ切断した。ダイの行または列を、切断を行うために犠牲にした。さまざまな金属層を、次に断片上に堆積した。金属層および厚さは、次のようであった、金 (2000) / ニッケル (100)、ニッケル (2000)、タンタル (2000)、アルミニウム (2000)、およびアルミニウム (約 100)。下記の金属をやはりテストした、アルミニウム (40000)、アルミニウム (40000) / チタン (200)、およびアルミニウム (40000) / チタン (1000)。一部の試料を、1 分プレスパッタのプレクリーニングを行ったが、他は、1 分プレスパッタ、待機、およびもう 1 回 1 分プレスパッタを行った。金 / ニッケル試料を、両方のプレクリーニング法でテストし、アルミニウムの 2000 試料を、ブリクリーニングせずにテストした。金属試料を、MRC643 スパッタ、Perkin - Elmer スパッタ、または Temescal スパッタのいずれかで堆積した。堆積後に、試料を超音波槽においてアセトン中に別々に浸した。アセトンは、レジストパターンおよびその上に堆積した金属を除去した。断片は、次に、ST22 および PRS1000 溶媒洗浄にかけ、NBTI 用のテストを行う前に、クリーンルーム内のドライボックス中に保管された。

#### 【0035】

実験の結果が図 4 に与えられ、グラフは、さまざまなソースパッド電極金属タイプについてのさまざまなしきい値電圧シフトの比較を示す。データ点の上方の変数「N」は、採用した測定値の数を表す。200 nm でのアルミニウム試料について、2 つのデータ点がグラフ上に現れる。最初の A1 (200 nm) データ点は、4.42 V の電圧しきい値シフト値を有する 1 つの試料を含むデータセットを表す。「A1 - 異常値なし」と名付けたデータ点は、異常値を除外した同じデータセットを含む。グラフ上で比較した各々の金属（アルミニウムを除く）は、0.25 V に近いしきい値電圧シフトを有する。金属は、ほんの約 0.05 から 0.2 V の偏差を有する。一方で、アルミニウムは、200 nm 試料（異常値なし）について 0.75 V に近く、4000 nm 試料については 6.6 V に近いしきい値電圧シフトを有する。200 nm アルミニウム（異常値なし）および 4000 nm アルミニウム金属の両者とも、それぞれ、約 0.5 V および 1.5 V の大きな偏差を有する。BTI 効果が典型的な SiC MOSFET においては数ボルト（例えば、2 V から 6 V）のしきい値電圧シフトを引き起こすことがあるので、本明細書において検討したようなソース電極 124 の使用は、デバイス信頼性に対して顕著な向上を提供することを理解されたい。

#### 【0036】

実験の結果は、インジウムがしきい値電圧シフトを制限するために適した材料であることを示唆するはずであるが、適用の方法がテストした他の金属とは異なっており、そのた

め真の比較は困難であった。また、A 1 のみのパッド金属を用いると、175 におけるNBTI測定値は、同等の金属厚さについての実験において試みた他のパッド金属のいずれよりも2~4倍の間で大きかった。信頼性の観点から、代替のパッド金属は、互いに0.1~0.2Vの範囲内であり、純粋なアルミニウムよりも狭い偏差を示した。代替のパッド金属はまた、基準線金属タイプと比較したときに相対的に狭い偏差を示した。200 アルミニウム試料は、40000 アルミニウム試料よりもほぼ6.5倍小さなNBTIシフトを示す。より小さなNBTIシフトは、20倍だけ試料の厚さを減少させることの反映であり得る。アルミニウム(40000) / チタン(200)の組み合わせは、残りの金属と同等のNBTIシフトを示した。少量のチタンが小さなNBTIシフトを有したという観測は、ある種の実施形態では、チタンが水素ゲッタとして主としては働くのではなく、アルミニウムとMOSFETの誘電体層との間の単純にバリアとして働くことを示唆した。行った実験では、金は、実際に小さなNBTIシフトを有したが、NBTIシフトは、インジウム、ニッケル、またはタンタルのシフトよりもわずかに大きかった。これゆえ、本明細書において検討したように、ソース電極124として存在するときに、アルミニウムパッド金属を誘電体層との物理的な接触から切り離すことが、MOSFETにおけるNBTIシフトの低減をもたらす。あるいは、上で検討したものなどの他の金属を、ソース電極124を形成するために、およびNBTIシフトの低減を実現するために使用することができる。

#### 【0037】

これゆえ、本明細書において検討したように、ある種のソース電極金属を有するMOSFETを製造することは、図3に図示したドリフトを大部分は防止するまたは制限するであろう。ある種の実施形態によれば、ソース電極124を、動作中のMOSFETデバイスのしきい値電圧のシフトを制限する金属から構成することができる。ある種の実施形態では、金属は、シリカ中に水分子から分解した原子状の水素を生成しないことがある。さらに、金属は、水素に対する拡散バリアであり得る。ある種の実施形態では、金属は、アルミニウムパッド金属をMOSFETの誘電体層との物理的接触から避ける方法として働くことができる。薄膜を堆積するスパッタリング法または任意の他の適切な堆積技術を使用することによって、金属を堆積することができる。例えば、ある種の実施形態では、ソース電極124を、ニッケル(Ni)の薄膜もしくは層(例えば、2000)またはタンタルの薄膜もしくは層(例えば、2000)から構成することができる。他の実施形態では、ソース電極124を、金属層の組み合わせから構成することができる。例えば、ソース電極124を、Niの薄膜もしくは層(例えば、100)と重ね合わせた金(Au)の薄膜もしくは層(例えば、2000)、またはチタンの薄膜もしくは層(例えば、200)と重ね合わせたアルミニウムの膜もしくは層(例えば、40000)から構成することができる。ある種の実施形態では、金属の層のうちの1つを、接着層として使用することができ、MOSFETとのソース電極124の接触を向上させることができる。理解されるように、本明細書において検討したような、ソース電極124としてまたはソース電極124とともに使用するためのさまざまな金属は、いくつかのこのような適切な金属または材料の例を単に表すにすぎない。これゆえ、他の金属または材料を、単独でまたは相互に組み合わせて、本明細書において検討したように、BTI(正および負の両方)の効果を制限するためにやはり使用することができ、本開示によって包含される。

#### 【0038】

実施形態の技術的な効果は、動作中の半導体デバイスのしきい値電圧のシフトを防止するように設計された半導体デバイス(例えば、炭化ケイ素(SiC)デバイス)を含む。ある種の実施形態では、半導体デバイスは、絶縁層上に配置されたゲート電極、ソース電極、層間誘電体、基板、ウェル領域、ソースコンタクト領域、およびドレイン電極を含む。ソース電極は、動作中の半導体デバイスのしきい値電圧のシフトを防止する金属であるように選択される。

#### 【0039】

本書は、最良の形態を含む本発明を開示するため、ならびに任意のデバイスまたはシス

テムを作成することおよび使用すること、および任意の組み込んだ方法を実行することを含めて本発明を当業者が実施することも可能にするために例を使用している。本発明の特許性のある範囲は、特許請求の範囲によって規定され、当業者なら思い付く別の例を含むことができる。このような別の例が特許請求の範囲の文面から逸脱しない構造的要素を有する場合、またはこのような別の例が特許請求の範囲の文面とは実質的に差異がない等価な構造的要素を含む場合には、このような別の例は、特許請求の範囲の範囲内であるものとする。

## 【符号の説明】

## 【0 0 4 0】

- 1 0 トランジスタ製造プロセス

1 2 炭化ケイ素ウェハ入手する

1 4 パターンをウェハの酸化膜層中に作る

1 6 n型領域およびp型領域を炭化ケイ素中に形成する

1 8 絶縁層を堆積する

2 0 ポリシリコンを、ゲート電極を形成するために絶縁層を覆って堆積する

2 2 層間誘電体を、ポリシリコン層を覆って堆積する

2 4 ソース電極を、層間誘電体を覆って堆積する

1 0 0 M O S F E T

1 0 2 基板

1 0 4 表面

1 0 6 ゲート電極

1 0 8 絶縁層

1 1 0 第2の表面

1 1 2 ドレイン電極

1 1 4 ドリフト領域

1 1 6 ウェル領域

1 1 8 チャネル領域

1 2 0 誘電体層

1 2 2 ソースコンタクト領域

1 2 4 ソース電極

1 2 5 ボディコンタクト領域

1 2 6 コンタクト層

1 4 0 プロット

1 4 2 「post neg」増幅特性曲線

1 4 4 「post pos」増幅特性曲線

10

20

30

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

## フロントページの続き

(51) Int.Cl. F I テーマコード(参考)

H 01 L 29/417 (2006.01) H 01 L 29/50 M

(72)発明者 ジョセフ・ダリル・マイケル

アメリカ合衆国、ニューヨーク州・12309、ニスカユナ、ビルディング・ケイ1-3エイ59

、ワン・リサーチ・サークル

(72)発明者 スティーブン・デイリー・アーサー

アメリカ合衆国、ニューヨーク州・12309、ニスカユナ、ビルディング・ケイ1-3エイ59

、ワン・リサーチ・サークル

(72)発明者 タミー・リン・ジョンソン

アメリカ合衆国、ニューヨーク州・12309、ニスカユナ、ビルディング・ケイ1-3エイ59

、ワン・リサーチ・サークル

(72)発明者 デイヴィッド・アラン・リリエンフェルド

アメリカ合衆国、ニューヨーク州・12309、ニスカユナ、ビルディング・ケイ1-3エイ59

、ワン・リサーチ・サークル

F ターム(参考) 4M104 AA03 BB01 BB05 BB14 BB17 CC01 DD19 DD26 DD37 FF06

FF13 FF14 FF17 FF21 FF31 GG09 GG15 HH04

【外國語明細書】

2014033200000001.pdf