(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5756594号

(P5756594)

(45) 発行日 平成27年7月29日(2015.7.29)

(24) 登録日 平成27年6月5日(2015.6.5)

|              |           |

|--------------|-----------|

| (51) Int.Cl. | F 1       |

| G 06 T 1/20  | (2006.01) |

| G 09 G 5/00  | (2006.01) |

| G 09 G 5/377 | (2006.01) |

| H 04 N 5/66  | (2006.01) |

|              |           |

| GO 6 T       | 1/20      |

| GO 9 G       | 5/00      |

| GO 9 G       | 5/00      |

| HO 4 N       | 5/36      |

|              |           |

|              | 5/66      |

|              | Z         |

請求項の数 4 (全 18 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2009-264631 (P2009-264631)  |

| (22) 出願日  | 平成21年11月20日 (2009.11.20)      |

| (65) 公開番号 | 特開2011-108135 (P2011-108135A) |

| (43) 公開日  | 平成23年6月2日 (2011.6.2)          |

| 審査請求日     | 平成24年11月16日 (2012.11.16)      |

| 審判番号      | 不服2014-7347 (P2014-7347/J1)   |

| 審判請求日     | 平成26年4月21日 (2014.4.21)        |

|           |                                               |

|-----------|-----------------------------------------------|

| (73) 特許権者 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号 |

| (74) 代理人  | 110000028<br>特許業務法人明成国際特許事務所                  |

| (72) 発明者  | 氣賀澤 和義<br>長野県諏訪市大和三丁目3番5号 セイコ<br>ーエプソン株式会社内   |

合議体

審判長 藤井 浩

審判官 小池 正彦

審判官 渡辺 努

最終頁に続く

(54) 【発明の名称】 画像処理装置、画像処理方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の画素により構成された画像を表す画像データを処理する画像処理装置であって、前記画像データに対応した表示画像を水平方向および垂直方向に二次元的に分割した各部分画像に対応して設けられ、該部分画像に対応した画像データを入力し、該部分画像を構成する各画素のデータを、該部分画像の外側の前記部分画像の画素データである周辺画素データを参照して処理する複数の画像処理ユニットと、

該画像処理ユニットによって前記画像処理が行われた後の画素のデータを用いて、表示用画像データを出力する画像出力ユニットと

を備え、

前記複数の画像処理ユニットの各々は、

前記画像処理に先立つ2回のタイミングの各々で、前記各画像処理ユニットに水平方向または垂直方向にそれぞれ隣接する画像処理ユニットとの間で、前記周辺画素データのやり取りをし、

1回目のタイミングにおいて、該画像処理ユニットに水平方向または垂直方向のいずれか一方に隣接する前記画像処理ユニットと、互いに、前記周辺画素データをやり取りし、

前記1回目のタイミングとは別の2回目のタイミングで、該画像処理ユニットに水平方向または垂直方向のいずれか他方に隣接する前記画像処理ユニットと、互いに、前記周辺画素データをやり取りし、

前記2回のやり取りにより取得された、当該画像処理ユニットに対応する前記部分画像

に対角方向に隣接する対角隣接部分画像の周辺画素データを含んで、前記画像処理を行う

画像処理装置。

**【請求項 2】**

請求項1記載の画像処理装置であって、更に、

前記画像データを入力する画像データ入力部と、

前記画像データに対応した前記表示画像を二次元的に分割して複数の前記部分画像とし

、該各部分画像を前記各画像処理ユニットに入力する画像分割部と

を備える画像処理装置。

**【請求項 3】**

請求項1または請求項2記載の画像処理装置であって、更に、

前記各画像処理ユニットが前記周辺画素データのやり取りをする、時分割された複数の

タイミングを制御するタイミング制御部を備える画像処理装置。

**【請求項 4】**

複数の画素により構成された画像を表す画像データを、前記画像データに対応した表示

画像を水平方向および垂直方向に二次元的に分割した各部分画像に対応して設けられ、該

部分画像に対応した画像データを入力し、該部分画像を構成する各画素のデータを、該部分

画像の外側の前記部分画像の画素データである周辺画素データを参照して処理する複数

の画像処理ユニットを用いて処理をする画像処理方法であって、

前記複数の画像処理ユニットの各々は、

前記画像処理に先立つ2回のタイミングの各々で、前記各画像処理ユニットに水平方向

または垂直方向にそれぞれ隣接する画像処理ユニットとの間で、前記周辺画素データのや

り取りをし、

1回目のタイミングにおいて、該画像処理ユニットに水平方向または垂直方向のいずれ

か一方に隣接する前記画像処理ユニットと、互いに、前記周辺画素データをやり取りし、

前記1回目のタイミングとは別の2回目のタイミングで、該画像処理ユニットに水平方

向または垂直方向のいずれか他方に隣接する前記画像処理ユニットと、互いに、前記周辺

画素データをやり取りし、

前記2回のやり取りにより取得された、当該画像処理ユニットに対応する前記部分画像

に対角方向に隣接する対角隣接部分画像の周辺画素データを含んで、前記画像処理を行な

う

画像処理方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は画像処理の技術に関する。

**【背景技術】**

**【0002】**

近年、プロジェクター、液晶テレビ、プラズマテレビなどの映像表示機器に入力される

画像の高解像度化が進んでおり、こうした機器では、画面を構成する多数の画素に対する

画像処理を短時間に終了するために、入力された画像データを複数の部分画像データに分

割して並列に処理する方法がとられる場合がある。複数の部分画像データに分割されて入

力されたデータに対して、複数の画像処理部で処理を施そうとする時、各画像処理部は分

割された各画部分像データの周辺領域の画素データ（以下、周辺画素データとも呼ぶ）を

参照する、所謂フィルター処理を行う。周辺画素データを参照してフィルター処理を行う

技術としては例えば特許文献1が挙げられる。

**【先行技術文献】**

**【特許文献】**

**【0003】**

【特許文献1】特開2006-5524

10

20

30

40

50

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

各画像処理部同士で直接に周辺画素データを交換する方法としては、従来、以下の方法が採られてきた。各画像処理部が、隣接する部分画像データの処理を担当する複数の画像処理部と、各々に周辺画素データ交換用のラインで接続されていて、それぞれ直接に通信をして周辺画素データを交換する方法である。この方法では、1つの画像処理部が周囲の他の画像処理部と最大で8個、それぞれ通信をする必要がある。具体的には、1つの部分画像を中心に、上、下、左、右、上右斜め、上左斜め、下左斜め、下右斜めの各方向に隣接する各部分画像データの処理を担当する画像処理部、計8個の画像処理部と、周辺画素データの交換が必要である。よって、トランシーバー数、配線数、デバイスのピン数等の数が多くなってしまう。

10

**【課題を解決するための手段】****【0005】**

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態又は適用例として実現することが可能である。

**[形態]**

複数の画素により構成された画像を表す画像データを処理する画像処理装置であって、前記画像データに対応した表示画像を水平方向および垂直方向に二次元的に分割した各部分画像に対応して設けられ、該部分画像に対応した画像データを入力し、該部分画像を構成する各画素のデータを、該部分画像の外側の前記部分画像の画素データである周辺画素データを参照して処理する複数の画像処理ユニットと、該画像処理ユニットによって前記画像処理が行われた後の画素のデータを用いて、表示用画像データを出力する画像出力ユニットとを備え、前記複数の画像処理ユニットの各々は、前記画像処理に先立つ2回のタイミングの各々で、前記各画像処理ユニットに水平方向または垂直方向にそれぞれ隣接する画像処理ユニットとの間で、前記周辺画素データのやり取りをし、1回目のタイミングにおいて、該画像処理ユニットに水平方向または垂直方向のいずれか一方に隣接する前記画像処理ユニットと、互いに、前記周辺画素データをやり取りし、前記1回目のタイミングとは別の2回目のタイミングで、該画像処理ユニットに水平方向または垂直方向のいずれか他方に隣接する前記画像処理ユニットと、互いに、前記周辺画素データをやり取りし、前記2回のやり取りにより取得された、当該画像処理ユニットに対応する前記部分画像に対角方向に隣接する対角隣接部分画像の周辺画素データを含んで、前記画像処理を行なう。

20

**【0006】****[適用例1]**

複数の画素により構成された画像を表す画像データを処理する画像処理装置であって、前記画像データに対応した表示画像を分割した各部分画像に対応して設けられ、該部分画像に対応した画像データを入力し、該部分画像を構成する各画素のデータを該画素の周辺画素のデータを参照して処理する複数の画像処理ユニットと、該画像処理ユニットによって前記画像処理が行われた後の画素のデータを用いて、表示用画像データを出力する画像出力ユニットとを備え、前記複数の画像処理ユニットには、少なくとも、第1の部分画像について前記画像処理を行う際、当該第1の部分画像と隣り合った他の部分画像を構成する画素のうち、少なくとも前記第1の部分画像に隣接する領域の画素のデータを取得して、前記周辺画素のデータとして、前記画像処理に用いる第1の画像処理ユニットと、前記第1の部分画像とは異なる第2の部分画像について前記画像処理を行うと共に、前記第1の画像処理ユニットが前記周辺画素として扱う画素の少なくとも一部のデータを、前記第1の画像処理ユニットが扱う部分画像に隣り合った部分画像を処理する画像処理ユニットから、前記第1の画像処理ユニットに向けて仲介する第2の画像処理ユニットとが含まれる画像処理装置。

30

**【0007】**

40

50

この画像処理装置によると、第1の画像処理ユニットが参照する第1の部分画像に隣り合った他の部分画像の周辺画素データを第2の画像処理ユニットが仲介するので、第1の画像処理ユニットは隣り合った他の部分画像から直接に取得することなしに、周辺画素データを取得することができる。

**[適用例2]**

適用例1記載の画像処理装置であって、前記第2の画像処理ユニットは、当該第2の画像処理ユニットが前記参照のために必要な周辺画素データの取得に併せて、前記第1の画像処理ユニットが前記参照のために必要な前記周辺画素データを仲介する画像処理装置。

この画像処理装置によると、第2の画像処理ユニットは周辺画素データの取得に併せて、第1画像処理ユニットが参照する周辺画素データを仲介するので、取得と仲介とを別々に行う場合と比較して、これらの処理を高速に行うことができる。 10

**[0008]**

**[適用例3]**

適用例2記載の画像処理装置であって、前記各部分画像は、前記画像データに対応した前記表示画像を水平方向および垂直方向に二次元的に分割した画像であり、前記第1の画像処理ユニットが、前記第1の部分画像に対角方向で隣接する対角隣接部分画像の周辺画素データを参照する場合に、前記第2の部分画像は、前記第1の部分画像および前記対角隣接部分画像のうちの一方に水平方向で、他方に垂直方向で隣接して位置し、前記第2の画像処理ユニットは、前記第1の画像処理ユニットが前記参照に必要な前記対角隣接部分画像の周辺画素データを仲介する画像処理装置。 20

この画像処理装置によると、対角方向に隣接する画像処理ユニット同士が互いに直接に周辺画素データを交換する場合と比べて、各画像処理ユニットが周辺画素データの取得、および仲介をする経路を構造的に簡易化することができる。

**[0009]**

**[適用例4]**

適用例3記載の画像処理装置であって、前記各画像処理ユニットは、時分割された2回のタイミングで前記周辺画素データのやり取りをし、前記2回のタイミングのうち1回目に、該画像処理ユニットに水平方向または垂直方向のいずれか一方に隣接する前記画像処理ユニットと、互いに、前記周辺画素データをやり取りし、前記2回のタイミングの内の2回目に、該画像処理ユニットに水平方向または垂直方向のいずれか他方に隣接する前記画像処理ユニットと、互いに、前記周辺画素データをやり取りする画像処理装置。 30

この画像処理装置によると、全ての画像処理ユニットが、処理に必要な周辺画素データをやり取りするタイミングを最小限にできる。

**[0010]**

**[適用例5]**

適用例1記載の画像処理装置であって、前記複数の画像処理ユニットは、対応する部分画像に隣接する部分画像にそれぞれ対応する複数の他の画像処理ユニットのうち奇数個の画像処理ユニットから、前記対応する部分画像に隣接する領域の一部の画素のデータを、前記参照用の前記周辺画素データとして取得する画像処理ユニットを0個、若しくは2個含み、前記各画像処理ユニット同士を、該画像処理ユニット同士が互いに直接に前記周辺画素データを取得する経路であるデータ取得経路で結ぶことによって、前記各画像処理ユニットと前記データ取得経路とから構成され、全ての前記画像処理ユニットを1度ずつ通るデータ通信経路が形成される画像処理装置。 40

**[0011]**

この画像処理装置によると、データ通信経路は、画像処理ユニットを全て通る所謂「一筆書き」の経路構成となっている。従って、そのデータ通信経路の始点と終点とが異なる一筆書きの経路構成の場合は、各画像処理ユニットは最大で2つの隣接する画像処理ユニットと互いに直接に周辺画素データの取得を行うのみで処理に必要な周辺画素データの取得が可能なデータ取得経路の構成が可能であり、データ通信経路の始点と終点と同じ、つまり閉路の構成である一筆書きの経路構成の場合は、その経路はループ状となり 50

、その経路構成を最短の経路として構成した場合には、隣接する1つの画像処理ユニットからのみ周辺画素データを取得する処理を繰り返すことで、各画像処理ユニットは処理に必要な周辺画素データを取得することが可能である。

#### 【0012】

##### [適用例6]

適用例1ないし適用例5のいずれか記載の画像処理装置であって、更に、前記画像データを入力する画像データ入力部と、前記画像データに対応した前記表示画像を前記二次元的に分割して複数の前記部分画像とし、該各部分画像を前記各画像処理ユニットに入力する画像分割部とを備える画像処理装置。

この画像処理装置によると、画像分割部を備えるので、直接に表示画像に対応する画像データを画像処理装置に入力して、画像分割部で部分画像に分割し、各画像処理ユニットによって部分画像を処理することが可能である。 10

#### 【0013】

##### [適用例7]

適用例1ないし適用例6のいずれか記載の画像処理装置であって、更に、前記各画像処理ユニットが前記周辺画素データのやり取りをする、時分割された複数のタイミングを制御するタイミング制御部を備える画像処理装置。

この画像処理装置によると、タイミング制御部を備えるので、周辺画素データの取得のタイミングを制御する制御装置を外部に設けることや、タイミングを制御する制御信号を入力することなく、周辺画素データの取得のタイミングを制御することが可能である。 20

#### 【0014】

##### [適用例8]

複数の画素により構成された画像を表す画像データを、前記画像データに対応した表示画像を分割した各部分画像に対応して設けられ、該部分画像に対応した画像データを入力し、該部分画像を構成する各画素のデータを該画素の周辺画素のデータを参照して処理する複数の画像処理ユニットを用いて処理をする画像処理方法であって、前記複数の画像処理ユニットのうち、第1の画像処理ユニットを用いて、第1の部分画像について前記画像処理を行う際、当該第1の部分画像と隣り合った他の部分画像を構成する画素のうち、少なくとも前記第1の部分画像に隣接する領域の画素のデータを取得して、前記周辺画素のデータとして、前記画像処理に用い、第2の画像処理ユニットを用いて、前記第1の部分画像とは異なる第2の部分画像について前記画像処理を行うと共に、前記第1の画像処理ユニットが前記周辺画素として扱う画素の少なくとも一部のデータを、前記第1の画像処理ユニットが扱う部分画像に隣り合った部分画像を処理する画像処理ユニットから、前記第1の画像処理ユニットに向けて仲介し、前記複数の画像処理ユニットによって前記画像処理が行われた後の画素のデータを用いて、表示用画像データを出力する画像処理方法。 30

#### 【0015】

この画像処理方法によると、第1の画像処理ユニットが参考する第1の部分画像に隣り合った他の部分画像の周辺画素データを第2の画像処理ユニットによって仲介するので、第1の画像処理ユニットは隣り合った他の部分画像から直接に取得することなしに、周辺画素データを取得することができる。 40

##### 【図面の簡単な説明】

#### 【0016】

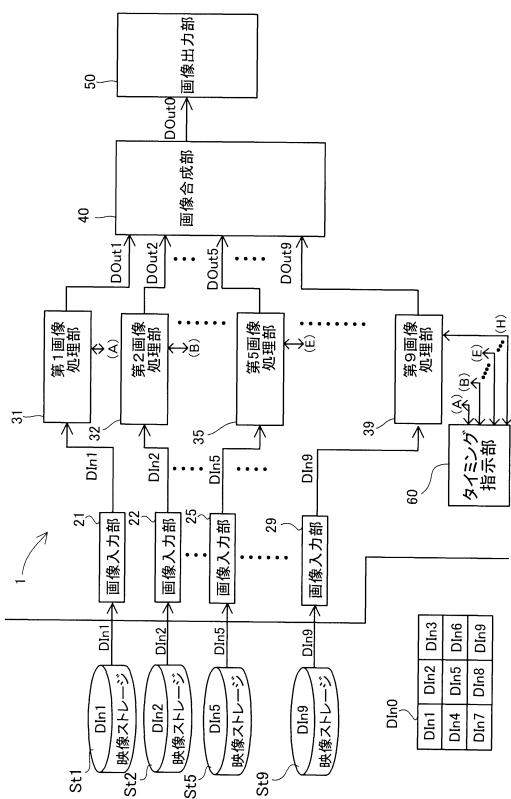

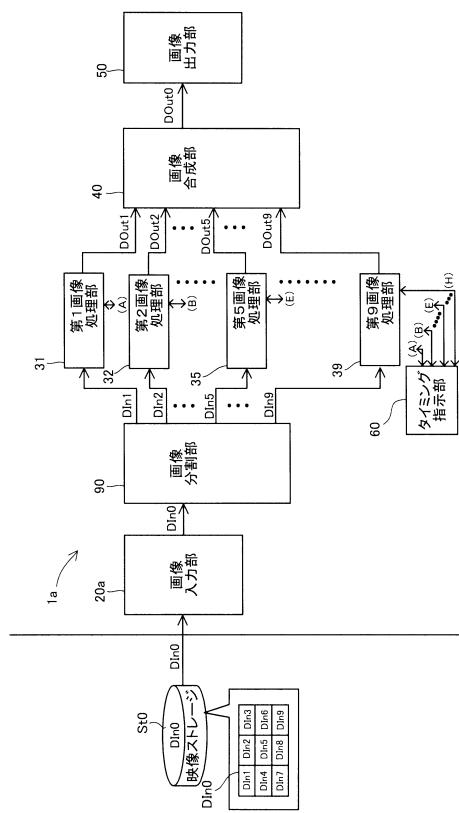

【図1】第1実施例としての画像処理装置1の構成を示す構成図である。

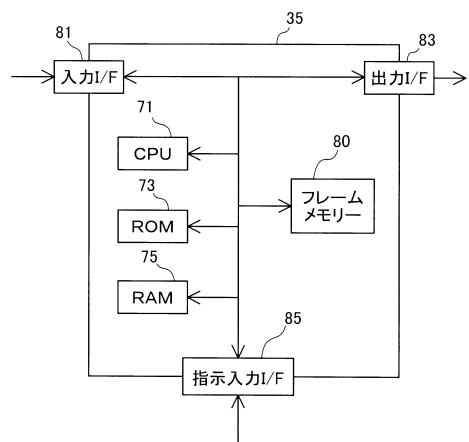

【図2】第5画像処理部35の内部構成を示すブロック図である。

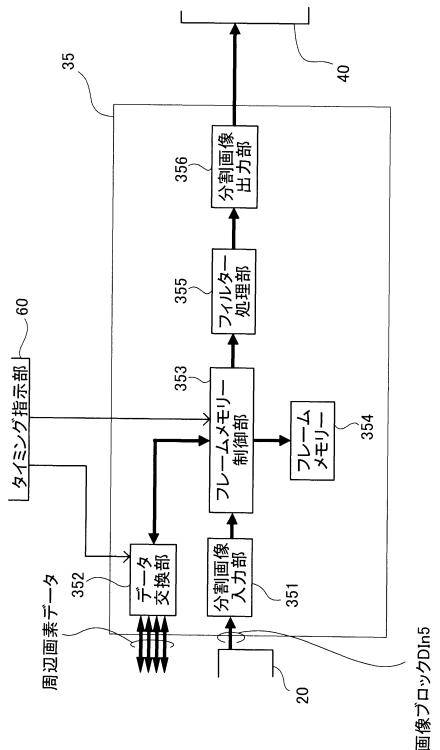

【図3】第5画像処理部35での処理を模式的に示すブロック図である。

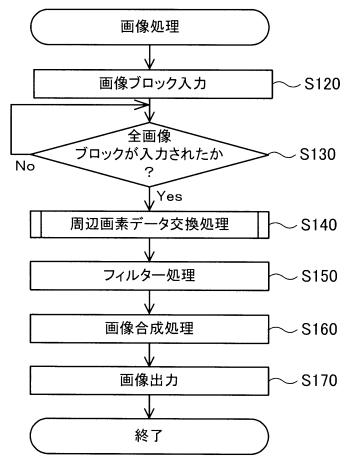

【図4】画像処理装置1における画像処理の流れを示すフローチャートである。

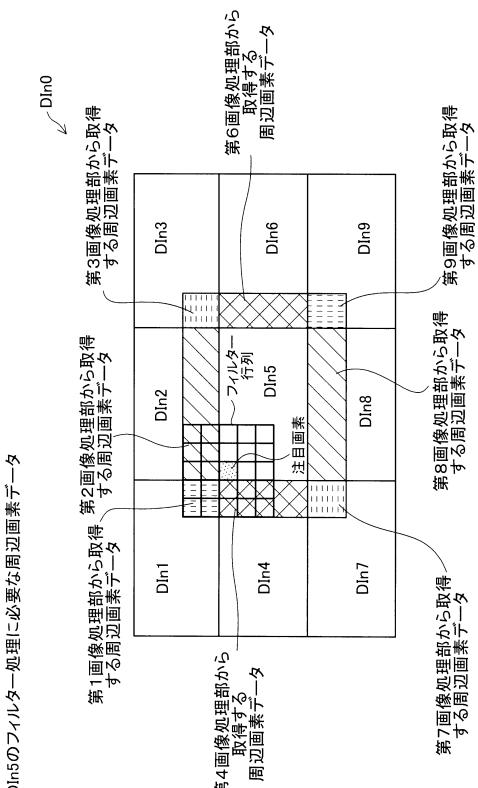

【図5】第5画像処理部35が必要な周辺画素データを説明する説明図である。

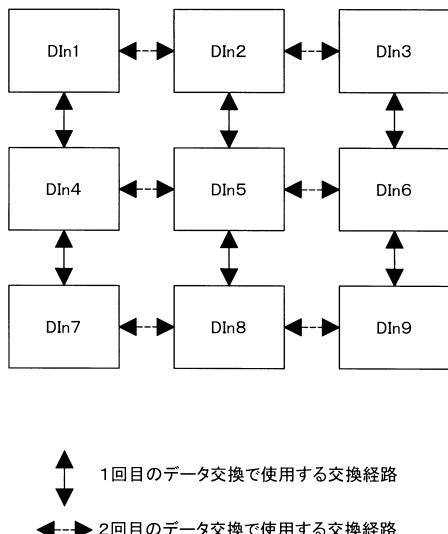

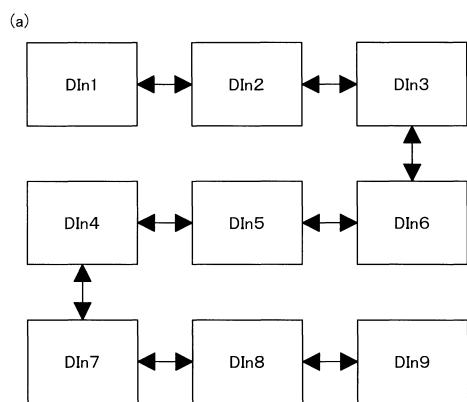

【図6】各画像ブロックDInの周辺画素データの交換経路を説明する説明図である。

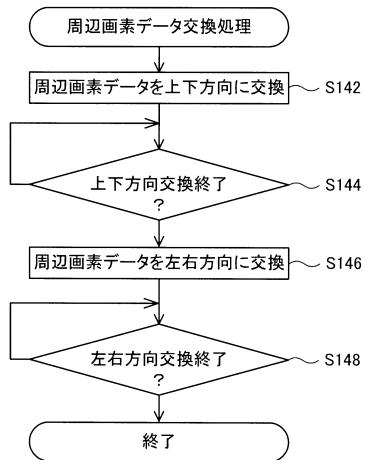

【図7】周辺画素データ交換処理の流れについて説明したフローチャートである。

【図8】周辺画素データの交換の様子を示す説明図である。 50

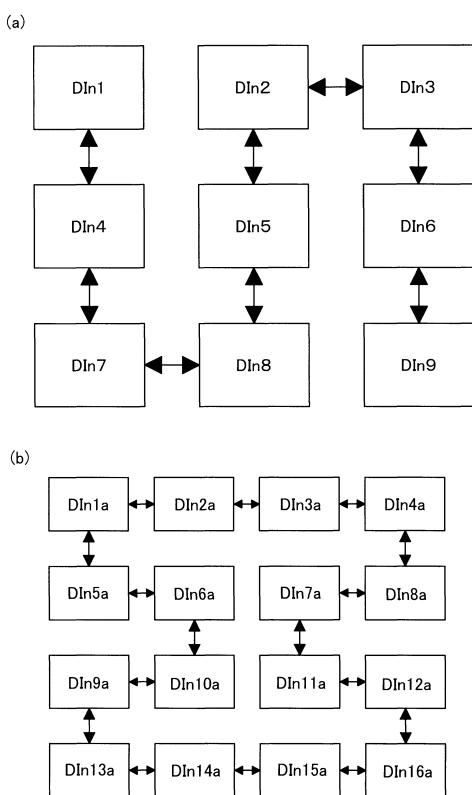

【図9】第2実施例における周辺画素データの交換経路の一例を示した説明図である。

【図10】変形例3の具体例を示す説明図である。

【図11】変形例5の具体例を示す説明図である。

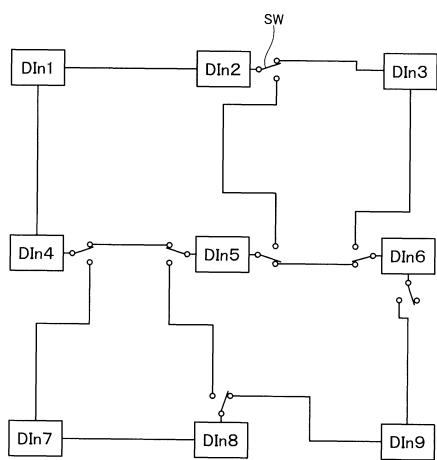

【図12】変形例6の具体例を示す説明図である。

【発明を実施するための形態】

【0017】

本発明の実施の形態を実施例に基づいて説明する。

A. 第1実施例：

(A1) 画像処理装置の構成：

本実施例では、高解像度の液晶プロジェクターに搭載された画像処理装置を例に挙げて説明を行う。図1は、液晶プロジェクターに搭載された、本発明の第1実施例としての画像処理装置1の構成を示す構成図である。液晶プロジェクターは、映像ストレージSt1～St9と外部で接続されており、画像処理装置1が備える画像入力部21～29を介して、画像データを入力する。各映像ストレージSt1～St9には、図1に示すように、1画面分の画像データであるDIn0を3×3(計9つ)に分割した部分画像である画像ブロックDIn1～DIn9が記憶されており、各映像ストレージSt1～St9から、画像処理装置1が備える画像入力部21～29に、DIn1～DIn9が入力される。画像ブロックDIn1～DIn9はデジタルデータとして、各映像ストレージSt1～St9から画像処理装置1に入力される。各映像ストレージSt1～St9は、複数のコンピューターからなるPCクラスターにおける、各コンピューターに備えられている。

【0018】

画像処理装置1は、上述した画像入力部21～29と、画像ブロックDIn1～9を並列に処理する9つの画像処理部である第1画像処理部31～第9画像処理部39と、各画像処理部で並列に処理された画像ブロックに対応した画像データDOut1～9を、1画面の画像データに合成する画像合成部40と、合成された画像データDOut0を、図示しない液晶プロジェクターの液晶パネル駆動部に出力信号として出力する画像出力部50と、タイミング指示部60とを備える。

【0019】

各画像処理部31～39においては、第1画像処理部31ではDIn1を処理し、第2画像処理部32ではDIn2を処理する、と言ったように、各画像処理部の番号と各画像ブロックの番号とが対応して、各画像ブロックDIn1～9を処理する。以下では、主として第5画像処理部35の構成について説明する。

【0020】

図2は、第5画像処理部35の内部構成を示すブロック図である。第5画像処理部35は、デジタル信号処理プロセッサー(DSP)としての機能を有するCPU71、動作プログラムなどを記憶したROM73、ワークエリアとして利用されるRAM75、画像データDIn0を分割した画像データ、つまり画像ブロックDIn5より若干大きな記憶容量を有するフレームメモリー80、映像ストレージSt5から画像ブロックDIn5を受け取る入力インターフェース81、画像合成部40に画像データDOut5を出力する出力インターフェース83、タイミング指示部60からのタイミング信号を受け取る指示入力インターフェース85を備える。CPU71は、第5画像処理部35の全体の動作を統御するが、特にフレームメモリー80に高速にアクセスして、所定の画像処理(フィルター処理)を行なうことができる専用のプロセッサーである。なお、CPU71の機能は、FPGA(Field Programmable Array)や、画像処理専用LSIなどを用いて実現してもよい。

【0021】

次に各画像処理部の機能的な構成について説明する。図3は、第5画像処理部35での処理を模式的に示すブロック図である。第5画像処理部35は、機能的には、分割画像入力部351、データ交換部352、フレームメモリー制御部353、フレームメモリー354、フィルター処理部355、分割画像出力部356を備える。なお、これらの各ブロックの動作は、実際には、CPU71が所定のプログラムを実行することにより実現され

10

20

30

40

50

る。これら各機能部の詳細は後で説明する。

#### 【0022】

##### (A2) 画像処理：

次に、画像処理装置1が行う画像処理について説明する。図4は画像処理装置1における画像処理の流れを示すフローチャートである。画像処理は、映像ストレージSt1～St9(図1参照)から、画像入力部21～29に、画像ブロックDIn1～DIn9が入力されることにより開始される。

#### 【0023】

各画像処理部31～39には、画像入力部21～29から分割画像入力部351～391(図3参照)を介して、それぞれに画像ブロックDIn1～9が入力される(ステップS120)。各画像処理部のフレームメモリー制御部は、入力された画像ブロックDInをフレームメモリーに記憶する。フレームメモリー制御部は、画像ブロックDInのフレームメモリーへの記憶が完了すると、これをタイミング指示部60に通知する。タイミング指示部60は、各画像処理部31～39における画像ブロックDInの蓄積の状況を解析し、全画像ブロックDIn1～9の各画像処理部への入力が完了したと判断した場合(ステップS130: Yes)、各画像処理部のデータ交換部に対してデータ交換の開始を指示する。各データ交換部はタイミング指示部60からデータ交換開始の指示を受信すると、各画像処理部が処理を担当する画像ブロックの処理に必要な周辺画素データを、所定の画像処理部内のデータ交換部と交換をする周辺画素データ交換処理を行う(ステップS140)。周辺画素データ交換処理については、後で詳しく説明する。データ交換は、画像データの受信が順次行なわれていることに鑑み、データ交換可能な画像処理部間でのデータ交換から順次指示するものとしてもよいが、本実施例では、ステップS130で示したように、本発明の理解を容易にするため、データ交換は、第1ないし第9画像処理部31～39の全てが画像データを受け取った後に行うものとした。

#### 【0024】

各画像処理部のデータ交換部によって周辺画素データの交換が終了すると、各フレームメモリー制御部が、フレームメモリーに記憶されている画像ブロックDInと周辺画素データ交換処理によって取得した周辺画素データとを、各フィルター処理部に出力し、各フィルター処理部はそれら2つのデータを用いて、フィルター処理を行う(ステップS150)。フィルター処理部はフィルター処理を終了すると、処理後のデータを各分割画像出力部を介して画像合成部40に出力する。画像合成部40は、各分割画像出力部から受信した画像データDOut1～9を合成し(ステップS160)、画像データDOut0として画像出力部50に出力する。画像出力部50は入力された画像データDOut0を液晶パネル駆動部に出力信号として出力し(ステップS170)する。このような画像処理を、入力されてくる画像ブロックDIn1～9に対して繰り返し行い、画像処理装置1は画像処理を行う。

#### 【0025】

##### (A3) 周辺画素データ交換処理：

次に、上述した周辺画素データ交換処理(図4:ステップS140参照)について説明する。まず、周辺画素データについて説明する。図5は、具体例として、第5画像処理部35が画像ブロックDIn5のフィルター処理を行うために必要な周辺画素データを説明する説明図である。フィルター処理部355は、画像ブロックDIn5において処理の対象となる画素(以下、注目画素とも呼ぶ)を中心に、5行×5列のフィルター行列を用い、注目画素の周囲の2画素ずつの画素データを参照しながら注目画素に対してフィルター処理を行う。具体的には、エッジ強調やノイズ除去のためのラプラシアンフィルターやメディアンフィルター、その他、カルマンフィルター等の画像処理用フィルターによってフィルター処理を行う。このようなフィルター処理を行う場合、画像ブロックDIn5の垂直方向に上と下、水平方向に左と右の計4辺(上辺、下辺、左辺、右辺)から内側に2画素ずつの画素が各々注目画素として処理対象となった場合、フィルター処理として参照する画素は画像ブロックDIn5の周囲の画像ブロックである画像ブロックDIn1～4，

10

20

30

40

50

6～9に含まれる画素にまで及ぶ。よって、第5画像処理部35は、画像ブロックDIn5の周囲の画像ブロックDIn1～4, 6～9から、周辺画素データとして、図5に示す周辺画素データを取得する必要がある。第5画像処理部35のデータ交換部352は、これらの周辺画素データを、周辺画素データ交換処理（図4：ステップS140参照）によって取得する。なお、以後、垂直方向に上方向と下方向とを単に「上、下」と呼び、水平方向に左方向と右方向とを単に「左、右」と呼ぶことがある。

#### 【0026】

次に、各画像処理部が周辺画素データを交換する経路について説明する。図6は、各画像ブロックDInの周辺画素データの交換経路を模式的に説明する説明図である。実際は、各画像処理部のデータ交換部が互いに接続されており周辺画素データを交換するが、理解を容易にするため、各画像処理部が処理を担当する各画像ブロックDIn1～9によって周辺画素データの交換経路について模式的に説明する。図6に示した矢印は、各画像処理部間の周辺画素データの交換経路を示しており、一回のデータ交換で双方向のデータ交換が可能である。また本実施例では、周辺画素データの交換は2回のタイミングで行われ、図6においては、1回目のデータ交換で使用する交換経路を実線の矢印で、2回目のデータ交換で使用する交換経路を破線の矢印で示した。

#### 【0027】

図6に示すように、例えば、画像ブロックDIn5（実際は第5画像処理部35）は、画像データDIn0における画像ブロックDInの位置関係として、上下左右に隣接する画像ブロックDIn2, DIn4, DIn6, DIn8の処理を担当する各画像処理部のデータ交換部と接続されている。そして、それらの画像処理部とだけ、周辺画素データ交換を行う。他の各画像処理部も同様に、画像ブロックの位置関係として、その画像処理部に対応する画像ブロックが、上下左右方向に隣接する画像ブロックに対応する画像処理部とだけ接続されており、周辺画素データの交換を行う。従って、例えば、DIn5（第5画像処理部35）のデータ交換部は4つの通信線で接続され、DIn1は2つ、DIn3は3つのデータ交換用の通信線で接続されている。本実施例においては、各画像処理部31～39のデータ交換部はどれも、4つのデータ交換処理デバイスを備え、図6に示した通信経路の必要数に応じて、データ交換処理デバイスに通信線を接続することで、周辺画素データ交換用の通信経路が構成されている。

#### 【0028】

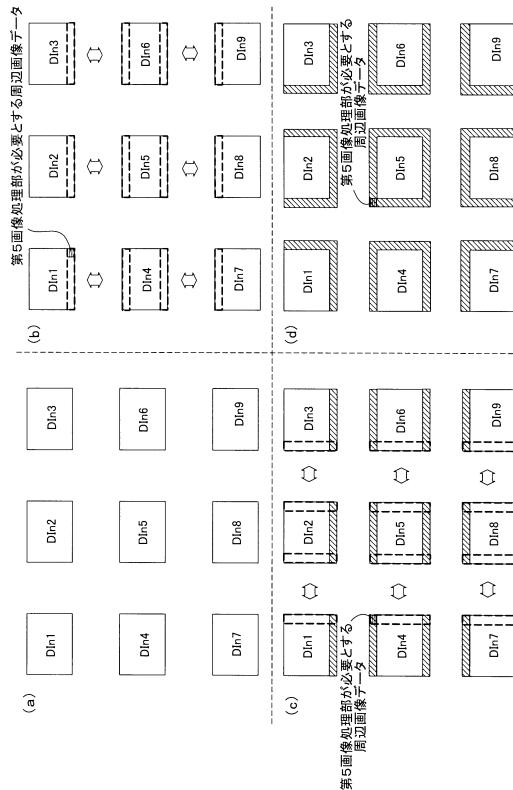

次に、各画像処理部間で行う周辺画素データ交換処理の流れについて説明する。図7は周辺画素データ交換処理の流れについて説明したフローチャートである。周辺画素データ交換処理は、画像処理装置1における画像処理（図4参照）のサブルーチン（図4：ステップS140）として行われる。周辺画素データ交換処理が開始されると、最初に画像ブロックDInの位置関係として、上下方向に隣接する画像ブロックDInの画像処理を担当する各画像処理部同士で周辺画素データの交換を行う（ステップS142）。図8は、周辺画素データの交換の様子を示す説明図である。図8(a)は画像ブロックDIn1～DIn9が各画像処理部に保存されている状態を示している。図8(b)は、ステップS142で説明した、画像ブロックDInの位置関係として、上下方向に隣接する各画像処理部同士で周辺画素データの交換を行っている様子を示す説明図である。図8(b)の点線で囲まれた部分が、上下に互いに隣接する画像ブロックDInの画像処理を担当する各画像処理部間で交換される周辺画素データを示す。図8(b)に示すように、例えば、画像ブロックDIn2の画像処理を担当する第2画像処理部32は、下方向に隣接する画像ブロックDIn5を担当する第5画像処理部35と互いに周辺画素データを交換し、画像ブロックDIn5の画像処理を担当する第5画像処理部35は、上方向および下方向に隣接する、画像ブロックDIn2及び画像ブロックDIn8をそれぞれ担当する第2画像処理部32, 第8画像処理部38と互いに周辺画素データを交換する。

#### 【0029】

この時、例えば、画像ブロックDIn1は、画像ブロックDIn4が画像処理に必要とする周辺画像データをDIn4に送信するとともに、画像ブロックDIn5が画像処理に

10

20

30

40

50

必要な周辺画素データのうち、画像ブロック D I n 1 に含まれる周辺画素データ（図 8 ( b ) の横線ハッチング部分）も同時に、画像ブロック D I n 4 に送信する。画像ブロック D I n 4 に対応する第 4 画像処理部 3 4 のデータ交換部 3 4 1 は、それらの周辺画素データを取得すると一時的に、第 4 画像処理部が備えるフレームメモリー 3 4 4 に記憶する。この場合、画像ブロック D I n 1 が画像ブロック D I n 4 に送信した周辺画素データのうち、画像ブロック D I n 5 が処理に必要とする周辺画素データは、画像ブロック D I n 4 が処理に必要とする周辺画素データの中に含まれる。つまり、説明の便宜上、この二つの周辺画素データは別個のものとして説明したが、実際は、画像ブロック D I n 1 は画像ブロック D I n 4 に対して、画像ブロック D I n 4 が処理に必要な周辺画素データを送信する。

10

### 【 0 0 3 0 】

各画像処理部が上下方向の周辺画素データの交換を完了すると、各データ交換部が、これをタイミング指示部 6 0 に通知する。タイミング指示部 6 0 は、各データ交換部における周辺画素データの交換の状況を解析し、全ての画像処理部において周辺画素データの交換が終了したと判断した場合（ステップ S 1 4 4 : Y e s ）、続いて、画像ブロック D I n の位置関係として、左右方向に隣接する画像ブロック D I n の画像処理を担当する各画像処理部同士で周辺画素データの交換を行う（ステップ S 1 4 6 ）。図 8 ( c ) は、左右方向に隣接する画像ブロック D I n の画像処理を担当する各画像処理部同士で周辺画素データの交換を行っている様子を示す説明図である。図 8 ( c ) の斜線のハッチングを施した部分が、図 8 ( b ) で説明した、上下方向に隣接する画像ブロック同士での周辺画素データの交換により、各画像ブロック D I n が取得した周辺画素データである。また、図 8 ( c ) の各画像ブロック D I n の点線で囲まれた部分が、左右方向に互いに隣接する画像ブロック D I n の画像処理を担当する各画像処理部間で交換される周辺画素データを示す。図 8 ( c ) に示すように、例えば、画像ブロック D I n 4 は、右方向に隣接する画像ブロック D I n 5 と互いに周辺画素データを交換し、画像ブロック D I n 5 は、左右方向に隣接する画像ブロック D I n 4 、画像ブロック D I n 6 とそれぞれ周辺画素データを交換する。

20

### 【 0 0 3 1 】

この時、画像ブロック D I n 4 は、画像ブロック D I n 5 が処理に必要とする画像ブロック D I n 4 に含まれる周辺画素データを送信するとともに、ステップ S 1 4 2 で画像ブロック D I n 4 が画像ブロック D I n 1 から取得した周辺画素データのうち、画像ブロック D I n 5 （第 5 画像処理部 3 5 ）が処理に必要とする周辺画素データ（図 8 ( c ) 参照）も同時に送信する。つまり、画像ブロック D I n 4 （第 4 画像処理部 3 4 ）は、画像ブロック D I n 1 （第 1 画像処理部 3 1 ）から画像ブロック D I n 5 （第 5 画像処理部 3 5 ）に送信される周辺画素データを仲介する。換言すれば、画像ブロック D I n 4 （第 4 画像処理部 3 4 ）は、画像ブロック D I n 5 （第 5 画像処理部 3 5 ）が周辺画素として扱う画素の少なくとも一部のデータを、画像ブロック D I n 1 （第 1 画像処理部 3 1 ）から、画像ブロック D I n 5 （第 5 画像処理部 3 5 ）に向けて仲介する。第 4 画像処理部 3 4 が第 1 画像処理部 3 1 から第 5 画像処理部 3 5 に送信される周辺画素データを仲介することに着目した場合、第 5 画像処理部 3 5 が、特許請求の範囲に記載の「第 1 の部分画像について画像処理を行う際、当該第 1 の部分画像と隣り合った他の部分画像を構成する画素のうち、少なくとも第 1 の部分画像に隣接する領域の画素のデータを取得して、周辺画素のデータとして、画像処理に用いる第 1 の画像処理ユニット」に相当し、第 4 画像処理部 3 4 が、特許請求の範囲に記載の「第 1 の部分画像とは異なる第 2 の部分画像について画像処理を行うと共に、第 1 の画像処理ユニットが周辺画素として扱う画素の少なくとも一部のデータを、第 1 の画像処理ユニットが扱う部分画像に隣り合った部分画像を処理する画像処理ユニットから、第 1 の画像処理ユニットに向けて仲介する第 2 の画像処理ユニット」に相当する。また、他の画像処理部間ににおいても、同様の方法によって周辺画素データの交換が行われる。例えば、画像ブロック D I n 1 が処理に必要とする画像ブロック D I n 5 に含まれる周辺画素データは、ステップ S 1 4 2 の処理で画像ブロック D I n 2 に送

30

40

50

信され、ステップ S 146 の処理で画像ブロック DIn2 から画像ブロック DIn1 に送信される。このようにして、各画像処理部が左右方向の周辺画素データの交換を完了すると、各データ交換部が、これをタイミング指示部 60 に通知する。タイミング指示部 60 は、各データ交換部における周辺画素データの交換の状況を解析し、全ての画像処理部において周辺画素データの交換が終了したと判断した場合（ステップ S 148 : Yes）、周辺画素データ交換処理は終了する。図 8 (d) は、上記図 8 (b), (c) で説明した周辺画素データ交換処理によって交換された周辺画素データを示す説明図である。斜線のハッチングが施された部分が、周辺画素データ交換処理によって、各画像ブロック DIn が取得した周辺画素データである。このように周辺画素データを交換することで、各画像処理部が画像処理に必要な周辺画素データを交換することが可能である。

10

### 【0032】

以上説明したように、第 1 実施例における周辺画素データの交換方法を用いることで、上下方向（図 7：ステップ S 142）と左右方向（図 7：ステップ S 146）の合計 2 回の周辺画素データの交換で、各画像処理部が画像処理に必要な周辺画素データの交換が可能であり、周辺画素データの交換を高速に行うことが可能である。また、図 6 からわかるように、各画像処理部は、全ての画像処理部と接続されている必要はなく、画像ブロック DIn の位置関係として、上下左右に隣接する画像ブロック DIn の画像処理を担当する画像処理部と接続されればよい。つまり、1 つの画像処理部は最大で 4 つの画像処理部と接続されればよい。従って、各画像処理部が、隣接する全ての画像処理部と、各自に周辺画素データ交換用のラインで接続されていて、それぞれ直接に通信をして周辺画素データを交換する場合と比べて、画像処理装置の構造上、トランシーバー数、配線数、デバイスのピン数等を減少させることができる。なお、特許請求の範囲との対応関係としては、画像ブロック DIn1 ~ 9 が、特許請求の範囲に記載の部分画像に相当し、各画像処理部が、特許請求の範囲に記載の画像処理ユニットに相当し、画像合成部 40 が、特許請求の範囲に記載の画像出力ユニットに相当する。

20

### 【0033】

また、第 1 実施例では、画像データ DIn0 を  $3 \times 3$  に分割した例で説明したが、より多くの分割数、例えば、 $4 \times 4$  や、 $10 \times 10$ 、 $16 \times 9$  などに分割しても、第 1 実施例と同様の効果を得ることができる。つまり、画像ブロック DIn の位置関係として、各画像ブロック DIn の処理を担当する各画像処理部が、上下左右に隣接する画像ブロック DIn の画像処理を担当する画像処理部と接続されれば、1 つの画像処理部は最大で 4 つの画像処理部との接続によって、上下方向と左右方向の合計 2 回の周辺画素データの交換で、各画像処理部が画像処理に必要な周辺画素データの交換が可能であり、周辺画素データの交換を高速に行うことができる。

30

### 【0034】

本実施例では、複数の画像処理部のうち、他の画像処理部が処理に必要な周辺画素データを仲介する画像処理部と、仲介しない画像処理部とが存在するが、全ての画像処理部が仲介を行う機能を備え、処理を担当する画像ブロック DIn の画像データ DIn0 における配置関係によって、必要に応じ仲介処理を行うとしてもよい。この場合、複数の画像処理部は、少なくとも、「第 1 の部分画像について画像処理を行う際、当該第 1 の部分画像と隣り合った他の部分画像を構成する画素のうち、少なくとも第 1 の部分画像に隣接する領域の画素のデータを取得して、前記周辺画素のデータとして、画像処理に用いる第 1 の画像処理ユニット」と、「第 1 の部分画像とは異なる第 2 の部分画像について画像処理を行うと共に、第 1 の画像処理ユニットが周辺画素として扱う画素の少なくとも一部のデータを、第 1 の画像処理ユニットが扱う部分画像に隣り合った部分画像を処理する画像処理ユニットから、前記第 1 の画像処理ユニットに向けて仲介する第 2 の画像処理ユニット」とを含んでいればよい。

40

### 【0035】

#### B . 第 2 実施例 :

次に第 2 実施例について説明する。第 1 実施例と第 2 実施例との違いは、各画像プロッ

50

ク D I n の周辺画素データの交換経路である。またそれに伴って、周辺画素データの交換の流れも第 1 実施例と第 2 実施例では異なる。第 2 実施例における周辺画素データの交換経路は、画像ブロック D I n の位置関係において、画像ブロック D I n 1 ~ 9 間を、1 経路で、かつ、同じ経路を 2 度通ることなく結ぶように交換経路を構成する。換言すれば、画像ブロック D I n 1 ~ 9 間を、いわゆる「一筆書き (an Eulerian path (閉路の場合) 又は a traversable figure (始点と終点が異なる場合) )」の要領で経路構成する。その一例を図 9 に示す。図 9 ( a ) は、第 2 実施例における、各画像ブロック D I n の周辺画素データの交換経路の一例を示した説明図である。画像ブロック ( 実際は画像処理部 ) 同士は、交換経路で結ばれている。この交換経路は、画像ブロック ( 実際は画像処理部 ) 同士が互いに直接に周辺画素データを取得する経路である。なお、この交換経路が特許請求の範囲に記載のデータ取得経路に相当する。図 9 ( a ) に示すように、周辺画素の交換経路は、画像ブロック D I n 1 ~ 9 間を、1 つの経路で、かつ、同じ画像ブロックを 2 度通ることなく結ぶように構成されている。このような交換経路を用いて、各画像処理部は周辺画素データを交換する。なお、図 9 ( a ) に示した矢印は、各画像処理部間の周辺画素データの交換経路を示しており、一回のデータ交換で双方向のデータ交換が可能である。なお、一筆書きが可能である条件として、「頂点から出ている線の数が奇数本である頂点の数が、0 個 (閉路) か 2 個 (始点と終点が異なる) の場合」に一筆書きが可能である。これを本実施例に置き換えると、「画像処理部に接続されている周辺画素データ交換経路の数が奇数個である画像処理部の数が、0 個、若しくは 2 個の場合」に、このような一筆書きの経路構成が可能である。換言すれば、「各データ交換部のうち、奇数個の他のデータ交換部と直接にデータ交換をするデータ交換部の数が 0 個または 2 個の場合」に、一筆書きの経路構成が可能である。このように、各画像処理ユニットとデータ取得経路とから構成され、全ての画像処理ユニットを 1 度ずつ通る経路が形成される。なお、このような一筆書きが可能な一連の周辺画素データの交換経路が、特許請求の範囲に記載のデータ通信経路に相当する。

#### 【 0 0 3 6 】

次に、周辺画素データの交換の方法について説明する。例えば、画像ブロック D I n 5 の画像処理に必要な、画像ブロック D I n 1 に含まれる周辺画素データ ( 図 5 参照 ) を交換する場合、D I n 1 D I n 2 D I n 3 D I n 6 D I n 5 の交換経路で、D I n 5 に周辺画素データが送信される。また、上述したように、データ交換は一回のデータ交換で双方向のデータ交換が可能である。例えば、最も周辺画素データの交換経路として遠い D I n 1 と D I n 4 ( 又は、D I n 6 と D I n 9 ) とは、5 回のタイミングでデータ交換を行うことによって周辺画素データの交換が可能である。

#### 【 0 0 3 7 】

図 9 ( b ) は、D I n 1 と D I n 4 がデータ交換するために必要なデータ交換のタイミングと、その交換の向きについて説明した説明図である。説明の便宜上、D I n 1 から D I n 4 までの周辺画素データの交換経路を直線状に表現した。実線の矢印は、D I n 4 が必要な D I n 1 に含まれる周辺画素データを、D I n 1 から順に D I n 2 、D I n 3 、D I n 6 、D I n 5 を経由して D I n 4 に送信されている様子を示している。一方、破線の矢印は、D I n 1 が必要な D I n 4 に含まれる周辺画素データを、D I n 4 から順に D I n 5 、D I n 6 、D I n 3 、D I n 2 を経由して D I n 1 に送信されている様子を示している。

#### 【 0 0 3 8 】

矢印の上に付した数字はデータ交換が行われるタイミングを示している。つまり、1 回目のデータ交換のタイミングで、D I n 1 D I n 2 のデータ交換と、D I n 4 D I n 5 のデータ交換が行われる。2 回目のデータ交換のタイミングで、D I n 2 D I n 3 のデータ交換と、D I n 5 D I n 6 のデータ交換が行われる。このように周辺画素データの交換を行うことによって、D I n 1 と D I n 4 とは 5 回のデータ交換のタイミングで、周辺画素データの交換を行うことができる。また、この 5 回のデータ交換のタイミング内で、例えば、D I n 2 と D I n 5 や、D I n 3 と D I n 5 などが、周辺画素データの交換

を、他の画像ブロック D I n を経由して行うことが可能である。勿論、直接に周辺画素データを交換する D I n 1 と D I n 2 や、 D I n 5 と D I n 4 などは、この 5 回のデータ交換のタイミング内で直接に周辺画素データの交換が可能である。

#### 【 0 0 3 9 】

他の各画像処理部が必要とする周辺画素データについても、同様に、図 9 ( a ) に示した交換経路上を介し、他の画像処理部を経由して、その周辺画像データを必要とする画像処理部に送信される。また図 9 ( a ) に示した交換経路は、一筆書きで言えば、「始点と終点とが異なる場合」に相当する。この場合、各画像処理部は、双方向に周辺画素データを交換して、各画像処理部が必要な周辺画素データを取得する。なお、交換経路を、一筆書きで言う「閉路」で構成する事も可能であり、この場合は、交換経路はループ状となるので、各画像処理部が交換経路上を一方向のみに周辺画素データを送信し、各画像処理部が処理に必要な周辺画素データが当該画像処理部を通過する際に、その周辺画素データを取得（または参照）するとしてもよい。その具体的な経路については、後の変形例で説明する。

#### 【 0 0 4 0 】

以上説明したように、第 2 実施例における周辺画素データの交換方法を用いることで、各画像処理部は、全ての画像処理部と接続されている必要はなく、1 つ乃至 2 つの画像処理部と接続されればよい。従って、第 1 実施例と比較してさらに、画像処理装置の構造上、トランシーバー数、配線数、デバイスのピン数等を減少させることができる。

#### 【 0 0 4 1 】

##### C . 変形例 :

なお、この発明は上記の実施例や実施形態に限られるものではなく、その要旨を逸脱しない範囲において種々の態様において実施することが可能であり、例えば次のような変形も可能である。

#### 【 0 0 4 2 】

##### ( C 1 ) 変形例 1 :

上記実施例では、画像データ D I n 0 を  $3 \times 3$  に分割したが、 $4 \times 4$  や、 $4 \times 3$  など、 $M \times N$  ( $M, N$  は 2 以上の正の整数) に分割するとしても同様の効果を得ることができる。分割数を多くした場合、各画像処理部が処理をする画素数が減るので、画像処理の処理速度が、上記実施例と比較してさらに高速となる。

#### 【 0 0 4 3 】

##### ( C 2 ) 変形例 2 :

上記第 1 実施例では、周辺画素データ交換処理は上下方向（垂直方向）を先に行い、後に左右方向（水平方向）を行ったが、変形例 2 として、先に左右方向（水平方向）を行い、後に上下方向（垂直方向）を行ってもよい。このようにしても、上記第 1 実施例と同様の効果を得ることが可能である。

#### 【 0 0 4 4 】

##### ( C 3 ) 変形例 3 :

上記実施例 2 では、図 9 に示した周辺画素データの交換経路によって周辺画素データを交換したが、これに限ることなく、D I n 0 を、 $3 \times 3$  や、それ以外の分割数に分割することが可能である。例えば図 10 に示した交換経路を構成して周辺画素データを交換することが可能である。図 10 ( a ) および図 10 ( b ) に示した交換経路は、各画像ブロック D I n 間を、1 つの経路で、かつ、同じ経路を 2 度通ることなく結ぶように構成されている。図 10 ( b ) は、上記で説明した「閉路」の経路構成である。このように構成した交換経路によって周辺画素データを交換する場合、上述したように、各データ交換部は、周辺画素データを経路上の一方向のみに送信すればよい。このような経路構成としても、上記第 2 実施例と同様の効果を得ることが可能である。

#### 【 0 0 4 5 】

##### ( C 4 ) 変形例 4 :

上記実施例では、各画像処理部に部分画像データが蓄積された後にタイミング指示部が

10

20

30

40

50

データ交換開始の指示を各画像処理部に出力していたが、本変形例では、タイミング指示部 60 は、各画像処理部 31 ~ 39 における画像データの蓄積の状況を解析し、第 1 ないし第 9 画像処理部 31 ~ 39 のうち、データ交換が可能になった処理部に対してデータ交換の開始を指示する。このようにデータ交換をすると、上記実施例と比較して、さらにデータ交換を高速に行うことが可能である。

#### 【0046】

##### (C5) 変形例 5 :

上記実施例では、映像ストレージ St1 ~ St9 から、画像ブロック DI n1 ~ 9 が画像入力部 21 ~ 29 を介してプロジェクターに入力されたが、変形例 5 においては、プロジェクターに画像データ DI n0 が入力され、画像処理装置 1a において画像データ DI n0 を画像ブロック DI n1 ~ DI n9 に分割する。10 図 11 は、変形例 5 における画像処理装置 1a の構成を説明する説明図である。第 1 実施例と同じ機能を備える機能部には同じ符号を付している。図 11 に示すように、画像データ DI n0 を記憶している映像ストレージ St0 から画像入力部 20a に画像データ DI n0 が入力され、画像処理装置 1a が備える画像分割部 90 が画像データ DI n0 を画像ブロック DI n1 ~ DI n9 に分割し、各画像処理部 31 ~ 39 に送信する。以降の処理は第 1 実施例と同様の処理である。このような構成にしても上記実施例と同様の効果が得られる。

#### 【0047】

##### (C6) 変形例 6 :

上記実施例では、データ交換部は、他の画像処理部と周辺画素データのやり取りをするデータ交換処理デバイスを複数備えることによって、他の複数の画像処理部とデータの交換を行っていたが、変形例 6 として、データ交換の方向を切り換える切り換えスイッチ SW を備えることにより、データ交換処理デバイスの数を上記実施例より少なくする構成としてもよい。20

#### 【0048】

図 12 は、変形例 6 の具体例を説明する説明図である。図 12 に示すように、画像処理装置は、上記第 1 実施例と同様に、各画像処理部は、上下左右に隣接している画像処理部と接続されている。さらに、変形例 6 の特徴として、接続経路上に、必要に応じて、切り換えスイッチ SW を備える。図 12 においては、切り換えスイッチ SW は、画像処理部の外部に設ける構成であるが、画像処理部の内部に設ける構成としてもよい。30 図 12 の具体例の場合は、各画像処理部間で周辺画素データを互いに交換する場合は、データ交換をするタイミングで、必要に応じて切り換えスイッチ SW を切り換えることにより、最大で 4 つの画像処理部との通信が可能となり、第 1 実施例と実質的に同等のデータ交換が可能である。このような構成にすることで、画像処理部が 4 つのデータ交換処理デバイスを備える必要がなく、データ交換処理デバイスの数を減らすことができる。

#### 【0049】

また、各画像処理部との接続経路を第 2 実施例と同様に所謂一筆書きの構成とし、2つ以上の画像処理部とデータ交換を行う画像処理部が、切り換えスイッチ SW を備え、必要に応じて、データ交換のタイミングで切り換えスイッチ SW を切り換えるとしてもよい。40 このようにすることで、データ交換処理デバイスの数を上記第 2 実施例と比べて減らすことが可能である。

#### 【符号の説明】

##### 【0050】

- 1 ... 画像処理装置

- 10 ... 画像入力部

- 20 ... 画像分割部

- 31 ~ 39 ... 第 1 ~ 第 9 画像処理部

- 40 ... 画像合成部

- 50 ... 画像出力部

- 60 ... タイミング指示部

7 1 ... C P U

8 0 ... フレームメモリー

8 1 ... 入力インタフェース

8 3 ... 出力インタフェース

8 5 ... 指示入力インタフェース

3 4 1 ... データ交換部

3 4 4 ... フレームメモリー

3 5 1 ... 分割画像入力部

3 5 2 ... データ交換部

3 5 3 ... フレームメモリー制御部

3 5 4 ... フレームメモリー

3 5 5 ... フィルター処理部

3 5 6 ... 分割画像出力部

D In 0 ... 画像データ

D In 1 ~ 9 ... 画像ブロック

D Out 0 ... 画像データ

S t 1 ~ S t 9 ... 映像ストレージ

S W ... 切り替えスイッチ

P C 1 ~ P C 9 ... コンピューター

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

---

フロントページの続き

(56)参考文献 特開2006-5524(JP,A)

特開昭62-208158(JP,A)

特開昭60-140456(JP,A)

(58)調査した分野(Int.Cl., DB名)

G06T 1/00