(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2012-0037520

(43) 공개일자 2012년04월20일

(51) 국제특허분류(Int. Cl.)

*H01L 29/78* (2006.01) *H01L 27/092* (2006.01)

*H01L 21/8238* (2006.01)

(21) 출원번호 10-2010-0098119

(22) 출원일자 2010년10월08일

심사청구일자 없음

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

(72) 발명자

김대익

경기도 용인시 기흥읍 농서리 남자 기숙사 월계수

동 610호

오용철

경기도 수원시 영통구 청명로 100, 청명마을

건영APT 424동 1301호 (영통동)

(뒷면에 계속)

(74) 대리인

권혁수, 송윤호, 오세준

전체 청구항 수 : 총 30 항

(54) 발명의 명칭 수직 채널 트랜지스터를 구비하는 반도체 장치 및 그 제조 방법

### (57) 요 약

수직 채널 트랜지스터를 구비하는 반도체 장치 및 그 제조 방법이 제공된다. 이 장치는 제 1 및 제 2 전계효과 트랜지스터들을 포함하고, 제 1 전계효과 트랜지스터의 채널 영역은 제 2 전계효과 트랜지스터의 소오스/드레인 전극을 구성하고, 제 2 전계효과 트랜지스터의 채널 영역은 제 1 전계효과 트랜지스터의 소오스/드레인 전극을 구성한다.

대 표 도 - 도1

(72) 발명자

황유상

경기도 수원시 영통구 영통로200번길 156, 1001동

504호 (망포동, 방죽마을영통뜨란채)

조영승

경기도 용인시 처인구 고림로110번길 1-4, 서울주

택 C동 402호 (고림동)

정현우

서울특별시 중랑구 상봉로16가길 25 (망우동)

## 특허청구의 범위

### 청구항 1

제 1 전계효과 트랜지스터 및 제 2 전계효과 트랜지스터를 포함하되,

상기 제 1 전계효과 트랜지스터의 채널 영역은 상기 제 2 전계효과 트랜지스터의 소오스 전극을 구성하고,

상기 제 2 전계효과 트랜지스터의 채널 영역은 상기 제 1 전계효과 트랜지스터의 드레인 전극을 구성하되,

상기 제 1 및 제 2 전계효과 트랜지스터들의 채널 영역들은 직접 접촉하는 것을 반도체 장치.

### 청구항 2

청구항 1에 있어서,

상기 반도체 장치는 차례로 배열된 제 1, 제 2, 제 3 및 제 4 영역들을 포함하는 활성 패턴을 포함하고, 상기 제 1 및 제 3 영역들은 같은 도전형이고, 상기 제 2 및 제 4 영역들은 같은 도전형이고, 상기 제 1 영역과 상기 제 2 영역은 서로 다른 도전형이되,

상기 제 1, 제 2 및 제 3 영역들은 차례로 상기 제 1 전계효과 트랜지스터의 소오스 전극, 채널 영역 및 드레인 전극으로 사용되고,

상기 제 2, 제 3 및 제 4 영역들은 차례로 상기 제 2 전계효과 트랜지스터의 소오스 전극, 채널 영역 및 드레인 전극으로 사용되는 반도체 장치.

### 청구항 3

청구항 2에 있어서,

상기 제 1 영역에 전기적으로 연결된 메모리 요소를 더 포함하는 반도체 장치.

### 청구항 4

청구항 2에 있어서,

상기 제 2 영역은 상기 제 1 및 제 3 영역들을 통해서만 그것의 외부에 배치된 도전성 패턴에 전기적으로 연결되고,

상기 제 3 영역은 상기 활성 패턴의 일 측에 배치되는 하부 배선에 전기적으로 연결되는 반도체 장치.

### 청구항 5

청구항 2에 있어서,

상기 제 1 전계효과트랜지스터는 상기 제 2 영역의 측면에 배치되는 상부 게이트 패턴을 포함하고, 상기 제 2 전계효과트랜지스터는 상기 제 3 영역의 측면에 배치되는 적어도 하나의 하부 게이트 패턴을 포함하되,

상기 하부 게이트 패턴은 상기 제 4 영역과 전기적으로 오믹하게(Ohmicly) 연결되는 반도체 장치.

### 청구항 6

청구항 5에 있어서,

상기 제 1 전계효과트랜지스터는 상기 상부 및 하부 게이트 패턴들의 측벽들과 상기 활성 패턴의 측벽 사이에 배치되는 게이트 절연막 구조체를 포함하되,

상기 게이트 절연막 구조체는 수평적으로 연장되어 상기 상부 게이트 패턴의 바닥면을 덮는 반도체 장치.

### 청구항 7

청구항 2에 있어서,

상기 제 2 전계효과트랜지스터는 상기 활성 패턴의 측면에 배치되는 제 1 및 제 2 하부 게이트 패턴들을 포함하고,

상기 제 1 전계효과트랜지스터는 상기 제 1 하부 게이트 패턴의 상부에 배치되는 상부 게이트 패턴을 포함하는 반도체 장치.

### 청구항 8

청구항 7에 있어서,

상기 제 2 하부 게이트 패턴의 상부면은 상기 상부 게이트 패턴의 바닥면보다 상기 제 4 영역에 가까운 반도체 장치.

### 청구항 9

청구항 7에 있어서,

상기 제 2 하부 게이트 패턴의 상부면은 상기 제 1 하부 게이트 패턴의 상부면보다 상기 제 1 영역에 가깝게 형성되어, 상기 제 2 하부 게이트 패턴과 상기 제 2 영역의 측벽들은 서로 마주보는 반도체 장치.

### 청구항 10

청구항 2에 있어서,

상기 제 1 및 제 2 전계효과트랜지스터들은 각각 상기 활성 패턴의 둘레에 배치되는 하나의 상부 게이트 패턴 및 하나의 하부 게이트 패턴을 포함하되,

상기 하부 게이트 패턴은 상기 활성 패턴의 제 1 측면에 인접하게 배치되고,

상기 상부 게이트 패턴은, 상기 제 1 측면을 마주보는, 상기 활성 패턴의 제 2 측면에 인접하게 배치되고,

상기 하부 게이트 패턴의 상부면은 상기 상부 게이트 패턴의 하부면보다 상기 제 1 영역에 가깝게 형성되어, 상기 하부 게이트 패턴과 상기 제 2 영역의 측벽들은 서로 마주보는 반도체 장치.

### 청구항 11

청구항 2에 있어서,

상기 하부 게이트 패턴은 상기 제 4 영역과 같은 도전형의 반도체 물질 또는 상기 제 4 영역에 오직하게 연결되는 도전성 물질을 포함하는 반도체 장치.

### 청구항 12

청구항 1에 있어서,

상기 제 1 및 제 2 전계효과 트랜지스터들 중의 하나는 n-채널 모스 전계효과트랜지스터이고, 상기 제 1 및 제 2 전계효과 트랜지스터들 중의 다른 하나는 p-채널 모스 전계효과트랜지스터인 반도체 장치.

### 청구항 13

기판의 상부면에 수직한 장축을 가지면서 상기 기판 상에 2차원적으로 배열되는 활성 패턴들; 및

상기 기판의 상부면에 수직한 장축을 가지면서 상기 활성 패턴들 사이에 배치되는 게이트 패턴들을 포함하되,

상기 활성 패턴들 각각은

상기 기판과 다른 도전형의 제 1 영역;

상기 기판과 같은 도전형이면서 상기 제 1 영역과 상기 기판 사이에 배치되는 제 2 영역; 및

상기 기판과 다른 도전형이면서 상기 제 2 영역과 상기 기판 사이에 배치되는 제 3 영역을 포함하고,

상기 게이트 패턴들은

상기 제 3 영역과 함께 모스 커패시터를 구성하는 하부 게이트 패턴들; 및

상기 제 2 영역과 모스 커패시터를 구성하는 상부 게이트 패턴들을 포함하는 반도체 장치.

#### 청구항 14

청구항 13에 있어서,

상기 기판의 상부면에 평행한 장축을 가지면서 상기 활성 패턴들 사이에서 상기 활성 패턴들을 가로지르는 하부 배선들; 및

상기 기판의 상부면에 평행한 장축을 가지면서 상기 게이트 패턴들의 상부에서 상기 하부 배선들을 가로지르는 상부 배선들을 더 포함하되,

상기 상부 게이트 패턴들 각각은 상기 상부 배선들 중의 하나에 전기적으로 연결되고,

상기 하부 게이트 패턴들은 상기 기판에 전기적으로 연결되는 반도체 장치.

#### 청구항 15

청구항 14에 있어서,

상기 활성 패턴들은 복수의 활성 그룹들을 구성하고, 상기 활성 그룹들 각각은, 인접하는 한 쌍의 상기 하부 배선들 사이에 배치되는, 상기 활성 패턴들 중의 일부로 구성되되,

상기 인접하는 한 쌍의 하부 배선들 중의 하나는, 상기 활성 그룹들 중에서 선택된 하나를 구성하는, 상기 활성 패턴들 중의 홀수번째 것들에 접속하고,

상기 인접하는 한 쌍의 하부 배선들 중의 다른 하나는, 상기 선택된 활성 그룹을 구성하는, 상기 활성 패턴들 중의 짝수번째 것들에 접속하는 반도체 장치.

#### 청구항 16

청구항 13에 있어서,

상기 활성 패턴들 중의 일부는 제 1 및 제 2 그룹들을 구성하고,

상기 제 1 및 제 2 그룹들 각각은, 동일한 y 좌표 및 다른 x 좌표들을 갖는, 복수의 상기 활성 패턴들로 구성되고,

상기 상부 게이트 패턴들은 상기 제 1 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 짝수번째 것들 그리고 상기 제 2 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 홀수번째 것들에 국소적으로 배치되는 반도체 장치.

#### 청구항 17

청구항 16에 있어서,

상기 하부 게이트 패턴들은 상기 제 1 및 제 2 그룹들 각각을 구성하는 상기 활성 패턴들 사이의 공간들 모두에 배치되는 반도체 장치.

#### 청구항 18

청구항 16에 있어서,

상기 하부 게이트 패턴들은 상기 제 1 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 홀수번째 것들 그리고 상기 제 2 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 짝수번째 것들에 국소적으로 배치되는 반도체 장치.

#### 청구항 19

청구항 16에 있어서,

상기 제 1 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 홀수번째 것들 그리고 상기 제 2 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 짝수번째 것들에 배치되는, 상기 하부 게이트 패턴들의 상부면은 상

기 상부 게이트 패턴들의 상부면보다 상기 제 1 영역에 인접하는 반도체 장치.

#### 청구항 20

청구항 16에 있어서,

상기 제 1, 제 2 및 제 3 영역들 그리고 상기 상부 게이트 패턴은 제 1 전계효과트랜지스터를 구성하고,

상기 제 2 및 제 3 영역들, 상기 기판 그리고 상기 하부 게이트 패턴은 제 2 전계효과트랜지스터를 구성하되,

상기 제 2 영역은 상기 제 1 및 제 2 전계효과트랜지스터들의 채널 영역 및 소오스 전극으로 각각 사용되고,

상기 제 3 영역들은 상기 제 1 및 제 2 전계효과트랜지스터들의 드레인 전극 및 채널 영역으로 각각 사용되는 반도체 장치.

#### 청구항 21

기판을 패터닝하여 제 1 트렌치를 형성하는 단계;

상기 제 1 트렌치 내에 상기 기판에 전기적으로 연결되는 하부 게이트막을 형성하는 단계;

상기 기판 및 상기 하부 게이트막을 패터닝하여 상기 제 1 트렌치를 가로지르는 제 2 트렌치를 형성함으로써, 활성 패턴 및 하부 게이트 패턴을 형성하는 단계; 및

상기 제 2 트렌치 내에 상기 활성 패턴의 하부 영역에 접속하는 하부 배선을 형성하는 단계를 포함하는 수직한 채널 영역을 갖는 반도체 장치의 제조 방법.

#### 청구항 22

청구항 21에 있어서,

상기 제 1 트렌치 내에 상부 게이트막을 형성하는 단계;

상기 상부 게이트막이 형성된 결과물 상에 상부 도전막을 형성하는 단계; 및

상기 상부 도전막을 패터닝하여 상기 하부 배선을 가로지르는 상부 배선을 형성하는 단계를 더 포함하되,

상기 상부 도전막은 상기 하부 배선을 형성한 이후에 형성되는 반도체 장치의 제조 방법.

#### 청구항 23

청구항 22에 있어서,

상기 상부 게이트막은, 상기 제 2 트렌치를 형성하기 전에, 상기 제 1 트렌치 내에 형성되는 것을 특징으로 하는 반도체 장치의 제조 방법.

#### 청구항 24

청구항 22에 있어서,

상기 상부 게이트막은, 상기 하부 배선을 형성한 후에, 상기 제 1 트렌치 내에 형성되는 것을 특징으로 하는 반도체 장치의 제조 방법.

#### 청구항 25

청구항 22에 있어서,

상기 상부 배선을 형성하기 전에, 상기 제 1 트렌치 내에 플러그 절연막을 형성하는 단계를 더 포함하되,

상기 플러그 절연막은, 상기 배선들 각각과 그것의 아래에 위치하는 상기 하부 게이트 패턴들 중의 일부 사이에 국소적으로 형성되는 반도체 장치의 제조 방법.

#### 청구항 26

청구항 25에 있어서,

상기 플러그 절연막은 상기 하부 배선을 형성한 후에 형성되는 반도체 장치의 제조 방법.

### 청구항 27

청구항 25에 있어서,

상기 플러그 절연막은 상기 상부 게이트막을 형성하기 전에 형성되는 반도체 장치의 제조 방법.

### 청구항 28

청구항 25에 있어서,

상기 플러그 절연막을 형성하는 단계는

상기 상부 게이트막을 패터닝하여 상기 제 1 트렌치의 일부 영역을 노출시키는 캡 영역을 형성하는 단계; 및

상기 캡 영역을 채우는 상기 플러그 절연막을 형성하는 단계를 포함하는 반도체 장치의 제조 방법.

### 청구항 29

청구항 25에 있어서,

상기 플러그 절연막은 상기 제 2 트렌치를 형성하기 전에 상기 하부 게이트막이 형성된 상기 제 1 트렌치를 채우도록 형성되는 반도체 장치의 제조 방법.

### 청구항 30

청구항 21에 있어서,

상기 하부 배선을 형성하기 전에, 상기 활성 패턴의 하부 영역에 하부 불순물 영역을 형성하는 단계를 더 포함하되,

상기 하부 게이트 패턴의 상부면은 적어도 상기 하부 불순물 영역의 가장 낮은 상부면보다 높게 형성되는 반도체 장치의 제조 방법.

## 명세서

### 기술 분야

[0001]

본 발명은 반도체 장치 및 그 제조 방법에 관한 것으로, 보다 구체적으로는 수직 채널 트랜지스터를 구비하는 반도체 장치 및 그 제조 방법에 관한 것이다.

### 배경 기술

[0002]

반도체 장치의 집적도를 증가시키기 위해, 반도체 장치의 제작자들은 패턴들의 선폭을 감소시키기 위해 노력해 왔다. 하지만, 차세대 반도체 장치를 위한 미세 패턴 형성 기술은 새로운 그리고 고비용의 노광 기술을 도입함으로써 달성될 수 있다.

[0003]

대안으로, 반도체 장치의 제작자들은 반도체 장치를 구성하는 기본 소자의 점유 면적을 감소시킬 수 있는 방안을 찾기 위해 노력하고 있다. 예를 들면, 채널 영역의 상부 및 하부에 각각 소오스 전극 및 드레인 전극을 형성하는 수직 채널 트랜지스터가 최근 활발하게 연구되고 있다. 상기 수직 채널 트랜지스터의 경우, 소오스 및 드레인 전극들을 위한 면적이 불필요하기 때문에, 채널 영역의 양 측에 소오스 및 드레인 전극들이 배치되는 종래의 2차원적 모오스 전계효과트랜지스터에 비해 반도체 장치의 집적도는 크게 증가될 수 있다. 물론, 이러한 수직 채널 트랜지스터가 차세대의 미세 패턴 형성 기술을 통해 제조될 경우, 이를 포함하는 반도체 장치의 집적도는 더욱 증가될 수 있을 것이다.

[0004]

하지만, 수직 채널 트랜지스터의 경우, 종래의 2차원 트랜지스터에서와는 다른 기술적 어려움들이 존재하며, 따라서 수직 채널 트랜지스터를 이용한 반도체 장치가 양산 단계에 들어서기 위해서는 이러한 기술적 어려움들을 해결할 수 있는 새로운 기술이 필요하다.

### 발명의 내용

## 해결하려는 과제

[0005] 본 발명이 이루고자 하는 일 기술적 과제는 수직 채널 트랜지스터의 플로팅 바디(floating body) 현상을 해결할 수 있는 반도체 장치를 제공하는 데 있다.

[0006] 본 발명이 이루고자 하는 다른 기술적 과제는 수직 채널 트랜지스터의 플로팅 바디 현상을 해결할 수 있는 반도체 장치의 제조 방법을 제공하는 데 있다.

## 과제의 해결 수단

[0007] 수직 채널 트랜지스터를 구비하는 반도체 장치가 제공된다. 이 장치는 제 1 전계효과 트랜지스터 및 제 2 전계효과 트랜지스터를 포함하고, 상기 제 1 전계효과 트랜지스터의 채널 영역은 상기 제 2 전계효과 트랜지스터의 소오스 전극을 구성하고, 상기 제 2 전계효과 트랜지스터의 채널 영역은 상기 제 1 전계효과 트랜지스터의 드레인 전극을 구성한다. 상기 제 1 및 제 2 전계효과 트랜지스터들의 채널 영역들은 직접 접촉한다.

[0008] 일부 실시예들에 따르면, 상기 반도체 장치는 차례로 배열된 제 1, 제 2, 제 3 및 제 4 영역들을 포함하는 활성 패턴을 포함하고, 상기 제 1 및 제 3 영역들은 같은 도전형이고, 상기 제 2 및 제 4 영역들은 같은 도전형이고, 상기 제 1 영역과 상기 제 2 영역은 서로 다른 도전형일 수 있다. 이에 더하여, 상기 제 1, 제 2 및 제 3 영역들은 차례로 상기 제 1 전계효과 트랜지스터의 소오스 전극, 채널 영역 및 드레인 전극으로 사용되고, 상기 제 2, 제 3 및 제 4 영역들은 차례로 상기 제 2 전계효과 트랜지스터의 소오스 전극, 채널 영역 및 드레인 전극으로 사용될 수 있다.

[0009] 일부 실시예들에 따르면, 상기 제 2 영역은 상기 제 1 및 제 3 영역들을 통해서만 그것의 외부에 배치된 도전성 패턴에 전기적으로 연결되고, 상기 제 3 영역은 상기 활성 패턴의 일 측에 배치되는 하부 배선에 전기적으로 연결될 수 있다.

[0010] 일부 실시예들에 따르면, 상기 제 1 전계효과트랜지스터는 상기 제 2 영역의 측면에 배치되는 상부 게이트 패턴을 포함하고, 상기 제 2 전계효과트랜지스터는 상기 제 3 영역의 측면에 배치되는 적어도 하나의 하부 게이트 패턴을 포함할 수 있다. 이 경우, 상기 하부 게이트 패턴은 상기 제 4 영역과 전기적으로 오믹하게(Ohmically) 연결될 수 있다.

[0011] 일부 실시예들에 따르면, 상기 제 2 전계효과트랜지스터는 상기 활성 패턴의 측면에 배치되는 제 1 및 제 2 하부 게이트 패턴들을 포함하고, 상기 제 1 전계효과트랜지스터는 상기 제 1 하부 게이트 패턴의 상부에 배치되는 상부 게이트 패턴을 포함할 수 있다. 상기 제 2 하부 게이트 패턴의 상부면은 상기 상부 게이트 패턴의 바닥면 보다 상기 제 4 영역에 가까울 수 있다. 하지만, 상기 제 2 하부 게이트 패턴의 상부면은 상기 제 1 하부 게이트 패턴의 상부면보다 상기 제 1 영역에 가깝게 형성될 수도 있다. 이 경우, 상기 제 2 하부 게이트 패턴과 상기 제 2 영역의 측벽들은 서로 마주볼 수 있다.

[0012] 일부 실시예들에 따르면, 상기 제 1 및 제 2 전계효과트랜지스터들은 각각 상기 활성 패턴의 둘레에 배치되는 하나의 상부 게이트 패턴 및 하나의 하부 게이트 패턴을 포함할 수 있다. 이때, 상기 하부 게이트 패턴은 상기 활성 패턴의 제 1 측면에 인접하게 배치되고, 상기 상부 게이트 패턴은, 상기 제 1 측면을 마주보는, 상기 활성 패턴의 제 2 측면에 인접하게 배치되고, 상기 하부 게이트 패턴의 상부면은 상기 상부 게이트 패턴의 하부면보다 상기 제 1 영역에 가깝게 형성될 수 있다.

[0013] 본 발명의 다른 측면에 따르면, 상기 반도체 장치는 기판의 상부면에 수직한 장축을 가지면서 상기 기판 상에 2 차원적으로 배열되는 활성 패턴들 및 상기 기판의 상부면에 수직한 장축을 가지면서 상기 활성 패턴들 사이에 배치되는 게이트 패턴들을 포함할 수 있다. 이때, 상기 활성 패턴들 각각은 상기 기판과 다른 도전형의 제 1 영역, 상기 기판과 같은 도전형이면서 상기 제 1 영역과 상기 기판 사이에 배치되는 제 2 영역, 및 상기 기판과 다른 도전형이면서 상기 제 2 영역과 상기 기판 사이에 배치되는 제 3 영역을 포함할 수 있다. 이에 더하여, 상기 게이트 패턴들은 상기 제 3 영역과 함께 모스 커패시터를 구성하는 하부 게이트 패턴들 및 상기 제 2 영역과 모스 커패시터를 구성하는 상부 게이트 패턴들을 포함할 수 있다.

[0014] 일부 실시예들에 따르면, 상기 활성 패턴들 사이에는, 상기 기판의 상부면에 평행한 장축을 가지면서 상기 활성 패턴들을 가로지르는 하부 배선들이 더 배치되고, 상기 게이트 패턴들의 상부에는, 상기 기판의 상부면에 평행한 장축을 가지면서 상기 하부 배선들을 가로지르는 상부 배선들이 더 배치될 수 있다. 이때, 상기 상부 게이트 패턴들 각각은 상기 상부 배선들 중의 하나에 전기적으로 연결되고, 상기 하부 게이트 패턴들은 상기 기판에 전

기적으로 연결될 수 있다.

[0015] 일부 실시예들에 따르면, 상기 활성 패턴들은 복수의 활성 그룹들을 구성하고, 상기 활성 그룹들 각각은, 인접하는 한 쌍의 상기 하부 배선들 사이에 배치되는, 상기 활성 패턴들 중의 일부로 구성될 수 있다. 이에 더하여, 상기 인접하는 한 쌍의 하부 배선들 중의 하나는, 상기 활성 그룹들 중에서 선택된 하나를 구성하는, 상기 활성 패턴들 중의 홀수번째 것들에 접속하고, 상기 인접하는 한 쌍의 하부 배선들 중의 다른 하나는, 상기 선택된 활성 그룹을 구성하는, 상기 활성 패턴들 중의 짹수번째 것들에 접속할 수 있다.

[0016] 일부 실시예들에 따르면, 상기 활성 패턴들 중의 일부는 제 1 및 제 2 그룹들을 구성하고, 상기 제 1 및 제 2 그룹들 각각은, 동일한 y 좌표 및 다른 x 좌표들을 갖는, 복수의 상기 활성 패턴들로 구성될 수 있다. 이 경우, 상기 상부 게이트 패턴들은 상기 제 1 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 짹수번째 것들 그리고 상기 제 2 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 홀수번째 것들에 국소적으로 배치될 수 있다.

[0017] 이에 더하여, 일부 실시예들에 따르면, 상기 하부 게이트 패턴들은 상기 제 1 및 제 2 그룹들 각각을 구성하는 상기 활성 패턴들 사이의 공간들 모두에 배치될 수 있다. 하지만, 다른 실시예들에 따르면, 상기 하부 게이트 패턴들은 상기 제 1 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 홀수번째 것들 그리고 상기 제 2 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 짹수번째 것들에 국소적으로 배치될 수 있다.

[0018] 한편, 일부 실시예들에 따르면, 상기 제 1 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 홀수번째 것들 그리고 상기 제 2 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 짹수번째 것들에 배치되는, 상기 하부 게이트 패턴들의 상부면은 상기 상부 게이트 패턴들의 상부면보다 상기 제 1 영역에 인접할 수 있다.

[0019] 일부 실시예들에 따르면, 상기 제 1, 제 2 및 제 3 영역들 그리고 상기 상부 게이트 패턴은 제 1 전계효과트랜지스터를 구성하고, 상기 제 2 및 제 3 영역들, 상기 기판 그리고 상기 하부 게이트 패턴은 제 2 전계효과트랜지스터를 구성할 수 있다. 이 경우, 상기 제 2 영역은 상기 제 1 및 제 2 전계효과트랜지스터들의 채널 영역 및 소오스 전극으로 각각 사용되고, 상기 제 3 영역들은 상기 제 1 및 제 2 전계효과트랜지스터들의 드레인 전극 및 채널 영역으로 각각 사용될 수 있다.

[0020] 수직 채널 트랜지스터를 구비하는 반도체 장치의 제조 방법이 제공된다. 이 방법은 기판을 패터닝하여 제 1 트렌치를 형성하고, 상기 제 1 트렌치 내에 상기 기판에 전기적으로 연결되는 하부 게이트막을 형성한 후, 상기 기판 및 상기 하부 게이트막을 패터닝하여 상기 제 1 트렌치를 가로지르는 제 2 트렌치를 형성하는 단계를 포함할 수 있다. 이에 따라, 활성 패턴 및 하부 게이트 패턴이 형성된다. 이후, 상기 제 2 트렌치 내에 상기 활성 패턴(ACT)의 하부 영역에 접속하는 하부 배선을 형성한다.

[0021] 한편, 상기 제 1 트렌치 내에 상부 게이트막을 형성하는 단계, 상기 상부 게이트막이 형성된 결과물 상에 상부 도전막을 형성하는 단계, 및 상기 상부 도전막을 패터닝하여 상기 하부 배선을 가로지르는 상부 배선을 형성하는 단계가 더 실시될 수 있다. 일부 실시예들에 따르면, 상기 상부 도전막은 상기 하부 배선을 형성한 이후에 형성될 수 있다. 예를 들면, 상기 상부 게이트막은, 상기 제 2 트렌치를 형성하기 전에 형성되거나 상기 하부 배선을 형성한 후에, 상기 제 1 트렌치 내에 형성될 수 있다.

### 발명의 효과

[0022] 본 발명의 실시예들에 따르면, 서로 다른 도전형의 제 1 및 제 2 전계효과 트랜지스터들이 수직적으로 적층된다. 이때, 상기 제 1 및 제 2 전계효과 트랜지스터들의 채널 영역들은 서로 직접 접촉하도록 형성된다. 즉, 상기 제 1 전계효과 트랜지스터의 채널 영역은 상기 제 2 전계효과 트랜지스터의 소오스/드레인 전극으로 사용되고, 상기 제 2 전계효과 트랜지스터의 채널 영역은 상기 제 1 전계효과 트랜지스터의 소오스/드레인 전극으로 사용된다. 이에 따라, 제 1 또는 제 2 전계효과 트랜지스터의 채널 영역들에서의 플로팅 바디 현상은 예방될 수 있다.

### 도면의 간단한 설명

[0023] 도 1은 본 발명의 실시예들에 따른 반도체 장치의 일 측면을 도식적으로 설명하기 위한 회로도이다.

도 2a 내지 도 2c는 본 발명의 실시예들에 따른 반도체 장치들을 보다 구체적으로 설명하기 위한 도면들이다.

도 3은 본 발명의 실시예들에 따른 반도체 장치의 일 측면을 도시하는 도식도(schematic diagram)이다.

도 4는 본 발명의 제 1 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 순서도이다.

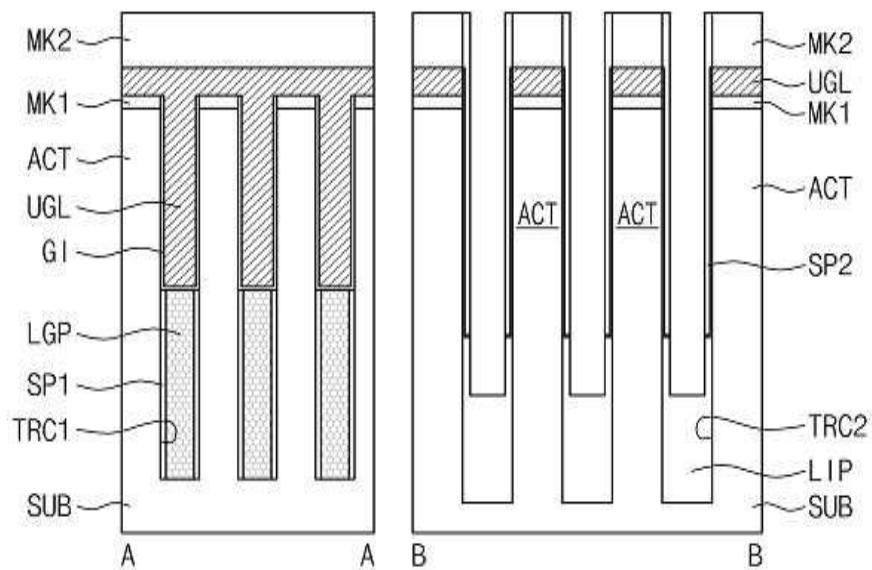

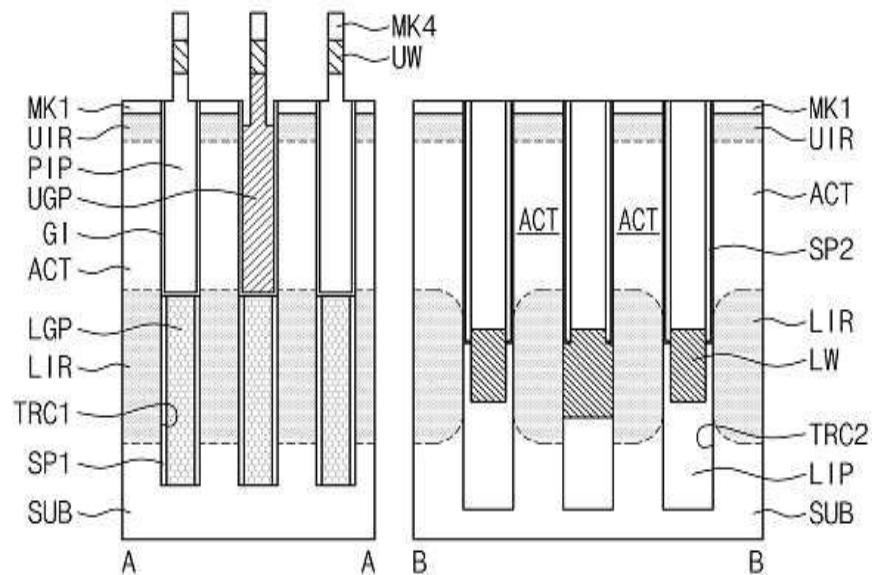

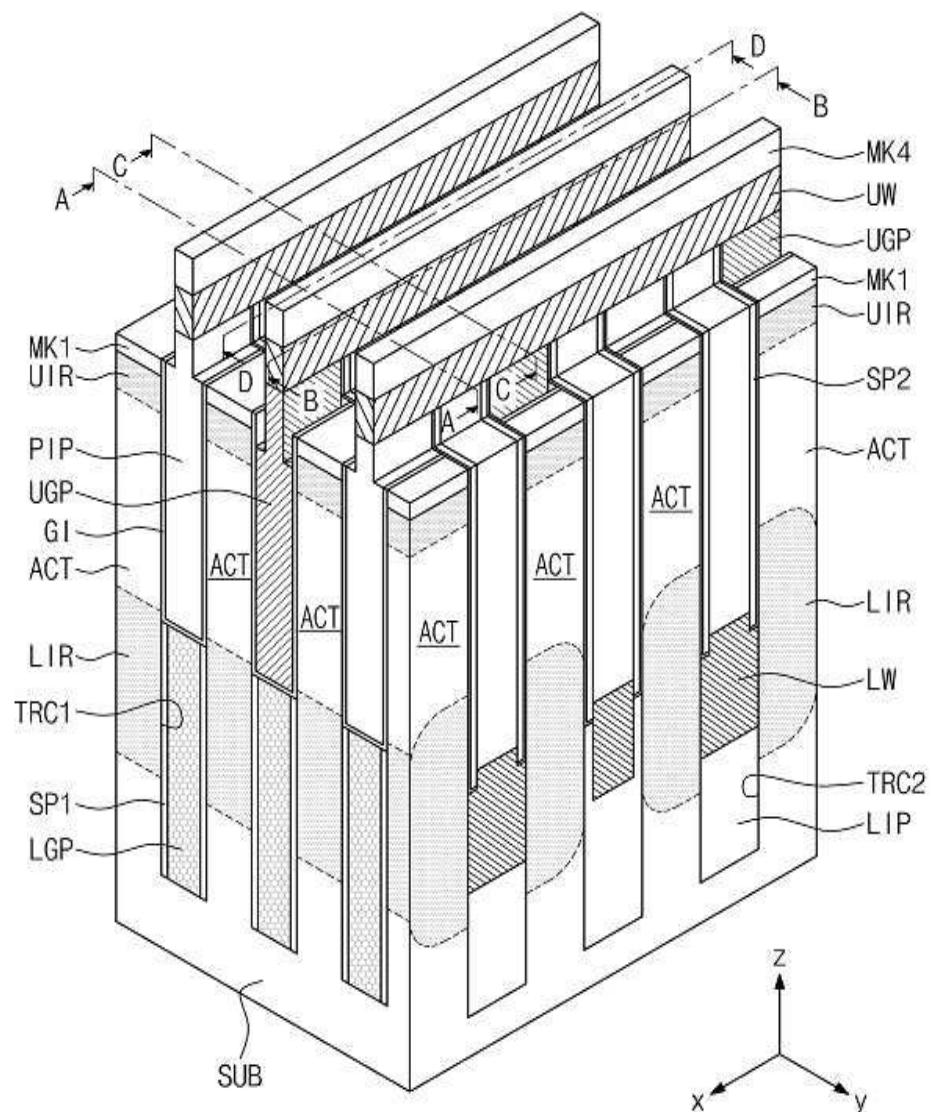

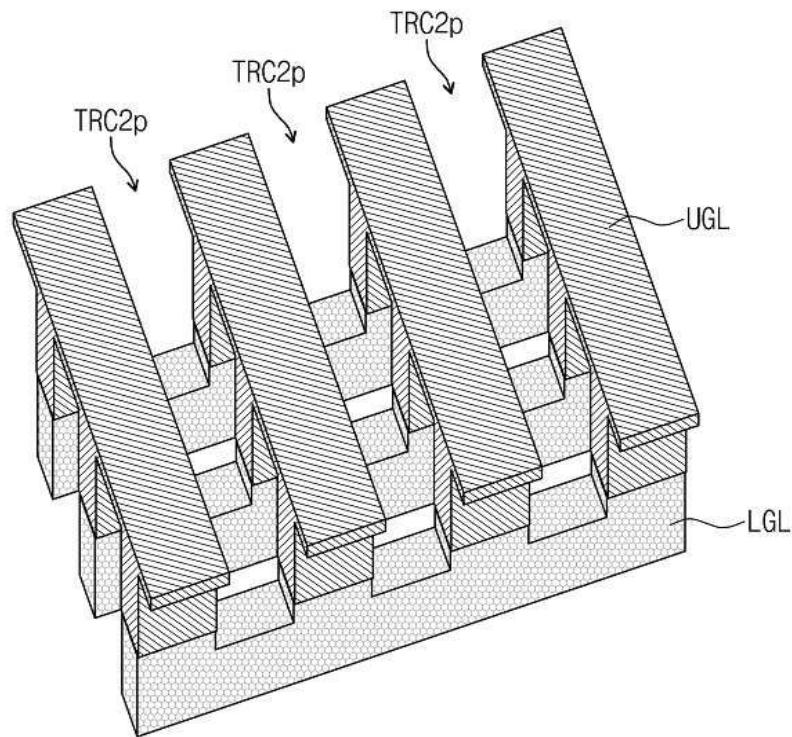

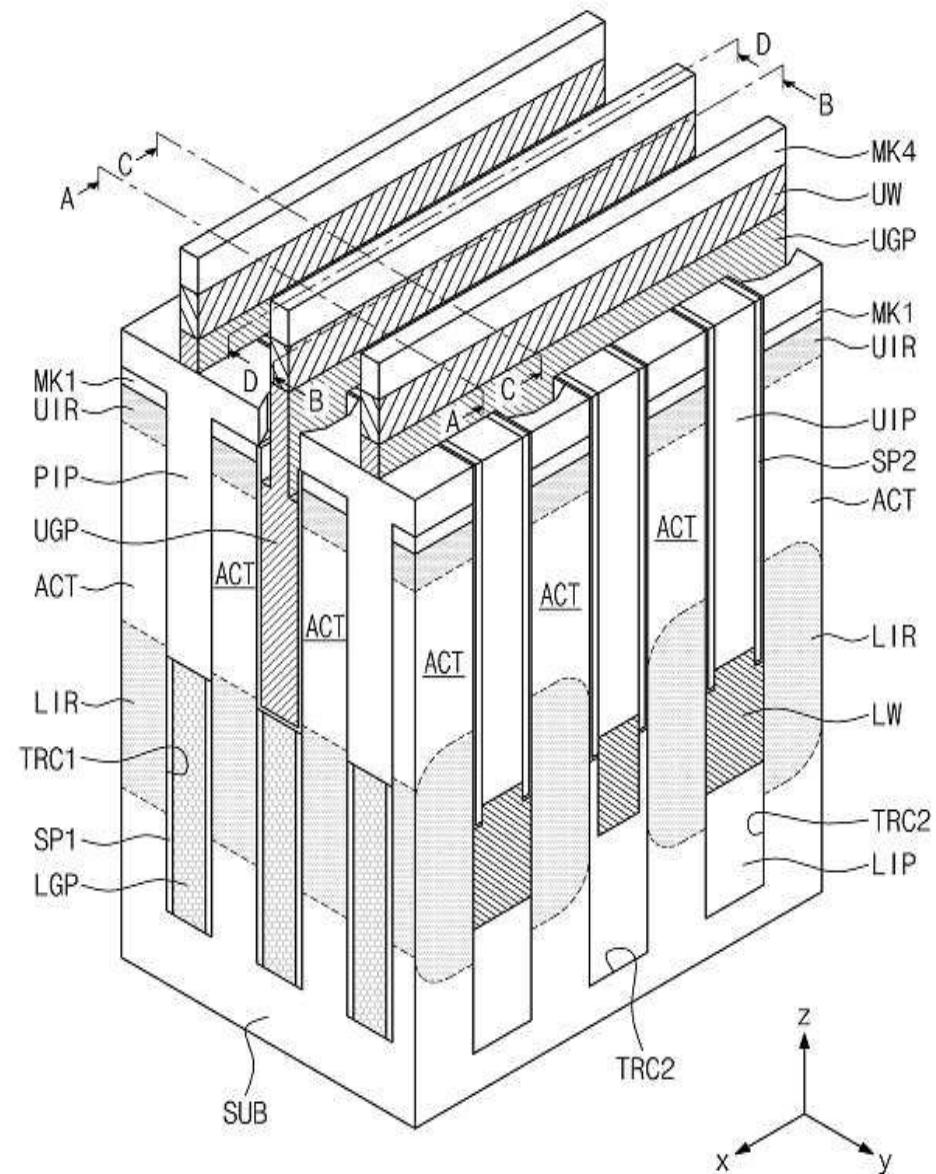

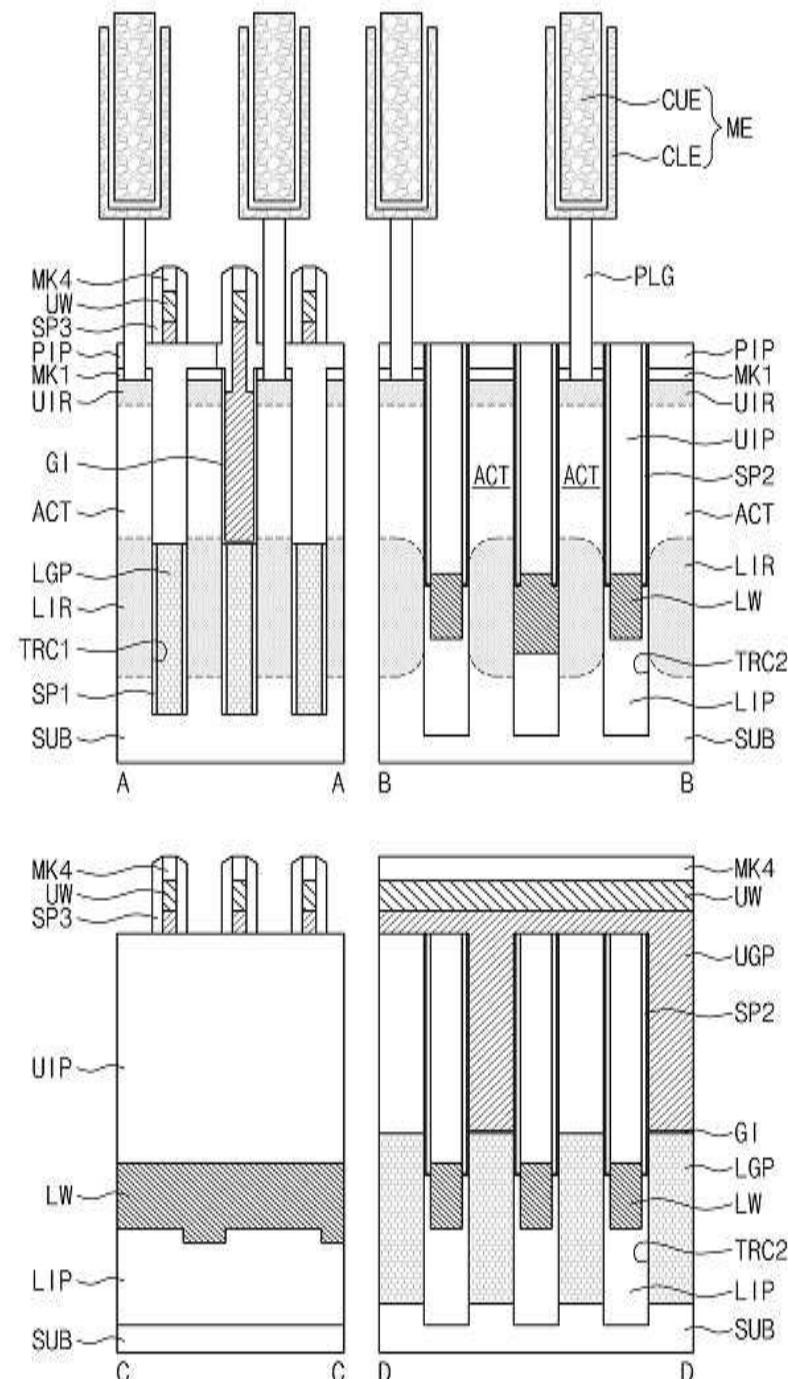

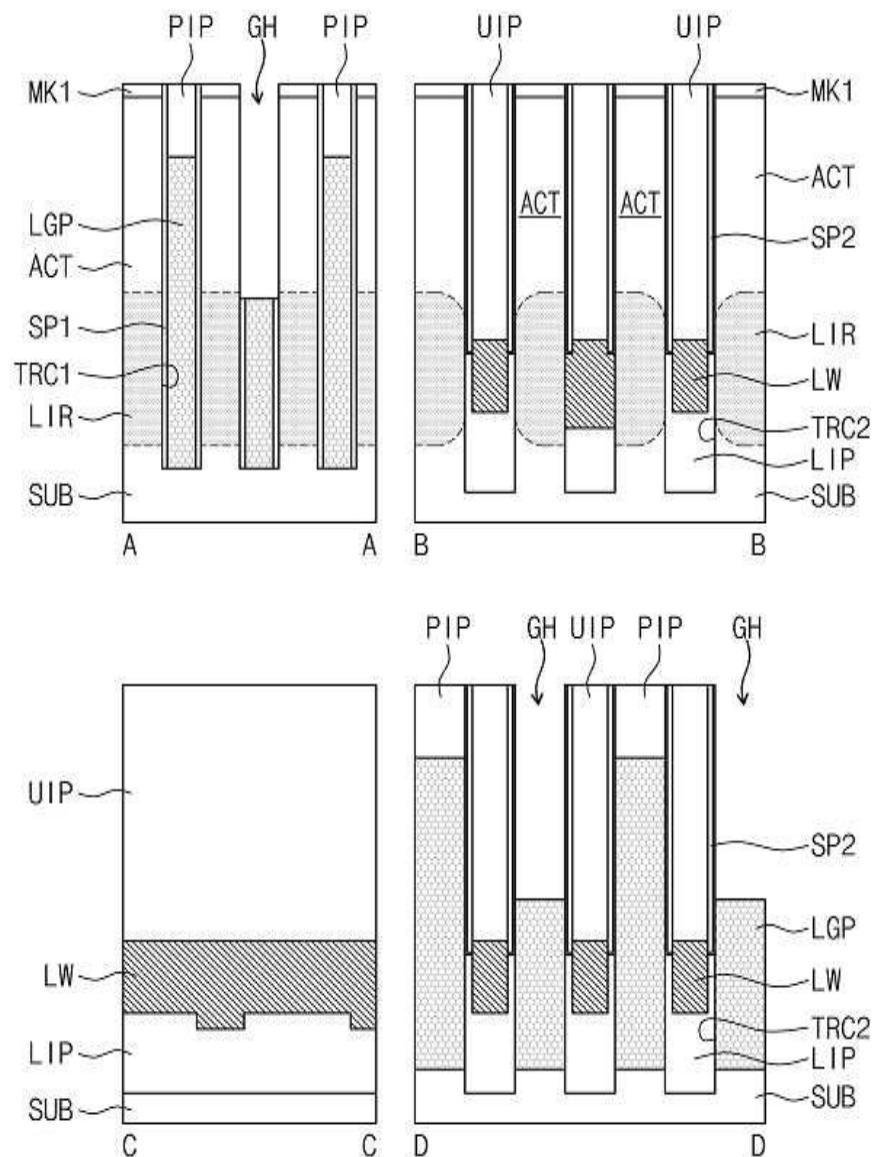

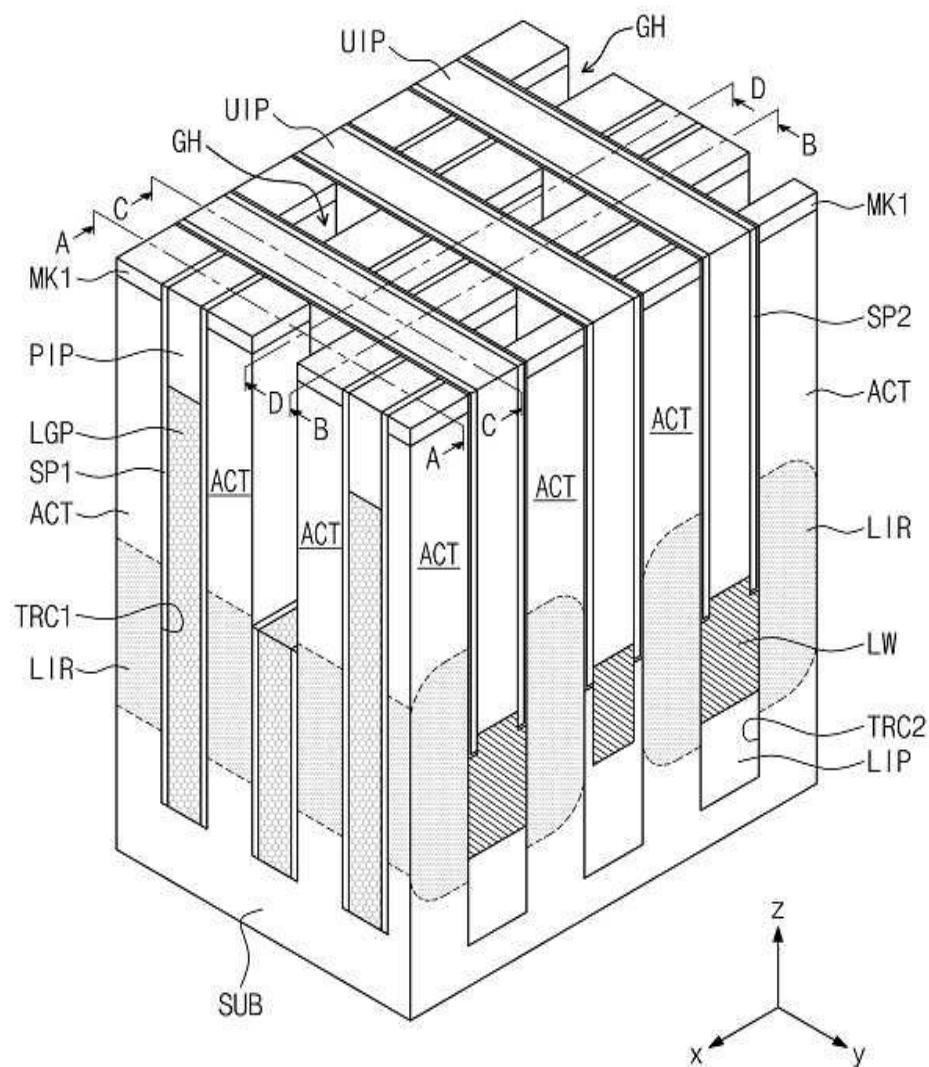

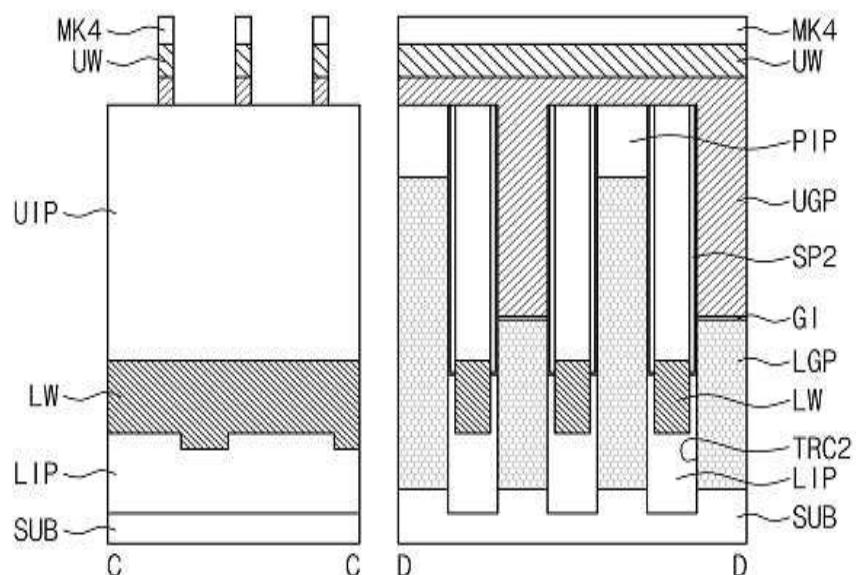

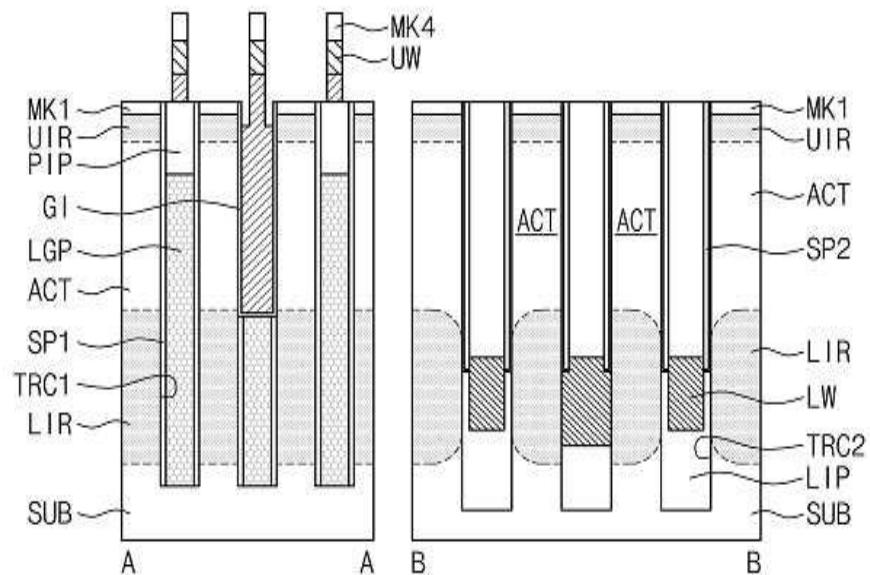

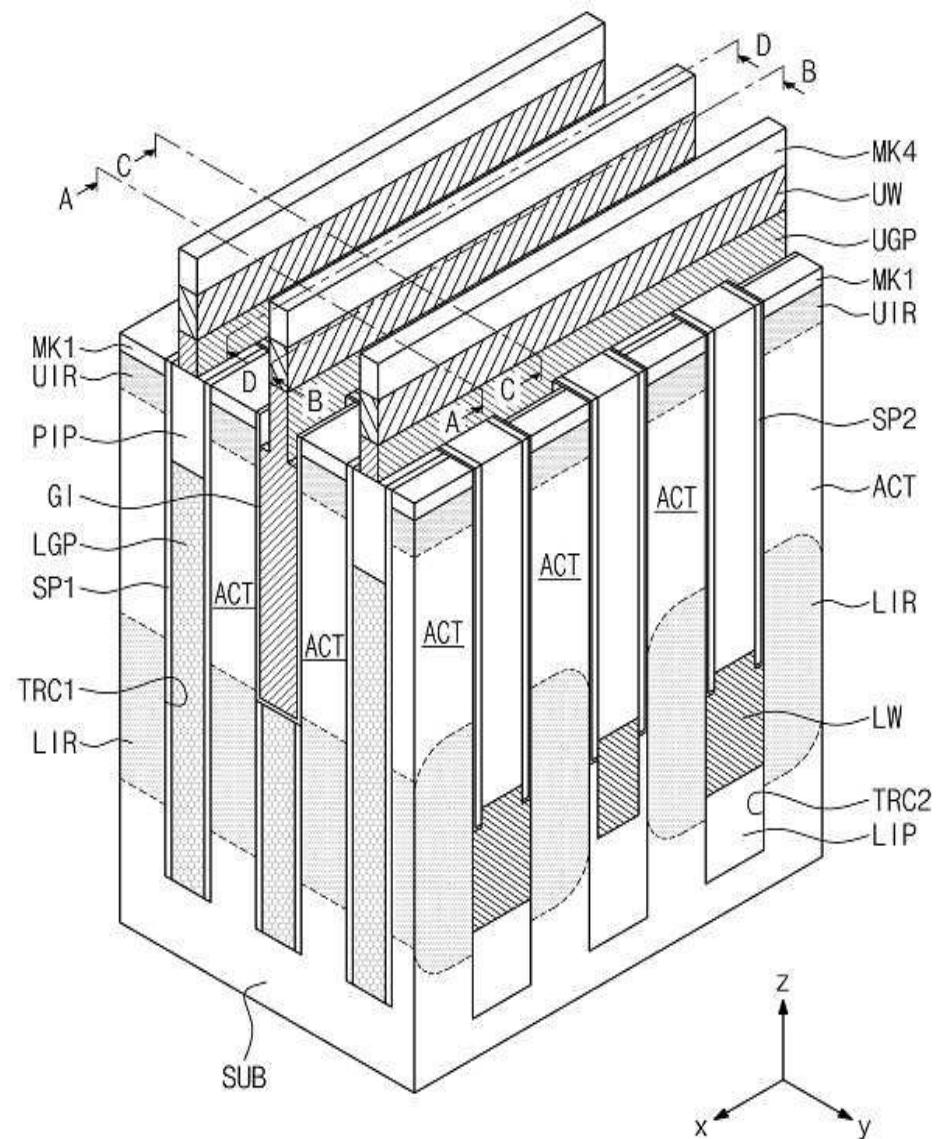

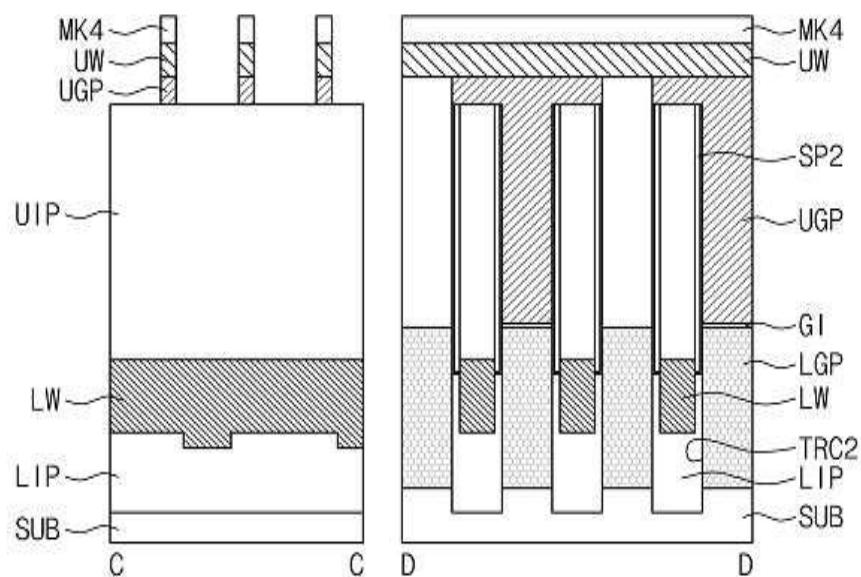

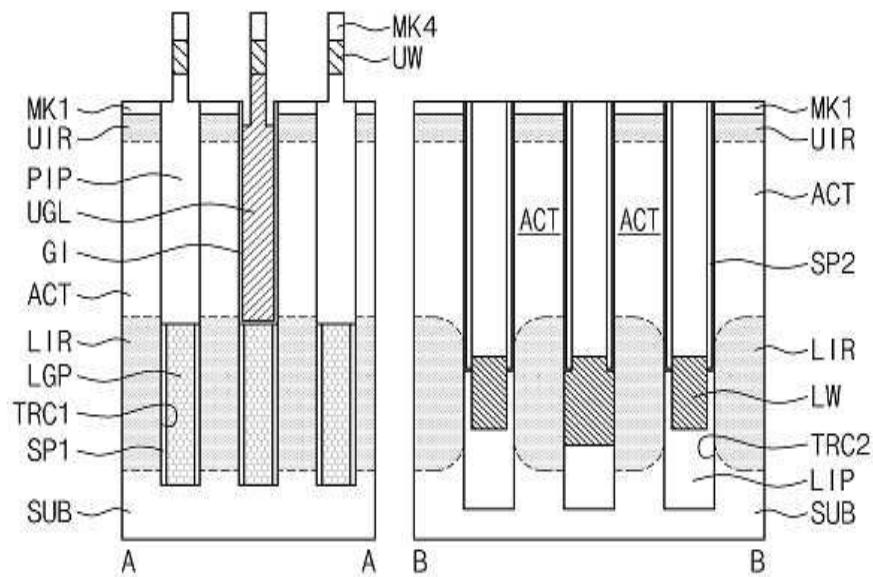

도 5a 내지 도 19a는 본 발명의 제 1 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 단면도들이다.

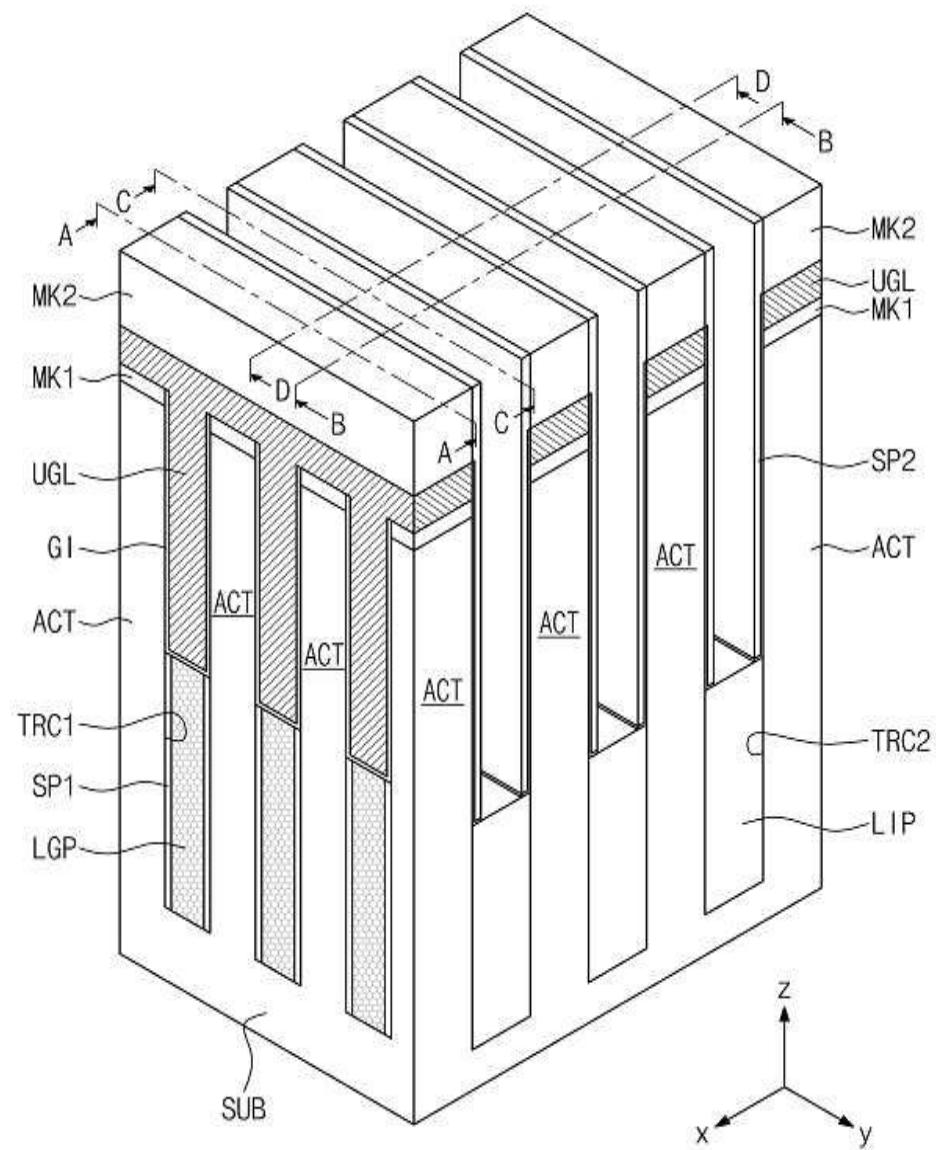

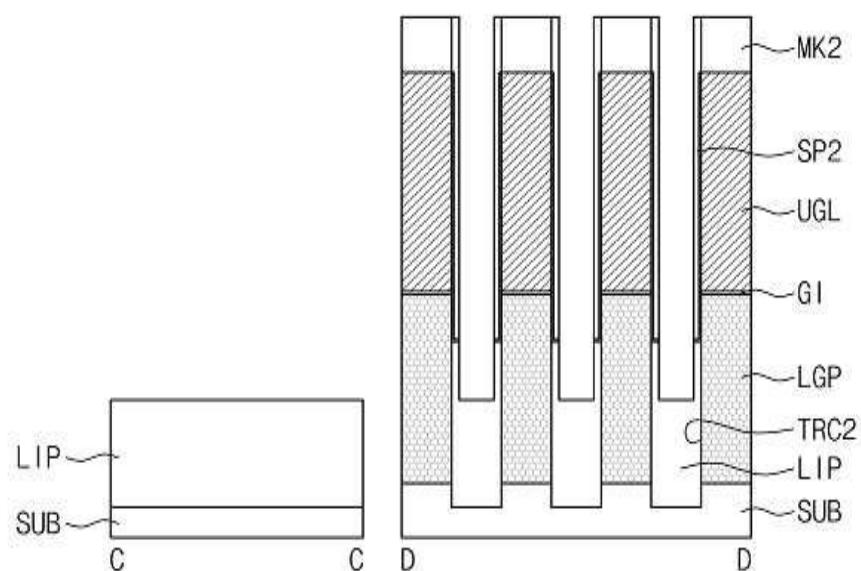

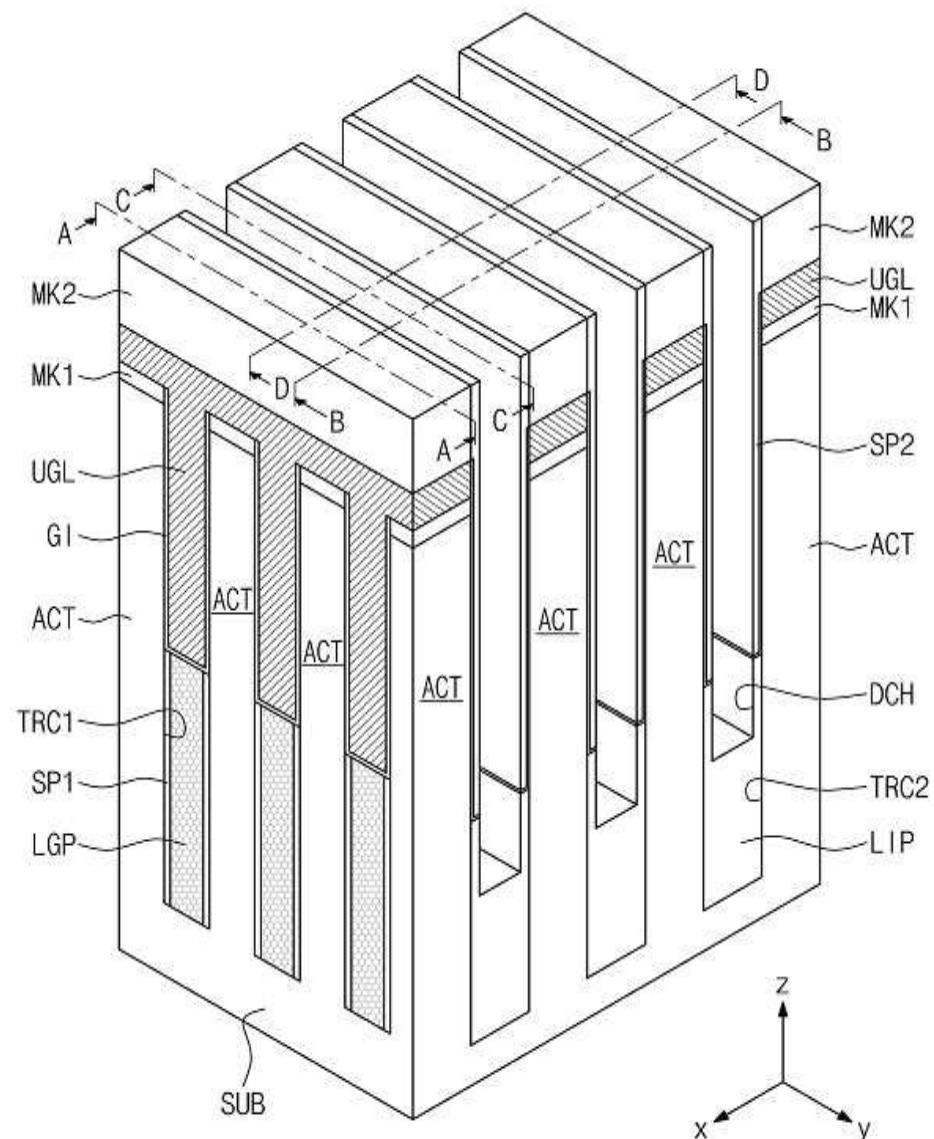

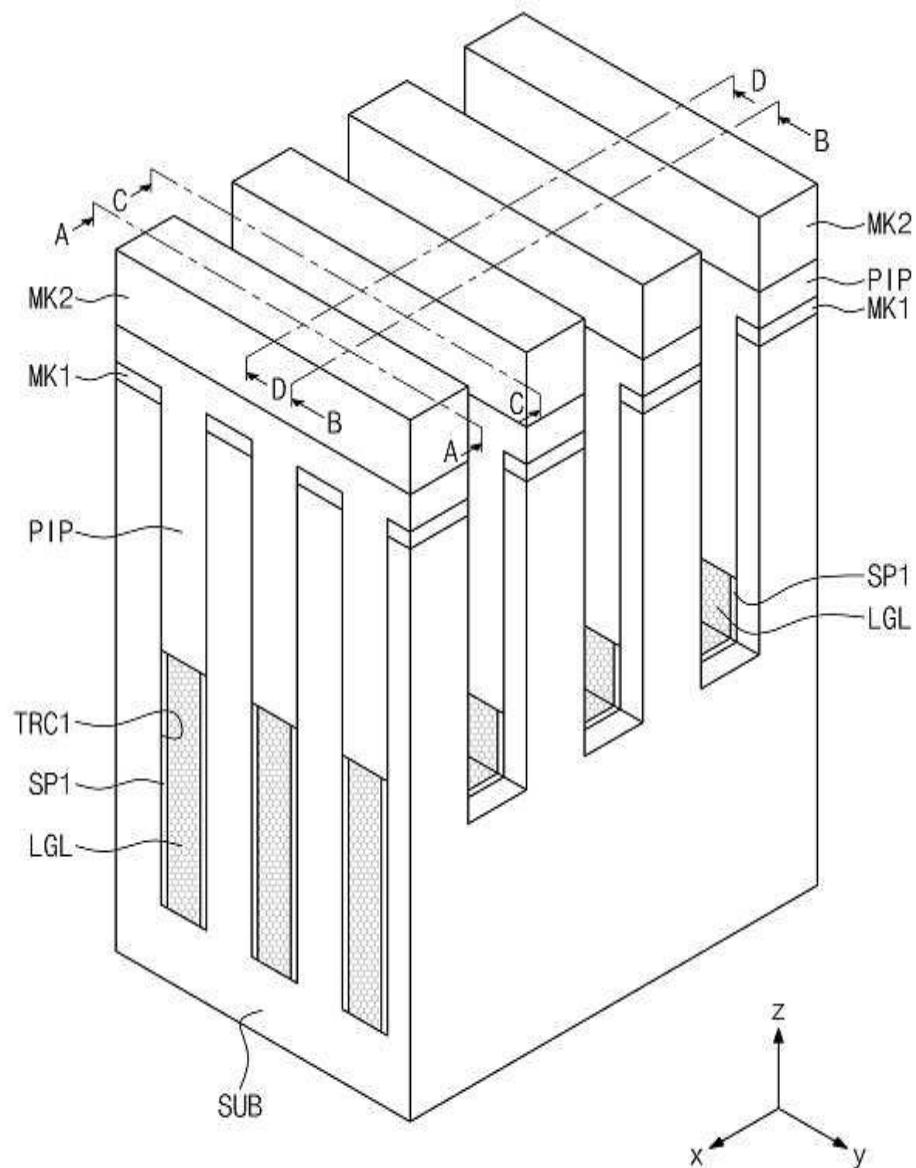

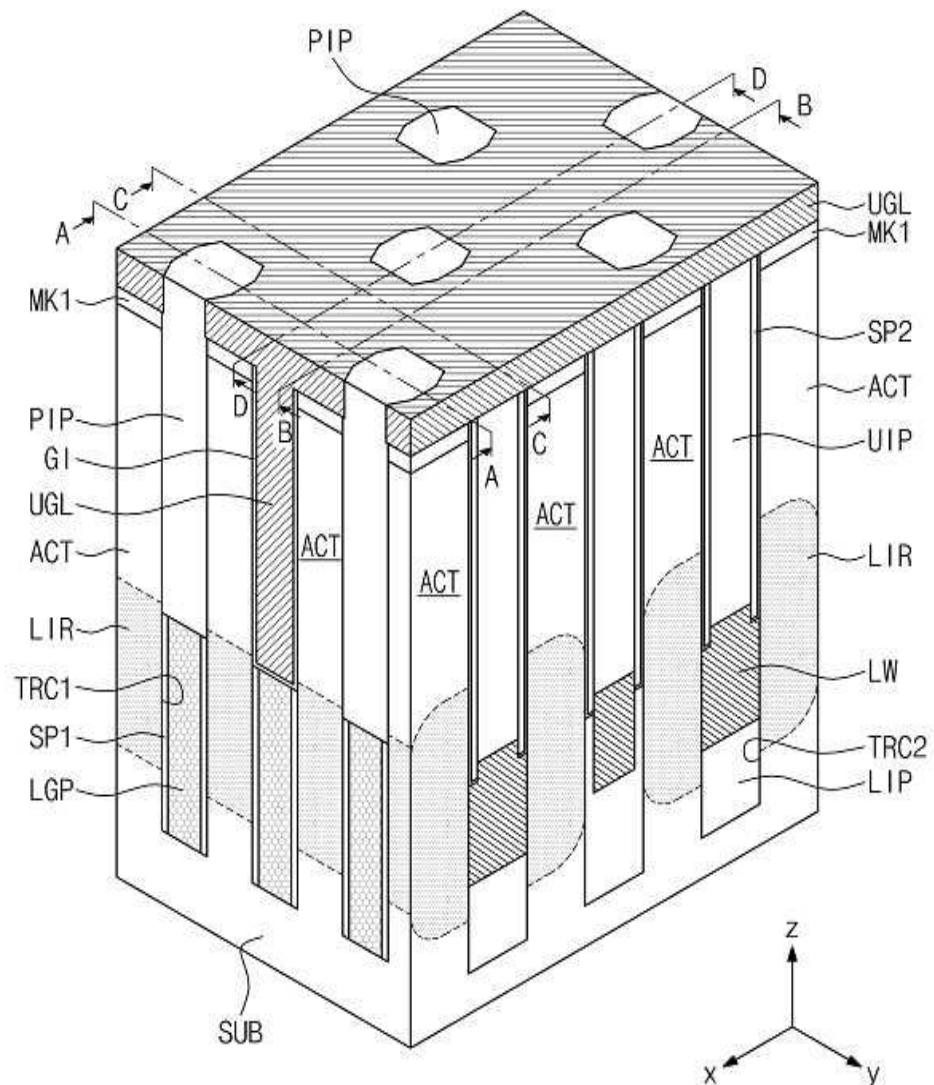

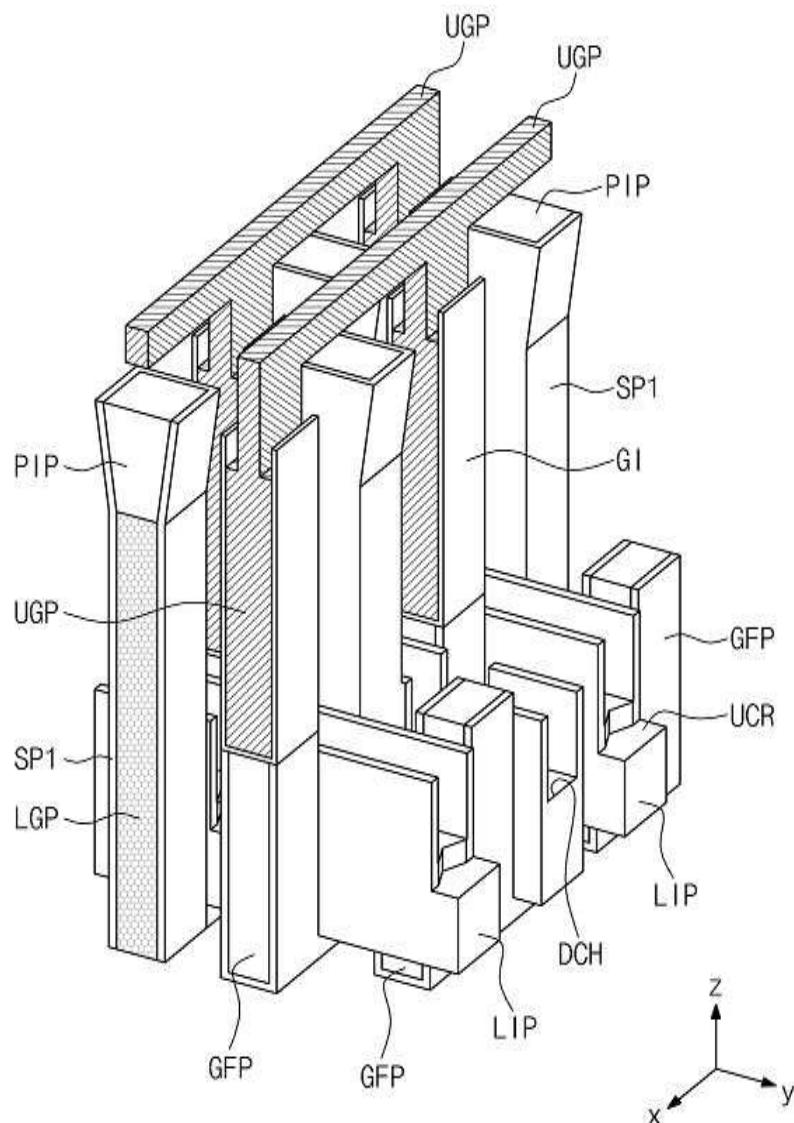

도 5b 내지 도 19b는 본 발명의 제 1 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 사시도들이다.

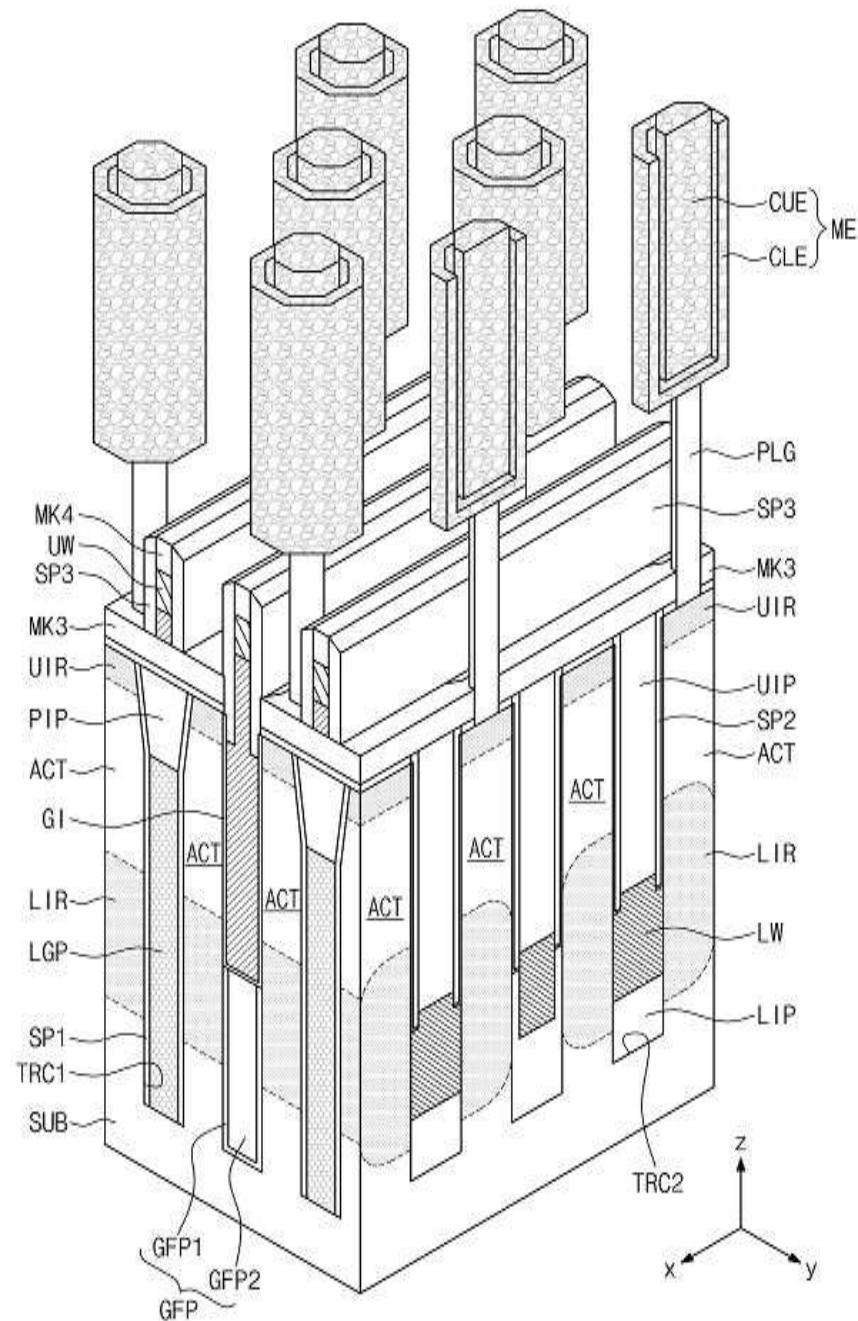

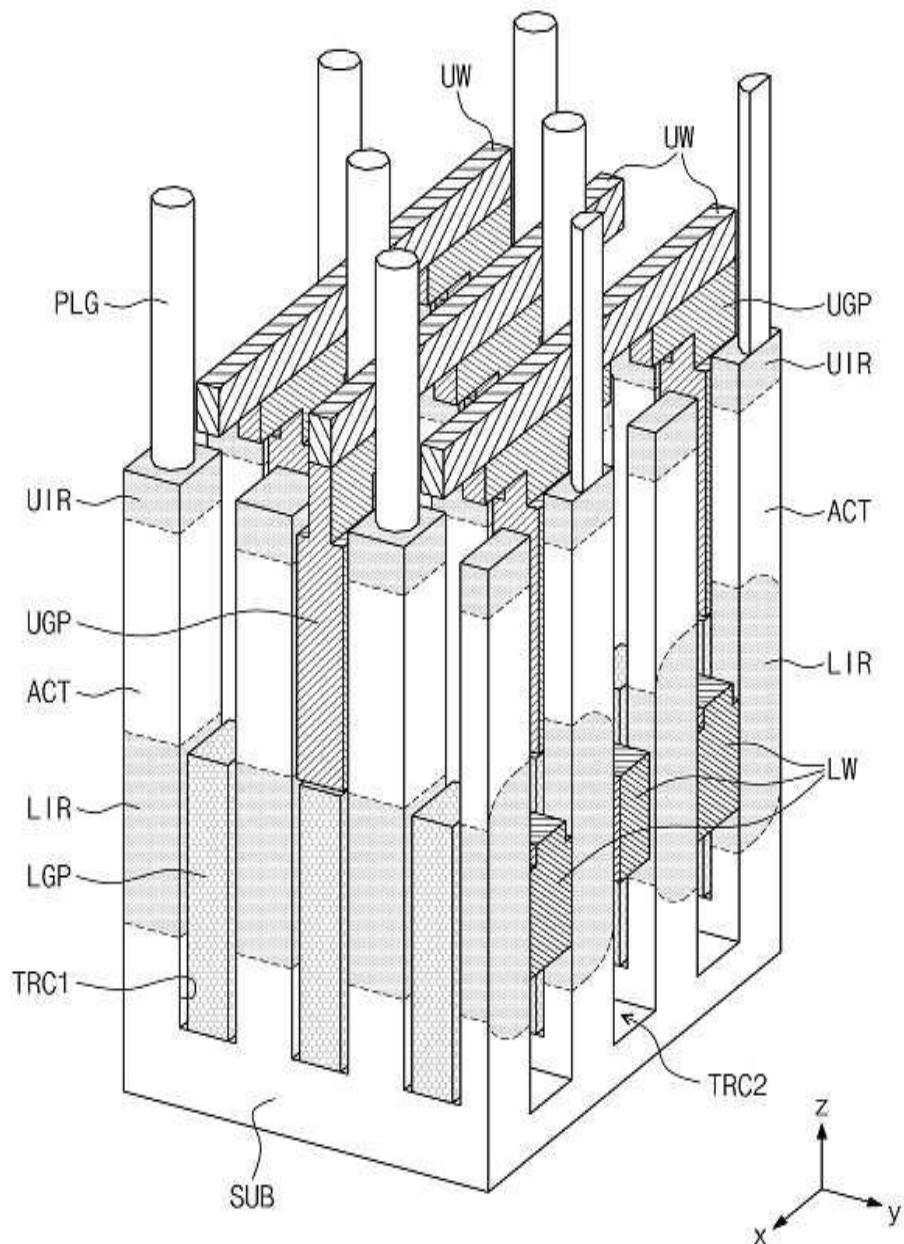

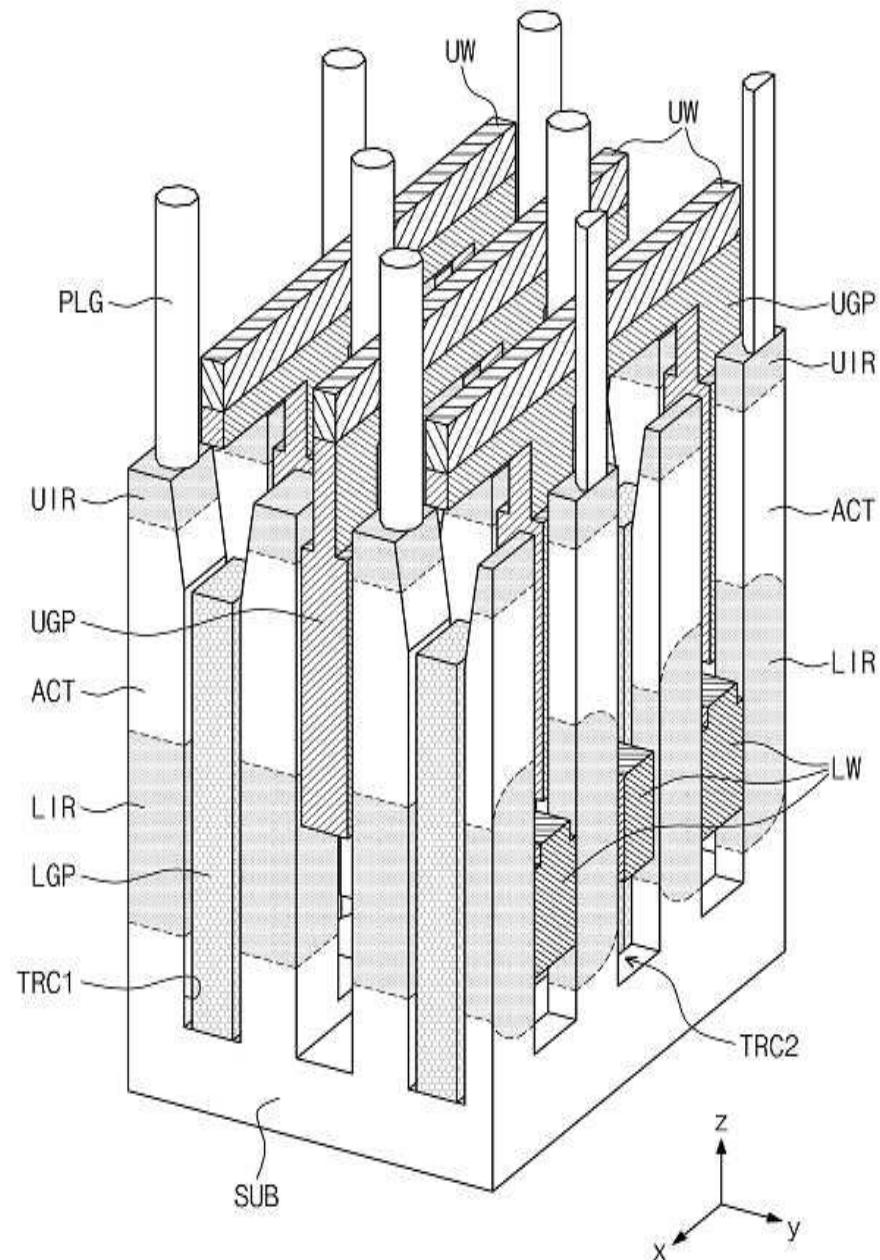

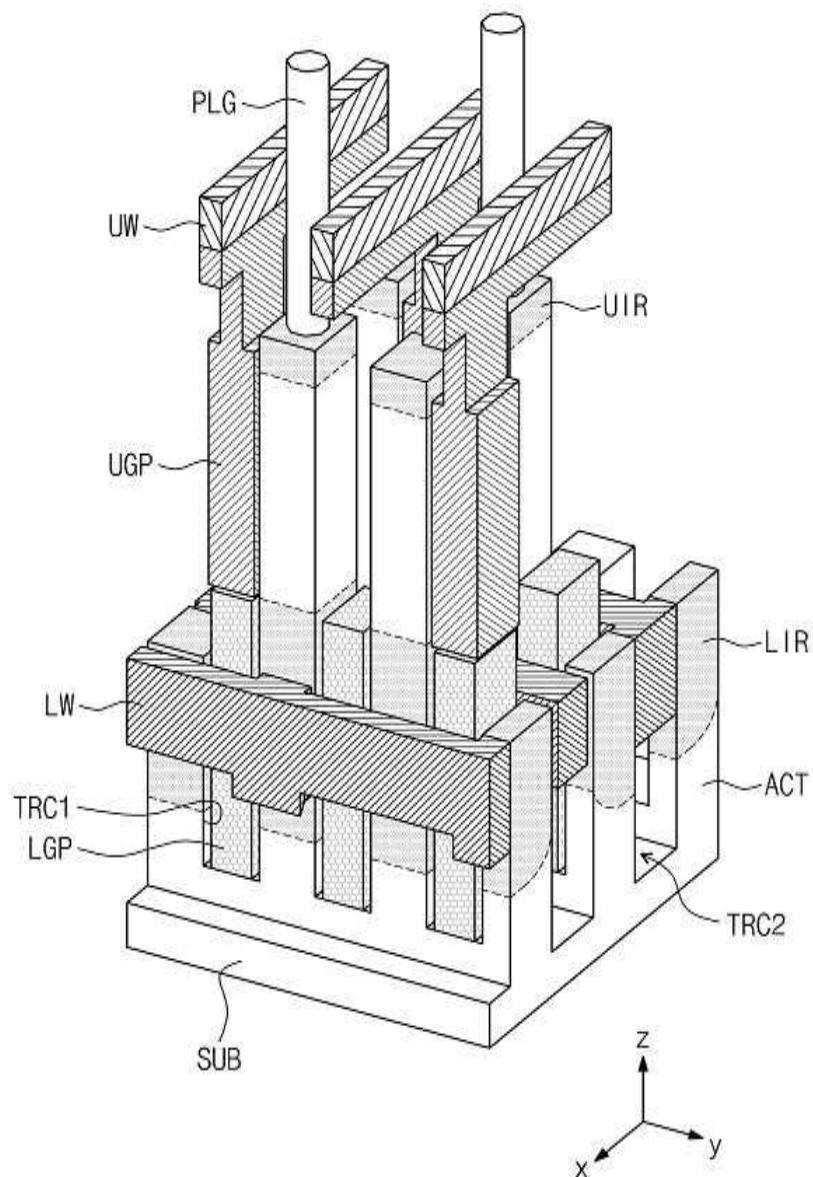

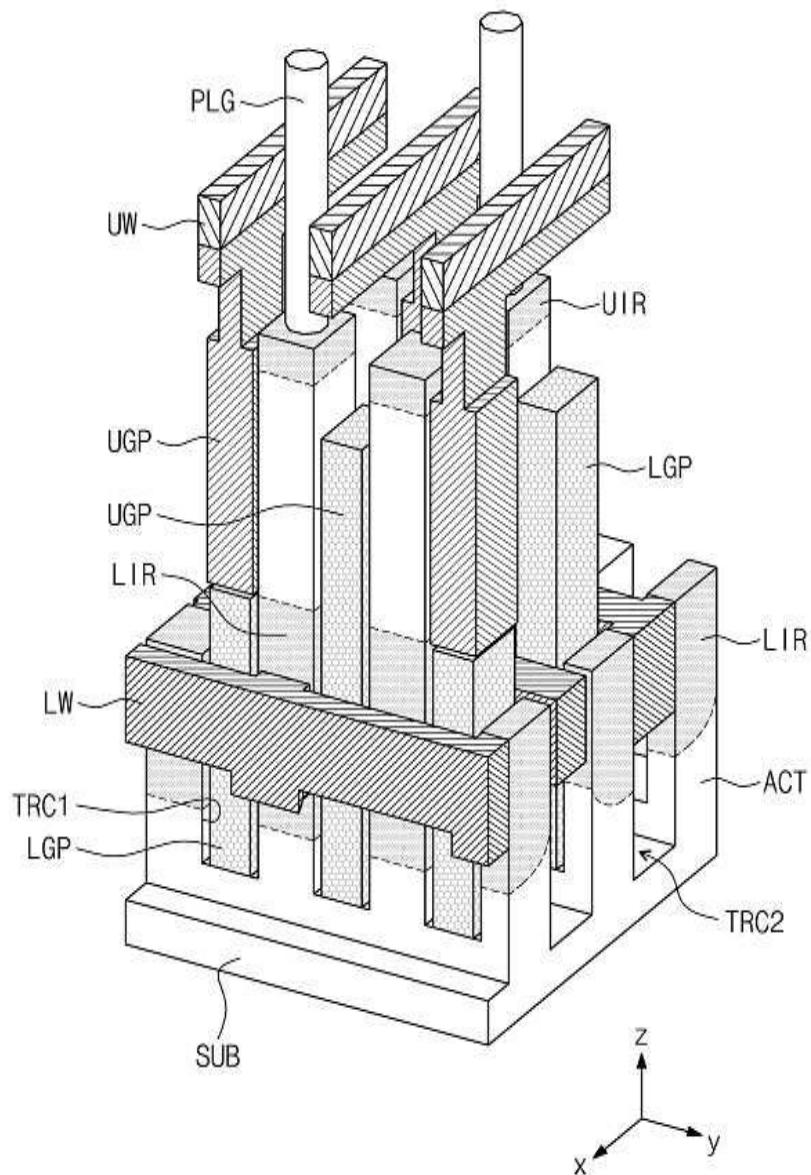

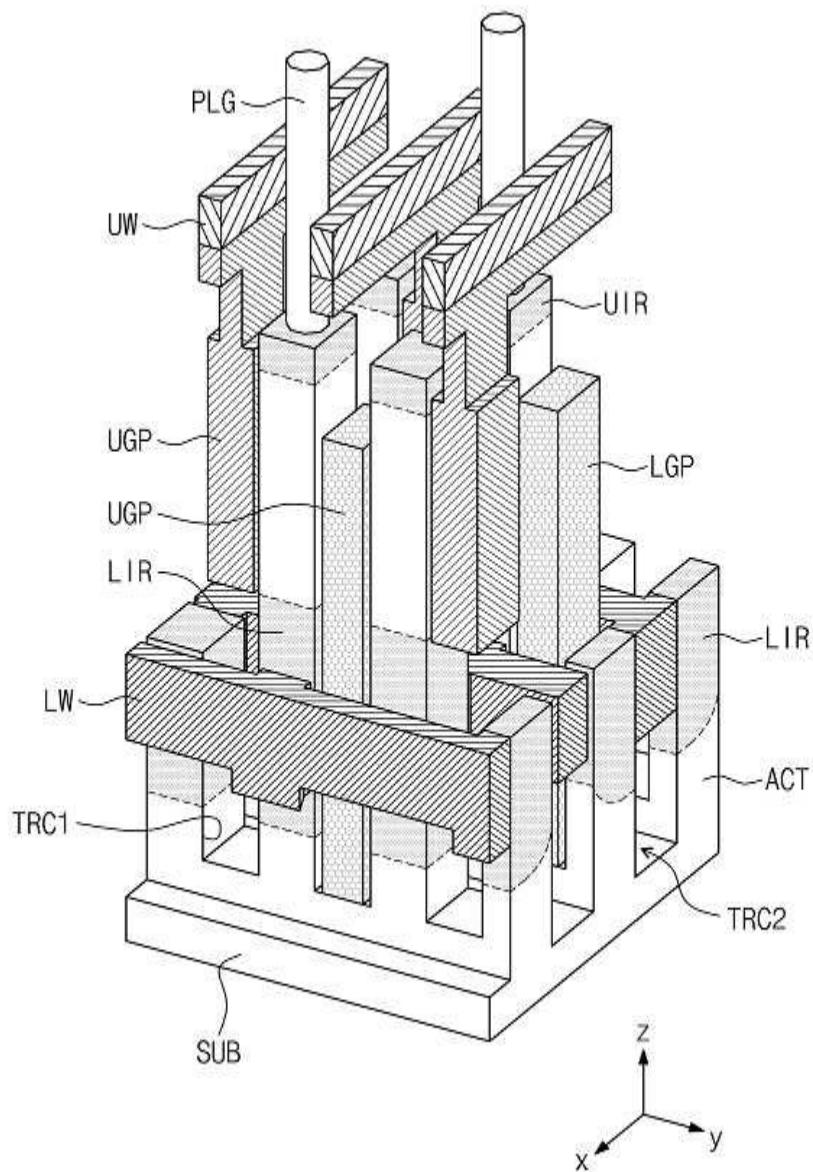

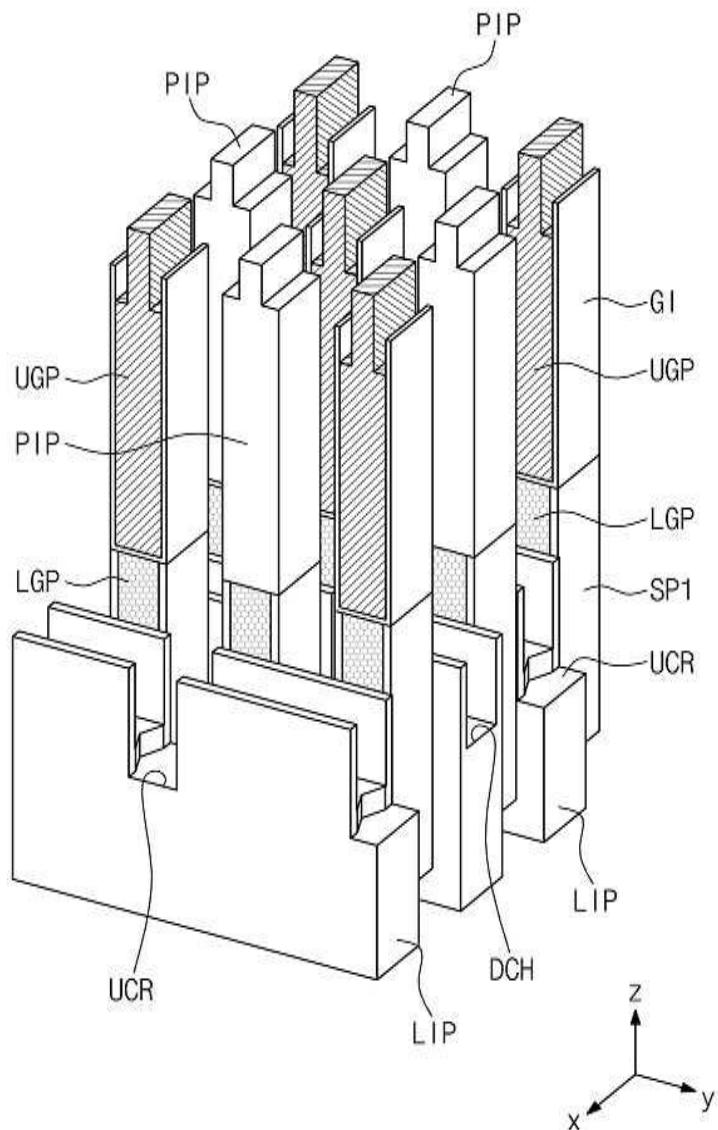

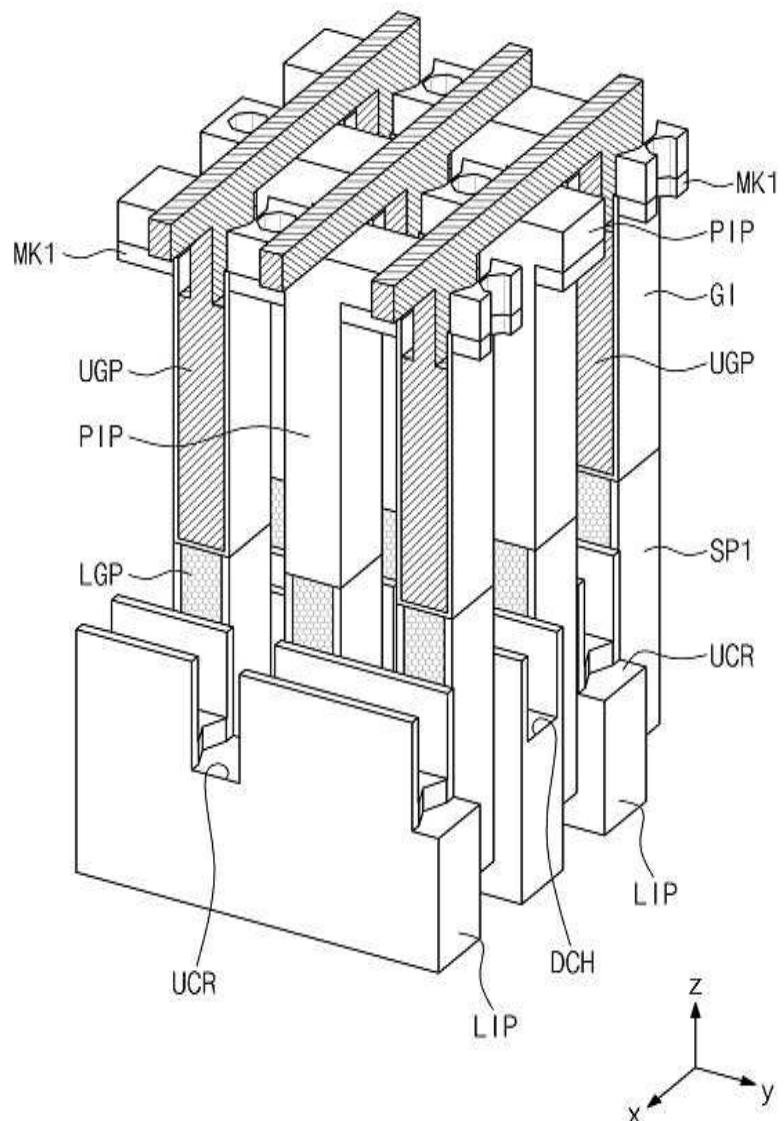

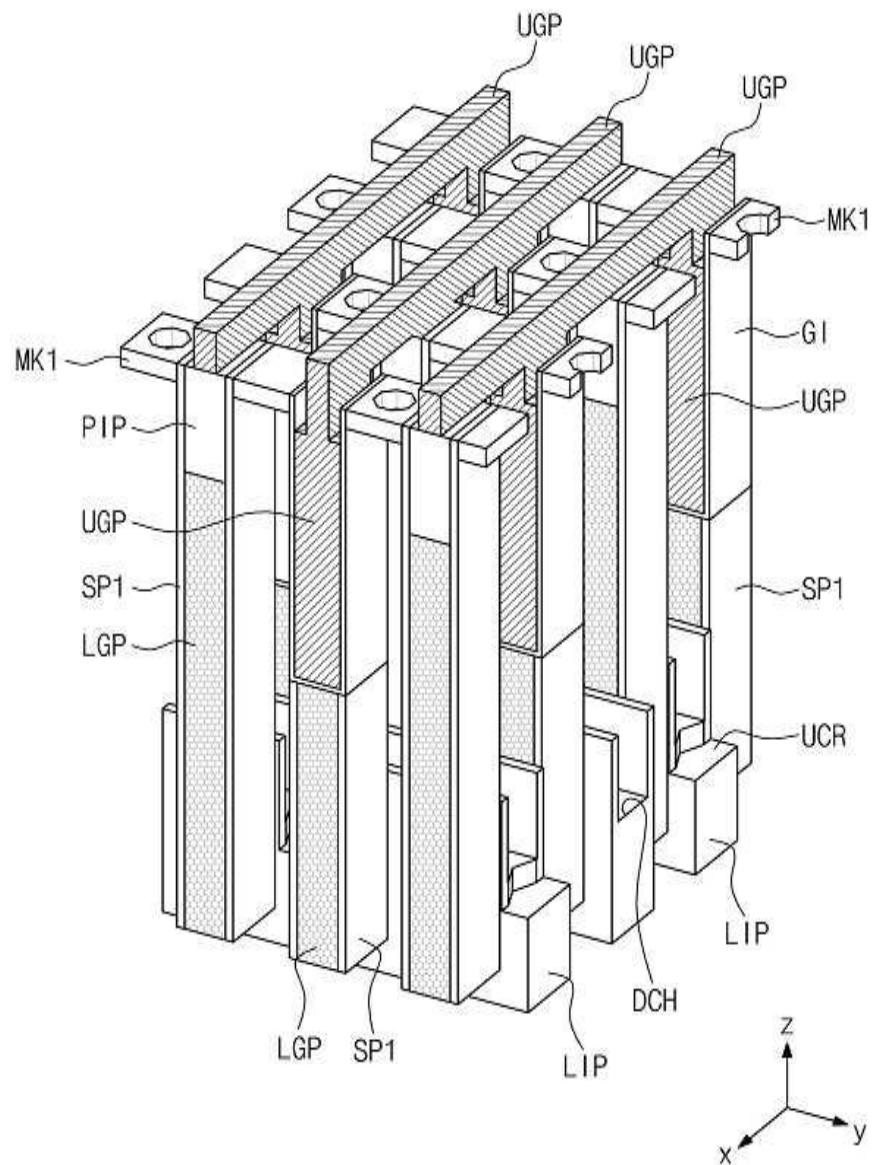

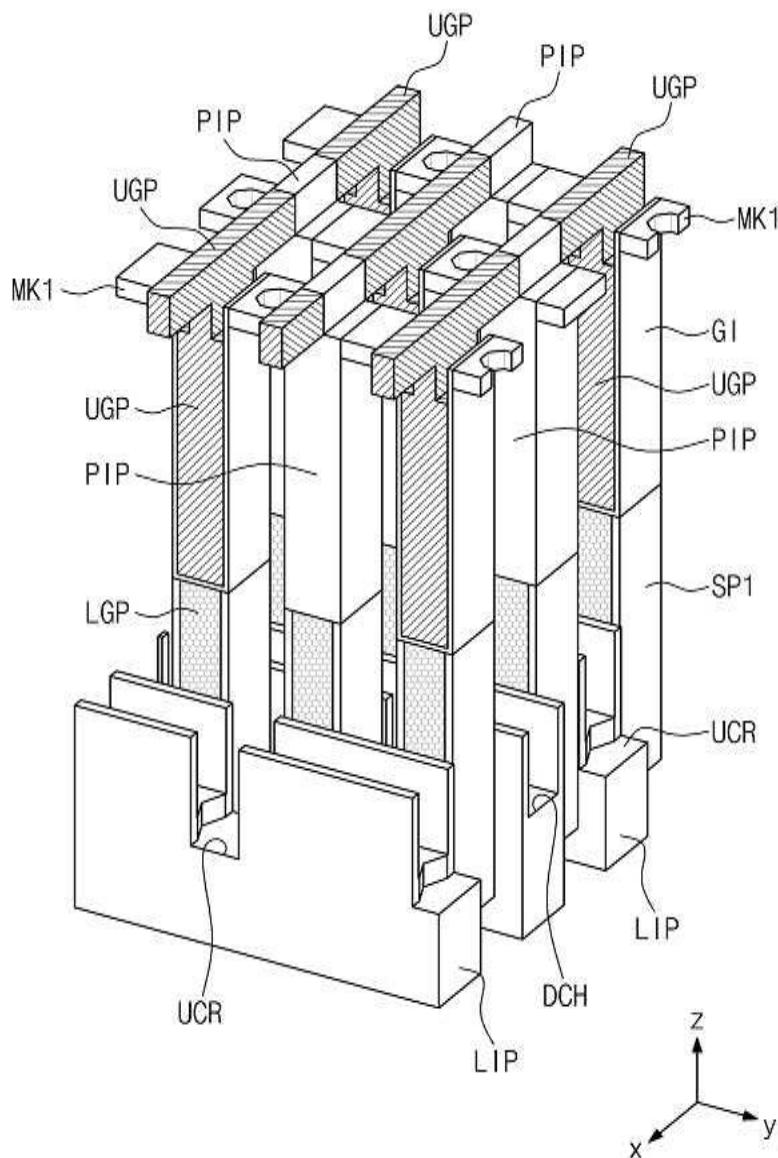

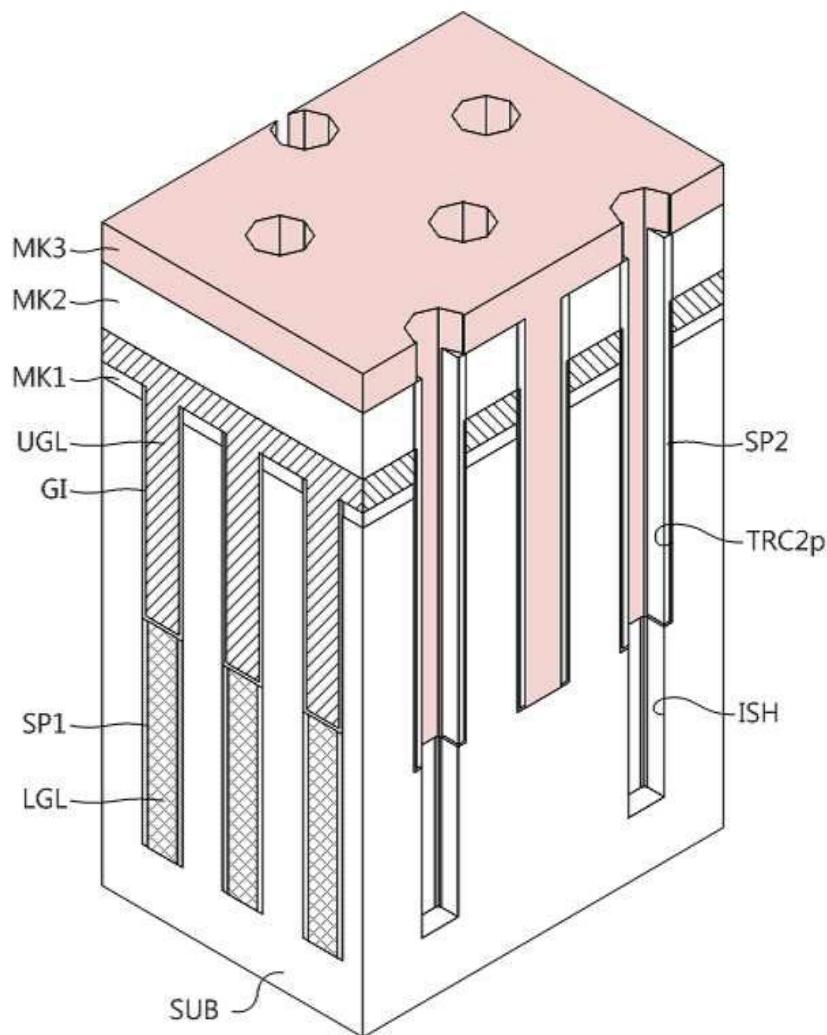

도 20 내지 도 22는 본 발명의 제 1 실시예에 따른 반도체 장치의 제조 방법에서의 일부 특징들을 예시적으로 그리고 보다 명확하게 보여주기 위해 제공되는 사시도들이다.

도 23는 본 발명의 제 2 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 순서도이다.

도 24a 내지 도 31a는 본 발명의 제 2 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 단면도들이다.

도 24b 내지 도 31b는 본 발명의 제 2 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 사시도들이다.

도 32는 본 발명의 제 3 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 순서도이다.

도 33a 내지 도 40a는 본 발명의 제 3 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 단면도들이다.

도 33b 내지 도 40b는 본 발명의 제 3 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 사시도들이다.

도 41는 본 발명의 제 4 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 순서도이다.

도 42a 내지 도 46a는 본 발명의 제 4 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 단면도들이다.

도 42b 내지 도 46b는 본 발명의 제 4 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 사시도들이다.

도 47는 본 발명의 제 5 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 순서도이다.

도 48a 내지 도 56a는 본 발명의 제 5 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 단면도들이다.

도 48b 내지 도 56b는 본 발명의 제 5 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 사시도들이다.

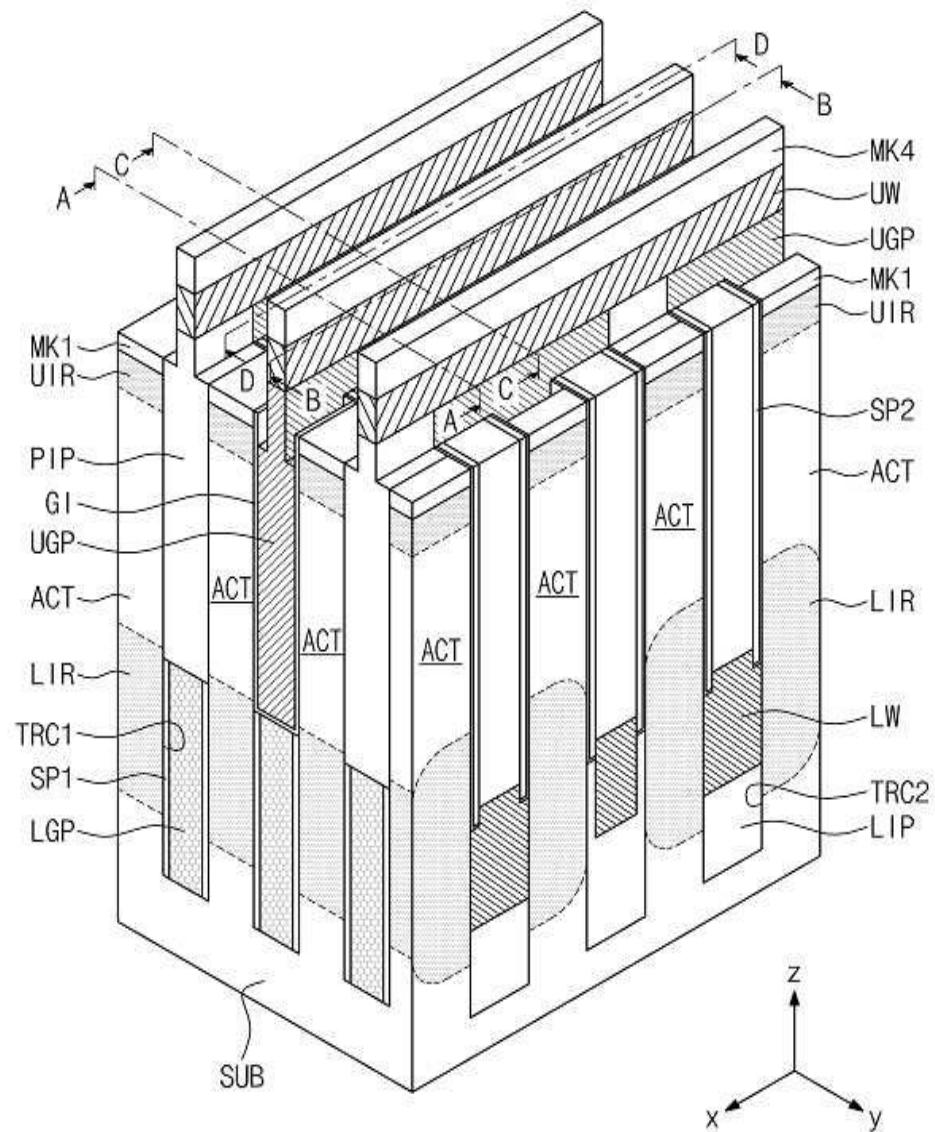

도 57 내지 도 67은 본 발명의 기술적 사상에 따른 반도체 장치들의 일 측면을 예시적으로 보여주는 사시도들이다.

도 68 내지 도 72는 본 발명의 실시예들에 따른 반도체 장치의 다른 측면을 예시적으로 도시하는 사시도들이다.

도 73 및 도 74는 본 발명의 일 측면을 설명하기 위한 평면도들이다.

도 75 내지 도 79는 본 발명의 변형된 실시예에 따른 반도체 장치의 제조 방법을 보여주는 사시도들이다.

도 80 및 도 81은 도 75 내지 도 79를 참조하여 설명된 실시예에 따른 반도체 장치의 평면도 및 사시도이다.

도 82 및 도 83는 본 발명의 실시예들에 따른 수직 채널 트랜지스터들을 포함하는 전자 장치들을 도식적으로 설명하기 위한 도면들이다.

### 발명을 실시하기 위한 구체적인 내용

[0024] 이상의 본 발명의 목적들, 다른 목적들, 특징들 및 이점들은 첨부된 도면과 관련된 이하의 바람직한 실시예들을 통해서 쉽게 이해될 것이다. 그러나 본 발명은 여기서 설명되는 실시예에 한정되지 않고 다른 형태로 구체화될 수도 있다. 오히려, 여기서 소개되는 실시예는 개시된 내용이 철저하고 완전해질 수 있도록 그리고 당업자에게 본 발명의 사상이 충분히 전달될 수 있도록 하기 위해 제공되는 것이다.

[0025] 본 명세서에서, 어떤 막이 다른 막 또는 기판 상에 있다고 언급되는 경우에 그것은 다른 막 또는 기판 상에 직접 형성될 수 있거나 또는 그들 사이에 제 3의 막이 개재될 수도 있다는 것을 의미한다. 또한, 도면들에 있어서, 막 및 영역들의 두께는 기술적 내용의 효과적인 설명을 위해 과장된 것이다. 또한, 본 명세서의 다양한 실시예들에서 제1, 제2, 제3 등의 용어가 다양한 영역, 막들 등을 기술하기 위해서 사용되었지만, 이를 영역, 막들이 이 같은 용어들에 의해서 한정되어서는 안 된다. 이를 용어들은 단지 어느 소정 영역 또는 막을 다른 영역 또는 막과 구별시키기 위해서 사용되었을 뿐이다. 따라서, 어느 한 실시예에의 제1막질로 언급된 막질이 다른 실시예에서는 제2막질로 언급될 수도 있다. 여기에 설명되고 예시되는 각 실시예는 그것의 상보적인 실시예도 포함한다.

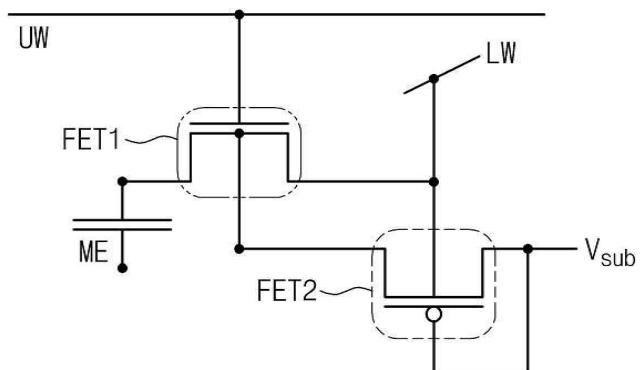

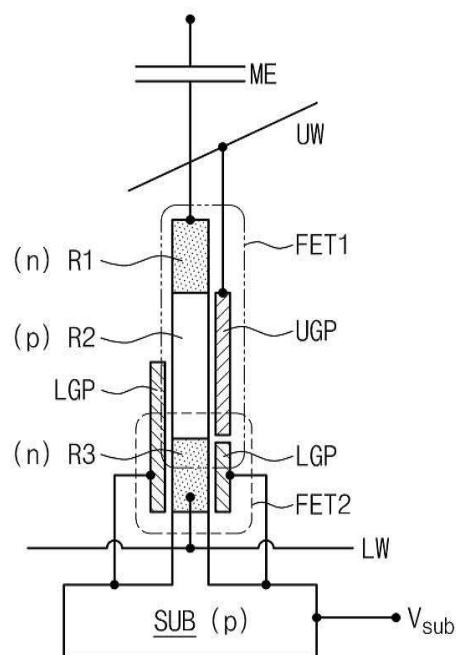

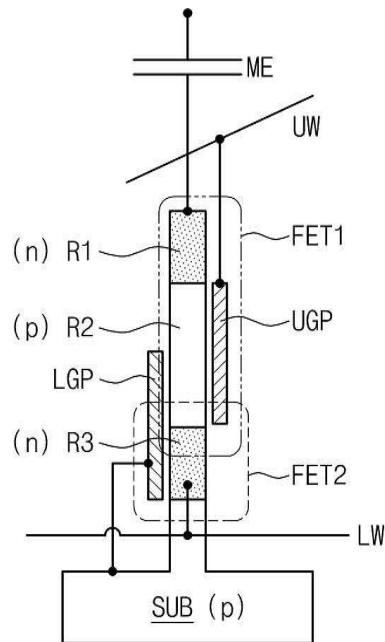

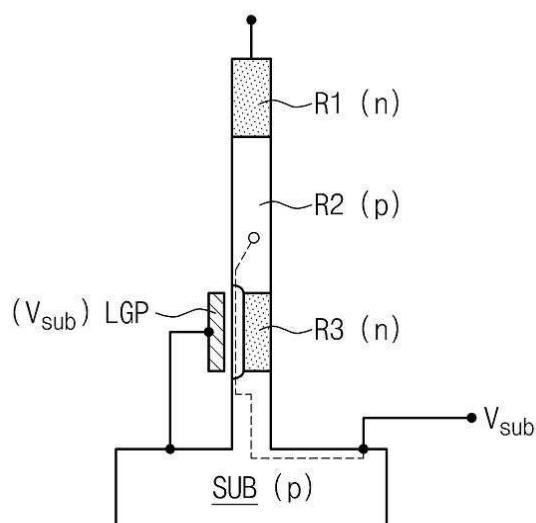

- [0026] 도 1은 본 발명의 실시예들에 따른 반도체 장치의 일 측면을 도식적으로(schematically) 설명하기 위한 회로도이다.

- [0027] 도 1을 참조하면, 직렬로 연결된 제 1 전계효과트랜지스터(FET1) 및 제 2 전계효과트랜지스터(FET2)가 제공된다. 일 실시예에 따르면, 도시된 것처럼, 상기 제 1 및 제 2 전계효과트랜지스터들(FET1, FET2)은 각각 엔모스펫(NMOSFET) 및 피모스펫(PMOSFET)일 수 있다. 하지만, 변형된 실시예들에 따르면, 상기 제 1 및 제 2 전계효과트랜지스터들은 각각 피모스펫(PMOSFET) 및 엔모스펫(NMOSFET)일 수 있다. 당업자는 아래에서 설명되는 본 발명의 실시예들에 기초하여 용이하게 이러한 변형을 구현할 수 있을 것이라는 점에서, 이러한 변형된 실시예들에 대한 설명은 생략한다.

- [0028] 본 발명의 기술적 사상에 따르면, 도시된 것처럼, 상기 제 1 전계효과트랜지스터(FET1)의 소오스/드레인 전극들 중의 하나는 상기 제 2 전계효과트랜지스터(FET2)의 채널 영역으로 사용되고, 상기 제 2 전계효과트랜지스터(FET2)의 소오스/드레인 전극들 중의 하나는 상기 제 1 전계효과트랜지스터(FET1)의 채널 영역으로 사용된다.

- [0029] 일 실시예에 따르면, 상기 제 1 전계효과트랜지스터(FET1)의 소오스/드레인 전극들 중의 다른 하나는 메모리 요소(ME)에 전기적으로 연결되고, 상기 제 2 전계효과트랜지스터(FET2)의 소오스/드레인 전극들 중의 다른 하나는 소정의 외부 전압(Vsub)이 공급되는 외부 단자에 전기적으로 연결될 수 있다. 아래에서는, 디램 메모리 소자를 구성하는 커패시터가 상기 메모리 요소(ME)로서 예시적으로 설명될 것이다. 하지만, 도 1에 도시된 제 1 및 제 2 전계효과트랜지스터들(FET1, FET2)은 알려진 다양한 메모리 소자들에서 그것의 메모리 요소로의 전기적 연결을 제어하는 스위칭 소자로서 사용될 수 있다. 다시 말해, 상기 메모리 요소(ME)는 커패시터, 강유전체 커패시터, 자기터널접합(MTJ), 가변 저항성 요소 또는 전하저장 기제(mechanism)에 기초한 메모리 요소일 수 있지만, 여기에 예시된 것들에 한정되는 것 역시 아니다.

- [0030] 상기 제 2 전계효과트랜지스터(FET2)의 채널 영역은 하부 배선(LW; lower wiring)에 전기적으로 연결되고, 상기 제 1 전계효과트랜지스터(FET1)의 게이트 전극은 상부 배선(UW; upper wiring)에 전기적으로 연결될 수 있다. 일 실시예에 따르면, 상기 상부 배선(UW)은 상기 하부 배선(LW)을 가로지르도록 배치될 수 있다.

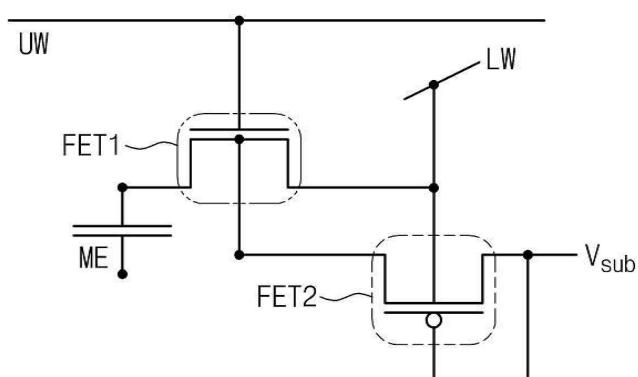

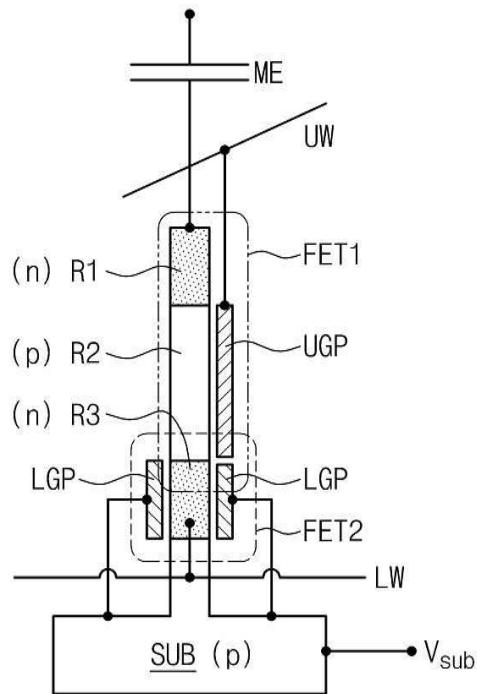

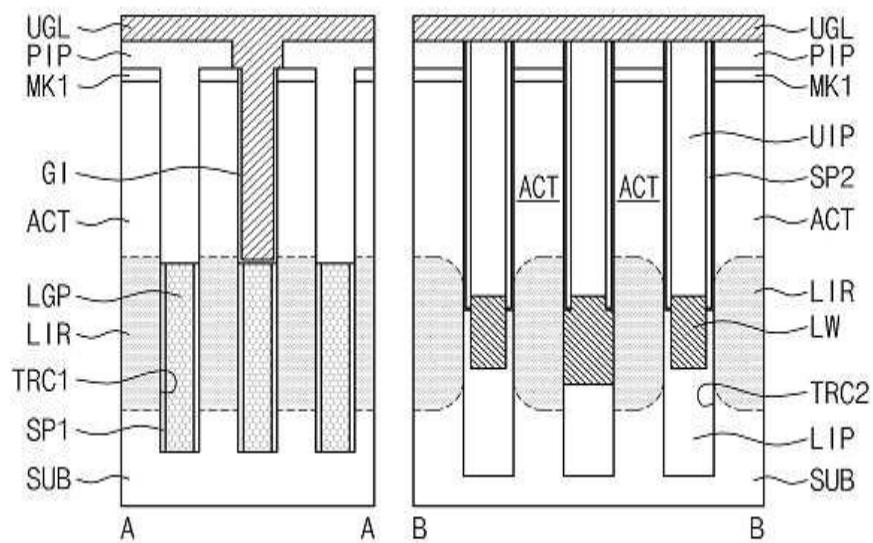

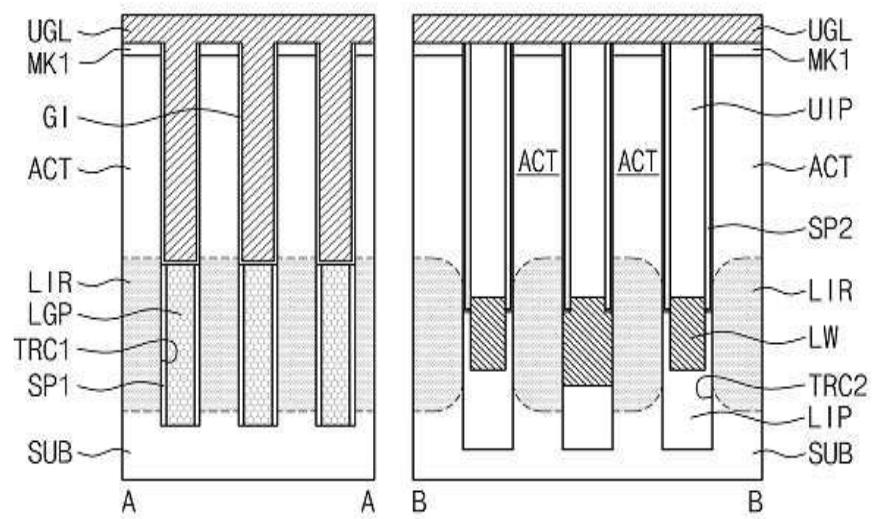

- [0031] 도 2a 내지 도 2c는 본 발명의 실시예들에 따른 반도체 장치들을 보다 구체적으로 설명하기 위한 도면들이다.

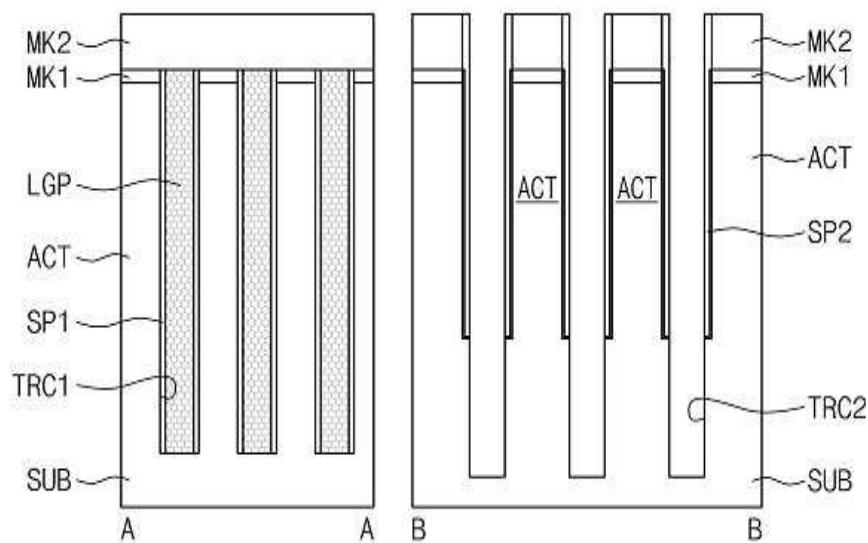

- [0032] 도 2a 내지 도 2c를 참조하면, 도 1을 참조하여 설명된 상기 제 1 및 제 2 전계효과트랜지스터들(FET1, FET2)은 기판(SUB)의 상부면으로부터 위쪽으로 돌출된 활성 패턴을 채널 영역으로 사용하는 수직 채널 트랜지스터들일 수 있다. 상기 활성 패턴은 반도체 특성을 갖는 물질로 형성될 수 있으며, 상기 기판(SUB) 상의 제 1 영역(R1), 상기 기판(SUB)과 상기 제 1 영역(R1) 사이의 제 2 영역(R2) 및 상기 기판(SUB)과 상기 제 2 영역(R2) 사이의 제 3 영역(R3)을 포함할 수 있다. 즉, 상기 제 3, 제 2 및 제 1 영역들(R3, R2, R1)은 상기 기판(SUB) 상에 차례로 그리고 직접 접촉하면서 배치된다. 상기 제 1 및 제 3 영역들(R1, R3)은 상기 기판(SUB)과 다른 도전형이고, 상기 제 2 영역(R2)은 상기 기판(SUB)과 같은 도전형 또는 진성 반도체일 수 있다. 따라서, 예시적으로 도시된 것처럼, 상기 기판(SUB)이 피형의 반도체인 경우, 상기 제 1 및 제 3 영역들(R1, R3)은 엔형이고, 상기 제 2 영역(R2)은 피형 또는 진성(intrinsic)일 수 있다.

- [0033] 이에 더하여, 상기 활성 패턴의 주변에는 상기 제 2 영역(R2) 및 제 3 영역(R3)의 측벽들을 각각 마주보는 상부 및 하부 게이트 패턴들(UGP, LGP)이 배치될 수 있다. 이때, 상기 상부 및 하부 게이트 패턴들(UGP, LGP)은 상기 활성 패턴의 측벽으로부터 이격되어 배치됨으로써, 상기 제 2 영역(R2) 및 상기 제 3 영역(R3)과 각각 모스 커패시터들(MOS capacitors)를 구성할 수 있다. 본 발명의 일부 실시예들에 따르면, 상기 상부 게이트 패턴(UGP)은 상부 배선(UW)에 오직하게 연결(Ohmically connected)되고, 상기 하부 게이트 패턴(LGP)은 상기 기판(SUB)에 오직하게 연결될 수 있다.

- [0034] 상기 제 1 전계효과트랜지스터(FET1)는 상기 제 1, 제 2 및 제 3 영역들(R1, R2, R3) 그리고 상기 상부 게이트 패턴(UGP)에 의해 구성되고, 상기 제 2 전계효과트랜지스터(FET2)는 상기 제 2 및 제 3 영역들(R2, R3), 상기 기판(SUB) 그리고 상기 하부 게이트 패턴(LGP)에 의해 구성될 수 있다. 즉, 상기 제 2 및 제 3 영역들(R2, R3)은 각각 상기 제 1 및 제 2 전계효과트랜지스터들(FET1, FET2)의 채널 영역들로 사용될 수 있다. 본 발명의 다른 측면에 따르면, 상기 제 2 영역(R2)은 상기 제 2 전계효과트랜지스터(FET2)의 소오스 전극으로 사용되고, 상기 제 3 영역(R3)은 상기 제 1 전계효과트랜지스터(FET1)의 드레인 전극으로 사용될 수 있다.

- [0035] 메모리 반도체 장치를 위한 본 발명의 일부 실시예들에 따르면, 상기 제 1 영역(R1)에는 도 1의 상기 메모리 요소(ME)가 접속하고, 상기 제 3 영역(R3)에는 도 1의 상기 하부 배선(LW)이 접속할 수 있다. 상기 하부 배선(LW)은 상기 상부 배선(UW)을 가로지르도록 배치될 수 있다. 한편, 본 발명의 일부 실시예들에 따르면, 상기 제 2

영역(R2)은 상기 제 1 및 제 3 영역들(R1, R3)을 제외한 다른 어떠한 도전성 패턴들로부터도 전기적으로 분리될 수 있다. 이 경우, 상기 제 2 영역(R2)은 상기 제 1 및 제 3 영역들(R1, R3)과 다이오드를 구성하기 때문에, 상기 제 2 영역(R2)은 플로팅 상태에 있을 수 있다. 상기 제 2 영역(R2)은 상술한 것처럼 상기 제 1 전계효과트랜지스터(FET1)의 채널 영역으로 사용되기 때문에, 상기 제 2 영역(R2)의 이러한 플로팅 상태는 상기 제 1 전계효과트랜지스터(FET1)에서 플로팅 바디 효과(floating body effect)가 발생하는 것을 가능하게 한다. 알려진 것처럼, 상기 플로팅 바디 효과는 트랜지스터의 문턱전압에서의 불안정성을 증가시키고, 메모리 반도체 장치의 동적 기준(dynamic reference) 특성에서의 열화를 가져올 수 있다.

[0036] 하지만, 본 발명의 실시예들에 따르면, 상술한 것처럼, 상기 제 3 영역(R3)은 상기 제 2 전계효과트랜지스터(FET2)의 채널 영역으로 사용된다. 이에 따라, 도 3에 도시된 것처럼, 상기 하부 게이트 패턴(LGP)에 상기 제 3 영역(R3)을 반전시킬 수 있는 전압이 인가될 경우, 상기 제 2 영역(R2)은 상기 기판(SUB)과 전기적으로 연결되어 상술한 플로팅 바디의 문제는 억제될 수 있다.

[0037] 한편, 도 2a 및 도 2b에 도시된 것처럼, 상기 하부 게이트 패턴(LGP)은 상기 활성 패턴의 양쪽 측벽들 상에 각각 하나씩 배치될 수 있다. 이 경우, 상기 상부 게이트 패턴(UGP)은 상기 하부 게이트 패턴들(LGP) 중의 하나의 상부에 배치될 수 있다. 하지만, 도 2c에 도시된 것처럼, 상기 하부 게이트 패턴(LGP)은 상기 활성 패턴의 한 측벽 상에 국소적으로 배치될 수도 있다.

[0038] 본 발명의 다른 측면에 따르면, 도 2b에 도시된 것처럼 상기 하부 게이트 패턴들(LGP) 중의 하나 또는 도 2c에 도시된 것처럼 상기 하부 게이트 패턴(LGP)은 상기 제 2 영역(R2)의 측벽을 마주보도록 위쪽으로 연장될 수 있다. 즉, 상기 하부 게이트 패턴(LGP)의 상부면은 상기 제 2 및 제 3 영역들(R2, R3)의 경계면 또는 상기 상부 게이트 패턴(UGP)의 바닥면보다 상기 기판(SUB)으로부터 더 멀리 떨어진 위치에 형성될 수 있다. 이처럼, 상기 하부 게이트 패턴(LGP)의 일부가 상기 제 2 영역(R2)을 마주보도록 형성될 경우, 상기 제 1 전계효과트랜지스터(FET1)의 채널 영역으로 사용되는 상기 제 2 영역(R2)의 전위는 상기 하부 게이트 패턴(LGP)에 의해서도 제어될 수 있다. 상기 하부 게이트 패턴(LGP)은 문턱 전압과 같은 상기 제 1 전계효과트랜지스터(FET1)의 전기적 특성을 제어하는데 이용될 수 있다.

#### [제조 방법- 제 1 실시예]

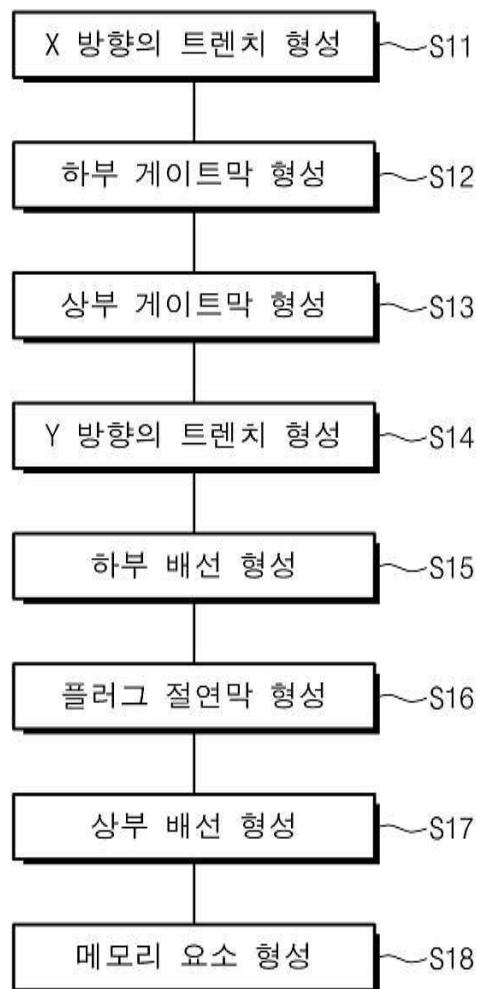

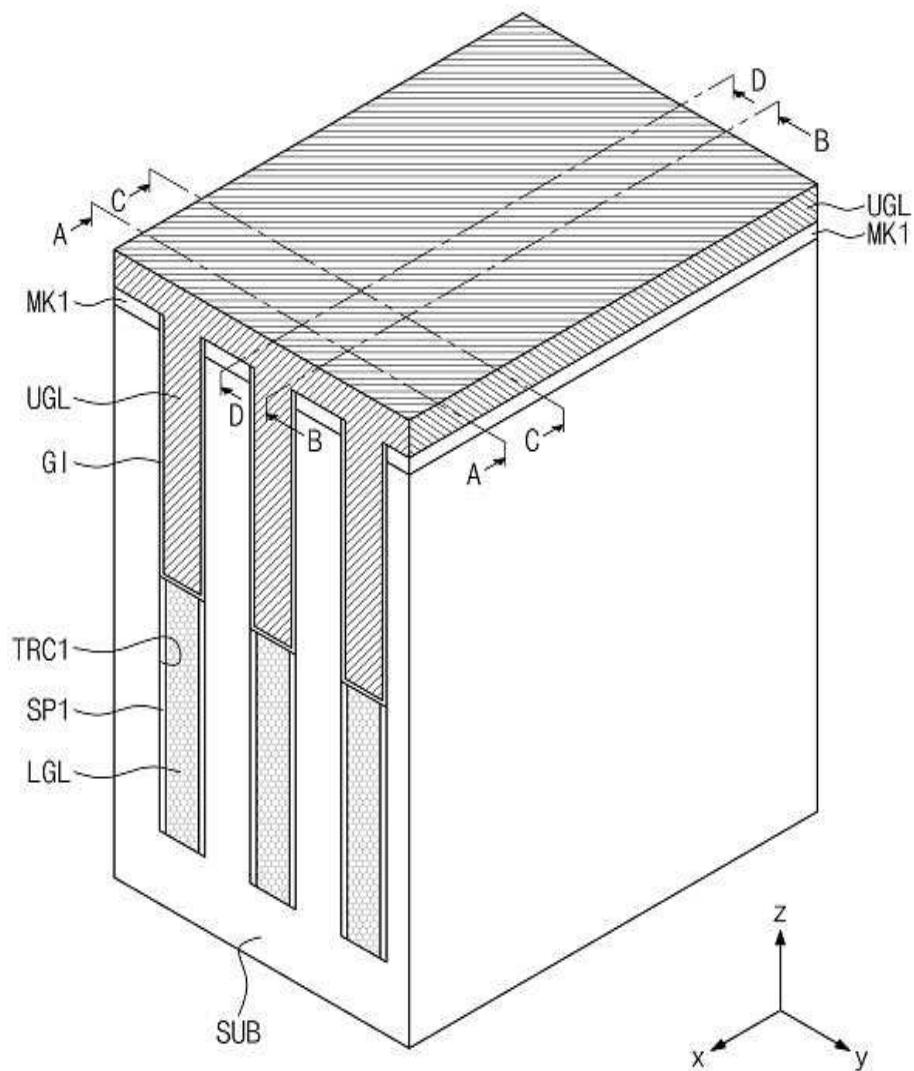

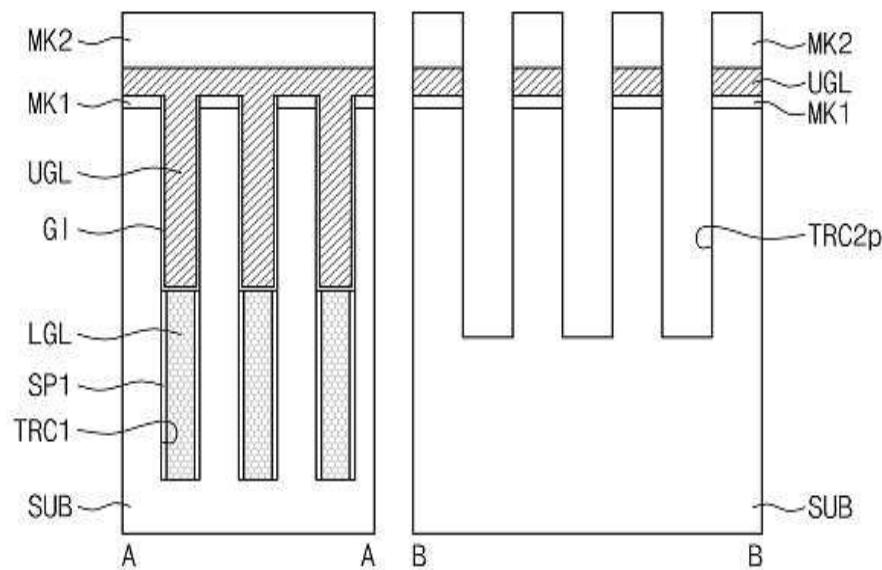

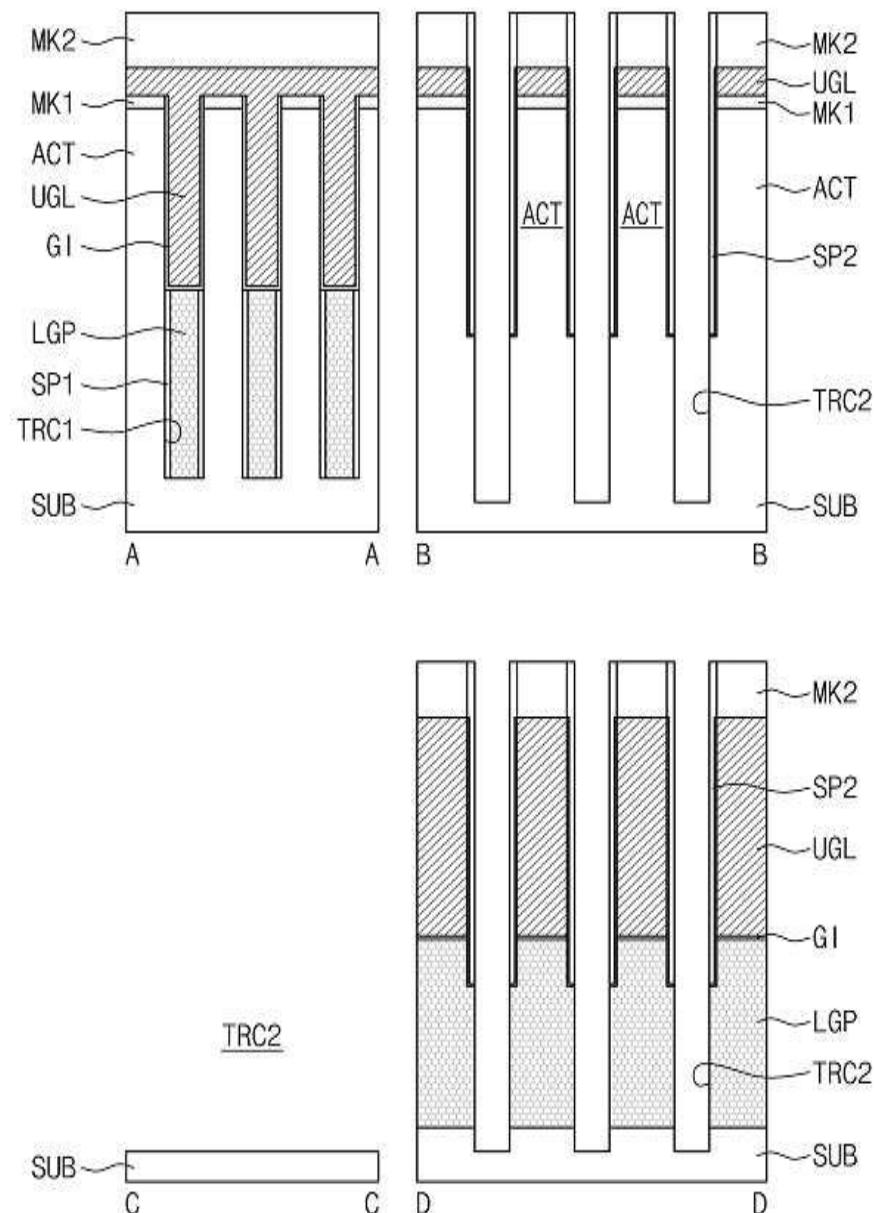

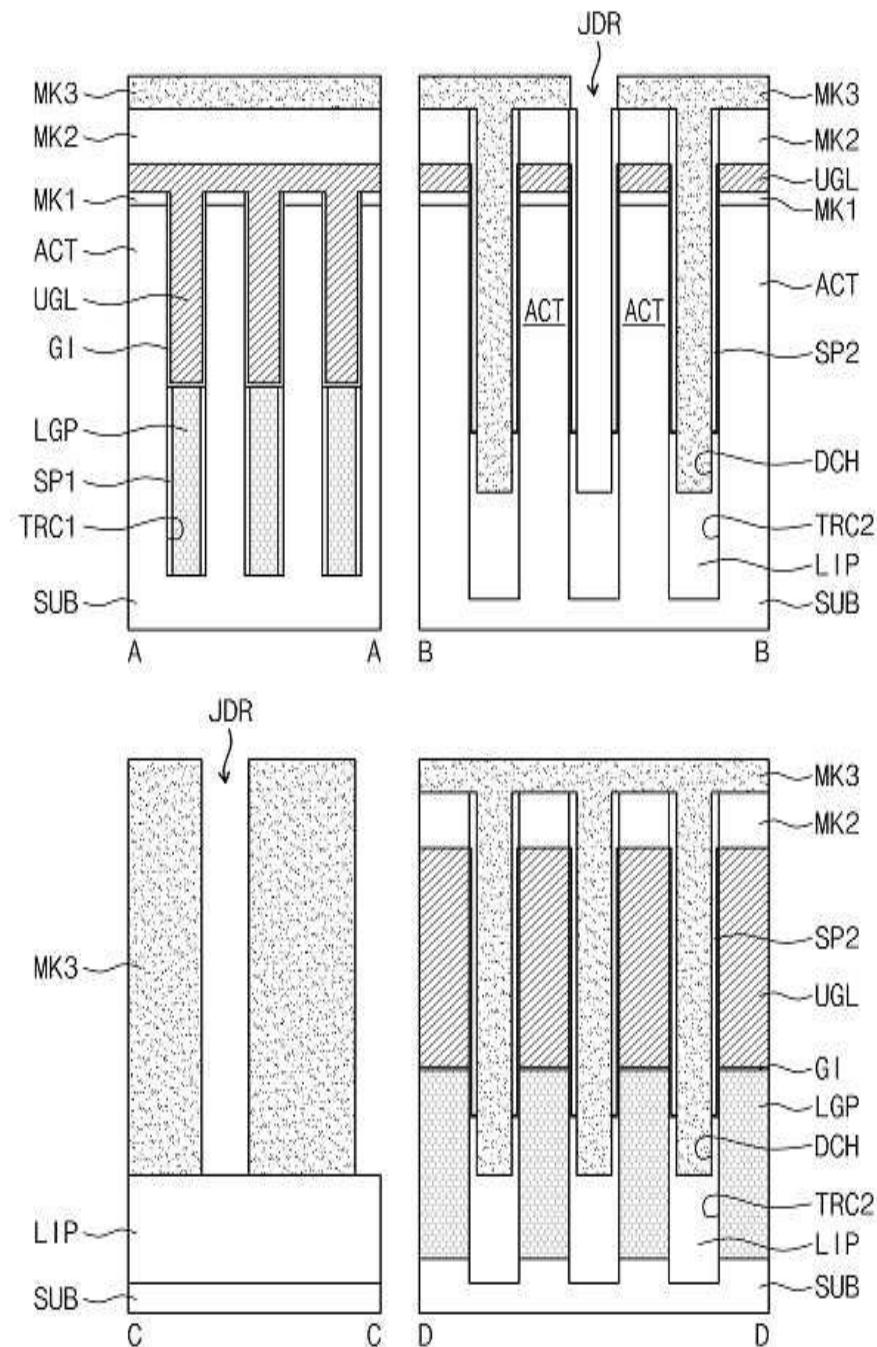

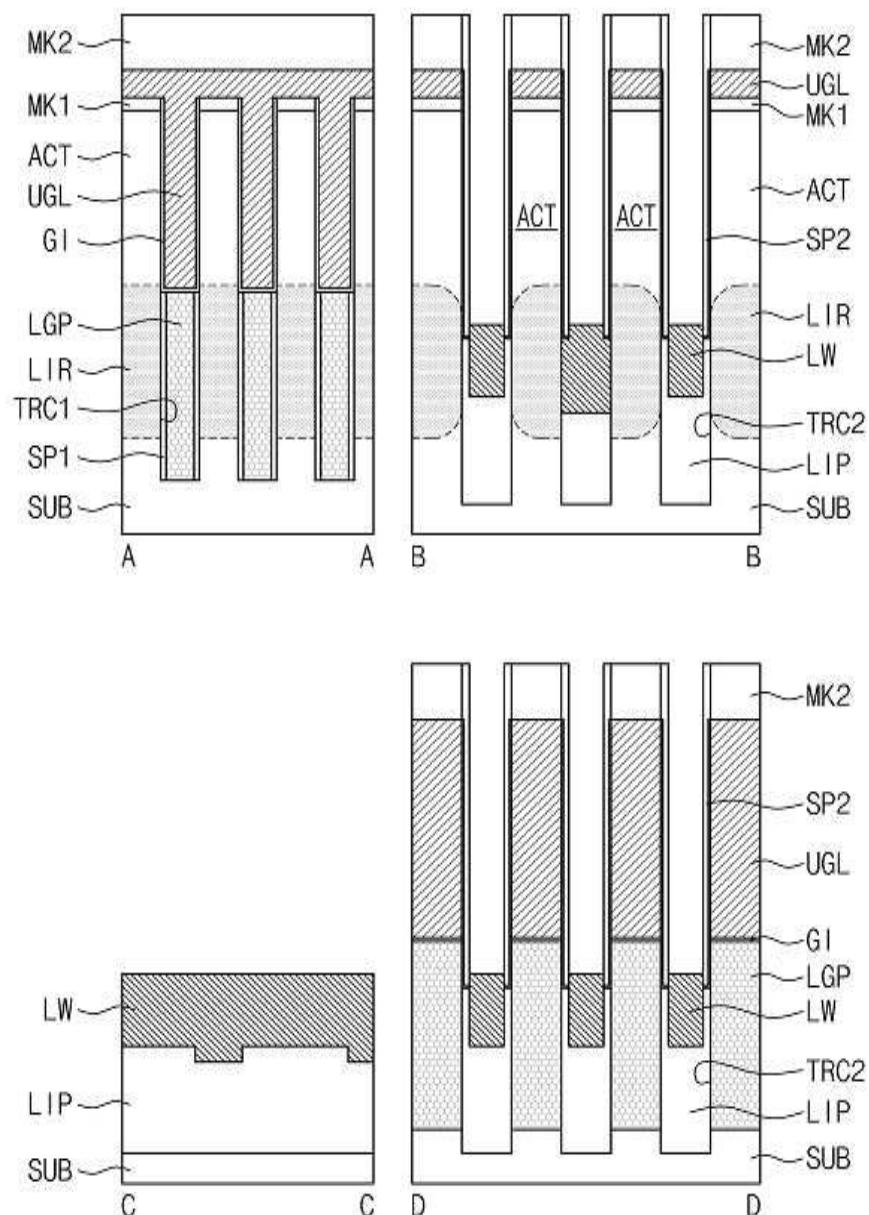

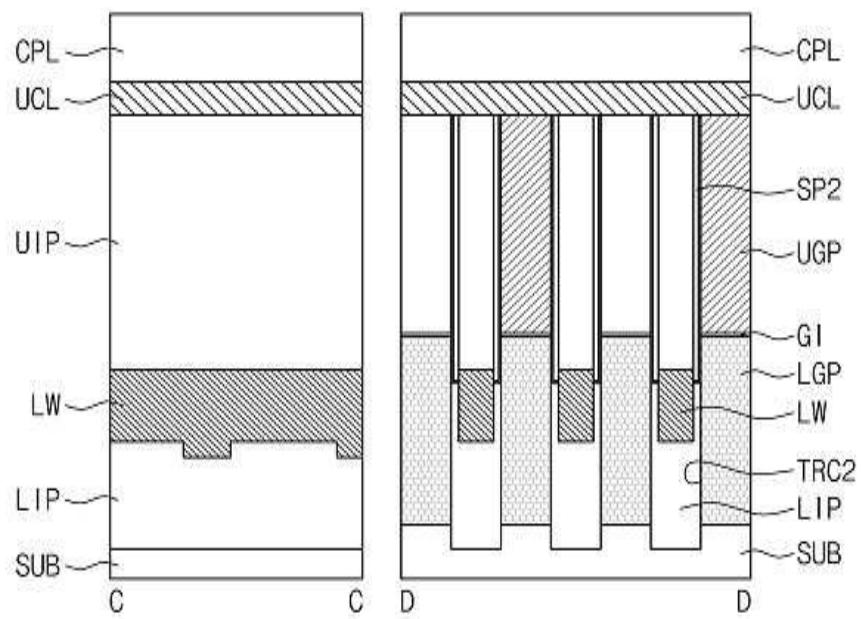

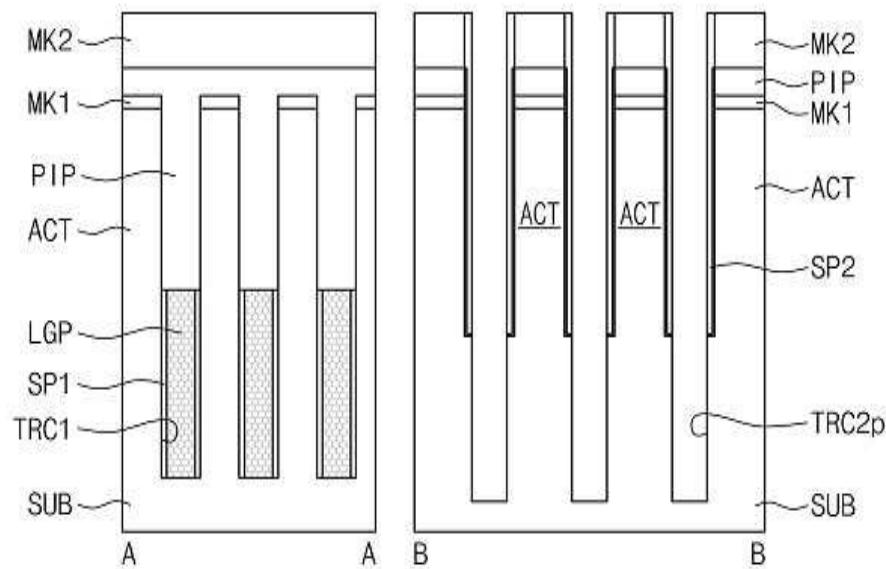

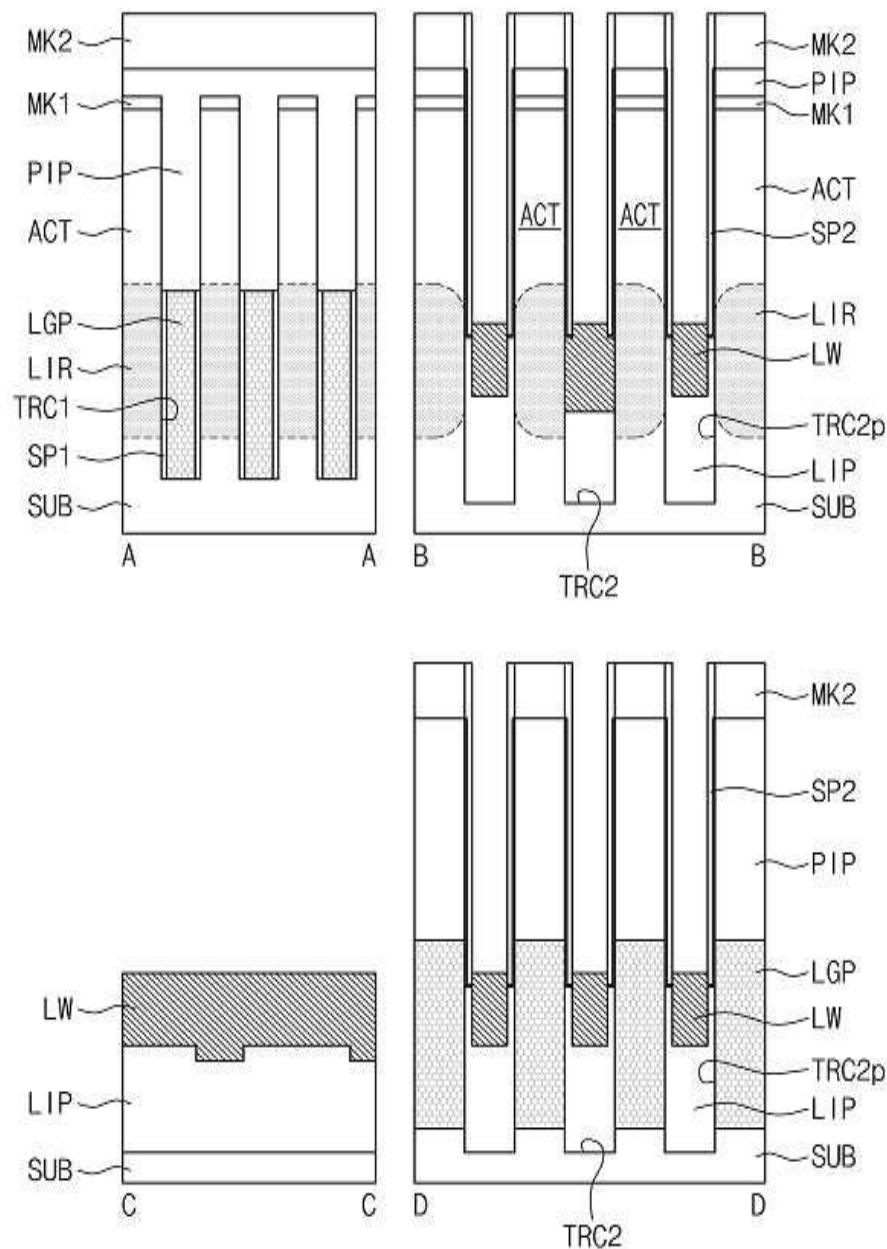

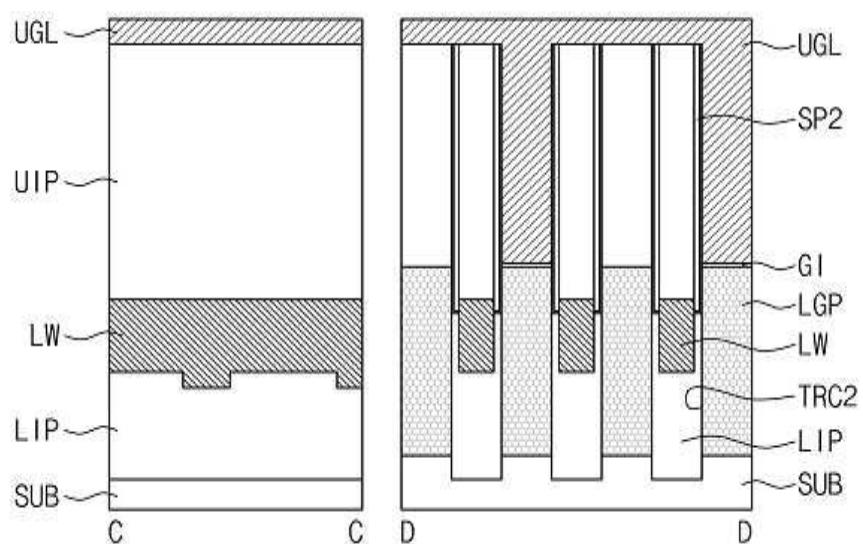

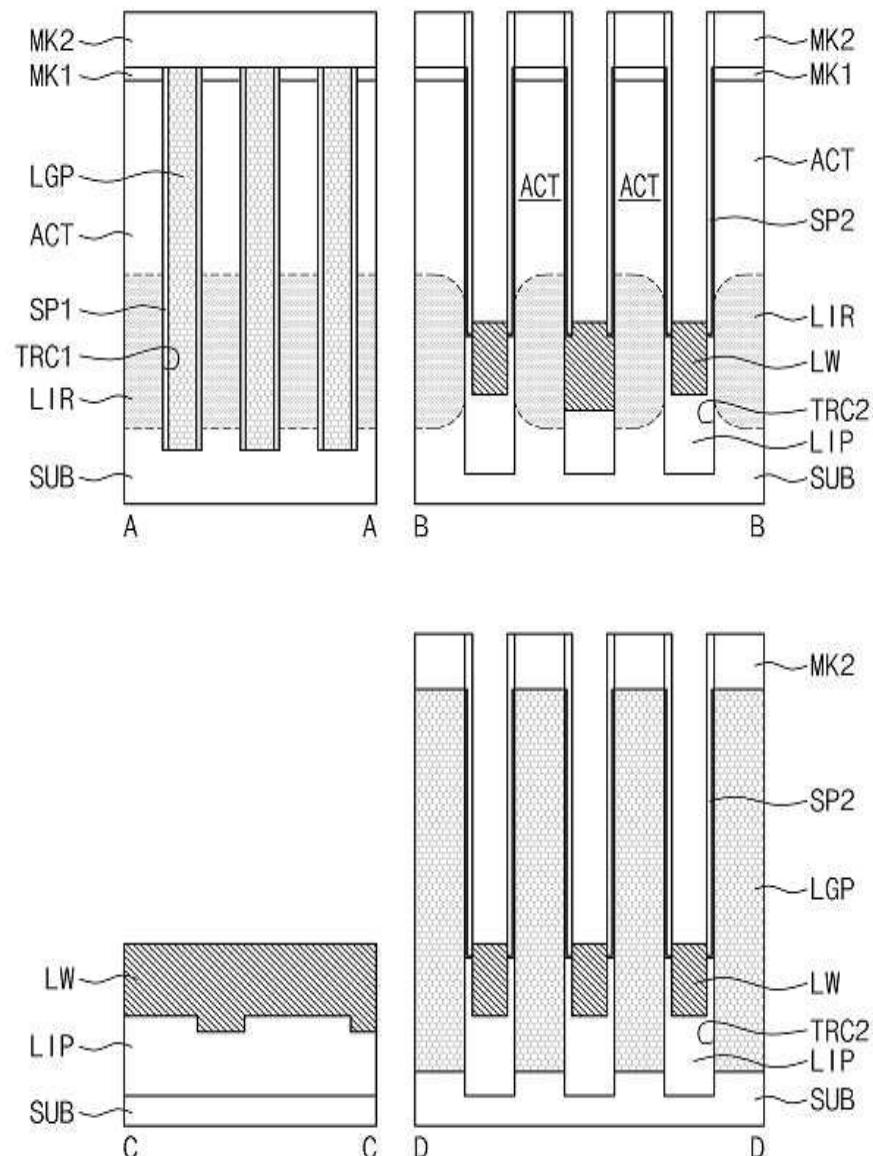

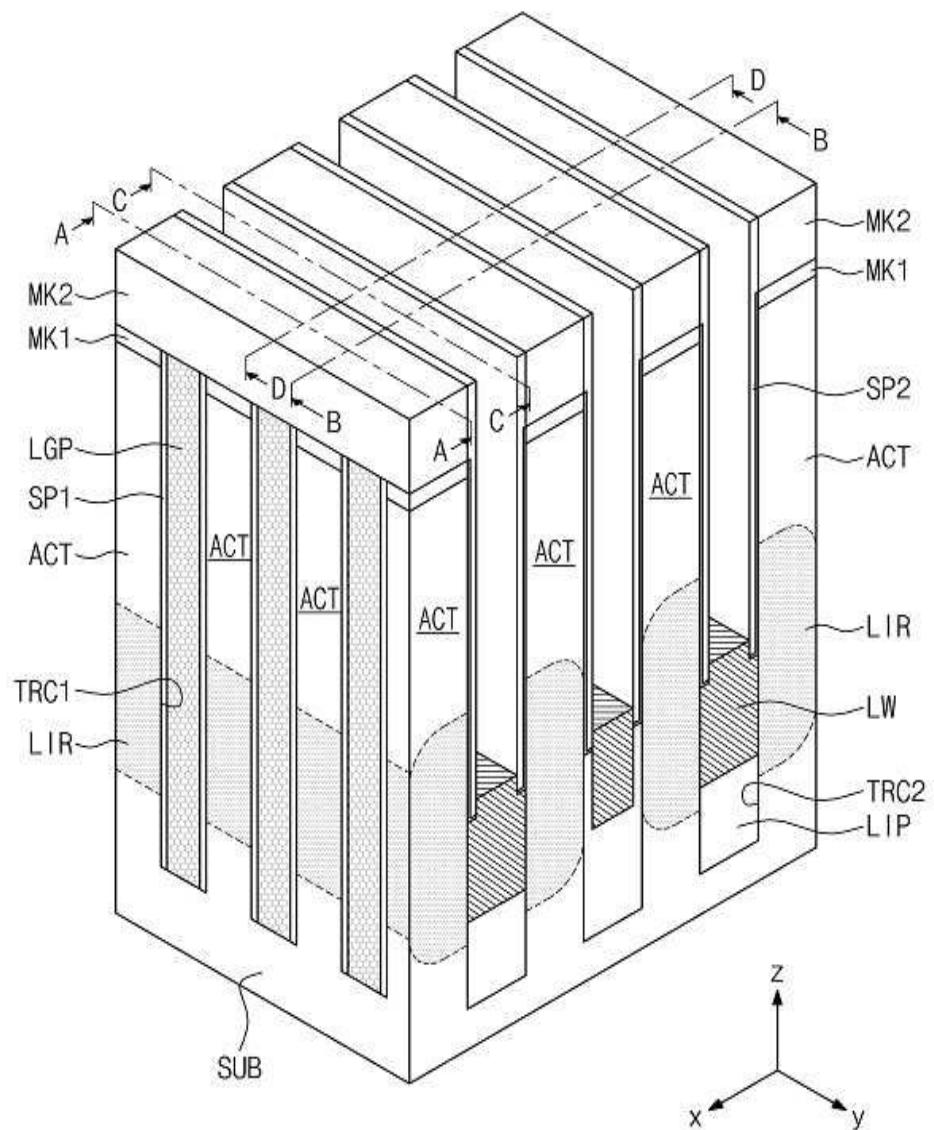

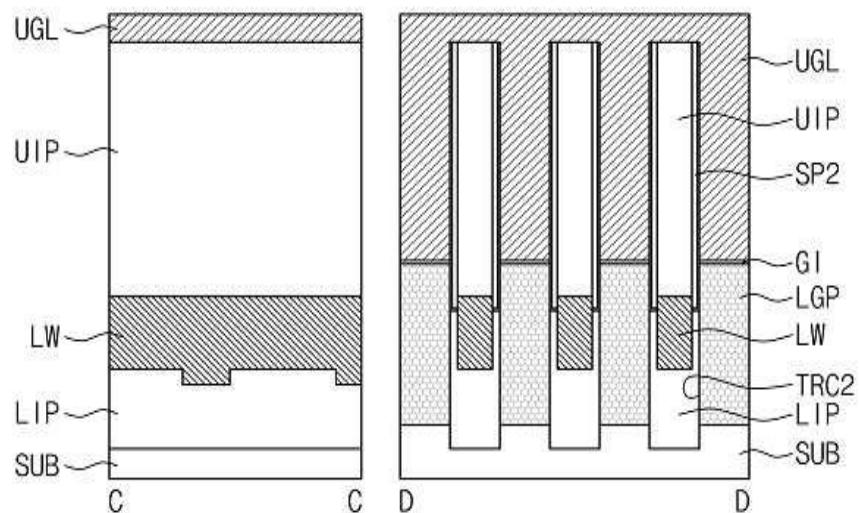

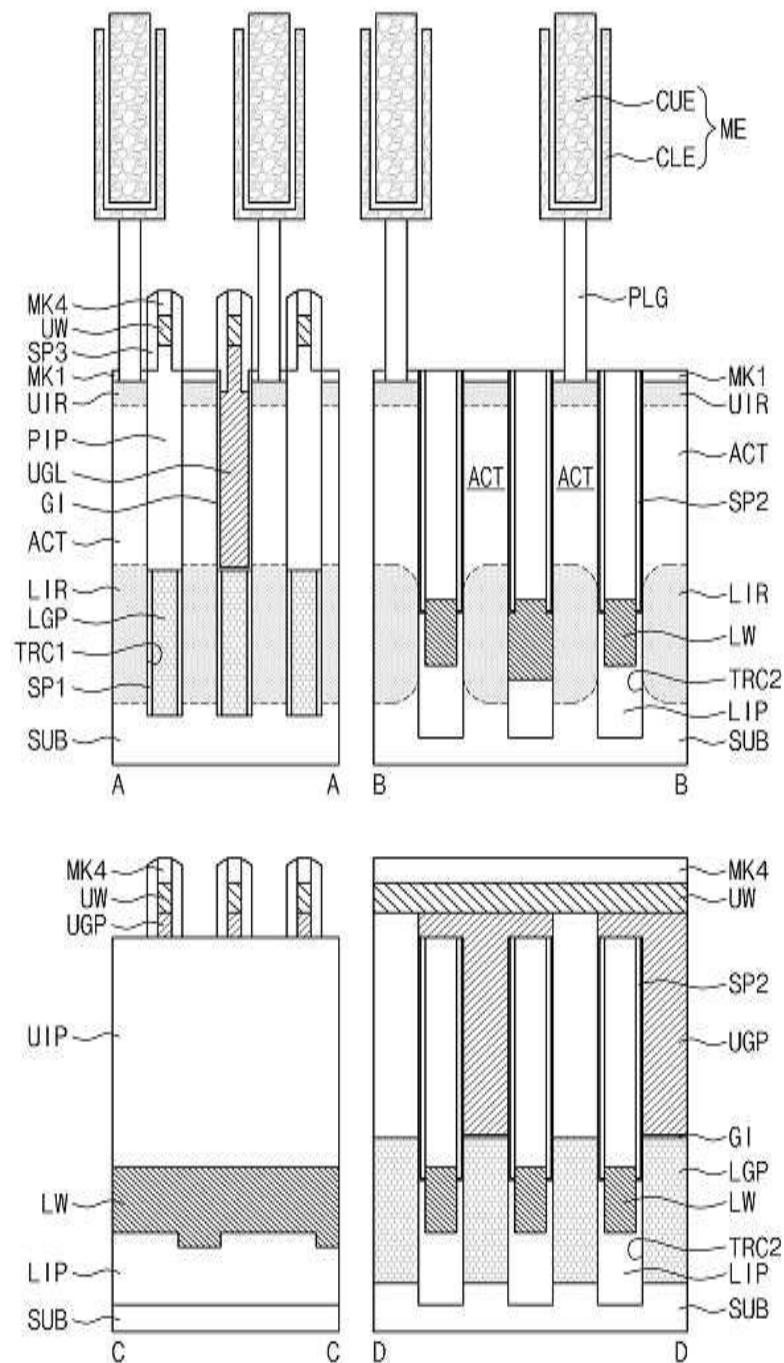

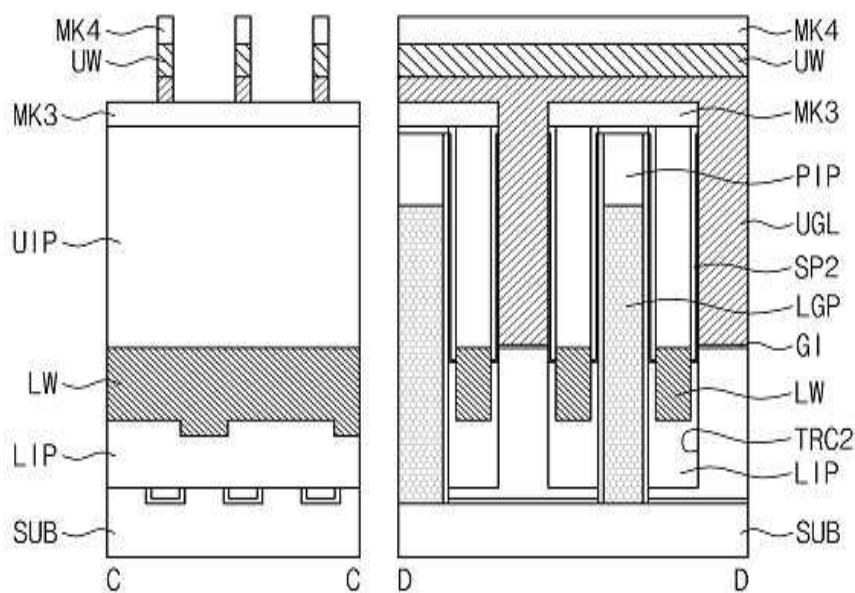

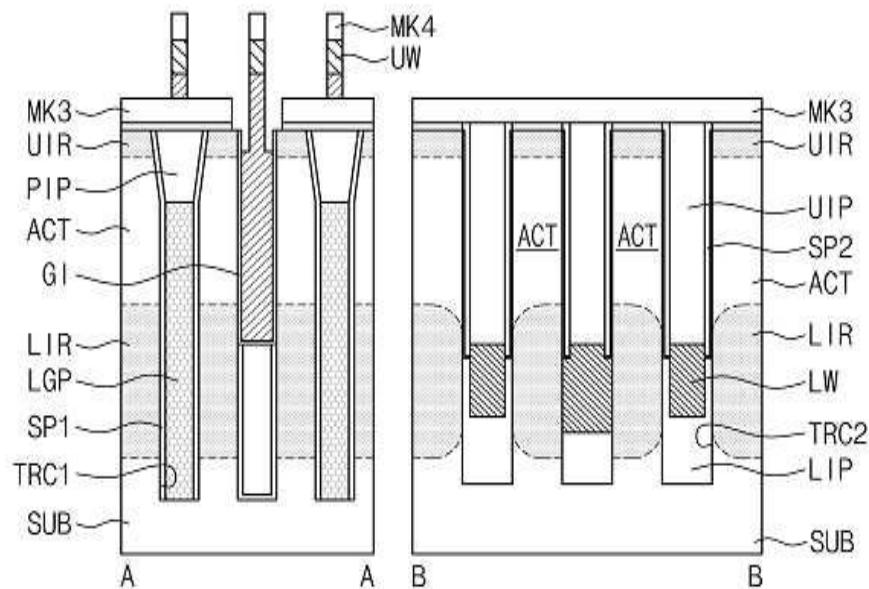

[0040] 도 4는 본 발명의 제 1 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 순서도이다. 도 5a 내지 도 19a는 본 발명의 제 1 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 단면도들이다. 도 5b 내지 도 19b는 본 발명의 제 1 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 사시도들이다.

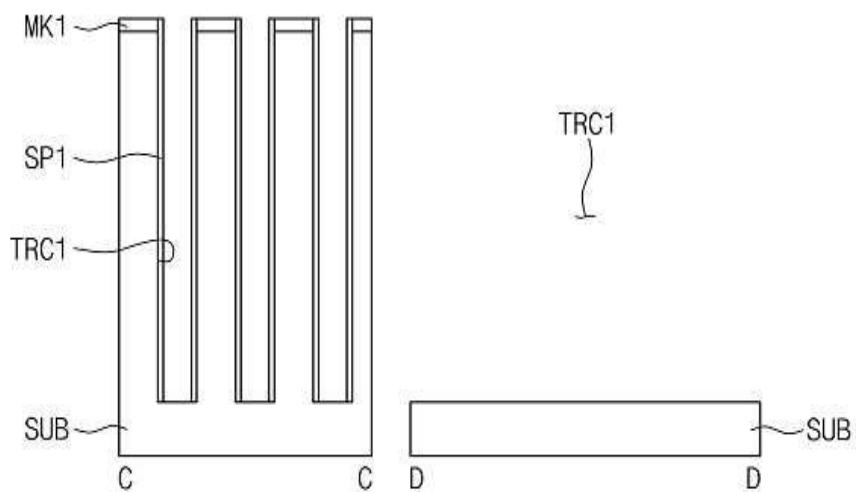

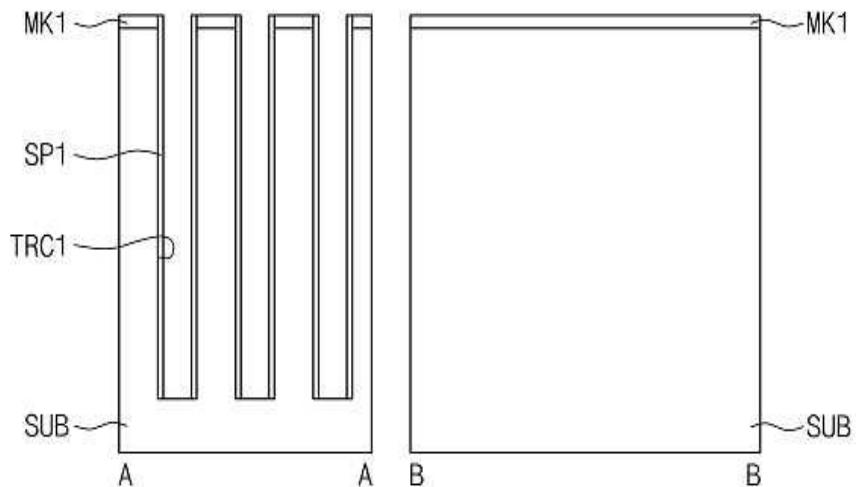

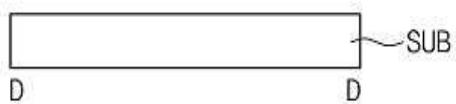

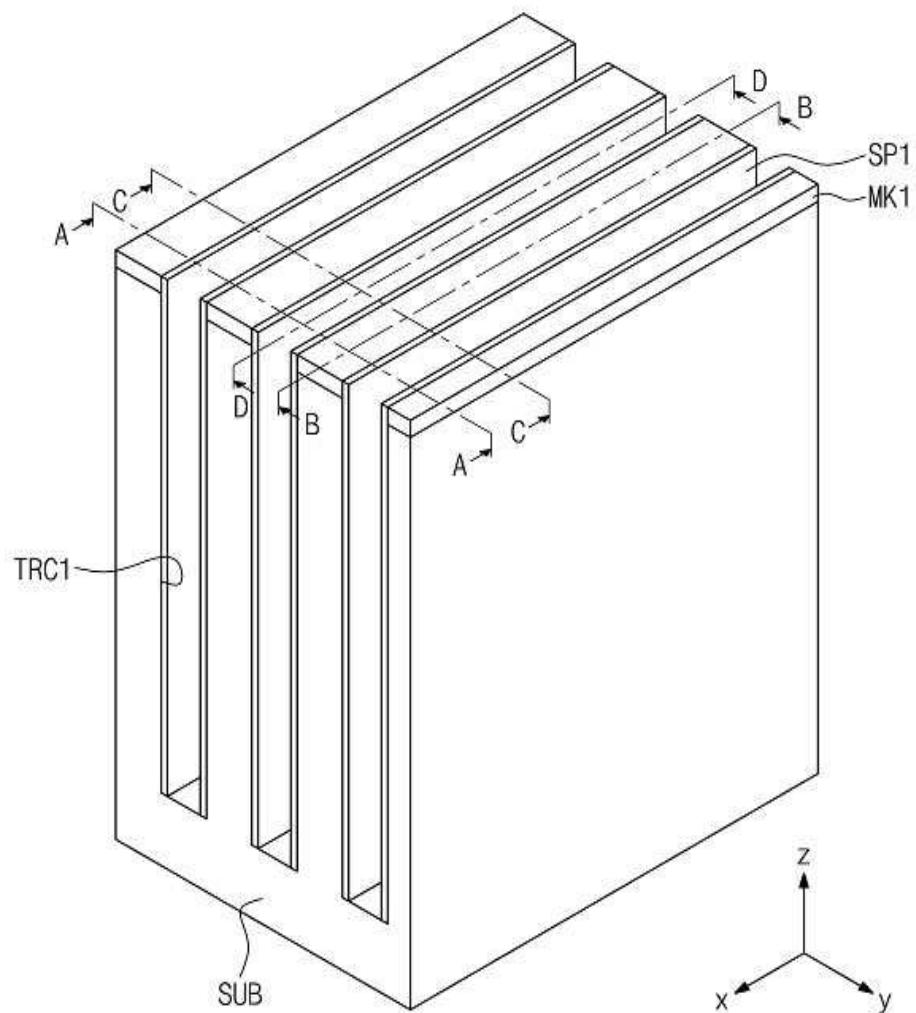

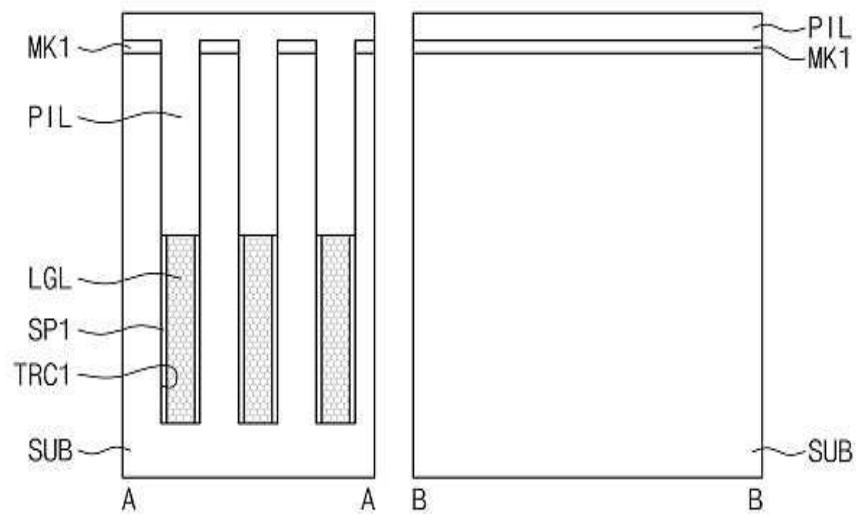

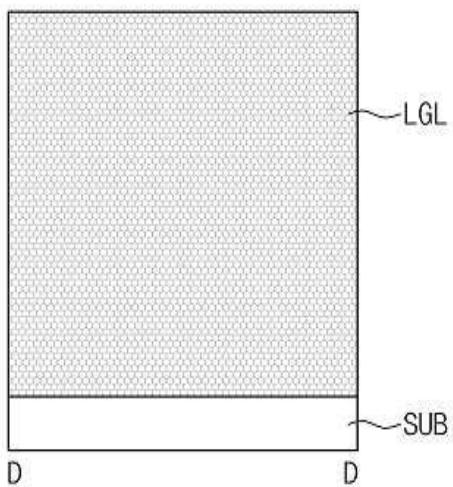

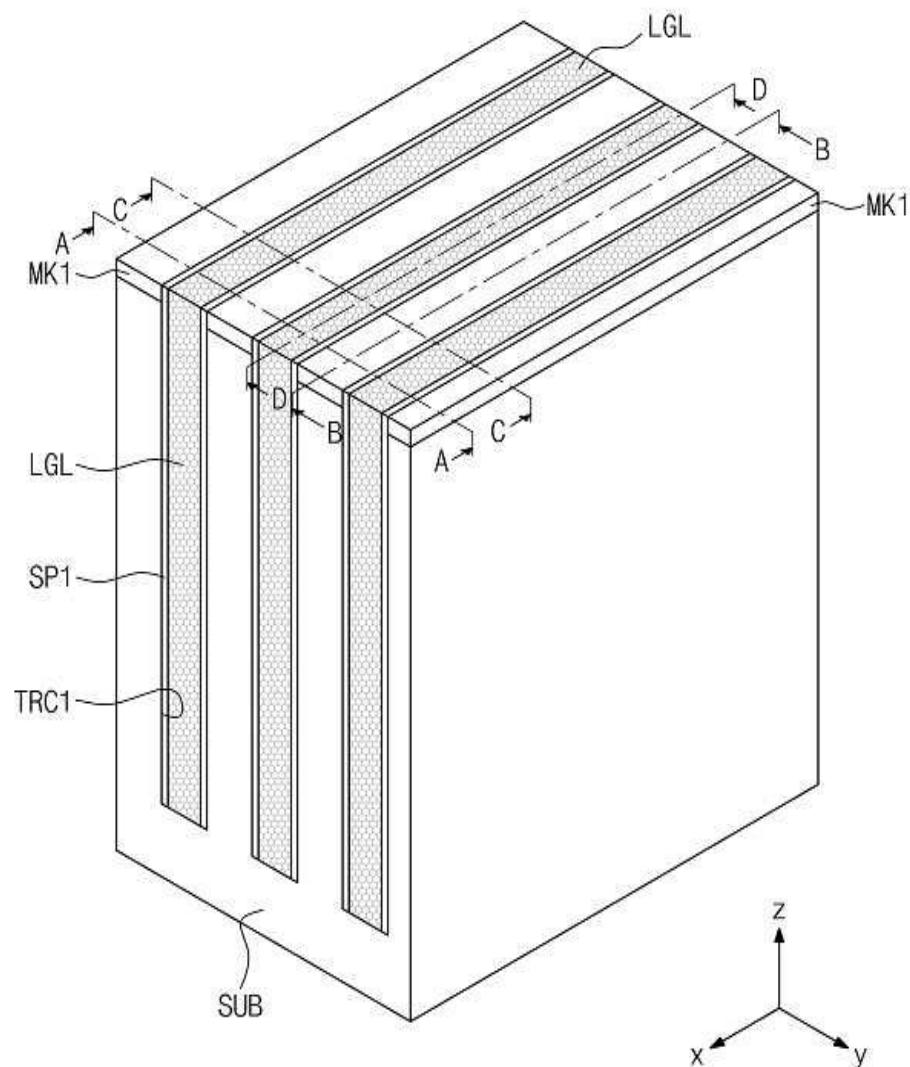

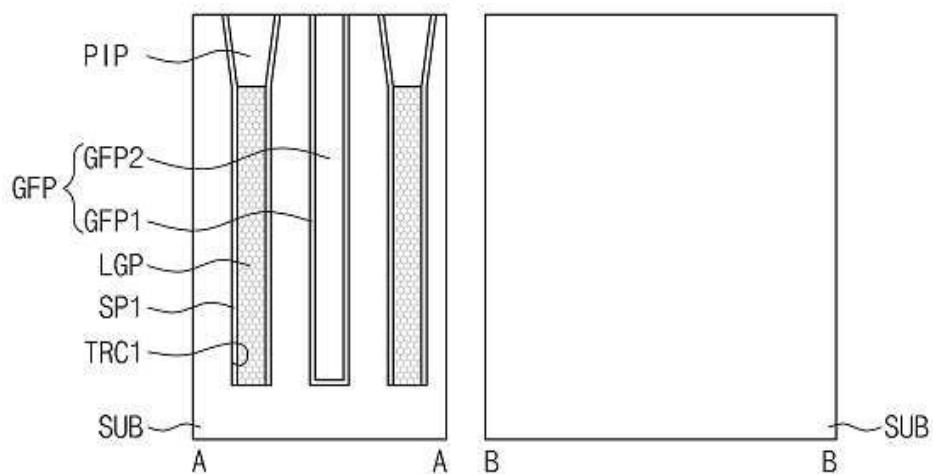

[0041] 도 4를 참조하면, 기판(SUB)을 패터닝하여 제 1 트렌치들(TRC1)을 형성한 후(S11), 상기 제 1 트렌치들(TRC1) 내에 하부 게이트막(LGL)을 형성한다(S12).

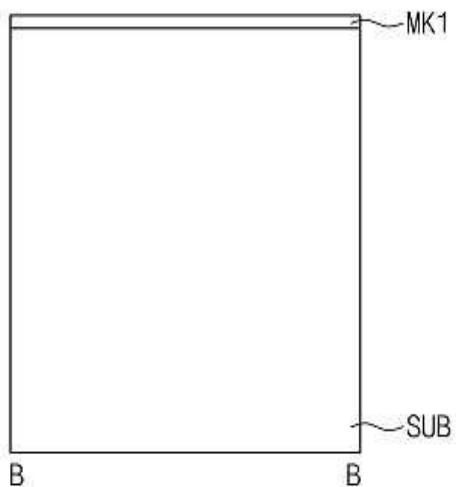

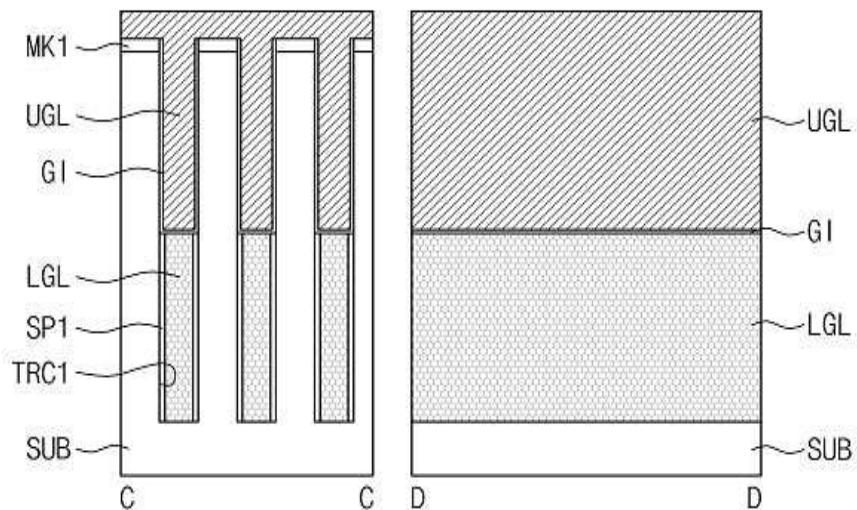

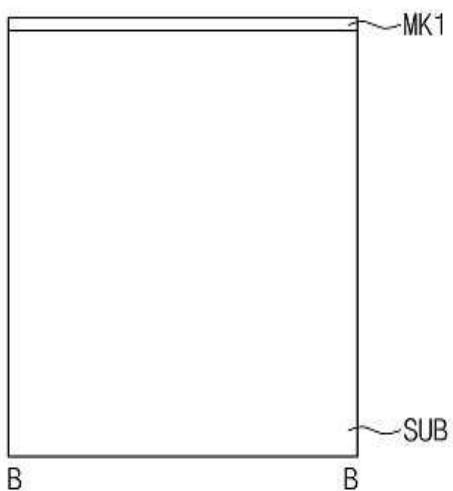

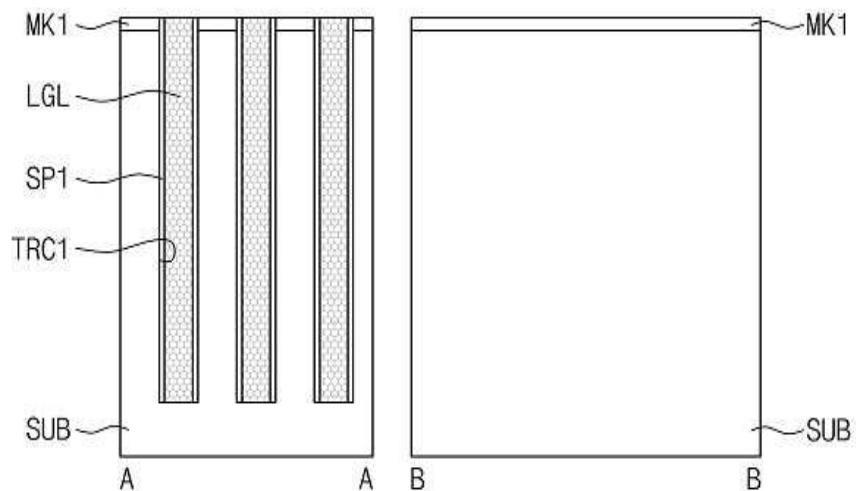

[0042] 상기 제 1 트렌치들(TRC1)은 제 1 방향(이하, x 방향)에 평행하게 형성될 수 있다. 이 단계(S11)는 도 5a 및 도 5b에 도시된 것처럼 상기 x 방향에 평행한 장축을 갖는 제 1 마스크 패턴들(MK1)을 형성한 후, 이를 식각 마스크로 사용하여 상기 기판(SUB)을 식각하는 단계를 포함할 수 있다.

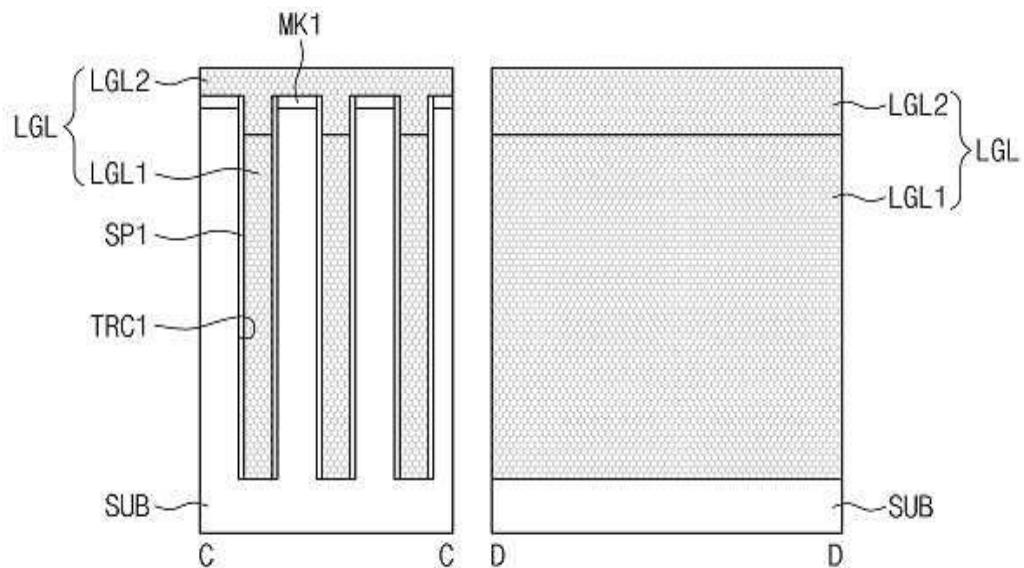

[0043] 상기 하부 게이트막(LGL)은 상기 제 1 트렌치(TRC1)의 바닥에서는 상기 기판(SUB)에 직접 연결되고 상기 제 1 트렌치(TRC1)의 측벽으로부터는 이격되도록 형성될 수 있다. 이를 위해, 상기 하부 게이트막(LGL)과 상기 제 1 트렌치(TRC1)의 측벽들 사이에는 절연성 물질로 형성되는 제 1 스페이서(SP1)가 더 형성될 수 있다. 보다 구체적으로, 이 단계(S12)는, 도 6a 및 도 6b에 도시된 것처럼, 상기 제 1 트렌치(TRC1)의 측벽에 상기 제 1 트렌치(TRC1)의 바닥면을 노출시키는 상기 제 1 스페이서(SP1)를 형성한 후, 그 결과물 상에 상기 제 1 트렌치(TRC1)를 채우는 상기 하부 게이트막(LGL)을 형성하는 단계를 포함할 수 있다.

[0044] 상기 하부 게이트막(LGL)은 상기 기판(SUB)에 오직하게 연결될 수 있는 도전성 물질로 형성될 수 있다. 예를 들면, 상기 하부 게이트막(LGL)은 상기 기판(SUB)과 같은 도전형을 갖는 반도체 물질일 수 있다. 이에 더하여, 일부 실시예들에 따르면, 상기 하부 게이트막(LGL)은 상기 기판(SUB)보다 낮은 비저항을 갖는 물질로 형성될 수 있다. 예를 들면, 상기 하부 게이트막(LGL)은 상기 기판(SUB)과 같은 도전형을 가지면서 상기 기판(SUB)보다 더 높은 불순물 농도를 갖는 반도체 물질이거나, (금속 질화물과 같은) 장벽 금속막(barrier metal layer) 또는 (금속 또는 금속 실리사이드와 같은) 금속성 물질들 중의 적어도 하나를 포함할 수 있다.

[0045] 일부 실시예에 따르면, 상기 하부 게이트막(LGL)을 형성하는 단계는 적어도 두번의 구분되는 막-형성 단계들을

포함할 수 있다. 예를 들면, 도 6a 및 도 6b에 도시된 것처럼, 상기 하부 게이트막(LGL)은 상기 제 1 트렌치(TRC1)의 하부 영역 및 상부 영역을 차례로 채우는 제 1 하부 게이트막(LGL1) 및 제 2 하부 게이트막(LGL2)을 포함할 수 있다. 일 실시예에 따르면, 상기 제 1 하부 게이트막(LGL1)은 상기 제 1 스페이서(SP1)에 의해 노출된 상기 제 1 트렌치(TRC1)의 바닥면을 씨드로 사용하여 결정 성장되는 에피택시얼막이고, 상기 제 2 하부 게이트막(LGL2)은 중착 공정을 사용하여 형성되는 중착막일 수 있다. 상기 제 2 하부 게이트막(LGL2)이 형성될 경우, 그 결과물의 평탄도가 개선되어 후속 공정의 진행이 용이할 수 있지만, 다른 변형된 실시예들에 따르면 상기 제 2 하부 게이트막(LGL2)을 형성하는 단계는 생략될 수 있다. 즉, 상기 하부 게이트막(LGL)은 한번의 막 형성 단계를 통해 형성되는 에피택시얼막 또는 중착막일 수도 있다.

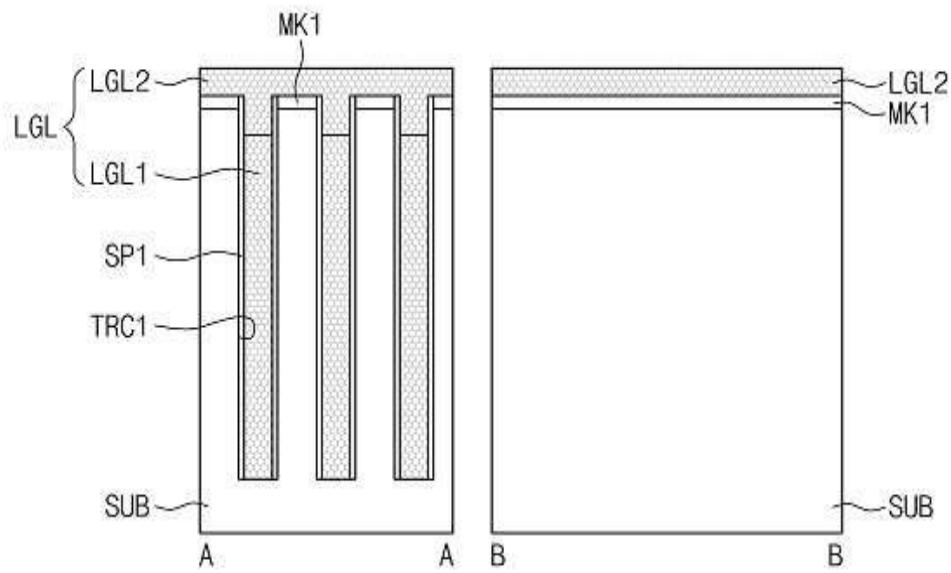

[0046] 다시 도 4를 참조하면, 상기 제 1 트렌치(TRC1)의 상부 영역에 상부 게이트막(UGL; upper gate layer)을 형성한다(S13). 이 단계(S13)는 상기 하부 게이트막(LGL) 및 상기 제 1 스페이서(SP1)를 식각하여 상기 제 1 트렌치(TRC1)의 상부 측벽을 노출시킨 후, 그 결과물 상에 게이트 절연막(GI; gate insulator) 및 상기 상부 게이트막(UGL)을 형성하는 단계를 포함할 수 있다.

[0047] 상기 제 1 트렌치(TRC1)의 상부 측벽을 노출시키는 단계는 상기 하부 게이트막(LGL)을 전면 식각하여 상기 제 1 스페이서(SP1)의 내측벽을 노출시킨 후, 상기 제 1 스페이서(SP1)의 노출된 부분을 제거하는 단계를 포함할 수 있다. 상기 하부 게이트막(LGL)을 전면식각하는 단계는, 상기 제 1 스페이서(SP1)에 대해 식각 선택성을 갖는, 등방성 또는 이방성 식각의 방법을 사용하여 실시될 수 있다. 또한, 이 단계는 상기 하부 게이트막(LGL)의 상부 면이 상기 제 1 마스크 패턴(MK1)의 바닥면 또는 상기 기판(SUB)의 상부면보다 낮아지도록 실시될 수 있다. 이에 따라, 상술한 것처럼, 상기 제 1 스페이서(SP1)의 내측벽은 상기 제 1 트렌치(TRC1)의 상부 영역에서 다시 노출될 수 있다. 상기 제 1 스페이서(SP1)를 제거하는 단계는, 상기 기판(SUB) 및 상기 하부 게이트막(LGL)에 대해 식각 선택성을 갖는, 등방성 또는 이방성 식각의 방법을 사용하여 실시될 수 있다.

[0048] 상기 게이트 절연막(GI)은, 상기 제 1 스페이서(SP1)가 제거됨으로써 노출되는, 상기 제 1 트렌치(TRC1)의 상부 내벽 상에 형성될 수 있다. 이에 더하여, 상기 게이트 절연막(GI)은 상기 하부 게이트막(LGL)의 상부면에도 형성될 수 있다. 결과적으로, 상기 게이트 절연막(GI)은 상기 하부 및 상부 게이트막들(LGL, UGL) 사이에 개재될 수도 있다. 상기 게이트 절연막(GI)을 형성하는 단계는 상기 기판(SUB) 및/또는 상기 하부 게이트막(LGL)의 노출된 표면을 열산화시키는 방법을 통해 형성될 수 있다. 예를 들어, 상기 기판(SUB) 및/또는 상기 하부 게이트막(LGL)이 실리콘인 경우, 상기 게이트 절연막(GI)은 열산화 공정을 통해 형성되는 실리콘 산화막일 수 있다. 하지만, 변형된 실시예에 따르면, 상기 게이트 절연막(GI)은 화학기상증착 또는 원자층증착 기술을 사용하여 형성되는 박막일 수 있으며, 그 종류는 실리콘 산화막 또는 실리콘산화막보다 높은 유전률을 갖는 고유전막들 중의 한가지일 수 있다.

[0049] 상기 상부 게이트막(UGL)은 도전성 물질들 중의 적어도 하나를 포함할 수 있다. 예를 들면, 상기 상부 게이트막(UGL)은 도핑된 실리콘막, 금속 질화물들 또는 금속물질들 중의 적어도 하나를 포함할 수 있다. 상기 상부 게이트막(UGL)은 상기 게이트 절연막(GI)이 형성된 상기 제 1 트렌치(TRC1)를 채우도록 형성될 수 있으며, 그 형성 방법은 화학적기상증착 기술 또는 물리적기상증착 기술들 중의 하나일 수 있다. 이 경우, 상기 상부 게이트막(UGL)은 상기 제 1 마스크 패턴(MK1) 상에 잔존할 수 있다. 본 발명의 변형된 실시예들에 따르면, 상기 상부 게이트막(UGL)을 형성한 후, 상기 제 1 마스크 패턴(MK1) 또는 상기 기판(SUB)의 상부면이 노출되도록 상기 상부 게이트막(UGL) 및/또는 상기 제 1 마스크 패턴(MK1)을 전면식각하는 단계가 더 실시될 수 있다.

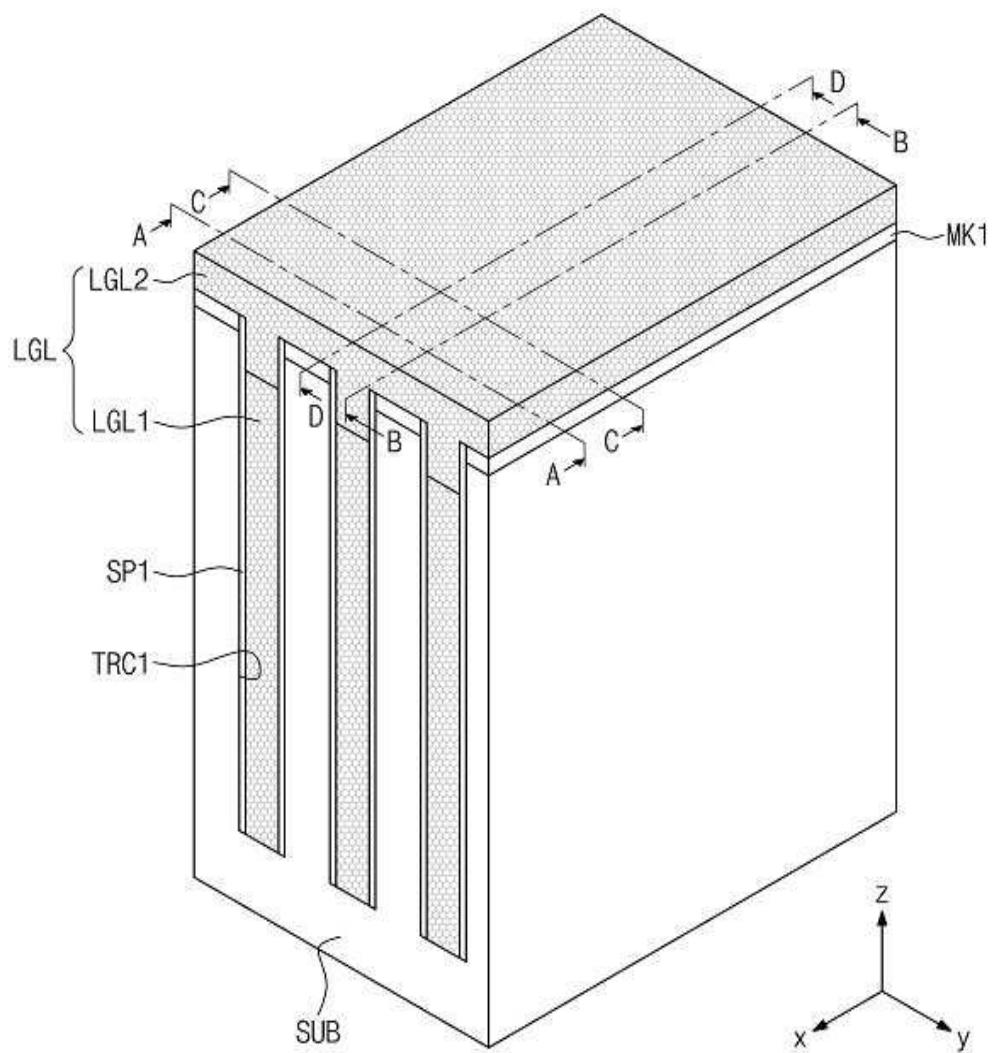

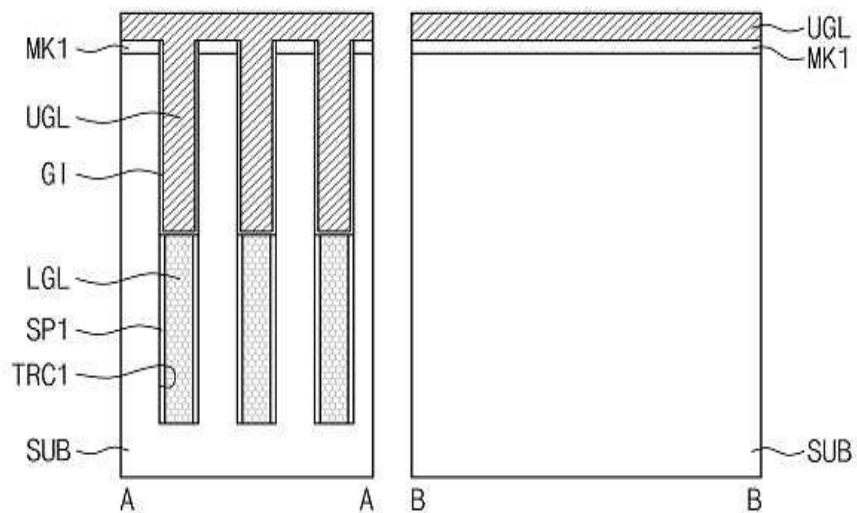

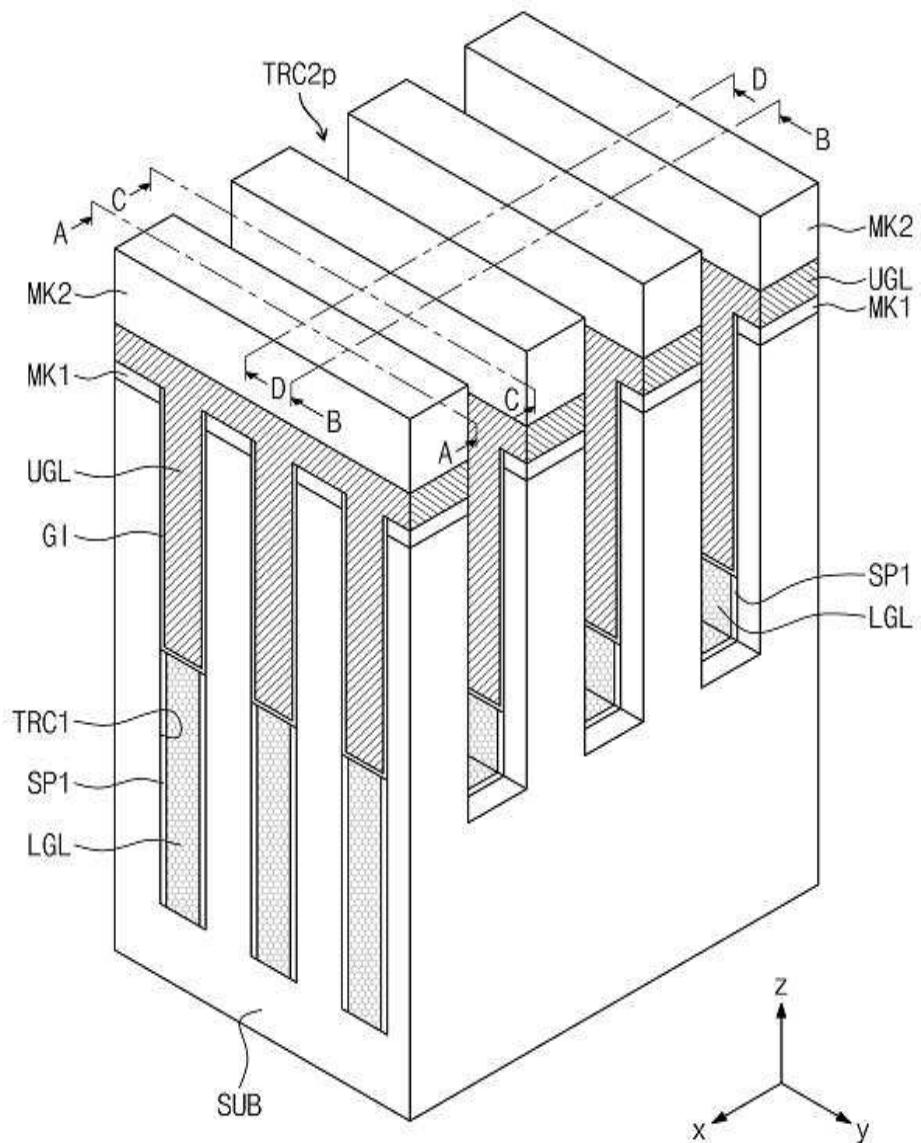

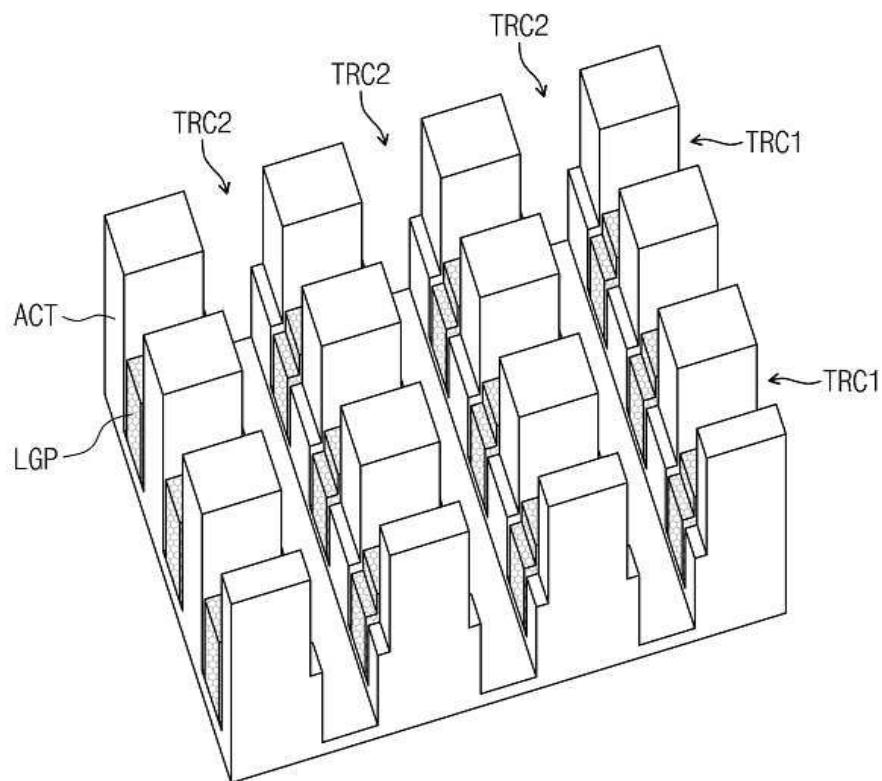

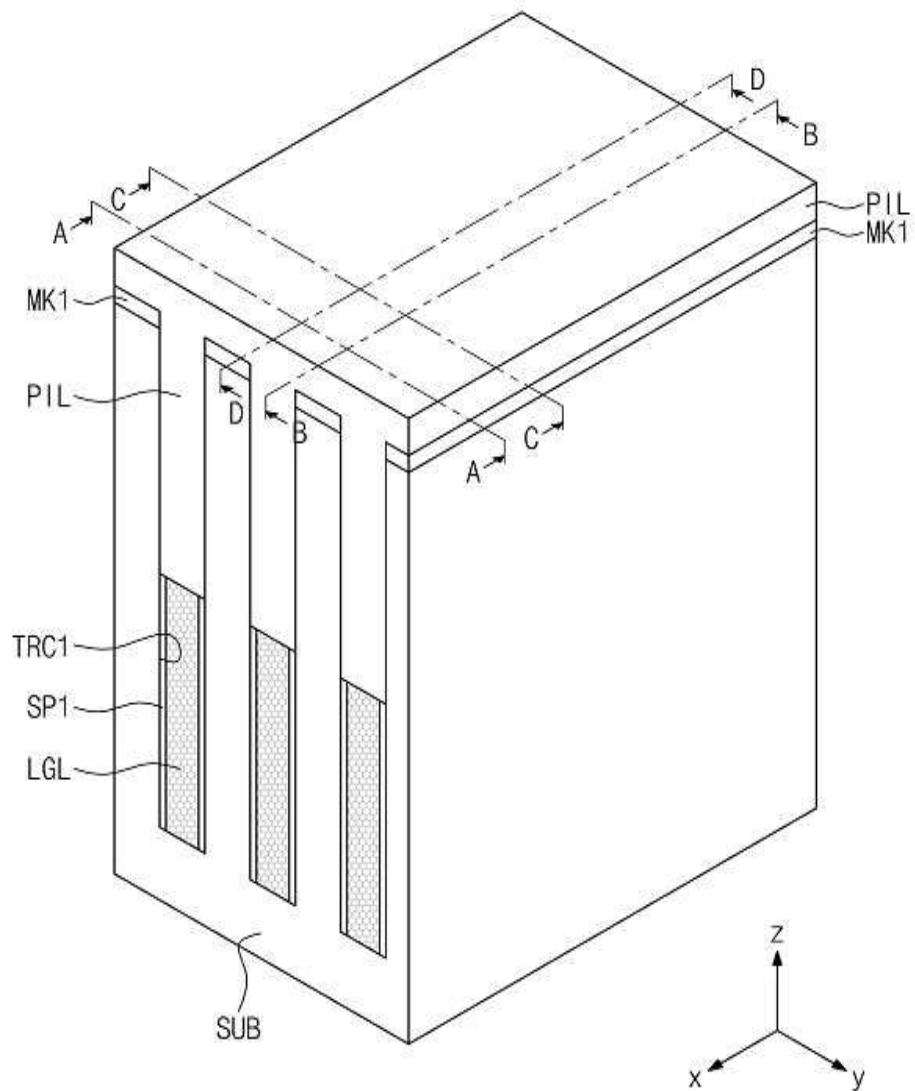

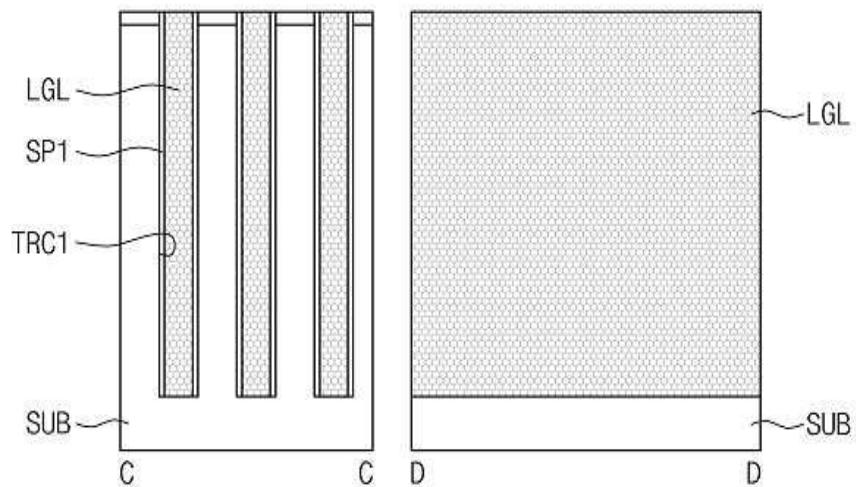

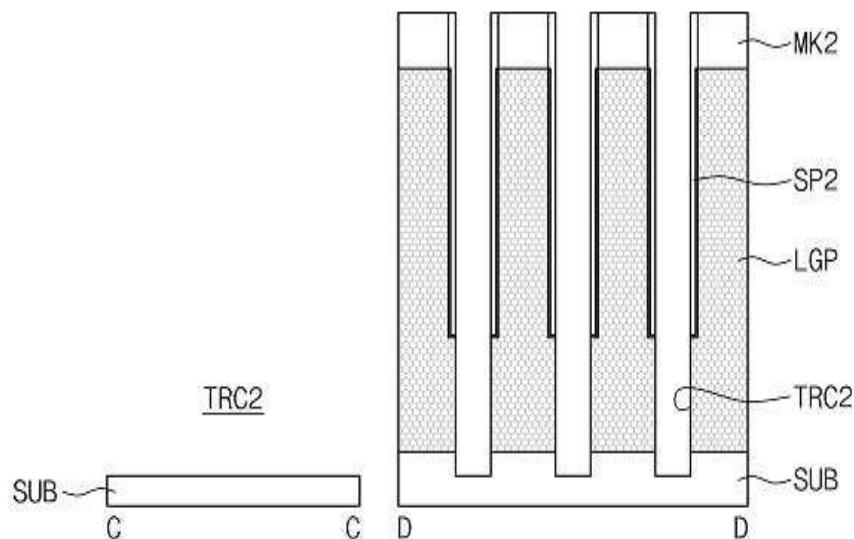

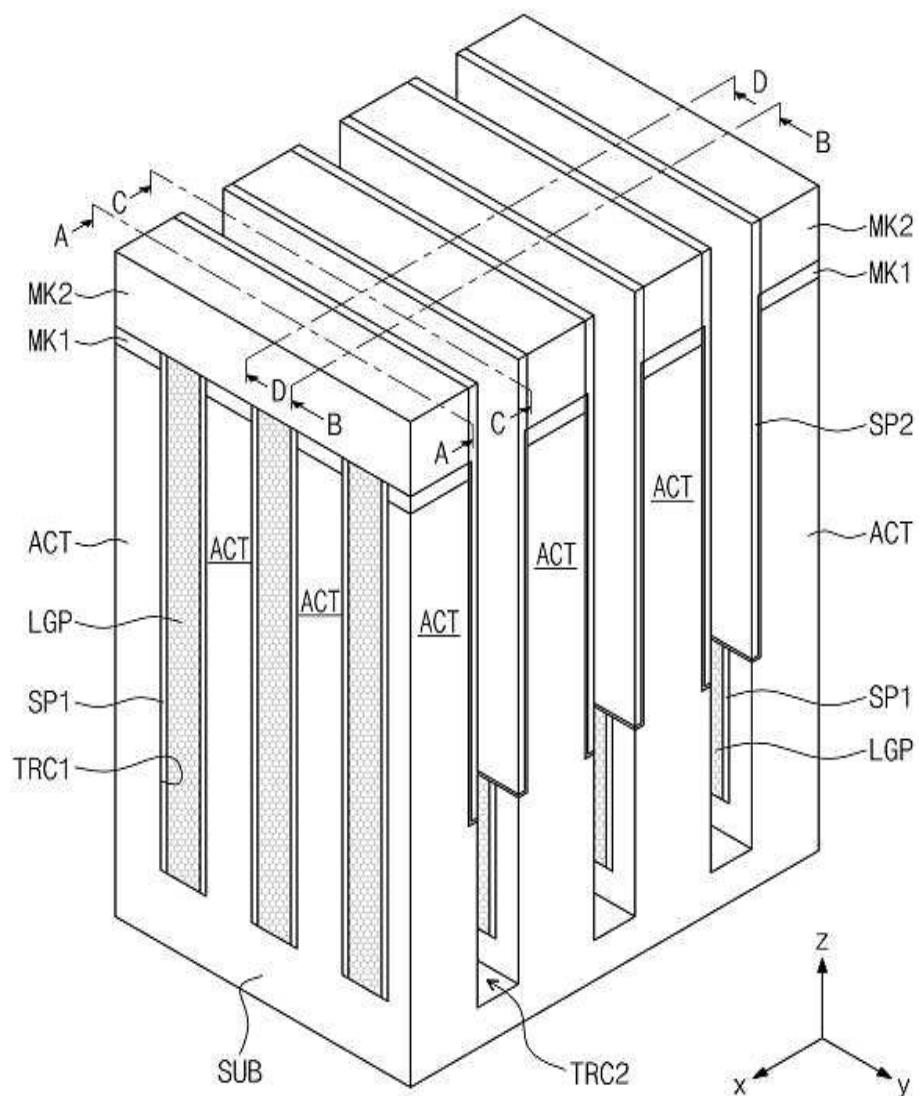

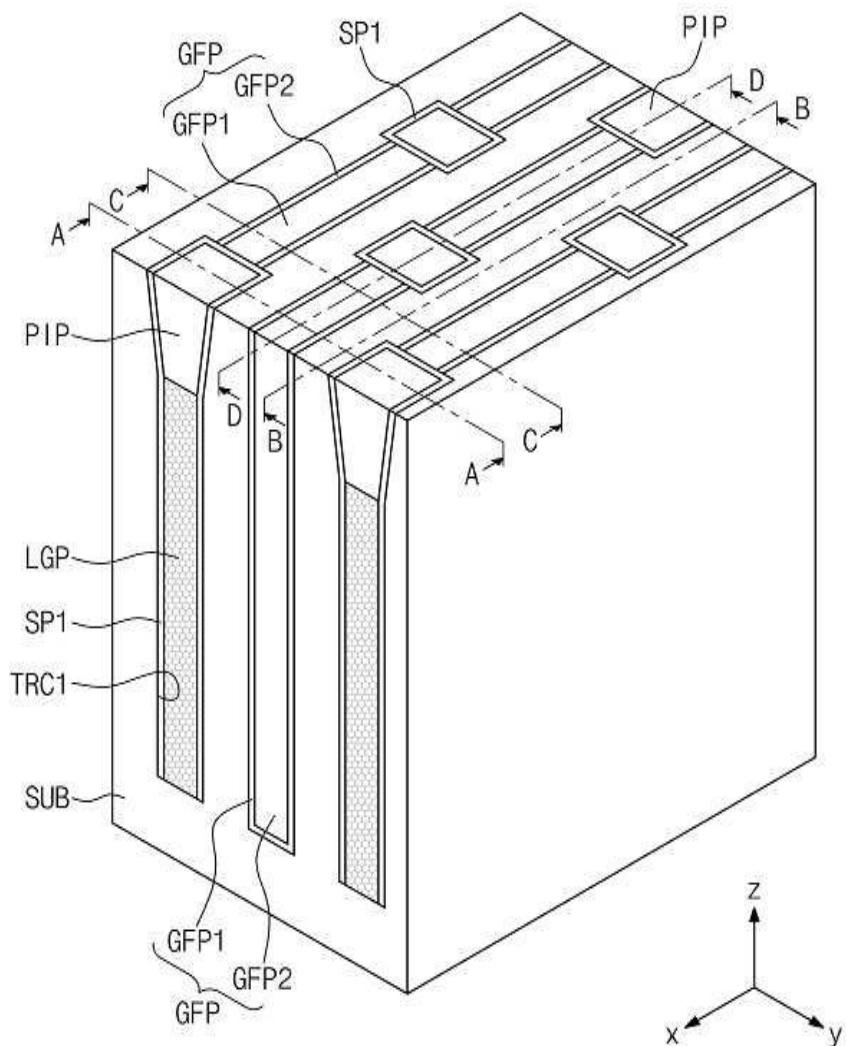

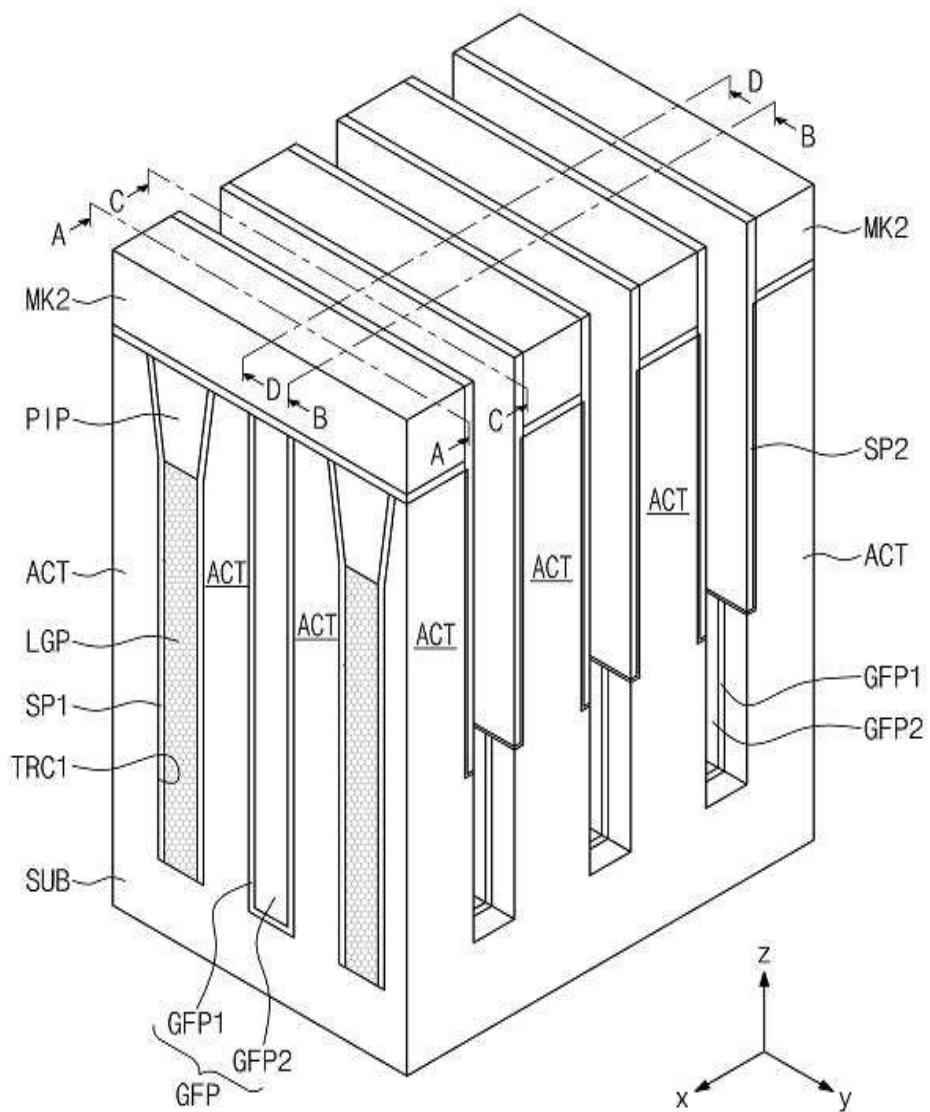

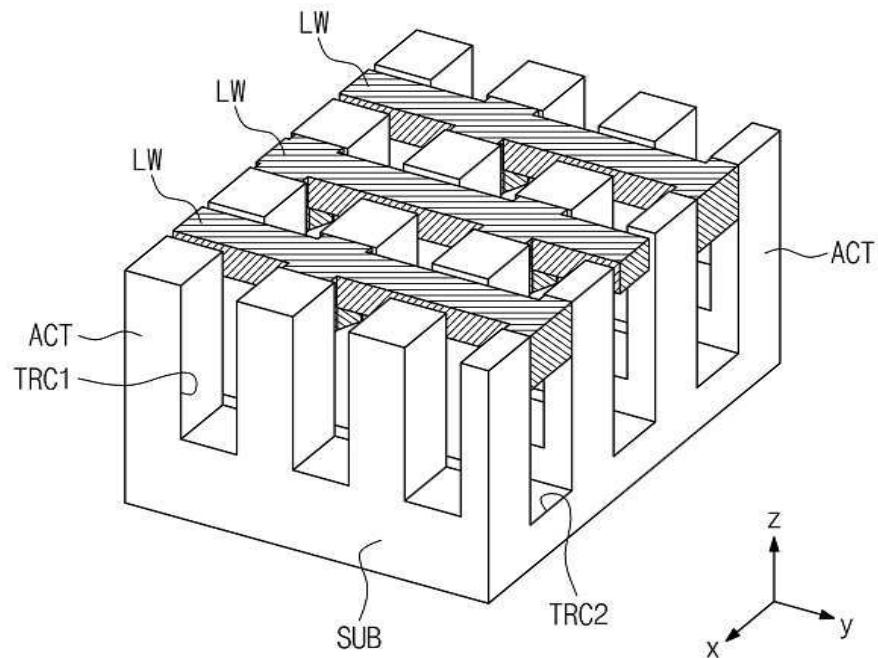

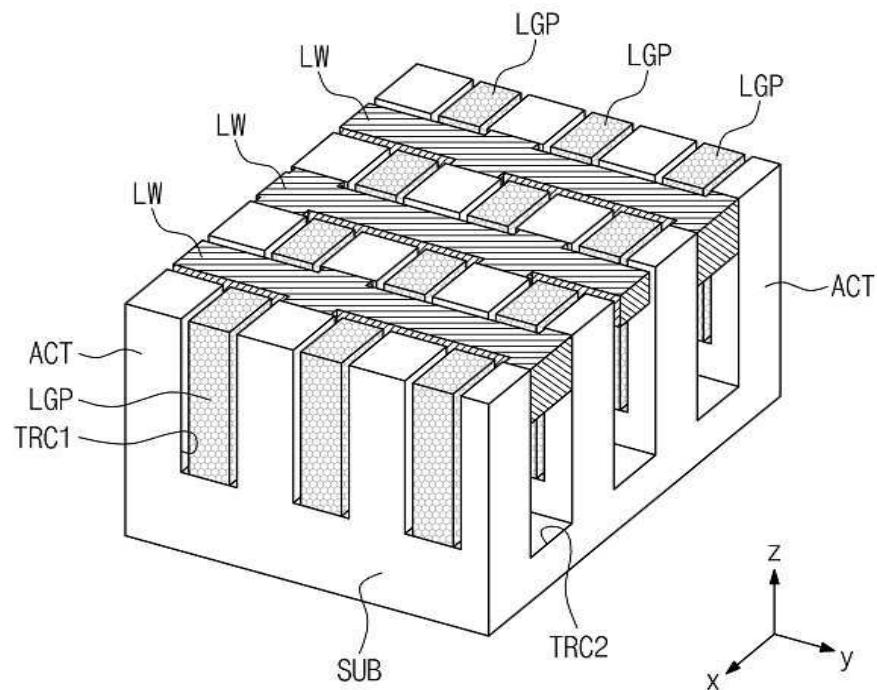

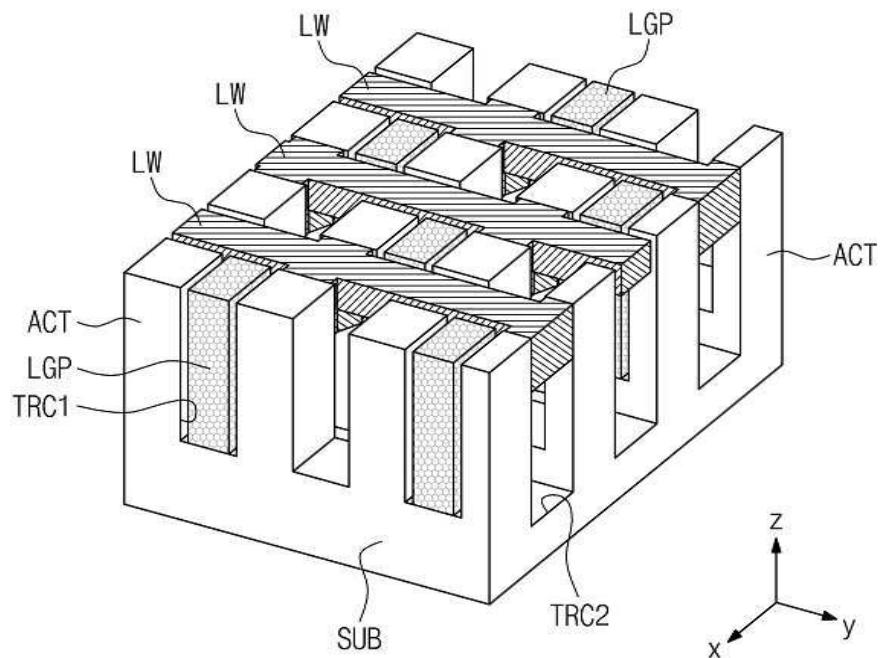

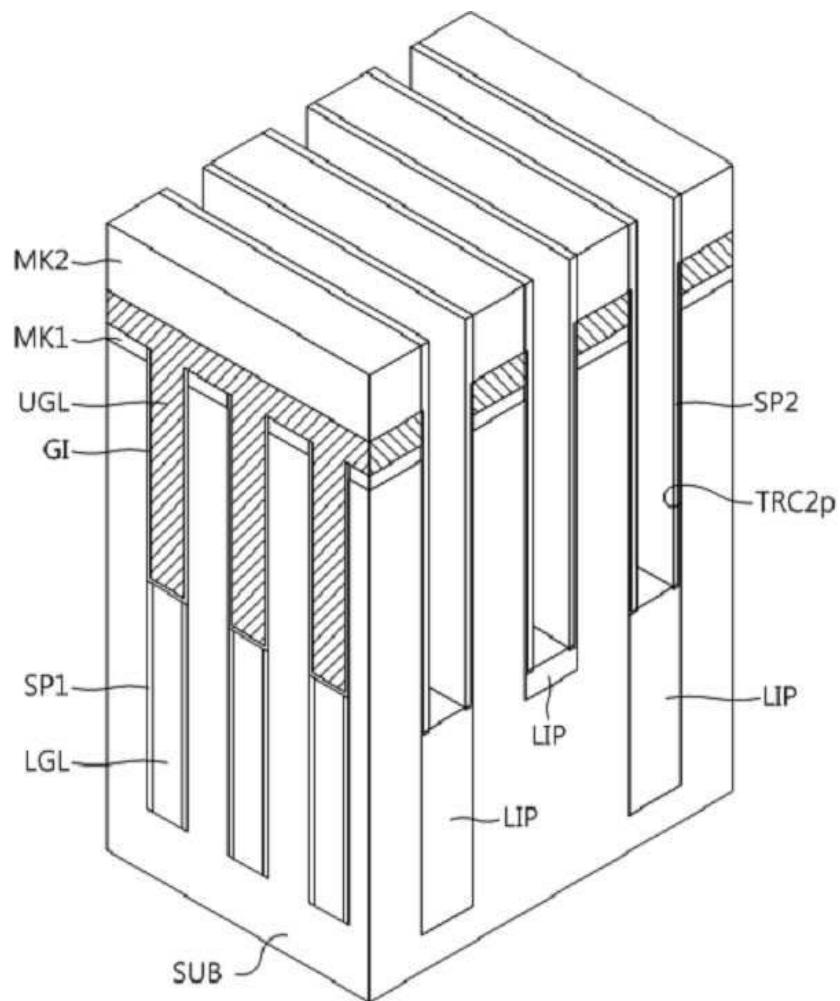

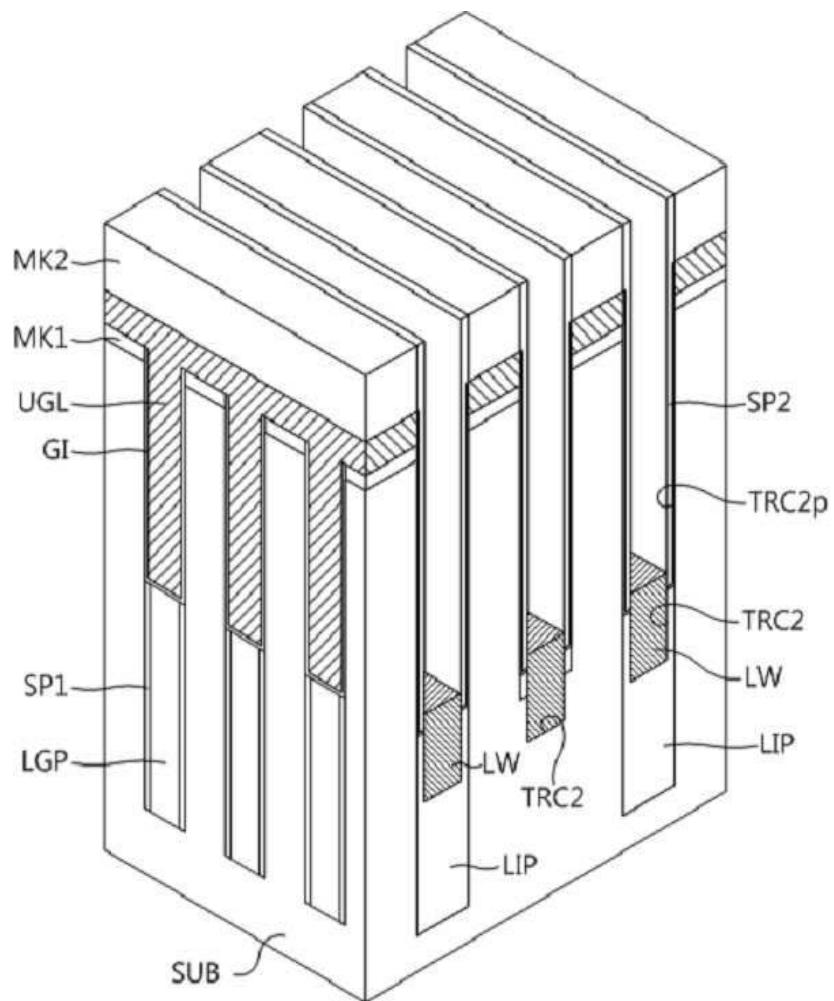

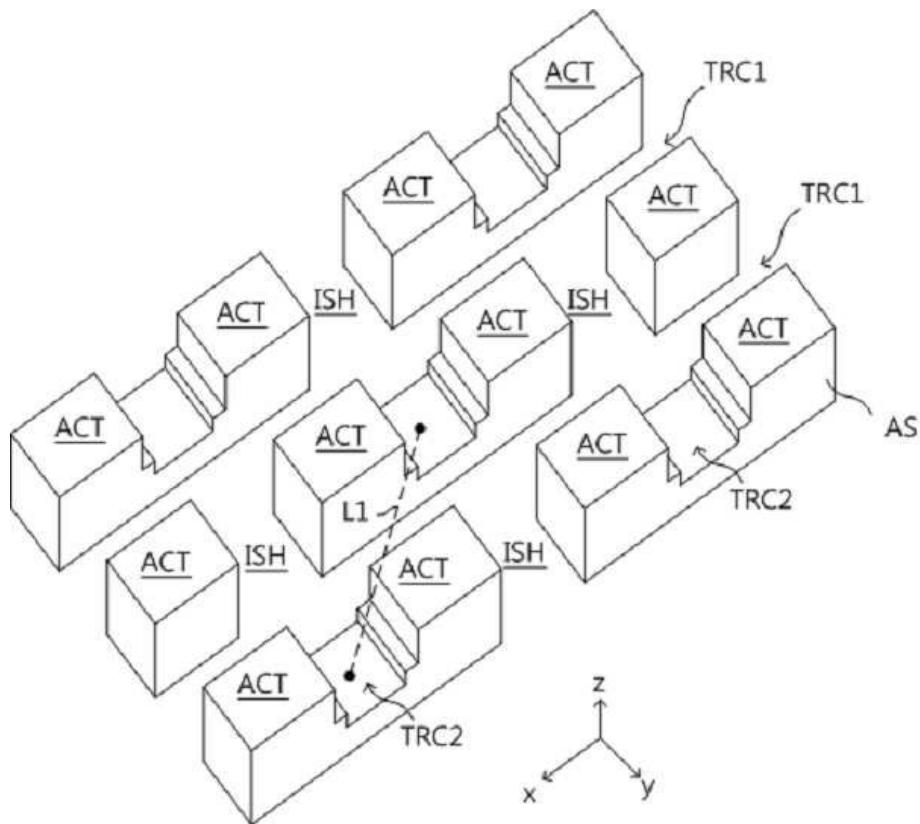

[0050] 다시 도 4를 참조하면, 상기 기판(SUB)을 다시 패터닝하여 제 2 트렌치들(TRC2)을 형성한다(S14). 상기 제 2 트렌치들(TRC2)은 상기 제 1 트렌치들(TRC1)을 가로지르는 장축들을 갖도록 형성될 수 있다. 상기 제 2 트렌치들(TRC2)이 상기 제 1 트렌치들(TRC1)을 가로지르기 때문에, 도 21에 도시된 것처럼, 상기 제 1 및 제 2 트렌치들(TRC1, TRC2)은 상기 기판(SUB) 상에 2차원적으로 배열되는 활성 패턴들(ACT)의 측벽들을 정의한다. 또한, 상기 활성 패턴들(ACT)은 두번의 패터닝 공정들을 통해 형성되기 때문에, 상기 기판(SUB)의 상부면에 평면에 투영되는 상기 활성 패턴(ACT)의 단면은 실질적으로 사각형일 수 있다.

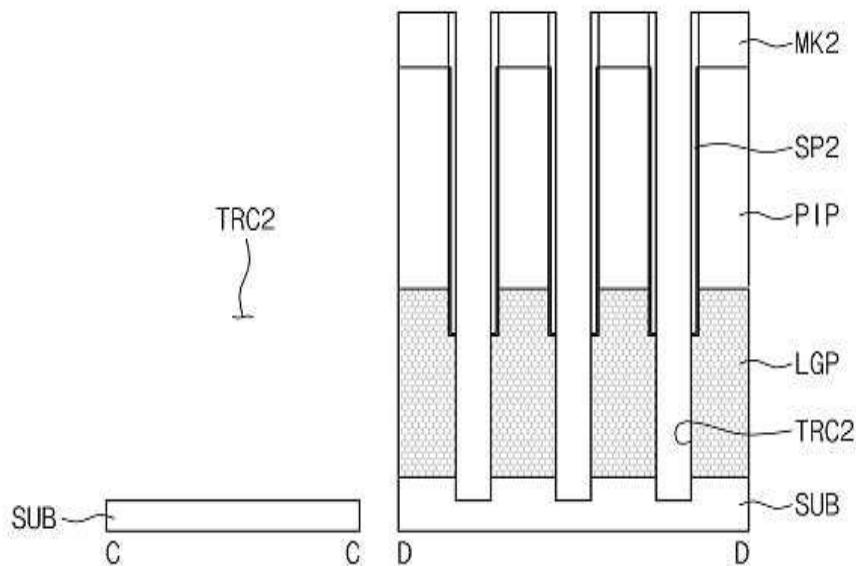

[0051] 본 발명의 일부 실시예들에 따르면, 상기 제 2 트렌치들(TRC2)을 형성하는 단계(S14)는, 도 8a 및 도 8b에 도시된 것처럼 상기 제 1 트렌치들(TRC1)을 가로지르는 예비 트렌치들(TRC2p)을 형성하고, 도 9a 및 도 9b에 도시된 것처럼 상기 예비 트렌치들(TRC2p)의 내측벽에 제 2 스페이서들(SP2)을 형성한 후, 도 10a 및 도 10b에 도시된 것처럼 상기 예비 트렌치들(TRC2p)을 아래쪽으로 연장함으로써 제 2 트렌치들(TRC2)을 형성하는 단계를 포함할 수 있다.

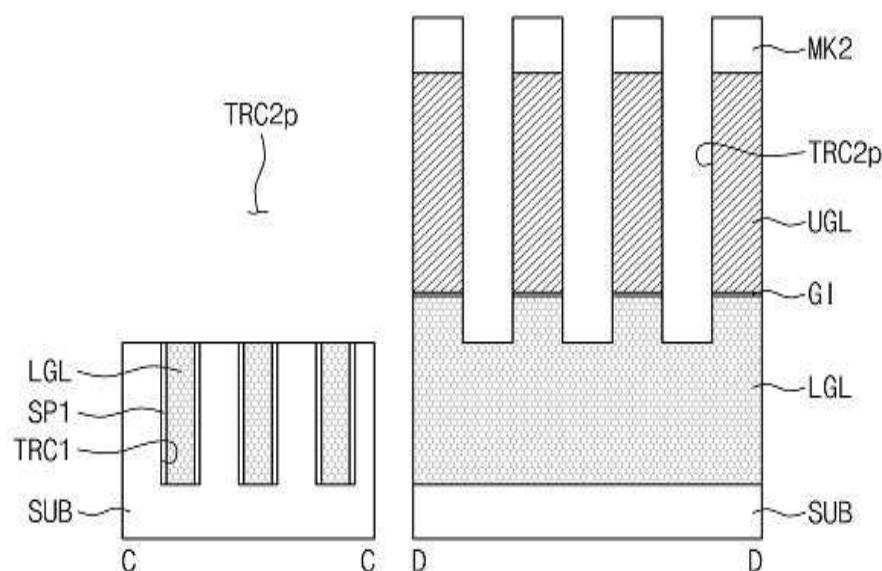

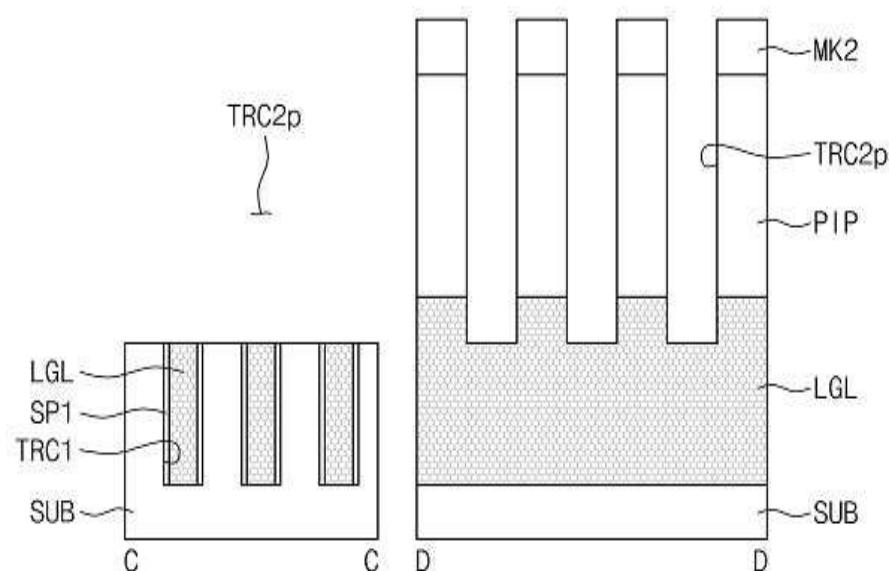

[0052] 보다 구체적으로, 도 8a 및 도 8b를 참조하면, 상기 예비 트렌치들(TRC2p)을 형성하는 단계는 상기 상부 게이트

막(UGL)이 형성된 결과물 상에 상기 제 1 트렌치들(TRC1)을 가로지르는 장축을 갖는 제 2 마스크 패턴들(MK2)을 형성한 후, 이를 식각 마스크로 사용하여 상기 기판(SUB) 및 상기 상부 게이트막(UGL)을 패터닝하는 단계를 포함할 수 있다. 이에 따라, 도 20에 도시된 것처럼, 상기 상부 게이트막(UGL)은, 상기 예비 트렌치들(TRC2p)에 의해 수평적으로 분리되어, 상기 제 1 트렌치들(TRC1) 내에 배치된 상기 하부 게이트막(LGL)을 가로지른다. 이에 더하여, 이 단계 동안, 상기 제 1 마스크 패턴들(MK1) 및 상기 게이트 절연막(GI)도 함께 식각될 수 있다. 즉, 상기 제 1 마스크 패턴들(MK1) 및 상기 게이트 절연막(GI)은 상기 예비 트렌치들(TRC2p)에 의해 분리되어, 상기 활성 패턴들(ACT)과 마찬가지로 상기 기판(SUB) 상에 2차원적으로 배열될 수 있다. 일부 실시예들에 따르면, 상기 예비 트렌치들(TRC2p)의 바닥면들은 상기 상부 게이트막(UGL)의 하부면보다 낮을 수 있다.

[0053] 도 9a 및 도 9b를 참조하면, 상기 예비 트렌치(TRC2p)의 측벽에 상기 제 2 스페이서들(SP2)을 형성한다. 상기 제 2 스페이서들(SP2)은 상기 예비 트렌치(TRC2p)와 마찬가지로 상기 제 1 트렌치들(TRC1)을 가로지르면서 상기 예비 트렌치(TRC2p)의 바닥면을 노출시킬 수 있다. 일부 실시예들에 따르면, 상기 제 2 스페이서(SP2)는 실리콘 산화물에 대해 식각 선택성을 갖는 물질들 중의 하나(예를 들면, 실리콘 질화물)로 형성되는 마스크 스페이서(SP2b)를 포함할 수 있다. 이에 더하여, 상기 제 2 스페이서(SP2)는 상기 마스크 스페이서(SP2b)와 상기 예비 트렌치들(TRC2p) 사이에 개재되는 베퍼 스페이서(SP2a)를 더 포함할 수 있다. 상기 베퍼 스페이서(SP2a)는 실리콘 산화물로 형성될 수 있으며, 수평적으로 연장되어 상기 마스크 스페이서(SP2b)의 아래에 배치되는 부분을 포함하는 'L'자형 스페이서일 수 있다.

[0054] 도 10a 및 도 10b를 참조하면, 상기 제 2 마스크 패턴(MK2) 및 상기 제 2 스페이서(SP2)를 식각 마스크로 사용하여 상기 예비 트렌치(TRC2p)의 바닥면을 식각한다. 이에 따라, 상기 예비 트렌치(TRC2p)보다 좁은 폭을 갖는 상기 제 2 트렌치들(TRC2)이 형성된다.

[0055] 일부 실시예들에 따르면, 도 10a의 단면 D-D에 도시된 것처럼, 상기 제 2 트렌치(TRC2)의 바닥면은 상기 하부 게이트막(LGL)의 바닥면보다 낮을 수 있다. 이 경우, 상기 하부 게이트막(LGL)은 상기 제 2 트렌치들(TRC2)에 의해 수평적으로 분리되어, 도 21에 도시된 것처럼, 상기 제 1 트렌치들(TRC1) 내에 2차원적으로 배열되는 하부 게이트 패턴들(LGP)이 형성될 수 있다. 하지만, 본 발명의 변형된 실시예들에 따르면, 상기 제 2 트렌치(TRC2)의 바닥면은 상기 하부 게이트막(LGL)의 바닥면보다 위쪽에 위치함으로써, 상기 하부 게이트막(LGL)은 상기 제 2 트렌치들(TRC2)에 의해 완전하게 분리되지 않을 수 있다. 이러한 변형된 실시예들에 대한 설명은 기술(description)의 간결함을 위해 생략한다.

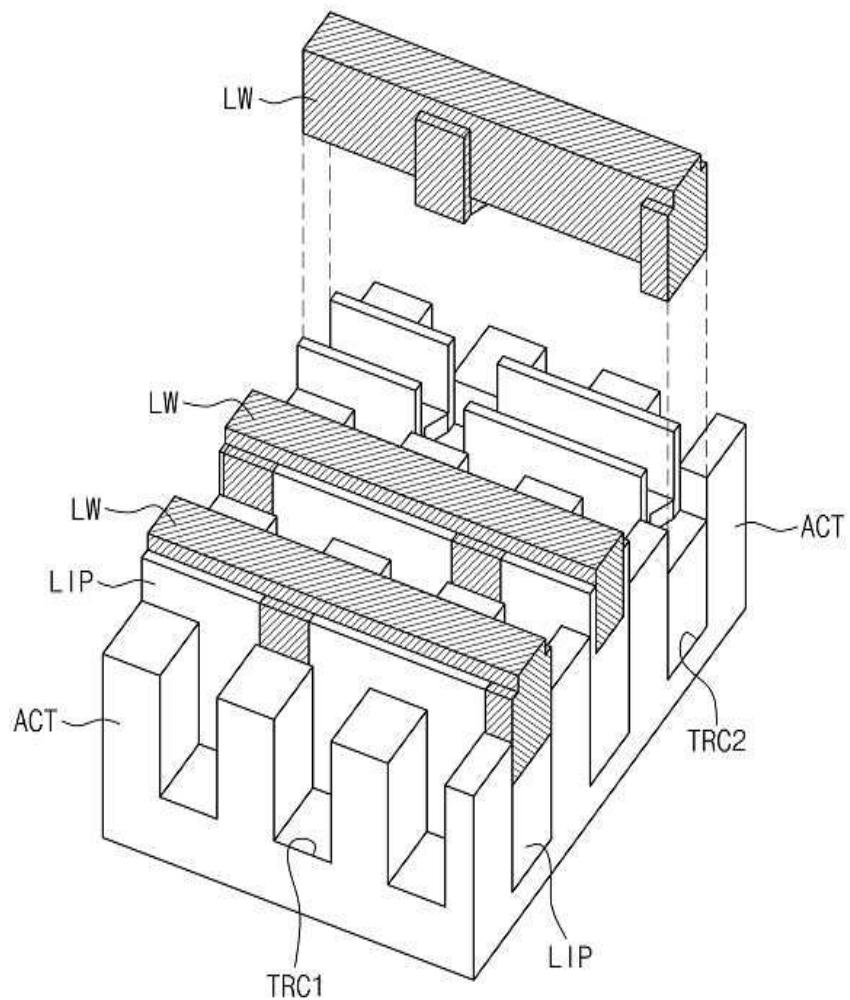

[0056] 다시 도 4를 참조하면, 상기 제 2 트렌치(TRC2)의 하부 영역에서 상기 활성 패턴(ACT)의 측벽에 접촉하는 하부 배선들(LW)을 형성한다(S15). 이 단계(S15)는 상기 제 2 트렌치(TRC2)의 하부 영역을 채우는 하부 절연 패턴(LIP)을 형성하고, 상기 하부 절연 패턴(LIP)을 패터닝하여 상기 제 1 트렌치들(TRC1)을 가로지르는 도랑들(DCH) 및 상기 활성 패턴들(ACT)의 측벽들을 노출시키는 언더컷 영역들(UCR)을 형성한 후, 상기 도랑들(DCH) 및 상기 언더컷 영역들(UCR)을 채우는 상기 하부 배선들(LW)을 형성하는 단계를 포함할 수 있다. 도 22는 상기 도랑들(DCH), 상기 언더컷 영역들(UCR), 및 상기 하부 배선들(LW)의 배치 및 모양들을 예시적으로 도시하는 분해사시도이다.

[0057] 보다 구체적으로, 일부 실시예들에 따르면, 상기 하부 절연 패턴(LIP)은 상기 제 2 트렌치(TRC2)에 의해 노출되는 상기 활성 패턴들(ACT)의 측벽들 및 상기 하부 게이트 패턴들(LGP)의 측벽들을 열산화시킴으로써 형성될 수 있다. 이 경우, 도 11a 및 도 11b에 도시된 것처럼, 상기 활성 패턴(ACT)을 구성하는 원자들이 산화되어 상기 하부 절연 패턴(LIP)을 형성하기 때문에, 상기 하부 절연 패턴(LIP)의 폭은 상기 제 2 스페이서들(SP2) 사이의 간격보다 넓을 수 있다. 즉, 상기 하부 절연 패턴(LIP)은 상기 제 2 스페이서(SP2)의 아래에도 형성될 수 있다. 일부 실시예들에 따르면, 상기 하부 절연 패턴(LIP)은 도 11a 및 도 11b에 도시된 것(즉, 상기 예비 트렌치(TRC2p)의 폭)보다 넓은 폭을 갖도록 형성될 수도 있다. 변형된 실시예에 따르면, 상기 하부 절연 패턴(LIP)은 상술한 열산화 공정에 더하여 추가적으로 실시되는 증착 공정을 통해 완성될 수도 있다.

[0058] 상기 도랑들(DCH)은 상기 제 2 스페이서들(SP2)을 식각 마스크로 사용하여 상기 하부 절연 패턴(LIP)의 상부면을 이방성 식각함으로써 형성될 수 있다. 이에 따라, 도 12a 및 도 12b에 도시된 것처럼, 상기 도랑(DCH)은 상기 제 2 트렌치(TRC2) 내에서 상기 활성 패턴들(ACT)의 측벽들로부터 이격되어 형성된다. 즉, 상기 제 2 스페이서(SP2)의 아래에는 상기 이방성 식각 단계에서 식각되지 않은 상기 하부 절연 패턴(LIP)의 부분이 잔존할 수 있으며, 상기 도랑(DCH)과 이에 인접하는 상기 활성 패턴들(ACT)은 상기 하부 절연 패턴(LIP)의 상기 잔존 부분에 의해 분리될 수 있다.

[0059] 상기 언더컷 영역들(UCR)은 도 13a 및 도 13b에 도시된 것처럼 제 3 마스크 패턴(MK3)을 형성한 후, 도 14a 및

도 14b에 도시된 것처럼 상기 제 3 마스크 패턴(MK3)을 마스크로 사용하여 상기 하부 절연 패턴(LIP)을 패터닝 하는 단계를 통해 형성될 수 있다. 보다 구체적으로, 상기 제 3 마스크 패턴(MK3)은 상기 도랑들(DCH)의 일부분 을 노출시키는 홀 모양의 접합 정의 영역들(JDR)을 정의하도록 형성될 수 있다. 본 발명의 일부 실시예들에 따르면, 상기 제 3 마스크 패턴(MK3)은 사진 공정을 통해 형성되는 포토레지스트 패턴일 수 있다. 상기 언더컷 영 역들(UCR)은 상기 접합 정의 영역들(JDR)에 의해 노출되는 상기 도랑들(DCH)을 등방적으로 확장함으로써 형성되며, 상기 접합 정의 영역들(JDR)에 인접하는 활성 패턴들(ACT)의 측벽들을 노출시킨다. 이러한 등방적 확장의 결과로서, 도 14a의 단면 C-C에 예시적으로 도시된 것처럼, 상기 언더컷 영역(UCR)은 상기 도랑(DCH)보다 낮은 바닥면을 갖도록 형성될 수 있다.

[0060] 상기 접합 정의 영역들(JDR) 및 상기 언더컷 영역들(UCR)은 상기 기판(SUB) 상에 2차원적으로 형성될 수 있다. 본 발명의 일 측면에 따르면, 이들의 중심점들은 상기 제 2 트렌치(TRC2)에 포함되지만 상기 제 1 트렌치들 (TRC1)에 포함되지 않는 영역들 내부에 위치할 수 있다. 즉, 상기 접합 정의 영역들(JDR) 및 상기 언더컷 영역 들(UCR)의 중심점들은, 상기 제 2 트렌치들(TRC2)에 의해 새롭게 형성되는, 상기 기판(SUB)의 리세스 영역들 내에 위치할 수 있다. 하지만, 변형된 실시예들에 따르면, 상기 중심점에서 벗어난 상기 접합 정의 영역(JDR) 또는 상기 언더컷 영역(UCR)의 다른 부분은 상기 제 1 트렌치(TRC1)에 포함되는 영역까지 확장될 수 있다. 즉, 상기 제 2 트렌치(TRC2)의 장축 방향(이하, y 방향)을 따라 측정되는, 상기 접합 정의 영역(JDR) 또는 상기 언더컷 영역(UCR)의 폭은 상기 활성 패턴(ACT)의 폭보다 클 수 있다.

[0061] 이에 더하여, 상기 제 2 트렌치들(TRC2) 중의 하나의 내부에서 y 방향을 따라 측정되는, 상기 접합 정의 영역들 (JDR) 사이의 거리 또는 상기 언더컷 영역들(UCR) 사이의 거리는 상기 활성 패턴(ACT)의 피치(pitch)(즉, 폭 및 간격의 합)보다 클 수 있다. 예를 들면, 상기 제 2 트렌치들(TRC2) 중의 하나의 내부에서 상기 언더컷 영역들 (UCR)의 중심점들 사이의 거리는 상기 활성 패턴(ACT)의 피치의 두배일 수 있다. 이 경우, 상기 제 2 트렌치들 (TRC2) 중의 하나의 내부에서, 상기 언더컷 영역들(UCR)은 짹수번째의 활성 패턴들(ACT) 사이에 국소적으로 형 성되고 홀수번째 활성 패턴들(ACT) 사이에는 형성되지 않을 수 있다.

[0062] 한편, 한 쌍의 인접하는 제 2 트렌치들(TRC2)을 고려할 경우, 이들 중의 하나의 내부에 배치되는 언더컷 영역들 (UCR)은 짹수번째의 활성 패턴들(ACT)의 측벽들을 노출시키고, 다른 하나의 내부에 배치되는 언더컷 영역들 (UCR)은 홀수번째의 활성 패턴들(ACT)의 측벽들을 노출시키도록 형성된다. 결과적으로, 상기 접합 정의 영역들 (JDR) 또는 상기 언더컷 영역들(UCR)의 수는 대략 상기 활성 패턴들(ACT)의 수의 절반일 수 있다.

[0063] 도 15a 및 도 15b에 도시된 것처럼, 상기 하부 배선(LW)을 형성하기 전에, 상기 언더컷 영역들(UCR)을 통해, 이에 인접하는 상기 활성 패턴들(ACT)의 하부 영역들을 상기 기판(SUB)과 다른 도전형의 불순물들로 도핑하는 단 계가 더 실시될 수 있다. 상기 도핑 단계의 결과로서, 상기 활성 패턴들(ACT)의 하부 영역들에는, 하부 불순물 영역들(LIR; lower impurity region)이 형성될 수 있다.

[0064] 본 발명의 일부 실시예들에 따르면, 상기 하부 불순물 영역들(LIR)은 상기 언더컷 영역(UCR)에 인접하는 상기 활성 영역의 일 측벽으로부터 이를 마주보는 측벽까지 수평적으로 확장될 수 있다. 이에 따라, 상기 하부 불순 물 영역(LIR), 그리고 그것의 상부 및 하부에 위치하는 상기 활성 영역의 상부 및 하부 영역들은 피엔피 구조 또는 엔피엔 구조를 형성할 수 있다. 즉, 상기 활성 패턴(ACT)의 상부 영역은 상기 하부 불순물 영역(LIR)에 의해 상기 기판(SUB) 또는 상기 활성 패턴(ACT)의 하부 영역으로부터 전기적으로 분리될 수 있다. 상기 하부 불순 물 영역들(LIR)은 도 1을 참조하여 설명된 상기 제 2 영역(R2)을 구성할 수 있다.

[0065] 또한, 상기 하부 불순물 영역들(LIR)은 상기 언더컷 영역(UCR)으로부터 상기 상부 게이트막(UGL)의 하부면 근방 까지 수직적으로 확장될 수 있다. 한편, 상기 활성 패턴(ACT)의 내부에서 상기 불순물들의 확산이 등방적으로 이루어질 경우, 도 15a에 도시된 것처럼 상기 하부 불순물 영역(LIR)은 라운드된 단면 도핑 프로파일을 가질 수 있다. 즉, 상기 활성 패턴(ACT)의 상부면으로부터 상기 하부 불순물 영역(LIR)까지의 거리는 상기 언더컷 영역 (UCR)에 인접하는 측벽에서보다 이를 마주보는 측벽에서 더 길수 있다.

[0066] 상기 하부 배선들(LW)은 상기 도랑들(DCH) 및 상기 언더컷 영역들(UCR)을 채우도록 형성될 수 있다. 그 결과, 상기 하부 배선들(LW)은 상기 언더컷 영역들(UCR)을 통해 상기 활성 패턴들(ACT) 또는 상기 하부 불순물 영역들 (LIR)에 접속할 수 있다. 상기 하부 배선들(LW)은 금속막과 같은 도전성 물질을 포함하도록 형성될 수 있다. 예를 들면, 상기 하부 배선(LW)은 상기 하부 불순물 영역(LIR)과의 오믹 접촉을 위한 적어도 하나의 장벽 금속막 (barrier metal layer) 및 금속막을 포함할 수 있다.

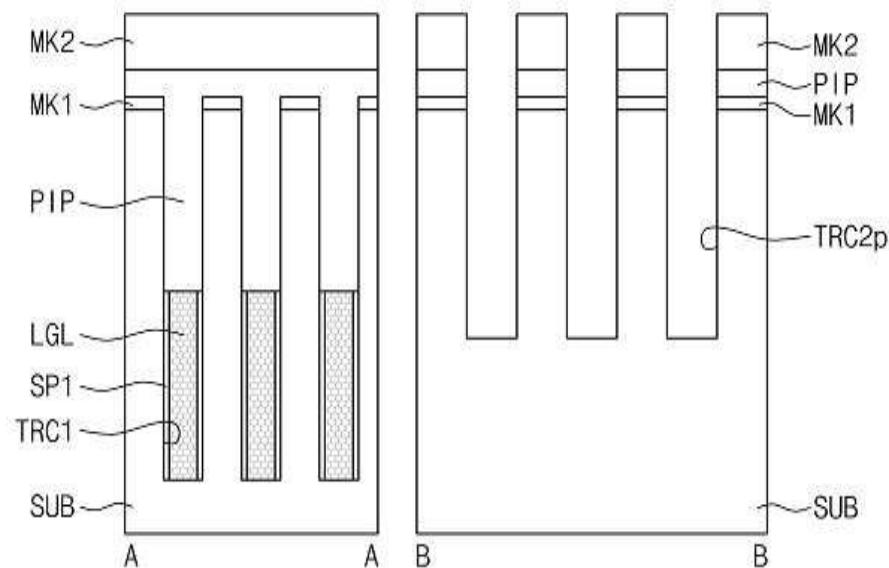

[0067] 다시 도 4를 참조하면, 상기 하부 게이트 패턴들(LGP) 중의 일부의 상부에 배치되는 플러그 절연 패턴들(PIP)을

형성한다(S16). 이 단계(S16) 동안, 상기 하부 배선들(LW)이 형성된 상기 제 2 트렌치들(TRC2)을 채우는 상부 절연 패턴들(UIP)이 더 형성될 수 있다. 본 발명의 일 실시예에 따르면, 상기 플러그 절연 패턴(PIP) 및 상기 상부 절연 패턴(UIP)은 실리콘 산화막일 수 있다. 또한, 이 단계(S16) 동안, 상기 상부 게이트막(UGL)은 y 방향을 따라 분리됨으로써 상부 게이트 패턴들(UGP)을 형성할 수 있다.

[0068] 상기 플러그 절연 패턴들(PIP)은 상기 상부 게이트막(UGL)을 패터닝하여 상기 제 1 트렌치들(TRC1)의 상부에서 상기 게이트 절연막(GI)을 노출시키는 홀들을 형성하고, 이들을 채우는 플러그 절연막을 형성한 후, 상기 플러그 절연막을 평탄화 식각하는 단계를 통해 형성될 수 있다. 상기 평탄화 식각의 결과로서, 도시된 것처럼, 상기 상부 게이트 패턴들(UGP)의 상부면이 노출될 수 있지만, 본 발명의 기술적 사상이 이러한 실시예에 한정되는 것은 아니다.

[0069] 변형된 실시예들에 따르면, 상기 게이트 절연막(GI)은 상기 플러그 절연 패턴(PIP)을 위한 홀들을 형성하는 동안 제거됨으로서, 상기 활성 패턴(ACT)의 상부 측벽이 노출될 수 있다. 이에 더하여, 상기 홀들은 그것의 아래에서 상기 상부 게이트막(UGL)을 제거하도록 형성될 수 있다. 이 경우, 상기 플러그 절연 패턴(PIP)은 상기 하부 게이트 패턴(LGP)의 상부면과 직접 접촉하거나, 도 16a 및 도 16b에 도시된 것처럼, 상기 게이트 절연막(GI)만이 상기 플러그 절연 패턴(PIP)과 상기 하부 게이트 패턴(LGP) 사이에 개재될 수 있다.

[0070] 일부 실시예들에 따르면, 상기 플러그 절연막은 상기 상부 절연 패턴(UIP)을 위한 절연막과 동시에 형성될 수 있다. 하지만, 다른 실시예에 따르면, 상기 상부 절연 패턴(UIP)을 위한 절연막을 형성한 후, 상기 플러그 절연막은 이와는 독립적으로 형성될 수 있다.

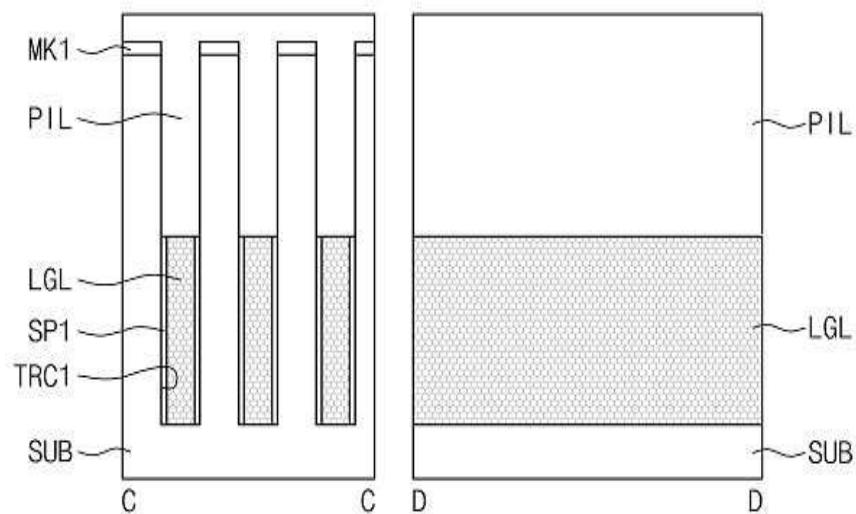

[0071] 상기 플러그 절연 패턴들(PIP)의 중심점들은 상기 제 1 트렌치들(TRC1)에 포함되면서 상기 제 2 트렌치들(TRC2)에 포함되지 않는 영역들 내부에 위치할 수 있다. 보다 구체적으로, y 방향을 따라 측정되는, 상기 플러그 절연 패턴들(PIP)의 중심점들 사이의 거리는 상기 활성 패턴(ACT)의 피치의 두배일 수 있다. 즉, 동일한 x 좌표를 가지면서 y 방향을 따라 배열되는 상기 활성 패턴들(ACT)(이하, 제 1 그룹) 사이의 공간들 중에서, 홀수번째 것들에는 상기 플러그 절연 패턴들(PIP)이 배치되고, 짝수번째 것들에는 상기 상부 게이트 패턴들(UGP)이 잔존한다.

[0072] 한편, 동일한 x 좌표를 가지면서 y 방향을 따라 배열되면서, 상기 제 1 그룹에 인접하는 상기 활성 패턴들(ACT)은 제 2 그룹을 구성할 수 있다. 이 경우, 상기 제 2 그룹의 상기 활성 패턴들(ACT) 사이에 형성되는 공간들 중에서, 홀수번째 것들에는 상기 상부 게이트 패턴들(UGP)이 잔존하고 짝수번째 것들에는 상기 플러그 절연 패턴들(PIP)이 배치될 수 있다. 즉, 상기 플러그 절연 패턴들(PIP) 및 상기 게이트 패턴들(GP)은 모두 체크 보드 모양의 배열을 구성하도록 배치되어, 이들은 서로 겹치지 않도록 배치된다. 도 16b는 상기 플러그 절연 패턴들(PIP)과 상기 게이트 패턴들(GP) 사이의 이러한 상대적 배치를 예시적으로 도시한다.

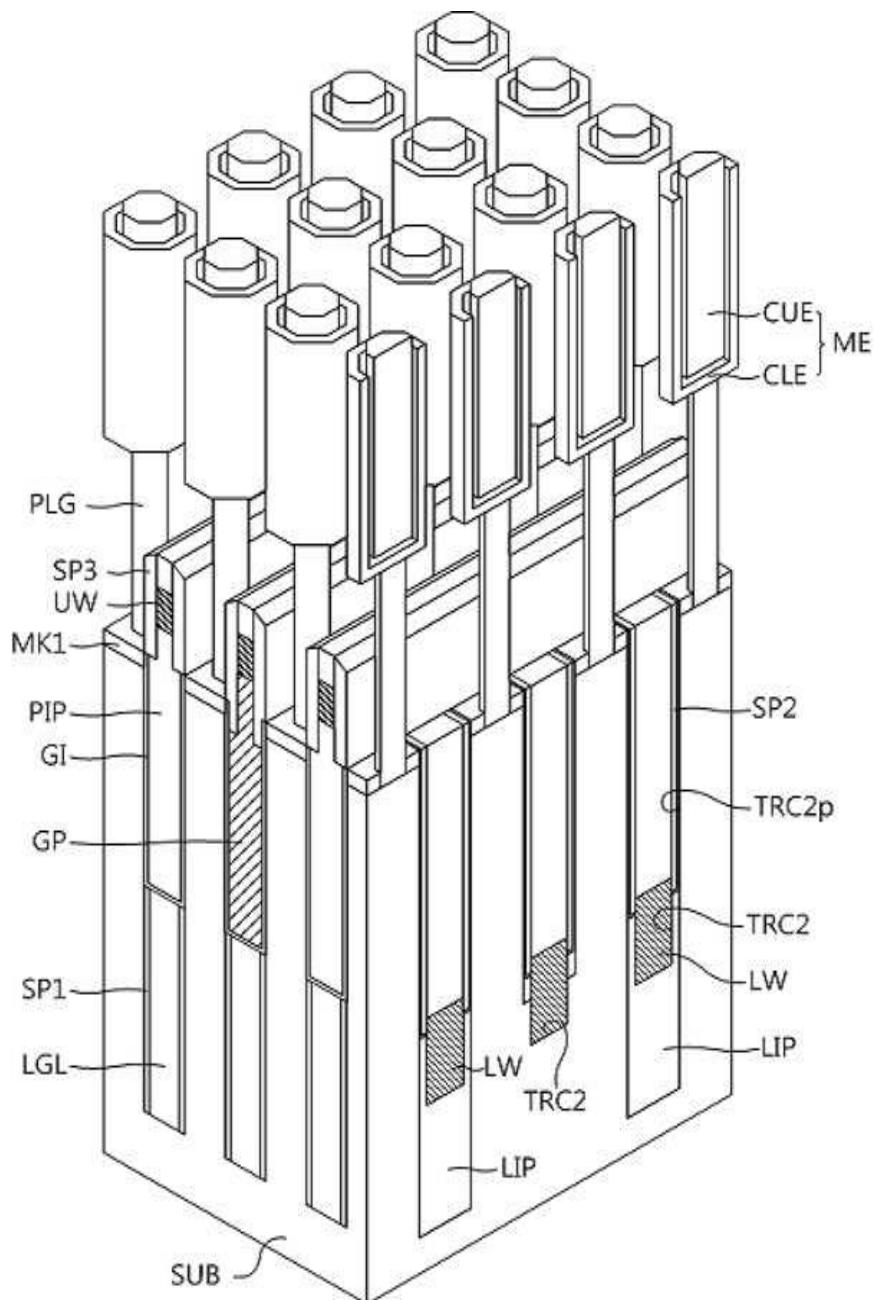

[0073] 다시 도 4를 참조하면, 상기 상부 게이트 패턴들(UGP)에 접속하는 상부 배선들(UW; upper wiring)을 형성한다(S17). 상기 상부 배선들(UW)은 상기 하부 배선들(LW) 또는 상기 제 2 트렌치들(TRC2)을 가로지르면서 상기 상부 게이트 패턴들(UGP)을 연결하도록 형성될 수 있다.

[0074] 보다 구체적으로, 상기 상부 배선들(UW)은 도 17a 및 도 17b에 도시된 것처럼 상기 플러그 절연 패턴들(PIP)이 형성된 결과물 상에 상부 도전막(UCL; upper conductive layer) 및 캐핑막(CPL; capping layer)을 차례로 형성한 후, 도 18a 및 도 18b에 도시된 것처럼 이를 패터닝하여 차례로 적층된 상기 상부 배선(UW) 및 제 4 마스크 패턴(MK4)을 형성하는 단계를 포함할 수 있다. 상기 상부 도전막(UCL)은 금속 물질들, 금속 질화물들 또는 실리사이드 물질들 중의 적어도 하나를 포함할 수 있다. 상기 캐핑막(CPL) 또는 상기 제 4 마스크 패턴(MK4)은 상기 상부 도전막(UCL)을 패터닝하는 단계에서 식각 마스크로 사용될 수 있는 물질(예를 들면, 실리콘 질화물)로 형성될 수 있다.

[0075] 일부 실시예들에 따르면, 상기 상부 배선(UW)은 상기 활성 패턴(ACT)보다 작은 폭을 갖도록 형성될 수 있다. 또한, 상기 제 4 마스크 패턴(MK4) 양측에서, 상기 상부 게이트 패턴(UGP)의 상부면은 리세스되어 상기 활성 패턴(ACT)의 상부면보다 낮아질 수 있다. 이에 따라, 상기 상부 게이트 패턴(UGP)의 상기 활성 패턴(ACT)의 상부로 연장된 부분은 제거될 수 있다. 이에 더하여, 상기 상부 배선(UW)을 형성하는 동안, 상기 제 1 마스크 패턴(MK1)이 제거되어 상기 활성 패턴(ACT)의 상부면이 노출될 수 있다.

[0076] 본 발명의 실시예들에 따르면, 도 18a 및 도 18b에 도시된 것처럼 상기 활성 패턴(ACT)의 상부 영역을 상기 기판(SUB)과 다른 도전형을 갖는 불순물들로 도핑함으로써 상부 불순물 영역들(UIR)을 형성할 수 있다. 상기 상부 불순물 영역들(UIR)은 이온 주입 공정을 통해 형성될 수 있다.

[0077] 다시 도 4를 참조하면, 상기 상부 불순물 영역들(UIR)에 접속하는 메모리 요소들(ME)을 형성한다(S18). 이 단계는 상기 제 4 마스크 패턴(MK4) 및 상기 상부 배선(UW)의 측벽을 덮는 제 3 스페이서(SP3)를 형성한 후, 상기 상부 불순물 영역들(UIR)에 접속하는 플러그들(PLG) 및 상기 플러그들(PLG)에 접속하는 상기 메모리 요소들(ME)을 형성하는 단계를 포함할 수 있다.

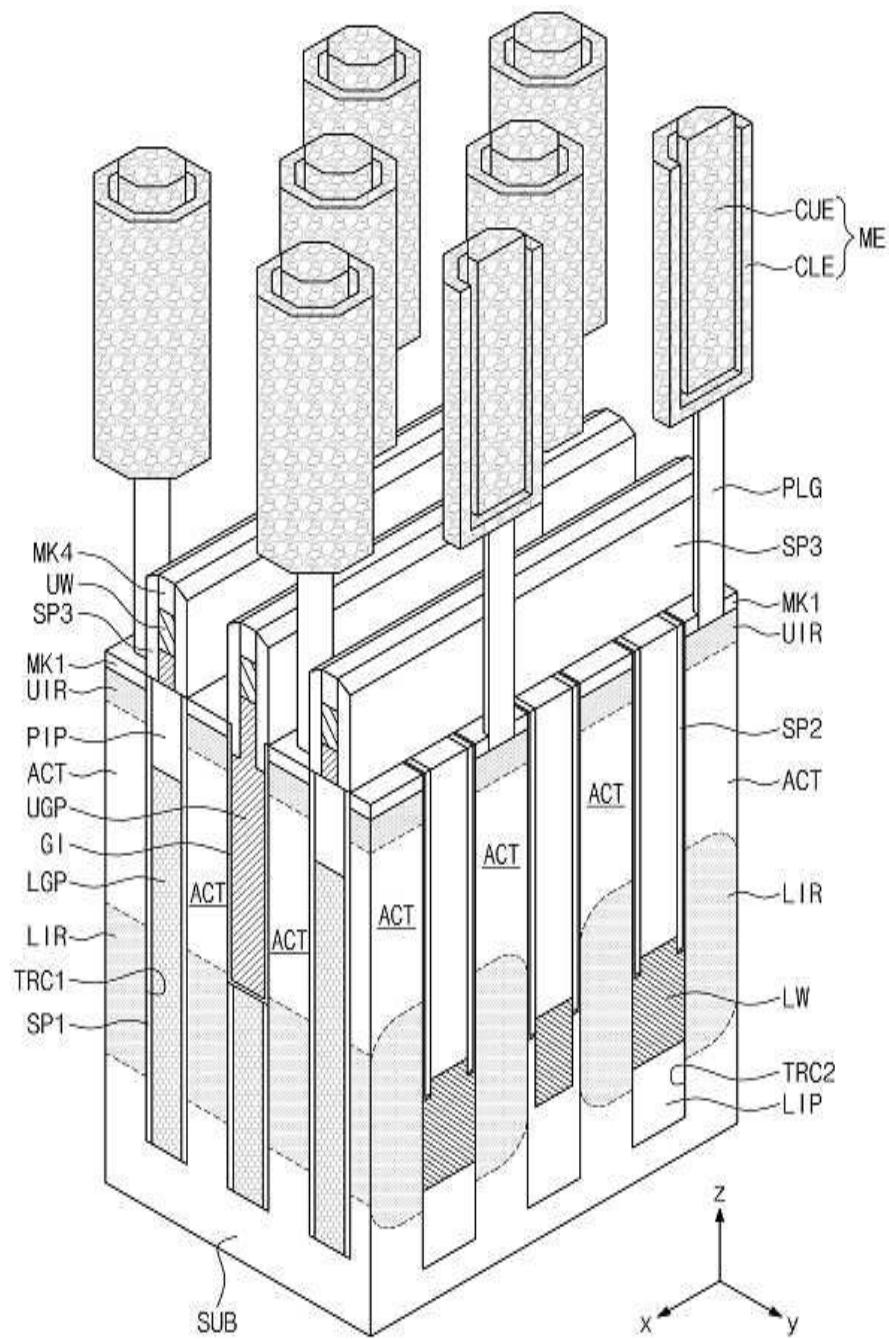

[0078] 도 19a 및 도 19b에 도시된 것처럼, 상기 메모리 요소(ME)는 상기 플러그(PLG)를 통해 상기 상부 불순물 영역(UIR)에 접속하는 커패시터 하부 전극(CLE) 및 상기 커패시터 하부 전극(CLE)을 마주보는 커패시터 상부 전극(CUE)을 포함하는 커패시터일 수 있다. 하지만, 변형된 실시예들에 따르면, 상기 메모리 요소(ME)는 커패시터, 강유전체 커패시터, 자기터널접합(MTJ), 가변 저항성 요소 또는 전하저장 기제(mechanism)에 기초한 메모리 요소일 수 있다. 또다른 변형된 실시예들에 따르면, 상기 상부 불순물 영역들(UIR)은 상기 제 3 스페이서(SP3)를 형성한 후에 형성될 수 있다.

[0079] 본 발명의 실시예들에 따르면, 도 79에 도시된 것처럼, 상기 플러그들(PLG) 각각은 상기 활성 패턴들(ACT) 각각의 상부에 하나씩 형성될 수 있다. 즉, 상기 플러그들(PLG) 또는 상기 메모리 요소들(ME)의 수는, 동일한 면적 내에 포함되는, 상기 활성 패턴들(ACT)의 수와 동일할 수 있다. 하지만, 도면에서의 복잡성을 피하기 위해, 도 19b에서, 상기 플러그들(PLG) 또는 상기 메모리 요소들(ME)의 일부는 생략되었다.

#### [제조 방법- 제 2 실시예]

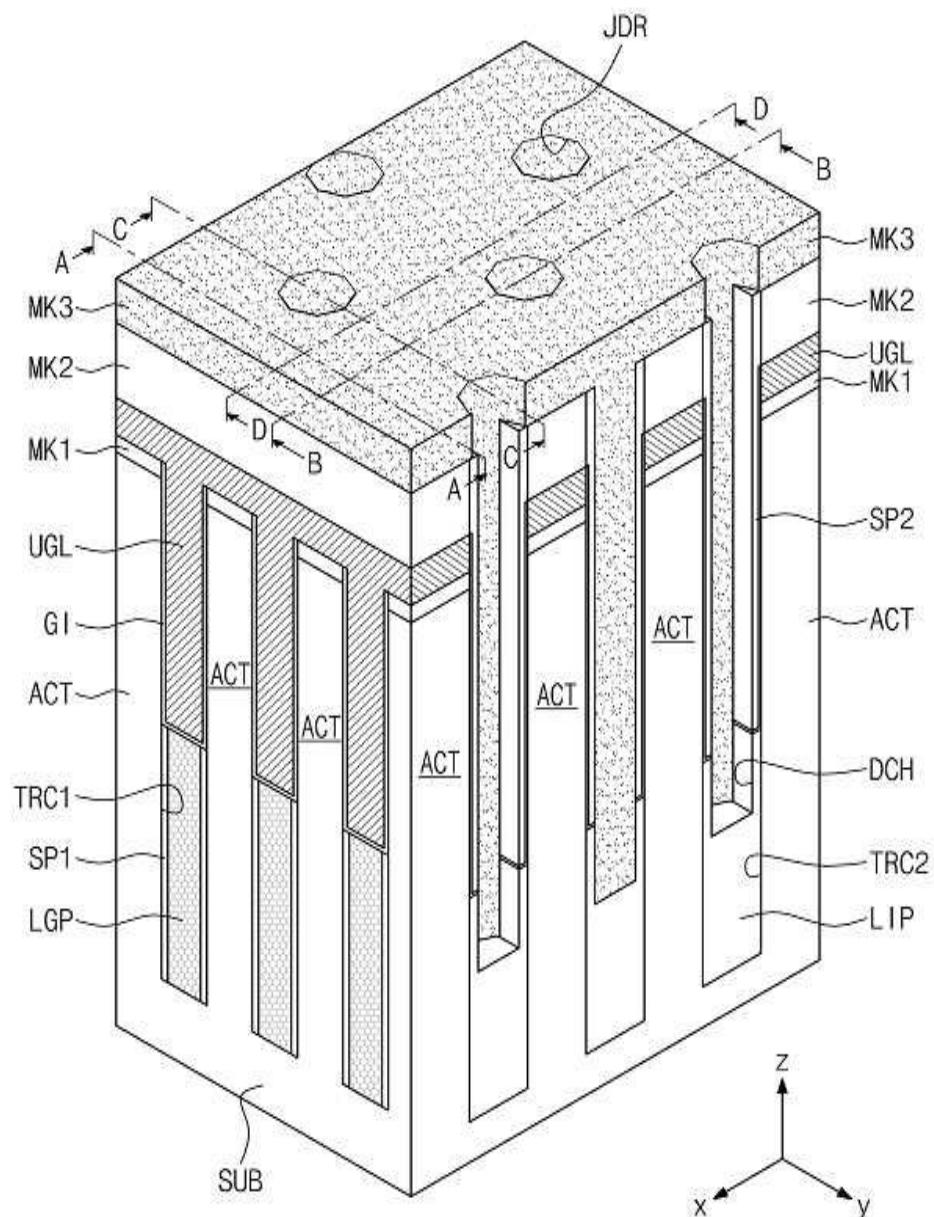

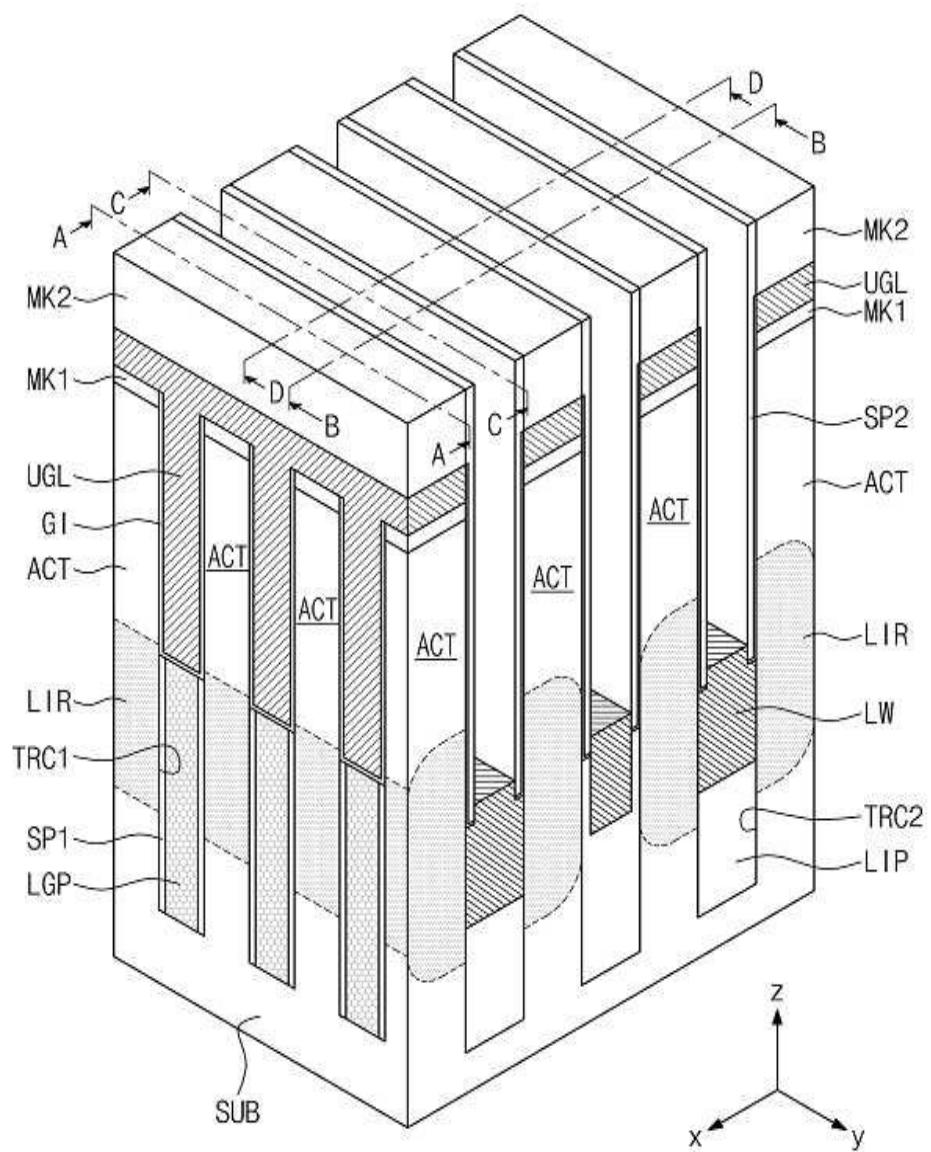

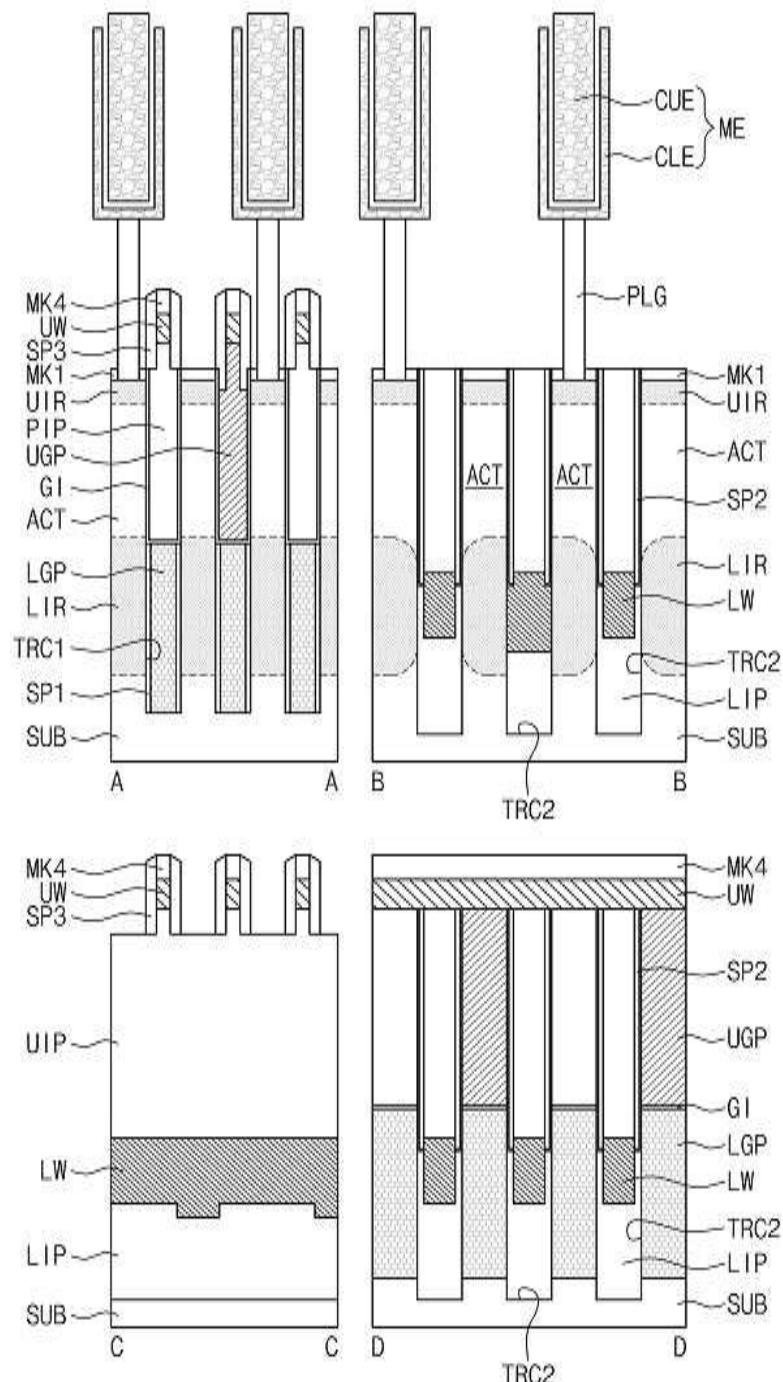

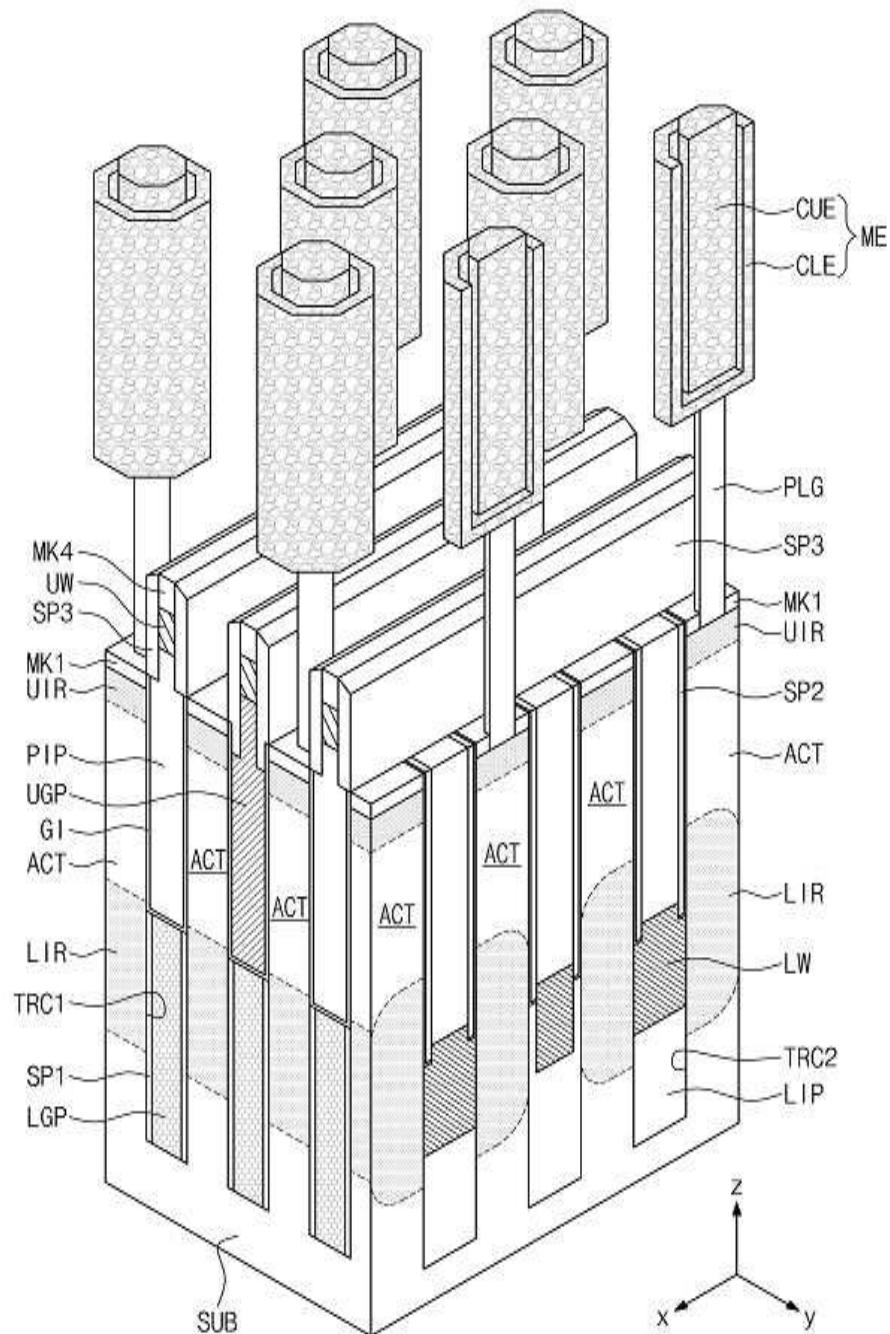

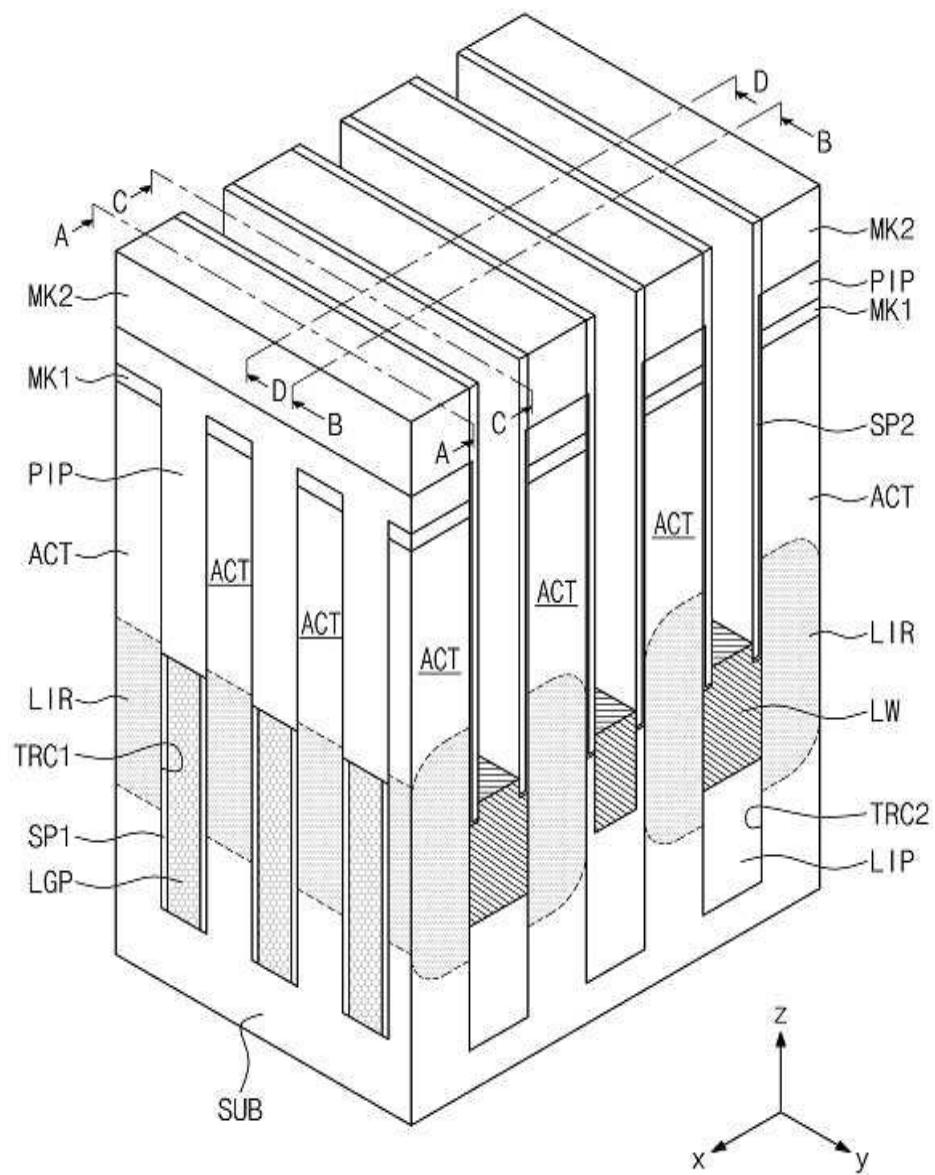

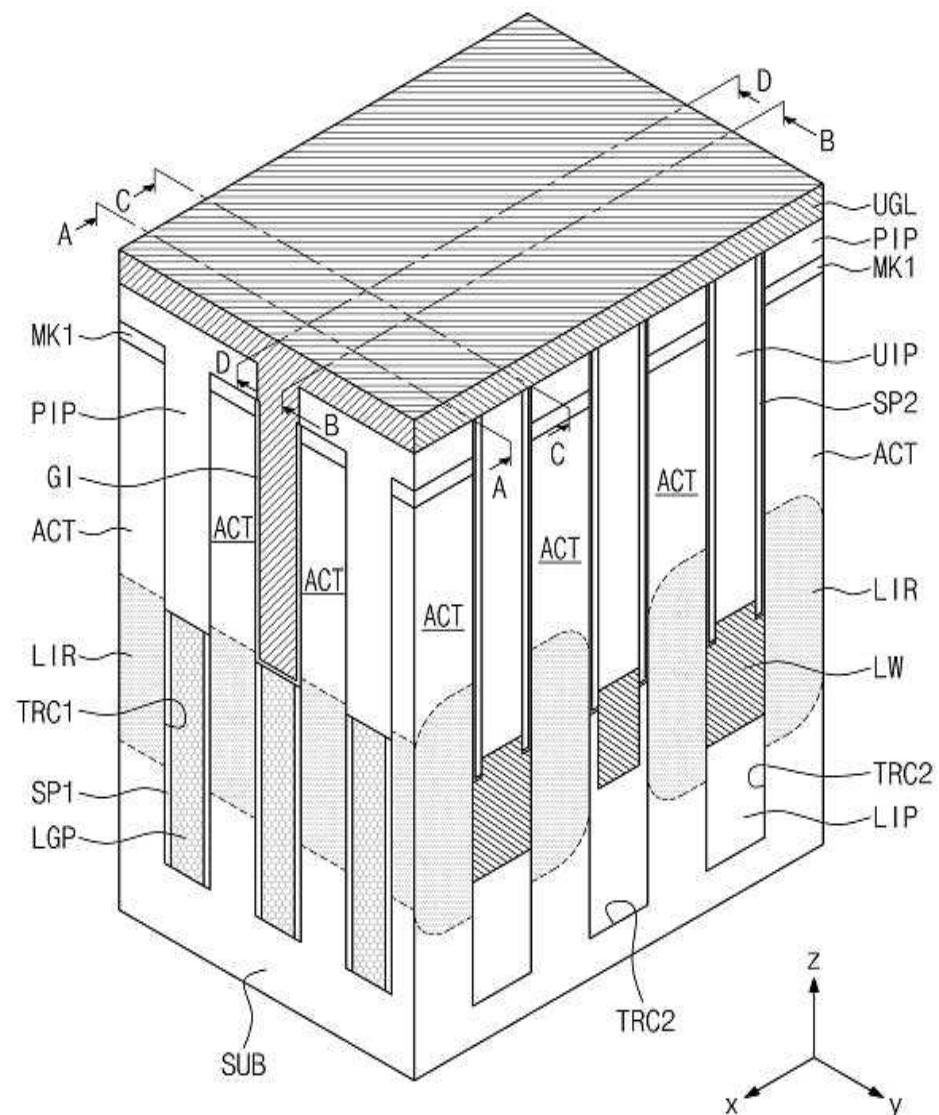

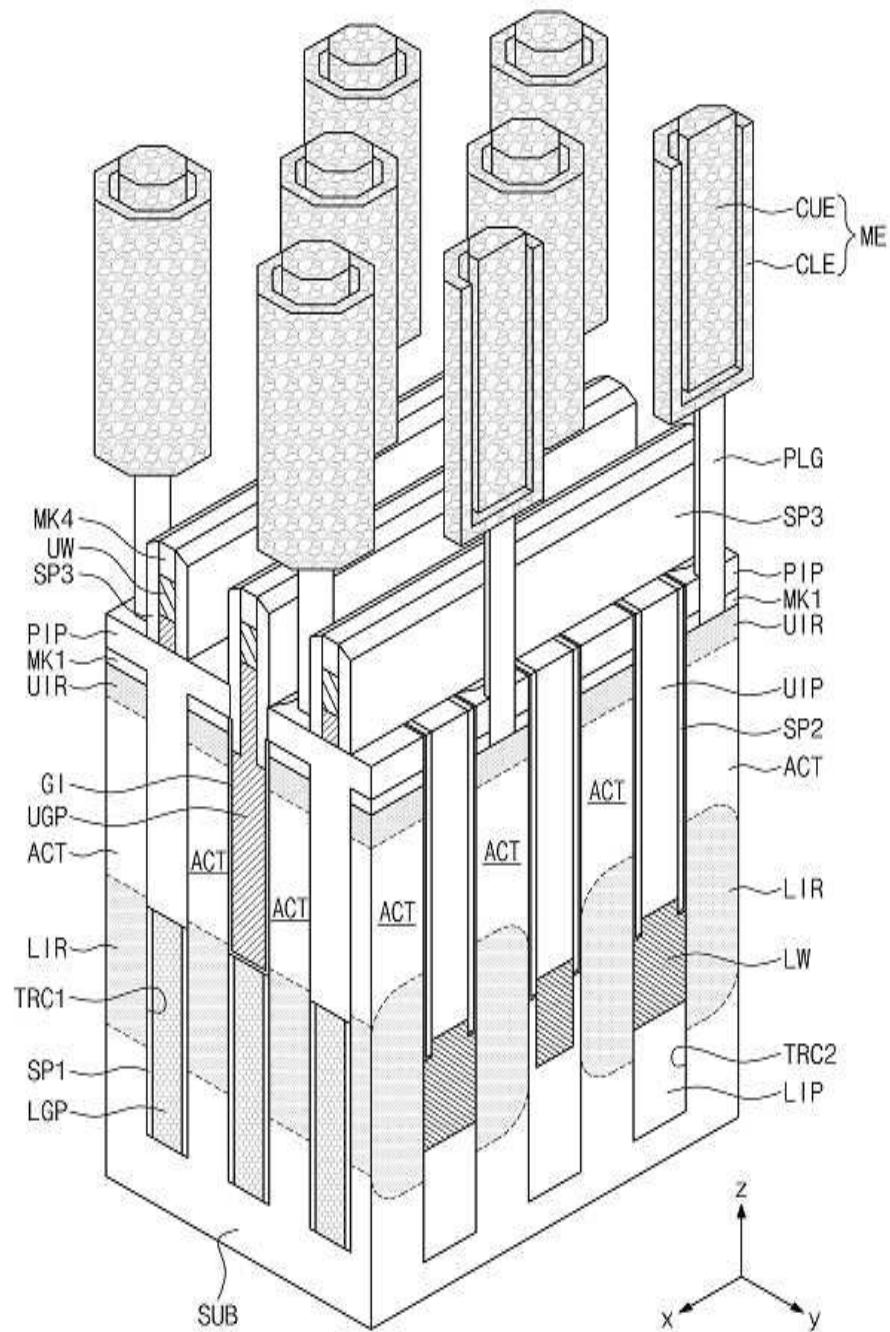

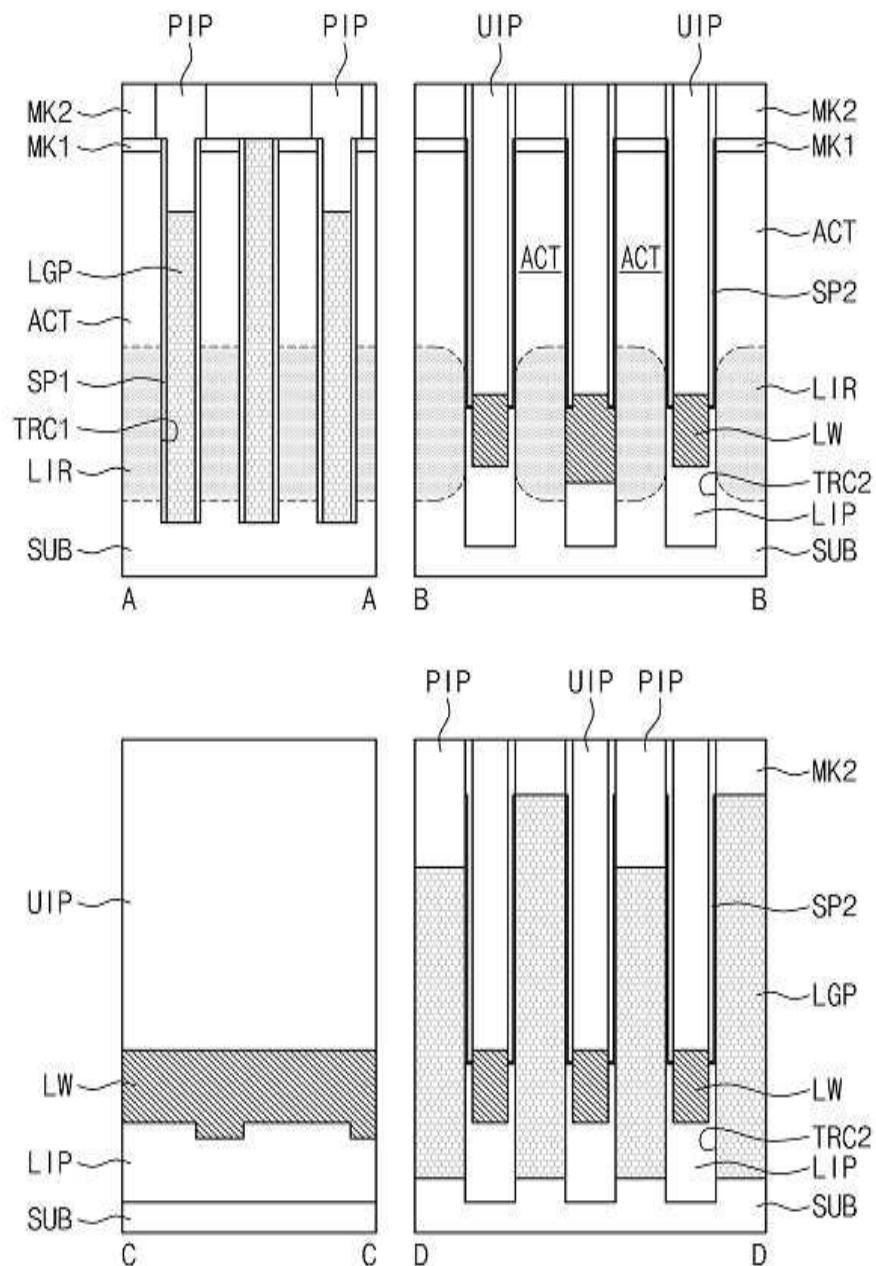

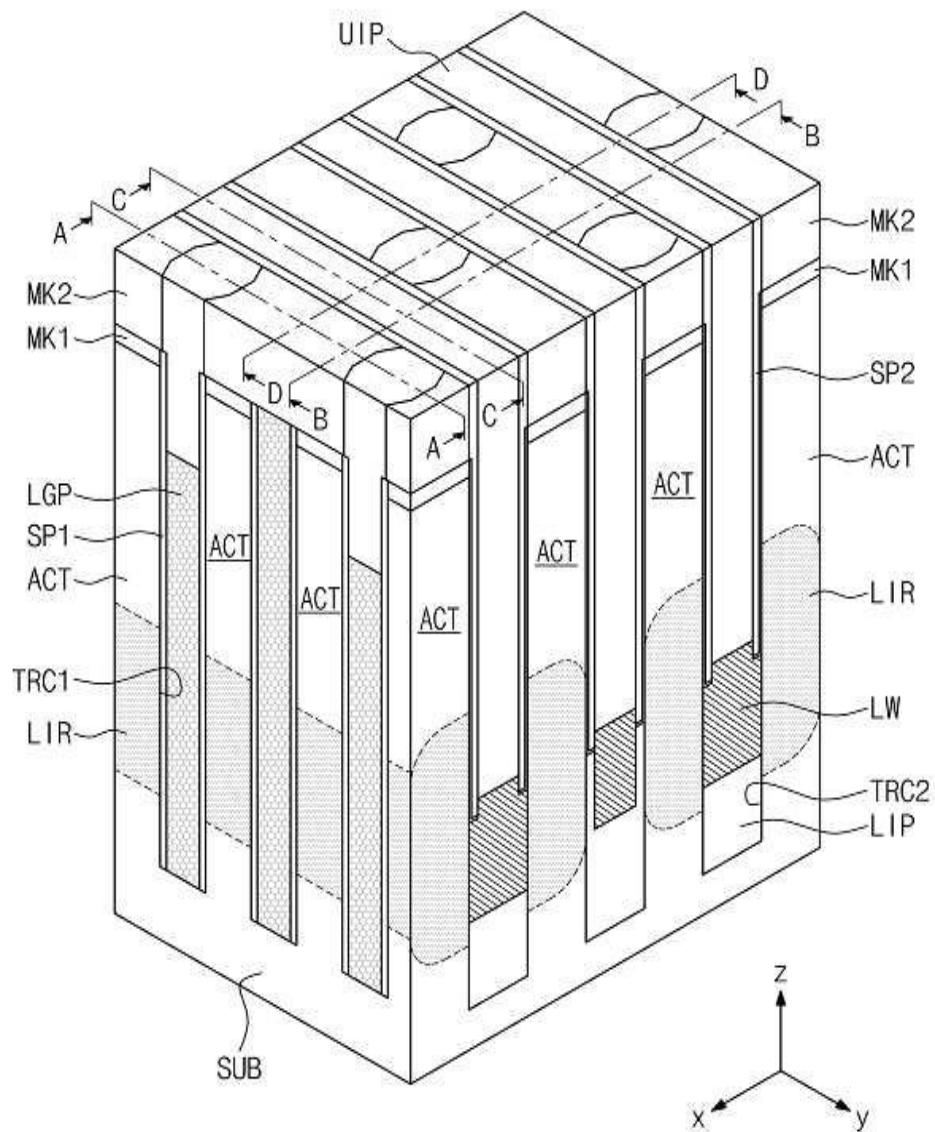

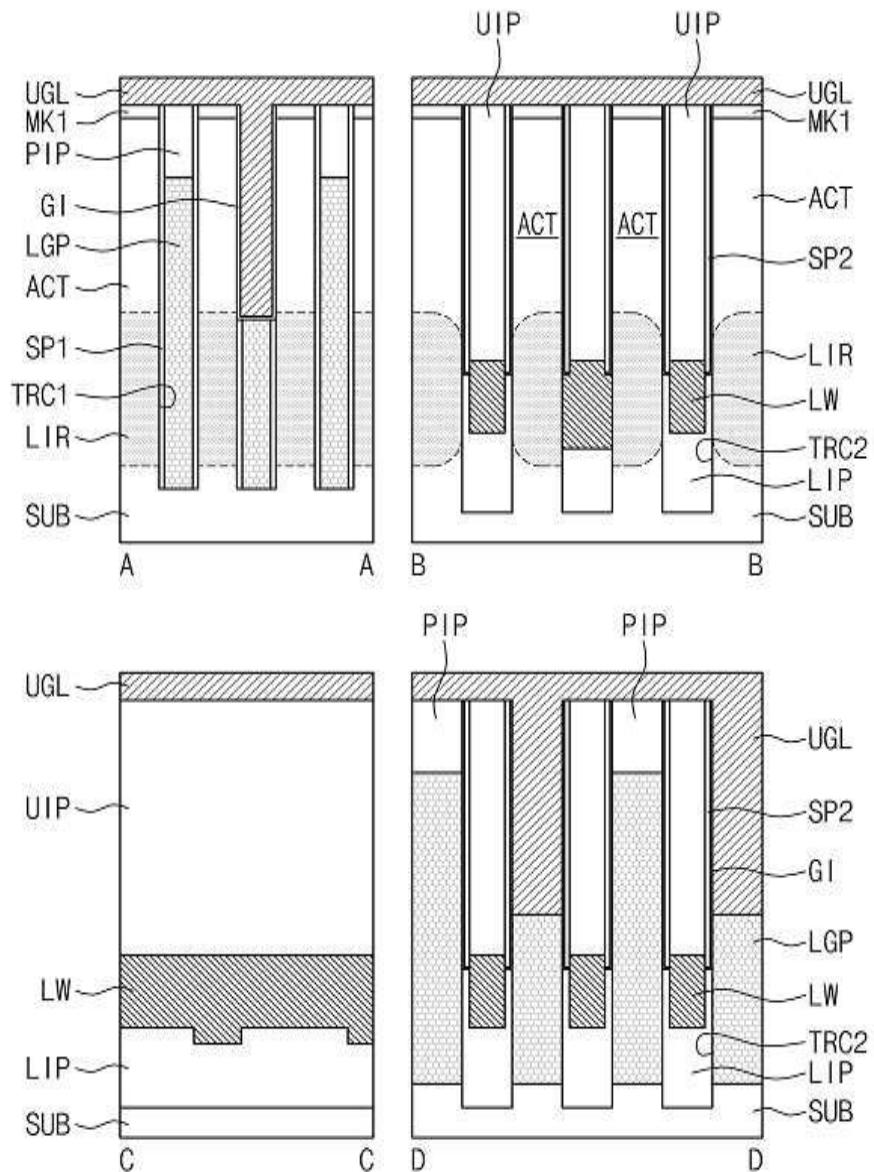

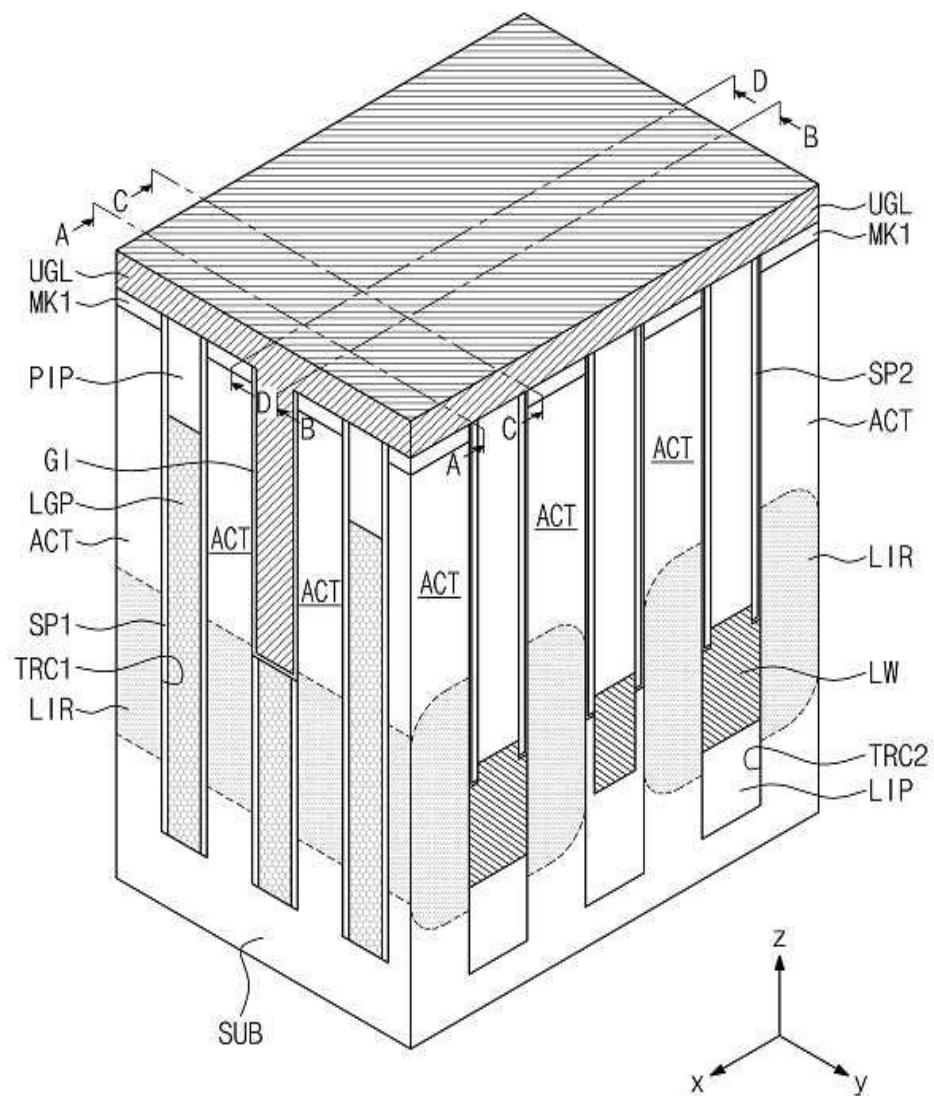

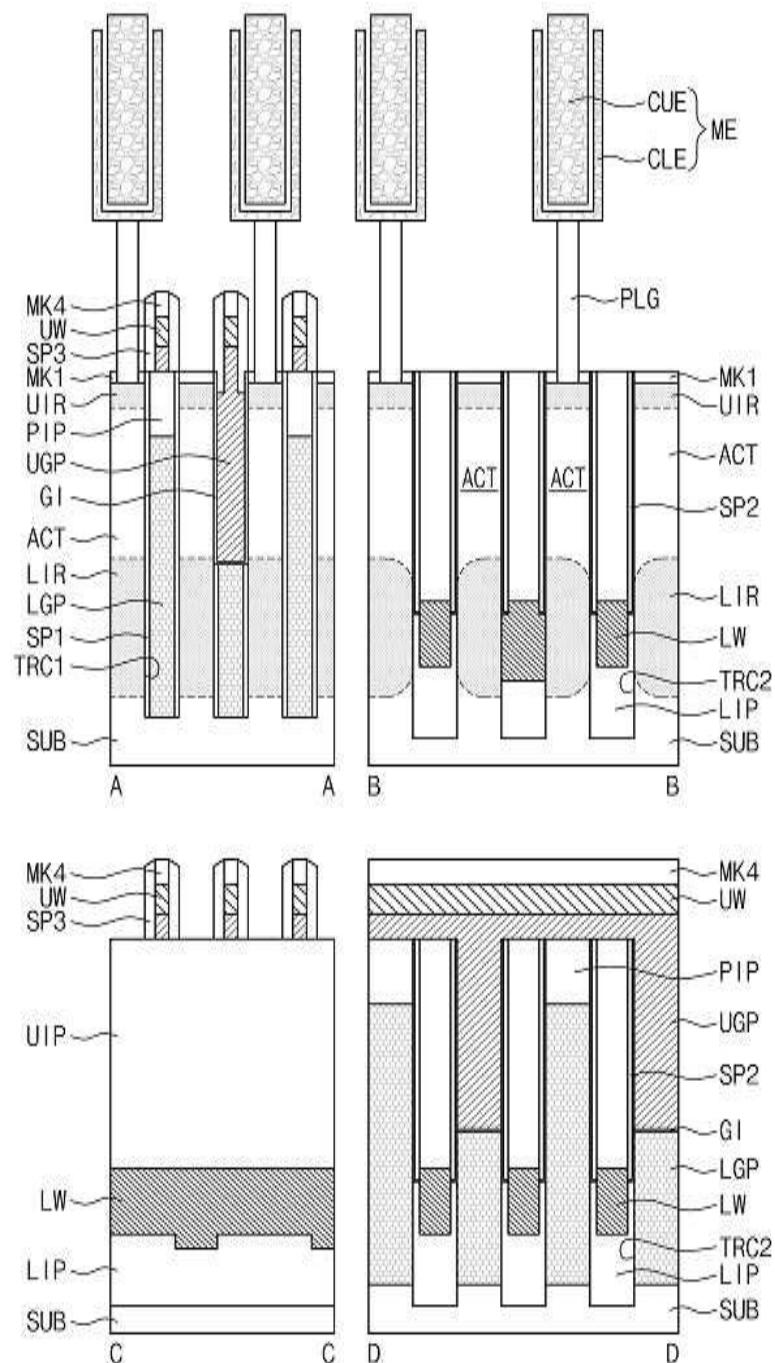

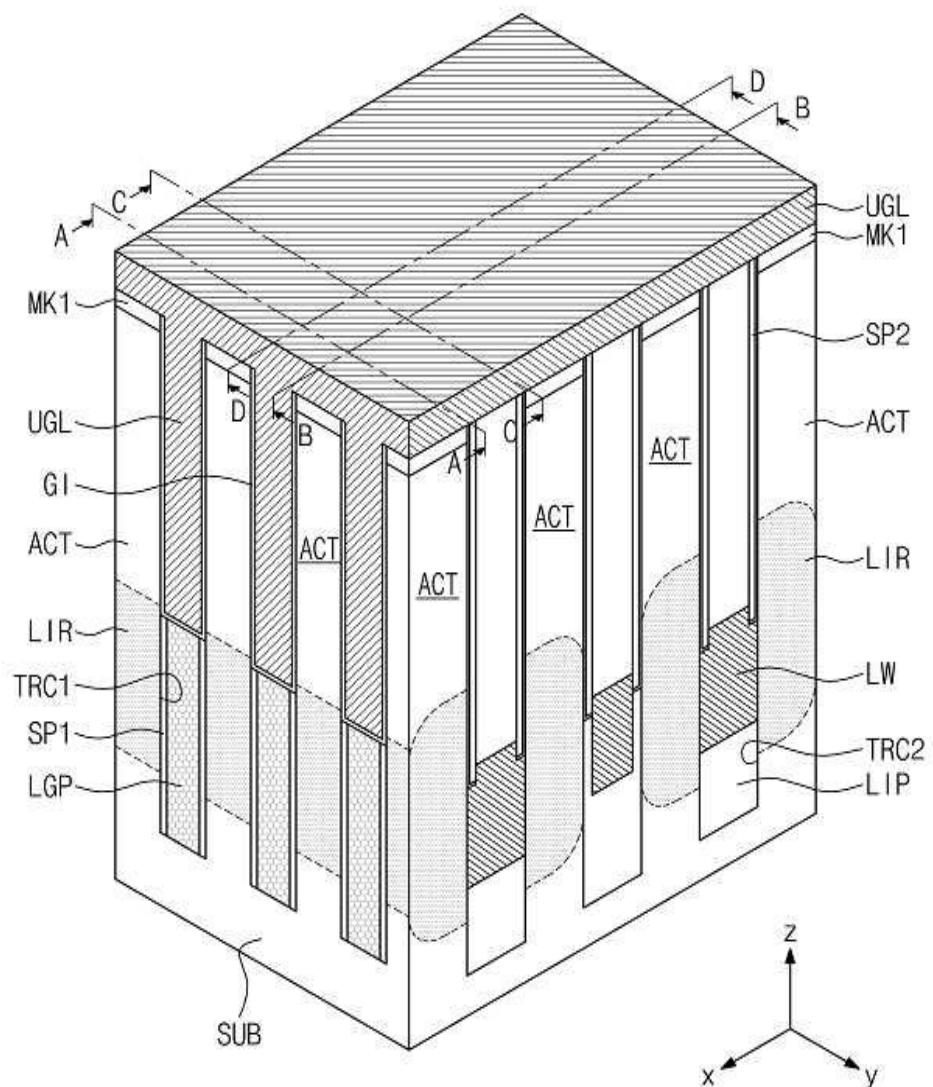

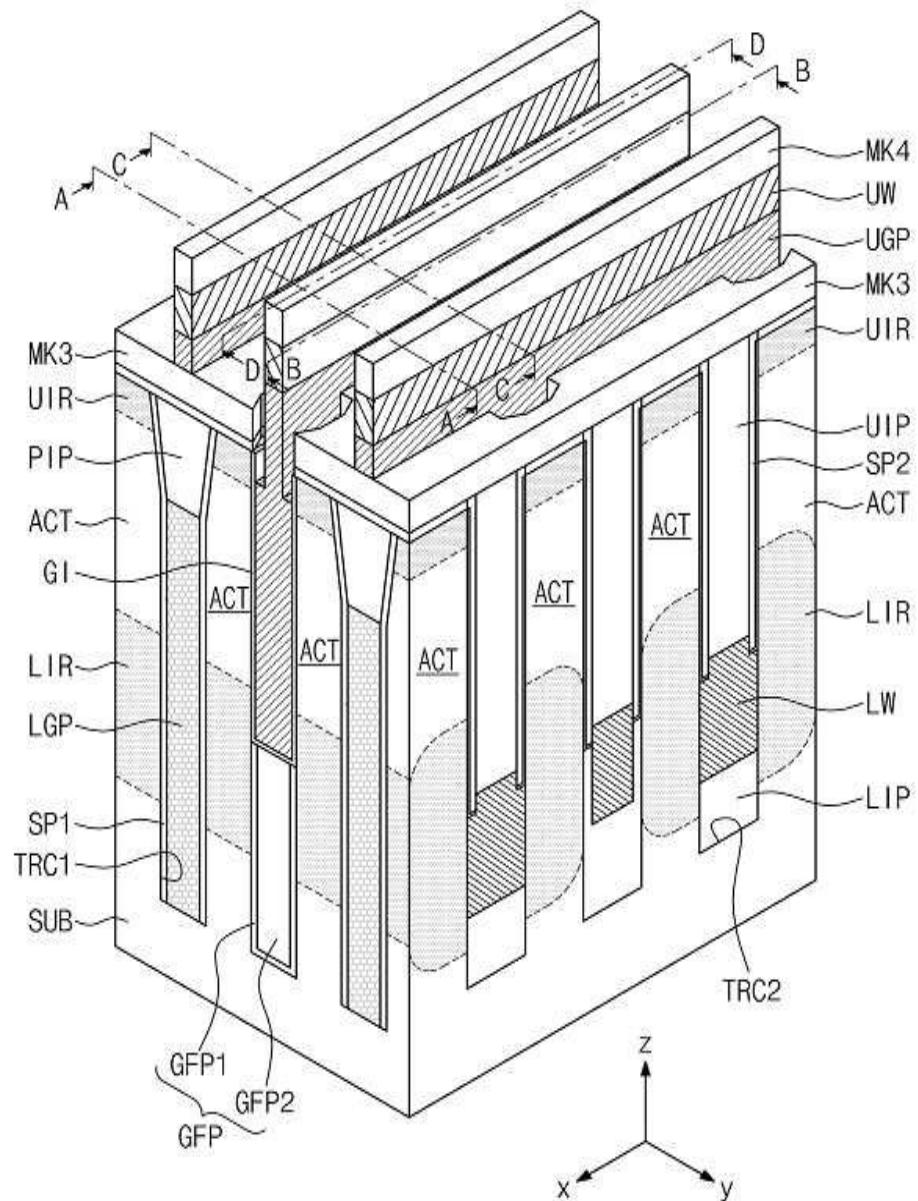

[0081] 도 23은 본 발명의 제 2 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 순서도이다. 도 24a 내지 도 31a는 본 발명의 제 2 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 단면도들이다. 도 24b 내지 도 31b는 본 발명의 제 2 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 사시도들이다.

[0082] 도 4와 도 23을 비교하면, 플러그 절연막을 형성하는 단계(S23)가 y 방향의 트렌치를 형성하는 단계(S24)에 앞서 실시된다는 점에서, 이 실시예는 도 4를 참조하여 설명한 제 1 실시예와 다르다. 이러한 차이에 의해 유발되는 제조 방법에서의 차이를 제외하면, 이 실시예는 상술한 제 1 실시예의 제조 방법에 기초하여 또는 이를 변형하여 실시될 수 있다. 따라서, 설명의 간결함을 위해, 상술한 제 1 실시예와 중복되는 기술적 특징들에 대한 설명은 생략될 수 있다.

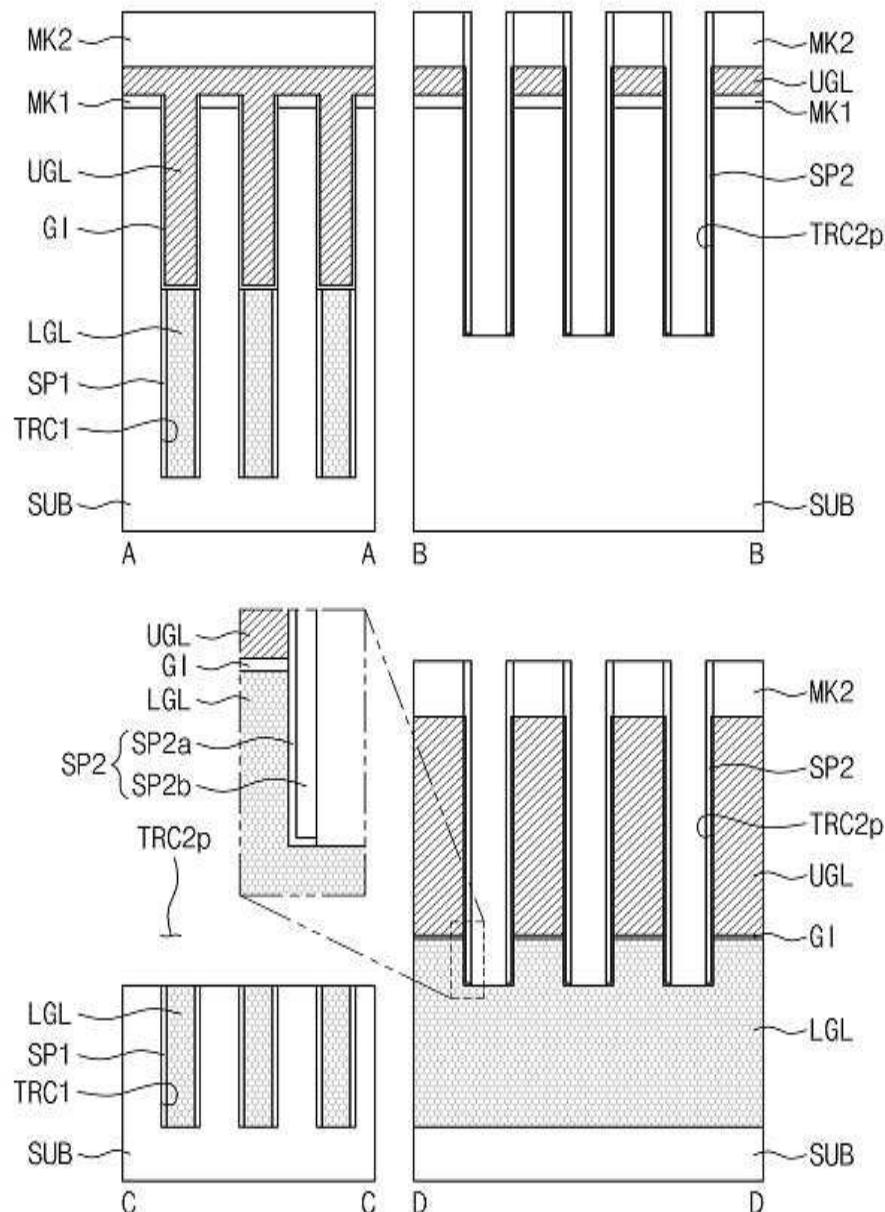

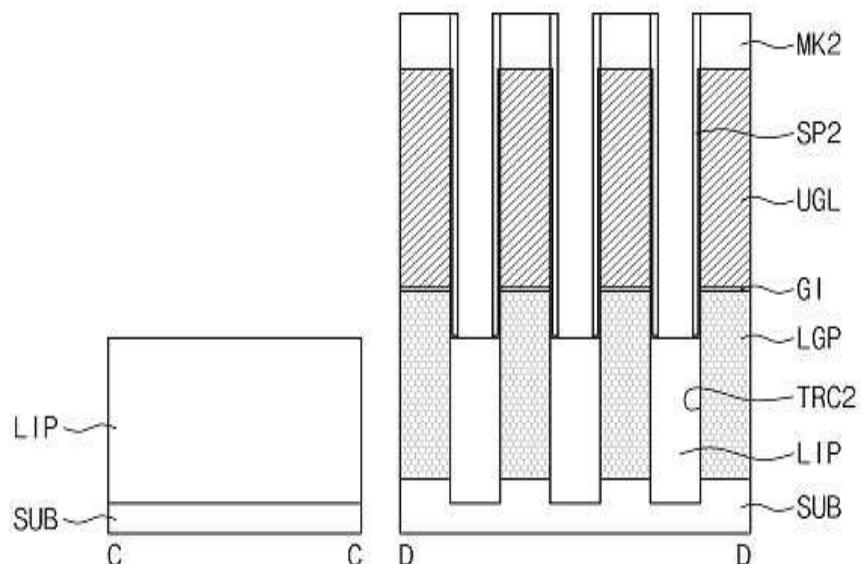

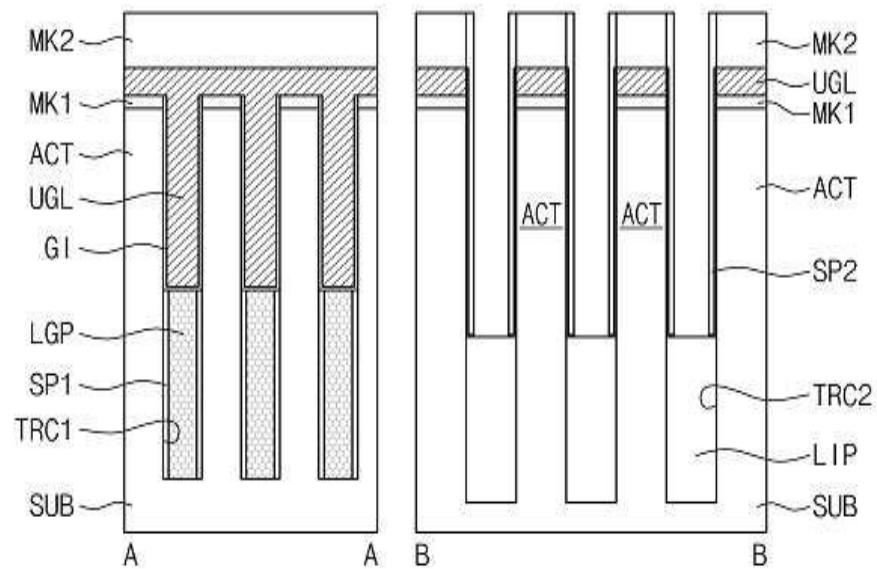

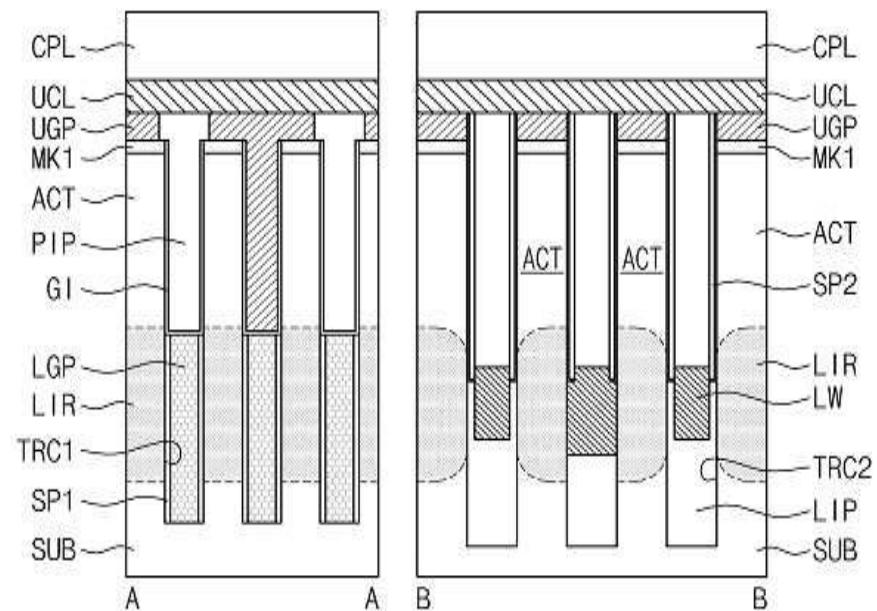

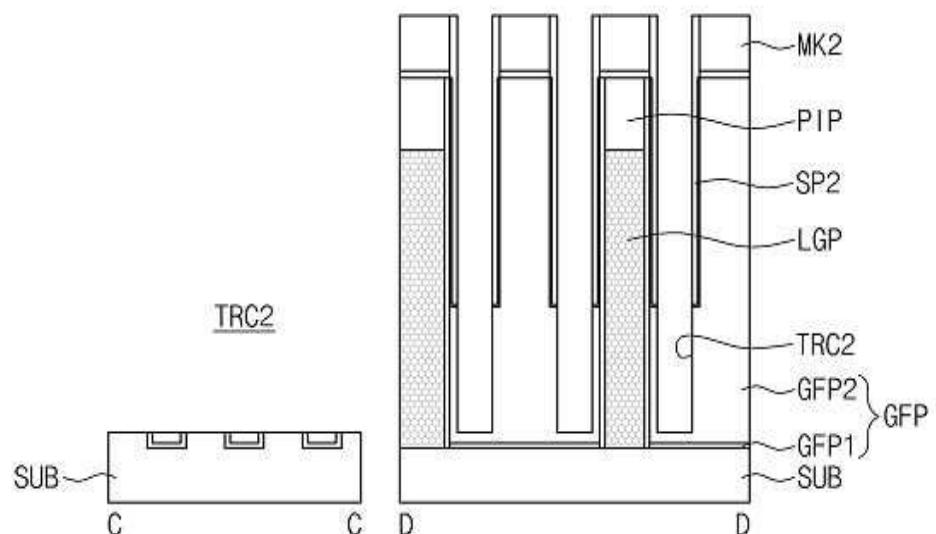

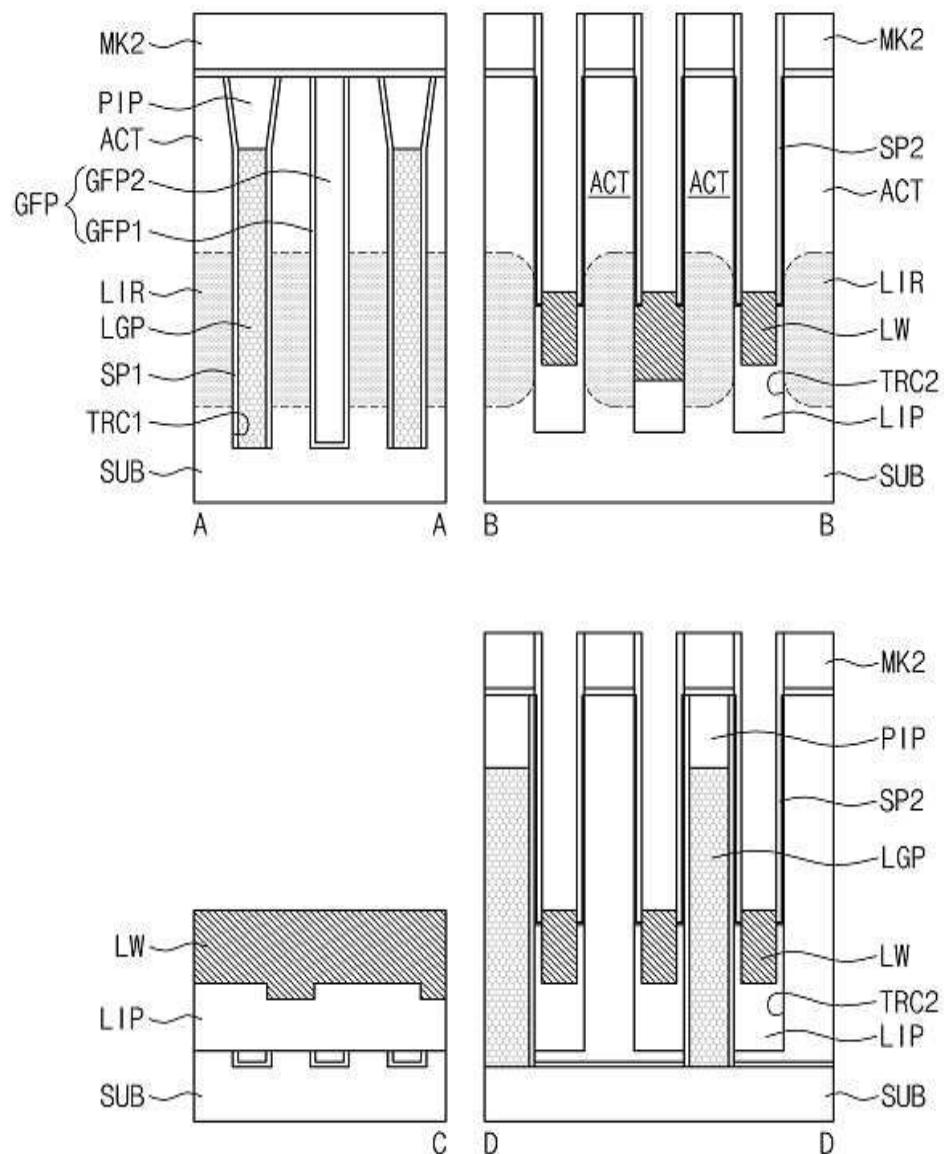

[0083] 도 23를 참조하면, 기판(SUB)을 패터닝하여 x 방향의 장축을 갖는 제 1 트렌치들(TRC1)를 형성한 후(S21), 상기 제 1 트렌치들(TRC1)의 하부 영역들을 채우는 하부 게이트막(LGL)을 형성한다(S22). 상기 제 1 트렌치들(TRC1) 및 상기 하부 게이트막(LGL)은 도 5a 내지 도 7a를 참조하여 설명된 제 1 실시예와 실질적으로 동일한 방법을 사용하여 형성될 수 있다. 이에 따라, 도 24a 및 도 24b에 도시된 것처럼, 상기 기판(SUB)의 상부에는 상기 제 1 트렌치들(TRC1)을 정의하는 제 1 마스크 패턴들(MK1)이 형성되고, 상기 제 1 트렌치(TRC1)와 상기 하부 게이트막(LGL)의 측벽들 사이에는 제 1 스페이서들(SP1)이 형성될 수 있다.

[0084] 이어서, 상기 제 1 트렌치들(TRC1)의 상부 영역들을 채우는 플러그 절연막(PIL)을 형성한다(S23). 상기 플러그 절연막(PIL)은 절연성 물질들 중의 하나로 형성될 수 있다. 예를 들면, 상기 플러그 절연막(PIL)은 실리콘 산화막 또는 실리콘 질화막일 수 있다. 일부 실시예에 따르면, 상기 플러그 절연막(PIL)을 형성하기 전에, 상기 제 1 트렌치(TRC1)의 측벽을 덮는 열산화막을 형성하는 단계가 더 실시될 수 있다. 이 경우, 상기 열산화막은 상기 플러그 절연막(PIL)과 상기 제 1 트렌치(TRC1) 사이에 개재될 수 있다. 하지만, 다른 실시예들에 따르면, 상기 열산화막을 형성하는 단계는 생략될 수 있다.

[0085] 이어서, 상기 제 1 트렌치들(TRC1)을 가로지르는 장축을 갖는 제 2 마스크 패턴들(MK2)을 형성한 후, 이를 식각 마스크로 사용하여 상기 플러그 절연막(PIL), 상기 기판(SUB) 및 상기 하부 게이트막(LGL)을 패터닝한다. 이에 따라, 도 26a 및 도 26b에 도시된 것처럼, 플러그 절연 패턴들(PIP), 활성 패턴들(ACT) 및 하부 게이트 패턴들(LGP)을 정의하는 제 2 트렌치들(TRC2)가 형성된다(S24). 구체적으로, 이 단계(S24)는 도 25a 및 도 25b에 도시된 것처럼 예비 트렌치들(TRC2p)을 형성하고, 도 26a 및 도 26b에 도시된 것처럼 상기 예비 트렌치들(TRC2p)의 측벽에 제 2 스페이서들(SP2)을 형성하는 단계를 더 포함할 수 있다. 상기 제 2 트렌치들(TRC2)을 형성하기 위한 일련의 단계들은 도 8a 내지 도 10a를 참조하여 설명된 제 1 실시예의 제조 방법을 이용하여 당업자에 의해 용이하게 실시될 수 있을 것이다. 따라서, 이에 대한 설명은 생략한다.

[0086] 이어서, 상기 제 2 트렌치(TRC2) 내에 하부 배선들(LW)을 형성한다(S25). 이 단계(S25)는 도 11a 내지 도 15a를 참조하여 설명된 실시예와 동일하게 실시될 수 있다. 그 결과, 도 27a 및 도 27b에 도시된 것처럼, 상기 하

부 배선(LW)의 아래에는 상기 하부 배선(LW)을 형성하기 위한 주형으로 이용되는 하부 절연 패턴들(LIP)이 형성되고, 상기 활성 패턴들(ACT)의 하부 영역들에는 상기 하부 배선들(LW)에 의해 연결되는 하부 불순물 영역들(LIR)이 형성될 수 있다.

[0087] 상기 하부 배선(LW) 상에 배치되어 상기 제 2 트렌치(TRC2)의 상부영역들 채우는 상부 절연 패턴들(UIP)을 형성한 후, 상기 플러그 절연 패턴들(PIP)을 패터닝하여 상기 하부 게이트 패턴들(LGP) 중의 일부의 상부면들을 노출시키는 게이트 홀들(GH)을 형성한다. 도 28a 및 도 28b에 도시된 것처럼, 상기 게이트 홀들(GH)은 도 16a에서 상기 상부 게이트 패턴들(UGP)이 형성되는 영역들에 대응되는 위치들에 형성될 수 있다.

[0088] 이어서, 상기 게이트 홀들(GH)의 내벽에 게이트 절연막(GI)을 형성한 후, 상기 게이트 홀들(GH)을 채우는 상부 게이트막(UGL)을 형성한다(S26). 상기 상부 게이트막(UGL)은 도 29a 및 도 29b에 도시된 것처럼, 상기 게이트 홀들(GH)로부터 연장되어 상기 플러그 절연 패턴들(PIP) 및 상기 상부 절연 패턴들(UIP)의 상부면을 덮을 수 있다. 상기 게이트 절연막(GI) 및 상기 상부 게이트막(UGL)은 도 7a를 참조하여 설명된 제 1 실시예의 제조 방법을 이용하여 형성될 수 있으며, 이러한 변형은 당업자에 의해 용이하게 실시될 수 있다는 점에서 이러한 변형된 제조 과정에 대한 설명은 생략한다.

[0089] 이후, 도 30a 및 도 30b 그리고 도 31a 및 도 31b에 도시된 것처럼, 상부 배선(UW) 및 메모리 요소(ME)를 차례로 형성한다(S27, S28). 이 단계들은 도 17a 내지 도 19a를 참조하여 설명된 제 1 실시예의 제조 방법을 이용하여 형성될 수 있다.

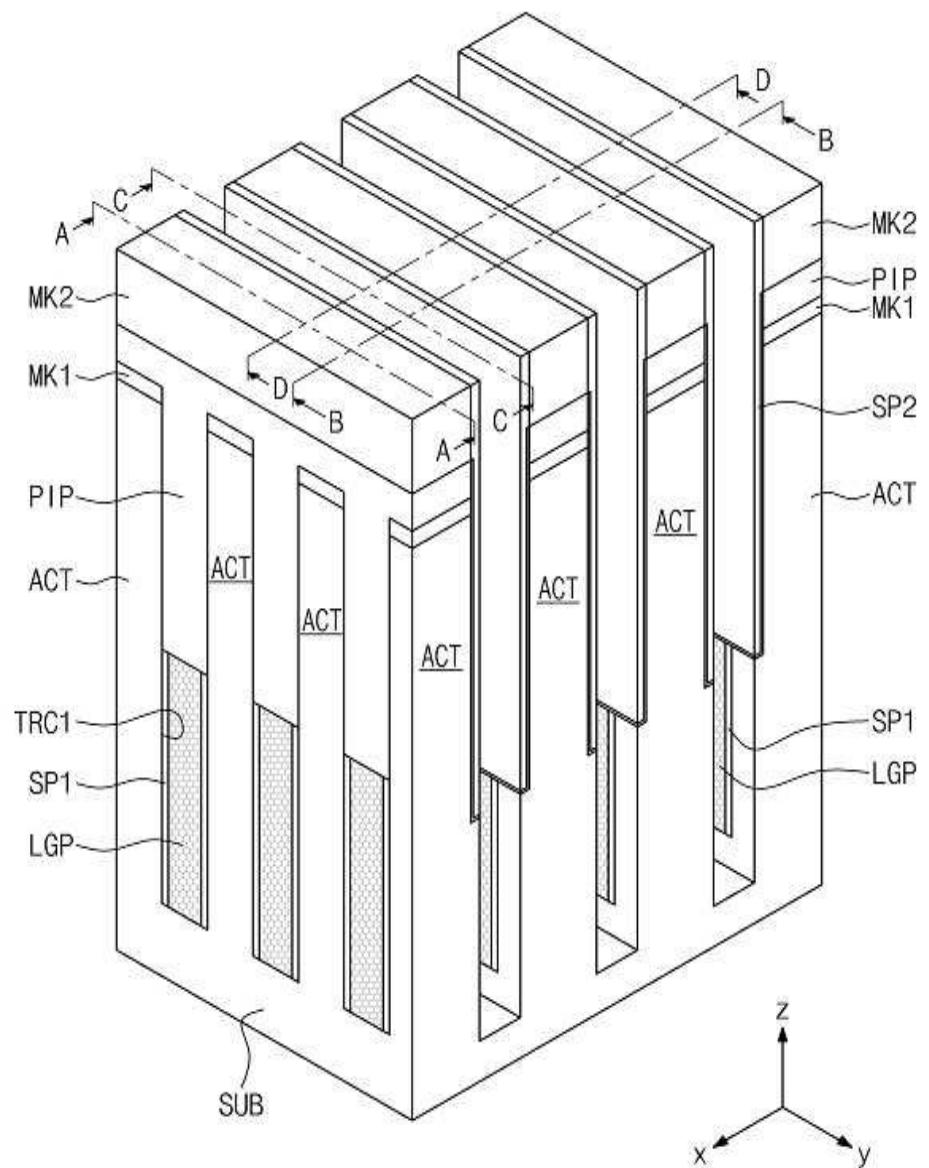

#### [0090] [제조 방법- 제 3 실시예]

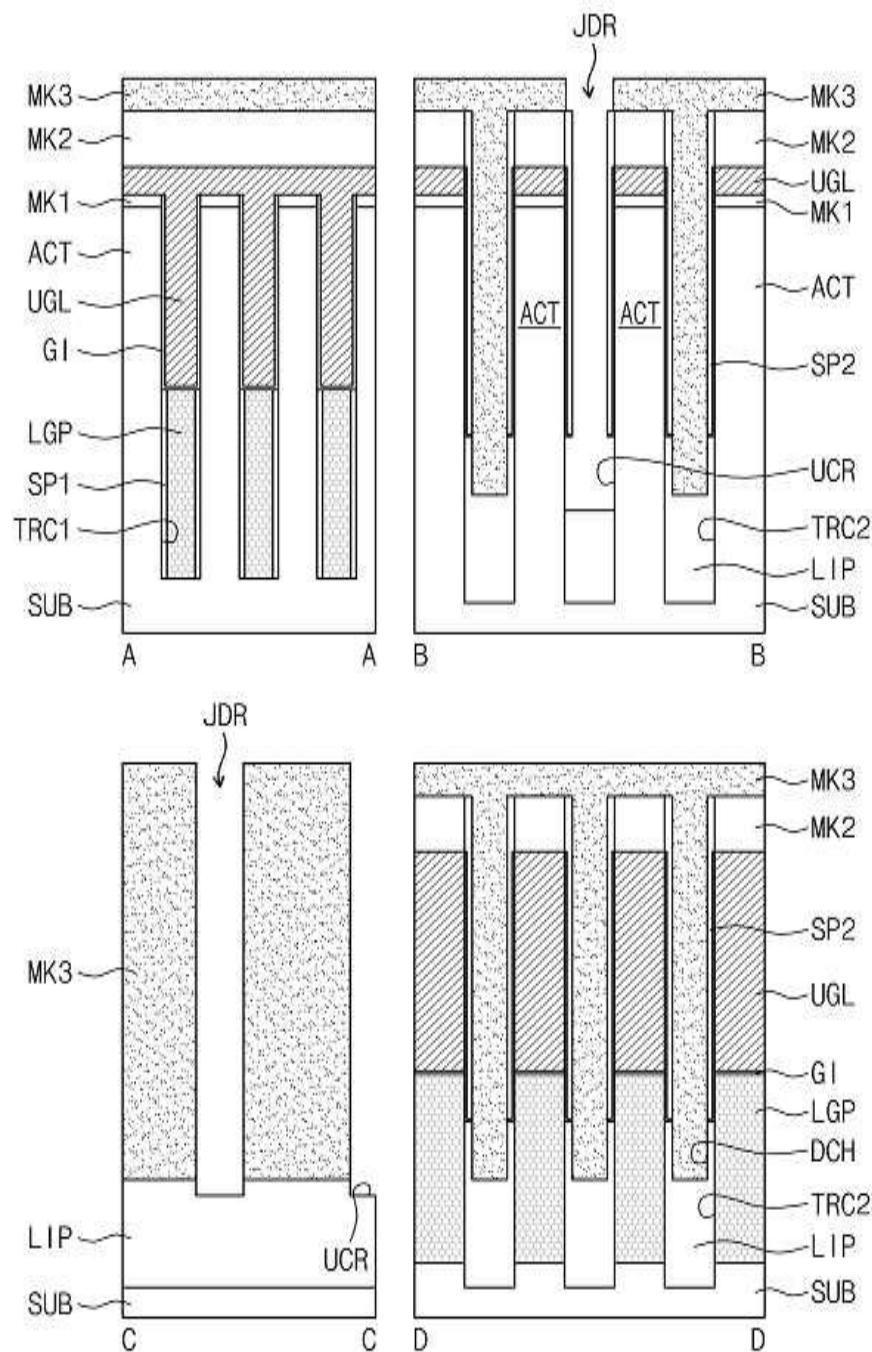

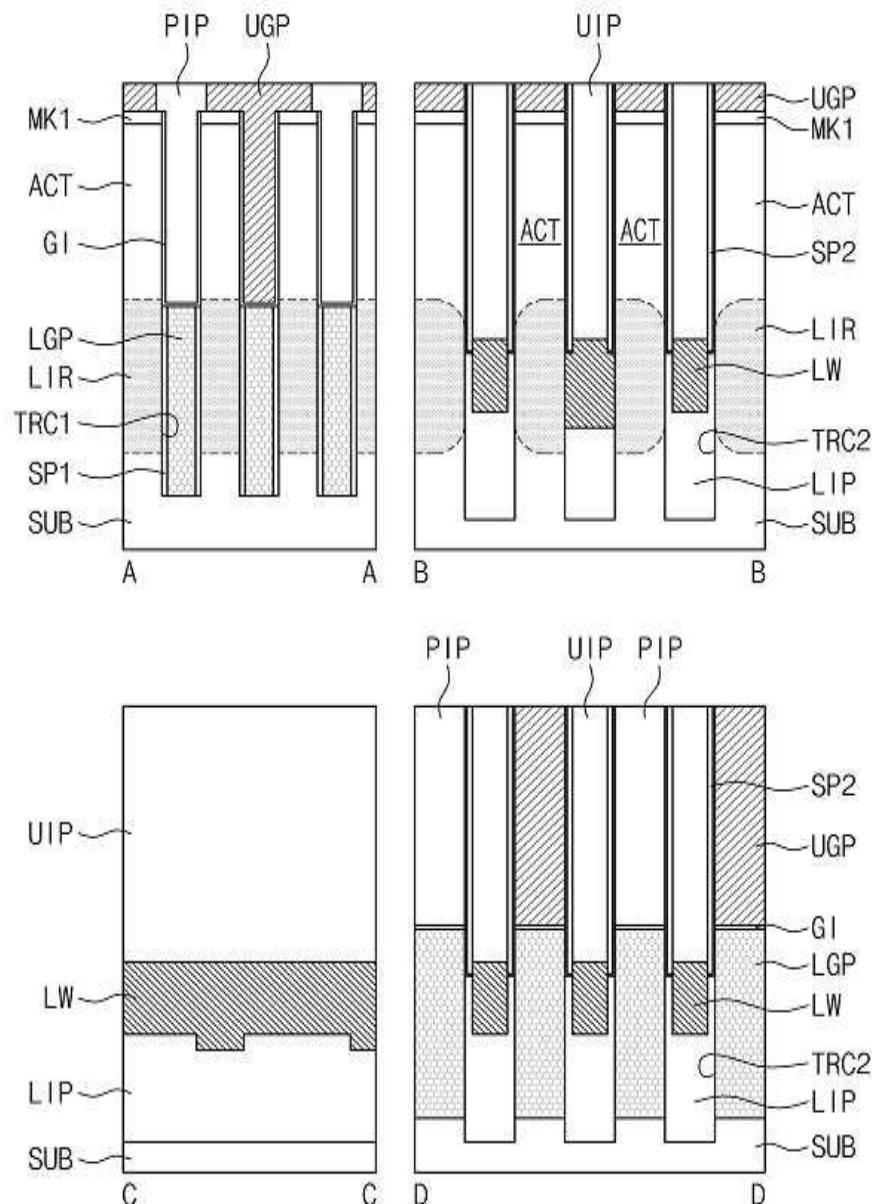

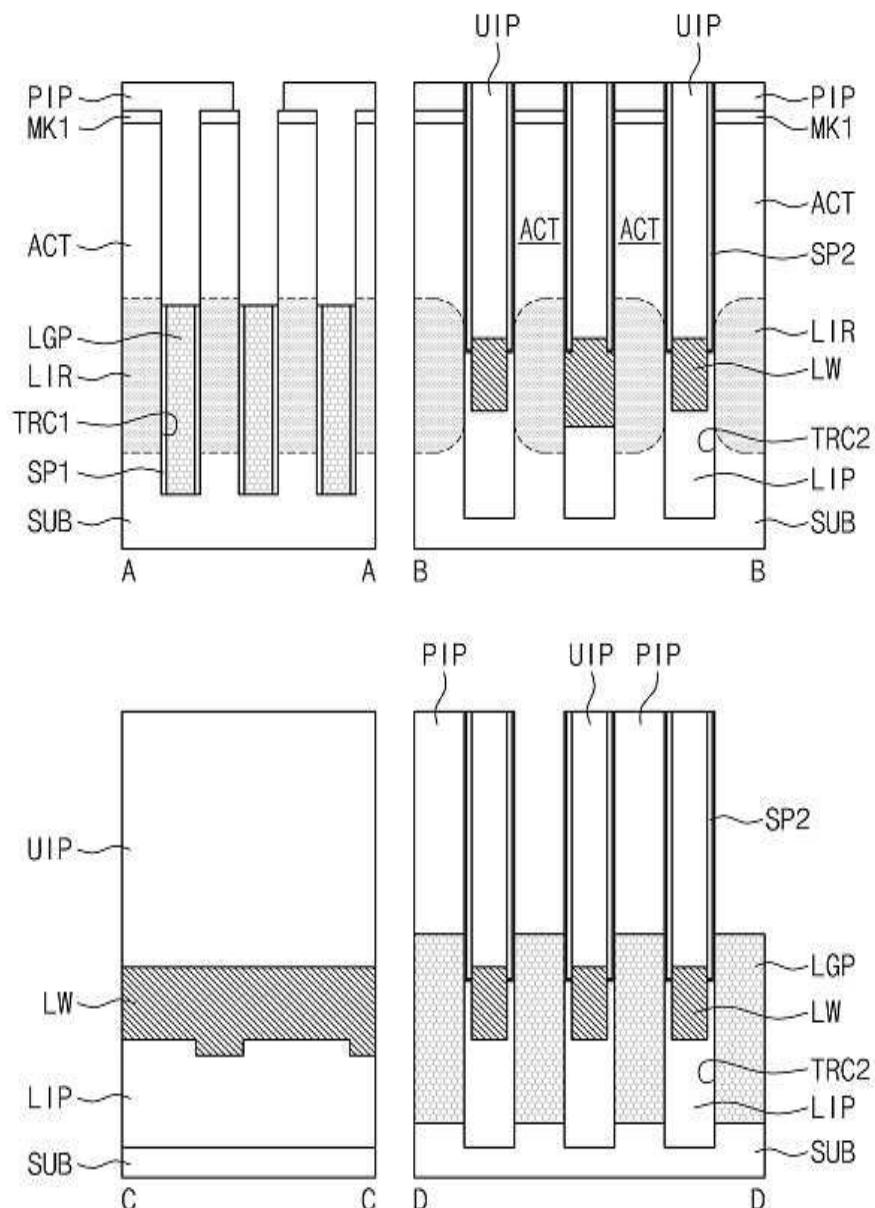

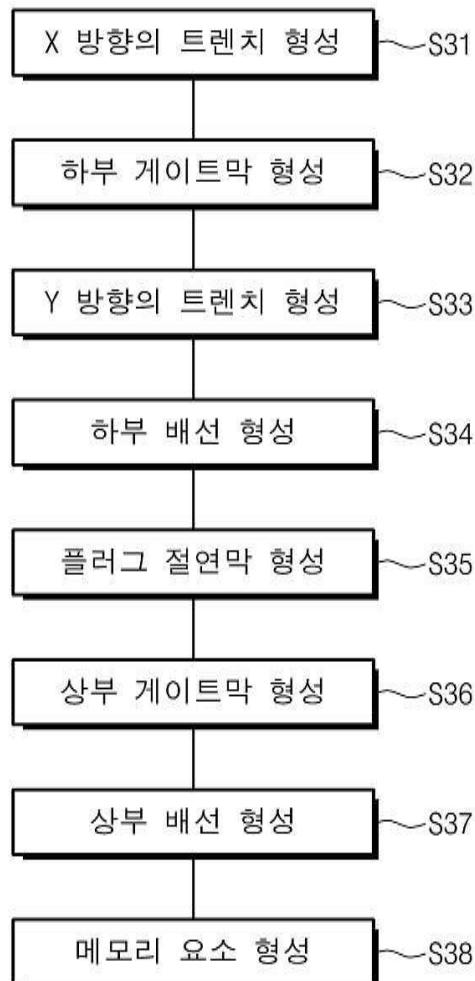

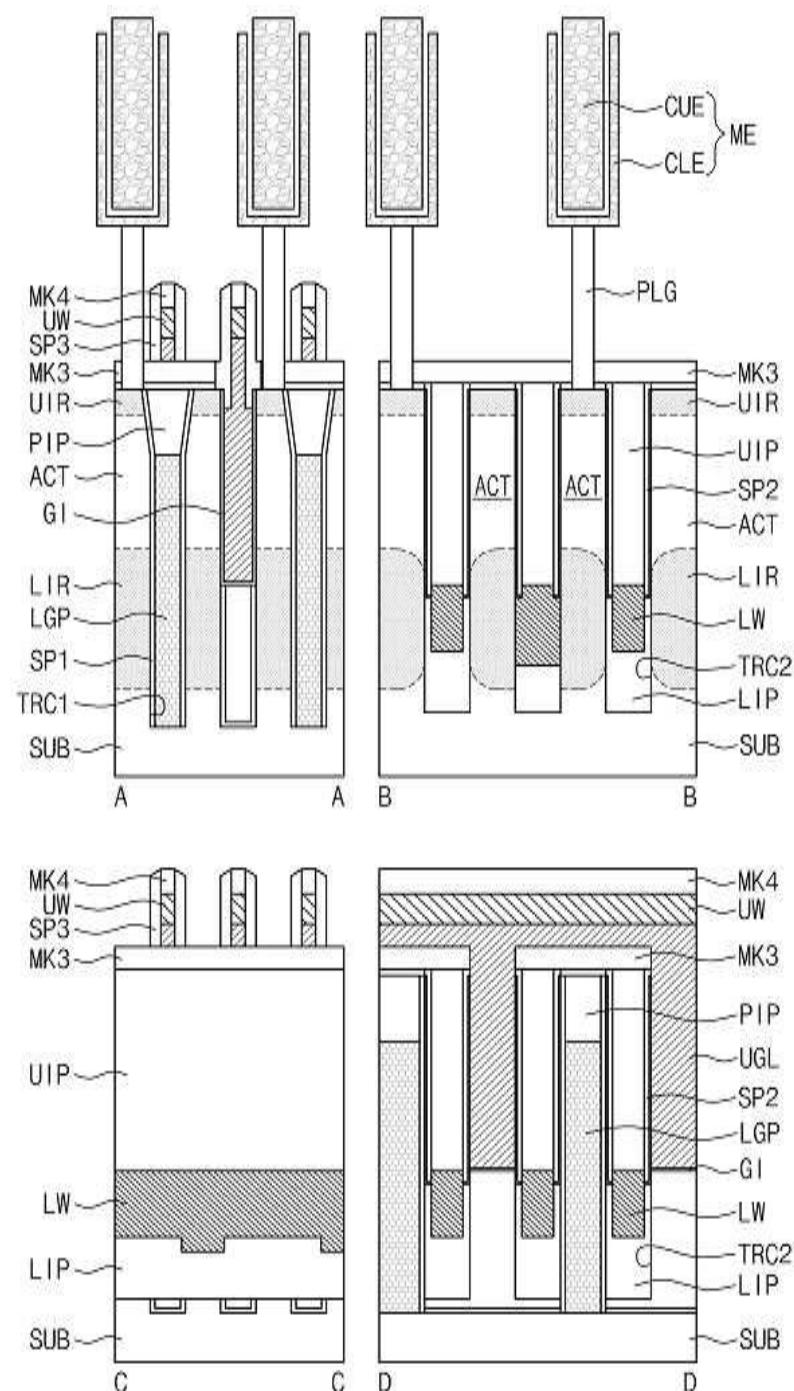

[0091] 도 32는 본 발명의 제 3 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 순서도이다. 도 33a 내지 도 40a는 본 발명의 제 3 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 단면도들이다. 도 33b 내지 도 40b는 본 발명의 제 3 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 사시도들이다.

[0092] 도 4와 도 32를 비교하면, 상부 게이트막을 형성하는 단계(S36)가 플러그 절연막을 형성하는 단계(S35) 이후에 실시된다는 점에서, 이 실시예는 도 4를 참조하여 설명한 제 1 실시예와 다르다. 이러한 차이에 의해 유발되는 제조 방법에서의 차이를 제외하면, 이 실시예는 상술한 제 1 실시예의 제조 방법에 기초하여 또는 이를 변형하여 실시될 수 있다. 따라서, 설명의 간결함을 위해, 상술한 제 1 실시예와 중복되는 기술적 특징들에 대한 설명은 생략될 수 있다.

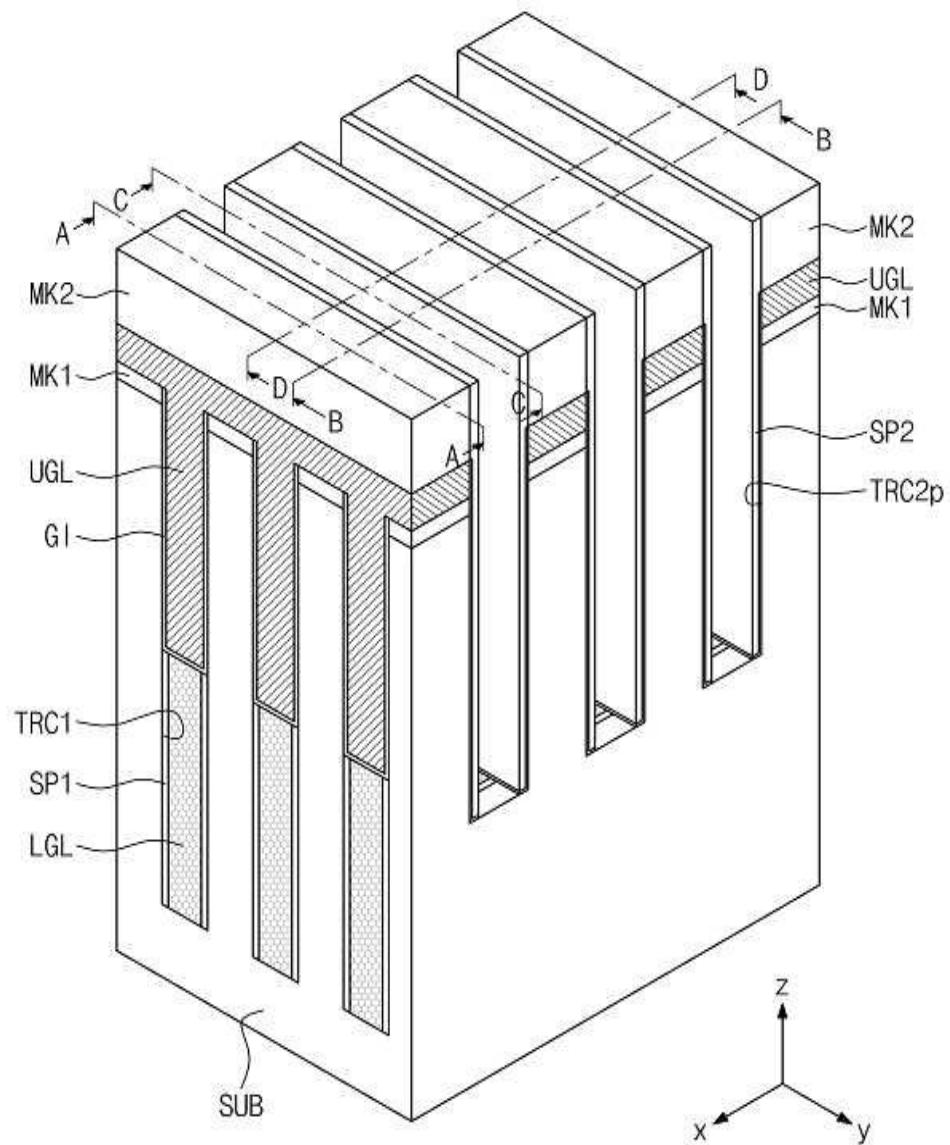

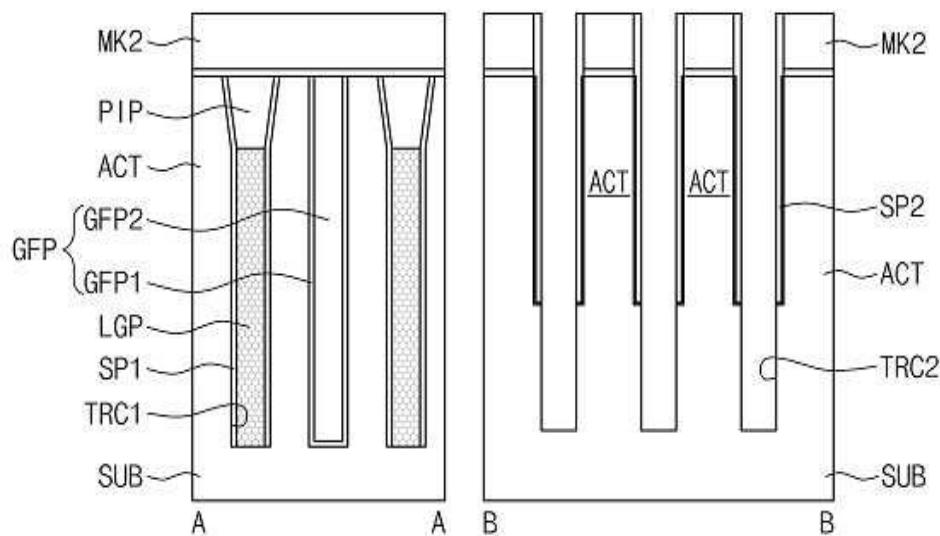

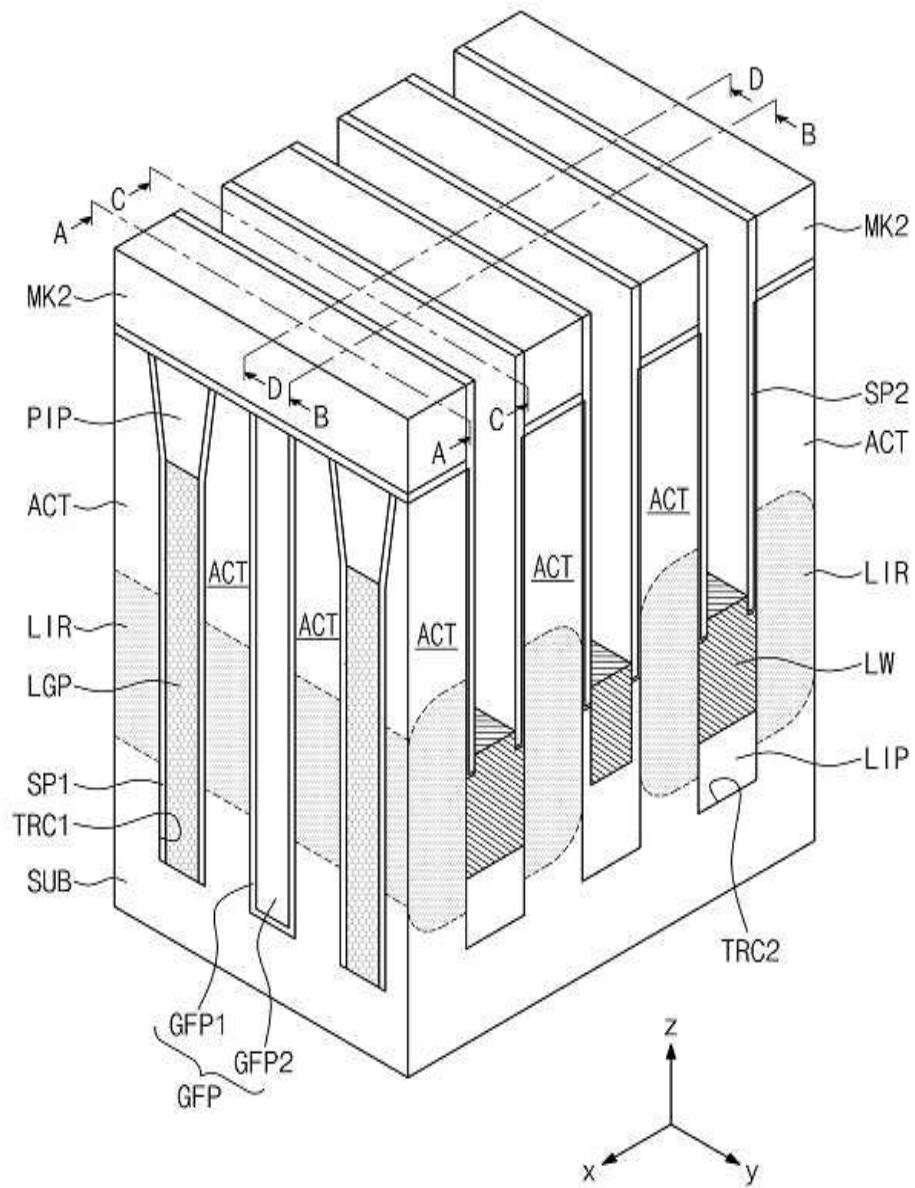

[0093] 도 32를 참조하면, 기판(SUB)을 패터닝하여 x 방향의 장축을 갖는 제 1 트렌치들(TRC1)를 형성한 후(S31), 상기 제 1 트렌치들(TRC1)을 채우는 하부 게이트막(LGL)을 형성한다(S32). 이 실시예에 따르면, 도 33a 및 도 33b에 도시된 것처럼, 상기 하부 게이트막(LGL)은 제 1 스페이서들(SP1)이 형성된 상기 제 1 트렌치들(TRC1)을 실질적으로 그리고 완전히 채우도록 형성될 수 있다.

[0094] 이어서, 상기 제 1 트렌치들(TRC1)을 가로지르는 장축을 갖는 제 2 마스크 패턴들(MK2)을 형성한 후, 이를 식각 마스크로 사용하여 상기 기판(SUB) 및 상기 하부 게이트막(LGL)을 패터닝한다. 이에 따라, 도 34a 및 도 34b에 도시된 것처럼, 활성 패턴들(ACT) 및 하부 게이트 패턴들(LGP)을 정의하는 제 2 트렌치들(TRC2)가 형성된다(S33). 구체적으로, 이 단계(S33)는 도 8a 내지 도 10a를 참조하여 설명된 제 1 실시예의 제조 방법을 이용하여 당업자에 의해 용이하게 실시될 수 있을 것이다.

[0095] 이어서, 상기 제 2 트렌치(TRC2) 내에 하부 배선들(LW)을 형성한다(S34). 이 단계(S34)는 도 11a 내지 도 15a를 참조하여 설명된 실시예와 동일하게 실시될 수 있다. 그 결과, 도 35a 및 도 35b에 도시된 것처럼, 상기 하부 배선(LW)의 아래에는 상기 하부 배선(LW)을 형성하기 위한 주형으로 이용되는 하부 절연 패턴들(LIP)이 형성되고, 상기 활성 패턴들(ACT)의 하부 영역들에는 상기 하부 배선들(LW)에 의해 연결되는 하부 불순물 영역들(LIR)이 형성될 수 있다.

[0096] 이어서, 상기 하부 게이트 패턴들(LGP) 중의 일부의 상부에 배치되는 플러그 절연 패턴들(PIP)을 형성한다(S35). 이 단계(S35)는 상기 하부 게이트 패턴들(LGP) 중 일부의 상부면들을 노출시키는 홀들을 형성한 후, 절연성 물질로 이들을 채우는 단계를 포함할 수 있다. 이 단계(S35) 동안, 상기 하부 배선들(LW)이 형성된 상기 제 2 트렌치들(TRC2)을 채우는 상부 절연 패턴들(UIP)이 더 형성될 수 있다.

[0097] 한편, 이 실시예에 따르면, 도 36a 및 도 36b에 도시된 것처럼, 상기 홀의 바닥면은 상기 하부 배선(LW)의 상부면과 상기 활성 패턴(ACT)의 상부면 사이에 위치할 수 있다. 결과적으로, 이 실시예는 상기 홀들의 깊이에 있어

서 상술한 제 1 실시예와 다를 수 있다. 또한, 상기 홀들을 형성하는 단계에서, 제 1 실시예에서의 상기 상부 게이트막(UGL)이 아직 형성되지 않았다는 점에서, 이 실시예는 상술한 제 1 실시예와 다르다. 이러한 차이점들을 제외하면, 상기 플러그 절연 패턴들(PIP)을 형성하는 방법은 도 16a 및 도 16b을 참조하여 설명된 제 1 실시예의 방법을 이용하여 실시될 수 있다. 또한, 도 36a 및 도 36b에 도시된 것처럼, 상기 플러그 절연 패턴들(PIP)이 형성되는 위치들은 제 1 실시예의 그것과 동일할 수 있다.

[0098] 이어서, 도 37a 및 도 37b에 도시된 것처럼 상기 하부 게이트 패턴들(LGP) 중의 다른 일부의 상부면들을 노출시키는 게이트 홀들(GH)을 형성한 후, 도 38a 및 도 38b에 도시된 것처럼 상기 게이트 홀들(GH)을 채우는 상부 게이트막(UGL)을 형성한다(S36). 이 단계(S36)는 도 28a 및 도 29a를 참조하여 설명된 제 2 실시예의 제조 방법을 이용하여 실시될 수 있다.

[0099] 이어서, 도 39a 및 도 39b에 도시된 것처럼 상기 제 4 마스크 패턴(MK4)을 사용하여 상기 상부 게이트막(UGL)을 패터닝함으로써, 상부 배선(UW) 및 이에 접속하는 상부 게이트 패턴들(UGP)을 형성한다(S37). 상기 활성 패턴들(ACT)의 상부 영역에 상부 불순물 영역(UIR)을 형성한 후, 도 40a 및 도 40b에 도시된 것처럼 상기 상부 불순물 영역들(UIR)에 접속하는 플러그들(PLG) 및 이들에 접속하는 메모리 요소들(ME)을 형성한다(S38). 이 단계들은 도 17a 내지 도 19a를 참조하여 설명된 제 1 실시예의 제조 방법을 이용하여 형성될 수 있다.

#### [0100] [제조 방법- 제 4 실시예]

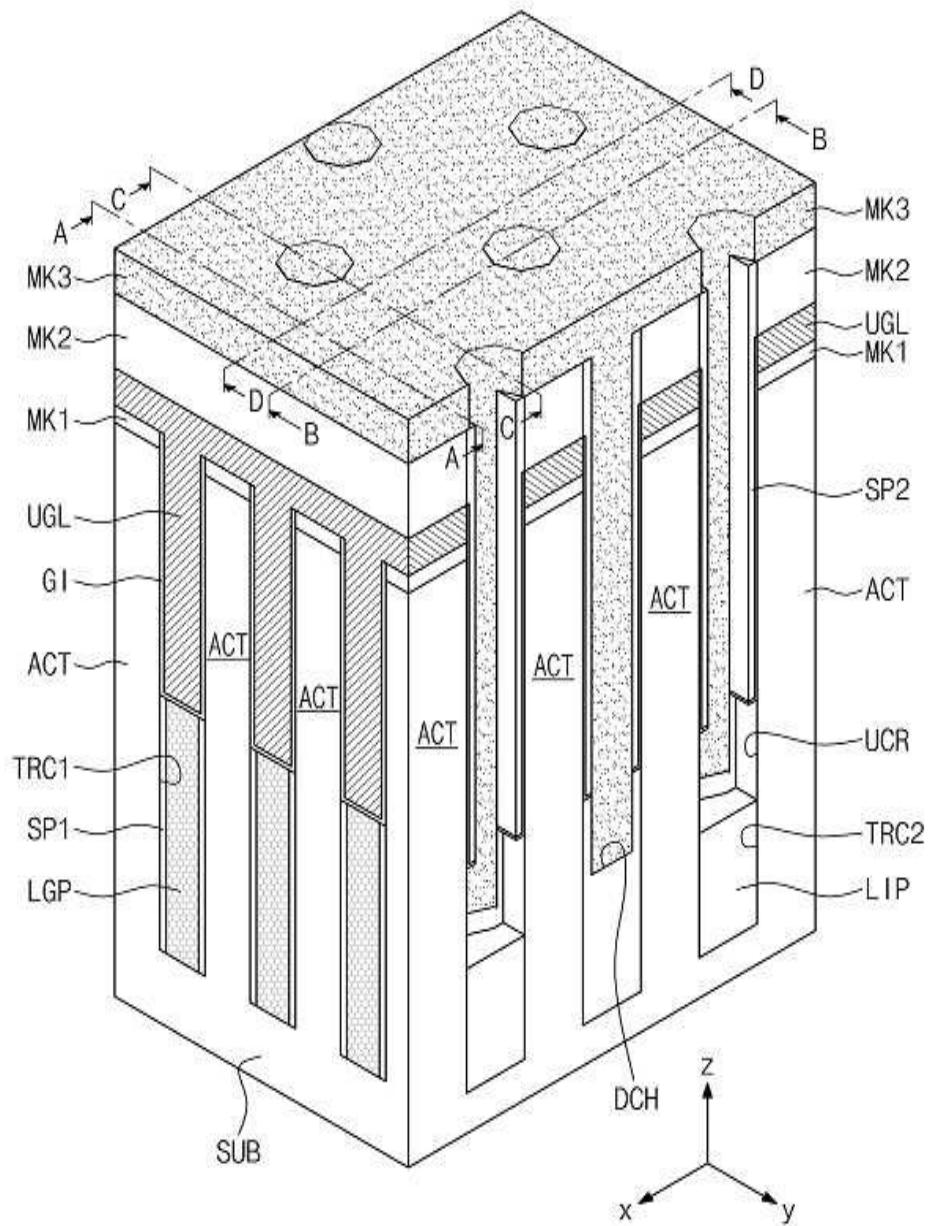

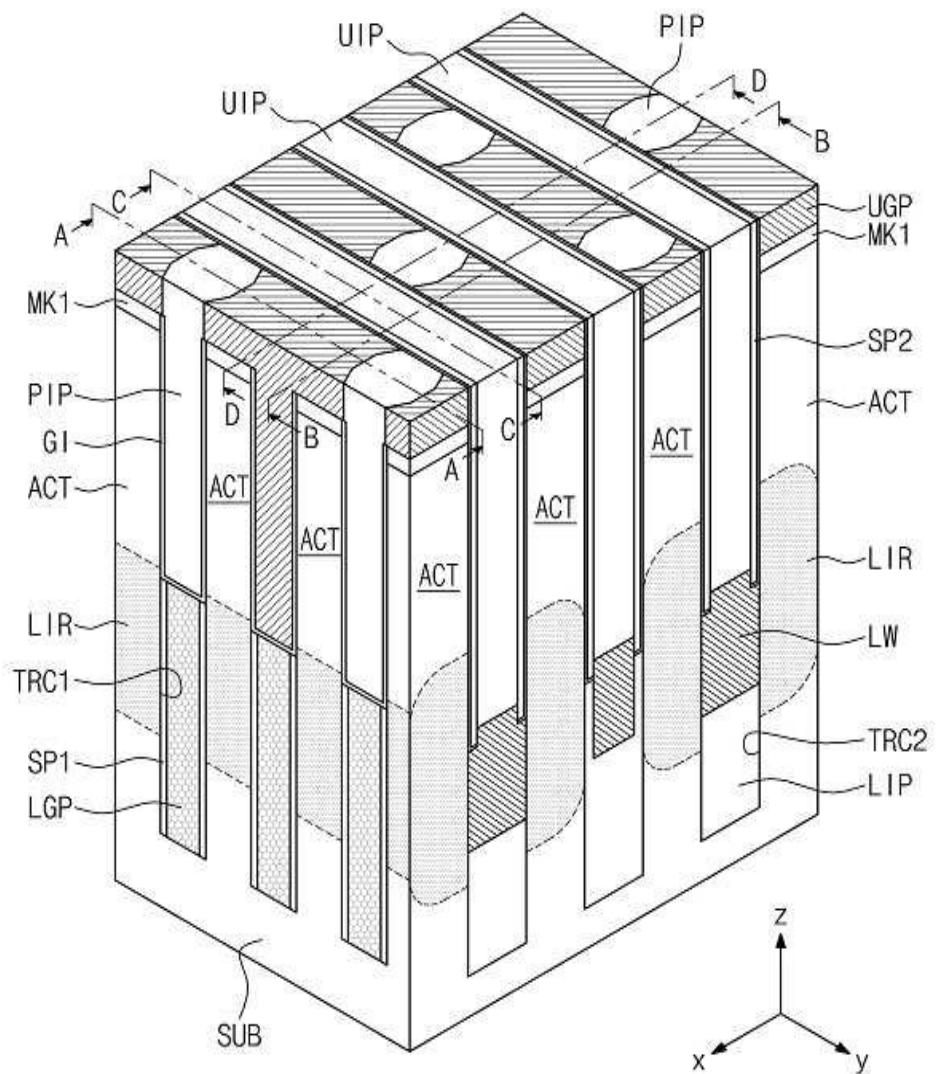

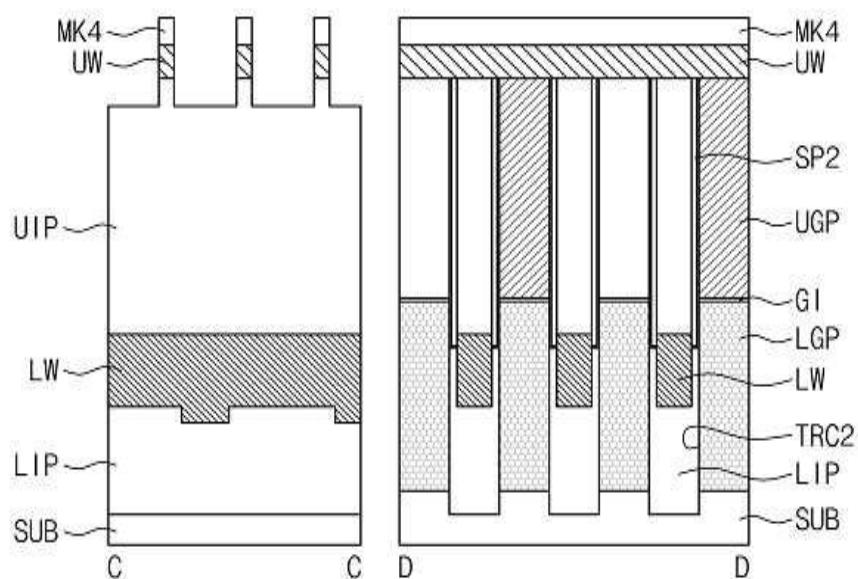

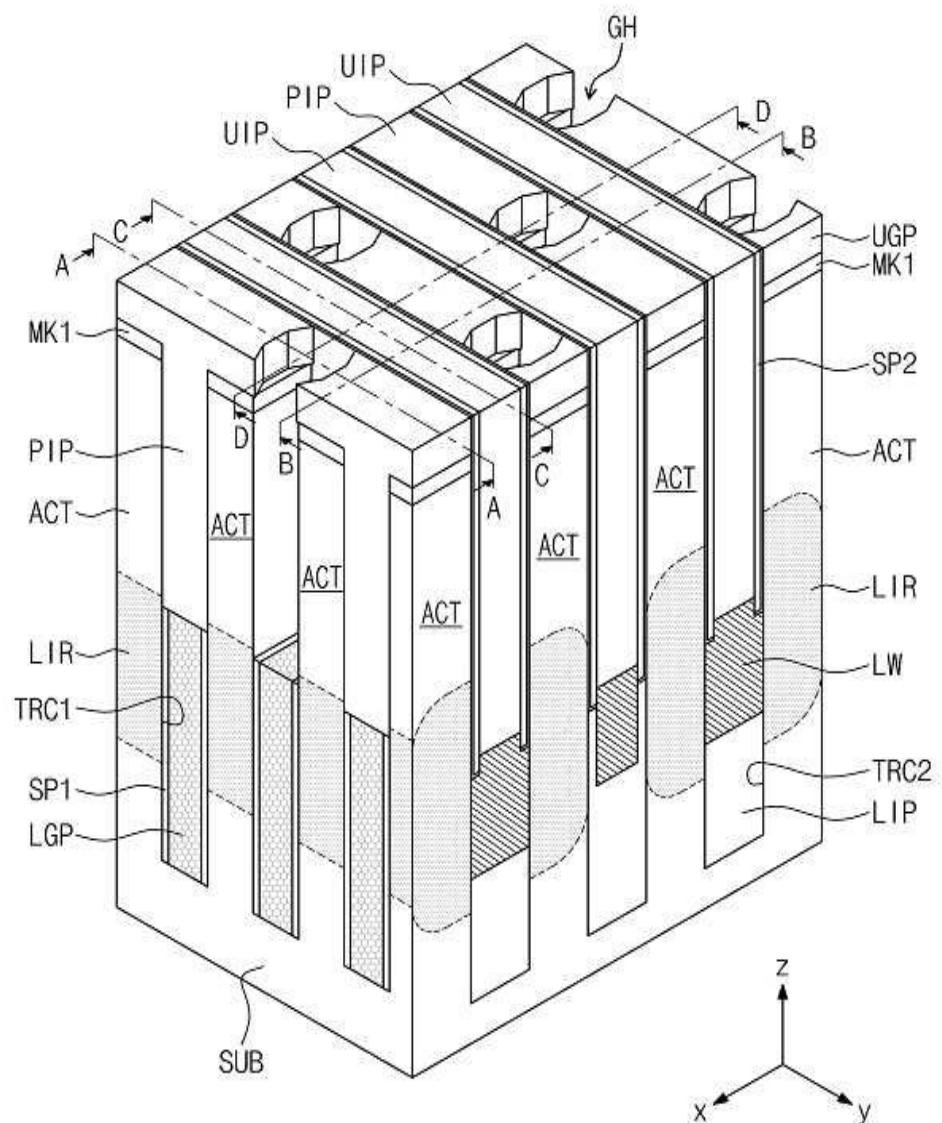

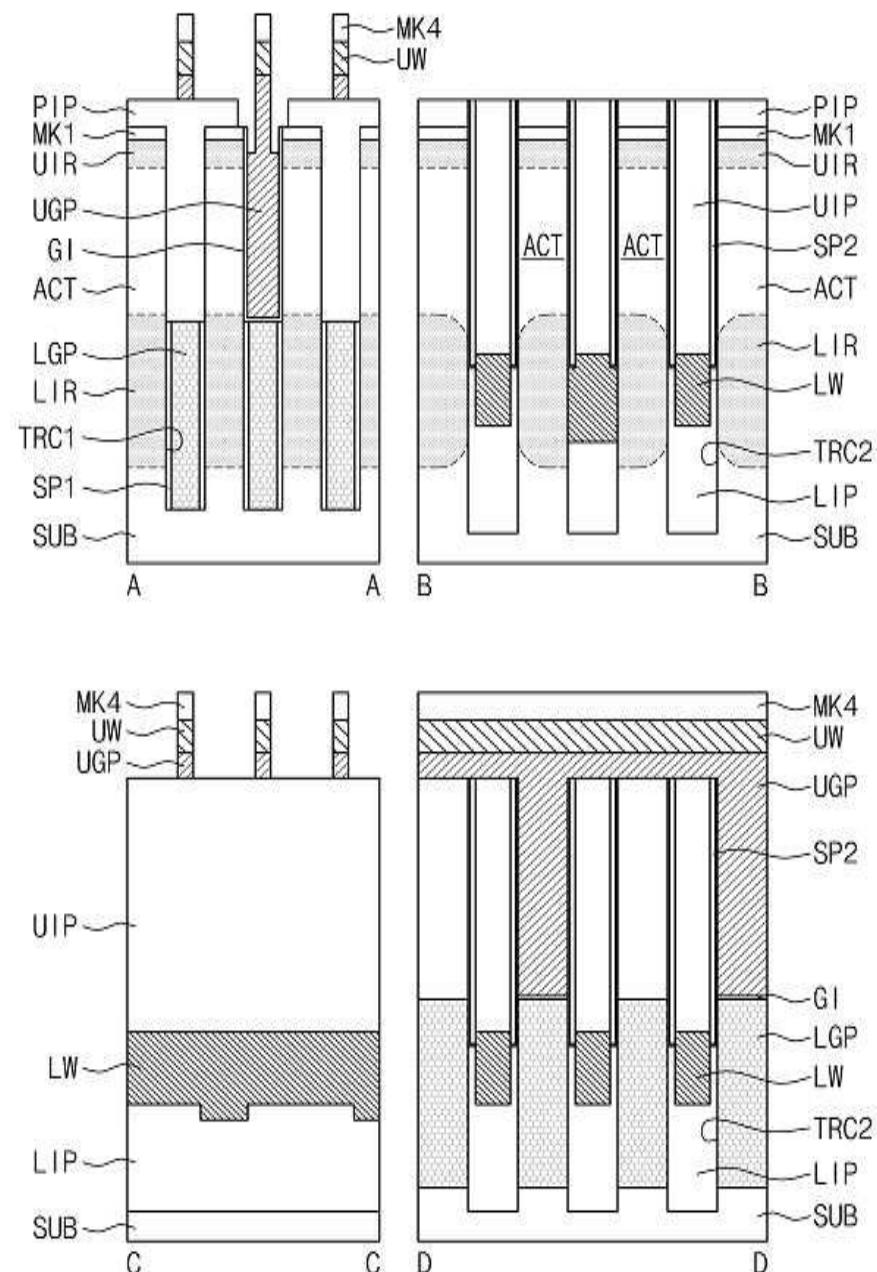

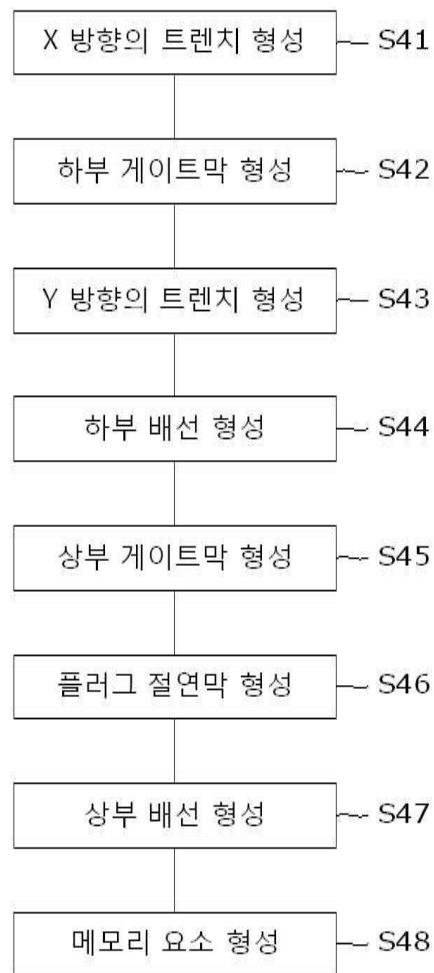

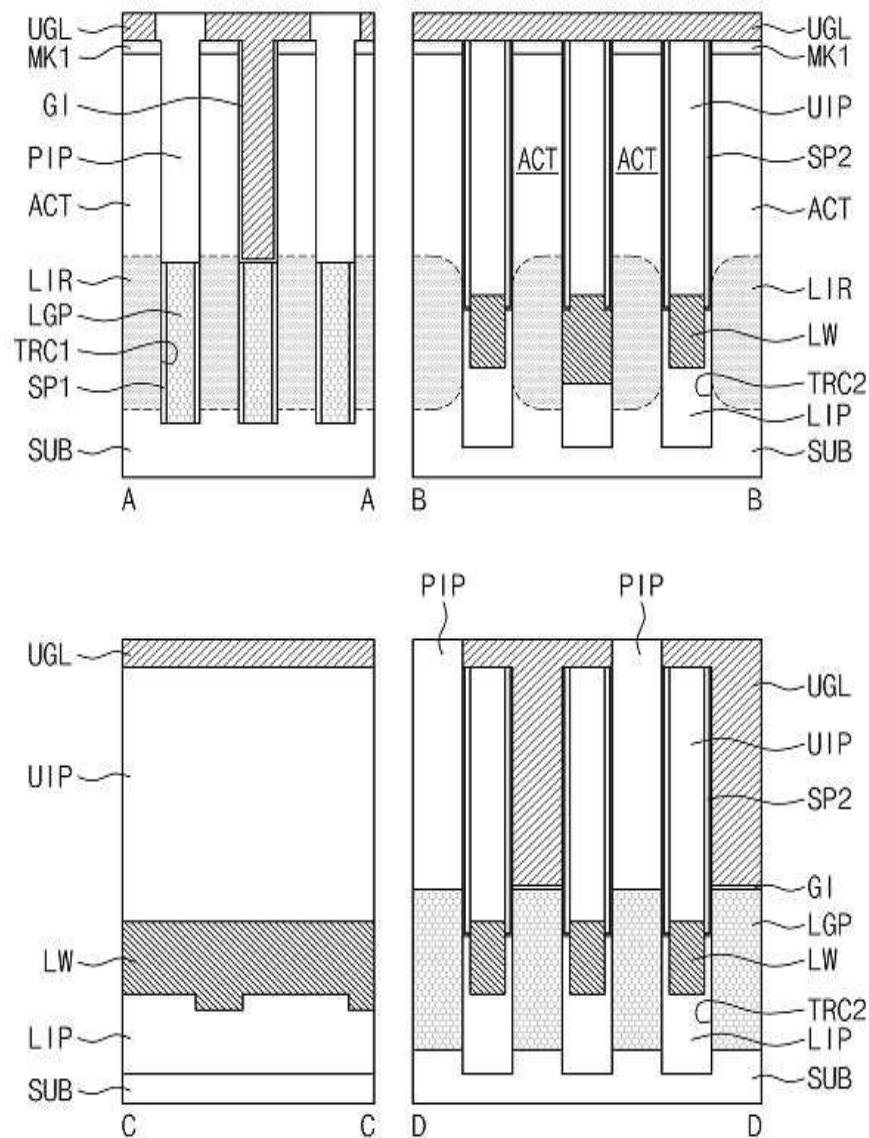

[0101] 도 41는 본 발명의 제 4 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 순서도이다. 도 42a 내지 도 46a는 본 발명의 제 4 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 단면도들이다. 도 42b 내지 도 46b는 본 발명의 제 4 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 사시도들이다. 설명의 간결함을 위해, 상술한 실시예들과 중복되는 기술적 특징들에 대한 설명은 생략될 수 있다.

[0102] 도 32와 도 41를 비교하면, 플러그 절연막을 형성하는 단계(S46)가 상부 게이트막을 형성하는 단계(S45) 이후에 실시된다는 점에서, 이 실시예는 도 32를 참조하여 설명한 제 3 실시예와 다르다. 이러한 차이에 의해 유발되는 제조 방법에서의 차이를 제외하면, 이 실시예는 상술한 제 3 실시예의 제조 방법에 기초하여 또는 이를 변형하여 실시될 수 있다. 따라서, 설명의 간결함을 위해, 상술한 제 1 내지 제 3 실시예들과 중복되는 기술적 특징들에 대한 설명은 생략될 수 있다.

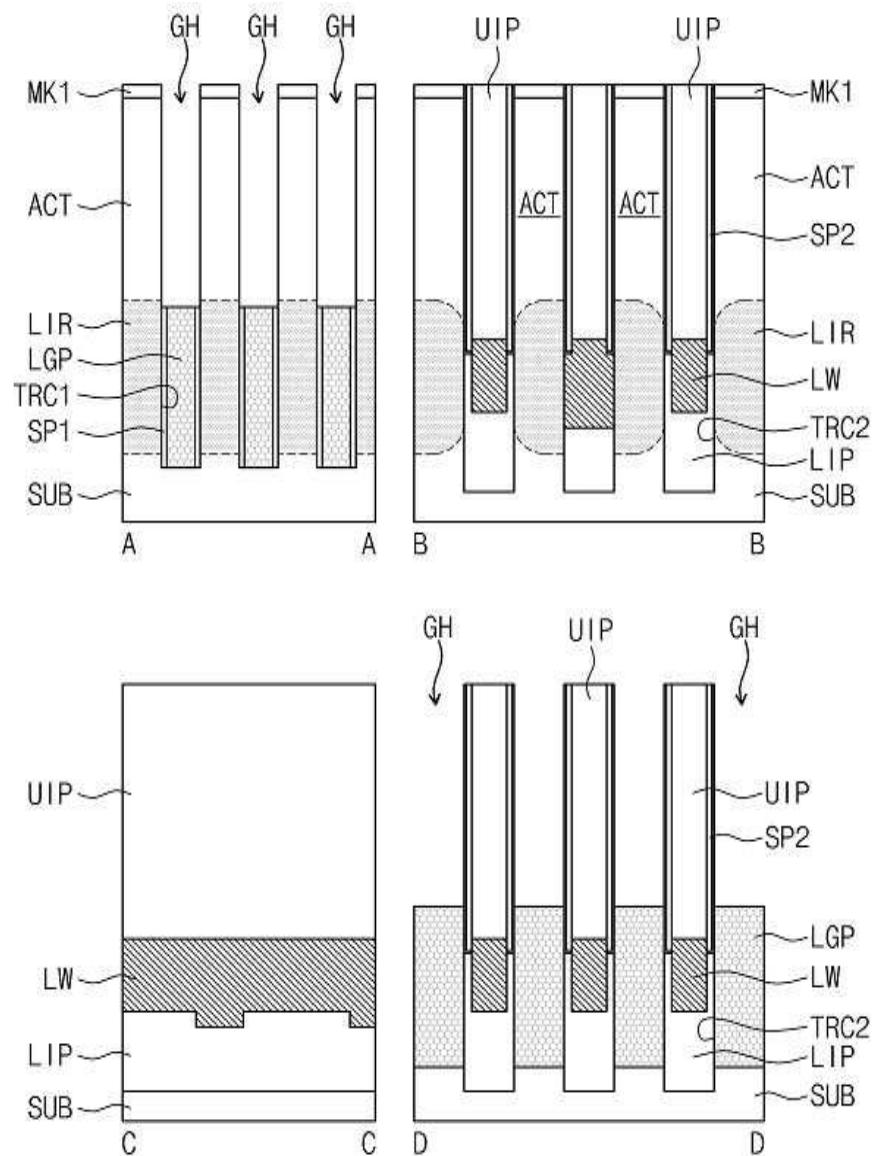

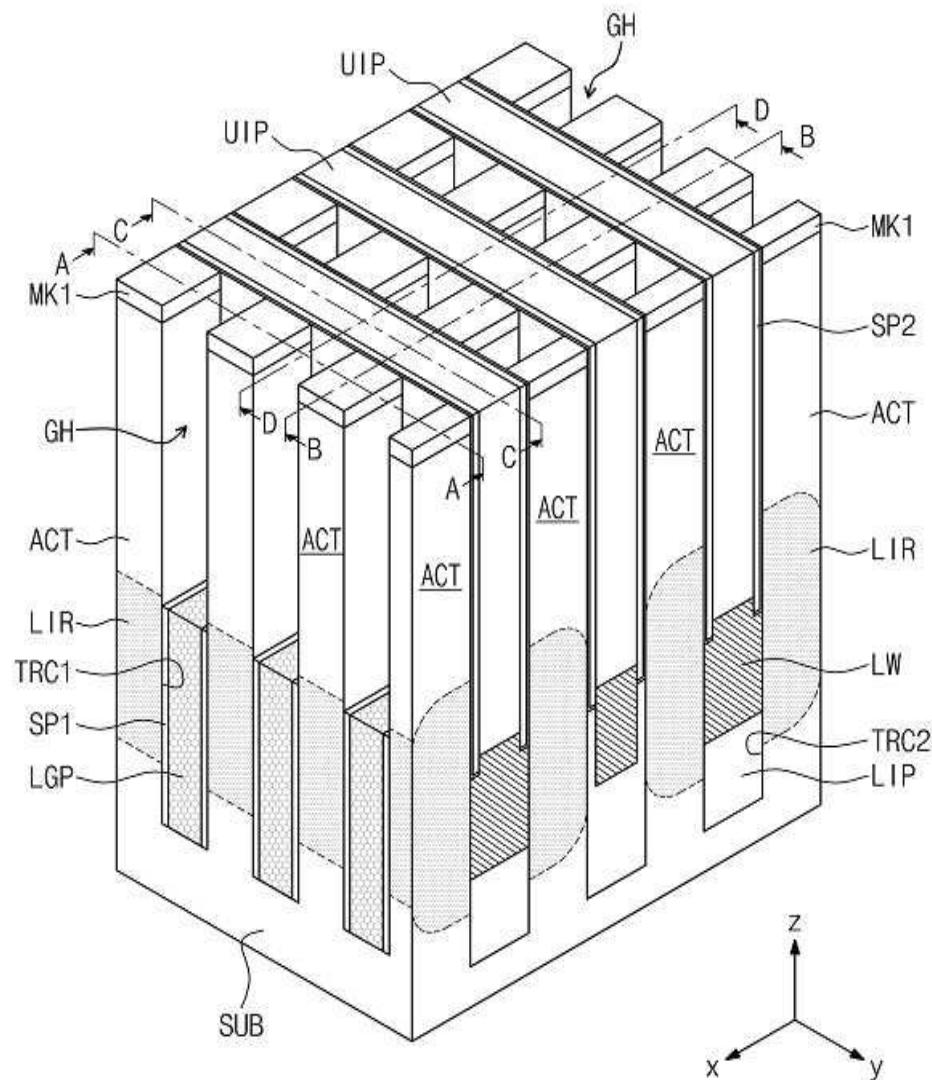

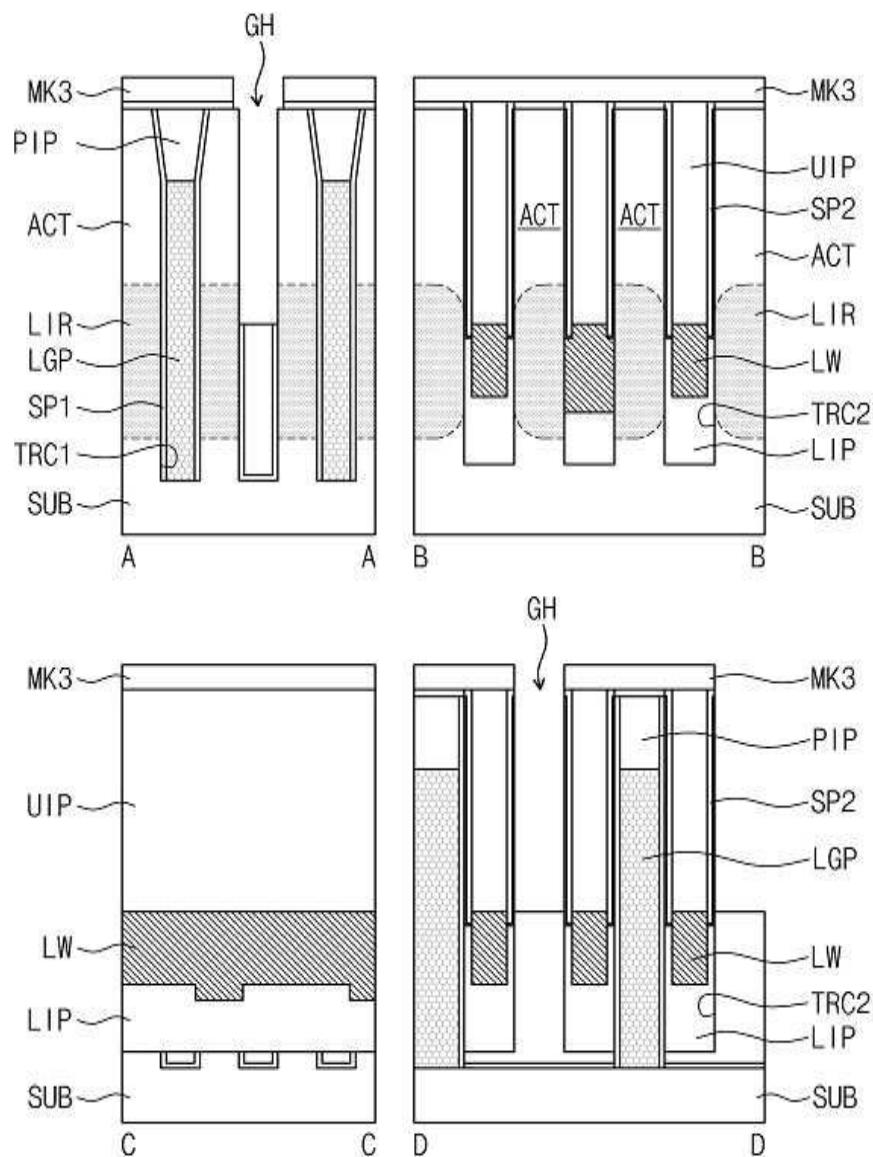

[0103] 도 41을 참조하면, 기판(SUB)을 패터닝하여 제 1 트렌치들(TRC1)를 형성한 후(S41), 상기 제 1 트렌치들(TRC1) 내에 하부 게이트막(LGL)을 형성한다(S42). 이어서, 하부 게이트 패턴들(LGP) 및 활성 패턴들(ACT)을 정의하는 제 2 트렌치들(TRC2)을 형성한 후(S43), 상기 제 2 트렌치(TRC2) 내에 배치되는 하부 배선들(LW)을 형성한다(S44). 이 단계들(S41-S44)은 상술한 제 3 실시예의 상응하는 단계들(S31-S34)과 동일하게 실시될 수 있다. 이 실시예에 따르면, 상기 하부 배선들(LW)을 형성한 후, 상기 제 2 트렌치들(TRC2)을 채우는 상부 절연 패턴들(UIP)이 더 형성될 수 있다.

[0104] 이어서, 도 42a 및 도 42b에 도시된 것처럼 상기 하부 게이트 패턴들(LGP)의 상부면들을 노출시키는 게이트 홀들(GH)을 형성한다. 이 실시예에 따르면, 상기 게이트 홀들(GH)의 바닥면은 상기 하부 배선(LW)의 상부면과 상기 활성 패턴(ACT)의 상부면 사이에 위치할 수 있다. 결과적으로, 이 실시예는 상기 홀들의 깊이에 있어서 상술한 제 1 실시예와 다를 수 있다.

[0105] 이후, 도 43a 및 도 43b에 도시된 것처럼 상기 게이트 홀들(GH)의 내벽을 덮는 게이트 절연막(GI) 및 상기 게이트 절연막(GI)이 형성된 상기 게이트 홀들(GH)을 채우는 상부 게이트막(UGL)을 차례로 형성한다(S45). 이 실시예에 따르면, 상기 게이트 홀들(GH)은 상기 하부 게이트 패턴들(LGP) 모두의 상부면들을 노출시키도록 형성될 수 있다. 이런 점에서, 이 실시예는 상술한 제 3 실시예와 차이가 있다. 또한, 상기 게이트 절연막(GI) 및 상기 상부 게이트막(UGL)을 형성하는 단계는 도 7a를 참조하여 설명된 제 1 실시예의 방법을 사용하여 실시될 수 있다. 상기 제 1 실시예에 따르면, 상기 상부 게이트막(UGL)이 상기 제 1 트렌치(TRC1)를 채우도록 형성되지만, 이 실시예에 따르면, 상기 상부 게이트막(UGL)이 상기 게이트 홀들(GH)을 채우도록 형성된다. 이런 점에서, 이 실시예는 상술한 제 1 실시예와 차이가 있다.

[0106] 이어서, 도 44a 및 도 44b에 도시된 것처럼 상기 하부 게이트 패턴들(LGP) 중의 일부의 상부에 배치되는 플러그 절연 패턴들(PIP)을 형성한다(S46). 이 단계(S46)는 상기 하부 게이트 패턴들(LGP) 중 일부의 상부면들을 노출시키는 홀들을 형성하고, 절연성 물질로 상기 홀들을 채운 후, 상기 절연성 물질을 씁쓸하여 상기 상부 게이트 패턴들(UGP)을 노출시키는 단계를 포함할 수 있다. 상기 플러그 절연 패턴들(PIP)을 형성하는 방법은 도 16a 및

도 16b를 참조하여 설명된 제 1 실시예의 방법을 이용하여 실시될 수 있으며, 상기 플러그 절연 패턴들(PIP)이 형성되는 위치들은 제 1 실시예의 그것과 동일할 수 있다.

[0107] 이어서, 도 45a 및 도 45b에 도시된 것처럼 상부 배선(UW) 및 상부 불순물 영역들(UIR)을 형성한 후(S47), 도 46a 및 도 46b에 도시된 것처럼 상기 상부 불순물 영역들(UIR)에 접속하는 플러그들(PLG) 및 이들에 접속하는 메모리 요소들(ME)을 형성한다(S48). 이 단계들은 도 17a 내지 도 19a를 참조하여 설명된 제 1 실시예의 제조 방법을 이용하여 형성될 수 있다.

#### [제조 방법- 제 5 실시예]

[0109] 도 47는 본 발명의 제 5 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 순서도이다. 도 48a 내지 도 56a는 본 발명의 제 5 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 단면도들이다. 도 48b 내지 도 56b는 본 발명의 제 5 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 사시도들이다. 설명의 간결함을 위해, 상술한 실시예들과 중복되는 기술적 특징들에 대한 설명은 생략될 수 있다.

[0110] 도 23과 도 47을 비교하면, 제 2 트렌치들(TRC2)을 형성하기 전에, 2차원적으로 분리된 하부 게이트 패턴들(LGP)이 형성된다는 점에서, 이 실시예는 도 23을 참조하여 설명한 제 2 실시예와 다르다. 이러한 차이에 의해 유발되는 제조 방법에서의 차이를 제외하면, 이 실시예는 상술한 제 2 실시예의 제조 방법에 기초하여 또는 이를 변형하여 실시될 수 있다. 따라서, 설명의 간결함을 위해, 상술한 제 1 내지 제 4 실시예들과 중복되는 기술적 특징들에 대한 설명은 생략될 수 있다.

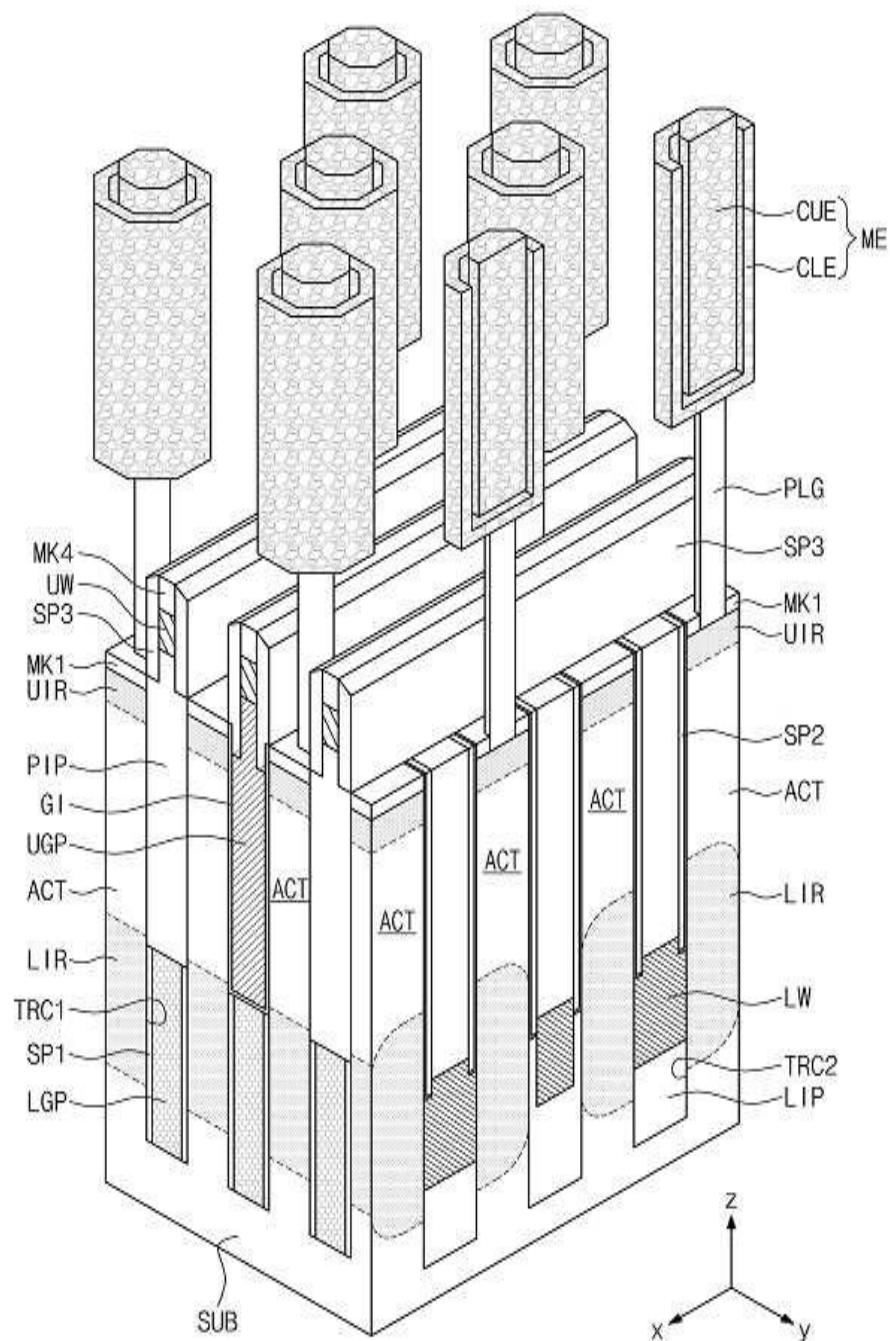

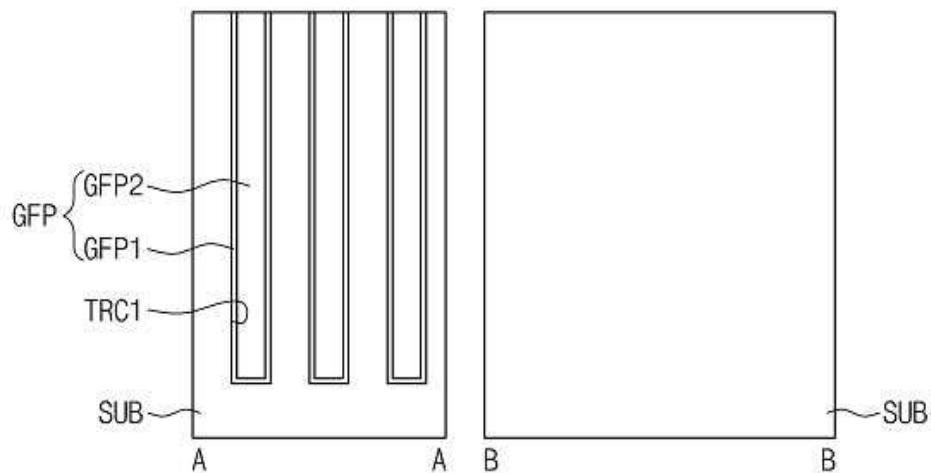

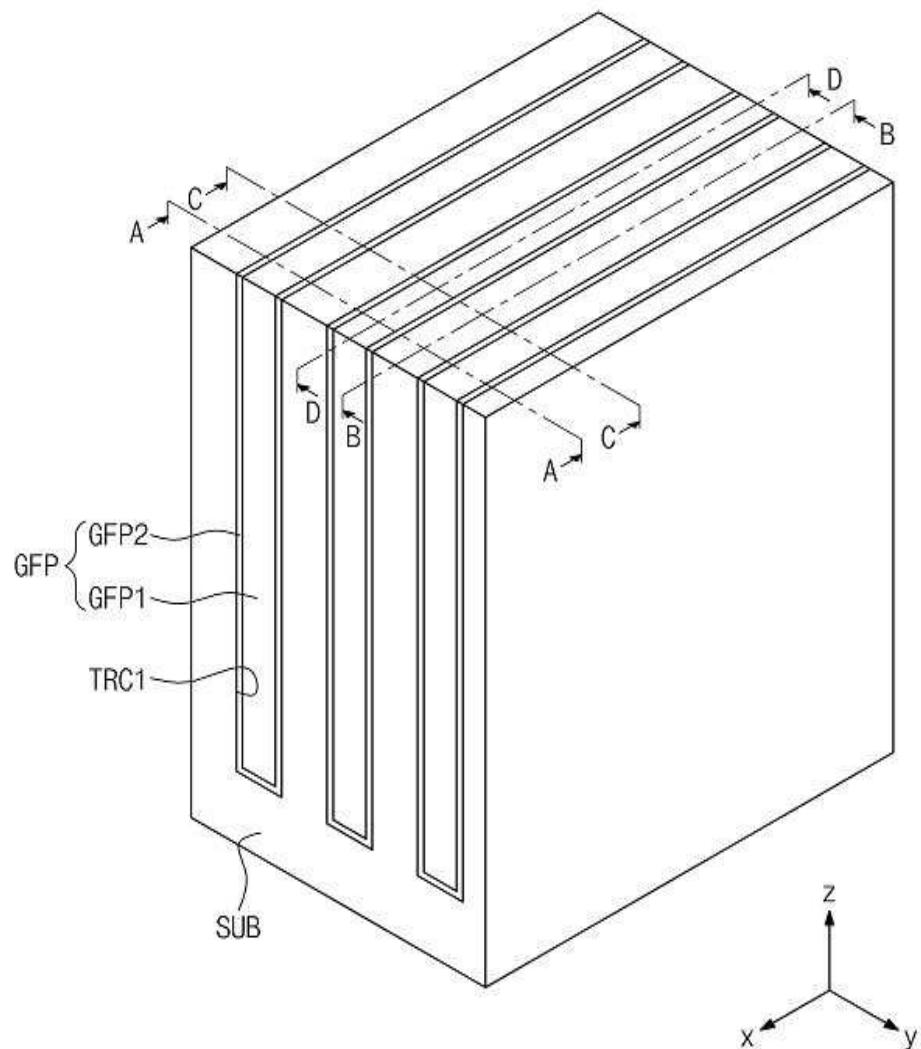

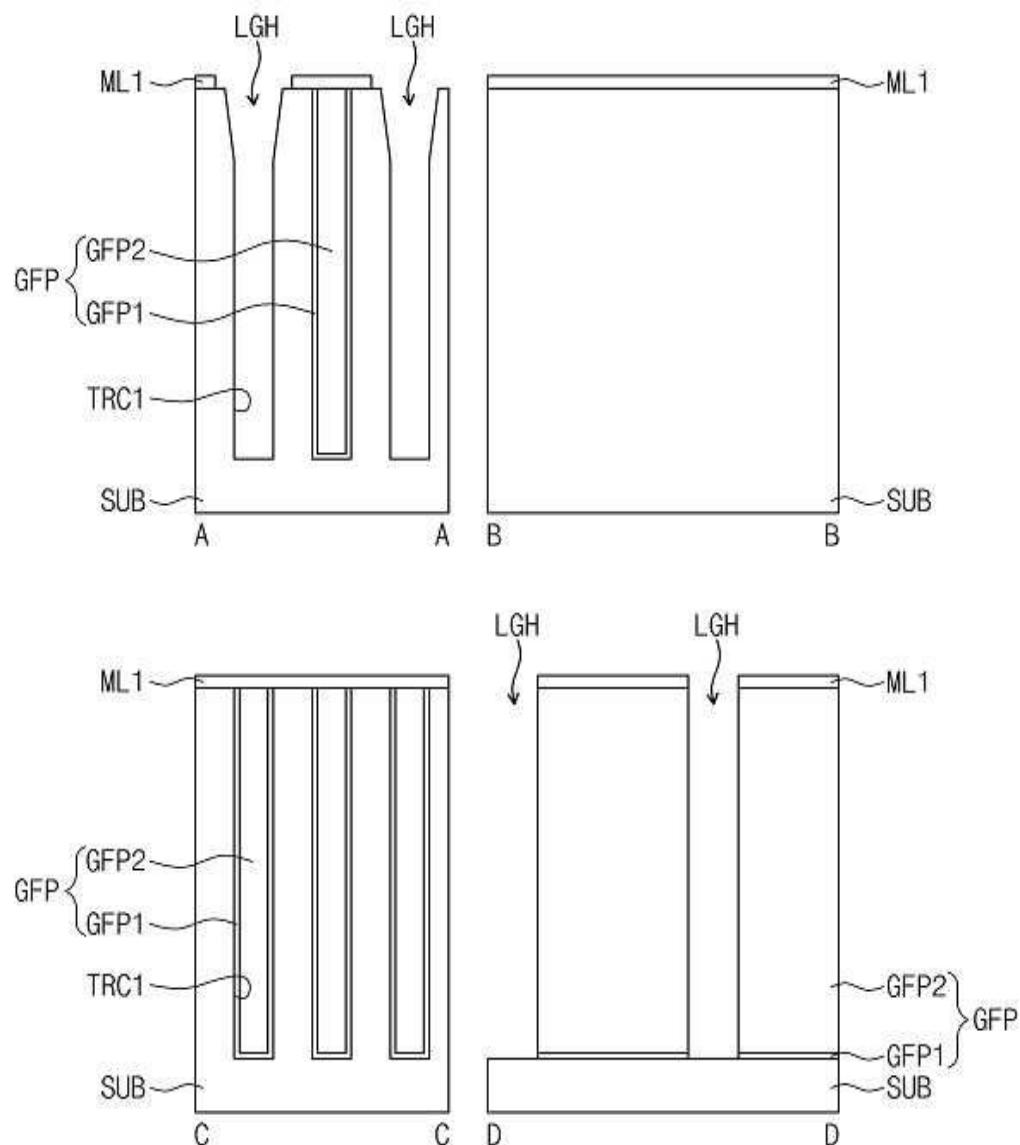

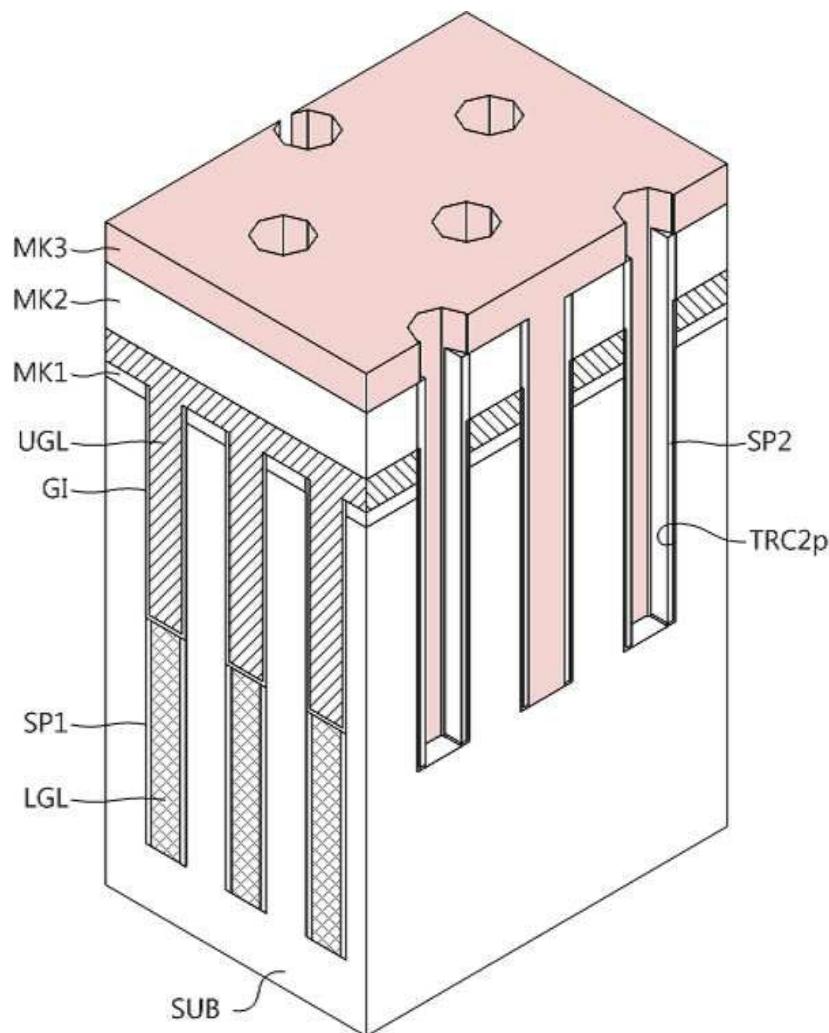

[0111] 도 47을 참조하면, 기판(SUB)을 패터닝하여 제 1 트렌치들(TRC1)를 형성한 후(S51), 상기 제 1 트렌치들(TRC1)을 채우는 매립 패턴들(GFP; gap-fill patterns)을 형성한다. 일 실시예에 따르면, 도 48a 및 도 48b에 도시된 것처럼 상기 매립 패턴들(GFP) 각각은 상기 제 1 트렌치들(TRC1)의 내벽을 덮는 제 1 매립 패턴(GFP1) 및 상기 제 1 매립 패턴(GFP1)이 형성된 상기 제 1 트렌치들(TRC1)을 채우는 제 2 매립 패턴(GFP2)을 포함할 수 있다. 상기 제 1 매립 패턴(GFP1)은 상기 제 1 트렌치(TRC1)의 내벽을 열산화시킴으로써 형성되는 열산화막일 수 있으며, 상기 제 2 매립 패턴(GFP2)은 상기 제 1 매립 패턴(GFP1)에 대해 식각 선택성을 갖는 물질들 중의 하나를 포함할 수 있다.

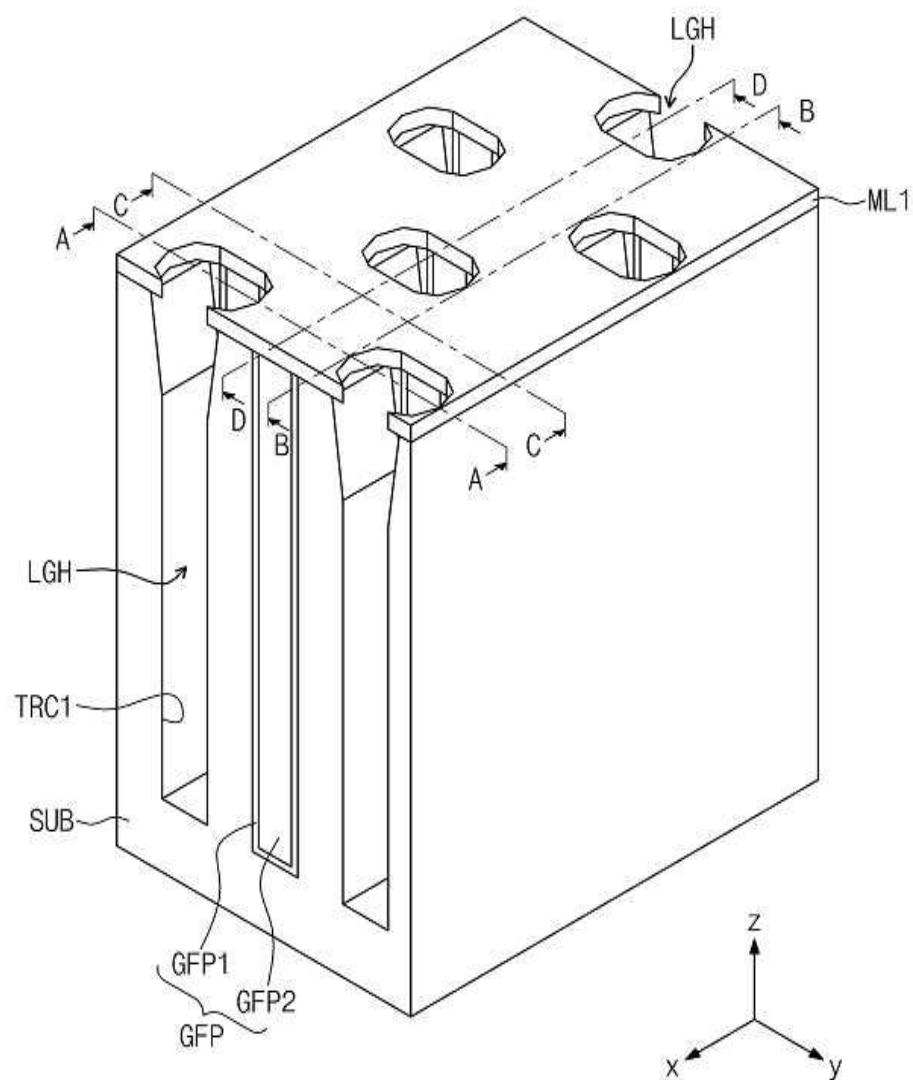

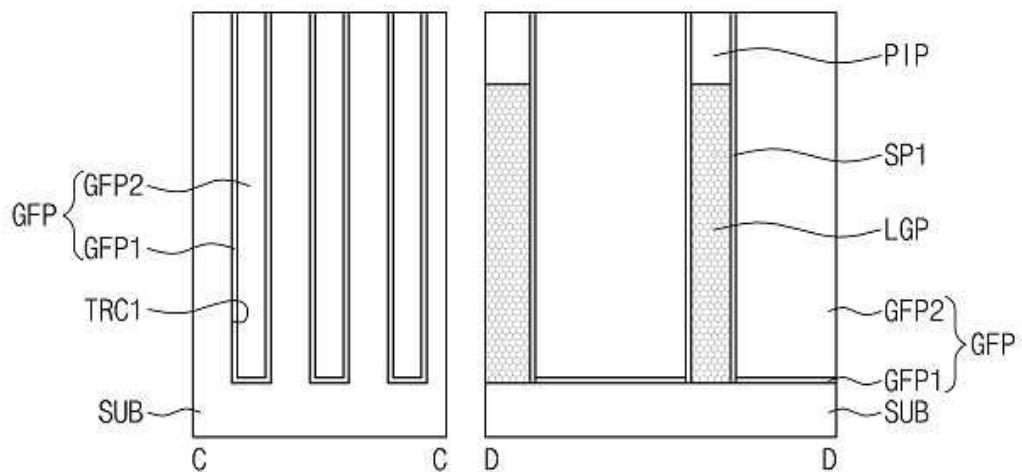

[0112] 이어서, 도 50a 및 도 50b에 도시된 것처럼 상기 기판(SUB) 상에 2차원적으로 배열된 하부 게이트 패턴들(LGP)을 형성한 후(S52), 상기 하부 게이트 패턴들(LGP)의 상부에 배치되는 플러그 절연 패턴들(PIP)을 형성한다. 이 단계들은 도 49a 및 도 49b에 도시된 것처럼 상기 기판(SUB) 상에 2차원적으로 배열된 하부 게이트 홀들(LGH)을 형성한 후, 도 50a 및 도 50b에 도시된 것처럼 상기 하부 게이트 홀들(LGH)을 채우는 상기 하부 게이트 패턴들(LGP) 및 상기 플러그 절연 패턴들(PIP)을 형성하는 단계를 포함할 수 있다.

[0113] 보다 구체적으로, 상기 하부 게이트 홀들(LGH)은 이들의 위치를 정의하는 개구부들이 형성된 소정의 제 1 마스크막(ML1)을 형성한 후, 이를 식각 마스크로 사용하여 상기 매립 패턴들(GFP)을 패터닝함으로써 형성될 수 있다. 상기 기판(SUB)의 상부면에 평행한 평면에 투영되는 상기 하부 게이트 홀들(LGH) 또는 상기 개구부들의 위치들은 도 16a 및 도 16b를 참조하여 설명된 제 1 실시예에서의 상기 플러그 절연 패턴들(PIP)의 위치들과 실질적으로 동일할 수 있다. 상기 제 1 마스크막(ML1)은 사진 공정을 통해 형성되는 포토레지스트막, 실리콘 산화막 또는 실리콘 질화막 중의 적어도 하나일 수 있다.

[0114] 상기 하부 게이트 패턴들(LGP)을 형성하는 단계는 상기 하부 게이트 홀들(LGH)의 내측벽에 제 1 스페이서들(SP1)을 형성한 후, 상기 제 1 스페이서들(SP1)이 형성된 상기 하부 게이트 홀들(LGH)을 채우는 하부 게이트막을 형성하는 단계를 포함할 수 있다. 이어서, 상기 하부 게이트막을 전면 식각하여 상기 기판(SUB)의 상부면 아래까지 상기 하부 게이트막의 상부면을 리세스시킨다. 이에 따라, 상기 하부 게이트막은, 상기 하부 게이트 홀들(LGH) 각각의 내부에 국소적으로 배치된, 상기 하부 게이트 패턴들(LGP)로 분리된다. 이 실시예에 따르면, 상기 제 1 스페이서(SP1)은 상기 하부 게이트 홀(LGH)의 내측벽을 덮기 때문에, 상기 하부 게이트 패턴(LGP)의 측면은 상기 제 1 스페이서(SP1)에 의해 둘러싸인다. 즉, 상기 제 1 스페이서(SP1)은, 상기 제 1 트렌치(TRC1)의 측벽들 및 상기 매립 패턴(GFP)의 측벽들 사이에 배치되는, 열린 실린더(open cylinder) 모양일 수 있다.

[0115] 상기 플러그 절연 패턴들(PIP)을 형성하는 단계는 상기 하부 게이트 패턴들(LGP)의 상부면을 리세스시킨 후, 상기 리세스된 영역들을 채우는 플러그 절연막을 형성하는 단계(S53)를 포함할 수 있다. 이후 상기 플러그 절연막을 전면 식각하여 상기 기판(SUB)의 상부면을 노출시킴으로써 도 50a 및 도 50b에 도시된 상기 플러그 절연 패턴들(PIP)을 완성한다. 일부 실시예들에 따르면, 상기 플러그 절연 패턴들(PIP)은 실리콘 산화막으로 형성될 수

있다.

[0116] 이어서, 도 51a 및 도 51b에 도시된 것처럼, 상기 제 1 트렌치들(TRC1)을 가로지르는 장축을 갖는 제 2 마스크 패턴들(MK2)을 형성한 후, 이를 식각 마스크로 사용하여 활성 패턴들(ACT)을 정의하는 제 2 트렌치들(TRC2)를 형성한다(S54). 이 단계(S54)는 앞선 실시예들에서와 같이 예비 트렌치들(TRC2p) 및 제 2 스페이서들(SP2)을 형성하는 단계를 더 포함할 수 있다. 구체적으로, 상기 제 2 트렌치들(TRC2)을 형성하기 위한 일련의 단계들은 도 8a 내지 도 10a를 참조하여 설명된 제 1 실시예의 제조 방법에 기초하여 또는 이를 변형하여 실시될 수 있다.

[0117] 이어서, 상기 제 2 트렌치(TRC2) 내에 하부 배선들(LW)을 형성한다(S55). 이 단계(S55)는 도 11a 내지 도 15a를 참조하여 설명된 제 1 실시예의 제조 방법과 실질적으로 동일하게 실시될 수 있다. 그 결과, 도 52a 및 도 52b에 도시된 것처럼, 상기 하부 배선(LW)의 아래에는 상기 하부 배선(LW)을 형성하기 위한 주형으로 이용되는 하부 절연 패턴들(LIP)이 형성되고, 상기 활성 패턴들(ACT)의 하부 영역들에는 상기 하부 배선들(LW)에 의해 연결되는 하부 불순물 영역들(LIR)이 형성될 수 있다.

[0118] 이어서, 상기 상부 게이트막(UGL)을 형성한다(S56). 이 단계는 상기 매립 패턴들(GFP)의 일부 영역들을 리세스 시키어 게이트 홀들(GH)을 형성한 후, 상기 상부 게이트막(UGL)으로 상기 게이트 홀들(GH)을 채우는 단계를 포함할 수 있다. 보다 구체적으로, 상기 게이트 홀들(GH)은 상기 기판(SUB) 상에 개구부들을 갖는 제 3 마스크 패턴(MK3)을 형성한 후, 이를 식각 마스크로 사용하여 상기 매립 패턴들(GFP)을 리세스시키는 단계를 통해 형성될 수 있다. 이에 따라, 도 53a 및 도 53b에 도시된 것처럼 상기 플러그 절연 패턴(PIP)의 하부면보다 낮은 바닥면을 갖는 게이트 홀들(GH)이 형성될 수 있다. 이후, 도 54a 및 도 54b에 도시된 것처럼, 상기 게이트 홀들(GH)의 내측벽을 덮는 게이트 절연막(GI)을 형성하고, 상기 게이트 절연막(GI)이 형성된 상기 게이트 홀들(GH)을 상기 상부 게이트막(UGL)으로 채운다.

[0119] 상기 게이트 홀들(GH)은 제 2 및 제 3 실시예들에서와 실질적으로 동일한 위치에 형성될 수 있다. 또한, 상기 게이트 홀들(GH) 및 상기 상부 게이트막(UGL)은 도 28a 내지 도 29a를 참조하여 설명된 제 2 실시예의 제조 방법에 기초하여 또는 이를 변형하여 실시될 수 있다. 한편, 상기 게이트 절연막(GI)은 열산화 공정 또는 증착 공정을 통해 형성되는 절연성 박막(예를 들면, 실리콘 산화막)일 수 있다. 상기 게이트 절연막(GI)이 증착 공정을 통해 형성될 경우, 상기 제 1 스페이서(SP1)와 같이, 상기 게이트 절연막(GI)은 열린 실린더(open cylinder) 모양일 수 있으며, (상기 게이트 홀(GH)에 삽입된) 상기 상부 게이트막(UGL)의 측면을 둘러싸도록 형성될 수 있다.

[0120] 이어서, 도 55a 및 도 55b에 도시된 것처럼 상부 배선(UW) 및 상부 불순물 영역들(UIR)을 형성한 후(S57), 도 56a 및 도 56b에 도시된 것처럼 상기 상부 불순물 영역들(UIR)에 접속하는 플러그들(PLG) 및 이들에 접속하는 메모리 요소들(ME)을 형성한다(S58). 이 단계들은 도 17a 내지 도 19a를 참조하여 설명된 제 1 실시예의 제조 방법을 이용하여 형성될 수 있다.

#### [반도체 장치]

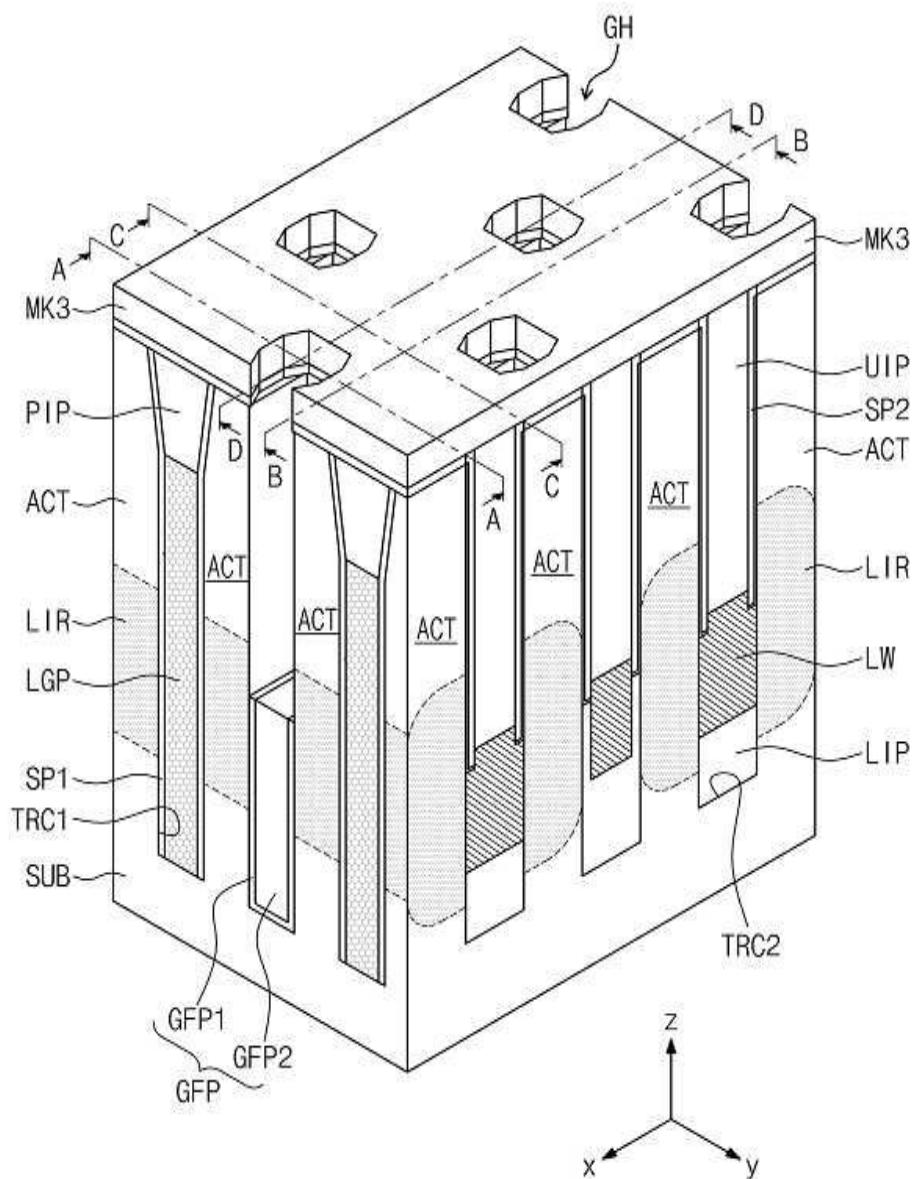

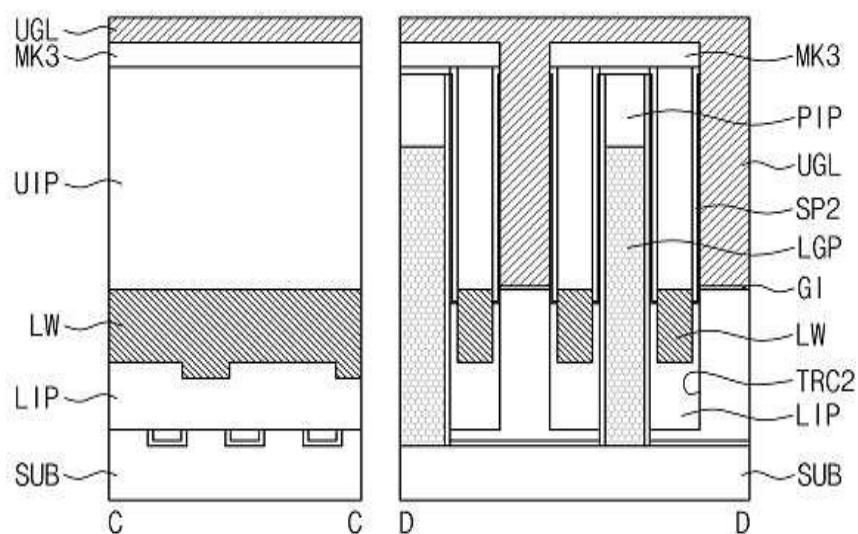

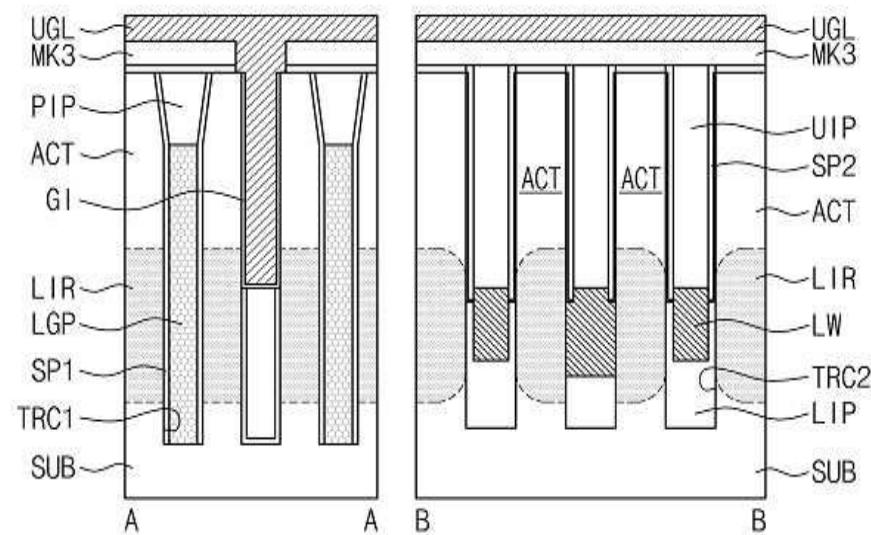

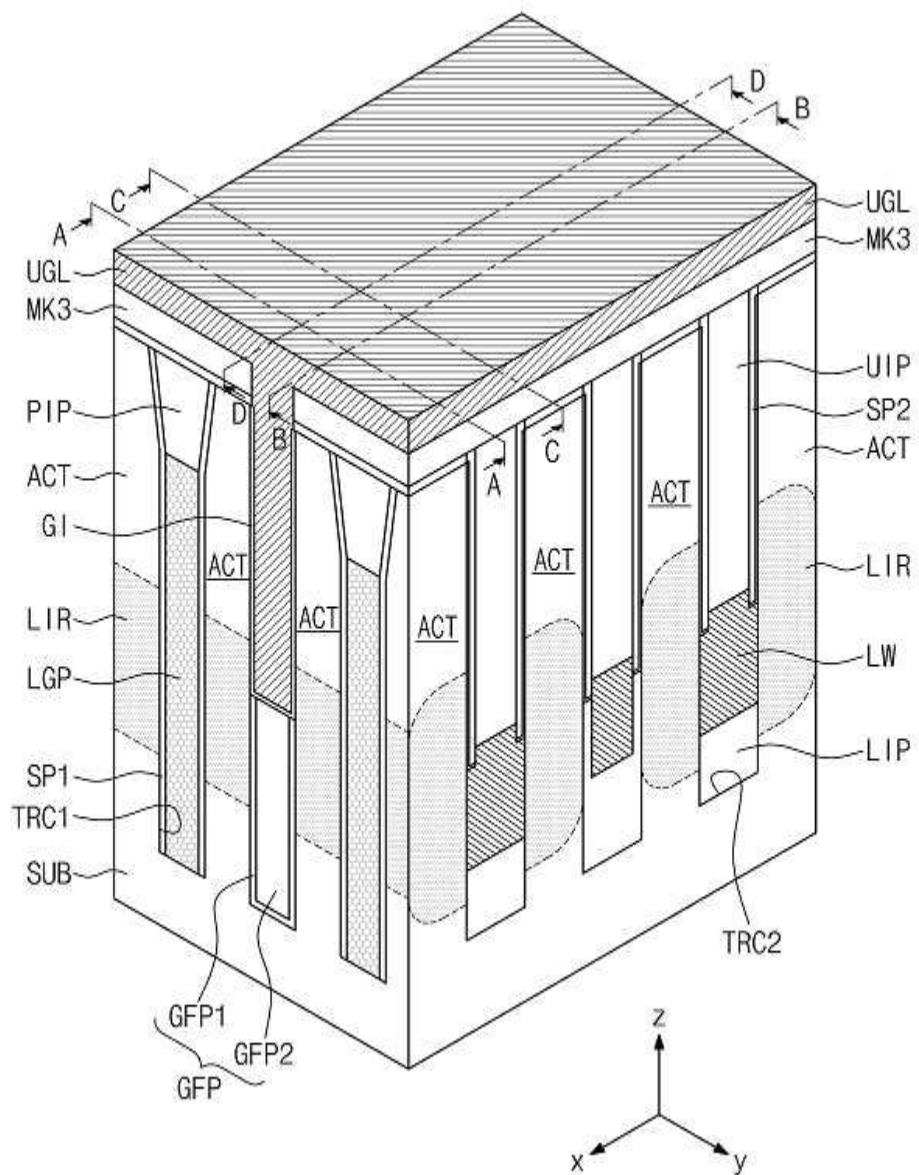

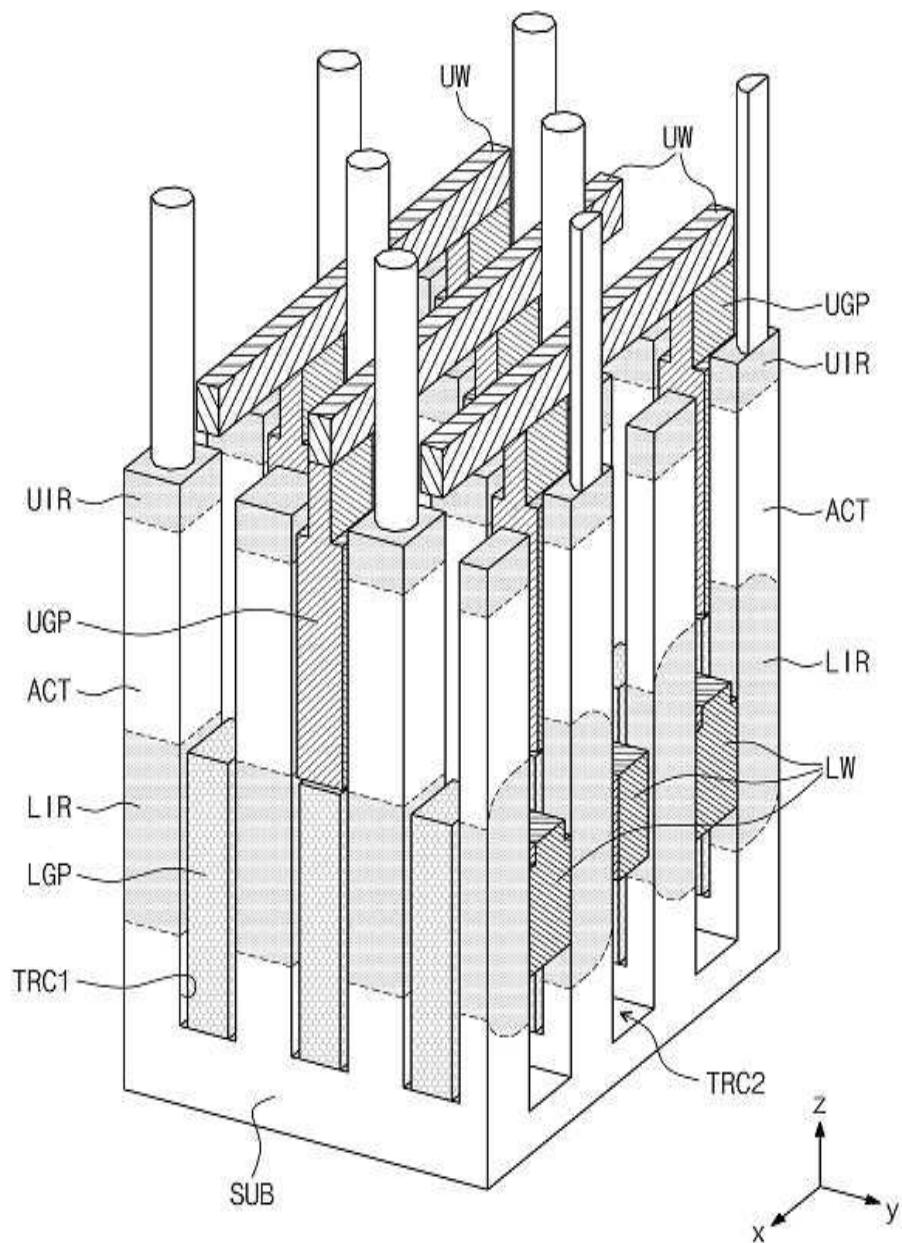

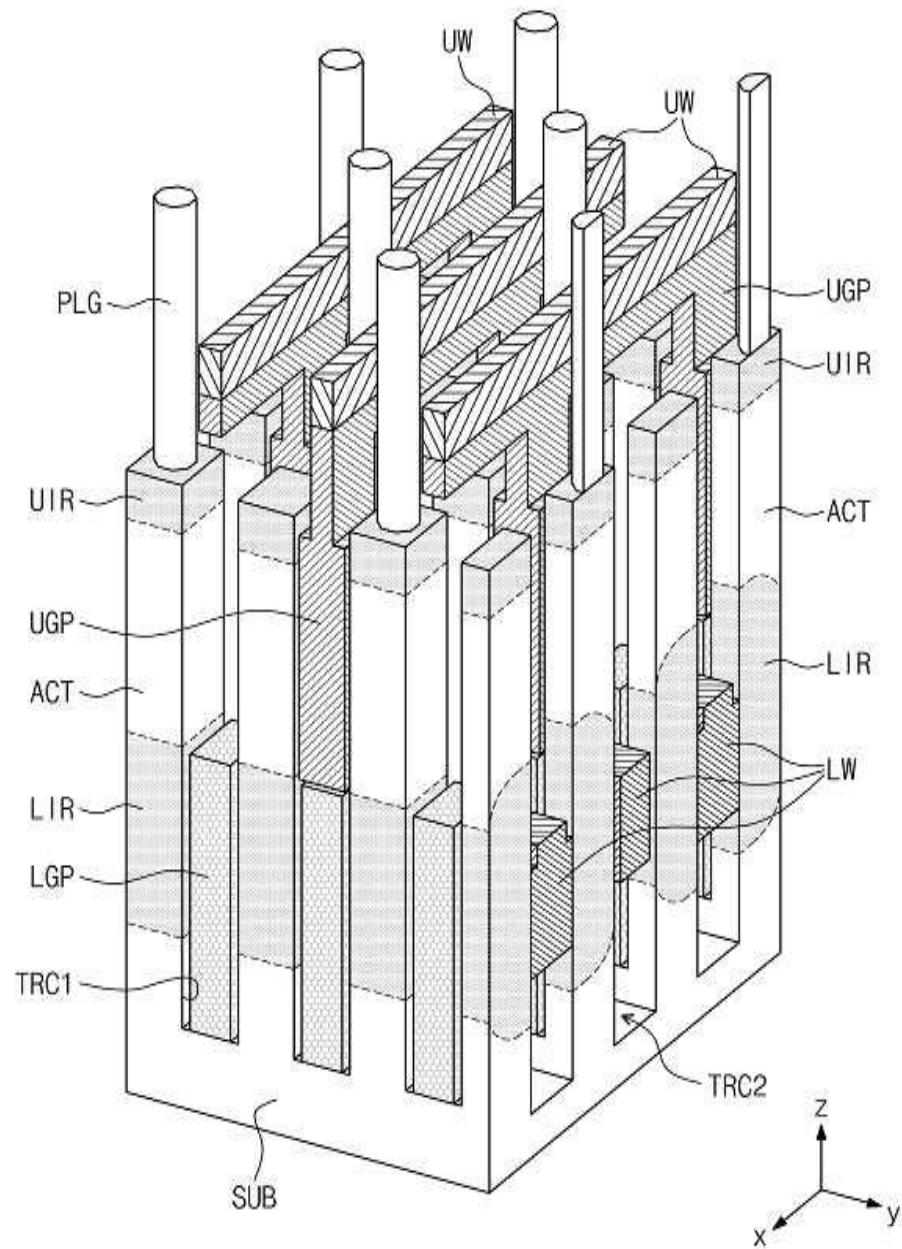

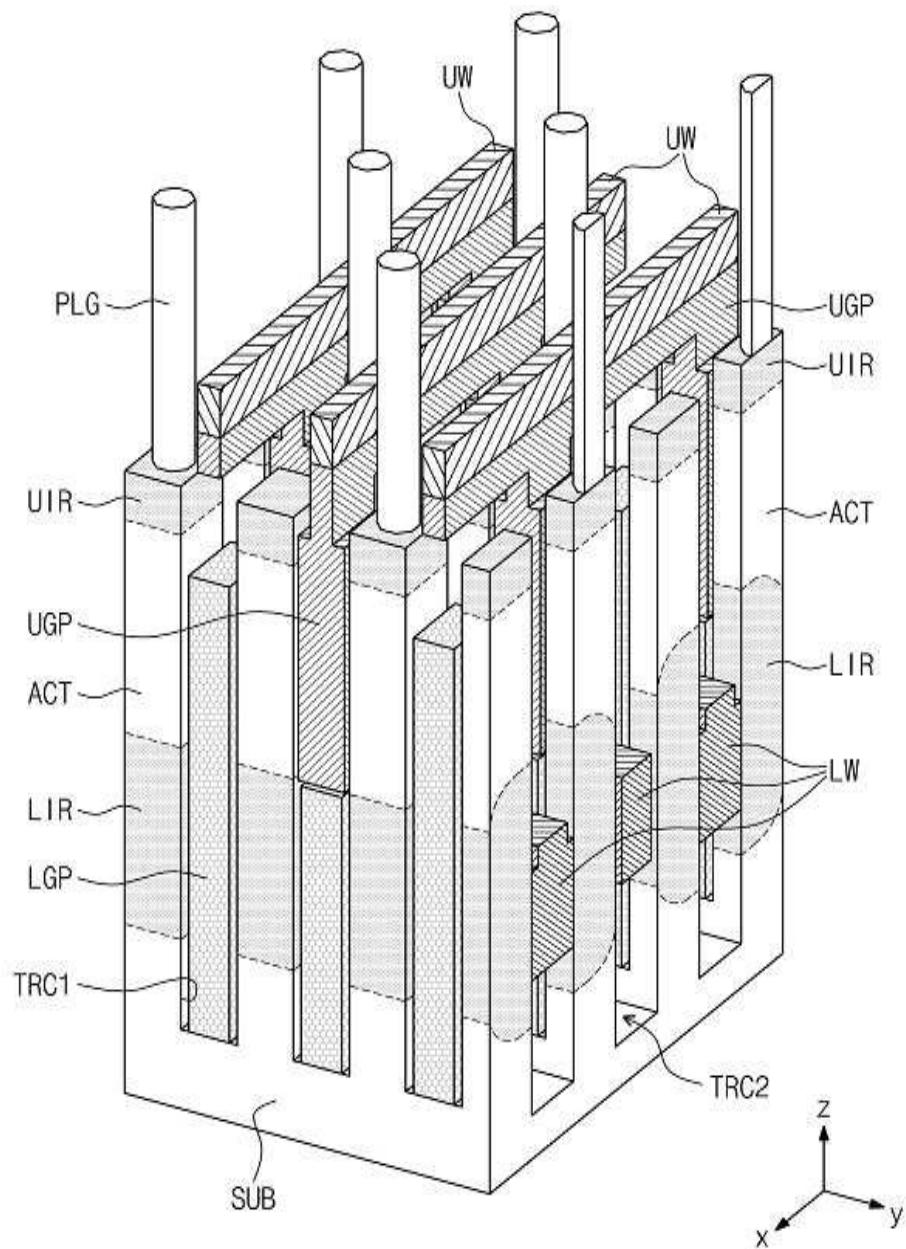

[0121] 도 57 내지 도 72은 본 발명의 기술적 사상에 따른 여러 실시예들을 통해 제조될 수 있는 반도체 장치들을 예시적으로 보여주는 사시도들이다. 도면에서의 복잡성을 줄이고 본 발명의 기술적 사상에 대한 보다 나은 이해를 위해, 반도체 장치를 구성하는 요소들의 일부분들은 의도적으로 생략되었다. 예를 들면, 전기적 신호의 전달을 위한 경로로서 사용되지 않는 절연성 물질들은 도 57 내지 도 64에서 생략되었다. 또한, 활성 패턴과 하부 배선 사이의 연결 구조를 설명하기 위해, 도 65 내지 도 67에서, 활성 패턴과 하부 배선 이외의 모든 구성 요소들은 생략되었다. 당업자에게 있어, 이러한 생략된 부분은 앞서 설명되는 제조 방법으로부터 용이하게 복원될 수 있다는 점에서, 이에 대한 별도의 설명은 생략한다.

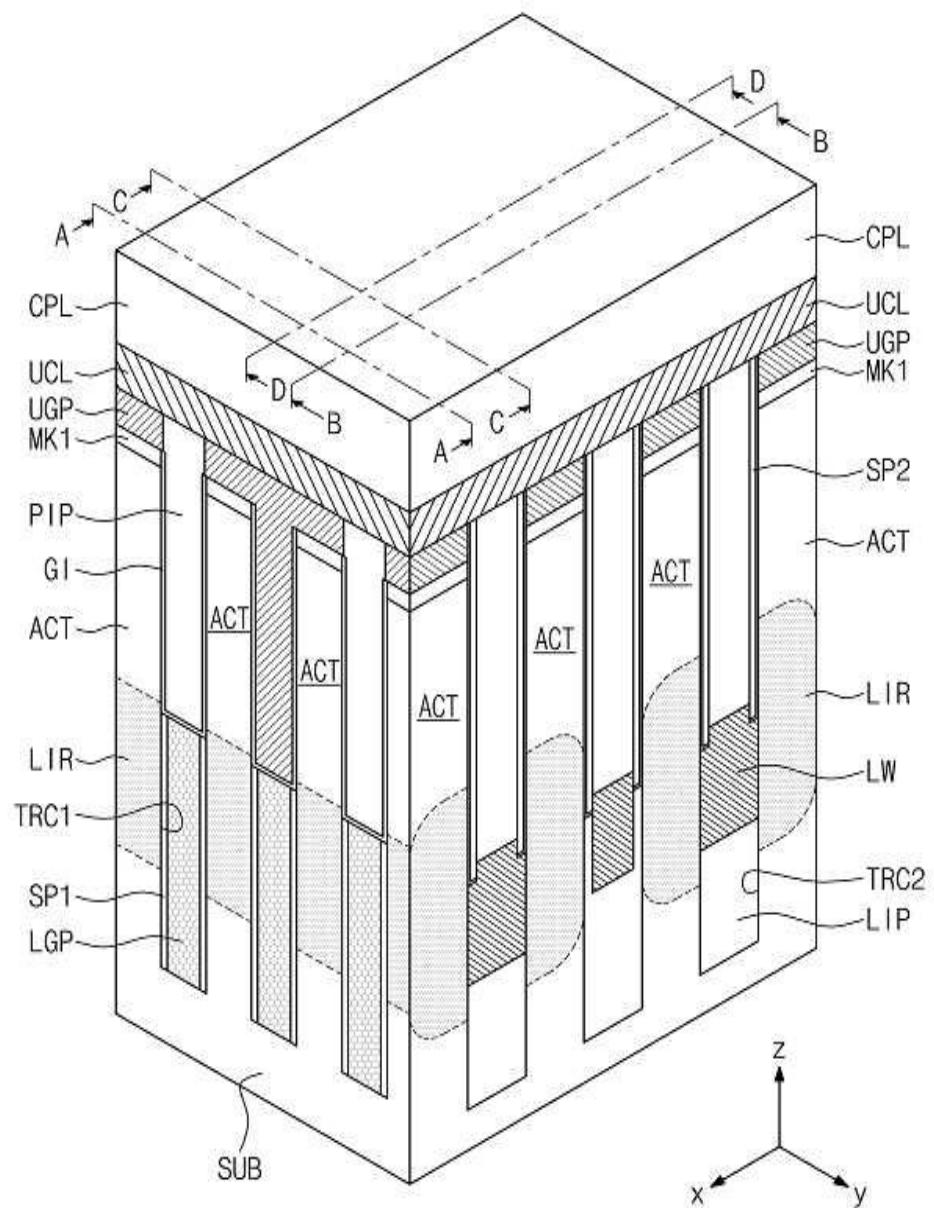

[0122] 도 57 내지 도 66을 참조하면, 기판(SUB) 상에 활성 패턴들(ACT)이 2차원적으로 배열된다. 상기 활성 패턴들(ACT)은 상기 기판(SUB)으로부터 연장된 반도체 물질일 수 있으며, 상기 활성 패턴들(ACT) 각각은, 그것의 내부에서 수직적으로 이격된, 상부 불순물 영역(UIR) 및 하부 불순물 영역(LIR)을 포함한다. 본 발명의 실시예들에 따르면, 상기 활성 패턴들(ACT) 각각은, x 방향에 평행한 제 1 트렌치들(TRC1) 및 상기 제 1 트렌치들(TRC1)을 가로지르는 제 2 트렌치들(TRC2)에 의해 정의되는, 측벽들을 가질 수 있다. 즉, 상기 활성 패턴들(ACT)은 상기 제 1 및 제 2 트렌치들(TRC1, TRC2) 사이의 영역들에 배치된다.

[0123] 하부 게이트 패턴들(LGP) 및 상부 게이트 패턴들(UGP)이, 상기 제 1 트렌치들(TRC1)에 포함되면서 상기 제 2 트렌치들(TRC2)에 포함되지 않는, 영역들에 배치된다. 상기 상부 게이트 패턴들(UGP)은, 상기 하부 게이트 패턴들

(LGP)의 일부의 상부에, 상기 하부 게이트 패턴들(LGP)로부터 수직적으로 이격되어 배치된다.

[0125] 상기 하부 및 상부 게이트 패턴들(LGP, UGP)은 상기 활성 패턴들(ACT)의 측벽으로부터 이격되어 형성된다. 본 발명의 일부 실시예들에 따르면, 상기 하부 게이트 패턴들(LGP)은 적어도 상기 하부 불순물 영역(LIR)의 측벽을 마주보도록 배치되어, 이들과 모스 커패시터를 구성할 수 있다. 유사하게, 상기 상부 게이트 패턴들(UGP)은, 상기 상부 및 하부 불순물 영역들(UIR, LIR) 사이에 위치하는, 상기 활성 패턴(ACT)의 측벽을 마주보도록 배치되어, 이들과 모스 커패시터를 구성할 수 있다. 외부로의 전기적 연결에 있어서, 상기 하부 게이트 패턴(LGP)은 상기 제 1 트렌치(TRC1)의 바닥면을 통해 상기 기판(SUB)에 오직하게 연결되고, 상기 상부 게이트 패턴(UGP)은, 그것의 상부에서 상기 제 2 트렌치들(TRC2)을 가로지르는, 상부 배선들(UW) 중의 하나에 전기적으로 연결된다.

[0126] 수평적 배치에 있어서, 상기 상부 게이트 패턴들(UGP)은 도 16a 및 도 16b를 참조하여 설명된 영역들에 배치될 수 있다. 이와 달리, 일부 실시예들에 따르면, 도 57 내지 도 60, 도 62, 도 63 그리고 도 65에 도시된 것처럼, 상기 하부 게이트 패턴들(LGP)은 상기 제 1 트렌치들(TRC1)에 포함되면서 상기 제 2 트렌치들(TRC2)에 포함되지 않는 영역들 모두에 형성될 수 있다. 한편, 상기 하부 게이트 패턴들(LGP)의 일부는, 높이에 있어서, 그것들의 다른 일부와 차이가 있을 수 있다. 예를 들면, 도 59 및 도 63에 도시된 것처럼, 상기 하부 게이트 패턴들(LGP)의 일부(이하, 제 1 하부 게이트 패턴)는, 상기 상부 게이트 패턴들(UGP)의 아래에 위치하는, 상기 하부 게이트 패턴들(LGP)의 다른 일부(이하, 제 2 하부 게이트 패턴)보다 상기 상부 불순물 영역(UIR)에 인접하게 형성될 수 있다. 이 경우, 상기 제 1 하부 게이트 패턴들은 상기 상부 및 하부 불순물 영역들(UIR, LIR) 사이에 위치하는, 상기 활성 패턴(ACT)의 측벽을 마주보도록 배치되어, 이들과 모스 커패시터를 구성할 수 있다.

[0127] 다른 실시예들에 따르면, 상기 하부 게이트 패턴들(LGP)은 상기 제 1 트렌치들(TRC1)에 포함되면서 상기 제 2 트렌치들(TRC2)에 포함되지 않는 영역들 중의 일부에 형성될 수 있다. 예를 들면, 도 61, 도 64 그리고 도 66에 도시된 것처럼, 상기 하부 게이트 패턴들(LGP)은, 상기 제 2 트렌치들(TRC2)에 포함되지 않으면서 상기 상부 게이트 패턴들(UGP)이 배치되지 않는, 상기 제 1 트렌치들(TRC1)의 일부 영역들에 배치될 수 있다.

[0128] 상기 하부 불순물 영역들(LIR)은, 상기 제 2 트렌치(TRC2) 내에 배치되어 상기 활성 패턴들(ACT)을 가로지르는, 하부 배선들(LW)에 전기적으로 연결된다. 도 65 내지 도 67에 도시된 것처럼, 상기 활성 패턴들(ACT) 각각은 그 것의 양측에 배치되는 두 개의 상기 하부 배선들(LW) 모두에 접속하지 않고, 이들 중의 하나에 접속된다. 상기 활성 패턴들(ACT)과 상기 하부 배선들(LW) 사이의 전기적 연결은, 도 14a 및 도 15a를 참조하여 설명된, 상기 접합 정의 영역들(JDR) 및 상기 언더컷 영역들(UCR)의 위치에 의해 결정되며, 도 67은 상기 활성 패턴들(ACT)과 상기 하부 배선들(LW) 사이의 연결 구조를 예시적으로 보여준다.

[0129] 한편, 도 68 내지 도 72는 본 발명의 실시예들에 따른 반도체 장치의 다른 측면을 예시적으로 도시하는 사시도들이다. 보다 구체적으로, 도 68 내지 도 72은, 본 발명의 실시예들에 따른, 절연성 패턴들(예를 들면, LIP, PIP, GI, GFP 등)의 모양 및 배치 또는 상기 상부 게이트 패턴(UGP) 및 상기 하부 게이트 패턴(LGP)의 모양 및 배치에 대한 보다 명확한 시각화를 위해 제공되었다. 하지만, 여기에 도시된 반도체 장치들은 차례로 상술한 제 1 내지 제 5 실시예들을 통해 제조될 수 있으며, 상술한 실시예들과 동일한 구성 요소들은 동일한 참조 번호로 도시되었다. 따라서, 이에 대한 별도의 설명은 생략한다.

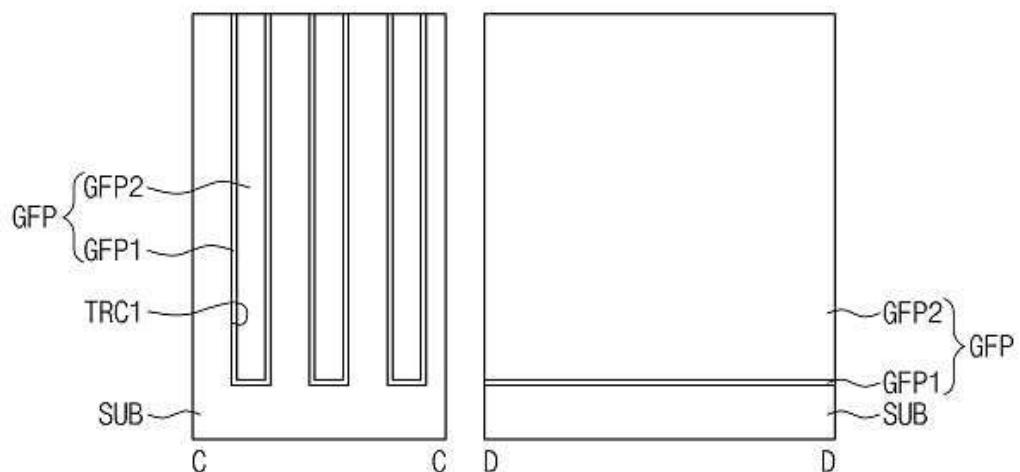

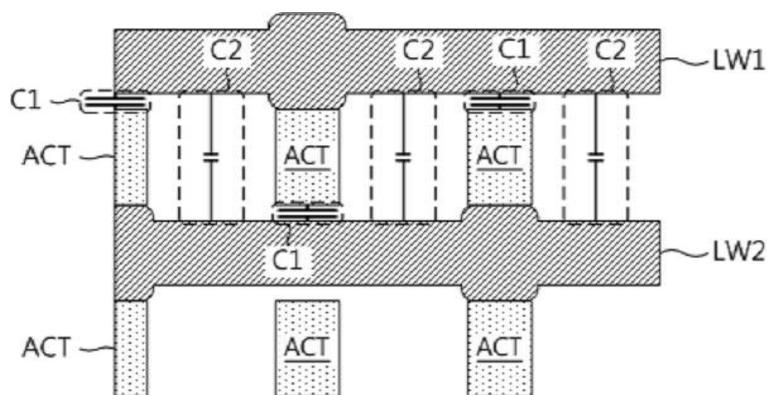

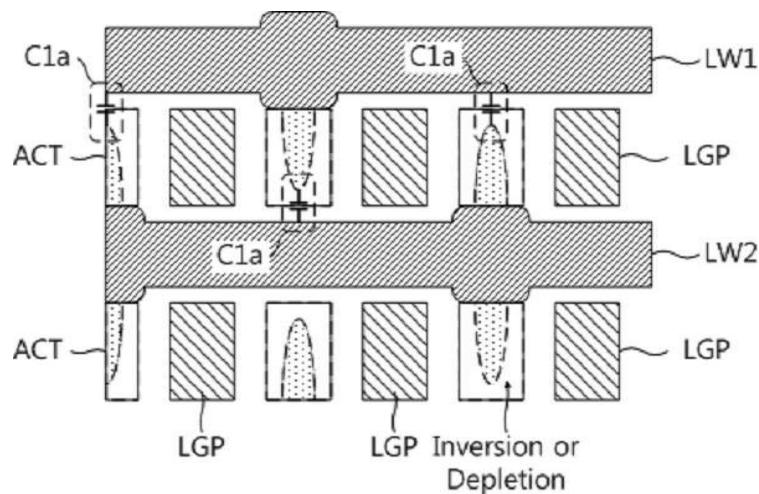

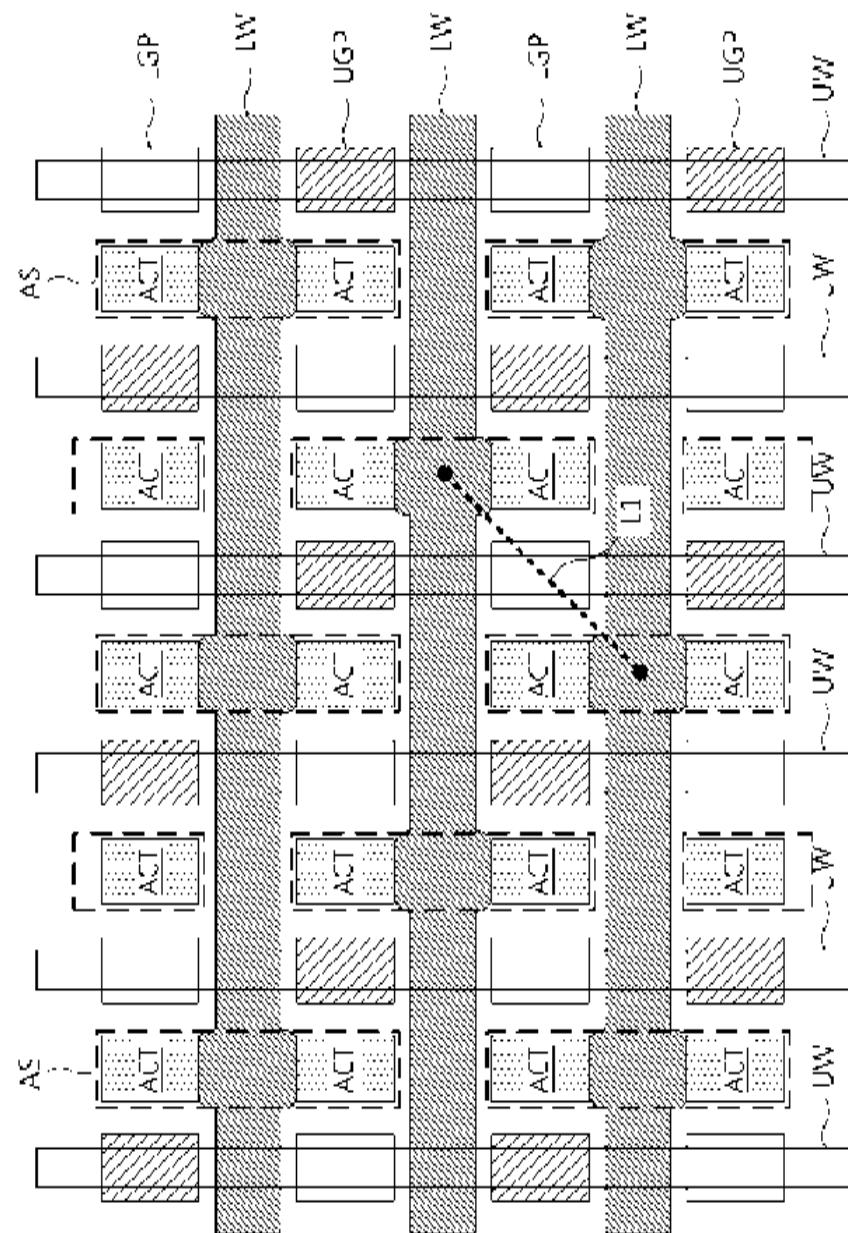

[0130] 도 73 및 도 74는 본 발명의 일 측면을 설명하기 위한 평면도들이다. 보다 구체적으로, 도 73은 하부 게이트 패턴들이 형성되지 않는 경우의 실시예이고, 도 74는 하부 게이트 패턴들이 활성 패턴들 사이이면서 및 하부 배선들 사이인 영역에 형성되는 실시예를 도시한다. 상술한 실시예들에 따르면, 하부 배선들은 활성 패턴들 사이에 형성되기 때문에, 인접하는 두 하부 배선들(LW1, LW2)은 서로 용량적으로 결합되어(capacitively coupled), 이들 사이에는 데이터 교란 또는 동작 속도의 저하를 초래하는 기생 커패시터들이 형성될 수 있다. 예를 들면, 도 73에 도시한 것처럼, 이러한 기생 커패시터들(C1, C2)은, 크게, 상기 활성 패턴(ACT)과 상기 하부 배선들(LW1, LW2) 중의 하나 사이에 형성되는 제 1 기생 커패시터(C1)와 상기 하부 배선들(LW1, LW2) 사이에 형성되는 제 2 기생 커패시터(C2)로 구분될 수 있다. 특히, 상기 제 1 기생 커패시터들(C1)의 경우, 그것을 구성하는 하부 배선과 활성 패턴들 사이의 거리가 작기 때문에, 큰 정전용량을 갖는 커패시터로서 기능할 수 있다.

[0131] 반면, 도 74에서와 같이, 활성 패턴들 사이이면서 및 하부 배선들 사이인 영역에 하부 게이트 패턴들(LGP)이 형성되는 경우, 이러한 기생 커패시터들(C1, C2)에 의한 데이터 교란 또는 동작 속도의 저하는 완화될 수 있다.

[0132] 보다 구체적으로, 상기 하부 게이트 패턴들(LGP)은 낮은 비저항을 갖는 물질로 형성되면서 상기 기판(SUB)에 접속하기 때문에, 상기 하부 배선들(LW) 사이의 전기장을 차폐(shield)시킬 수 있다. 이에 따라, 도 73을 참조하

여 설명된 상기 제 2 기생 커패시터들(C2)의 생성은 차폐체(shielding element)로서의 상기 하부 게이트 패턴들(LGP)에 의해 억제될 수 있다.

[0133] 또한, 상기 하부 게이트 패턴들(LGP)은 상기 기판(SUB)과 실질적으로 등전위 상태에 있기 때문에, 도 3을 참조하여 설명된 것처럼, 상기 하부 게이트 패턴(LGP)에 인접하는 상기 활성 패턴(ACT)의 영역들은 반전(inversion) 또는 공핍(depletion) 상태에 있을 수 있다. 이러한 반전 또는 공핍 영역에 의해, 상기 제 1 기생 커패시터(C1)의 전극들 사이의 대향 면적은 감소되고 이들 사이의 거리는 증가한다. 이에 따라, 도 74에서의 제 1 기생 커패시터(C1a)는 도 73에서의 상기 제 1 기생 커패시터(C1)보다 크게 감소된 커패시턴스(capacitance)를 가질 수 있다.

[0134] 도 75 내지 도 79는 본 발명의 변형된 실시예에 따른 반도체 장치의 제조 방법을 보여주는 사시도들이다. 설명의 간결함을 위해, 상술한 실시예들과 중복되는 기술적 특징들에 대한 설명은 생략한다.

[0135] 도 75에 도시된 것처럼, 도 9a 및 도 9b를 참조하여 설명된 결과물 상에, 2차원적으로 배열된 홀들을 구비하는 제 3 마스크 패턴(MK3)을 형성한 후, 도 76에 도시된 것처럼, 상기 제 3 마스크 패턴(MK3)을 식각 마스크로 사용하여 상기 기판(SUB)을 식각함으로써, 상기 홀들 아래에 소자분리홀들(isolation hole; ISH)을 형성한다.

[0136] 이어서, 도 77에 도시된 것처럼, 상기 제 3 마스크 패턴(MK3)을 제거한 후, 상기 노출된 기판(SUB)의 표면을 덮는 하부 절연막 패턴(LIP)을 형성한다. 상기 하부 절연막 패턴(LIP)을 형성하는 단계는 도 11a 및 도 11b를 참조하여 설명된 방법을 이용하여 실시될 수 있으며, 그 결과, 상기 하부 절연막 패턴(LIP)은 상기 소자분리홀들(ISH)을 채우도록 형성될 수 있다.

[0137] 이후, 상기 제 2 마스크 패턴(MK2) 및 상기 제 2 스페이서(SP2)를 식각 마스크로 사용하여 상기 예비 트렌치(TRC2p)의 바닥면을 리세스한다. 이에 따라, 도 78에 도시된 것처럼, 상기 활성 패턴들(ACT)을 가로지르는 제 2 트렌치(TRC2)가 형성된다. 도 15a 및 도 15b를 참조하여 설명된 제조 방법을 이용하여, 하부 불순물 영역들(LIR) 및 하부 배선(LW)을 형성한다. 이후, 도 17a 내지 도 19a를 참조하여 설명된 단계들을 실시한다. 도 79는 이 단계들이 완료된 반도체 장치를 예시적으로 도시한다.

[0138] 도 80 및 도 81은 도 75 내지 도 79를 참조하여 설명된 실시예에 따른 반도체 장치의 평면도 및 사시도이다.

[0139] 도 80 및 도 81에 도시된 것처럼, 상기 활성 패턴들은 복수의 활성 구조체들(AS)을 구성할 수 있고, 상기 활성 구조체들(AS) 각각은 상기 제 2 트렌치(TRC2)의 양 옆에 형성되는 한 쌍의 활성 패턴들(ACT)을 포함할 수 있다. 상기 활성 구조체들(AS)은 상기 제 1 트렌치들(TRC1)에 의해 정의되는 한 쌍의 측벽들 및 상기 소자분리홀들(ISH)에 의해 정의되는 다른 한 쌍의 측벽들을 갖는다. 상기 소자분리홀들(ISH)이 도 75에 도시된 것처럼 형성되기 때문에, 상기 활성 구조체들(AS)은 오프셋된 배치를 구성한다. 즉, 서로 인접하되 y좌표가 다른 두 활성 구조체들(AS)의 중심점을 연결하는 직선(L1)은 y 축 및 x 축 모두(다시 말해, 상기 상부 배선(UW) 및 상기 하부 배선(LW) 모두)에 평행하지 않을 수 있다.

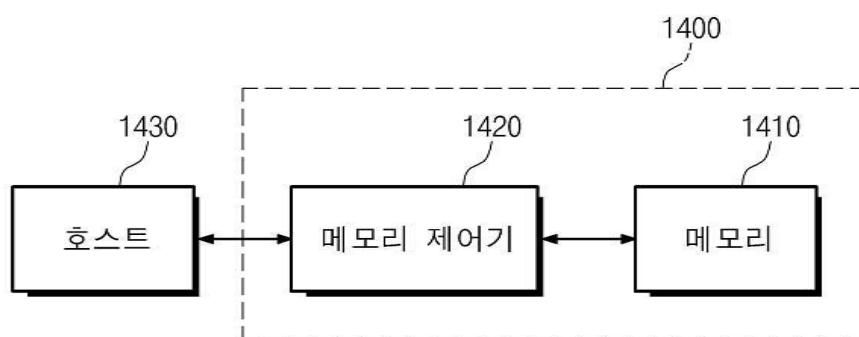

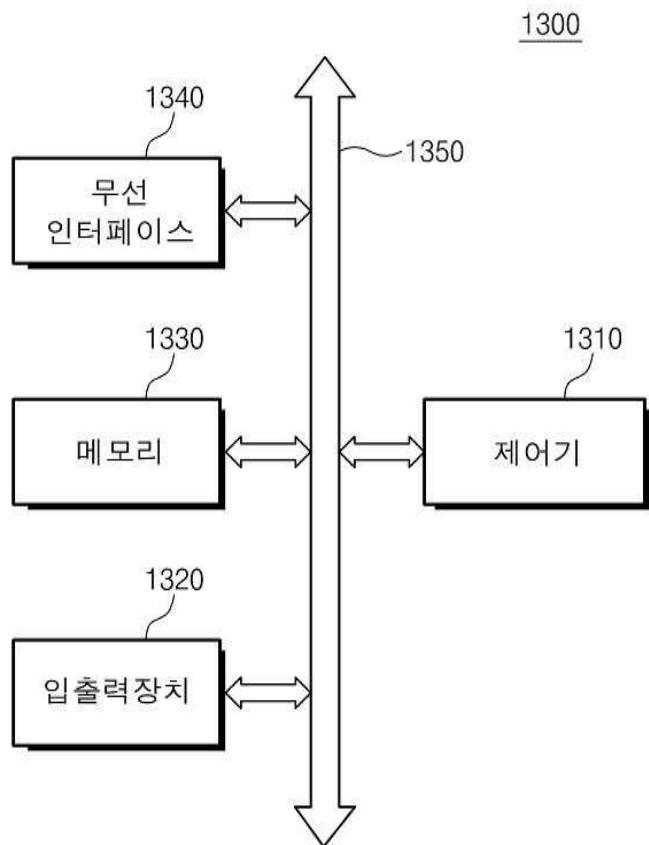

[0140] 도 82 및 도 83는 본 발명의 실시예들에 따른 수직 채널 트랜지스터들을 포함하는 전자 장치들을 도식적으로 설명하기 위한 도면들이다.

[0141] 도 82을 참조하면, 본 발명의 실시예들에 따른 수직 채널 트랜지스터를 포함하는 전자 장치(1300)는 PDA, 랩톱(laptop) 컴퓨터, 휴대용 컴퓨터, 웹 태블릿(web tablet), 무선 전화기, 휴대폰, 디지털 음악 재생기(digital music player), 유무선 전자 기기 또는 이들 중의 적어도 둘을 포함하는 복합 전자 장치 중의 하나일 수 있다. 전자 장치(1300)는 버스(1350)를 통해서 서로 결합한 제어기(1310), 키패드, 키보드, 화면(display) 같은 입출력 장치(1320), 메모리(1330), 무선 인터페이스(1340)를 포함할 수 있다. 제어기(1310)는 예를 들면 하나 이상의 마이크로프로세서, 디지털 신호 프로세서, 마이크로 컨트롤러, 또는 이와 유사한 것들을 포함할 수 있다. 메모리(1330)는 예를 들면 제어기(1310)에 의해 실행되는 명령어를 저장하는데 사용될 수 있다. 메모리(1330)는 사용자 데이터를 저장하는 데 사용될 수 있다. 메모리(1330)는 본 발명의 실시예들에 따른 수직 채널 트랜지스터를 포함한다. 전자 장치(1300)는 RF 신호로 통신하는 무선 통신 네트워크에 데이터를 전송하거나 네트워크에서 데이터를 수신하기 위해 무선 인터페이스(1340)를 사용할 수 있다. 예를 들어 무선 인터페이스(1340)는 안테나, 무선 트랜시버 등을 포함할 수 있다. 전자 장치(1300)는 CDMA, GSM, NADC, E-TDMA, WCDAM, CDMA2000 같은 3세대 통신 시스템 같은 통신 인터페이스 프로토콜에서 사용될 수 있다.

[0142]

도 83를 참조하면, 본 발명의 실시예들에 따른 반도체 메모리 장치들은 메모리 시스템(memory system)을 구현하기 위해 사용될 수 있다. 메모리 시스템(1400)은 대용량의 데이터를 저장하기 위한 메모리 소자(1410) 및 메모리 컨트롤러(1420)를 포함할 수 있다. 메모리 컨트롤러(1420)는 호스트(1430)의 읽기/쓰기 요청에 응답하여 메모리 소자(1410)로부터 저장된 데이터를 독출 또는 기입하도록 메모리 소자(1410)를 제어한다. 메모리 컨트롤러(1420)는 호스트(1430), 가령 모바일 기기 또는 컴퓨터 시스템으로부터 제공되는 어드레스를 메모리 소자(1410)의 물리적인 어드레스로 맵핑하기 위한 어드레스 맵핑 테이블(Address mapping table)을 구성할 수 있다. 메모리 소자(1410)는 본 발명의 실시예에 따른 수직 채널 트랜지스터를 포함할 수 있다.

[0143]

이상의 발명의 상세한 설명은 개시된 실시 상태로 본 발명을 제한하려는 의도가 아니며, 본 발명의 요지를 벗어나지 않는 범위 내에서 다양한 다른 조합, 변경 및 환경에서 사용할 수 있다. 첨부된 청구범위는 다른 실시 상태도 포함하는 것으로 해석되어야 할 것이다.

### 부호의 설명

[0144]

|                                    |                 |

|------------------------------------|-----------------|

| SUB: 기판                            | TRC2p: 예비 트렌치   |

| TRC1: 제 1 트렌치                      | TRC2: 제 2 트렌치   |

| LGL: 하부 게이트막                       | UGL: 상부 게이트막    |

| LGP: 하부 게이트 패턴                     | UGP: 상부 게이트 패턴  |

| GI: 게이트 절연막                        | PIP: 플리그 절연 패턴  |

| LIP: 하부 절연 패턴                      | UIP: 상부 절연 패턴   |

| JDR: 접합 정의 영역                      | UCR: 언더컷 영역     |

| LIR: 하부 불순물 영역                     | UIR: 상부 불순물 영역  |

| LW: 하부 배선                          | UW: 상부 배선       |

| UCL: 상부 도전막                        | CPL: 캐핑         |

| PLG: 플리그                           | CLE: 커패시터 하부 전극 |

| CUE: 커패시터 상부 전극                    | ME: 메모리 요소      |

| MK1/MK2/MK3/MK4: 제 1 내지 제 4 마스크 패턴 |                 |

| SP1/SP2/SP3: 제 1 내지 제 3 스페이서       |                 |

### 도면

#### 도면1

도면2a

도면2b

## 도면2c

## 도면3

도면4

도면5a

TRC1

도면5b

도면6a

도면6b

도면7a

도면7b

도면8a

도면8b

## 도면9a

도면9b

도면10a

## 도면10b

도면11a

도면11b

도면12a

도면12b

도면13a

도면13b

도면14a

도면14b

도면15a

### 도면 15b

도면16a

도면16b

도면17a

도면17b

도면18a

도면18b

도면19a

### 도면19b

도면20

도면21

도면22

## 도면23

도면24a

도면24b

도면25a

도면25b

도면26a

도면26b

도면27a

도면27b

도면28a

도면28b

도면29a

도면29b

도면30a

도면30b

도면31a

도면31b

## 도면32

도면33a

도면33b

도면34a

도면34b

도면35a

도면35b

도면36a

도면36b

도면37a

도면37b

도면38a

### 도면38b

도면39a

도면39b

도면40a

### 도면40b

## 도면41

도면42a

## 도면42b

도면43a

도면43b

도면44a

도면44b

도면45a

도면45b

도면46a

도면46b

## 도면47

도면48a

도면48b

도면49a

도면49b

도면50a

도면50b

도면51a

도면51b

도면52a

도면52b

도면53a

도면53b

도면54a

도면54b

도면55a

도면55b

도면56a

도면56b

도면57

도면58

도면59

## 도면60

도면61

도면62

도면63

도면64

도면65

도면66

도면67

도면68

도면69

## 도면70

도면71

도면72

도면73

## 도면74

### 도면75

도면76

도면77

도면78

도면79

도면80

도면81

도면82

도면83