등록특허 10-2210973

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2021년02월02일

(11) 등록번호 10-2210973

(24) 등록일자 2021년01월27일

- (51) 국제특허분류(Int. Cl.)

*G01R 31/12* (2006.01)

- (21) 출원번호 10-2014-0186751

(22) 출원일자 2014년12월23일

심사청구일자 2019년12월20일

- (65) 공개번호 10-2015-0073870

(43) 공개일자 2015년07월01일

(30) 우선권주장

14/138,575 2013년12월23일 미국(US)

- (56) 선행기술조사문현

US20110019444 A1

JP2012112937 A

US20100027176 A1

EP0792465 A

- (73) 특허권자

센사타 테크놀로지스 매사추세츠, 임크.

미합중국 매사추세츠주 애틀보로 플래전트 스트리트 529(우편번호: 02703)

- (72) 발명자

강 지안홍

미국 매사추세츠주 02067 샤론 제퍼슨 애비뉴 11

펠론 크리스티안 브이.

미국 매사추세츠주 02766 노튼 에린 레인 3

(뒷면에 계속)

- (74) 대리인

김진희, 김태홍

전체 청구항 수 : 총 20 항

심사관 : 이병수

(54) 발명의 명칭 멀티스트링 아크 고장 검출 디바이스의 개선된 노이즈 전파 면역성

**(57) 요 약**

개선된 노이즈 전파 면역성(noise propagation immunity)을 제공할 수 있는 DC 전력 시스템에서 아크 방전을 검출하는 시스템 및 방법. 시스템은 각각 적어도 2개의 전류 출력을 모니터링하기 위한 적어도 2개의 전류 센서를 포함한다. 전류 센서는 반대 극성을 갖고, 결합 전류 출력 신호를 제공하기 위해 병렬로 구성 및 배열된다. 전류 센서는 적어도 2개의 인접 전도체에 대해 전류 센서에 의해 모니터링하기 위해 제공되는 각각의 전류 출력을 모니터링한다. 제1 전도체의 임의의 위치에 아크 방전이 일어나면, 제1 전도체에서의 아크 방전과 동일한 아크 전류 시그니처를 갖는 아크 방전(인접 전도체 크로스토크)은 다른 인접 전도체 상의 임의의 위치에 일어날 수 있다. 시스템은 태양광(PV) 시스템 내의 이러한 인접 전도체 크로스토크를 효과적으로 상쇄할 수 있으며, 이로써 PV 스트링 레벨에서 아크 방전을 검출하기 위한 아크 고장 검출 디바이스의 능력을 개선한다.

**대 표 도**

(72) 발명자

마틴 리

미국 로드 아일랜드주 02906 프로비던스 바사 애비

뉴 75

카와테 키이스 더블유.

미국 매사추세츠주 02768 애틀보로 베지니아 애비

뉴 12

---

## 명세서

### 청구범위

#### 청구항 1

DC 전력 시스템에서 아크 방전(arcing)을 검출하는 방법에 있어서,

적어도 2개의 전류 센서에 의해 적어도 2개의 전류 출력을 각각 모니터링하는 단계로서, 상기 적어도 2개의 전류 센서는 반대 극성을 갖고, 상기 적어도 2개의 전류 출력은 상기 DC 전력 시스템에서, 상기 각각의 전류 센서에 의해 적어도 2개의 인접한 전도체에 대해 모니터링하기 위해 제공되는 것인, 상기 적어도 2개의 전류 출력을 각각 모니터링하는 단계;

결합 전류 출력을 제공하기 위해 상기 적어도 2개의 전류 출력을 결합하는 단계;

시간에 따른 상기 결합 전류 출력의 적어도 하나의 변화( $di/dt$ )에 응답하여 하나 이상의 펄스를 생성하는 단계

- 상기 각각의 펄스는 연관된 지속시간을 가짐 - ;

상기 DC 전력 시스템에서 아크 방전의 존재를 결정하기 위해 프로세서에 의해 상기 각각의 펄스를 프로세싱하는 단계로서,

미리 결정된 시간 인터벌 동안의 펄스 카운트를 제공하기 위해 적어도 하나의 상기 미리 결정된 시간 인터벌에서 상기 펄스의 개수를 카운트하는 단계;

상기 미리 결정된 시간 인터벌에서 상기 각각의 펄스의 지속시간에서의 변동(fluctuation)을 측정하는 단계;

상기 펄스 카운트에 대한 상기 각각의 펄스의 지속시간에서의 변동의 제1 비(ratio)를 계산하는 단계;

및

상기 제1 비에 적어도 부분적으로 기초하여 상기 DC 전력 시스템에서 아크 방전의 존재를 결정하는 단계

를 포함하는, 상기 각각의 펄스를 프로세싱하는 단계;

상기 프로세서에 의해 상기 DC 전력 시스템에서 상기 아크 방전의 존재를 나타내는 출력을 생성하는 단계

를 포함하는, 아크 방전 검출 방법.

#### 청구항 2

제1항에 있어서,

상기 아크 방전의 존재를 결정하는 단계는 상기 제1 비가 제1 특정 임계치를 초과한다고 결정하는 단계를 포함하는 것인, 아크 방전 검출 방법.

#### 청구항 3

제1항에 있어서,

상기 펄스의 개수를 카운트하는 단계는 상기 각각의 미리 결정된 시간 인터벌 동안의 펄스 카운트를 제공하기 위해 복수의 미리 결정된 시간 인터벌의 각각에 상기 펄스의 개수를 카운트하는 단계를 포함하고,

상기 각각의 펄스의 지속시간에서의 변동을 측정하는 단계는 상기 각각의 미리 결정된 시간 인터벌에서 각각의 펄스의 지속시간에서의 변동을 측정하는 단계를 포함하는 것인, 아크 방전 검출 방법.

#### 청구항 4

제3항에 있어서,

상기 제1 비를 계산하는 단계는,

각각의 미리 결정된 시간 인터벌 이후 상기 펄스 카운트의 평균을 계산하는 단계,

상기 각각의 미리 결정된 시간 인터벌 이후 상기 각각의 펄스의 지속시간에서의 변동의 평균을 계산하는 단계, 및

상기 각각의 펄스의 지속시간에서의 변동의 평균 및 상기 펄스 카운트의 평균에 기초하여 상기 제1 비를 계산하는 단계

를 포함하는 것인, 아크 방전 검출 방법.

#### 청구항 5

제1항에 있어서,

상기 프로세서에 의해 상기 각각의 펄스를 프로세싱하는 단계는,

상기 제1 비를 계산하는 단계 이전에, 상기 프로세서에 의해 상기 미리 결정된 시간 인터벌에서 상기 각각의 펄스의 지속시간의 변조(modulation)를 측정하는 단계를 더 포함하는, 아크 방전 검출 방법.

#### 청구항 6

제5항에 있어서,

상기 프로세서에 의해 상기 각각의 펄스를 프로세싱하는 단계는,

상기 제1 비를 계산하는 단계 이후에, 상기 프로세서에 의해 상기 각각의 펄스의 지속시간의 변조에 대한 상기 각각의 펄스의 지속시간의 변동의 제2 비를 계산하는 단계를 더 포함하는, 아크 방전 검출 방법.

#### 청구항 7

제6항에 있어서,

상기 아크 방전의 존재를 결정하는 단계는 상기 제1 비 및 상기 제2 비에 적어도 부분적으로 기초하여 상기 DC 전력 시스템에서 아크 방전의 존재를 결정하는 단계를 포함하는 것인, 아크 방전 검출 방법.

#### 청구항 8

제7항에 있어서,

상기 아크 방전의 존재를 결정하는 단계는,

상기 제1 비가 제1 특정 임계치를 초과한다고 결정하는 단계, 및

상기 제2 비가 제2 특정 임계치를 초과한다고 결정하는 단계

를 포함하는 것인, 아크 방전 검출 방법.

#### 청구항 9

제6항에 있어서,

상기 각각의 펄스의 지속시간에서의 변동을 측정하는 단계는 복수의 미리 결정된 시간 인터벌 동안의 상기 각각의 펄스의 지속시간에서의 변동을 측정하는 단계를 포함하고,

상기 각각의 펄스의 지속시간에서의 변조를 측정하는 단계는 상기 복수의 미리 결정된 시간 인터벌 동안의 상기 각각의 펄스의 지속시간에서의 변조를 측정하는 단계를 포함하는 것인, 아크 방전 검출 방법.

#### 청구항 10

제9항에 있어서,

상기 제2 비를 계산하는 단계는,

각각의 미리 결정된 시간 인터벌 이후 상기 각각의 펄스의 지속시간에서의 변동의 평균을 계산하는 단계,

상기 각각의 미리 결정된 시간 인터벌 이후 상기 각각의 펄스의 지속시간에서의 변조의 평균을 계산하는 단계, 및

상기 각각의 펄스의 지속시간에서의 변동의 평균 및 상기 각각의 펄스의 지속시간에서의 변조의 평균에 기초하여 상기 제2 비를 계산하는 단계

를 포함하는 것인, 아크 방전 검출 방법.

### 청구항 11

제6항에 있어서,

상기 프로세서에 의해 상기 각각의 펄스를 프로세싱하는 단계는,

상기 제1 비를 계산하는 단계 이전에, 상기 프로세서에 의해 상기 미리 결정된 시간 인터벌 동안의 상기 펄스 카운트에서의 변동을 측정하는 단계를 더 포함하는, 아크 방전 검출 방법.

### 청구항 12

제11항에 있어서,

상기 프로세서에 의해 상기 각각의 펄스를 프로세싱하는 단계는,

상기 아크 방전의 존재를 결정하는 단계 이전에, 상기 프로세서에 의해 상기 펄스 카운트에 대한 상기 펄스 카운트에서의 변동의 제3 비와 상기 각각의 펄스의 지속시간에 대한 상기 각각의 펄스의 지속시간에서의 변동의 제4 비 중 하나 이상을 계산하는 단계를 더 포함하는, 아크 방전 검출 방법.

### 청구항 13

제12항에 있어서,

상기 아크 방전의 존재를 결정하는 단계는 상기 제1 비, 및 상기 제2 비와 상기 제3 비와 상기 제4 비 중 하나 이상에 적어도 부분적으로 기초하여 상기 DC 전력 시스템에서 아크 방전의 존재를 결정하는 단계를 포함하는 것인, 아크 방전 검출 방법.

### 청구항 14

제13항에 있어서,

상기 아크 방전의 존재를 결정하는 단계는,

상기 제1 비가 제1 특정 임계치를 초과한다고 결정하는 단계,

상기 제2 비가 제2 특정 임계치를 초과한다고 결정하는 단계,

상기 제3 비가 제3 특정 임계치를 초과한다고 결정하는 단계, 및

상기 제4 비가 제4 특정 임계치를 초과한다고 결정하는 단계

를 포함하는 것인, 아크 방전 검출 방법.

### 청구항 15

제14항에 있어서,

상기 아크 방전의 존재를 결정하는 단계는,

상기 펄스 카운트가 제5 특정 임계치를 초과한다고 결정하는 단계, 및

상기 각각의 펄스의 지속시간이 제6 특정 임계치를 초과한다고 결정하는 단계

를 더 포함하는 것인, 아크 방전 검출 방법.

### 청구항 16

제15항에 있어서,

상기 펄스 카운트에서 상기 변동을 측정하는 단계는 복수의 미리 결정된 시간 인터벌 동안의 상기 펄스 카운트에서의 변동을 측정하는 단계를 포함하고,

상기 각각의 펄스의 지속시간의 변동을 측정하는 단계는 상기 복수의 미리 결정된 시간 인터벌 동안의 상기 각각의 펄스의 지속시간의 변동을 측정하는 단계를 포함하는 것인, 아크 방전 검출 방법.

### 청구항 17

제16항에 있어서,

상기 제3 비를 계산하는 단계는,

각각의 미리 결정된 시간 인터벌 이후 상기 펄스 카운트에서의 변동의 평균을 계산하는 단계,

상기 각각의 미리 결정된 시간 인터벌 이후 상기 펄스 카운트의 평균을 계산하는 단계, 및

상기 펄스 카운트에서의 변동의 평균 및 상기 펄스 카운트의 평균에 기초하여 상기 제3 비를 계산하는 단계

를 포함하는 것인, 아크 방전 검출 방법.

### 청구항 18

제16항에 있어서,

상기 제4 비를 계산하는 단계는,

각각의 미리 결정된 시간 인터벌 이후 상기 각각의 펄스의 지속시간에서의 변동의 평균을 계산하는 단계,

상기 각각의 미리 결정된 시간 인터벌 이후 상기 각각의 펄스의 지속시간의 평균을 계산하는 단계, 및

상기 각각의 펄스의 지속시간에서의 변동의 평균 및 상기 각각의 펄스의 지속시간의 평균에 기초하여 상기 제4 비를 계산하는 단계

를 포함하는 것인, 아크 방전 검출 방법.

### 청구항 19

DC 전력 시스템에서 아크 방전을 검출하는 시스템에 있어서,

적어도 2개의 전류 출력을 각각 모니터링하도록 동작하는 적어도 2개의 전류 센서로서, 상기 적어도 2개의 전류 센서는 결합 전류 출력을 제공하도록 구성 및 배열되고, 상기 적어도 2개의 전류 센서는 반대 극성을 갖고, 상기 적어도 2개의 전류 출력은 상기 DC 전력 시스템에서 상기 각각의 전류 센서에 의해 각각 적어도 2개의 인접한 전도체에 대해 모니터링하기 위해 제공되는 것인, 상기 적어도 2개의 전류 센서;

시간에 따른 상기 결합 전류 출력의 적어도 하나의 변화( $di/dt$ )에 응답하여 하나 이상의 펄스를 생성하도록 동작하는 비교기 - 상기 각각의 펄스는 연관된 지속시간을 가짐 - ; 및

프로세서

를 포함하고,

상기 프로세서는,

미리 결정된 시간 인터벌 동안의 펄스 카운트를 제공하기 위해 적어도 하나의 상기 미리 결정된 시간 인터벌에서 상기 펄스의 개수를 카운트하는 것,

상기 미리 결정된 시간 인터벌에서 상기 각각의 펄스의 지속시간에서의 변동을 측정하는 것,

상기 펄스 카운트에 대한 상기 각각의 펄스의 지속시간에서의 변동의 제1 비를 계산하는 것, 및

상기 제1 비에 적어도 부분적으로 기초하여 상기 DC 전력 시스템에서 아크 방전의 존재를 결정하는 것

에 의해 상기 DC 전력 시스템에서 아크 방전의 존재를 결정하기 위해, 상기 각각의 펄스를 프로세싱하도록, 그리고 상기 DC 전력 시스템에서 상기 아크 방전의 존재를 나타내는 출력을 생성하도록 동작하는 것인, 아크 방전 검출 시스템.

## 청구항 20

DC 전력 시스템에서 아크 방전을 검출하는 시스템에 있어서,

적어도 2개의 전류 출력을 각각 모니터링하도록 동작하는 적어도 2개의 전류 센서로서, 상기 적어도 2개의 전류 센서는 결합 전류 출력을 제공하도록 구성 및 배열되고, 상기 적어도 2개의 전류 출력은 상기 DC 전력 시스템에서 상기 각각의 전류 센서에 의해 각각 적어도 2개의 인접한 전도체에 대해 모니터링하기 위해 제공되고, 상기 적어도 2개의 인접한 전도체는 반대 방향으로 상기 적어도 2개의 전류 출력을 제공하도록 구성 및 배열되는 것인, 상기 적어도 2개의 전류 센서;

시간에 따른 상기 결합 전류 출력의 적어도 하나의 변화( $di/dt$ )에 응답하여 하나 이상의 펄스를 생성하도록 동작하는 비교기 - 상기 각각의 펄스는 연관된 지속시간을 가짐 - ; 및

프로세서

를 포함하고,

상기 프로세서는,

미리 결정된 시간 인터벌 동안의 펄스 카운트를 제공하기 위해 적어도 하나의 상기 미리 결정된 시간 인터벌에서 상기 펄스의 개수를 카운트하는 것,

상기 미리 결정된 시간 인터벌에서 상기 각각의 펄스의 지속시간에서의 변동을 측정하는 것,

상기 펄스 카운트에 대한 상기 각각의 펄스의 지속시간에서의 변동의 제1 비를 계산하는 것, 및

상기 제1 비에 적어도 부분적으로 기초하여 상기 DC 전력 시스템에서 아크 방전의 존재를 결정하는 것

에 의해 상기 DC 전력 시스템에서 아크 방전의 존재를 결정하기 위해 상기 각각의 펄스를 프로세싱하도록 그리고 상기 DC 전력 시스템에서 상기 아크 방전의 존재를 나타내는 출력을 생성하도록 동작하는 것인, 아크 방전 검출 시스템.

## 청구항 21

삭제

### 발명의 설명

#### 기술 분야

[0001] 본 특허출원은 발명의 명칭이 “SYSTEMS AND METHODS OF DISCRIMINATING DC ARCS AND LOAD SWITCHING NOISE”이고, 2012년 11월 16일에 출원된 미국 특허 출원 제13/679,039호의 일부 계속 출원(CIP)인, 발명의 명칭이 “HOME RUN ARC DETECTION AT THE PHOTOVOLTAIC STRING LEVEL USING MULTIPLE CURRENT SENSORS”이고, 2013년 3월 15일에 출원된 미국 특허 출원 제13/836,345호의 일부 계속 출원이다.

[0002] 본 출원은 일반적으로 전기 회로들에서 아크 방전(arcing)을 검출하는 것에 관한 것으로서, 특히 다수의 태양광(PV) 스트링을 갖는 PV 시스템에 채택된 아크 고장(arc fault) 검출 디바이스에서 노이즈 전파 면역성(noise propagation immunity)을 개선하는 시스템 및 방법에 관한 것이다.

### 배경 기술

삭제

[0004] 최근 수년 동안, 태양광(PV) 시스템들과 같은 DC 전력 시스템들이 배터리의 충전 내지 교류(alternating current, AC) 그리드(grid)에 대한 전력 공급 범위의 가정용 및 산업용 애플리케이션들에 점차 채택되고 있다. 이러한 PV 시스템들은 하나 이상의 PV 시스템을 형성하기 위해 직렬 연결된 복수의 PV 모듈(예를 들어, 태양 전

지판(solar panel))을 포함할 수 있다. 다수의 PV 스트링은 병렬 연결되어 차저(charger) 또는 인버터(inverter) 부하를 궁극적으로 구동하기 위한 커버라이너 박스(combiner box)을 통해 라우팅될 수 있다. 통상의 PV 시스템에서는, 각 PV 모듈은 50Vdc에서 최대 약 10 암페어의 전류 출력을 생성하도록 구성될 수 있고, PV 스트링에 연결된 PV 모듈들의 개수에 의존하여, 각 PV 스트링은 최대 약 1000Vdc 이상의 전압 출력을 생성하도록 구성될 수 있다. 또한, 병렬 연결된 PV 스트링들은 최대 약 200 암페어 이상의 통상의 PV 시스템의 총 전력 출력을 부스팅하도록 구성될 수 있다.

전술된 PV 시스템들과 같은 DC 전력 시스템들이 상대적으로 높은 전력 및 전압 출력들을 생성하도록 구성될 수 있기 때문에, 이러한 전력 시스템들에서 아크 방전(arcing)을 검출하는 시스템 및 방법에 대한 필요성이 있다. 예를 들어, 전류 출력 및 전압 출력이 각각 약 200 암페어 및 1000Vdc일 수 있는 통상적인 PV 시스템에서, 직렬 아크 방전(series arcing)은 PV 전력 케이블들을 분리함으로써 생성될 수 있고, 병렬 아크 방전(parallel arcing)은 PV 전력 케이블들을 단락시킴으로써 생성될 수 있고, 접지 고장 아크 방전(ground fault arcing)은 PV 전력 케이블들을 접지에 단락시킴으로써 생성될 수 있다. 그러나, 지금까지 전력 시스템들에서 아크 방전을 검출하는 공지의 시스템들 및 방법들은 일반적으로 직렬 아크 방전, 병렬 아크 방전, 접지 고장 아크 방전 등을 구분할 수 없었고, 차저 부하, 인버터 부하, DC-DC 부하 스위칭, DC-AC 부하 스위칭, DC 분리 스위치들, 무선 주파수(RF) 꼽업, DC 전력 라인 통신 등에서 노이즈가 생성될 가능성성이 높았다.

본 발명의 배경이 되는 기술은 미국 특허공개공보 US 2010-0027176 A1 (2010.02.04)에 개시되어 있다.

## 발명의 내용

### 해결하려는 과제

[0005]

본 출원에 따르면, 개선된 노이즈 전파 면역성을 제공할 수 있는, DC 전력 시스템에서 아크 방전을 검출하는 시스템 및 방법들이 개시된다. DC 전력 시스템에서 아크 방전을 검출하는 이러한 시스템은 각각 적어도 2개의 전류 출력을 모니터링하도록 동작하는 적어도 2개의 전류 센서(current sensor)를 포함하는데, 이들은 홈 런 케이블(home run cable) 또는 임의의 다른 적절한 와이어링 런(wiring run)에 제공된다. 적어도 2개의 전류 센서들은 반대 극성(예를 들어, “N극” 및 “S극”)을 가지며, 병렬, 직렬 또는 병렬/직렬 상호 연결의 임의의 조합으로 구성 및 배열되어 결합된 전류 출력 신호를 제공한다. 시스템은 정류기(rectifier), 필터(filter, 비교기(comparator), 펄스 적산기(pulse integrator), 및 프로세서를 더 포함한다. 적어도 2개의 전류 센서들은 태양광(PV) 시스템일 수 있는 DC 전력 시스템의 적어도 2개의 전류 출력을 모니터링하도록 동작한다. 적어도 2개의 전류 출력은 PV 시스템 내에서 각각의 전류 센서들에 의해 적어도 2개의 인접 PV 스트링에 대응하는 적어도 2개의 전도체에 대해 모니터링하기 위해 제공될 수 있다. PV 스트링들 중 첫번째 PV 스트링(“제1 PV 스트링”)에 대응하는 전도체 상의 일정 위치에 아크 방전이 일어나면, 제1 PV 스트링에 대한 아크 방전과 같은 아크 전류 시그니처(arc current signature)(예를 들어, 직렬 아크 방전)를 갖는 아크 방전은 제1 PV 스트링에 인접한 적어도 하나의 PV 스트링에 대응하는 전도체 상의 일정 위치에 일어날 수 있다. 인접한 PV 스트링들에 대응하는 전도체들 상에 일어날 수 있는 이러한 아크 방전은 또한 “인접 전도체 크로스토크(adjacent conductor crosstalk)”라고 지칭된다. 시스템은 PV 시스템 내의 이러한 인접 전도체 크로스토크를 효과적으로 상쇄하도록 구성되는데, PV 스트링 레벨에서 아크 방전을 검출하기 위한 아크 고장 검출 디바이스의 능력을 개선한다. 시스템은 또한 인버터 부하 노이즈로부터의 면역성이 개선된 이러한 아크 고장 검출 디바이스에 제공할 수 있다.

[0006]

개시된 시스템 내에서, 개별 전류 센서들에 의해 제공되는 결합 전류 출력 신호는 하나 이상의 중요한  $di/dt$  이벤트들을 나타내는 고주파 AC 전류 정보를 포함할 수 있는데, 이를 이벤트는 잠재적으로 하나 이상의 이벤트를 나타낼 수 있다. 정류기는 전류 센서로부터 AC 전류 정보를 포함하는 결합 전류 출력 신호를 수신하고, 후속 필터링을 위해 결합 전류 출력 신호의 정류된 버전을 필터에 제공한다. 다른 방법으로, AC 전류 정보를 포함하는 결합 전류 출력 신호가 정류되기 전에 필터링될 수 있다는 점에 유의한다. 비교기는 필터링된 신호를 수신하고, 잠재적 아크 방전 이벤트들에 응답하여 하나 이상의 펄스를 생성한다. 펄스 적산기는 비교기로부터 펄스들을 수신하고, 개별적인 펄스들의 지속시간을 나타내는 출력을 생성한다. 프로세서 또는 비교기로부터 펄스들을 수신하고, 복수의 미리 결정된 시간 인터벌 내에 미리 결정된 시간 인터벌당 펄스 카운트(pulse count, PC)를 결정하는데, 이러한 펄스 카운트는 잠재적 아크 방전 이벤트들의 개수에 대응한다. 프로세서는 펄스 적산기에 의해 생성된 출력을 더 수신하고, 각각의 잠재적 아크 방전 이벤트들의 강도에 대응할 수 있는 미리 결정된 시간 인터벌당 펄스 지속시간(pulse duration, PD)을 각각의 소정 시간 인터벌 내에서 결정한다. 그 후, 프로세서는 DC 아크와 부하-스위칭 노이즈를 더 잘 구별하기 위해 하나 이상의 아크 고장 검출 알고리즘들을 이용하

여 PC 및 PD를 프로세싱한다.

## 과제의 해결 수단

[0007] 일 양태에서, 프로세서는 2개의 변수, 즉 평균 펄스 카운트(average pulse count, APC) 및 평균 펄스 지속시간 변동(average pulse duration fluctuation, APDF)의 값들을 각각의 미리 결정된 시간 인터벌의 마지막에 계산한다. 예를 들어, 프로세서는 가장 최근의 시간 인터벌을 위한 PD와 가장 최근의 시간 인터벌보다 하나 또는 2개 이상의 시간 인터벌 이전에 일어난 시간 인터벌을 위한 PD 사이의 차이의 절대값을 취하거나, 또는 임의의 다른 적절한 기법에 의해 각각의 미리 결정된 시간 인터벌에서 펄스 지속시간 변동(pulse duration fluctuation, PDF)을 계산할 수 있다. 프로세서는 APDF/APC의 비가 제1 특정 임계치를 초과하는지 여부를 각 시간 인터벌의 마지막에 더 결정한다. APDF/APC의 비가 각 시간 인터벌의 마지막에 제1 특정 임계치를 초과하는 이벤트에서, 시간 인터벌은 실제 아크 방전 이벤트가 일어났을 수 있는 인터벌로 간주된다. 예를 들어, 프로세서가 APDF/APC의 비가 각각의 시간 인터벌 중에 제1 특정 임계치를 초과한다고 결정하면, “1”의 출력 또는 임의의 다른 적절한 출력을 생성할 수 있고, 그렇지 않으면, 프로세서는 “0”의 출력 또는 임의의 다른 적절한 출력을 생성할 수 있다. 프로세서는 복수의 시간 인터벌이 끝날 때까지 생성된 출력들(1 또는 0)을 평균화하고, 각각의 출력들의 평균이 제2 특정 임계치를 초과하면, 실제 아크 방전이 일어났을 것이라고 가정하고, 프로세서는 이러한 아크 방전을 나타내는 다른 출력을 생성한다. 이러한 방식으로, 프로세서는 다수의 시간 인터벌이 끝날 때까지 PDF를 평가할 수 있고, 다수의 시간 인터벌에 대한 PDF가 높다고 결정하면, 프로세서는 실제 아크 방전이 일어날 가능성에 있다고 지시하는 출력을 생성할 수 있다.

[0008] 다른 양태에서, 프로세서는 각각의 미리 결정된 시간 인터벌의 마지막에 3개의 변수, 즉 APC, APDF, 및 평균 펄스 지속시간 변조(average pulse duration modulation, APDM)의 값들을 계산한다. 예를 들어, 프로세서는 시간 인터벌의 1/4만큼 이격된 각각의 미리 결정된 시간 인터벌 동안 4개의 PD 측정(PD1, PD2, PD3, 및 PD4)을 취하고, 각 시간 인터벌의 마지막에 다음과 같이 APDM을 계산함으로써 APDM을 계산할 수 있는데,

$$APDM = | APD1 + APD2 - APD3 - APD4 | + | APD1 - APD2 - APD3 + APD4 |,$$

[0010] 여기서, 복수의 미리 결정된 시간 인터벌이 끝날 때까지, 또는 임의 다른 적절한 기법에 의해, “APD1”은 “PD1” 측정들의 평균이고, “APD2”는 “PD2” 측정들의 평균이고, “APD3”는 “PD3” 측정들의 평균이고, “APD4”는 “PD4” 측정들의 평균이다. 프로세서는 APDF/APC의 비가 제1 특정 임계치를 초과하는지 여부 및 APDF/APDM의 비가 제2 특정 임계치를 초과하는지 여부를 각 시간 인터벌의 마지막에 더 결정한다. APDF/APC의 비가 제1 특정 임계치를 초과하고, APDF/APDM의 비가 제2 특정 임계치를 초과한다고 각 시간 인터벌의 마지막에 결정된 이벤트에서, 이러한 시간 인터벌은 실제 아크 방전 이벤트가 일어났을 수 있는 인터벌이라고 간주된다. 예를 들어, 각각의 시간 인터벌 동안 APDF/APC의 비가 제1 특정 임계치를 초과하고, APDF/APDM의 비가 제2 특정 임계치를 초과한다고 결정하면, 프로세서는 “1”의 출력 또는 임의의 다른 적절한 출력을 생성할 수 있으며, 그렇지 않으면, 프로세서는 “0”의 출력 또는 임의의 다른 적절한 출력을 생성할 수 있다. 프로세서는 복수의 시간 인터벌이 끝날 때까지 생성된 출력들(1 또는 0)을 평균화하고, 각각의 출력들의 평균이 제3 특정 임계치를 초과하면, 실제 아크 방전이 일어났을 것이라고 가정하고, 프로세서는 이러한 아크 방전을 나타내는 다른 출력을 생성한다. 이러한 방식으로, 프로세서는 실제 아크 방전과 그리드 종속 인버터 부하들과 같이 매우 잡음이 많은 부하들을 더 신뢰 가능하게 구별할 수 있다.

[0011] 또 다른 양태에서, 프로세서는 각각의 미리 결정된 시간 인터벌의 마지막에 5개의 변수, 즉 APC, APDF, APDM, 평균 펄스 지속시간(average pulse duration, APD), 및 평균 펄스 카운트 변동(average pulse count fluctuation, APCF)을 계산한다. 예를 들어, 프로세서는 가장 최근의 시간 인터벌을 위한 PC와 가장 최근의 시간 인터벌보다 하나 또는 2개 이상의 시간 인터벌 이전에 일어난 시간 인터벌을 위한 PC 사이의 차이의 절대값을 취하거나, 또는 임의의 다른 적절한 기법에 의해 APCF를 계산할 수 있다. 프로세서는 APDF/APC의 비가 제1 특정 임계치를 초과하는지 여부, APDF/APDM의 비가 제2 특정 임계치를 초과하는지 여부, APCF/APC의 비가 제3 특정 임계치를 초과하는지 여부, APDF/APD의 비가 제4 특정 임계치를 초과하는지 여부, APC가 제5 특정 임계치를 초과하는지 여부, 및 APD가 제6 특정 임계치를 초과하는지 여부를 각 시간 인터벌의 마지막에 더 결정한다. 각 시간 인터벌의 마지막에, APDF/APC의 비가 제1 특정 임계치를 초과하고, APDF/APDM의 비가 제2 특정 임계치를 초과하고, APCF/APC의 비가 제3 특정 임계치를 초과하고, APDF/APD의 비가 제4 특정 임계치를 초과하고, APC가 제5 특정 임계치를 초과하고, 그리고 APD가 제6 특정 임계치를 초과한다고 결정된 이벤트에서, 이러한 시간 인터벌은 실제 아크 방전 이벤트가 일어날 수 있는 인터벌이라고 간주된다. 그러므로, 프로세서는 “1”의 출력 또는 임의의 적절한 출력을 생성할 수 있고, 그렇지 않으면, 프로세서는 “0”의 출력 또는 임의의 다른 적

절한 출력을 생성할 수 있다. 프로세서는 복수의 시간 인터벌이 끝날 때까지 생성된 출력들(1 또는 0)을 평균화하고, 각각의 출력들의 평균이 제7 특정 임계치를 초과하면, 실제 아크 방전이 일어났을 것이라고 가정하고, 프로세서는 이러한 아크 방전을 나타내는 다른 출력을 생성한다. 이러한 방식으로, DC 전력 시스템에서, 아크 방전 대 노이즈 잡음을 나타내는 약간의 최소 레벨의 정규화 평균 변동이 존재한다고 가정할 수 있다.

### 발명의 효과

[0012] 복수의 미리 결정된 시간 인터벌 내에, 적어도 미리 결정된 시간 인터벌당 펠스 카운트(PC) 및 미리 결정된 시간 인터벌당 펠스 지속시간(PD)을 결정하고 - 여기서, PC 및 PD는 DC 전력 시스템에서 잠재적 아크 방전 이벤트들의 개수 및 강도에 각각 대응할 수 있음 -, 하나 이상의 아크 고장 검출 알고리즘을 사용하여 PC 및 PD를 프로세싱함으로써, DC 전력 시스템들에서 아크 방전을 검출하는 개시된 시스템 및 방법들은 DC 아크와 부하-스위칭 노이즈(load-switching noise)를 증가된 신뢰도로 구별할 수 있다.

[0013] 본 발명의 다른 특징, 기능, 및 양태들은 다음의 상세한 설명으로부터 명백해질 것이다.

### 도면의 간단한 설명

[0014] 본 명세서의 일부에 통합되어 이를 구성하는 첨부 도면들은 여기에 설명된 하나 이상의 실시예들을 예시하고, 발명의 상세한 설명과 함께 이들 실시예를 설명한다.

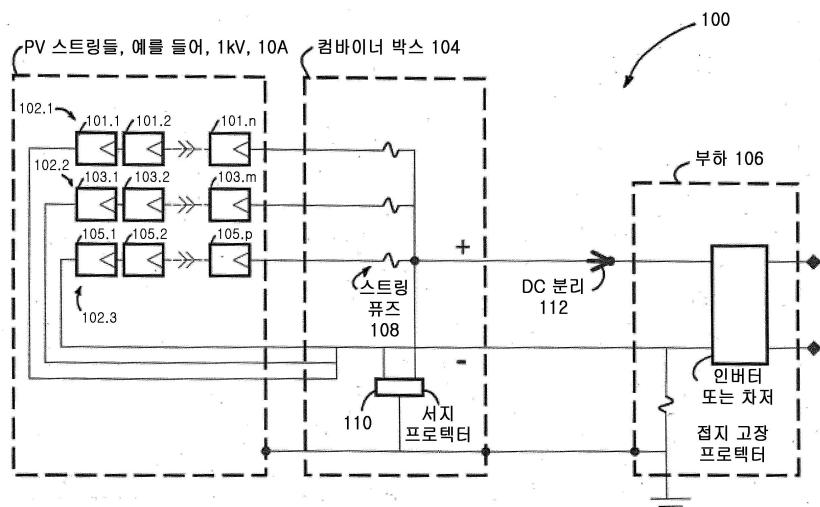

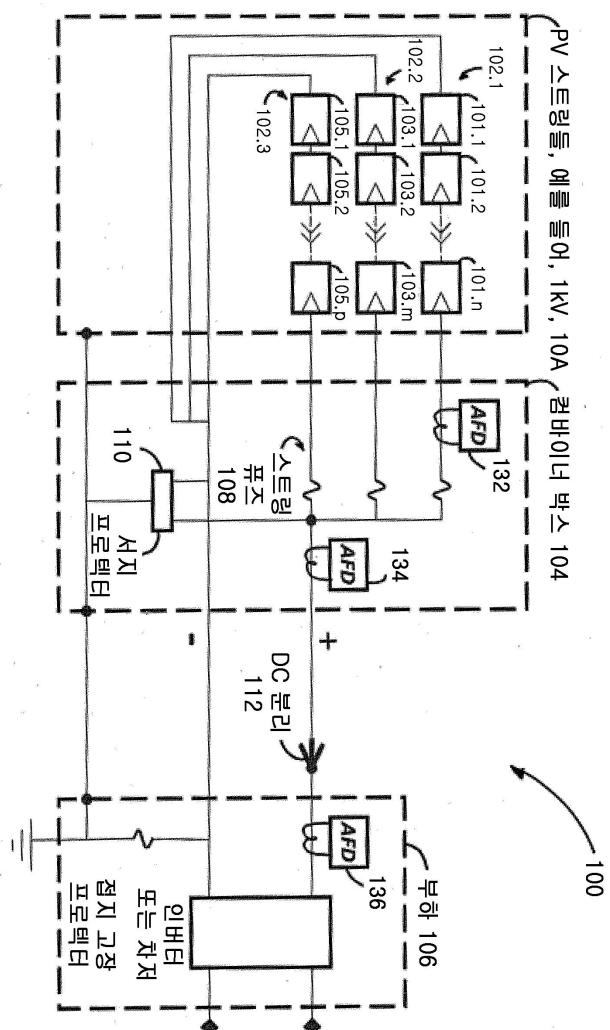

도 1a는 통상의 태양광(PV) 시스템의 블록도를 예시한다.

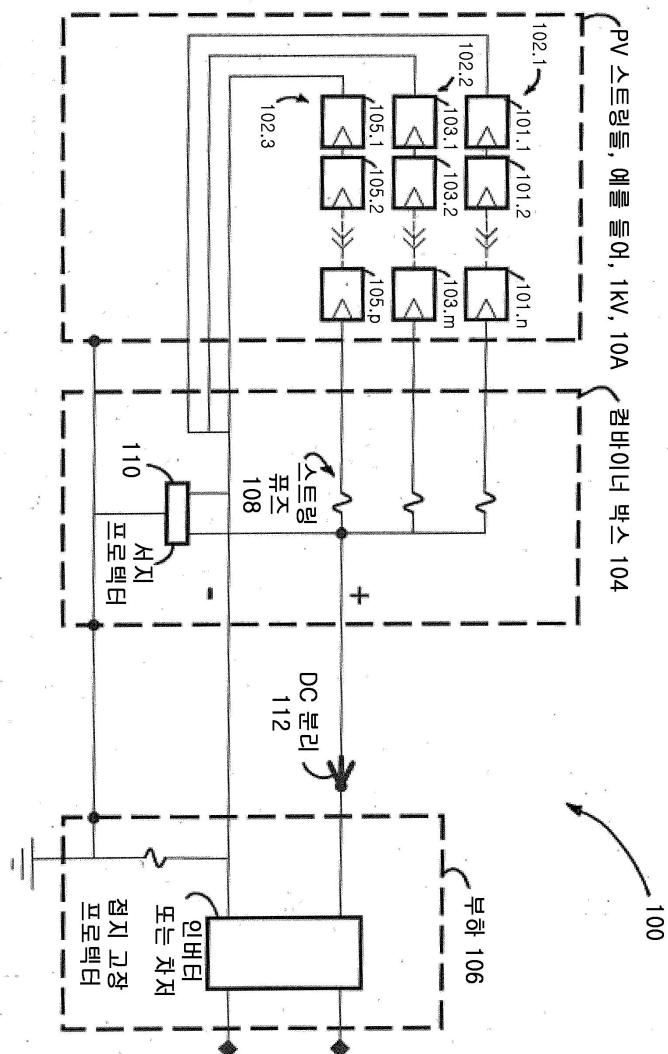

도 1b는 다양한 타입의 아크 방전의 가능한 위치를 더 나타내는 것을 예시한다.

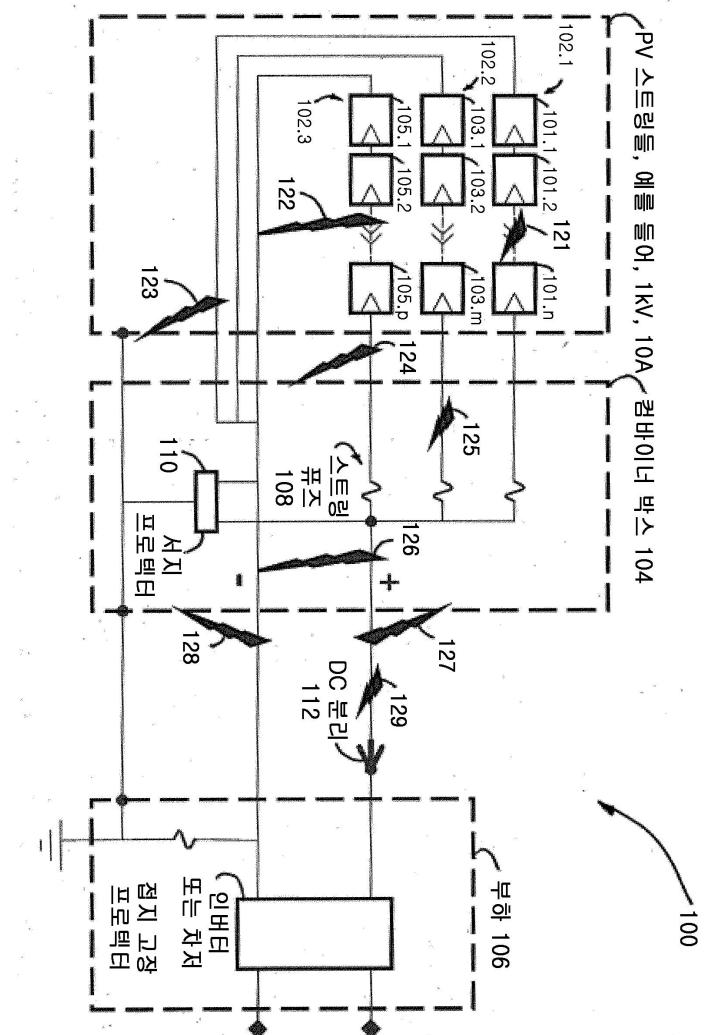

도 1c는 도 1b에 나타낸 다양한 타입의 아크 방전을 검출하는 아크 고장 검출기들의 가능한 지점들을 더 나타내는 도 1a의 PV 시스템을 예시한다.

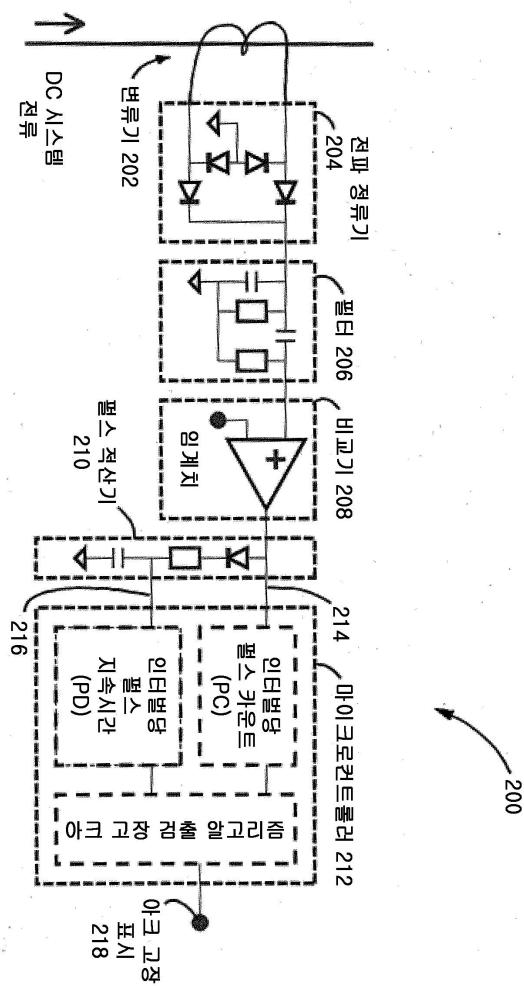

도 2는 본 출원에 따라 DC 전력 시스템에서 아크 방전을 검출하기 위한 예시 시스템의 블록도를 예시한다.

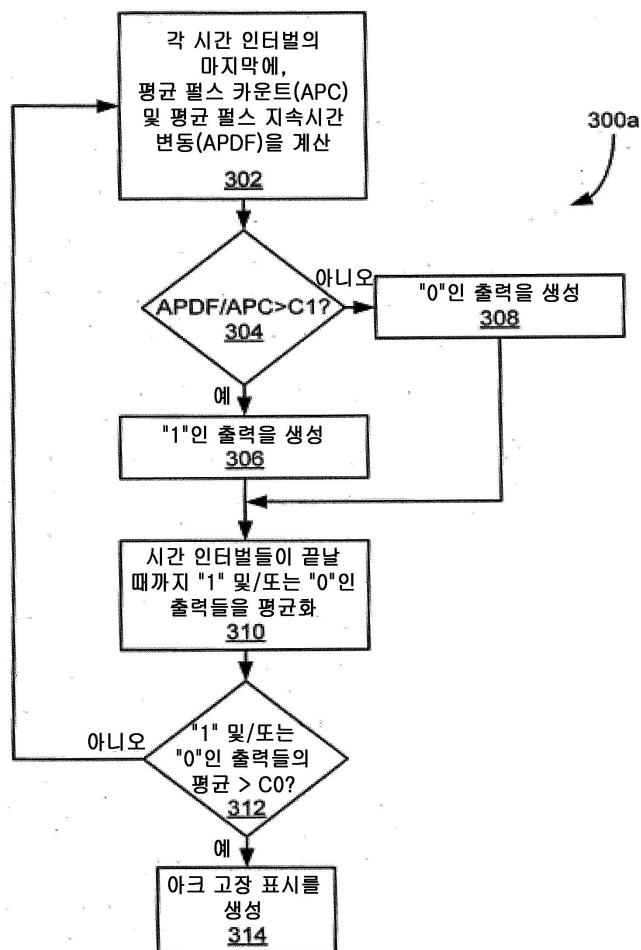

도 3a는 도 2의 시스템을 이용하여 DC 전력 시스템들에서 아크 방전을 검출하는 제1 예시 방법의 흐름도를 예시한다.

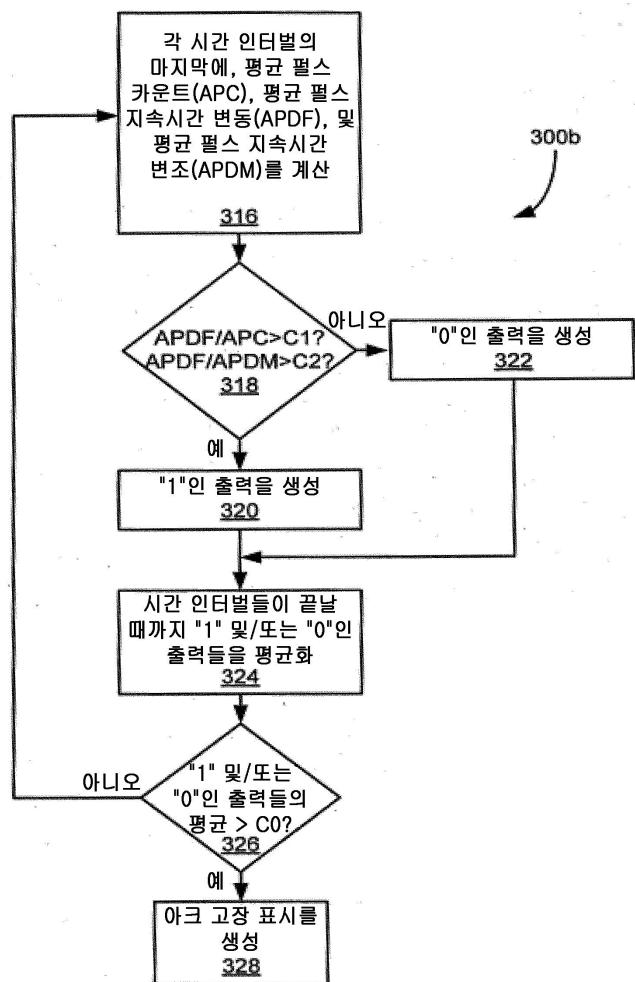

도 3b는 도 2의 시스템을 이용하여 DC 전력 시스템들에서 아크 방전을 검출하는 제2 예시 방법의 흐름도를 예시한다.

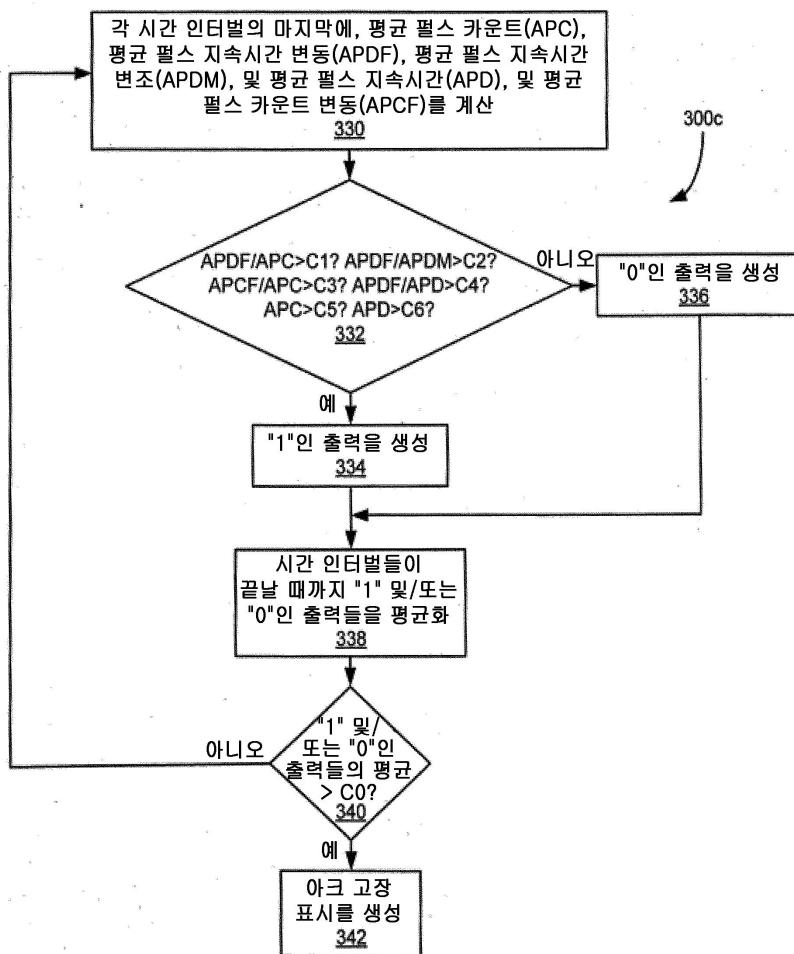

도 3c는 도 2의 시스템을 이용하여 DC 전력 시스템들에서 아크 방전을 검출하는 제3 예시 방법의 흐름도를 예시한다.

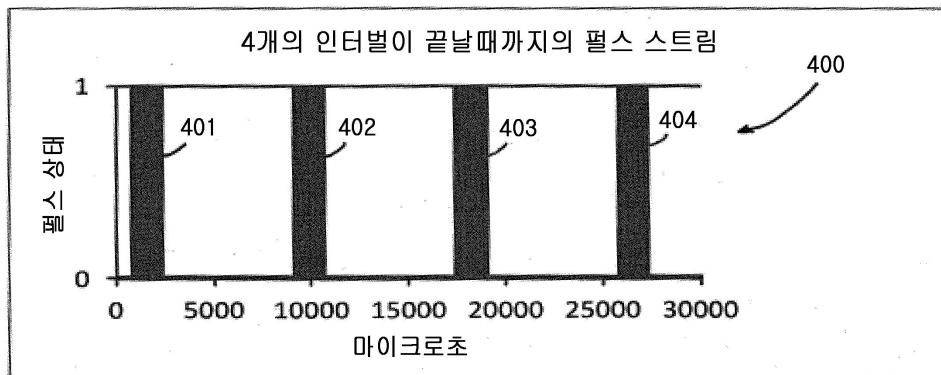

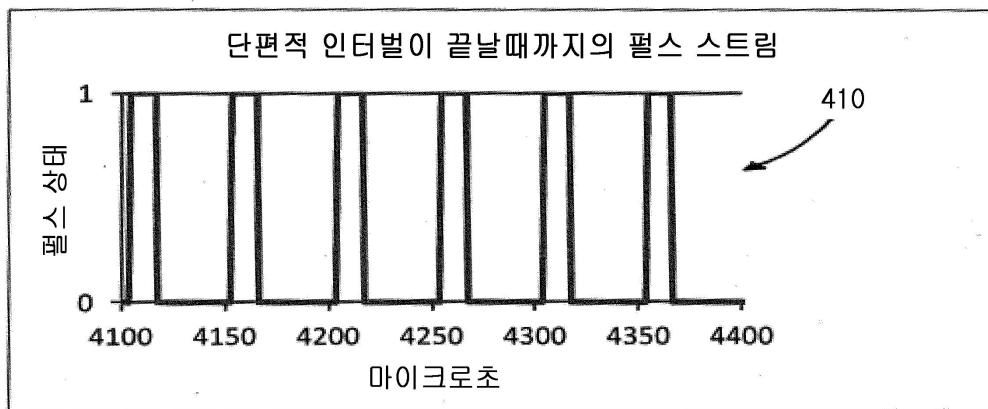

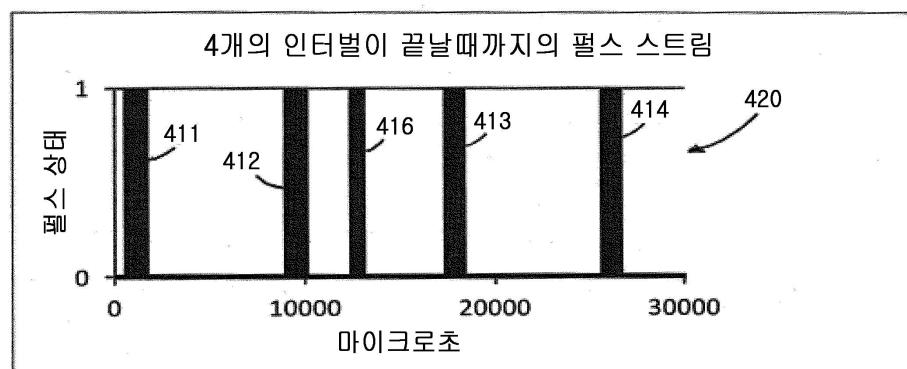

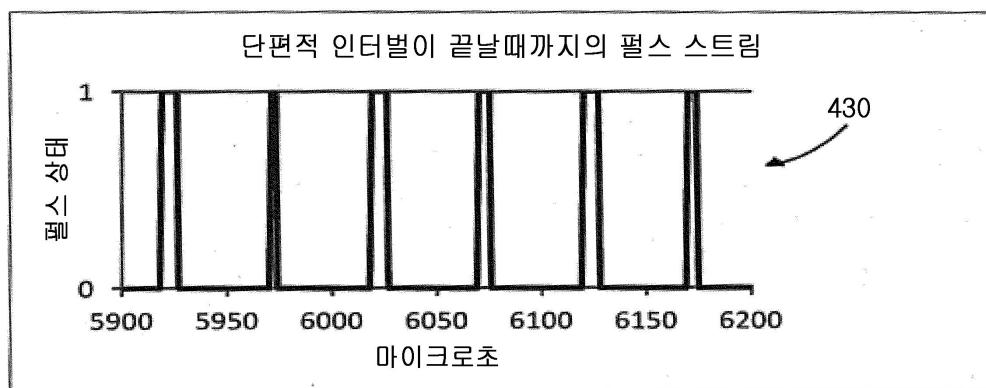

도 4a 내지 도 4d는 도 2의 시스템을 이용하여, 인버터 부하의 시작 동안, 및 연속적인 인버터 노이즈의 존재 시의 아크 방전 동안 생성될 수 있는 예시적인 펠스 스트립 데이터의 도면들을 예시한다.

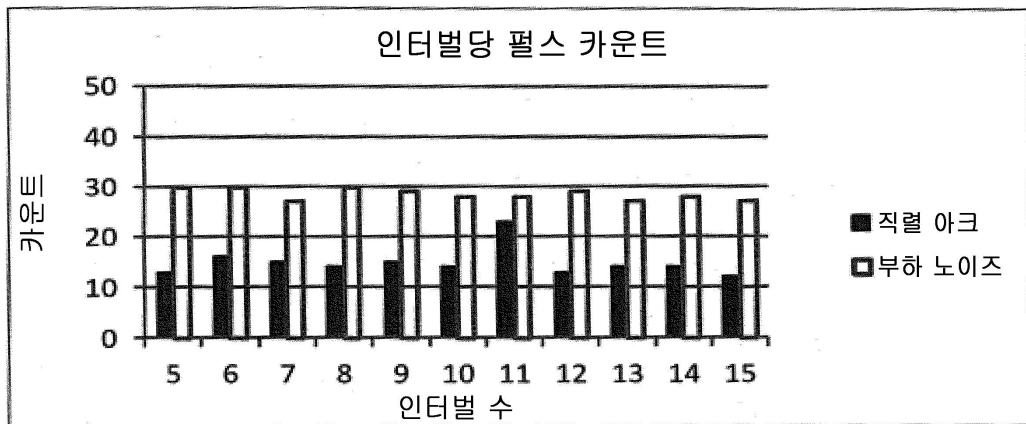

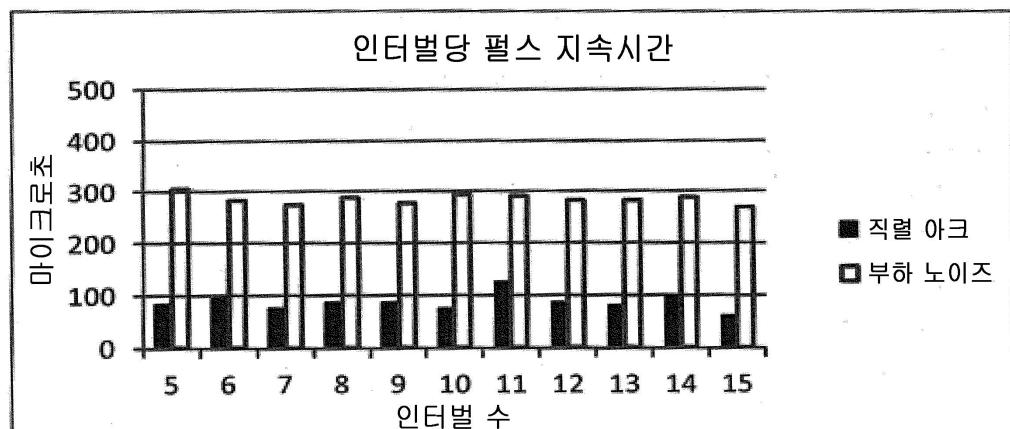

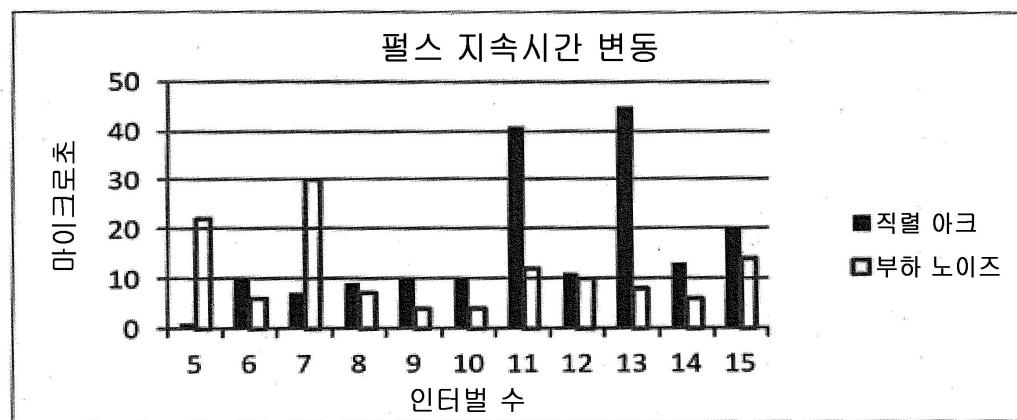

도 5a 내지 도 5c는 도 2의 시스템을 이용하여, 시간 인터벌들의 개수의 함수로서 측정 및 계산될 수 있는 예시적인 변수들의 도면을 예시한다.

도 6a 내지 도 6c는 도 2의 시스템을 이용하여 DC 아크를 부하-스위칭 노이즈와 구분하기 위한 예시적인 기법들의 도면들을 예시한다.

도 7은 본 출원에 따라, DC 전력 시스템들에서 직렬 아크들을 검출하기 위한 예시 시스템의 블록도를 예시한다.

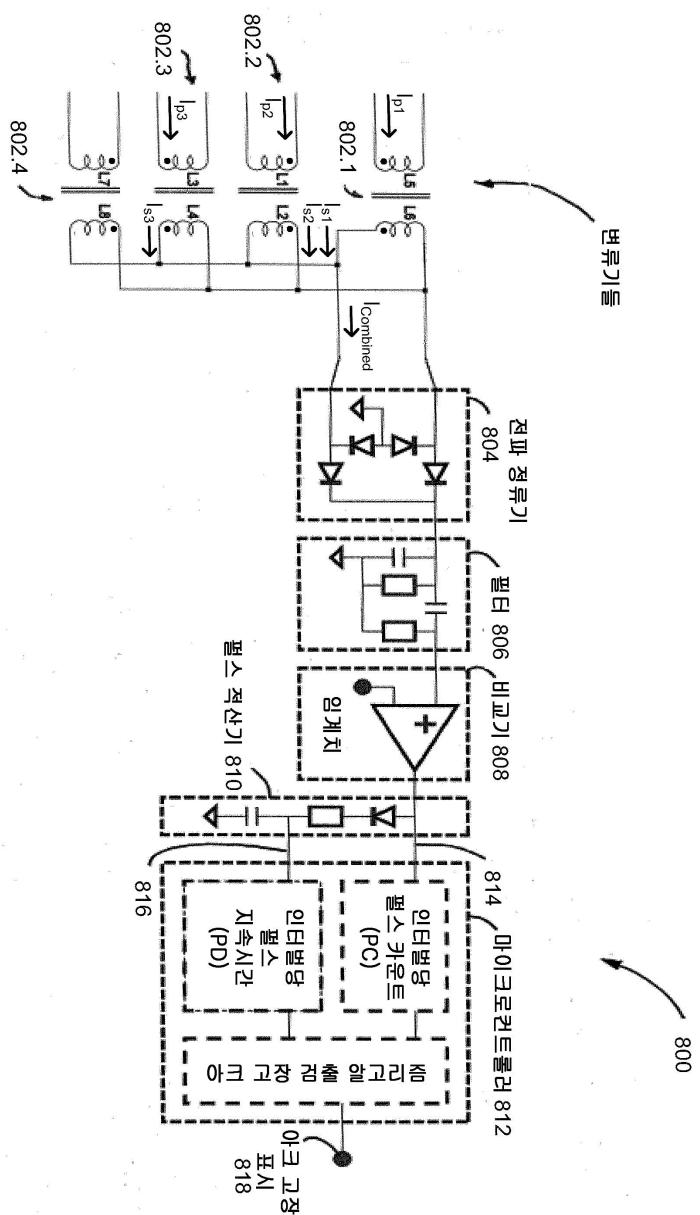

도 8은 도 7의 시스템의 다른 실시예의 블록도를 예시한다.

### 발명을 실시하기 위한 구체적인 내용

[0015] 발명의 명칭이 “HOME RUN ARC DETECTION AT THE PHOTOVOLTAIC STRING LEVEL USING MULTIPLE CURRENT SENSORS”이고, 2013년 3월 15일에 출원된 미국 특허 출원 제13/836,345호 및 발명의 명칭이 “SYSTEMS AND METHODS OF DISCRIMINATING DC ARCS AND LOAD SWITCHING NOISE”이고, 2012년 11월 16일에 출원된 미국 특허 출원 제13/679,039호의 개시는 전체적으로 참조로서 여기에 통합되어 있다.

[0016] 도 1a는 통상 DC 전력 시스템, 특히 태양광(PV) 시스템(100)을 도시한다. 이러한 PV 시스템들이 배터리 충전 내지 AC 그리드에 대한 전력 공급과 같은 가정용 및 산업용 애플리케이션들에서 점차 채택되고 있다. PV 시스템(100)은 복수의 PV 모듈(예를 들어, 태양 전지판)(101.1 내지 101.n, 103.1 내지 103.m, 및 105.1 내지

105.p), 캠바이너 박스(104), 및 부하(106)를 포함한다. 도 1a에 도시된 바와 같이, PV 모듈들(101.1 내지 101.n)은 직렬로 연결되어 제1 PV 스트링(102.1)을 형성하고, PV 모듈들(103.1 내지 103.n)은 직렬로 연결되어 제1 PV 스트링(102.2)을 형성하고, PV 모듈(105.1 내지 105.n)은 직렬로 연결되어 제3 PV 스트링(102.3)을 형성한다. 또한, 제1, 제2, 및 제3 PV 스트링(102.1, 102.2, 및 102.3)은 병렬 연결되고, 캠바이너 박스(104)를 통해 라우팅되어 궁극적으로 부하(106)를 구동할 수 있는데, 이러한 부하는 차저 부하, 인버터 부하, 또는 임의의 다른 적절한 부하일 수 있다. 도 1a에 더 도시된 바와 같이, 캠바이너 박스(104)는 PV 스트링마다 스트링 퓨즈(string fuse, 108)를 포함하고, 서지 프로텍터(surge protector, 110)를 포함할 수 있다. PV 시스템(100)은 또한 DC 분리 스위치(112)를 포함할 수 있다. 다른 방법으로, PV 시스템(100)은 임의의 다른 적절한 개수의 PV 스트링들을 형성하기 위해 직렬 연결되는 임의의 다른 적절한 개수의 PV 모듈들을 포함하도록 구성될 수 있다는 점에 유의한다.

[0017]

도 1b는 아크 방전이 잠재적으로 일어날 수 있는 PV 시스템(100) 내의 예시적인 위치들(121 내지 129)의 개수를 도시한다. 예를 들어, 직렬 아크 방전은 위치들(121, 125, 및 129)에서 잠재적으로 일어날 수 있고, 병렬 아크 방전은 위치들(122 및 126)에서 잠재적으로 일어날 수 있고, 접지 고장 아크 방전은 위치들(123, 124, 127, 및 128)에서 잠재적으로 일어날 수 있다. 더구나, 도 1c는 이러한 잠재적 아크 방전을 검출하기 위해 아크 고장 검출기들(arc fault detector, AFD; 132, 134, 및 136)이 위치할 수 있는 PV 시스템(100) 내에 여러 예시적인 지점들을 도시한다. 예를 들어, AFD(132 및 134)는 PV 스트링들이 결합되는 캠바이너 박스(104) 내에 위치할 수 있고, AFD(136)는 부하(106)에 근접하여 위치할 수 있다. PV 시스템(100) 내의 임의의 다른 적절한 지점들에서 아크 방전을 검출하기 위해 임의의 다른 적절한 개수의 AFD들이 채택될 수 있다는 점에 유의한다.

[0018]

도 2는 본 출원에 따라 DC 전력 시스템에서 아크 방전을 검출하기 위한 예시 시스템(200)을 도시한다. 예를 들어, 시스템(200)은 PV 시스템(100) 내의 AFD(132, 134, 및 136)와 같은 하나 이상의 AFD 내에 구현되어 DC 아크들과 부하-스위칭 노이즈를 증가된 신뢰도로 구별할 수 있다. 도 2에 도시된 바와 같이, 시스템(200)은 전류 센서(202), 정류기(204), 필터(206), 비교기(208), 펄스 적산기(210), 및 프로세서(212)를 포함한다. 전류 센서(202)는 DC 전력 시스템의 전류 출력을 모니터링하기 위한 변류기(current transformer)로서 구현될 수 있다. 예를 들어, 변류기로서 구현된 전류 센서(202)는 양(+)의 DC 전력 라인 또는 음(-)의 DC 전력 라인과 직렬로 연결될 수 있다. 전류 센서(202)는 하나 이상의 중요  $di/dt$  이벤트를 나타내는 고주파 AC 전류 정보를 포함하는 신호를 제공하는데, 이를 이벤트는 하나 이상의 잠재적 아크 방전 이벤트를 나타낼 수 있다. 전파 정류기(full-wave rectifier)로서 구현될 수 있는 정류기(204)는 전류 센서(202)로부터 AC 전류 정보를 포함하는 신호를 수신하고, 고대역 통과 필터링을 위해 신호의 전파 정류된 버전을 필터(206)에 제공한다.

[0019]

비교기(208)는 필터링된 신호를 수신하고, 잠재적 아크 방전 이벤트들에 응답하여 라인(214) 상으로 하나 이상의 펄스를 생성한다. 펄스 적산기(210)는 비교기(208)로부터 펄스들을 수신하고, 라인(216) 상으로 개별적인 펄스들의 지속시간을 나타내는 출력을 생성한다. 마이크로컨트롤러로서 구현될 수 있는 프로세서(212)는 라인(214) 상으로 비교기로부터 펄스들을 수신한다. 프로세서(212)는 잠재적 아크 방전 이벤트들의 개수에 대응할 수 있는 시간 인터벌당 펄스 카운트(PC)를 복수의 소정 시간 인터벌 내에 결정한다. 프로세서는 라인(216) 상에서 펄스 적산기(210)에 의해 생성된 출력을 더 수신하고, 각각의 잠재적 아크 방전 이벤트들의 강도에 대응할 수 있는 미리 결정된 시간 인터벌당 펄스 지속시간(PD)을 각각의 소정 시간 인터벌 내에서 결정한다. 하나 이상의 아크 검출 알고리즘을 이용하여, 여기에 더 설명되는 바와 같이, 프로세서(212)는 DC 아크들과 부하-스위칭 노이즈를 더 잘 구별하기 위해 적어도 PC 및 PD를 프로세싱하고, 경우에 따라 아크 고장 표시(218)를 출력으로서 생성한다.

[0020]

이하, 도 2뿐 아니라 도 3a를 참조하여, DC 전력 시스템들에서 아크 방전을 검출하는 제1 예시 방법(300a)이 설명된다. 방법(300a)을 이용하면, 시스템(200)은 다수의 미리 결정된 시간 인터벌이 끝날 때까지 PD의 변동을 평가할 수 있고, 각각의 시간 인터벌이 끝날 때까지 PD의 변동이 높다고 결정되면, 시스템(200)은 아크 고장 표시(218)를 생성함으로써 실제 아크 방전이 일어날 가능성이 있다고 나타낼 수 있다. 예를 들어, 각각의 미리 결정된 시간 인터벌은 임의의 적절한 시간 인터벌일 수 있다. 일부 실시예에서, 미리 결정된 시간 인터벌은 그리드 종속 인버터 부하들에 의해 생성된 스위칭 노이즈를 감소시킬 뿐 아니라 AC 전력 라인들에 대한 전자기 커플링(electromagnetic coupling)을 최소화하기 위해 AC 그리드 사이클 주기의 약 절반일 수 있다. 단계(302)에 도시된 바와 같이, 프로세서(212)는 2개의 변수, 즉 평균 펄스 카운트(APC) 및 평균 펄스 지속시간 변동(APDF)의 값들을 각 시간 인터벌의 마지막에 계산한다. 예를 들어, 이러한 평균화는 과도한 메모리를 요구하지 않고 변수 값들을 유지하기 위해 1차 저대역 통과 필터를 사용하여 탈성될 수 있다. 소위 스퍼터링 아크들(sputtering arcs)이 연속 아크 방전(continuous arcing)보다 횟수가 더 적지만 세기가 더 클 수 있기 때문에,

이러한 평균화는 더 연속적인 아크 방전뿐 아니라 스퍼터링 아크들이 다른 노이즈 소스들로부터 더 잘 구분될 수 있게 한다는 점에 유의한다. 이러한 평균화의 시간 상수(time constant)는 약 20msec 내지 약 200msec의 범위에 있거나, 임의의 다른 적절한 시간 값 범위에 있을 수 있다.

[0021]

프로세서(212)는 가장 최근의 시간 인터벌을 위한 PD와 가장 최근의 시간 인터벌보다 하나 또는 2개 이상의 시간 인터벌 이전에 일어난 시간 인터벌을 위한 PD 사이의 차이의 절대값을 취하거나, 또는 임의의 다른 적절한 기법에 의해 각각의 미리 결정된 시간 인터벌에서 폴스 지속시간 변동(PDF)을 계산할 수 있다. 단계(304)에 도시된 바와 같이, 프로세서(212)는 APDF/APC의 비가 제1 특정 임계치(C1)를 초과하는지 여부를 각 시간 인터벌의 마지막에 결정한다. APDF/APC의 비가 각 시간 인터벌의 마지막에 제1 특정 임계치(C1)를 초과하는 이벤트에서, 시간 인터벌은 실제 아크 방전 이벤트가 일어날 수 있는 인터벌로 간주된다. 예를 들어, 프로세서(212)가 APDF/APC의 비가 개별 시간 인터벌 중에 제1 특정 임계치(C1)를 초과한다고 결정하면, 단계(306)에 도시된 바와 같이, “1”의 출력 또는 임의의 다른 적절한 출력을 생성할 수 있다. 그렇지 않으면, 단계(308)에 도시된 바와 같이, 프로세서(212)는 “0”의 출력 또는 임의의 다른 적절한 출력을 생성할 수 있다. 단계(310)에 도시된 바와 같이, 프로세서(212)는 복수의 미리 결정된 시간 인터벌이 끝날 때까지 생성된 출력들(1 및/또는 0)을 평균화한다. 예를 들어, 이러한 평균화는 다수의 시간 인터벌이 끝날 때까지 저대역 통화 필터, 누적 합계(running sum), 또는 이벤트 카운터를 이용하여 수행되거나, 임의의 다른 적절한 기법을 이용하여 수행될 수 있다. 또한, 이러한 평균화의 시간 상수는 0.1sec 내지 1.0sec의 범위에 있을 수 있으며, 이는 임의의 가능한 아크 고장 표시들이 합리적인 시간 내에 일어나게 할 수 있다. 단계(312)에 도시된 바와 같이, 프로세서(212)는 각각의 출력들의 평균이 특정 임계 출력 값(C0)을 초과하는지 여부를 결정한다. 각각의 출력들의 평균이 특정 임계 출력 값(C0)을 초과하면, 실제 아크 방전이 일어났을 것이라고 가정하고, 단계(314)에 도시된 바와 같이 프로세서(212)는 아크 고장 표시(218)를 생성한다. 그렇지 않으면, 방법(300)은 단계(302)로 복귀한다.

[0022]

이하, 도 2뿐 아니라 도 3b를 참조하여, DC 전력 시스템들에서 아크 방전을 검출하는 제2 예시 방법(300b)이 설명된다. 이 방법(300b)을 이용하면, 시스템(200)은 실제 아크 방전과 그리드 종속 인버터 부하들과 같은 매우 노이즈가 많은 부하들을 더 신뢰 가능하게 구별할 수 있다. 단계(316)에 도시된 바와 같이, 프로세서(212)는 각 미리 결정된 시간 인터벌의 마지막에 3개의 변수, 즉 APC, APDF, 및 평균 폴스 지속시간 변조(APDM)의 값들을 계산한다. 예를 들어, 프로세서(212)는 시간 인터벌의 1/4만큼 이격된 각각의 미리 결정된 시간 인터벌 동안 4개의 PD 측정(PD1, PD2, PD3, 및 PD4)을 취하고, 각 시간 인터벌의 마지막에 다음과 같이 APDM을 계산함으로써 APDM을 계산할 수 있는데,

[0023]

$$APDM = | APD1 + APD2 - APD3 - APD4 | + | APD1 - APD2 - APD3 + APD4 | \quad (1)$$

[0024]

여기서, 복수의 시간 인터벌이 끝날 때까지, 또는 임의 다른 적절한 기법에 의해, “APD1”은 각 “PD1” 측정들의 평균이고, “APD2”는 각 “PD2” 측정들의 평균이고, “APD3”는 각 “PD3” 측정들의 평균이고, “APD4”는 각 “PD4” 측정들의 평균이다. 예를 들어, 각 1/4 인터벌 측정의 이러한 평균화는 다수의 시간 인터벌이 끝날 때까지 저대역 통과 필터를 사용하여 수행될 수 있다. 또한, 각 시간 인터벌은 AC 그리드 사이클 주기, 예를 들어, 60Hz 또는 50Hz AC 그리드들의 경우 1/(2\*55Hz)에 있거나, 그 근처에 있을 수 있다. 단계(318)에 도시된 바와 같이, 프로세서(212)는 APDF/APC의 비가 제1 특정 임계치(C1)를 초과하는지 여부 및 APDF/APDM의 비가 제2 특정 임계치(C2)를 초과하는지 여부를 각 시간 인터벌의 마지막에 결정한다. APDF/APC의 비가 제1 특정 임계치(C1)를 초과하고, APDF/APDM의 비가 제2 특정 임계치(C2)를 초과한다고 각 시간 인터벌의 마지막에 결정된 이벤트에서, 이러한 시간 인터벌은 실제 아크 방전 이벤트가 일어났을 수 있는 인터벌이라고 간주된다. 예를 들어, 각 시간 인터벌 중에 프로세서(212)가 APDF/APC의 비가 제1 특정 임계치(C1)를 초과하고, APDF/APDM의 비가 제2 특정 임계치(C2)를 초과한다고 결정하면, 단계(320)에 도시된 바와 같이, “1”의 출력 또는 임의의 다른 적절한 출력을 생성할 수 있다. 그렇지 않으면, 단계(322)에 도시된 바와 같이, 프로세서(212)는 “0”의 출력 또는 임의의 다른 적절한 출력을 생성할 수 있다. 단계(324)에 도시된 바와 같이, 프로세서(212)는 복수의 시간 인터벌이 끝날 때까지 생성된 출력들(1 및/또는 0)을 평균화한다. 단계(326)에 도시된 바와 같이, 프로세서(212)는 각각의 출력들의 평균이 특정 임계 출력 값(C0)을 초과하는지 여부를 결정한다. 각각 출력들의 평균이 특정 임계 출력 값(C0)을 초과하면, 실제 아크 방전이 일어났을 것이라고 가정하고, 단계(328)에 도시된 바와 같이 프로세서(212)는 아크 고장 표시(218)를 생성한다. 그렇지 않으면, 방법(300b)은 단계(316)로 복귀한다.

[0025]

이하, 도 2뿐 아니라 도 3c를 참조하여, DC 전력 시스템들에서 아크 방전을 검출하는 제3 예시 방법(300c)이 설명된다. 방법(300c)은 DC 전력 시스템에서 아크 방전 대 부하 노이즈를 나타내는 약간의 최소 레벨의 정규화 평균 변동이 존재한다고 확신하는 방식을 제공한다. 단계(330)에 도시된 바와 같이, 프로세서(212)는 각 미리

결정된 시간 인터벌의 마지막에 5개의 변수, 즉 APC, APDF, APDM, 평균 펄스 지속시간(APD), 및 평균 펄스 카운트 변동(APCF)을 계산한다. 예를 들어, 프로세서(212)는 가장 최근의 시간 인터벌을 위한 PC와 가장 최근의 시간 인터벌보다 하나 또는 2개 이상의 시간 인터벌 이전에 일어난 시간 인터벌을 위한 PC 사이의 차이의 절대값을 취하거나, 또는 임의의 다른 적절한 기법에 의해 APCF를 계산할 수 있다. 단계(332)에 도시된 바와 같이, 프로세서(212)는 APDF/APC의 비가 제1 특정 임계치(C1)를 초과하는지 여부, APDF/APDM의 비가 제2 특정 임계치(C2)를 초과하는지 여부, APCF/APC의 비가 제3 특정 임계치(C3)를 초과하는지 여부, APDF/APD의 비가 제4 특정 임계치(C4)를 초과하는지 여부, APC가 제5 특정 임계치(C5)를 초과하는지 여부, 및 APD가 제6 특정 임계치(C6)를 초과하는지 여부를 각 시간 인터벌의 마지막에 결정한다. 각 시간 인터벌의 마지막에 APDF/APC의 비가 제1 특정 임계치(C1)를 초과하고, APDF/APDM의 비가 제2 특정 임계치(C2)를 초과하고, APCF/APC의 비가 제3 특정 임계치(C3)를 초과하고, APDF/APD의 비가 제4 특정 임계치(C4)를 초과하고, APC가 제5 특정 임계치(C5)를 초과하고, 그리고 APD가 제6 특정 임계치(C6)를 초과한다고 결정된 이벤트에서, 이러한 시간 인터벌은 실제 아크 방전 이벤트가 일어났을 수 있는 인터벌이라고 간주된다. 그러므로, 단계(334)에 도시된 바와 같이, 프로세서(212)는 “1”의 출력 또는 임의의 다른 적절한 출력을 생성한다. 그렇지 않으면, 단계(336)에 도시된 바와 같이, 프로세서(212)는 “0”의 출력 또는 임의의 다른 적절한 출력을 생성한다. 단계(338)에 도시된 바와 같이, 프로세서(212)는 복수의 시간 인터벌이 끝날 때까지 생성된 출력들(1 및/또는 0)을 평균화한다. 단계(340)에 도시된 바와 같이, 프로세서(212)는 각각의 출력들의 평균이 특정 임계 출력 값(C0)을 초과하는지 여부를 결정한다. 각각의 출력들의 평균이 특정 임계 출력 값(C0)을 초과하면, 실제 아크 방전이 일어났을 것이라고 가정하고, 단계(342)에 도시된 바와 같이 프로세서(212)는 아크 고장 표시(218)를 생성한다. 그렇지 않으면, 방법(300c)은 단계(330)로 복귀한다.

[0026]

이하, DC 전력 시스템들에서 아크 방전을 검출하는 개시된 시스템 및 방법들은 다음의 예시 및 도 1, 도 2, 도 3a, 도 3b, 도 4a 내지 도 4d, 도 5a 내지 도 5c, 및 도 6a 내지 도 6c를 참조하여 더 설명된다. 제1 예시에서, 직렬 아크 방전은 DC 전력 시스템에서 펄스 지속시간 변동(PDF)과 펄스 지속시간 변조(PDM) 모두의 원인일 수 있다는 점이 입증된다. 도 4a는 인버터 부하일 수 있는 부하(106)의 시작 중에 라인(214) 상에 비교기(208)에 의해 생성된 예시적인 펄스 스트림(400)을 예시한다. 이러한 제1 예시에서, 이러한 인버터 부하는 약 60Hz와 동일한 주파수를 가질 수 있는 AC 그리드에 종속될 수 있다. 도 4a에 도시된 바와 같이, 펄스 스트림(400)은 인버터 부하의 시작 중에 생성된 부하-스위칭 노이즈를 일반적으로 나타내는 일련의 펄스 버스트(pulse bursts; 401, 402, 403, 및 404)를 포함한다. 각각의 펄스 버스트(401, 402, 403, 및 404)는  $1/(2*60\text{Hz})$  또는 약  $8,333\mu\text{sec}$ 의 미리 결정된 시간 인터벌 내에 일어난다. 도 4b는 펄스 버스트들(401, 402, 403, 및 404) 중 하나에 포함될 수 있는 일련의 예시적인 펄스들(410)을 예시한다. 도 4b에 도시된 바와 같이, 각 펄스들(410)의 주기와 지속시간들은 일관적으로 균일하다.

[0027]

도 4c는 연속적인 인버터 부하 노이즈의 존재 시의 직렬 아크 방전 동안 라인(214) 상에 비교기(208)에 의해 생성된 예시적인 펄스 스트림(420)을 예시한다. 도 4c에 도시된 바와 같이, 펄스 스트림(420)은 각각이 약  $8,333\mu\text{sec}$ 의 미리 결정된 시간 인터벌 내에 일어나는 일련의 펄스 버스트(411, 412, 413, 및 414)를 포함한다. 도 4c에 더 도시된 바와 같이, 직렬 아크 방전은 여분의 펄스 버스트(416)이 펄스 버스트들(412 및 413) 사이에 도입되게 하였다. 직렬 아크 방전에 의해 일어나는 여분의 펄스 버스트(416)는 부하 스위칭 노이즈로부터 초래되는 주기적 펄스 버스트들(411, 412, 413, 및 414)과 동기화되지 않는다는 점에 유의한다. 직렬 아크 방전이 펄스 버스트들(412 및 413) 사이의 여분의 펄스 버스트(416)를 도입하였기 때문에, 이러한 직렬 아크 방전은 펄스 스트림(420) 내의 시간 인터벌마다 약간의 PDF를 야기하였다.

[0028]

도 4d는 펄스 버스트들(411, 412, 413, 및 414) 중 하나에 포함될 수 있는 일련의 예시적인 펄스들(430)을 예시한다. 직렬 아크 방전 중에 생성된 일련의 펄스들(430)은 인버터 부하의 시작 중에 생성된 일련의 펄스들(410)과 비교함으로써, 직렬 아크 방전이 또한 일련의 펄스들(430) 내에 약간의 PDM을 야기하였다는 점이 관찰될 수 있다. 각 펄스들(430)의 폭들이 일반적으로 펄스들(410)의 폭보다 좁으며, 이는 인버터 부하의 시작 중에 생성된 펄스들(410)이 연속 인버터 부하 노이즈의 존재 시의 직렬 아크 방전 중에 생성된 펄스들(430)보다 세기가 강하다고 나타낸다는 점에 유의한다. 그럼에도 불구하고, 아크 방전의 일반적인 무작위성(randomness)이 더 균일한 부하-스위칭 노이즈보다 더 큰 PDF 및/또는 PDM을 생성할 수 있다는 점이 관찰될 수 있다.

[0029]

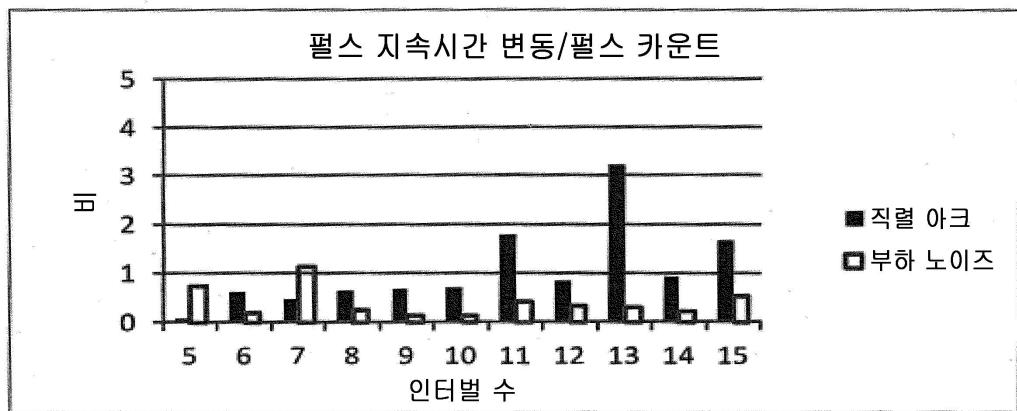

제2 예시에서, 시간 인터벌당 펄스 카운트(PC)와 시간 인터벌당 펄스 지속시간(PD) 모두가 연속 인버터 노이즈의 존재 시의 직렬 아크 방전 중에서보다 인버터 부하의 시작 중에 더 클 수 있고, 이에 따라 측정된 시간 인터벌당 PC 및/또는 PD가 DC 아크들과 부하 스위칭 노이즈를 신뢰 가능하게 구분하기에 불충분할 수 있다는 점이 입증된다. 도 5a는 5 내지 15로 번호가 매겨진 복수의 예시적인 시간 인터벌을 위해 프로세서(212)에 의해 측

정된 펄스 카운트들을 예시한다. 도 5a에 도시된 바와 같이, 일반적으로, 인버터 부하의 시작 중에 측정된 시간 인터벌당 PC는 약 20 내지 30 카운트들의 범위 내에 있고, 반면에 일반적으로 직렬 아크 방전 동안 측정된 시간 인터벌당 PC가 시간 인터벌 11을 제외하고 약 10 내지 20 카운트들의 범위 내에 있으며, 여기서 측정된 직렬 아크 방전 중의 PC는 20 카운트와 30 카운트 사이에 있다. 도 5b는 5 내지 15로 번호가 매겨진 예시적인 시간 인터벌을 위해 프로세서(212)에 의해 측정된 펄스 지속시간들을 예시한다. 도 5b에 도시된 바와 같이, 일반적으로, 인버터 부하의 시작 중에 측정된 시간 인터벌당 PD는 약 200 내지 300  $\mu$ sec의 범위 내에 있고, 반면에 일반적으로 직렬 아크 방전 동안 측정된 시간 인터벌당 PD가 시간 인터벌 11을 제외하고 약 0 내지 100  $\mu$ sec의 범위 내에 있으며, 여기서 측정된 직렬 아크 방전 중의 PD는 100  $\mu$ sec와 200  $\mu$ sec 사이에 있다.

[0030] 도 5c는 5 내지 15로 번호가 매겨진 예시적인 시간 인터벌을 위해 프로세서(212)에 의해 계산된 펄스 지속시간 변동(PDF)을 예시한다. 제1 예시 방법(300a)에 대해 여기에 설명된 바와 같이, 프로세서(212)는 가장 최근의 시간 인터벌을 위한 PD와 가장 최근의 시간 인터벌보다 하나 또는 2개 이상의 시간 인터벌 이전에 일어난 시간 인터벌을 위한 PD 사이의 차이의 절대값을 취함으로써 각각의 미리 결정된 시간 인터벌의 마지막에 PDF를 계산할 수 있다. 도 5c에 도시된 바와 같이, 일반적으로, 계산된 인버터 부하의 시작 중의 PDF는 0 내지 10  $\mu$ sec의 범위 내에 있는데, 각각 계산된 PDF가 20  $\mu$ sec 이상이고, 약 30  $\mu$ sec이고, 약 10  $\mu$ sec 이상이고, 10  $\mu$ sec와 20  $\mu$ sec 사이에 있는 시간 인터벌들 5, 7, 11, 및 15를 제외한다. 도 5c에 도시된 바와 같이, 일반적으로, 계산된 직렬 아크 방전 중의 PDF는 0 내지 10  $\mu$ sec의 범위 내에 있는데, 각각 계산된 PDF가 약 40  $\mu$ sec 이상이고, 40  $\mu$ sec와 50  $\mu$ sec 사이에 있고, 10  $\mu$ sec와 20  $\mu$ sec 사이에 있고, 약 20  $\mu$ sec인 시간 인터벌들 11, 13, 14, 및 15를 제외한다. 따라서, 도 5c에 예시되어 있는 계산된 PDF들에 기초하여, 계산된 시간 인터벌당 PDF의 분석이 또한 DC 아크들과 부하 스위칭 노이즈를 신뢰 가능하게 구분하기에 불충분할 수 있다.

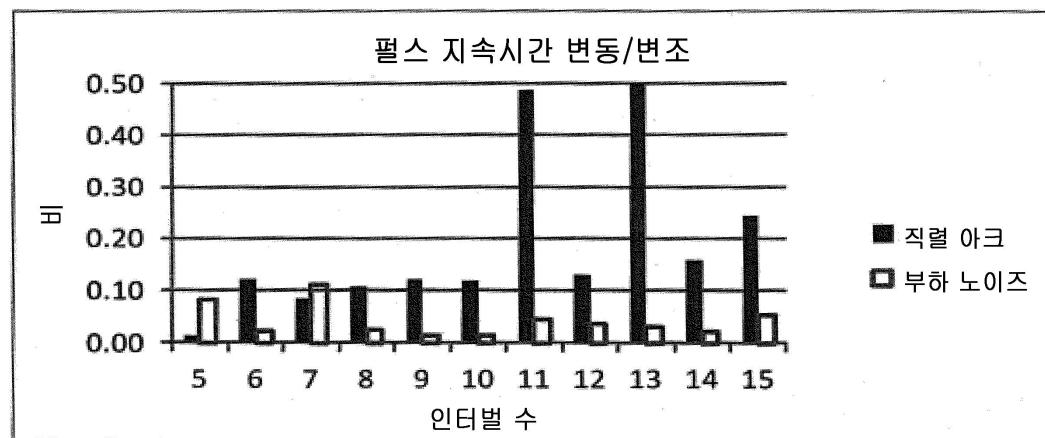

[0031] 제3 예시에서, 각 시간 인터벌의 마지막에 적어도 PDF/PC의 비의 분석이 DC 아크들과 부하 스위칭 노이즈를 신뢰 가능하게 구분하기에 충분할 것이라는 점이 입증된다. 도 6a는 프로세서(212)에 의해 결정되는 바와 같이, 5 내지 15로 번호가 매겨진 예시적인 시간 인터벌의 마지막에 PDF/PC의 비를 예시한다. 도 6a에 도시된 바와 같이, 일반적으로, 직렬 아크 방전 중에 결정된 PDF/PC의 비는 인버터 부하의 시작 중에 결정된 대응하는 PDF/PC의 비(예를 들어, 시간 인터벌들 6 및 8 내지 15를 위한 각각의 PDF/PC의 비 참조)보다 상당히 크다. (제1 예시 방법(300a)의 단계(304)를 참조하여 여기에 설명된 바와 같이) APDF/APC의 비가 각각의 번호가 매겨진 시간 인터벌의 마지막에 결정되었으면, 직렬 아크 방전 중에 결정된 이러한 APDF/APC의 비들은 인버터 부하의 시작 중에 결정된 대응하는 APDF/APC의 비들보다 상당히 더 클 것이라는 점에 유의한다. 더구나, 프로세서(212)가 각 번호가 매겨진 시간 인터벌의 마지막에 APDF 및 APC를 먼저 계산했고, 각각의 번호가 매겨진 시간 인터벌마다 APDF/APC의 비들을 결정했으면, 마찬가지로, 직렬 아크 방전 중에 결정된 이러한 APDF/APC의 비들은 인버터 부하의 시작 중에 결정된 대응하는 APDF/APC의 비들보다 상당히 클 것이다. 따라서, 도 6a에 예시된 PDF/PC의 비들에 기초하여, 각 시간 인터벌의 마지막에 적어도 PDF/PC의 비를 분석하는 것은 증가된 신뢰도로 DC 아크들과 부하-스위칭 노이즈를 구분하기에 충분할 것이라고 결론 내릴 수 있다.

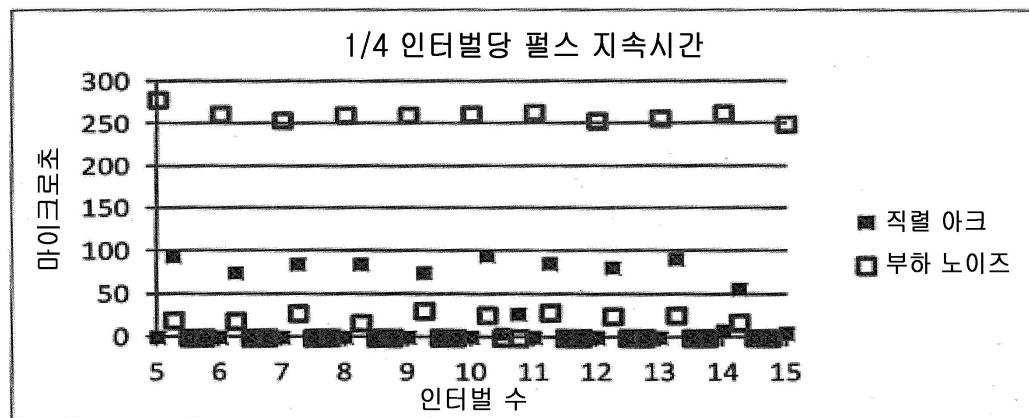

[0032] 제3 예시에서, 각 시간 인터벌의 마지막에 적어도 PDF/PDM의 비의 분석이 DC 아크들과 매우 노이즈가 많은 부하들을 신뢰 가능하게 구분하기에 충분할 것이라는 점이 더 입증된다. 도 6b는 프로세서(212)에 의해 측정된 바와 같이, 5 내지 15로 번호가 매겨진 예시적인 시간 인터벌을 위해 1/4 시간 인터벌당 PD를 예시한다. 도 6b에 도시된 바와 같이, 시간 인터벌당 PD의 대다수는 각 시간 인터벌의 일부 내에 일어난다. 예를 들어, 번호가 매겨진 시간 인터벌들의 각각의 경우, 약 250  $\mu$ sec 내지 300  $\mu$ sec 범위에 있는 PD의 대부분은 각 인터벌의 시작 근처의 시간 인터벌의 일부 내에 일어난다. 도 6b에 예시된, 측정된 1/4 시간 인터벌당 PD에 기초하여, 이러한 제3 예시에서, 그리드 주파수의 약 2배, 예를 들어  $2 \times 60\text{Hz}$  또는  $120\text{Hz}$ 에서 상당한 펄스 지속시간 변조(PDM)일 수 있다고 결론 내릴 수 있다.

[0033] 도 6c는 5 내지 15로 번호가 매겨진 예시적인 시간 인터벌을 위해 프로세서(212)에 의해 결정된 PDF/PDM의 비를 예시한다. 제2 예시 방법(300b)에 대해 여기에 설명된 바와 같이, APDM의 계산과 마찬가지로, PDM은 시간 인터벌의 1/4만큼 이격된 각각 번호가 매겨진 시간 인터벌 동안 4개의 PD 측정(PD1, PD2, PD3, 및 PD4)을 취하고, 각 시간 인터벌의 마지막에 다음과 같이 PDM을 계산함으로써 또는 임의의 다른 적절한 기법으로써 PDM을 계산할 수 있다.

$$\text{PDM} = | \text{PD1} + \text{PD2} - \text{PD3} - \text{PD4} | + | \text{PD1} - \text{PD2} - \text{PD3} + \text{PD4} | \quad (2)$$

[0035] 도 6c에 도시된 바와 같이, 일반적으로, 직렬 아크 방전 중에 결정된 PDF/PDM의 비는 인버터 부하의 시작 중에 결정된 대응하는 PDF/PDM의 비(예를 들어, 시간 인터벌들 6 및 8 내지 15를 위한 각각의 PDF/PDM의 비들을

참조)보다 상당히 크다. (제2 예시 방법(300b)의 단계(318)를 참조하여 여기에 설명된 바와 같이) APDF/APDM의 비가 각각의 번호가 매겨진 시간 인터벌의 마지막에 결정되었으면, 직렬 아크 방전 중에 결정된 이러한 APDF/APDM의 비들은 인버터 부하의 시작 중에 결정된 대응하는 APDF/APDM의 비들보다 상당히 더 클 것이라는 점에 유의한다. 더구나, 프로세서(212)가 각 번호가 매겨진 시간 인터벌의 마지막에 APDF 및 APDM를 먼저 계산했고, 각각의 번호가 매겨진 시간 인터벌마다 APDF/APDM의 비들을 결정했으면, 마찬가지로, 직렬 아크 방전 중에 결정된 이러한 APDF/APDM의 비들은 인버터 부하의 시작 중에 결정된 대응하는 APDF/APDM의 비들보다 상당히 클 것이다. 따라서, 도 6c에 예시된 PDF/PDM의 비들에 기초하여, 각 시간 인터벌의 마지막에 적어도 PDF/PDM의 비를 분석하는 것은 증가된 신뢰도로 DC 아크들과 부하-스위칭 노이즈를 구분하기에 충분할 것이라고 결론 내릴 수 있다.

[0036] DC 전력 시스템들에서 아크 방전을 검출하는 개시된 시스템들 및 방법들의 전술된 예시적인 실시예들을 설명하면, 다른 대체적인 실시예들 또는 변형예들이 행해질 수 있다. 예를 들어, 프로세서(212)는 APDF/APC의 비가 제1 특정 임계치(C1)를 초과하는지 여부, APDF/APDM의 비가 제2 특정 임계치(C2)를 초과하는지 여부, APCF/APC의 비가 제3 특정 임계치(C3)를 초과하는지 여부, APDF/APD의 비가 제4 특정 임계치(C4)를 초과하는지 여부, APC가 제5 특정 임계치(C5)를 초과하는지 여부, 및/또는 APD가 제6 특정 임계치(C6)를 초과하는지 여부를 각 시간 인터벌의 마지막에 결정할 수 있다는 점이 제3 예시 방법(300c)를 참조하여 여기에 설명되었다. 일부 실시예에서, 다른 방법으로, DC 전력 시스템들에서의 아크 방전의 검출은 PDF/PC의 비가 제1 특정 임계치(C1)를 초과하는지 여부, PDF/PDM의 비가 제2 특정 임계치(C2)를 초과하는지 여부, PCF/PC의 비가 제3 특정 임계치(C3)를 초과하는지 여부, PDF/PD의 비가 제4 특정 임계치(C4)를 초과하는지 여부, PC가 제5 특정 임계치(C5)를 초과하는지 여부, 및/또는 PD가 제6 특정 임계치(C6)를 초과하는지 여부를 각 시간 인터벌의 마지막에 결정하는 것에 기초할 수 있다.

[0037] 전류 센서(202)는 DC 전력 시스템의 전류 출력을 모니터링하기 위한 변류기로서 구현될 수 있다는 점 또한 설명되었다. 일부 실시예에서, 전류 센서(220)는 적절한 회로망을 갖는 AC 검출 변류기 역할을 할 수 있는 DC 전류 센서를 사용하여 구현될 수 있다. DC 전류 센서에 의해 제공되는 DC 전류 데이터가 고주파수 AC 전류 정보를 중대시켜 전력 시스템 노이즈에 비해 아크 고장 검출을 개선할 수 있다는 점에 유의한다. 더구나, 일부 실시예에서, DC 전력 시스템에서 아크 방전을 검출하기 위한 전류 출력을 대신하여 DC 전력 시스템의 전압 출력이 모니터링될 수 있다. 이러한 실시예들은 직렬 아크 방전과 병렬 아크 방전을 더 잘 구분하기 위해, 전력 시스템 전류 데이터뿐 아니라 전력 시스템 전압 데이터를 채택할 수 있다. 또한, 일부 실시예에서, 전류 센서(202)는 DC 전압 라인들의 양단에 연결될 수 있는 AC 전압 센서와 대체될 수 있다. 이러한 AC 전압 센서는 DC 전력 시스템과 하나 이상의 AFD 사이의 전기적 이격을 제공하기 위한 커패시터 결합 변류기로서 구현될 수 있다.

[0038] 또한, PV 시스템(100)은 일단 이러한 아크 방전이 검출되었으면 아크 방전을 소멸시키기 위해 채택될 수 있는 DC 분리 스위치(112)를 포함할 수 있다는 점이 여기에 설명되었다. 일부 실시예에서, 이러한 아크 방전을 소멸시키기 위해, PV 시스템들은 하나 이상의 PV 패널들을 분리하기 위한 하나 이상의 PV 모듈 내의 솔리드-스테이트 스위치, 하나 이상의 PV 스트링들을 부하로부터 분리하기 위한 컴바이너 박스 내의 하나 이상의 컨택터(contactor) 또는 회로 차단기(circuit breaker), 및/또는 부하를 개방/단락하기 위한 하나 이상의 기구를 포함할 수 있다.

[0039] 여기에서, PV 시스템(100)은 컴바이너 박스(104)를 포함할 수 있다고 설명되었다. 일부 실시예에서, 이러한 PV 시스템은 컴바이너 박스 없이 구현될 수 있는데, 이로써 하나 이상의 PV 스트링이 부하에 직접 연결되게 혼용한다.

[0040] 또한, 일반적으로, DC 전력 시스템들에서 아크 방전을 검출하는 예시적인 방법들(300a, 300b, 및 300c)에 채택된 비들은 복소 분할 연산들(complex division operations)의 사용을 요구하지 않고, 조건부 테스트를 이용하여, 예를 들어 특정 임계치들과 각 비들의 분모들을 곱한 이후에 수행될 수 있다는 점에 유의한다. 이들 비 중 2 이상을 결합함으로써 더 복잡한 테스트들이 정의될 수 있다는 점에 더 유의한다. 예를 들어, 2개의 APDF/APC의 비와 APDF/APDM의 비가 결합되어 단일한 APDF<sup>2</sup>/APC/APDM의 비를 형성할 수 있다. 마찬가지로, 2개의 PDF/PC의 비와 PDF/PDM의 비가 결합되어 단일한 PDF<sup>2</sup>/PC/PDM의 비를 형성할 수 있다. 이들 비의 다른 적절한 조합들은 또한 DC 아크들과 부하 스위칭 노이즈를 더 구분하기 위해 채택될 수 있다.

[0041] 여기에 설명된 하나 이상의 실시예가 각각의 PV 모듈 또는 PV 스트링이 자신의 최대 전력 지점에서 동작하도록 DC-DC 변환들을 조절하기 위한 옵티마이저(optimizer), 각각의 PV 모듈이 자신의 최대 전력 지점에서 동작하도록 DC-AC 변환들을 조정하기 위한 마이크로 인버터(micro-inverter), 및 하나 이상의 PV 스트링에 연결된 DC-AC

인버터들과 같은 PV 부하들을 포함할 수 있다는 점을 더 유의한다. 여기에 설명된 실시예들은 또한 각 PV 모듈에 부착된 아크 고장 검출기들(AFDs)과 결합될 수 있고, 접지 고장 검출기들과 함께 사용될 수 있다.

[0042] 또한, DC 전압 시스템들에서 아크 방전을 검출하기 위한 시스템(200)(도 2 참조)은 전류 센서(202), 정류기(204), 필터(206), 비교기(208), 펠스 적산기(210), 및 프로세서(212)를 포함할 수 있고, 전류 센서(202)가 DC 전력 시스템의 전류 출력을 모니터링하기 위한 변류기로서 구현될 수 있다는 점이 여기에 설명되었다. 일부 실시예에서, DC 전력 시스템들에서 아크 방전을 검출하기 위한 시스템은 DC 전력 시스템에서 직렬 아크 방전들의 개선된 검출을 제공하기 위해 복수의 전류 센서를 포함할 수 있다.

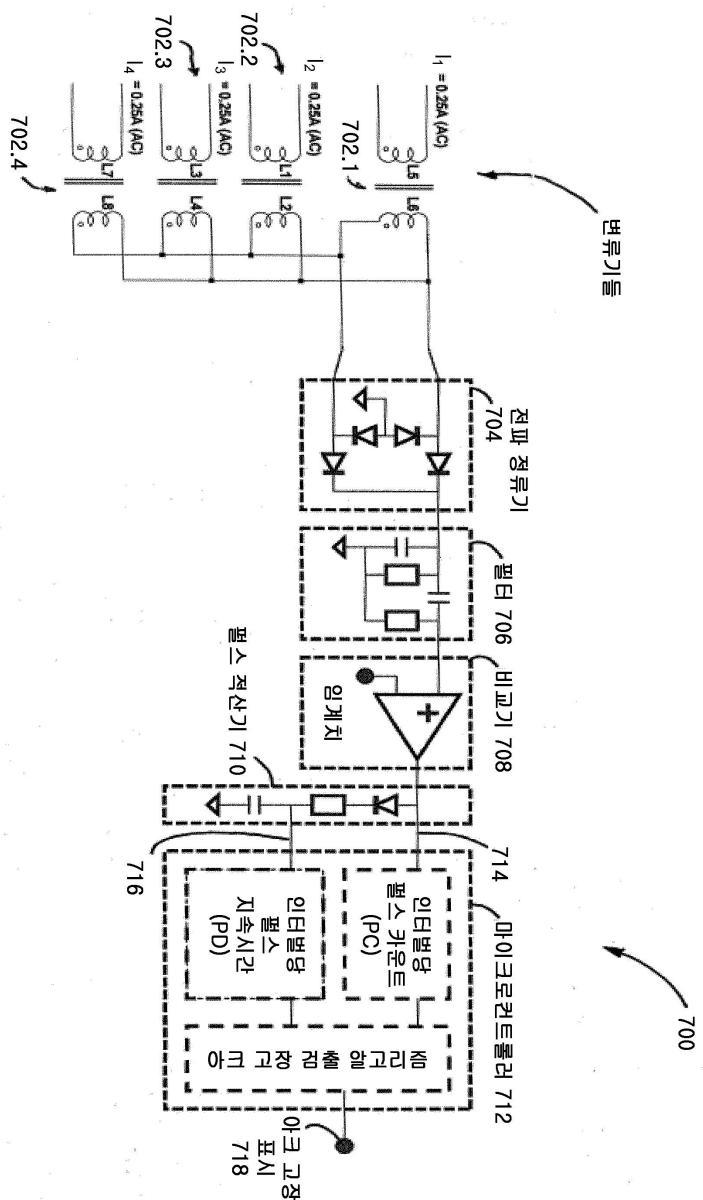

[0043] 도 7은 DC 전력 시스템에서 홈 런 케이블(home run cable) 또는 임의의 다른 적절한 와이어링 런(wiring run)에서 아크 방전을 검출하기 위한 예시 시스템(700)을 도시한다. 도 7에 도시된 바와 같이, 시스템(700)은 복수의 전류 센서(702.1 내지 702.4), 정류기(704), 필터(706), 비교기(708), 펠스 적산기(710), 및 프로세서(712)를 포함한다. 예를 들어, 복수의 전류 센서(702.1 내지 702.4)는 각각 DC 전력 시스템의 전류 출력을 모니터링하기 위한 변류기로서 구현될 수 있다. 시스템(700)이 4개의 전류 센서(702.1 내지 702.4)를 이용하여 동작한다는 점을 제외하고, 시스템(7000)의 동작은 시스템(200)의 동작과 같다. 도 7은 예시 목적으로 4개의 전류 센서(702.1 내지 702.4)를 포함하는 시스템(700)을 도시하고, 시스템(700)은 임의의 다른 적절한 개수의 이러한 전류 센서들을 포함할 수 있다는 점에 유의한다.

[0044] 시스템(700)은 다음의 예시 및 도 7을 참조하여 더 이해될 것이다. 이러한 예시에서, 4개의 전류 센서(702.1 내지 702.4)는 병렬 연결되어 총 12개 또는 임의의 다른 적절한 개수의 PV 스트링들을 포함할 수 있는 홈 런 케이블에서 4개의 PV 스트링을 모니터링한다. 또한, 이러한 예시에서, 직렬 아크 방전이 약 3 암페어(AC)의 전류 변동을 갖는 홈 런 케이블에 일어난다고 가정한다. 동일한 임피던스를 가정하면, 홈 런 케이블 상의 12개의 PV 스트링 각각은 약 3/12 또는 0.25 암페어(AC)의 아크 전류를 수신한다. 각각의 전류 센서들(702.1 내지 702.4)에 의해 모니터링되는 4개의 PV 스트링들의 경우, 전류 센서(702.1)에 의해 모니터링되는 제1 PV 스트링은 약 0.25 암페어(AC)의 아크 전류( $I_1$ )를 수신하고, 전류 센서(702.2)에 의해 모니터링되는 제2 PV 스트링은 약 0.25 암페어(AC)의 아크 전류( $I_2$ )를 수신하고, 전류 센서(702.3)에 의해 모니터링되는 제3 PV 스트링은 약 0.25 암페어(AC)의 아크 전류( $I_3$ )를 수신하고, 그리고 전류 센서(702.4)에 의해 모니터링되는 제4 PV 스트링은 약 0.25 암페어(AC)의 아크 전류( $I_4$ )를 수신한다. 그러나, 4개의 전류 센서(702.1 내지 702.4)가 병렬로 연결되기 때문에, 전파 정류기(704)에게 제공되는 결합 아크 전류는 약  $4*0.25$  또는 1 암페어(AC)이다.

[0045] 시스템(700)(도 7 참조) 내의 전파 정류기(704)에게 증가된 레벨의 아크를 제공하기 위해 병렬 연결된 4개의 전류 센서(702.1 내지 702.4)를 채택함으로써, 홈 런 케이블 또는 임의의 다른 적절한 와이어링 런 상의 직렬 아크의 개선된 검출이 달성될 수 있다. 도 7은 병렬 연결된 4개의 전류 센서(702.1 내지 702.4)를 도시하고 있지만, 임의의 적절한 개수의 전류 센서들이 병렬, 직렬, 또는 병렬/직렬 상호연결의 임의의 다른 적절한 조합으로 연결될 수 있다. 약 3 암페어(AC)의 전류 변동을 갖는 이러한 직렬 아크 방전이 예시 목적으로 앞서 설명되어 있고, 시스템(700)은 임의의 다른 적절한 레벨의 직렬 아크 방전을 검출하도록 채택될 수 있다는 점에 더 유의한다.

[0046] 도 8은 DC 전력 시스템에서 홈 런 케이블(home run cable) 또는 임의의 다른 적절한 와이어링 런(wiring run)에서 아크 방전을 검출하기 위한 추가적인 예시 시스템(800)을 도시한다. 시스템(700)(도 7 참조)의 대체 실시예인 시스템(800)은 다수의 PV 스트링을 갖는 PV 시스템에서 채택된 아크 고장 검출 디바이스에서 아크 잡음 전파의 효과들을 감소시키기 위해 사용될 수 있다. 예를 들어, 다수의 PV 스트링 중 첫번째 PV 스트링(“제1 PV 스트링”)에 대응하는 전도체 상의 일정 위치에 아크 방전이 일어나면, 제1 PV 스트링에 대한 아크 방전과 같은 아크 전류 시그니처(예를 들어, 직렬 아크 방전)를 갖는 아크 방전은 제1 PV 스트링에 인접한 적어도 하나의 PV 스트링에 대응하는 전도체 상의 일정 위치에 일어날 수 있다. 인접한 PV 스트링들에 대응하는 전도체들에 일어날 수 있는 이러한 아크 방전(이러한 아크 방전은 “인접한 전도체 크로스토크”라고 지칭됨)은 일반적으로 PV 시스템 내의 임피던스의 분배로 인한 것이고, 각각의 PV 스트링들의 임피던스에 따라, 진폭 및 위상 시프트를 감소시키는 것을 특징으로 한다. 도 8의 시스템(800)은 PV 시스템 내의 이러한 인접 전도체 크로스토크를 효과적으로 상쇄하도록 구성된다. 이러한 방식으로, PV 스트링 레벨에서 직렬 아크 방전 등의 아크 방전을 검출하기 위한 아크 고장 검출 디바이스의 능력이 개선될 수 있다.

[0047] 도 8에 도시된 바와 같이, 시스템(800)은 병렬 연결된 복수의 전류 센서(802.1 내지 802.4), 정류기(804), 필터(806), 비교기(808), 펠스 적산기(810), 및 프로세서(812)를 포함한다. 예를 들어, 복수의 전류 센서(802.1 내

지 802.4) 각각은 PV 시스템에서 PV 스트링의 전류 출력을 모니터링하기 위한 변류기로서 구현될 수 있다. 시스템(800)의 동작은 시스템(700)(도 7 참조)의 동작과 동일하다. 그러나, 시스템(700) 내의 전류 센서들(702.1 내지 702.4)이 동일한 극성(예를 들어, 동일한 “N극” 또는 “S극”)을 이용하여 구성되는 반면에, 인접한 PV 스트링들의 전류 출력들을 모니터링하는 시스템(800) 내의 전류 센서들(802.1 내지 802.4)은 반대 극성들을 이용하여 구성된다. 예를 들어, 인접한 PV 스트링들을 모니터링하는 전류 센서들(802.1 및 802.2)은 각각 반대의 극성인 S극 및 N극을 이용하여 구성될 수 있고, 인접한 PV 스트링들을 모니터링하는 전류 센서들(802.2 및 802.3)은 각각 반대의 극성인 N극 및 S극을 이용하여 구성될 수 있고, 인접한 PV 스트링들을 모니터링하는 전류 센서들(802.3 및 802.4)은 각각 반대의 극성인 S극 및 N극을 이용하여 구성될 수 있다.

[0048] 다른 방법으로, 전류 센서들(802.1 및 802.2)은 각각 반대의 극성인 N극 및 S극을 이용하여 구성될 수 있고, 전류 센서들(802.2 및 802.3)은 각각 반대의 극성인 S극 및 N극을 이용하여 구성될 수 있고, 전류 센서들(802.3 및 802.4)은 각각 반대의 극성인 N극 및 S극을 이용하여 구성될 수 있다는 점에 유의한다. 도 8은 예시 목적으로 4개의 전류 센서(802.1 내지 802.4)를 포함하는 시스템(800)을 도시하고, 다른 방법으로, 시스템(800)은 PV 시스템에서 임의의 다른 적절한 개수의 PV 스트링의 전류 출력들을 모니터링하기 위한 임의의 다른 적절한 개수의 전류 센서들을 포함할 수 있다는 점에 더 유의한다. 또한, 도 8은 병렬 연결된 4개의 전류 센서(802.1 내지 802.4)를 도시하고 있지만, 임의의 적절한 개수의 전류 센서들이 병렬, 직렬, 또는 병렬/직렬 상호연결의 임의의 다른 적절한 조합으로 연결될 수 있다.

[0049] 시스템(800)은 다음의 예시들 및 도 8을 참조하여 더 이해될 것이다. 제1 예시에서, 전류 센서들(802.1, 802.2, 802.3, 및 802.4)은 병렬 연결되어 총 12개 또는 임의의 다른 적절한 개수의 PV 스트링들을 포함할 수 있는 홈 런 케이블에서 제1, 제2, 제3, 및 제4 PV 스트링을 각각 모니터링한다. 각 전류 센서들(802.1 내지 802.4)에 의해 모니터링되는 4개의 PV 스트링의 경우, 제1 PV 스트링은 제2 PV 스트링에만 인접하고, 제2 PV 스트링은 제1 및 제3 PV 스트링 모두에 인접하고, 제3 PV 스트링은 제2 및 제4 PV 스트링에 인접하고, 제4 PV 스트링은 제3 PV 스트링에만 인접한다.

[0050] 이러한 제1 예시에서, 제1 PV 스트링에 대응하는 전도체 상의 일정 위치에 직렬 아크 방전이 일어난다고 가정한다. 이러한 직렬 아크 방전에 응답하여, 제1 PV 스트링에 대응하는 전도체는 전류 센서(802.1)의 1차 권선(L5)에 아크 전류( $I_{p1}$ )를 투입하여, 결과적으로 전류 센서(802.1)의 2차 권선(L6)에 대한 아크 전류( $I_{s1}$ )를 초래한다. 제1 PV 스트링이 제2 PV 스트링에 인접하기 때문에, 인접 전도체 크로스토크는 제1과 제2 PV 스트링 사이에 일어난다. 이러한 인접 전도체 크로스토크에 응답하여, 제2 PV 스트링에 대응하는 전도체는 전류 센서(802.2)의 1차 권선(L1)에 아크 전류( $I_{p2}$ )를 투입하여, 결과적으로 전류 센서(802.2)의 2차 권선(L2)에 대한 아크 전류( $I_{s2}$ )를 초래한다.

[0051] 전류 센서들(802.1 및 802.2)이 각각 반대 극성인 S극 및 N극으로 구성되기 때문에, 전류 센서(802.1)의 2차 권선(L6)에서의 아크 전류( $I_{s1}$ )는 전류 센서(802.2)의 2차 권선(L2)에서의 아크 전류( $I_{s2}$ )에 대해  $180^\circ$ 의 위상 시프트를 갖는다. 전류 센서(802.1)에 의해 모니터링되는 제1 PV 스트링 및 전류 센서(802.2)에 의해 모니터링되는 제2 PV 스트링은 실질적으로 동일한 임피던스를 갖고, 각각의 전류 센서들(802.1 및 802.2)은 실질적으로 동일한 특성을 갖는다고 가정하면, 제1 및 제2 PV 스트링 사이의 이러한 인접 전도체 크로스토크로부터 기인한 임의의 공통 모드 전류 노이즈는 아크 전류( $I_{s2}$ )에 대한 아크 전류( $I_{s1}$ )의  $180^\circ$  위상 시프트로 인해 아크 전류들( $I_{s1}$  및  $I_{s2}$ )의 조합(예를 들어, 결합 전류( $I_{combined}$ ); 도 8 참조)에서 상쇄될 것이다. 전류 센서들(802.3 및 802.4)이 또한 반대 극성인 S극 및 N극으로 구성되기 때문에, 제3 및 제4 PV 스트링 사이의 인접 전도체 크로스토크로부터 기인한 임의의 공통 모드 전류 노이즈는 유사한 방식으로 상쇄될 것이다.

[0052] 이러한 제2 예시에서, 제2 PV 스트링에 대응하는 전도체 상의 일정 위치에 직렬 아크 방전이 일어난다고 가정한다. 이러한 직렬 아크 방전에 응답하여, 제2 PV 스트링에 응답하는 전도체는 전류 센서(802.2)의 1차 권선(L1)에 아크 전류( $I_{p2}$ )를 투입하여, 결과적으로 전류 센서(802.2)의 2차 권선(L2)에 아크 전류( $I_{s2}$ )를 초래한다. 제2 PV 스트링이 제1 PV 스트링에 인접하기 때문에, 제2 PV 스트링과 제1 PV 스트링 사이에 인접 전도체 크로스토크가 일어난다. 제2 PV 스트링과 제1 PV 스트링 사이의 이러한 인접 전도체 크로스토크에 응답하여, 제1 PV 스트링에 대응하는 전도체는 전류 센서(802.1)의 1차 권선(L5)에 아크 전류( $I_{p1}$ )를 투입하여, 결과적으로 전류 센서(802.1)의 2차 권선(L6)에 아크 전류( $I_{s1}$ )를 초래한다. 또한, 제2 PV 스트링이 제3 PV 스트링에 인접하기 때문에, 제2 PV 스트링과 제3 PV 스트링 사이에 인접 전도체 크로스토크가 일어난다. 제2 PV 스트링과 제3 PV

스트링 사이의 이러한 인접 전도체 크로스토크에 응답하여, 제3 PV 스트링에 대응하는 전도체는 전류 센서(802.3)의 1차 권선(L3)에 아크 전류( $I_{p3}$ )를 투입하여, 결과적으로 전류 센서(802.3)의 2차 권선(L4)에 아크 전류( $I_{s3}$ )를 초래한다.

[0053] 전류 센서들(802.2 및 802.1)이 각각 반대 극성인 N극 및 S극으로 구성되기 때문에, 전류 센서(802.2)의 2차 권선(L2)에 대한 아크 전류( $I_{s2}$ )는 전류 센서(802.1)의 2차 권선(L6)에 대한 아크 전류( $I_{s1}$ )에 비해  $180^\circ$ 의 위상 시프트를 갖는다. 제1 예시에서와 같이, 제1 및 제2 PV 스트링이 실질적으로 동일한 임피던스를 갖고, 각각의 전류 센서들(802.1 및 802.2)이 실질적으로 동일한 특성을 갖는다고 가정하면, 제2 및 제1 PV 스트링 사이의 이러한 인접 전도체 크로스토크로부터 기인하는 임의의 공통 모드 전류 노이즈는 아크 전류( $I_{s1}$ )에 대한 아크 전류( $I_{s2}$ )의  $180^\circ$  위상 시프트로 인해 아크 전류들( $I_{s2}$  및  $I_{s1}$ )의 조합(즉, 결합 전류( $I_{combined}$ ); 도 8 참조)에서 상쇄될 것이다.

[0054] 마찬가지로, 전류 센서들(802.2 및 802.3)이 각각 반대 극성인 N극 및 S극으로 구성되기 때문에, 전류 센서(802.2)의 2차 권선(L2)에 대한 아크 전류( $I_{s2}$ )는 전류 센서(802.3)의 2차 권선(L4)에 대한 아크 전류( $I_{s3}$ )에 비해  $180^\circ$ 의 위상 시프트를 갖는다. 제2 및 제3 PV 스트링이 실질적으로 동일한 임피던스를 갖고, 각각의 전류 센서들(802.2 및 802.3)이 실질적으로 동일한 특성을 갖는다고 가정하면, 제2 및 제3 PV 스트링 사이의 이러한 인접 전도체 크로스토크로부터 기인하는 임의의 공통 모드 전류 노이즈는 또한 아크 전류( $I_{s3}$ )에 대한 아크 전류( $I_{s2}$ )의  $180^\circ$  위상 시프트로 인해 아크 전류들( $I_{s2}$  및  $I_{s3}$ )의 조합(즉, 결합 전류( $I_{combined}$ ); 도 8 참조)에서 상쇄될 것이다. 전류 센서들(802.3 및 802.2)이 반대 극성(S극 및 N극)으로 구성되고, 전류 센서들(802.3 및 802.4) 또한 반대 극성(S극 및 N극)으로 구성되기 때문에, 제3 및 제2 PV 스트링 사이 및 제3 및 제4 PV 스트링 사이의 인접 전도체 크로스토크로부터 기인한 임의의 공통 모드 전류 노이즈는 유사한 방식으로 상쇄될 것이다는 점에 유의한다.

[0055] 앞서, PV 시스템에서 인접한 PV 스트링들의 전류 출력을 모니터링하는 시스템(800)(도 8 참조) 내의 전류 센서들(802.1 내지 802.4)이 반대 극성으로 구성되어 인접 PV 스트링들 사이의 인접 전도체 크로스토크를 효과적으로 상쇄할 수 있다고 설명되었다. 일 실시예에서, 다른 방법으로, PV 시스템에서 인접한 PV 스트링들의 전류 출력들을 모니터링하는 전류 센서들(802.1 내지 802.4)은 동일한 극성(예를 들어, 동일한 N극 또는 S극)으로 구성될 수 있고, 각각의 인접 PV 스트링들에 대응하는 전도체들은 반대 방향으로 전류들을 제공하도록 구성 및 배열될 수 있다. 이러한 방식으로, 인접한 PV 스트링들 사이의 인접 전도체 크로스토크로부터 기인하는 임의의 공통 모드 전류 노이즈는 또한 방향이 반대인 전류들의 후속 조합에서 효과적으로 상쇄될 수 있다.

[0056] 여기에 설명된 하나 이상의 실시예들은 소프트웨어 및/또는 하드웨어의 여러 상이한 형태로 구현될 수 있다는 점이 명백할 것이다. 예를 들어, 여기에 설명된 하나 이상의 실시예는 하나 이상의 컴퓨터화된 디바이스, 하드웨어 프로세서 등의 적절한 구성들을 포함하여 여기에 설명된 시스템들 및/또는 방법들 중 어느 하나 또는 전부를 실시하고/거나 지원할 수 있다. 또한, 하나 이상의 컴퓨터화된 디바이스들, 프로세서들, 디지털 신호 프로세서들 등은 여기에 설명된 시스템 및 방법들을 구현하기 위해 프로그래밍되고/거나 구성될 수 있다.

[0057] 여기에 개시된 본 발명의 개념들로부터 벗어나지 않는 한, DC 전력 시스템들에서 아크 방전을 검출하는 전술한 시스템들 및 방법들에 대한 추가적인 수정 및 변형이 행해질 수 있다는 것이 당업자에 의해 이해될 것이다. 따라서, 본 발명은 첨부된 청구항들의 범위 및 사상에 의하는 경우를 제외하고, 제한되는 것으로 간주되지 않아야 한다.

도면

도면 1a

도면 1b

도면 1c

도면2

## 도면3a

## 도면3b

## 도면3c

## 도면4a

도면4b

도면4c

도면4d

도면5a

도면5b

도면5c

도면6a

도면6b

도면6c

도면7

## 도면8