(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6074585号

(P6074585)

(45) 発行日 平成29年2月8日(2017.2.8)

(24) 登録日 平成29年1月20日(2017.1.20)

(51) Int.Cl.

G09G 3/3233 (2016.01)

G09G 3/20 (2006.01)

F 1

G09G 3/3233

G09G 3/20 622K

G09G 3/20 622P

G09G 3/20 622R

G09G 3/20 650E

請求項の数 7 (全 30 頁) 最終頁に続く

(21) 出願番号

特願2012-170306 (P2012-170306)

(22) 出願日

平成24年7月31日 (2012.7.31)

(65) 公開番号

特開2014-29424 (P2014-29424A)

(43) 公開日

平成26年2月13日 (2014.2.13)

審査請求日

平成27年5月18日 (2015.5.18)

(73) 特許権者 514188173

株式会社 J O L E D

東京都千代田区神田錦町三丁目23番地

(74) 代理人 110001357

特許業務法人つばさ国際特許事務所

(72) 発明者 豊村 直史

東京都港区港南1丁目7番1号 ソニー株式会社内

(72) 発明者 山下 淳一

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 小川 浩史

最終頁に続く

(54) 【発明の名称】表示装置および電子機器、ならびに表示パネルの駆動方法

## (57) 【特許請求の範囲】

## 【請求項1】

表示パネルと、前記表示パネルを駆動する駆動回路とを備え、

前記表示パネルは、複数の画素を含む複数の表示画素を有し、

各画素は、発光素子と、前記発光素子を駆動する駆動トランジスタと、映像信号に対応する信号電圧を書き込む書込トランジスタと、前記駆動トランジスタのゲート-ソース間電圧を保持する保持容量とを含み、

前記駆動回路は、 $k$ 本( $k \geq 2$ )の表示画素行を1ユニットとしたときに、第1のユニットで、前記駆動トランジスタのゲート-ソース間電圧を前記駆動トランジスタの閾値電圧に近づけるV<sub>t h</sub>補正、および前記信号電圧の書き込みを実行した後に、前記第1のユニットと列方向において隣接する第2のユニットで、前記V<sub>t h</sub>補正、および前記信号電圧の書き込みを実行し、

前記駆動回路は、1表示画素行における各画素への前記信号電圧の書き込みを、ユニット単位で当該信号電圧の書き込みを行うときの走査方向とは反対方向に走査することにより実行する

表示装置。

## 【請求項2】

各表示画素に含まれる複数の画素は、 $2 \times y$ 行 $\times$  $y$ 列( $y \geq 2$ )のマトリクスで配置され、

前記駆動回路は、1表示画素行における各画素への前記信号電圧の書き込みを、下段の画素に対して実行したのち、上段の画素に対して実行する

請求項 1 に記載の表示装置。

**【請求項 3】**

前記表示パネルは、

1 ユニット内の各表示画素行における上段の画素行に対して 1 本ずつ割り当てられた複数の第 1 配線と、

1 ユニット内の各表示画素行における下段の画素行に対して 1 本ずつ割り当てられた複数の第 2 配線と

を有し、

各表示画素において、各画素の発光色は互いに異なっており、

各第 1 配線は、1 ユニット内で同一発光色の複数の画素に接続され、

10

各第 2 配線は、前記第 1 配線に接続された画素の発光色とは異なる発光色であって、かつ 1 ユニット内で同一発光色の複数の画素に接続されており、

前記駆動回路は、1 表示画素行における各画素への前記信号電圧の書き込みを、前記第 2 配線に接続された各画素に対して実行したのち、前記第 1 配線に接続された各画素に対して実行する

請求項 2 に記載の表示装置。

**【請求項 4】**

各画素は、さらに、前記駆動トランジスタのソースに接続された補助容量を含み、

前記表示パネルは、さらに、列方向において互いに隣接すると共に表示画素行の互いに異なる 2 本の画素行ごとに 1 本ずつ割り当てられ、かつ前記補助容量に接続された複数の基準電圧線を有する

20

請求項 3 に記載の表示装置。

**【請求項 5】**

各基準電圧線は、割り当てられた 2 本の画素行に含まれる全ての補助容量に接続されている

請求項 4 に記載の表示装置。

**【請求項 6】**

表示装置を備え、

前記表示装置は、表示パネルと、前記表示パネルを駆動する駆動回路とを有し、前記表示パネルは、複数の画素を含む複数の表示画素を有し、

30

各画素は、発光素子と、前記発光素子を駆動する駆動トランジスタと、映像信号に対応する信号電圧を書き込む書込トランジスタと、前記駆動トランジスタのゲート - ソース間電圧を保持する保持容量とを含み、

前記駆動回路は、 $k$  本 ( $k \geq 2$ ) の表示画素行を 1 ユニットとしたときに、第 1 のユニットで、前記駆動トランジスタのゲート - ソース間電圧を前記駆動トランジスタの閾値電圧に近づける  $V_{th}$  補正、および前記信号電圧の書き込みを実行した後に、前記第 1 のユニットと列方向において隣接する第 2 のユニットで、前記  $V_{th}$  補正、および前記信号電圧の書き込みを実行し、

前記駆動回路は、1 表示画素行における各画素への前記信号電圧の書き込みを、ユニット単位で当該信号電圧の書き込みを行うときの走査方向とは反対方向に走査することにより実行する

40

電子機器。

**【請求項 7】**

複数の画素を含む複数の表示画素を備えた表示パネルの駆動方法であって、

各画素は、発光素子と、前記発光素子を駆動する駆動トランジスタと、映像信号に対応する信号電圧を書き込む書込トランジスタと、前記駆動トランジスタのゲート - ソース間電圧を保持する保持容量とを含み、

当該駆動方法は、 $k$  本 ( $k \geq 2$ ) の表示画素行を 1 ユニットとしたときに、第 1 のユニットで、前記駆動トランジスタのゲート - ソース間電圧を前記駆動トランジスタの閾値電圧に近づける  $V_{th}$  補正、および前記信号電圧の書き込みを実行した後に、前記第 1 のユ

50

ニットと列方向において隣接する第2のユニットで、前記V<sub>t h</sub>補正、および前記信号電圧の書き込みを実行するステップを含み、

前記ステップにおいて、1表示画素行における各画素への前記信号電圧の書き込みを、ユニット単位で当該信号電圧の書き込みを行うときの走査方向とは反対方向に走査することにより実行する

表示パネルの駆動方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本技術は、例えば有機EL(Electro Luminescence)素子などの発光素子を画素ごとに有する表示パネルを備えた表示装置および電子機器と、そのような表示パネルの駆動方法とに関する。 10

**【背景技術】**

**【0002】**

近年、画像表示を行う表示装置の分野では、画素の発光素子として、流れる電流値に応じて発光輝度が変化する電流駆動型の発光素子、例えば有機EL素子を用いた表示装置が開発され、商品化が進められている。有機EL素子は、液晶素子などと異なり自発光素子である。そのため、有機EL素子を用いた表示装置(有機EL表示装置)では、光源(バックライト)が必要ないので、光源を必要とする液晶表示装置と比べて、薄型化、高輝度化することができる。 20

**【0003】**

ところで、一般的に、有機EL素子の電流-電圧(I-V)特性は、時間の経過に従つて劣化(経時劣化)する。有機EL素子を電流駆動する画素回路では、有機EL素子のI-V特性が経時変化すると、有機EL素子と、有機EL素子に直列に接続された駆動トランジスタとの分圧比が変化するので、駆動トランジスタのゲート-ソース間電圧も変化する。その結果、駆動トランジスタに流れる電流値が変化するので、有機EL素子に流れる電流値も変化し、その電流値に応じて発光輝度も変化する。 30

**【0004】**

また、駆動トランジスタの閾値電圧(V<sub>t h</sub>)や移動度(μ)が経時的に変化したり、製造プロセスのばらつきによってV<sub>t h</sub>やμが画素回路ごとに異なったりする場合がある。駆動トランジスタのV<sub>t h</sub>やμが画素回路ごとに異なる場合には、駆動トランジスタに流れる電流値が画素回路ごとにばらつくので、駆動トランジスタのゲートに同じ電圧を印加しても、有機EL素子の発光輝度がばらつき、画面の一様性(ユニフォーミティ)が損なわれる。

**【0005】**

そこで、有機EL素子のI-V特性が経時変化したり、駆動トランジスタのV<sub>t h</sub>やμが経時変化したりしても、それらの影響を受けることなく、有機EL素子の発光輝度を一定に保つようにするために、有機EL素子のI-V特性の変動に対する補償機能および駆動トランジスタのV<sub>t h</sub>やμの変動に対する補正機能を組み込んだ表示装置が開発されている(例えば、特許文献1参照)。 40

**【先行技術文献】**

**【特許文献】**

**【0006】**

**【特許文献1】特開2008-083272号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0007】**

ところで、駆動トランジスタのゲート-ソース間電圧を保持する保持容量を補間する目的で、駆動トランジスタのソースに補助容量を接続することがある。このとき、補助容量の一端に接続する一定電圧の配線(一定電圧線)を他の画素と共有することがある。しか 50

し、そのようにした場合には、一定電圧線を互いに共有している複数の画素において、一方の画素が駆動されているときに、その影響が一定電圧線を介して他方の画素に伝播し、他方の画素における駆動トランジスタのソース電圧が揺れる。その結果、他方の画素における駆動トランジスタのゲート電圧もソース電圧の揺れに応じて揺れる。

#### 【0008】

このように、複数の画素間でカップリングが生じている間、カップリングによる影響を受ける画素では、ゲート電圧の揺れはソース電圧の揺れに応じて変化する。カップリングの生じるタイミングが、駆動トランジスタの $\mu$ の変動に対する補正の後となる場合には、駆動トランジスタのゲート - ソース間電圧は、カップリング前の値とほとんど変わらない。ところが、カップリングの生じるタイミングが、駆動トランジスタの $\mu$ の変動に対する補正の前となる場合には、駆動トランジスタのゲート - ソース間電圧が、カップリング前の値よりも小さくなり、発光輝度が暗くなる。その結果、駆動トランジスタのゲート - ソース間電圧がカップリング前の値とほとんど変わらない画素と、駆動トランジスタのゲート - ソース間電圧がカップリング前の値よりも小さくなる画素とが混在する場合には、それらの間で、発光輝度の変化の傾向に差異が生じ、輝度ムラが生じるという問題があった。

。

10

#### 【0009】

本技術はかかる問題点に鑑みてなされたものであり、その目的は、カップリングに起因する輝度ムラを低減することの可能な表示装置および電子機器と、カップリングに起因する輝度ムラを低減することの可能な表示パネルの駆動方法とを提供することにある。

20

#### 【課題を解決するための手段】

#### 【0010】

本技術の表示装置は、表示パネルと、表示パネルを駆動する駆動回路とを備えている。表示パネルは、複数の画素を含む複数の表示画素を有している。各画素は、発光素子と、発光素子を駆動する駆動トランジスタと、映像信号に対応する信号電圧を書き込む書込トランジスタと、駆動トランジスタのゲート - ソース間電圧を保持する保持容量とを含んでいる。駆動回路は、 $k$ 本( $k \geq 2$ )の表示画素行を1ユニットとしたときに、第1のユニットで、駆動トランジスタのゲート - ソース間電圧を駆動トランジスタの閾値電圧に近づける $V_{th}$ 補正、および信号電圧の書き込み(以下、「信号書き込み」と称する。)を実行するようになっている。駆動回路は、第1のユニットでの $V_{th}$ 補正および信号書き込みを実行した後に、第1のユニットと列方向において隣接する第2のユニットで、 $V_{th}$ 補正および信号書き込みを実行するようになっている。駆動回路は、1表示画素行における各画素への信号書き込みを、ユニット単位で当該信号書き込みを行うときの走査方向とは反対方向に走査することにより実行するようになっている。

30

#### 【0011】

本技術の電子機器は、上記の表示装置を備えている。

#### 【0012】

本技術の表示パネルの駆動方法は、複数の画素を含む複数の表示画素を備えた表示パネルの駆動方法である。ここで、上記の表示パネルでは、各画素は、発光素子と、発光素子を駆動する駆動トランジスタと、映像信号に対応する信号電圧を書き込む書込トランジスタと、駆動トランジスタのゲート - ソース間電圧を保持する保持容量とを含んでいる。本技術の表示パネルの駆動方法は、 $k$ 本( $k \geq 2$ )の表示画素行を1ユニットとしたときに、第1のユニットで、駆動トランジスタのゲート - ソース間電圧を駆動トランジスタの閾値電圧に近づける $V_{th}$ 補正、および信号電圧の書き込みを実行する第1ステップを含んでいる。この駆動方法は、さらに、第1ステップを実行した後、第1のユニットと列方向において隣接する第2のユニットで、 $V_{th}$ 補正、および信号電圧の書き込みを実行する第2ステップを含んでいる。この駆動方法は、第1および第2のステップにおいて、1表示画素行における各画素への信号電圧の書き込みを、ユニット単位で当該信号電圧の書き込みを行うときの走査方向とは反対方向に走査することにより実行するステップを含んでいる。

40

50

## 【0013】

本技術の表示装置、本技術の電子機器、および本技術の表示パネルの駆動方法では、 $V_{th}$ 補正および信号書き込みがユニットごとに一括して実行される。このとき、1表示画素行における各画素への信号書き込みが、ユニット単位で信号書き込みを行うときの走査方向とは反対方向に走査することにより実行される。これにより、複数の表示画素間でカップリングが生じるような回路構成となっている場合であっても、カップリングによる影響を受けるすべての表示画素において、その影響の受け方の傾向が一致する。

## 【発明の効果】

## 【0014】

本技術の表示装置、本技術の電子機器、および本技術の表示パネルの駆動方法によれば、複数の表示画素間でカップリングが生じるような回路構成となっている場合であっても、カップリングによる影響を受けるすべての表示画素において、その影響の受け方の傾向を一致させることができるのである。これにより、カップリングによる影響を受けるすべての表示画素において、発光輝度の変化の傾向がほぼ一致するので、輝度ムラを低減することができる。

10

## 【図面の簡単な説明】

## 【0015】

【図1】本技術による一実施の形態に係る表示装置の概略構成図である。

20

【図2】各画素（サブピクセル）の回路構成の一例を表す図である。

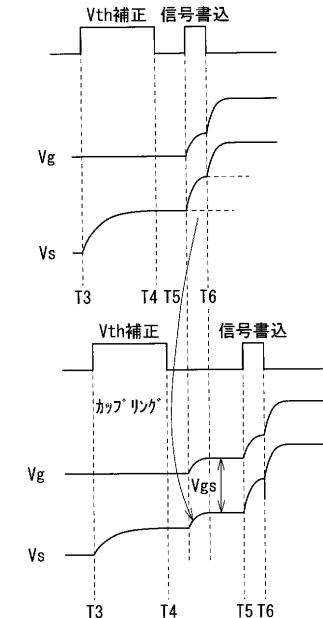

【図3】列方向に互いに隣接する2つの表示画素の回路構成の一例を表す図である。

【図4】列方向に互いに隣接する2つの表示画素の回路構成の他の例を表す図である。

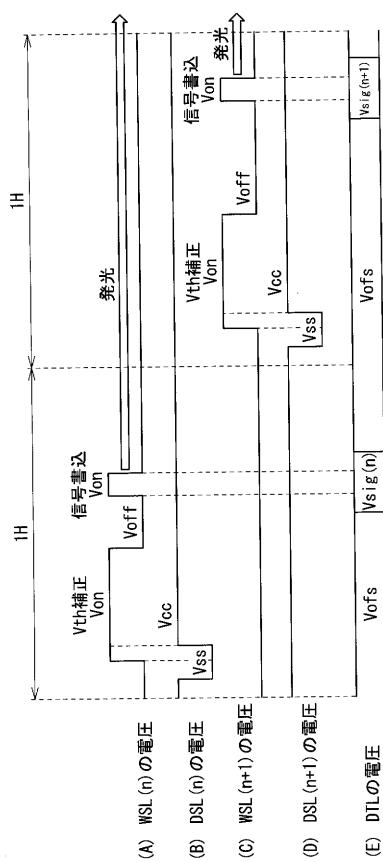

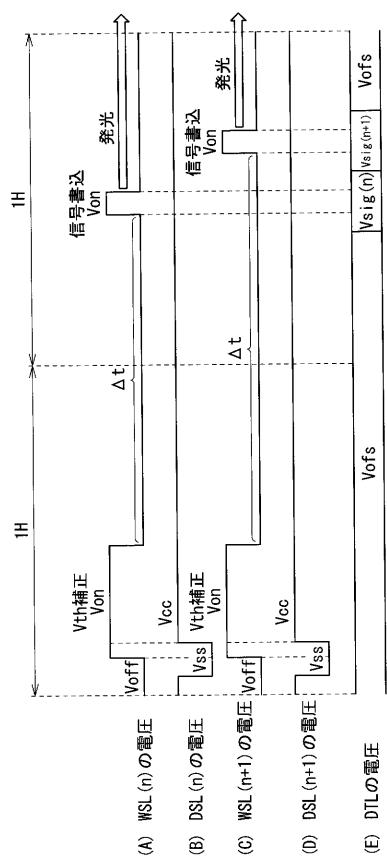

【図5】図3、図4のDTLに印加される電圧の一例を表す図である。

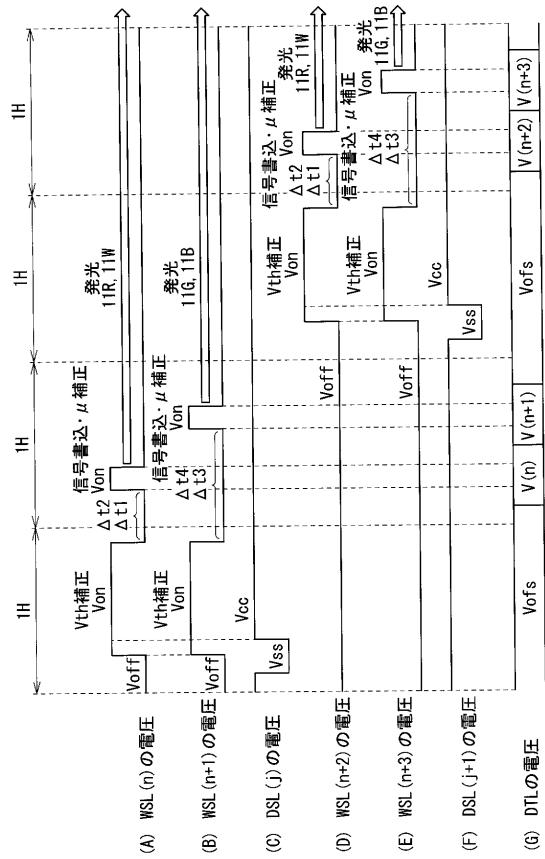

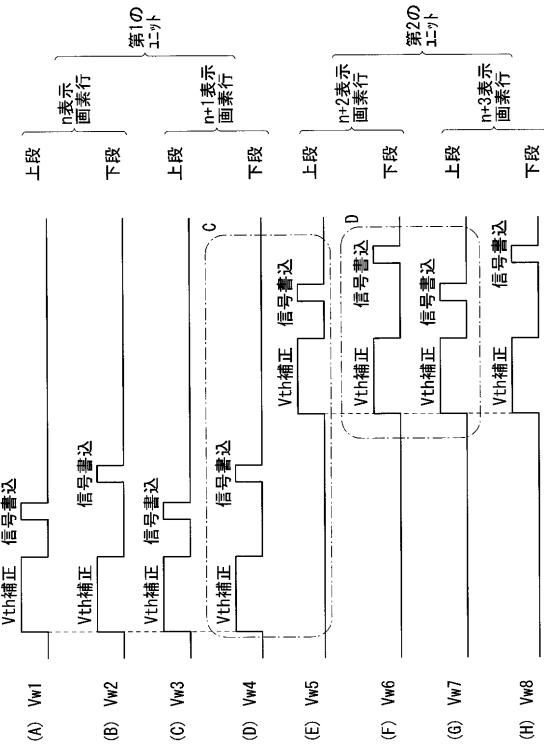

【図6】列方向に互いに隣接する2つのユニットに着目したときの各画素（サブピクセル）行に印加される選択パルスの経時変化の一例を表す波形図である。

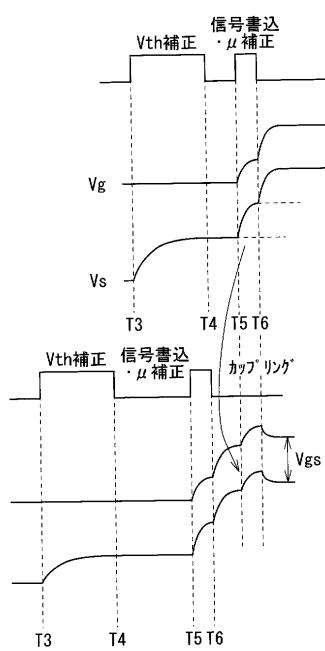

【図7】1つの画素（サブピクセル）に着目したときのWSL, DSL, DTLに印加される電圧、ゲート電圧、およびソース電圧の経時変化の一例を表す波形図である。

【図8】列方向に互いに隣接する2つのユニットに着目したときのWSL, DSL, DTLに印加される電圧の経時変化の一例を表す波形図である。

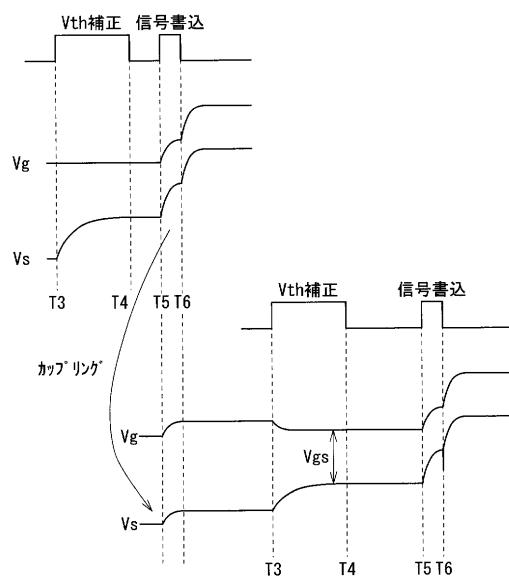

【図9】図6のAで囲まれた2つのWSLに対応する2つの画素間のカップリングについて説明するための波形図である。

30

【図10】図6のBで囲まれた2つのWSLに対応する2つの画素間のカップリングについて説明するための波形図である。

【図11】比較例に係る表示パネルにおける各画素の回路構成の一例を表す図である。

【図12】図11のレイアウトを備えた表示装置において、列方向に互いに隣接する2つの画素に着目したときのWSL, DSL, DTLに印加される電圧の経時変化の一例を表す波形図である。

【図13】図11のレイアウトを備えた表示装置において、列方向に互いに隣接する2つの画素に着目したときのWSL, DSL, DTLに印加される電圧の経時変化の他の例を表す波形図である。

40

【図14】束ね駆動によって生じる輝度ムラの一例を表す図である。

【図15】図3、図4のレイアウトを備えた表示装置において、列方向に互いに隣接する2つのユニットに着目したときのWSL, DSL, DTLに印加される電圧の経時変化の比較例を表す波形図である。

【図16】図15の波形をWSLの分枝ごとに表す波形図である。

【図17】図16のDで囲まれた2つのWSLに対応する2つの画素間のカップリングについて説明するための波形図である。

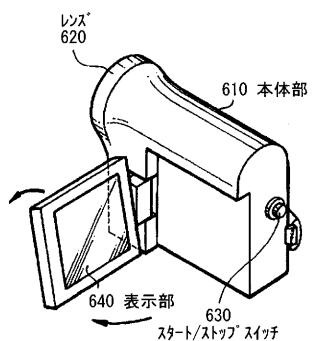

【図18】上記実施の形態の発光装置の適用例1の外観を表す斜視図である。

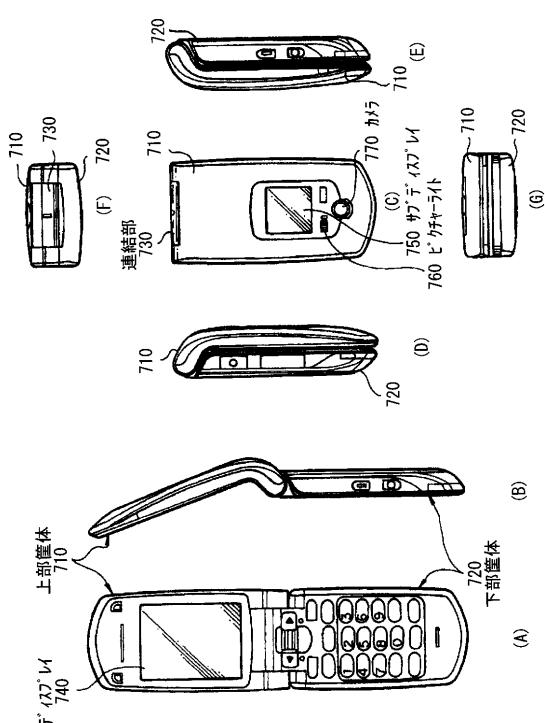

【図19】(A)は適用例2の表側から見た外観を表す斜視図であり、(B)は裏側から見た外観を表す斜視図である。

50

【図20】適用例3の外観を表す斜視図である。

【図21】適用例4の外観を表す斜視図である。

【図22】(A)は適用例5の開いた状態の正面図、(B)はその側面図、(C)は閉じた状態の正面図、(D)は左側面図、(E)は右側面図、(F)は上面図、(G)は下面図である。

#### 【発明を実施するための形態】

##### 【0016】

以下、発明を実施するための形態について、図面を参照して詳細に説明する。なお、説明は以下の順序で行う。

10

1. 実施の形態（表示装置）

2. 変形例（表示装置）

3. 適用例（電子機器）

##### 【0017】

<1. 実施の形態>

###### [構成]

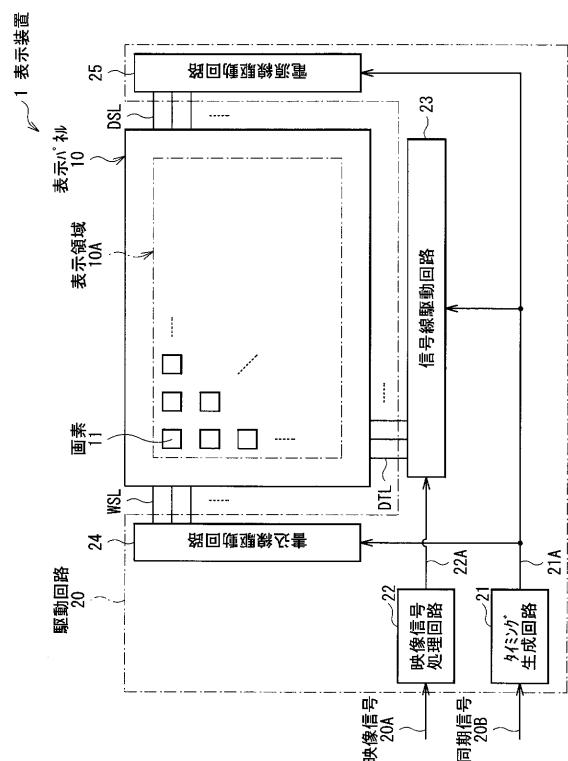

図1は、本技術の一実施の形態に係る表示装置1の概略構成を表したものである。この表示装置1は、表示パネル10と、外部から入力された映像信号20Aおよび同期信号20Bに基づいて表示パネル10を駆動する駆動回路20とを備えている。駆動回路20は、例えば、タイミング生成回路21、映像信号処理回路22、信号線駆動回路23、走査線駆動回路24、および電源線駆動回路25を有している。

20

##### 【0018】

###### (表示パネル10)

表示パネル10は、複数の画素11が表示パネル10の表示領域10A全面に渡ってマトリクス状に配置されたものである。表示パネル10は、駆動回路20によって各画素11がアクティブマトリクス駆動されることにより、外部から入力された映像信号20Aに基づく画像を表示するものである。

##### 【0019】

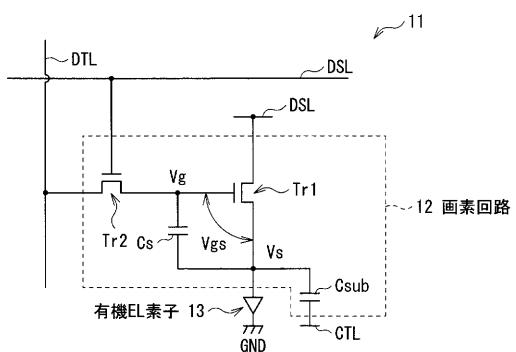

図2は、画素11の回路構成の一例を表したものである。各画素11は、例えば、画素回路12と、有機EL素子13とを有している。有機EL素子13は、例えば、アノード電極、有機層およびカソード電極が順に積層された構成を有している。有機EL素子13は、素子容量C<sub>ole</sub>d（図示せず）を有している。画素回路12は、例えば、駆動トランジスタTr1、書き込トランジスタTr2、保持容量Csおよび補助容量Cs<sub>ub</sub>によって構成されたものであり、2Tr2Cの回路構成となっている。

30

##### 【0020】

書き込トランジスタTr2は、駆動トランジスタTr1のゲートに対する、映像信号に対応した信号電圧の印加を制御するものである。具体的には、書き込トランジスタTr2は、後述の信号線DTLの電圧をサンプリングするとともに駆動トランジスタTr1のゲートに書き込むものである。駆動トランジスタTr1は、有機EL素子13を駆動するものであり、有機EL素子13に直列に接続されている。駆動トランジスタTr1は、書き込トランジスタTr2によって書き込まれた電圧の大きさに応じて有機EL素子13に流れる電流を制御するものである。保持容量Csは、駆動トランジスタTr1のゲート-ソース間に所定の電圧を保持するものである。補助容量Cs<sub>ub</sub>は、駆動トランジスタTr1から供給される電流の一部を流し込むものである。なお、画素回路12は、上述の2Tr2Cの回路に対して各種容量やトランジスタを付加した回路構成となっていてもよいし、上述の2Tr2Cの回路構成とは異なる回路構成となっていてもよい。

40

##### 【0021】

駆動トランジスタTr1および書き込トランジスタTr2は、例えば、nチャネルMOS型の薄膜トランジスタ（TFT（Thin Film Transistor））により形成されている。なお、TFTの種類は特に限定されるものではなく、例えば、逆スタガー構造（いわゆるボト

50

ムゲート型)であってもよいし、スタガー構造(トップゲート型)であってもよい。また、駆動トランジスタTr1および書込トランジスタTr2は、pチャネルMOS型のFETにより形成されていてもよい。

#### 【0022】

表示パネル10は、行方向に延在する複数の走査線WSLと、列方向に延在する複数の信号線DTLと、行方向に延在する複数の電源線DSLと、行方向に延在する複数のカソード線CTL(基準電圧線)を有している。走査線WSLは、各画素11の選択に用いられるものである。信号線DTLは、映像信号に応じた信号電圧の、各画素11への供給に用いられるものである。電源線DSLは、各画素11への駆動電流の供給に用いられるものである。

10

#### 【0023】

各信号線DTLと各走査線WSLとの交差点近傍には、画素11が設けられている。各信号線DTLは、後述の信号線駆動回路23の出力端(図示せず)と、書込トランジスタTr2のソースまたはドレインとに接続されている。各走査線WSLは、後述の走査線駆動回路24の出力端(図示せず)と、書込トランジスタTr2のゲートに接続されている。各電源線DSLは、固定の電圧を出力する電源の出力端(図示せず)と、駆動トランジスタTr1のソースまたはドレインに接続されている。カソード線CTLは、例えば、表示領域10Aの周囲に設けられた部材であって、かつ基準の電圧となっている部材に接続されている。

#### 【0024】

書込トランジスタTr2のゲートは、走査線WSLに接続されている。書込トランジスタTr2のソースまたはドレインが信号線DTLに接続され、書込トランジスタTr2のソースおよびドレインのうち信号線DTLに未接続の端子が駆動トランジスタTr1のゲートに接続されている。駆動トランジスタTr1のソースまたはドレインが電源線DSLに接続され、駆動トランジスタTr1のソースおよびドレインのうち電源線DSLに未接続の端子が有機EL素子13のアノードに接続されている。保持容量Csの一端が駆動トランジスタTr1のゲートに接続され、保持容量Csの他端が駆動トランジスタTr1のソース(図2では有機EL素子13側の端子)に接続されている。つまり、保持容量Csは、駆動トランジスタTr1のゲート-ソース間に挿入されている。補助容量Csubの一端が駆動トランジスタTr1のソース(図2では有機EL素子13側の端子)に接続され、補助容量Csubの他端がカソード線CTLに接続されている。

20

#### 【0025】

表示パネル10は、さらに、図2に示したように、有機EL素子13のカソードに接続されたグラウンド線GNDを有している。グラウンド線GNDは、グラウンド電位となっている外部回路(図示せず)と電気的に接続されるものである。グラウンド線GNDは、例えば、表示領域10A全体に渡って形成されたシート状の電極である。なお、グラウンド線GNDは、画素行または画素列に対応して短冊状に形成された帯状の電極であってもよい。表示パネル10は、さらに、例えば、表示領域10Aの周縁に、映像を表示しないフレーム領域を有している。フレーム領域は、例えば、遮光部材によって覆われている。

30

#### 【0026】

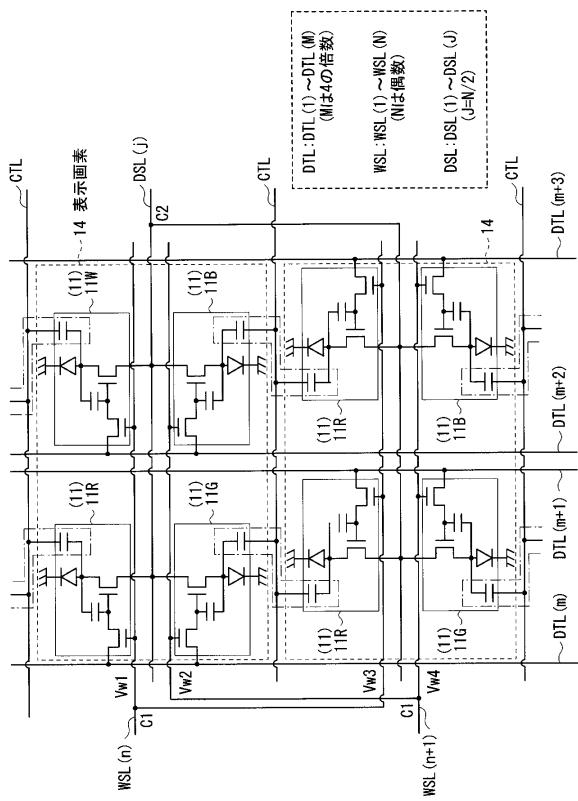

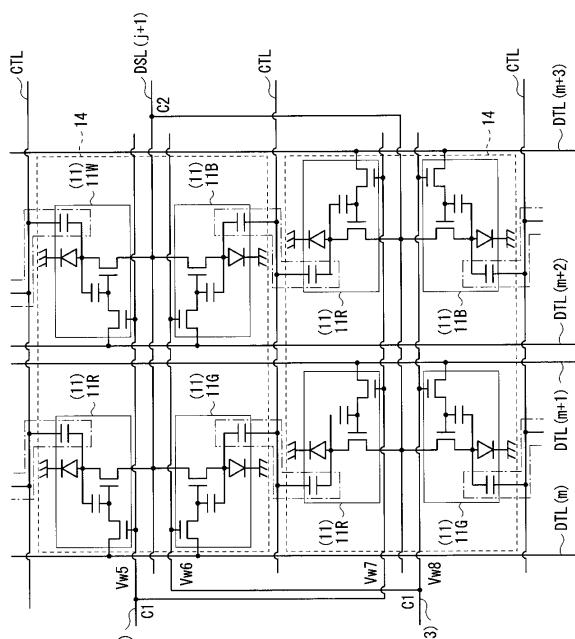

図3、図4は、列方向に互いに隣接する2つの表示画素14(後述)における回路構成の一例を表したものである。図3は、n行目(1 < n < N、Nは表示画素行の総数(偶数))およびn+1行目の表示画素行における各表示画素14の回路構成の一例を表したものである。図4は、n+2行目およびn+3行目の表示画素行における各表示画素14の回路構成の一例を表したものである。ここで、表示画素行とは、行方向に並んで配置された複数の表示画素14によって形成されるラインを指している。一方、画素行とは、行方向に並んで配置された複数の画素11によって形成されるラインを指しており、サブピクセル行に相当するものである。以下では、画素行と表示画素行との混同を避けるために、画素行をサブピクセル行と称する。

40

#### 【0027】

50

各画素 1 1 の回路レイアウトは、 $n$  表示画素行と、 $n + 2$  表示画素行とにおいて、互いに共通となっており、さらに、 $n + 1$  表示画素行と、 $n + 3$  表示画素行とにおいて、互いに共通となっている。以下では、説明の重複を避ける趣旨で、 $n + 2$  表示画素行および $n + 3$  表示画素行における各画素 1 1 の回路レイアウトについての説明を省略する。

#### 【0028】

各画素 1 1 は、表示パネル 1 0 上の画面を構成する最小単位の点に対応するものである。表示パネル 1 0 は、カラー表示パネルとなっており、画素 1 1 は、例えば赤、緑、青、または白などの単色の光を発するサブピクセルに相当する。なお、画素 1 1 は、例えば赤、緑、青、または黄色などの単色の光を発するサブピクセルに相当していてもよい。

#### 【0029】

本実施の形態では、発光色の互いに異なる 4 つの画素 1 1 によって表示画素 1 4 が構成されている。つまり、発光色の種類の数は 4 であり、各表示画素 1 4 に含まれる画素 1 1 の数も 4 である。表示画素 1 4 に含まれる 4 つの画素 1 1 は、例えば、赤色光を発する画素 1 1 R、緑色光を発する画素 1 1 G、青色光を発する画素 1 1 B、および白色光を発する画素 1 1 W で構成されている。各表示画素 1 4 において、4 つの画素 1 1 は、いわゆる田の字配列 (square4) となっており、 $2 \times 2$  のマトリクスで配置されている。また、各表示画素 1 4 において、4 つの画素 1 1 は共通の色配列となっている。例えば、図 3 に示したように、田の字配列の左上に画素 1 1 R が配置され、田の字配列の左下に画素 1 1 G が配置され、田の字配列の右下に画素 1 1 B が配置され、田の字配列の右上に画素 1 1 W が配置されている。

#### 【0030】

複数の走査線 WSL は、 $k$  本 ( $k \geq 2$ ) の表示画素行を 1 ユニットとしたときに 1 ユニットごとに  $k$  本ずつ割り当てられている。1 ユニットに含まれる表示画素行の数は 2 以上、発光色の種類の数以下である。具体的には、複数の走査線 WSL は、2 本の表示画素行を 1 ユニットとしたときに 1 ユニットごとに 2 本ずつ割り当てられている。従って、1 ユニットに含まれる表示画素行の数は 2 であり、1 ユニットに含まれる走査線 WSL の数も 2 である。走査線 WSL の総数は、表示画素行の総数と等しくなっており、 $N$  本となっている。なお、図 3 中の  $n$  は、1 以上、 $N / 2$  以下の正の整数であり、図 3 中の WSL ( $n$ ) は、 $n$  番目 ( $n$  行目) の走査線 WSL を意味している。

#### 【0031】

各走査線 WSL は、1 ユニット内で同一発光色の複数の画素 1 1 に接続されている。具体的には、1 ユニットに含まれる 2 本の走査線 WSL ( $n$ ), WSL ( $n + 1$ ) において、走査線 WSL ( $n$ ) は、1 ユニットに含まれる複数の画素 1 1 R および複数の画素 1 1 W に接続されており、走査線 WSL ( $n + 1$ ) は、1 ユニットに含まれる複数の画素 1 1 G および複数の画素 1 1 B に接続されている。また、各走査線 WSL は、1 ユニット内で同一発光色の全ての画素 1 1 に接続されている。具体的には、1 ユニットに含まれる 2 本の走査線 WSL ( $n$ ), WSL ( $n + 1$ ) において、走査線 WSL ( $n$ ) は、1 ユニット内の全ての画素 1 1 R および全ての画素 1 1 W に接続されており、走査線 WSL ( $n + 1$ ) は、1 ユニット内の全ての画素 1 1 G および全ての画素 1 1 B に接続されている。1 ユニット内で行が互いに異なり、かつ列方向において互いに隣接する 2 つの表示画素 1 4 において、走査線 WSL が共有される 2 種類の発光色の画素 1 1 の発光色の組み合わせが互いに等しくなっている。

#### 【0032】

各走査線 WSL (WSL ( $n$ ) ~ WSL ( $n + 3$ )) は、1 表示画素行に含まれるサブピクセル行の数と同一の本数の分枝 (つまり、2 本の分枝 (第 1 配線、第 2 配線)) を有している。各第 1 配線は、1 ユニット内の各表示画素行における上段のサブピクセル行に対して 1 本ずつ割り当てられている。各第 1 配線は、1 ユニット内で同一発光色の複数の画素 1 1 に接続されている。各第 2 配線は、1 ユニット内の各表示画素行における下段のサブピクセル行に対して 1 本ずつ割り当てられている。各第 2 配線は、第 1 配線に接続された画素 1 1 の発光色とは異なる発光色であって、かつ 1 ユニット内で同一発光色の複数

10

20

30

40

50

の画素 11 に接続されている。各走査線 WSL ( WSL ( n ) ~ WSL ( n + 3 ) ) において、各分岐は、当該表示パネル 10 内で互いに接続されている。分岐同士の接続点 C1 は、表示領域 10A 内にあってもよいし、表示領域 10A の周縁（フレーム領域）内にあってもよい。また、表示パネル 10 の法線方向から見たときに、同一ユニット内において、各走査線 WSL は、他の走査線 WSL と交差している。各走査線 WSL の分岐は、田の字配列の中央を横断している。書込トランジスタ Tr2 のゲート電極 14A は、走査線 WSL の分岐に接続されている。

#### 【 0033 】

複数の電源線 DSL は、1 ユニットごとに 1 本ずつ割り当てられている。従って、1 ユニットに含まれる電源線 DSL の数は 1 である。電源線 DSL の総数は、表示画素行の総数の半分に相当しており、 $J (= N / 2)$  本となっている。なお、図 3 中の j は、1 以上、 $N / 2$  以下の正の整数であり、図 3 中の DSL ( j ) は、j 番目の電源線 DSL を意味している。各電源線 DSL は、1 ユニット内の全ての画素 11 に接続されている。具体的には、1 ユニットに含まれる 1 本の電源線 DSL は、1 ユニットに含まれる全ての画素 11 ( 11R, 11G, 11B, 11W ) に接続されている。

#### 【 0034 】

さらに、図 3、図 4 では、各電源線 DSL ( DSL ( j ), DSL ( j + 1 ) ) については、1 ユニットに含まれる表示画素行の数と同一の本数の分枝（つまり、2 本の分枝）を有している。各電源線 DSL ( DSL ( j ), DSL ( j + 1 ) ) においても、各分枝は、当該表示パネル 10 内で互いに接続されている。分岐同士の接続点 C2 は、表示領域 10A 内にあってもよいし、表示領域 10A の周縁（フレーム領域）内にあってもよい。このように、各走査線 WSL や各電源線 DSL に分枝を設けることにより、各走査線 WSL の間隔や、各電源線 DSL の間隔を広くすることができる。その結果、配線レイアウトが容易となる。各電源線 DSL の分枝は、田の字配列の中央を横断している。

#### 【 0035 】

複数の信号線 DTL は、各表示画素行において表示画素 14 ごとに 2 本ずつ割り当てられている。各表示画素行において表示画素 14 ごとに割り当てられた 2 本の信号線 DTL において、一方の信号線 DTL は、走査線 WSL が共有されていない 2 種類の発光色の画素 11 に接続されており、他方の信号線 DTL は、残りの 2 種類の発光色の画素 11 に接続されている。以下では、n 行目および n + 1 行目の表示画素行に含まれる複数の表示画素 14 のうち、列方向に互いに隣接する 2 つの表示画素 14 に着目して、上記の接続態様について説明する。なお、上記の 2 つの表示画素 14 は、1 ユニット内で表示画素行が互いに異なり、かつ列方向に互いに隣接する 2 つの表示画素 14 に相当する。

#### 【 0036 】

上記の 2 つの表示画素 14 のうち n 行目の表示画素行に含まれる表示画素 14 には、2 本の信号線 DTL ( m ), DTL ( m + 2 ) が割り当てられている。さらに、上記の 2 つの表示画素 14 のうち n + 1 行目の表示画素行に含まれる表示画素 14 には、2 本の信号線 DTL ( m + 1 ), DTL ( m + 3 ) が割り当てられている。つまり、1 ユニット内で表示画素行が互いに異なり、かつ列方向に互いに隣接する 2 つの表示画素 14 において、一方の表示画素 14 に対しては偶数列目の 2 本の信号線 DTL ( m ), DTL ( m + 2 ) が割り当てられ、他方の表示画素 14 に対しては奇数列目の 2 本の信号線 DTL ( m + 1 ), DTL ( m + 3 ) が割り当てられている。これにより、信号線 DTL の総数が最小限に抑えられている。

#### 【 0037 】

複数の信号線 DTL は、列方向において互いに隣接する 2 つの表示画素 14 ごとに 4 本ずつ割り当てられている。従って、信号線 DTL の総本数は、M ( M は 4 の倍数 ) 本となっている。図 3 において、m は、1 以上、M - 4 以下の正の整数であり、1 以外の場合には ( 4 の倍数 + 1 ) に相当する数である。従って、図 3 中の DTL ( m ) は、m 番目の信号線 DTL を意味している。列方向において互いに隣接する 2 つの表示画素 14 には、例えば、4 本の信号線 DTL ( m ), DTL ( m + 1 ), DTL ( m + 2 ), DTL ( m + 3 ) が割り当てられる。

10

20

30

40

50

3) が割り当てられている。4本の信号線 DTL(m), DTL(m+1), DTL(m+2), DTL(m+3) は、行方向において、この順に並んで配置されている。各表示画素 14 において、4つの画素 11 のうち左側の2つの画素 11 が、行方向から信号線 DTL(m) と信号線 DTL(m+1) とによって挟まれている。また、各表示画素 14 において、4つの画素 11 のうち右側の2つの画素 11 が、行方向から信号線 DTL(m+2) と信号線 DTL(m+3) とによって挟まれている。

#### 【0038】

また、1ユニット内で表示画素行が互いに異なり、かつ列方向において互いに隣接する2つの表示画素 14 において、発光色の互いに等しい2つの画素 11 が共通の2本の信号線 DTL の間に配置されている。具体的には、1ユニット内で表示画素行が互いに異なり、かつ列方向において互いに隣接する2つの表示画素 14 において、2つの画素 11 R が2本の信号線 DTL(m), DTL(m+1) の間に配置されている。同様に、1ユニット内で表示画素行が互いに異なり、かつ列方向において互いに隣接する2つの表示画素 14において、2つの画素 11 G が2本の信号線 DTL(m), DTL(m+1) の間に配置されている。また、1ユニット内で表示画素行が互いに異なり、かつ列方向において互いに隣接する2つの表示画素 14において、2つの画素 11 B が2本の信号線 DTL(m+2), DTL(m+3) の間に配置されている。また、1ユニット内で表示画素行が互いに異なり、かつ列方向において互いに隣接する2つの表示画素 14において、2つの画素 11 W が2本の信号線 DTL(m+2), DTL(m+3) の間に配置されている。

#### 【0039】

上記の2本の信号線 DTL(m), DTL(m+2) は、それぞれ、走査線 WSL が互いに共有されていない2種類の発光色の画素 11 に接続されている。具体的には、信号線 DTL(m) は、走査線 WSL が互いに共有されていない2種類の発光色の画素 11 R, 11 G に接続されており、信号線 DTL(m+2) は、走査線 WSL が互いに共有されていない2種類の発光色の画素 11 B, 11 W に接続されている。さらに、上記2つの表示画素 14 のうち n + 1 行目の画素行に含まれる表示画素 14 には、2本の信号線 DTL(m+1), DTL(m+3) が割り当てられている。その2本の信号線 DTL(m+1), DTL(m+3) は、走査線 WSL が互いに共有されていない2種類の発光色の画素 11 に接続されている。具体的には、信号線 DTL(m+1) は、走査線 WSL が共有されていない2種類の発光色の画素 11 R, 11 G に接続されており、信号線 DTL(m+3) は、残りの2種類の発光色の画素 11 B, 11 W に接続されている。

#### 【0040】

複数のカソード線 CTL は、2本のサブピクセル行ごとに1本ずつ割り当てられている。具体的には、複数のカソード線 CTL は、列方向において互いに隣接すると共に表示画素行の互いに異なる2本のサブピクセル行ごとに1本ずつ割り当てられている。例えば、図3に示したように、n 表示画素行内の下段のサブピクセルの1つである画素 11 G と、n + 1 表示画素行内の上段のサブピクセルの1つである画素 11 R とが、共通のカソード線 CTL に接続されている。同様に、例えば、n + 1 表示画素行内の下段のサブピクセルの1つである画素 11 G と、n + 2 表示画素行内の上段のサブピクセルの1つである画素 11 R が、共通のカソード線 CTL に接続されている。また、例えば、図3に示したように、n 表示画素行内の下段のサブピクセルの1つである画素 11 B と、n + 1 表示画素行内の上段のサブピクセルの1つである画素 11 W とが、共通のカソード線 CTL に接続されている。同様に、例えば、n + 1 表示画素行内の下段のサブピクセルの1つである画素 11 B と、n + 2 表示画素行内の上段のサブピクセルの1つである画素 11 W とが、共通のカソード線 CTL に接続されている。

#### 【0041】

各カソード線 CTL は、割り当てられた2本のサブピクセル行に含まれる全ての補助容量 Csub に接続されている。例えば、図3に示したように、n 表示画素行内の下段のサブピクセル行に含まれる全ての画素 11 G, 11 B の補助容量 Csub と、n + 1 表示画素行内の上段のサブピクセル行に含まれる全ての画素 11 R, 11 W の補助容量 Csub

10

20

30

40

50

とが、共通のカソード線 C T L に接続されている。同様に、例えば、図 3 , 図 4 に示したように、 $n + 1$  表示画素行内の下段のサブピクセル行に含まれる全ての画素 1 1 G , 1 1 B の補助容量 C s u b と、 $n + 2$  表示画素行内の上段のサブピクセル行に含まれる全ての画素 1 1 R , 1 1 W の補助容量 C s u b とが、共通のカソード線 C T L に接続されている。

#### 【 0 0 4 2 】

( 駆動回路 2 0 )

次に、駆動回路 2 0 について説明する。駆動回路 2 0 は、上述したように、例えば、タイミング生成回路 2 1 、映像信号処理回路 2 2 、信号線駆動回路 2 3 、走査線駆動回路 2 4 および電源線駆動回路 2 5 を有している。タイミング生成回路 2 1 は、駆動回路 2 0 内の各回路が連動して動作するように制御するものである。タイミング生成回路 2 1 は、例えば、外部から入力された同期信号 2 0 B に応じて（同期して）、上述した各回路に対して制御信号 2 1 A を出力するようになっている。

#### 【 0 0 4 3 】

映像信号処理回路 2 2 は、例えば、外部から入力されたデジタルの映像信号 2 0 A に対して所定の補正を行い、それにより得られた映像信号 2 2 A を信号線駆動回路 2 3 に出力するものである。所定の補正としては、例えば、ガンマ補正や、オーバードライブ補正などが挙げられる。

#### 【 0 0 4 4 】

信号線駆動回路 2 3 は、例えば、制御信号 2 1 A の入力に応じて（同期して）、映像信号処理回路 2 2 から入力された映像信号 2 2 A に対応するアナログの信号電圧を、各信号線 D T L に印加するものである。信号線駆動回路 2 3 は、例えば、2 種類の電圧 ( V o f s 、 V s i g ) を出力可能となっている。具体的には、信号線駆動回路 2 3 は、走査線駆動回路 2 4 により選択された画素 1 1 へ、信号線 D T L を介して 2 種類の電圧 ( V o f s 、 V s i g ) を供給するようになっている。

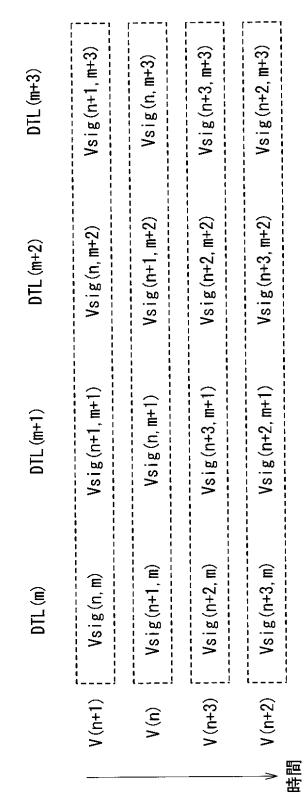

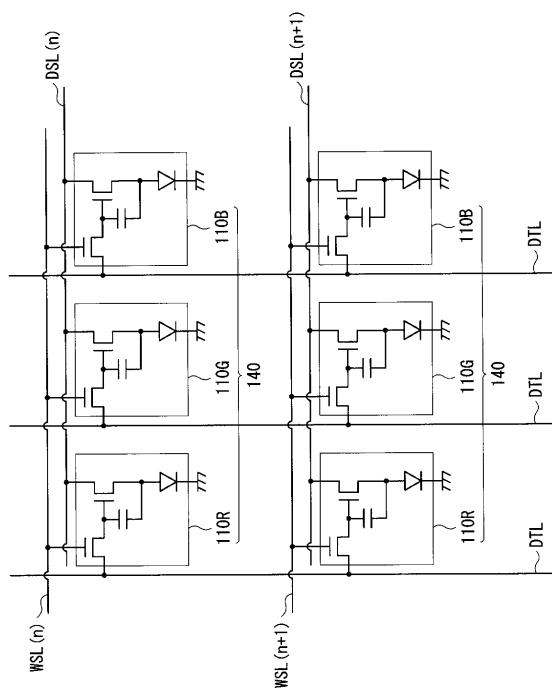

#### 【 0 0 4 5 】

図 5 は、列方向に互いに隣接する 2 つのユニットにおいて列方向に配列された 4 つの表示画素 1 4 に接続された 4 本の信号線 D T L ( D T L ( m ) 、 D T L ( m + 1 ) 、 D T L ( m + 2 ) 、 D T L ( m + 3 ) ) に対して、走査線 W S L の走査に応じて順次、印加される信号電圧 V ( n ) 、 V ( n + 1 ) 、 V ( n + 2 ) 、 V ( n + 3 ) の一例を表したものである。信号線駆動回路 2 3 は、走査線 W S L ( n ) の選択に対応して信号電圧 V ( n ) を出力し、走査線 W S L ( n + 1 ) の選択に対応して信号電圧 V ( n + 1 ) を出力するようになっている。同様に、信号線駆動回路 2 3 は、走査線 W S L ( n + 2 ) の選択に対応して信号電圧 V ( n + 2 ) を出力し、走査線 W S L ( n + 3 ) の選択に対応して信号電圧 V ( n + 3 ) を出力するようになっている。ここで、走査線駆動回路 2 4 は、後述するように、信号電圧の書き込みに際して、走査線 W S L を、 W S L ( n + 1 ) 、 W S L ( n ) 、 W S L ( n + 3 ) 、 W S L ( n + 2 ) の順に選択するようになっている。そのため、信号線駆動回路 2 3 は、信号電圧の書き込みに際して、信号電圧 V s i g を、 V ( n + 1 ) 、 V ( n ) 、 V ( n + 3 ) 、 V ( n + 2 ) の順に出力するようになっている。

#### 【 0 0 4 6 】

信号線駆動回路 2 3 は、例えば、図 5 に示したように、走査線駆動回路 2 4 により同時に選択された複数の画素 1 1 のうち、 $n$  表示画素行に属する複数の画素 1 1 に対しては、偶数番目の信号線 D T L ( m ) , D T L ( m + 2 ) を介して、 $n$  表示画素行に対応する電圧 V s i g ( V s i g ( n , m ) , V s i g ( n , m + 2 ) ) を供給するようになっている。さらに、信号線駆動回路 2 3 は、走査線駆動回路 2 4 により同時に選択された複数の画素 1 1 のうち、 $n + 1$  表示画素行に属する複数の画素 1 1 に対しては、奇数番目の信号線 D T L ( m + 1 ) , D T L ( m + 3 ) を介して、 $n + 1$  表示画素行に対応する電圧 V s i g ( V s i g ( n + 1 , m + 1 ) , V s i g ( n + 1 , m + 3 ) ) を供給するようになっている。

#### 【 0 0 4 7 】

10

20

30

40

50

つまり、信号線駆動回路 23 は、信号書き込み時に、走査線 WSL(n) が選択されたときには、偶数番目の信号線 DTL(m), DTL(m+2) に対して n 表示画素行に対応する電圧 Vsig(n, m), Vsig(n, m+2) を出力すると同時に、奇数番目の信号線 DTL(m+1), DTL(m+3) に対して n+1 表示画素行に対応する電圧 Vsig(n+1, m+1), Vsig(n+1, m+3) を出力するようになっている。また、信号線駆動回路 23 は、信号書き込み時に、走査線 WSL(n+1) が選択されたときには、偶数番目の信号線 DTL(m), DTL(m+2) に対して n+1 表示画素行に対応する電圧 Vsig(n+1, m), Vsig(n+1, m+2) を出力すると同時に、奇数番目の信号線 DTL(m+1), DTL(m+3) に対して n 表示画素行に対応する電圧 Vsig(n, m+1), Vsig(n, m+3) を出力するようになっている。なお、信号線駆動回路 23 は、n+2 画素行および n+3 画素行についても、n 画素行および n+1 画素行と同様にして、電圧を印加するようになっている。10

#### 【0048】

Vsig は、映像信号 20A に対応する電圧値となっている。Vofs は、映像信号 20A とは無関係の一定電圧である。Vsig の最小電圧は Vofs よりも低い電圧値となっており、Vsig の最大電圧は Vofs よりも高い電圧値となっている。

#### 【0049】

走査線駆動回路 24 により同時に選択された複数の画素 11 のうち、偶数番目の信号線 DTL(m) と、奇数番目の信号線 DTL(m+1) との間に配置された 2 つの画素 11 は、発光色の互いに等しい画素である。同様に、走査線駆動回路 24 により同時に選択された複数の画素 11 のうち、偶数番目の信号線 DTL(m+2) と、奇数番目の信号線 DTL(m+3) との間に配置された 2 つの画素 11 も、発光色の互いに等しい画素である。従って、信号線駆動回路 23 は、走査線 WSL(n) が選択されたときに、信号線 DTL(m), DTL(m+1) に対して、発光色の互いに等しい画素に対応する電圧 Vsig を出力すると同時に、信号線 DTL(m+2), DTL(m+3) に対して、別の種類で発光色の互いに等しい画素に対応する電圧 Vsig を出力するようになっている。例えば、信号線駆動回路 23 は、走査線 WSL(n) が選択されたときに、信号線 DTL(m), DTL(m+1) に対して、画素 11R に対応する電圧 Vsig を出力すると同時に、信号線 DTL(m+2), DTL(m+3) に対して、画素 11W に対応する電圧 Vsig を出力するようになっている。2030

#### 【0050】

走査線駆動回路 24 は、例えば、制御信号 21A の入力に応じて（同期して）、複数の走査線 WSL を所定のシーケンスで選択することにより、Vth 補正や、信号電圧 Vsig の書き込み、および  $\mu$  補正を所望の順番で実行させるものである。ここで、Vth 補正とは、駆動トランジスタ Tr1 のゲート - ソース間電圧 Vgs を駆動トランジスタの閾値電圧に近づける補正動作を指している。信号電圧 Vsig の書き込み（信号書き込み）とは、駆動トランジスタ Tr1 のゲートに対して、信号電圧 Vsig を、書込トランジスタ Tr2 を介して書き込む動作を指している。 $\mu$  補正とは、駆動トランジスタ Tr1 のゲート - ソース間に保持される電圧 Vgs を、駆動トランジスタ Tr1 の移動度  $\mu$  の大きさに応じて補正する動作を指している。信号書き込みと、 $\mu$  補正とは、互いに別個のタイミングで行われることもある。本実施の形態では、走査線駆動回路 24 が、1 つの選択パルスを、走査線 WSL へ出力することによって、信号書き込みと、 $\mu$  補正とを同時に（もしくは間髪空けずに連続して）行うようになっている。40

#### 【0051】

ところで、駆動回路 20 は、Vth 補正および信号書き込みをユニットごとに一括して実行するようになっている。具体的には、駆動回路 20 は、図 6 に示したように、第 1 のユニットで、Vth 補正および信号書き込みを実行した後に、第 1 のユニットと列方向において隣接する第 2 のユニットで、Vth 補正および信号書き込みを実行するようになっている。つまり、駆動回路 20 は、一連の動作（Vth 補正および信号書き込み）を、ユニット単位で順次、実行するようになっている。50

## 【0052】

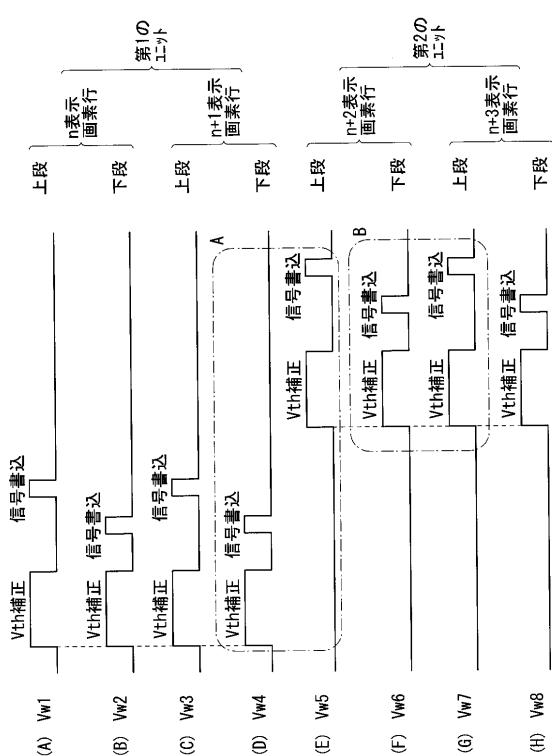

なお、図6は、列方向に互いに隣接する2つのユニット内の各サブピクセル行に印加される選択パルスの経時変化の一例を表したものである。図6において、Vw1は、n表示画素行における上段のサブピクセル行に対応して設けられた走査線WSLの分枝の電圧波形である。Vw2は、n表示画素行における下段のサブピクセル行に対応して設けられた走査線WSLの分枝の電圧波形である。Vw3は、n+1表示画素行における上段のサブピクセル行に対応して設けられた走査線WSLの分枝の電圧波形である。Vw4は、n+1表示画素行における下段のサブピクセル行に対応して設けられた走査線WSLの分枝の電圧波形である。Vw5は、n+2表示画素行における上段のサブピクセル行に対応して設けられた走査線WSLの分枝の電圧波形である。Vw6は、n+2表示画素行における下段のサブピクセル行に対応して設けられた走査線WSLの分枝の電圧波形である。Vw7は、n+3表示画素行における上段のサブピクセル行に対応して設けられた走査線WSLの分枝の電圧波形である。Vw8は、n+3表示画素行における下段のサブピクセル行に対応して設けられた走査線WSLの分枝の電圧波形である。なお、図6中で一点鎖線で囲んだA,Bについては、後に詳述する。

## 【0053】

走査線駆動回路24は、Vth補正に際しては、1ユニットに含まれる全ての走査線WSLを、同時に（または同時期に）選択するようになっている。具体的には、走査線駆動回路24は、Vth補正に際しては、1ユニットに含まれる2本の走査線WSL(n), WSL(n+1)を、同時に（または同時期に）選択するようになっている。つまり、走査線駆動回路24は、Vth補正に際しては、n表示画素行の上段のサブピクセル行に含まれる複数の画素11（例えば画素11R, 11W）と、n表示画素行の下段のサブピクセル行に含まれる複数の画素11（例えば画素11G, 11B）と、n+1表示画素行の上段のサブピクセル行に含まれる複数の画素11（例えば画素11R, 11W）と、n+1表示画素行の下段のサブピクセル行に含まれる複数の画素11（例えば画素11G, 11B）とを、同時に（または同時期に）選択するようになっている。

## 【0054】

さらに、走査線駆動回路24は、信号書き込みに際しては、1ユニットに含まれる複数の走査線WSLを、一連の動作（Vth補正および信号書き込み）をユニット単位で順次実行する際の走査方向（以下、「ユニット走査方向」と称する。）とは反対方向に順次、選択するようになっている。ユニット走査方向は、例えば、表示パネル10の上端側から下端側に向かう方向と平行な方向である。従って、走査線駆動回路24は、1表示画素行における各画素11への信号書き込みを、第2配線に接続された各画素11に対して実行したのち、第1配線に接続された各画素11に対して実行するようになっている。なお、ユニット走査方向は、表示パネル10の下端側から上端側に向かう方向と平行な方向であつてもよい。このときは、図示しないが、走査線駆動回路24は、1表示画素行における各画素11への信号書き込みを、第1配線に接続された各画素11に対して実行したのち、第2配線に接続された各画素11に対して実行するようになっている。

## 【0055】

走査線駆動回路24は、信号書き込みに際して、1ユニットに含まれる2つの走査線WSL(n), WSL(n+1)を、走査線WSL(n+1)、走査線WSL(n)の順に選択するようになっている。そのため、走査線駆動回路24は、信号書き込みに際して、走査線WSL(n+1)を介して、n表示画素行の下段のサブピクセル行に含まれる複数の画素11と、n+1表示画素行の下段のサブピクセル行に含まれる複数の画素11とを同時に選択したのち、走査線WSL(n)を介して、n表示画素行の上段のサブピクセル行に含まれる複数の画素11と、n+1表示画素行の上段のサブピクセル行に含まれる複数の画素11とを、同時に選択するようになっている。

## 【0056】

走査線駆動回路24は、例えば、2種類の電圧（Von, Voff）を出力可能となっている。具体的には、走査線駆動回路24は、駆動対象の画素11へ、走査線WSLを介

して2種類の電圧( $V_{on}$ 、 $V_{off}$ )を供給し、書込トランジスタTr2のオンオフ制御を行うようになっている。ここで、 $V_{on}$ は、書込トランジスタTr2のオン電圧以上の値となっている。 $V_{on}$ は、後述の「Vth補正準備期間の後半部分」や、「Vth補正期間」、「信号書込・μ補正期間」などに走査線駆動回路24から出力される書込パルスの波高値である。 $V_{off}$ は、書込トランジスタTr2のオン電圧よりも低い値となっており、かつ、 $V_{on}$ よりも低い値となっている。 $V_{off}$ は、後述の「Vth補正準備期間の前半部分」や、「発光期間」などに走査線駆動回路24から出力される書込パルスの波高値である。

#### 【0057】

電源線駆動回路25は、例えば、制御信号21Aの入力に応じて(同期して)、複数の電源線DSLを所定の単位ごとに順次選択するものである。電源線駆動回路25は、例えば、2種類の電圧( $V_{cc}$ 、 $V_{ss}$ )を出力可能となっている。電源線駆動回路25は、走査線駆動回路24により選択された画素11を含む1ユニット全体(つまり1ユニットに含まれる全ての画素11)へ、電源線DSLを介して2種類の電圧( $V_{cc}$ 、 $V_{ss}$ )を供給するようになっている。ここで、 $V_{ss}$ は、有機EL素子13の閾値電圧 $V_{el}$ と、有機EL素子13のカソード電圧 $V_{cath}$ とを足し合わせた電圧( $V_{el} + V_{cath}$ )よりも低い電圧値である。 $V_{cc}$ は、電圧( $V_{el} + V_{cath}$ )以上の電圧値である。

#### 【0058】

[動作] 次に、本実施の形態の表示装置1の動作(消光から発光までの動作)について説明する。本実施の形態では、有機EL素子13のI-V特性が経時変化したり、駆動トランジスタTr1の閾値電圧や移動度が経時変化したりしても、それらの影響を受けることなく、有機EL素子13の発光輝度を一定に保つようにするために、有機EL素子13のI-V特性の変動に対する補償動作および駆動トランジスタTr1の閾値電圧や移動度の変動に対する補正動作を組み込んでいる。

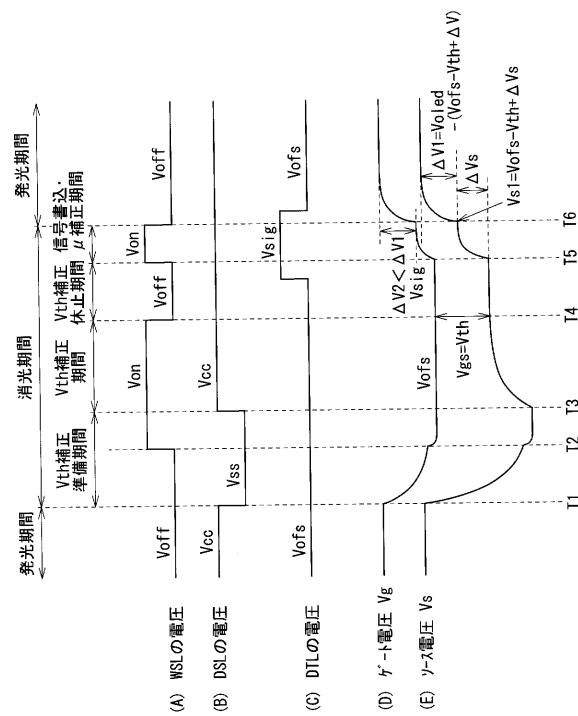

#### 【0059】

図7は、表示装置1における各種波形の一例を表したものである。図7には、走査線WSL、電源線DSLおよび信号線DTLにおいて、時々刻々と2値の電圧変化が生じている様子が示されている。さらに、図7には、走査線WSL、電源線DSLおよび信号線DTLの電圧変化に応じて、駆動トランジスタTr1のゲート電圧 $V_g$ およびソース電圧 $V_s$ が時々刻々と変化している様子が示されている。

#### 【0060】

##### (Vth補正準備期間)

まず、駆動回路20は、駆動トランジスタTr1のゲート-ソース間電圧 $V_{gs}$ を駆動トランジスタTr1の閾値電圧に近づけるVth補正の準備を行う。具体的には、走査線WSLの電圧が $V_{off}$ となっており、信号線DTLの電圧が $V_{of}$ となっており、電源線DSLの電圧が $V_{cc}$ となっている時(つまり有機EL素子13が発光している時)に、電源線駆動回路25は、制御信号21Aに応じて電源線DSLの電圧を $V_{cc}$ から $V_{ss}$ に下げる(T1)。すると、ソース電圧 $V_s$ が $V_{ss}$ まで下がり、有機EL素子13が消光する。このとき、保持容量Csを介したカップリングによりゲート電圧 $V_g$ も下がる。

#### 【0061】

次に、電源線DSLの電圧が $V_{ss}$ となっており、かつ信号線DTLの電圧が $V_{of}$ となっている間に、走査線駆動回路24は、制御信号21Aに応じて走査線WSLの電圧を $V_{off}$ から $V_{on}$ に上げる(T2)。すると、ゲート電圧 $V_g$ が $V_{of}$ まで下がる。このとき、ゲート電圧 $V_g$ とソース電圧 $V_s$ との電位差 $V_{gs}$ が駆動トランジスタTr1の閾値電圧よりも小さくなっていてもよいし、それと等しいか、またはそれよりも大きくなっていてもよい。

#### 【0062】

10

20

30

40

50

(V<sub>t</sub>h補正期間)

次に、駆動回路20は、V<sub>t</sub>hの補正を行う。具体的には、信号線DTLの電圧がV<sub>of</sub>sとなっており、かつ、走査線WSLの電圧がV<sub>on</sub>となっている間に、電源線駆動回路25は、制御信号21Aに応じて電源線DSLの電圧をV<sub>ss</sub>からV<sub>cc</sub>に上げる(T3)。すると、駆動トランジスタTr1のドレイン-ソース間に電流I<sub>ds</sub>が流れ、ソース電圧V<sub>s</sub>が上昇する。このとき、ソース電圧V<sub>s</sub>がV<sub>of</sub>s-V<sub>t</sub>hよりも低い場合(V<sub>t</sub>h補正がまだ完了していない場合)には、駆動トランジスタTr1がカットオフするまで(電位差V<sub>gs</sub>がV<sub>t</sub>hになるまで)、駆動トランジスタTr1のドレイン-ソース間に電流I<sub>ds</sub>が流れる。これにより、ゲート電圧V<sub>g</sub>がV<sub>of</sub>sとなり、ソース電圧V<sub>s</sub>が上昇し、その結果、保持容量C<sub>s</sub>がV<sub>t</sub>hに充電され、電位差V<sub>gs</sub>がV<sub>t</sub>hとなる。

10

【0063】

その後、信号線駆動回路23は、制御信号21Aに応じて信号線DTLの電圧をV<sub>of</sub>sからV<sub>sig</sub>に切り替える前に、走査線駆動回路24が制御信号21Aに応じて走査線WSLの電圧をV<sub>on</sub>からV<sub>off</sub>fに下げる(T4)。すると、駆動トランジスタTr1のゲートがフローティングとなるので、電位差V<sub>gs</sub>を信号線DTLの電圧の大きさに拘わらずV<sub>t</sub>hのままで維持することができる。このように、電位差V<sub>gs</sub>をV<sub>t</sub>hに設定することにより、駆動トランジスタTr1の閾値電圧V<sub>t</sub>hが画素回路12ごとにばらついた場合であっても、有機EL素子13の発光輝度がばらつくのをなくすることができる。

20

【0064】

(V<sub>t</sub>h補正休止期間)

その後、V<sub>t</sub>h補正の休止期間中に、信号線駆動回路23は、信号線DTLの電圧をV<sub>of</sub>sからV<sub>sig</sub>に切り替える。

【0065】

(信号書き込み・μ補正期間)

V<sub>t</sub>h補正休止期間が終了した後(つまりV<sub>t</sub>h補正が完了した後)、駆動回路20は、映像信号20Aに応じた信号電圧の書き込みと、μ補正を行う。具体的には、信号線DTLの電圧がV<sub>sig</sub>となっており、かつ電源線DSLの電圧がV<sub>cc</sub>となっている間に、走査線駆動回路24は、制御信号21Aに応じて走査線WSLの電圧をV<sub>off</sub>fからV<sub>on</sub>に上げ(T5)、駆動トランジスタTr1のゲートを信号線DTLに接続する。すると、駆動トランジスタTr1のゲート電圧V<sub>g</sub>が信号線DTLの電圧V<sub>sig</sub>となる。このとき、有機EL素子13のアノード電圧はこの段階ではまだ有機EL素子13の閾値電圧V<sub>e1</sub>よりも小さく、有機EL素子13はカットオフしている。そのため、電流I<sub>ds</sub>は有機EL素子13の素子容量C<sub>ole</sub>dおよび補助容量C<sub>sub</sub>bに流れ、素子容量C<sub>ole</sub>dおよび補助容量C<sub>sub</sub>bが充電されるので、ソース電圧V<sub>s</sub>がV<sub>s</sub>だけ上昇し、やがて電位差V<sub>gs</sub>がV<sub>sig</sub>+V<sub>t</sub>h-V<sub>s</sub>となる。このようにして、書き込みと同時にμ補正が行われる。ここで、駆動トランジスタTr1の移動度μが大きい程、V<sub>s</sub>も大きくなるので、電位差V<sub>gs</sub>を発光前にV<sub>s</sub>だけ小さくすることにより、画素11ごとの移動度μのばらつきを取り除くことができる。

30

【0066】

(発光)

最後に、走査線駆動回路24は、制御信号21Aに応じて走査線WSLの電圧をV<sub>on</sub>からV<sub>off</sub>fに下げる(T6)。すると、駆動トランジスタTr1のゲートがフローティングとなり、駆動トランジスタTr1のドレイン-ソース間に電流I<sub>ds</sub>が流れ、ソース電圧V<sub>s</sub>が上昇する。その結果、有機EL素子13に閾値電圧V<sub>e1</sub>以上の電圧が印加され、有機EL素子13が所望の輝度で発光する。

40

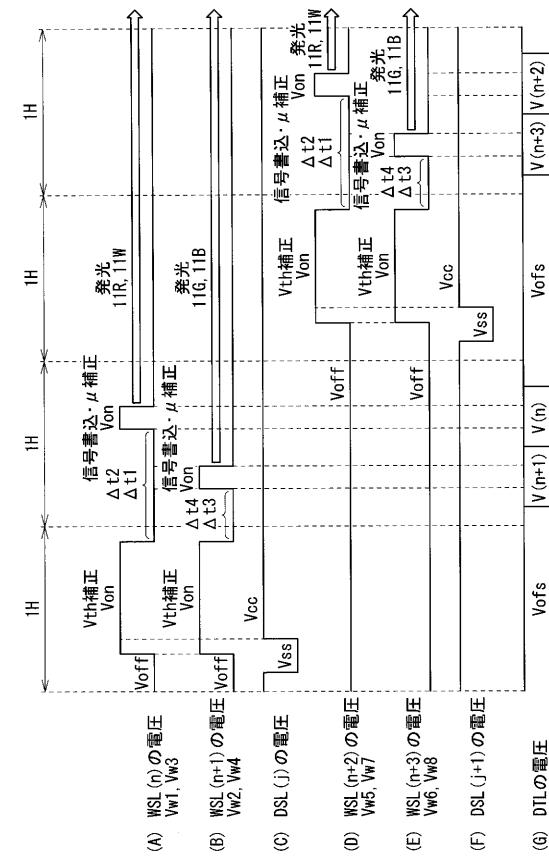

【0067】

次に、図7、図8を参照しつつ、本実施の形態の表示装置1におけるV<sub>t</sub>h補正と信号書き込み・μ補正の走査の一例について説明する。なお、図8は、列方向に互いに隣接する

50

2つのユニットにおけるVth補正と信号書き込み・μ補正の走査の一例を表したものである。

#### 【0068】

なお、以下では、1ユニット内の全ての画素11を、接続された走査線WSLごとにグループに分けたものとして、説明を行う。本実施の形態では、1ユニット内の全ての画素11Rおよび全ての画素11Wが1つのグループとなり、そのユニット内の全ての画素11Gおよび全ての画素11Bが1つのグループとなる。そこで、以下では、走査線WSL(n)、WSL(n+1)が接続されたユニット内の全ての画素11Rおよび全ての画素11Wが第1のグループとなっており、そのユニット内の全ての画素11Gおよび全ての画素11Bが第2のグループとなっているものとする。さらに、走査線WSL(n+2)、WSL(n+3)が接続されたユニット内の全ての画素11Rおよび全ての画素11Wが第3のグループとなっており、そのユニット内の全ての画素11Gおよび全ての画素11Bが第4のグループとなっているものとする。10

#### 【0069】

駆動回路20は、Vth補正を1ユニット内の全てのグループ（第1および第2のグループ）に対して同時期に行ったのち、信号書き込みを、そのユニット内の全てのグループ（第1および第2のグループ）に対して、グループごとに順番に行う。このとき、駆動回路20は、信号書き込みを、1画素行内の下段に配置された画素11からなる第2のグループに対して行ったのち、その画素行内の上段に配置された画素11からなる第1のグループに対して行う。20

#### 【0070】

その後、駆動回路20は、Vth補正を次のユニット内の全てのグループ（第3および第4のグループ）に対して同時期に行ったのち、信号書き込みを、そのユニット内の全てのグループ（第3および第4のグループ）に対して、グループごとに順番に行う。このとき、駆動回路20は、上記と同様に、信号書き込みを、1画素行内の下段に配置された画素11からなる第4のグループに対して行ったのち、1画素行内の上段に配置された画素11からなる第3のグループに対して行う。

#### 【0071】

このとき、駆動回路20は、1つのユニットに対して、1水平期間(1H)内でVth補正を行ったのち、次の1水平期間(1H)内で、信号書き込みを行う。つまり、駆動回路20は、1つのユニットに対して、2水平期間(2H)を連続して使って、Vth補正と、信号書き込みとを行う。30

#### 【0072】

さらに、駆動回路20は、グループごとに信号書き込みを行う際に、そのグループに含まれる全ての画素11に対して信号書き込みを同時に使う。具体的には、駆動回路20は、走査線WSL(n)が選択されたときには、各信号線DTLに対して、上述の電圧V(n)を出力する。すなわち、駆動回路20は、走査線WSL(n)が選択されたときには、偶数番目の信号線DTL(DTL(m)、DTL(m+2))に対してn画素行目の電圧Vsig(Vsig(n,m),Vsig(n,m+2))を出力すると同時に、奇数番目の信号線DTL(m+1)、DTL(m+3)に対してn+1画素行に対応する電圧Vsig(Vsig(n+1,m+1),Vsig(n+1,m+3))を出力する。さらに、駆動回路20は、走査線WSL(n+1)が選択されたときには、偶数番目の信号線DTL(DTL(m)、DTL(m+2))に対してn+1画素行目の電圧Vsig(Vsig(n+1,m),Vsig(n+1,m+2))を出力すると同時に、奇数番目の信号線DTL(m+1)、DTL(m+3)に対してn画素行に対応する電圧Vsig(Vsig(n,m+1),Vsig(n,m+3))を出力する。40

#### 【0073】

そのようにした結果、同一色の各画素11Rにおいて、Vth補正が終わってからμ補正が始まるまでの期間（いわゆる、待ち時間t1）が一致するので、複数の画素11Rにおける待ち時間t1が画素行ごとに一致する。本実施の形態では、各画素11Wの待50

ち時間  $t_2$  は、各画素 11 R の待ち時間  $t_1$  と等しい。そのため、同一色の各画素 11 W においても、待ち時間  $t_2$  が一致するので、複数の画素 11 W における待ち時間  $t_2$  が画素行ごとに一致する。さらに、同一色の各画素 11 G においても、待ち時間  $t_3$  が一致するので、複数の画素 11 G における待ち時間  $t_3$  が画素行ごとに一致する。本実施の形態では、各画素 11 B の待ち時間  $t_4$  は、各画素 11 G の待ち時間  $t_3$  と等しい。そのため、同一色の各画素 11 B においても、待ち時間  $t_4$  が一致するので、複数の画素 11 B における待ち時間  $t_4$  が画素行ごとに一致する。なお、画素 11 R, 11 W の待ち時間  $t_1, t_2$  と、画素 11 G, 11 B の待ち時間  $t_3, t_4$  とが互いに異なるが、これは色再現性に若干影響するだけであり、色むらに影響することはない。

10

#### 【0074】

次に、カソード線 CTL を介した複数の画素におけるカップリングについて説明する。図 9 は、図 6 中で一点鎖線で丸を付した A 内のそれぞれの波形が印加される 2 つの画素 11 におけるカップリングの様子を表したものである。図 10 は、図 6 中で一点鎖線で丸を付した B 内のそれぞれの波形が印加される 2 つの画素 11 におけるカップリングの様子を表したものである。なお、図 9 において、カップリングの発生元が  $n+1$  表示画素行の下段の画素 11 となっており、カップリングの影響を受ける画素が  $n+2$  表示画素行の上段の画素 11 となっている。また、図 10 において、カップリングの発生元が  $n+2$  表示画素行の下段の画素 11 となっており、カップリングの影響を受ける画素が  $n+3$  表示画素行の上段の画素 11 となっている。

20

#### 【0075】

$n+1$  表示画素行の下段の画素 11 ( 例えば、画素 11 G ) の補助容量  $C_{sub}$  と、 $n+2$  表示画素行の上段の画素 11 ( 例えば、画素 11 R ) の補助容量  $C_{sub}$  とは、図 3、図 4 に示したように、カソード線 CTL を介して互いに接続されている。そのため、 $n+1$  表示画素行の下段の画素 11 において、信号書き込みが行われると、 $n+1$  表示画素行の下段の画素 11 の駆動トランジスタ Tr 1 のソース電圧  $V_s$  の変動 ( 上昇 ) が、カソード線 CTL および補助容量  $C_{sub}$  を介して、 $n+2$  表示画素行の上段の画素 11 の駆動トランジスタ Tr 1 のソース電極に伝播する。その結果、 $n+2$  表示画素行の上段の画素 11 の駆動トランジスタ Tr 1 において、ソース電圧  $V_s$  が変動 ( 上昇 ) し、それに伴ってゲート電圧  $V_g$  も変動 ( 上昇 ) する。このとき、ゲート - ソース間電圧  $V_{gs}$  には、ソース電圧  $V_s$  およびゲート電圧  $V_g$  の変動の前後で大きな変化はない。しかし、 $n+2$  表示画素行の上段の画素 11 では、そのような電圧変動が起こった後に、 $V_{th}$  補正が行われる。このとき、ソース電圧  $V_s$  には、ゲート電圧  $V_g$  の大きさに応じた変動 ( 上昇 ) が生じるので、ソース電圧  $V_s$  は、ゲート電圧  $V_g$  の上昇分だけ余計に変動 ( 上昇 ) する。その結果、 $V_{th}$  補正後のゲート - ソース間電圧  $V_{gs}$  は、カップリングの影響を受けている場合よりも小さくなる。

30

#### 【0076】

一方、 $n+2$  表示画素行の下段の画素 11 ( 例えば、画素 11 G ) の補助容量  $C_{sub}$  と、 $n+3$  表示画素行の上段の画素 11 ( 例えば、画素 11 R ) の補助容量  $C_{sub}$  とは、図 4 に示したように、カソード線 CTL を介して互いに接続されている。そのため、 $n+2$  表示画素行の下段の画素 11 において、信号書き込みが行われると、 $n+2$  表示画素行の下段の画素 11 の駆動トランジスタ Tr 1 のソース電圧  $V_s$  の変動 ( 上昇 ) が、カソード線 CTL および補助容量  $C_{sub}$  を介して、 $n+3$  表示画素行の上段の画素 11 の駆動トランジスタ Tr 1 のソース電極に伝播する。その結果、 $n+3$  表示画素行の上段の画素 11 の駆動トランジスタ Tr 1 において、ソース電圧  $V_s$  が変動 ( 上昇 ) し、それに伴ってゲート電圧  $V_g$  も変動 ( 上昇 ) する。このとき、ゲート - ソース間電圧  $V_{gs}$  には、ソース電圧  $V_s$  およびゲート電圧  $V_g$  の変動の前後で大きな変化はない。しかし、 $n+3$  表示画素行の上段の画素 11 では、そのような電圧変動が起こった後に、信号書き込み ( および  $\mu$  補正 ) が行われる。このとき、ゲート電圧  $V_g$  は、ゲート電圧  $V_g$  の上昇分だけ、 $V_{off}$  よりも大きな電圧値となっている。そのため、実効的な信号電圧が減少するの

40

50

で、信号書き込み（および $\mu$ 補正）時のゲート - ソース間電圧 $V_{g_s}$ は、カップリングの影響を受けていない場合よりも小さくなる。

#### 【0077】

このように、本実施の形態では、 $n+1$ 表示画素行の下段の画素 $1_1$ における信号書き込みが $n+2$ 表示画素行の上段の画素 $1_1$ へ与える影響と、 $n+2$ 表示画素行の下段の画素 $1_1$ における信号書き込みが $n+3$ 表示画素行の上段の画素 $1_1$ へ与える影響とが、互いに等しくなっている。つまり、複数の画素 $1_1$ 間でカップリングが生じるような回路構成となっている場合であっても、カップリングによる影響を受けるすべての画素 $1_1$ において、その影響の受け方の傾向が一致する。これにより、カップリングによる影響を受けるすべての画素 $1_1$ において、発光輝度の変化の傾向がほぼ一致する。

10

#### 【0078】

##### [効果]

次に、本実施の形態の表示装置1における効果について説明する。

#### 【0079】

図11は、従来から一般的に用いられる画素配列の一例を表したものである。従来では、表示画素140に含まれる各画素 $110R$ ,  $110G$ ,  $110B$ が共通の走査線 $W_{SL}(n)$ および電源線 $D_{SL}(n)$ に接続されている。このような画素配列となっている場合に、例えば、図12に示したように、 $V_{th}$ 補正および信号書き込みが1H期間ごとに行われるときには、1H期間を短くし、1H当たりの走査期間を短くする（つまり、高速駆動化する）ことが難しかった。そのため、例えば、図13に示したように、 $V_{th}$ 補正が共通の1H期間内に2ラインまとめて行われたのち、信号書き込みが次の1H期間内にラインごとに行われる。この駆動方法は、 $V_{th}$ 補正が束ねられていることから、高速駆動に向いている。しかし、 $V_{th}$ 補正が終わってから信号書き込みが始まるまでの待ち時間 $t$ がラインごとに異なる。そのため、同一階調の信号電圧がそれぞれのラインの駆動トランジスタのゲートに印加されたとしても、図14に示したように、発光輝度がラインごとに異なってしまい、輝度ムラが生じるという問題があった。

20

#### 【0080】

一方、本実施の形態では、各画素 $1_1$ の選択に用いられる各走査線 $W_{SL}$ が、1ユニット内で同一発光色の複数の画素 $1_1$ に接続されている。さらに、各画素 $1_1$ への駆動電流の供給に用いられる各電源線 $D_{SL}$ が、1ユニット内の全ての画素 $1_1$ に接続されている。これにより、上述したように、 $V_{th}$ 補正を、1ユニット内の全てのグループに対して同時期に行ったのち、信号電圧の書き込みを、そのユニット内の全てのグループに対してグループごとに行うことができる。その結果、同一色の各画素 $1_1$ において、 $V_{th}$ 補正が終わってから $\mu$ 補正が始まるまでの待ち時間が一致するので、同一色の画素 $1_1$ における待ち時間がラインごとに一致する。従って、 $V_{th}$ 補正を束ねたことによる輝度ムラの発生を低減することができる。

30

#### 【0081】

図15は、比較例に係る表示装置において、列方向に互いに隣接する2つのユニットにおける $V_{th}$ 補正と信号書き込み・ $\mu$ 補正の走査の一例を表したものである。図16は、列方向に互いに隣接する2つのユニット内の各サブピクセル行に印加される選択パルスの経時変化の一例を表す波形図である。なお、比較例に係る表示装置において、画素構成は、上記実施の形態の画素構成と同一となっている。

40

#### 【0082】

本比較例では、駆動回路20は、本実施の形態と同様に、 $V_{th}$ 補正を1ユニット内の全てのグループ（第1および第2のグループ）に対して同時期に行ったのち、信号電圧の書き込み（および $\mu$ 補正）を、そのユニット内の全てのグループ（第1および第2のグループ）に対して、グループごとに順番に行う。このとき、走査線駆動回路24は、信号書き込みに際しては、1ユニットに含まれる複数の走査線 $W_{SL}$ を、一連の動作（ $V_{th}$ 補正および信号書き込み）をユニット単位で順次実行する際の走査方向（以下、「ユニット走査方向」と称する。）と同一の方向に順次、選択するようになっている。そのようにし

50

た結果、同一色の各画素 1 1において、V t h 補正が終わってから  $\mu$  補正が始まるまでの期間（いわゆる、待ち時間）が一致するので、同一色の各画素 1 1における待ち時間が画素行ごとに一致する。この点では、比較例に係る表示装置と、上記実施の形態に係る表示装置 1との間に相違は無い。

#### 【0083】

次に、本比較例におけるカップリングについて説明する。図 17 は、図 16 中で一点鎖線で丸を付した D 内のそれぞれの波形が印加される 2 つの画素 1 1におけるカップリングの様子を表したものである。なお、図 16 中で一点鎖線で丸を付した C 内のそれぞれの波形が印加される 2 つの画素 1 1におけるカップリングの様子は、図 9 と同様である。

#### 【0084】

本比較例において、n + 2 表示画素行の下段の画素 1 1（例えば、画素 1 1 G）の補助容量 C sub と、n + 3 表示画素行の上段の画素 1 1（例えば、画素 1 1 R）の補助容量 C sub とは、図 4 に示したように、カソード線 CTL を介して互いに接続されている。そのため、n + 2 表示画素行の下段の画素 1 1において、信号書き込みが行われると、n + 2 表示画素行の下段の画素 1 1の駆動トランジスタ Tr 1 のソース電圧 Vs の変動（上昇）が、カソード線 CTL および補助容量 C sub を介して、n + 3 表示画素行の上段の画素 1 1の駆動トランジスタ Tr 1 のソース電極に伝播する。その結果、n + 3 表示画素行の上段の画素 1 1の駆動トランジスタ Tr 1 において、ソース電圧 Vs が変動（上昇）し、それに伴ってゲート電圧 Vg も変動（上昇）する。このとき、ゲート - ソース間電圧 Vgs には、ソース電圧 Vs およびゲート電圧 Vg の変動の前後で大きな変化はない。

ところで、本比較例では、そのような電圧変動は、信号書き込み（および  $\mu$  補正）の後に生じる。そのため、次の消光期間が始まるまでの間（つまり、発光期間の間）、ゲート - ソース間電圧 Vgs には、特段の変化はない。

#### 【0085】

このように、本比較例では、n + 1 表示画素行の下段の画素 1 1における信号書き込みが n + 2 表示画素行の上段の画素 1 1へ与える影響と、n + 2 表示画素行の下段の画素 1 1における信号書き込みが n + 3 表示画素行の上段の画素 1 1へ与える影響とが、互いに異なっている。そのため、n + 2 表示画素行の上段の画素 1 1では、ゲート - ソース間電圧 Vgs が小さくなつことに起因して、発光輝度が若干暗くなる。その一方で、n + 3 表示画素行の上段の画素 1 1では、ゲート - ソース間電圧 Vgs に変化が生じていないことに起因して、発光輝度が n + 2 表示画素行の上段の画素 1 1の発光輝度よりも明るくなる。その結果、図 14 に示したような輝度ムラが生じてしまう。

#### 【0086】

一方、上記実施の形態では、上述したように、n + 1 表示画素行の下段の画素 1 1における信号書き込みが n + 2 表示画素行の上段の画素 1 1へ与える影響と、n + 2 表示画素行の下段の画素 1 1における信号書き込みが n + 3 表示画素行の上段の画素 1 1へ与える影響とが、互いに等しくなっている。つまり、複数の画素 1 1間でカップリングが生じるような回路構成となっている場合であつても、カップリングによる影響を受けるすべての画素 1 1において、その影響の受け方の傾向が一致する。これにより、カップリングによる影響を受けるすべての画素 1 1において、発光輝度の変化の傾向がほぼ一致するので、輝度ムラを低減することができる。

#### 【0087】

##### <2. 変形例>

以下に、上記実施の形態の表示装置 1 の種々の変形例について説明する。なお、以下では、上記実施の形態の表示装置 1 と共に通する構成要素に対しては、同一の符号が付与される。さらに、上記実施の形態の表示装置 1 と共に通する構成要素についての説明は、適宜、省略されるものとする。

#### 【0088】

##### [変形例 1]

上記実施の形態において、複数の走査線 WSL は、1 ユニットごとに 2 本ずつ割り当て

10

20

30

40

50

られ、1ユニットに含まれる走査線W S Lの数が2となっていた。しかし、図示しないが、複数の走査線W S Lが、1ユニットごとに、1ユニットに含まれる画素行の数と同じ数ずつ割り当てられ、1ユニットに含まれる走査線W S Lの数が、1ユニットに含まれる画素行の数と同じ数となっていてもよい。ただし、その場合には、複数の走査線W S Lは、2本ごとに同一の電圧が印加されるようになっている。

## 【0089】

## [変形例2]

上記実施の形態において、複数の電源線D S Lは、1ユニットごとに1本ずつ割り当てられ、1ユニットに含まれる電源線D S Lの数が1となっていた。しかし、図示しないが、複数の電源線D S Lが、1ユニットごとに、1ユニットに含まれる画素行の数と同じ数ずつ割り当てられ、1ユニットに含まれる電源線D S Lの数が、1ユニットに含まれる画素行の数と同じ数となっていてもよい。ただし、その場合には、複数の電源線D S Lは、10ユニットごとに同一の電圧が印加されるようになっている。

## 【0090】

## [変形例3]

上記実施の形態において、1ユニット内で行が互いに異なり、かつ互いに隣接する2つの表示画素14において、発光色の互いに等しい2つの画素11が共通の2本の信号線D T Lの間に配置されていた。しかし、1ユニット内で行が互いに異なり、かつ互いに隣接する2つの表示画素14において、発光色の互いに等しい2つの画素11のうち一方の画素11が、2本の信号線D T L(m), D T L(m+1)の間に配置され、他方の画素11が、2本の信号線D T L(m+2), D T L(m+3)の間に配置されていてもよい。例えば、1ユニット内で行が互いに異なり、かつ互いに隣接する2つの表示画素14において、2つの画素11Rのうち一方の画素11Rが、2本の信号線D T L(m), D T L(m+1)の間に配置され、他方の画素11Rが、2本の信号線D T L(m+2), D T L(m+3)の間に配置されていてもよい。

## 【0091】

## [変形例4]

上記実施の形態では、表示画素14が、発光色の互いに異なる4つの画素11によって構成されていた。さらに、各表示画素14において、4つの画素11は、いわゆる田の字配列(square4)となっており、 $2 \times 2$ のマトリクスで配置されていた。しかし、表示画素14が、発光色の互いに異なる6つ以上の偶数個の画素11によって構成されていてもよい。このとき、各表示画素14において、6つ以上の偶数個の画素11は、 $2 \times a$ のマトリクスで配置されていてもよい。ここで、aは、(表示画素14内の画素11の数)/2である。

## 【0092】

## &lt;3. 適用例&gt;

以下、上記実施の形態およびその変形例(以下、「上記実施の形態等」と称する。)で説明した表示装置1の適用例について説明する。上記実施の形態等の表示装置1は、テレビジョン装置、デジタルカメラ、ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラなど、外部から入力された映像信号あるいは内部で生成した映像信号を、画像あるいは映像として表示するあらゆる分野の電子機器の表示装置に適用することが可能である。

## 【0093】

## (適用例1)

図18は、上記実施の形態等の表示装置1が適用されるテレビジョン装置の外観を表したものである。このテレビジョン装置は、例えば、フロントパネル310およびフィルターガラス320を含む映像表示画面部300を有しており、この映像表示画面部300は、上記実施の形態等に係る表示装置1により構成されている。

## 【0094】

## (適用例 2 )

図 19 は、上記実施の形態等の表示装置 1 が適用されるデジタルカメラの外観を表したものである。このデジタルカメラは、例えば、フラッシュ用の発光部 410 、表示部 420 、メニュースイッチ 430 およびシャッターボタン 440 を有しており、その表示部 420 は、上記実施の形態等に係る表示装置 1 により構成されている。

## 【 0095】

## (適用例 3 )

図 20 は、上記実施の形態等の表示装置 1 が適用されるノート型パーソナルコンピュータの外観を表したものである。このノート型パーソナルコンピュータは、例えば、本体 510 , 文字等の入力操作のためのキー ボード 520 および画像を表示する表示部 530 を有しており、その表示部 530 は、上記実施の形態等に係る表示装置 1 により構成されている。

10

## 【 0096】

## (適用例 4 )

図 21 は、上記実施の形態等の表示装置 1 が適用されるビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部 610 , この本体部 610 の前方側面に設けられた被写体撮影用のレンズ 620 , 撮影時のスタート / ストップスイッチ 630 および表示部 640 を有しており、その表示部 640 は、上記実施の形態等に係る表示装置 1 により構成されている。

20

## 【 0097】

## (適用例 5 )

図 22 は、上記実施の形態等の表示装置 1 が適用される携帯電話機の外観を表したものである。この携帯電話機は、例えば、上側筐体 710 と下側筐体 720 とを連結部 ( ヒンジ部 ) 730 で連結したものであり、ディスプレイ 740 , サブディスプレイ 750 , ピクチャーライト 760 およびカメラ 770 を有している。そのディスプレイ 740 またはサブディスプレイ 750 は、上記実施の形態等に係る表示装置 1 により構成されている。

20

## 【 0098】

以上、実施の形態および適用例を挙げて本技術を説明したが、本技術は上記実施の形態等に限定されるものではなく、種々変形が可能である。

## 【 0099】

例えば、上記実施の形態等では、アクティブマトリクス駆動のための画素回路 12 の構成は、上記各実施の形態で説明したものに限られず、必要に応じて容量素子やトランジスタを追加してもよい。その場合、画素回路 12 の変更に応じて、上述した信号線駆動回路 23 や、走査線駆動回路 24 、電源線駆動回路 25 などの他に、必要な駆動回路を追加してもよい。

30

## 【 0100】

また、上記実施の形態等では、信号線駆動回路 23 、走査線駆動回路 24 および電源線駆動回路 25 の駆動をタイミング生成回路 21 および映像信号処理回路 22 が制御していたが、他の回路がこれらの駆動を制御するようにしてもよい。また、信号線駆動回路 23 、走査線駆動回路 24 および電源線駆動回路 25 の制御は、ハードウェア ( 回路 ) で行われていてもよいし、ソフトウェア ( プログラム ) で行われていてもよい。

40

## 【 0101】

また、上記実施の形態等では、書込トランジスタ Tr2 のソースおよびドレインや、駆動トランジスタ Tr1 のソースおよびドレインが固定されたものとして説明されていたが、いうまでもなく、電流の流れる向きによっては、ソースとドレインの対向関係が上記の説明とは逆になることがある。そのときは、上記実施の形態等において、ソースをドレインと読み替えるとともに、ドレインをソースと読み替えてよい。

## 【 0102】

また、上記実施の形態等では、書込トランジスタ Tr2 および駆動トランジスタ Tr1 が n チャネル M O S 型の T F T により形成されているものとして説明されていたが、書込

50

トランジスタTr2および駆動トランジスタTr1の少なくとも一方がpチャネルMOS型のTFTにより形成されていてもよい。なお、駆動トランジスタTr1がpチャネルMOS型のTFTにより形成されている場合には、上記実施の形態等において、有機EL素子13のアノードがカソードとなり、有機EL素子13のカソードがアノードとなる。また、上記実施の形態等において、書込トランジスタTr2および駆動トランジスタTr1は、常に、アモルファスシリコン型のTFTやマイクロシリコン型のTFTである必要はなく、例えば、低温ポリシリコン型のTFTや、酸化物半導体TFTであってもよい。

### 【0103】

また、例えば、本技術は以下のような構成を取ることができる。

(1)

10

表示パネルと、前記表示パネルを駆動する駆動回路とを備え、

前記表示パネルは、複数のサブピクセルを含む複数の画素を有し、

各サブピクセルは、発光素子と、前記発光素子を駆動する駆動トランジスタと、映像信号に対応する信号電圧を前記駆動トランジスタのゲートに書き込む書込トランジスタと、前記駆動トランジスタのゲート-ソース間電圧を保持する保持容量とを含み、

前記駆動回路は、k本(k>2)の画素行を1ユニットとしたときに、第1のユニットで、前記駆動トランジスタのゲート-ソース間電圧を前記駆動トランジスタの閾値電圧に近づけるVth補正、および前記信号電圧の書き込みを実行した後に、前記第1のユニットと列方向において隣接する第2のユニットで、前記Vth補正、および前記信号電圧の書き込みを実行し、

20

前記駆動回路は、1画素行における各サブピクセルへの前記信号電圧の書き込みを、ユニット単位で当該信号電圧の書き込みを行うときの走査方向とは反対方向に走査することにより実行する

表示装置。

(2)

各画素に含まれる複数のサブピクセルは、 $2 \times y$ (y>2)のマトリクスで配置され、

前記駆動回路は、1画素行における各サブピクセルへの前記信号電圧の書き込みを、下段のサブピクセルに対して実行したのち、上段のサブピクセルに対して実行する

(1)に記載の表示装置。

(3)

30

前記表示パネルは、

1ユニット内の各画素行における上段のサブピクセル行に対して1本ずつ割り当てられた複数の第1配線と、

1ユニット内の各画素行における下段のサブピクセル行に対して1本ずつ割り当てられた複数の第2配線と

を有し、

各画素において、各サブピクセルの発光色は互いに異なっており、

各第1配線は、1ユニット内で同一発光色の複数のサブピクセルに接続され、

各第2配線は、前記第1配線に接続されたサブピクセルの発光色とは異なる発光色であつて、かつ1ユニット内で同一発光色の複数のサブピクセルに接続されており、

40

前記駆動回路は、1画素行における各サブピクセルへの前記信号電圧の書き込みを、前記第2配線に接続された各サブピクセルに対して実行したのち、前記第1配線に接続された各サブピクセルに対して実行する

(2)に記載の表示装置。

(4)

各サブピクセルは、さらに、前記駆動トランジスタのソースに接続された補助容量を含み、

前記表示パネルは、さらに、列方向において互いに隣接すると共に画素行の互いに異なる2本のサブピクセル行ごとに1本ずつ割り当てられ、かつ前記補助容量に接続された複数の基準電圧線を有する

50

(2) または (3) に記載の表示装置。

(5)

各基準電圧線は、割り当てられた 2 本のサブピクセル行に含まれる全ての補助容量に接続されている

(4) に記載の表示装置。

(6)

表示装置を備え、

前記表示装置は、表示パネルと、前記表示パネルを駆動する駆動回路とを有し、

前記表示パネルは、複数のサブピクセルを含む複数の画素を有し、

各サブピクセルは、発光素子と、前記発光素子を駆動する駆動トランジスタと、映像信号に対応する信号電圧を前記駆動トランジスタのゲートに書き込む書き込トランジスタと、前記駆動トランジスタのゲート - ソース間電圧を保持する保持容量とを含み、

10

前記駆動回路は、 $k$  本 ( $k \geq 2$ ) の画素行を 1 ユニットとしたときに、第 1 のユニットで、前記駆動トランジスタのゲート - ソース間電圧を前記駆動トランジスタの閾値電圧に近づける  $V_{th}$  補正、および前記信号電圧の書き込みを実行した後に、前記第 1 のユニットと列方向において隣接する第 2 のユニットで、前記  $V_{th}$  補正、および前記信号電圧の書き込みを実行し、

前記駆動回路は、1 画素行における各サブピクセルへの前記信号電圧の書き込みを、ユニット単位で当該信号電圧の書き込みを行うときの走査方向とは反対方向に走査することにより実行する

20

電子機器。

(7)

複数のサブピクセルを含む複数の画素を備えた表示パネルの駆動方法であって、

各サブピクセルは、発光素子と、前記発光素子を駆動する駆動トランジスタと、映像信号に対応する信号電圧を前記駆動トランジスタのゲートに書き込む書き込トランジスタと、前記駆動トランジスタのゲート - ソース間電圧を保持する保持容量とを含み、

当該駆動方法は、 $k$  本 ( $k \geq 2$ ) の画素行を 1 ユニットとしたときに、第 1 のユニットで、前記駆動トランジスタのゲート - ソース間電圧を前記駆動トランジスタの閾値電圧に近づける  $V_{th}$  補正、および前記信号電圧の書き込みを実行した後に、前記第 1 のユニットと列方向において隣接する第 2 のユニットで、前記  $V_{th}$  補正、および前記信号電圧の書き込みを実行するステップを含み、

30

前記ステップにおいて、1 画素行における各サブピクセルへの前記信号電圧の書き込みを、ユニット単位で当該信号電圧の書き込みを行うときの走査方向とは反対方向に走査することにより実行する

表示パネルの駆動方法。

【符号の説明】

【0104】

1 ... 表示装置、10 ... 表示パネル、10A ... 表示領域、11, 11R, 11G, 11B, 11W ... 画素、12, 12R, 12G, 12B, 12W ... 画素回路、13 ... 有機EL素子、14 ... 表示画素、14A, 15A ... ゲート電極、14B, 15B ... ソース電極、14C, 15C ... ドレイン電極、15D ... コンタクト、20 ... 駆動回路、20A ... 映像信号、20B ... 同期信号、21 ... タイミング生成回路、21A ... 制御信号、22 ... 映像信号処理回路、22A ... 映像信号、23 ... 信号線駆動回路、24 ... 走査線駆動回路、25 ... 電源線駆動回路、300 ... 映像表示画面部、310 ... フロントパネル、320 ... フィルターガラス、410 ... 発光部、420, 530, 640 ... 表示部、430 ... メニュースイッチ、440 ... シャッターボタン、510 ... 本体、520 ... キーボード、610 ... 本体部、620 ... レンズ、630 ... スタート / ストップスイッチ、710 ... 上側筐体、720 ... 下側筐体、730 ... 連結部、740 ... デイスプレイ、750 ... サブディスプレイ、760 ... ピクチャーライト、770 ... カメラ、Cs ... 保持容量、DTL, DTL(m), DTL(m+1), DTL(m+2), DTL(m+3) ... 信号線、DSL, DSL(j), DSL(i)

40

50

+ 1 ) ... 電源線、 G N D ... グラウンド線、 I d s ... 電流、 T r 1 ... 駆動トランジスタ、 T r 2 ... 書込トランジスタ、 V c c , V o f s , V o n , V s i g , V s s ... 電圧、 V g ... ゲート電圧、 V g s ... ゲート - ソース間電圧、 V o l e d ... 有機 E L 素子の電圧、 V s ... ソース電圧、 V t h ... 閾値電圧、 W S L , W S L ( n ) , W S L ( n + 1 ) ... 走査線、 t , t 1 , t 2 , t 3 ... 待ち時間。

【 义 1 】

【 义 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【 四 8 】

【図9】

【 図 10 】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

---

フロントページの続き

(51)Int.Cl.

| F I     |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 3 U |

| G 0 9 G | 3/20 | 6 2 3 D |

| G 0 9 G | 3/20 | 6 2 1 M |

| G 0 9 G | 3/20 | 6 4 1 C |

| G 0 9 G | 3/20 | 6 1 1 H |

| G 0 9 G | 3/20 | 6 4 2 A |

(56)参考文献 特開2006-133731(JP,A)

特開2009-237041(JP,A)

特開2011-154237(JP,A)

特開2011-64957(JP,A)

特許第5891493(JP,B2)

(58)調査した分野(Int.Cl., DB名)

G 0 9 G 3 / 2 0 - 3 / 3 8