### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2009-123882 (P2009-123882A)

(43) 公開日 平成21年6月4日 (2009.6.4)

| (51) Int.Cl. |        |           | F I         |             | テーマコート    | ・ (参考) |

|--------------|--------|-----------|-------------|-------------|-----------|--------|

| HO1L         | 29/786 | (2006.01) | HO1L 29/78  | 626A        | 4M1O4     |        |

| HO1L         | 21/28  | (2006.01) | HO1L 21/28  | 301A        | 5F033     |        |

| HO1L         | 29/41  | (2006.01) | HO1L 29/44  | L           | 5F048     |        |

| HO1L         | 29/423 | (2006.01) | HO1L 29/58  | G           | 5 F 1 1 O |        |

| HO1L         | 29/49  | (2006.01) | HO1L 21/90  | D           |           |        |

|              |        |           | 審査請求 未請求 請求 | ママック 11 O L | (全 16 頁)  | 最終頁に続く |

(21) 出願番号 (22) 出願日 特願2007-295770 (P2007-295770) 平成19年11月14日 (2007.11.14) (71) 出願人 500174247

エルピーダメモリ株式会社 東京都中央区八重洲2-2-1

(74)代理人 100123788

弁理士 宮崎 昭夫

(74)代理人 100106138

弁理士 石橋 政幸

(74)代理人 100127454

弁理士 緒方 雅昭

(72) 発明者 内山 博之

東京都中央区八重洲2-2-1 エルピー

ダメモリ株式会社内

最終頁に続く

## (54) 【発明の名称】半導体装置およびその製造方法

## (57)【要約】

【課題】高密度に搭載可能な構造を有する電界効果トランジスタを備えた半導体装置を提供する。

【解決手段】基板と、この基板上に設けられた第1の絶縁層と、第1の絶縁層に埋め込まれた導電層と、この導電層に電気的に接続し直上に配置された下部拡散層、この下部拡散層上の半導体層、及びこの半導体層上の上部拡散層を有する柱状半導体部と、前記半導体層の周囲側面に設けられたゲート絶縁膜と、このゲート絶縁膜上に設けられたゲート電極と、このゲート電極および前記柱状半導体部を埋め込むように設けられた第2の絶縁層を有する半導体装置。

【選択図】図35

#### 【特許請求の範囲】

### 【請求項1】

基板と、

前記基板上に設けられた第1の絶縁層と、

第1の絶縁層に埋め込まれた導電層と、

前記導電層に電気的に接続し該導電層の直上に配置された下部拡散層、該下部拡散層上の半導体層、及び該半導体層上の上部拡散層を有する柱状半導体部と、

前記半導体層の周囲側面に設けられたゲート絶縁膜と、

前記ゲート絶縁膜上に設けられたゲート電極と、

前記ゲート電極および前記柱状半導体部を埋め込むように設けられた第2の絶縁層を有する半導体装置。

【請求項2】

前記ゲート電極は、前記半導体層の周囲を取り囲むように前記ゲート絶縁膜上に設けられている請求項1に記載の半導体装置。

【請求項3】

前記下部拡散層は、ポリシリコン層上の不純物含有単結晶シリコン層からなる請求項 1 又は 2 に記載の半導体装置。

【請求項4】

第1の絶縁層の上面を覆う窒化シリコン膜を有し、該窒化シリコン膜上に前記ゲート電極および第2の絶縁層が設けられている請求項1から3のいずれかに記載の半導体装置。

【請求項5】

前記基板は絶縁基板である請求項1から4のいずれかに記載の半導体装置。

【請求項6】

前記ゲート電極は、基板平面方向に延在する延在部を有し、

前記半導体装置は、第2の絶縁層上に設けられた第3の絶縁層と、第3の絶縁層を貫通し、前記上部拡散層に接続する第1の導電プラグと、第3の絶縁層および第2の絶縁層を貫通し、前記ゲート電極の延在部に接続する第2の導電プラグと、第1の導電プラグに接続し、第3の絶縁層上に設けられた導電層と、第2の導電プラグに接続し、第3の絶縁層上に設けられた導電層とを有する請求項1から5のいずれかに記載の半導体装置。

【請求項7】

第2の絶縁層上に設けられた第3の絶縁層と、

第3の絶縁層上に設けられた第4の絶縁層と、

第4の絶縁層に埋め込まれた導電層と、

前記導電層に電気的に接続し該導電層の直上に配置された下部拡散層、該下部拡散層上の半導体層、及び該半導体層上の上部拡散層を有する柱状半導体部と、

前記半導体層の周囲側面に設けられたゲート絶縁膜と、

前記ゲート絶縁膜上に設けられたゲート電極と、

前記ゲート電極および前記柱状半導体部を埋め込むように設けられた第5の絶縁層を有する請求項1から5のいずれかに記載の半導体装置。

【請求項8】

基板上に、導電層が埋め込まれた第1の絶縁層を形成する工程と、

第1の絶縁層上に犠牲層を形成する工程と、

前記犠牲層に、前記導電層に達するホールを形成する工程と、

前記ホール内を含む表面上にポリシリコン膜を形成する工程と、

前記ホール内を埋め込むようにマスク膜を形成する工程と、

前記マスク膜の一部が前記ホール底に残るように前記マスク膜を除去する工程と、

前記マスク膜残部をマスクに用いて前記ポリシリコン膜を除去し、該ポリシリコン膜の 一部を前記ホール底に残す工程と、

前記マスク膜残部を除去した後、前記ポリシリコン膜残部の少なくとも上層部分を単結晶化して第1の単結晶シリコン層を形成する工程と、

10

20

30

40

第 1 の単結晶シリコン層に不純物を注入して下部拡散層を形成する工程と、 前記ホール内において、前記下部拡散層上に第 2 の単結晶シリコン層を形成する工程と

第2の単結晶シリコン層の表面層部分に不純物を注入して上部拡散層を形成する工程と

前記犠牲層を除去して、前記ホール内に形成されていた前記下部拡散層、この下部拡散層上の半導体層、この半導体層上の前記上部拡散層を有する柱状半導体部を露出させる工程と、

前記半導体層の周囲側面にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上にゲート電極を形成する工程と、

前記ゲート電極および前記柱状半導体部上に第2の絶縁層を形成する工程を有する半導体装置の製造方法。

#### 【請求項9】

第1の絶縁層上に第1のエッチング防止膜を形成した後に前記犠牲層を形成し、 前記犠牲層の除去は、第1の絶縁層を保護するために第1のエッチング防止膜を利用し たエッチングによって行う請求項8に記載の半導体装置の製造方法。

### 【請求項10】

第2の単結晶シリコン層に、前記下部拡散層の不純物と反対導電型の不純物を注入し、前記上部拡散層の形成においては、前記下部拡散層の不純物と同じ導電型の不純物を注入する請求項8又は9に記載の半導体装置の製造方法。

#### 【請求項11】

前記柱状半導体部が形成された前記ホール内を埋め込むように第2のエッチング防止膜を形成する工程と、第2のエッチング防止膜の一部が前記ホール内に残るように第2のエッチング防止膜を除去する工程をさらに有し、

前記ゲート電極を形成する工程において、前記ゲート絶縁膜を形成した後に、不純物含有ポリシリコン膜を全面に形成し、前記柱状半導体部を保護するために第2のエッチング防止膜残部を利用したエッチバックを行って、前記柱状半導体部の周囲側面を覆うサイドウォールを形成する工程と、前記サイドウォールの形成後に全面に導電膜を形成し、この導電膜をパターニングして導電膜パターンを形成する工程を実施し、前記サイドウォールと前記導電膜パターンとで構成されるゲート電極を形成する、請求項8から10のいずれかに記載の半導体装置の製造方法。

【発明の詳細な説明】

## 【技術分野】

#### [0001]

本発明は、半導体装置およびその製造方法に関するものである。

#### 【背景技術】

## [ 0 0 0 2 ]

MOSトランジスタの高性能化を目的として、種々のMOSトランジスタが提案されているが、現在、シリコン基板上にゲート絶縁膜を介して設けられたゲート電極、およびその両側に設けられたソース拡散層およびドレイン拡散層を有する、いわゆる平面型トランジスタが主流である。

## [0003]

この平面型トランジスタを用いる場合、その実装密度は基板面積や素子分離の占有面積により制約され、加えて、トランジスタの実装密度増加に伴う配線の複雑化や配線占有面積の増大により、これ以上の高密度化が困難になっている。また、コスト低減のため、基板の大口径化を行って一枚の基板から取得できるチップ数の増大を図っているが、シリコン基板のこれ以上の大口径化も困難になってきている。さらに、シリコン基板は、その製造方法からその平面形状が円形であるが、通常の矩形の半導体チップの製造において円形基板周縁部が利用されないで残るという問題もある。

#### [0004]

10

20

30

一方、このような平面型トランジスタに対して、シリコン基板を用いなくてもよい、い わゆる縦型トランジスタが提案されている。例えば、特開平7-297406号公報には 、 基 板 面 と 垂 直 方 向 に ド レ イ ン 電 極 、 シ リ コ ン 層 及 び ソ ー ス 電 極 が 積 層 さ れ て な る 縦 型 薄 膜半導体装置であって、前記ドレイン電極が前記基板面に接して形成されており、そのド レイン電極が前記ソース電極より広い面積を有している縦型薄膜半導体装置が開示されて いる。

【特許文献1】特開平7-297406号公報

【発明の開示】

【発明が解決しようとする課題】

[00005]

本発明の目的は、高密度に搭載可能な構造を有する電界効果トランジスタを備えた半導 体装置およびその製造方法を提供することにある。

【課題を解決するための手段】

[0006]

本発明によれば、以下の半導体装置およびその製造方法が提供される。

[0007]

(1)基板と、

前記基板上に設けられた第1の絶縁層と、

第1の絶縁層に埋め込まれた導電層と、

前記導電層に電気的に接続し該導電層の直上に配置された下部拡散層、該下部拡散層上 の半導体層、及び該半導体層上の上部拡散層を有する柱状半導体部と、

前記半導体層の周囲側面に設けられたゲート絶縁膜と、

前記ゲート絶縁膜上に設けられたゲート電極と、

前記ゲート電極および前記柱状半導体部を埋め込むように設けられた第2の絶縁層を有 する半導体装置。

[0008]

(2)前記ゲート電極は、前記半導体層の周囲を取り囲むように前記ゲート絶縁膜上に 設けられている上記(1)項に記載の半導体装置。

[0009]

(3)前記下部拡散層は、ポリシリコン層上の不純物含有単結晶シリコン層からなる上 記(1)項又は(2)に項記載の半導体装置。

[0010]

( 4 ) 第 1 の 絶 縁 層 の 上 面 を 覆 う 窒 化 シ リ コ ン 膜 を 有 し 、 該 窒 化 シ リ コ ン 膜 上 に 前 記 ゲ ート電極および第2の絶縁層が設けられている上記(1)項から(3)項のいずれかに記 載の半導体装置。

[0011]

( 5 )前記基板は絶縁基板である上記( 1 )項から( 4 )項のいずれかに記載の半導体 装置。

[0012]

( 6 ) 前記ゲート電極は、基板平面方向に延在する延在部を有し、

前記半導体装置は、第2の絶縁層上に設けられた第3の絶縁層と、第3の絶縁層を貫通 し、前記上部拡散層に接続する第1の導電プラグと、第3の絶縁層および第2の絶縁層を 貫 通 し 、 前 記 ゲ ー ト 電 極 の 延 在 部 に 接 続 す る 第 2 の 導 電 プ ラ グ と 、 第 1 の 導 電 プ ラ グ に 接 続 し 、 第 3 の 絶 縁 層 上 に 設 け ら れ た 導 電 層 と 、 第 2 の 導 電 プ ラ グ に 接 続 し 、 第 3 の 絶 縁 層 上に設けられた導電層とを有する上記(1)項から(5)項のいずれかに記載の半導体装 置。

[0013]

(7) 第2の絶縁層上に設けられた第3の絶縁層と、

第3の絶縁層上に設けられた第4の絶縁層と、

第4の絶縁層に埋め込まれた導電層と、

10

20

30

40

前記導電層に電気的に接続し該導電層の直上に配置された下部拡散層、該下部拡散層上の半導体層、及び該半導体層上の上部拡散層を有する柱状半導体部と、

前記半導体層の周囲側面に設けられたゲート絶縁膜と、

前記ゲート絶縁膜上に設けられたゲート電極と、

前記ゲート電極および前記柱状半導体部を埋め込むように設けられた第5の絶縁層を有する上記(1)項から(5)項のいずれかに記載の半導体装置。

#### [0014]

(8)基板上に、導電層が埋め込まれた第1の絶縁層を形成する工程と、

第1の絶縁層上に犠牲層を形成する工程と、

前記犠牲層に、前記導電層に達するホールを形成する工程と、

前記ホール内を含む表面上にポリシリコン膜を形成する工程と、

前記ホール内を埋め込むようにマスク膜を形成する工程と、

前 記 マ ス ク 膜 の 一 部 が 前 記 ホ ー ル 底 に 残 る よ う に 前 記 マ ス ク 膜 を 除 去 す る 工 程 と 、

前記マスク膜残部をマスクに用いて前記ポリシリコン膜を除去し、該ポリシリコン膜の 一部を前記ホール底に残す工程と、

前記マスク膜残部を除去した後、前記ポリシリコン膜残部の少なくとも上層部分を単結晶化して第1の単結晶シリコン層を形成する工程と、

第1の単結晶シリコン層に不純物を注入して下部拡散層を形成する工程と、

前記ホール内において、前記下部拡散層上に第2の単結晶シリコン層を形成する工程と

第2の単結晶シリコン層の表面層部分に不純物を注入して上部拡散層を形成する工程と

前記犠牲層を除去して、前記ホール内に形成されていた前記下部拡散層、この下部拡散層上の半導体層、この半導体層上の前記上部拡散層を有する柱状半導体部を露出させる工程と、

前記半導体層の周囲側面にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上にゲート電極を形成する工程と、

前記ゲート電極および前記柱状半導体部上に第2の絶縁層を形成する工程を有する半導体装置の製造方法。

## [ 0 0 1 5 ]

(9)第1の絶縁層上に第1のエッチング防止膜を形成した後に前記犠牲層を形成し、 前記犠牲層の除去は、第1の絶縁層を保護するために第1のエッチング防止膜を利用し たエッチングによって行う上記(8)項に記載の半導体装置の製造方法。

## [0016]

(10)第2の単結晶シリコン層に、前記下部拡散層の不純物と反対導電型の不純物を 注入し、

前記上部拡散層の形成においては、前記下部拡散層の不純物と同じ導電型の不純物を注入する上記(8)項又は(9)項に記載の半導体装置の製造方法。

## [0017]

(11)前記柱状半導体部が形成された前記ホール内を埋め込むように第2のエッチング防止膜を形成する工程と、第2のエッチング防止膜の一部が前記ホール内に残るように第2のエッチング防止膜を除去する工程をさらに有し、

前記ゲート電極を形成する工程において、前記ゲート絶縁膜を形成した後に、不純物含有ポリシリコン膜を全面に形成し、前記柱状半導体部を保護するために第2のエッチング防止膜残部を利用したエッチバックを行って、前記柱状半導体部の周囲側面を覆うサイドウォールを形成する工程と、前記サイドウォールの形成後に全面に導電膜を形成し、この導電膜をパターニングして導電膜パターンを形成する工程を実施し、前記サイドウォールと前記導電膜パターンとで構成されるゲート電極を形成する、上記(8)項から(10)項のいずれかに記載の半導体装置の製造方法。

## 【発明の効果】

40

10

20

30

#### [0018]

本発明によれば、高密度に搭載可能な構造を有する電界効果トランジスタを備えた半導体装置およびその製造方法を提供することができる。

【発明を実施するための最良の形態】

### [0019]

従来のMOSトランジスタは、基板の平面上に設けられるものであり、基板面積の制約を受けるため、高密度に搭載することは困難であった。近年、ゲートのメタル化や拡散層の浅化傾向に伴うプロセスの低温化にしたがって、トランジスタ形成プロセスと配線形成プロセスの差異が小さくなってきている。そこで、本発明者は、基板の平面上ではなく、配線層間膜中に形成可能なトランジスタ構造を鋭意検討し、本発明を見出した。

[0020]

本発明は、MIS型電界効果トランジスタ(以下「トランジスタ」)を備えた半導体装置に効果的に適用できる。

### [0021]

本発明の一実施形態によるトランジスタは、絶縁層に埋め込まれた導電層に電気的に接続しその直上に配置された下部拡散層、この下部拡散層上の半導体層、及びこの半導体層上の上部拡散層を有する柱状半導体部と、前記半導体層の周囲側面に設けられたゲート絶縁膜と、このゲート絶縁膜上に設けられたゲート電極を有する。このゲート電極および前記柱状半導体部は絶縁層により埋め込まれる。

## [0022]

本実施形態によれば、複数のトランジスタをそれぞれ複数の配線層間に形成することが可能であり、単位面積辺りのトランジスタ実装数を増加させることができる。

#### [0023]

また本実施形態によれば、トランジスタの構成要素であるソース、チャネル形成領域、 及びドレインを基板平面に垂直方向に積層配置しているため、従来の平面型トランジスタ に対して占有面積を縮小でき、単位面積辺りのトランジスタ実装数を増加させることがで きる。さらに、完全空乏型トランジスタを容易に形成できる。

#### [0024]

また本実施形態によれば、トランジスタを配線層間に形成できるため、比較的高価な半導体単結晶基板に代えて安価な絶縁基板を用いることが可能になり、コストの低減が図れる。また、例えば石英基板を使用すると、基板の大きさを1m以上、基板形状を矩形にすることも可能となり、チップ取得数の増大、基板全面の使用効率の向上が図れる。

[0025]

また本実施形態によれば、トランジスタは層間絶縁膜により分離されるため、従来の素子分離プロセスが不要となりコスト低減が図れる。

#### [0026]

また本実施形態によれば、ゲート長の制御を、従来のリソグラフィ技術とエッチング技術による制御に代えて、成膜技術による膜厚制御で行うことができるため、ゲート長の制御性を向上させることができる。

### [0027]

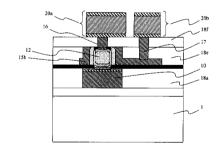

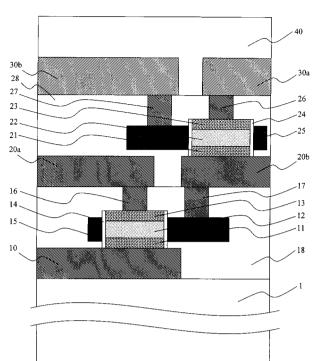

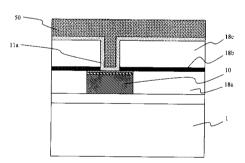

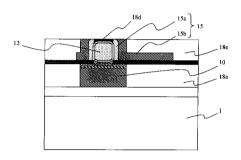

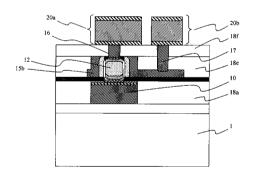

図 1 に、本発明の一実施例として、 2 個の M O S トランジスタを配線層間の 2 層にそれぞれ形成した場合の概略の断面構造を示す。

#### [0028]

基板1は、平坦性および耐熱性が十分であれば特に制限されず、例えば石英基板を用いることができる。

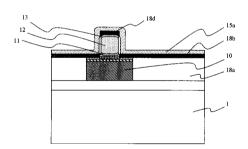

## [ 0 0 2 9 ]

基板1の表面上には、十分な耐熱性を有する配線層10が形成され、その配線層10上に、下部拡散層(ソース)11、半導体層(チャネル領域)12、上部拡散層(ドレイン)13が高さ方向(基板平面に垂直方向)に積層された構造をもつ柱状半導体部が形成されている。そして、この柱状半導体部を取り囲むようにゲート酸化膜14、ゲート電極1

10

20

30

30

40

10

20

30

40

50

5 が形成され、層間絶縁膜18内でMOSトランジスタ(以下「第1のトランジスタ」)が構成されている。

[0030]

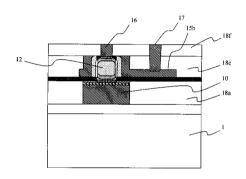

第1のトランジスタの柱状半導体部の上部拡散層13は、コンタクトプラグ16を介して、層間絶縁膜18上の配線層20aに接続され、ゲート電極15は、コンタクトプラグ17を介して配線層20bに接続されている。なお、図示されていないが、下層側の配線層10と上層側の配線層とを接続するためのビアプラグも必要に応じて形成される。

[0031]

配線層20 b上には、その下層側に位置する第1のトランジスタと同様の構造をもつMOSトランジスタ(以下「第2のトランジスタ」)が設けられる。下部拡散層(ソース)21、半導体層(チャネル領域)22、上部拡散層(ドレイン)23が積層された構造を持つ柱状半導体部が形成されている。この柱状半導体部を取り囲むようにゲート酸化膜24、ゲート電極25が形成され、層間絶縁膜28内で第2のトランジスタが構成されている。

[0032]

第2のトランジスタの柱状半導体部の上部拡散層23は、コンタクトプラグ26を介して、層間絶縁膜28上の配線層30aに接続され、ゲート電極25は、コンタクトプラグ27を介して配線層30bに接続されている。なお、図示されていないが、下層側の配線層20bと上層側の配線層とを接続するためのビアプラグも必要に応じて形成される。

[0033]

配線層30a、30b上には絶縁保護膜40が成膜されている。なお、これらの配線層上や絶縁保護膜上に、必要に応じてさらにMOSトランジスタや配線層を形成してもよい

[0034]

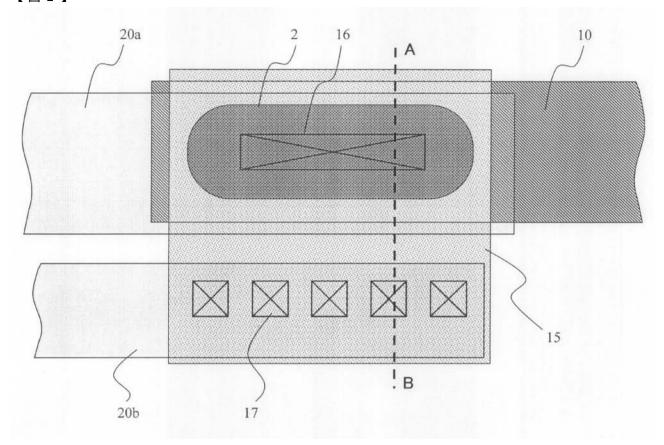

図 2 は、本実施例における 1 個の M O S トランジスタの基本的な平面レイアウト図を示す。

[0035]

MOSトランジスタを構成する柱状半導体部(ソース / チャネル領域 / ドレインの積層体) 2 は、図 2 における横方向に長いパターンを有している。短辺の長さ(縦方向の幅)は、周囲を囲っているゲート電極 1 5 から印加される電界によってチャネル領域を完全空乏化するために、例えば 1 0 0 n m以下に設定される。長辺の長さ(横方向の幅)は、回路動作に必要な電流を流すために必要十分な長さに設定される。

[0036]

この柱状半導体部2は、その下部拡散層(ソース)11が配線層10と接続するように、配線層10上に配置される。柱状半導体部2上には、その上部拡散層(ドレイン)13 と配線層20aとを接続するコンタクトプラグ16が配置される。

[0037]

ゲート電極15は、図中の縦方向(柱状半導体部の延在方向に垂直な方向)の一方に延在し、柱状半導体部2に隣接するこの延在領域上に、ゲート電極15と配線層20bを接続するコンタクトプラグ17が配置される。ゲート電極の延在方向や延在領域の形状および面積は適宜設定することができ、本図に限定されるものではない。

[0038]

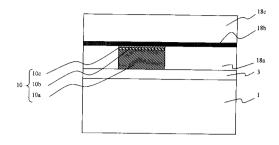

以下に、図3Aから図3Sを参照して本発明の半導体装置の製造方法の一実施例を説明する。図3Aから図3Sは、図2におけるAB線に沿った断面に対応する各工程の断面構造を示している。

[0039]

まず、図3Aに示すように、石英基板1上に、必要に応じてシリコン酸化膜等の絶縁膜3を形成した後、配線層10を形成する。この配線層10は、例えばタングステン膜10a、窒化チタン膜10b、チタン膜10cをこの順で積層し、通常の方法でパターニングして形成することができる。

10

20

30

40

50

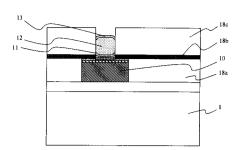

#### [0040]

次に、配線間を埋め込むように酸化シリコン膜18aを形成する。この酸化シリコン膜18aを化学的機械的研磨(CMP)等により平坦化するとともに、配線層10を露出させる。その後、窒化シリコン膜18bおよび酸化シリコン膜(犠牲酸化膜)18cを形成する。窒化シリコン膜18bの膜厚と酸化シリコン膜18cの膜厚の合計のサイズは、後に形成されるトランジスタのゲート長を決定する。電流駆動能力等の性能を優先する場合には、ゲート長をできるだけ短くする必要があり、この合計サイズを例えば80nmに設定することができる。特性の安定性を優先する場合には、ゲート長を長く設定する必要があり、この合計サイズを例えば200nmに設定することができる。このように設定された膜厚の合計サイズにおいて、窒化シリコン膜18bは、後のフッ酸エッチングに耐えられる必要最小限の膜厚(例えば10nm)に設定される。

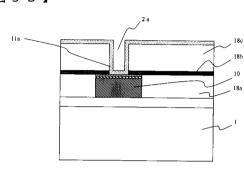

[0041]

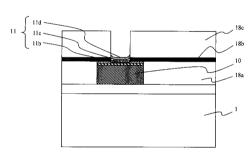

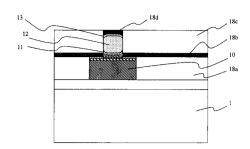

次に、図3Bに示すように、リソグラフィ技術とドライエッチング技術を用いて、後に柱状半導体部2が形成されるホール2bを、底部に配線層10が露出するように形成する。次いで、このホール内を含む全面にポリシリコン膜11aをCVD法で成膜する。このポリシリコン膜11aの膜厚は、ホール2aが埋まらない程度(例えば15nm)に設定される。

[0042]

次に、図3Cに示すように、ホール2aを埋め込むように、レジスト膜50を全面に形成する。

[0043]

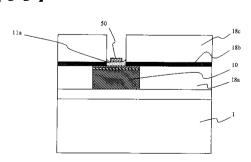

次に、ホール2aの底にレジスト膜の一部が残るようにレジスト膜50を除去する。続いて、図3Dに示すように、この残ったレジスト膜をマスクとしてポリシリコン膜11aを、例えば等方的なドライエッチングで除去して、ホールの底にのみポリシリコン膜11aを残す。レジスト膜50の一部をホール底に残す方法としては、例えば、ポジレジストを用いて露光量を制御し、ホール内の所定深さまでのレジストを除去する方法や、〇₂/CF₄ガス等を用いたアッシャー処理によりエッチバックしてエッチ量を制御し、ホール内に所定の厚みのレジスト膜を残す方法がある。

[0044]

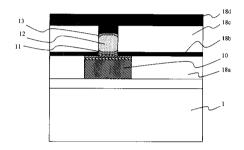

次に、残ったレジスト膜 5 0 を除去した後、レーザーアニール等を用いて局所的にポリシリコン膜表面を単結晶化する。その後、NチャネルトランジスタであればN型不純物として砒素やリンをイオン注入し、PチャネルトランジスタであればP型不純物としてボロンをイオン注入し、続いて熱処理を行う。以上のプロセスにより、図3 E に示すように、単結晶シリコンの拡散層 1 1 c、ポリシリコンと下地 T i との反応により形成されたチタンシリサイド層 1 1 b が形成され、その形成と共に、表面の結晶性が回復する。

[0045]

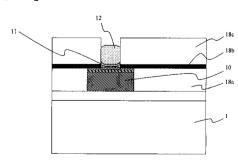

次に、図3Fに示すように、ホール2aの底の単結晶シリコン表面を核として、選択的に、例えばMOCVDエピタキシャル法によりシリコン結晶を成長させる。この時、NチャネルランジスタであればP型不純物としてボロンを導入し、PチャネルトランジスタであればN型不純物としてリンを導入し、MOSトランジスタの半導体層(チャネル領域)12を形成する。

[0046]

次に、図3Gに示すように、半導体層12の上部表面層に上部拡散層13を形成する。 この上部拡散層13は、NチャネルトランジスタであればN型不純物としてリンあるいは 砒素をイオン注入し、PチャネルトランジスタであればP型不純物としてボロンをイオン 注入し、続いて熱処理を行って形成することができる。

[0047]

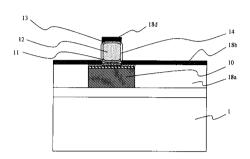

次に、図3Hに示すように、ホール2aを完全に埋め込むように窒化シリコン膜18dを形成する。続いて、図3Iに示すように、ホール内にのみ窒化シリコン膜18dを残す

ように、例えばСMP法によりホール外部表面上の窒化シリコン膜を除去する。

### [0048]

次に、図3 Jに示すように、酸化シリコン膜18 cを、例えばフッ酸溶液を用いたウェットエッチングにより除去する。次いで、半導体層12を含む柱状半導体部の側面に、例えば熱酸化法によりゲート酸化膜14を形成する。

### [0049]

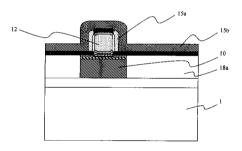

次に、図3Kに示すように、不純物含有ポリシリコン膜15aを例えばCVD法で成膜し、その後、図3Lに示すように、エッチバックすることにより、柱状半導体部の側面上のポリシリコン膜が残るようにポリシリコン膜15aを除去して、この柱状半導体部の側面上に残ったポリシリコン膜15aからなるポリシリコンサイドウォールを形成する。このサイドウォールは、後にゲート電極の一部となる。このサイドウォールを設けることにより、しきい値(Vth)の制御性を向上でき、また、ゲート酸化膜の信頼性を確保することができる。

## [0050]

次に、図3Mに示すように、タングステン膜15bを、例えばCVD法で堆積し、続いて、図3Nに示すように、リソグラフィ技術とドライエッチング技術によりパターニングを行って、タングステン膜15bとポリシリコンサイドウォール15aとの極15を形成する。このタングステン膜15bとポリシリコンサイドウォール15aとの反応を抑制するために、これらの間に窒化タングステン膜を設けてもよい。

## [0051]

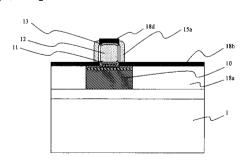

次に、図30に示すように、ゲート電極15を埋め込むように酸化シリコン膜18eを 例えばCVD法により形成する。

### [0052]

次に、図3Pに示すように、CMP法により、上部拡散層13上のゲート電極15が除去され、窒化シリコン膜18dが露出するまで研磨を行って平坦化を行う。

## [0053]

次に、露出したゲート電極15、窒化シリコン膜18dを覆うように、酸化シリコン膜18e上に酸化シリコン膜18fを例えばCVD法で形成する。次いで、図3Qに示すように、上部拡散層13に達するコンタクトホール16a、ゲート電極に達するコンタクトホール17aを、リソグラフィ技術とドライエッチング技術を用いて形成する。窒化シリコン膜18dは、コンタクトホール16aの形成においてエッチングストッパとして利用することができる。

#### [0054]

次に、例えば、これらホール内を含む表面にチタン膜および窒化チタン膜を順に形成した後、これらホールを埋め込むようにタングステン膜を形成し、CMP法によりホール外部表面上のこれら導体膜を除去する。こうして、図3Rに示すように、上部拡散層13に接続するコンタクトプラグ16、およびゲート電極15に接続するコンタクトプラグ17を形成する。

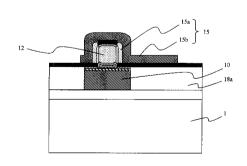

## [0055]

次に、図3Sに示すように、窒化チタン膜、アルミ膜、窒化チタン膜からなる積層膜を 例えばスパッタ法で成膜した後、リソグラフィ技術とドライエッチング技術を用いてパタ ーニングして配線層20a、20bを形成する。

## [0056]

以上のプロセスにより、下層側の配線層10と上層側の配線層20a、20bと間の層間膜中に縦型MOSトランジスタが形成される。

## [0057]

本実施例において、配線層20a、20bに代えて、配線層10の形成方法と同様な方法により配線層を形成し、その上部に、上記縦型MOSトランジスタの形成方法と同様な方法によりさらに縦型MOSトランジスタを形成することにより、図1に示すような、複数のトランジスタを上下の異なる層に有する構造を得ることができる。さらに、図示しな

10

20

30

00

40

いが同様のプロセスを繰り返すことにより、配線層間の3層以上にそれぞれ縦型MOSト ランジスタを有する構造も形成できる。

#### [0058]

本実施例においては、半導体単結晶基板を用いない例を説明したが、半導体単結晶基板 を用いて通常の平面型MOSトランジスタを基板上に形成し、この平面型MOSトランジ スタの上層側において、上記の縦型MOSトランジスタを形成してもよい。

【図面の簡単な説明】

- [0059]

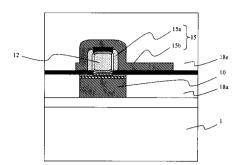

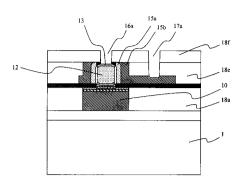

- 【図1】本発明の半導体装置の一実施例の概略構造を示す断面図。

- 【図2】図1に示す実施例における1個のMOSトランジスタの平面図。

【図3A】本発明の半導体装置の製造方法の一実施例を説明するための一工程を示す断面 図。

- 【図3B】図3Aに示す製造工程に続く工程を示す断面図。

- 【図3C】図3Bに示す製造工程に続く工程を示す断面図。

- 【図3D】図3Cに示す製造工程に続く工程を示す断面図。

- 【図3E】図3Dに示す製造工程に続く工程を示す断面図。

- 【図3F】図3Eに示す製造工程に続く工程を示す断面図。

- 【図3G】図3Fに示す製造工程に続く工程を示す断面図。

- 【図3H】図3Gに示す製造工程に続く工程を示す断面図。

- 【図3Ⅰ】図3日に示す製造工程に続く工程を示す断面図。

- 【図3 」】図3 Iに示す製造工程に続く工程を示す断面図。

- 【図3K】図3Jに示す製造工程に続く工程を示す断面図。

- 【図3L】図3Kに示す製造工程に続く工程を示す断面図。

- 【図3M】図3Lに示す製造工程に続く工程を示す断面図。

- 【図3N】図3Mに示す製造工程に続く工程を示す断面図。

- 【図30】図3Nに示す製造工程に続く工程を示す断面図。

- 【図3P】図30に示す製造工程に続く工程を示す断面図。

- 【図3Q】図3Pに示す製造工程に続く工程を示す断面図。

- 【図3R】図3Qに示す製造工程に続く工程を示す断面図。

- 【図35】図3尺に示す製造工程に続く工程を示す断面図。

【符号の説明】

- [0060]

- 1

- M O S トランジスタの柱状半導体部 ( ソース / チャネル領域 / ドレインの積層体 )

- 2 a 柱状半導体部形成用ホール

- 3 絶縁膜

- 10 第1のトランジスタの下層側の配線層

- 10a タングステン層

- 10b 窒化チタン層

- 1 0 c チタン層

- 第1のトランジスタの下部拡散層(ソース) 1 1

- 1 1 a ポリシリコン膜

- 11b チタンシリサイド層

- 1 1 c 拡散層(ポリシリコン)

- 1 1 d 拡散層(単結晶)

- 12 第1のトランジスタの半導体層(チャネル領域)

- 第1のトランジスタの上部拡散層(ドレイン)

- 14 第1のトランジスタのゲート酸化膜

- 15 第1のトランジスタのゲート電極

10

20

30

40

- 1 5 a 不 純 物 含 有 ポ リ シ リ コ ン 膜

- 15 b タングステン膜

- 16 上部拡散層接続用コンタクトプラグ

- 16a 上部拡散層接続用コンタクトホール

- 17 ゲート電極接続用コンタクトプラグ

- 17a ゲート電極接続用コンタクトホール

- 18層間絶縁膜

- 18a 酸化シリコン膜

- 18b 窒化シリコン膜

- 18 c 酸化シリコン膜(犠牲酸化膜)

- 18d 窒化シリコン膜

- 18e 酸化シリコン膜

- 18f 酸化シリコン膜

- 20 a 第1のトランジスタの上層側配線層

- 2 0 b 第 1 のトランジスタの上層側配線層

- 2 1 第 2 のトランジスタの下部拡散層 (ソース)

- 22 第2のトランジスタの半導体層(チャネル領域)

- 23 第2のトランジスタの上部拡散層(ドレイン)

- 24 第2のトランジスタのゲート酸化膜

- 25 第2のトランジスタのゲート電極

- 2 6 上部拡散層接続用コンタクトプラグ

- 2 7 ゲート電極接続用コンタクトプラグ

- 2 8 層間絶縁膜

- 3 0 a 第 2 のトランジスタの上層側の配線層

- 30b 第2のトランジスタの上層側の配線層

- 4 0 絶縁保護膜

- 50 レジスト膜

10

【図1】

【図3A】

【図3B】

【図3C】

【図3E】

【図3D】

【図3F】

【図3G】

【図3I】

【図3H】

【図3」】

【図3K】

【図3M】

【図3L】

【図3N】

【図30】

【図3Q】

【図3P】

【図3R】

【図3S】

【図2】

# フロントページの続き

| (51) Int.CI.    |               |        |               | FΙ   |         |         |      |       |      | テーマコード(参考) |

|-----------------|---------------|--------|---------------|------|---------|---------|------|-------|------|------------|

| H 0 1 L 21/768  | (20           | 06.01) |               | ŀ    | H 0 1 L | _ 29/   | 78   | 6 1 3 | Z    |            |

| H 0 1 L 23/522  | 522 (2006.01) |        | H 0 1 L 29/78 |      |         | 6 1 8 C |      |       |      |            |

| H 0 1 L 27/00   | (2006.01)     |        | H 0 1 L 29/78 |      | 6 1 7 K |         |      |       |      |            |

| H 0 1 L 21/8234 | (2006.01)     |        | H 0 1 L 27/00 |      | 3 0 1 A |         |      |       |      |            |

| H 0 1 L 27/088  | (2006.01)     |        | H 0 1 L 27/08 |      | 1 0 2 E |         |      |       |      |            |

|                 |               |        |               |      |         |         |      |       |      |            |

| F ターム(参考) 4M104 | AA01          | BB01   | BB14          | BB25 | BB40    | CC01    | CC05 | DD04  | DD43 | DD65       |

|                 | DD84          | FF01   | FF13          | FF18 | FF22    | FF26    | GG09 | GG10  | GG14 |            |

| 5F033           | GG03          | HH08   | HH33          | JJ18 | JJ19    | JJ27    | JJ33 | KK18  | KK19 | KK33       |

|                 | 80MM          | NN06   | NN07          | PP15 | QQ08    | QQ09    | QQ11 | QQ25  | QQ37 | QQ48       |

|                 | QQ70          | QQ73   | RR04          | RR06 | SS11    | VV06    |      |       |      |            |

| 5F048           | AA01          | AC01   | ACO4          | BA16 | BA19    | BA20    | BB06 | BB07  | BB09 | BB12       |

|                 | BD07          | BF07   | BF12          | BF16 | CB01    | CB03    | CB04 | CB07  |      |            |

| 5F110           | AA04          | BB11   | CC09          | CC10 | DD03    | DD13    | EE01 | EE04  | EE09 | EE14       |

|                 | EE15          | EE22   | EE24          | EE38 | EE45    | FF02    | FF23 | GG02  | GG12 | GG22       |

|                 | GG28          | GG29   | GG32          | GG44 | HJ01    | HJ13    | HJ22 | HK01  | HK04 | HK22       |

|                 | HK40          | HL01   | HL03          | HL12 | HL23    | HM17    | NN03 | NN23  | NN35 | PP36       |

|                 | QQ19          |        |               |      |         |         |      |       |      |            |