## **PCT**

## WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

## INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification 5:

H04B 1/26

A1

(11) International Publication Number: WO 93/15560

(43) International Publication Date: 5 August 1993 (05.08.93)

US

(21) International Application Number:

PCT/US93/00855

(22) International Filing Date:

22 January 1993 (22.01.93)

(30) Priority data:

(57) Abstract

829,828

3 February 1992 (03.02.92)

(71) Applicant: MOTOROLA, INC. [US/US]; 1303 East Algonquin Road, Schaumburg, IL 60196 (US).

(72) Inventor: HECK, Joseph, P.; 1940 E. Oak Knoll Circle, Fort Lauderdale, FL 33324 (US).

(74) Agents: GHOMESHI, M., Mansour et al.; Motorola, Inc., Patent Dept., 8000 West Sunrise Boulevard, Fort Lauderdale, FL 33322 (US). (81) Designated States: JP, European patent (AT, BE, CH, DE, DK, ES, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE).

**Published**

With international search report.

(54) Title: BALANCED MIXER CIRCUIT

A balanced mixer circuit (200) includes a first balanced input (RF(+) and RF(-)), a second balanced input (LO(+) and LO(-)), and a balanced output (OUT+ and OUT-). The balanced mixer circuit (200) also includes a mixer (210) for mixing a first signal with a second signal. The mixer (210) further includes a first input and second input which is coupled to the second input of the balanced mixer circuit (200). The balanced mixer circuit (200) also includes a pair of couplers (204 and 206) for coupling the first input of the mixer circuit (200) to the first input of the mixer (210). Each of the pair of couplers (204 and 206) includes a feedback circuit (202 and 208) for improving the performance of the balanced mixer circuit (200).

## FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AT | Austria                  | FR  | France                       | MR | Mauritania               |

|----|--------------------------|-----|------------------------------|----|--------------------------|

| AU | Australia                | GA  | Gabon                        | MW | Malawi                   |

| BB | Barbados                 | GB  | United Kingdom               | NL | Netherlands              |

| BE | Belgium                  | GN  | Guinca                       | NO | Norway                   |

| BF | Burkina Faso             | GR  | Greece                       | NZ | New Zealand              |

| BG | Bulgaria                 | ผบ  | Hungary                      | PL | Poland                   |

| BJ | Benin                    | ΙE  | Ireland                      | PT | Portugal                 |

| BR | Brazil                   | IT  | Italy                        | RO | Romania                  |

| CA | Canada                   | JР  | Japan                        | RU | Russian Federation       |

| CF | Central African Republic | KP  | Democratic People's Republic | SD | Sudan                    |

| CG | Congo                    |     | of Korea                     | SE | Sweden                   |

| CH | Switzerland              | KR  | Republic of Korea            | SK | Slovak Republic          |

| CI | Côte d'Ivoire            | ΚZ  | Kazakhstan                   | SN | Senegal                  |

| CM | Cameroon                 | Ll  | Liechtenstein                | SU | Soviet Union             |

| CS | Czechoslovakia -         | LK  | Sri Lanka                    | TD | Chad                     |

| CZ | Czech Republic           | 1.U | Luxembourg                   | TG | Togo                     |

| DE | Germany                  | MC  | Monaco                       | UA | Ukraine                  |

| DK | Denmark                  | MG  | Madagascar                   | US | United States of America |

| ES | Spain                    | ML. | Mali                         | VN | Viet Nam                 |

| Fi | Finland                  | MN  | Mongolia                     |    |                          |

WO 93/15560 PCT/US93/00855

#### BALANCED MIXER CIRCUIT

5

### **Technical Field**

This invention is generally related to radio

communication devices and more specifically to mixers in radio communication devices.

#### **Background**

Mixers are used in communication devices to down step 15 or up step the frequency of their input signal. In receivers, mixers are utilized to mix a received signal with a locally generated reference or injection signal to produce a difference signal. This difference signal is further processed and demodulated according to a variety of demodulation schemes 20 before being presented to a user. Mixers in general, and balanced mixers in particular, are well known in the art and have been used by radio designers extensively. A variety of balanced mixers are available. Some with one balanced port, others with two or three balanced ports. Doubly balanced 25 mixers have two of their ports balanced. Triply balanced mixer have all three of their ports balanced. The advantages of balanced mixers include improved spurious response, improved noise degradation, simplicity of their matching networks, and so forth. Various topologies have been used in realizing mixer requirements. In general, however, a doubly 30 balanced mixer includes a balanced or differential radio frequency (RF) input port and a balanced or differential local oscillator (LO) input port where each port accommodates a balanced signal to be mixed with the other. Integrated doubly 35 balanced mixers are generally based on a structure known as Gilbert Cell. The Gilbert structure has limitations to its intermodulation (IM) distortion performance, noise figure,

10

15

20

current drain performance, and a trade off amongst these three criteria. These limitations have limited the use of balanced mixers in communication devices with stringent performance requirements.

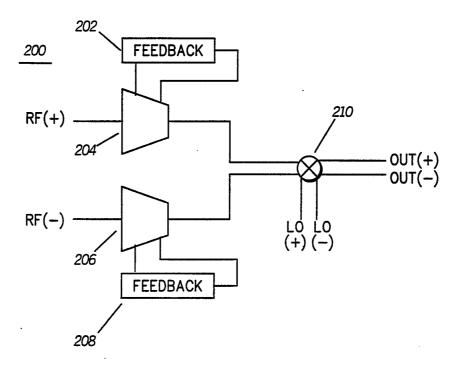

Referring to FIG. 1, a circuit diagram of a mixer 100 is shown utilizing presently known circuit topologies. The mixer 100 includes transistors 106, 108, 110, and 112 that are ultimately coupled to balanced local oscillator inputs LO(+) and LO(-). Coupled to these transistors are two input gates. transistors 114 and 116 which couple balanced radio frequency inputs RF(+) and RF(-). A balanced RF signal applied to the base of transistors 114 and 116 is switched at the rate of the local oscillator signals applied to transistors 106, 108, 110 and 112. The switching of the RF signal results in a signal appearing at the output Out (+) and Out (-) equal to the difference of the RF and LO signals. Two degeneration resistors 118 and 120 couple the emitters of transistors 114 and 116 to a current source shown by a transistor 122 and a resistor 124. The degeneration resistors 118 and 120 are used to provide improvements in the third order IM at the expense of some gain and noise figure. It can be shown that the third order IM intercept point is given by the following equation:

$$IP3i|_{dBm} = 10 + 20 \cdot \log (4VT) + 30 \cdot \log \left\{1 + \frac{R_{\mathsf{E}} \cdot I_{\mathsf{EE}}}{4VT}\right\} - 10 \cdot \log \left(\frac{Ri}{50}\right)$$

25 Where

30

$V_T = kT/q$

$K = 1.38 \times 10^{-24}$  (Boltzman's Constant)

T = Kelvin Temperature

$q = 1.6 \times 10^{-19}$  (Electron Charge)

Ri = RF port input impedance.

Since the gain of the mixer 100 is set essentially by the value of R<sub>E</sub> it can be concluded from the equation that with

35 this circuit configuration of a given gain the only way to improve intercept point is to increase the current drain or to

reduce Ri. Normally, input impedance is set by other criteria and cannot be changed or if it is changed will result in a no win shift in all performance parameter values. With high demands on performance improvements and reduced current consumption it can be seen that IM and noise figure can be limitedly improved at the cost of increased current drain. It is therefore desired to have a mixer circuit that has improved IM and noise figure performance without a significant increase in current drain.

10

15

20

30

5

#### **Summary of the Invention**

Briefly, according to the invention, a mixer circuit having a first input, a second input, and an output is provided. The mixer circuit includes a mixing means for mixing a first signal with a second signal. The mixing means includes a first input and a second input which is coupled to the second input of the mixer circuit. The mixer circuit also includes a coupler means for coupling the first input of the mixer circuit to the first input of the mixer means. The coupling means includes a feedback circuit for improving the performance of the mixer circuit.

#### Brief Description of the Drawings

FIG. 1 shows a schematic diagram of a presently available mixer circuit.

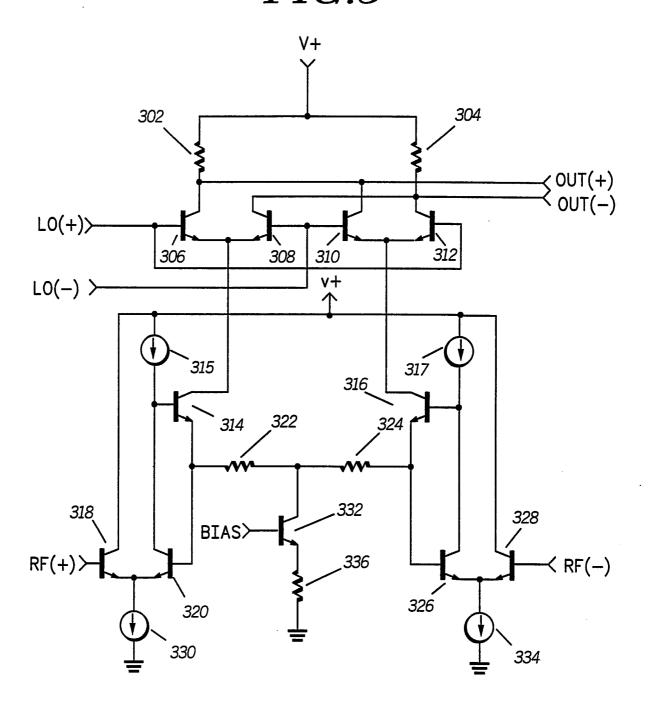

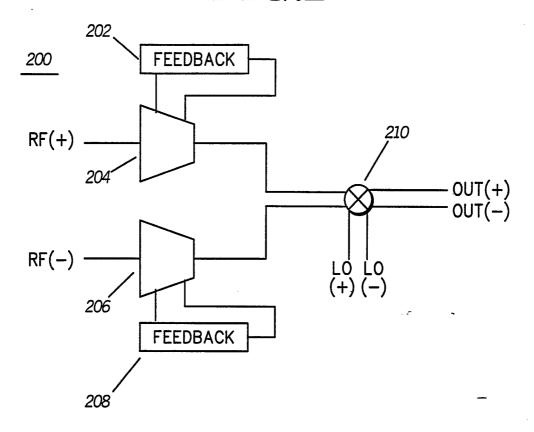

FIG. 2 shows a block diagram of a mixer in accordance with the present invention.

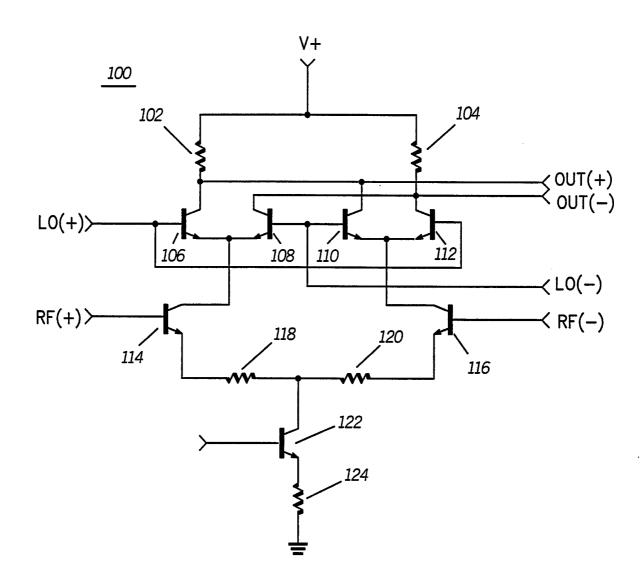

FIG 3 shows a schematic diagram of a mixer in accordance with the present invention.

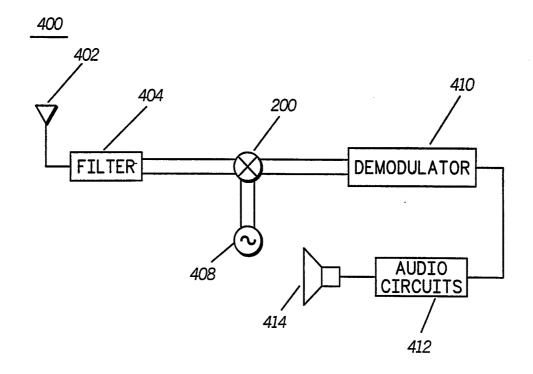

FIG. 4 shows a block diagram of a communication device in accordance with the present invention.

## Detailed Description of the Preferred Embodiment

Radio communication designers are often plagued with having to design a mixer circuit that meets their device performance requirements without sacrificing other

5

30

35

important parameters. In particular, the traditional methods of improving intermodulation (IM) performance of a balanced mixer result in noise figure degradation and/or an increase in the current drain. Other problems are observed as other parameters are tackled. This invention provides a mixer circuit that overcomes the negative inter-dependance of these parameters, e.g. better IM performance for a given level of current drain and gain.

Referring to FIG. 2, a block diagram of a balanced 10 mixer circuit 200 in accordance with the principles of the present invention is shown. The balanced mixer circuit 200 is a triply balanced mixer in that it includes a balanced pair of Radio Frequency (RF) inputs, RF(+) and RF(-), a balanced pair of local oscillator inputs, LO(+) and LO(-), and a balanced pair 15 of outputs, OUT(+) and OUT(-). The two RF inputs are coupled to a balanced mixer 210 through a pair of amplifiers, preferably transconductance amplifiers 204 and 206. The transconductance amplifiers 204 and 206 amplify the voltage of the RF signals at RF(+) and RF(-), convert it to current, and 20 then apply it to the mixer 210. These amplifiers include feedback circuits 202 and 208, respectively. The balanced RF signals are mixed with the local oscillator signals to produce output signals at OUT(+) and OUT(-). The elements of the feedback circuits 202 and 208 provide the means for reducing 25 intermodulation without sacrificing noise figure or increasing current drain in the circuit of the mixer circuit 200.

FIG. 3 shows a schematic diagram of the elements of the mixer circuit 200, in accordance with the present invention. To facilitate the understanding of the operation of the components of this figure, cross references are made to the block diagram of FIG.2. The mixer circuit 200 includes transistors 306, 308, 310 and 312 which feed the output resistors 302 and 304. These transistors are the components of the mixer block 210, as shown in FIG. 2. The bases of the transistors 306 and 312 are combined to form the LO(+) input while the bases of transistors 308 and 310 are combined to

form the LO(-). Collectors of transistors 306 and 310 are combined to form the first RF output, OUT(+). Similarly, the collectors of transistors 308 and 312 are coupled together to form the second RF output, OUT(-). The first RF input signal is coupled to the mixer 210 at the emitter junction of

- is coupled to the mixer 210 at the emitter junction of transistors 306 and 308. The transistor 314 forms a portion of the feedback loop 202. Transistors 318 and 320 and two current sources 315 and 330 constitute the transconductance amplifier 204. The current source 315 is also a part of the feedback loop

- 10 202. The base of the transistor 318 receives the RF(+) signal and converts it to current, before applying it to the emitter junction of transistors 306 and 308 through the feedback transistor 314. Similarly, transistors 326 and 328 in combination with current sources 317 and 334 constitute the

- second transconductance amplifier 206. A transistor 316, in conjunction with the current source 317, constitute the feedback 208. The output signal current of the transconductance amplifier 206 is available at the collector of the transistor 316. This signal is coupled to the mixer 210 at

- the emitter junction of transistors 310 and 312. The base of the transistor 328 is coupled to the RF (-) and receives an RF signal in the form of a voltage. Bias for the circuit 200 is applied to the base of a transistor 332, which is coupled to ground through an emitter resistor 336. It is well understood

- that the RF and LO inputs must be biased for the circuit 200 to properly operate. This bias may be provided via resistor divider circuits at these inputs. Alternatively, RF(-) and LO(-) may be connected simply to a DC bias voltage equal to the DC bias voltage at RF(+) and LO(+), respectively. Two

- degeneration resistors 322 and 324 couple the two transconductance amplifiers 204 and 206 to the current source formed by the biasing transistor 332 and resistor 336. These resistor values set the gain of the mixer and the degree of feedback.

- A balanced RF signal, applied to RF(+) and RF(-), is converted to current before it is applied to the transistors 306, 308, 310 and 312. These transistors switch at the rate

10

15

20

25

30

35

6

determined by the local oscillator LO(+) and LO(-). The switching of these transistors results in the signal at OUT(+) and OUT(-) to have the difference frequency of the frequency of RF signals and LO signals. The operation of the switching circuit comprising the mixer 210 is well known in the art. A detailed description of the operation of one such circuit is found in the "Analog Integrated Circuits for Communication Principles Simulation and Design" by Donald O. Peterson and Kartikeya Mayaram, published by Ruler Academic Publishers (1991).

Feedback paths comprising transistors 314 and 316 allow for a reduction in the intermodulation (IM) without compromising the noise figure or increasing the current drain. In other words, the circuit configuration of the mixer circuit 200 achieves a better trade-off amongst intercept point gain and noise figures. The improvement in performance is achieved by use of the feedback circuits 202 and 208 in place of single transistors at the RF(+) and the RF(-) inputs. The feedback circuit is an improvement in linearity, which results in improved IM performance. The gain of the mixer is virtually unchanged (indeed gain is slightly increased with the feedback circuit) and is set by the values of the emitter degeneration resistors 322 and 324. The noise figure of the circuit 200 has been found to be equal to or lower than the presently available mixers, such as mixer 100. The improvement in linearity decreases with increasing frequency of operation because the open loop gain of the feedback circuit rolls off with increasing frequency. Conversely, as current drain increases, the open loop gain and the linearity increase, and hence IM performance improves. In the preferred embodiment, the current sources 315 and 317 are set to produce currents equal to that produced by current sources 330 and 334. It is understood that the balanced nature of the circuit 200 demands that currents produced by sources 330, 334 be equal. Also, by varying the DC current magnitude produced by sources 330, 334 and the transistor 332, the IM

35

performance can be programmed for different operating conditions or frequencies.

In summary, the mixer circuit 200 is shown to have realized improved IM performance along with improved gain and noise figure performances. By utilizing the feedback circuits 202 and 208 the transconductance amplifiers 204 and 206 can operate more linearly resulting in concurrent improvements of highly dependent parameters.

FIG. 4 is a block diagram of a communication device in accordance with the present invention. The device 400. 10 includes an antenna 402 where RF signals are received and coupled to a filter 404. The filter 404 removes undesired components of the received signal before differentially applying it to the mixer circuit 200. The mixer circuit 200 15 receives its differential local oscillator signals from an oscillator 408 with balanced outputs. The balanced outputs of the mixer circuit 200 are either coupled to a demodulator 410. where the now-converted received signal is demodulated and decoded. The demodulator 410 includes such circuits as IF 20 amplifiers and IF filters to amplify and filter the IF output signal of the mixer circuit 200. The demodulated signal of the demodulator 410 is applied to an audio circuit block 412, where it is processed before being presented to the user via a speaker 414. In addition to the audio circuit 412 and the speaker 414, a 25 controller and a display may be used to present data signals to the user. Although the mixer circuit 200 is shown to be differential IN differential OUT, it is well understood that the principles of the present invention may be applied to mixers having differential inputs and single ended outputs, or single 30 ended inputs and differential outputs, or single ended input and single ended output.

It is understood that the circuits 200 and 400 are intended to provide the preferred embodiments of the present invention and not limitations thereto. It is further understood that modifications to these circuits are possible without significant departure from the spirit of the invention. It is therefore the scope of the claims that should define the scope

WO 93/15560 PCT/US93/00855

8

of the protection and not the specific embodiments presented here.

It can be seen that by employing a transconductance amplifier along with the feedback loop, the coupling of the RF input signal to the switching portion of the mixer allows for performance improvements in the areas not collectively possible. The use of the circuit 200 overcomes the deficiencies of the prior art in allowing the intermodulation to be improved along with noise performance and gain without significant increase in current drain. The circuit is particularly useful in portable communication devices where batteries are used as a main power source. In such devices, and in order to save valuable battery energy, it is highly desirable that any steps taken to reduce undesired interferences does not result in increased power consumption.

What is claimed is:

5

10

15

## **Claims**

- 1. A mixer circuit having a first input, a second input, and an output, the mixer circuit comprising:

- 5 mixer means for mixing a first signal with a second signal, the mixer means having a first input, a second input coupled to the second input of the mixer circuit; and

- coupler means for coupling the first input of the mixer circuit to the first input of the mixer means, the coupler means including a feedback means for improving the linearity of the mixer circuit.

- 2. The mixer circuit of claim 1, wherein the coupler means includes a transconductance amplifier.

- 3. The mixer circuit of claim 1, further including a biasing means for biasing the coupler and mixer means..

- 20 4. The mixer circuit of claim 1, wherein the mixer means comprises balanced mixer means.

- 5. The mixer circuit of claim 4, wherein the balanced mixer means includes a doubly-balanced mixer.

- 6. The mixer circuit of claim 4, wherein the balanced mixer means includes a triply-balanced mixer.

WO 93/15560 PCT/US93/00855

7. A balanced mixer circuit having a pair of differential inputs, balanced mixer circuit comprising:

10

5

10

balanced mixer means having a pair of differential inputs for differentially mixing a first signal with a second signal to produce an output signal; and coupler means for coupling the differential inputs of the balanced mixer circuit to the differential inputs of the balanced mixer means, the coupler means including a feedback means for reducing interference at the output signal.

8. The balanced mixer circuit of claim 7, wherein the balanced mixer means includes a switching means for15 switching the first signal at a pre-determined rate.

10

15

20

25

- 9. A balanced mixer circuit for differentially mixing a first differential signal, received at a first pair of differential inputs, with a second differential signal received at a second pair of differential inputs to produce an output signal, the balanced mixer circuit comprising:

- a mixer means having a plurality of switches for switching the first differential signal at the rate of the second differential signal;

- a pair of transconductance amplifiers differentially coupled to each other for coupling the first pair of differential inputs of the balanced mixer circuit to the mixer means; and

- a pair of feedback means coupled to each of the pair of transconductance amplifiers for minimizing interference on the output signal.

- 10. A communication device, comprising:

- a receiver, including:

- a balanced mixer circuit having a pair of differential inputs, the balanced mixer circuit comprising: balanced mixer means having a pair of differential inputs for differentially mixing a first signal with a second signal to produce an output signal; and coupler means for coupling the differential inputs of the balanced mixer circuit to the differential inputs of the balanced mixer means, the coupler means including a feedback means for reducing interference at the output signal.

1/3

# FIG.1

(PRIOR ART)

}

2/3 **FIG.3**

)

3/3

FIG.2

FIG.4

## INTERNATIONAL SEARCH REPORT

Inte...ational application No.

PCT/US93/00855

| •                                                                                                                             |                                                                                                                                                                    |                                                                                                                                    |                                   |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|--|

| IPC(5) :H04B 1/26<br>US CL :455/326                                                                                           |                                                                                                                                                                    |                                                                                                                                    |                                   |  |  |  |  |  |

| According to International Patent Classification (IPC) or to both national classification and IPC                             |                                                                                                                                                                    |                                                                                                                                    |                                   |  |  |  |  |  |

| B. FIELDS SEARCHED                                                                                                            |                                                                                                                                                                    |                                                                                                                                    |                                   |  |  |  |  |  |

| Minimum d                                                                                                                     | documentation searched (classification system follower                                                                                                             | ed by classification symbols)                                                                                                      |                                   |  |  |  |  |  |

| U.S. : 455/323,325,327,333, 307/529                                                                                           |                                                                                                                                                                    |                                                                                                                                    |                                   |  |  |  |  |  |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched |                                                                                                                                                                    |                                                                                                                                    |                                   |  |  |  |  |  |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)  |                                                                                                                                                                    |                                                                                                                                    |                                   |  |  |  |  |  |

| C. DOC                                                                                                                        | CUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                  |                                                                                                                                    |                                   |  |  |  |  |  |

| Category*                                                                                                                     | Citation of document, with indication, where a                                                                                                                     | ppropriate, of the relevant passages                                                                                               | Relevant to claim No.             |  |  |  |  |  |

| Y                                                                                                                             | US,A, 4,931,746 (TRANKLE ET AL                                                                                                                                     | 1-10                                                                                                                               |                                   |  |  |  |  |  |

|                                                                                                                               | 05 JUNE 1990<br>See col. 1, line 56, vol. 3, line 20                                                                                                               |                                                                                                                                    |                                   |  |  |  |  |  |

| Y                                                                                                                             | US,A, 4,619,001 (KANE)                                                                                                                                             |                                                                                                                                    | 1-10                              |  |  |  |  |  |

|                                                                                                                               | 21 OCTOBER 1986                                                                                                                                                    |                                                                                                                                    | 1-10                              |  |  |  |  |  |

|                                                                                                                               | See col. 2, line 47-col. 3, line 62                                                                                                                                |                                                                                                                                    |                                   |  |  |  |  |  |

| Y                                                                                                                             | US,A, 4,480,337 (GRAZIADEI ET A<br>30 OCTOBER 1984                                                                                                                 | 1-10                                                                                                                               |                                   |  |  |  |  |  |

|                                                                                                                               | See abstract                                                                                                                                                       |                                                                                                                                    | •                                 |  |  |  |  |  |

|                                                                                                                               |                                                                                                                                                                    |                                                                                                                                    |                                   |  |  |  |  |  |

|                                                                                                                               |                                                                                                                                                                    |                                                                                                                                    |                                   |  |  |  |  |  |

|                                                                                                                               |                                                                                                                                                                    |                                                                                                                                    |                                   |  |  |  |  |  |

| Furth                                                                                                                         | ner documents are listed in the continuation of Box C                                                                                                              | See patent family annex.                                                                                                           |                                   |  |  |  |  |  |

| "A" doc                                                                                                                       | ecial categories of cited documents;<br>cument defining the general state of the art which is not considered<br>be part of particular relevance                    | "T" later document published after the inte<br>date and not in conflict with the applica<br>principle or theory underlying the inv | ition but cited to understand the |  |  |  |  |  |

| "E" car                                                                                                                       | lier document published on or after the international filing date                                                                                                  | "X" document of particular relevance; the considered novel or cannot be considered.                                                |                                   |  |  |  |  |  |

| cite                                                                                                                          | cument which may throw doubts on priority claim(s) or which is<br>ed to establish the publication date of another citation or other<br>scial reason (as specified) | when the document is taken alone "Y" document of particular relevance; the                                                         |                                   |  |  |  |  |  |

| *O" document referring to an oral disclosure, use, exhibition or other means                                                  |                                                                                                                                                                    | considered to involve an inventive<br>combined with one or more other such<br>being obvious to a person skilled in th              | documents, such combination       |  |  |  |  |  |

| the                                                                                                                           | cument published prior to the international filing date but later than priority date claimed                                                                       | *&* document member of the same patent family                                                                                      |                                   |  |  |  |  |  |

| 14 APRIL                                                                                                                      | actual completion of the international search                                                                                                                      | Date of mailing of the international search report  19 MAY 1993                                                                    |                                   |  |  |  |  |  |

| Name and mailing address of the ISA/US Commissioner of Patents and Trademarks Box PCT Washington, D.C. 20231                  |                                                                                                                                                                    | Authorized officer Ngotto Ngueyeu                                                                                                  |                                   |  |  |  |  |  |

|                                                                                                                               |                                                                                                                                                                    | EDWARD URBAN L'ESTITIT NOCC-NO                                                                                                     |                                   |  |  |  |  |  |

| Facsimile No. NOT APPLICABLE                                                                                                  |                                                                                                                                                                    | Telephone No. (703) 305-4385                                                                                                       | SECTEL DEVENTOR                   |  |  |  |  |  |

Form PCT/ISA/210 (second sheet)(July 1992)★