(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5084079号

(P5084079)

(45) 発行日 平成24年11月28日(2012.11.28)

(24) 登録日 平成24年9月14日(2012.9.14)

(51) Int.Cl.

H04B 1/7093 (2011.01)

F 1

H04J 13/00 421

請求項の数 5 (全 11 頁)

(21) 出願番号 特願2001-284240 (P2001-284240)

(22) 出願日 平成13年9月19日 (2001.9.19)

(65) 公開番号 特開2002-111540 (P2002-111540A)

(43) 公開日 平成14年4月12日 (2002.4.12)

審査請求日 平成20年9月19日 (2008.9.19)

(31) 優先権主張番号 09/664646

(32) 優先日 平成12年9月19日 (2000.9.19)

(33) 優先権主張国 米国(US)

(73) 特許権者 596092698

アルカテルルーセント ユーエスエー

インコーポレーテッド

アメリカ合衆国 07974 ニュージャ

ーシー, マレイ ヒル, マウンテン アヴ

エニュー 600-700

(74) 代理人 100094112

弁理士 岡部 謙

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100085176

弁理士 加藤 伸晃

(74) 代理人 100106703

弁理士 産形 和央

最終頁に続く

(54) 【発明の名称】 フェージングチャネルにおいて複数シーケンスを検出し識別するためのセグメント化アーキテクチャ

## (57) 【特許請求の範囲】

## 【請求項 1】

シンボルの数と同一の数を有する相関器を用いて複数のシンボルを含む受信した信号を検出し識別する方法であって、前記複数のシンボルの各々は複数のチップを含み、前記方法は、

前記受信した情報を少なくとも第1及び第2のセグメントへセグメント化するステップであって、各セグメントが前記複数のシンボルの各々からの少なくとも1つのチップを有する、ステップと、

少なくとも第1及び第2のシンボル相関出力セットを生成するために、前記少なくとも第1及び第2のセグメントにおける前記少なくとも1つのチップにより表される前記複数のシンボルの各々を、前記相関器の各々を用いて代表的なシンボルに相関させるステップと、

少なくとも第1及び第2の信号識別出力セットを生成するステップであって、前記第1の信号識別出力セットは、前記第1のシンボル相関出力セットにより表される第1の信号と複数の予期される信号強度の各々との間でのマッチングの程度を示し、前記第2の信号識別出力セットは、前記第2のシンボル相関出力セットによって表される第2の信号と前記複数の予期される信号強度の各々との間でのマッチングの程度を示す、ステップと、

複数の加算信号識別出力を形成するために、前記少なくとも第1及び第2の信号識別出力セットからの対応する信号識別出力を加算するステップと、そして、

前記受信した信号を検出し識別するために、前記複数の加算信号識別出力を閾値と比較

するステップとを含む方法。

【請求項 2】

前記セグメントの少なくとも 1 つをデインタリープするステップをさらに含む請求項 1 記載の方法。

【請求項 3】

前記代表的なシンボルが少なくとも 2 つのシンボルについて同じである請求項 1 記載の方法。

【請求項 4】

前記閾値が各加算信号識別出力について同じである請求項 1 記載の方法。

【請求項 5】

シンボルの数と同一の数を有する相関器を用いて、受信した信号を検出し識別する方法であって、

前記受信した信号を、少なくとも第 1 及び第 2 のセグメントへセグメント化するステップであって、前記セグメントの各々は少なくとも 2 つのシンボルを有する、ステップと、

少なくとも第 1 及び第 2 のシンボル相関出力セットを生成するために、前記少なくとも第 1 及び第 2 のセグメントの前記シンボルの各々を、前記相関器の各々を用いて代表的なシンボルと相関させるステップと、

少なくとも第 1 及び第 2 の信号識別出力セットを生成するステップであって、前記第 1 の信号識別出力セットは、前記第 1 のシンボル相関出力セットにより表される第 1 の信号と複数の予期される信号強度の各々との間でのマッチング程度の程度を示し、前記第 2 の信号識別出力セットは、前記第 2 のシンボル相関出力セットによって表される第 2 の信号と前記複数の予期される信号強度の各々との間でのマッチングの程度を示す、ステップと、

複数の加算信号識別出力を形成するために、前記少なくとも第 1 及び第 2 の信号識別出力セットからの対応する信号識別出力を加算するステップと、そして、

前記受信した信号を検出し識別するために、各加算信号識別出力を閾値と比較し、前記閾値が各加算信号識別出力について同じである、ステップを含む方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

関連する主題は、本明細書と同時出願された以下の出願に開示されている：「フェージングチャネルにおいて信号を検出するためのセグメント化された相関器アーキテクチャ (Segmented Correlator Architecture For Signal Detection In Fading Channels)」と題する米国特許出願第 09/665,511 号。

本発明は通信に関し、特に無線通信に関する。

【0002】

【従来の技術】

無線通信は、移動通信局と基地局との間に音声またはデータの通信チャネルを作成することを含む。通信チャネルのセットアップには、通常、移動局が基地局によって監視されるアクセスチャネル上で既知のシーケンスを送信することを含む。基地局は既知のシーケンスを検出し、移動局と基地局との間のタイミング差推定等の機能にこれを用いる。

【0003】

移動局によりアクセスチャネルを介して基地局に送信される信号は、通常、S 個のシンボルを含む M 個の可能なシグネチャシーケンスのうちの 1 つに基づく既知のシーケンスを含む。このようなシステムの 1 つにおいては、M = 16 個の異なるシグネチャシーケンスを利用でき、各シグネチャシーケンスは、S = 16 個のシンボルを含む。UMTS WCDMA は、16 長ウォルシュ - アダマールシーケンスをシグネチャシーケンスとして用いる。これらシーケンスは当分野で周知であり、3GPP TSG RAN 「拡散と変調 (Spreading and Modulation) (FDD)」 (TS25.213V3.2.b.) の第 15、16 頁に記載されている。16 シンボルシグネチャシーケンスのうちの 1 つが選択されると、これを用いて、基地局に送信

10

20

30

40

50

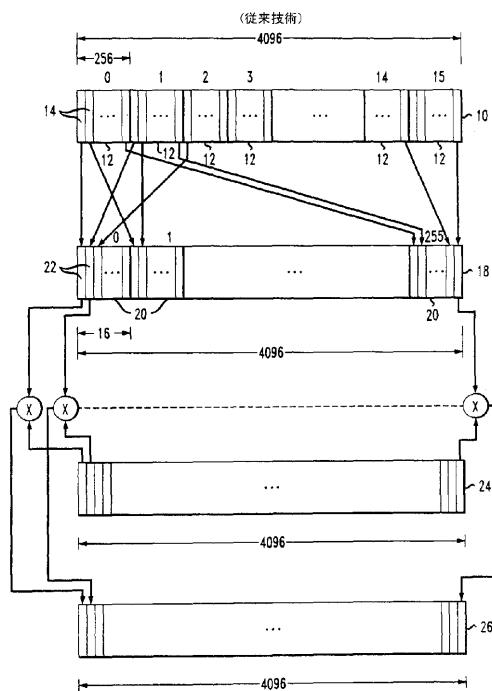

するシーケンスを生成する。図1は、どのように送信シーケンスが16シンボルシグネチャシーケンスから生成されるかを示したものである。シーケンス10は、シンボル期間12を有する16シンボルシグネチャシーケンスを表し、ここで各シンボルは+1または-1である。16シンボル期間はそれぞれCのチップすなわちサンプル期間14に分割され、この例ではC=256である。その結果、シグネチャシーケンスは総計Kのチップすなわちサンプル期間を含むことになり、ここではK=4,096である(S=16シンボル期間×シンボル期間当たりC=256のチップ期間)。シグネチャシーケンスを用いて、インタリードシーケンス18を生成する。インタリードシーケンスは256(K/C)の反復期間20を含み、該反復期間20はそれぞれ16(S)チップ期間22、総計で4,096(K)のチップ期間を有する。インタリードシーケンスは、シグネチャシーケンス10のシンボル期間0~15の最初のチップ期間のシンボル値を用いて、インタリードシーケンス18の反復期間0の最初の16チップ期間を埋めることで作成される。インタリードシーケンス18の反復期間1のチップ期間は、シグネチャシーケンス10の16シンボル期間それぞれの二番目のチップ期間におけるシンボル値を用いて埋められる。同様に、インタリードシーケンス18の反復期間2のチップ期間は、シグネチャシーケンス10のシンボル期間0~15の三番目のチップ期間におけるシンボル値を用いて埋められる。このプロセスは、最後の反復期間(反復期間255)の16チップ期間が、シグネチャシーケンス10の16シンボル期間それぞれの最後のチップ期間におけるシンボル値を用いて埋められるまで続けられる。その結果、インタリードシーケンス18は、16チップ期間をそれぞれ含む256反復期間からなる。各反復期間は、シグネチャシーケンス10の各シンボル期間からの1つのチップ期間の値に等しい値を有する16チップ期間を含む。したがって、シグネチャシーケンス10のシンボル期間0~15のサンプルは、インタリードシーケンス18の各反復期間のチップ0~15それに含まれる。

#### 【0004】

移動局から基地局に送信される既知のシーケンスを生成する際の最後のステップは、インタリードシーケンス18と4,096(K)チップ期間二値シーケンス24とのチップ期間ごとの乗算を行うことを含む。二値シーケンス24は既知であり、移動体が通信する特定の基地局に割り当てられる。チップ期間ごとの乗算の結果は送信シーケンス26であり、これが次に移動体によって基地局に送信される。

#### 【0005】

可能な送信シーケンス26のセットは、移動体送信を受信することになる基地局に知れている。利用できるシグネチャシーケンス、二値シーケンス、およびインタリードパターンは知られているため、可能な送信シーケンス26のセットもまた利用できる各シグネチャシーケンスごとに知れている。

#### 【0006】

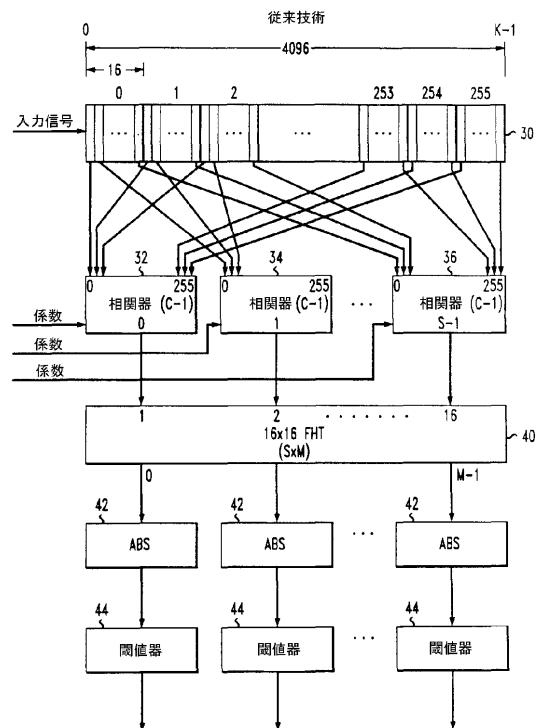

図2は、移動局によって送信され、基地局で受信される既知のシーケンスを識別し検出するために基地局によって用いられる多重信号検出器を示している。シフトレジスタ30は、受信したシーケンスのサンプルを受信する。シフトレジスタ30は、受信したシーケンスを構成する4,096のチップ期間に対応する4096のサンプルに備えるために、4,096(K)のロケーションを有する。受信したシーケンスを作成するために用いたインタリードを考慮するため、シフトレジスタ30から相関器32、34、および36にサンプルを提供しながら、デインタリードプロセスを実行する。各16チップ長反復期間の最初のチップ期間は、相関器32に提供されることに留意されたい。同様に、各16チップ長反復期間の二番目のチップ期間は、相関器34に提供される。このプロセスは、総計16の相関器について続けられ、16番目の相関器すなわち相関器36が各16チップ長反復期間の最後のチップを受信する。このデインタリードプロセスは、各相関器にシンボル期間の256チップ期間サンプルを提供する。各相関器には、1つのシンボルを表す256チップ期間値に関する一連の値を表す係数が提供されている。相関器に提供される一連の係数は、インタリードシーケンス18と二値シーケンス24との間のチップ期間

10

20

30

40

50

ごとの乗算を考慮に入れたものであることに留意する。各相関器によって提供される出力は、シンボル期間からの 256 チップ期間値が +1 または -1 シンボルに予期される一連のチップ期間値にどの程度良好にマッチするかを示す。その結果、高速アダマール変換器 (FHT) 40 が 16 個の相関器それぞれからの入力を受信する。ここで、各入力は、相関器によって検査される 256 チップ期間値がシンボルにどの程度良好に対応するか、およびその対応が +1 シンボルであるか、または -1 シンボルであるかを表す。

#### 【0007】

FHT は当分野で周知であり、D. Elliot および K. Rao による「高速変換：アルゴリズム、解析、応用 (Fast transforms: algorithms, analysis, applications)」(Academic Press, Orlando, Florida, 1982) 等の参照に記載されている。FHT 40 には、相関器から提供される出力に基づいて、可能な 16 のシグネチャシーケンスのいずれを受信しているかを識別するために用いられる係数が提供されている。FHT は、可能なシグネチャシーケンスのうちの 1 つにそれぞれ対応する 16 の出力を提供する。ここで、出力の大きさは、シフトレジスタ 30 におけるサンプルが各シーケンスにどの程度良好にマッチするかを示す。FHT 40 の出力はそれぞれ絶対値発生器 42 に提供される。該絶対値発生器 42 は、各 FHT の出力の絶対値または絶対値の二乗をとる。絶対値発生器 42 の各出力は閾値器 44 に提供され、該閾値器 44 が絶対値発生器 42 からの値を所定の閾値と比較する。値が閾値を上回る場合、検出が宣言され、閾値超過信号を生成した FHT 出力によって、受信したシーケンスが特定のシグネチャシーケンスに対応するものとして識別される。

10

#### 【0008】

基地局が検索窓と呼ばれる時間期間でシーケンスを検出しようとするに留意されたい。検索窓は、通常、受信したシーケンスのサンプル期間の N 倍である。シフトレジスタ 30 は、初期サンプルセットで埋められると、N - 1 回新しいサンプルをシフトインすると共に、古いサンプルをシフトアウトする。この結果、シフトレジスタ 30 に提供されるサンプル間の時間期間を N 倍したものに等しい検索窓にあたり、予期されるシーケンスの検出を N 回試みることになる。検出されたシーケンスの検索窓における位置は、検出すべきシグネチャパターンに対応する FHT の出力の 1 つが閾値を越える場合に、シフトレジスタ 30 により行われるシフトの数によって決定される。検索窓における検出されたシーケンスの位置は、移動局と基地局との間の往復遅延の測度である。

20

#### 【0009】

##### 【発明が解決しようとする課題】

移動局が高速で移動中の自動車または列車内にある場合、シフトレジスタに供給される信号は高速フェージングを受ける。その結果、シフトレジスタが受信するシーケンスは部分的に破損し、低い FHT 出力を生成する。その結果、閾値と比較する FHT 出力は閾値を超えず、そのため受信したシグネチャシーケンスを検出または識別することができない。

30

#### 【0010】

##### 【課題を解決するための手段】

本発明は、セグメント化相関器および FHT (高速アダマール変換) アーキテクチャを用いて、高速フェージング環境においてウォルシュ - ハダマードシーケンスおよびスクランブルシーケンスからなるシーケンス等、既知のシーケンスの検出および識別を提供する。サンプルまたはデータの入力シーケンスがブロックにセグメント化される。各ブロックは、相関器 / FHT セグメントを用いて個々に検出される。各相関器 / FHT セグメントの出力を識別する各シーケンスは、他の相関器 / FHT セグメントの対応する出力と加算される。各和は閾値と比較され、特定のシーケンスが検出され識別されたかを判断する。

40

#### 【0011】

##### 【発明の実施の形態】

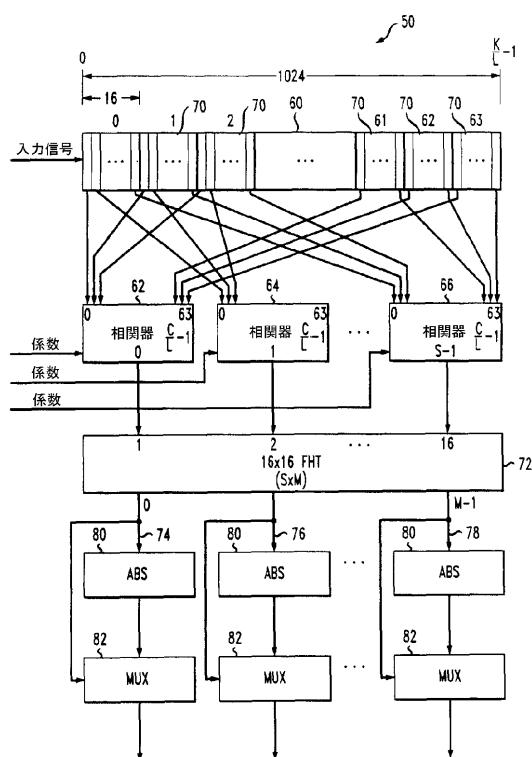

図 3 は、セグメント化されたシーケンス検出器 / 識別器の相関器 / FHT セグメント 50 の機能ブロック図を示す。この例において、信号検出器 / 識別器は、図 3 に示す  $L = 4$  のセグメントを含む。図 4 は、検出器 / 識別器を構成する  $L$  セグメント間の関係を示す。各

50

Lセグメントは入力信号のK / Lサンプルを受信するが、但しKはそのシーケンスを含むチップ期間またはサンプルの数である。新しいサンプルが最初のセグメントにシフトインされると、最も古いサンプルが最初のセグメントからシフトアウトされ、二番目のセグメントにシフトインされる。同様に、残っているセグメントはそれぞれ先行セグメントから入力を受け取り、最も古いサンプルを次のセグメントにシフトアウトする。

#### 【0012】

検出および識別プロセスは、入力信号のKサンプルの初期セットを受信した（すなわち、各セグメントがK / Lサンプルの初期セットを有する）後に開始する。図3に戻り、シフトレジスタ60は、受信したシーケンスの初期すなわちK / L(1024)サンプルを受信するが、但しLは検出器/識別器を構成するセグメントの数であり、基地局で移動局から受信したシーケンスを構成するチップ期間またはサンプルの数である（この例では、K = 4096）。他の値のLを用いてもよく、Lの値が大きいほど、ハードウェアおよび/または処理を犠牲にして、高速フェージング環境においてパフォーマンスが改良される。受信シーケンスはシフトレジスタ60においてデインタリーブされ、相関器62、64～66に提供される。デインタリーブは、シーケンスが移動局によって生成されたときに行われたあらゆるインタリーブ化を解除するために用いられる。送信されたシーケンスがインタリーブなしで生成された場合には、デインタリーブを省いてもよい。3つの相関器しか示さないが、この実施形態において、長さ64の16個の相関器を用いることに留意されたい。シグネチャシーケンスがS = 16シンボルを含むものと前提するため、この例では16個の相関器を用いる。一般的に、相関器の数は、識別すべきシーケンスにおけるシンボルの数と一致すべきであり、相関器はC / Lの長さであるべきである。但し、Cはシグネチャシーケンスにおけるシンボル期間当たりのチップ期間の数である。この例では、C = 256である。16シンボルの例に戻り、16チップ長の反復期間70それぞれの最初の期間のチップ値は、相関器62に提供され、16チップ長の反復期間70それぞれの二番目の期間のチップ値は相関器64に提供され、相関器66が16チップ長の反復期間70それぞれの最後のチップ値を受信するまで、同様にして残りの相関器が入力値で埋められる。相関器62、64、および66に提供される係数すなわち代表的なシンボルは、インタリーブドシーケンスと基地局関連の二値シーケンスとの間でのチップ期間ごとの乗算を考慮に入れた場合に予期されるC / L(64)チップ値シーケンスである。各相関器の出力は、相関器に提供されるC / Lチップ値が、+1または-1シンボルについて予期される一連のチップ期間値にどの程度良好にマッチするかを示す。相関器62、64、および66のシンボル相関器の出力は、 $16 \times 16 (S \times M) FHT 72$ に提供される。ここで、Sはシグネチャシーケンスにおけるシンボルの数であり、Mは受信可能な異なるシグネチャシーケンスの数である。相関器からの出力に基づいて、FHT72は、相関器からの信号相関入力によって表される信号が、16(M)個の可能なシグネチャシーケンスにどの程度良好に対応するかを示す16(M)個の信号識別出力それについての出力値を提供する。たとえば、出力74は、レジスタ60におけるシーケンスが最初のシグネチャシーケンスにどの程度良好に対応するかを示す。同様に、出力76は、レジスタ60におけるシーケンスが二番目のシグネチャシーケンスにどの程度良好に対応するかを示す。最後に、出力78は、レジスタ60におけるシーケンスが16番目(M番目)のシグネチャシーケンスにどの程度良好に対応するかを示す。M個の可能なシグネチャシーケンスが識別される場合、M個の出力FHTを用いるべきであることに留意されたい。さらに、シンボル数SがMに等しいことが望ましい。図3に戻り、各FHTまたは信号識別出力は、絶対値発生器80およびマルチプレクサ82に提供される。絶対値発生器80は、FHT72からの出力の絶対値か、絶対値の二乗のいずれかを発生し、その値をマルチプレクサ82に提供する。マルチプレクサ82は、FHT72の出力か、または絶対値発生器80の出力を選択する。高速フェージング環境において信号の検出が試みられている場合には、絶対値発生器80の出力が選択される。深刻さのより低いフェージング環境において信号の検出が試みられている場合には、FHT72の出力が選択される。マルチプレクサ82の出力は、図4に示すように組み合わせられる。

10

20

30

40

50

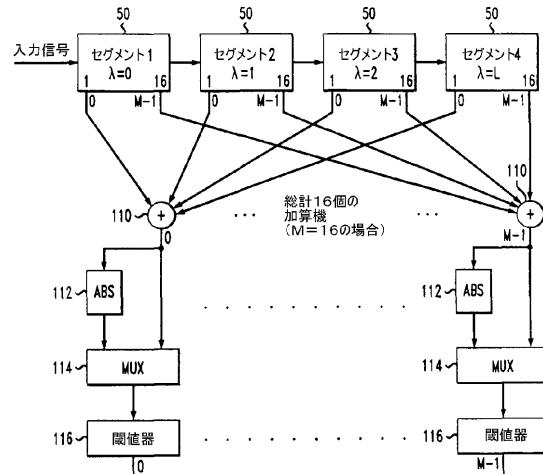

## 【0013】

図4は、 $L = 4$ の相関器 / FHTセグメント50を組み合わせて、セグメント化されたシーケンス検出器 / 識別器を提供する様式を示す。各セグメント50は、図3に示す相関器 / FHTセグメントに対応する。各セグメント50は、特定のシグネチャシーケンスにそれぞれ関連する16( $M$ )個の信号識別出力を提供する。セグメント50からの出力は加算器110で加算され、各加算器は、特定のシグネチャシーケンスに関連する一群の出力を加算する。この例では、16( $M$ )個の可能なシグネチャシーケンスがあるため、16個の加算器110がある。しかし、図を簡潔にするため、2個の加算器しか示さない。各加算器110の出力は、絶対値発生器112およびマルチプレクサ114に提供される。絶対値発生器は、加算器110によって生成される出力の絶対値、または絶対値の二乗を発生する。次に、絶対値発生器112の出力がマルチプレクサ114に提供される。マルチプレクサ114を用いて加算器110の出力と、絶対値発生器112の出力を選択する。高速フェージング環境では、マルチプレクサ114を用いて加算器110の出力を選択する。深刻さのより低いフェージング環境では、マルチプレクサ114を用いて絶対値発生器の出力を選択する。マルチプレクサ114の出力は閾値器116に提供され、閾値器116が、マルチプレクサの出力を所定の閾値と比較する。各シグネチャシーケンスに1つが関連する16( $M$ )個の閾値116がある。閾値の1つが、入力が所定の閾値を超過することを示す場合、その閾値器に関連するシグネチャシーケンスが検出され、識別される。

## 【0014】

20

入力信号は、入力シフトレジスタ60を介し、セグメント50を通してシフトされて検査され、入力信号サンプル期間のN倍の検索窓が検査されるまで、既知のまたは予期されるシーケンスを検出 / 識別するよう試みる。これは、入力信号の初期Kサンプルを検査してから、Kサンプルの次の新しいN-1セットそれぞれを検査することで達成される。新しいKサンプルセットは、シフトレジスタ60が新しい入力信号サンプルをシフトインし、最も古いサンプルをシフトアウトする度に生成される。検出 / 識別されたシーケンスの検索窓における位置は、閾値器116による閾値を超過を検出したときに、シフトレジスタ60によって行われるシフトの数によって決定される。

## 【0015】

30

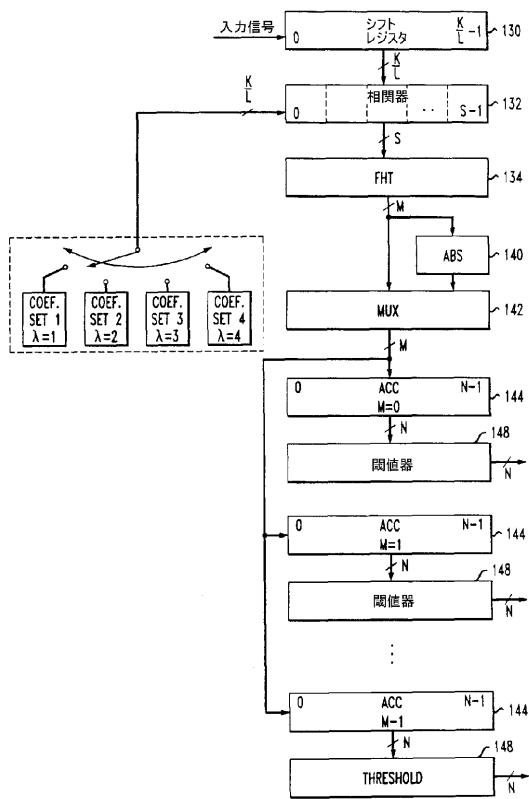

図5は、セグメント化された時分割多重アーキテクチャを用いる検出器 / 識別器アーキテクチャを示す。この例において、検索窓はサンプル期間のN個分の長さであり、NはK / L以下である。ここで、Kサンプルの入力シーケンスは長さK / LのL個のセグメントにセグメント化される。入力シフトレジスタ130は、各セグメントについてデータを左から右にN-1回シフトし、そうすることでNセットのK / Lサンプルを相関器132に提供する。この例において、シーケンスはS個のシンボルからなり、各シンボルはCのチップ期間を含む。したがって、それぞれ長さC / Lを有するS個の相関器を用いることが望ましい。この結果、相関器132は、各セグメントごとにNセットのSシンボル相関出力を生成することになる。この例では、L個の異なるセグメントがあるため、L個の異なる係数セットが相関器132に提供される。ここで、各係数セットは、代表的なシンボルの予期されるシーケンスセグメントまたはシーケンスを表す。最初のセグメントが相関器132に提供されると、最初のセットのK / L係数もまた該相関器に提供される。同様に、二番目のセグメントのK / Lサンプルが相関器132に提供され、第2のセットのK / L係数が相関器に提供される。このプロセスは、サンプルの最後のすなわちL番目のセグメントが相関器132に提供されるまで続けられる。各セグメントについて、相関器132からのNセットのS個の出力はそれぞれ、FHT134に提供される。FHT134はS × MのFHTである。但し、Mは識別すべき可能なシグネチャシーケンスの数である。FHT134のM出力はそれぞれ、相関器132のS個の出力で表されるシーケンスまたは信号が、M個の可能なシグネチャシーケンスの1つすなわち予期されるシーケンスとどの程度良好にマッチするかを示す。その結果、各セグメントについて、FHT134からのNセットのM個の信号識別出力が、絶対値発生器140およびマルチプレクサ142の双

方に提供される。上述したように、絶対値発生器 140 は、FHT134 の出力の絶対値または絶対値の二乗をとることができる。高速フェージング環境で信号検出を行う場合、マルチプレクサ 142 は絶対値発生器 140 の出力を選択して、これを累算器 144 に提供する。深刻さがより低いフェージング環境では、マルチプレクサ 142 は FHT134 の出力を選択し、これを累算器 144 に提供する。マルチプレクサ 142 から受信した M 個の出力それぞれに、別個の累算器 144 が設けられる。この結果、M 個の可能なシグネチャシーケンスそれぞれに別個の累算器が用いられることになる。L 個のセグメントそれぞれに、N セットの M 個の出力が生成されることを想起すると、N 個の別個の累算が生成されて、各累算器 144 に格納される。ここで、N 個の累算はそれぞれ、検索窓における異なる位置に関連付けられる。その結果、入力データストリームが L 個のセグメントに分割される場合、各累積器 144 は別個の N 個の累算それぞれに L 個の値を累積する。L 個の値が N 個の累積それぞれに累積された後、累積器 144 の出力が閾値器 148 に提供される。M 個の閾値器 148 がある。各閾値器は、M 個の可能なシグネチャシーケンスのうちの異なる 1 つに対応する。シグネチャシーケンスは、M 個の閾値のいずれが、閾値を越えたことを示すかによって識別される。さらに、検索窓における識別されたシーケンスの位置は、N 個の累積器のいずれが閾値を超えるかによって示される。累積器が L 個のセグメントについて完了した後、かつ N 個の累積すべてを閾値と比較した後、累積器 144 およびシフトレジスタ 130 がクリアされ、プロセスが次の信号受信期間の開始において繰り返される。

## 【0016】

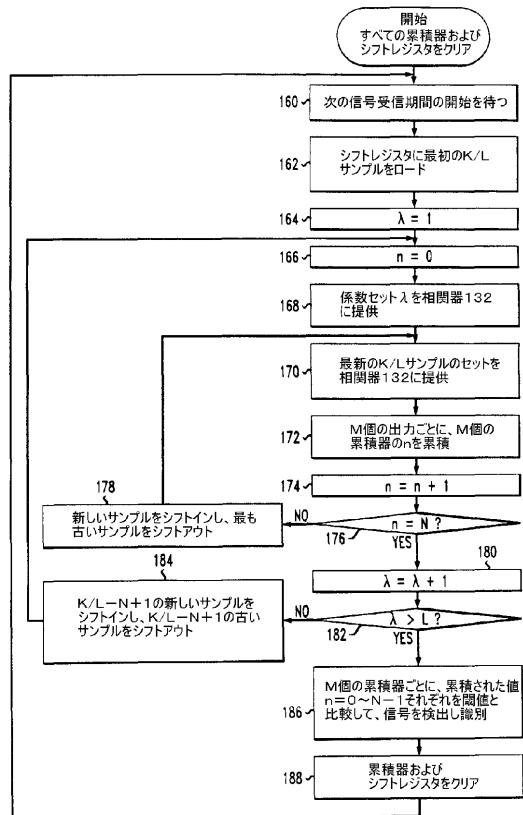

図 6 は、図 5 の時分割多重化アーキテクチャを用いて、信号の検出および識別がどのように達成されるかを示すフローチャートである。最初に、累積器 144 およびシフトレジスタ 130 がクリアされる。ステップ 160 において、プロセスは、基地局の次の信号受信期間の開始を待つ。信号受信期間が開始すると、ステップ 162 が実行され、ここでシフトレジスタ 130 に入力信号の最初の K / L サンプルがロードされる。ステップ 164 においてインデックス  $n$  が 1 に等しくセットされ、ステップ 166 においてインデックス  $n$  が 0 に等しくセットされる。ステップ 168 において、係数セット  $n$  が相関器 132 に提供される。ステップ 170 において、シフトレジスタ 130 からの最新の K / L サンプルセットが相関器 132 に提供される。相関器 132 からの結果得られるシンボル相関出力が FHT134 に提供され、FHT134 の M 個の出力が絶対値発生器 140 およびマルチプレクサ 142 に提供される。マルチプレクサ 142 の M 個のシンボル識別出力は M 個の累積器 144 に提供され、ステップ 172 において、各累積器が M 個の出力のうちの 1 つを受信し、これを累積  $n$  に追加する。ステップ 174 において、インデックス  $n$  は  $n + 1$  に等しくセットされる。ステップ 176 において、インデックス  $n$  が検索窓におけるサンプル期間の数である N に等しいか否かを決定する。インデックス  $n$  が N 未満である場合、ステップ 178 が実行され、ここで入力信号の新しいサンプルがシフトレジスタ 130 にシフトインされ、最も古いサンプルがシフトレジスタからシフトアウトされる。ステップ 178 において、ステップ 170 が実行され、ここでシフトレジスタ 130 からの最新の K / L サンプルセットが相関器 132 に提供される。このプロセスは、N セットの K / L サンプルが検査されるまで、かつ各セットの M 個の結果が累積器 144 内の対応する  $n$  累積に格納されるまで繰り返される。N セットの入力サンプルが評価されると、ステップ 176 が  $n = N$  であると判断し、ステップ 180 が実行される。ステップ 180 において、インデックス  $n$  が  $N + 1$  に等しくセットされる。ステップ 182 において、インデックス  $n$  が L よりも大きいか否かが判断される。インデックス  $n$  が L 以下である場合、ステップ 184 が実行され、検査のために、シフトレジスタ 130 に次のセグメントが提供される。ステップ 184 において、入力信号の K / L - N + 1 の新しいサンプルがシフトレジスタ 130 にシフトインされ、K / L - N + 1 の古いサンプルがシフトレジスタからシフトアウトされる。ステップ 184 の後、ステップ 166 が実行され、ここでインデックス  $n$  が 0 に等しくセットされ、ステップ 168 が実行され、ここで相関器 132 に使用すべき次の係数セットが提供される。先行セグメントのように、N セットの K / L サンプルが検

10

20

30

40

50

査され、M個の累積器144におけるN個の別個の累積に累積されるNセットのM個の出力を生成する。ステップ182に戻り、 $g_L$ よりも大きいと判断された場合、ステップ186が実行される。インデックス $L$ は $L$ よりも大きいため、入力信号に関するすべてのセグメントが検査されている。ステップ186において、M個の累積器144それぞれにおける $L$ 値のN個の各累積が、閾値器148において所定の閾値と比較され、既知の信号またはシーケンスが検出されたか否かを判断する。信号またはシーケンスは、M個の閾値のうちのいずれが閾値を越えることを示すことで識別される。閾値を超える特定の累積 $n$ （但し、 $n$ は0～N-1に等しい）が、検索窓における検出された信号の位置を決定する。ステップ186後、ステップ188が実行され、ここで累積器144およびシフトレジスタ130がクリアされる。次に、ステップ160が実行され、プロセスは再び、基地局の次の信号受信期間の開始を待つ。

10

#### 【0017】

図3～図5に示すアーキテクチャは、機能ブロック図に示される機能を行う、各ブロックに関連する個々の回路、特定用途向け集積回路（ASIC）、またはデジタル信号プロセッサ（DSP）等の汎用プロセッサを用いて実行しうることに留意されたい。

#### 【図面の簡単な説明】

【図1】シグネチャシーケンスを使用して、どのように移動局から基地局に送信される送信シーケンスを生成するかを示す。

【図2】従来技術による信号検出器および識別器を示す。

【図3】セグメント化された相関器およびFHTアーキテクチャを用いる信号検出器および識別器を示す。

20

【図4】複数にセグメント化された相関器およびFHT出力の結果を組み合わせての最終的な出力の生成を示す。

【図5】セグメント化された時分割多重相関器およびFHTアーキテクチャを示す。

【図6】セグメント化された時分割多重相関器およびFHTアーキテクチャを用いる信号の検出および識別のフローチャートである。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(74)代理人 100096943

弁理士 白井 伸一

(74)代理人 100091889

弁理士 藤野 育男

(74)代理人 100101498

弁理士 越智 隆夫

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100102808

弁理士 高梨 憲通

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100107401

弁理士 高橋 誠一郎

(74)代理人 100106183

弁理士 吉澤 弘司

(72)発明者 ジュン アー リー

アメリカ合衆国 08867 ニュージャーシィ, ピツツタウン, グローヴ ファーム ロード

40

(72)発明者 スティーヴン アンドリュー ウッド

イギリス国 ピース8 4エヌキュー ブリストル, ホットウェルズ, ホットウェル ロード

307 フラット 4

(72)発明者 グレゴリー ジェー. ロクロウスキ

アメリカ合衆国 07405 ニュージャーシィ, キネロン, チェリー ツリー レーン 14

(72)発明者 ウッドソン デール ウィン

アメリカ合衆国 07920 ニュージャーシィ, バスキング リッジ, ジュニパー ウェイ 5

6

審査官 岡 裕之

(56)参考文献 国際公開第99/041846 (WO, A1)

米国特許第06028887 (US, A)

InterDigital Comm. Corp., Reissue of SMG2 L1 Documents on RACH Preamble Detection, 3GP

P R1-99138, 1999年 3月26日

Nokia, Further clarification of Nokia's RACH preamble proposal, 3GPP R1-99599, 199

9年 6月 4日

3GPP TS25.213 V3.2.0, 2000年 3月, pp.15,16

(58)調査した分野(Int.Cl., DB名)

H04B 1/7093