244 Sheets-Sheet 1

**ATTORNEY**

Filed Dec. 26, 1957

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

IC

3,036,773

Filed Dec. 26, 1957

3,036,773

Filed Dec. 26, 1957

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

244 Sheets-Sheet 12

3,036,773

Filed Dec. 26, 1957

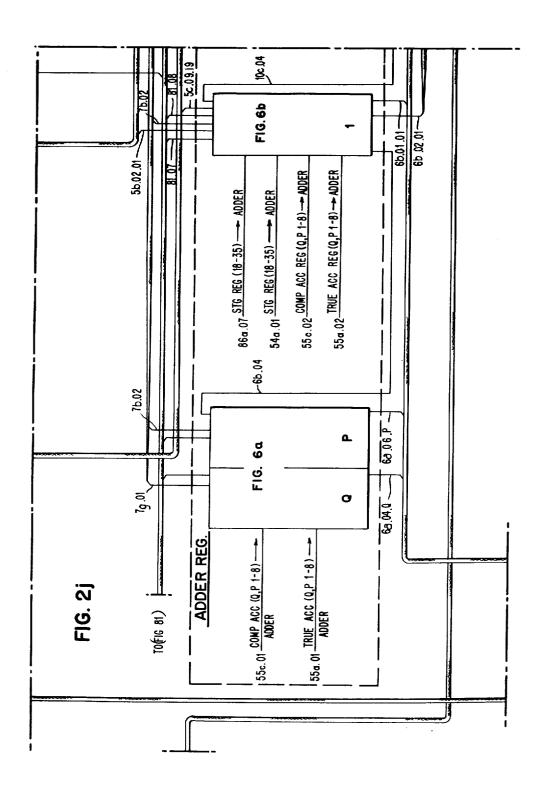

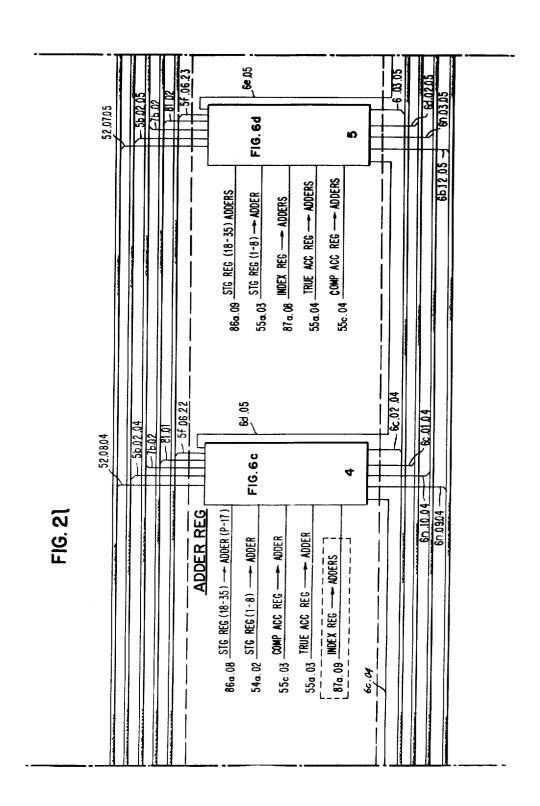

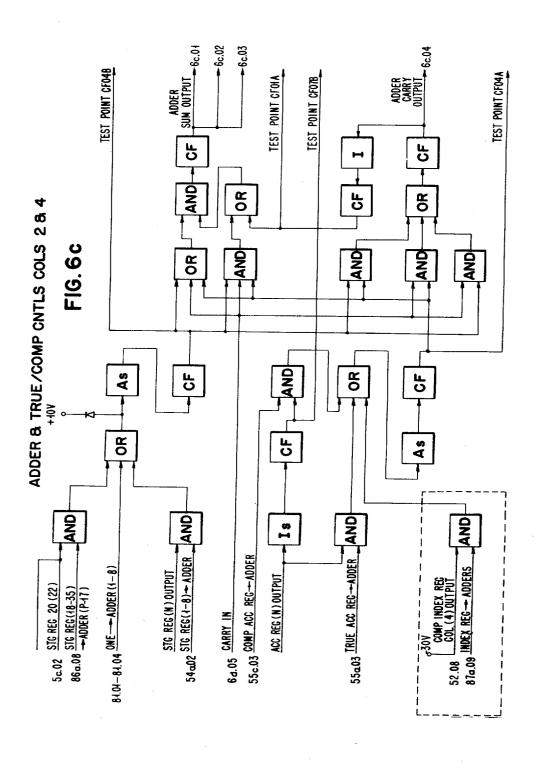

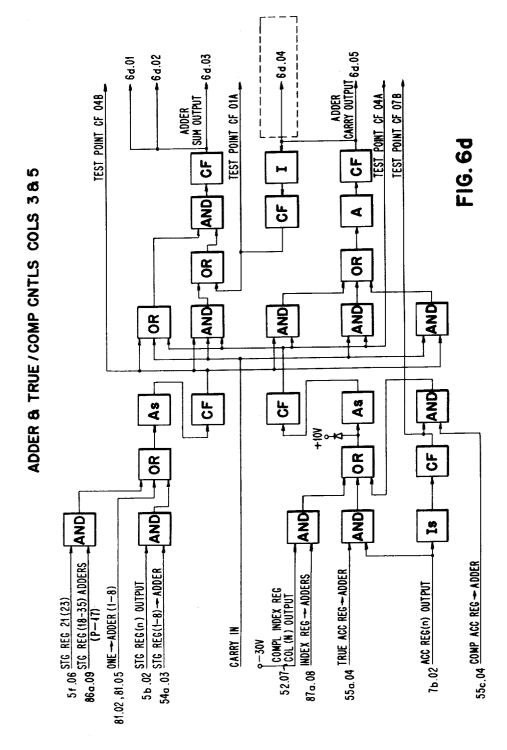

90.00 FIG. 6d 52.07.3 6n.06.03 54 a. 03 STG REG (1-8) --- ADDER 55a.04 TRUE ACC REG --- ADDERS 55c.04 COMP ACC REG --- ADDER 86a.09 STG REG (18-35) ADDERS 87a.08 INDEX REG --- ADDERS ADDER REG 8.05 FIG. 6c N 89a.08 STG REG(18-35) -- ADDER (P-17) 55c.03 COMP ACC REG --- ADDER 55a.03 TRUE ACC REG ---- ADDER

3,036,773

Filed Dec. 26, 1957

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

244 Sheets-Sheet 15

3,036,773

Filed Dec. 26, 1957

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

244 Sheets-Sheet 16

3,036,773

Filed Dec. 26, 1957

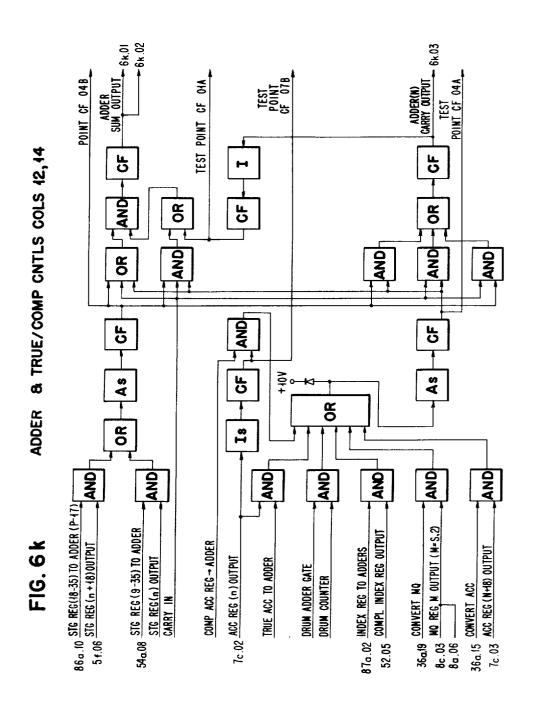

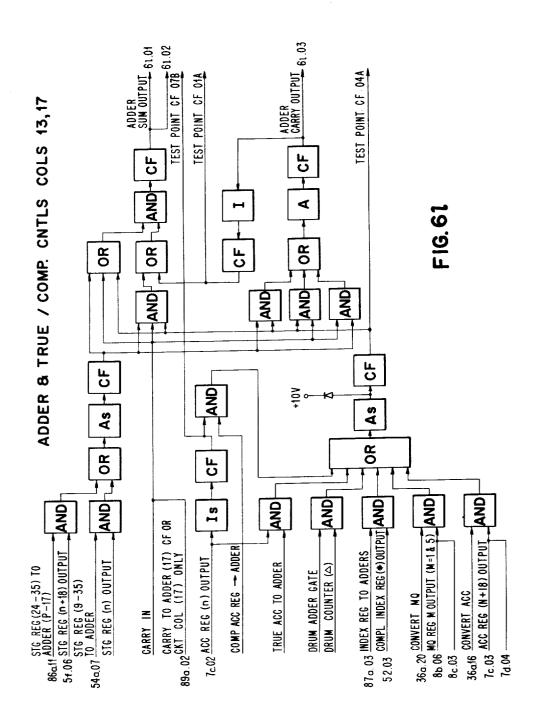

SF.06.32 FIG. 6k 8 b. 03.02 55c.13 COMP ACC REG --- ADDER 54a.08 STG REG ( 9-35) TO ADDER 86o.10 STG REG (18-35) TO ADDER 87a. 02 INDEX REG TO ADDERS 55a.12 TRUE ACC TO ADDER DRUM ADDER GATE 36a 19 CONVERT NO 36a.15 CONVERT ACC Bn.31.13 52.03.13 IC .03.31 FIG. 6 10 70.02 86.03.01 54a.07 STG REG (9 -35) TO ADDER 86a.11 STG REG (24-35) TO ADDER 55c.13 COMP ACC REG -- ADDER 87c 03 MDEX REG TO ADDERS 55a.12 TRUE ACC TO ADDER DRUM ADDER GATE 36a.20 CONVERT NO 2

Filed Dec. 26, 1957

### J. L. BROWN INDIRECT ADDRESSING IN AN ELECTRONIC DATA PROCESSING MACHINE

Filed Dec. 26, 1957

244 Sheets-Sheet 19

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

### J. L. BROWN INDIRECT ADDRESSING IN AN ELECTRONIC DATA PROCESSING MACHINE

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

### J. L. BROWN INDIRECT ADDRESSING IN AN ELECTRONIC DATA PROCESSING MACHINE

3,036,773

Filed Dec. 26, 1957

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

244 Sheets-Sheet 27

3,036,773

Filed Dec. 26, 1957

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

3,036,773

Filed Dec. 26, 1957

3,036,773

Filed Dec. 26, 1957

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

FIG. 2mm

| F1G.2a  | FIG.2a FIG.2b   | FIG. 2c | FIG.24 | FIG. 2e | FIG.2c FIG.2d FIG.2e FIG.2f FIG.2g | FIG. 29 |         |         |                                                                                     |         |         |        |        |

|---------|-----------------|---------|--------|---------|------------------------------------|---------|---------|---------|-------------------------------------------------------------------------------------|---------|---------|--------|--------|

| FIG.2h  | FIG.2h FIG.2 i  | F1G.2j  | FIG.2k | FIG.21  | FIG.2m                             | F16.2n  | FIG.20  | FIG.2p  | FIG.2) FIG.2k FIG.21 FIG.2m FIG.2n FIG.20 FIG.2q FIG.2q FIG.2r FIG.2s FIG.2t FIG.2u | FIG.2 r | FIG.28  | FIG.21 | F16.2u |

| F1G.2v  | FIG.2v FIG.2w   | FIG.2x  | FIG.2y | FIG. 2z | FIG. 2aa                           | FIG.2bb | FIG.2cc | FIG.2dd | FIG.2x FIG.2y FIG.2a FIG.2bb FIG.2cc FIG.2dd FIG.2ee FIG.2ff FIG.2gg                | FIG2ff  | FIG.299 |        |        |

| FIG.2hh | FIG.21h FIG.211 |         |        |         |                                    |         |         |         |                                                                                     |         |         |        |        |

| FIG2jj  | FIG2jj FIG.2KK  | FIG.211 |        |         |                                    |         |         |         |                                                                                     |         |         |        |        |

Filed Dec. 26, 1957

244 Sheets-Sheet 42

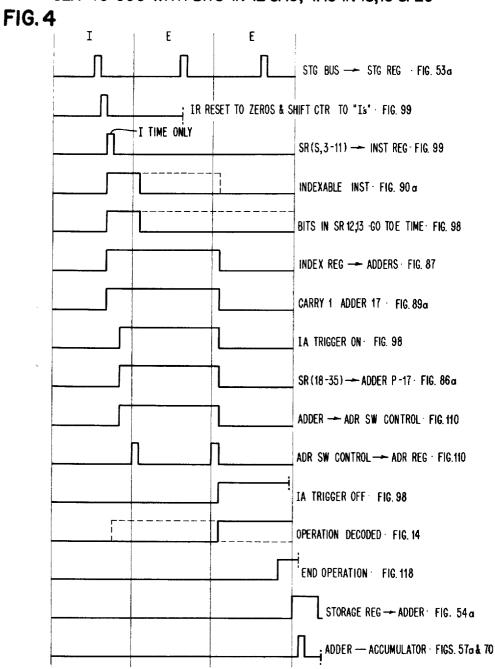

#### CLA TO 500 WITH BITS IN 12 & 13, TAG IN 18,19 & 20

Filed Dec. 26, 1957

3,036,773

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

Filed Dec. 26, 1957

244 Sheets-Sheet 47

3,036,773

Filed Dec. 26, 1957

3,036,773

Filed Dec. 26, 1957

3,036,773

Filed Dec. 26, 1957

3,036,773

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

----

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

244 Sheets-Sheet 71

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

Filed Dec. 26, 1957

244 Sheets-Sheet 79

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

3,036,773

Filed Dec. 26, 1957

244 Sheets-Sheet 83

#### SECONDARY OPERATION DECODER

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

244 Sheets-Sheet 84

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

May 29, 1962

Filed Dec. 26, 1957

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

244 Sheets-Sheet 87

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

Filed Dec. 26, 1957

244 Sheets-Sheet 91

3,036,773

Filed Dec. 26, 1957

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

Filed Dec. 26, 1957

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

Filed Dec. 26, 1957

244 Sheets-Sheet 96

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

FIG. 38

Filed Dec. 26, 1957

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE 244 Sheets-Sheet 129

Filed Dec. 26, 1957

-54p02 F) S AND OR S -ADDERS AND AND AND AND AND AND AND AND STG REG-LOGICAL COMPARE ACC WITH STG INST REG SIGN MINUS (2) TEST INDS (STG) 2nd STEP 48.09 TR INDS (ACC) 2nd STEP 39.09 TEST INDS (STG) 1st STEP ERG (04) ON EXCHANGE 41.03 PLACE INDS --- ACC 1223.11 E9 TILL CT2 (2) 122e.15 ER 4 (D2) 36 a. 26 ADD FOR CONVERT 42.02 HALF INDS CNTL 37.03 EXCL OR TO ACC 1220.44 ER TIME 122a.08 ER 0 (04) 122k.04 ER 10 (02) 122d.27 A 3 (04) 122:.04 A8 (04) 122e.26 14 (02) 39.14

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

3,036,773

244 Sheets-Sheet 136 Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

244 Sheets-Sheet 145

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

244 Sheets-Sheet 162

#### FLOATING POINT TALLY COUNTER

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

244 Sheets-Sheet 163

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

t.

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

244 Sheets-Sheet 174

#### INSTRUCTION REGISTER SIGN PLUS & MINUS

FIG.100

Filed Dec. 26, 1957

244 Sheets-Sheet 178

#### F.P. ENTRY TO SHIFT CTR. (10-17)

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

FIG. 112

PRIMARY DRIVE CIRCUITS

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

Filed Dec. 26, 1957

244 Sheets-Sheet 188

3,036,773

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

3,036,773,

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

244 Sheets-Sheet 200

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

----

Filed Dec. 26, 1957

244 Sheets-Sheet 210

3,036,773

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

244 Sheets-Sheet 221

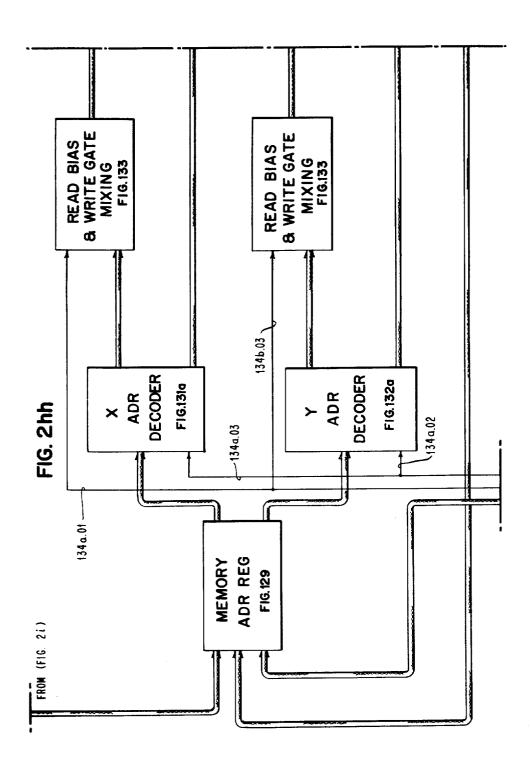

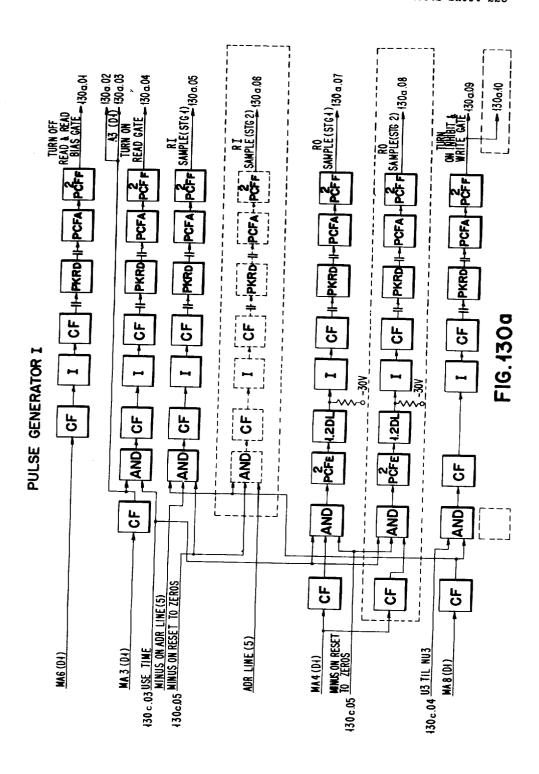

### FIG. 129a STORAGE ADDRESS REGISTER

Filed Dec. 26, 1957

244 Sheets-Sheet 222

#### STORAGE ADDRESS REGISTER FIG. 129b STOR ADR REG 12 1296.01 CF 1475.09 RESET STOR ADR REG & BUFFER REG STOR ADR REG 12 1296 .02 1340 05 STOR ADD REG R1 121 .08 U TIME CF 16a .02 ADR LINE 12 AND T ADR BUS 12 -129b.13 KHK 121 . 08 B TIME STOR ADR REG 13 1296.03 AND CF STOR ADR REG 13 - 1296 .04 CF AND 16a 06 ADR LINE 13 ADR BUS 13 -129b .14 KHX STOR ADR REG 14 1296 .05 AND CF STOR ADR REG 14 129b .06 CF 16a 10 ADR LINE 14 **AND** ADR BUS 14 PCF. -129b 15 N KHA STOR ADR REG 15 129b 07 AND CF STOR ADR REG 15 1296 .08 CF AND 16a 14 ADR LINE 15 ADR BUS 15 -129b 16 STOR ADR REG 16 129b.09 **PCFJ** AND CF STOR ADR REG 16 1295 10 CF AND T 16a .18 ADR LINE 16 ADR REG 16 **PCFJ** -129b.17 支子 STOR ADR REG 17 129a.11 AND CF STOR ADR REG 17 1290.12 CF AND 16a.22 ADR LINE 17 ADR BUS 17 → 129b 18 ₹₩₩

Filed Dec. 26, 1957

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

3,036,773

Filed Dec. 26, 1957

244 Sheets-Sheet 225

FIG. 131a

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

3,036,773

Filed Dec. 26, 1957

244 Sheets-Sheet 226

FIG. 131b

Filed Dec. 26, 1957

244 Sheets-Sheet 227

FIG. 132a

Filed Dec. 26, 1957

DATA PROCESSING MACHINE

244 Sheets-Sheet 228

3,036,773

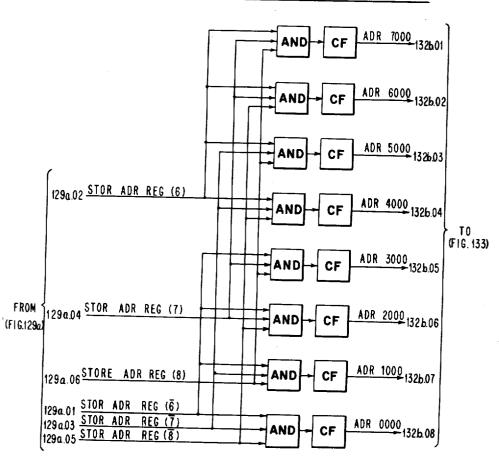

FIG. 132b

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

Filed Dec. 26, 1957

244 Sheets-Sheet 229

3,036,773

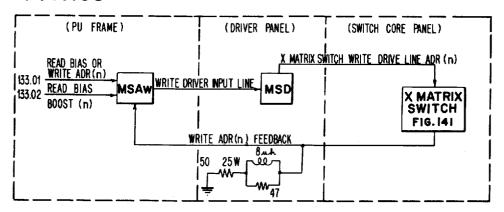

#### X MATRIX SWITCH WRITE DRIVER FIG.135

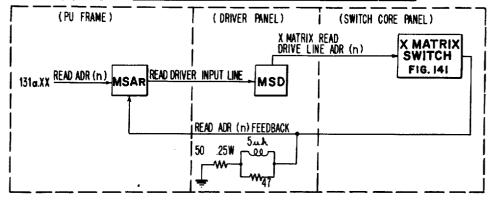

#### FIG. 136 X MATRIX SWITCH READ DRIVER

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

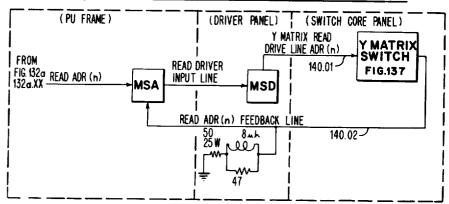

244 Sheets-Sheet 233

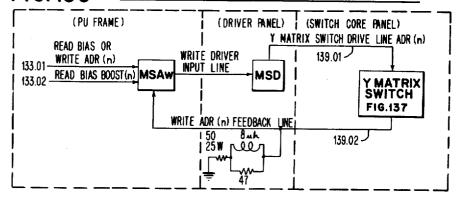

#### Y MATRIX SWITCH WRITE DRIVER FIG. 139

#### FIG.140 Y MATRIX SWITCH READ DRIVER

## FIG.143 DIGIT PLANE SELECT CIRCUITS

Filed Dec. 26, 1957

Filed Dec. 26, 1957

May 29, 1962

J. L. BROWN

INDIRECT ADDRESSING IN AN ELECTRONIC

DATA PROCESSING MACHINE

3,036,773

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

Filed Dec. 26, 1957

## United States Patent Office

1

3,036,773

INDIRECT ADDRESSING IN AN ELECTRONIC DATA PROCESSING MACHINE

Joseph L. Brown, Poughkeepsie, N.Y., assignor to International Business Machines Corporation, New York, N.Y., a corporation of New York

Filed Dec. 26, 1957, Ser. No. 705,445

9 Claims. (Cl. 235—157)

This invention relates to electronic data processing ma- 10 chines of the stored program type and more particularly ton an apparatus for modifying the address portion of an instruction word.

In electronic digital data processing machines, the instruction word includes a plurality of binary bits in which some of those bits are known as the operation part of the instruction and some others of these bits are known as the address part of the instruction. The operation part of the instruction word identifies some particular operation which the computer is to perform, and the address part of the instruction identifies the location in storage of the information upon which the specified operation is to be performed. In other instances, the address part of the instruction word identifies the address in storage of another instruction. It has been customary to store a plurality of instruction words in sequential addresses in storage and data words upon which operations are performed in other storage positions. The plurality of instruction words arranged in sequence is called a program and many of the programs are arranged to run in a loop fashion with some instructions being performed over and over in the same sequence with provision for variation being made when certain conditions occur which change the iterative process.

One way an instruction in a stored program may have its address modified by some predetermined amount is by indexing which is accomplished by a set of registers called Index registers. Each indexing instruction specifies an Indexing operation and a register in addition to an address and operation, and the number stored in the Index register is automatically added to the address of the instruction producing a sum which is the actual address used. To modify Instruction addresses, the instruction must specify the particular Index register which is to take part in the modifying operation and this is accomplished by an appropriate digit in the instruction word. The instruction is then executed as if its address field had contained the address minus the contents of the specified Index register. An instruction may refer to more than one Index register with the proper designation in the tag field and the use of a multiple tag results in the logical OR sum of the contents of the specified Index register being used to modify the address. In Direct addressing, an instruction word is decoded according to the operation portion and the address portion controls necessary apparatus to bring a word from Storage which is operated upon in a fashion as determined by the operation portion of the word. In Direct addressing with Indexing operations, the Operations part of the instruction is decoded and the address part of the instruction is delivered to a register where that address part of the instruction is modified by adding to or subtracting from it the contents of a specified one of several of the Index registers. The modified address now specifies the location in Storage 65 2

from which information is taken to be manipulated in accordance with the operation part of the instruction.

Just as Index registers are addressed with a tag, indirect addressing is specified by the presence of a code in the designated position of the instruction word. With such a predetermined code designation in the instruction an effective address may be computed in the usual way by subtracting the contents of an Index register if any are selected. The Calculator then examines the word whose location is specified by this effective address and senses the tags in the address part of this word to determine whether a second effective address is to be specified. If this last word is not indirectly addressed the instruction is then executed as if its address field had contained the second effective address.

Briefly stated, in accordance with the principles of this invention an indirected addressing instruction is brought from Storage and decoded and the address part of the instruction is delivered to a register where the address part may or may not be modified by adding to or subtracting from it the contents of predetermined ones of the Index Registers. The address (modified or not) now refers to a location in Storage from which the contents are extracted. These contents may be a data word or another indirectly addressed control word including an address which is entered into the register where it may be modified by indexing if desired. The result now specifies the location in Storage from which another word is taken for subsequent operations which may either be continued indirect addressing operations or data manipulations. The last word of the sequence of words is then operated upon according to the operation part of the initial indirect addressing word.

Indirect addressing is a flexible address modification means. For example, if ten instructions have addresses referring directly to the same data location, it is usually necessary to change the address portion of all ten instructions when the data location is changed. However, if the ten instructions had indirect addresses all referring to a single effective address (which specifices the data location), it would be necessary to change only the one effective address. Indirect addressing may be used in conjunction with standard indexing techniques. Indirect addressing may also be used as a relatively inexpensive substitute for standard indexing techniques by utilizing instructions which increment, or decrement, indirectly addressed effective addresses.

An object of the present invention is to provide an improved Address modification system for digital data 50 processing machines.

It is another object of this invention to provide an improved address modification apparatus wherein the contents of a location in storage are not treated as data but the address of the contents of the location in storage specifies the location from which data or another address may be had for subsequent operations.

Another object is to provide apparatus having an object as described above including means for modifying each of the instruction words by the contents of a selected one of a group of Index registers.

Another object of this invention is to provide apparatus having an object as described above including means for selectively modifying each of the instruction words by the contents of at least two Index registers.

Another object of this invention is to provide improved

address modification apparatus wherein an instruction word is taken from storage at a location specified by an initial instruction word which may have its address portion modified a predetermined amount by an Index register, the latter referring to another instruction word which may have its address portion modified by the same or another Index register as determined by the instruction

It is another object of this invention to provide apparatus for performing N order indirect addressing opera- 10 tions and (N+1) order indexing operations selectively at

the option of the programmer.

It is a still further object of this invention to provide apparatus for executing an indirect addressing instruction having instruction, address, and tag parts including a 15 logical block form. storage device and a computer for decoding operations and performing arithmetic operations including circuits responsive to the tag for delaying the decoding of the operation and for reading out the contents of the location in storage specified by the address as selectively modified by arithmetic operations.

Other objects of the invention will be pointed out in the following description and claims and illustrated in the accompanying drawings, which disclose, by way of example, the principle of the invention and the best mode, which has been contemplated of applying that principle.

In the drawings:

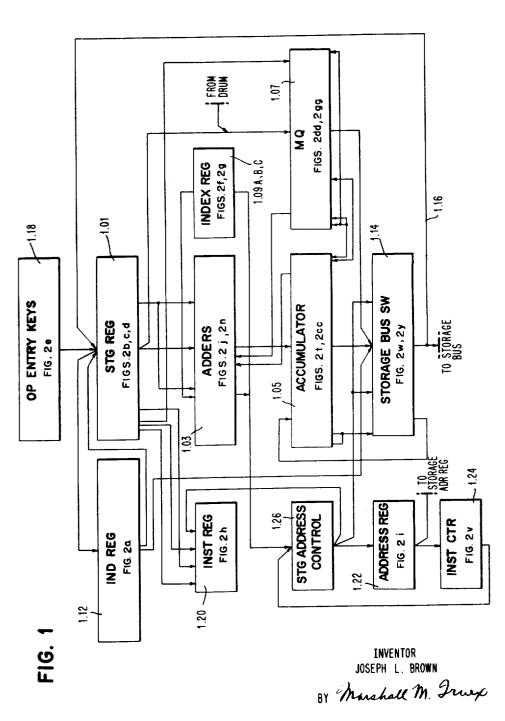

FIGURE 1 is an overall block diagram illustrating the general arrangement of interconnections of the major components comprising the Central Processing Unit.

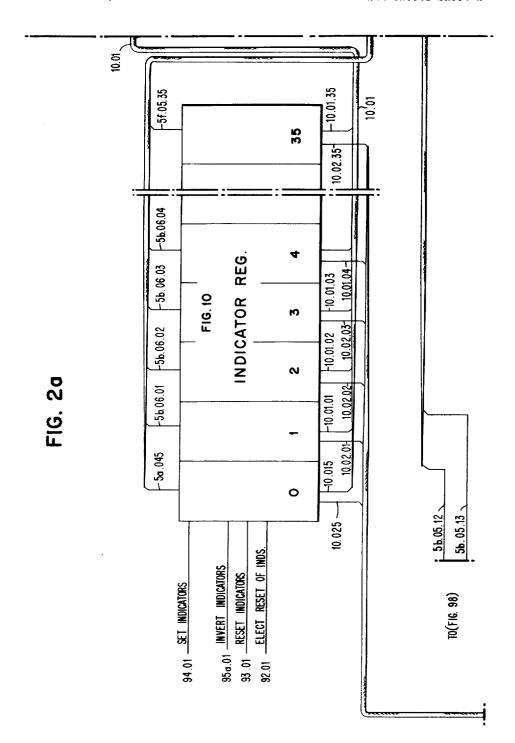

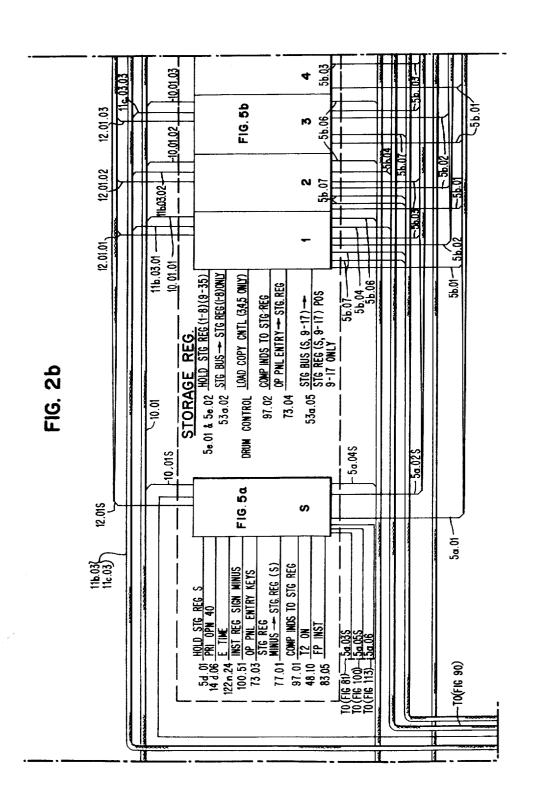

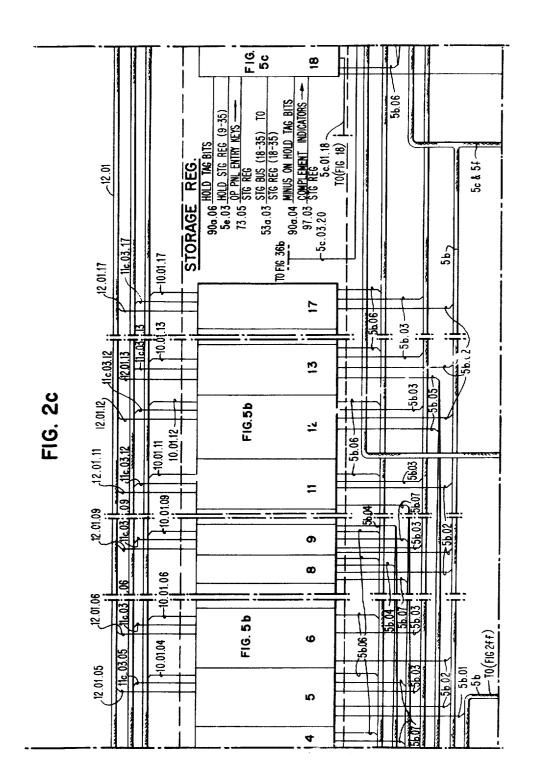

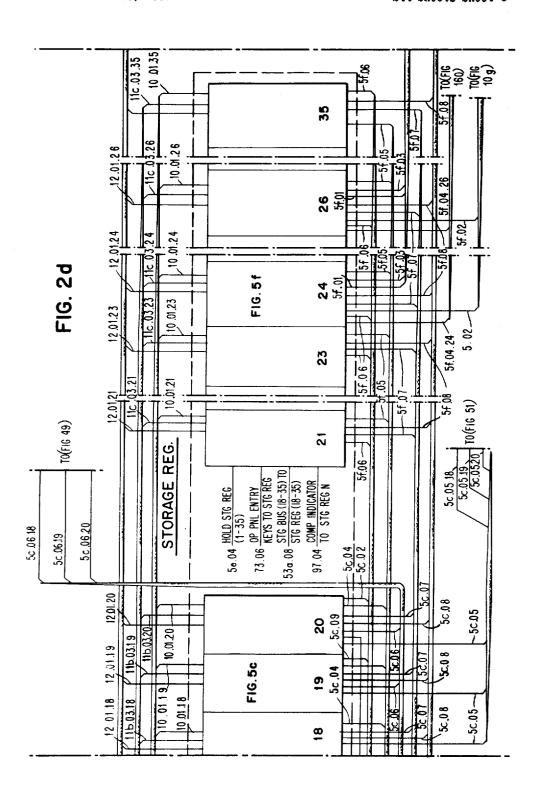

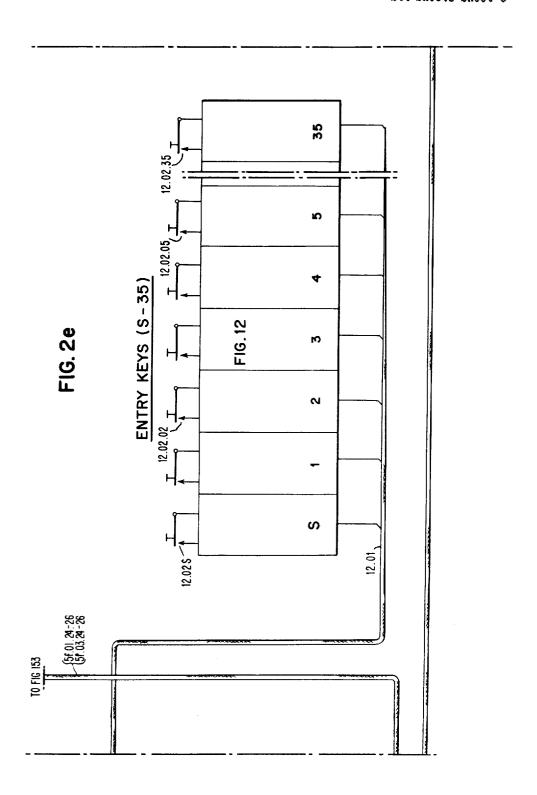

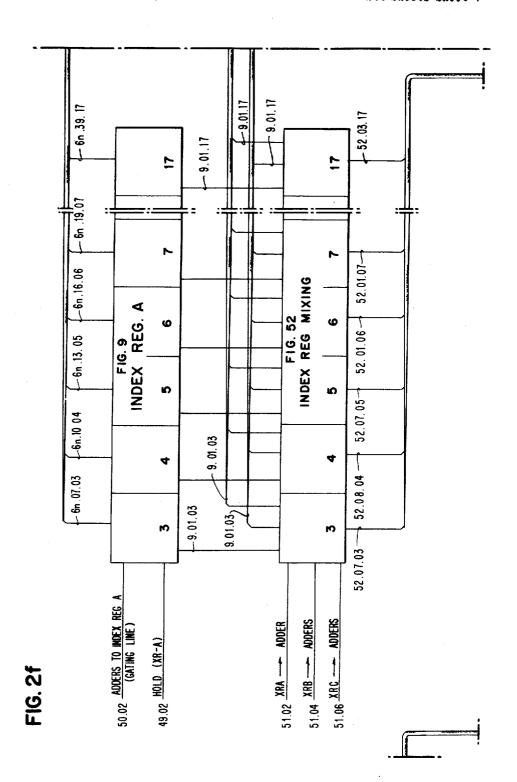

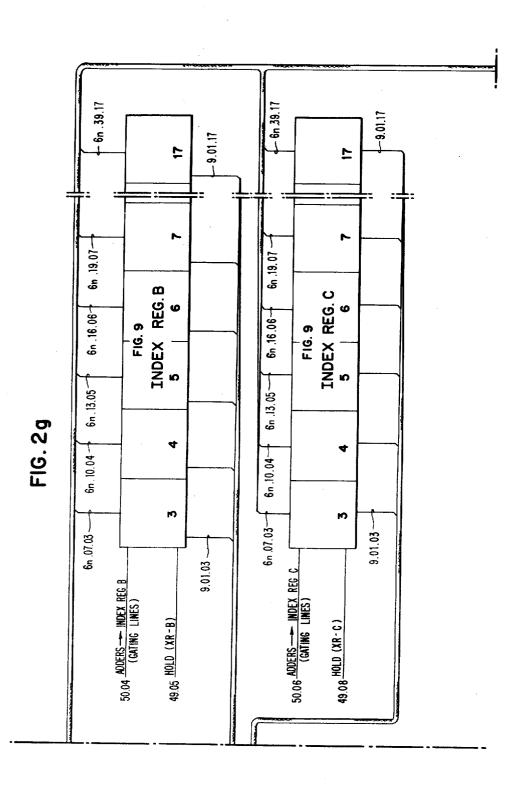

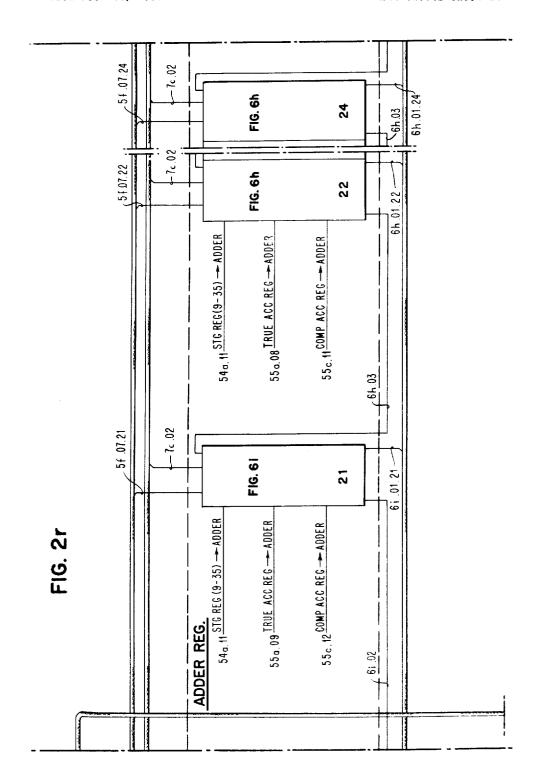

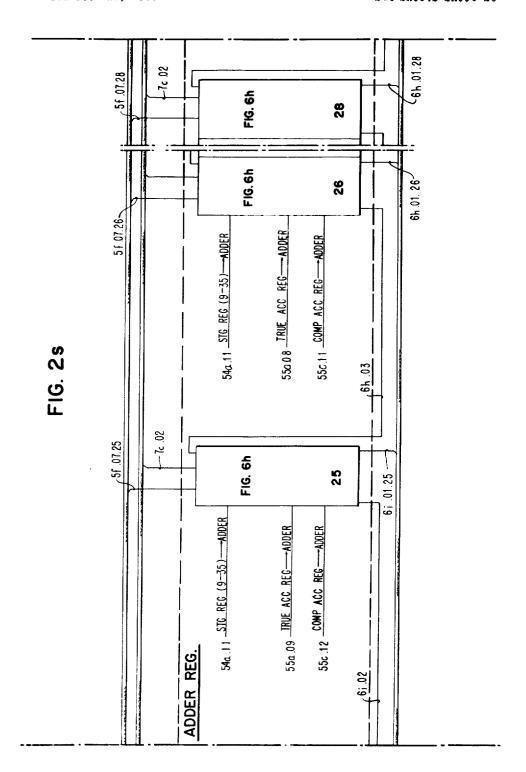

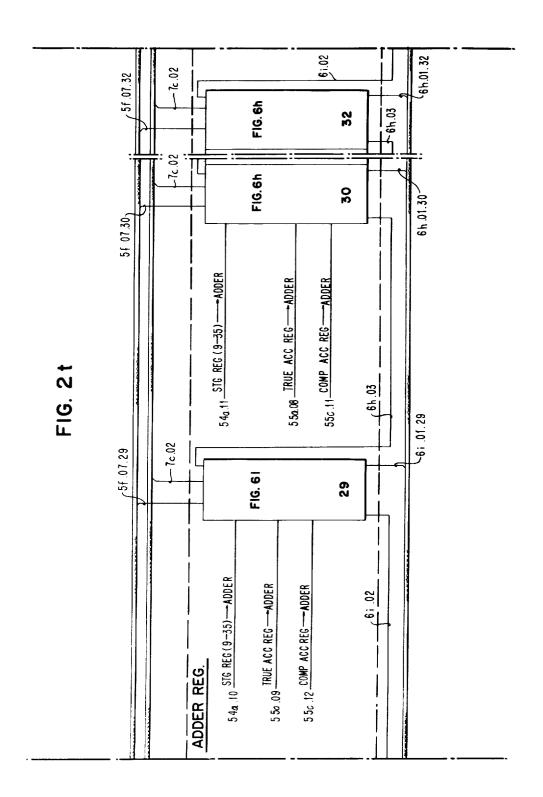

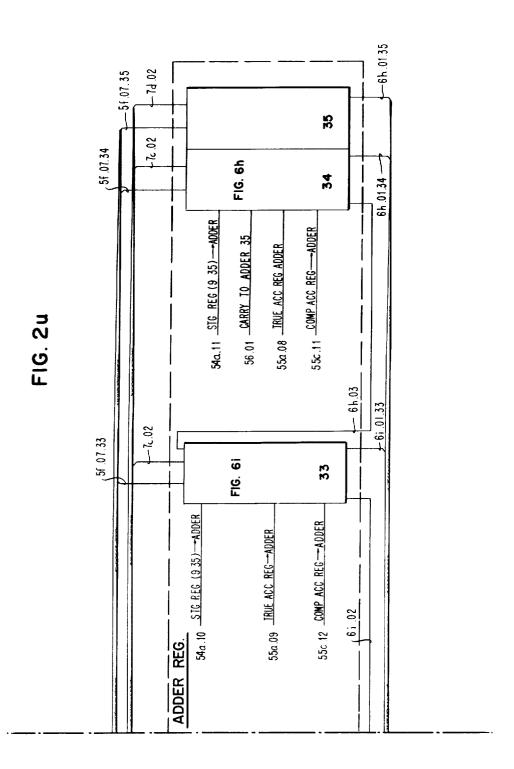

FIGURES 2a through 2ll form the logical block diagram for the principal data portions of the Central Processing Unit and Magnetic Core Storage.

FIGURE 2mm illustrates how FIGURES 2a through 211, inclusive, may be placed to form a composite block diagram of the major data portions of the Central Processing System.

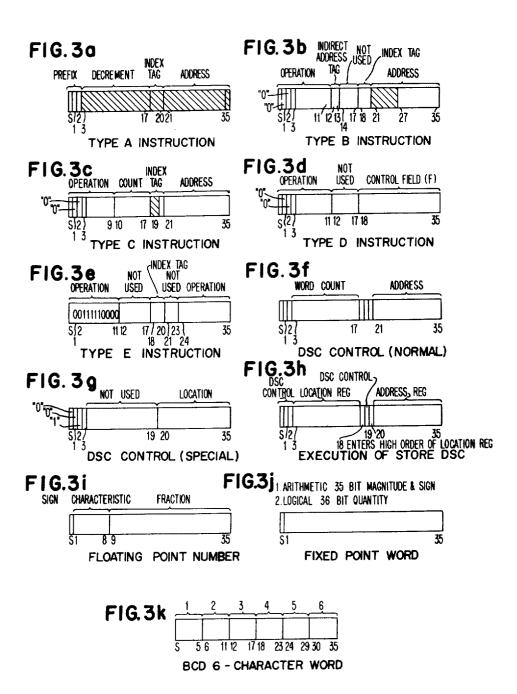

FIGURES 3a through 3k illustrate the Word Formats used in the Data Processing System.

FIGURE 4 is a Timing Chart of a Clear and Add 40 Instruction with Indirect Addressing.

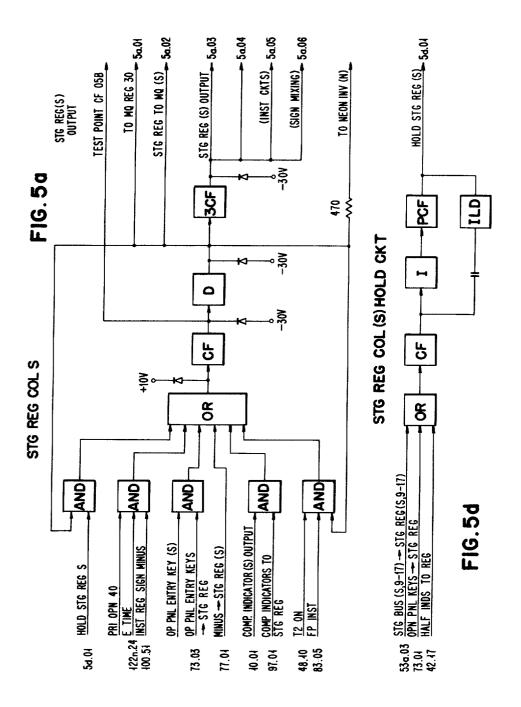

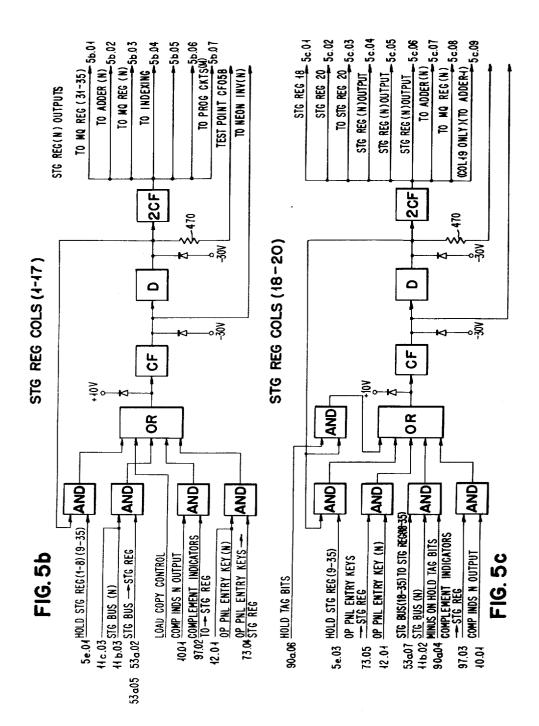

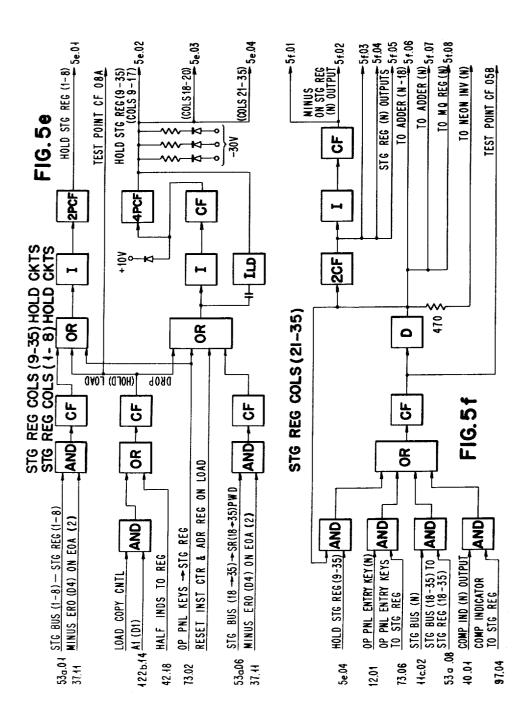

FIGURES 5a through 5f illustrate positions of the Storage Register and Storage Register Hold Circuits in logical block form.

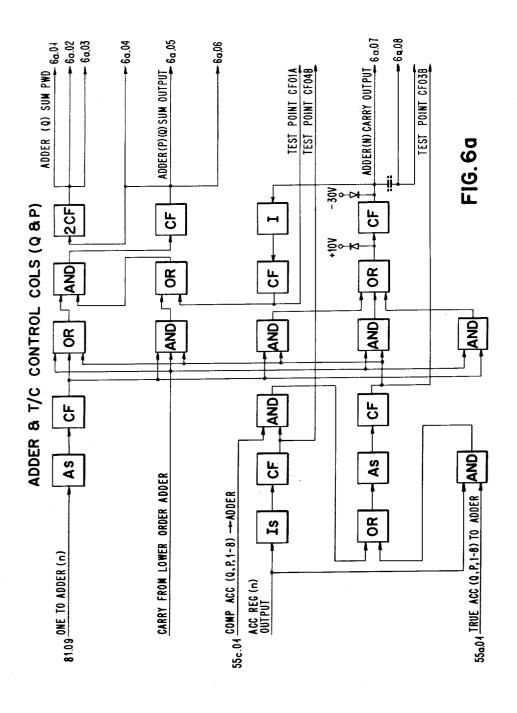

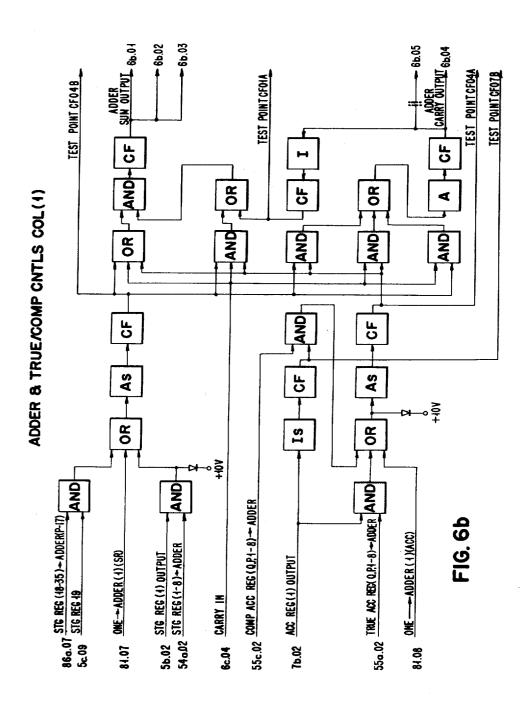

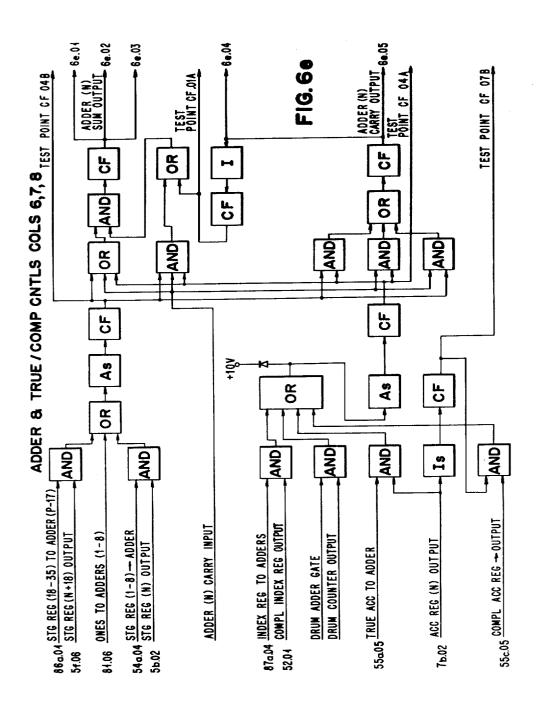

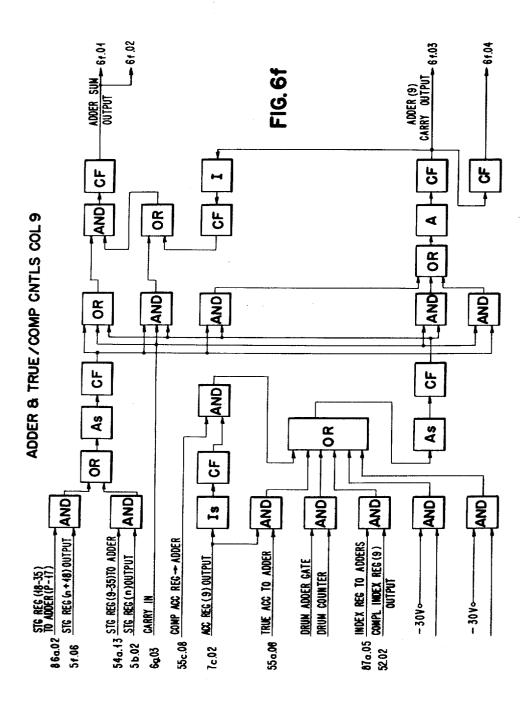

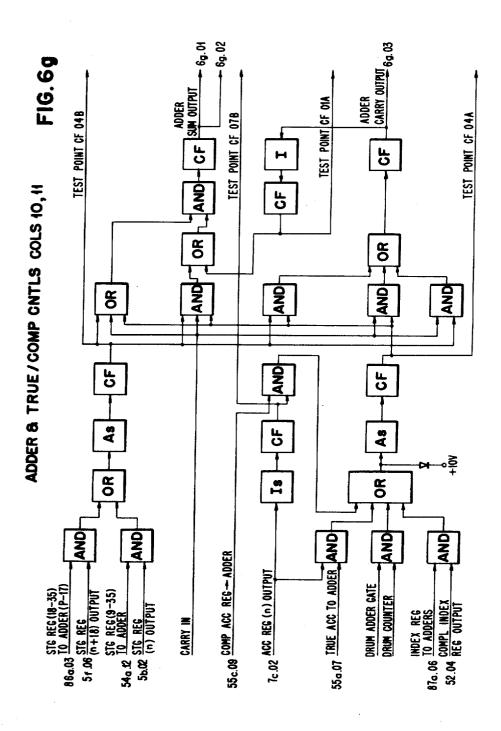

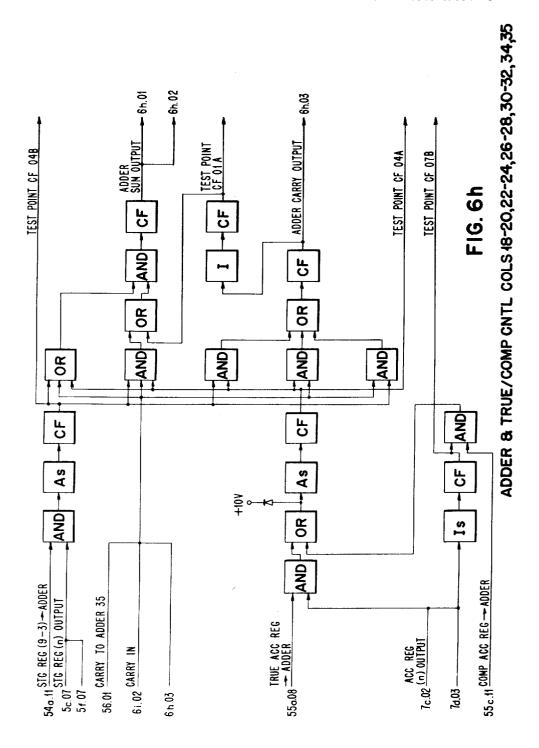

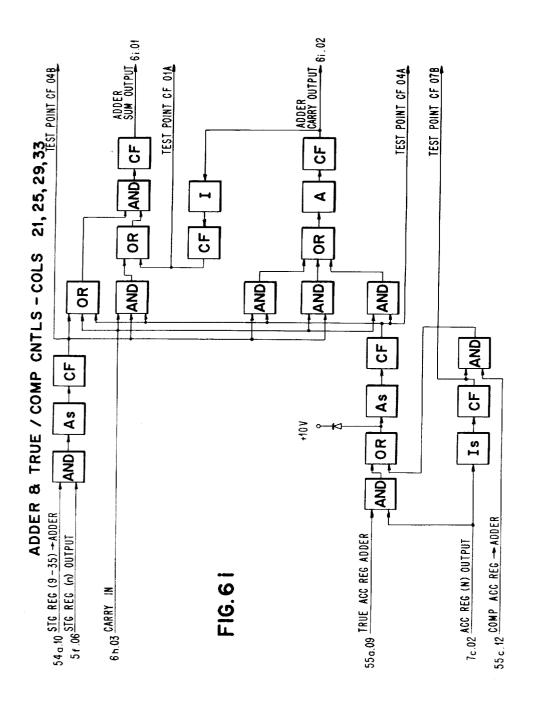

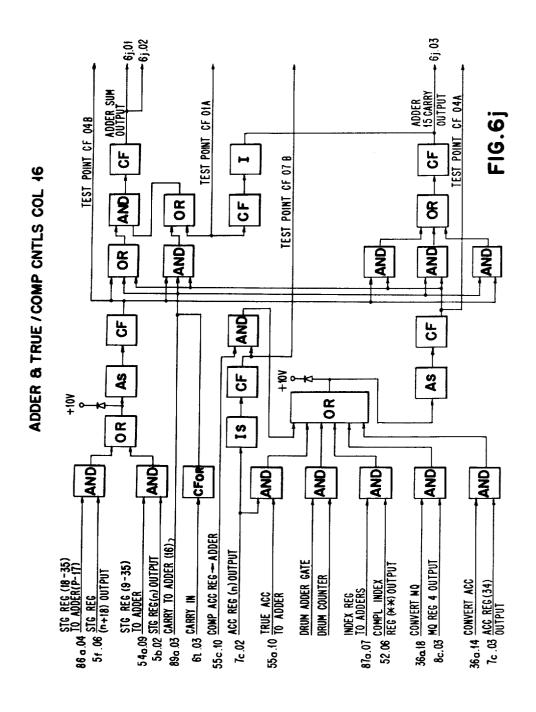

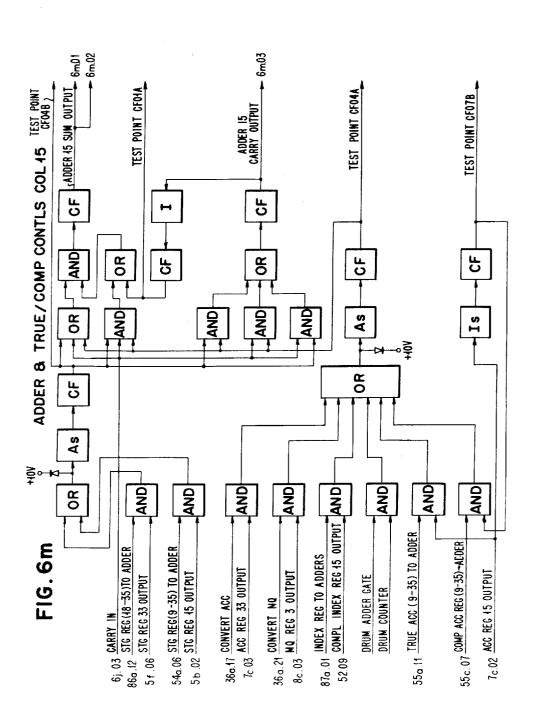

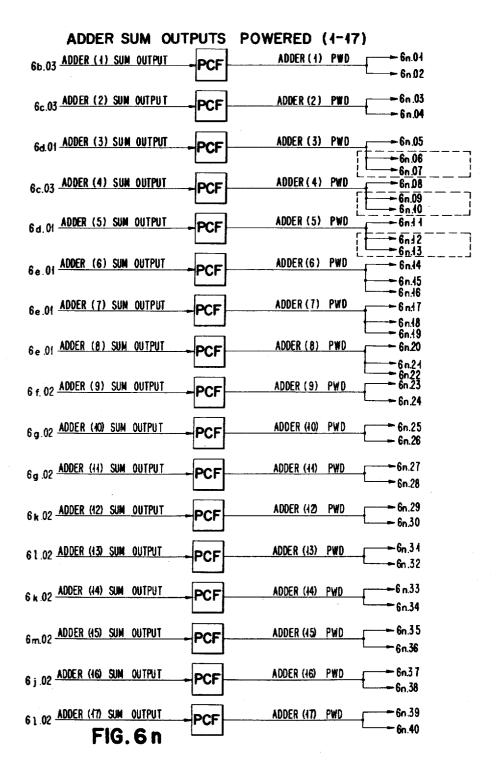

Complement Controls in logical block form.

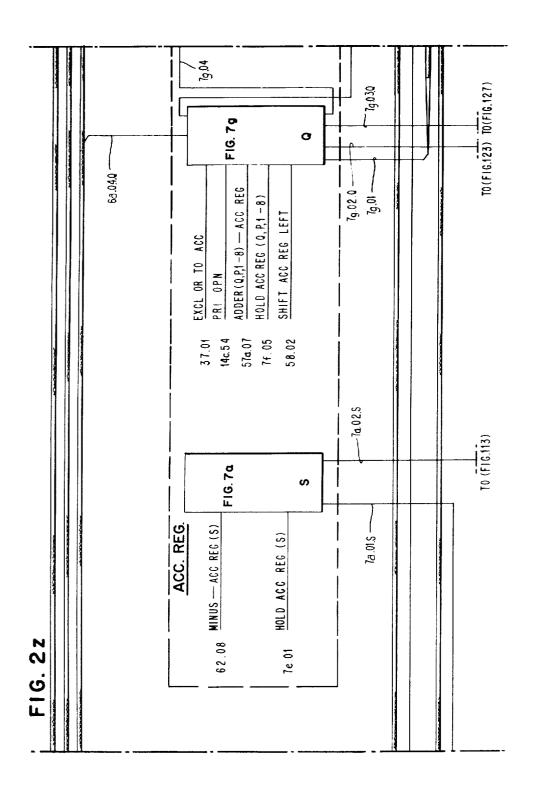

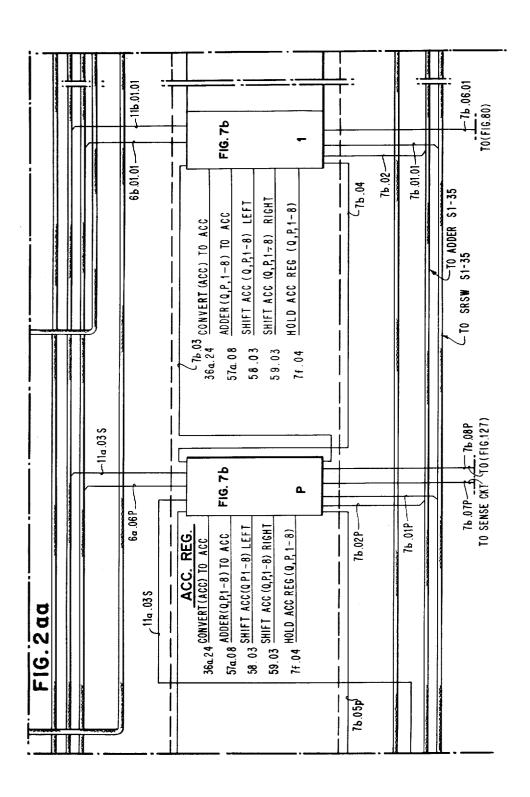

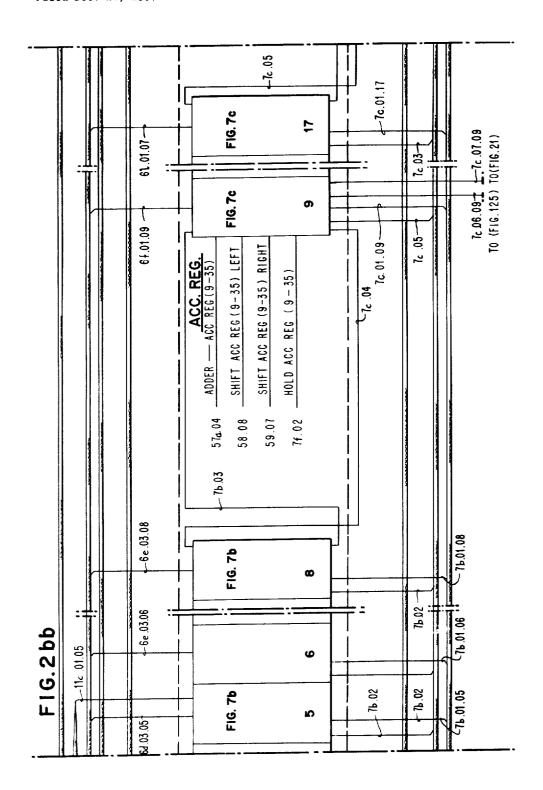

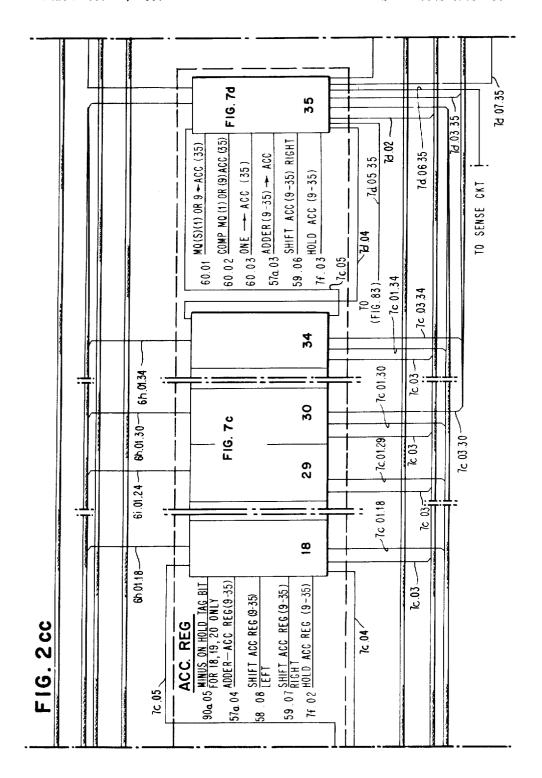

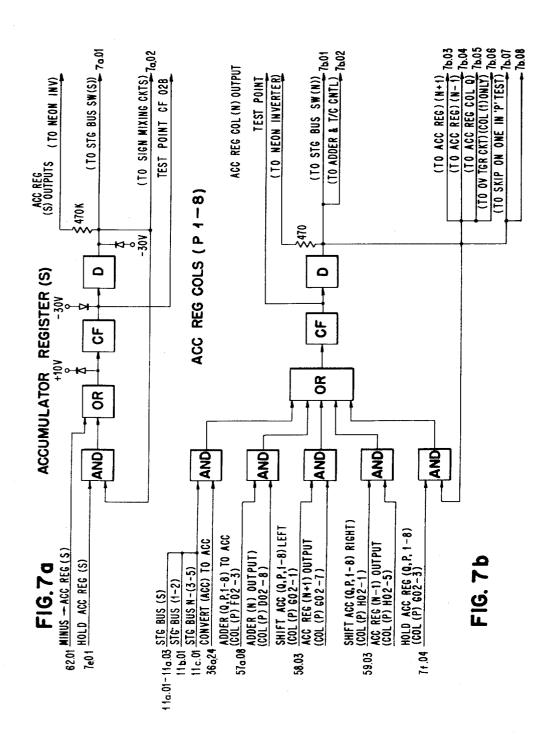

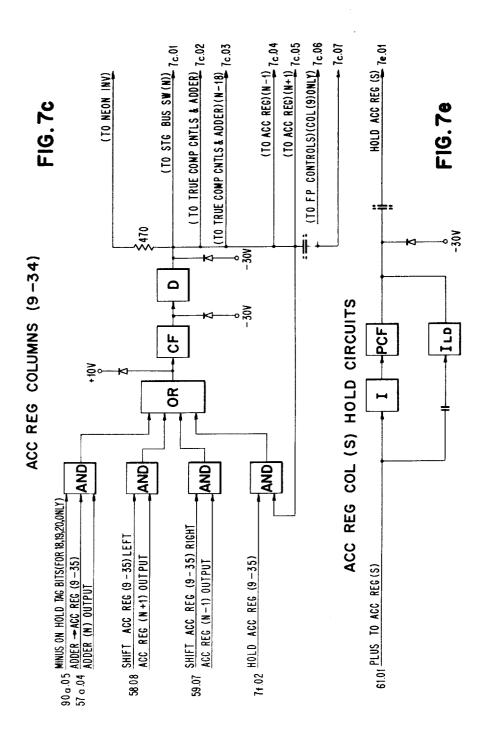

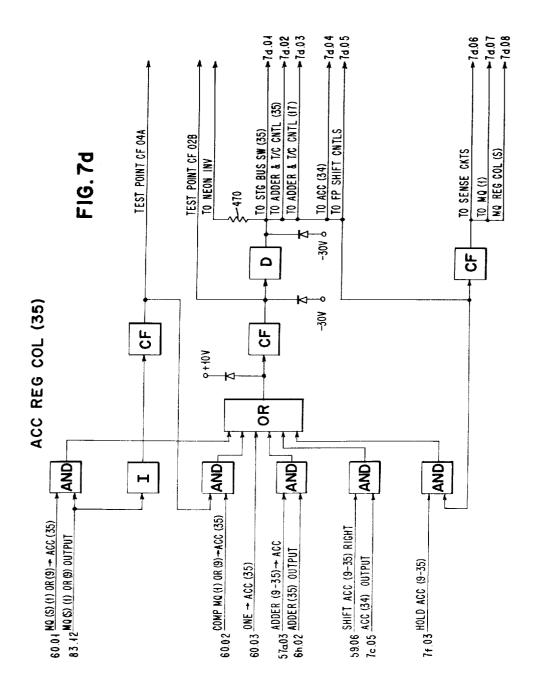

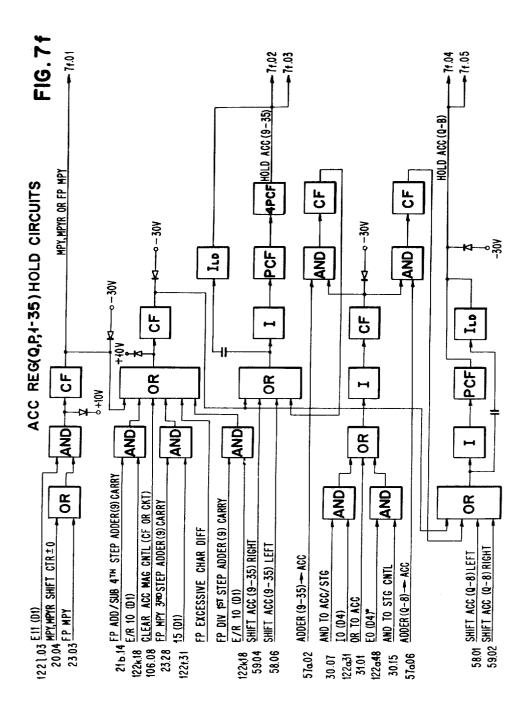

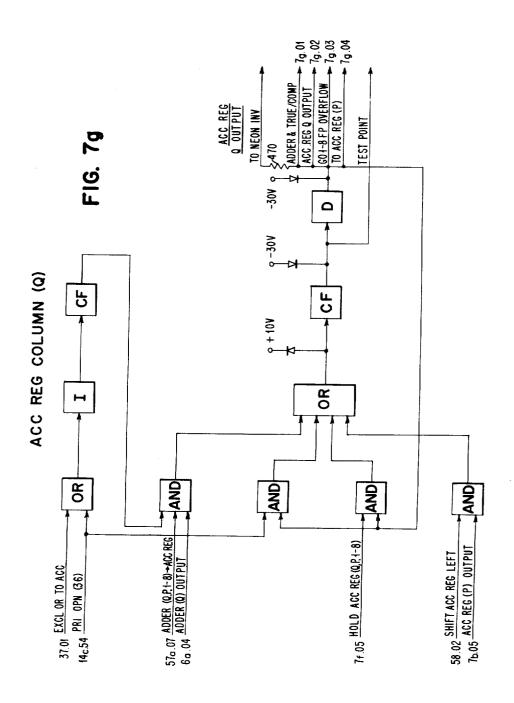

FIGURES 7a through 7g illustrate the Accumulator Registers in logical block form.

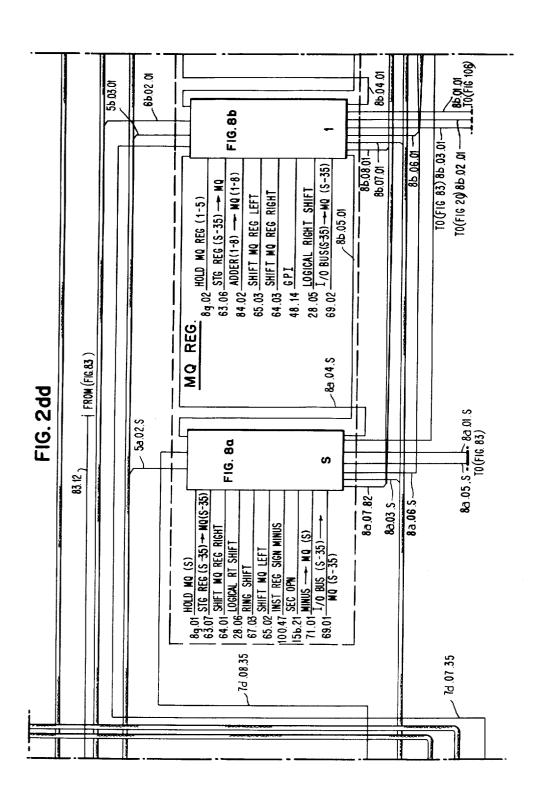

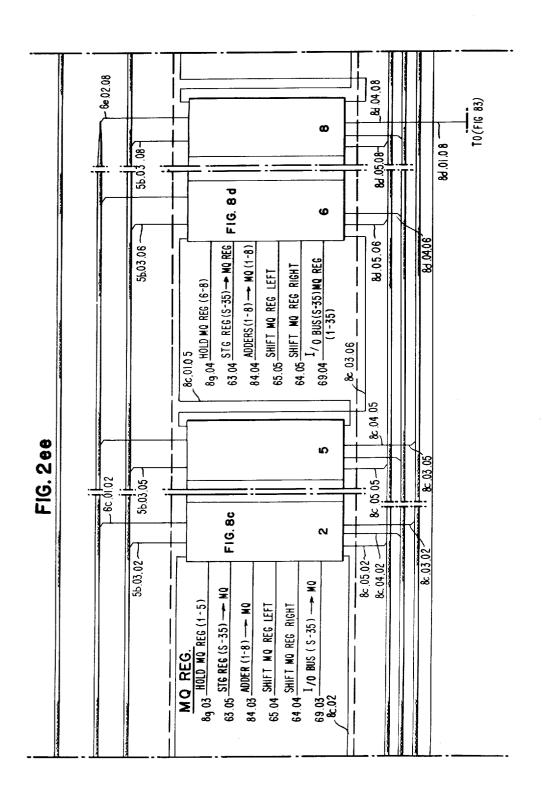

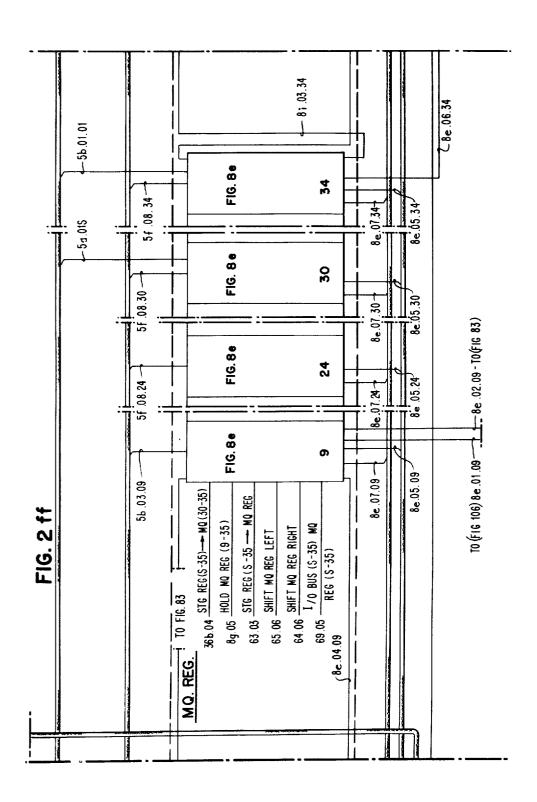

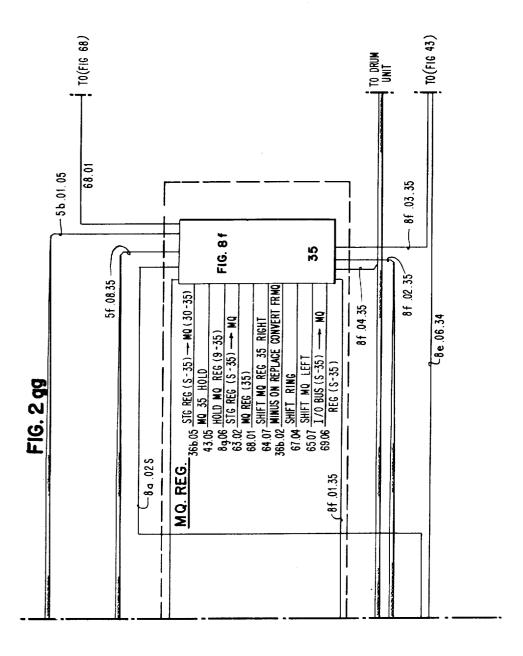

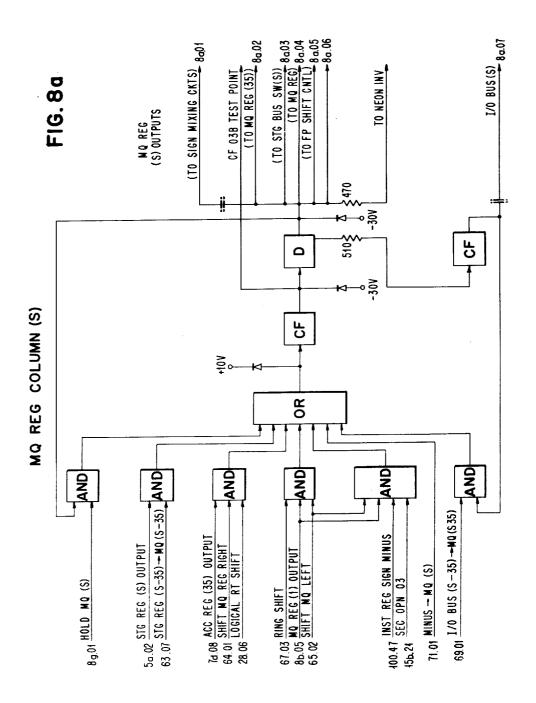

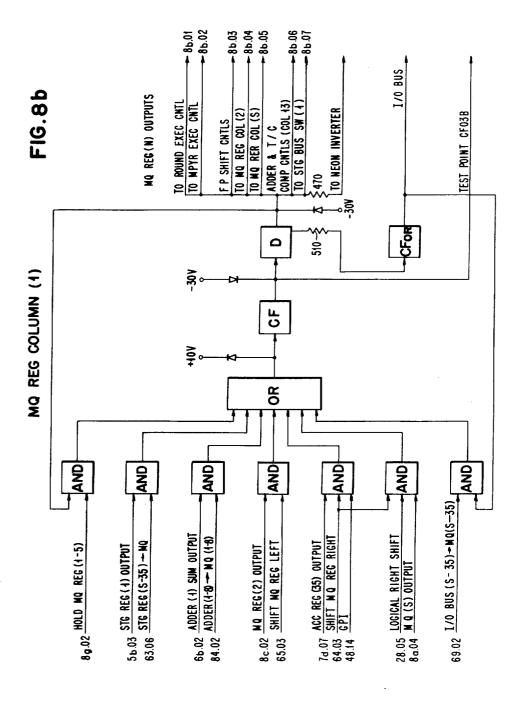

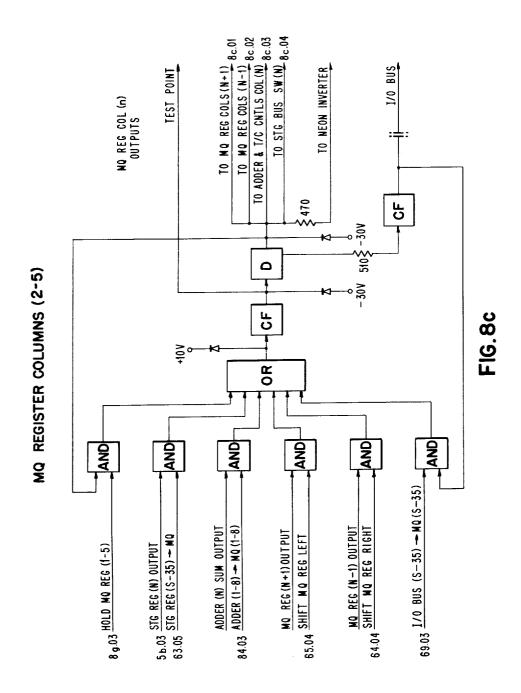

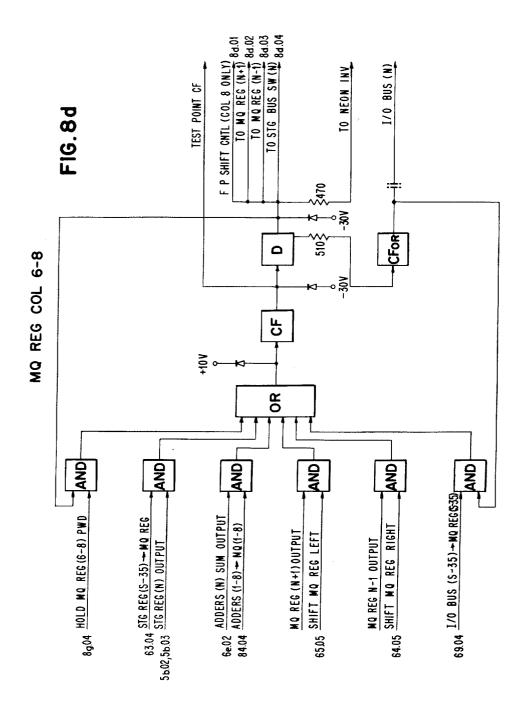

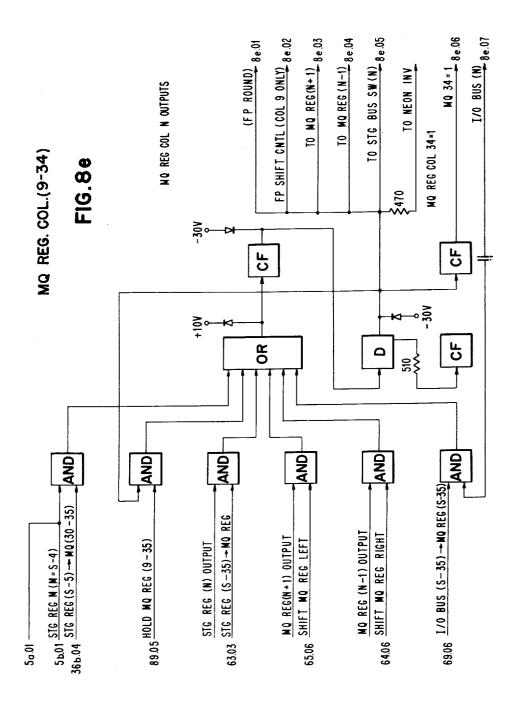

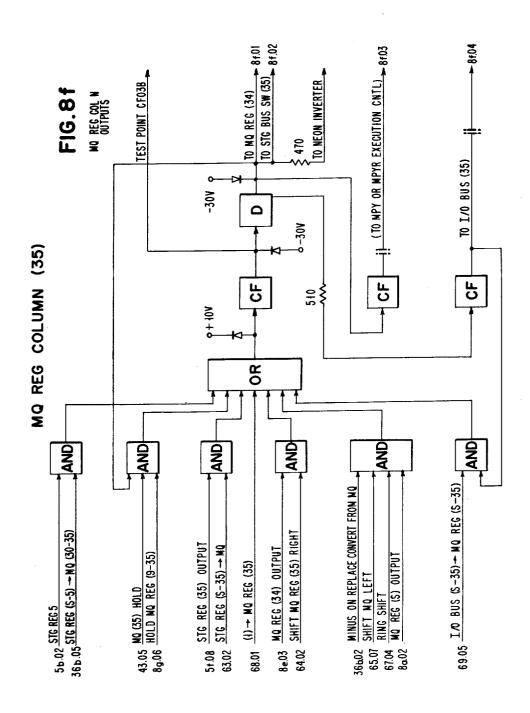

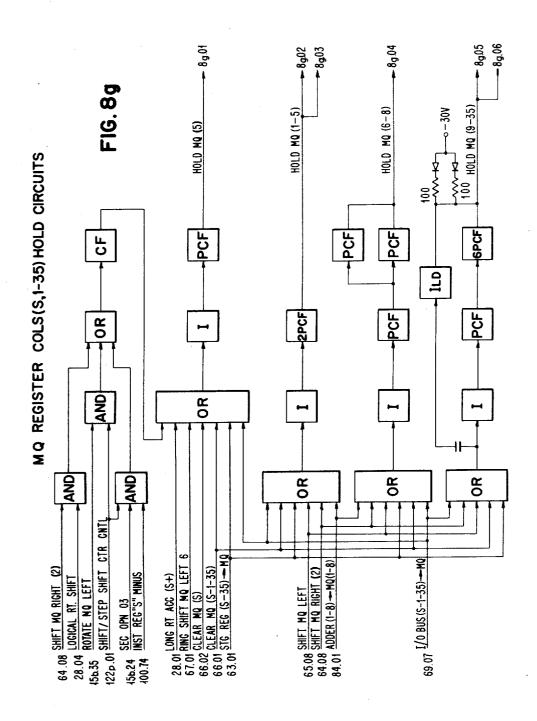

FIGURES 8a through 8g illustrate the Multiplier logical block form.

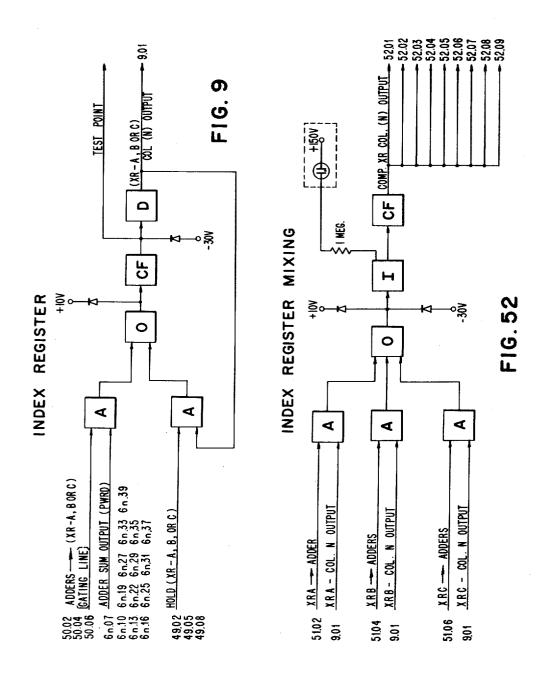

FIGURE 9 illustrates the Index Register in logical block form.

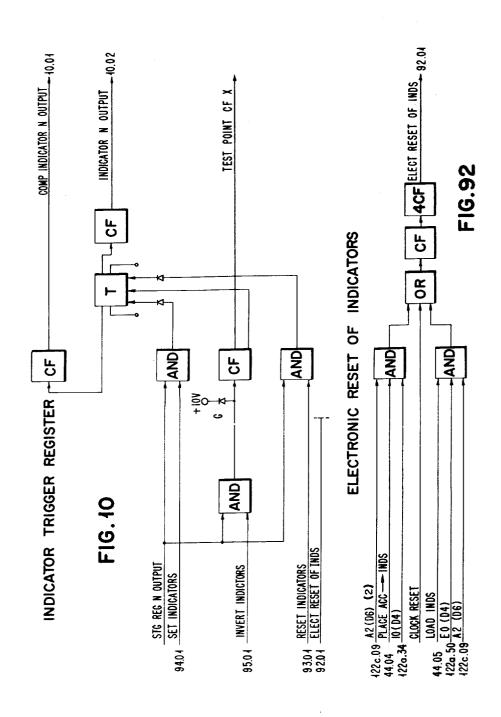

FIGURE 10 illustrates the Indicator Trigger Register in logical block form.

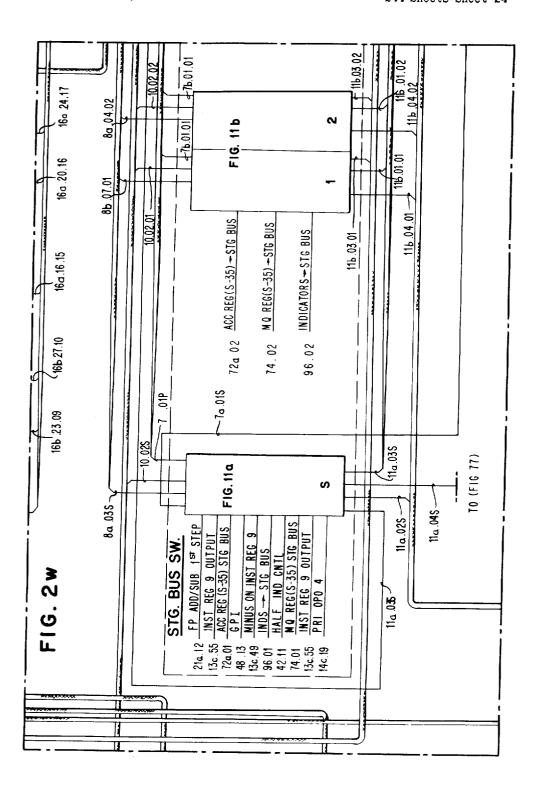

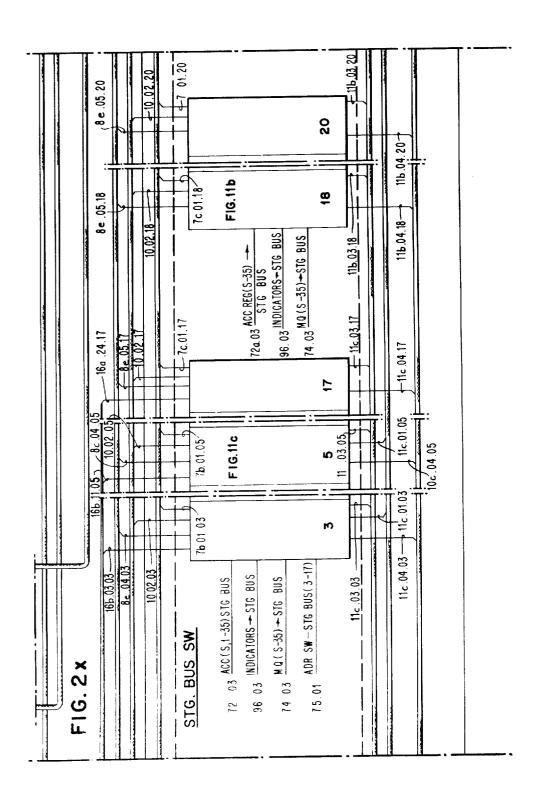

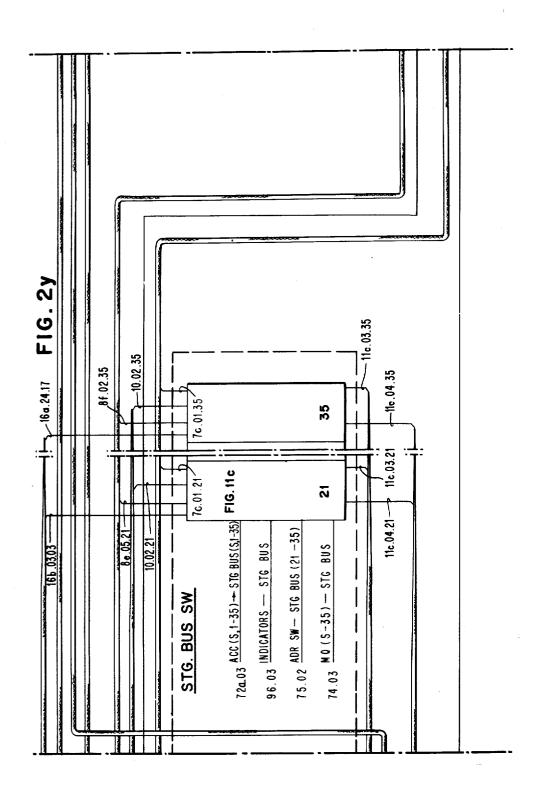

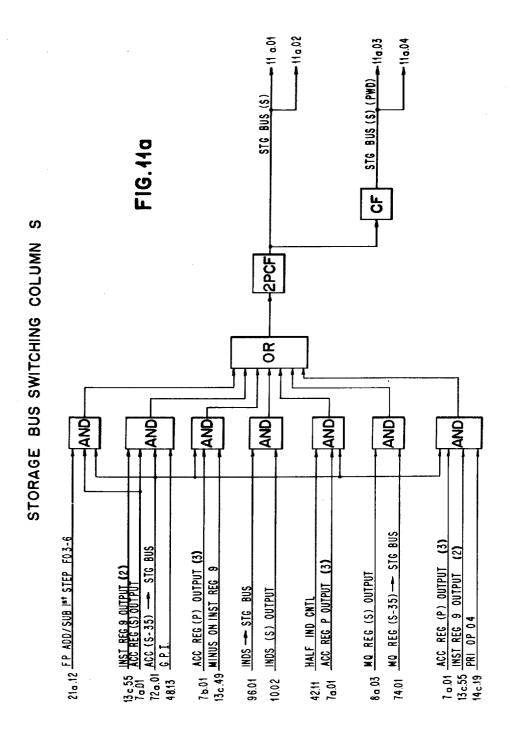

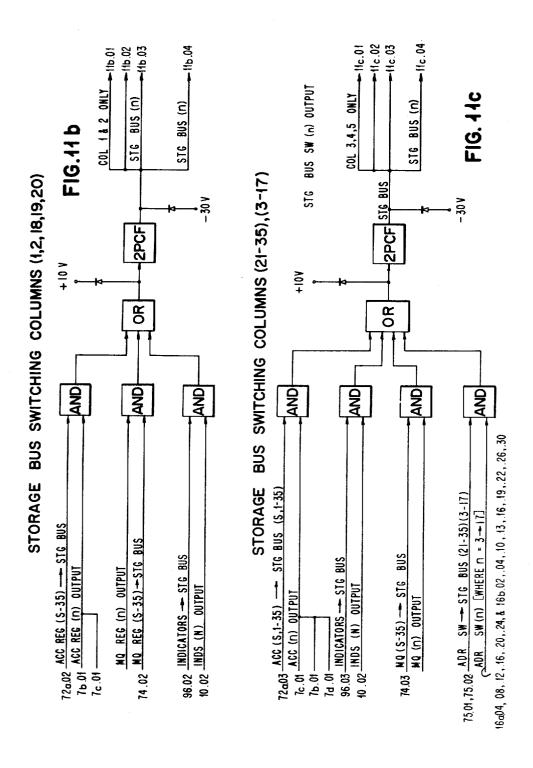

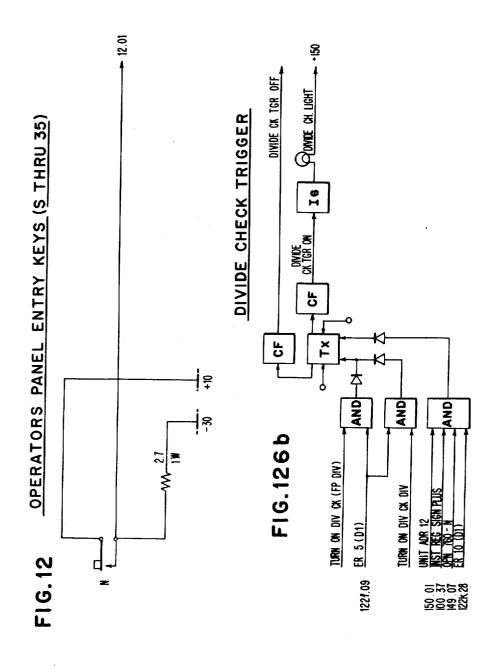

FIGURES 11a, 11b and 11c illustrate the Storage Bus Switching, columns S through 35, in logical block form. FIGURE 12 illustrates the Operator's Panel Entry Keys (S through 35).

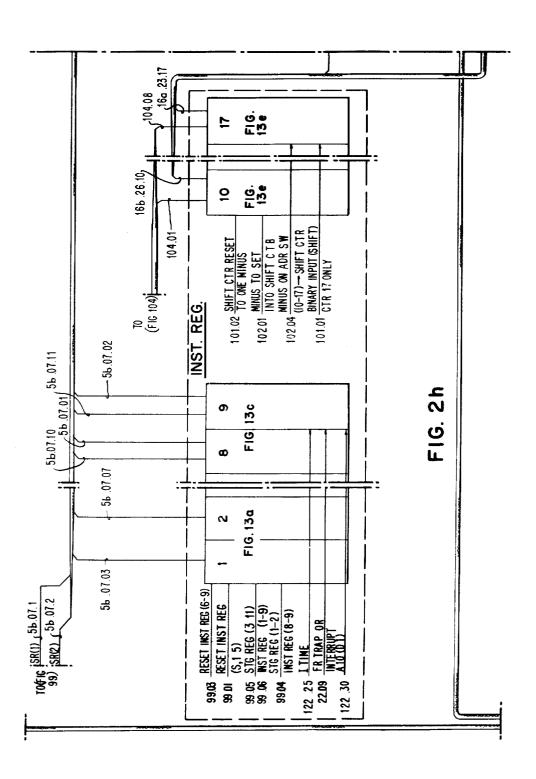

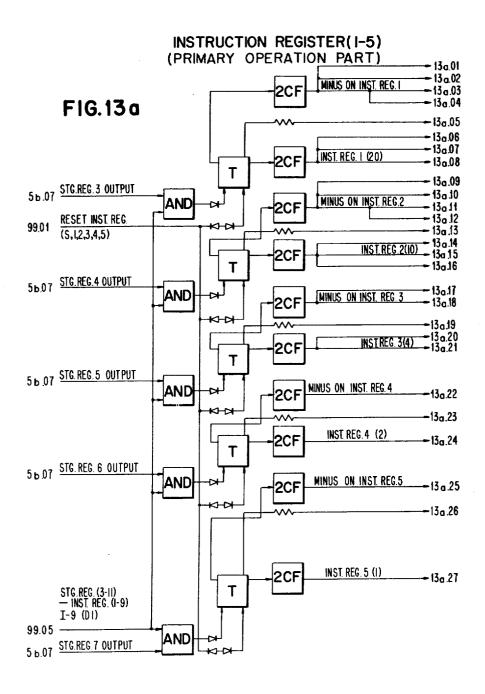

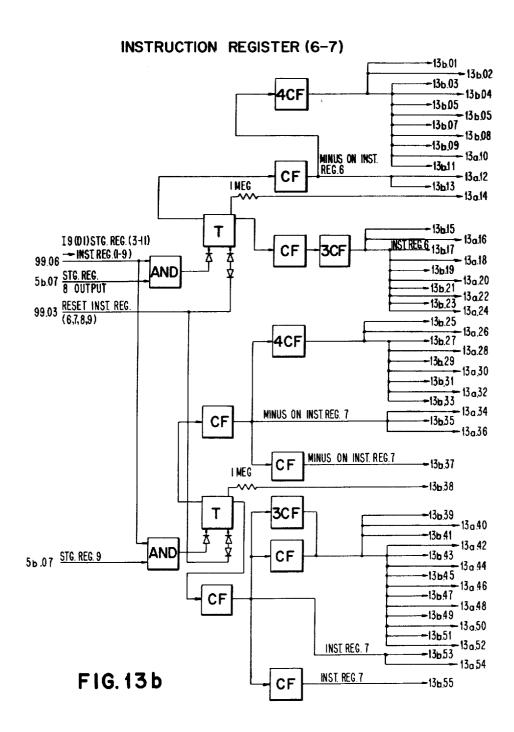

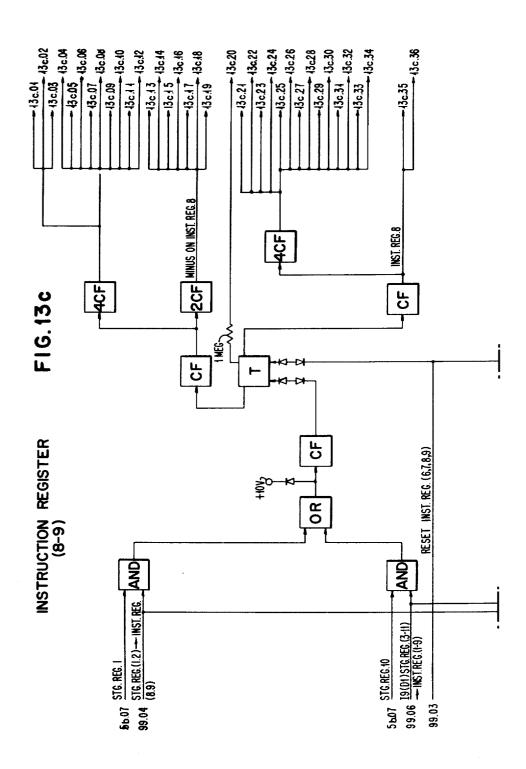

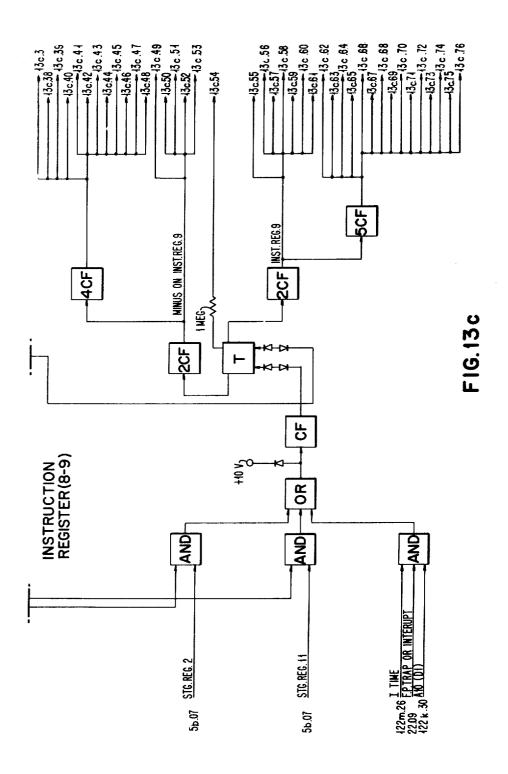

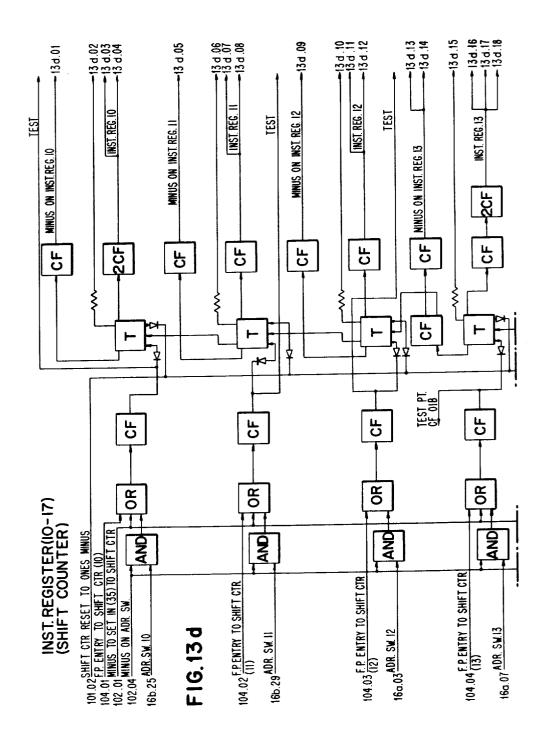

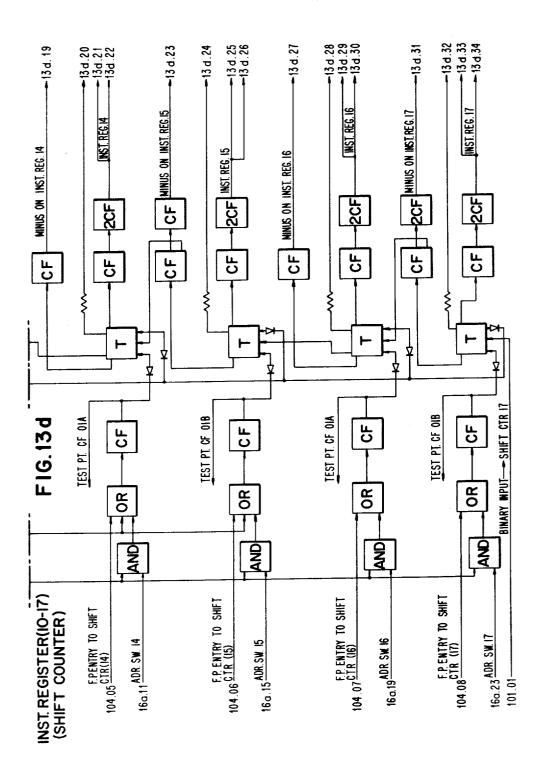

FIGURES 13a, 13b, 13c (2 sheets) and 13d (3 sheets) illustrate positions 1 through 17 of the Instruction Register (Primary Operation Part) in logical block form.

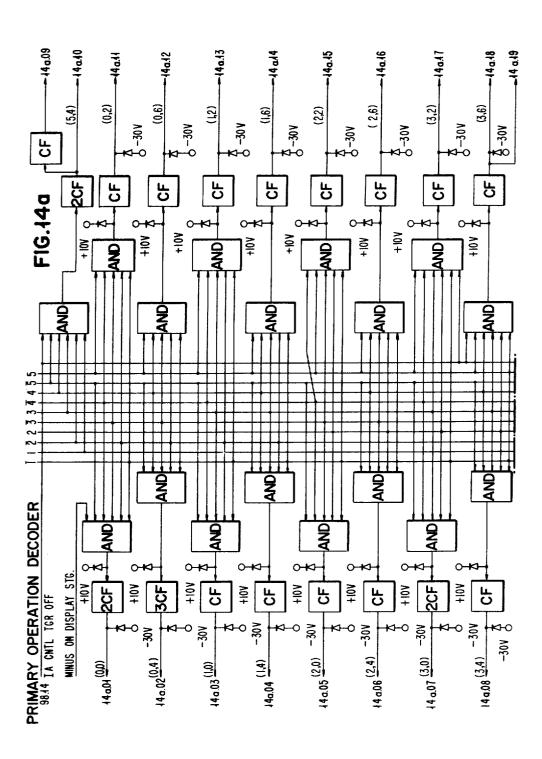

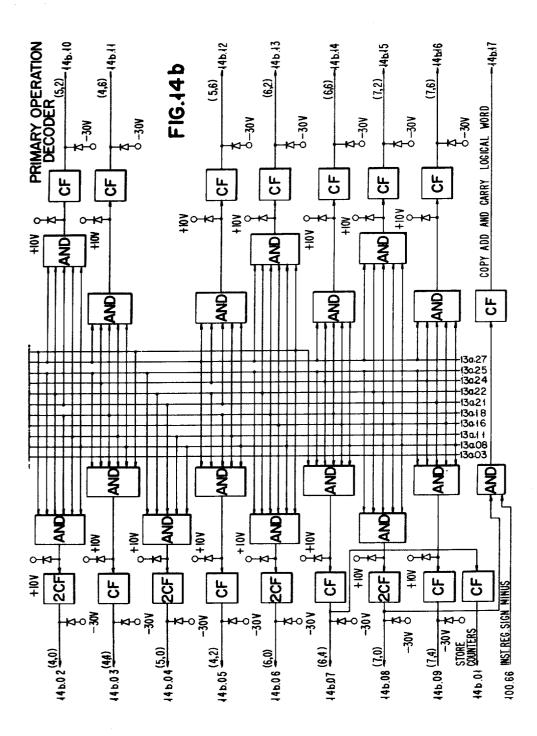

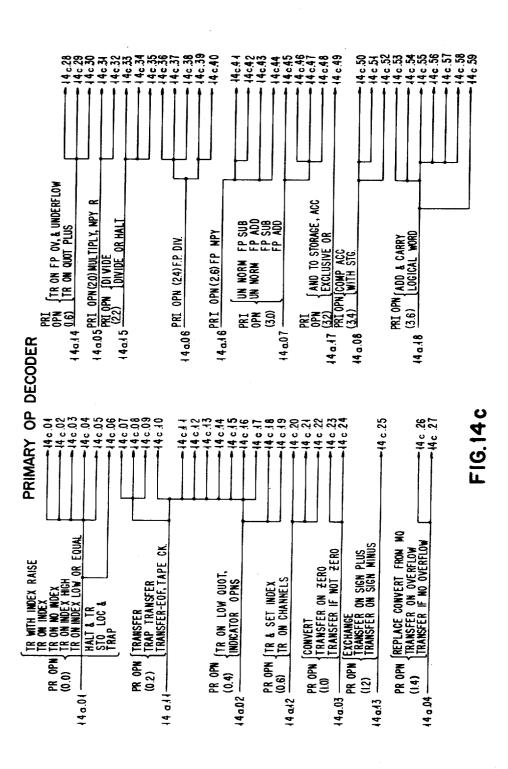

FIGURES 14a through 14d illustrate the Primary Operation Decoder in logical block form.

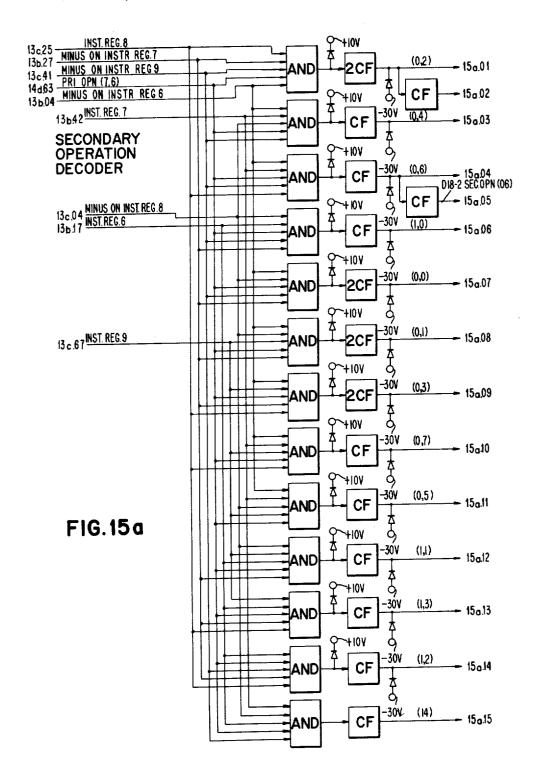

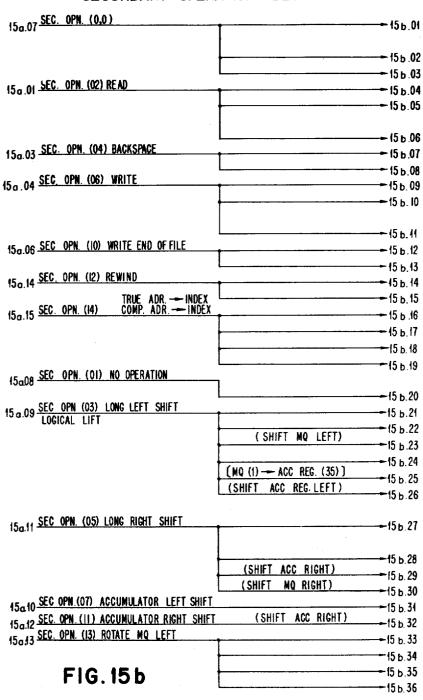

FIGURES 15a and 15b illustrate the Secondary Operation Decoder in logical block form.

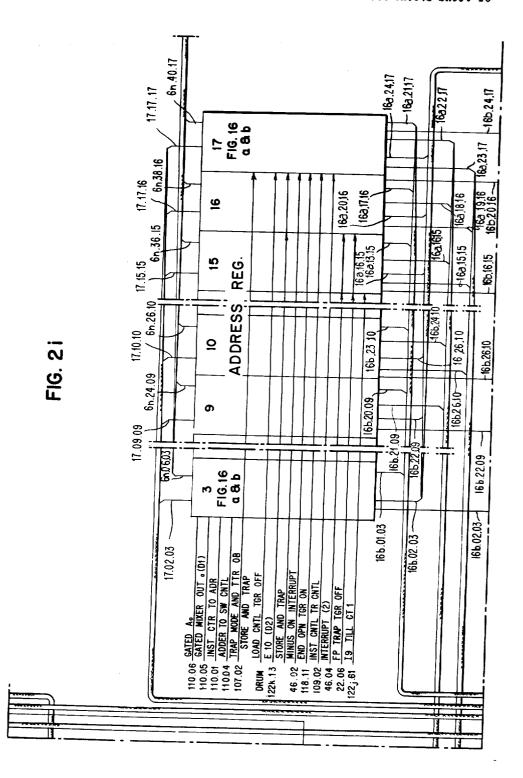

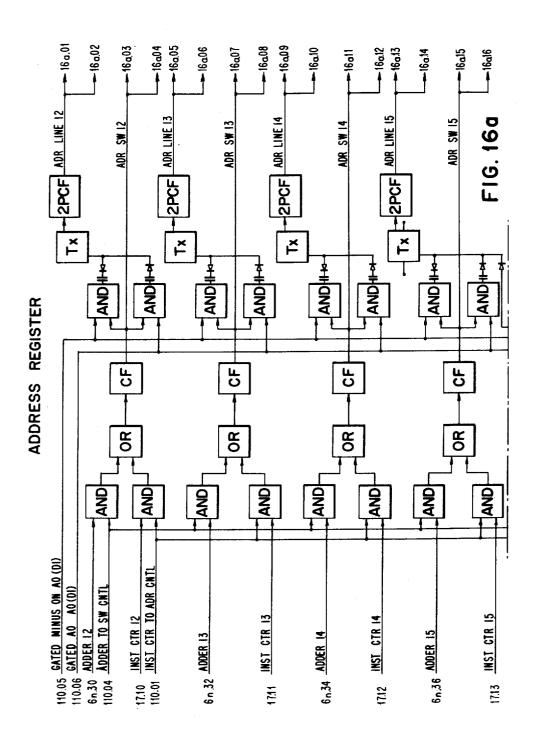

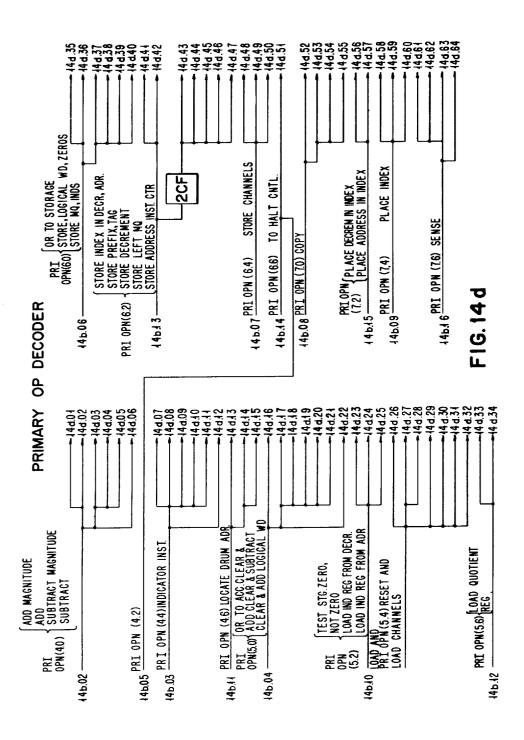

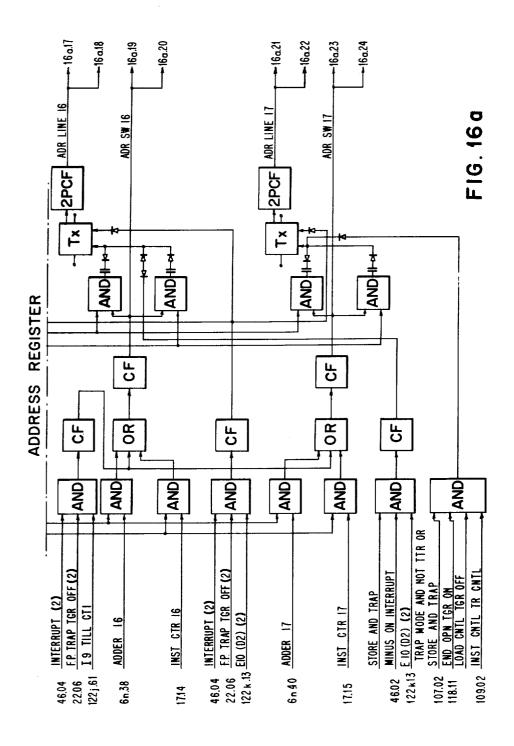

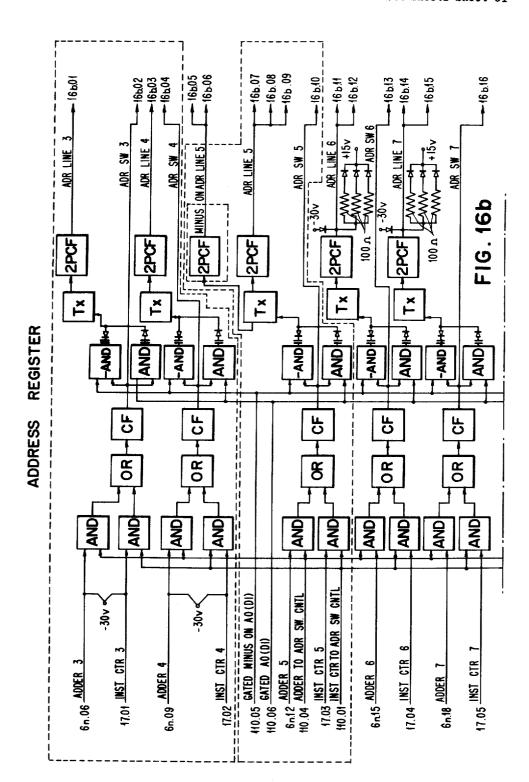

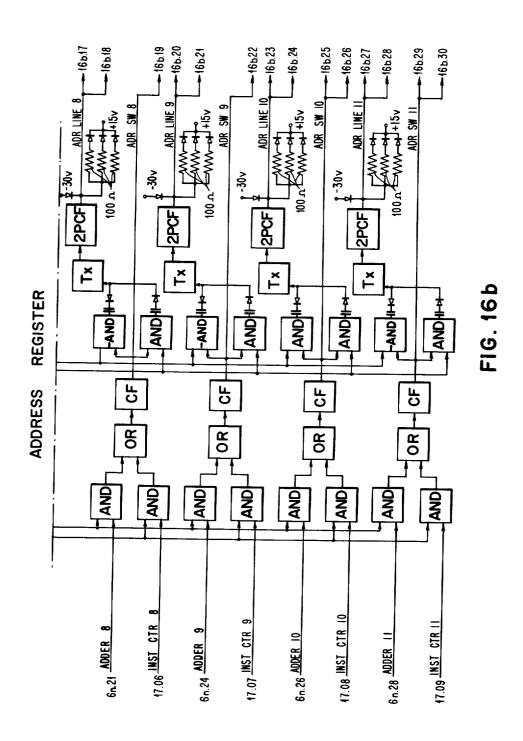

FIGURES 16a (2 sheets) and 16b (2 sheets) illustrate the Address Register in logical block form.

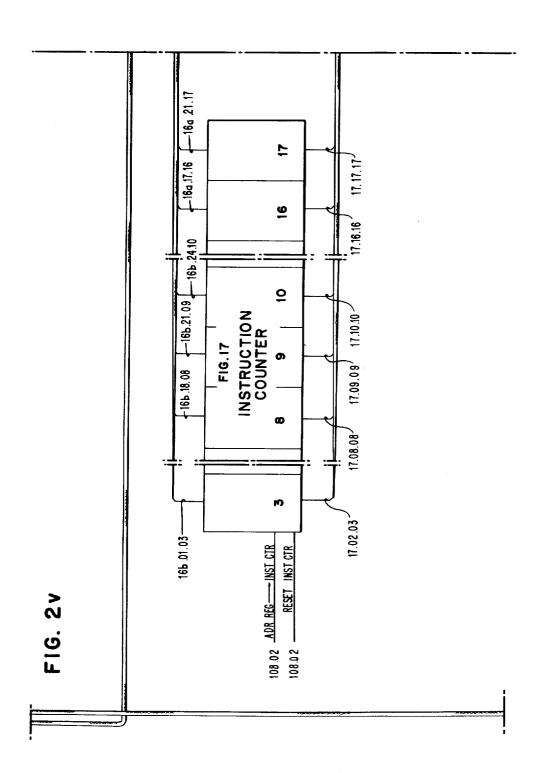

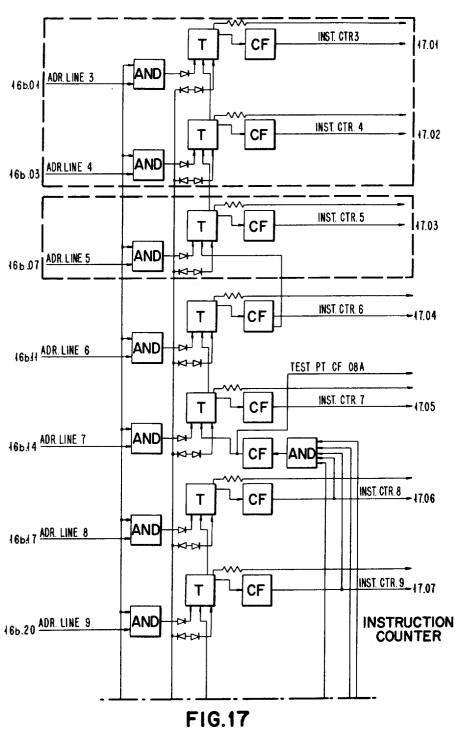

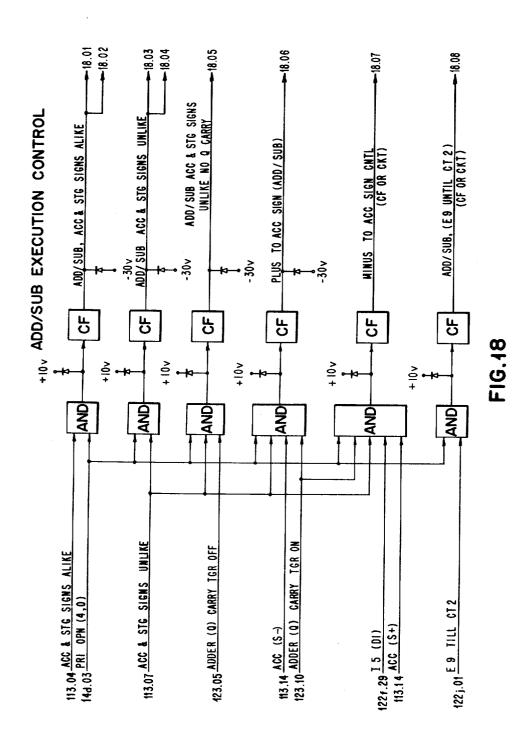

FIGURE 17 (2 sheets) illustrates the Instruction Counter in logical block form.

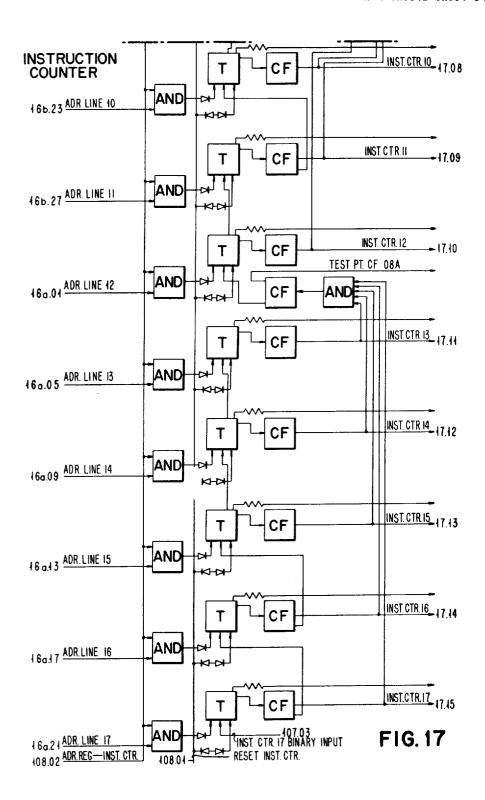

FIGURE 18 illustrates the Add and Subtract Execution Control in logical block form.

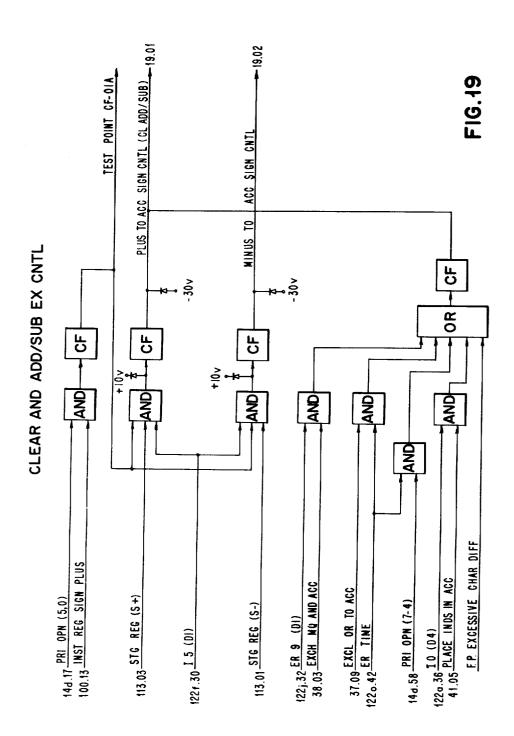

FIGURE 19 illustrates Clear and Add/Subtract Execution Control in logical block form.

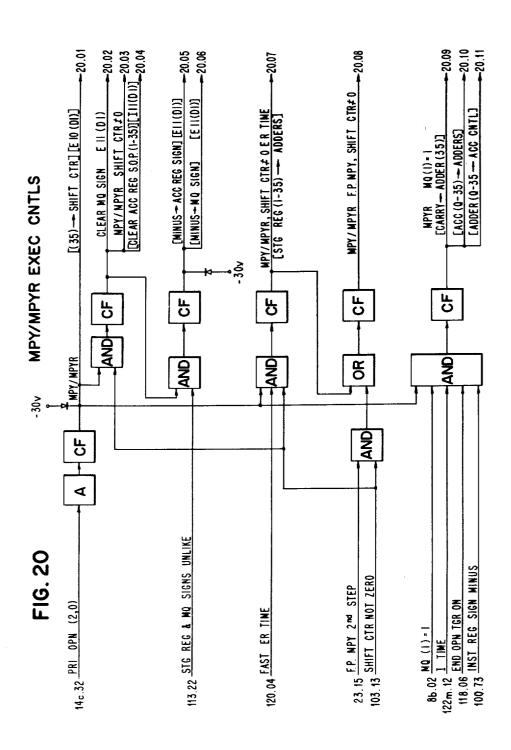

FIGURE 20 illustrates MPY/MPYR EXEC CNTLS (Multiply Execution Controls) in logical block form.

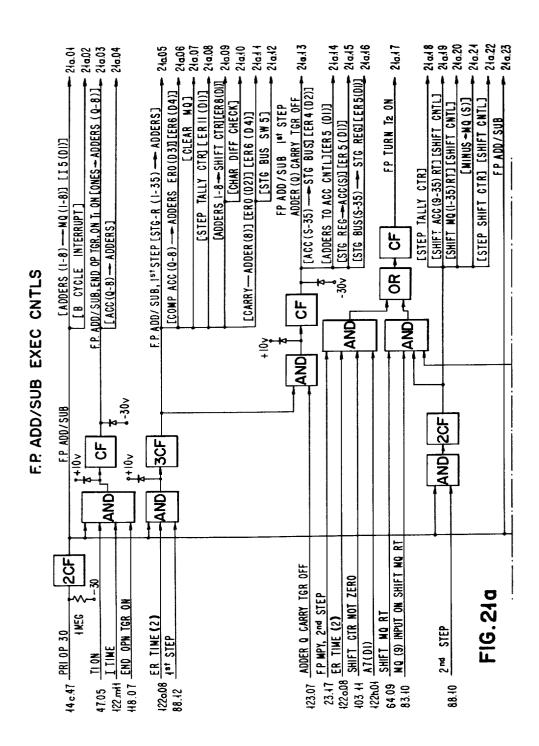

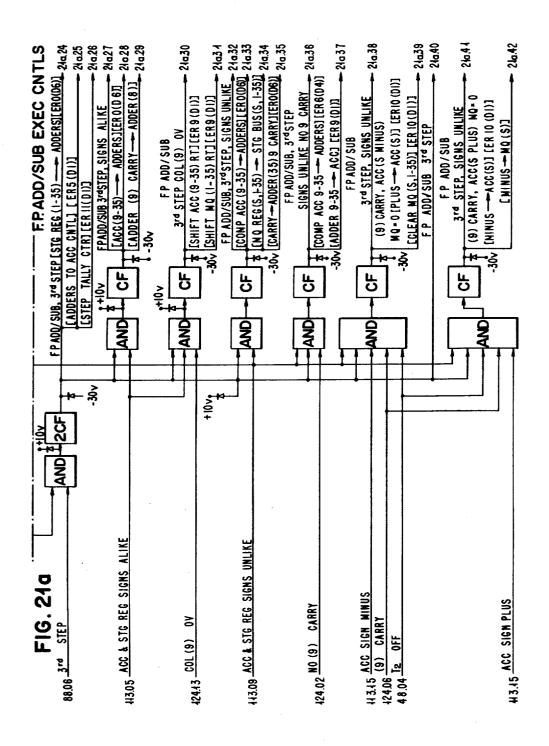

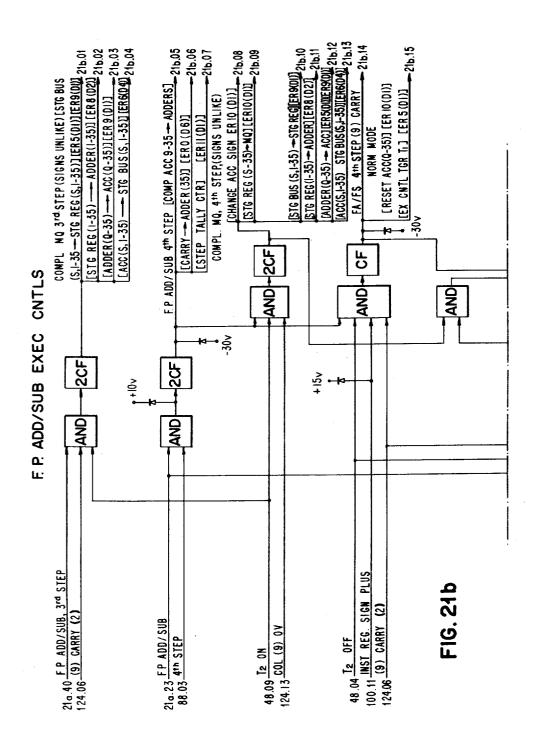

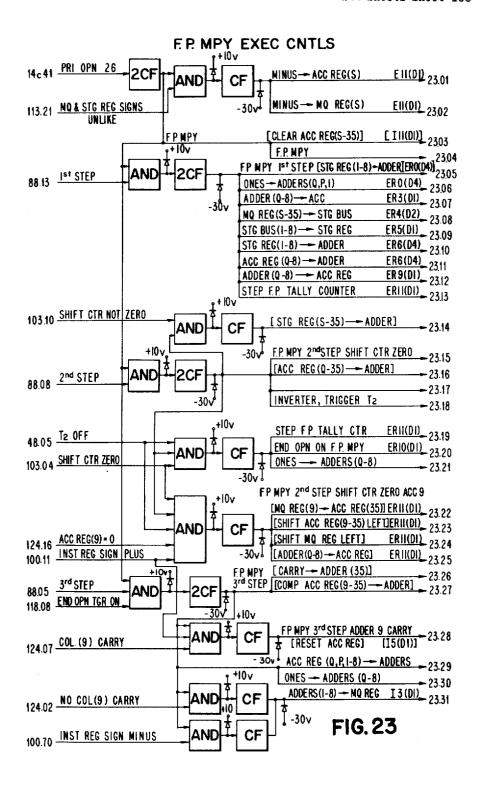

FIGURES 21a (2 sheets) and 21b (2 sheets) illustrate Floating Point Add/Subtract Execution Controls in logical block form.

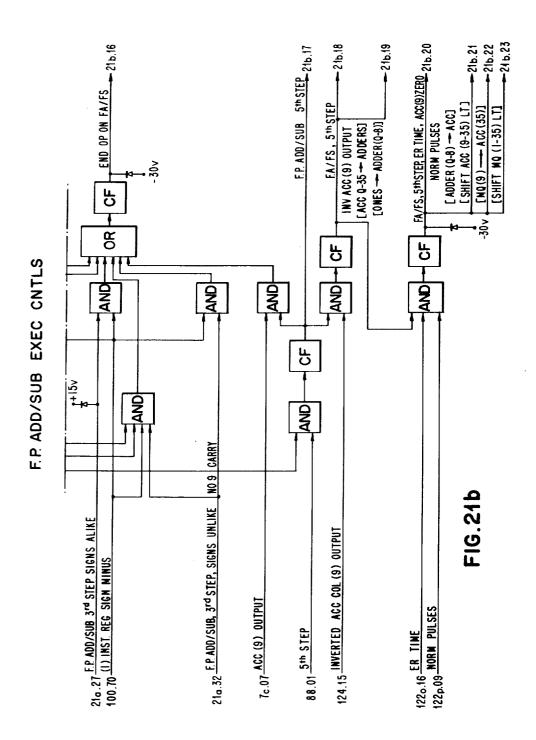

FIGURE 22 illustrates Floating Point Trap Trigger in logical block form.

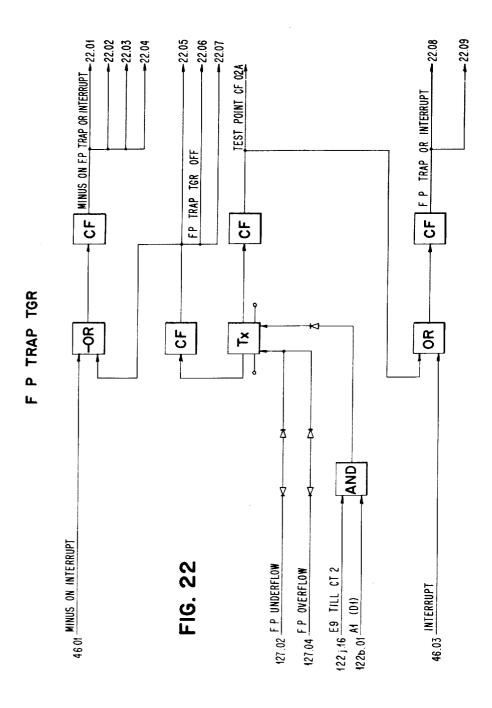

FIGURE 23 illustrates Foating Point Multiply Execution Controls in logical block form.

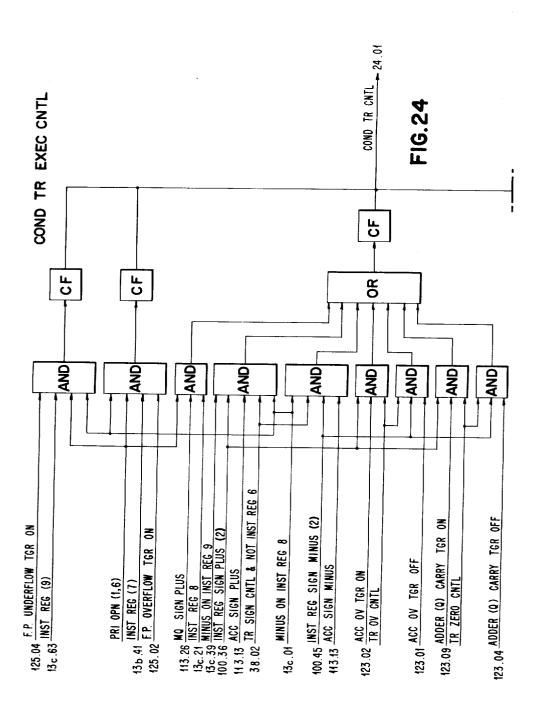

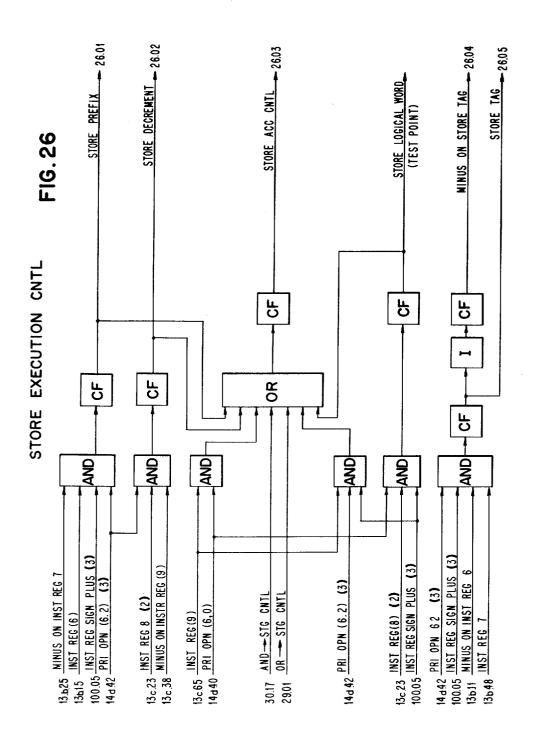

FIGURE 24 (2 sheets) illustrates Conditional Transfer Execution and Control in logical block form.

FIGURE 25 illustrates Conditional Transfer Controls for transfer on Low MQ in logical block form.

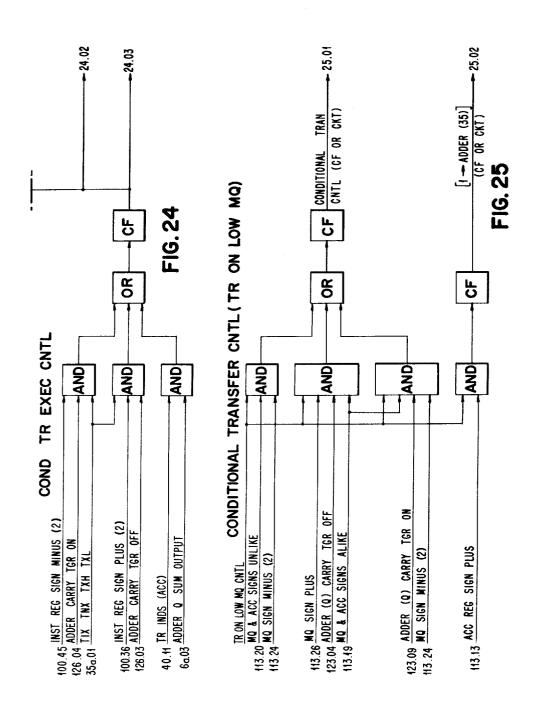

FIGURE 26 illustrates Store Execution Controls in

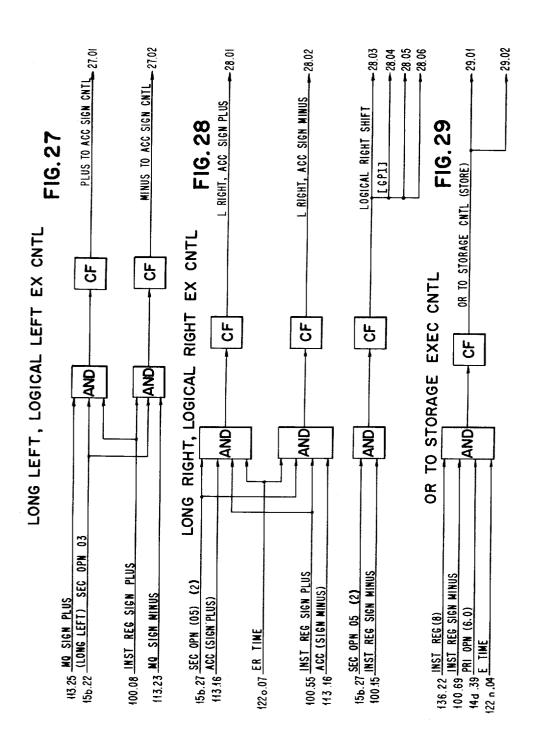

FIGURE 27 illustrates Long Left, Logical Left Execution Control in logical block form.

FIGURE 28 illustrates Long Right, Logical Right Execution Control in logical block form.

FIGURE 29 illustrates OR to Storage Execution Control.

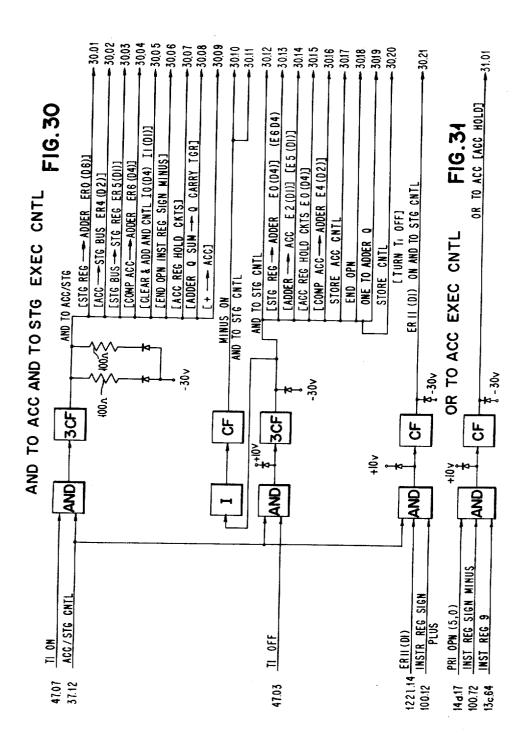

FIGURE 30 illustrates AND to Accumulator and to Storage Execution Control.

FIGURE 31 illustrates OR to Accumulator Execution

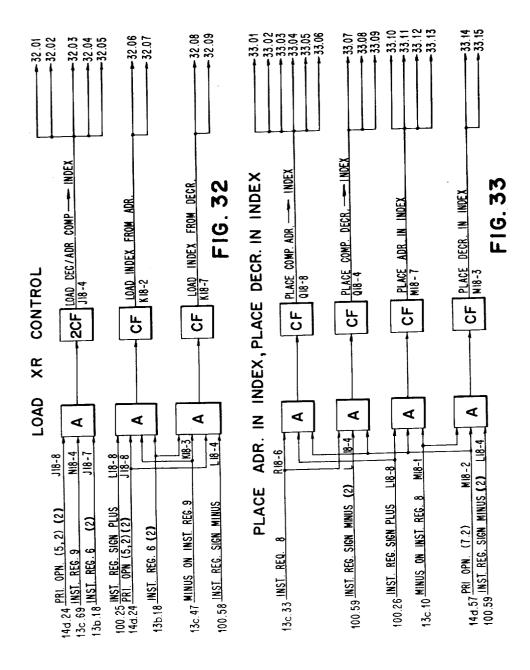

FIGURE 32 illustrates Load Index Register Control.

FIGURE 33 illustrates Place Address in Index Register Control and Place Decrement in Index Register in logical block form.

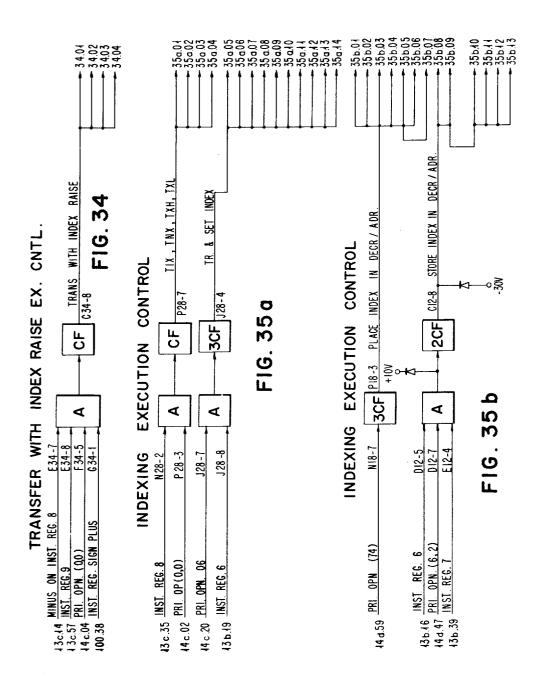

FIGURE 34 illustrates Transfer with Index Raise Execution Control.

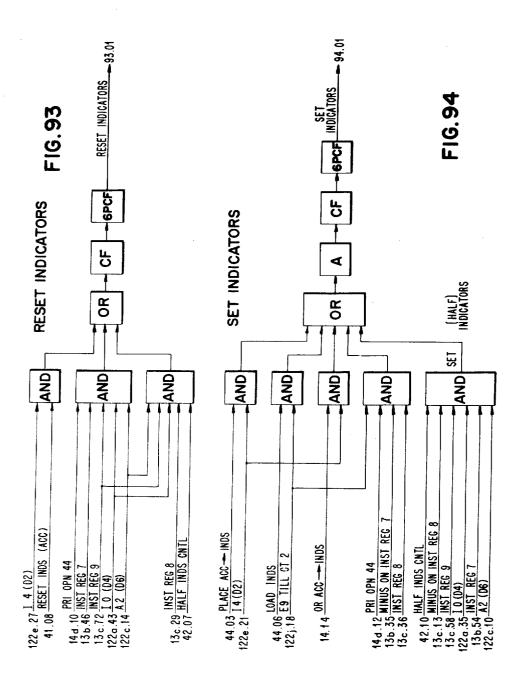

FIGURES 35a and 35b illustrate Indexing Execution Control in logical block form.

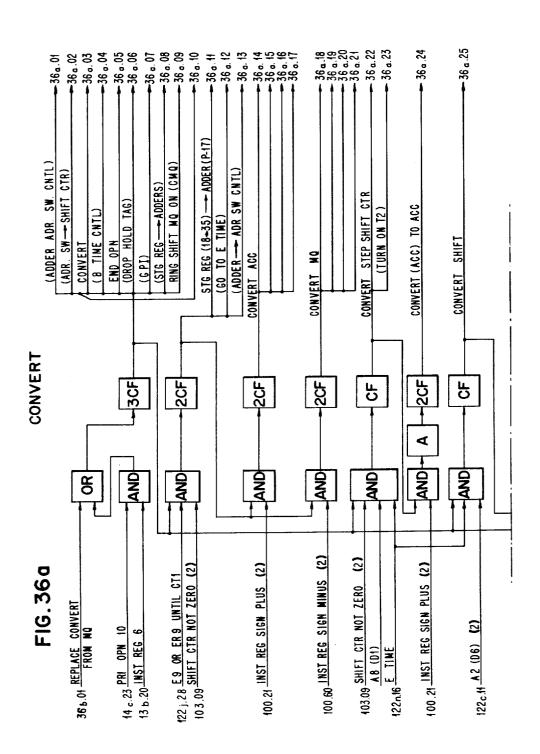

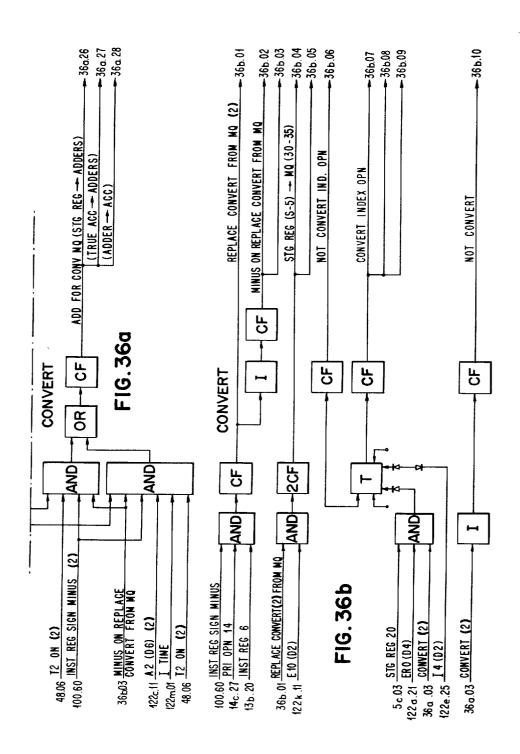

FIGURES 36a (2 sheets and 36b illustrate Convert 35 Control in logical block form.

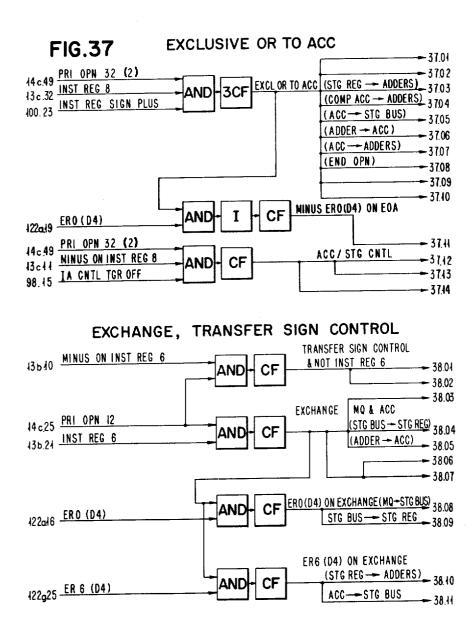

FIGURE 37 illustrates Exclusive OR to Accumulator in logical block form.

FIGURE 38 illustrates Exchange, Transfer Sign Control in logical block form.

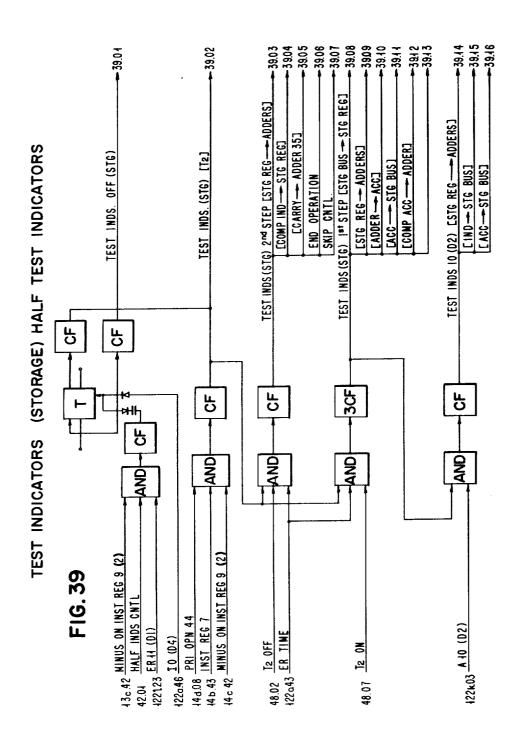

FIGURE 39 illustrates Test Indicators (Storage) Half Test Indicators in logical block form.

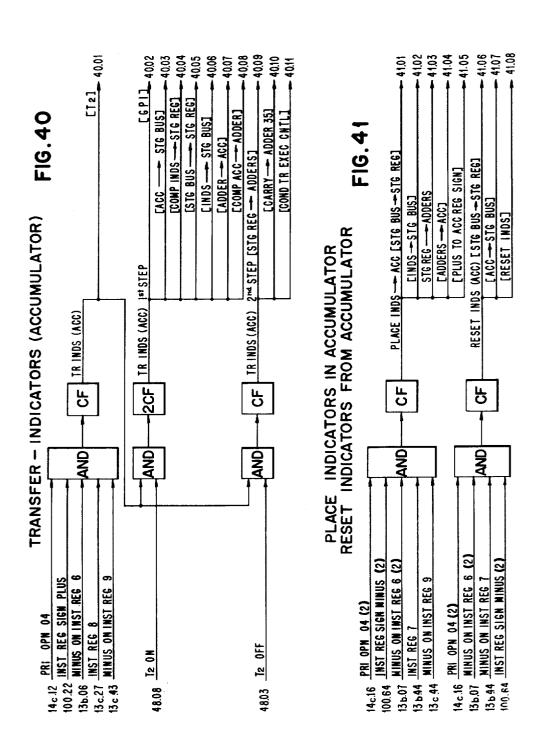

FIGURE 40 illustrates Transfer-Indicators to (Accumulator) in logical block form.

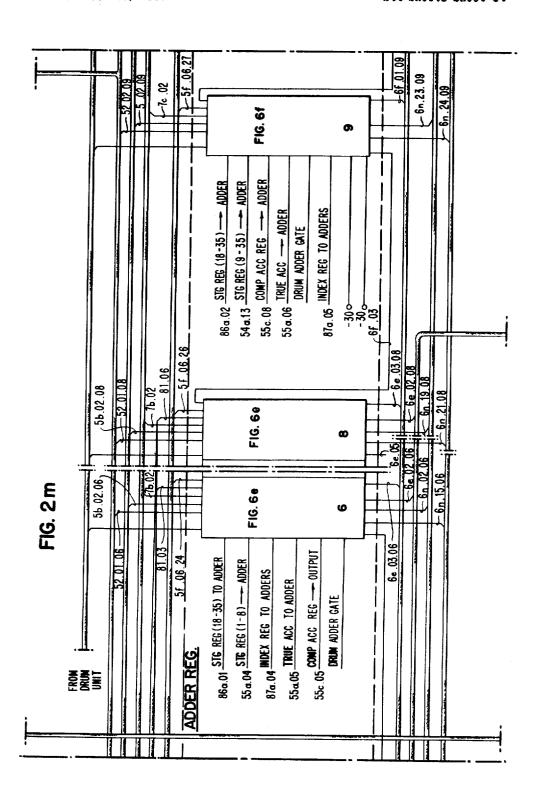

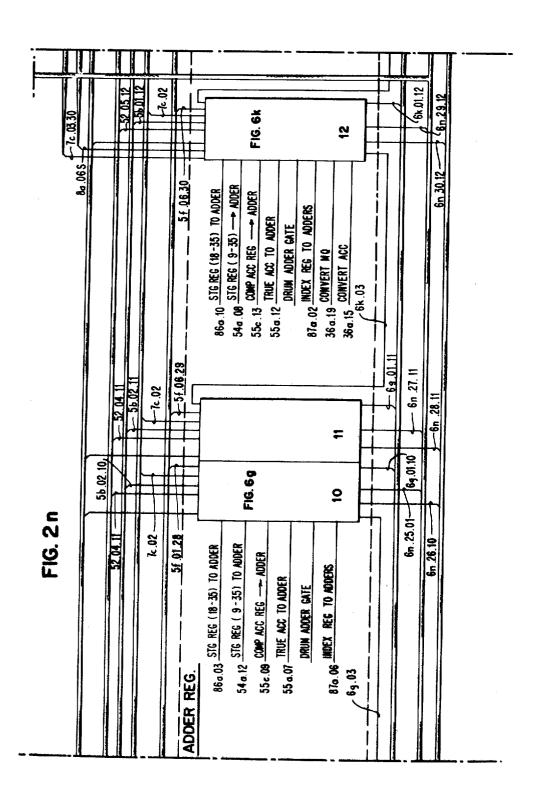

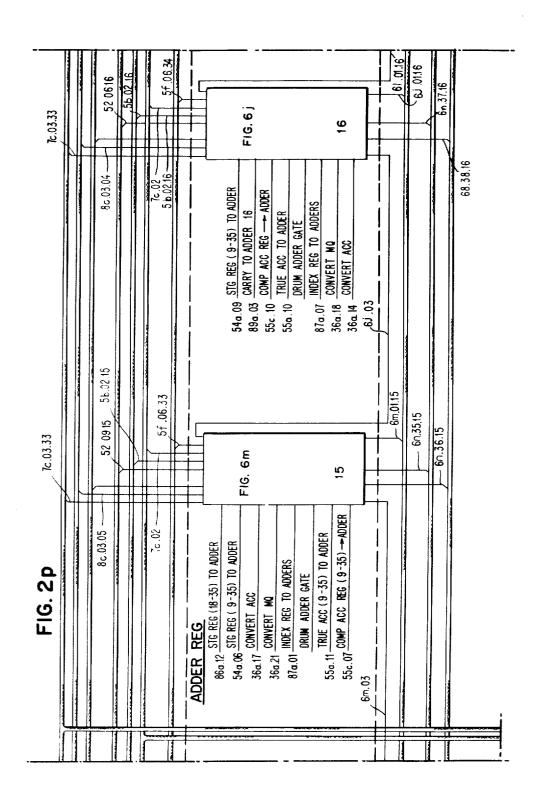

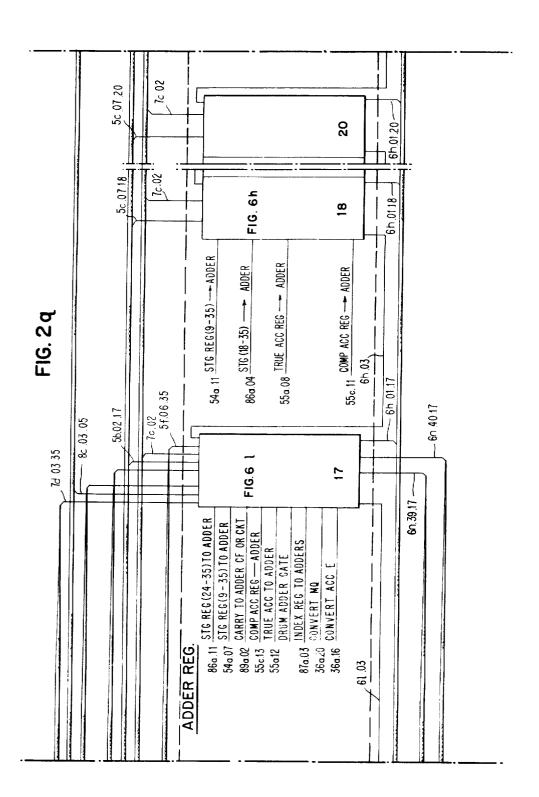

FIGURE 41 illustrates Place Indicators in Accumulator FIGURES 6a through 6n illustrate the Adder and True 45 and Reset Indicators from Accumulator in logical block form.

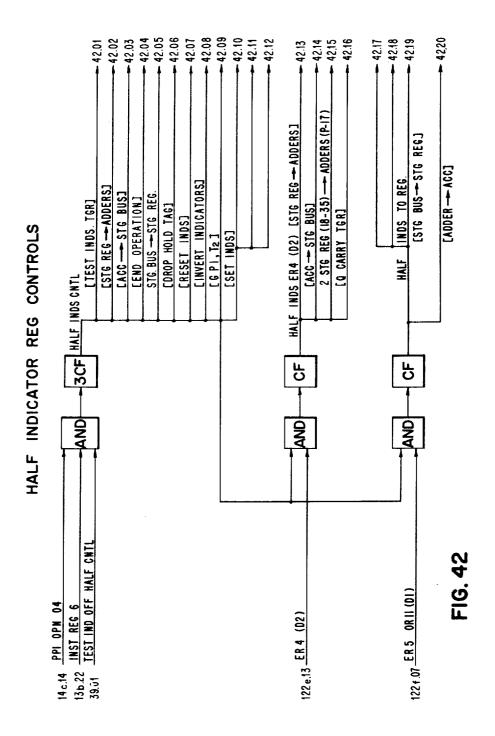

FIGURE 42 illustrates Half Indicator Register Controls in logical block form.

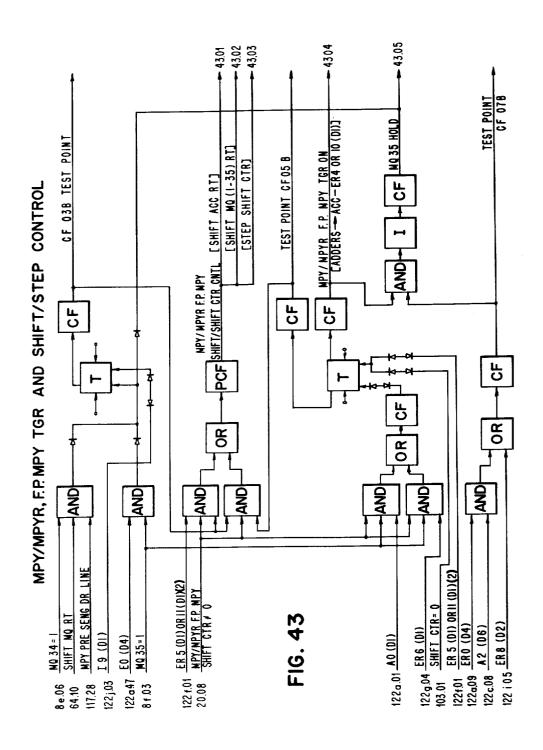

FIGURE 43 illustrates Multiply and Multiplier, Float-Quotient Register and its associated Hold Circuits in 50 ing Point Multiply Trigger and Shift/Step controls in logical block form.

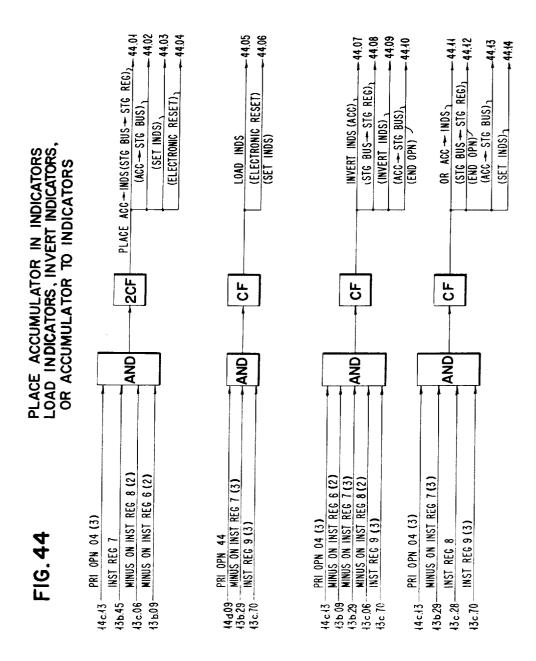

FIGURE 44 illustrates Place Accumulator in Indicators Load Indicators, Invert Indicators or Accumulator Indicators in logical block form.

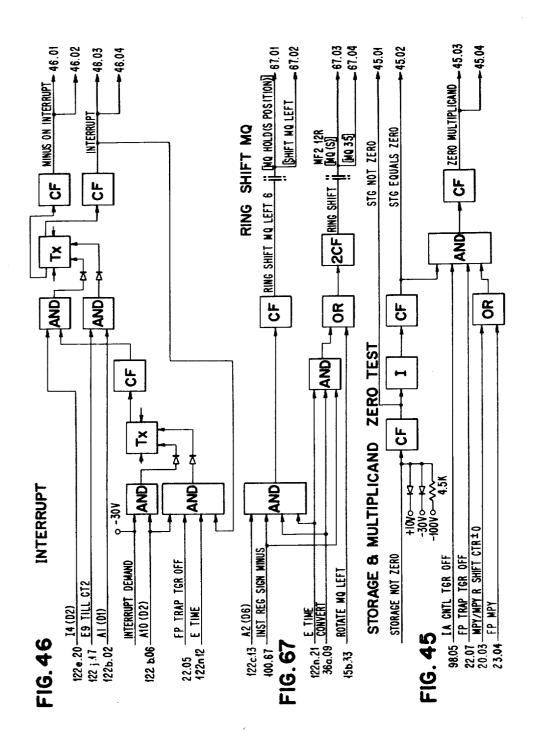

FIGURE 45 illustrates Storage and Multiplicand Zero Test in logical block form.

FIGURE 46 illustrates Interrupt Control in logical block form.

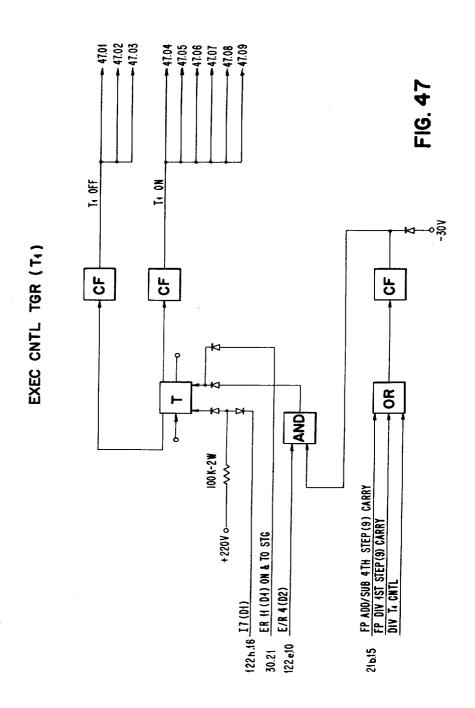

FIGURE 47 illustrates Execution Control Trigger (T1).

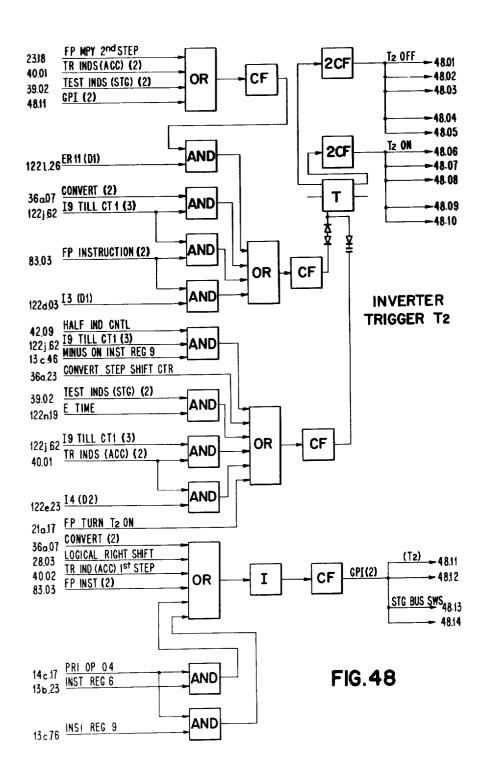

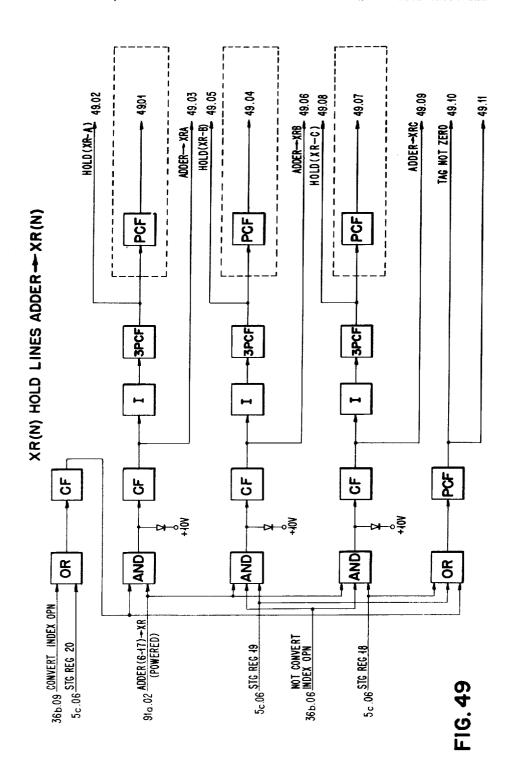

FIGURE 48 illustrates Inverter Trigger T2. FIGURE 49 illustrates Index Register (N) Hold Lines

Adder to Index Register (N).

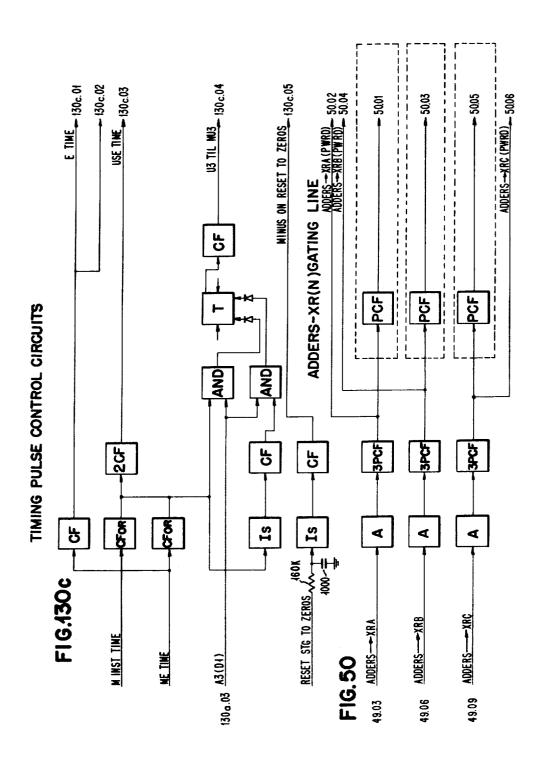

FIGURE 50 illustrates Adders to Index Register (N) Gating Line Control.

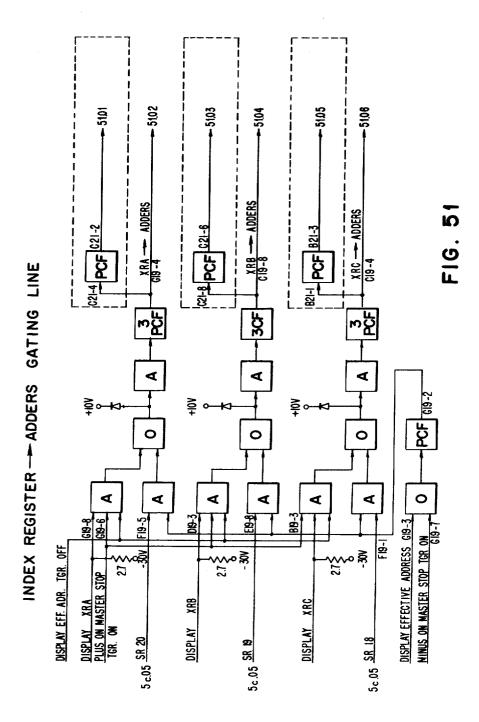

FIGURE 51 illustrates Index Register to Adders Gating Line.

FIGURE 52 illustrates Idex Register Mixing Unit in logical block form.

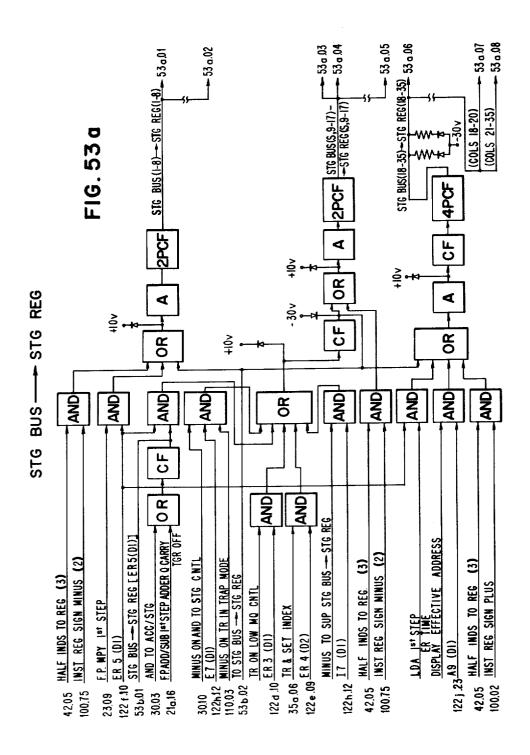

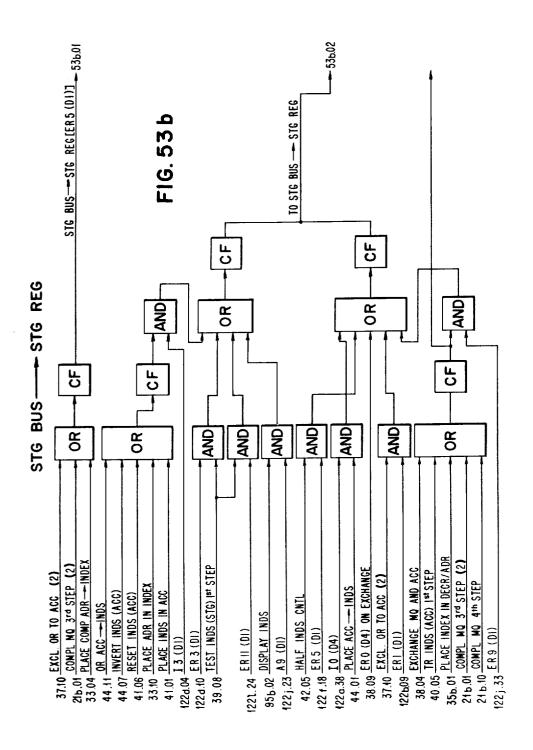

FIGURES 53a and 53b illustrate Storage Bus to Storage Register.

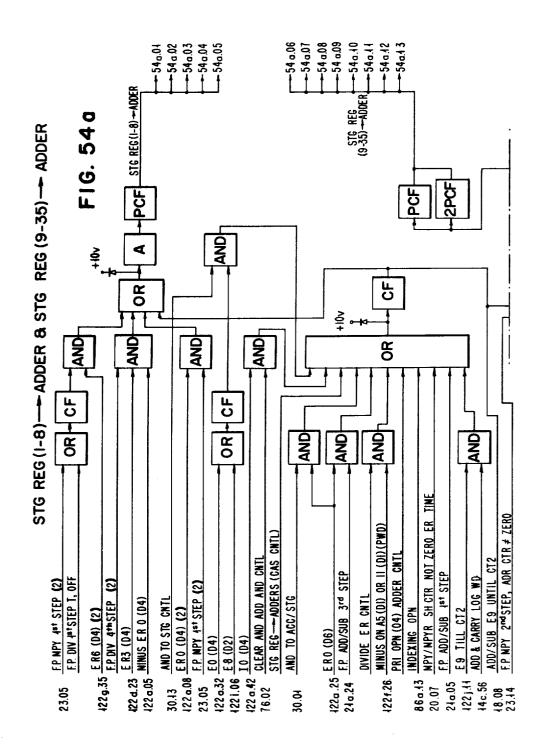

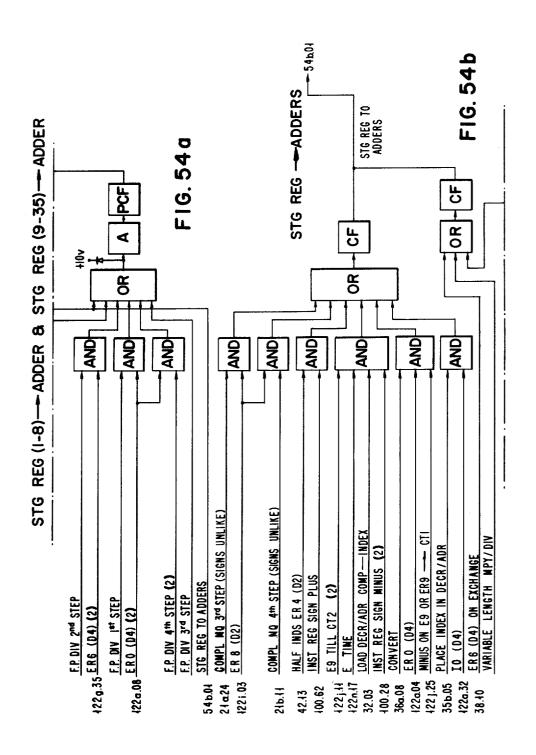

FIGURES 54a (2 sheets) and 54b (2 sheets) illustrate Storage Register (1-8) to Adder and Storage Register (9-35) to Adder.

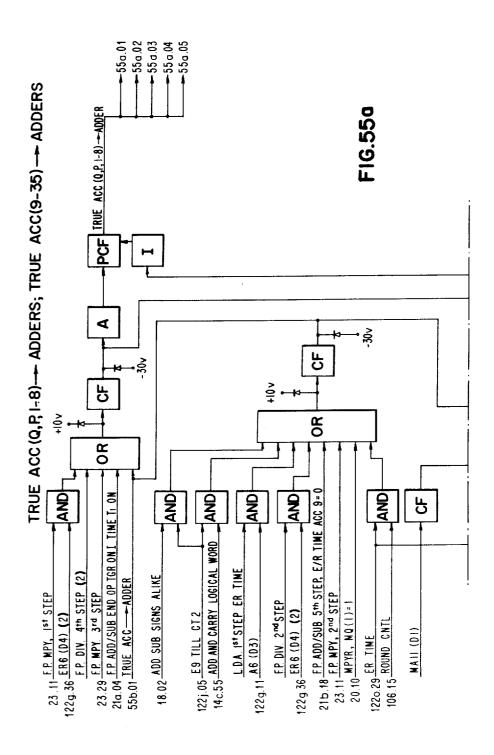

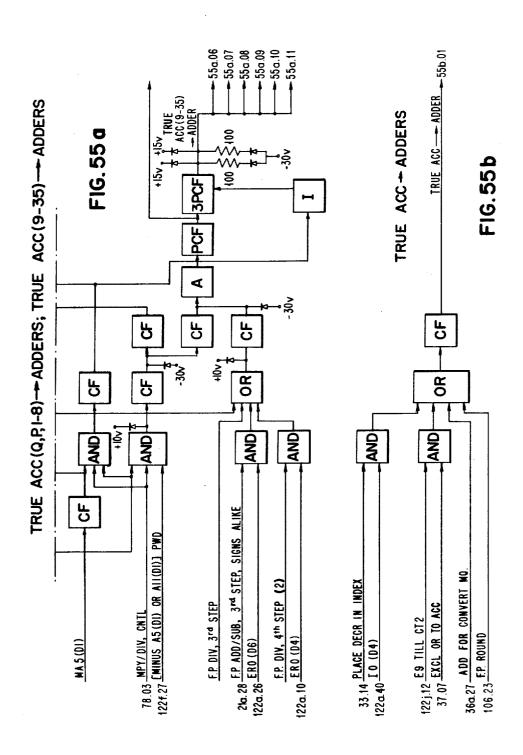

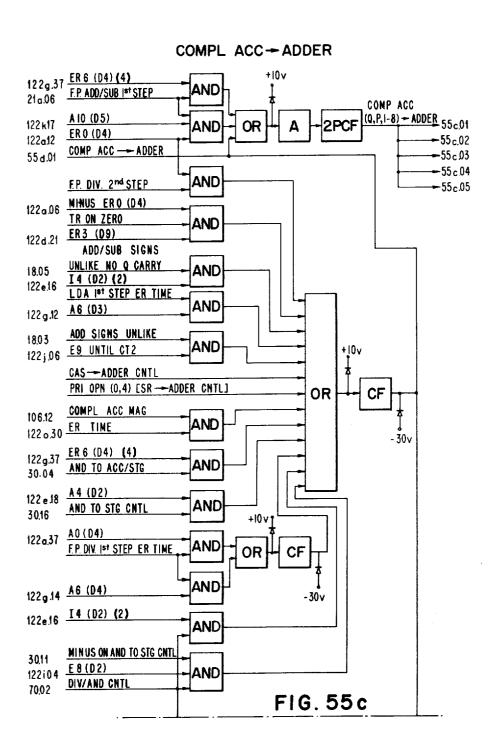

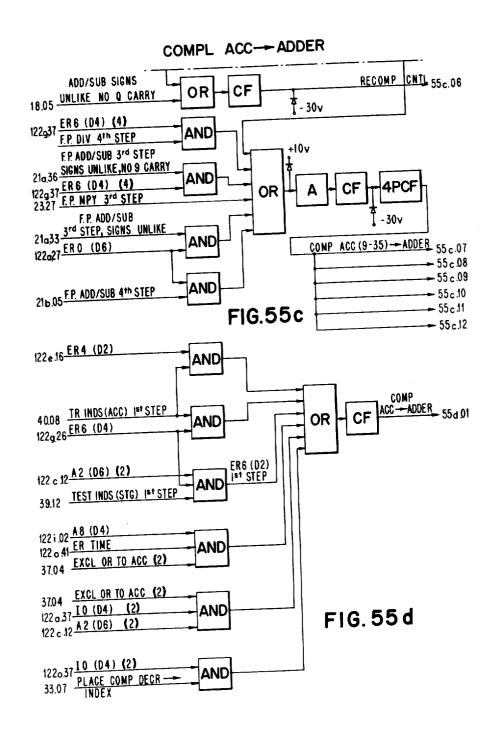

FIGURES 55a (2 sheets), 55b, 55c (2 sheets) and 55d

illustrate True Accumulator (Q, P, 1-8) to Adders; True Accumulator (9-35) to Adders.

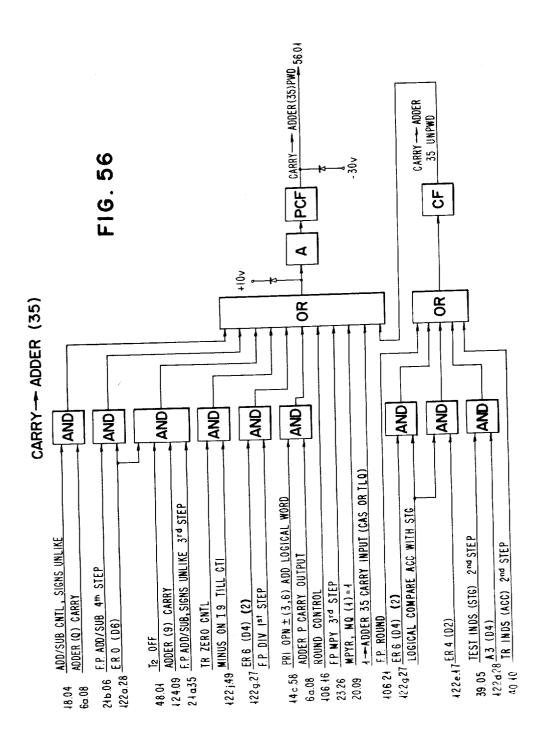

FIGURE 56 illustrates Carry to Adder (35) in logical block form.

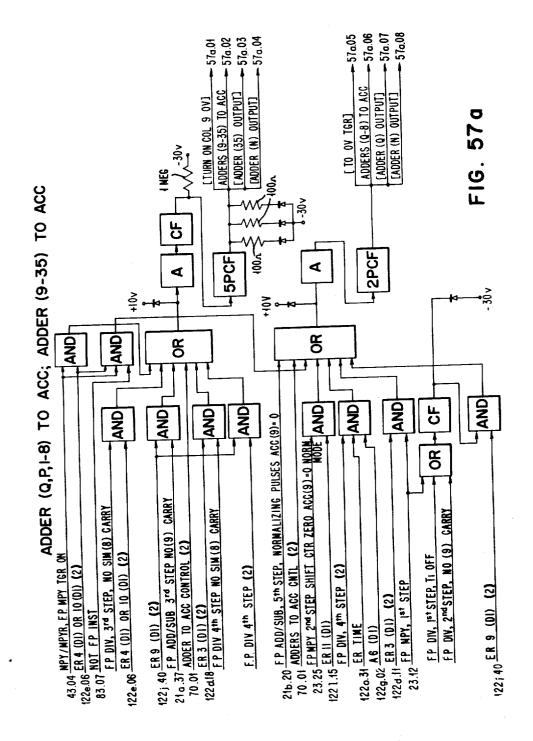

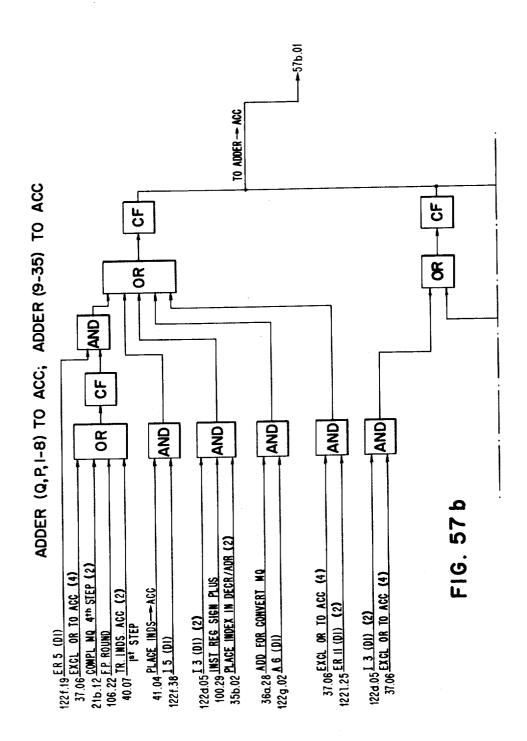

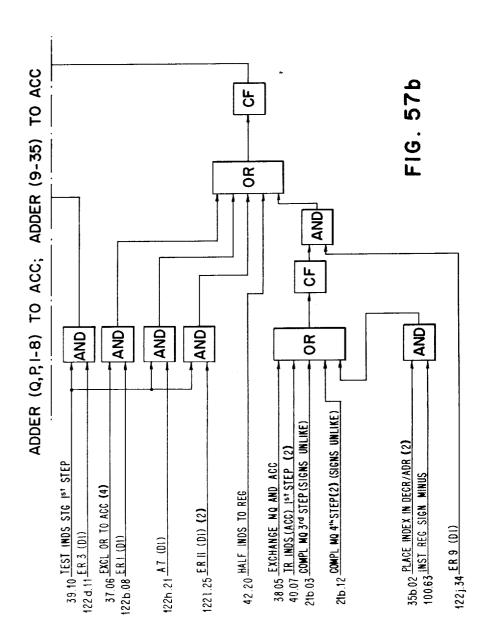

FIGURES 57a and 57b (2 sheets) illustrate Adder (Q, P, 1-8) to Accumulator; Adder (9-35) to Accumulator in logical block form.

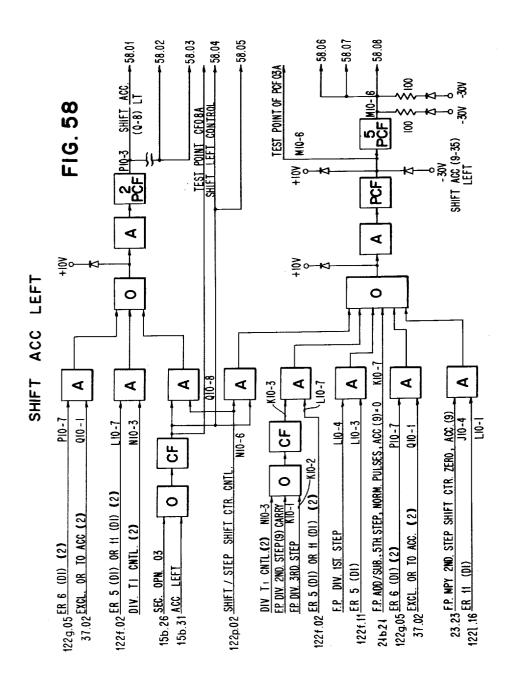

FIGURE 58 illustrates Shift Accumulator Register Left Control.

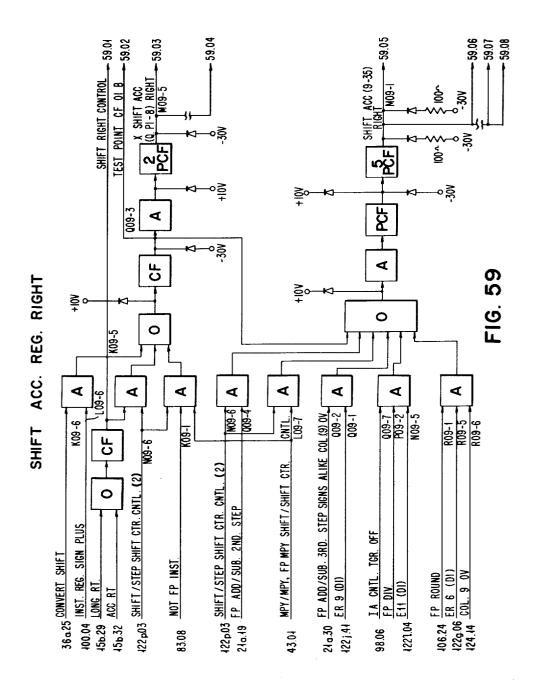

FIGURE 59 illustrates Shift Accumulator Register 10 logical block form. Right Control. FIGURE 95b illustrates

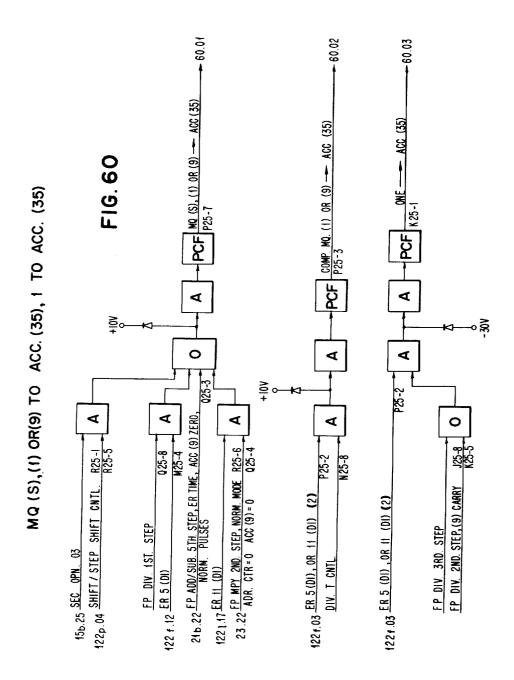

FIGURE 60 illustrates MQ positions S, 1 or 9 to Accumulator 35, 1 to Accumulator 35 Control in logical block form.

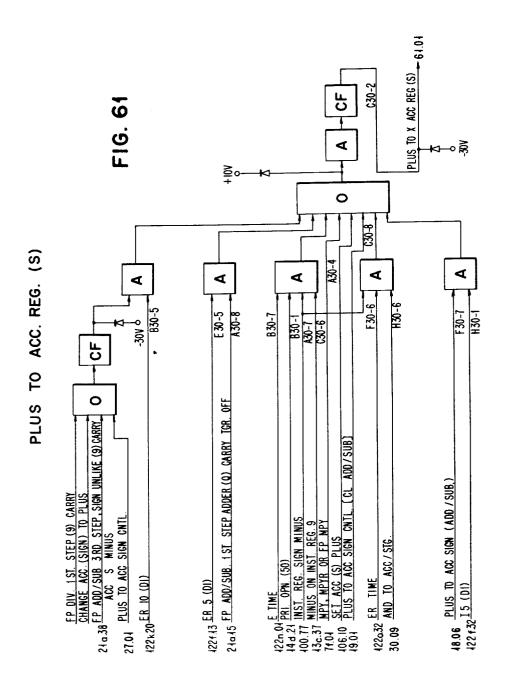

FIGURE 61 illustrates Plus to Accumulator Register  $_{15}$  position S control.

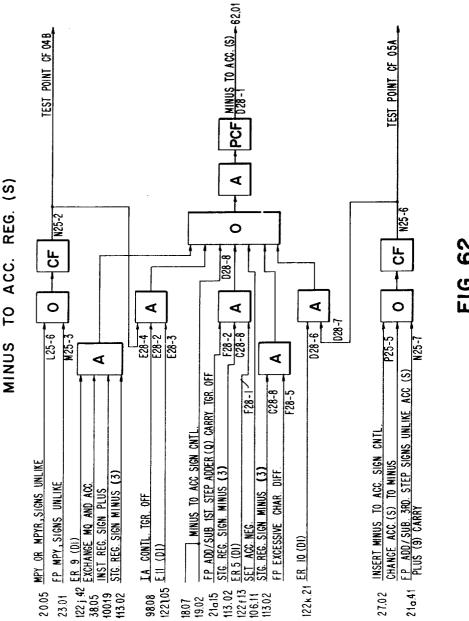

FIGURE 62 illustrates Minus to Accumulator Register S Control.

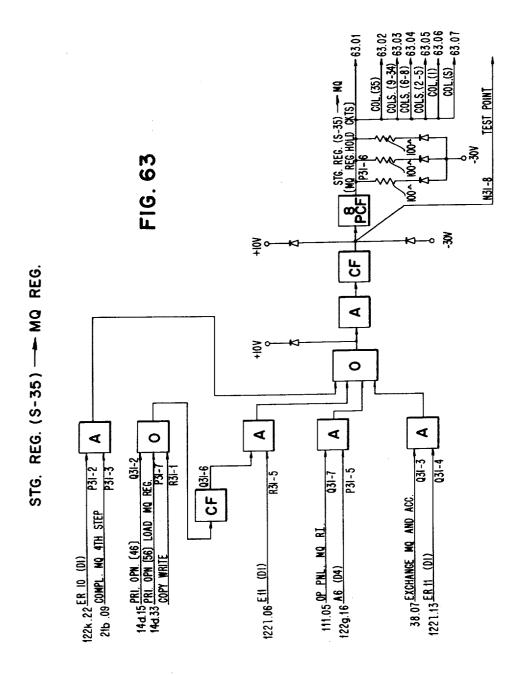

FIGURE 63 illustrates Storage Register S, 1 through 35 to MQ Register Controls in logical block form.

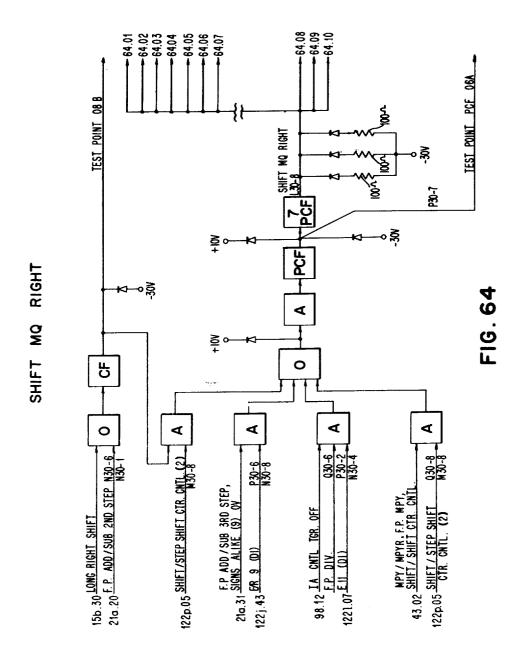

FIGURE 64 illustrates Shift MQ Right Controls in logical block form.

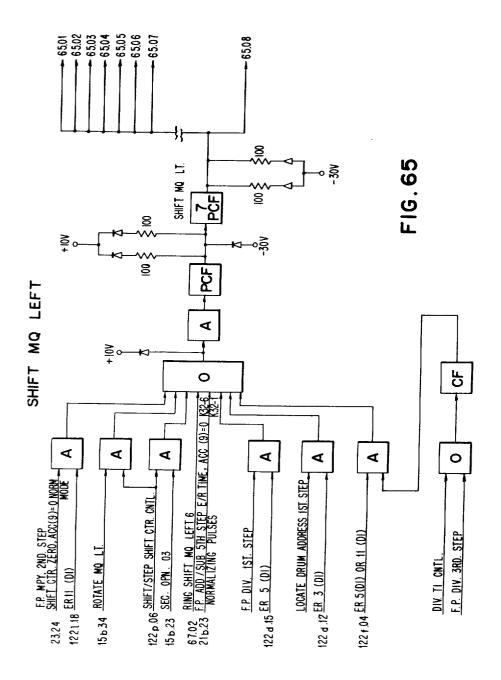

FIGURE 65 illustrates Shift MQ Left Controls in logical block form.

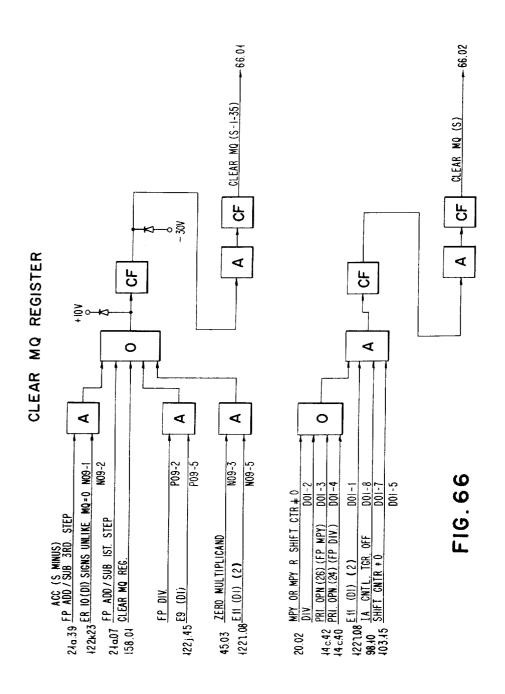

FIGURE 66 illustrates Clear MQ Register in logical 25 2 in logical block form.

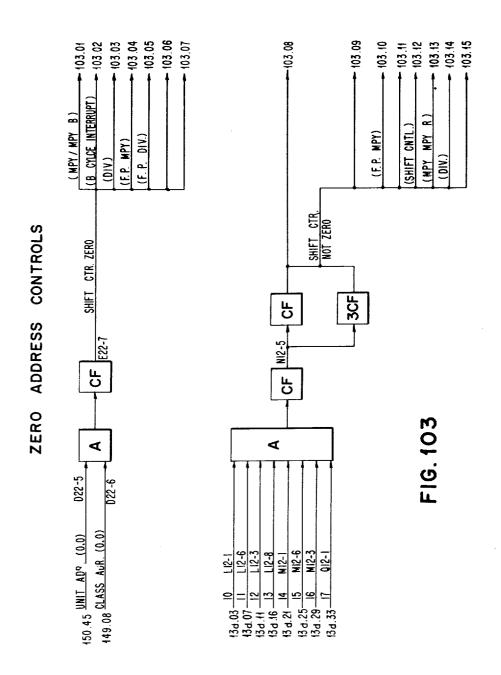

FIGURE 103 illustrates Clear MQ Register in logical block form.

FIGURE 67 illustrates Ring Shift MQ in logical block form

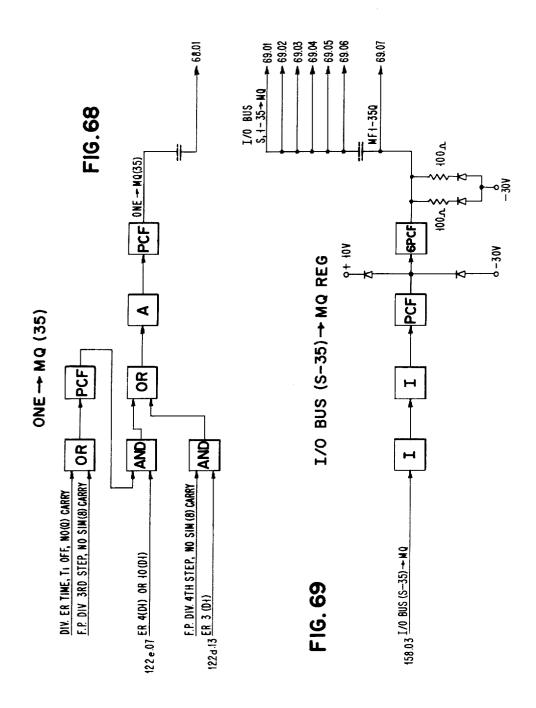

FIGURE 68 illustrates 1 to MQ Register position 35 Control in logical block form.

FIGURE 69 illustrates I/O Bus, S through 35, to MQ Register Controls in logical block form.

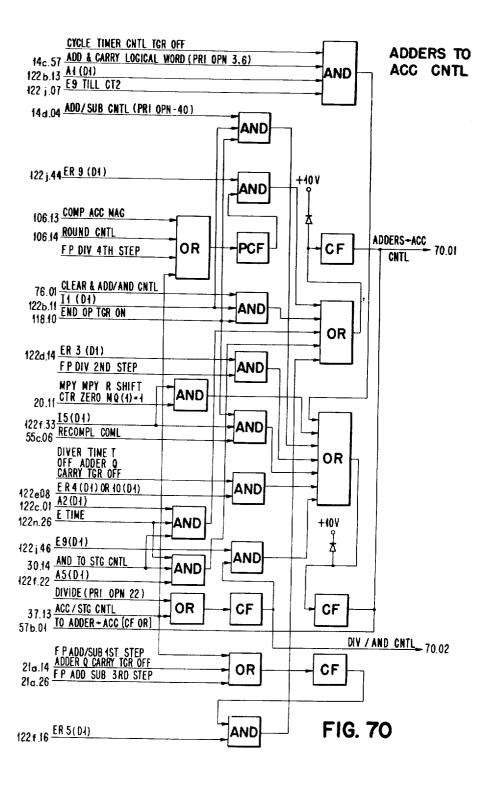

FIGURE 70 illustrates Adders to Accumulator Controls in logical block form.

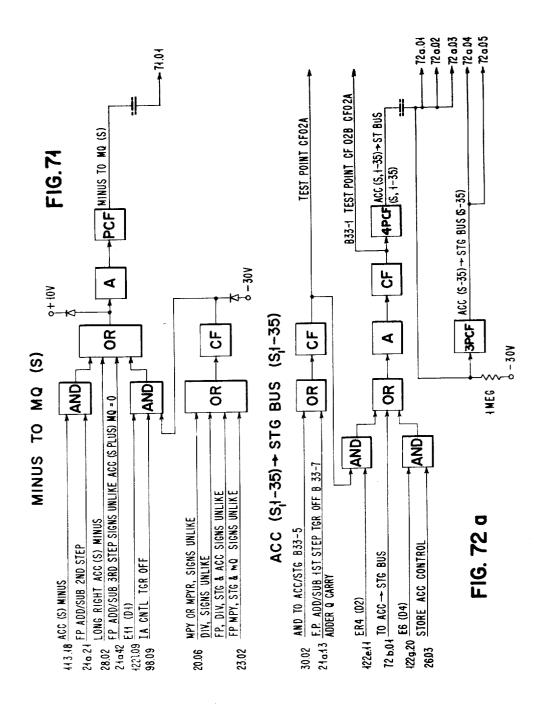

FIGURE 71 illustrates Minus to MQ position S con- 35 trols in logical block form.

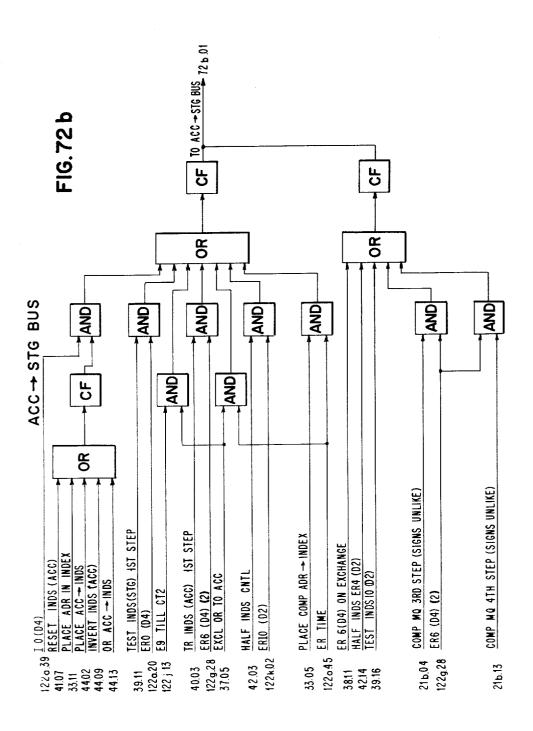

FIGURE 72a and 72b illustrate Accumulator to Storage Bus Controls.

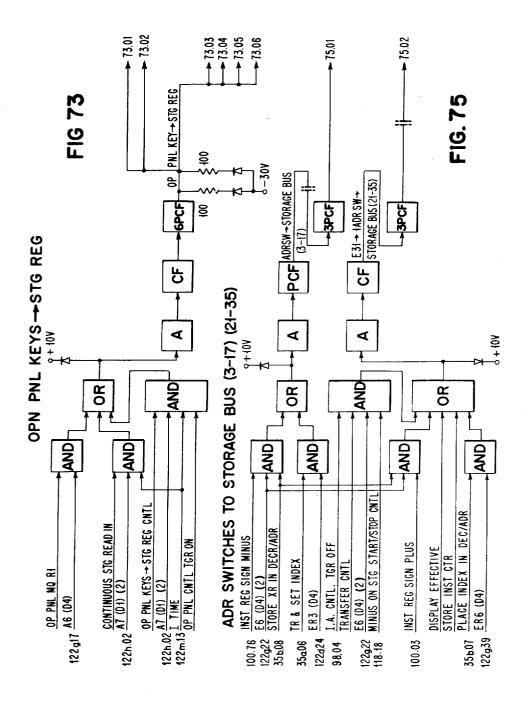

FIGURE 73 illustrates operation Panel Keys to Storage Register Controls.

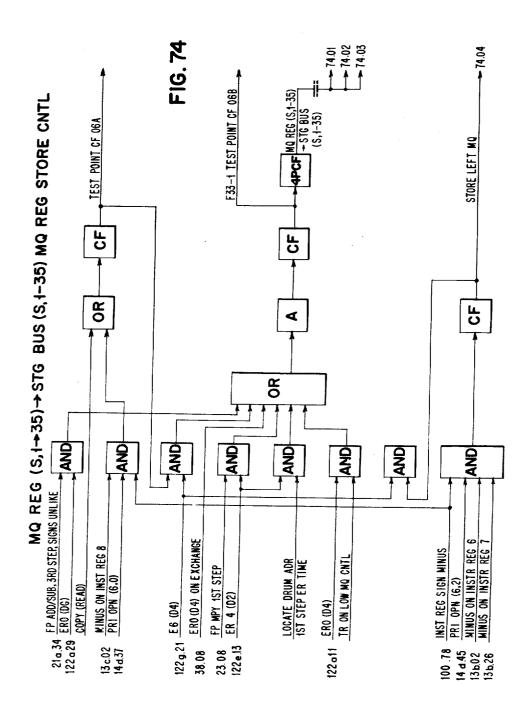

FIGURE 74 illustrates MQ Register S, 1 through 35 to Bus S, 1 through 35 and Storage MQ Register Store Control.

FIGURE 75 illustrates Address Switches to Storage Bus 3 through 17, 21 through 35 control.

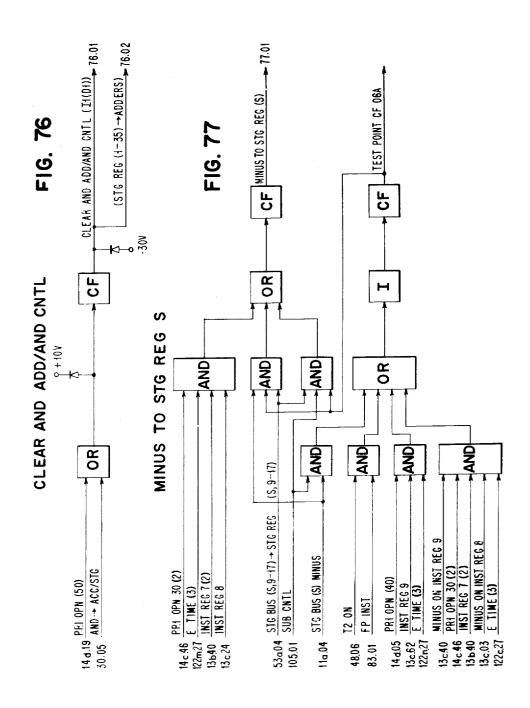

FIGURE 76 illustrates Clear and Add AND Control. FIGURE 77 illustrates Minus to Storage Register S Control in logical block form.

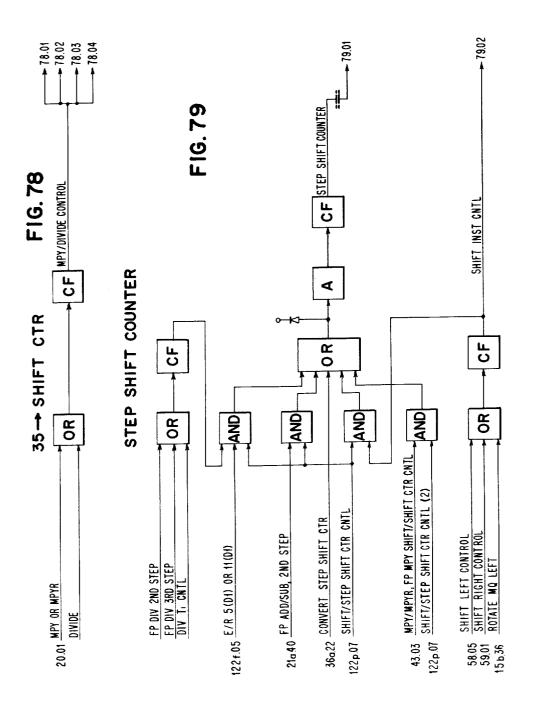

FIGURE 78 illustrates 35 to Shift Counter Control in logical block form.

FIGURE 79 illustrates Step Shift Counter Countrols in logical block form.

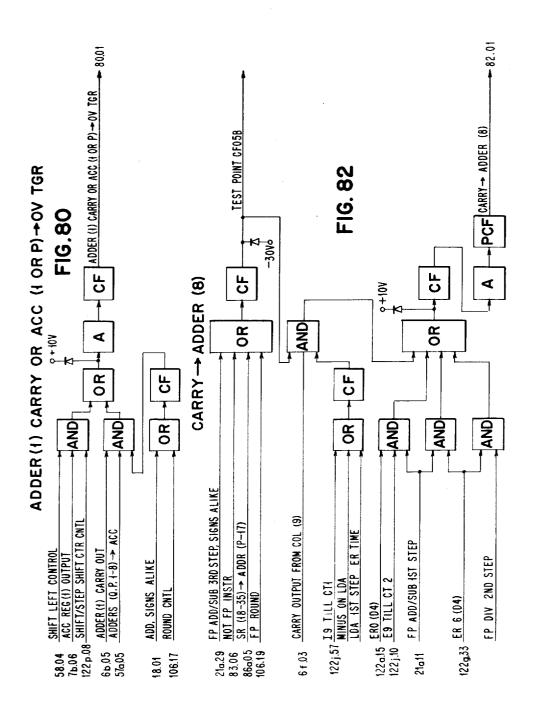

FIGURE 80 illustrates Adder (1) Carry or Accumulator (1 or P) to Overflow Trigger Controls.

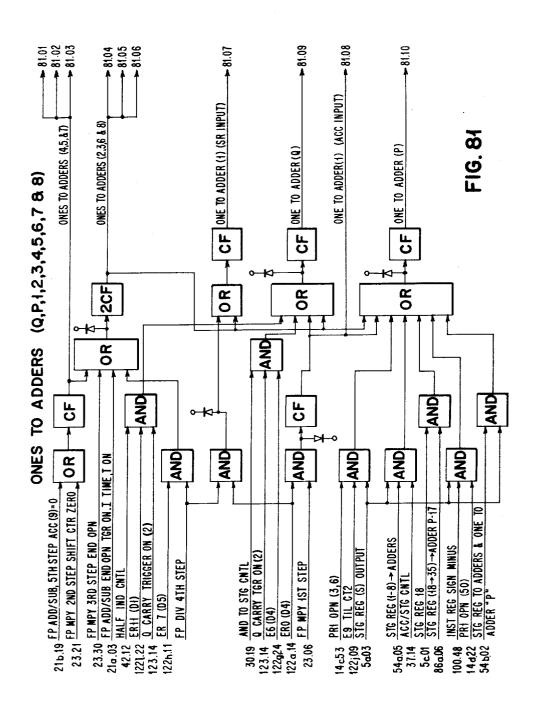

FIGURE 81 illustrates Ones to Adders Q, P, 1 through 55 8 Controls in logical block form.

FIGURE 82 illustrates Carry to Adder Position 8 Controls in logical block form.

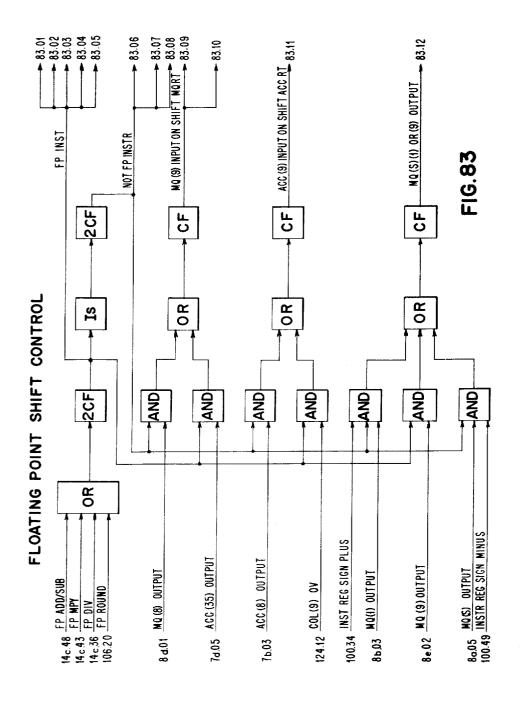

FIGURE 83 illustrates Floating Point Shift Control in logical block form.

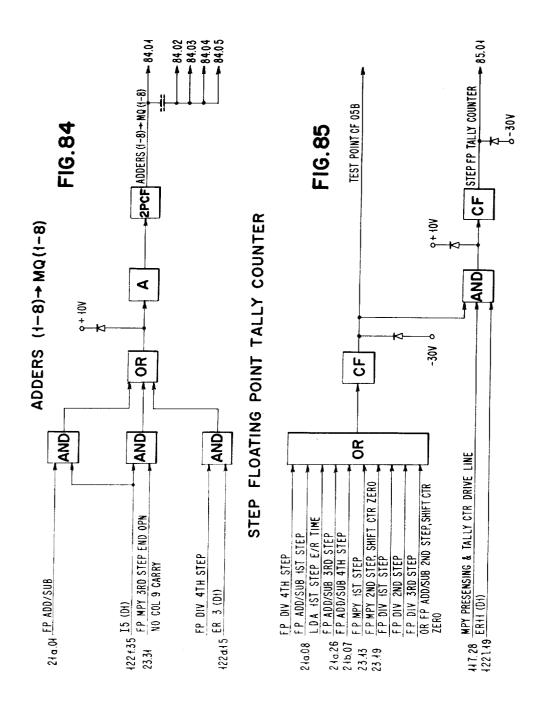

FIGURE 84 illustrates Adders 1 through 8 to MQ 1 through 8 in logical block form.

FIGURE 85 illustrates Step Floating Point Tally Counter in logical block form.

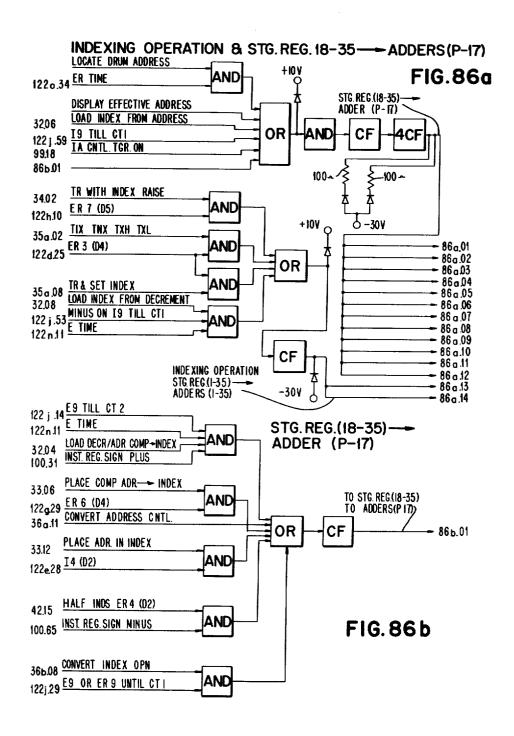

FIGURES 86a and 86b illustrate Indexing Operation and Storage Register 18 through 35 to Adders P through 17

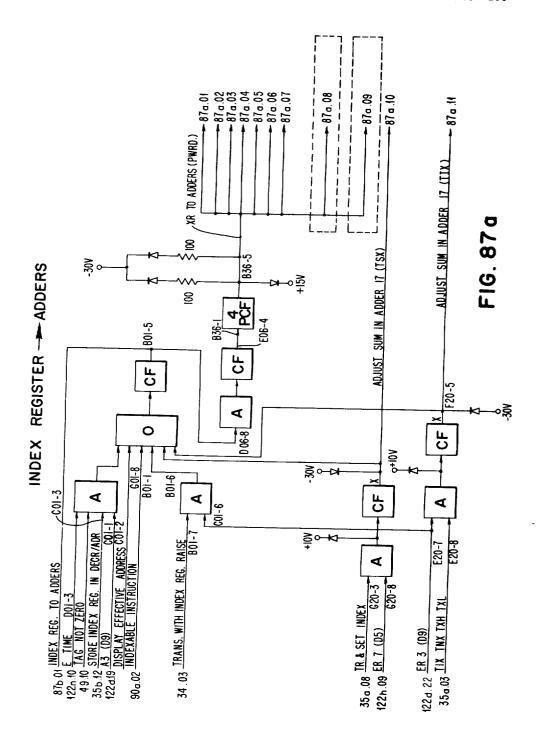

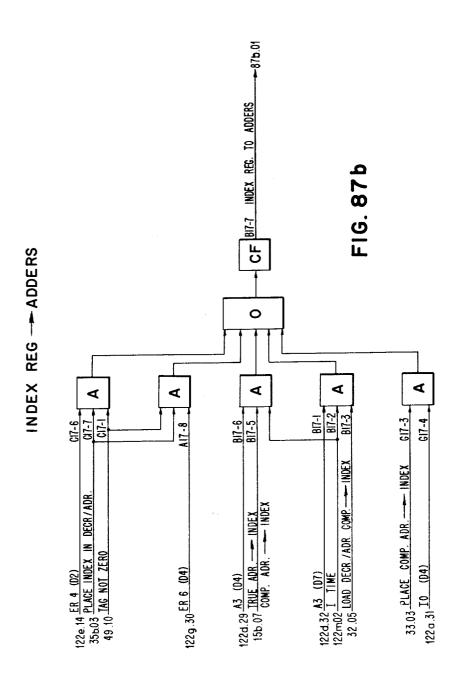

FIGURES 87a and 87b illustrate Index Register to Adder Controls in logical block form.

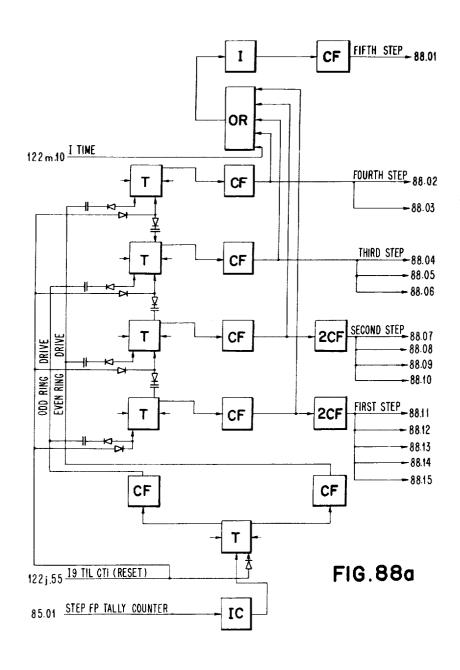

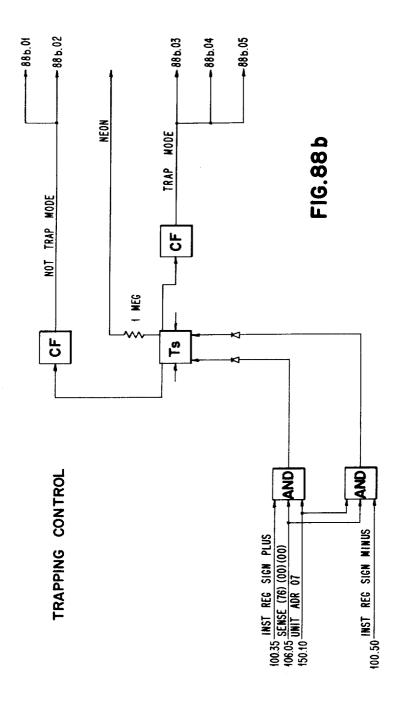

FIGURE 88a illustrates Floating Point Tally Counter. 70 FIGURE 88b illustrates Trapping Control in logical block form.

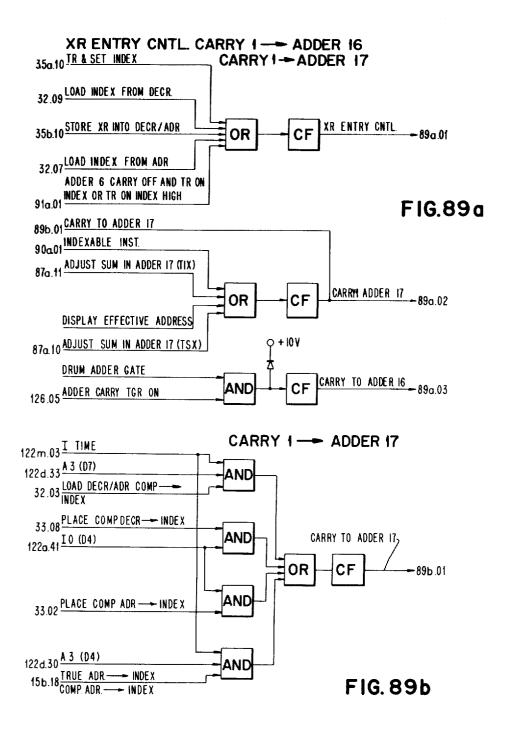

FIGURES 89a and 89b illustrate Index Register Entry Control Carry One to Adder 16 and Carry One to Adder 17 Controls.

6

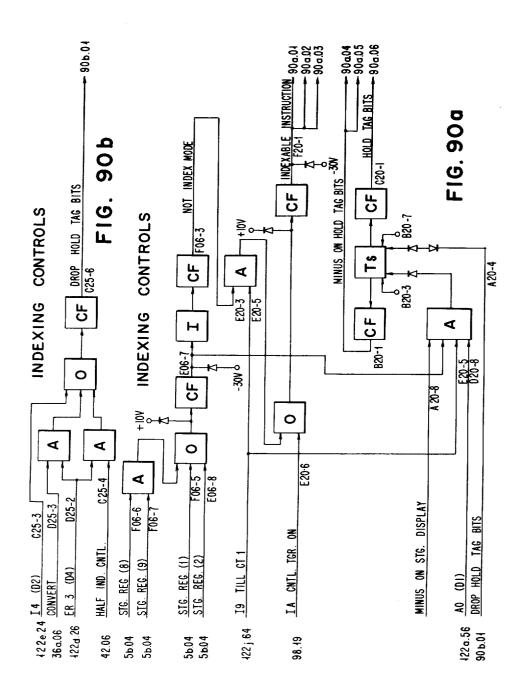

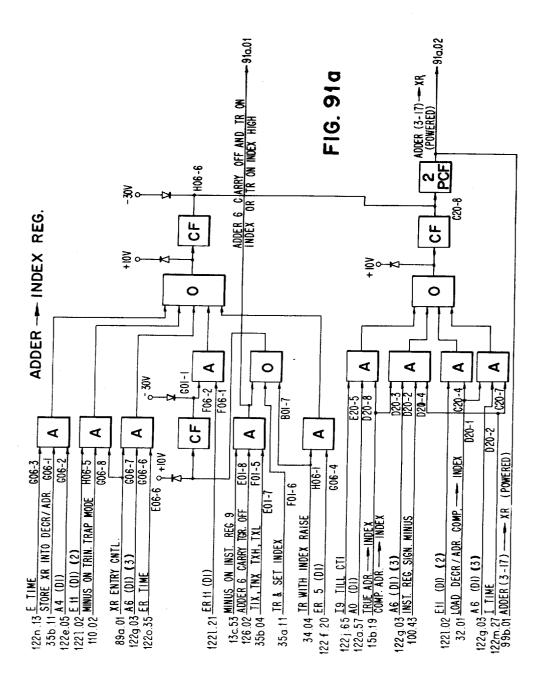

FIGURES 90a and 90b illustrate Indexing Controls. FIGURES 91a and 91b illustrate Adder to Index Register.

FIGURE 92 illustrates Electronic Reset of Indicators.

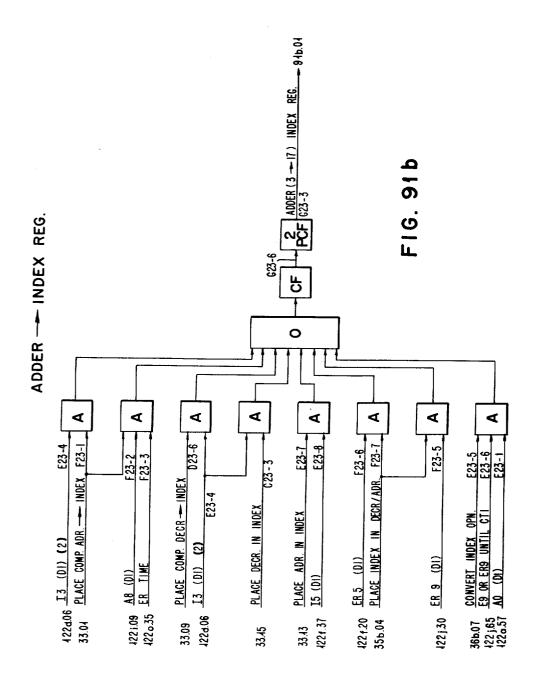

FIGURE 93 illustrates Reset Indicators Controls in logical block form.

FIGURE 94 illustrates Set Indicators Controls in logical block form.

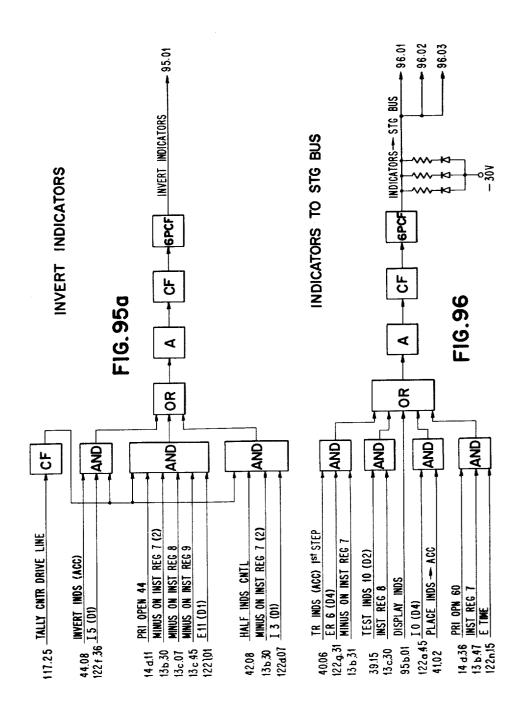

FIGURE 95a illustrates Invert Indicators Controls in logical block form.

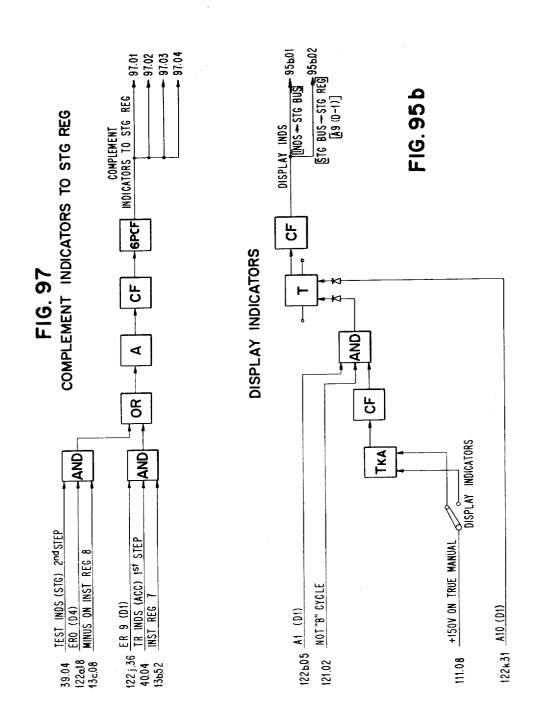

FIGURE 95b illustrates Display Indicators.

FIGURE 96 illustrates Indicators to Storage Bus Controls in logical block form.

FIGURE 97 illustrates complement Indicators to Storage Register Controls in logical block form.

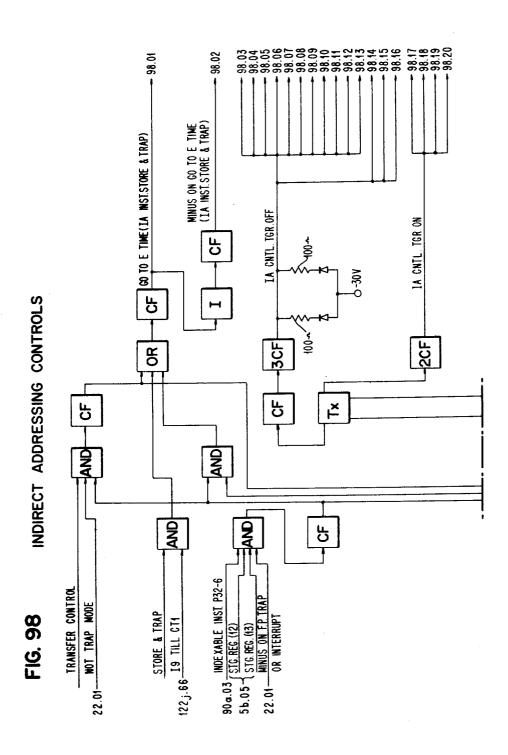

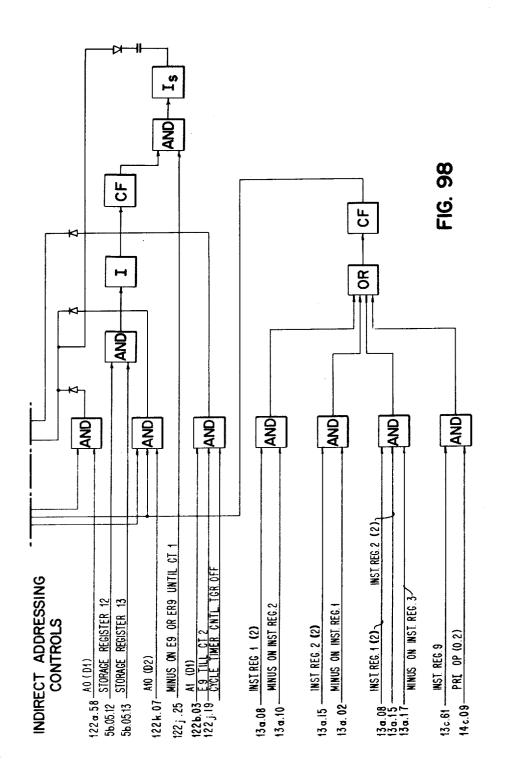

FIGURE 98 illustrates Indirect Addressing Controls in logical block form.

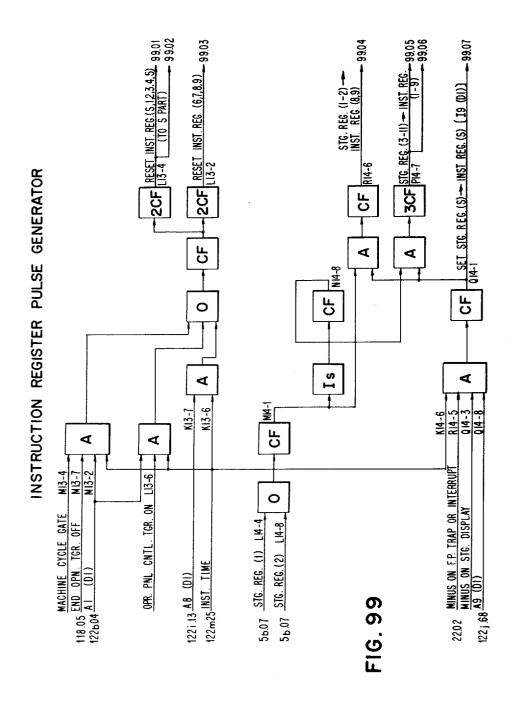

FIGURE 99 illustrates Instruction Register Pulse Generator in logical block form.

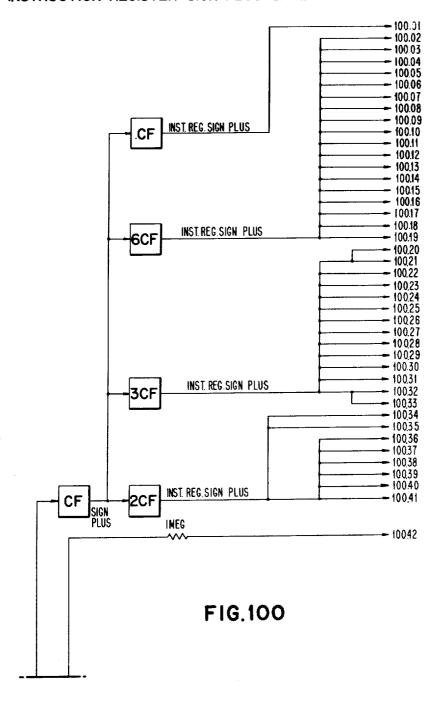

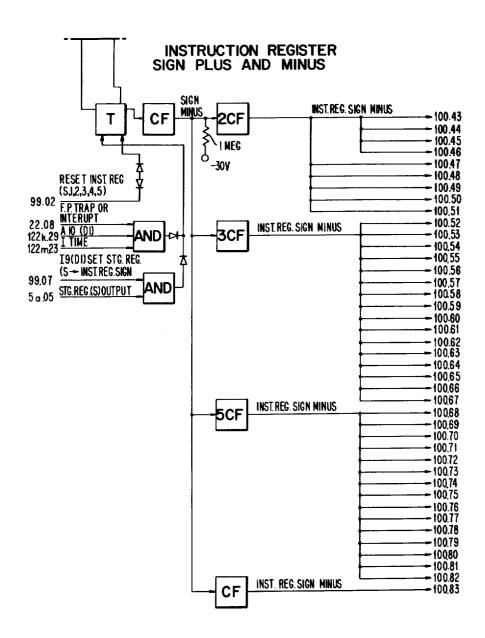

FIGURE 100 (2 sheets) illustrates Instruction Register Sign, Plus and Minus Controls in logical block form.

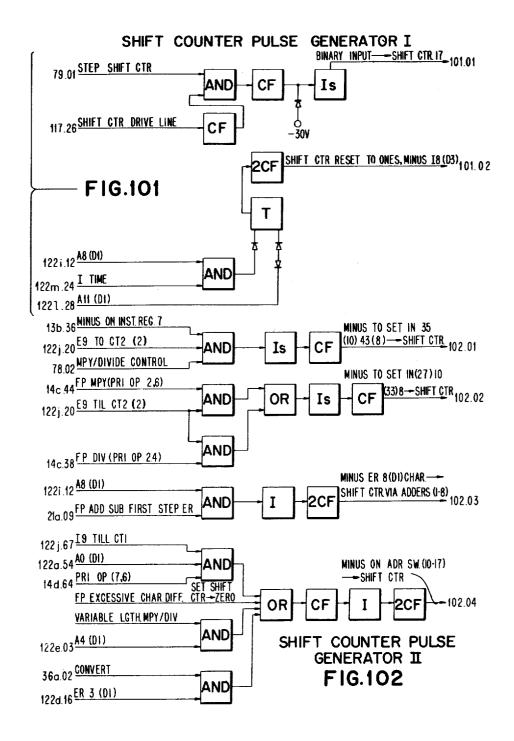

FIGURE 101 illustrates Shift Counter Plus Generator 1 in logical block form.

FIGURE 102 illustrates Shift Counter Pulse Generator

FIGURE 103 illustrates Zero Address Controls.

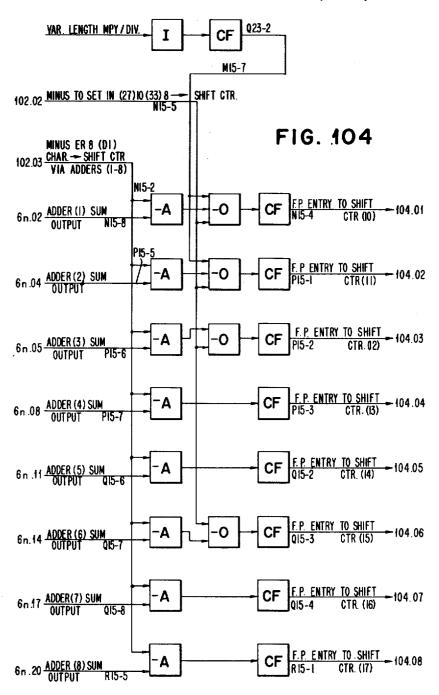

FIGURE 104 illustrates Floating Point Entry to Shift Counter 10 through 17 Controls.

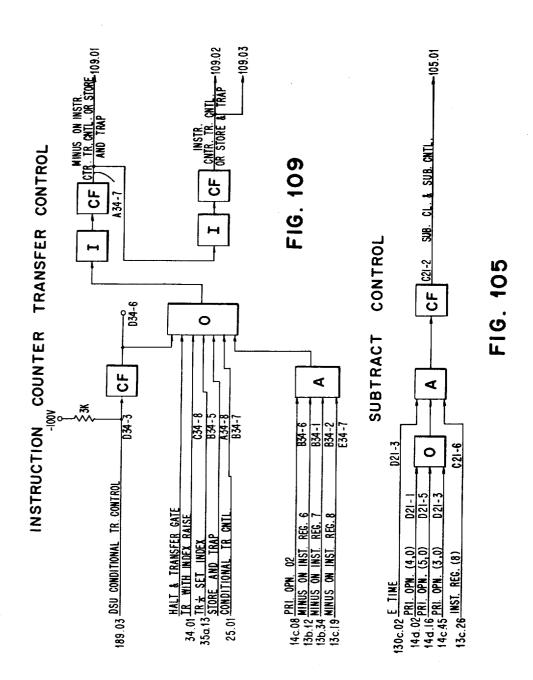

FIGURE 105 illustrates Subtract Control in logical 30 block form.

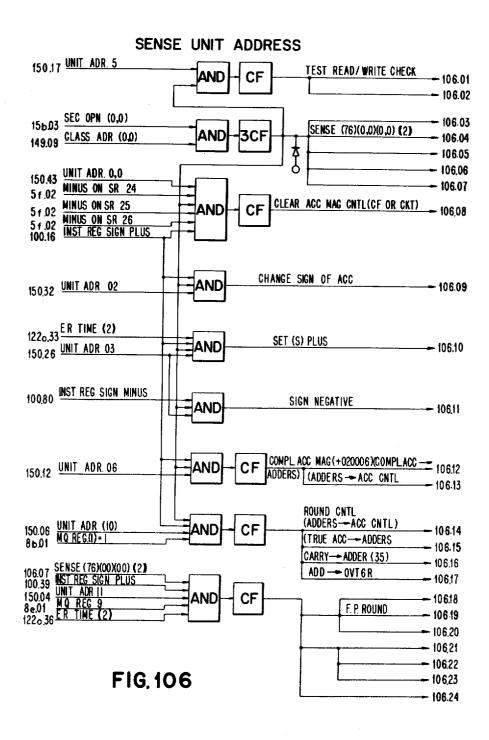

FIGURE 106 illustrates Sense Unit Address in logical block form.

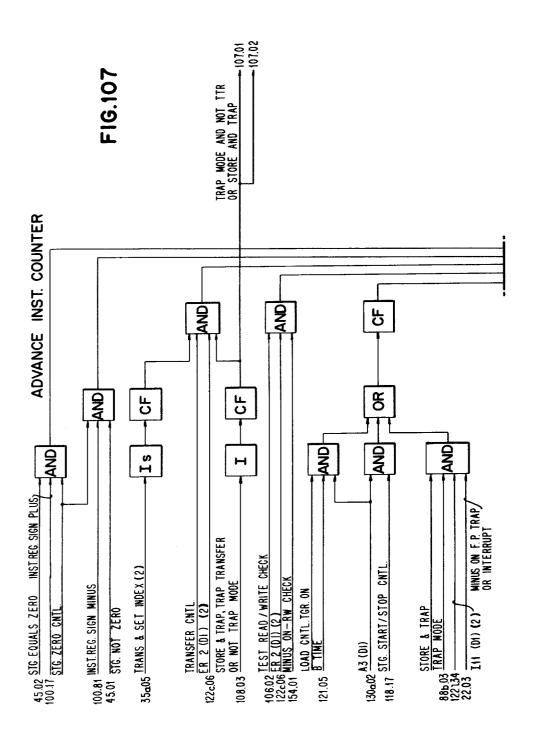

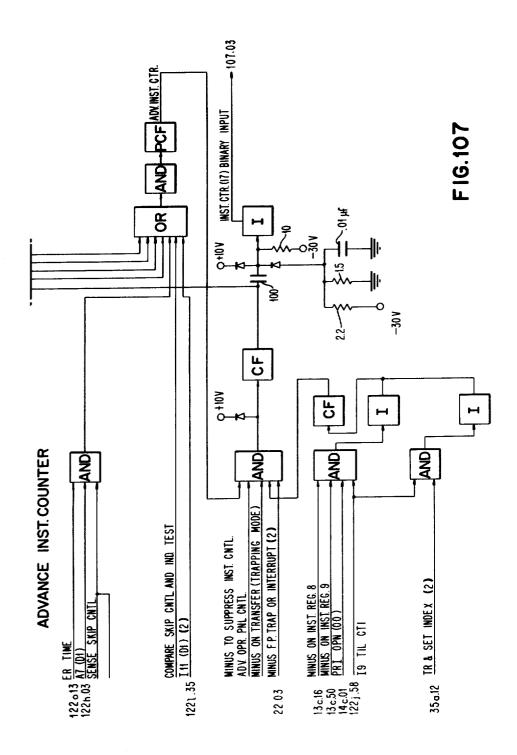

FIGURE 107 (2 sheets) illustrates Advance Instruction Counters in logical block form.

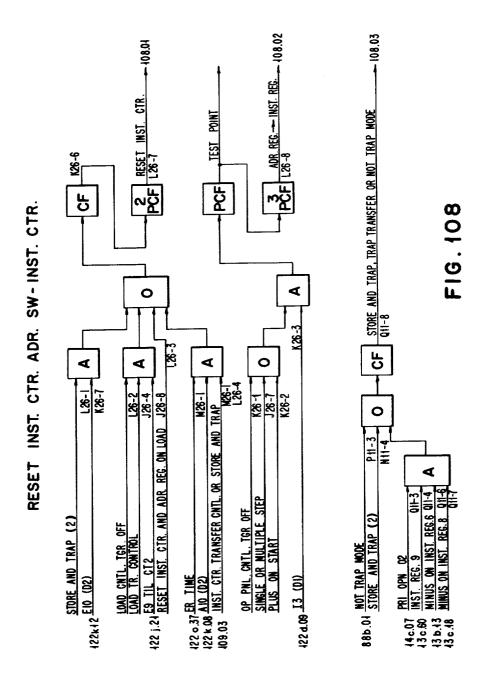

FIGURE 108 illustrates Reset Instruction Counter Address Switch to Instruction Counter Control in logical block form.

FIGURE 109 illustrates Instruction Counter Transfer Control in logical block form.

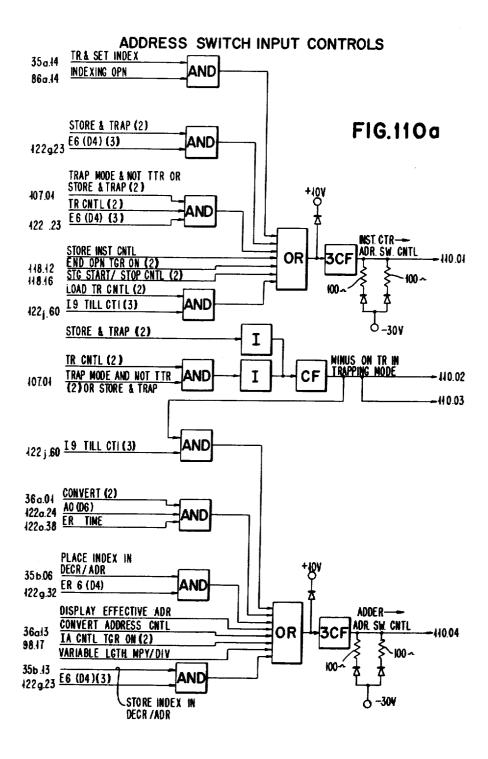

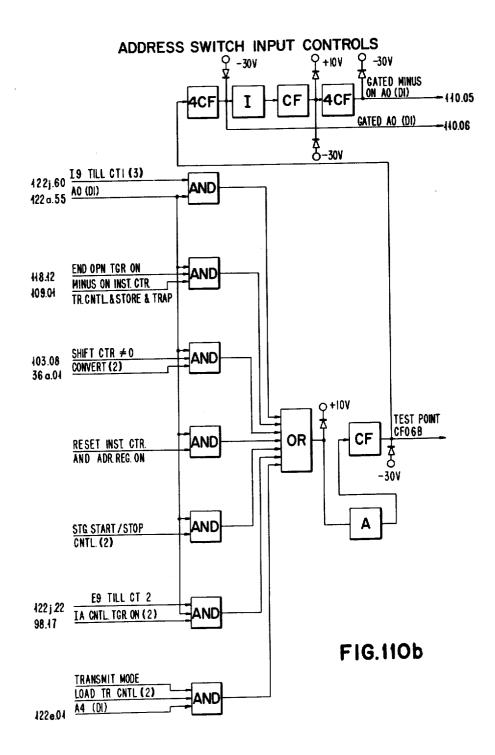

FIGURES 110a and b illustrate Address Switch Input Controls in logical block form.

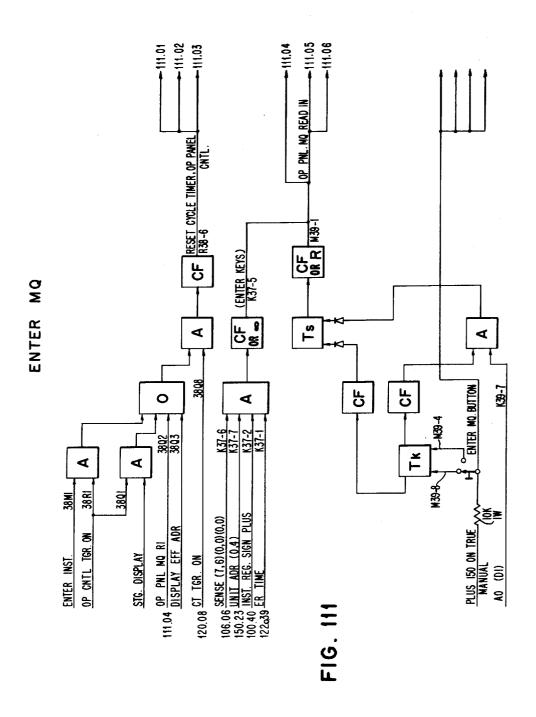

FIGURE 111 illustrates Enter MQ Control in logical block form.

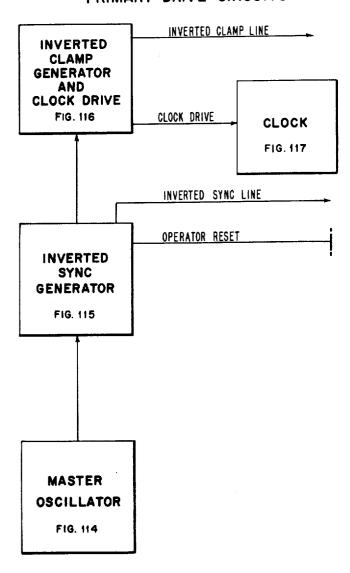

FIGURE 112 illustrates the Primary Drive Circuits.

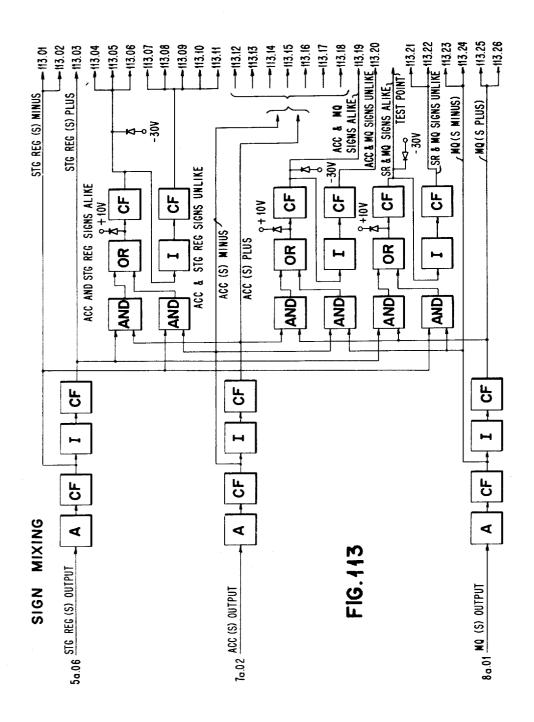

5 FIGURE 113 illustrates a Sign Mixing Controls.

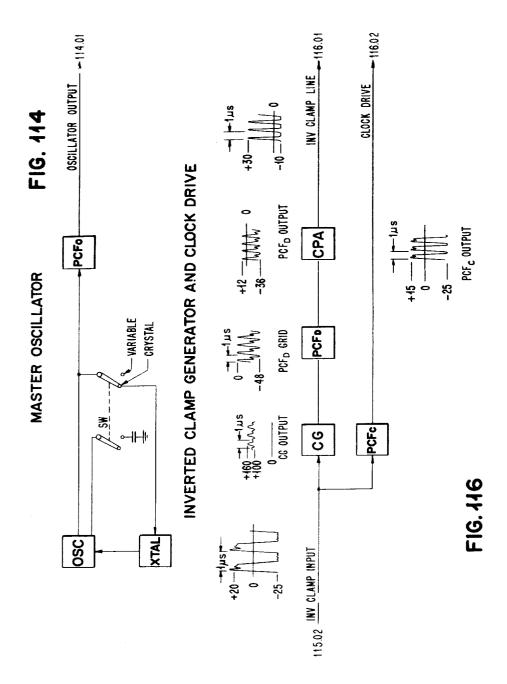

FIGURE 114 illustrates the Master Oscillator.

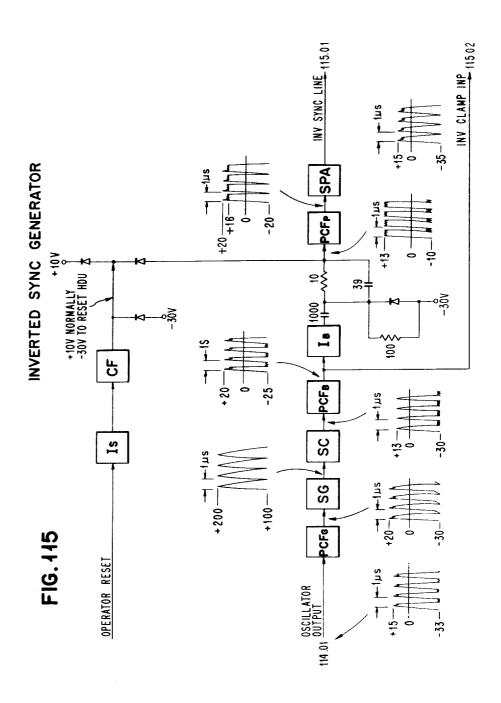

FIGURE 115 illustrates the Inverted Sync Generator. FIGURE 116 illustrates the Inverted Clamp Generator and Clock Drive.

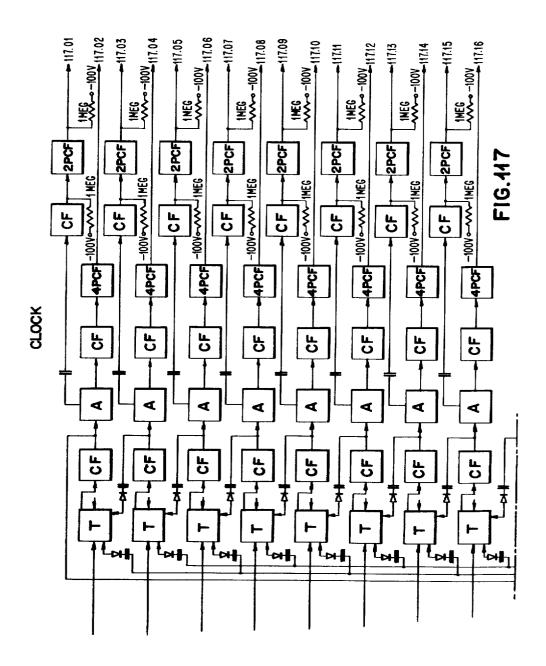

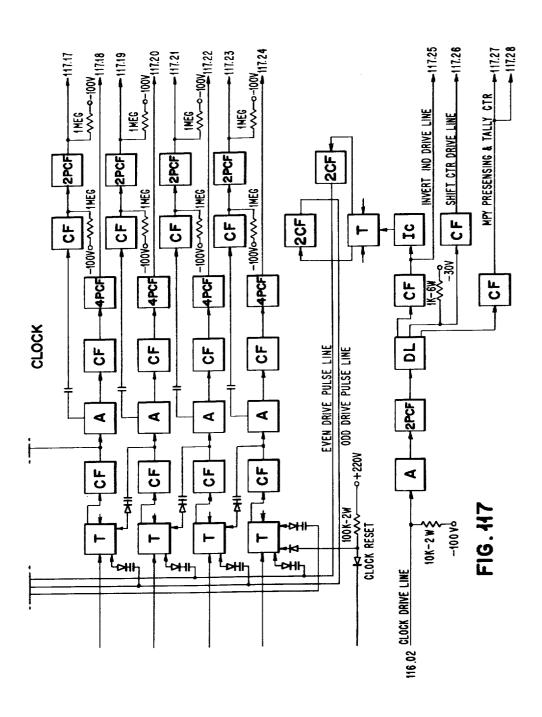

FIGURE 117 (2 sheets) illustrates the Clock.

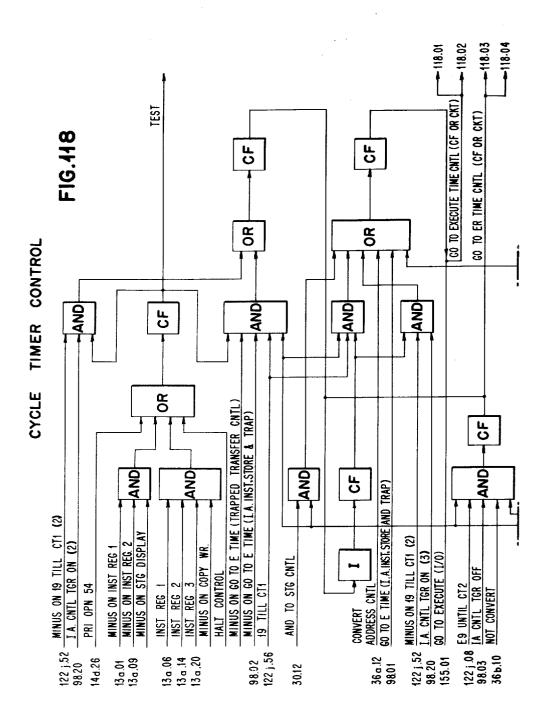

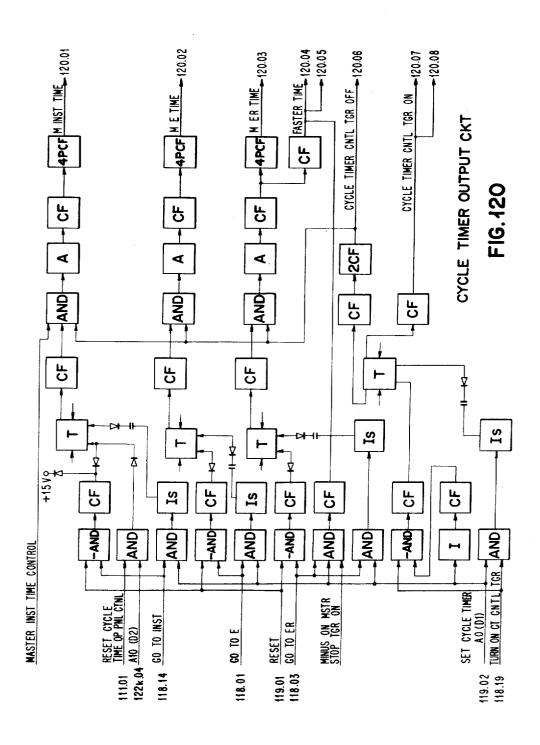

FIGURE 118 (2 sheets) illustrates Cycle Timer Control.

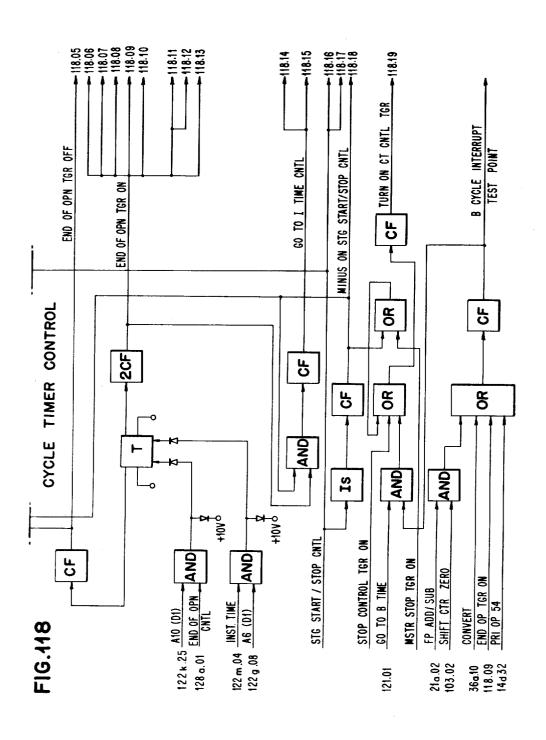

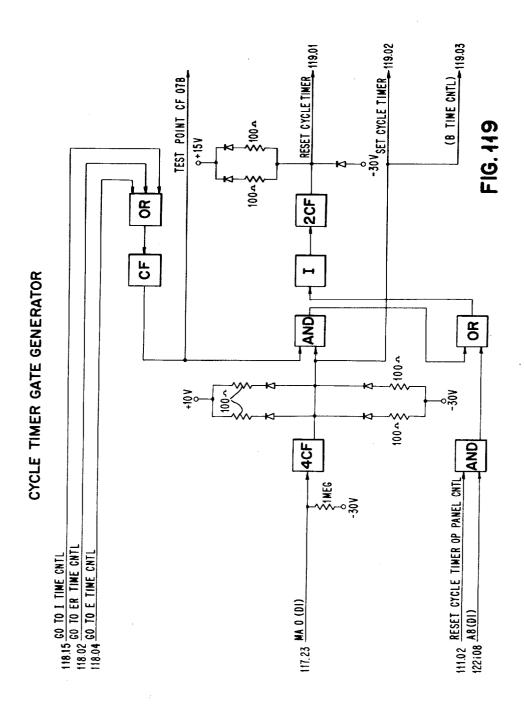

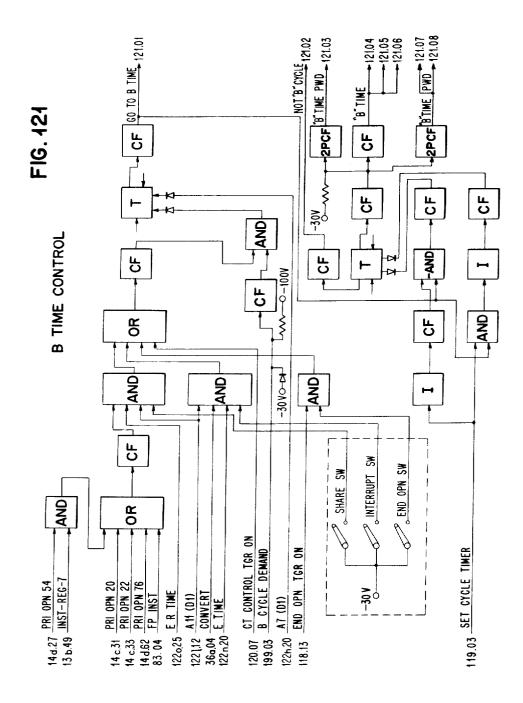

FIGURE 119 illustrates Cycle Timer Gate Generator. FIGURE 120 illustrates Cycle Timer Output Circuit. FIGURE 121 illustrates B Time Control.

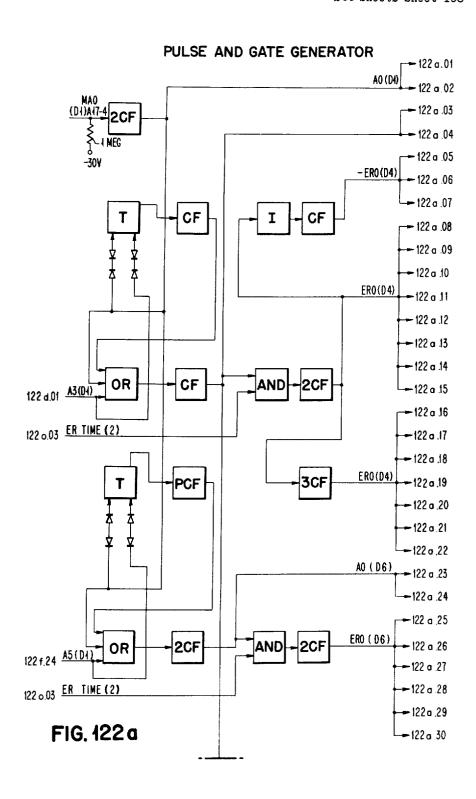

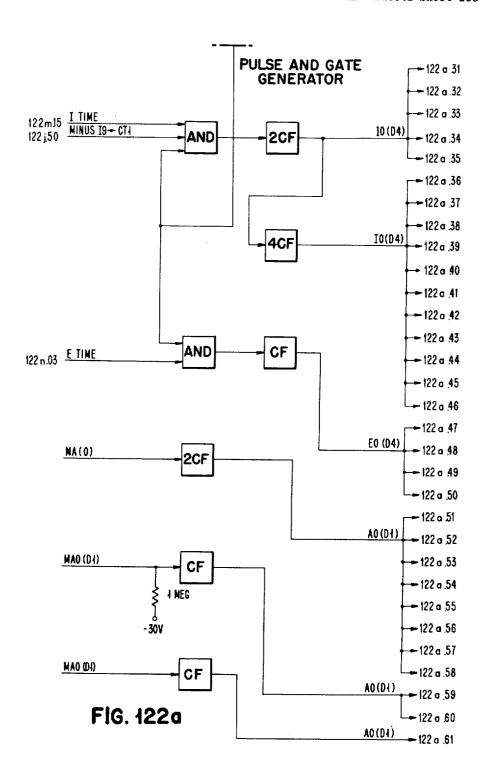

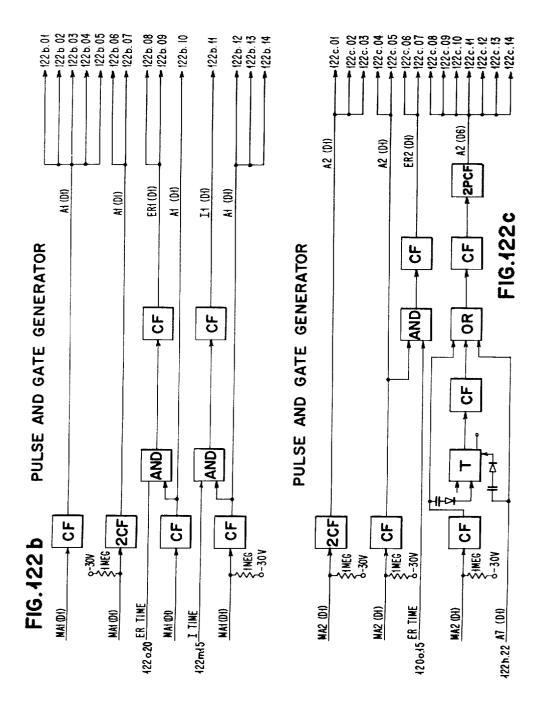

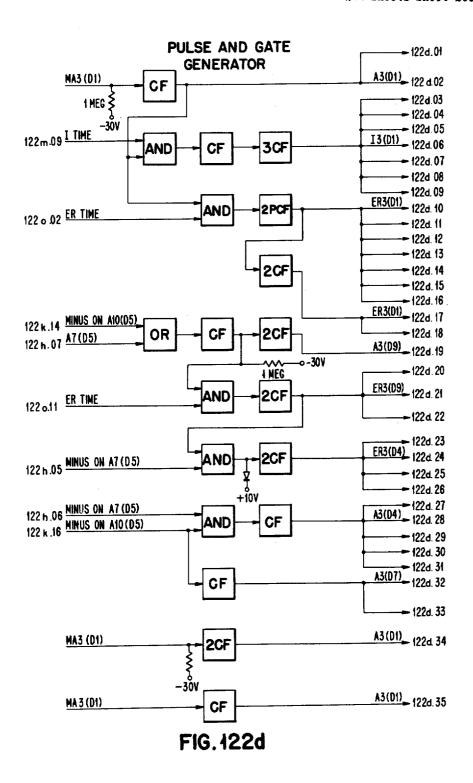

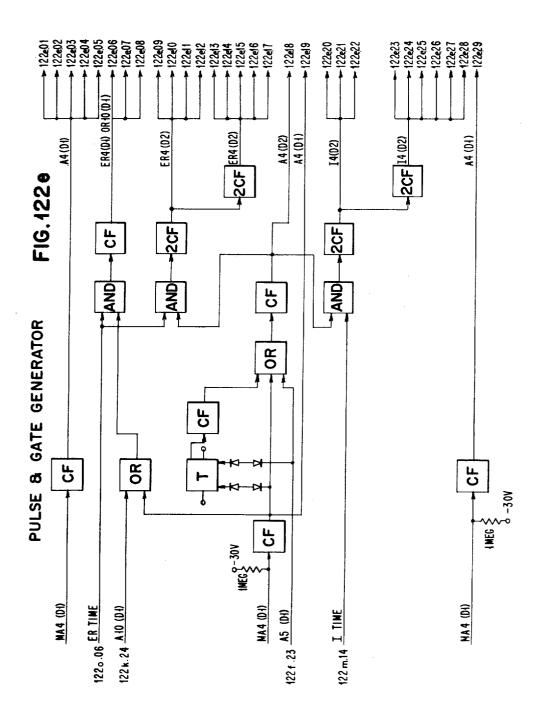

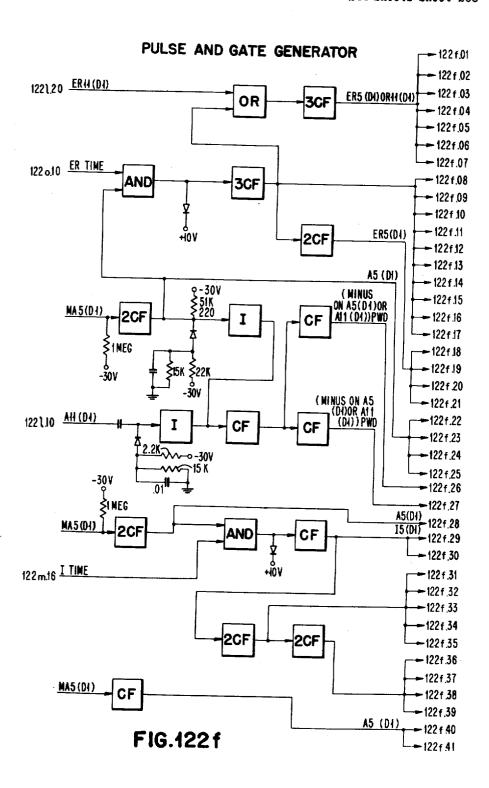

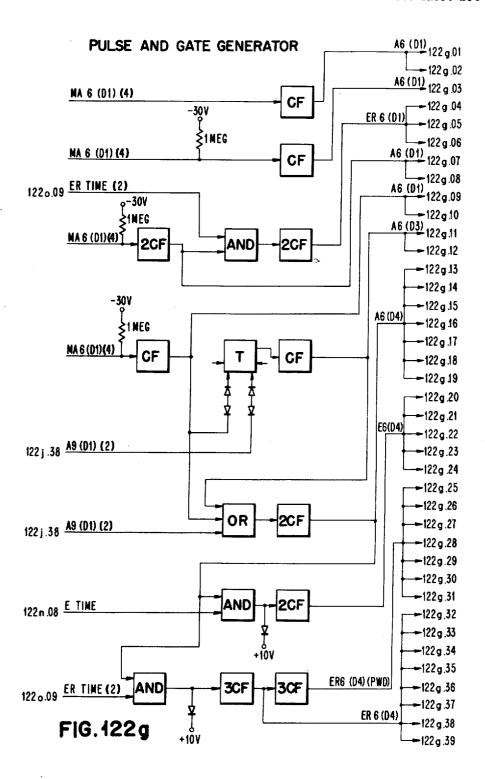

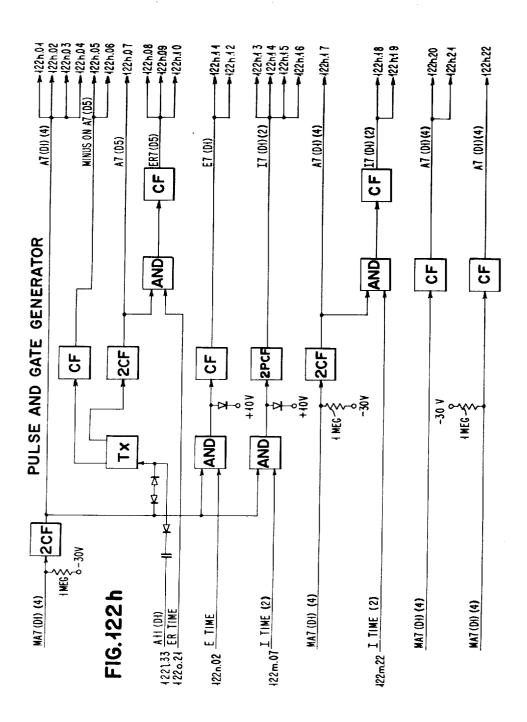

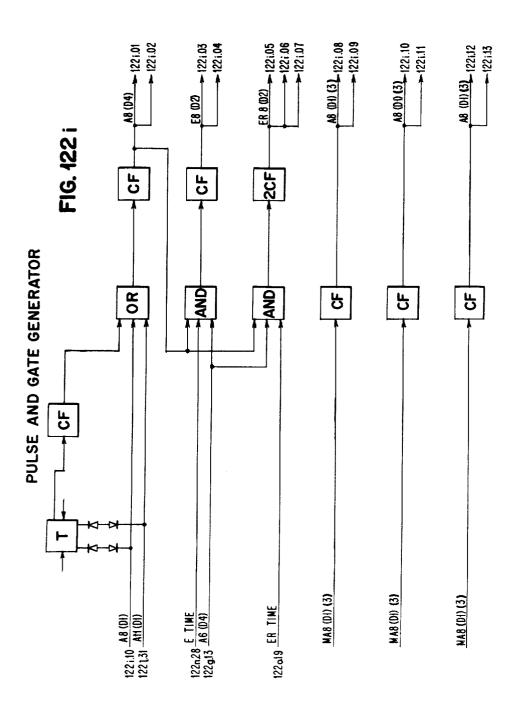

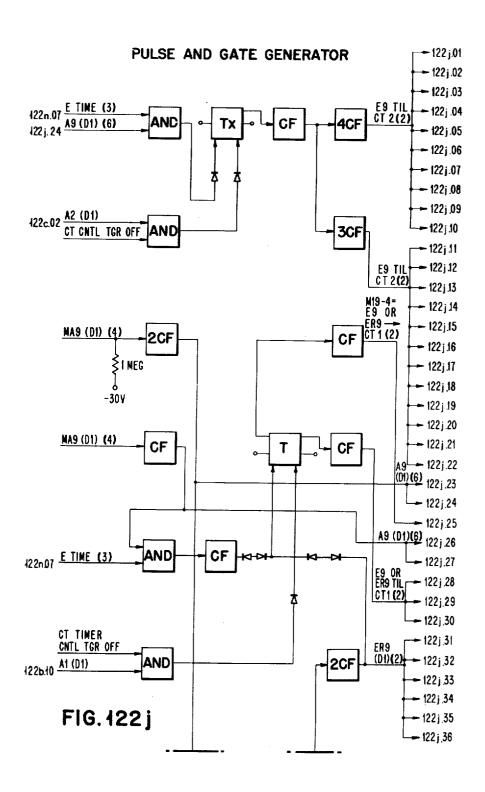

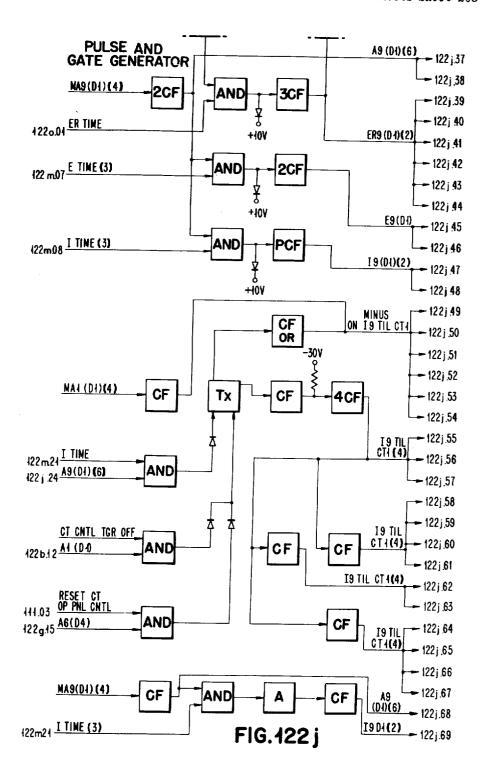

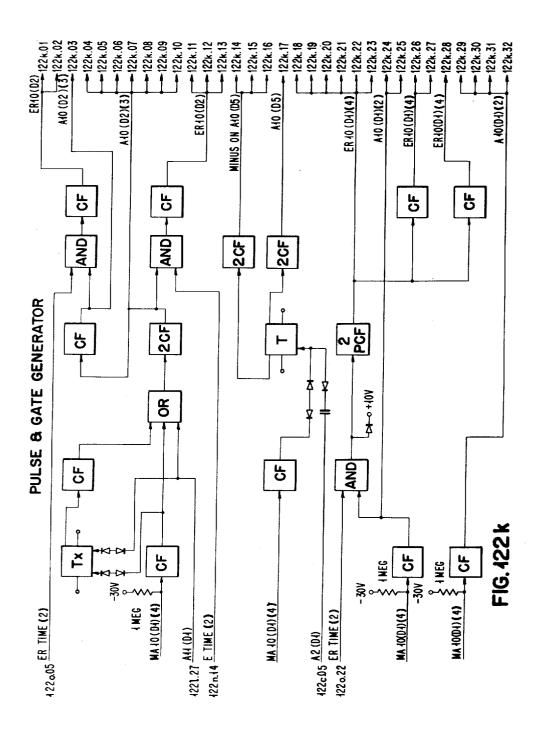

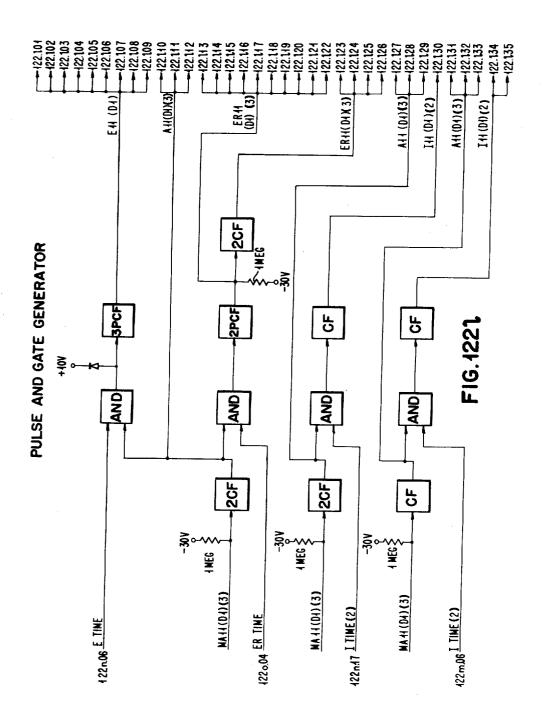

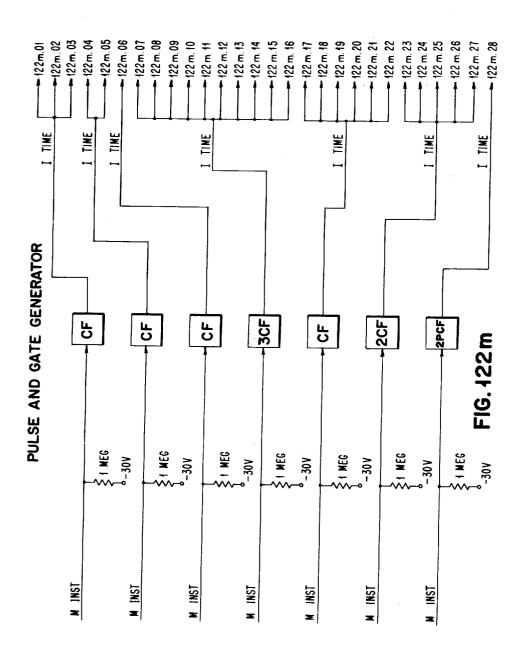

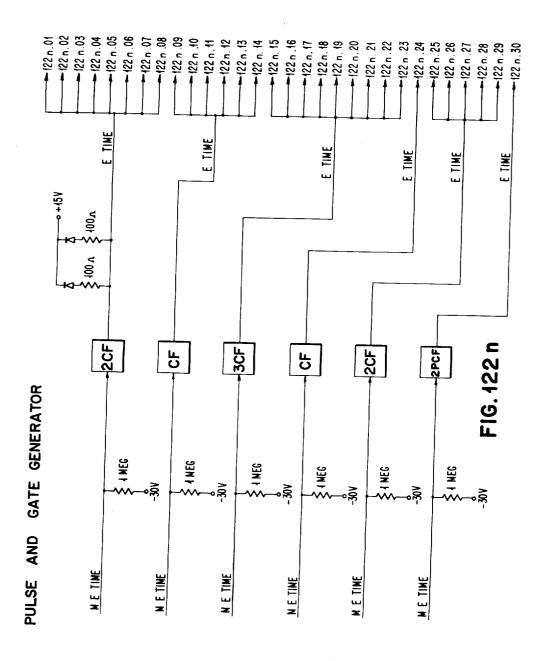

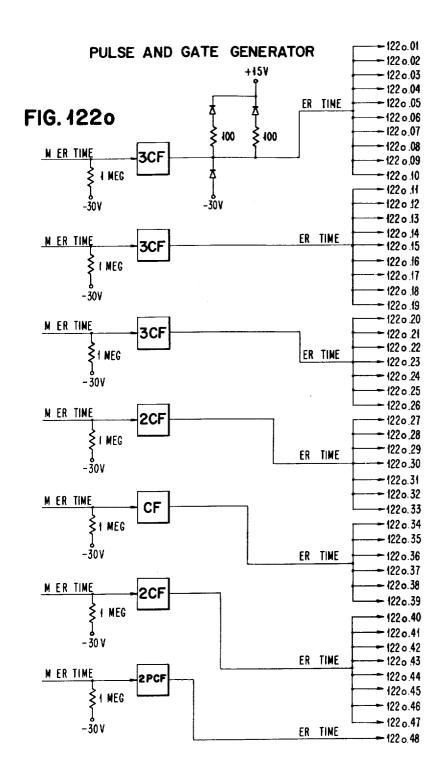

FIGURES 122a (2 sheets) to p illustrate Pulse and Gate Generator Controls.

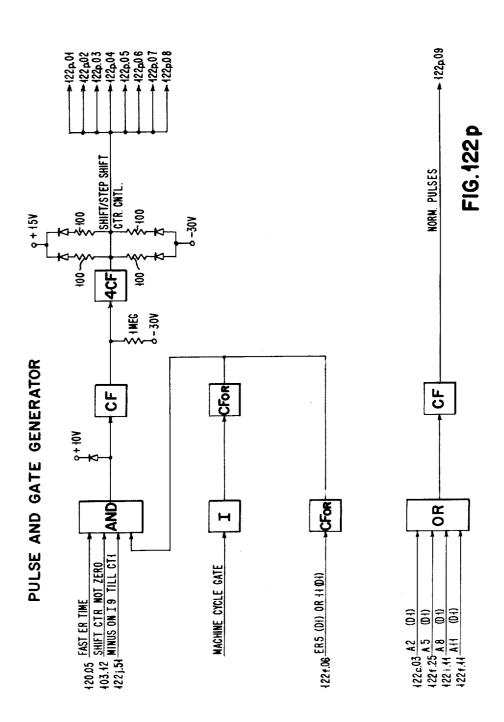

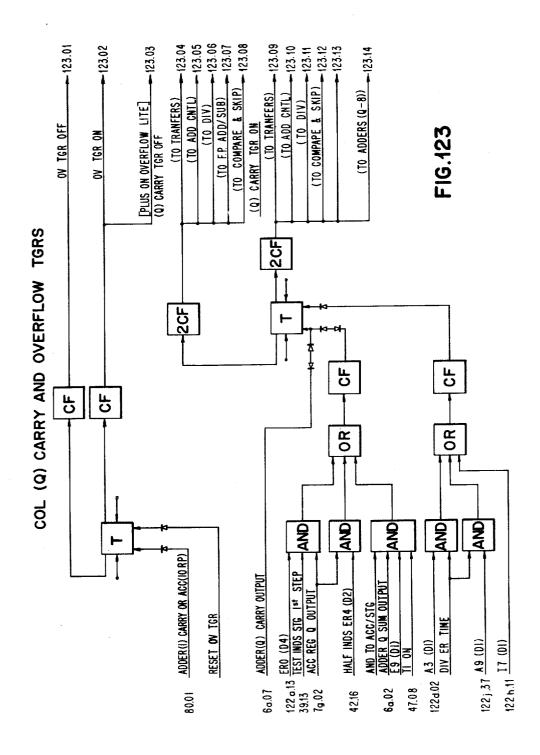

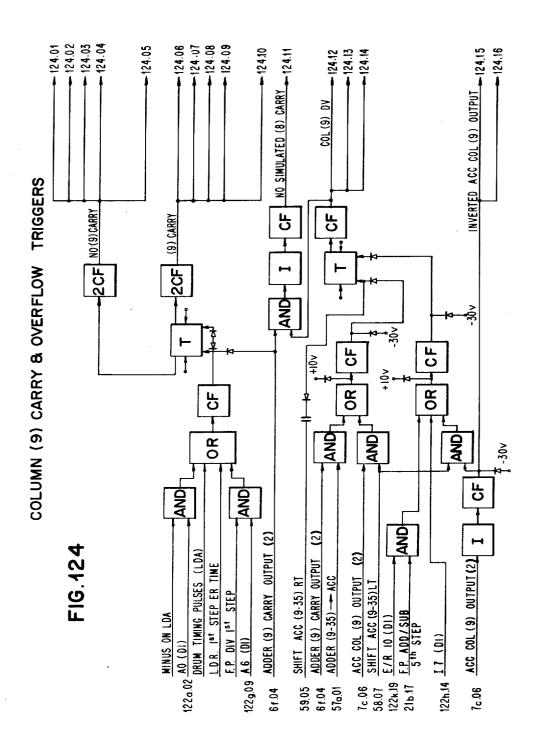

FIGURE 123 illustrates Column Q Carry and Overflow Triggers.

FIGURE 124 illustrates Column 9 Carry and Overflow Triggers.

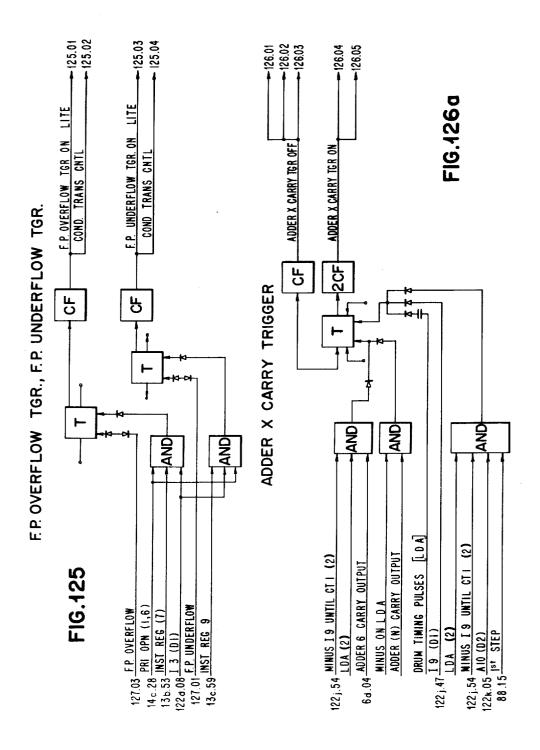

FIGURE 125 illustrates Floating Point Overflow Trigger and Floating Point Underflow Trigger.

FIGURE 126a indicates Adder X Carry Trigger.

FIGURE 126b illustrates Divide Check Trigger.

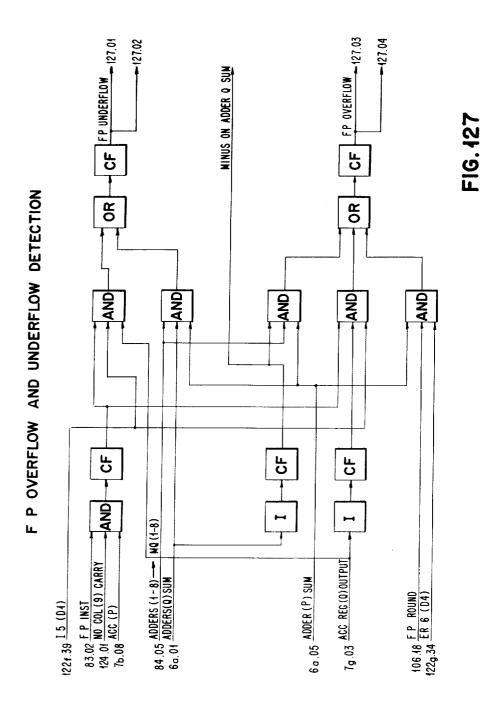

FIGURE 127 illustrates Floating Point Overflow and Underflow Detection.

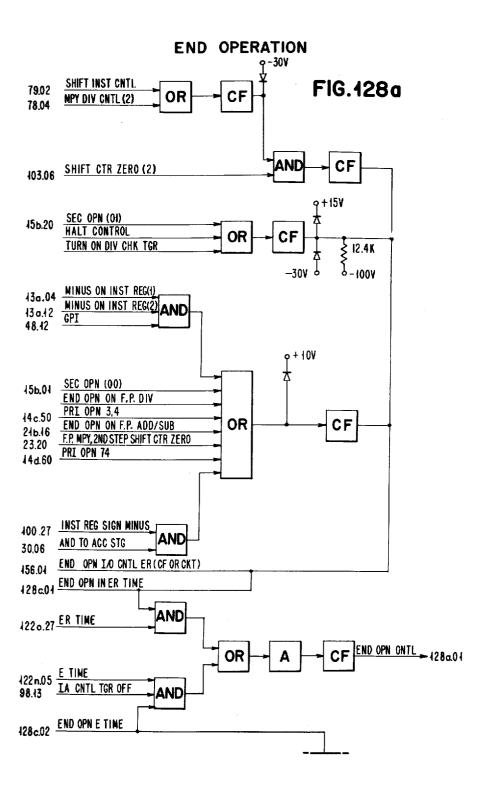

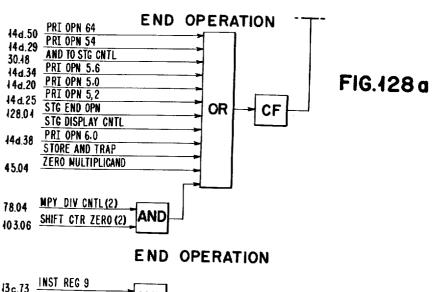

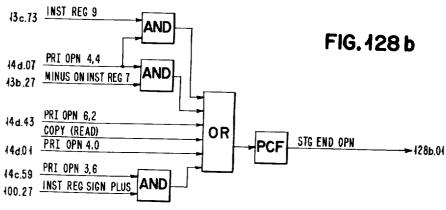

FIGURES 128a (2 sheets), b and c illustrate End Operation Control.

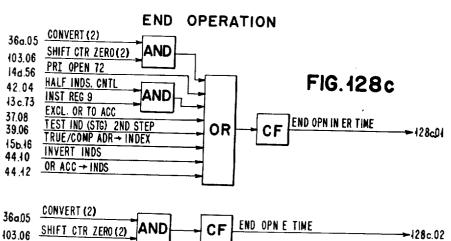

70 FIGURE 129a and b illustrates the Storage Address Register.

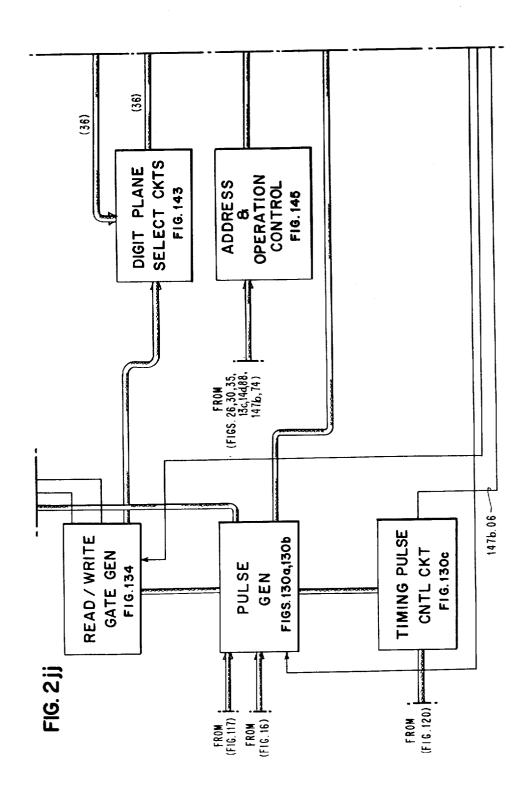

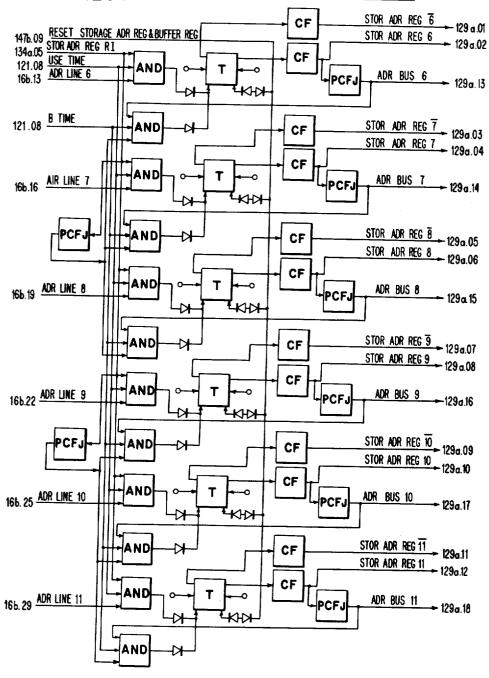

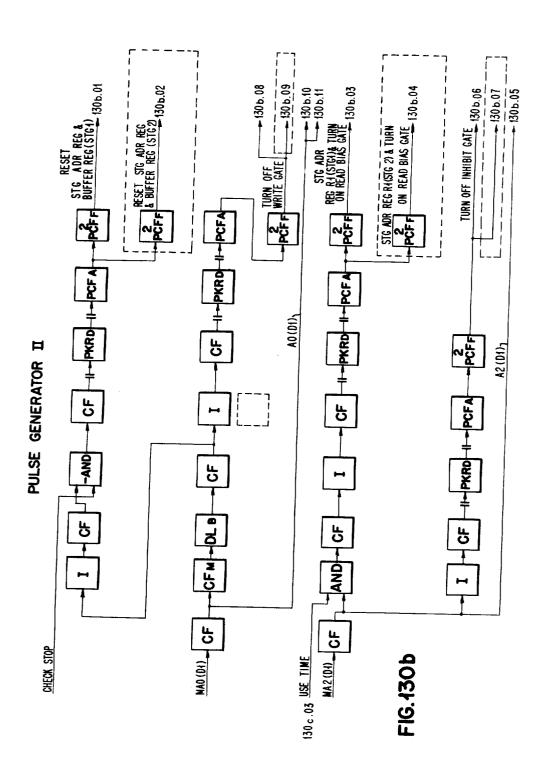

FIGURES 130a and b illustrate the Pulse Generator I and II.

FIGURE 130c illustrates Timing Pulse Control Cir-75 cuits.

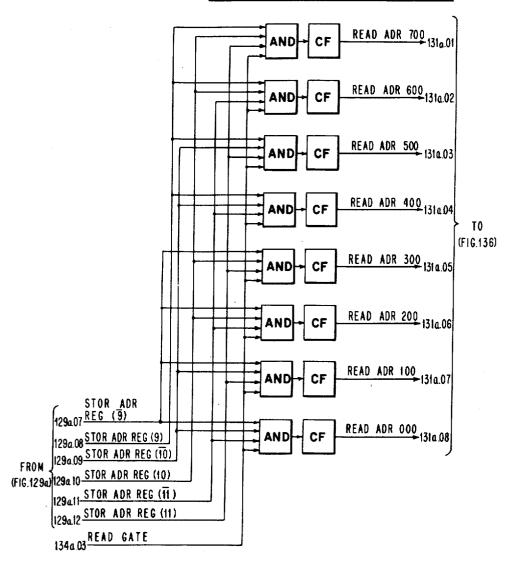

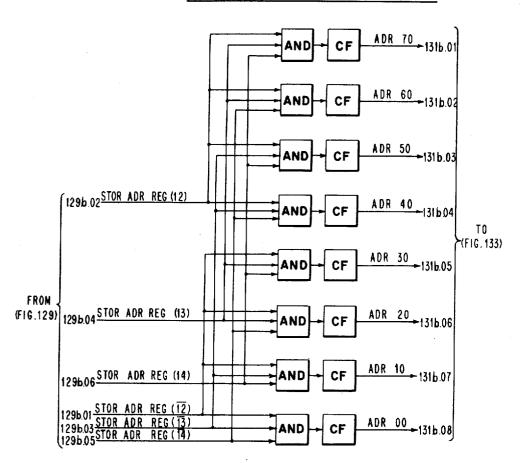

FIGURES 131a and b illustrate the Address Decoder Circuit.

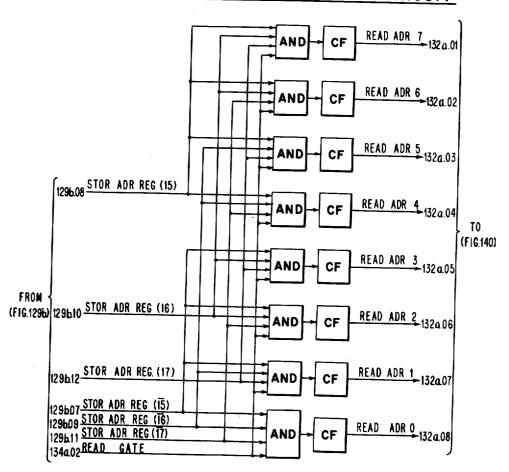

FIGURES 132a and b illustrate the Address Decoder Circuit.

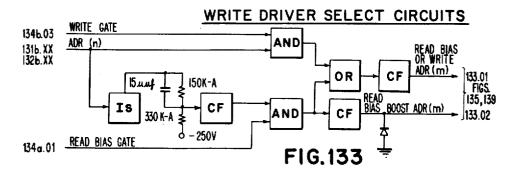

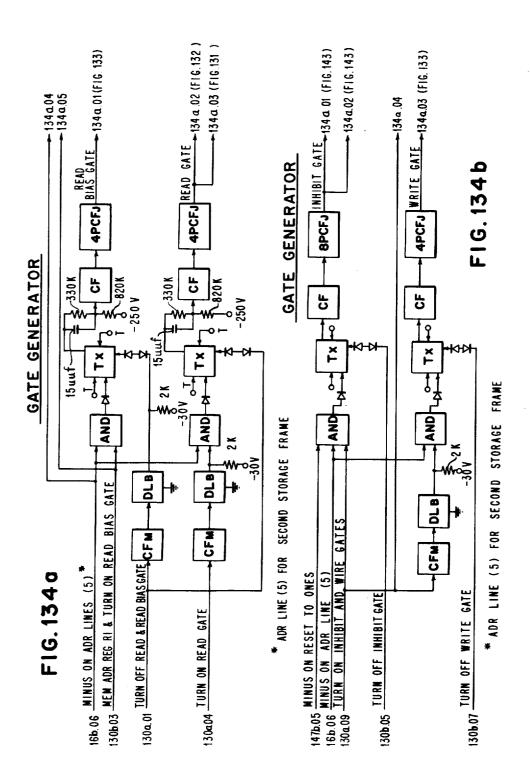

FIGURE 133 illustrates Write Driver Select Circuits. 5 FIGURE 134a and b illustrate Gate Generator.

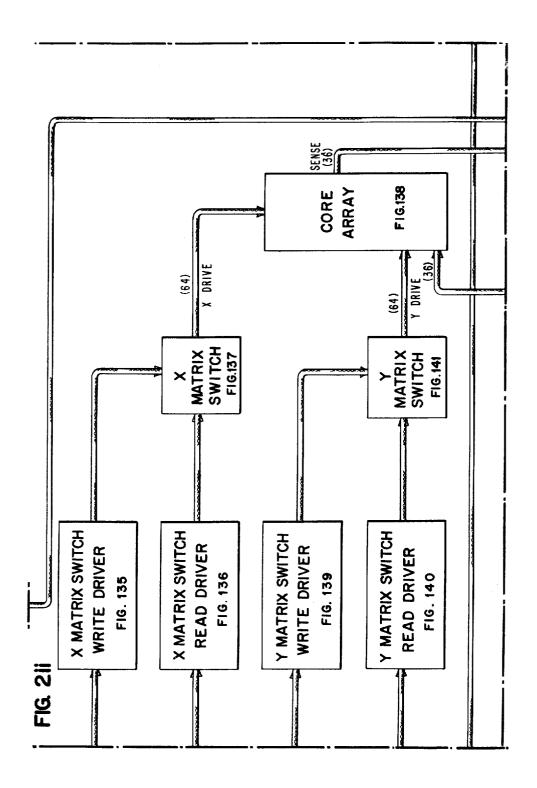

FIGURE 135 illustrates the X Matrix Switch Write Driver.

FIGURE 136 illustrates the X Matrix Switch Read Driver.

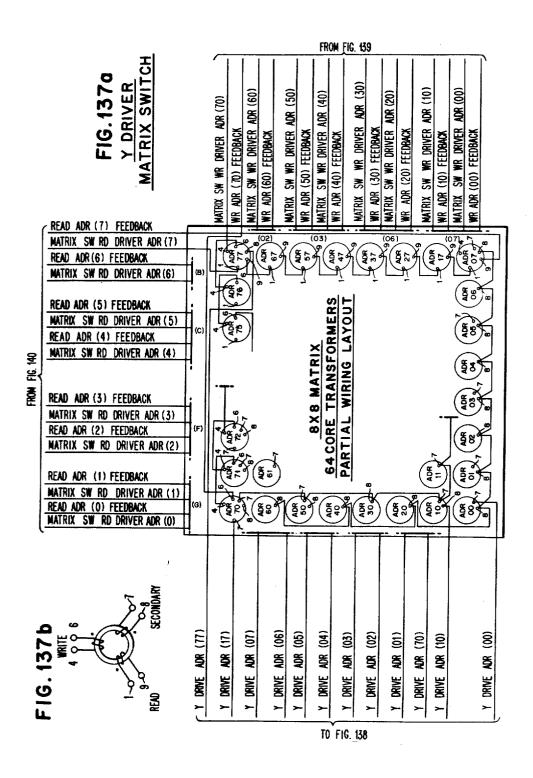

FIGURES 137a illustrates the Y Driver Matrix Switch

FIGURE 137b illustrates diagrammatically a Core with certain of its Control Windings.

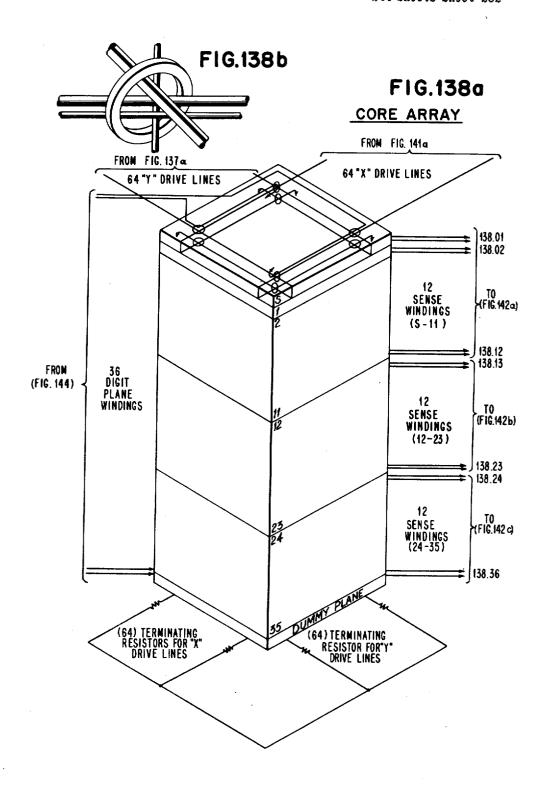

FIGURE 138a illustrates diagrammatically the Core 15 Array Layout.

FIGURE 138b illustrates in isometric, a Core with Windings.

FIGURE 139 illustrates the Y Matrix Switch Write Driver.

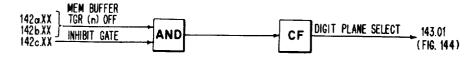

FIGURE 140 illustrates Y Matrix Switch Read Driver. FIGURE 141a illustrates the X Driver Matrix Switch

FIGURE 141b illustrates diagrammatically a Core with certain of its Control Windings is in FIG. 137b.

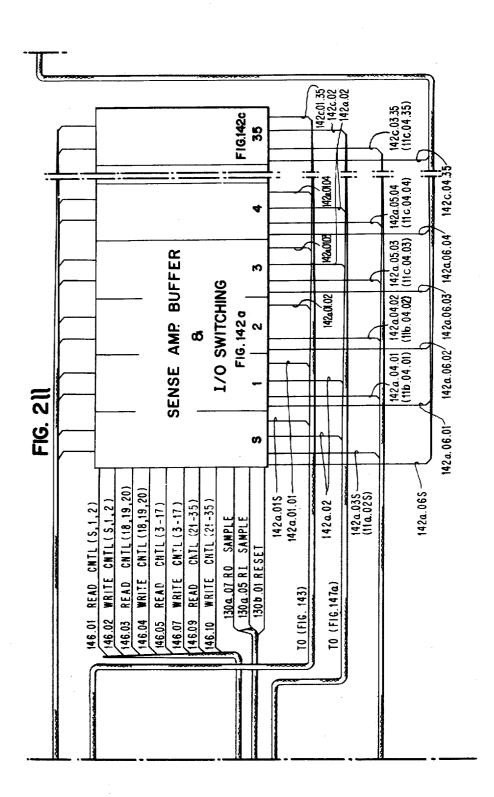

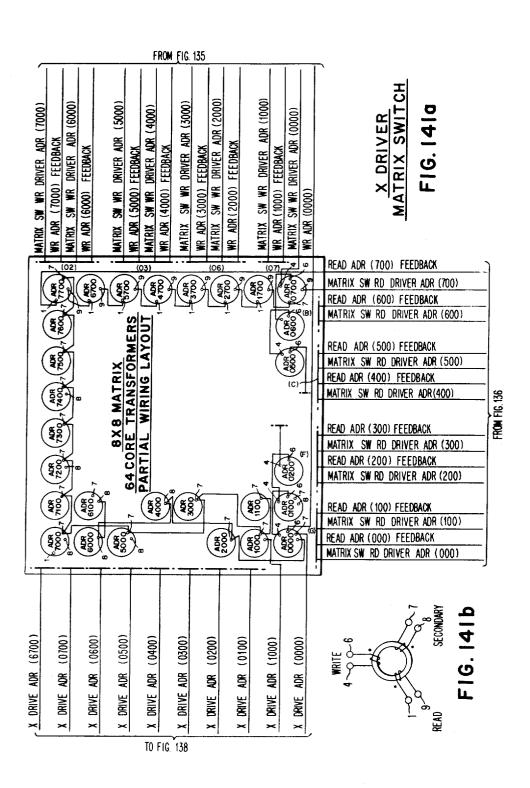

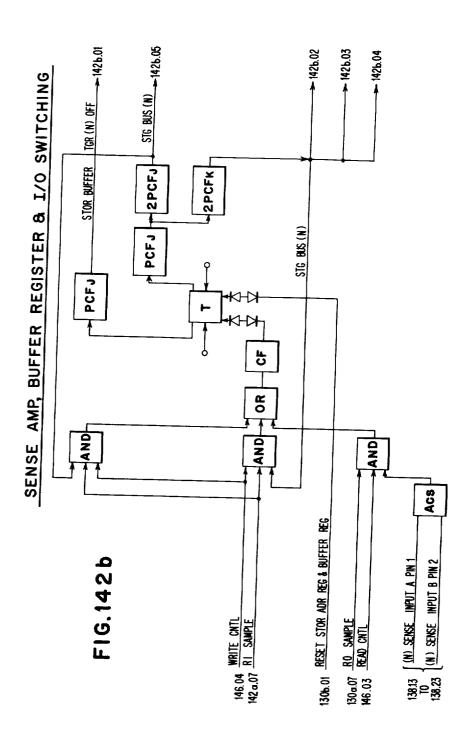

FIGURES 142a, b, and c illustrate the Sense Amplifier, Buffer Register and I/O Switching.

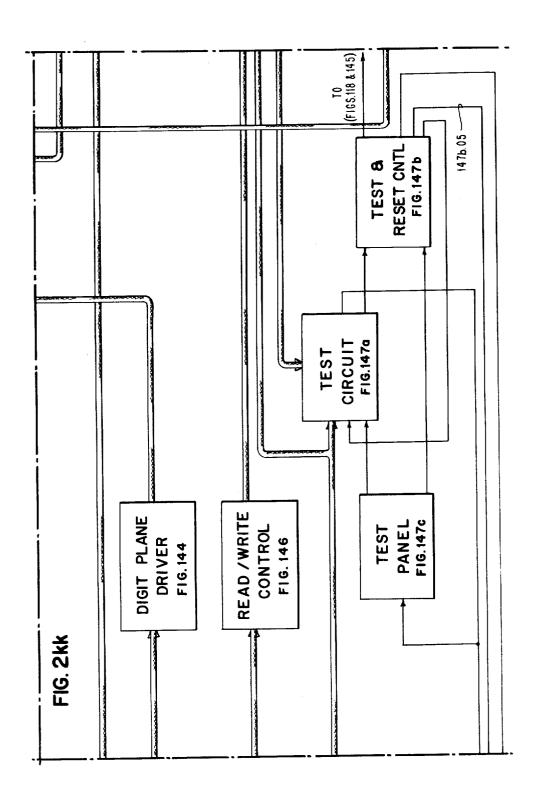

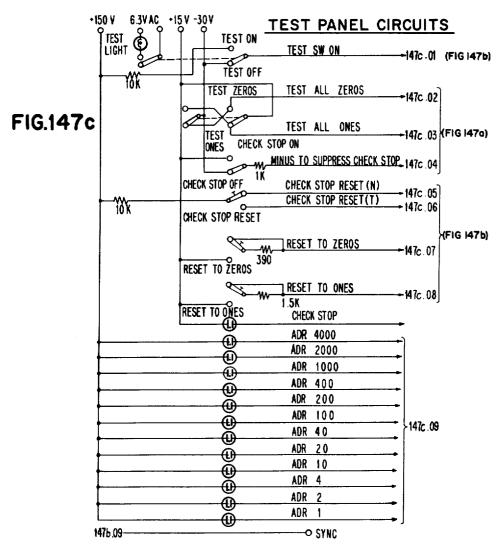

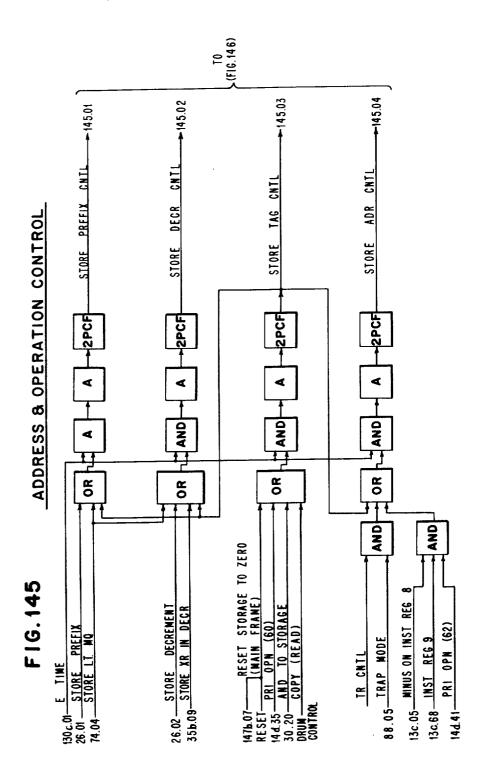

FIGURE 143 illustrates the Digit Plane Select Circuits. FIGURE 144 illustrates the Digit Plane Driver Circuits. FIGURE 145 illustrates the Address and Operation 30 Control.

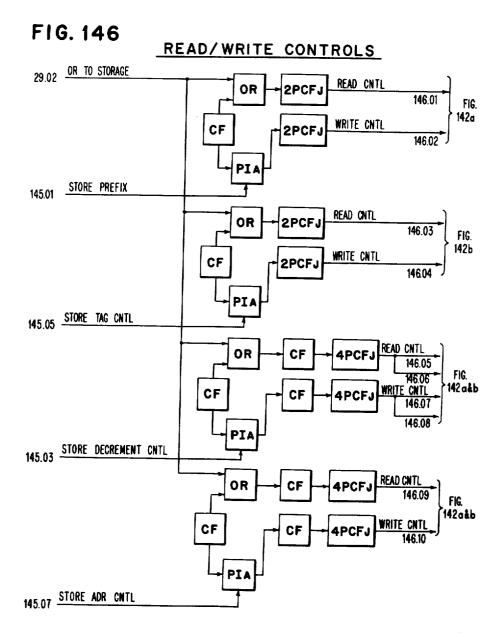

FIGURE 146 illustrates the Read/Write Controls.

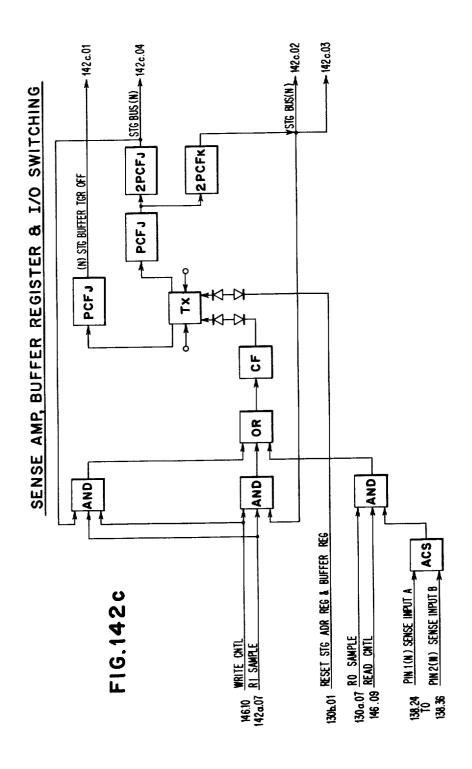

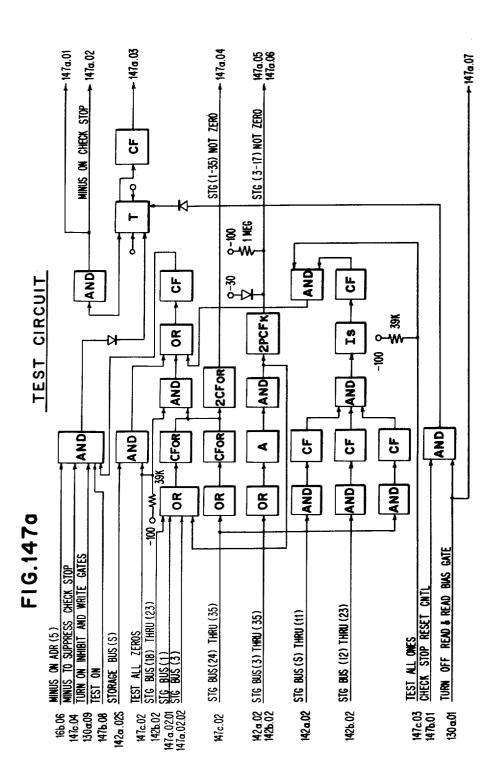

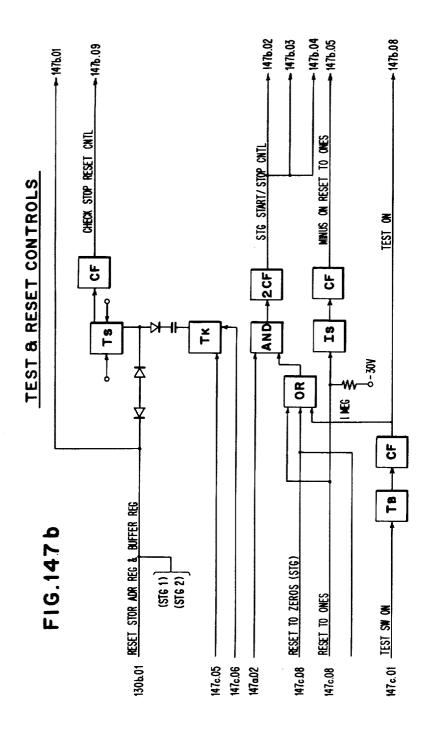

FIGURES 147a, b, and c illustrate Test Circuits, Test and Reset Controls and the Test Panel Circuits.

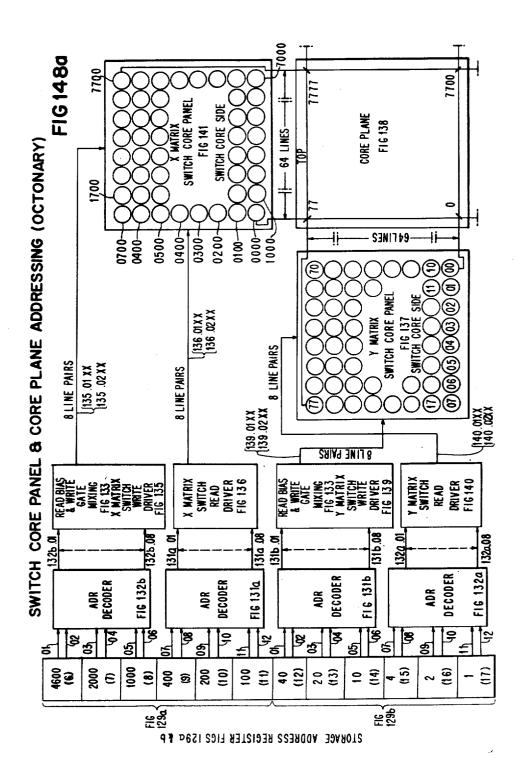

FIGURE 148a illustrates Switch Core Panel and Core 35 Plane Addressing (Octonary).

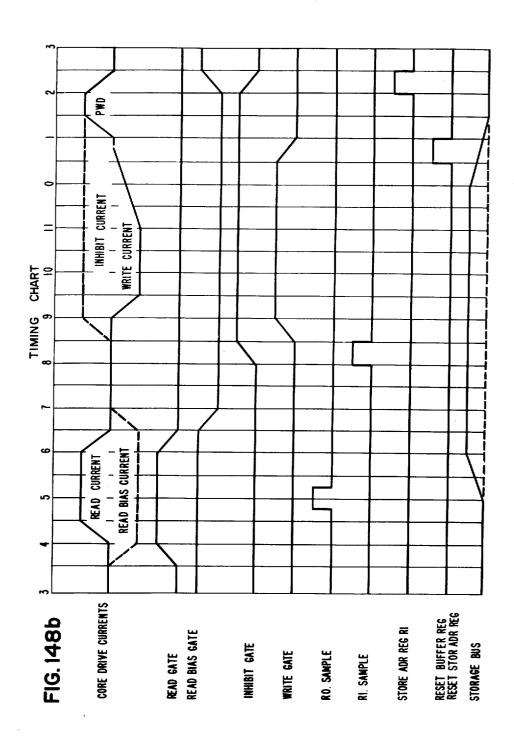

FIGURE 148b is a timing chart illustrating the Timing of Magnetic Core Storage in sequence for one cycle from 3 time of a first cycle until 3 time of a second cycle.

The convention employed in numbering lines in the 40 logical block diagrams is as follows: from left to right, the first numbers and the letter, if any, to the period or point is the figure number from which the line originated; the next two numbers to the second point refer to the "output" lines (generally numbered according to their positions on the sheet from top to bottom); and the last two numbers, when used, refer to the numerical position of the line with the word S, 1 through 35. Each input line in the block diagram bears the number derived from its point of origin. In the composite drawings, data flows generally into the block at the top and out of the block at the bottom, and control lines which cause the movement of data to enter the block from the left.

In FIGURE 1, there is shown a Central Processing Unit of a high speed Data Processing system which is controlled by an internally stored program with instructions of the single address type which direct the machine to execute instructions at the rate of about 20,000 per second. The funcions of transferring data in and out of the Central Processing Unit from Input-Output devices, Magnetic Core Storage, Magnetic Drum Storage, are controlled by the stored program as well. Internally, the Central Processing Unit operates in the binary number system, but the Input-Output number system may be those used in punched card systems, the decimal system, or the binary coded decimal (BCD) system to name a few. Many of the basic devices of the Central Processing Unit, shown generally in FIGURE 1, and more specifically in FIGURE 2, assume two stable states and are well suited is indicative of a binary "one" and the other state is indicative of a binary "zero." The basic unit of information, the Word, consists of thirty-six binary digits and may be alphabetic, numeric, symbolic, an instruction, or any

8

any reason. The thirty-six positions of the word are shown schematically in FIGURE 3 where S refers to the sign position, 1 refers to bit position 1, 2 refers to bit position 2 and so forth. Only when a word is interpreted as numerical data does position S have any algebraic significance. Then, with position S containing a "zero" the word is signified as positive and with position S containing a "one" the word is signified as negative. When a logical operation is performed upon a word, the word 10 is interpreted as a thirty-six bit signless number.

Individual location in Magnetic Core Storage, Magnetic Drum Unit and individual units such as Magnetic Tape Units and all other Input-Output Units are identified by systems of numerical addresses, as described more fully in copending application, Serial No. 705,447, filed December 26, 1957. By means of a number contained in the Address part of the Instruction, it is possible to refer to the information contained in any location in Magnetic Core Storage or any Input-Output Unit of the system.

In FIGURE 1, the Central Processing Unit has data portions which comprise a thirty-six order Storage Register 1.01 comprising thirty-five orders and a sign order, a thirty-six order Adder 1.03 plus one overflow order, an Accumulator Regiser 1.05 of thirty-five orders plus two overflow orders P and Q and a sign order S, a Multiplier Quotient Register 1.07 comprising thirty-five orders and a sign order, three Index Registers 1.09 A, B and C of fifteen orders and their associated Index Register controls, an Indicator Trigger Register 1.12 of thirty-six orders 0 through 35, Storage Bus Switching 1.14 of thirty-six orders connected to a Storage Bus 1.16 of thirty-six orders, the latter being connected to Magnetic Core Storage, and Operator's Entry Keys 1.18 of thirty-six orders. Associated with the data portion previously described is an Instruction Register 1.20 of eighteen positions S, 1 through 17, an Address Register 1.22, and in Instruction Counter 1.24 with related Storage Address Controls 1.26. Information may be placed in Core Storage from either the Accumulator Register 1.05, the Multiplier Quotient Register 1.07, or the Indicator Register 1.12. It is a function of the Sstorage Bus Switches 1.14 to switch the contents of the Accumulator Register, the MQ Register, or the Indicator Register onto the Storage Busses 1.16 in accordance with the execution of certain instructions which require that information be located in Storage.

The Central Processing Unit and Core Storage of the present invention may be employed in a data processing system whihe includes Data Synchronizers, Tape Control Units, Tape Drive Units, Printers, Perforating machines and Readers. The Data Synchronizers are used to control the flow of information from the input-output devices such as Tape Control Units, Tape Drive Units and Readers to Core Storage and to control the flow of information from Core Storage to the Tape Units, Printers, and Perforating machines. The Tape Control Unit controls all operations to be executed by the Tape Drive Units and assembles and disassembles 36 bit words as required in the transmission of data through the system.

A detailed description of general operations of a computer of this class may be performed in response to wellknown instructions is found in copending application Computer for 701, Serial No. 419,642, Haddad et al., filed March 30, 1954. Certain arithmetic, logical, and other operations may be performed by the device of the present invention in response to instructions tabulated immediately below in accordance with the principles set forth in Manual of Operations, Electronic Data Processing Machines, Type 704, Form No. 24-6661, copyright 1954, 1955, and printed in the U.S.A. by International to the binary system of notation where one specified state 70 Business Machines Corporation, the assignee of this application. The operation codes specify the particular operation to be performed and are tabulated in numeric form below. However, each numeric code must be translated into machine language which is in the binary code. pattern of thirty-six bits desired by the programmer for 75 For example, 0361 (octal) is expressed as 000011110001.

| Add and Carry Logical Word.   ACL+0361     Add   ADD+0400     Add Magnitude.   ADD   Hou     Add Magnitude.   ADD   Hou     Accumulator Left Shift.   ALS+0767     AND to Accumulator Right Shift.   ARS+0771     Backspace Tape.   ANS+0320     Accumulator Right Shift.   ARS+0771     Backspace Tape.   BST+0764     Clear and Add Logical Word.   CAL-0500     Compare Accumulator with Storage.   CAS+0340     Change Sin.   CHS+0760   0002     Clear and Add   CLM+0760   0002     Clear and Subtract.   CLM+0760   0000     Divide Check Test.   DCT+0760   0001     Divide or Halt.   DVH+0220     Divide or Froceed.   DVP+0221     Enter Trappling Mode.   ETM+0760   0007     Floating Add.   FDH+0240     Floating Multiply   FMP+0200     Floating Subtract.   FDH+0240     Floating Subtract.   FSB+0302     Halt and Transfer.   HTR+0000     Low Order Bit Test.   LBT+0760   0001     Low Order Bit Test.   LBT+0760   0001     Low Order Bit Test.   LBT+0760   0001     Loate Drum Address.   LDA+0460     Lordad Lordad MQ   LDQ+0560     Lordad Left.   LGL-0763     Long Left Shift.   LLS+0763     Last-0765   Last-0765     Leave Trappling Mode   LTM-0760   0007     Load Index from Address.   LX +0534     Load Index from Decrement.   LXD-0534     Multiply and Round.   MPR-0200     Minus Sense.   MSE+0760     Mon Operation.   NOP+0761     OR to Accumulator.   ORA-0501     OR to Storage.   ORS-0602     Place Decrement.   PAX+0734     P-Bit Test.   PBT-0760   0001     Pasce Decrement.   SEB-0706     Round.   RND+0760   0003     Store Decrement.   STD-0763     Read Select.   RDS+0760   0003     Store Decrement.   STD-0603     Store Decrement.   ST   | Title                            | Operation Code              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------|

| Add         ADM+9401           Accumulator Left Shift         ADM+9401           Accumulator         AND to Accumulator           AND to Storage         ANS+0320           AND to Storage         ANS+0320           Accumulator Right Shift         ARS+071           Backspace Tape         BST+0764           Clear and Add Logical Word         CA1-0500           Compare Accumulator with Storage         CA8+0340           Clear Magnitude         CLM+0760         0002           Clear and Add         CLA-0500           Clear Magnitude         CLM+0760         0000           Clear and Subtract         CLS+0502         0001           Complement Magnitude         CDM+0760         0002           Clear and Subtract         CLS+0502         0001           Complement Magnitude         CDM+0760         0002           Divide or Halt         DVH+0220         DVH+0220           Divide or Froceed         ETM+0760         0007           Floating Divide or Proceed         FDH+0241           Floating Subtract         FSB+0302           Halt and Transfer         FTR-0420           Halt and Transfer         HTR-0420           Floating Subtract         BT-0760                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Add and Carry Logical Word       | ACL+0361                    |

| AND to Storage.  ANS +0820 Accumulator Right Shift.  Backspace Tape.  Clear and Add Logical Word. Compare Accumulator with Storage. Clear and Add. Clear Accumulator with Storage. Clear and Add. Clear Accumulator with Storage. Change Sign. Clear and Add. Clear Accumulator with Storage. Clear and Add. Clear Accumulator. Clear and Subtract. CLS+0500 Clear and Subtract. CLS+0500 Compiement Magnitude. COM+0760. Clear Magnitude. COM+0760. Clear Accumulator. COMPIEMENT COMPIE | Add Magnitude                    | ADD+0400                    |

| AND to Storage.  ANS +0820 Accumulator Right Shift.  Backspace Tape.  Clear and Add Logical Word. Compare Accumulator with Storage. Clear and Add. Clear Accumulator with Storage. Clear and Add. Clear Accumulator with Storage. Change Sign. Clear and Add. Clear Accumulator with Storage. Clear and Add. Clear Accumulator. Clear and Subtract. CLS+0500 Clear and Subtract. CLS+0500 Compiement Magnitude. COM+0760. Clear Magnitude. COM+0760. Clear Accumulator. COMPIEMENT COMPIE | Accumulator Left Shift           | ALS-10767                   |

| Accumulator Right Shift. Backspace Taye. Clear and Add Logical Word. Compare Accumulator with Storage. CAS+0340 Change Sign. Clear and Add. Clear Magnitude. Clear and Add. Clear Magnitude. Clear and Subtract. Complement Magnitude. Clum+0760. Clear and Subtract. CLS+0502. Complement Magnitude. Clum+0760. Clear and Subtract. CLS+0502. Clown Horko. Complement Magnitude. Clum+0760. Clown Horko. Clum+0760. Clum+076 |                                  |                             |

| Compare Accumulator with Storage Change Sign. Clear and Add Clear and Add CLA+0500 Clear and Subtract Complement Magnitude CLS+0502 Complement Magnitude CDN+0760 . 0000 Divide Check Test DCT+0760 . 0012 Divide or Halt Divide or Proceed. ETM+0760 . 0012 Divide or Proceed. DVP+0221 Enter Trapping Mode Floating Divide or Halt Floating Divide or Proceed Froating Divide or Froceed Froating Subtract Froating Subtract Froating Subtract Froating Subtract Froating Subtract Froating Subtract Froating Divide or Proceed Halt and Proceed Halt and Transfer Halt and Transfer Load MQ Load MQ Logical Left Load MQ Logical Left Load MQ Logical Left Load MQ Logical Left Load Index from Address Load Index from Decrement Load Index from Decrement Multiply Multiply Multiply Multiply Mobility  | AND to Storage                   | ANS+0320                    |

| Compare Accumulator with Storage Change Sign. Clear and Add Clear and Add CLA+0500 Clear and Subtract Complement Magnitude CLS+0502 Complement Magnitude CDN+0760 . 0000 Divide Check Test DCT+0760 . 0012 Divide or Halt Divide or Proceed. ETM+0760 . 0012 Divide or Proceed. DVP+0221 Enter Trapping Mode Floating Divide or Halt Floating Divide or Proceed Froating Divide or Froceed Froating Subtract Froating Subtract Froating Subtract Froating Subtract Froating Subtract Froating Subtract Froating Divide or Proceed Halt and Proceed Halt and Transfer Halt and Transfer Load MQ Load MQ Logical Left Load MQ Logical Left Load MQ Logical Left Load MQ Logical Left Load Index from Address Load Index from Decrement Load Index from Decrement Multiply Multiply Multiply Multiply Mobility  | Reckspace Tope                   | ARS+0771<br>  BST±0784      |

| Compare Accumulator with Storage Change Sign. Clear and Add Clear and Add CLA+0500 Clear and Subtract Complement Magnitude CLS+0502 Complement Magnitude CDN+0760 . 0000 Divide Check Test DCT+0760 . 0012 Divide or Halt Divide or Proceed. ETM+0760 . 0012 Divide or Proceed. DVP+0221 Enter Trapping Mode Floating Divide or Halt Floating Divide or Proceed Froating Divide or Froceed Froating Subtract Froating Subtract Froating Subtract Froating Subtract Froating Subtract Froating Subtract Froating Divide or Proceed Halt and Proceed Halt and Transfer Halt and Transfer Load MQ Load MQ Logical Left Load MQ Logical Left Load MQ Logical Left Load MQ Logical Left Load Index from Address Load Index from Decrement Load Index from Decrement Multiply Multiply Multiply Multiply Mobility  | Clear and Add Logical Word       | CAL-0500                    |

| Clear And Add                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Compare Accuminator with Storage | CASTUMU                     |

| Clear and Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Change Sign                      | CHS+0760 0002               |

| Floating Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Clear Magnitude                  | CLM-4-0760 0000             |

| Floating Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Clear and Subtract               | CLS+0502                    |

| Floating Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Complement Magnitude             | COM+0760 0006               |

| Floating Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  | DCT+0760 0012<br>  DVH+0220 |

| Floating Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Divide or Proceed                | DVP+0221                    |

| Floating Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Enter Trapping Mode              | ETM+0760 0007               |

| Floating Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Floating Add                     | FAD+0300                    |

| Floating Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Floating Divide or Proceed       | FDP+0240                    |

| Floating Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Floating Multiply                | FMP+0260                    |

| Halt and Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Floating Subtract                | FSB+0302                    |

| Long Left Shift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Halt and Proceed                 | HPR+0420                    |